ADV11-A, KWV11-A, AAV11-A, DRV11 user's manual

digital equipment corporation • maynard, massachusetts

1st Edition, July 1976 2nd Printing (Rev) November 1976 3rd Printing (Rev) April 1977 Copyright © 1976, 1977 by Digital Equipment Corporation

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors which may appear in this manual.

Printed in U.S.A.

This document was set on DIGITAL's DECset-8000 computerized typesetting system.

The following are trademarks of Digital Equipment Corporation, Maynard, Massachusetts:

| DEC          | DECtape | PDP               |

|--------------|---------|-------------------|

| DECCOMM      | DECUS   | RSTS              |

| DECsystem-10 | DIGITAL | <b>TYPESET-8</b>  |

| DECSYSTEM-20 | MASSBUS | <b>TYPESET-11</b> |

|              |         | UNIBUS            |

# CONTENTS

# Page

10.001

| CHAPTER 1 | INTRODUCTION                                                |

|-----------|-------------------------------------------------------------|

| 1.1       | GENERAL                                                     |

| 1.2       | REFERENCES                                                  |

|           |                                                             |

| CHAPTER 2 | ADV11-A ANALOG-TO-DIGITAL CONVERTER                         |

| 2.1       | GENERAL DESCRIPTION                                         |

| 2.2       | SPECIFICATIONS 2-1                                          |

| 2.2.1     | Electrical                                                  |

| 2.2.2     | Coding                                                      |

| 2.2.3     | Performance                                                 |

| 2.2.4     | Timing                                                      |

| 2.2.5     | Test Signals                                                |

| 2.2.6     | Power Requirements                                          |

| 2.3       | FUNCTIONAL DESCRIPTION                                      |

| 2.3.1     | Channel Selection                                           |

| 2.3.2     | A/D Conversion $2-4$                                        |

| 2.3.3     | Interface Functions                                         |

| 2.3.4     | Control                                                     |

| 2.4       | USER INTERFACING                                            |

| 2.4.1     | Analog Inputs                                               |

| 2.4.1.1   | Single-Ended Mode                                           |

| 2.4.1.2   | Quasi-Differential Mode                                     |

| 2.4.2     | Avoiding Spurious Signals                                   |

| 2.4.2.1   | Twisted Pair Input Lines                                    |

| 2.4.2.2   | Shielded Input Lines                                        |

| 2.4.2.3   | Allowing for Input Settling with High Source Impedance 2-11 |

| 2.4.3     |                                                             |

|           | Connections                                                 |

| 2.4.3.1   | Distribution Panel                                          |

| 2.4.3.2   | External and Clock Starts                                   |

| 2.4.3.3   | Mode Control                                                |

| 2.4.4     | Vector and Address Selection                                |

| 2.5       | PROGRAMMING                                                 |

| 2.5.1     | Control/Status Register (CSR)                               |

| 2.5.2     | Data Buffer Register (DBR) 2-16                             |

| 2.5.3     | Programming Example                                         |

| CHAPTER 3 | KWV11-A PROGRAMMABLE REAL-TIME CLOCK                        |

| 3.1       | GENERAL DESCRIPTION                                         |

| 3.2       | SPECIFICATIONS                                              |

| 3.2.1     | Clock                                                       |

| 3.2.2     | Input and Output Signals                                    |

| 3.2.2.1   | Input Signals                                               |

| 3.2.2.2   | Output Signals                                              |

| 3.2.2.3   | Power Requirements (from LSI-11 Bus Power Supply)           |

| 5.4.4.5   | 10  were requirements (nom LSI-11 Bus rower suppry) 3-3'    |

o

# CONTENTS (Cont)

I

¢

|           |                                                                | Page |

|-----------|----------------------------------------------------------------|------|

| 3.3       | FUNCTIONAL DESCRIPTION                                         | 3-3  |

| 3.3.1     | Bus Control                                                    | 3-3  |

| 3.3.2     | Control/Status Register                                        |      |

| 3.3.3     | Mode Control                                                   |      |

| 3.3.3.1   | Mode 0 (Single Interval)                                       |      |

| 3.3.3.2   | Mode 1 (Repeated Interval)                                     |      |

| 3.3.3.3   | Mode 2 (External Event Timing)                                 |      |

| 3.3.3.4   | Mode 3 (External Event Timing from Zero Base)                  |      |

| 3.3.3.5   | Flag Overrun                                                   |      |

| 3.3.4     | Oscillator, Divider, Rate Control Chain                        |      |

| 3.3.5     | Buffer/Preset and Counter Registers                            |      |

| 3.3.6     | Schmitt Triggers                                               |      |

| 3.4       | CONNECTORS, SWITCHES, AND CONTROLS                             | 3-6  |

| 3.4.1     | 40-Pin Connector                                               |      |

| 3.4.2     | FAST ON Connectors (Clock Overflow and ST1 Outputs)            |      |

| 3.4.3     | Selector Switches (Address, Vector, and Slope/Reference Level) |      |

| 3.4.3.1   | Address Selection                                              |      |

| 3.4.3.2   | Vector Selection                                               |      |

| 3.4.3.3   | Slope and Reference Level Selector Switches and Controls       |      |

| 3.5       | PROGRAMMING                                                    |      |

| 3.5.1     | CSR Bit Assignments                                            |      |

| 3.5.2     | Buffer/Preset Register (BPR)                                   |      |

| 3.5.3     | Normal Control Sequences                                       |      |

| 3.5.3.1   | Mode 0 (Single Interval)                                       |      |

| 3.5.3.2   | Mode 1 (Repeated Interval)                                     |      |

| 3.5.3.3   | Mode 2 (External Event Timing)                                 |      |

| 3.5.3.4   | Mode 3 (External Event Timing from Zero Base)                  |      |

| 3.5.4     | Programming Example                                            |      |

| CHAPTER 4 | AAV11-A DIGITAL-TO-ANALOG CONVERTER                            |      |

| 4.1       | GENERAL DESCRIPTION                                            | 4-1  |

| 4.2       | SPECIFICATIONS                                                 |      |

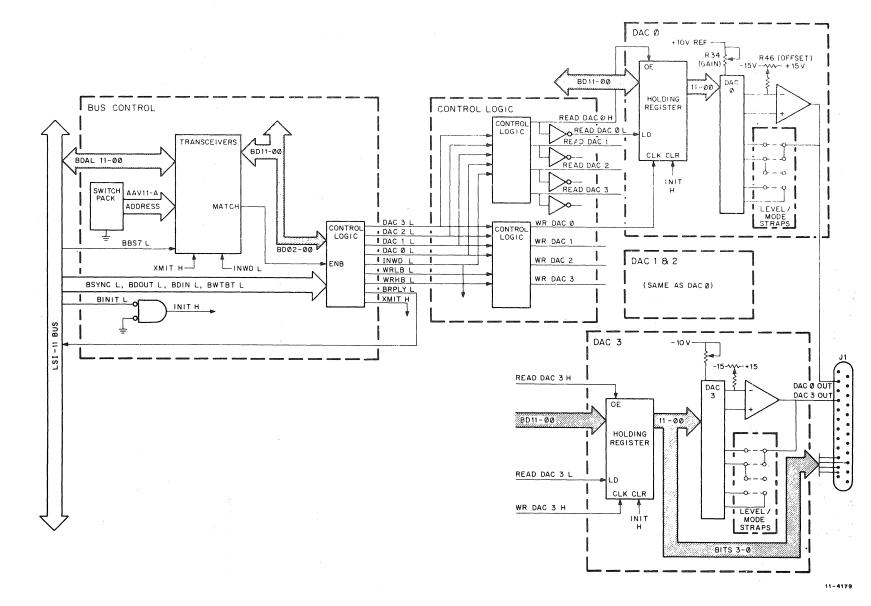

| 4.3       | FUNCTIONAL DESCRIPTION                                         | 4-2  |

| 4.3.1     | Bus Control                                                    | 4-2  |

| 4.3.2     | Control Logic                                                  | 4-2  |

| 4.3.3     | DACs 0, 1, and 2                                               | 4-2  |

| 4.3.4     | DAC 3                                                          |      |

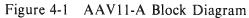

| 4.4       | CONNECTORS, SWITCHES, AND CONTROLS                             | 4-4  |

| 4.4.1     | 40-Pin Connector                                               | 4-4  |

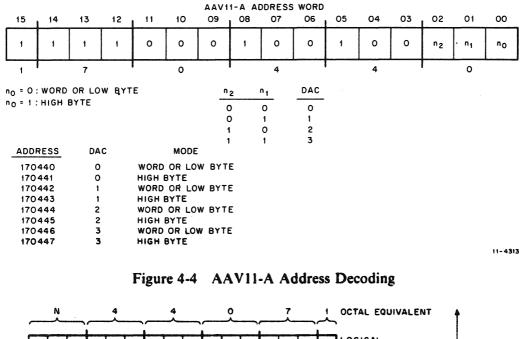

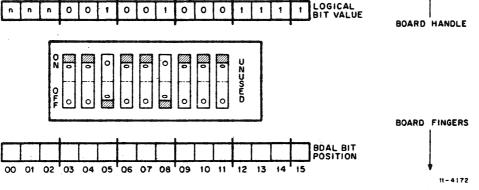

| 4.4.2     | Address Switches                                               | 4-5  |

| 4.4.3     | Mode/Level Selector Jumpers                                    | 4-6  |

| 4.5       | INTERFACING TO OUTPUT DEVICES                                  | 4-6  |

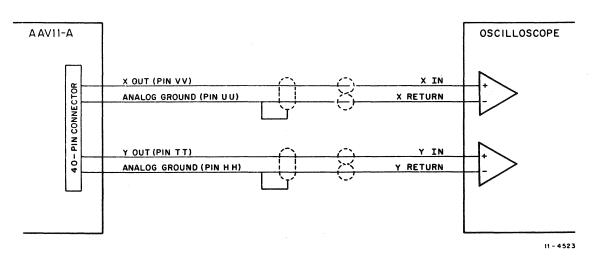

| 4.5.1     | Ground Connections                                             | 4-6  |

| 4.5.2     | Twisting                                                       |      |

# CONTENTS (Cont)

|           |                                                                                                             | Page   |

|-----------|-------------------------------------------------------------------------------------------------------------|--------|

| 4.5.3     | Shielding                                                                                                   | . 4-7  |

| 4.5.4     | Drive Capability                                                                                            |        |

| 4.6       | PROGRAMMING                                                                                                 |        |

| 4.0       |                                                                                                             | . +-/  |

| CHAPTER 5 | DRV11 PARALLEL LINE UNIT                                                                                    | ·      |

| 5.1       | GENERAL DESCRIPTION                                                                                         | . 5-1  |

| 5.2       | JUMPER-SELECTED ADDRESSING AND VECTORS                                                                      | . 5-1  |

| 5.2.1     | Locations                                                                                                   | . 5-1  |

| 5.2.2     | Addressing                                                                                                  | . 5-2  |

| 5.2.3     | Vectors                                                                                                     | . 5-2  |

| 5.3       | INTERFACING TO THE USER'S DEVICE                                                                            | . 5-3  |

| 5.3.1     | General                                                                                                     | . 5-3. |

| 5.3.2     | Output Data Interface                                                                                       | . 5-3  |

| 5.3.3     | Input Data Interface                                                                                        | . 5-5  |

| 5.3.4     | Request Flags                                                                                               | . 5-5  |

| 5.3.5     | Initialization                                                                                              | . 5-6  |

| 5.3.6     | NEW DATA READY and DATA TRANSMITTED Pulse                                                                   |        |

|           | Width Modification                                                                                          | . 5-6  |

| 5.4       | PROGRAMMING                                                                                                 | . 5-6  |

| 5.4.1     | Addressing                                                                                                  | . 5-6  |

| 5.4.2     | Interrupt Vectors                                                                                           | . 5-7  |

| 5.4.3     | Word Formats                                                                                                | . 5-7  |

| 5.4.4     | I/O Timing                                                                                                  | . 5-7  |

|           |                                                                                                             |        |

| CHAPTER 6 | ADV11-A, KWV11-A, and AAV11-A MAINTENANCE                                                                   |        |

| 6.1       | MAINTENANCE PHILOSOPHY                                                                                      |        |

| 6.2       | ADV11-A ANALOG-TO-DIGITAL CONVERTER                                                                         |        |

| 6.2.1     | Installation                                                                                                |        |

| 6.2.1.1   | Location                                                                                                    |        |

| 6.2.1.2   | Address and Vector Selection                                                                                |        |

| 6.2.1.3   | Board Insertion                                                                                             |        |

| 6.2.1.4   | Test Connector                                                                                              | . 6-1  |

| 6.2.1.5   | Shields                                                                                                     |        |

| 6.2.1.6   | Acceptance                                                                                                  |        |

| 6.2.1.7   | Final Connections                                                                                           |        |

| 6.2.2     | ADV11-A Circuitry $\ldots$ |        |

| 6.2.2.1   | ADV11-A Analog Power Supply                                                                                 |        |

| 6.2.2.2   | ADV11-A A/D Conversion Circuit                                                                              |        |

| 6.2.2.3   | The Vernier DAC                                                                                             |        |

| 6.2.3     | ADV11-A Performance Test (MAINDEC-11-DVADA-A)                                                               |        |

| 6.2.4     | Maintenance                                                                                                 |        |

| 6.2.5     | Calibration                                                                                                 |        |

| 6.3       | KWV11-A REAL TIME CLOCK                                                                                     | . 6-10 |

| 6.3.1     | Installation                                                                                                | . 6-10 |

| 6.3.1.1   | Location                                                                                                    | . 6-10 |

C

## **CONTENTS** (Cont)

### Page

2-5

2-7

2-8

2-9

3-2

3-4

| 6.3.1.2          | Address and Vector Selection                      |

|------------------|---------------------------------------------------|

| 6.3.1.3          | Board Insertion                                   |

| 6.3.1.4          | Test Connections                                  |

| 6.3.1.5          | Acceptance                                        |

| 6.3.2            | Final Connections                                 |

| 6.3.3            | KWV11-A Circuitry                                 |

| 6.3.4            | KWV11-A Diagnostic (MAINDEC-11-DVKWA-A-D) 6-11    |

| 6.3.5            | Maintenance                                       |

| 6.4              | AAV11-A DIGITAL-TO-ANALOG CONVERTER               |

| 6.4.1            | Installation                                      |

| 6.4.1.1          | Location                                          |

| 6.4.1.2          | Address Selection                                 |

| 6.4.1.3          | Board Insertion                                   |

| 6.4.1.4          | Test Connectors                                   |

| 6.4.1.5          | Acceptance Test                                   |

| 6.4.2            | Final Connections                                 |

| 6.4.3            | Mode/Level Selection                              |

| 6.4.4            | AAV11-A Circuitry                                 |

| 6.4.4.1          | AAV11-A Analog Power Supply                       |

| 6.4 <b>,</b> 4.2 | Digital-to-Analog Circuits                        |

| 6.4.5            | AAV11-A Diagnostic Test (MAINDEC-11-DVAAA-A) 6-14 |

| 6.4.6            | Maintenance                                       |

| 6.4.7            | Calibration                                       |

|                  |                                                   |

## **ILLUSTRATIONS**

#### Figure No. Title Page 2-1 ADV11-A Functional Block Diagram 2-2 Single-Ended Input Referenced to User's Ground 2-3 2-4 Single-Ended Versus True Differential Input Modes 2-5 ADV11-A Quasi-Differential Mode 2-6 2-7 2-8 2-9 2-10 ADV11-A Address and Vector Switches (Rocker or Slide Switches) 2-11 2-12 ADV11-A Data Buffer Register (DBR) 3-1 KWV11-A Connectors, Switches, and Controls 3-2 KWV11-A Real-Time Clock Block Diagram

# ILLUSTRATIONS (Cont)

| Figure No. | Title                                                                                                                                      | Page   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 3-3        | Connecting External User-Supplied Slope and Level Controls                                                                                 | . 3-6  |

| 3-4        | 40-Pin Connector Pin Assignments                                                                                                           |        |

| 3-5        | KWV11-A CSR Address Switches (Set for 170420)                                                                                              | . 3-7  |

| 3-6        | KWV11-A Vector Address Switches (Set for 000440)                                                                                           | . 3-8  |

| 3-7        | KWV11-A Slope/Reference Level Selector Switches and Controls                                                                               | . 3-9  |

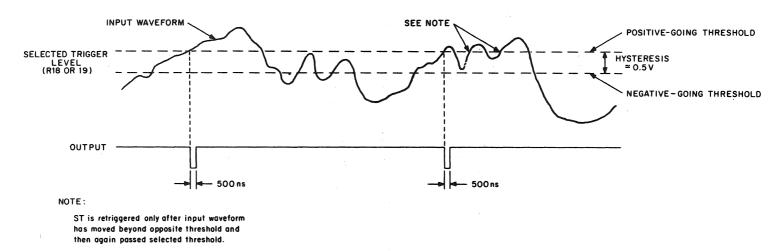

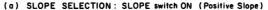

| 3-8        | KWV11-A Slope Selection                                                                                                                    | . 3-10 |

| 3-9        | CSR Bit Assignments                                                                                                                        | . 3-13 |

| 4-1        | AAV11-A Block Diagram                                                                                                                      | . 4-3  |

| 4-2        | AAV11-A Connectors, Switches, and Controls                                                                                                 | . 4-4  |

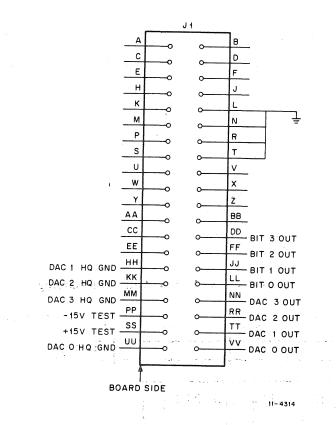

| 4-3        | 40-Pin Connector Pin Assignments                                                                                                           | . 4-5  |

| 4-4        | AAV11-A Address Decoding                                                                                                                   |        |

| 4-5        | AAV11-A Address Switches (Set for 17044n)                                                                                                  | . 4-6  |

| 4-6        | Connection to Oscilloscope with Differential Input                                                                                         |        |

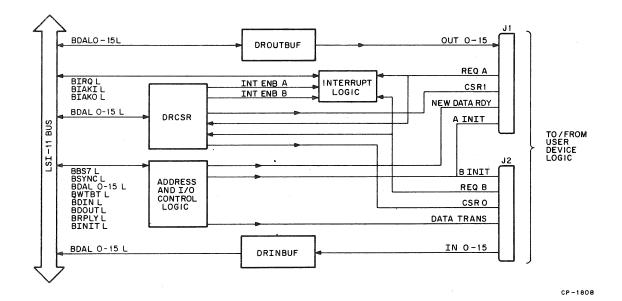

| 5-1        | DRV11 Parallel Line Unit ·                                                                                                                 | . 5-1  |

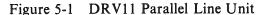

| 5-2        | DRV11 Jumper Locations                                                                                                                     |        |

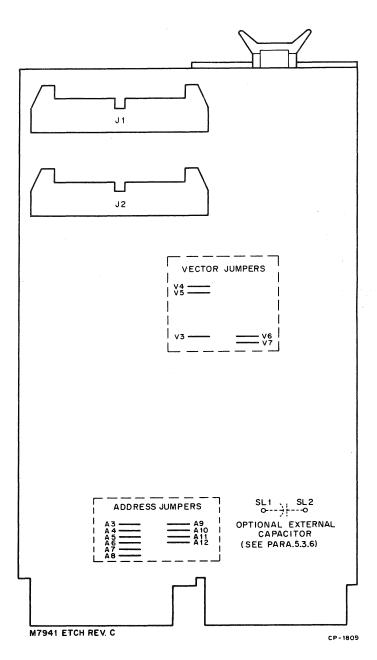

| 5-3        | DRV11 Device Address                                                                                                                       | . 5-3  |

| 5-4        | DRV11 Vector Address                                                                                                                       | . 5-3  |

| 5-5        | J1 or J2 Connector Pin Locations                                                                                                           | . 5-4  |

| 5-6        | DRV11 Word Formats                                                                                                                         |        |

| 5-7        | DRV11 Interface Signal Sequence                                                                                                            |        |

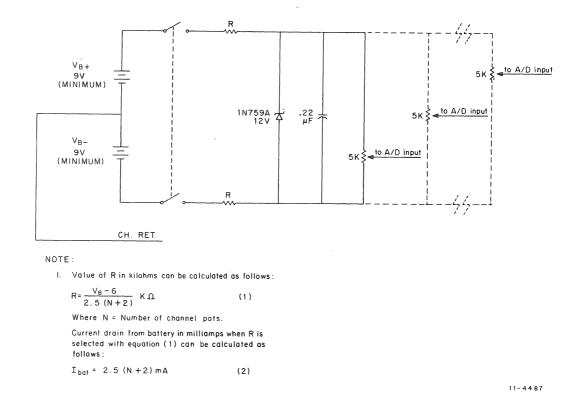

| 6-1        | Battery-Operated Potentiometer Box for ADV11-A A/D Converter                                                                               |        |

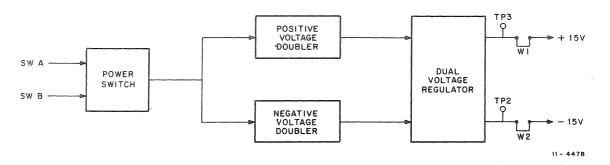

| 6-2        | Analog Power Supply Block Diagram                                                                                                          |        |

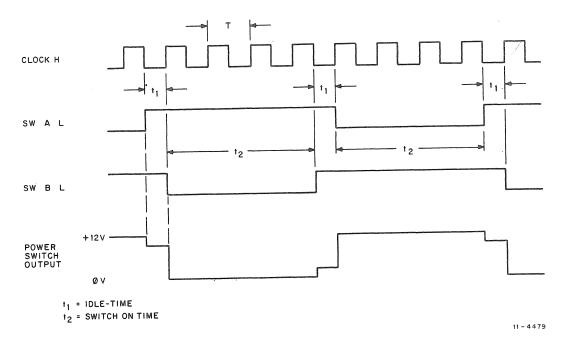

| 6-3        | DC-DC Converter Signals                                                                                                                    |        |

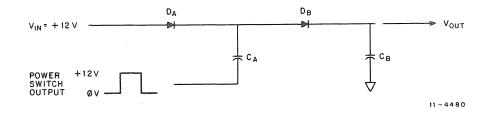

| 6-4        | Basic Positive Voltage Doubler                                                                                                             |        |

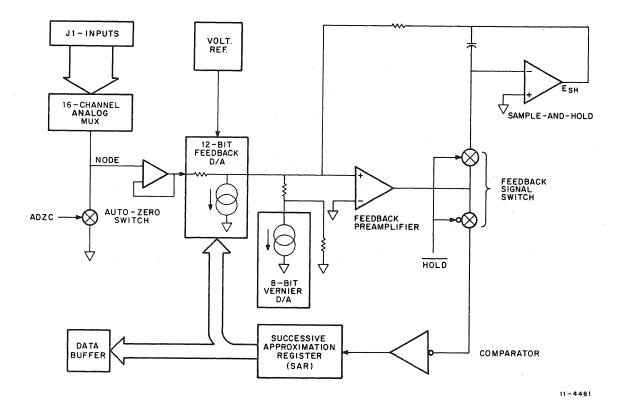

| 6-5        | ADV11-A A/D Conversion Circuit Block Diagram                                                                                               | . 6-5  |

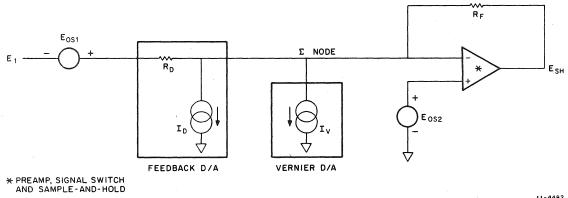

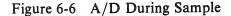

| 6-6        | A/D During Sample                                                                                                                          | . 6-5  |

| 6-7        | A/D During Conversion                                                                                                                      | . 6-6  |

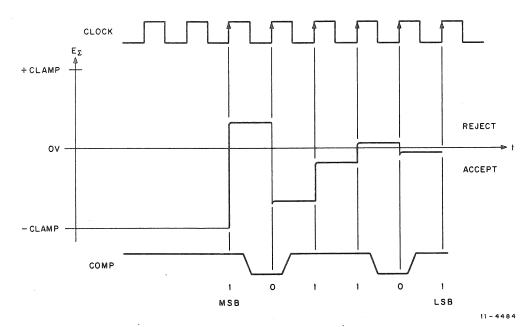

| 6-8        | $\Sigma$ Node During Conversion $\ldots \ldots \ldots$ | . 6-7  |

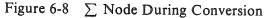

| 6-9        | ADV11-A Troubleshooting Procedure                                                                                                          | . 6-9  |

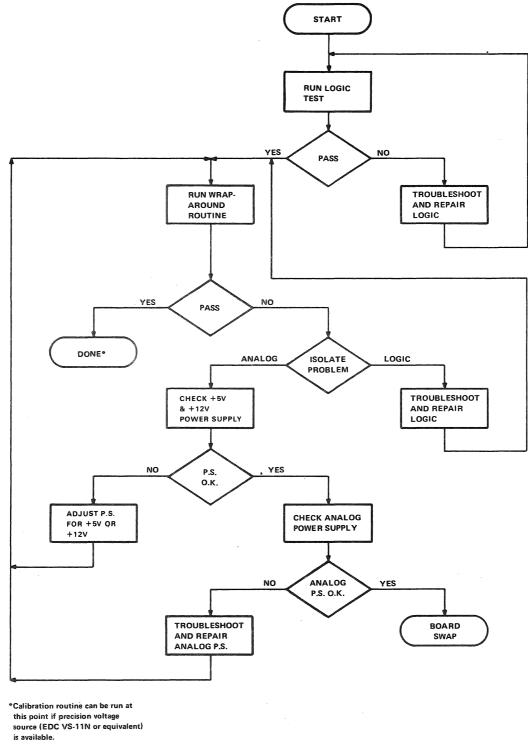

| 6-10       | AAV11-A Troubleshooting Procedure                                                                                                          | . 6-15 |

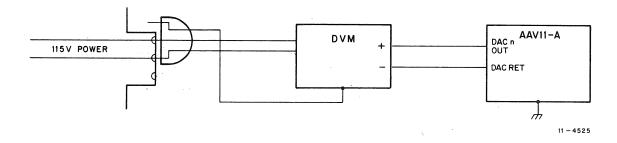

| 6-11       | Floating the DVM                                                                                                                           | . 6-16 |

## TABLES

## Table No.

. 1

## Title

Page

| 3-1 | KWV11-A CSR Bit Definitions                             |

|-----|---------------------------------------------------------|

| 3-2 | CSR Bit Settings for Mode 0, Single Interval            |

| 3-3 | CSR Bit Settings for Mode 1, Repeated Interval          |

| 3-4 | CSR Bit Settings for Mode 2, External Event Timing 3-16 |

| 4-1 | AAV11-A Digital-to-Analog Conversions                   |

| 5-1 | DRV11 Input and Output Signal Pins                      |

| 5-2 | Word Formats                                            |

# TABLES (Cont)

| Table No.                | Title                                     | Page             |

|--------------------------|-------------------------------------------|------------------|

| 6-1<br>6-2<br>6-3<br>6-4 | ADV11-A Voltage/Current/Bit Relationships | . 6-12<br>. 6-13 |

# CHAPTER 1 INTRODUCTION

#### **1.1 GENERAL**

This manual contains information necessary for the operation, installation, and maintenance of the family of real-time analog and digital I/O devices which DEC provides as options for the LSI-11 Processor, i.e., the ADV11-A Analog-to-Digital Converter, the KWV11-A Real-Time Clock, the AAV11-A Digital-to-Analog Converter, and the DRV11 Parallel Line Interface. Operating information for each device is provided in a chapter specific to that device which includes functional description, specifications, theory of operation, and programming background. Installation and maintenance information is provided for all units in Chapter 6.

All members of the LSI-11 real-time I/O family are designed to interface between the processor and analog or digital signals in the world external to the processor. All devices are configured on one quad or double-height board designed to mount in an LSI-11 backplane or expander box and to receive power from LSI-11 supplies. All communicate with the LSI-11 bus and receive interrupt priority as a function of their location in the backplane. Finally, all have facilities to permit users to assign device addresses, and where appropriate, interrupt vector locations.

A number of recommendations are made in this text regarding specific interfacing configurations and general good practice. However, no specific interfacing claims are made over and above those expressed in the general specifications for each module. The responsibility for connecting DEC modules to external equipment rests ultimately with the user.

#### **1.2 REFERENCES**

• Microcomputer Handbook (EB-06583 76 09/53)

• LSI-11 Bus Specification

1-1

# CHAPTER 2 ADV11-A ANALOG-TO-DIGITAL CONVERTER

### 2.1 GENERAL DESCRIPTION

The ADV11-A is a 12-bit successive-approximation analog-to-digital converter with built-in multiplexer and sample-and-hold for use on the LSI-11 bus. The multiplexer section accommodates 16 single-ended or 8 quasi-differential inputs, and the converter section utilizes a patented auto-zeroing design that measures the sampled signal with respect to the offset of its own internal circuitry and thus effectively cancels out its own offset error contributions to the measurement.

A/D conversions are initiated either by program command, clock overflow, or external events as determined by program control of the ADV11-A's Control/Status Register (CSR). The clock overflow command is supplied by the KWV11-A clock option. External event inputs may originate directly from user equipment or from the Schmitt trigger output on the KWV11-A clock. Digital A/D conversion data is routed through a buffer register to the LSI-11 for programmed transfer into memory. This buffering optimizes the throughput rate of the converter by allowing data from one conversion to be transferred to the processor after a subsequent conversion begins.

A vernier offset digital-to-analog converter is included in the ADV11-A's analog circuitry to facilitate very accurate program-controlled trimming of the A/D's offset. Three test signals – two dc levels and one bipolar triangular waveform – are available for use on any channel input. The triangular wave can be used in conjunction with diagnostic software and the vernier DAC to produce extremely thorough and precise analog testing.

### 2.2 SPECIFICATIONS

2.2.1 Electrical (@ 25° C unless otherwise specified)

#### Inputs

Analog Input Protection

Fusible resistor guaranteed to open at  $\pm 85$  V within 6.25 seconds. Guaranteed not to open from -20 V to +15 V at the input. Overload affects no components other than the fusible resistor on the overloaded channel; no other channels are affected.

Logic Input Protection

Fusible resistor guaranteed to open at  $\pm$  25 V within 6.25 seconds. Guaranteed not to open from -3 V to +8 V at the input.

Analog Input Full Scale Range (FSR) 10.24 V bipolar (-5.12 V to +5.12 V)

# Inputs (Cont)

| Analog Input<br>Dynamic Resistance<br>$(/Vin/ \leq 5.12 V)$ | 100 MΩ, minimum                            |                                                      |

|-------------------------------------------------------------|--------------------------------------------|------------------------------------------------------|

| Analog Input Bias Current $(/Vin/ \leq 5.12 \text{ V})$     | 50 nA, maximum                             |                                                      |

| Logic Input Voltages                                        | $Low = 0.0 \text{ to } +0.7 \text{ V}_{2}$ | ; high = $+2$ V to $+5$ V                            |

| Logic Input Currents                                        | Low = -6.8  mA at  0                       | V in.; high = $+1.3$ mA at $+5$ V in                 |

| Logic Input Rise/Fall Time                                  | 400 ns, maximum                            |                                                      |

| 2.2.2 Coding                                                |                                            |                                                      |

| A/D Converter                                               |                                            |                                                      |

| Resolution                                                  | 12 bits, binary weighte                    | ed                                                   |

| Format                                                      | Parallel offset binary,                    | right justified                                      |

|                                                             | Input Voltage                              | Output Code                                          |

| · .                                                         | +FS-1 LSB<br>0<br>-FS                      | 7777<br>4000<br>0                                    |

|                                                             |                                            | (FS = 5.12 V; 1 LSB = 2.5 mV)                        |

| Vernier D/A                                                 |                                            |                                                      |

| Resolution                                                  | 8 bits, binary weighted                    | 1                                                    |

| Format                                                      | Offset binary encoded                      |                                                      |

|                                                             | Input Code<br>377<br>200                   | Approximate Offset Voltage<br>+2.5 A/D LSB (+6.4 mV) |

|                                                             | 0                                          | -2.5 A/D LSB (-6.4 mV)                               |

| 2.2.3 Performance                                           |                                            |                                                      |

| Gain Error                                                  | Adjustable to zero                         |                                                      |

| Offset Error                                                | Adjustable to zero                         |                                                      |

| Differential Linearity                                      | No skipped states; no widths $\pm 1/2$ LSB | states wider than 2 LSB. 99% of state-               |

| Integral Linearity                                          | ±1 LSB, maximum no                         | on-linearity (referenced to end points)              |

**Performance** (Cont)

| Temperature Coefficients | Gain = 6 ppm per degree C<br>Linearity = 2 ppm of full-scale range per degree C<br>Offset = 7.5 ppm of full-scale range per degree C |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Noise                    | Module = 0.4 LSB rms; 2 LSB peak<br>System = 1/2 LSB rms; 2 LSB peak                                                                 |

| Warm-Up Time             | 5 minutes, maximum                                                                                                                   |

| 2.2.4 Timing             |                                                                                                                                      |

| External Start           | Low level pulse, 50 ns minimum to 10 $\mu$ s maximum; conversion starts on leading edge                                              |

| Synchronization          | 0 to T                                                                                                                               |

| Conversion Time          | 16T<br>(T = clock period = 2.14 $\mu$ s ± 6%)                                                                                        |

| Transition Interval*     | $9 \ \mu s \ \pm \ 12\%$                                                                                                             |

| Sample and Hold          | Aperture Delay = 200 ns<br>Aperture Uncertainty = 2 ns                                                                               |

#### 2.2.5 Test Signals

The ADV11-A provides three output voltages for test purposes:

- 1. Positive dc level,  $+4.4 \text{ V} (\pm 15\%)$

- 2: Negative dc level,  $-4.4 \text{ V} (\pm 15\%)$

- 3. Triangular wave, 15 Hz nominal  $(\pm 15\%)$

2.2.6 Environmental (Ref: DEC STD 102, class B)

#### 2.2.7 Power Requirements

+5 Vdc ±5% @2.0 A, maximum +12 Vdc ±3% @450 mA, maximum

## **2.3** FUNCTIONAL DESCRIPTION

The ADV11-A performs its function in seven successive steps:

- 1. It enables the specified channel.

- 2. It samples 1 of 16 single-ended (or 1 of 8 differential) analog input channels specified by the control program long enough to acquire a reliable internal reference equivalent.

- 3. It accepts a command to perform an A/D conversion.

- 4. It holds the sampled reference equivalent during 12 successive interrogation intervals.

\*Reacquisition interval between end of conversion or channel change and start of new conversion.

- 5. When the least significant bit has been resolved in the Successive Approximation Register (SAR), the ADV11-A transfers the contents of the now-filled SAR to the DATA Buffer Register (DBR) where that data can be accessed by the processor.

- 6. It informs the processor that conversion data is available.

- 7. It reacquires and tracks the programmed channel.

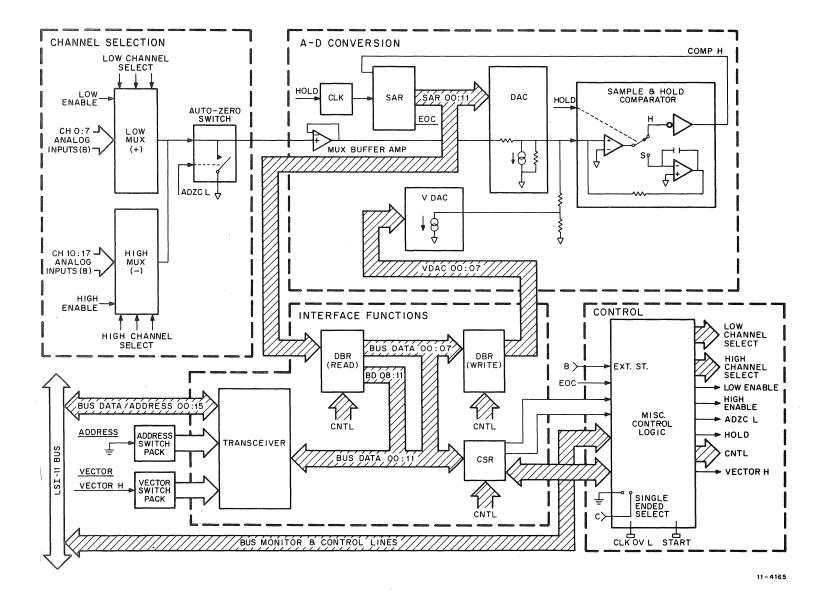

These steps are implemented in the ADV11-A by components that can be grouped together in four functional categories:

- 1. Channel selection

- 2. A/D conversion

- 3. Processor/ADV11-A interface

- 4. Control logic that coordinates the above steps with respect to one another and to the needs of the processor.

These categories are discussed below.

#### 2.3.1 Channel Selection

Channel selection is accomplished under program control by two 8-channel multiplexers and is a function of the data asserted in bits 8 through 11 of the Control/Status Register (CSR). Each of the 16 analog input channels is routed to the single output channel through a MOS field-effect transistor which acts as a normally-open switch. During the sample interval, the data pattern in CSR bits 8 through 11 selects one of these transistors and causes it to change from a condition of nearly infinite resistance (1 G $\Omega$  or more) to one of very low resistance (1000  $\Omega$  or less). Since in the selected state the transistor conducts current within the ±5.12 V limits equally well in both directions, it now functions as a closed switch, effectively routing to the output line whatever analog signal is connected to its input.

#### 2.3.2 A/D Conversion

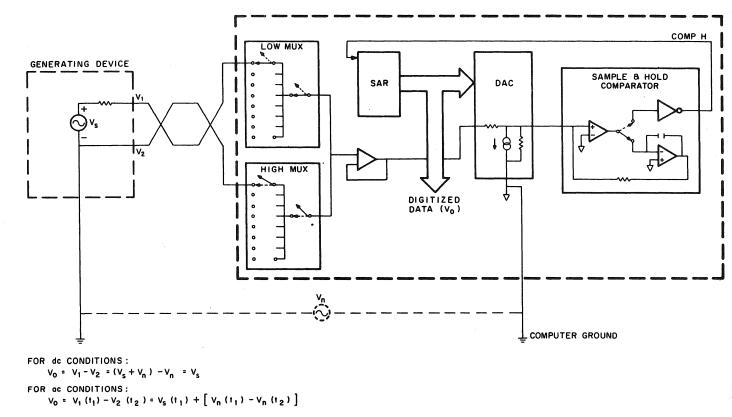

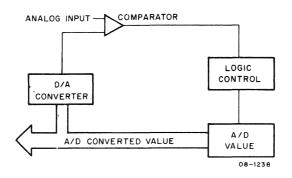

A/D conversions can be initiated in three ways: under program control, on overflow from the KWV11-A Real-Time Clock, or on external input. When a conversion is completed or the control program writes a multiplexer address into the CSR, the control logic initiates the Transition Interval – a delay of about 9  $\mu$ s to allow the multiplexer adequate selection and settling time and to permit a valid representation of the signal level to be established in the sample circuit. If no A/D Start signal has occurred by the time the Transition Interval has elapsed, the sample circuit merely follows the signal transmitted to it through the selected multiplexer channel and waits for an A/D Start signal. When an A/D Start signal occurs – or at the end of the Transition Interval if A/D Start was previously generated by the writing of the CSR GO bit - the sample and hold circuits are switched to hold, sustaining the sampled level for the next step. The multiplexer output is then set to its hold condition, i.e., to ground if the single-ended (S.E.) input is set low for single-ended measurement, to the second differental input (return line) if the S.E. input is not set low. Note that if an external or clock start signal occurs during the Transition Interval, conversion starts immediately without waiting for the Transition Interval to be completed. Bit 15 of the CSR (AD ERROR) is set, however, and an interrupt is generated if bit 14 (error interrupt enable) is set - alerting the program that conversions are occurring too fast and are consequently liable to be in error.

6 3 r

11121

Figure 2-1 ADV11-A Functional Block Diagram

2-5

ø 5 F . -

Under normal conditions, it is not until the Transition Interval is complete that the measurement process is begun. The Successive Approximation Register (SAR) is cycled through 13 states by the clock. In the first state its output code involves only the most significant bit (MSB) of the 12-bit SAR word. This output code causes the feedback digital-to-analog converter (DAC) to generate an output equivalent to that produced by the hold circuits in response to a sample voltage of 0. The DAC output is summed with that produced by the hold circuits and with that coming from the grounded multiplexer output (single-ended mode) or from the second differential input (quasi-differential mode). If the current from the summing node is negative, the first approximation was too low, and the comparator signals the SAR to maintain the state of bit 11 and repeat the process with bit 10. If the current from the summing node is positive, the first approximation was too high and the SAR changes the state of bit 11 before cycling into the second approximation. This process continues until all 12 bits in the word have been set, tested, and if necessary, changed. The 13th state (end of conversion, or EOC) indicates that the measurement is complete and that the SAR now contains an offset binary equivalent of the sampled voltage and may therefore be transfered to the processor. EOC causes the sample and hold circuits to return to the sample mode and to reset the SAR, preventing further SAR activity until the occurrence of the next hold condition.

Note that because the reference point against which the sample voltage is compared is at the output of the multiplexer itself rather than internal to the sample and hold circuits, all offset voltages generated by the intervening circuits are common to both sample and hold conditions and are therefore cancelled out of any measurement. In single-ended mode, grounding the multiplexer output (and thereby establishing this reference point) is identified as auto-zeroing the converter.

## 2.3.3 Interface Functions

In addition to stopping the SAR clock and reestablishing the sample mode, the end-of-conversion signal also initiates the process that causes the SAR data to be transferred to the processor. Since this operation takes a finite amount of time which would interfere with subsequent measuring operations, the SAR data is first transferred to a holding device, the Data Buffer Register (DBR), where it will remain until the processor can be notified to read the conversion data for processing. In the meantime, the channel selection and A/D conversion circuits can begin the next measurement as dictated by Control/Status Register (CSR) bit conditions controlled by the processor.

Included in the ADV11-A interface is an extension of the DBR designed to accept 8-bit write information from the BUS DATA/ADDRESS lines. This buffer permits programmed setting of the Vernier DAC (see Paragraph 6.2.2.3). Also included are transceivers that connect the bi-directional BUS DATA lines to the LSI-11 Bus DATA/ADDRESS lines. Associated with these transceivers are switches that permit assigning device and vector addresses to any given ADV11-A.

### 2.3.4 Control

As the above discussion suggests, a large number of signals must be precisely orchestrated each time the ADV11-A executes a conversion. The control logic contains an assortment of gates, latches, readonly memories, and timing circuits designed to assure that multiplexer channels are properly selected, sample durations are of adequate length, conversions are not initiated during uncompleted previous conversions, etc. In general, this logic precludes the need for the user to attend to any but the mostelementary details of the conversion process, e.g., making necessary connections to the system and writing control programs that make appropriate use of the CSR.

#### 2.4 USER INTERFACING

## 2.4.1 Analog Inputs

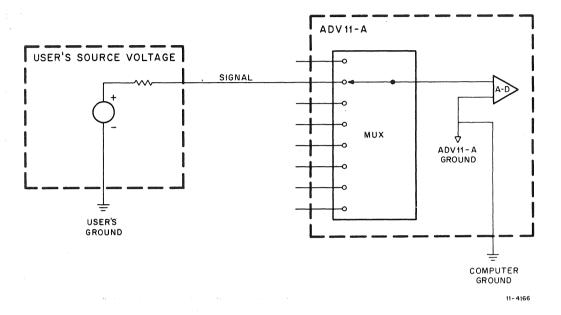

2.4.1.1 Single-Ended Mode\* – Single-ended analog input signals for the ADVV11-A may be of two types, grounded and floating. A grounded input is one whose level is referenced to the ground of the instrument that is producing it, as illustrated in Figure 2-2. Since the instrument may be located at a

<sup>\*</sup>The ADV11-A is factory-set for differential mode. Single-ended mode must be selected as described in Paragraph 2.4.3.3.

distance from the computer, there may be some voltage difference between the instrument ground and the computer ground. The voltage seen by the ADV11-A will be the sum of the undesired ground difference voltage and the desired instrument signal voltage. In cases where such differences are encountered, they can be minimized by plugging the instrument into an ac outlet as close as possible to that providing power to the computer. Do *not* run a wire from user's ground to the ADV11-A analog ground. Such a wire can cause ground loop currents which affect results not only on the input channel in question, but also on other channels.

Figure 2-2 Single-Ended Input Referenced to User's Ground

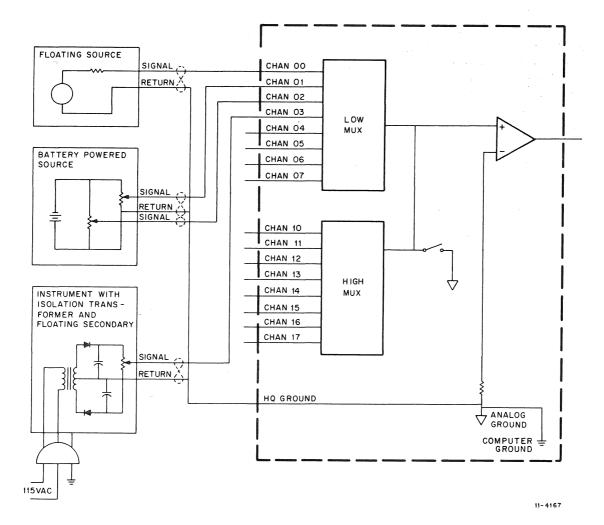

A floating input is one whose signal voltage is developed with respect to a point not connected to ground, as illustrated in Figure 2-3. The identifying characteristic of a floating source is that connecting the signal return to the ADV11-A ground does not result in a current path between the ADV11-A ground and the instrument ground.

Note that the return of a floating input must be connected to one of the ADV11-A's analog ground terminals (see Figure 2-3). Ground points may be shared among channels, as illustrated by the battery-powered sources in Figure 2-3.

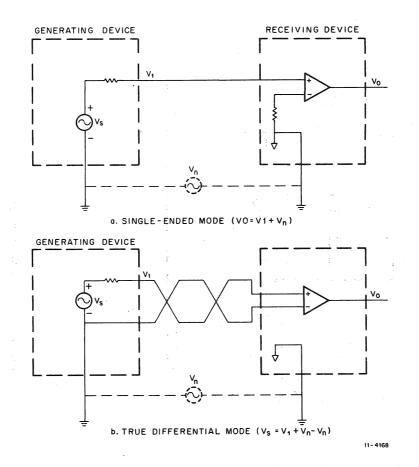

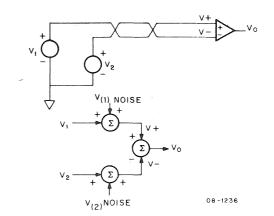

**2.4.1.2** Quasi-Differential Mode – The "quasi" prefix in "quasi-differential" can best be explained in the context of a preliminary review of true differential operation. A true differential input involves two signal lines connected to a differential amplifier in such a way that the output of the device is a function of the instantaneous *difference* between the voltages on the two signal lines. One advantage of such a configuration is illustrated in Figure 2-4.

Figure 2-4(a) assumes a single-ended generating device that produces a signal,  $V_s$ , with respect to its ground and is situated sufficiently far from the receiving device for a significant noise voltage,  $V_n$ , to be developed in the power distribution ground lines. The result is that, at any given instant, the differential amplifier in the receiving device sees both the signal voltage and the noise voltage. Its output,  $V_o$ , is a function of  $V_s + V_n$  and is in error with respect to  $V_s$  alone.

Figure 2-3 Floating ADV11-A Input Signals

Figure 2-4(b) illustrates the same device connected in true differential mode. The same noise voltage exists in the power distribution ground system, but this time the generating device ground is connected directly to the negative input of the receiving differential amplifier. Since the instantaneous noise voltage is common to both the + and the – inputs, it is cancelled out of the final amplifier output.  $V_0$  now provides a valid representation of  $V_s$  alone.

Figure 2-5 illustrates the ADV11-A operating in the quasi-differential mode.

The major contrast between true differential operation as described above and the operation of the ADV11-A in differential mode is that in the latter, the two sides of the signal are not simultaneously input to a differential amplifier. Rather, their difference is established by a sequential operation that first samples the voltage at one of the two inputs and then, holding this value fixed, in effect subtracts from it the voltage at the second input. For near dc conditions, this procedure produces a result like that of true differential operation – that is, the output is a function of the difference between the two input voltages, and common mode voltages are cancelled out. But, since there is a significant time lapse between taking the sample and completing the final approximation, a possibility for error is introduced by the ADV11-A that increases as a function of common mode signal frequency. The result

is that the common mode rejection ratio, while essentially infinite at dc, rolls off for ac signals, and is about 40 dB at 60 Hz line frequency. In addition, since the holding action of the sample-and-hold circuit is only in effect on the first (non-inverting, signal) input but not on the second (inverting, return) input, the voltage rate of change on the second input should be kept below 25 mV/ms. This is the slope that results in a quarter-LSB change during the conversion interval. Such a rate of change corresponds to 125 mV peak-to-peak at 60 Hz line frequency. This dynamic response difference between the two inputs requires us to distinguish the ADV11-A's differential mode from true differential operation. Hence the term "quasi-differential."

Figure 2-4 Single-Ended Versus True Differential Input Modes

#### 2.4.2 Avoiding Spurious Signals

As a preliminary step, confirm that the computer power supply ground is connected to power line (earth) ground. If continuity checks reveal no such connection, attach a length of 12-gauge wire between the power supply ground and a convenient point associated with earth ground. (All DECLAB 11/03 systems are provided with this connection at the factory.)

**2.4.2.1** Twisted Pair Input Lines – The effects of magnetic coupling on the input signals may be reduced for floating single-ended or differential inputs by twisting the signal and return lines in the input cable. If the inductive pickup voltages of the two leads match, the net effect seen at the ADV11-A input is zero. Use of twisted pairs has no effect with a single-ended non-floating signal (referenced to ground at the instrument end).

Solid switch positions indicate sample state (11); dotted positions indicate hold state (12)

Figure 2-5 ADV11-A Quasi-Differential Mode

11-4169

THEFT

5 A. 21

2-10

**2.4.2.2** Shielded Input Lines – The effects of electrostatic coupling on the input signals may be reduced by shielding the signal wires. This is especially important if the instrument or transducer has high source impedance. To prevent the shield from carrying current and thus developing ground loop voltages within the ADV11-A; connect it to ground at the instrument end only.

2.4.2.3 Allowing for Input Settling with High Source Impedance – All solid-state multiplexers inject a small amount of charge into their input lines when changing channels, causing a transient error voltage that is discharged by the input signal's source impedance. The ADV11-A shares this characteristic, and also injects a small charge into the selected input line at the end of each conversion when the auto-zero switch is turned off (see Paragraph 2.3.2). After any channel change and after any conversion, the ADV11-A's control logic allows a 9  $\mu$ s interval (identified as the Transition Interval) during which conversions cannot start without generating error conditions. Normally, this is sufficient time for the input transient to settle out. However, more time may be needed when the multiplexer is switching into an input channel with high source impedance, particularly when large amounts of shunt capacitance exist in the interconnecting cables. Source impedance/cable shunt capacitance products greater than 1  $\mu$ s should be avoided whenever conversions are to be made at maximum rate with less than 1/2 LSB error. This means that cable shunt capacitance for a 1000  $\Omega$  source should not exceed 1000 pF (10<sup>3</sup> ×  $10^{-9} = 10^{-6}$ ), that shunt capacitance for a 100  $\Omega$  source should not exceed 0.01  $\mu$ F ( $10^2 \times 10^{-8} = 10^{-6}$ ). etc. Assuming twisted pair cable capacitance of 50 pF/foot, these constraints translate into a maximum run of 20 feet from a 1000- $\Omega$  source, 200 feet from a 100- $\Omega$  source, etc. Note that these values are consistent with good practice for avoiding noise pickup in long cable runs. Note also that settling errors can be eliminated by increasing the time between conversions or incorporating a software delay between channel changes and program start commands.

#### 2.4.3 Connections

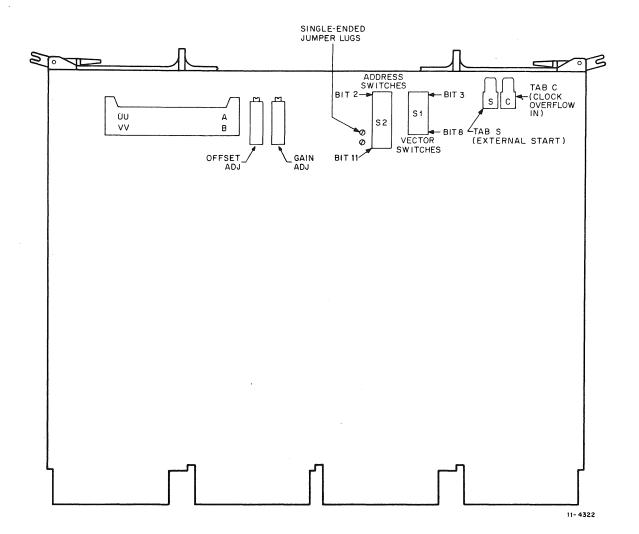

Figure 2-6 illustrates the location of user connectors and switches on the component side of the ADV11-A board.

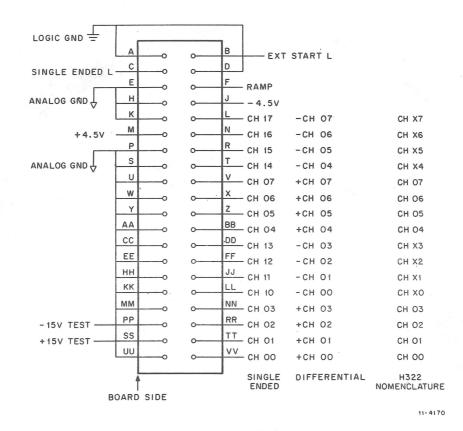

Analog input signals are input to the ADV11-A through the 40-pin connector. Pin assignments for the connector are shown in Figure 2-7. The proper Berg-to-Berg cable is the BC08R; the proper Berg to prepared open-ended cable is the BC04Z. (See Maintenance chapter for further information.)

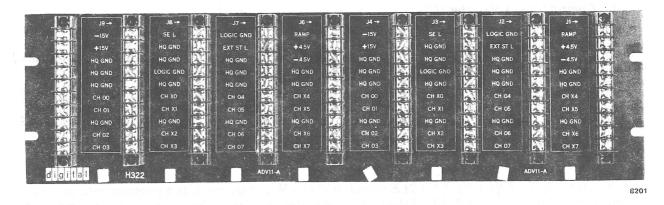

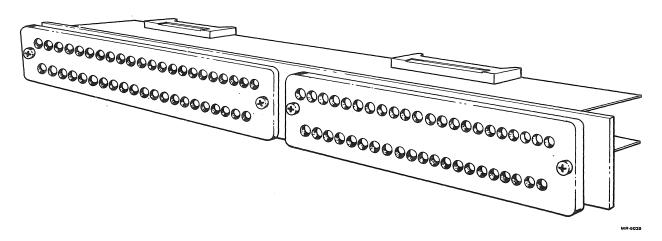

**2.4.3.1** Distribution Panel – Figure 2-8 shows an H322 Distribution Panel that is connected on the rear to the ADV11-A Berg connector and on the front provides easily identifiable and conveniently accessible barrier strip connections for user apparatus. Each H322 accommodates two ADV11-As or one ADV11-A and one other single-connector device. The ADV11-A is shipped with decal sets that specifically identify ADV11-A inputs and outputs. Note that the H323-B Potentiometer Box may *not* be used with the ADV11-A. (See Maintenance chapter for appropriate potentiometer box circuit.)

**2.4.3.2** External and Clock Starts – The external start signal line, pin B of the Berg connector or TAB S (see Figures 2-6 and 2-7), is a TTL-compatible input that presents five unit loads (8.0 mA) to any driving output. Conversions start on the high-to-low transitions of this signal.

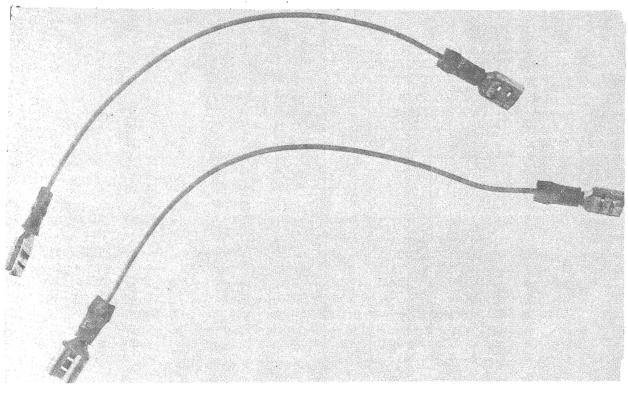

In most cases, the external start signal will be produced by a grounded (non-floating) pulse generator or logic circuitry located in a grounded instrument. The return path for the External Start signal will be through the power line ground system. For this reason, ground differences between source and computer should be minimized to prevent spurious start pulses due to ground noise. In no case should a separate return line be run between grounded source and the computer ground. Only with floating devices should return lines be run between source logic ground and logic ground pins on the ADV11-A Berg connector. External devices that require buffering can be interfaced to the ADV11-A through Schmitt Trigger 1 of the KWV11-A clock (ST1). Connection is made by means of a DEC 7010771 type jumper (Figure 2-9) to TAB S (Figure 2-6) of the ADV11-A.

Figure 2-6 ADV11-A Connectors and Switches

Conversions that must be initiated in consequence of time intervals or on every nth external event may be triggered from the KWV11-A through a DEC 7010771 type jumper connected from the clock output tab (CLK) to the ADV11-A clock overflow tab (C).

**2.4.3.3** Mode Control – The ADV11-A is equipped with jumper lugs (see Figure 2-6) that permit changing operating mode from quasi-differential (no connection) to single-ended (jumper installed). The single-ended mode can also be selected by connecting Berg connector pin C to logic ground. This alternative is provided to permit convenient external mode selection in installations that require frequent alternation between one mode and the other.

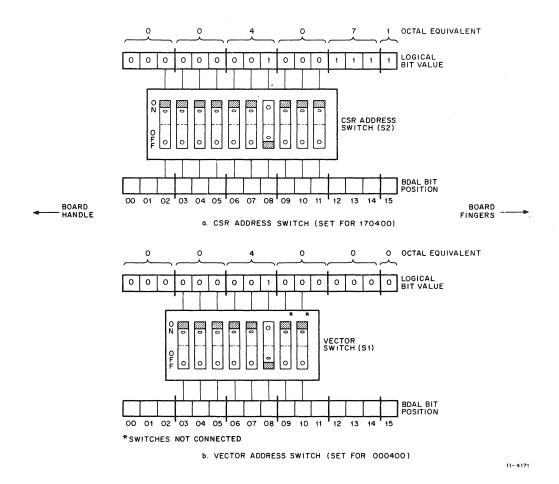

2.4.4 Vector and Address Selection – Device and vector addresses are assigned to the ADV11-A by means of two switch packs (S2 and S1, Figure 2-6). S2 is a pack containing 10 single-pole/single-throw switches, numbered 1–10, that communicate with data lines BDAL 2–11. Assuming BDAL lines 12–15 to be set by the processor to 1, S1 permits assigning any address between 170000 and 177774. The recommended address for the ADV11-A Status Register is 170400, set as illustrated in Figure 2-10(a). The Data Buffer Register automatically receives the next even address following that assigned to the CSR.

Figure 2-7 ADV11-A 40-Pin Connector Pin Assignments

Figure 2-8 H322 Distribution Panel

The A/D done interrupt vector address is set by means of S1, an 8-switch pack of which only six switches are utilized. These switches communicate with BDAL lines 3 through 8 and can be set in increments of  $10_8$ . The error interrupt vector automatically receives an address that is four locations higher than the A/D done interrupt vector whose recommended address is 000400 [see Figure 2-10(b)].

M-0599

## Figure 2-9 Module Jumpers

## 2.5 PROGRAMMING

2.5.1 Control/Status Register (CSR)

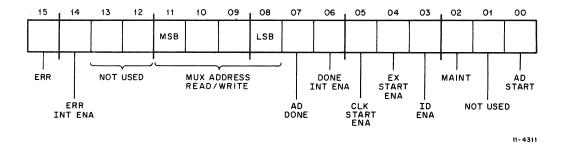

The significance of the CSR bits is defined below:

Bit 15: A/D ERROR (Read/Write) – The A/D ERROR may be program set or cleared and is cleared by the processor INITIALIZE. It is set by any of the following conditions:

- 1. Attempting an external or clock start during the transition interval (see Paragraph 2.3.2)

- 2. Attempting any start during a conversion in progress

- 3. Failing to read the result of a previous conversion before the end of the current conversion.

Bit 14: ERROR INTERRUPT ENABLE (Read/Write) – When set, enables a program interrupt upon an error condition (A/D ERROR). Interrupt is generated whenever bits 14 and 15 are set, regardless of which was set first.

Bits 13-12: Not used.

*Bits 11-8: MULTIPLEXER ADDRESS (Read/Write)* – Contain the number of the current analog input channel being addressed.

*Bit 07: A/D DONE (Read)* – Set at the completion of a conversion when the data buffer is updated. Cleared when the data buffer is read and by the processor INITIALIZE. If enabled interrupts are requested simultaneously by both bits 07 and 15, bit 07 has the higher priority.

Bit 06: DONE INTERRUPT ENABLE (Read/Write) – When set, enables a program interrupt at the completion of a conversion (A/D DONE). Interrupt is generated when bit 07 and bit 06 are both set, regardless of sequence.

Bit 05: CLOCK START ENABLE (Read/Write) – When set, enables conversions to be initiated by an overflow from the clock option.

Bit 04: EXTERNAL START ENABLE (Read/Write) – When set, enables conversions to be initiated by an external signal or through a Schmitt trigger from the clock option.

Bit 03: ID ENABLE (Read/Write) – When set, causes bit 12 of the Data Buffer Register to be loaded to a 1 at the end of any conversion.

*Bit 02: MAINTENANCE (Read/Write)* – Loads, when set, all bits of the converted data output equal to Multiplexer Address LSB (bit 08) at the completion of the next conversion. Cleared by the processor INITIALIZE. Used for "all 0s" and "all 1s" tests of A/D conversion logic.

Bit 01: Not used.

Bit 00: A/D START (Read/Write) – Initiates a conversion when set. Cleared at the completion of the conversion and by the processor INITIALIZE.

Figure 2-10 ADV11-A Address and Vector Switches (Rocker or Slide Switches)

Figure 2-12 ADV11-A Data Buffer Register (DBR)

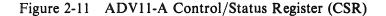

#### 2.5.2 Data Buffer Register (DBR)

The DBR is actually two separate registers – one read only, the other write only.

Read Only (Cleared at processor initialize)

Bits 15-13: Not used. Should read as 0.

Bit 12: ID (Read) – When ID ENABLE (bit 03) of the CSR has been set, DBR bit 12 will be loaded to a 1 at the end of conversion.

Bits 11-00: CONVERTED DATA (Read) – These bits contain the results of the last A/D conversion.

Write Only (Set to 200<sub>8</sub> at processor initialize)

Bits 15-08: Not used.

Bits 07-00: VERNIER D/A (Write) – These bits provide a programmed offset to the converted value (scaled 1 D/A LSB = 1/50 A/D LSB). The hardware initializes this value to 200<sub>8</sub> (mid-range). Values greater than 200<sub>8</sub> make the input voltage appear more positive.

## 2.5.3 Programming Example

Read  $100_8$  A/D conversions from channel 0 into locations  $4000_8$ -4176<sub>8</sub> and halt.

| START: | CLR    | PADSR       | CLEAR A/D STATUS REGISTER   |

|--------|--------|-------------|-----------------------------|

|        | MOV    | #4000,R0    | SET UP FIRST ADDRESS        |

|        | INC    | PADSR       | START A/D CONVERSION        |

| L00P:  | TSTR   | ADSR        | CHECK DONE FLAG             |

|        | BPL    | LOOP        | WAIT UNTIL FLAG SET         |

|        | INC    | ADSR        | START NEXT CONVERSION*      |

|        | MOV    | @ADBR,(RO)+ | PLACE CONVERTED VALUE       |

|        |        |             | FROM A/D BUFFER INTO MEMORY |

|        |        |             | LOCATION AND SET UP NEXT    |

|        |        |             | LOCATION FOR TRANSFER*      |

|        | CMP    | R0,#4200    | CHECK IF 100 CONVERSIONS    |

|        |        |             | HAVE BEEN DONE              |

|        | BNE    | LOOP        | INO, GET NEXT CONVERSION    |

|        | HALT   |             | DONE                        |

| ADSR:  | 170400 |             | A/D STATUS REGISTER ADDRESS |

| ADBR:  | 170402 |             | AD BUFFER REGISTER ADDRESS  |

|        | END    | START       |                             |

|        |        |             |                             |

<sup>\*</sup>Starting a subsequent conversion before moving data from a previous conversion is to be recommended only with systems equipped with non-processor memory refresh, as provided in the REV11 options. Without this capability, data will be lost occasionally by CPU memory refresh intervening between the INC and MOV commands. In general, non-processor memory refresh is essential to realizing the full potential of the ADV11-A.

ίų. vo

a de la comparison de la c Anno de la comparison de la Anno de la comparison de la

# CHAPTER 3 KWV11-A PROGRAMMABLE REAL-TIME CLOCK

#### **3.1 GENERAL DESCRIPTION**

The KWV11-A is a programmable clock/counter combination that provides a variety of means for determining time intervals or counting events. It can be used to generate interrupts to the LSI-11 processor at predetermined intervals, to synchronize the processor to external events, or to measure time intervals or establish programmed ratios between input and output events. It can also be used to start the ADV11-A Analog-to-Digital Converter either by clock counter overflow or by the firing of a Schmitt trigger.

The clock counter has a resolution of 16 bits and can be driven from any of five internal crystalcontrolled frequencies (100 Hz to 1 MHz), from a line frequency input or from a Schmitt trigger fired by an external input. The KWV11-A can be operated in any of four programmable modes: single interval, repeated interval, external event timing, and external event timing from zero base.

The KWV11-A includes two Schmitt triggers, each with integral slope and level controls. The Schmitt triggers permit the user to start the clock, initiate A/D conversions, or generate program interrupts in response to external events.

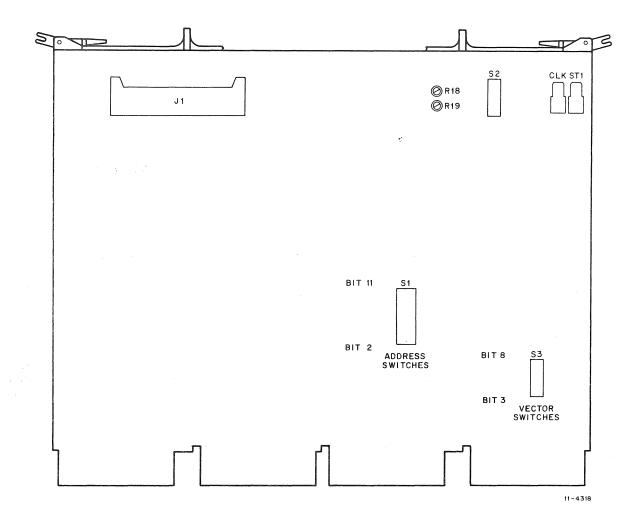

The physical structure of the KWV11-A is illustrated in Figure 3-1. The unit is contained on one quad size module whose fingers interface to the LSI-11 Bus. User interfacing for the Schmitt triggers and clock overflow signals is accomplished by means of a multi-pin connector (J1). FAST ON connectors (CLK, ST1) are provided to permit direct and simple connections of clock overflow and Schmitt trigger outputs to corresponding terminals on the ADV11-A A/D Converter. Switch packs permit selecting CSR (Control/Status Register) address, interrupt vector address, and Schmitt trigger slope and level conditions. Screwdriver controls (R18 and R19) permit setting Schmitt trigger levels. Provision is also made via the multi-pin connector J1 for external user-provided slope switches and level controls.

3.2 SPECIFICATIONS (@ 25° C unless otherwise specified)

## 3.2.1 Clock

Oscillator Accuracy

0.01%

Range

Base frequency (10 MHz) divided into five selectable rates (1 MHz, 100 kHz, 10 kHz, 1 kHz, 100 Hz); line frequency; Schmitt trigger 1 input

## 3.2.2 Input and Output Signals

All inputs and outputs are TTL compatible unless otherwise specified.

Figure 3-1 KWV11-A Connectors, Switches, and Controls

## 3.2.2.1 Input Signals

1. ST1 IN (Schmitt Trigger 1 Input)

| Input Range<br>(maximum limits)<br>Assertion Level | -30 V to +30 V                                                                                                   |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|                                                    | Depends upon position of slope reference selector switch and level control; triggering range, $-12$ V to $+12$ V |

| Origin                                             | User device                                                                                                      |

| Response Time                                      | Depends upon input waveform and amplitude; typically 600 ns with TTL logic input                                 |

| Hysteresis                                         | Approximately 0.5 V, positive and negative                                                                       |

| Characteristics                                    | Single-ended input; 100 k $\Omega$ impedance to ground                                                           |

| ST2 IN (Schmitt Trigger 2 Inn                      |                                                                                                                  |

2. ST2 IN (Schmitt Trigger 2 Input)

Same description as ST1 IN

### 3.2.2.2 Output Signals

Duration

1. CLK OV (Clock Overflow)

Asserted Level

Destination

Low

User device or ADV11-A

Approximately 500 ns

Characteristics TTL open-collector driver with 470  $\Omega$  pull-up to +5 V

Maximum source current from output through load to ground when output is high ( $\ge 2.4$  V): 5 mA

Maximum sink current from external source voltage through load to output when output is low ( $\leq 0.8$  V): 8 mA

2. ST1 Out (Schmitt Trigger 1 Output)

Same description as CLK OV

3. ST2 OUT (Schmitt Trigger 2 Output)

Same description as CLK OV

3.2.2.3 Environmental (ref: DEC STD 102, class C)

### **3.2.2.4** Power Requirements (from LSI-11 Bus Power Supply)

- +5 V 1.75 A typical

- +12 V 10 mA typical

## **3.3 FUNCTIONAL DESCRIPTION**

#### 3.3.1 Bus Control

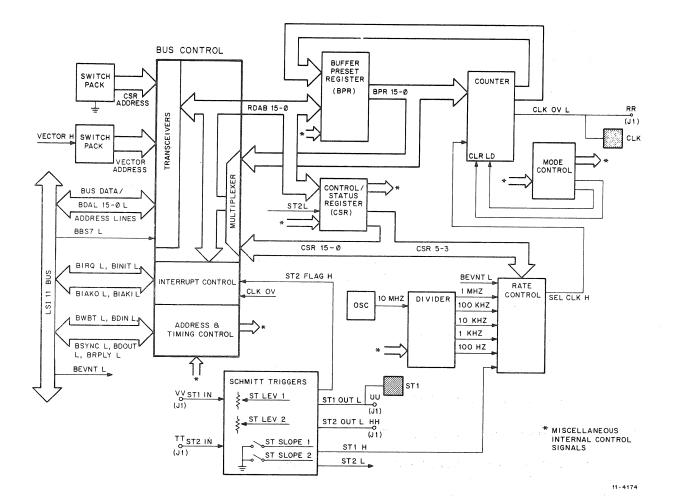

Figure 3-2 illustrates the KWV11-A in block diagram form.

The logic associated with the bus control block maintains proper communications protocol between the processor bus and the KWV11-A. This logic generates and monitors the bus signals involved during interrupts and data transfers between the processor and the KWV11-A. It permits the KWV11-A to recognize when it is being addressed by the processor (address defined by the Address Switch Pack), to prescribe the location in memory pointing to the starting addresses of interrupt service routines (by means of the Vector Address Switch Pack), to input control data from the processor, and to output data to the processor.

Interrupts can be enabled for both counter overflow and operation of ST2. Since each of these conditions raises a flag bit in the Control/Status Register, and since separate interrupt vectors exist for each condition, the conditions may be distinguished either by vectors or by testing flag bits.

## 3.3.2 Control/Status Register

The Control/Status Register (CSR) provides a means for the processor to control the operation of the KWV11-A and to derive information about its operating condition. Bits are provided for enabling interrupts, mode selection, maintenance operations, starting the counter, and overflow and Schmitt trigger event monitoring. (See Figure 3-9 and Table 3-1.)

Figure 3-2 KWV11-A Real-Time Clock Block Diagram

#### 3.3.3 Mode Control

Logic circuitry associated with the mode control block permits KWV11-A operation in four different modes as specified by bits 2–1 of the CSR.

#### **3.3.3.1** Mode 0 (Single Interval)

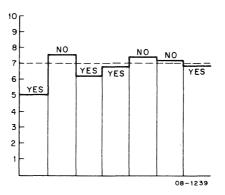

When the GO bit is set in this mode either by the processor or by a Schmitt Trigger 2 event, the counter is loaded from the Buffer/Preset Register (which has previously been loaded with the 2's complement of the number of counts desired before overflow). Once loaded, the counter will increment at the selected rate until it overflows. Overflow clears the GO bit, sets the Overflow Flag, and interrupts the processor if that function has been enabled. If interrupt has not been enabled, the KWV11-A waits for processor intervention.

#### **3.3.3.2** Mode 1 (Repeated Interval)

When the GO bit is set in this mode, the counter is loaded from the Buffer/Preset Register (BPR) and is then incremented to overflow as for Mode 0. In Mode 1, however, overflow does not clear the GO bit; instead, it causes the counter to be reloaded from the BPR, raises the Overflow Flag, initiates an interrupt sequence if the CSR Interrupt on Overflow bit is set, and causes the count to be continued with no loss of data.

#### **3.3.3.3** Mode 2 (External Event Timing)

When the GO bit is set in this mode, the counter is set to 0 and then incremented at the selected rate as long as the GO bit remains set. An external signal to Schmitt Trigger 2 (ST2) causes the current contents of the counter to be loaded into the BPR while the counter continues to run. At the same time the ST2 Flag is set and, if Interrupt 2 is enabled, an interrupt is generated, thus permitting the program to read the value held in the BPR.

The counter continues to run after the ST2 event and also continues to run after overflow. Interrupt on Overflow may be enabled to alert the program to the overflow condition.

#### **3.3.3.4** Mode 3 (External Event Timing from Zero Base)

Operation in Mode 3 is identical to that in Mode 2 except that the counter is zeroed each time an ST2 event loads its contents into the BPR.

#### 3.3.3.5 Flag Overrun

In all modes, if a second overflow occurs before the Overflow Flag is reset (i.e., before a prior event is serviced by the processor), or if ST 2 fires when the ST 2 flag is already set, the Flag Overrun bit is set.

#### 3.3.4 Oscillator, Divider, Rate Control Chain

The circuitry associated with these blocks provides the time base that is fed to the counter. The KWV11-A permits eight clock conditions to be specified by bits 5–3 of the CSR: STOP, 1 MHz, 100 kHz, 10 kHz, 1 kHz, 100 Hz, an external time base applied to ST1, and line frequency (50 or 60 Hz) picked up from bus line BEVNT. External periodic or aperiodic pulses may be applied to ST1 and counted, provided they meet the criteria in Paragraphs 3.2 and 3.3.6.

#### 3.3.5 Buffer/Preset and Counter Registers

The Buffer/Preset Register is a word-oriented, 16-bit read/write register that can be loaded either under program control or from the counter. In Modes 2 and 3, the firing of ST2 causes the BPR to be loaded with the contents of the counter. The BPR cannot be loaded by the program in these modes as long as the GO bit is set.

The counter is a 16-bit internal register accessible only by way of the BPR; in Modes 2 and 3 it can be read indirectly through the BPR.

## 3.3.6 Schmitt Triggers

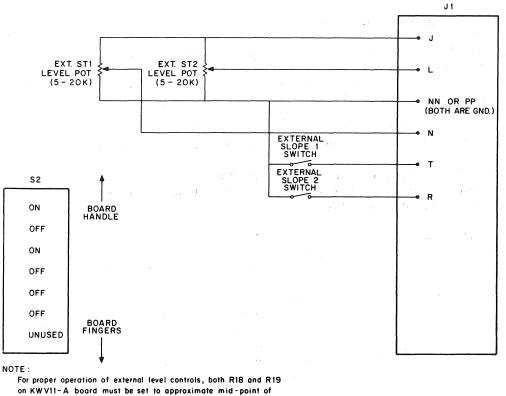

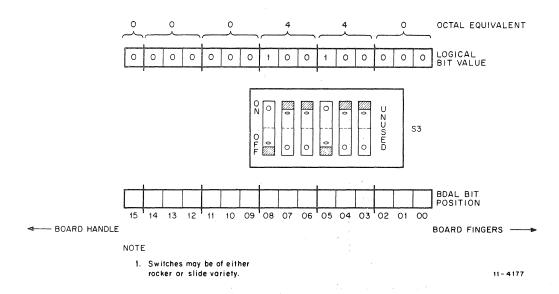

Both Schmitt triggers are equipped with switches to permit selecting slope direction (+ or -) and threshold reference level (TTL or -12V to +12V continuously variable). Each Schmitt trigger is also equipped with a screwdriver-operated potentiometer to permit setting the variable threshold level. Switch-pack and potentiometer terminals are all brought to multiple connector J1 to permit attachment of external user-provided slope and level controls. (See Figure 3-3.)

The two Schmitt triggers are used in somewhat different ways:

STI – Performs as an external time base input or external input for aperiodic signals to be counted. Outputs both to ST1 FAST ON connector to provide external start signals to ADV11-A and, through rate control circuitry, to permit selection as input to the counter. Maximum frequency varies as a function of input waveform.

ST2 – When the ST2 GO ENABLE bit is set, firing ST2 in any mode sets the GO bit and initiates counter action, causes the ST2 Flag to be asserted, and generates an interrupt if that function is enabled. When the GO bit is set in Modes 2 and 3, firing ST2 causes the Buffer/Preset Register to be loaded from the counter, the ST2 Flag to be set, and an interrupt to be generated if enabled.

rotation, and the S2 switches must be set as shown.

Figure 3-3 Connecting External User-Supplied Slope and Level Controls

11-4337

#### 3.4 CONNECTORS, SWITCHES, AND CONTROLS

Figure 3-1 illustrates the location of user connectors, switches, and controls on the component side of the KWV11-A board.

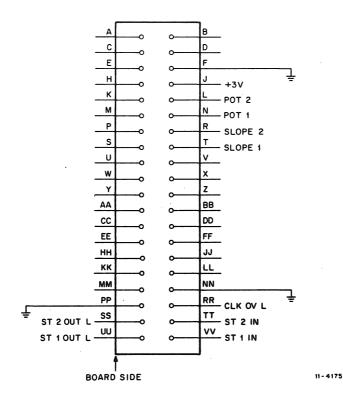

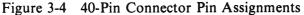

## 3.4.1 40-Pin Connector

Figure 3-4 illustrates the 40-pin connector pin assignments for user inputs and outputs. These pins may be connected to the optional H322 Distribution Panel\* (see Paragraph 2.4.3.1) for convenient external user access. The proper Berg-to-Berg cable is the BC08R. The proper Berg to prepared open-ended cable is the BC04Z.

#### **3.4.2 FAST ON Connectors (Clock Overflow and ST1 Outputs)**

Two FAST ON connector tabs labeled CLK and ST1 are situated in the upper-right corner of the KWV11-A board (see Figure 3-1). These tabs are electrically in parallel with pins RR (CLK OV L) and UU (ST1 OUT L) on the 40-pin connector and are intended to facilitate connections by means of module jumpers (shown in Figure 2-9) to the clock overflow and external start inputs on the ADV11-A (see Paragrapgh 2.4.3).

#### 3.4.3 Selector Switches (Address, Vector, and Slope/Reference Level)

Figure 3-1 identifies three switch packs (S1, S2, and S3) that the KWV11-A provides to facilitate the selection of CSR address, vector address, and slope/reference level conditions for Schmitt Triggers 1 and 2.

\*The KWV11-A is shipped with decals which permit permanent identification of signal lines associated with H322 terminals.

**3.4.3.1** Address Selection – Switch Pack S1 contains 10 single-pole/single-throw switches that communicate with data lines BDAL 11–2. The KWV11-A reads the BDAL lines only in response to BBS7 which the processor asserts only for an address of 160000 or higher. For this reason, and because the KWV11-A transceivers are hard wired to respond only when BDAL bit 12 is set to 1, S1 permits assigning the CSR any address ending in 0 or 4 between 170000<sub>8</sub> and 177774<sub>8</sub>. The recommended address for the KWV11-A CSR is 170420, set as illustrated in Figure 3-5. The BPR automatically receives the next even address following that assigned to the CSR.

Figure 3-5 KWV11-A CSR Address Switches (Set for 170420)

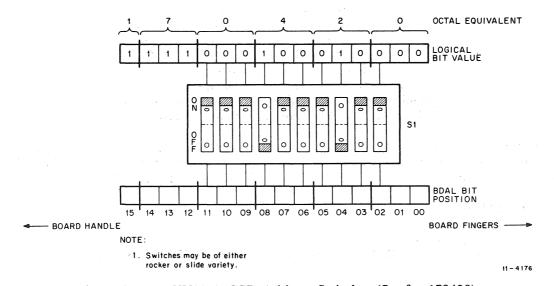

**3.4.3.2** Vector Selection – The clock overflow interrupt vector address is set by means of S3, a 7switch pack of which only six switches are utilized. These switches communicate with BDAL lines 8–3 and can be set in increments of  $10_8$ . The ST2 interrupt vector automatically receives an address that is four locations higher than the clock overflow interrupt vector whose recommended address is 0000440 (see Figure 3-6).

Figure 3-6 KWV11-A Vector Address Switches (Set for 000440)

3.4.3.3 Slope and Reference Level Selector Switches and Controls (See Figure 3-7) – Slope and reference level selection for ST1 and ST2 are accomplished by means of S2, a 7-switch pack of which only switches 1-6 are used. Two reference modes are selectable for each Schmitt trigger – one that picks a fixed level appropriate to TTL logic, and one that picks a variable level that permits setting the ST threshold to any point between -12 and +12 V.

#### NOTE

User should take care that both TTL and variable switches for either Schmitt trigger are not on simultaneously. This condition will do no damage to components, but produces unpredictable reference levels. Note also that if no signal is connected to a Schmitt trigger input, both threshold switches for that ST should be open for noise immunity. Alternatively, ST1 IN and ST2 IN can be grounded\_externally.

Slope selection is accomplished by separate switches for ST1 and ST2, respectively. When the related switch is on, the firing point effectively occurs on the positive slope of the input waveform. When the switch is off, the firing point occurs on the negative slope. (See Figure 3-8.)

# 3.5 **PROGRAMMING**

#### 3.5.1 CSR Bit Assignments

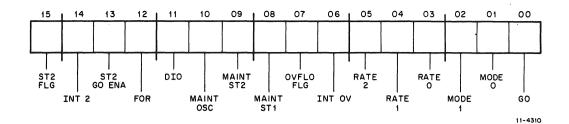

CSR bit assignments are identified in Figure 3-9 and defined in Table 3-1.

Figure 3-7 KWV11-A Slope/Reference Level Selector Switches and Controls

#### 3.5.2 Buffer/Preset Register (BPR)

The BPR is a 16-bit, word-oriented, read/write register. Any attempt to write a byte into this register will result in a whole word being written. In Modes 0 and 1 the program may load it with the 2's complement of the number of counts desired before overflow. In Modes 2 and 3 it permits indirect reading of the clock counter.

#### 3.5.3 Normal Control Sequences

3.5.3.1 Mode 0 (Single Interval) – Control code for operation in Mode 0 must support the following sequence:

- 1. Control program writes desired count (2's complement) into BPR (see Paragraph 3.3.5).

- 2. Program writes control code into Control/Status Register as indicated in Table 3-2.

- 3. If GO bit is set high, KWV11-A responds by loading the 16-bit counter (see Paragraph 3.3.5) from the BPR and enabling the counter; if GO bit is set low and ST2 GO ENABLE bit is set high, KWV11-A waits for ST2 event, then sets the GO bit and loads and enables the counter.

- 4. Counter increments until overflow, then halts (GO bit is cleared)

- 5. KWV11-A raises Overflow Flag and issues interrupt if the CSR INT OV bit is set; if interrupt is not enabled, KWV11-A waits for program intervention.

- 6. Program responds to interrupt or intervenes in consequence of other criteria (e.g., testing the Overflow Flag or the A/D Done Flag if overflow was used to start an A/D conversion). Program reads the CSR, clears the Overflow Flag, and if no counting or mode changes are required, sets the GO bit or the ST2 GO ENABLE bit to reenter the sequence at step 3.

3-10

| Bit                                                         | Set By/Cleared By                                                                                                                                                                                                                                                                                              | Remarks                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

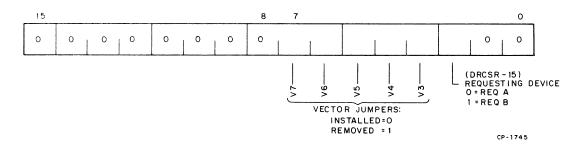

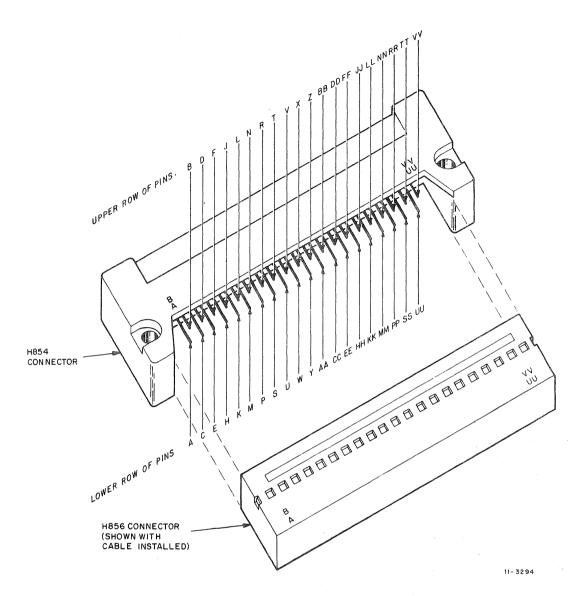

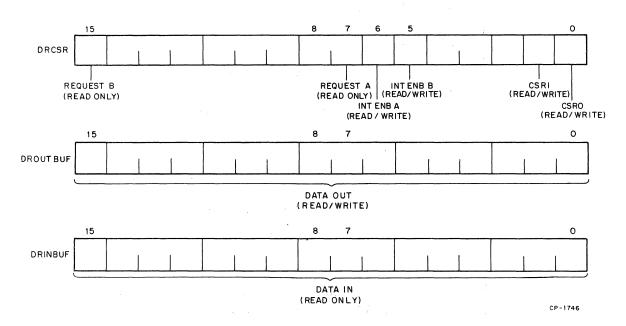

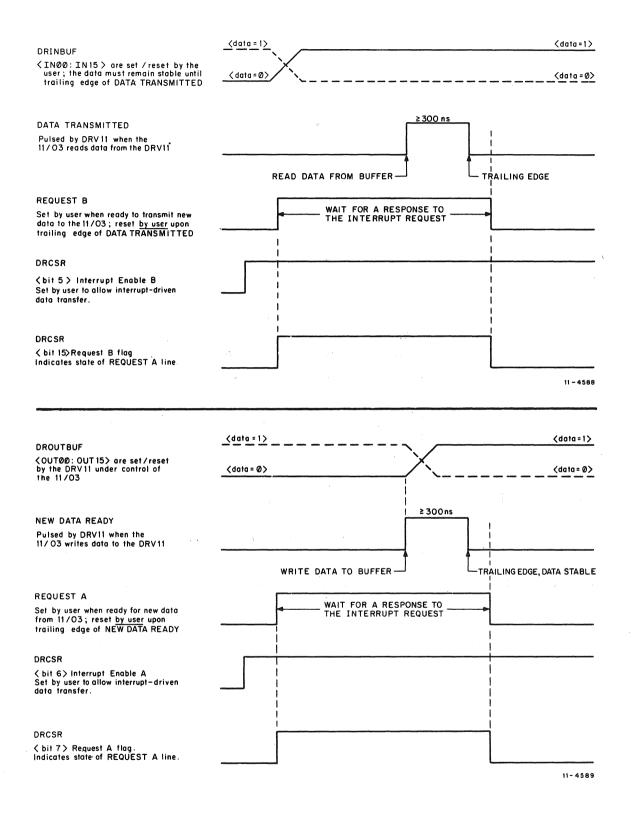

| 15 ST2 Flag<br>Read/Write to 0                              | Set by the firing of Schmitt Trigger<br>2 or the setting of the MAINT ST2<br>bit in any mode while the GO bit or<br>the ST2 GO ENABLE bit is set.<br>Cleared under program control.<br>Also cleared at the "1"-going tran-<br>sition of the GO bit unless the ST2<br>GO ENABLE bit has previously<br>been set. | Must be cleared after servicing an<br>ST2 interrupt to enable further<br>interrupts. When cleared, any<br>pending ST2 interrupt request will<br>be cancelled. If enabled interrupts<br>are requested at the same time by<br>bits 07 and 15, bit 07 has the higher<br>priority. |