# Service Guide

Publication number 01660-97026 First edition, November 1997

For Safety information, Warranties, and Regulatory information, see the pages at the end of the book.

© Copyright Hewlett-Packard Company 1987–1997 All Rights Reserved.

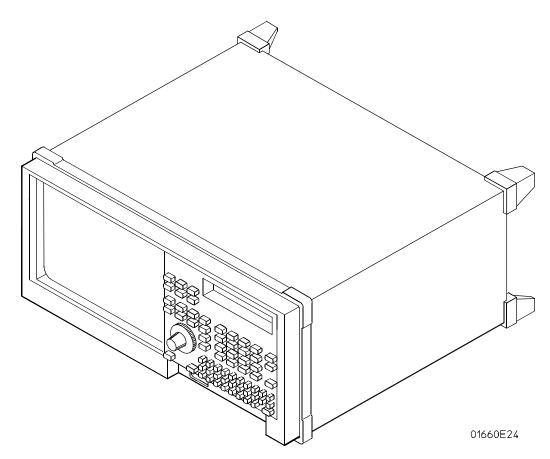

HP 1660C/CS/CP-Series Logic Analyzers

# HP 1660C-Series, HP 1660CS-Series, and HP 1660CP-Series Logic Analyzers

The HP 1660C-Series are 100-MHz State/500 MHz Timing Logic Analyzers.

The HP 1660CS-Series includes all the features of the HP 1660C-Series, as well as a 2-channel, 1 GSa/s oscilloscope.

The HP 1660CP-Series includes all the features of the HP 1660C-Series, as well as a 32-channel pattern generator.

#### **Features**

Some of the main features of the HP 1660C-Series Logic Analyzers are as follows:

- 128 data channels and 6 clock/data channels in the HP 1660C

- 96 data channels and 6 clock/data channels in the HP 1661C

- 64 data channels and 4 clock/data channels in the HP 1662C

- 32 data channels and 2 clock/data channels in the HP 1663C

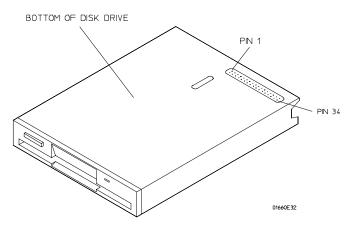

- 3.5-inch flexible disk drive

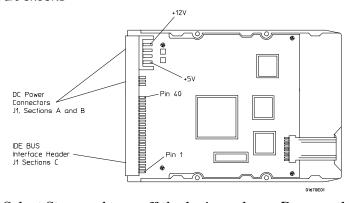

- 540 MB hard disk drive

- HP-IB, RS-232-C, and Centronics printer interfaces

- Variable setup/hold time

- 4k states deep memory on all channels with 8k states in half channel mode

- Marker measurements

- 12 levels of trigger sequencing for state and 10 levels of sequential triggering for timing

- 100 MHz time and number-of-states tagging

- Full programmability

- DIN mouse

- DIN keyboard support

The HP 1660CP-Series Logic Analyzers also include the following features:

- 32 channels of stimulus

- Maximum output rate of 200 MHz in half-channel mode and 100 MHz in full-channel mode

- Memory depth of 258,048 vectors

- Support for TTL, 3-state TTL/3.3v, 3-state TTL/CMOS, ECL terminated, ECL unterminated, and differential ECL (without pod).

The HP 1660CS-Series Logic Analyzers also include the following features:

- 1 GSa/s digitizing for 250 MHz bandwidth single shot oscilloscope

- 8000 samples per channel

- Automatic pulse parameters displays time between markers, acquires until specified time between markers is captured, performs statistical analysis on time between markers

- Lightweight miniprobes

## **Options**

The HP 1660C-Series, HP 1660CP-Series, and HP 1660CS-Series Logic Analyzers can be ordered with the optional Thinlan and Ethertwist LAN ports.

### **Service Strategy**

The service strategy for this instrument is the replacement of defective assemblies. This service guide contains information for finding a defective assembly by testing and servicing the HP 1660C/CS/CP-Series Logic Analyzers.

This logic analyzer can be returned to Hewlett-Packard for all service work, including troubleshooting. Contact your nearest Hewlett-Packard Sales Office for more details.

The HP 1660-Series Logic Analyzer

## In This Book

This book is the service guide for the HP 1660C/CS/CP-Series Logic Analyzers and is divided into eight chapters.

Chapter 1 contains information about the logic analyzer and includes accessories, specifications and characteristics, and equipment required for servicing.

Chapter 2 tells how to prepare the logic analyzer for use.

Chapter 3 gives instructions on how to test the performance of the logic analyzer.

Chapter 4 contains calibration instructions for the logic analyzer.

Chapter 5 contains self-tests and flowcharts for troubleshooting the logic analyzer.

Chapter 6 tells how to replace assemblies of the logic analyzer and how to return them to Hewlett-Packard.

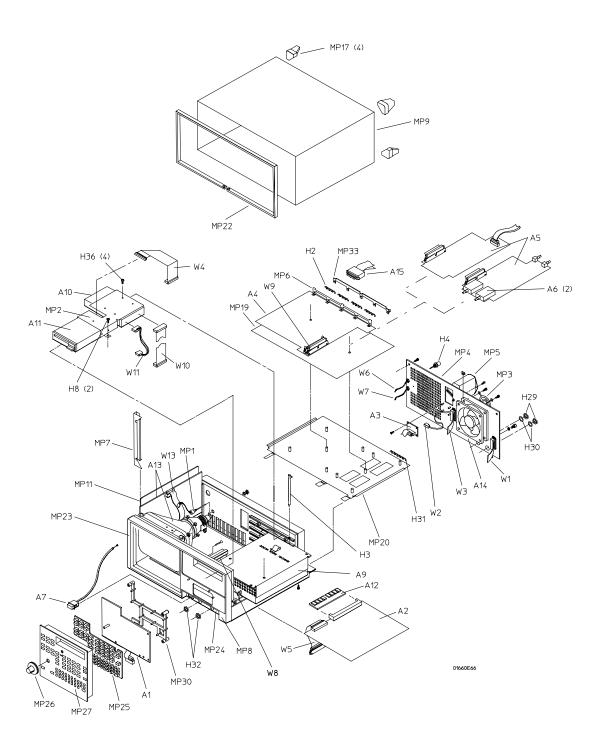

Chapter 7 lists replaceable parts, shows an exploded view, and gives ordering information.

Chapter 8 explains how the logic analyzer works and what the self-tests are checking.

## **Table of Contents**

## 1 General Information

Accessories 1–2

Specifications (logic analyzer) 1–3

Specifications (oscilloscope) 1–4

Specifications (pattern generator) 1–4

Characteristics (logic analyzer) 1–5

Characteristics (oscilloscope) 1–5

Characteristics (pattern generator) 1–6

Supplemental Characteristics (logic analyzer) 1–7

Supplemental Characteristics (oscilloscope) 1–10

Recommended test equipment (logic analyzer) 1–14

Recommended test equipment (oscilloscope) 1–15

Recommended test equipment (pattern generator) 1–16

#### 2 Preparing for Use

To inspect the logic analyzer 2–2

To apply power 2–3

To operate the user interface 2–3

To set the line voltage 2–3

To degauss the display 2–4

To clean the logic analyzer 2–4

To test the logic analyzer 2–4

#### 3 Testing Performance

To perform the self-tests 3–3

To make the test connectors (logic analyzer) 3-7

To test the threshold accuracy (logic analyzer) 3-9

Set up the equipment 3–9 Set up the logic analyzer 3–10

Connect the logic analyzer 3-10

Test the TTL threshold 3-11

Test the ECL threshold 3-13

Test the – User threshold 3–14

Test the + User threshold 3-15

Test the 0 V User threshold 3-16

Test the next pod 3-17

To test the glitch capture (logic analyzer) 3–18

Set up the equipment 3-18

Set up the logic analyzer 3-19

Connect the logic analyzer 3-19

Test the glitch capture on the connected channels 3-21

Test the next channels 3-23

```

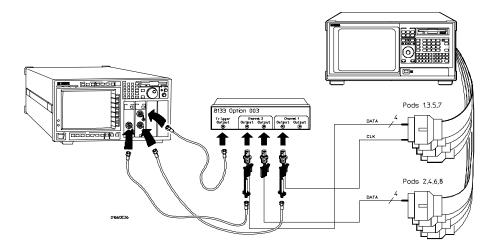

To test the single-clock, single-edge, state acquisition (logic analyzer) 3-24

Set up the equipment 3-24

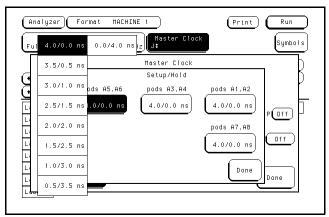

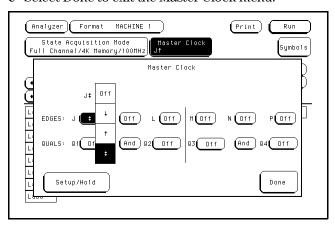

Set up the logic analyzer 3-25

Connect the logic analyzer 3-27

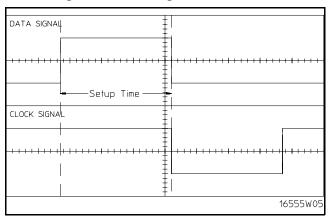

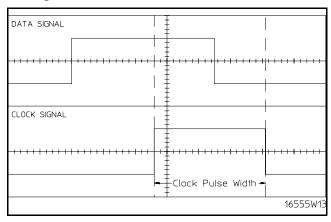

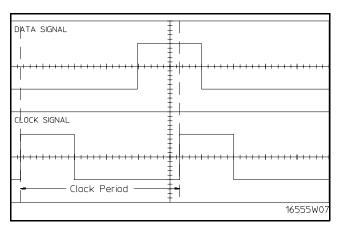

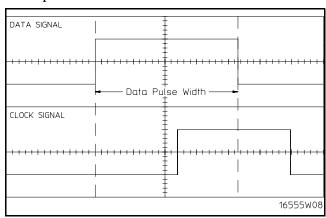

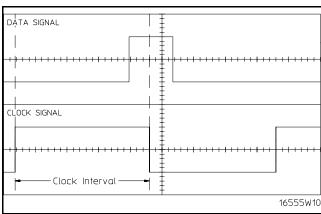

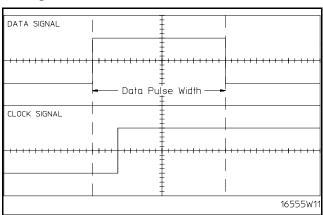

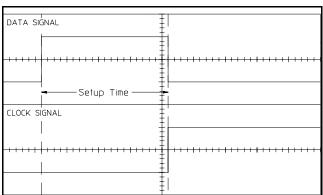

Verify the test signal 3-29

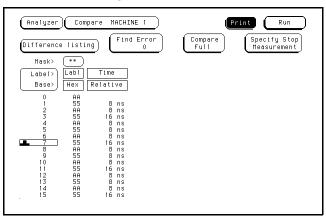

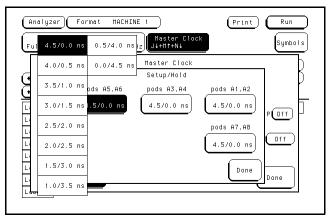

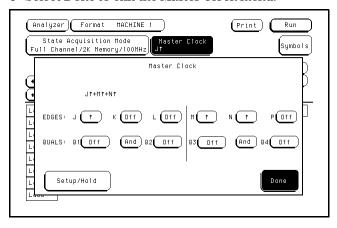

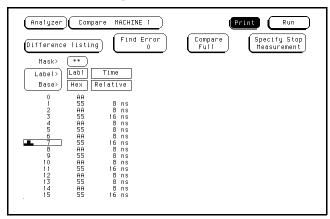

Check the setup/hold combination 3-31

Test the next channels 3-36

To test the multiple-clock, multiple-edge, state acquisition (logic analyzer) 3–37

Set up the equipment 3-37

Set up the logic analyzer 3-38

Connect the logic analyzer 3-40

Verify the test signal 3-42

Check the setup/hold with single clock edges, multiple clocks 3-44

Test the next channels 3-48

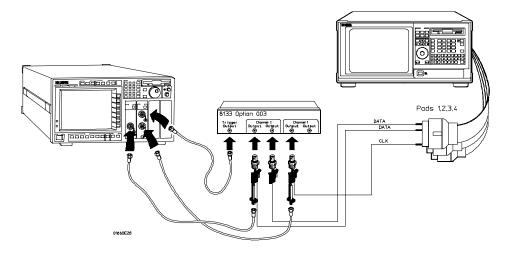

To test the single-clock, multiple-edge, state acquisition (logic analyzer) 3-49

Set up the equipment 3-49

Set up the logic analyzer 3-50

Connect the logic analyzer 3-52

Verify the test signal 3-54

Check the setup/hold with single clock, multiple clock edges 3-56

Test the next channels 3-59

To test the time interval accuracy (logic analyzer) 3-60

Set up the equipment 3-60

Set up the logic analyzer 3-61

Connect the logic analyzer 3-64

Acquire the data 3-64

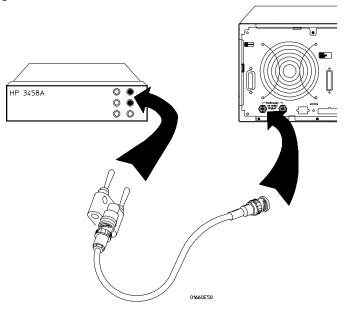

To test the CAL OUTPUT ports (oscilloscope) 3-65

Set up the equipment 3-65

Set up the logic analyzer 3-66

Verify the DC CAL OUTPUT port 3-67

Set up the logic analyzer 3-68

Verify the AC CAL OUTPUT port 3-68

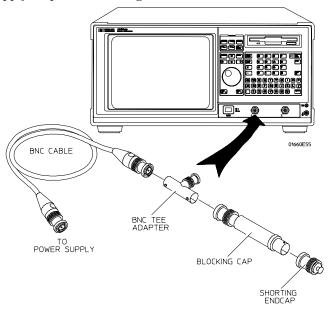

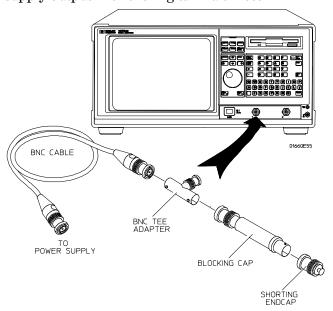

To test the input resistance (oscilloscope) 3-69

Set up the equipment 3-69

Set up the logic analyzer 3-70

Connect the logic analyzer 3–71

Acquire the data 3-72

```

Perform an operational accuracy calibration 3–72

```

To test the voltage measurement accuracy (oscilloscope) 3-73

Set up the equipment 3-73

Set up the logic analyzer 3-74

Connect the logic analyzer 3-75

Acquire the data 3-76

To test the offset accuracy (oscilloscope) 3–77

Set up the equipment 3-77

Set up the logic analyzer 3-78

Connect the logic analyzer 3–79

Acquire the zero input data 3-80

Acquire the DC input data 3-81

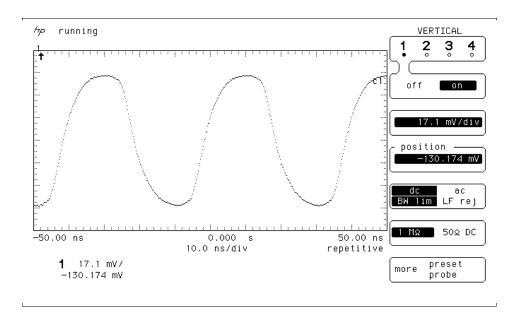

To test the bandwidth (oscilloscope) 3-82

Set up the equipment 3-82

Set up the logic analyzer 3-83

Connect the logic analyzer 3-85

Acquire the data 3-86

To test the time measurement accuracy (oscilloscope) 3–87

Set up the equipment 3-87

Set up the logic analyzer 3-88

Connect the logic analyzer 3-90

Acquire the data 3-90

To test the trigger sensitivity (oscilloscope) 3–91

Set up the equipment 3-91

Set up the logic analyzer 3-92

Connect the logic analyzer 3-94

Acquire the data 3-94

Performance Test Record (logic analyzer) 3–95

Performance Test Record (oscilloscope) 3-101

```

Performance Test Record (pattern generator) 3–104

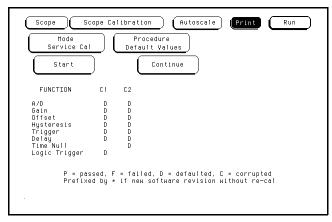

#### 4 Calibrating and Adjusting

Logic analyzer calibration 4–2

Self Cal menu calibrations 4-5

To calibrate the oscilloscope 4–3 Set up the equipment 4–3 Load the Default Calibration Factors 4–4

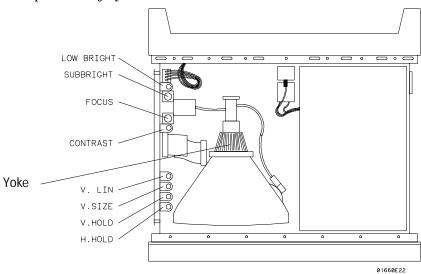

To adjust the CRT monitor alignment 4-6

To adjust the CRT intensity 4–8

#### 5 Troubleshooting

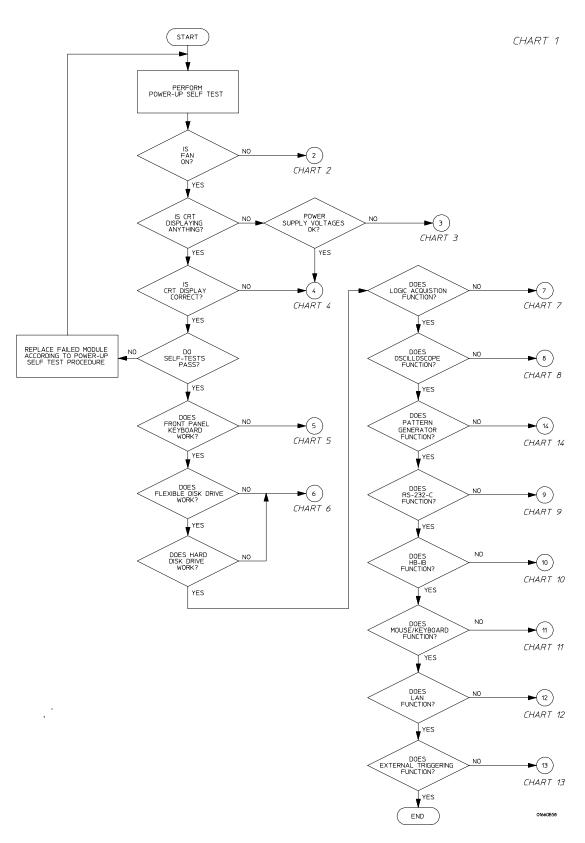

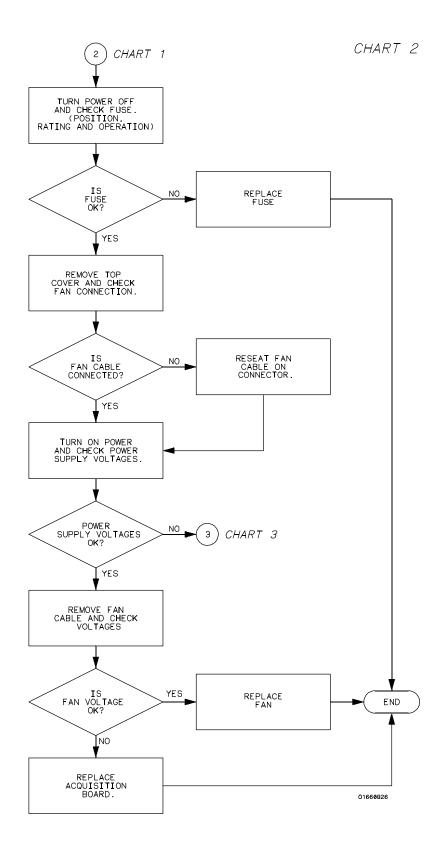

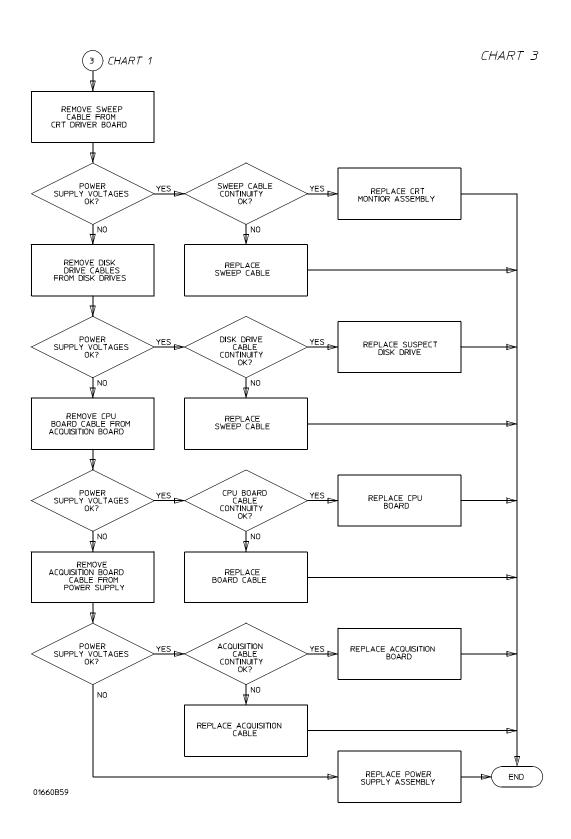

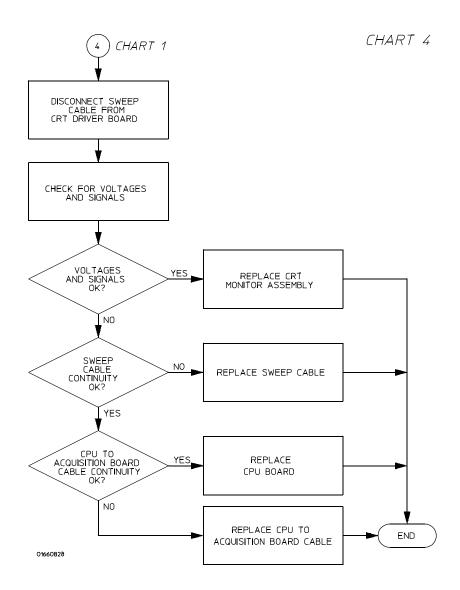

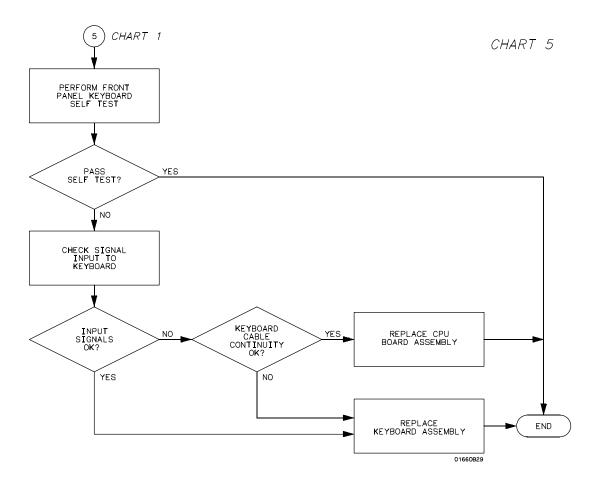

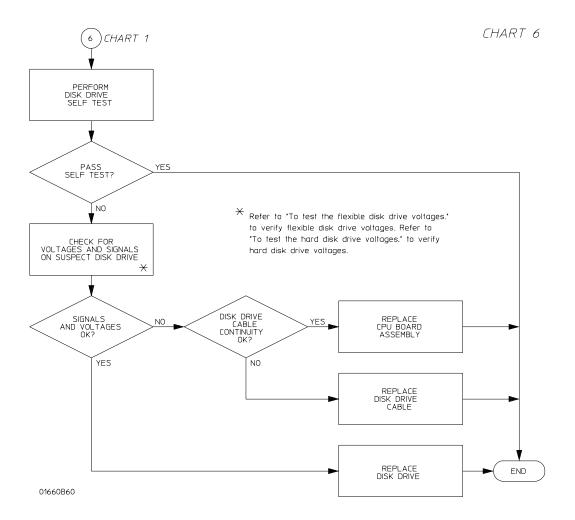

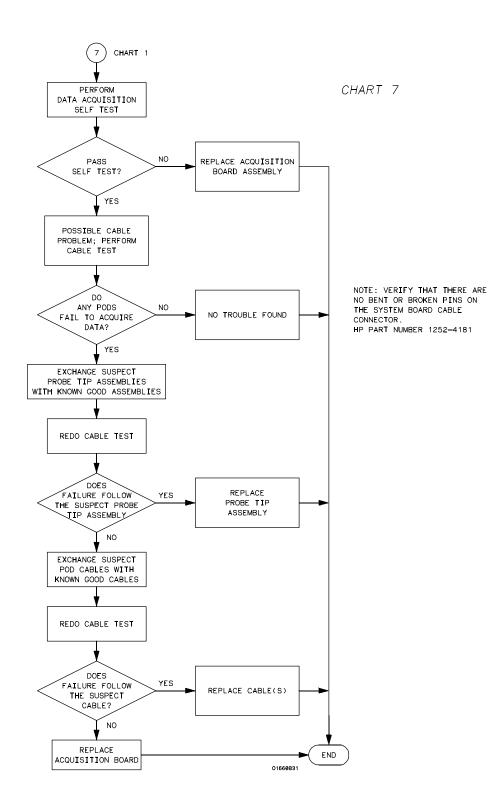

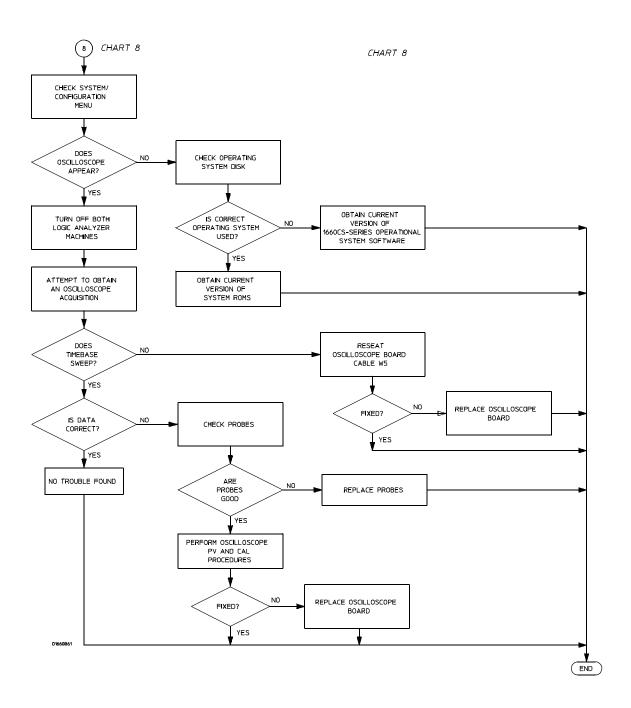

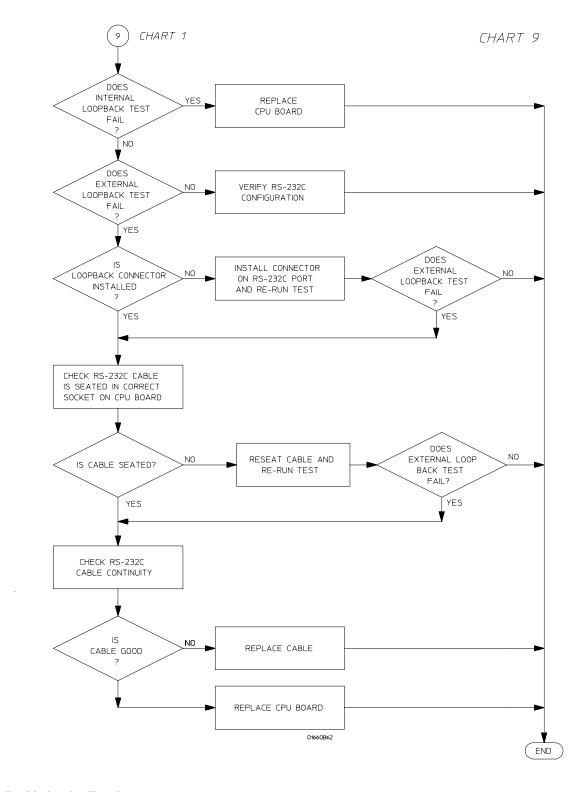

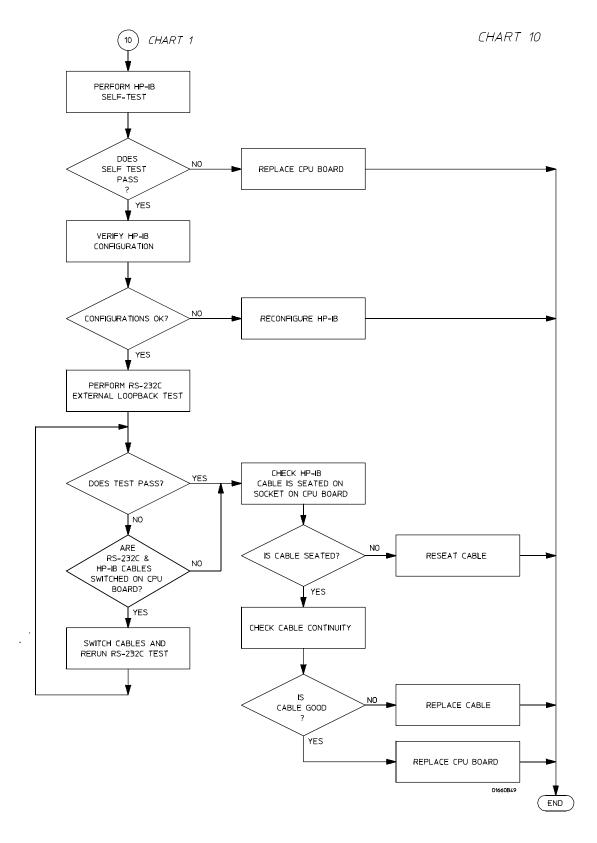

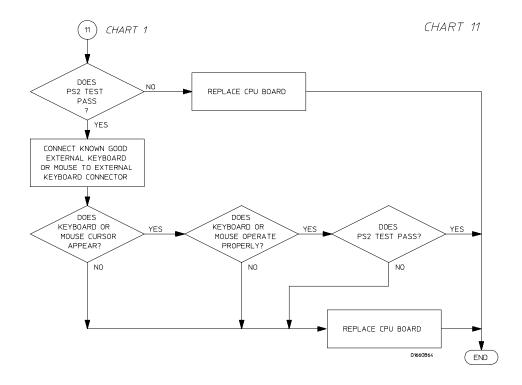

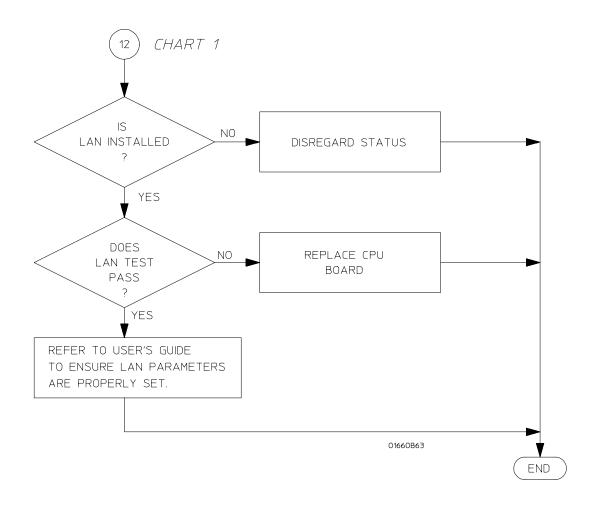

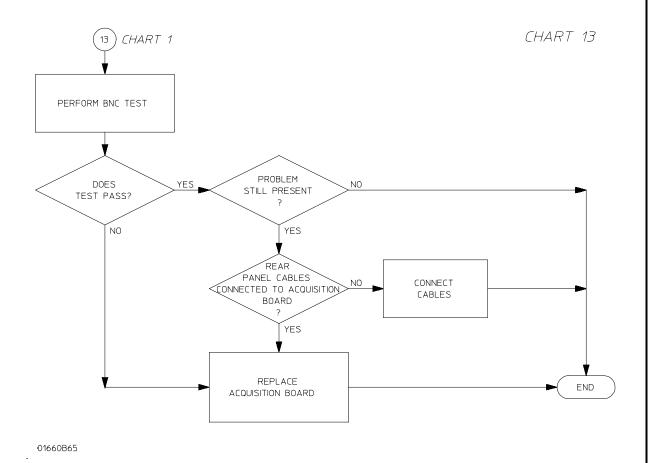

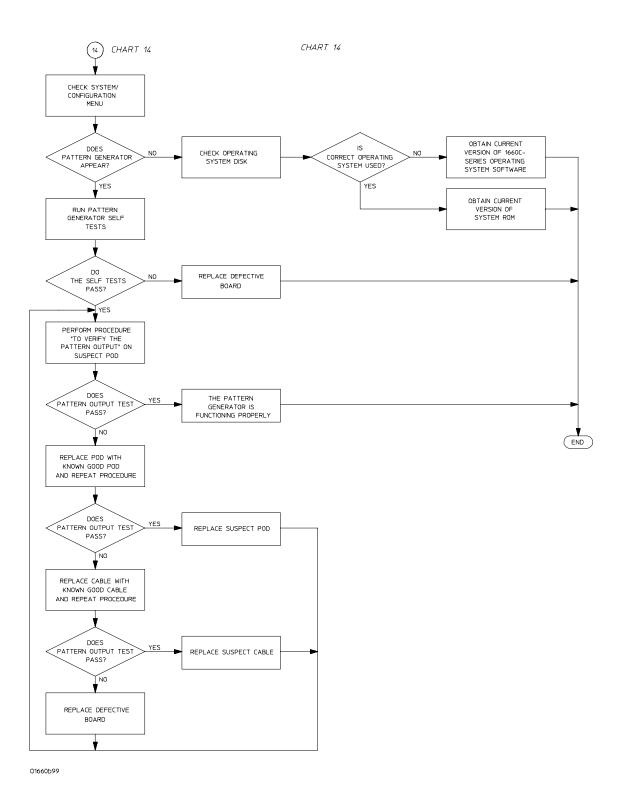

To use the flowcharts 5-2

To check the power-up tests 5-17

To run the self-tests 5–18

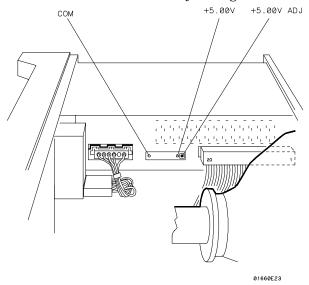

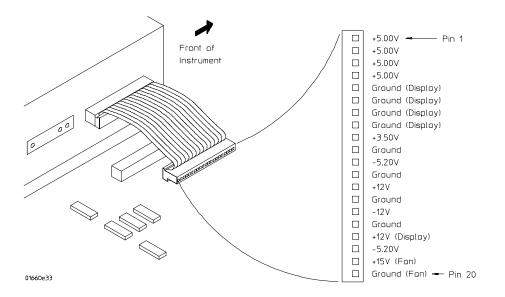

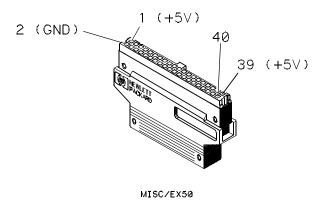

To test the power supply voltages 5-24

To test the CRT monitor signals 5-26

To test the keyboard signals 5-27

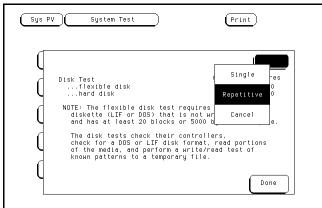

To test the flexible disk drive voltages 5-28

To test the hard disk drive voltages 5-30

To perform the BNC test 5-31

To test the logic analyzer probe cables 5–32

To verify pattern output (HP 1660CP-Series only) 5-36

To test the auxiliary power 5–38

#### 6 Replacing Assemblies

To remove and replace the handle 6-5

To remove and replace the feet and tilt stand 6-5

To remove and replace the cover 6-5

To remove and replace the disk drive assembly 6-6

To remove and replace the power supply 6-7

To remove and replace the CPU board 6-7

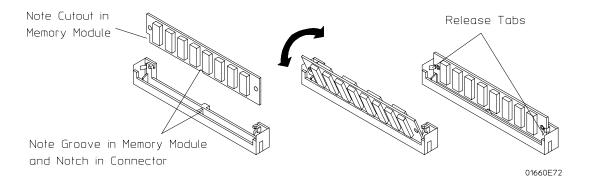

To remove and replace SIMM memory 6-8

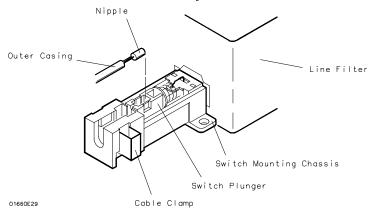

To remove and replace the switch actuator assembly 6–9

To remove and replace the rear panel assembly 6–10

To remove and replace the HP 1660C-series acquisition board 6-11

To remove and replace the HP 1660CS-series oscilloscope board 6-12

To remove and replace the HP 1660CP-series pattern generator board 6-13

To remove and replace the front panel and keyboard 6-14

To remove and replace the intensity adjustment 6-14

To remove and replace the monitor 6-15

To remove and replace the handle plate 6-15

To remove and replace the fan 6-16

To remove and replace the line filter 6–16

To remove and replace the HP 1660CP-series pattern generator cables 6-17

To remove and replace the HP-IB and RS-232-C cables 6-17

To remove and replace the I/O board 6-18

To return assemblies 6-18

### 7 Replaceable Parts

Replaceable Parts Ordering 7–2 Replaceable Parts List 7–3 Exploded View 7–4 Power Cables and Plug Configurations 7–8

## **8 Theory of Operation**

Block-Level Theory 8–3

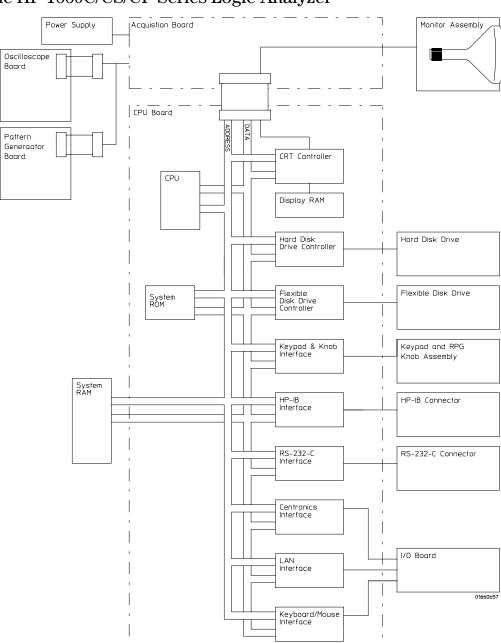

The HP 1660C/CS/CP Series Logic Analyzer 8–3

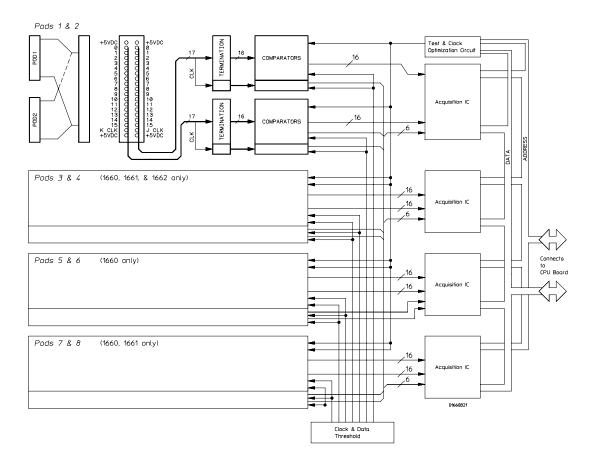

The Logic Acquisition Board 8–7

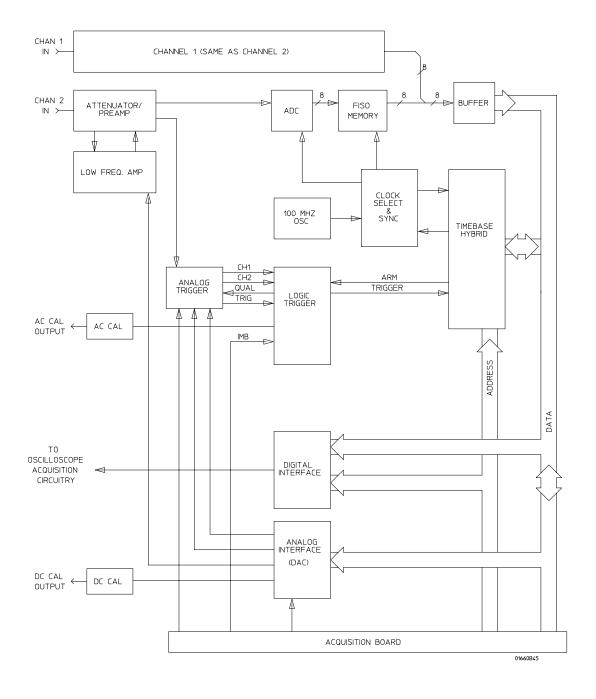

The Oscilloscope Board 8–10

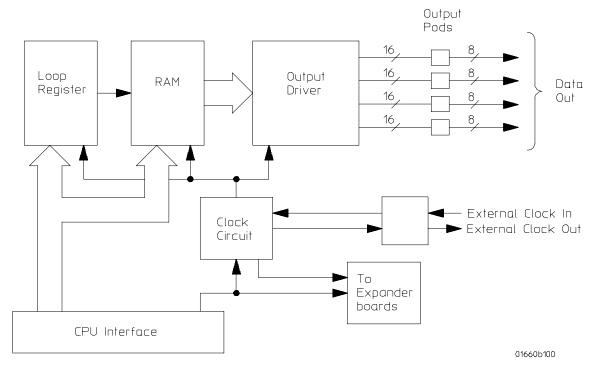

The Pattern Generator Board 8–13

Self-Tests Description 8–15 Power-up Self-Tests 8–15 System Tests (System PV) 8–16 Analyzer Tests (Analy PV) 8–20 Oscilloscope tests (Scope PV) 8–22 Pattern Generator tests (Patt Gen) 8–23

HP-IB 8-27

RS-232-C 8-28

Accessories 1–2

Specifications (logic analyzer) 1–3

Specifications (oscilloscope) 1–4

Specifications (pattern generator) 1–4

Characteristics (logic analyzer) 1–5

Characteristics (oscilloscope) 1–5

Characteristics (pattern generator) 1–6

Supplemental Characteristics (logic analyzer) 1–7

Supplemental Characteristics (oscilloscope) 1–10

Recommended test equipment (logic analyzer) 1–14

Recommended test equipment (oscilloscope) 1–15

Recommended test equipment (pattern generator) 1–16

# **General Information**

This chapter lists the accessories, the specifications and characteristics, and the recommended test equipment.

## Accessories

The following accessories are supplied with the HP 1660C/CS/CP-series logic analyzers.

| Accessories Supplied             | <b>HP Part Number</b> | Qty    |

|----------------------------------|-----------------------|--------|

| Probe tip assemblies             | 01650-61608           | Note 1 |

| Probe cables                     | 01660-61605           | Note 2 |

| Grabbers (20 per pack)           | 5090-4356             | Note 1 |

| Probe ground (5 per pack)        | 5959-9334             | Note 1 |

| Demo Training Kit                | E2433-60012           | 1      |

| HP 1660C User's Guide            | 01660-99016           | 1*     |

| Symbol Utility (disk and manual) | E2450A                | 1      |

| Accessories Pouch                | 01660-84501           | 1      |

| RS-232-C Loopback Connector      | 01650-63202           | 1      |

| PS2 Mouse                        | A2839B                | 1      |

$<sup>^{*}</sup>$  The HP 1660CS and HP 1660CP have their own User's Guide. For those products, the HP 1660C User's Guide is not shipped.

| Note 1 Quantities: | 8 - 1660C.CS | Note 2 Quantities: | 4 - 1660C.CS |

|--------------------|--------------|--------------------|--------------|

|                    | 6 - 1661C.CS |                    | 3 - 1661C.CS |

|                    | 4 - 1662C.CS |                    | 2 - 1662C.CS |

|                    | 2 - 1663C.CS |                    | 1 - 1663C.CS |

#### **CP-Series Additional Accessories**

| <b>Accessories Supplied</b> | <b>HP Part Number</b> | Qty |

|-----------------------------|-----------------------|-----|

| Data Output Cable           | 16522-61601           | 4   |

| Clock Output Cable          | 16522-61602           | 1   |

| HP 1660CP User's Guide      | 01660-97023           | 1   |

## **CS-Series Additional Accessories**

| <b>Accessories Supplied</b> | <b>HP Part Number</b> | Qty |

|-----------------------------|-----------------------|-----|

| 10:1 probes                 | 10430A                | 2   |

| BNC miniprobe adapter       | 1250-1454             | 1   |

| HP 1660CS User's Guide      | 01660-99019           | 1   |

## **Accessories Available**

Other accessories available for the HP 1660C/CS/CP Series Logic Analyzer are listed in the Accessories for HP Logic Analyzers brochure.

# Specifications (logic analyzer)

The specifications are the performance standards against which the product is tested.

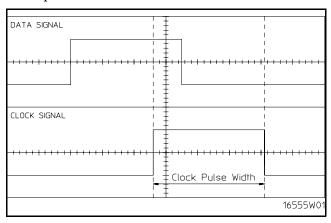

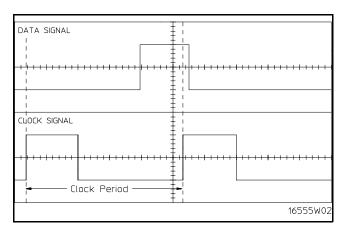

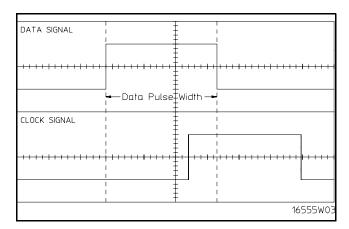

$\begin{array}{ll} \text{Maximum State Speed} & 100 \text{ MHz} \\ \text{Minimum State Clock Pulse Width}^* & 3.5 \text{ ns} \\ \text{Minimum Master to Master Clock Time}^* & 10.0 \text{ ns} \\ \text{Minimum Glitch Width}^* & 3.5 \text{ ns} \\ \end{array}$

Threshold Accuracy  $\pm (100 \text{ mV} + 3\% \text{ of threshold setting})$

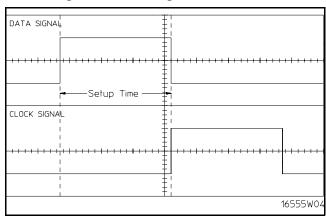

Setup/Hold Time:\*

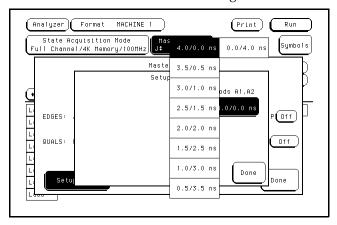

Single Clock, Single Edge 0.0/3.5 ns through 3.5/0.0 ns,

adjustable in 500-ps increments

Single Clock, Multiple Edges 0.0/4.0 ns through 4.0/0.0 ns,

adjustable in 500-ps increments

Multiple Clocks, Multiple Edges 0.0/4.5 ns through 4.5/0.0 ns,

adjustable in 500-ps increments

$<sup>^{\</sup>star}$  Specified for an input signal VH = -0.9 V, VL = -1.7 V, slew rate = 1 V/ns, and threshold = -1.3 V.

Trigger Sensitivity<sup>(\*)</sup>

# Specifications (oscilloscope)

The HP 1660CS Logic Analyzers also include the following specifications:

Bandwidth (\*,1) DC to 250 MHz (real time, dc-coupled)

Time Interval Measurement Accuracy (\*, 2)  $\pm [(0.005\% \text{ X} \Delta t) +$

$(2 \times 10^{-6} \times \text{delay setting}) + 150 \text{ ps}$

DC Offset Accuracy  $\pm (1.0\% \text{ of channel offset} + 2.0\% \text{ of full scale})$

Voltage Measurement Accuracy $^{(*,3)}$   $\pm$  [(1.5% of full scale + offset accuracy)

+ (0.008 x V/div)]

DC to 50 MHz: 0.063 x full scale,

50 to 250 MHz: 0.125 x full scale

Input R (selectable)  $^{(*)}$  1 M $\Omega$ :  $\pm 1\%$ , 50  $\Omega$ :  $\pm 1\%$

\* Specifications (valid within ± 10° C of auto-calibration temperature, excluding bandwidth–see note 1 for bandwidth specification.)

1. Upper bandwidth reduces by 2.5 MHz for every degree C above 35° C.

2. Specification applies to the maximum sampling rate. At lower rates, the specification is: $\pm$  [(0.005% x  $\Delta$ t)+(2 x  $10^{-6}$  x delay setting) + (0.15 x sample interval)] for bandwidth limited signals (t<sub>r</sub> = 1.4 x sample interval). Sample interval is defined as  $\frac{1}{sample\ rate}$

3. Digitizing level = (#vertical divisions) $(\frac{1}{2})(\frac{1}{LSR})$ , where LSB=2 #bits in ADC

# Specifications (pattern generator)

There are no specifications for the pattern generator portion of the HP 1660CP-Series Logic Analyzers.

# Characteristics (logic analyzer)

These characteristics are not specifications, but are included as additional information.

|                                  | Full Channel       | Half Channel       |

|----------------------------------|--------------------|--------------------|

| Maximum State Clock Rate         | 100 MHz            | $100~\mathrm{MHz}$ |

| Maximum Conventional Timing Rate | $250~\mathrm{MHz}$ | 500 MHz            |

| Maximum Transitional Timing Rate | $125~\mathrm{MHz}$ | $250~\mathrm{MHz}$ |

| Maximum Timing with Glitch Rate  | N/A                | $125~\mathrm{MHz}$ |

| Memory Depth                     | 4K                 | $8K^*$             |

| Channel Count:                   |                    |                    |

| HP 1660C,CP,CS                   | 136                | 68                 |

| HP 1661C,CP, CS                  | 102                | 51                 |

| HP 1662C,CP,CS                   | 68                 | 34                 |

| HP 1663C,CP,CS                   | 34                 | 17                 |

<sup>\*</sup> For all modes except glitch.

## Characteristics (oscilloscope)

The HP 1660CS Logic Analyzers also include the following characteristics:

Maximum Sample Rate 1 Gigasample per second

Number of Channels 2 Rise Time<sup>(1)</sup> 1.4 ns

ADC 8-bit real time

Vertical Resolution 8 bits over 4 vertical divisions ( $\pm 0.4\%$ )

Waveform Record Length 8000 points

Vertical (DC) Gain Accuracy<sup>(2)</sup> ±1.25% of full scale

Input Coupling 1 M $\Omega$ : ac and DC, 50  $\Omega$ : DC only

Input C Approximately 7 pF

<sup>1.</sup> Rise time is calculated from the formula:  $t_r = \frac{0.35}{bandwidth}$

<sup>2.</sup> Vertical gain accuracy decreases 0.08% per degree C from software calibration temperature.

## Characteristics (pattern generator)

The HP 1660CP Logic Analyzers also include the following characteristics:

Output channels 16 channels at 200 MHz clock; 32 channels at

$100~\mathrm{MHz}~\mathrm{clock}$

Memory depth 258,048 vectors

Logic levels (data pods)

TTL, 3-state TTL/3.3v, 3-state TTL/CMOS,

ECL terminated, ECL unterminated, and differential

ECL (without pod)

Data inputs 3-bit pattern - level sensing (clock pod)

Clock outputs Synchronized to output data, delay of 11 ns in 9 steps

(clock pod)

Clock input DC to 200 MHz (clock pod)

Internal clock period Programmable from 5 ns to 250 µs in a 1, 2, 2.5, 4, 5, 8

sequence

External clock period (user supplied) DC to 200 MHz

External clock duty cycle 2 ns minimum high time

Maximum number of "IF condition"

blocks at 50 MHz clock

1

Maximum number of different macros100Maximum number of lines in a macro1024Maximum number of macro invocations1,000Maximum number of Repeat loop1,000

invocations

Maximum number of Wait event patterns 4

# Supplemental Characteristics (logic analyzer)

## Supplemental Characteristics (logic analyzer)

#### **Probes**

Input Resistance  $100 \text{ k}\Omega, \pm 2\%$

Input Capacitance ~ 8 pF

Minimum Voltage Swing 500 mV, peak-to-peak

Threshold Range ± 6.0 V, adjustable in 50-mV increments, CAT I

Maximum Input Voltage ± 40 volts, CAT I

**State Analysis**

State/Clock Qualifiers 1660/61C,CP,CS - 6; 1662C,CP,CS - 4; 1663C,CP,CS - 2

Time Tag Resolution\* 8 ns or 0.1%, whichever is greater

Maximum Time Count

Between States 34 secondsMaximum State Tag Count\*  $4.29 \times 10^9$

**Timing Analysis**

Sample Period Accuracy 0.01 % of sample period

Channel-to-Channel Skew 2 ns, typical

Time Interval Accuracy ± [sample period + channel-to-channel skew

+(0.01%)(time reading)]

**Triggering**

Sequencer Speed 125 MHz, maximum

State Sequence Levels 12 Timing Sequence Levels 10

Maximum Occurrence Counter

Value 1,048,575

Pattern Recognizers 10

Maximum Pattern Width 136 channels in HP 1660C, CP, CS, 102 channels in

HP 1661C, CP, CS, 68 channels in HP 1662C, CP, CS,

34 channels in HP 1663C,CP,CS

Range Recognizers 2

Range Width 32 bits each

Timers 2

Timer Value Range 400 ns to 500 seconds

Glitch/Edge Recognizers 2 (timing only)

Maximum Glitch/Edge Width 136 channels in HP 1660C,CP,CS, 102 channels in

HP 1661C,CP,CS, 68 channels in HP 1662C,CP,CS,

34 channels in HP 1663C,CP,CS

<sup>\*</sup>Maximum state clock rate with time or state tags on is 100 MHz. When all pods are assigned to a state or timing machine, time or state tags halve the memory depth.

#### **Measurement and Display Functions**

**Displayed Waveforms** 24 lines maximum, with scrolling across 96 waveforms.

#### **Measurement Functions**

**Run/Stop Functions** Run starts acquisition of data in specified trace mode.

**Stop** In single trace mode or the first run of a repetitive acquisition, Stop halts acquisition and displays the current acquisition data. For subsequent runs in repetitive mode, Stop halts acquisition of data and does not change the current display.

**Trace Mode** Single mode acquires data once per trace specification. Repetitive mode repeats single mode acquisitions until Stop is pressed or until the time interval between two specified patterns is less than or greater than a specified value, or within or not within a specified range.

#### **Indicators**

**Activity Indicators** Provided in the Configuration and Format menus for identifying high, low, or changing states on the inputs.

**Markers** Two markers (X and O) are shown as vertical dashed lines on the display.

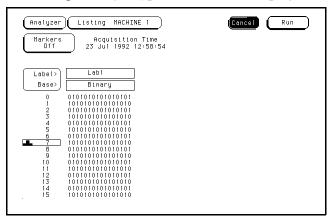

**Trigger** Displayed as a vertical dashed line in the Timing Waveform display and as line 0 in the State Listing display.

#### Data Entry/Display

**Labels** Channels may be grouped together and given a 6-character name. Up to 126 labels in each analyzer may be assigned with up to 32 channels per label.

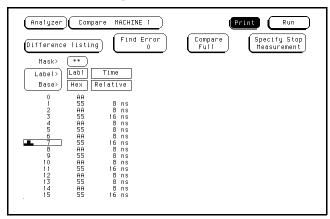

**Display Modes** State listing, State Waveforms, Chart, Compare Listing, Compare Difference Listing, Timing Waveforms, and Timing Listings. State Listing and Timing Waveforms can be time-correlated on the same displays.

**Timing Waveform** Pattern readout of timing waveforms at X or O marker.

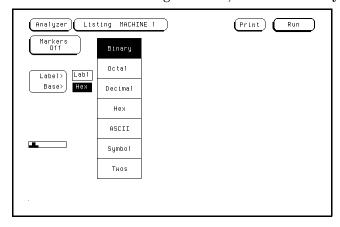

**Bases** Binary, Octal, Decimal, Hexadecimal, ASCII (display only), Two's Complement, and User-defined symbols.

**Symbols** 1,000 maximum. Symbols can be downloaded over RS-232 or HP-IB.

#### **Marker Functions**

**Time Interval** The X and O markers measure the time interval between a point on a timing waveform and the trigger, two points on the same timing waveform, two points on different waveforms, or two states (time tagging on).

**Delta States (state analyzer only)** The X and O markers measure the number of tagged states between one state and trigger or between two states.

**Patterns** The X and O markers can be used to locate the *nth* occurrence of a specified pattern from trigger, or from the beginning of data. The O marker can also find the *nth* occurrence of a pattern from the X marker.

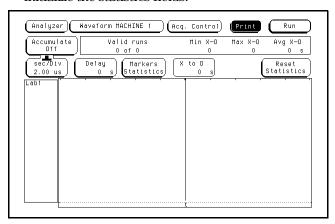

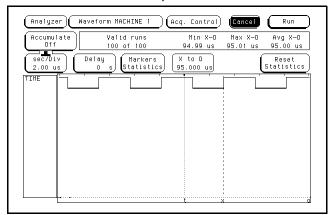

**Statistics** X and O marker statistics are calculated for repetitive acquisitions. Patterns must be specified for both markers, and statistics are kept only when both patterns can be found in an acquisition. Statistics are minimum X to O time, maximum X to O time, average X to O time, and ratio of valid runs to total runs.

#### **Auxiliary Power**

Power through cables 1/3 amp at 5 V maximum per cable, CAT I, Pollution degree 2.

#### **Operating Environment**

Temperature Instrument, 0 °C to 55 °C (+32 °F to 131 °F).

Probe lead sets and cables,  $0 \, ^{\circ}\text{C}$  to  $65 \, ^{\circ}\text{C}$  (+32  $^{\circ}\text{F}$  to  $149 \, ^{\circ}\text{F}$ ).

Humidity Instrument, probe lead sets, and cables, up to

80% relative humidity at +40 °C (+122 °F).

Altitude To 3067 m (10,000 ft).

Vibration Operating: Random vibration 5 to 500 Hz,

10 minutes per axis,  $\approx 0.3$  g (rms).

Non-operating: Random vibration 5 to 500 Hz,

10 minutes per axis,  $\approx 2.41$  g (rms);

and swept sine resonant search, 5 to 500 Hz, 0.75 g (0-peak), 5 minute resonant dwell

at 4 resonances per axis.

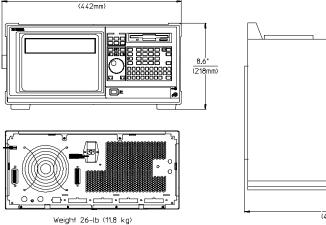

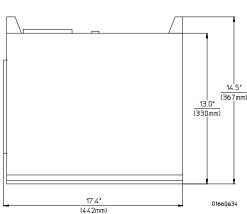

#### **Dimensions**

17.4

## **Product Regulations**

**( €** ISM 1-A

C N279

Safety IEC 1010-1:1990+A1 / EN 61010-1:1993

UL3111

CSA-C22.2 No. 1010.1:1993

EMC This product meets the requirement of the European

Communities (EC) EMC Directive 89/336/EEC.

Emissions EN55011/CSIPR 11 (ISM, Group1, Class A equipment)

IEC 555-2 and IEC 555-3

Immunity EN50082-1 Code<sup>1</sup> Notes<sup>2</sup>

IEC 801-2 (ESD)4kV CD, 8kV AD 1

IEC 801-3 (Rad.) 3V/m 1

IEC 801-4 (EFT) 1kV 1

<sup>1</sup>Performance Codes:

1 PASS - Normal operations, no effect.

$2\ \mathrm{PASS}$  - Temporary degradation, self recoverable.

3 PASS - Temporary degradation, operator intervention required.

4 FAIL - Not recoverable, component damage.

# Supplemental Characteristics (oscilloscope)

## Vertical (at BNC)

Vertical Sensitivity Range 4 mV/div to 10 V/div in 1-2-4 increments

(1:1 Probe)

DC Offset Range (1:1 Probe)

Vertical Sensitivity Available Offset

Probe Factors Any integer ratio from 1:1 to 1000:1

Maximum Safe Input Voltage 1 MΩ: ±250 V [DC + peak ac (< 10 KHz)], CAT II

$50 \Omega$ : ±5 VRMS

Channel-to-Channel Isolation DC to 50 MHz: 40 dB, 50 MHz to 250 MHz: 30 dB

Timebase

Range 1 ns/div to 5 s/div

Resolution 20 ps

Delay Pre-trigger Range

Time/div Setting

Available Delay

1 µs to 5 s/div

-8 x (s/div)

1 ns to 500 ns/div  $-4 \mu s$

Delay Post-trigger Range

Time/div Setting Available Delay

100 ms to 5 s/div 2.5 ks

$1~\mu s$  to 50~m s/div  $33{,}500~x~(s/div)$

1ns to 500 ns/div 16.7 ms

**Triggering**

Trigger Level Range Within display window (full scale and offset)

Trigger Modes

Immediate Triggers immediately after arming

condition is met.

Edge Triggers on rising or falling edge of

any internal channel, count adjustable from

1 to 32,000.

Pattern Triggers on entering or exiting a

specified pattern of both internal

channels, count adjustable from 1 to 32,000.

Pattern Duration Triggers on pattern duration specified

across one or both channels. Modes are "Present<", "Present>", and "Range."

Patterns longer than 20 ns but shorter

than 160 ms can be detected.

Pattern Occurrence Triggers on entering or exiting a

specified pattern across one or both channels.

Auto-Trigger If enabled, the module will self-trigger

if no trigger condition is found within approximately 50 ms after arming.

nth edge or pattern, as specified by the user. The number of events (n) can be set from 1 to 32,000 events. Maximum

count frequency is 70 MHz.

Intermodule Arms another measurement module or

triggers the rear panel BNC.

External If enabled, the oscilloscope will trigger

on an ECL level signal (-1.3 V).

## Supplemental Characteristics (oscilloscope)

Digitizer

Resolution 8 bits (1 part in 256)

Digitizing Rate Up to 1 Gigasample per second

Digitizing Technique Real-time digitizing; each 8000 samples are acquired on a single

acquisition

Acquisition Memory Size 8000 samples per channel

**Waveform Display**

Displayed Waveforms Eight waveform windows maximum, with scrolling across 96

waveforms.

Display Formats Waveforms can be displayed in an overlapping and/or

non-overlapping format. Display capability of A-B and A+B is

also provided.

Display Resolution 500 points horizontal, 240 points vertical.

**Display Modes**

Normal (Single) New acquisition replaces old acquisition on screen.

Accumulate New acquisition is displayed in addition to previous

acquisitions until screen is erased.

Average New acquisitions are averaged with old acquisitions, with

the updated waveform displayed until erased. Maximum

number of averages is 256.

Overlay Up to 8 acquired waveforms from separate channels can be

overlayed in the same display area.

Connect-the-dots Provides a display of the sample points connected by

straight lines.

Waveform Reconstruction When there is insufficient data to fill every horizontal

location, a post acquisition reconstruction filter fills in

missing data points for time base < 50 ns/div.

Waveform Math Display capability of A-B and A+B functions is provided.

#### **Measurement and Display Functions**

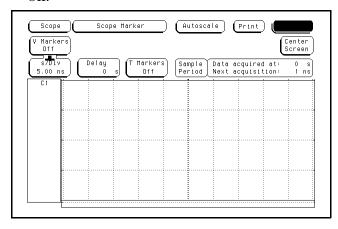

**Time Markers** Two vertical markers, X and O, are provided for measurements of time and voltage. Capabilities are: measure voltage at point where X and O markers cross each analog waveform; measure time from trigger to X, trigger to O, and X to O; automatic marker placement by specifying percentage of edge, edge number, and rising or falling edge type; run until X to O > than, < than, in range, and not in range provides selective event search; X to O statistics (mean, max, and min) provide analysis of time interval deviation.

**Voltage Markers** Two horizontal markers, A and B, are provided for voltage measurements. These markers can each be placed on any acquisition channel trace. A delta voltage display provides delta V between markers on the same channel or between channels.

**Automatic Search** Searches for a percentage voltage level at a positive or negative edge, count adjustable from 1 to 100.

**Auto Search Statistics** Mean, maximum, and minimum values for elapsed time from X to O markers for multiple runs. Number of valid runs and total number of runs available.

**Automatic Measurements** The following pulse parameter measurements can be performed automatically:

| Frequency | Rise time | + pulse width |

|-----------|-----------|---------------|

| Period    | Fall time | -pulse width  |

| V p-p     | Preshoot  | V amplitude*  |

|           | 0 1 /     |               |

Overshoot

(\*gives difference between top and base voltages; only available over bus)

**Grid** Graticules can be displayed in background of waveform.

#### **Setup Aids**

**Autoscale** Autoscales the vertical and horizontal ranges, offset, and trigger level to display the input signals. Requires a frequency between 50 Hz and 250 MHz.

**Presets** Scales the vertical range, offset, and trigger level to predetermined values for displaying ECL or TTL waveforms.

**Calibration** Vertical, trigger, delay, and all defaults. Calibration factors stored in NV-RAM on the circuit board.

**Probe Compensation Source** External BNC supplies a square wave approximately 0.0 mV to -800 mV into the open circuit at approximately 1000 Hz.

# Recommended test equipment (logic analyzer)

## **Equipment Required**

| Equipment                             | Critical Specifications                                                                     | Recommended<br>Model/Part           | Use* |

|---------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------|------|

| Pulse Generator                       | 100 MHz, 3.5 ns pulse width, < 600 ps rise time                                             | HP 8133A Option 003                 | P,T  |

| Digitizing Oscilloscope               | ≥ 6 GHz bandwidth, < 58 ps rise time                                                        | HP 54750A, with<br>HP 54751A plugin | Р    |

| Function Generator                    | Accuracy $\leq$ (5)(10 <sup>-6</sup> ) $\times$ frequency,<br>DC offset voltage $\pm$ 6.3 V | HP 3325B Option 002                 | Р    |

| Digital Multimeter                    | 0.1 mV resolution, 0.005% accuracy                                                          | HP 3458A                            | Р    |

| BNC-Banana Cable                      | •                                                                                           | HP 11001-60001                      | Р    |

| BNC Tee                               | BNC (m)(f)(f)                                                                               | HP 1250-0781                        | Р    |

| Cable                                 | BNC (m)(m) 48 inch                                                                          | HP 10503A                           | P,T  |

| SMA Coax Cable (Qty 3)                | 18 GHz bandwidth                                                                            | HP 8120-4948                        | Р    |

| Adapter (Qty 4)                       | SMA(m)-BNC(f)                                                                               | HP 1250-1200                        | P, T |

| Adapter                               | SMA(f)-BNC(m)                                                                               | HP 1250-2015                        | Р    |

| Coupler (Qty 4)                       | BNC (m)(m)                                                                                  | HP 1250-0216                        | P, T |

| 20:1 Probes (Qty 2)                   |                                                                                             | HP 54006A                           | Р    |

| BNC Test Connector, 17x2<br>(Qty 1)** |                                                                                             |                                     | Р    |

| BNC Test Connector, 6x2<br>(Qty 4)**  |                                                                                             |                                     | P,T  |

| Digitizing Oscilloscope               | > 100 MHz Bandwidth                                                                         | HP 54600B                           | T    |

| BNC Shorting Cap                      |                                                                                             | HP 1250-0074                        | T    |

| BNC-Banana Adapter                    |                                                                                             | HP 1251-2277                        | T    |

| Light Power Meter                     |                                                                                             | United Detector 351                 | Α    |

| Alignment Tool                        |                                                                                             | 8710-1300                           | Α    |

|                                       |                                                                                             |                                     |      |

<sup>\*</sup>A = Adjustment P = Performance Tests T = Troubleshooting \*\*Instructions for making these test connectors are in chapter 3, "Testing Performance."

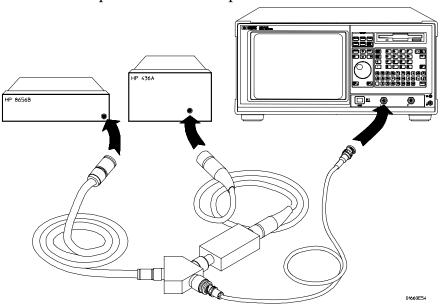

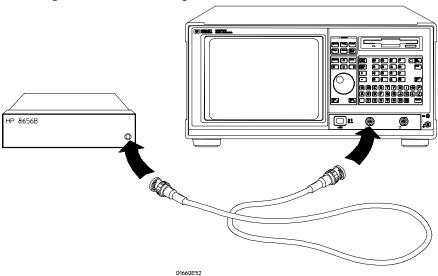

# Recommended test equipment (oscilloscope)

## **Equipment Required**

| Equipment              | Critical Specifications                                                                                         | Recommended<br>Model/Part | Use* |

|------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------|------|

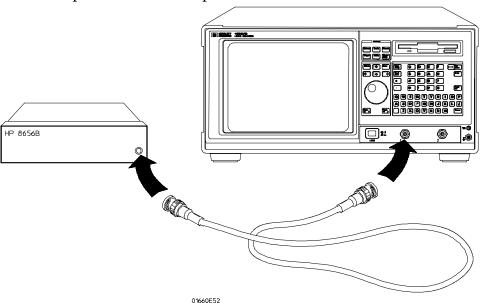

| Signal Generator       | Frequency: 1 - 250 MHz at approx.<br>170 mV RMS<br>Output Accuracy: ± 1 dB<br>1 MHz time base accuracy 0.25 ppm | HP 8656B Option 001       | Р    |

| DC Power Supply        | Range: -35.000 to +35.000 Vdc, ±1 mV                                                                            | HP 3245A Option 002       | Р    |

| Digital Multimeter     | 0.1 mV resolution<br>Accuracy: better than 0.005%<br>Resistance measurement: better than<br>0.25% accuracy      | HP 3458A                  | Р    |

| Power Meter/Sensor     | 1 - 250 MHz ±3% accuracy                                                                                        | HP 436/8482A              | Р    |

| Power Splitter         | Outputs differ by <0.15 dB                                                                                      | HP 11667B                 | Р    |

| Blocking Capacitor     | BNC (m)(f), 0.18 μF, ±200 V                                                                                     | HP 10240B                 | Р    |

| BNC Shorting Cap       |                                                                                                                 | HP 1250-0074              | Р    |

| Adapter                | BNC (f)(f) (UG-914/U)                                                                                           | HP 1250-0080              | С    |

| Adapter                | BNC(f)-to-Dual Banana Plug                                                                                      | HP 1251-2277              | Р    |

| Adapter                | Type N(m)-to-BNC(f)                                                                                             | HP 1250-0780              | Р    |

| BNC Tee                | BNC (m)(f)(f)                                                                                                   | HP 1250-0781              | P,C  |

| Cable                  | Type N(m-to-m) 24-inch                                                                                          | HP 11500B                 | Р    |

| Cable                  | 50 $\Omega$ BNC (m-to-m) 48-inch                                                                                | HP 10503A                 | P, C |

| Cable (2)              | 50 $\Omega$ BNC (m-to-m) 9 inch                                                                                 | HP 10502A                 | С    |

| *P = Performance Tests | C = Calibration                                                                                                 |                           |      |

# Recommended test equipment (pattern generator)

## **Equipment Required**

| Equipment       | Critical Specifications | Recommended<br>Model/Part | Use* |

|-----------------|-------------------------|---------------------------|------|

| Oscilloscope    | ≥ 500 MHz Bandwidth     | HP 54522A                 | T    |

| Probe           | 500 MHz Bandwidth       | HP 10441A                 | T    |

| Output Data Pod | no substitute           | 10460A - series           | T    |

<sup>\*</sup> T = Troubleshooting

To inspect the logic analyzer 2–2

To apply power 2–3

To operate the user interface 2–3

To set the line voltage 2–3

To degauss the display 2–4

To clean the logic analyzer 2–4

To test the logic analyzer 2–4

# Preparing For Use

This chapter gives you instructions for preparing the logic analyzer for use.

## **Power Requirements**

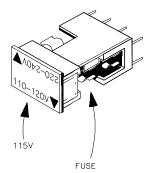

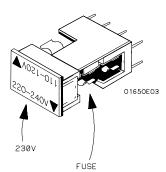

The logic analyzer power source requirements are either 115 V ac or 230 V ac, -22 % to +10 %, single phase, 48 to 66 Hz, 200 Watts maximum power.

## **Operating Environment**

The operating environment is listed in chapter 1. Note the noncondensing humidity limitation listed below. Condensation within the instrument can cause poor operation or malfunction. Provide protection against internal condensation.

The logic analyzer will operate at all specifications within the temperature and humidity range given in chapter 1. However, reliability is enhanced when operating the logic analyzer within the following ranges:

• Temperature: +20 °C to +35 °C (+68 °F to +95 °F)

• Humidity: 20% to 80% noncondensing

### Storage

Store or ship the logic analyzer in environments within the following limits:

• Temperature: -40 °C to + 75 °C (-40 °F to + 167 °F

• Humidity: Up to 90% at 65 °C

• Altitude: Up to 15,300 meters (50,000 feet)

Protect the logic analyzer from temperature extremes which cause condensation on the instrument.

# To inspect the logic analyzer

1 Inspect the shipping container for damage.

If the shipping container or cushioning material is damaged, keep them until you have checked the contents of the shipment and checked the instrument mechanically and electrically.

2 Check the supplied accessories.

Accessories supplied with the logic analyzer are listed in "Accessories" in chapter 1.

3 Inspect the product for physical damage.

Check the logic analyzer and the supplied accessories for obvious physical or mechanical defects. If you find any defects, contact your nearest Hewlett-Packard Sales Office. Arrangements for repair or replacement are made, at Hewlett-Packard's option, without waiting for a claim settlement.

## To apply power

1 Check that the line voltage selector, located on the rear panel, is on the correct setting and the correct fuse is installed.

See also, "To set the line voltage" on this page.

2 Connect the power cord to the instrument and to the power source.

This instrument is equipped with a three-wire power cable. When connected to an appropriate AC power outlet, this cable grounds the instrument cabinet. The type of power cable plug shipped with the instrument depends on the country of destination. Refer to chapter 7, "Replaceable Parts," for option numbers of available power cables and plug configurations.

3 Turn on the instrument power switch located on the bottom of the front panel.

## To operate the user interface

To select a field on the logic analyzer screen, use the arrow keys to highlight the field, then press the Select key. For more information about the logic analyzer interface, refer to the *HP 1660-Series Logic Analyzer User's Guide*.

To set the HP-IB address or to configure for RS-232-C, refer to the *HP 1660-Series Logic Analyzer User's Guide*.

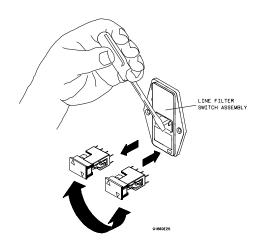

## To set the line voltage

When shipped from HP, the line voltage selector is set and an appropriate fuse is installed for operating the instrument in the country of destination. To operate the instrument from a power source other than the one set, perform the following steps.

- 1 Turn the power switch to the Off position, then remove the power cord from the instrument.

- 2 Remove the fuse module by carefully prying at the top center of the fuse module until you can grasp it and pull it out by hand.

**3** Reinsert the fuse module with the arrow for the appropriate line voltage aligned with the arrow on the line filter assembly switch.

**4** Reconnect the power cord. Turn on the instrument by setting the power switch to the On position.

## To degauss the display

If the logic analyzer has been subjected to strong magnetic fields, the CRT might become magnetized and display data might become distorted. To correct this condition, degauss the CRT with a conventional external television type degaussing coil.

# To clean the logic analyzer

With the instrument turned off and unplugged, use mild soap and water to clean the front and cabinet of the logic analyzer. Harsh soap might damage the water-base paint.

# To test the logic analyzer

- If you require a test to verify the specifications, start at the beginning of chapter 3, "Testing Performance."

- If you require a test to initially accept the operation, perform the self-tests in chapter 3.

- If the logic analyzer does not operate correctly, go to the beginning of chapter 5, "Troubleshooting."

To perform the self-tests 3-3 To make the test connectors (logic analyzer) 3-7 To test the threshold accuracy (logic analyzer) 3-9 To test the glitch capture (logic analyzer) 3–18 To test the single-clock, single-edge, state acquisition (logic analyzer) 3-24 To test the multiple-clock, multiple-edge, state acquisition (logic analyzer) 3–37 To test the single-clock, multiple-edge, state acquisition (logic analyzer) 3-49 To test the time interval accuracy (logic analyzer) 3-60 To test the CAL OUTPUT ports (oscilloscope) 3-65 To test the input resistance (oscilloscope) 3-69 Perform an operational accuracy calibration 3-72 To test the voltage measurement accuracy (oscilloscope) 3-73 To test the offset accuracy (oscilloscope) 3-77 To test the bandwidth (oscilloscope) 3-82 To test the time measurement accuracy (oscilloscope) 3–87 To test the trigger sensitivity (oscilloscope) 3-91 Performance Test Record (logic analyzer) 3–95 Performance Test Record (oscilloscope) 3-101 Performance Test Record (pattern generator) 3–104

# **Testing Performance**

This chapter tells you how to test the performance of the logic analyzer against the specifications listed in chapter 1. To ensure the logic analyzer is operating as specified, you perform software tests (self-tests) and manual performance tests on the analyzer. The logic analyzer is considered performance-verified if all of the software tests and manual performance tests have passed. The procedures in this chapter indicate what constitutes a "Pass" status for each of the tests.

### The Logic Analyzer Interface

To select a field on the logic analyzer screen, use the arrow keys to highlight the field, then press the Select key. For more information about the logic analyzer interface, refer to the *HP 1660 Series Logic Analyzer User's Guide*.

### **Test Strategy**

For a complete test, start at the beginning with the software tests and continue through to the end of the chapter. For an individual test, follow the procedure in the test. The examples in this chapter were performed using an HP 1660CS. Other analyzers in the series will have appropriate pods showing on the screen.

With the HP 1660CS-series Logic Analyzers, ensure that the operational accuracy calibration has been done before doing the performance verification tests (see chapter 4).

The performance verification procedures starting on page 3–8 are each shown from power-up. To exactly duplicate the setups in the tests, save the power-up configuration to a file on a disk, then load that file at the start of each test.

If a test fails, check the test equipment setup, check the connections, and verify adequate grounding. If a test still fails, the most probable cause of failure would be the acquisition board or oscilloscope board.

#### **Test Interval**

Test the performance of the logic analyzer against specifications at two-year intervals or if it is replaced or repaired.

#### **Performance Test Record**

A performance test record for recording the results of each procedure is located at the end of this chapter. Use the performance test record to gauge the performance of the logic analyzer over time.

### **Test Equipment**

Each procedure lists the recommended test equipment. You can use equipment that satisfies the specifications given. However, the procedures are based on using the recommended model or part number. Before testing the performance of the logic analyzer, warmup the instrument and the test equipment for 30 minutes.

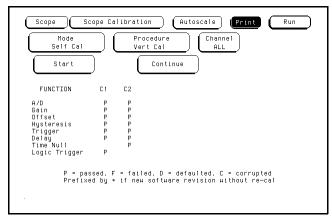

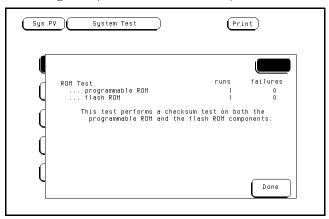

# To perform the self-tests

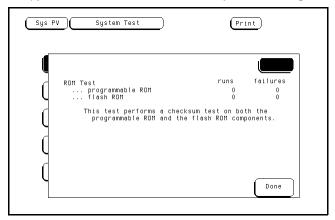

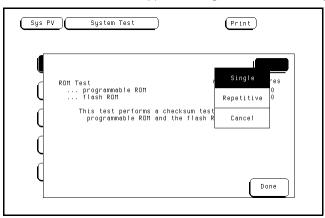

The self-tests verify the correct operation of the logic analyzer. Self-tests can be performed all at once or one at a time. While testing the performance of the logic analyzer, run the self-tests all at once.

The performance verification (PV) self-tests consist of system PV tests, analyzer PV tests, and oscilloscope PV tests (HP 1660CS series only).

These procedures assume the files on the PV disk have been copied to the /SYSTEM subdirectory on the hard disk drive. If they have not already been copied, insert the PV disk in the flexible disk drive before starting this procedure.

- 1 Disconnect all inputs, then turn on the power switch. Wait until the power-up tests are complete.

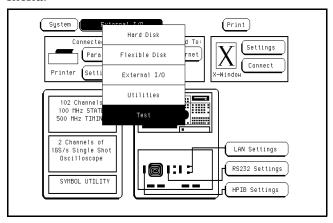

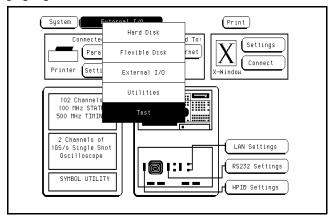

- **2** Press the System key. Select the field next to System, then select Test in the pop-up menu.

- **3** Select the box labeled Load Test System, then select Continue.

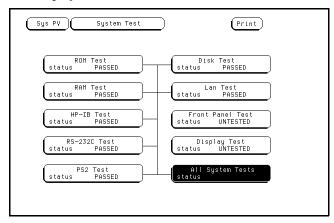

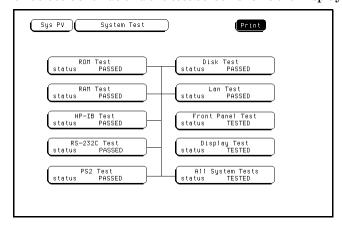

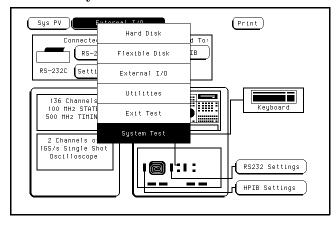

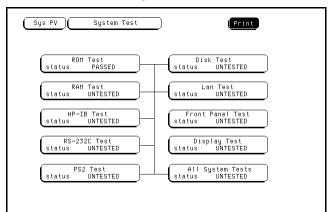

- 4 Press the System key. Select the field next to Sys PV, then select System Test in the pop-up menu.

- **5** Install a formatted disk that is not write-protected into the disk drive. Connect an RS-232-C loopback connector onto the RS-232-C port.

- 6 Select All System Tests.

You can run all tests at one time, except for the Front Panel Test and Display Test, by running All System Tests. To see more details about each test when troubleshooting failures, you can run each test individually. This example shows how to run all tests at once.

When the tests finish, the status for each test shows PASSED or FAILED, and the status for the All System Tests changes from UNTESTED to TESTED. Note that the Front Panel Test and Display Test remain UNTESTED.

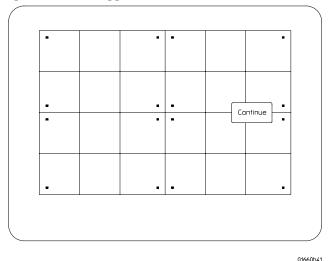

#### 7 Select the Front Panel Test.

A screen duplicating the front panel appears on the screen.

- **a** Press each key on the front panel. The corresponding key on the screen will change from a light to a dark color. Test the knob by turning it in both directions.

- **b** Note any failures, then press the Done key a second time to exit the Front Panel Test. The status of the test changes from UNTESTED to TESTED.

- 8 Select the Display Test.

A white grid pattern is displayed. These display screens are not normally used, but can be used to adjust the display. Refer to chapter 4, "Calibrating and Adjusting" for display adjustments.

- a Select Continue and the screen changes to full bright.

- **b** Select Continue and the screen changes to half bright.

- c Select Continue and the test screen shows the Display Test status changed to Tested.

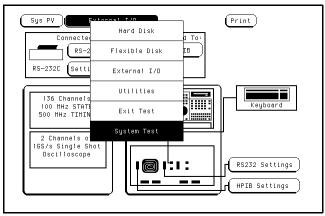

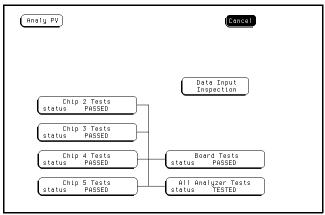

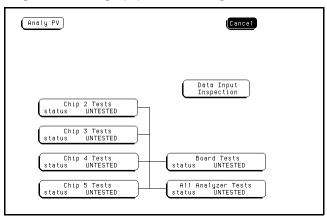

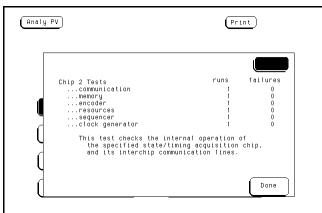

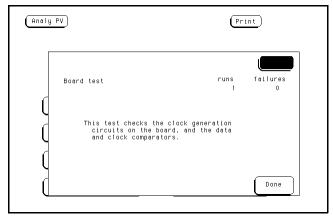

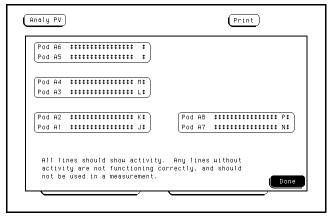

**9** Select Sys PV, then select Analy PV in the pop-up menu. In the Analy PV menu, Select All Analyzer Tests.

You can run all tests at one time, except for the Data Input Inspection, by running All Analyzer Tests. To see more details about each test when troubleshooting failures, you can run each test individually. This example shows how to run all tests at once.

When the tests finish, the status for each test shows Passed or Failed, and the status for the All Analyzer Tests changes from Untested to Tested.

- 10 Record the results of the tests on the performance test record at the end of this chapter.

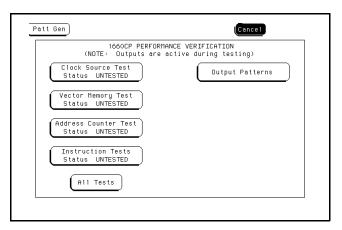

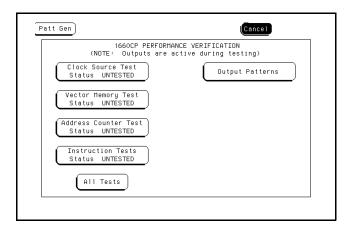

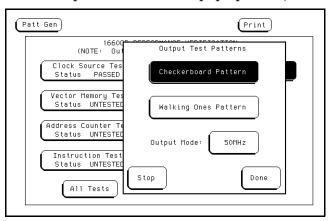

- 11 For the HP 1660CP-series Logic Analyzers, Select Analy PV, then select Patt Gen in the pop-up menu. In the Patt Gen menu select All Tests.

You can run all tests at one time (except the Output Patterns routine) by selecting All Tests. To see more details about each test, you can run each test individually. This example shows how to run all tests at once.

When the tests finish, the status for each test shows Passed or Failed.

12 Record the results of the tests on the performance test record at the end of this chapter, then continue with step 15.

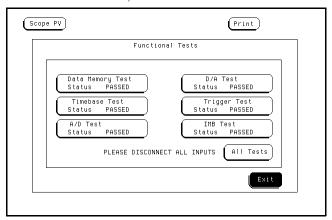

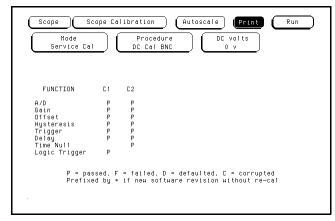

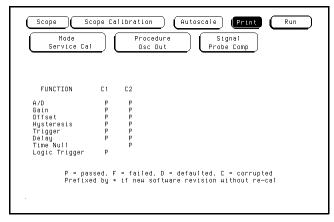

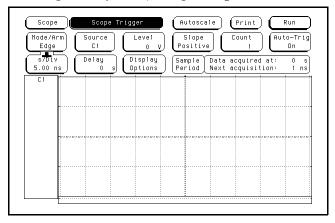

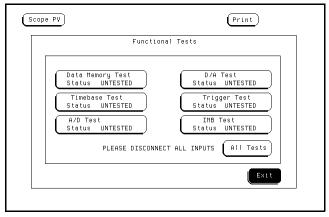

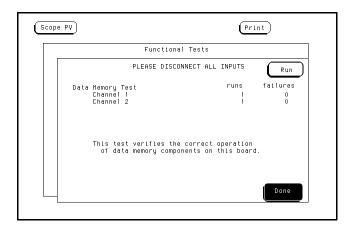

13 For the HP 1660CS-series Logic Analyzers, Select Analy PV, then select Scope PV in the pop-up menu. In the Scope PV menu, select Functional Tests then select All Tests.

You can run all tests at one time, except for the Data Input Inspection, by running All Tests. To see more details about each test when troubleshooting failures, you can run each test individually. This example shows how to run all tests at once.

When the tests finish, the status for each test shows Passed or Failed.

- 14 Record the results of the tests on the performance test record at the end of this chapter.

- 15 To exit the test system, press the System key, then press the Select key. Select Exit Test, then select Exit Test System.

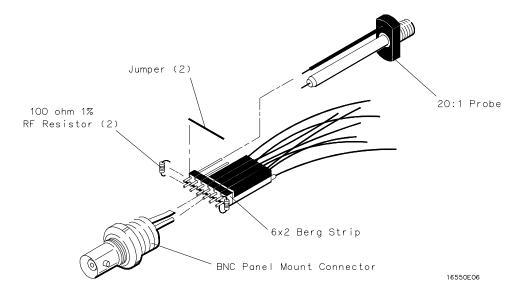

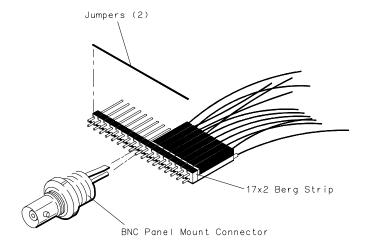

## To make the test connectors (logic analyzer)

The test connectors connect the logic analyzer to the test equipment. The following materials are required to make the test connectors.

#### **Materials Required**

| Description              | Recommended Part | Qty |  |

|--------------------------|------------------|-----|--|

| BNC (f) Connector        | HP 1250-1032     | 5   |  |

| 100 $\Omega$ 1% resistor | HP 0698-7212     | 8   |  |

| Berg Strip, 17-by-2      |                  | 1   |  |

| Berg Strip, 6-by-2       |                  | 4   |  |

| 20:1 Probe               | HP 54006A        | 2   |  |

| Jumper wire              |                  |     |  |

- 1 Build four test connectors using BNC connectors and 6-by-2 sections of Berg strip.

- a Solder a jumper wire to all pins on one side of the Berg strip.

- **b** Solder a jumper wire to all pins on the other side of the Berg strip.

- c Solder two resistors to the Berg strip, one at each end between the end pins.

- **d** Solder the center of the BNC connector to the center pin of one row on the Berg strip.

- **e** Solder the ground tab of the BNC connector to the center pin of the other row on the Berg strip.

- **f** On two of the test connectors, solder a 20:1 probe. The probe ground goes to the same row of pins on the test connector as the BNC ground tab.

- 2 Build one test connector using a BNC connector and a 17-by-2 section of Berg strip.

- a Solder a jumper wire to all pins on one side of the Berg strip.

- ${f b}$  Solder a jumper wire to all pins on the other side of the Berg strip.

- ${f c}$  Solder the center of the BNC connector to the center pin of one row on the Berg strip.

- **d** Solder the ground tab of the BNC connector to the center pin of the other row on the Berg strip.

16550E05

## To test the threshold accuracy (logic analyzer)

Testing the threshold accuracy verifies the performance of the following specification:

#### • Clock and data channel threshold accuracy.

These instructions include detailed steps for testing the threshold settings of pod 1. After testing pod 1, connect and test the rest of the pods one at a time. To test the next pod, follow the detailed steps for pod 1, substituting the next pod for pod 1 in the instructions.

Each threshold test tells you to record the voltage reading in the performance test record located at the end of this chapter. To check if each test passed, verify that the voltage reading you record is within the limits listed on the performance test record.

#### **Equipment Required**

| Equipment                   | Critical Specifications                                                                     | Recommended Model/Part |

|-----------------------------|---------------------------------------------------------------------------------------------|------------------------|

| Digital Multimeter          | 0.1 mV resolution, 0.005% accuracy                                                          | HP 3458A               |

| Function Generator          | Accuracy $\leq$ (5)(10 <sup>-6</sup> ) $\times$ frequency,<br>DC offset voltage $\pm$ 6.3 V | HP 3325B Option 002    |

| BNC-Banana Cable            | 9                                                                                           | HP 11001-60001         |

| BNC Tee                     |                                                                                             | HP 1250-0781           |

| BNC Cable                   |                                                                                             | HP 10503A              |

| BNC Test Connector,<br>17x2 |                                                                                             |                        |

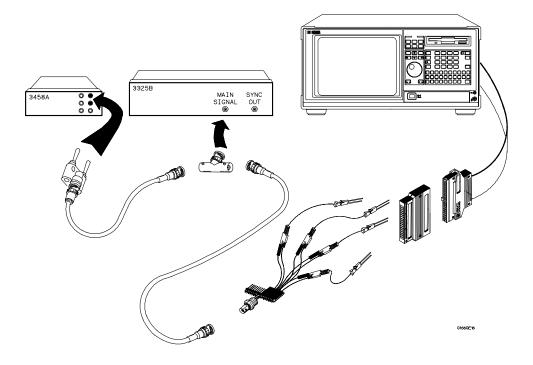

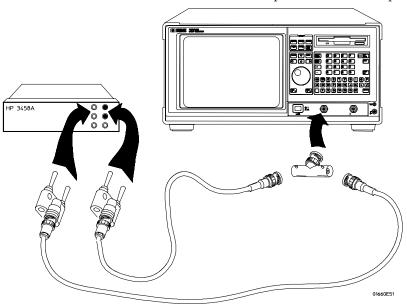

## Set up the equipment

- 1 Turn on the equipment required and the logic analyzer. Let them warm up for 30 minutes before beginning the test.

- **2** Set up the function generator.

- **a** Set up the function generator to provide a DC offset voltage at the Main Signal output.

- **b** Disable any AC voltage to the function generator output, and enable the high voltage output.

- c Monitor the function generator DC output voltage with the multimeter.

## Set up the logic analyzer

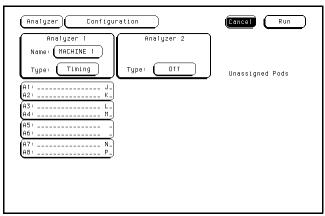

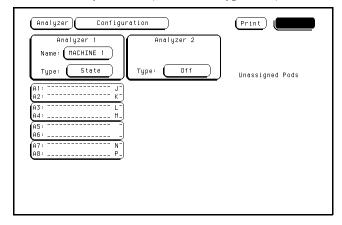

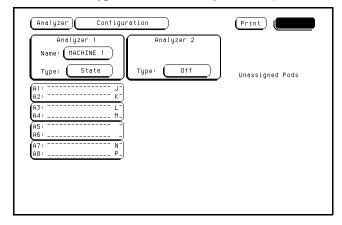

- 1 Press the Config key.

- **2** Unassign Pods 3 and 4, Pods 5 and 6, and Pods 7 and 8. To unassign the pods, select the pod field. In the pop-up menu, select Unassigned.

## Connect the logic analyzer

- 1 Using the 17-by-2 test connector, BNC cable, and probe tip assembly, connect the data and clock channels of pod 1 to one side of the BNC Tee.

- 2 Using a BNC-banana cable, connect the voltmeter to the other side of the BNC Tee.

- **3** Connect the BNC Tee to the Main Signal output of the function generator.

#### Test the TTL threshold

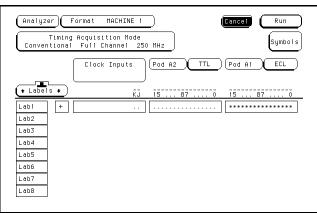

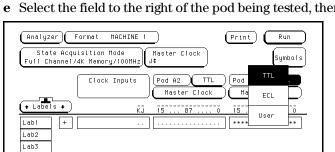

- 1 Press the Format key. Select the field to the right of Pod A1, then select TTL in the pop-up menu.

- 2 On the function generator front panel, enter  $1.750~V\pm 1~mV$  DC offset. Use the multimeter to verify the voltage.

The activity indicators for pod 1 should show all data channels and the J-clock channel at a logic high.

3 Using the Modify down arrow on the function generator, decrease offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels at a logic low. Record the function generator voltage in the performance test record.

4 Using the Modify up arrow on the function generator, increase offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels at a logic high. Record the function generator voltage in the performance test record.

#### Test the ECL threshold

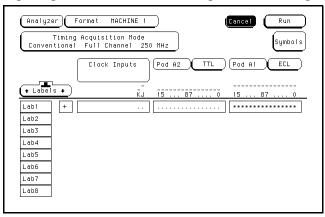

- 1 Select the field to the right of Pod A1, then select ECL in the pop-up menu.

- 2 On the function generator front panel, enter  $-1.160~V\pm 1~mV$  DC offset. Use the multimeter to verify the voltage.

- The activity indicators for pod 1 should show all data channels and the J-clock channel at a logic high.

- **3** Using the Modify down arrow on the function generator, decrease offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels are at a logic low. Record the function generator voltage in the performance test record.

4 Using the Modify up arrow on the function generator, increase offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels are at a logic high. Record the function generator voltage in the performance test record.

#### Test the – User threshold

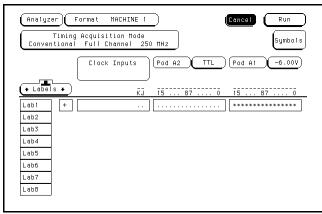

- 1 Move the cursor to the field to the right of Pod A1. Type –6.00, then use the left and right cursor control keys to highlight V. Press the Select key.

- 2 On the function generator front panel, enter –5.718 V ±1 mV DC offset. Use the multimeter to verify the voltage.

- The activity indicators for pod 1 should show all data channels and the J-clock channel at a logic high.

- 3 Using the Modify down arrow on the function generator, decrease offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels at a logic low. Record the function generator voltage in the performance test record.

4 Using the Modify up arrow on the function generator, increase offset voltage in 1-mV increments until all activity indicators show the channels at a logic high. Record the function generator voltage in the performance test record.

#### Test the + User threshold

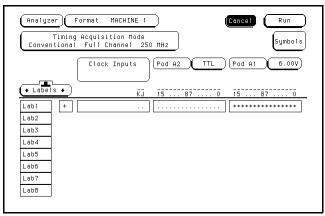

- 1 Move the cursor to the field to the right of Pod A1. Type +6.00, then use the left and right cursor control keys to highlight V. Press the Select key.

- 2 On the function generator front panel, enter +6.282 V ±1 mV DC offset. Use the multimeter to verify the voltage.

- The activity indicators for pod 1 should show all data channels and the J-clock channel at a logic high.

- 3 Using the Modify down arrow on the function generator, decrease offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels at a logic low. Record the function generator voltage in the performance test record.

4 Using the Modify up arrow on the function generator, increase offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels at a logic high. Record the function generator voltage in the performance test record.

#### Test the 0 V User threshold

- 1 Move the cursor to the field to the right of Pod A1. Type 0, then press the Select key.

- 2 On the function generator front panel, enter +0.102 V  $\pm 1$  mV DC offset. Use the multimeter to verify the voltage.

- The activity indicators for pod 1 should show all data channels and the J-clock channel at a logic high.

- 3 Using the Modify down arrow on the function generator, decrease offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels at a logic low. Record the function generator voltage in the performance test record.

4 Using the Modify up arrow on the function generator, increase offset voltage in 1-mV increments until all activity indicators for pod 1 show the channels at a logic high. Record the function generator voltage in the performance test record.

## Test the next pod

- 1 Using the 17-by-2 test connector and probe tip assembly, connect the data and clock channels of the next pod to the output of the function generator until all pods have been tested.

- To unassign a pod pair and assign the next pod pair to be tested, press the Config key. Select the pod pairs, then select assign or unassign in the pop-up menu.

- 2 Start with "Test the TTL threshold" on page 3–11, substituting the next pod to be tested for pod 1.

## To test the glitch capture (logic analyzer)

Testing the glitch capture verifies the performance of the following specification:

#### • Minimum detectable glitch.

This test checks the minimum detectable glitch on sixteen data channels at a time.

#### **Equipment Required**

| Equipment                                                                | Critical Specifications                                                                                    | Recommended Model/Part                                                  |

|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Pulse Generator<br>Digitizing Oscilloscope<br>SMA Coax<br>(Oty 3)        | 100 MHz 3.5 ns pulse width, < 600 ps rise time $\geq$ 6 GHz bandwidth , < 58 ps rise time 18 GHz bandwidth | HP 8133A Option 003<br>HP 54750A, with HP 54751A plugin<br>HP 8120-4948 |

| Adapter (Qty 4)<br>Coupler (Qty 4)<br>BNC Test Connector,<br>6x2 (Qty 4) | SMA(m)-BNC(f)<br>BNC (m)(m)                                                                                | HP 1250-1200<br>HP 1250-0216                                            |

## Set up the equipment

- 1 Turn on the equipment required and the logic analyzer. Let them warm up for 30 minutes before beginning the test if you have not already done so.

- 2 Set up the pulse generator.

#### **Pulse Generator Setup**

| Timebase          | Channel 2                | Period             | Channel 1                   |

|-------------------|--------------------------|--------------------|-----------------------------|

| Mode: Int         | Mode: Pulse              | Divide: Divide ÷ 1 | Mode: Pulse                 |

| Period: 22.000 ns | Divide: PULSE ÷ 1        | Ampl: 0.50 V       | Delay: 0.000 ns             |

|                   | Width: 3.500 ns          | Offs: 0.00 V       | Width: 3.500 ns             |

|                   | High: -0.90 V            |                    | High: -0.90 V               |

|                   | Low: -1.70 V             |                    | Low: -1.70 V                |

|                   | COMP: Disabled (LED Off) |                    | COMP: Disabled<br>(LED Off) |

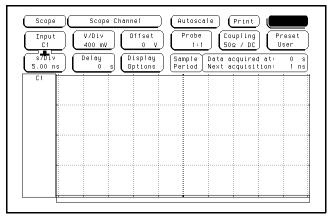

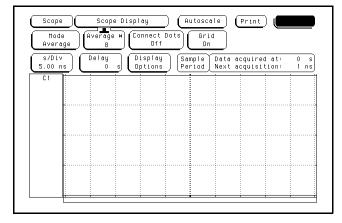

#### **3** Set up the oscilloscope.

#### Oscilloscope Setup

| Time Base             | Display       | Delta V                   | Delta T              |

|-----------------------|---------------|---------------------------|----------------------|

| Time/Div: 1.00 ns/div | mode: avg     | V markers on              | T markers on         |

| delay: 17.7000 ns     | # of avg: 16  | marker 1 position: Chan 1 | start on: Pos Edge 1 |

|                       | screens: dual | marker 2 position: Chan 2 | stop on: Pos Edge 1  |

| Channel               |               |                           |                      |

|                       | Channel 1     | Channel 2                 |                      |

| Display               | on            | on                        |                      |

| Probe Atten           | 20.00         | 20.00                     |                      |

| Volts/Div             | 400 mV        | 400 mV                    |                      |

| Offset                | −1.3000 V     | -1.3000 V                 |                      |

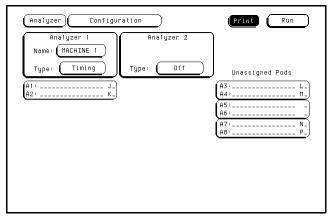

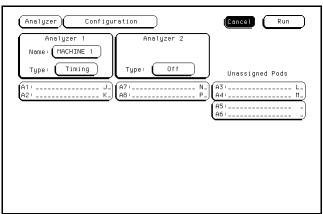

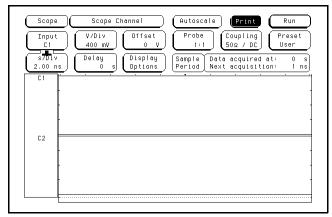

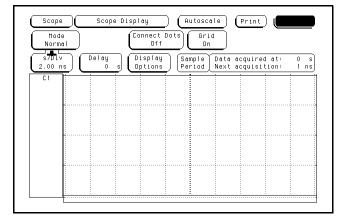

## Set up the logic analyzer

- 1 Press the Config key. Assign all pod fields to Machine 1. To assign the pod fields, select the pod fields, then select Machine 1 in the pop-up menu.

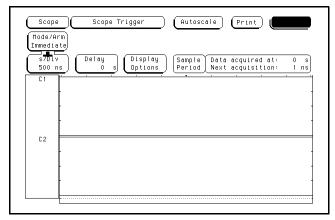

- 2 In the Analyzer 1 box, select the Type field. Select Timing in the pop-up menu.

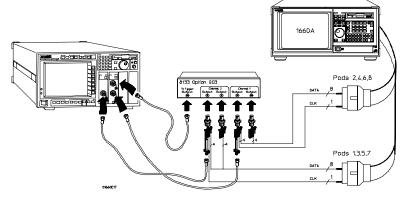

## Connect the logic analyzer

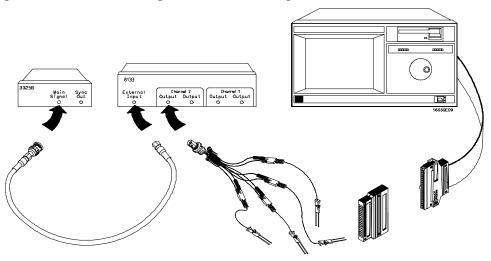

- 1 Using SMA cables, connect the oscilloscope to the pulse generator channel 1 Output, channel 2 Output, and Trig Output.

- 2 Using the 6-by-2 test connectors, connect the first combination of logic analyzer clock and data channels listed in the table to the pulse generator.

You will repeat this test for the remaining combinations.

The table includes all the HP 1660C/CS/CP Series. Use the pods that correspond to your logic analyzer:

- $\bullet~$  HP 1660C/CS/CP pods 1 through 8

- $\bullet~$  HP 1661C/CS/CP pods 1 and 2, pods 3 and 4, and pods 5 and 6

- HP 1662C/CS/CP pods 1 and 2, and pods 3 and 4

- $\bullet$  HP 1663C/CS/CP pods 1 and 2

### Connect the Logic Analyzer to the Pulse Generator

| Testing<br>Combinations | To HP 8133A<br>Channel 2 Output                    | To HP 8133A<br>Channel 2 Output | To HP 8133A<br>Channel 1 Output                    | To HP 8133A<br>Channel 1 Output |

|-------------------------|----------------------------------------------------|---------------------------------|----------------------------------------------------|---------------------------------|

| 1                       | Pod 1<br>ch 0, 2, 4, 6,<br>J-clock                 | Pod 1<br>ch 1, 3, 5, 7          | Pod 3<br>ch 0, 2, 4, 6,<br>L-clock                 | Pod 3<br>ch 1, 3, 5, 7          |

| 2                       | Pod 1<br>ch 8, 10, 12, 14,<br>J-clock              | Pod 1<br>ch 9, 11, 13, 15       | Pod 3<br>ch 8, 10, 12, 14,<br>L-clock              | Pod 3<br>ch 9, 11, 13, 15       |

| 3                       | Pod 2<br>ch 0, 2, 4, 6,<br>K-clock                 | Pod 2<br>ch 1, 3, 5, 7          | Pod 4<br>ch 0, 2, 4, 6,<br>M-clock                 | Pod 4<br>ch 1, 3, 5, 7          |

| 4                       | Pod 2<br>ch 8, 10, 12, 14,<br>K-clock              | Pod 2<br>ch 9, 11, 13, 15       | Pod 4<br>ch 8, 10, 12, 14,<br>M-clock              | Pod 4<br>ch 9, 11, 13, 15       |

| 5                       | Pod 5<br>ch 0, 2, 4, 6,<br>N-clock (1661C only)    | Pod 5<br>ch 1, 3, 5, 7          | Pod 7<br>ch 0, 2, 4, 6,<br>N-clock (1660C only)    | Pod 7<br>ch 1, 3, 5, 7          |

| 6                       | Pod 5<br>ch 8, 10, 12, 14,<br>N-clock (1661C only) | Pod 5<br>ch 9, 11, 13, 15       | Pod 7<br>ch 8, 10, 12, 14,<br>N-clock (1660C only) | Pod 7<br>ch 9, 11, 13, 15       |

| 7                       | Pod 6<br>ch 0, 2, 4, 6,<br>P-clock (1661C only)    | Pod 6<br>ch 1, 3, 5, 7          | Pod 8<br>ch 0, 2, 4, 6,<br>P-clock (1660C only)    | Pod 8<br>ch 1, 3, 5, 7          |

| 8                       | Pod 6<br>ch 8, 10, 12, 14,<br>P-clock (1661C only) | Pod 6<br>ch 9, 11, 13, 15       | Pod 8<br>ch 8, 10, 12, 14,<br>P-clock (1660C only) | Pod 8<br>ch 9, 11, 13, 15       |

|                         |                                                    |                                 |                                                    |                                 |

## Test the glitch capture on the connected channels

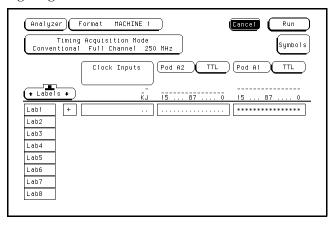

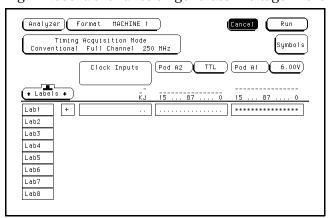

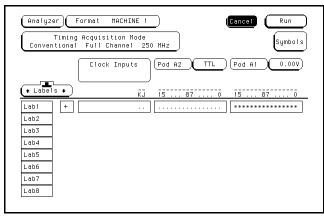

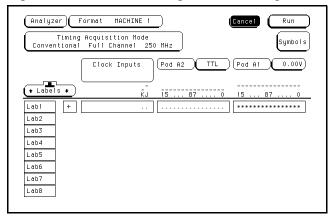

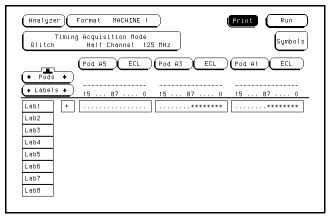

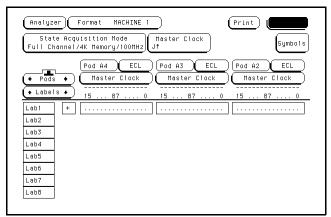

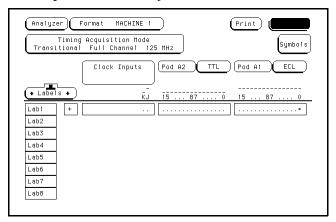

- 1 Set up the Format menu.

- a Press the Format key.

- **b** Select the field to the right of each pod, then select ECL in the pop-up menu. Use the knob to access pods not shown on the screen (to activate the knob for pods, use the cursor to select the Pods field and push Select).

- c Select Timing Acquisition Mode, then select Glitch Half Channel 125 MHz.

- 2 Turn on the channels that correspond to the channels being tested.

The channels being tested are the channels connected to the pulse generator in "Connect the logic analyzer."

- a Select the pod field, then select one of the two pods in the pop-up. Move the cursor to the channel assignment field of the pod and press the Clear entry key until all channels of the pod are de-assigned (all periods). Press the Done key.

- **b** Select the bit assignment field for the pod. Using the arrow keys, move the selector to a channel, then press the Select key. An asterisk means that the channel is turned on. Press the Done key when the channels being tested are turned on.

- **c** Access the next pod, then turn on the channels being tested until all pod channels being tested are turned on.

- **d** Turn on the clock/data channels that correspond to the clocks being tested. Turn off the data channels and clock/data channels that are not being tested.

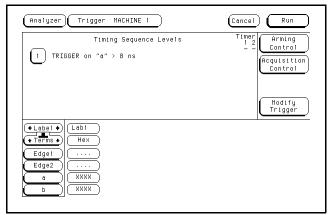

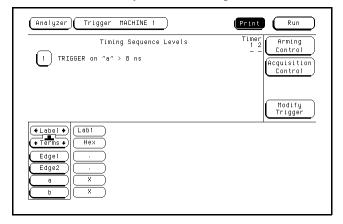

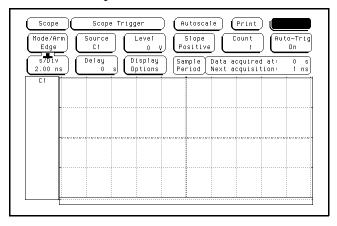

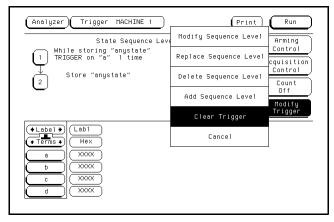

- 3 Set up the Trigger menu.

- a Press the Trigger key.

- **b** Select Modify Trigger, then select Clear Trigger, then select All.

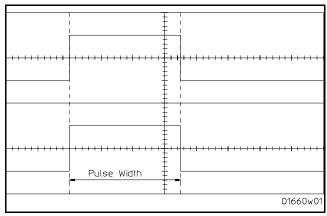

4 Using the [Shift] + width: channel 1 and [Shift] + width: channel 2 of the oscilloscope, verify that the pulse widths of the pulse generator channels 1 and 2 are 3.450 ns, +50 ps or -100 ps. If necessary, adjust the pulse widths of the pulse generator channels 1 and 2.

- **5** Set up the Waveform menu to view all the channels.

- a Select one of the Glitch labels, then select Delete All in the pop-up menu.

- **b** Select All, then select continue.

- **c** Press the Select key, then select Insert in the pop-up menu.

- d Press the Select key, then select Sequential in the pop-up menu.

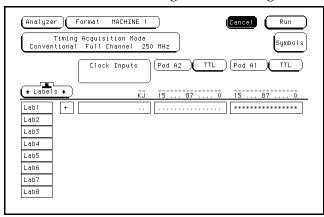

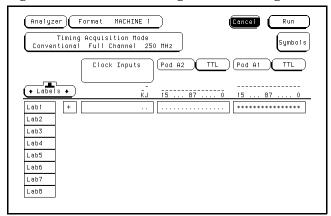

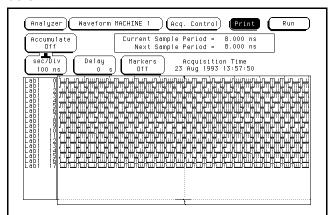

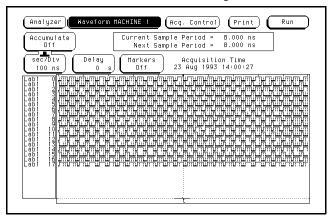

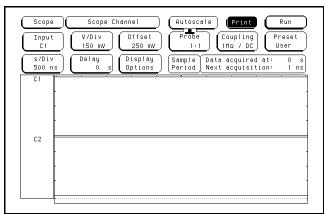

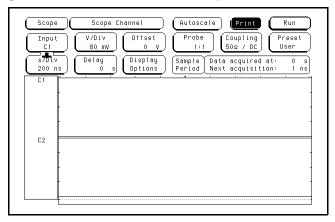

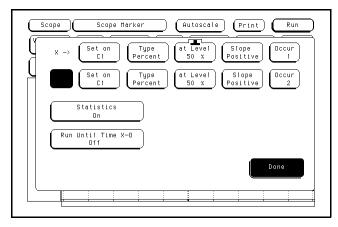

**6** On the logic analyzer, press the Run key. The display should be similar to the figure below.

- 7 On the pulse generator, enable Channel 1 and Channel 2 COMP (with the LED on).

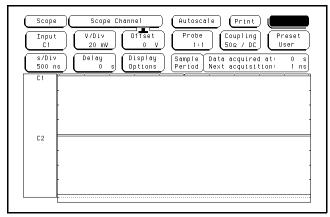

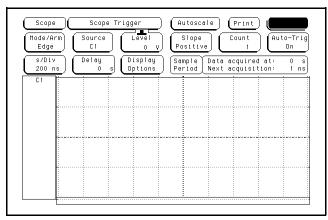

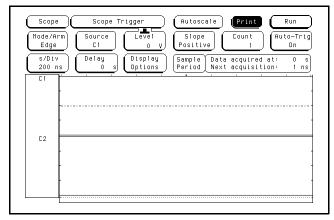

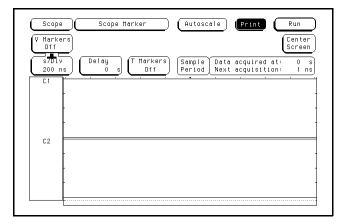

- 8 On the logic analyzer, press the Run key. The display should be similar to the figure below. Record Pass or Fail in the performance test record.

#### Test the next channels

• Return to "Connect the logic analyzer" on page 3–19 and connect and test the next combination of data and clock channels until all pods are tested.

To access pods 2, 4, 6, or 8 in the Format menu, select pods 1, 3, 5, or 7 fields, then select the other pod in the pop-up menu. Use the knob to access pods that are not shown on the screen.

## To test the single-clock, single-edge, state acquisition (logic analyzer)

Testing the single-clock, single-edge, state acquisition verifies the performance of the following specifications:

- Minimum master-to-master clock time

- Maximum state acquisition speed

- Setup/Hold time for single-clock, single-edge, state acquisition

- Minimum clock pulse width

This test checks two combinations of data channels using a single-edge clock at three selected setup/hold times.

#### **Equipment Required**

| Equipment                                     | Critical Specifications                        | Recommended Model/Part           |

|-----------------------------------------------|------------------------------------------------|----------------------------------|

| Pulse Generator                               | 100 MHz 3.5 ns pulse width, < 600 ps rise time | HP 8133A option 003              |

| Digitizing Oscilloscope                       | ≥ 6 GHz bandwidth, < 58 ps rise time           | HP 54750A, with HP 54751A plugin |

| Adapter                                       | SMA(m)-BNC(f)                                  | HP 1250-1200                     |

| SMA Coax Cable (Qty 3)                        | 18 GHz bandwidth                               | HP 8120-4948                     |

| Coupler<br>BNC Test Connector,<br>6x2 (Qty 4) | BNC(m)(m)                                      | HP 1250-0216                     |

## Set up the equipment

- 1 Turn on the equipment required and the logic analyzer. Let them warm up for 30 minutes before beginning the test if you have not already done so.

- **2** Set up the pulse generator.

- a Set up the pulse generator according to the following table.

#### **Pulse Generator Setup**

| Timebase          | Channel 2         | Period             | Channel 1       |

|-------------------|-------------------|--------------------|-----------------|

| Mode: Int         | Mode: Pulse       | Divide: Divide ÷ 2 | Mode: Pulse     |

| Period: 10.000 ns | Divide: PULSE ÷ 2 | Ampl: 0.50 V       | Delay: 0.000 ns |

|                   | Width: 3.500 ns   | Offs: 0.00 V       | Width: 3.500 ns |

|                   | High: -0.90 V     |                    | High: -0.90 V   |

|                   | Low: -1.70 V      |                    | Low: −1.70 V    |

**b** Disable the pulse generator channel 1 COMP (with the LED off).

- **3** Set up the oscilloscope. If the oscilloscope was not configured for the previous test, then do the following steps.

- a Select Setup, then select Default Setup.

- **b** Configure the oscilloscope according to the following table.

#### Oscilloscope Setup Acquisition Display Trigger [Shift] $\Delta$ Time Averaging: On Graticule Level: -250 mV Stop src: channel 2 [Enter] # of averages: 16 Graphs: 2 Channel 1 Channel 2 Define meas Alternate Scale Alternate Scale Thresholds: user-defined Attenuation: 20.00:1 Attenuation: 20.00:1 Units: Volts Upper: -980 mV Scale: 200 mV/div Scale: 200 mV/div Offset: -1.300 V Offset: -1.300 V Middle: -1.30 V Lower: -1.62 V

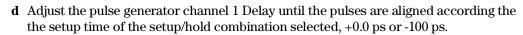

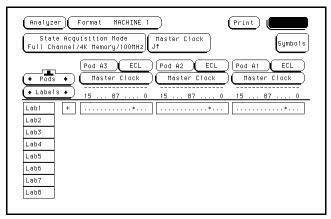

## Set up the logic analyzer

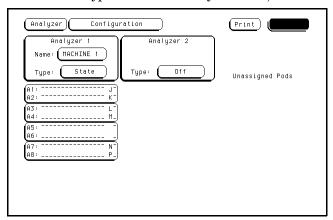

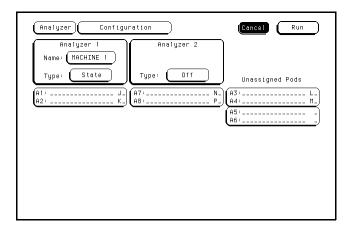

- 1 Set up the Configuration menu.

- a Press the Config key.

- **b** In the Configuration menu, assign all pods to Machine 1. To assign the pods, select the pod fields, then select Machine 1 in the pop-up menu.

- c Select the Type field in the Analyzer 1 box, then select State.

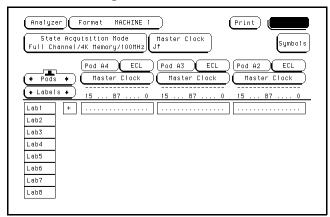

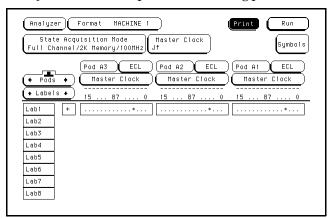

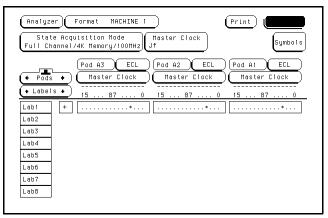

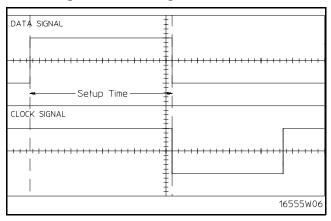

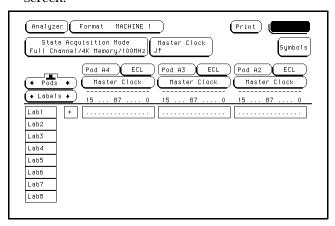

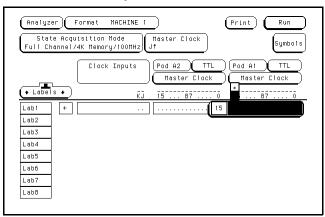

- 2 Set up the Format menu.

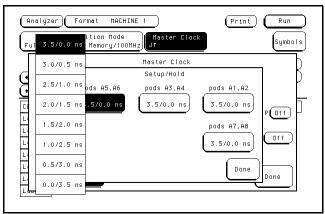

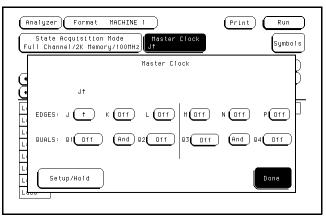

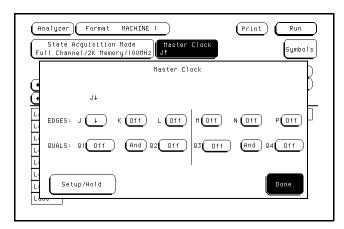

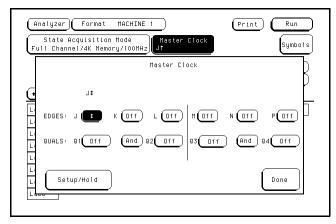

- a Press the Format key. Select State Acquisition Mode, then select Full Channel/4K Memory/100MHz.

- **b** Select the field to the right of each pod, then select ECL in the pop-up menu. Use the knob to access pods not shown on the screen.

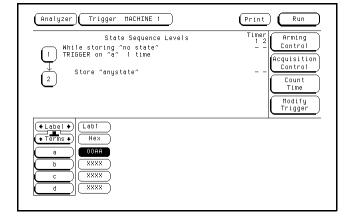

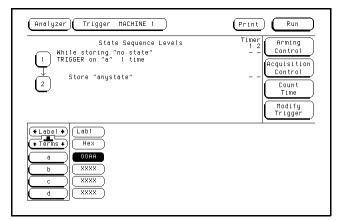

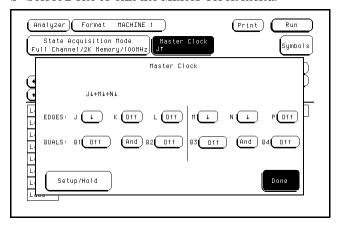

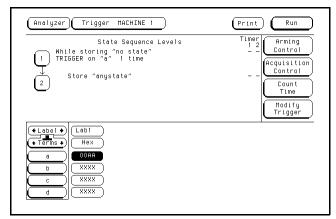

- **3** Set up the Trigger menu.

- **a** Press the Trigger key. Select Modify Trigger, select Clear Trigger, then select All in the pop-up menu.

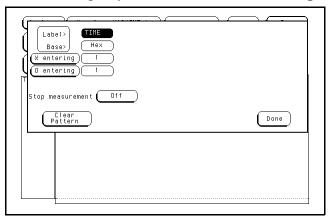

- **b** Select Count Off. Press Select again, then select Time in the pop-up menu. Select Done to exit the menu.

- **c** Select the field labeled 1 under the State Sequence Levels. Select the field labeled "anystate," then select "no state." Select Done to exit the State Sequence Levels menu.

- **d** Select the field next to "a," under the label Lab1. Type the following for your logic analyzer, then press the Select key.

HP 1660C/CS – "00AA" HP 1662C/CS – "00AA" HP 1661C/CS – "002A" HP 1663C/CS – "000A"

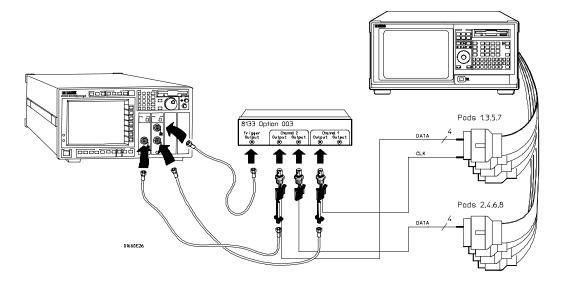

## Connect the logic analyzer

- 1 Using the 6-by-2 test connectors, connect the first combination of logic analyzer clock and data channels listed in one of the following tables to the pulse generator. If you are testing an HP 1660C or HP 1661C, you will repeat this test for the second combination.

- 2 Using SMA cables, connect the oscilloscope to the pulse generator channel 1 Output, channel 2 Output, and Trig Output.

#### Connect the HP 1660C/CS/CP or HP 1661C/CS/CP Logic Analyzer to the Pulse Generator

| Testing<br>Combinations | Connect to<br>HP 8133A<br>Channel 2 Output                                       | Connect to<br>HP 8133A Channel<br>2 Output                                       | Connect to<br>HP 8133A Channel<br>1 Output |

|-------------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------|

| 1                       | Pod 1, channel 3<br>Pod 3, channel 3<br>Pod 5, channel 3<br>Pod 7, channel 3     | Pod 2, channel 3<br>Pod 4, channel 3<br>Pod 6, channel 3<br>Pod 8, channel 3     | J-clock                                    |

| 2                       | Pod 1, channel 11<br>Pod 3, channel 11<br>Pod 5, channel 11<br>Pod 7, channel 11 | Pod 2, channel 11<br>Pod 4, channel 11<br>Pod 6, channel 11<br>Pod 8, channel 11 | J-clock                                    |

#### Connect the HP 1662C or HP 1663C Logic Analyzer to the Pulse Generator