# HP 16510B Logic Analyzer Module for the HP 16500A Logic Analysis System

# **Getting Started Guide**

# **Getting Started Guide**

# HP 16510B Logic Analyzer Module

for the HP 16500A Logic Analysis System

©Copyright Hewlett-Packard Company 1989

Publication Number 5952-0173

Printed in the U.S.A. July 1989

This guide teaches you the basic operation of the HP 16510B Logic Analyzer Module for the HP 16500A Logic Analysis System. It is organized in a task-oriented format that guides you through the touch-screen menus and basic measurements that you will use to solve digital system problems.

You should read this guide and perform the learning tasks once you have become familiar with the operation of the HP 16500A mainframe.

If you are an experienced HP logic analyzer user but new to this family of logic analyzers, you may want to go directly to the *HP 16510B Front-Panel Reference*, but we would like to suggest that you read chapters 1 through 4 of this guide first. These chapters describe the basics of the user interface and will only take a few minutes to go through. The user interfaces of the HP 16500A Logic Analysis System and its modules are very friendly and easy to learn.

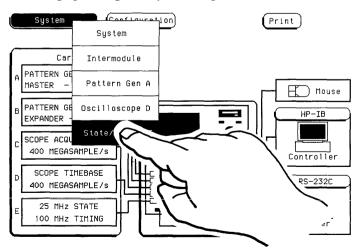

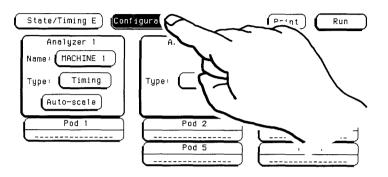

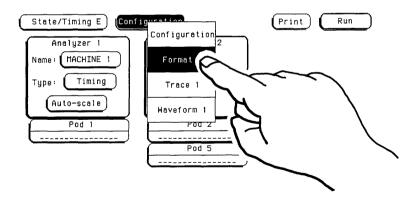

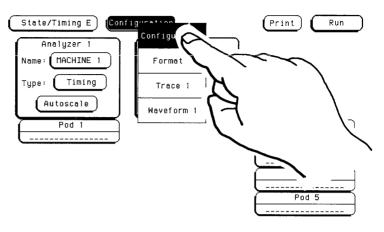

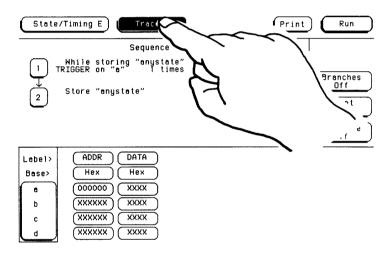

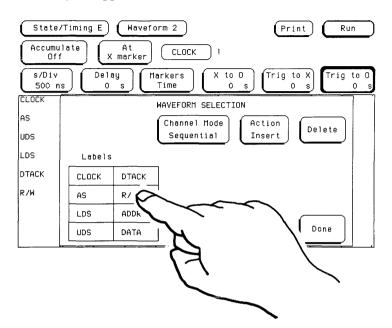

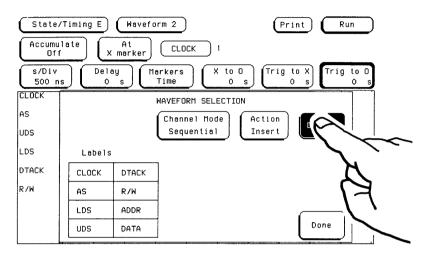

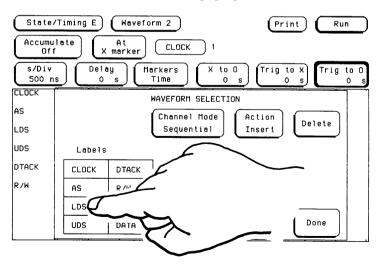

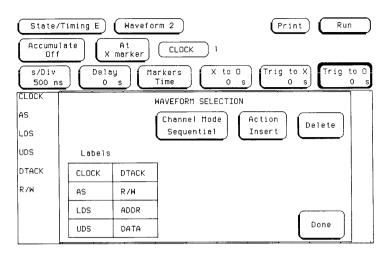

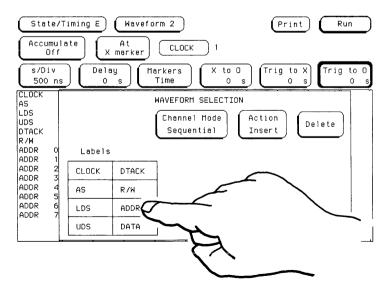

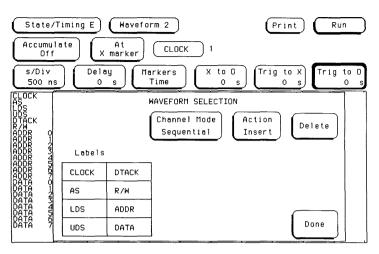

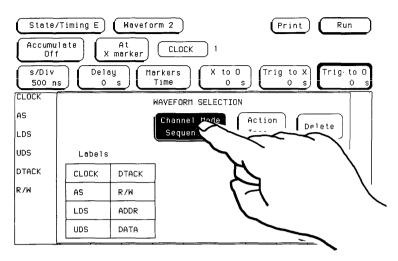

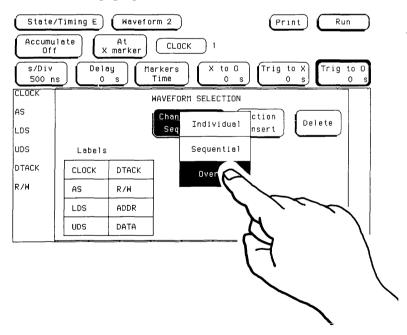

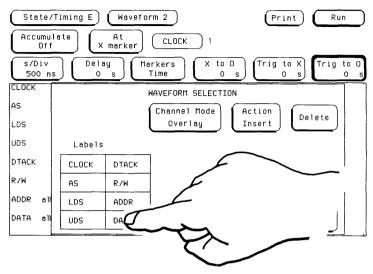

This guide is formatted to help you through setups and measurements in the shortest time possible. To that end, you will occasionally see illustrations interspersed with or alongside the text showing a menu with a hand pointing to the field we are talking about. If you are going through a sequence for the first time, you may want to refer to the illustrations while reading the text to aid your understanding. If you know the basic operation and just need to refresh your memory about the sequence, you can follow the same steps without reading the text by just referring to the illustrations.

# Introduction

| About this<br>book | Welcome to the new generation of HP logic analyzers! The HP 16500A<br>Logic Analysis System has been designed to make it easier to use than<br>any previous Hewlett-Packard logic analyzer. And because of its<br>configurable architecture, it can easily be tailored to you specific logic<br>design and debug needs.                                                                             |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | The user interface of the HP 16500A was designed to be as easy to<br>operate as possible. The use of "pop up" windows and color graphics<br>help lead you through setups and measurements without having to<br>memorize a lot of steps. As you read this and the other references<br>about the mainframe and the acquisition modules, you will see just how<br>easy to use the HP 16500A really is. |

|                    | We do not, however, try to cover every feature and function of the HP 16510B Logic Analyzer Module in this guide. That's the job of your <i>HP 16510B Front-Panel Reference</i> .                                                                                                                                                                                                                   |

|                    | If you're new to logic analysis or just need a refresher, we think you'll find <i>Feeling Comfortable With Logic Analyzers</i> valuable reading. It will help you sort out any confusion you may have about their application and show you how to get the most out of your new logic analyzer.                                                                                                      |

|                    | If you haven't already read "How to Use This Guide", you should do so<br>now. It will help get you started in the right direction.                                                                                                                                                                                                                                                                  |

# Contents

| Chapter 1: | What is the HP 16510B                   |            |

|------------|-----------------------------------------|------------|

| Chapter 2: | Cables and Probes                       |            |

|            | Introduction                            | <b>~</b> 1 |

|            | What Cables and Probes Are Included?    |            |

|            | Probe Assembly Identification           |            |

|            | Connecting Pods to Probe Cables         |            |

|            | Disconnecting Probes from Pods          |            |

|            | Connecting Grabbers to Probes           |            |

|            | Connecting Grabbers to Test Points      |            |

|            | Pod Grounds                             |            |

|            | Probe Grounds                           |            |

|            | Labeling Pods Probes and Cables         |            |

|            | Signal Line Loading                     |            |

|            | Probe Interface                         |            |

|            | Summary                                 |            |

|            | Summary                                 | 2-9        |

| Chapter 3: | Getting to the Logic Analyzer Menus     |            |

| -          | Touch or Mouse?                         | 3-1        |

|            | System Power Up                         |            |

|            | Moving to the Logic Analyzer            |            |

|            | Getting Back to System Level            |            |

| Chapter 4: | Learning the Basic Logic Analyzer Menus |            |

|            |                                         | 11         |

|            | Introduction                            |            |

|            | Selector Pop-up Menu                    |            |

|            | Assigning Pods                          |            |

|            | Choosing Specification Menus            |            |

|            | Alpha Entry Pop-up Menu                 |            |

|            | Changing Alpha Entries                  |            |

|            | Numeric Entry Menus                     |            |

|            | Assignment/ Specification Menus         |            |

|            | Assigning Bits to Pods                  |            |

|            | Specifying Patterns4-                   | ·17        |

| Specifying Edges | <br> |

|------------------|------|

| Summary          | <br> |

| Chapter 5: | Using the Timing Analyzer                |  |

|------------|------------------------------------------|--|

| -          | Introduction                             |  |

|            | Problem Solving with the Timing Analyzer |  |

|            | What Am I Going to Measure?              |  |

|            | How Do I Configure the Logic Analyzer?   |  |

|            | Connecting the Probes                    |  |

|            | Activity Indicators                      |  |

|            | Configuring the Timing Analyzer          |  |

|            | Specifying a Trigger Condition           |  |

|            | Acquiring the Data                       |  |

|            | The Timing Waveform Menu                 |  |

|            | Display Resolution                       |  |

|            | The Timing Markers                       |  |

|            | Making the Measurement                   |  |

|            | Finding the Answer                       |  |

|            | Summary                                  |  |

### Chapter 6:

### Using the State Analyzer

| ]  | Introduction                            | 6-1   |

|----|-----------------------------------------|-------|

| ]  | Problem Solving with the State Analyzer | 6-2   |

|    | What Am I Going to Measure?             |       |

| ]  | How Do I Configure the Logic Analyzer?  | 6-4   |

| (  | Connecting the Probes                   | 6-9   |

| 4  | Activity Indicators                     | 6-9   |

| (  | Configuring the State Analyzer          | .6-10 |

|    | Specifying the J Clock                  | .6-16 |

| \$ | Specifying a Trigger Condition          | .6-19 |

|    | Acquiring the Data                      | .6-24 |

| 5  | The State Listing                       | .6-26 |

| ]  | Finding the Answer                      | .6-27 |

| S  | Summary                                 | .6-29 |

|    |                                         |       |

| Chapter 7: | Using the Timing/State Analyzer                |  |

|------------|------------------------------------------------|--|

|            | Introduction                                   |  |

|            | Problem Solving with the Timing/State Analyzer |  |

|            | What Am I Going to Measure?                    |  |

|            | How Do I Configure the Logic Analyzer?         |  |

|            | Configuring the State Analyzer                 |  |

|            | Connecting The Probes                          |  |

|            | Acquiring the Data                             |  |

|            | Finding the Problem                            |  |

|            | What Additional Measurements Must I Make?      |  |

|            | How Do I Re-configure the Logic Analyzer?      |  |

|            | Configuring the Timing Analyzer                |  |

|            | Setting the Timing Analyzer Trigger            |  |

|            | Time-Correlating the Data                      |  |

|            | Connecting the Timing Analyzer Probes          |  |

|            | The Timing Waveform Menu                       |  |

|            | Displaying the Waveforms                       |  |

|            | Overlapping Timing Waveforms                   |  |

|            | Re-acquiring the Data                          |  |

|            | Mixed Mode Display                             |  |

|            | Finding the Answer                             |  |

|            | Summary                                        |  |

Chapter 8:

What Next?

# What is the HP 16510B

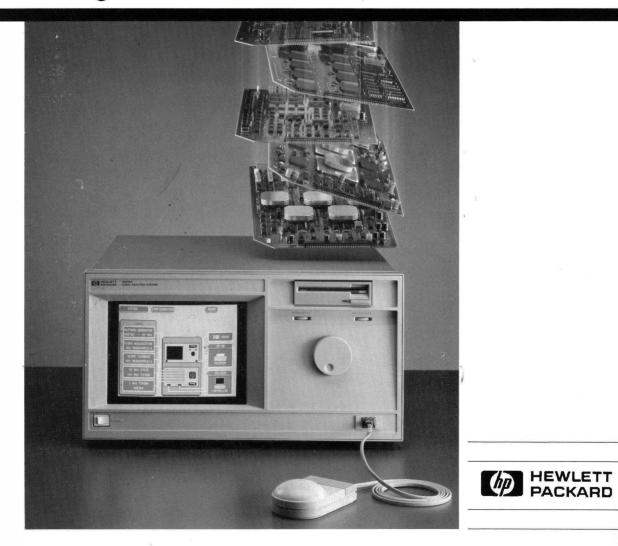

The HP 16510B Logic Analyzer is a programmable logic analyzer module that is installed in the HP 16500A Logic Analysis System. It offers 80 data channels, thus allowing the HP 16500A to have up to 400 channels when configured with five HP 16510B cards. It is capable of 100 MHz timing and 35 MHz state analysis on all channels.

The key features of the HP 16510B are:

- Transitional or glitch timing modes

- Simultaneous state/state or state/timing modes

- 1k-deep memory on all channels

- Glitch detection on all channels

- Marker measurements

- Pattern, edge, and glitch triggering

- Overlapping of timing waveform

- Eight sequence levels

- Eight pattern recognizers

- One range recognizer

- Small, lightweight probing

- Time and number of state tagging

- Pre-store

- State Compare

- State Waveform

- State Chart

Not all of these features will be covered in this *Getting Started Guide*. However, you can find the details of these and all the features of the HP 16510B in the *HP 16510B Front-Panel Reference*.

## **Cables and Probes**

| This chapter describes the cables and probes that connect the HP 16510B module to your test system. If your system was ordered without the cards (PC boards) installed, or if you want to move the cards to another instrument, refer to the HP 16510B Front-Panel |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reference.                                                                                                                                                                                                                                                         |

### What Cables and Probes Are Included?

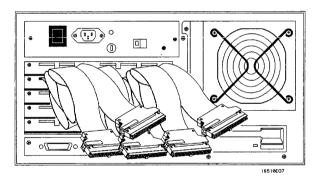

The cables are already connected when you receive your instrument, exiting via the rear panel. Each card comes with five 1.4 m (4.5 ft.) 2 by 20, ribbon cables.

The cable for pod 1 is the far left cable (rear view). Cables 2 through 5 follow cable 1 consecutively from left to right.

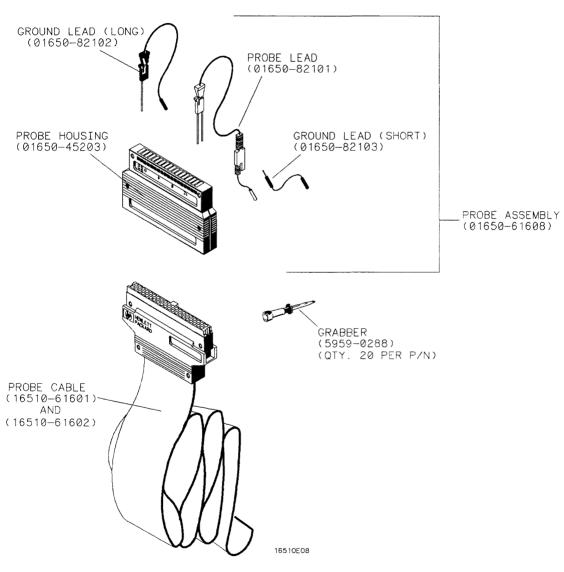

It also comes with one bag of probes, leads and grabbers. This bag contains five sets of each of the following:

- 1 probe pod

- 17 acquisition probes

- 1 pod ground

- 2 probe grounds

- 20 grabbers

### Probe Assembly Identification

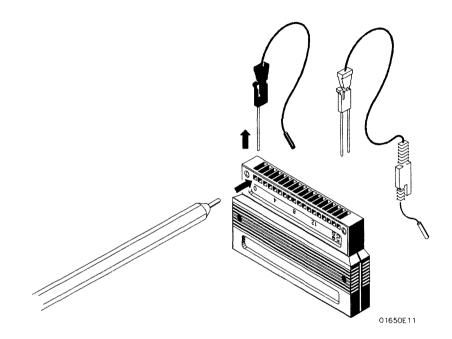

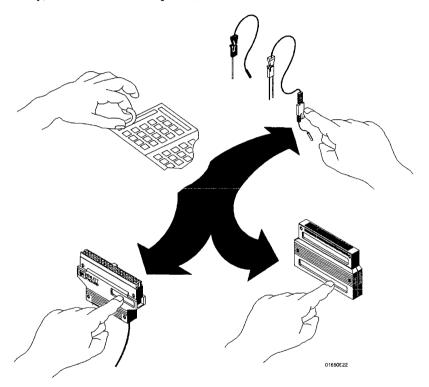

The illustration below identifies the different probes and assemblies used to connect to a test system.

Cables and Probes 2-2

HP 16510B Getting Started Guide

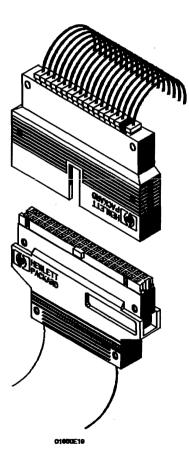

### Connecting Pods to Probe Cables

The pods of the HP 16510B differ from those of other logic analyzers in that they are passive (have no active circuits at the outer end of the cable). The pods are the connector bodies in which the probes are installed when you receive your instrument. To connect the pod to the cable, align the key on the cable connector with the slot on the pod connector and push them together.

### Disconnecting Probes from Pods

You can disconnect un-used probes from the pods to eliminate clutter. To disconnect a probe, insert the tip of a ball-point pen into the latch opening and push while gently pulling the probe out of the pod connector as shown below.

To reconnect a probe, insert the double-pin end of the probe into the pod. The probes and pod connector body are both keyed (chamfered) so that they will fit together in only one way.

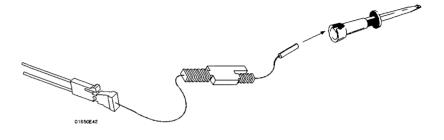

### Connecting Grabbers to Probes

Connect the grabbers to the probes by slipping the connector at the end of the probe onto the recessed pin in the side of the grabber as shown below.

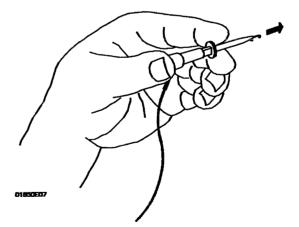

Connecting Grabbers to Test Points

The grabbers have a hook that fits around IC pins and component leads. You connect the grabber by pushing the rear of the grabber to expose the hook, hooking the lead, and releasing your thumb as shown below.

| Pod Grounds   | Each pod has a separate ground lead that allows you to connect the ground side of all the probes to a common ground. Connect it directly or with a grabber to a ground point on your test system. Connect the grabber to the ground lead by slipping the connector of the lead onto the recessed pin in the side of the grabber. |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | To connect the ground lead directly to the ground pins on the test system, the pins must be $0.63 \text{ mm} (0.025 \text{ in.})$ square pins or round pins with a diameter from $0.66 \text{ mm} (0.026 \text{ in.})$ to $0.84 \text{ mm} (0.033 \text{ in.})$ .                                                                |

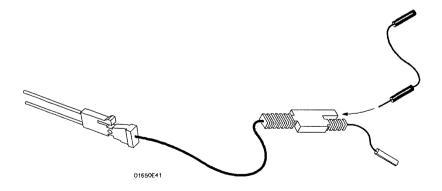

| Probe Grounds | You can ground the probes in one of two ways. You can ground them<br>with the pod ground only; however, the ground path won't be the same                                                                                                                                                                                        |

with the pod ground only; however, the ground path won't be the same length as the signal path through the probe. If your probe ground path must be the same as your signal path, use the short ground lead (probe ground). The probe ground lead connects to the probe body via a pin and socket as shown below. A grabber can be used to connect the probe ground to the test system, or it can be connected directly to square 0.63 mm (0.025 in.) or round 0.66 mm (0.026 in.) pins on the test system.

If you need additional probe ground leads, order HP part number 01650-82103 from your nearest Hewlett-Packard sales office.

HP 16510B Getting Started Guide

Cables and Probes 2-6

### Labeling Pods Probes and Cables

Included with your logic analyzer are self-adhesive labels you can attach to each pod, cable and probe. These provide a means of quickly locating and identifying the desired probes and pods for easy accurate connections.

The labels come in sets. Each set has a label for the pod connector body, a label for the clock probe, and 16 labels for each of the channels.

| Signal Line<br>Loading | Any signal line to be connected to a probe must be able to supply a minimum of 600 mV to the probe tip, which has an input impedance of 100 k $\Omega$ shunted by 8 pF. If the signal line can't supply this voltage, not only will you get an incorrect measurement, the system under test could malfunction.                                                                                                                                                                                                                                                                                                                                           |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Probe Interface        | Instead of connecting the probe tips directly to the signal lines, you may<br>use the HP 10269C Probe Interface (optional accessory). It allows you<br>to connect the pod cables (without the probes) to connectors on the<br>interface. When the appropriate preprocessor is installed in the<br>interface, you will have a way to connect the interface directly to the<br>microprocessor under test. A number of microprocessor-specific<br>preprocessors are available as optional accessories. They are listed in<br>the <i>HP 16510B Front-Panel Reference</i> along with additional details on<br>how the probe interface and preprocessors work. |

# SummaryThis chapter acquainted you with:• what cables and probes are included with the module;• how to identify the different probe assemblies;• how to identify the different probe assemblies;• how to connect the pods to the cables;• how to connect and disconnect the probes from the pods;• how to connect and use the grabbers;• how to connect and use the grabbers;• the pod and probe grounds;• labeling the probes, pods and cables;• the minimum output for a signal line that you want to measure.For more information on the probes and cables, refer to theHP 16510B Front-Panel Reference.

# **Getting to the Logic Analyzer Menus**

| Touch or<br>Mouse? | Before talking about the actual operation of the HP 16510B, we should<br>mention that it has three user interface devices: the knob on the front<br>panel, the touch-sensitive screen, and the optional mouse. If you are<br>unfamiliar with their use, refer to the <i>Front-Panel Reference</i> for the<br>HP 16500A mainframe.                                                |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | "Touching" in this guide means touching the screen or using the mouse.<br>For example, if the guide says to touch a specific field, it means you<br>may touch that field on the screen (provided the touch screen is<br>activated) or you may move the cursor to that field with the mouse and<br>press the left button on the mouse.                                            |  |

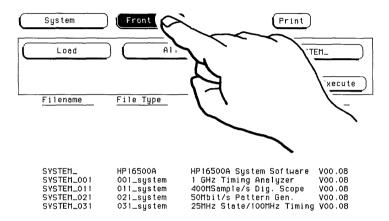

| System Power<br>Up | When the system is powered up, you should see a menu like the one below.                                                                                                                                                                                                                                                                                                         |  |

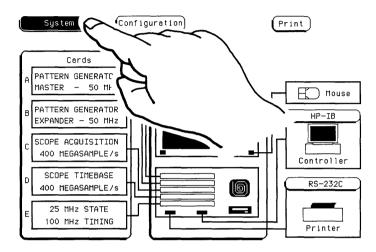

|                    | Cards         A         PATTERN GENERATOR         B         PATTERN GENERATOR         C         SCOPE         AO         MEGASAMPLE/s         C         SCOPE         AO         MEGASAMPLE/s         C         SCOPE         AO         MEGASAMPLE/s         C         SCOPE         TIMEBASE         400         MEGASAMPLE/s         E         100         MHz         TIMING |  |

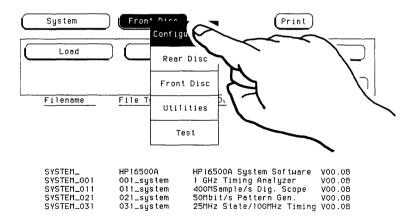

This is the System Configuration menu. If you have a different menu on the screen, you can get back to the Configuration menu with the following steps:

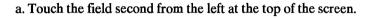

- 1. Touch the field second from the left at the top of the screen.

- 2. When the pop-up appears, touch the field labeled "Configuration."

# Moving to the Logic Analyzer

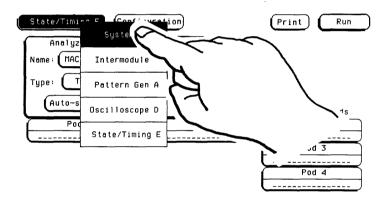

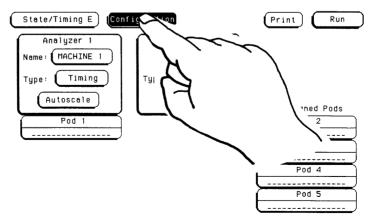

Now touch the field in the upper left of the screen labeled "System." A pop-up will appear displaying all the modules in the mainframe similar to that shown below.

The actual order and content of the pop-up will depend on which modules you have installed and in which slots. In this example, to get to the logic analyzer menus, you should touch the "State/Timing E" field. This will bring up the logic analyzer configuration menu.

HP 16510B Getting Started Guide **Getting to the Logic Analyzer Menus**

### Getting Back to System Level

Depending on which module menu you are in, the name of the module will appear at the top left of the screen. This is the same field that previously said System. An important feature to remember about the HP 16500A menu structure is this: you are typically not more than three touches away from the system configuration menu. Why is this important? Because this makes it next to impossible to go so deep in menus that you can't find your way out.

To get back to the System Configuration menu, touch the field at the top left of the screen. When the pop-up appears, touch the field labeled "System."

# Learning the Basic Logic Analyzer Menus

| Introduction            | In this chapter you will learn the most common pop-up menu types by<br>doing some basic exercises. The pop-up menu types you will learn in<br>this chapter are:<br>• Selector<br>• Alpha Entry<br>• Numeric Entry<br>• Assignment/Specification<br>To begin, move to the logic analyzer Configuration menu by following<br>the method described in "Moving to the Logic Analyzer" in Chapter 3. |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Selector<br>Pop-up Menu | In the selector type of pop-up menu you do what the name implies:<br>make a selection from two or more options. The best way to introduce<br>the selector type of menu is to have you work with one right away.                                                                                                                                                                                 |

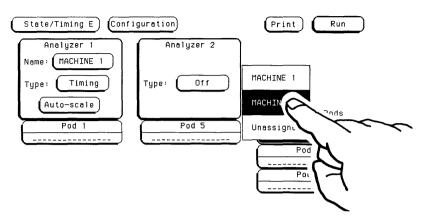

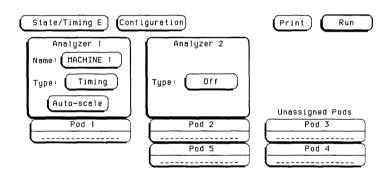

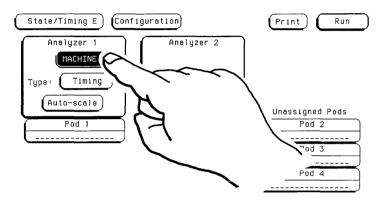

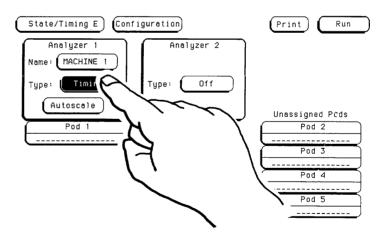

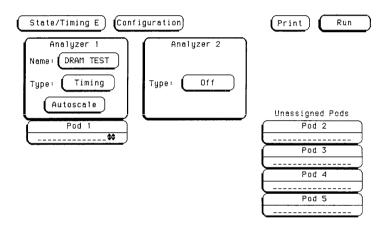

| Assigning Pods          | You will use a selector type of pop-up menu to assign pods to the analyzers. To assign pods:                                                                                                                                                                                                                                                                                                    |

|                         | 1. Touch one of the pod fields in the Configuration menu on the right side of the display.                                                                                                                                                                                                                                                                                                      |

In the pop-up, touch the field labeled "Machine 2."

The pop-up closes and your desired pod is now assigned to Analyzer 2.

Learning the Basic Logic Analyzer Menus 4-2

HP 16510B Getting Started Guide

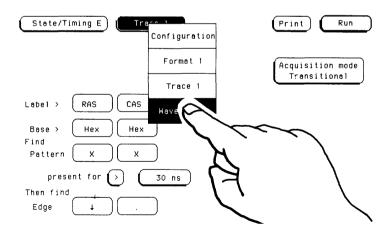

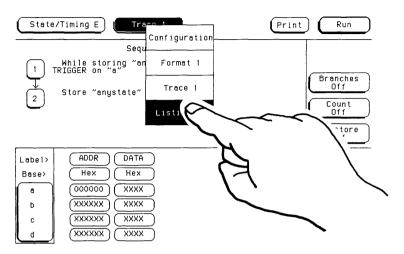

### Choosing Specification Menus

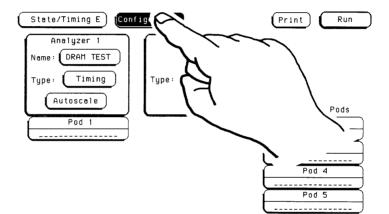

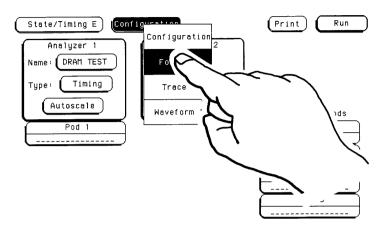

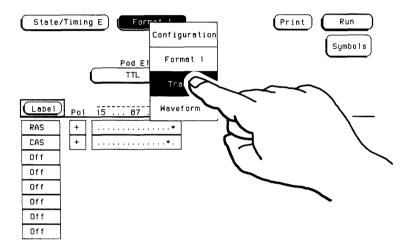

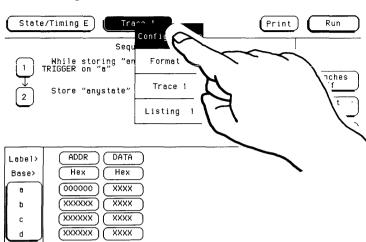

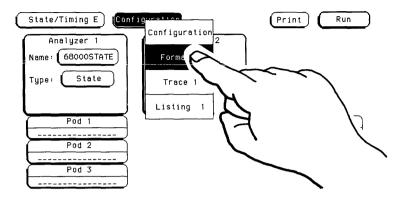

Another selector menu type that you will use quite often allows you to switch between specification menus. To do this:

1. Touch the field second from the left at the top of the screen.

2. The pop-up that appears is shown below. Choose which specification menu you want and touch that field. For example to get to the timing Format specification menu, touch the field labeled Format 1.

This closes the pop-up and puts you in the timing Format menu.

| Alpha Entry<br>Pop-up Menu | You can give specific names to several things. These names can represent your measurement specifically. |

|----------------------------|---------------------------------------------------------------------------------------------------------|

| • •                        | The two major examples of items that can be named are:                                                  |

- Both analyzers

- Labels

To learn how this type of pop-up works, you will name Analyzer 1 LEARN. However, you will misspell it. You will then be shown how to correct it.

- 1. Get back to the logic analyzer Configuration menu by touching the field second from the left at the top of the screen. Then touch the field labeled Configuration in the pop-up.

- 2. In the Configuration menu, touch the field labeled Machine 1.

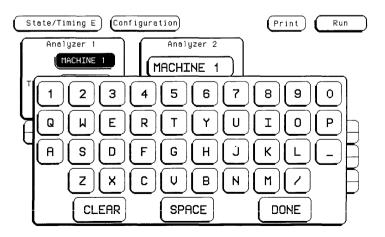

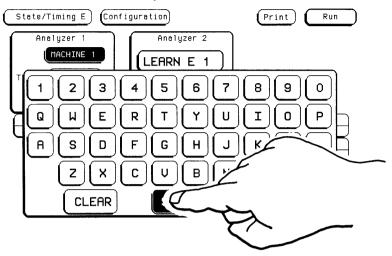

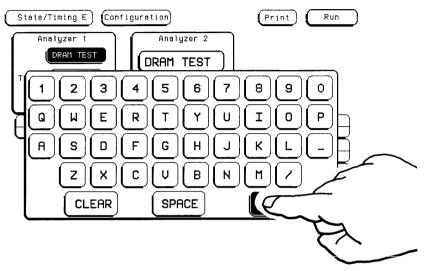

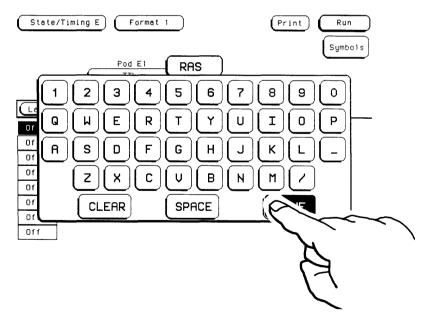

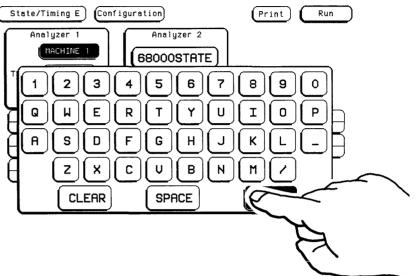

You will now see an alphanumeric keyboard similar to a typewriter keyboard, as shown below.

At the top of the keyboard you will see a space that contains the label "Machine 1." The cursor in this area will tell you where the next letter or number will appear when you touch it on the keyboard. The cursor can be moved within the display with the KNOB.

The cursor is not printed on a hardcopy printout therefore it is not printed in the illustrations in this guide.

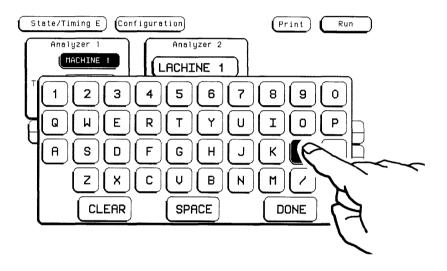

3. Now that you are ready to name Analyzer 1, position the cursor over the M in Machine and touch the L key. Notice that "M" has been changed to "L."

Learning the Basic Logic Analyzer Menus 4-6

4. Touch the E, A, R, and M keys.

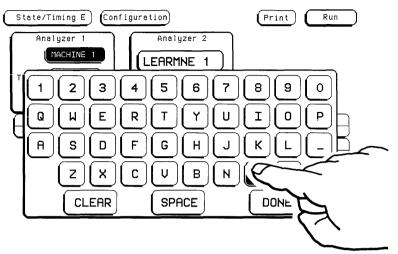

You should now see LEARMNE 1 in the display above the keyboard. Since this is not the name you wanted, change it.

### Changing Alpha Entries

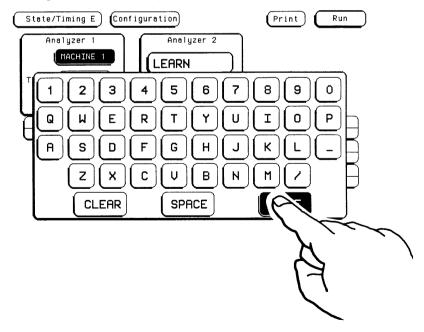

To change the name, place the cursor on the character you wish to change and touch the new character.

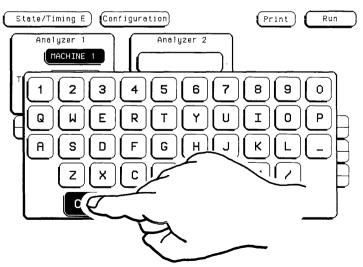

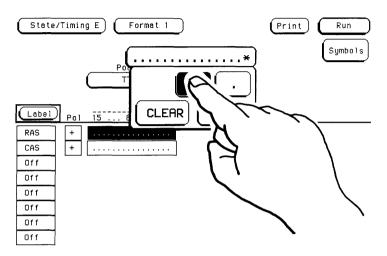

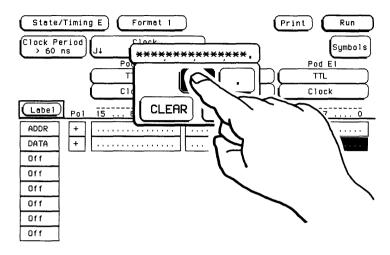

If you want to erase the entire entry and place the cursor at the beginning of the name box, touch the key labeled CLEAR.

Learning the Basic Logic Analyzer Menus

If you want to replace a character with a space, place the cursor on that character and touch the key labeled SPACE.

Correct the name that we are working on from LEARMNE 1 to LEARN using the KNOB and the appropriate keys. After the name is correct, touch the field labeled DONE. This closes the pop-up and changes the name of analyzer 1 to LEARN.

Learning the Basic Logic Analyzer Menus 4-8

HP 16510B Getting Started Guide

|                        | Now that you have entered and edited a name, you will know how to<br>use the Alpha Entry pop-up menu when it appears in other logic<br>analyzer menus.                                                                                                                                                                                                                              |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Numeric Entry<br>Menus | There are many pop-up menus in which you enter numeric data. The two major types are:                                                                                                                                                                                                                                                                                               |

|                        | <ul> <li>Numeric entry with fixed units</li> <li>Numeric entry with variable units (i.e. ms, ns, etc.)</li> </ul>                                                                                                                                                                                                                                                                   |

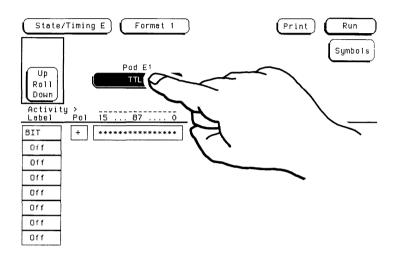

|                        | There are several numeric entry menus where you enter only the value,<br>the units being pre-determined. There are other numeric entry menus<br>for which you will be required to specify the units. One such type of<br>numeric entry pop-up is the POD Threshold pop-up menu.                                                                                                     |

|                        | Besides being able to set the pod thresholds to either of the preset values (TTL or ECL), you can set the thresholds to a specific voltage between $-9.9$ V and $+9.9$ V.                                                                                                                                                                                                           |

|                        | To set pod thresholds to a specific voltage, follow these steps:                                                                                                                                                                                                                                                                                                                    |

|                        | <ol> <li>Select either Format 1 or Format 2 to get to either the timing or<br/>state Format specification menu using the method described in<br/>"Choosing Specification Menus" earlier in this chapter. This<br/>displays either the state or timing Format specification. It does<br/>not matter whether you are in the timing or state Format<br/>specification menu.</li> </ol> |

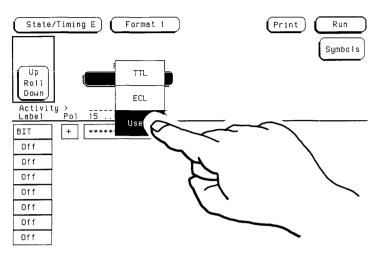

2. Touch the field of any pod displayed. You will now see a pop-up with the choices TTL, ECL, and User.

If you don't see any pods displayed, it simply means that you do not have any pods assigned to this analyzer. Either switch analyzers or assign a pod to the analyzer with which you are working.

3. In the pop-up, touch the field labeled "User."

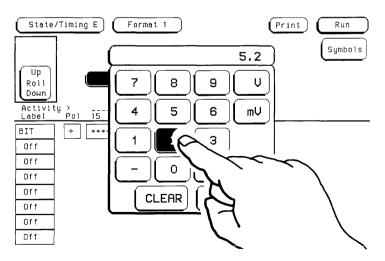

A numeric keypad will appear. You can use the keypad to enter your desired threshold. The space above the keypad will display the numbers as you touch them. To enter -5.2 V:

4. Touch the keys labeled "5", ". ", and "2." Notice that 5.2 appears in the display above the keypad.

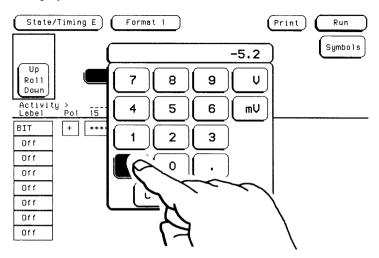

5. Touch the key with the - sign. Now you will see - 5.2 in the display.

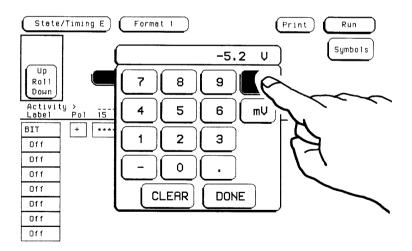

6. Select your units by touching either of the keys on the right side of the keypad. For this example, touch the key labeled "V." The display now shows - 5.2 V.

# Learning the Basic Logic Analyzer Menus 4-12

HP 16510B Getting Started Guide

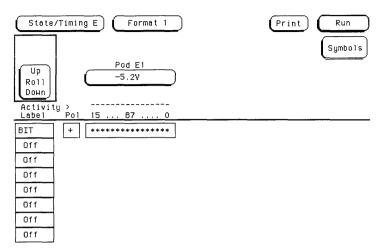

# 7. Touch the DONE field to close the pop-up and place the new threshold in the Pod field.

### Assignment/ Specification Menus

There are a number of pop-up menus in which you assign or specify what you want the logic analyzer to do. The basic menus of this type consist of:

- Assigning bits to pods

- Specifying patterns

- Specifying edges

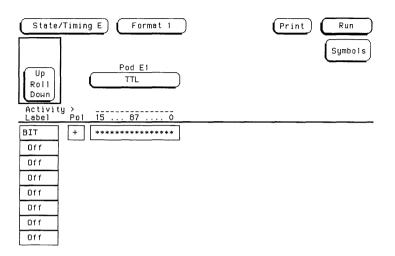

### Assigning Bits to Pods

The bit assignment fields in both state and timing analyzers work

identically. Before starting this exercise you need to know how the logic analyzer knows which bits are assigned and which ones are not assigned. The convention for bit assignment is:

- \* (asterisk) indicates assigned bits

- . (period) indicates un-assigned bits

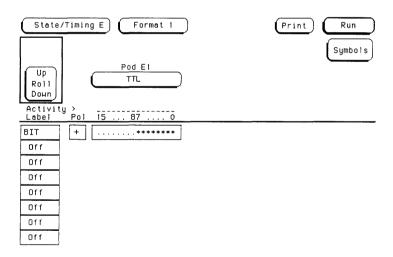

In the following menu example, bits 0 through 7 are assigned to the label BIT.

Learning the Basic Logic Analyzer Menus 4-14

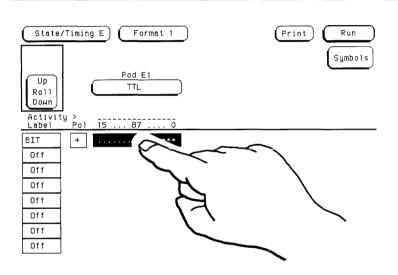

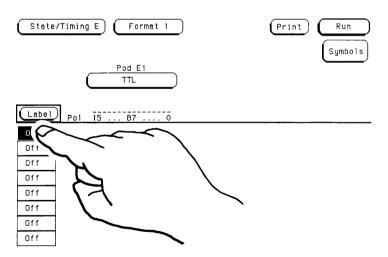

To assign bits:

- 1. Get into either the timing or state Format specification menu using the method described in "Choosing Specification Menus" earlier in this chapter.

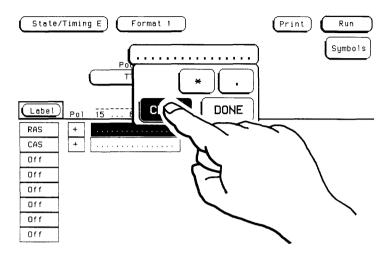

- 2. Touch one of the bit assignment fields.

If you don't see any bit assignment fields, it simply means you don't have any pods assigned to this analyzer. Either switch analyzers or assign a pod to the analyzer with which you are working.

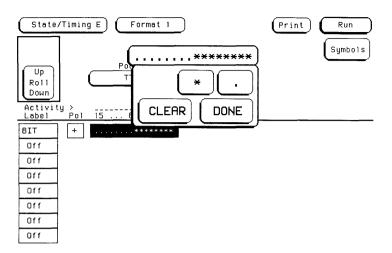

You will see the following pop-up menu.

3. Rotate the KNOB to place the cursor on any one of the asterisks or periods in the pop-up. To assign the bit, touch the field containing the asterisk. To un-assign the bit, touch the field with the period.

4. You close the pop-up by touching the DONE field.

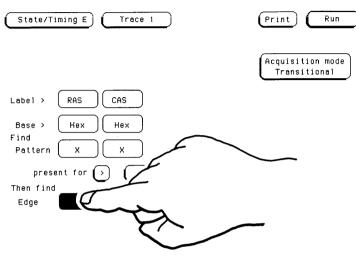

# Specifying<br/>PatternsThe Specify Pattern fields appear in several menus in both the timing<br/>and state analyzers. Patterns can be specified in one of several number<br/>bases. For now we'll use hexadecimal (HEX) since it is the default base.

Before starting this exercise you need to know how the logic analyzer knows which patterns to ignore (doesn't care about). Whenever you see an "X" in this type of menu it indicates a "don't care."

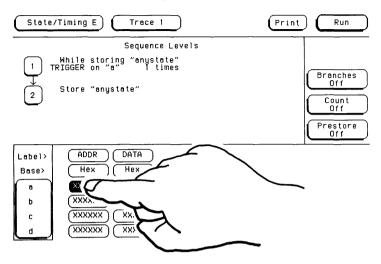

To specify patterns:

- 1. Get into the timing Trace specification menu.

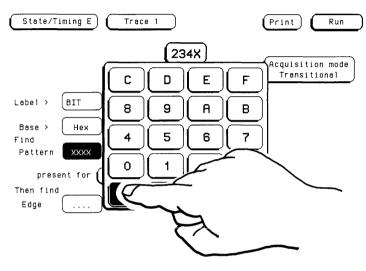

- 2. Touch the field to the right of Find Pattern. A pop-up keyboard display will appear.

If the field does not contain four X's (representing don't cares) do not be alarmed. It simply means the number of bits in your label is different than the label in this example. Go to the timing Format specification menu and assign all the bits in the pod, using the method described in the previous section. Return to the timing Trace specification menu and continue.

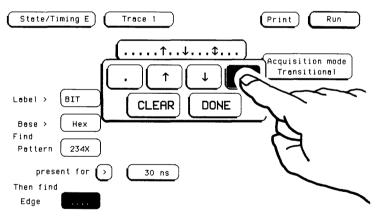

| State/Timing E Trace 1        | Print Run                        |

|-------------------------------|----------------------------------|

|                               | Acquisition mode<br>Transitional |

| Label > BIT                   |                                  |

| Base > Hex<br>Find<br>Pattern |                                  |

| present for                   | $\sim$                           |

| Edge                          |                                  |

| [7]                           |                                  |

|                               |                                  |

|                               | $\mathbf{N}$                     |

Learning the Basic Logic Analyzer Menus 4-18

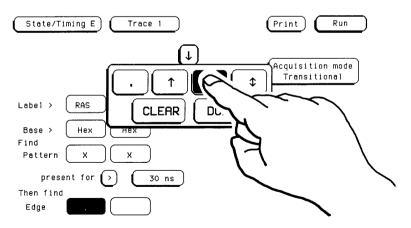

HP 16510B Getting Started Guide 3. On the pop-up keyboard, touch the keys 2, 3, 4, and X. You will see 234X in the display above. This will be the pattern in hexadecimal that you want the logic analyzer to recognize. If you make an error when entering a number, use the KNOB to position the cursor over the incorrect digit and touch the desired key.

4. Close the pop-up keyboard display by touching the DONE field.

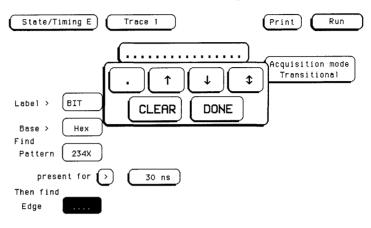

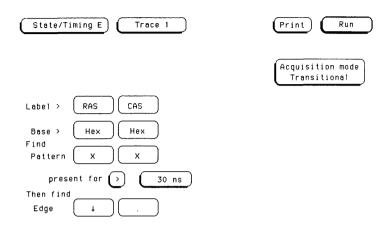

#### Specifying Edges

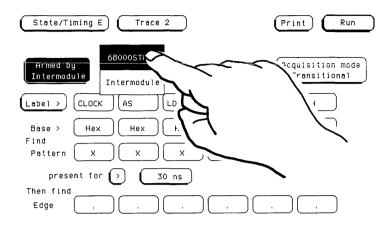

You specify edges in the timing Trace specification menu by following these steps:

- 1. Get into the timing Trace specification menu.

- 2. Touch the field to the right of "Then Find Edge."

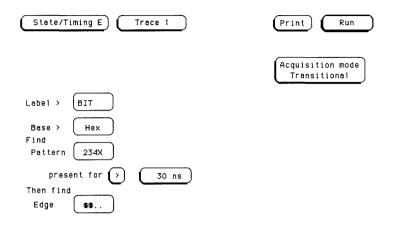

| State/Timing E Trace 1               | (Print) (Run                     |

|--------------------------------------|----------------------------------|

|                                      | Acquisition mode<br>Transitional |

| Lobel > BIT                          |                                  |

| Base > Hex<br>Find<br>Pattern 234X   |                                  |

| present for (>) (30 ns)<br>Then find |                                  |

|                                      |                                  |

| $\mathcal{A}$                        | $\backslash$                     |

| F                                    |                                  |

|                                      |                                  |

|                                      |                                  |

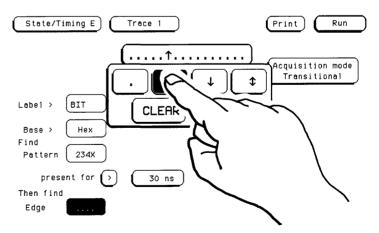

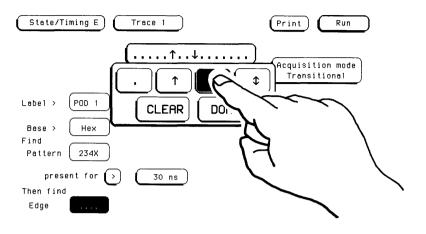

Learning the Basic Logic Analyzer Menus 4-20 A pop-up menu will appear as shown below. You will notice 16 periods in the pop-up. Each period represents an unassigned edge for each bit assigned to the label. Don't be alarmed if you have a different number of unassigned edges; it simply means that the number of bits in your label is different than the label in this example.

3. Use the KNOB to place the cursor on one of the unassigned edges. Touch the field with the arrow pointing up. The period is replaced with the arrow.

4. Move the cursor to another unassigned edge. Touch the field with the arrow pointing down. The period is replaced with the arrow.

5. Move the cursor to yet another unassigned edge. Touch the field with the arrow pointing both ways. The period is replaced with an arrow pointing both up and down.

You have just selected a positive-going  $(\uparrow)$ , negative-going  $(\downarrow)$ , and either edge  $(\uparrow)$  for your edge parameter.

Learning the Basic Logic Analyzer Menus 4-22 HP 16510B Getting Started Guide

### 6. Touch the DONE field. The pop-up will close and you will see the following display.

Note

When you close the pop-up after specifying edges, you will see dollar signs (\$\$...) in the Then Find Edge field if the logic analyzer cannot display the data correctly in the number base you have selected.

#### Summary

In this chapter you have learned some of the most common pop-up menu types. You will use these pop-up menus as you set up the logic analyzer in the measurement example exercises in chapters 5 through 7.

If you are already familiar with logic analysis and feel you are comfortable enough with the HP 16500A interface, you may be ready for the *HP 16510B Front-Panel Reference*.

If you are not familiar with logic analyzers or logic analysis, you should continue with this guide.

### **Using the Timing Analyzer**

#### Introduction

In this chapter you will learn how to use the timing analyzer by setting up the logic analyzer to make a simple measurement. We give you the measurement results as actually measured by the logic analyzer, since you may not have the same circuit available.

The exercise in this chapter is organized in a task format. The tasks are ordered in the same way you will most likely use them once you become an experienced user. The steps in this format are both numbered and lettered. The numbered steps state the step objective. The lettered steps explain how to accomplish each step objective. There is also an example of each menu after it has been properly set up.

How you use the steps depends on how much you remember from chapters 3 and 4. If you can set up each menu by just looking at the menu picture, go ahead and do so. If you need a reminder of what steps you need to perform, follow the numbered steps. If you need still more information about "how," use the lettered steps.

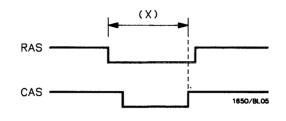

Problem Solving with the Timing Analyzer

In this exercise, assume you are designing a dynamic RAM memory (DRAM) controller and you must verify the timing of the row address strobe (RAS) and the column address strobe (CAS). You are using a 4116 dynamic ram and the data book specifies that the minimum time from when LRAS is asserted (goes low) to when LCAS is no longer asserted (goes high) is 250 ns. You could use an oscilloscope but you have an HP 16500A with an HP 16510B module installed. Since the timing analyzer will do just fine when you don't need voltage parametrics, you decide to go ahead and use the logic analyzer.

#### What Am I Going to Measure?

After configuring the logic analyzer and hooking it up to your circuit under test, you will be measuring the time (x) from when the RAS goes low to when the CAS goes high, as shown below.

#### How Do I Configure the Logic Analyzer?

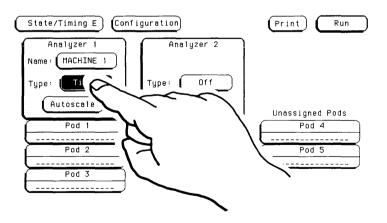

In order to make this timing measurement, you must configure the logic analyzer as a timing analyzer. By following these steps you will configure Analyzer 1 as the timing analyzer.

If you are in the analyzer Configuration menu, you are already in the right place and can start with step 2; otherwise, start with step 1.

- 1. Display the analyzer Configuration menu.

- a. If you are in the State/Timing Analyzer module, go on to step b. Touch the field in the top left corner. When the pop-up appears, touch the field labeled State/Timing E.

b. Touch the field second from the left at the top of the screen.

Using the Timming Analyzer 5-2

HP 16510B Getting Started Guide c. When the pop-up appears, touch the field labeled "Configuration."

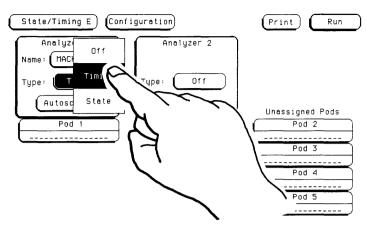

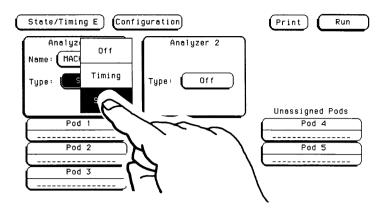

- 2. In the Configuration menu, change Analyzer 1 Type to Timing. If analyzer 1 is already a timing analyzer, go on to step 3.

- a. Touch the field to the right of Type:\_\_\_\_\_

#### b. Touch the field labeled Timing.

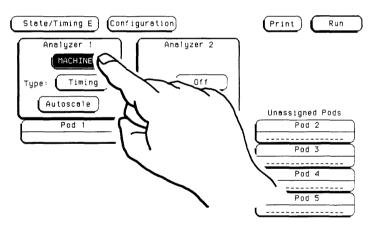

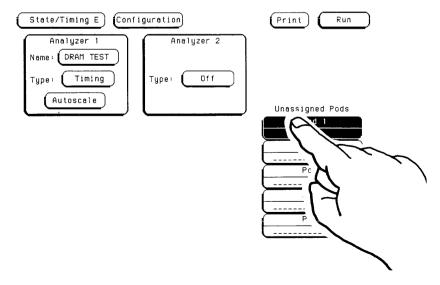

3. Name analyzer 1 "DRAM TEST" (optional)

a. Touch the field to the right of Name: \_\_\_\_\_ under Analyzer 1.

b. When the alphanumeric keyboard pop-up appears, touch the appropriate keys to change the name to "DRAM TEST" (see "Alpha Entry Pop-up Menu" in Chapter 4 if you need a reminder).

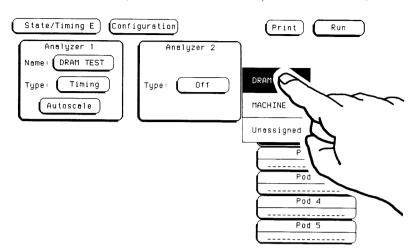

- 4. Assign pod 1 to the timing analyzer if it is not already assigned or if it is assigned to analyzer 2.

- a. Touch the Pod 1 field.

b. In the Pod 1 pop-up, touch the field labeled DRAM TEST (or Machine 1 if you didn't name the analyzer DRAM TEST).

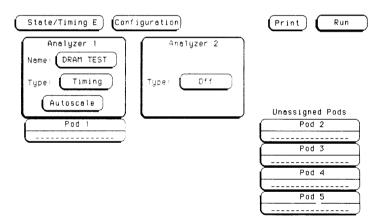

The analyzer Configuration menu should look like that shown below.

#### Connecting the Probes

At this point, if you had a target system with a 4116 DRAM memory IC, you would connect the logic analyzer to your system. Since you will be assigning Pod 1 bit 0 to the RAS label, you hook Pod 1 bit 0 to the memory IC pin connected to the RAS signal. You hook Pod 1 bit 1 to the IC pin connected to the CAS signal.

#### Activity Indicators

When the logic analyzer is connected and your target system is running, you will see two 1 at the right-most end (least significant bits) of the Pod 1 field in the analyzer Configuration menu. This indicates that the RAS and CAS signals are transitioning.

## Configuring the Timing Analyzer

Now that you have configured the logic analyzer module, you are ready to configure the timing analyzer. You will:

- Create two names (labels) for the input signals

- Assign the channels connected to the input signals

- Specify a trigger condition

1. Display the timing Format (Format 1) specification menu.

a. Touch the field second from the left at the top of the screen.

Using the Timming Analyzer 5-8

b. Touch the field labeled Format 1. This gets you to the Format specification menu of analyzer 1, which you have configured as a timing analyzer.

2. Name two labels, one RAS and one CAS.

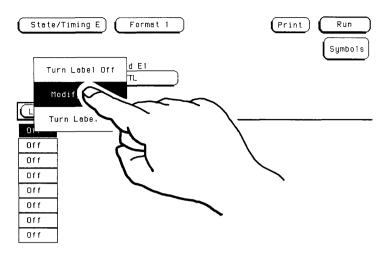

a. Touch the top field in the label column.

b. In the pop-up, touch the Modify Label field.

c. With the alphanumeric keyboard, change the name of the label to RAS (see "Alpha Entry Pop-up Menu" in Chapter 4 if you need a reminder).

Using the Timming Analyzer 5-10

HP 16510B Getting Started Guide d. Name the second label CAS by touching the second field in the label column and then repeating steps b and c. The timing Format specification with the labels is shown below.

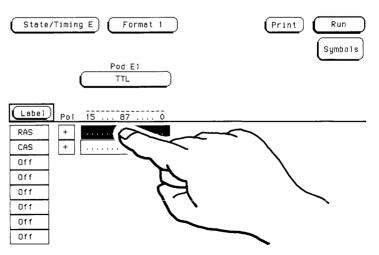

- 3. Assign the channels connected to the input signals (Pod 1 bits 0 and 1) to the labels RAS and CAS, respectively.

- a. Touch the bit assignment field below Pod 1 and to the right of RAS.

Using the Timming Analyzer 5-11

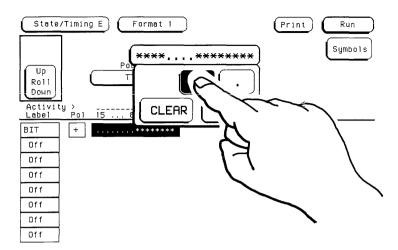

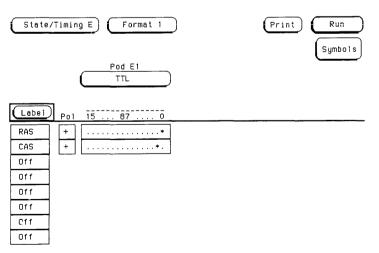

b. Any combination of bits may be already assigned to this pod; however, you will want only bit 0 assigned to the RAS label. The easiest way to assign bits is to press the CLEAR field to unassign any assigned bits before you start.

c. Use the KNOB to position the cursor on bit 0. This is the bit on the far right end of the bit assignment field. Touch the asterisk field. This places an asterisk in the pop-up for bit 0 indicating that Pod 1 bit 0 is now assigned to the RAS label. Touch the DONE field to close the pop-up.

d. Assign Pod 1 bit 1 to the CAS label by repeating steps a through c for bit 1. The resulting timing Format menu is shown below.

#### Specifying a Trigger Condition

To capture and place the data of interest in the center of the Timing waveform menu display, you need to tell the logic analyzer when to trigger. Since the first event of interest is when the LRAS is asserted (negative-going edge of RAS), you need to tell the logic analyzer to trigger on a negative-going edge of the RAS signal.

- 1. Display the timing Trace specification menu.

- a. Touch the field second from the left at the top of the screen.

- b. When the pop-up appears, touch the field labeled "Trace 1."

Using the Timming Analyzer 5-14

- 2. Set the trigger so that the logic analyzer triggers on the negative-going edge of the RAS signal.

- a. Touch the field to the right of Then Find Edge and under the label "RAS."

b. In the pop-up, touch the field with the arrow pointing down. This replaces the period with the arrow, indicating a negative-going edge.

c. Touch the DONE field. The pop-up closes and a ↓ is located in the Then Find Edge field. The ↓ indicates that a negative-going edge has been specified.

## Acquiring the Data

Now that you have configured and connected the logic analyzer, you can acquire the data for your measurement. To do so, first display the timing Waveform menu:

- 1. Touch the field second from the left at the top of the screen.

- 2. When the pop-up appears, touch the field labeled "Waveform 1."

Using the Timming Analyzer 5-16

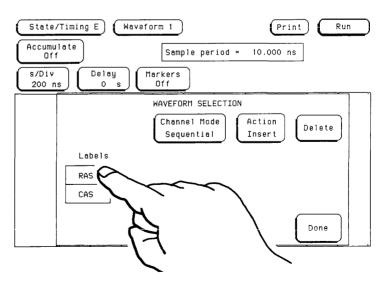

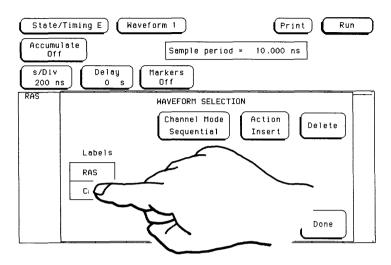

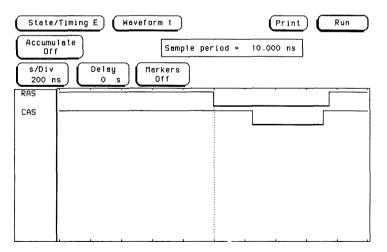

HP 16510B Getting Started Guide If this is the first time you acquire data and you have not previously set up the timing Waveform menu, you will get a blank area at the bottom of the display. You need to turn on the RAS and CAS labels. To do so, follow these steps:

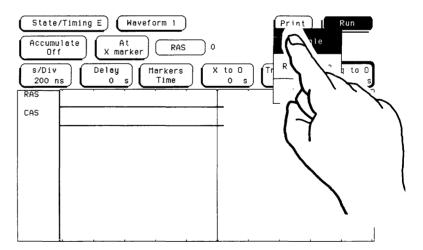

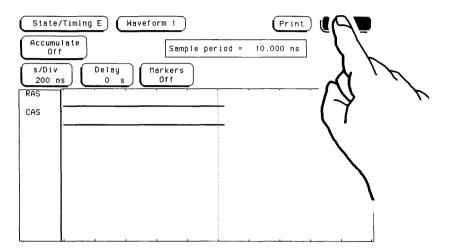

- State/Timing E Haveform 1 Print Run Accumulate Off Sample period = 10.000 ns S/Div 200 ns O s Off

- 1. Touch the long blue field on the left side of the screen.

2. In the pop-up, touch the field labeled "RAS" located under Labels. The label RAS appears at the top of the long blue field.

3. Touch the field labeled "CAS" located under Labels. The label CAS appears in the long blue field under RAS.

4. Touch the DONE field to close the pop-up.

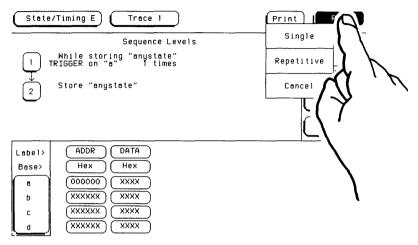

To acquire the data, touch the green field in the upper right-hand corner labeled "Run." Do not lift your finger off the screen.

When you touch the Run field a pop-up appears next to it with the options Single, Repetitive and Cancel. With your finger still on the screen, move to the field labeled Single. It will turn white, indicating that it has been selected.

The Run field appears in, and can be activated from every specification menu. However, if the timing Waveform menu has not previously been set up, you need to display the Waveform menu as described above and get it ready. Thereafter, you can Run a test from any specification menu.

While the logic analyzer is acquiring data, the Run field changes color from green to red, and instead of Run it says Stop. This allows you to stop the data acquisition at any time just by touching this field.

If you select Cancel, the logic analyzer will return to the state it was in before the Run field was touched.

Using the Timming Analyzer 5-20

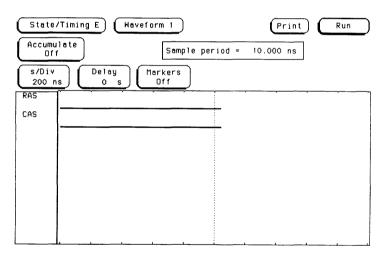

When you touch Run, the logic analyzer will look for a negative edge on the RAS signal and trigger if it sees one. When it triggers waveforms appear on the display.

The RAS label shows you the RAS signal and the CAS label shows you the CAS signal. Notice the RAS signal goes low at or near the center of the waveform display area (horizontal center).

| The Timing<br>Waveform Menu | The timing Waveform menu differs from the other menus you have<br>used so far in this exercise. Besides displaying the acquired data, it has<br>menu fields that you can use to change the way the acquired data is<br>displayed, such as s/Div, and fields that give you timing answers, such<br>as the Markers field. These will now be discussed. |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Display Resolution          | You get the best resolution by changing the s/Div to a value that<br>displays one negative-going and one positive-going edge of both the<br>RAS and CAS waveforms. Set the s/Div by following these steps:                                                                                                                                           |

1. If the s/Div field is already light blue, go on to step 2. If it is not light blue, touch the field.

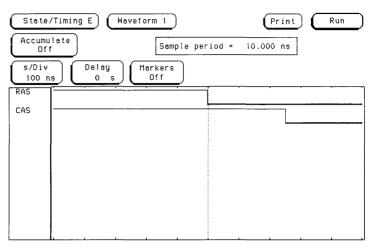

2. The light blue color of the field indicates that the value can be changed with the KNOB or by touching the field to get a pop-up keypad. For this exercise, rotate the KNOB until your waveform shows you only one negative-going edge of the RAS waveform and one positive-going edge of the CAS waveform. In this example 200 ns is best.

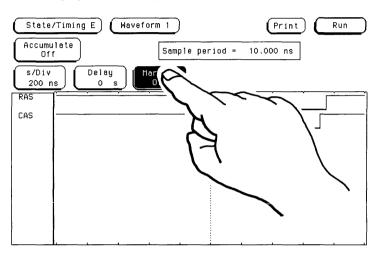

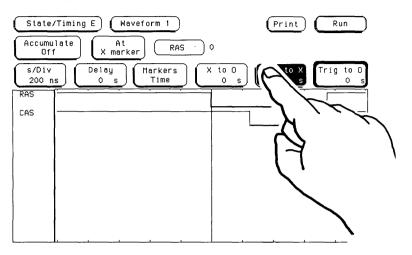

#### The Timing Markers

The logic analyzer supplies two markers that you can use to make timing measurements. One is called the X marker and the other is the O marker. You place them on the points of interest on your waveforms, and the logic analyzer displays the time between the markers. To turn the timing markers on:

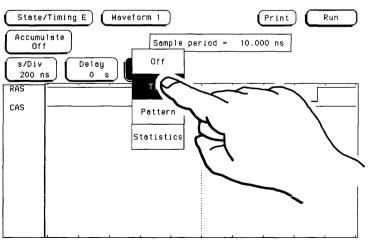

1. Touch the field third from the left, third row down from the top of the display. It should say "Markers Off."

2. In the pop-up, touch the field labeled "Time." This closes the pop-up and turns the timing markers on.

Three more fields will appear on the screen next to the Markers field. The first one tells you the time between the X and O markers. The second field, which is outlined in green, tells you the time from the X marker to the trigger point. The third field, which is outlined in yellow, tells you the time from the O marker to the trigger point.

You will also see a multi-colored line down the center of the waveforms display area. This line is actually made up of three lines: a red line, a yellow line, and a green line. The green line is the X marker, and the yellow line is the O marker. The red line indicates the trigger point you specified in the timing Trace specification menu. Notice that it is superimposed on the negative-going edge of the RAS signal.

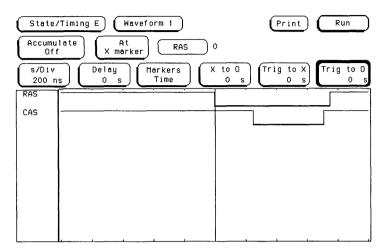

#### Making the Measurement

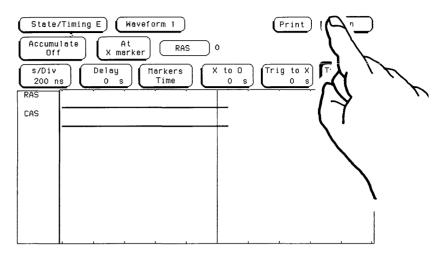

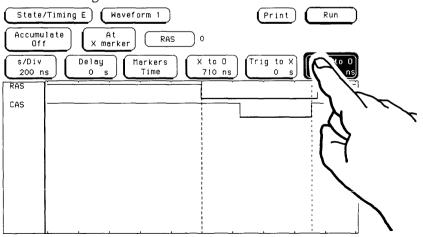

What you want to know is how much time elapses between the time RAS goes low and the time CAS goes high again. You will use the X and O markers to quickly find the answer. Remember that you specified the negative-going edge of the RAS to be your trigger point. Therefore, the X marker should be on this edge if Trig to X = 0. If not, follow steps 1 and 2.

1. Touch the field labeled "Trig to X." This turns the field light blue. Remember that a light blue field means that the value can be changed with the KNOB or by touching the field to get a pop-up keypad. For this exercise we'll use the KNOB.

- 2. Rotate the KNOB to place the X marker (green line) on the negative-going edge of the RAS waveform. The field should read "Trig to X = 0 s."

- 3. Touch the field labeled "Trig to O." This field should now be light blue. Use the KNOB to place the O marker (yellow line) on the positive-going edge of the CAS waveform. The field should now read "Trig to O = 710 ns."

Using the Timming Analyzer 5-25

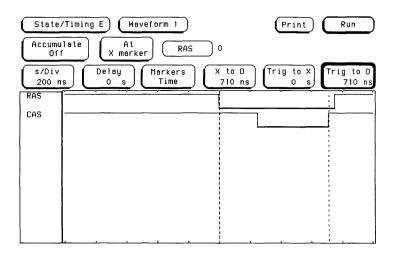

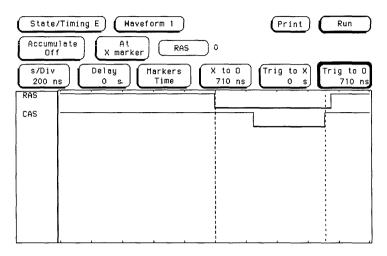

#### The timing Waveform menu should look like that shown below.

#### Finding the Answer

The time elapsed between the time RAS goes low and the time CAS goes high can be calculated by adding the Trig to X time and the Trig to O time, but there is no need. The logic analyzer has already calculated this answer and displays it in the X to O field on the display.

This example indicates that the time is 710 ns. Since the data book specifies a minimum of 250 ns, it appears your DRAM controller circuit is designed properly.

#### **Summary**

You have just learned how to make a simple timing measurement with the HP 16510B Logic Analyzer module in the HP 16500A. You have:

- specified a timing analyzer

- assigned pod 1

- assigned bits

- assigned labels

- specified a trigger condition

- learned which probes to connect

- acquired the data

- configured the display

- set the s/Div for best resolution

- positioned the markers for the measurement answer

You have seen how easy it is to use the timing analyzer to make timing measurements which you could have made with an oscilloscope. You can use the timing analyzer for any timing measurement that neither requires voltage parametrics nor surpasses the accuracy of the timing analyzer.

The next chapter teaches you how to use the state analyzer. You will go through a simple state measurement in the same way you did the timing measurement in this chapter.

### **Using the State Analyzer**

#### Introduction

In this chapter you will learn how to use the state analyzer by setting up the logic analyzer to make a simple state measurement. We give you the measurement results as actually measured by the logic analyzer, since you may not have the same circuit available.

The exercise in this chapter is organized in a task format. The tasks are ordered in the same way you will most likely use them once you become an experienced user. The steps in this format are both numbered and lettered. The numbered steps state the step objective. The lettered steps explain how to accomplish each step objective. There is also an example of each menu after it has been properly set up.

How you use the steps depends on how much you remember from chapters 3 and 4. If you can set up each menu by just looking at the menu picture, go right ahead and do so. If you need a reminder of what steps you need to perform, follow the numbered steps. If you still need more information about "how," use the lettered steps.

| Problem<br>Solving with<br>the State<br>Analyzer | In this example assume you have designed a microprocessor controlled<br>circuit. You have completed the hardware and the software designer<br>has completed the software and programmed the ROM (read-only<br>memory). When you turn your circuit on for the first time your circuit<br>doesn't work properly. You have checked the power supply voltages<br>and the system clock and they are working properly.<br>Since the circuit has never worked before, you and the software<br>engineer aren't sure if it is a hardware or a software problem. The<br>problem now requires some testing to find a solution. |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| What Am I<br>Going to<br>Measure?                | You decide to start where the microprocessor starts when power is<br>applied. We will describe a 68000 microprocessor; however, every<br>processor has similar start-up routines.<br>When you power up a 68000 microprocessor it is held in reset for a<br>specific length of time before it starts doing anything to stabilize the                                                                                                                                                                                                                                                                                 |

|                                                  | power supplies. This time during which the microprocessor is held in<br>reset ensures stable levels (states) on all the devices and buses in your<br>circuit. When this reset period has ended, the 68000 performs a specific<br>routine called "fetching the reset vector."                                                                                                                                                                                                                                                                                                                                        |

|                                                  | The first thing you check is the time the microprocessor is held in reset.<br>You find that the time is correct. The next thing to check is whether the<br>microprocessor fetches the reset vector properly.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                  | The steps of the 68000 reset vector fetch are:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                  | 1. Set the stack pointer to a location you specify which is in ROM at address locations 0 and 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                  | 2. Find the first address location in memory where the micro-<br>processor fetches its first instruction. This is also specified by you<br>and stored in ROM at address locations 4 and 6.                                                                                                                                                                                                                                                                                                                                                                                                                          |

What you decide to find out is:

- 1. What ROM address does the microprocessor look at for the location of the stack pointer, and what is the stack pointer location stored in ROM?

- 2. What ROM address does the microprocessor look at for the address where its first instruction is stored in ROM, and is the instruction correct?

- 3. Does the microprocessor then go to the address where its first instruction is stored?

- 4. Is the executable instruction stored in the first instruction location correct?

Your measurement, then, requires verification of the sequential addresses the microprocessor looks at and of the data in ROM at these addresses. If the reset vector fetch is correct (in this example) you will see the following list of numbers in HEX (default base) when your measurement results are displayed:

| 0 | 000000 | 0000 |

|---|--------|------|

| 1 | 000002 | 04FC |

| 2 | 000004 | 0000 |

| 3 | 000006 | 8048 |

| 4 | 008048 | 3E7C |

This list of numbers will be explained in detail later in this chapter in "The State Listing."

### How Do I Configure the Logic Analyzer?

In order to make this state measurement, you must configure the logic analyzer as a state analyzer. By following these steps you will configure Analyzer 1 as the state analyzer.

If you are in the analyzer Configuration menu you are in the right place and can start with step 2; otherwise, start with step 1.

- 1. Display the analyzer Configuration menu.

- a. If you are in the State/Timing Analyzer mode, go on to step b. If you are in another mode (i.e. operating from a different module), refer to "Moving to the Logic Analyzer" in Chapter 3 to see how to get to the analyzer mode.

- b. Touch the field second from the left at the top of the screen.

c. When the pop-up appears, touch the field labeled "Configuration".

- 2. In the analyzer Configuration menu, change the Analyzer 1 type to State. If Analyzer 1 is already a state analyzer, go on to step 3.

- a. Touch the field to the right of Type: \_\_\_\_\_.

b. Touch the field labeled "State".

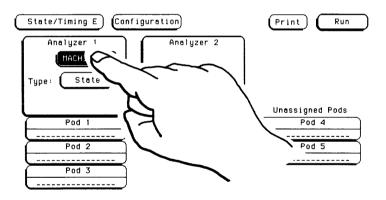

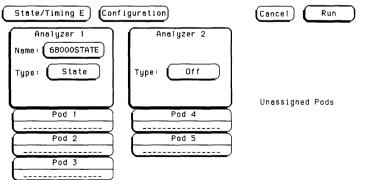

- 3. Name analyzer 1 68000STATE (optional).

- a. Touch the field to the right of Name: \_\_\_\_\_.

b. When the alphanumeric keyboard pop-up appears, touch the appropriate keys to change the name to 68000STATE (see "Alpha Entry Pop-up Menu" in Chapter 4 if you need a reminder).

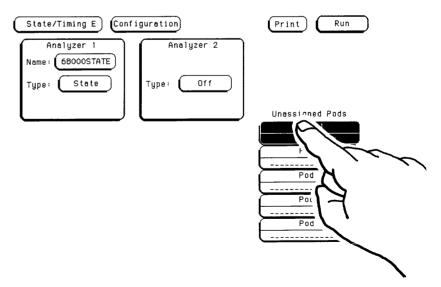

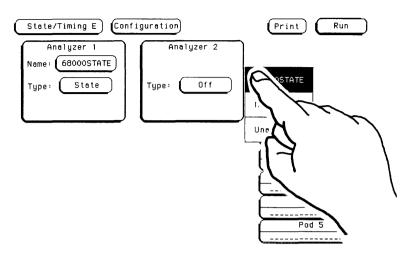

4. Assign pods 1, 2, and 3 to the state analyzer.

a. Touch the Pod 1 field.

b. In the Pod 1 pop-up, touch the field labeled "68000STATE".

c. Repeat steps a and b for pods 2 and 3.

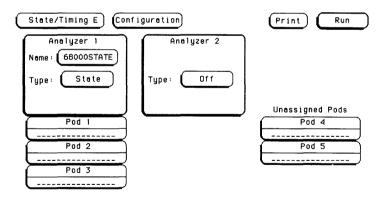

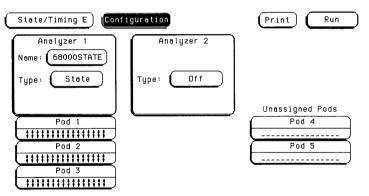

The analyzer Configuration menu should look similar to that shown below.

| Connecting the<br>Probes | At this point, if you had a target system with a 68000 microprocessor,<br>you would connect the logic analyzer to your system. Since you will be<br>assigning labels ADDR and DATA, you hook the probes to your<br>system accordingly:                                                                 |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                          | <ul> <li>Pod 1 probes 0 through 15 to the data bus lines D0 through D15.</li> <li>Pod 2 probes 0 through 15 to the address bus lines A0 through A15.</li> <li>Pod 3 probes 0 through 7 to the address bus lines A16 through A23.</li> <li>Pod 1, CLK (J clock) to the address strobe (LAS).</li> </ul> |  |

| Activity<br>Indicators   | When the logic analyzer is connected and your target system is running, you will see ( ‡ ) in the Pod 1, 2, and 3 fields of the analyzer Configuration menu. This indicates which signal lines are transitioning.                                                                                      |  |

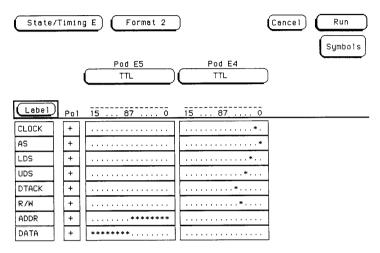

## Configuring the State Analyzer

Now that you have configured the system, you are ready to configure the state analyzer. You will be:

- Creating two names (labels) for the input signals

- Assigning the channels connected to the input signals

- Specifying the State (J) clock

- Specifying a trigger condition

- 1. Display the state Format specification menu.

Using the State Analyzer 6-10

b. Touch the field labeled "Format 1".

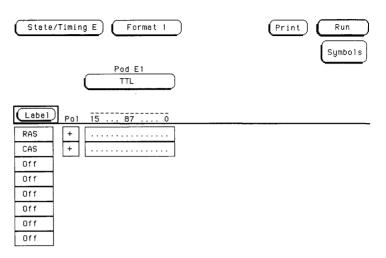

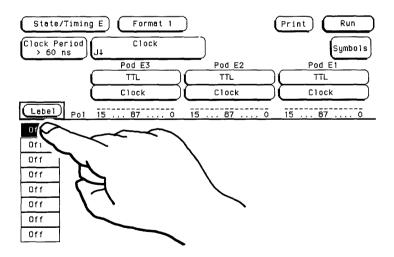

#### 2. Name two labels, one ADDR and one DATA.

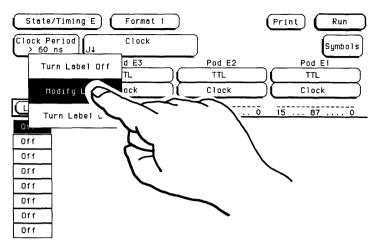

a. Touch the top field in the label column.

b. When the pop-up appears, touch the field labeled "Modify Label".

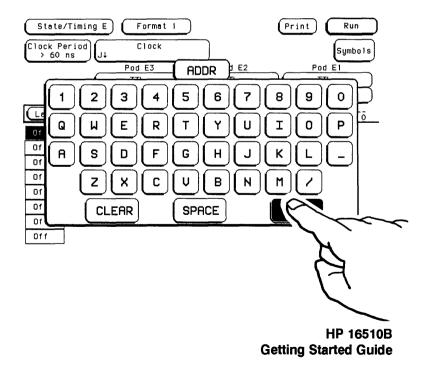

c. With the alphanumeric keypad pop-up, change the name of the label to ADDR (see "Alpha Entry Pop-up Menu" in Chapter 4 if you need a reminder).

Using the State Analyzer 6-12

#### d. Name the second label DATA by repeating steps a through c.

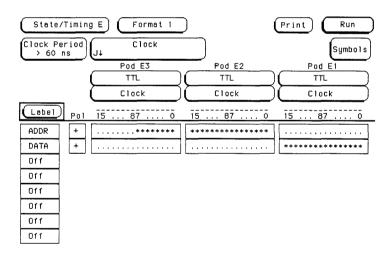

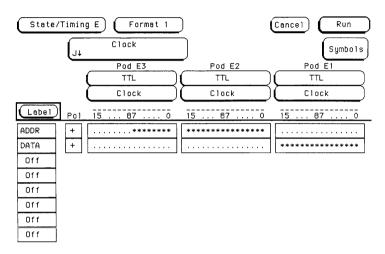

- 3. Assign Pod 1 bits 0 through 15 to the label DATA.

- a. Touch the bit assignment field under Pod 1 and to the right of DATA.

b. Any combination of bits may already be assigned to this pod; however, you will want all 16 bits assigned to the DATA label. Start at the left end and touch the asterisk field 16 times to assign all the bits. Touch Done to close the pop-up.

- 4. Assign Pod 2 bits 0 through 15 to the label ADDR by repeating step 3.

- 5. Assign Pod 3 bits 0 through 7 to the label ADDR.

If any other bit assignment field has bits assigned in it, clear that field so that the bits are all unassigned.

Using the State Analyzer 6-14

HP 16510B Getting Started Guide

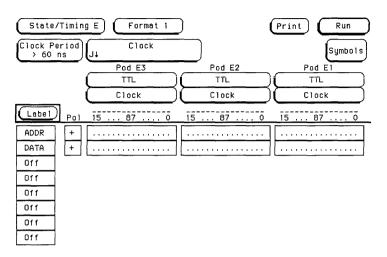

| State/Timing E Format 1<br>$(100 \text{ K Period}) \int_{J^{\perp}} Clock$ |           | Print Run<br>Symbols |

|----------------------------------------------------------------------------|-----------|----------------------|

| Pod E3                                                                     | Pod E2    | Pod E1               |

| TTL                                                                        | ) ( TTL ) |                      |

| Clock                                                                      | Clock     | Clock                |

| Label Pol 15 87 0                                                          | 15 87 0   | 15 87 0              |

| ADDR +********                                                             | *****     |                      |

| DATA +                                                                     |           | ****                 |

| Off                                                                        |           |                      |

| DIT                                                                        |           |                      |

| Off                                                                        |           |                      |

The state Format specification menu should now look like that below.

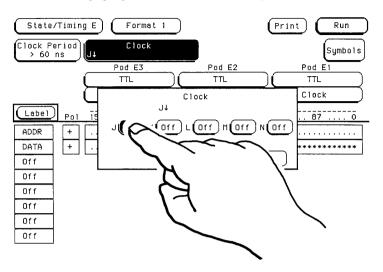

# Specifying the J Clock

If you remember from "What's a State Analyzer" in *Feeling Comfortable With Logic Analyzers*, the state analyzer samples the data under the control of an external clock which is "synchronous" with your circuit under test. Therefore, you must specify which clock probe you will use for your measurement. In this exercise you will use the J clock, which is accessable through pod 1.

- 1. Display the state Format specification menu.

- 2. Set the J Clock to sample on a negative-going edge.

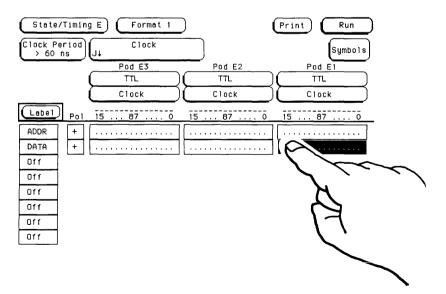

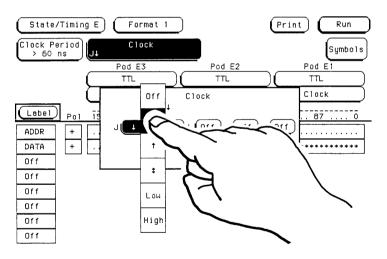

- State/Timing E Format 1 Print Run Clock Period Symbols > 60 ns Pod E3 Pod E1 TTL TTL Clock Clock Label 15 Pol . . 87 87 õ ADDR + \*\*\*\*\*\* DATA + . . . . . . . . . . . . . . . Off Off Off Off Off Off

- a. Touch the field labeled "Clock".

b. In the pop-up, touch the field to the right of J.

c. Touch the field with the arrow pointing down.

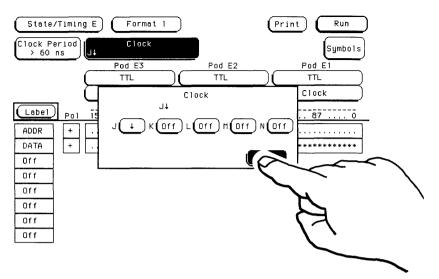

3. Turn off all other clocks (K-N) if any are on by repeating steps a through c above.

#### d. Touch the Done field to close the pop-up.

The state Format specification menu should look like that shown below.

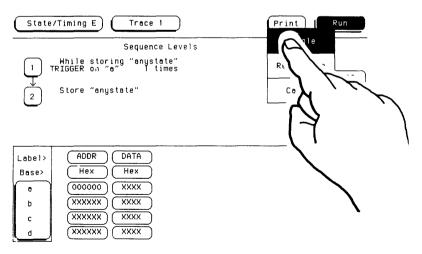

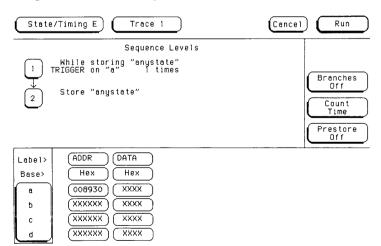

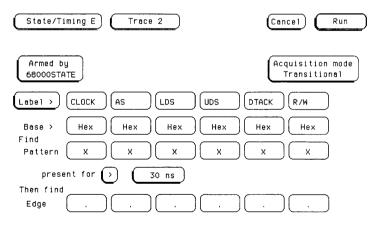

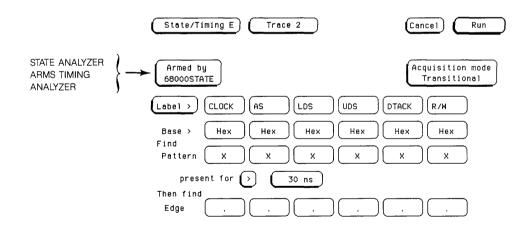

### Specifying a Trigger Condition

To capture the data and place the data of interest in the center of the display of the state Listing menu, you need to tell the state analyzer when to trigger. Since the first event of interest is address 0000, you need to tell the state analyzer to trigger when it detects address 0000 on the address bus.

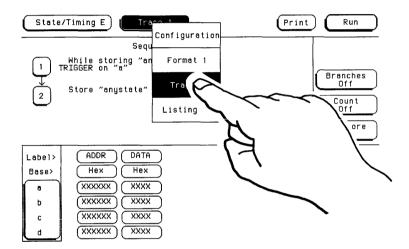

- 1. Display the state Trace specification menu.

- a. Touch the field second from the left at the top of the screen.

- b. Touch the field labeled "Trace 1".

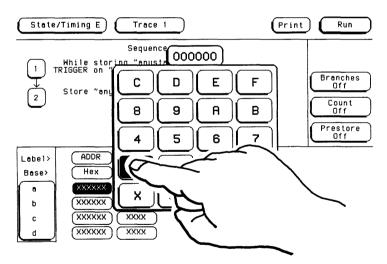

2. Set the trigger so that the state analyzer triggers on address 0000.

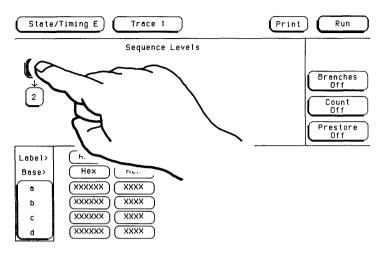

a. Touch the 1 in the Sequence Levels field of the menu.

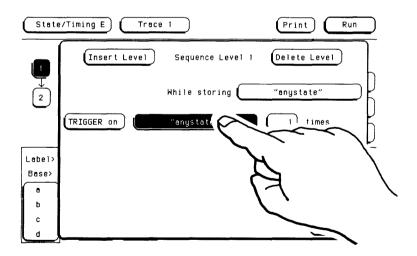

b. In the pop-up touch the field labeled "anystate" to the right of the TRIGGER on field.

Using the State Analyzer 6-20

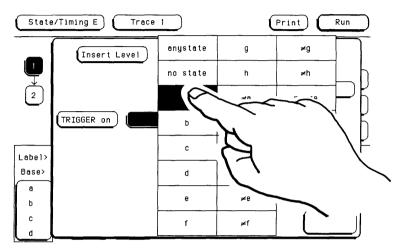

HP 16510B Getting Started Guide Another pop-up appears showing you a list of "trigger on" options. Options a through h are qualifiers that allow you to assign a pattern for the trigger specification.

c. Touch the field with the "a" option.

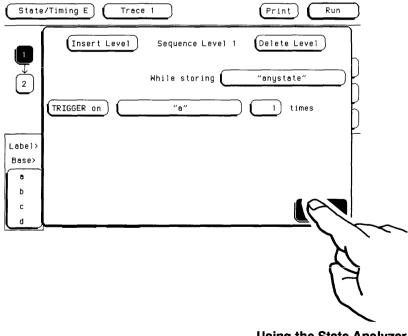

d. Touch the Done field in the Sequence Levels pop-up.

Using the State Analyzer 6-21 e. Touch the field to the right of "a" under the label ADDR.

f. With the pop-up keypad, touch the 0 (zero) key until all zeros appear in the display space above the keypad. Touch the Done field to close the pop-up.

Using the State Analyzer 6-22

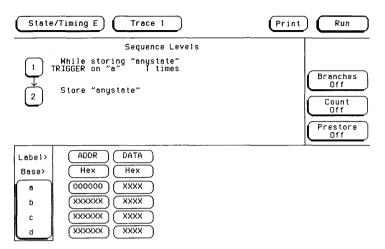

HP 16510B Getting Started Guide Your trigger specification now states: "While storing anystate trigger on "a" once and then store anystate."

When the state analyzer is connected to your circuit and is acquiring data, it continuously stores until it sees 0000 on the address bus, at which time it begins to store anystate until the analyzer memory is filled.

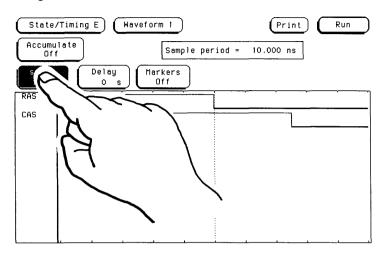

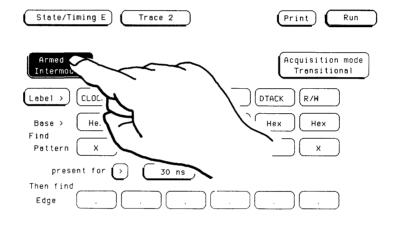

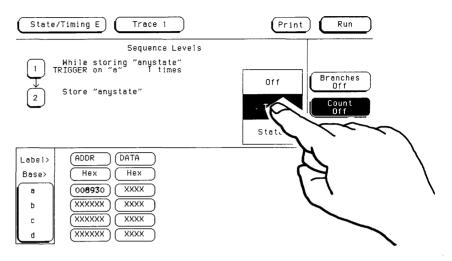

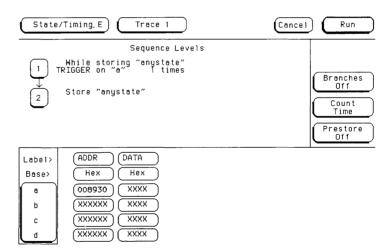

# Acquiring the Data

To acquire the data, you touch the green field in the upper right-hand corner of the screen labeled Run. Unlike the timing analyzer you do not have to go to the data display (state Listing) menu for the first run. You can simply touch the Run field while in any state specification menu. After touching the Run field, don't lift your finger off the screen.

When you touch the Run field a pop-up appears next to it with the options Single, Repetitive and Cancel. With your finger still on the screen, move it to the field labeled "Single". Single will turn white indicating that it has been selected.

Using the State Analyzer 6-24

HP 16510B Getting Started Guide If you want to go to the state listing menu before taking a measurement, touch the field second from the left at the top of the screen. When the pop-up appears, touch the field labeled "Listing 1".

Since you want to capture the data when the microprocessor sends address 0000 on the bus after power-up, you touch the Run field to arm the state analyzer and then force a reset of your circuit. When the reset cycle ends, the microprocessor should send address 0000 trigger the state analyzer and switch the display to the state Listing menu.

We'll assume this is what happens in this example, since the odds of the microprocessor not sending address 0000 are very low.

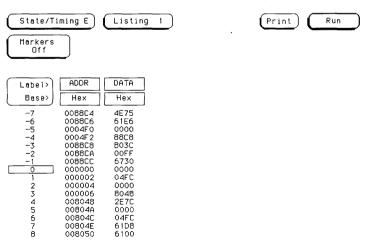

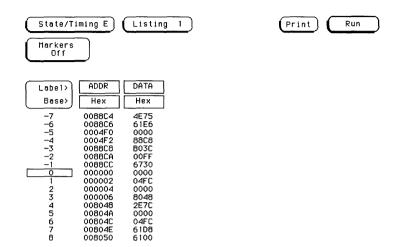

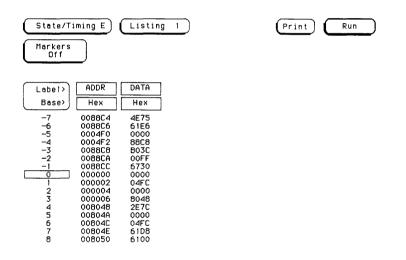

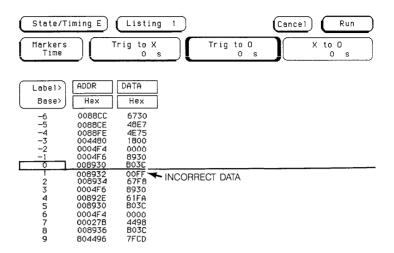

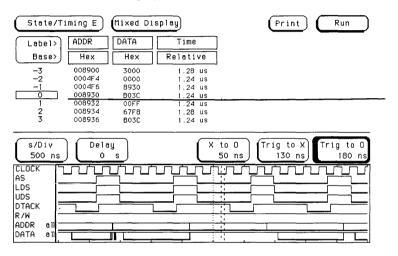

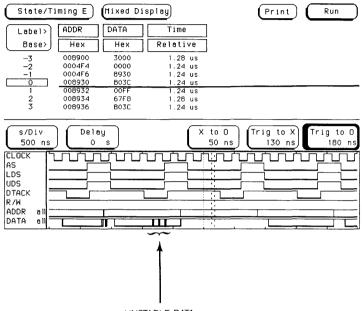

### The State Listing

The state listing displays three columns of numbers as shown:

The first column of numbers are the state line number locations as they relate to the trigger point. The trigger state is on the line 0 in the vertical center of the list area. The negative numbers indicate states occurring before the trigger and the positive numbers indicate the states occurring after the trigger.

The second column of numbers are the states (listed in HEX) the state analyzer sees on the address bus. This column is labeled ADDR.

The third column of numbers are the states (listed in HEX) the state analyzer sees on the data bus. This column is labeled DATA.

Using the State Analyzer 6-26

| Finding the<br>Answer | Your answer is now found in this listing of the states 0 through 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | The 68000 always reads address locations 0, 2, 4, and 6 to find the stack<br>pointer location and memory location for the instruction it fetches after<br>power-up. The 68000 uses two words for each of the locations that it is<br>looking for, a high word and a low word. When the software designer<br>programs the ROM he must put the stack pointer location at address<br>locations 0 and 2. 0 is the high word location and 2 is the low word<br>location. Similarly, the high word of the instruction fetch location must<br>be in address location 4 and the low word in location 6. |

|                       | Since the software design calls for the reset vector to:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                       | 1. set the stack pointer to be set to 04FC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       | 2. read memory address location 8048 for its first instruction fetch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | you are interested in what is on both the address bus and the data bus in states 0 through 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                       | You look at the following listing and see that states 0 and 1 do contain<br>address locations 0 and 2 under the ADDR label, indicating that the<br>microprocessor did look to the correct locations for the stack pointer<br>data. You also see that the data contained in these ROM locations are<br>0000 and 04FC, which are correct.                                                                                                                                                                                                                                                         |

|                       | You then look at states 2 and 3. You see that the next two address locations are 4 and 6, which is correct, and the data found at these locations is 0000 and 8048, which is also correct.                                                                                                                                                                                                                                                                                                                                                                                                      |