# System 8000

03-3198-01

March, 1982

Copyright 1981 by Zilog, Inc. All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Zilog.

The information in this publication is subject to change without notice.

Zilog assumes no responsibility for the use of any circuitry other than circuitry embodied in a Zilog product. No other circuit patent licenses are implied.

## NOTICE TO OWNER

## FEDERAL COMMUNICATIONS COMMISSION RADIO FREQUENCY INTERFERENCE STATEMENT

**Warning:** This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. As temporarily permitted by regulation it has not been tested for compliance with the limits for Class A computing devices pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

٠ \* • . .

i

Zilog

,

٠

a . 2

#### SYSTEM 8000 HARDWARE REFERENCE MANUAL

.

,

#### PRELIMINARY VERSION

The information contained in this draft may undergo changes, both in content and organization, before arriving at its final form.

i

#### PREFACE

This manual contains the information that is necessary to install, operate, understand, and maintain Zilog's System 8000<sup>™</sup> family of 16-bit microcomputers. The audience that this manual addresses consists of field engineers (FE), service technicians, and all others who require in-depth knowledge of the hardware aspects of the system.

This manual and the related manuals listed below provide the complete technical documentation of the System 8000.

#### Title

#### Zilog Number

١.

| System 8000 User Manual<br>ZEUS System Administrator Manual<br>ZEUS Utiltites Manual<br>ZEUS Reference Manual<br>CPU Hardware Reference Manual<br>Secondary Serial Board<br>Manual | 03-3199<br>03-3197<br>03-3196<br>03-3195<br>03-3200<br>03-3201 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| Memory Subsystem                                                                                                                                                                   | 03-3202                                                        |

| Winchester Disk Controller                                                                                                                                                         | 03-3203                                                        |

| Cartridge Tape Controller                                                                                                                                                          | 03-3204                                                        |

System 8000<sup>IM</sup> and ZEUS<sup>IM</sup> are registered trademarks of Zilog, Inc.

iii

. .

## TABLE OF CONTENTS

| SECTION 1 | OVE:                                   | RVIEW 1                                                                                                                               |                  |

|-----------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------------------|

|           | 1.1<br>1.2                             | System Descriptionl<br>Functional Relationshipsl                                                                                      |                  |

|           |                                        | 1.2.1CPU Board31.2.2Winchester Disk Controller31.2.3Cartridge Tape Controller31.2.4Memory Subsystem Controller31.2.5ECC Memory Array9 |                  |

|           | 1.3                                    | System Expansion9                                                                                                                     |                  |

| SECTION 2 | SYS                                    | TEM SPECIFICATIONS 1]                                                                                                                 | L                |

|           | 2.1<br>2.2<br>2.3<br>2.4               | Electrical Specifications                                                                                                             | 1<br>2           |

|           |                                        | 2.4.1 Modules 13<br>2.4.2 I/O Connectors 15                                                                                           |                  |

|           | 2.5<br>2.6                             |                                                                                                                                       | 8<br>8           |

| SECTION 3 | INS                                    | TALLATION 27                                                                                                                          | 7                |

|           | 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Receiving Inspection                                                                                                                  | 7<br>7<br>8<br>8 |

| •         |                                        | 3.6.1 Assembly and Interconnecting 29<br>3.6.2 Disassembly 30                                                                         |                  |

|           | 3.7                                    | System Location 32                                                                                                                    | 2                |

|           |                                        | 3.7.1System Enclosure Location33.7.2Operating Temperature33.7.3Relative Humidity33.7.4Cabinet Access3                                 | 2<br>3           |

|           | 3.8                                    | Electrical Power Requirements 3                                                                                                       | 3                |

••

HRM

C

Anna an

v

Zilog

HRM

v

HRM

TABLE OF CONTENTS (continued)

| SECTION | 3 | INST                            | LLATION                      | (continu                      | ied)                                                      |                            |               |                |

|---------|---|---------------------------------|------------------------------|-------------------------------|-----------------------------------------------------------|----------------------------|---------------|----------------|

|         |   | 3.9                             | System                       | Interconn                     | ection                                                    |                            | •••••         | 33             |

|         |   | -                               | 3.9.1                        | Interconn                     | ect Proce                                                 | dure                       | •••••         | 34             |

|         |   |                                 |                              |                               | tor Unloc                                                 |                            |               |                |

| SECTION | 4 | THEOR                           | RY OF OF                     | PERATION .                    | •••••••                                                   | •••••                      | ••••••        | 41             |

|         |   | 4.1<br>4.2<br>4.3<br>4.4<br>4.5 | System<br>Bus Con<br>Bus Sig | Bus<br>ventions<br>mals       |                                                           | • • • • • • • • •          |               | 41<br>41<br>43 |

|         |   |                                 | 4.5.1                        | CPU Modul                     | e                                                         | •••••                      | •••••         | 50             |

|         |   |                                 |                              |                               | I/O Bus .<br>Serial I/                                    |                            |               |                |

|         |   |                                 | 4.5.2                        | Wincheste                     | er Disk Co                                                | ontroller                  | •••••         | 58             |

|         |   |                                 |                              | 4.5.2.2                       | CPU Inter<br>Controlle<br>Interface<br>Command a<br>Words | er-Drive<br>e<br>and Statu | 15            | 61             |

|         |   |                                 | 4.5.3                        | Cartridge                     | e Tape Cor                                                | ntroller                   | • • • • • • • | 70             |

|         |   |                                 |                              |                               | ZBI Inter<br>Drive Int                                    |                            |               |                |

|         |   |                                 | 4.5.4<br>4.5.5               |                               | troller Og<br>ubsystem (                                  |                            |               |                |

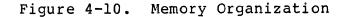

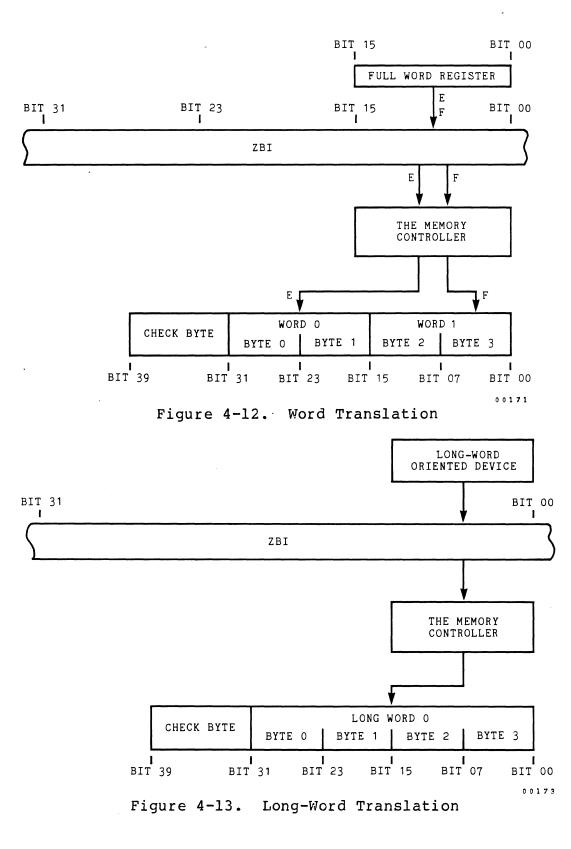

|         |   |                                 |                              | 4.5.5.1<br>4.5.5.2<br>4.5.5.3 | Byte Trar<br>Word Trar<br>Long-Word<br>Translati          | nslation<br>1              | • • • • • • • | 85<br>85<br>86 |

|         |   | 4.6<br>4.7                      |                              |                               | terrupts                                                  |                            |               | 86<br>86       |

|         |   |                                 | 4.7.1<br>4.7.2               |                               | MI<br>il NMI                                              |                            |               | 90<br>90       |

vi

#### TABLE OF CONTENTS (continued)

#### SECTION 4 THEORY OF OPERATION (continued)

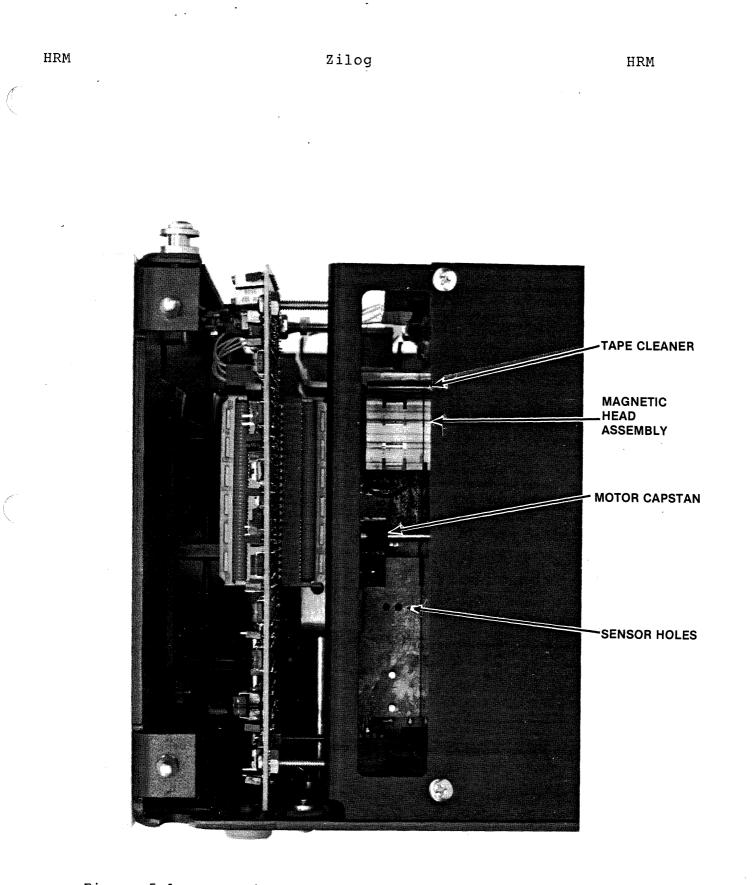

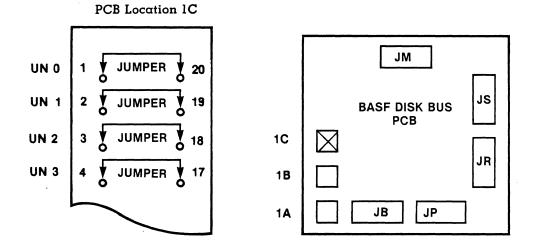

ECC Memory Error NMI ..... 90 4.7.3 NMI Source Identification ..... 90 4.7.4 4.8 Vectored Interrupts ..... 91 4.9 Memory Management Unit (MMU) ..... 93 4.9.1 MMU Operation (Non-Segmented) ... 94 4.9.2 MMU Operation (Segmented) ..... 94 4.9.3 MMU Configurations ..... 95 Break Registers ..... 95 4.9.4 4.9.5 System Access to User Space ..... 96 4.9.6 System Segments and System SECTION 5 5.1 5.2 Preventive Maintenance ..... 99 5.3 Tape Drive Periodic Maintenance ..... 99 Magnetic Head Cleaning ..... 99 Tape Cleaner Cleaning ..... 100 5.3.1 5.3.2 5.3.3 Motor Capstan Cleaning ..... 100 5.3.4 Heat Sink, Circuit Board, and Sensor Hole Cleaning ..... 102 5.4 Disk Drive Assembly Cleaning ..... 102 5.5 Disk Drive Configuration Options ..... 102 5.6 Disk Drive Mounting ..... 108 Cabling and Connections ..... 108 5.7 5.8 Power ON Procedures and Precautions .... 111 5.9 Problem Analysis ..... 113 5.10 System Power-Up Diagnostics (SPUD) .... 113 5.11 Stand-alone Diagnostic Interactive Executive (SADIE) ..... 116 Purpose of SADIE ..... 116 5.11.1 5.11.2 Organization and Principals of Operation ..... 116 5.13 SADIE Program Initialization ..... 118 5.14 SADIE Diagnostic Functions ..... 118 5.14.1 Console Interactions ..... 118

HRM

vii

٠

TABLE OF CONTENTS (continued)

| SECTION 5 | 5 | MAINTENANCE (continued)                                                          |

|-----------|---|----------------------------------------------------------------------------------|

|           |   | 5.14.2 START and RESET Interactions 121                                          |

|           |   | 5.15 Command Level Test Functions 121                                            |

|           |   | 5.15.1 Command Level T: Choose and<br>run a single TEST                          |

|           |   | previously loaded single test 124<br>5.15.3 Command Level L: Run                 |

|           |   | current test LIST                                                                |

|           |   | run a test list                                                                  |

|           |   | 5.15.5 Command Level E: EDIT test<br>list 126<br>5.15.6 Command Level D: DISPLAY |

|           |   | error log 229<br>5.15.7 Command Level Q: QUIT 129                                |

|           | ÷ | 5.16 SADIE Test Line and Control<br>Statements 129                               |

|           |   | 5.16.1 SADIE Test List                                                           |

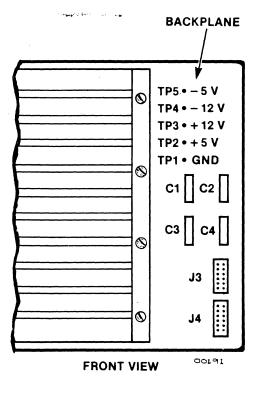

|           |   | 5.17 Using SADIE 131<br>5.18 Power Supply Voltages 135                           |

| APPENDIX  | A | SUMMARY OF Z8001 INSTRUCTION SET 139                                             |

| APPENDIX  | В | SUMMARY OF PROGRAMMABLE DEVICES 155                                              |

| APPENDIX  | С | WINCHESTER DISK CONTROLLER COMMANDS 169                                          |

| APPENDIX  | D | CARTRIDGE TAPE ERROR CONDITIONS 175                                              |

| APPENDIX  | E | SADIE TEST DESCRIPTIONS                                                          |

Zilog

viii

HRM

## LIST OF ILLUSTRATIONS

Figure

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7               | System 8000<br>System 8000 CPU Board<br>System 8000 Winchester Disk Controller<br>System 8000 Cartridge Tape Controller<br>System 8000 ECC Memory Controller<br>ECC Memory Array, 256 Kilobytes<br>System 8000 Functional Relationships                                                   | 7<br>8                                                      |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

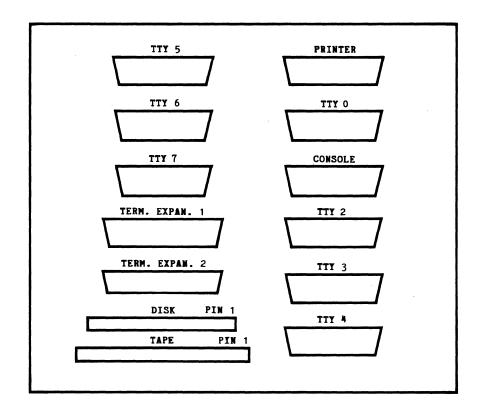

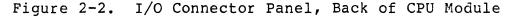

| 2-1<br>2-2<br>2-3                                           | Modules without Side Panels, Dimensions<br>I/O Connector Panel, Back of CPU Module<br>Backplane of Card Cage in CPU Module,<br>Slot Assignment (Viewed from front of Card Cage)                                                                                                           | 14<br>15<br>21                                              |

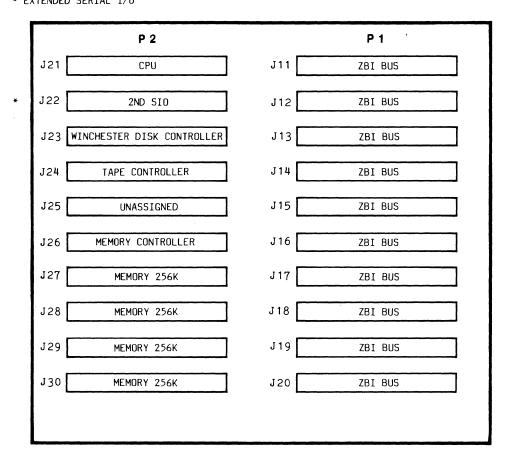

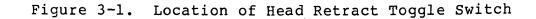

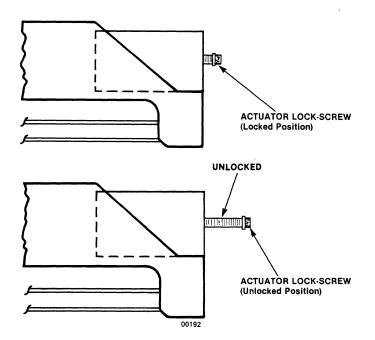

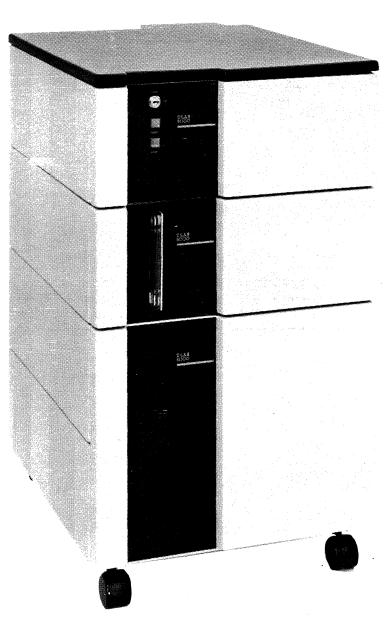

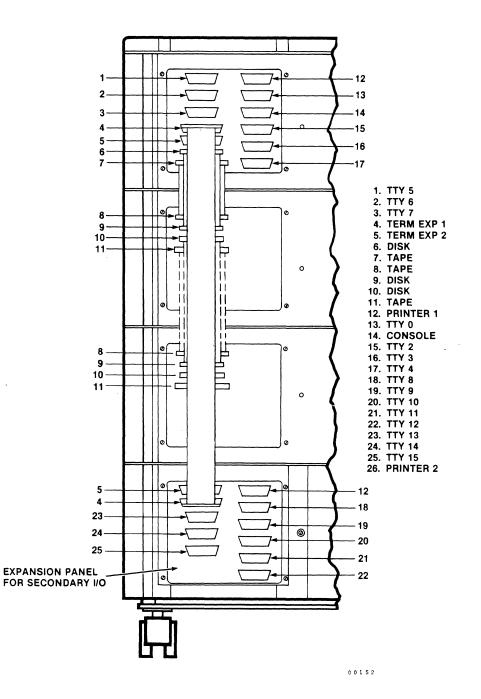

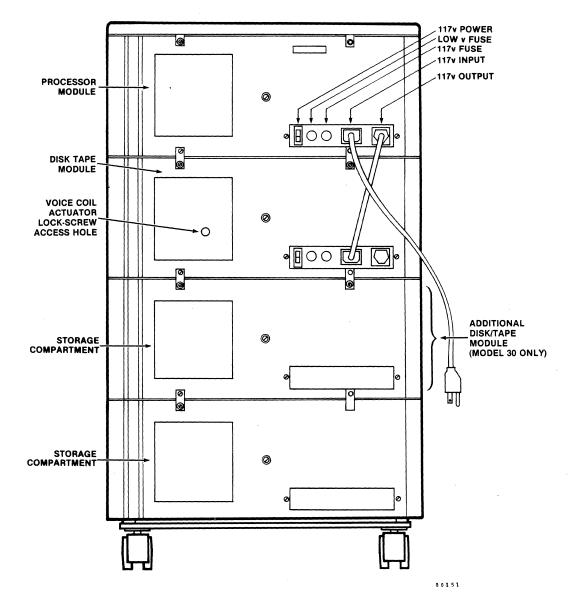

| 3-1<br>3-2<br>3-3<br>3-4<br>3-5                             | Location of Heat Retract Toggle Switch<br>Linear Voice-Coil Actuator Lock Screw, BASF Drives<br>System 8000<br>Connector Identification<br>System 8000, Model 20, Rear View                                                                                                               | 37<br>37<br>38<br>39<br>40                                  |

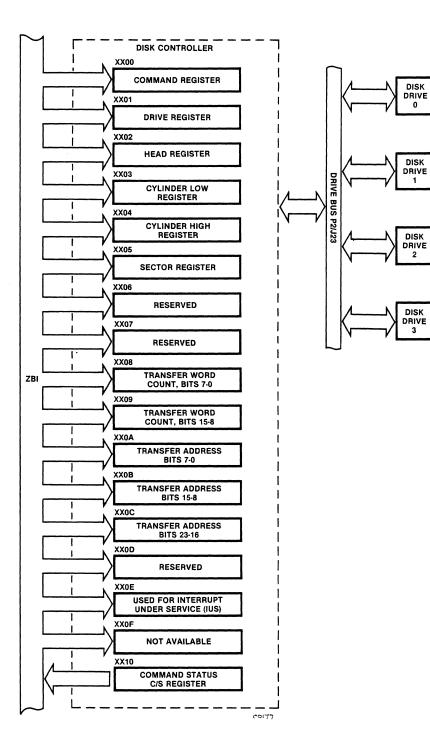

| 4-1<br>4-2<br>4-3                                           | System 8000, Functional Relationships<br>CPU Module, Functional Relationships<br>Winchester Disk Controller,                                                                                                                                                                              | 42<br>53                                                    |

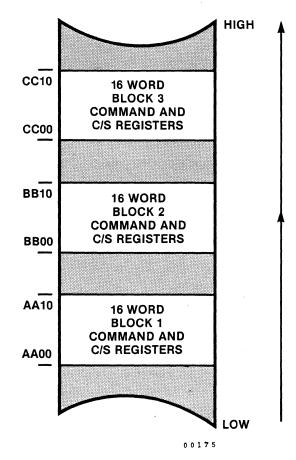

| 4-4                                                         | Functional Relationships<br>Disk Controller Command and Command Status (C/S)                                                                                                                                                                                                              | 5 <b>9</b>                                                  |

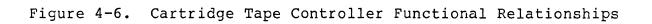

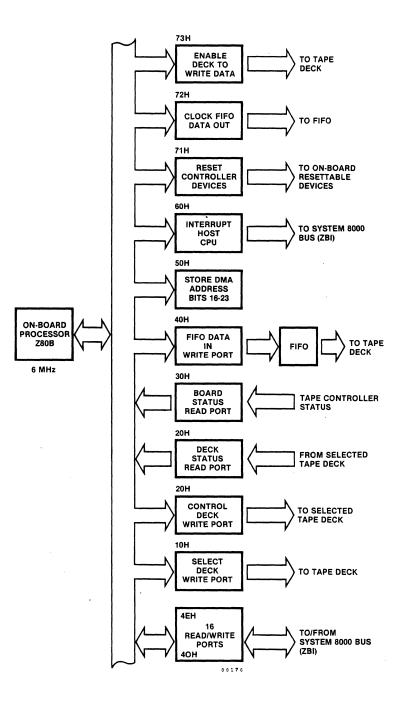

| 4-5<br>4-6                                                  | Registers<br>Disk Controller, I/O Space<br>Cartridge Tape Controller Functional                                                                                                                                                                                                           |                                                             |

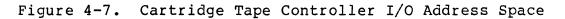

| 4-7<br>4-8<br>4-9                                           | Relationships<br>Cartridge Tape Controller I/O Space<br>Cartridge Tape Controller, Command Processing<br>Memory Subsystem Controller, Functional                                                                                                                                          | 71<br>72<br>84                                              |

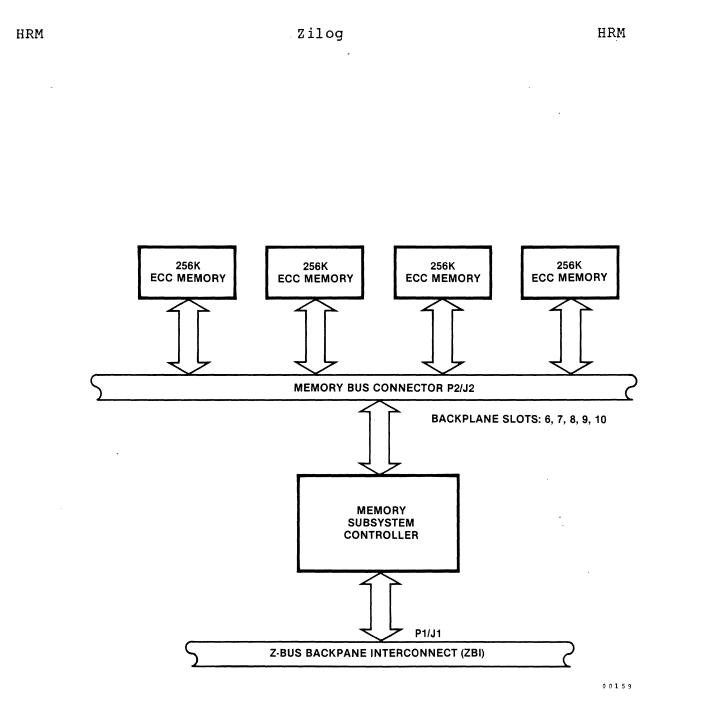

| 4-10<br>4-11                                                | Relationships<br>Memory Organization<br>Byte Translation<br>Word Translation<br>Long-Word Translation<br>Interrupt Priority Connections                                                                                                                                                   | 87<br>88<br>89<br>89<br>93                                  |

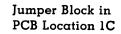

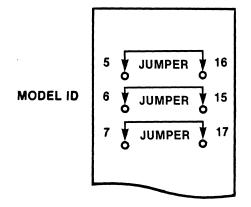

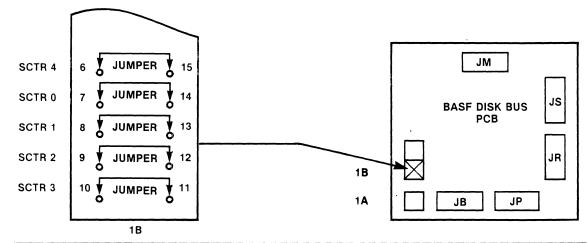

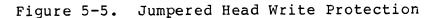

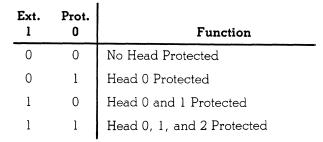

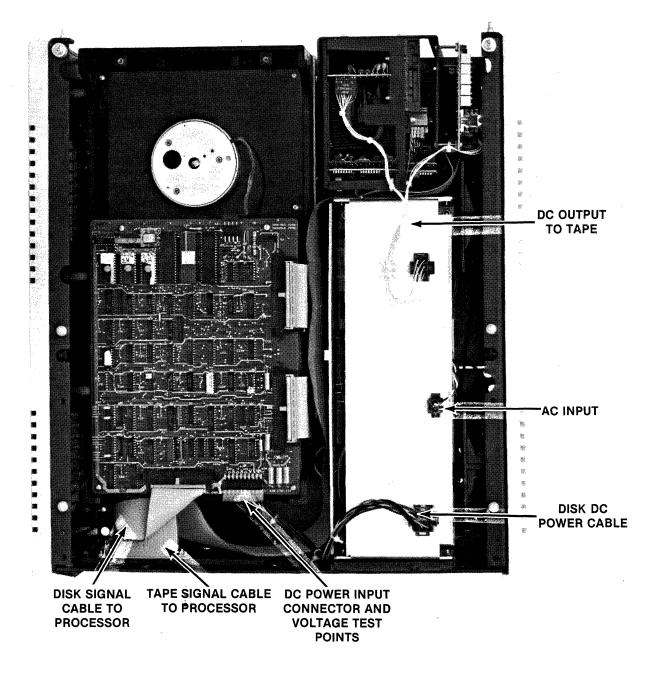

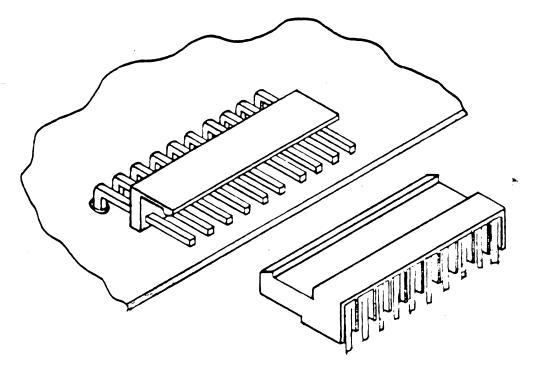

| 5-1<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8<br>5-9 | Location of Parts Requiring Periodic Cleaning<br>Unit Address Selection<br>Model ID Selection<br>Sector Size Selection<br>Jumpered Head Write Protection<br>Programmed Head Write Protect<br>Disk Drive Cable Locations<br>Disk Drive Power Connector<br>Power Supply Voltage Test Points | 101<br>103<br>104<br>105<br>107<br>108<br>110<br>112<br>137 |

Zilog

X

LIST OF TABLES

| Tabl | е |

|------|---|

|------|---|

| 2-1   | ······································             | 11       |

|-------|----------------------------------------------------|----------|

| 2-2   |                                                    | 11       |

| 2-3   |                                                    | 12       |

| 2-4   |                                                    | 12       |

| 2-5   |                                                    | 13       |

| 2-6   |                                                    | 16       |

| 2-7   |                                                    | 16       |

| 2-8   |                                                    | 17       |

| 2-9   |                                                    | 18       |

| 2-10  | Backplace Connector, Jll through J20 (ZBI)         |          |

|       |                                                    | 19       |

| 2-11  | CPU Board, Connector P2/J21, Slot 1                |          |

|       |                                                    | 23       |

| 2-13  | Winchester Disk Controller, Connector P2/J23,      |          |

|       |                                                    | 24       |

| 2-14  | Catridge Tape Controller, Connnector P2/J24,       | ~ -      |

| ~ · - |                                                    | 25       |

| 2-15  | System 8000 Memory Bus, Connector P2/J26-J30       |          |

|       | Slots 6 through 10                                 | 26       |

|       |                                                    |          |

| 4-1   |                                                    | 43       |

| 4-2   |                                                    | 49       |

| 4-3   |                                                    | 49       |

| 4-4   |                                                    | 51       |

| 4-5   |                                                    | 54       |

| 4-6   | Parallel Printer Output Control Signals,           |          |

|       | Port A                                             | 55       |

| 4-7   | Parallel Printer Input Status Signals, Port A      | 55       |

| 4-8   | Parallel Printer Data, Port B                      | 55       |

| 4-9   | Serial I/O Devices and Channel Assignments         | 55<br>56 |

| 4-10  | Serial Channels and Baud Rate Generators           |          |

|       | Baud Rate Settings, Switch u70                     | 56<br>57 |

|       | I/O Channels and Their Addresses                   | 57       |

| 4-13  | Disk Controller and Disk Drive, Interface Signals, | 62       |

| A 7 A | Connector P2/J23, Slot 3                           |          |

|       | Command and Command Status Registers               | 64       |

| 4-15  | Jumper Settings for Address of Command and C/S     | 66       |

| 1 10  | <b>j</b>                                           |          |

|       | Disk Controller Jumper Settings for Memory         | 67       |

| 4-1/  | Disk Controller Jumper Settings for Selection of   | <u> </u> |

| 4 10  | BASF or IMI Disk Drive                             | 68       |

|       | Disk Command and Status Words                      | 69       |

|       | ZBI Tape Controller, Interface Registers           | 73       |

|       | Tape Controller Jumper Selection for Base Address  | 74       |

|       | Tape Interrupt Vector, Bit Definitions             | 76       |

| 4-22  | Host-Tape Controller Commands                      | 77       |

Х

## LIST OF TABLES (continued)

## Table

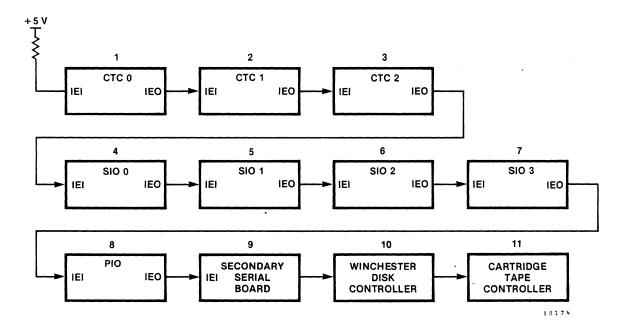

| 4-24<br>4-25<br>4-26 | Status Register, Bit Definition<br>Master Interrupt Control Register, Bit Definition<br>Tape Controller to Drive Interface Signals<br>Tape Drive to Controller Interface Signals<br>Device Priority Scheme | 80<br>81<br>83 |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| 5-2                  | Cleaning Schedule<br>Interface Cables<br>SPUD Diagnostics Error List                                                                                                                                       | 109            |

.

Carlos and

xi

. \* .

1

#### SECTION 1

#### CVERVIEW

#### 1.1 System Description

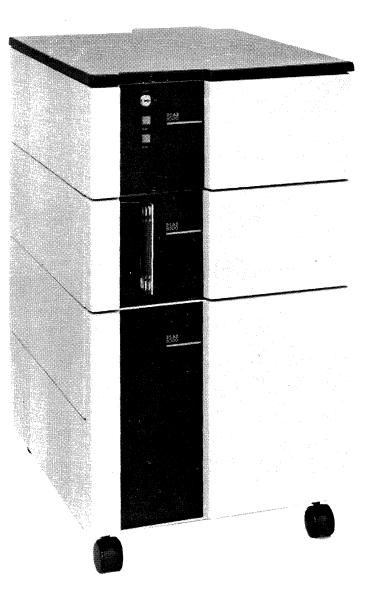

The System 8000 is a free-standing, semiportable unit, based on Zilog's 16-bit Z8001 microprocessor and running on the ZEUS Operating System at 5.5 megahertz. Figure 1-1 shows the enclosure containing the modules that make up the system. The top module has a ten-slot card cage and, behind the card cage, two power supplies. The module beneath the top module has a 24-megabyte Winchester disk drive and a 17-megabyte cartridge tape drive. The remainder of the enclosure beneath the two modules can be used for storage or for expanding the capabilities of the system by adding additional disk or tape units or both.

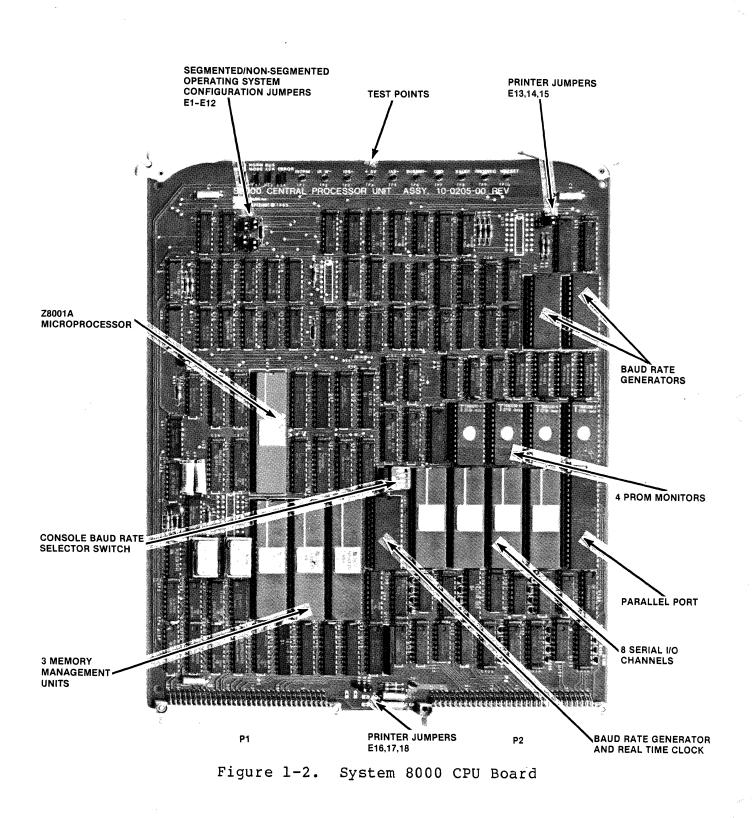

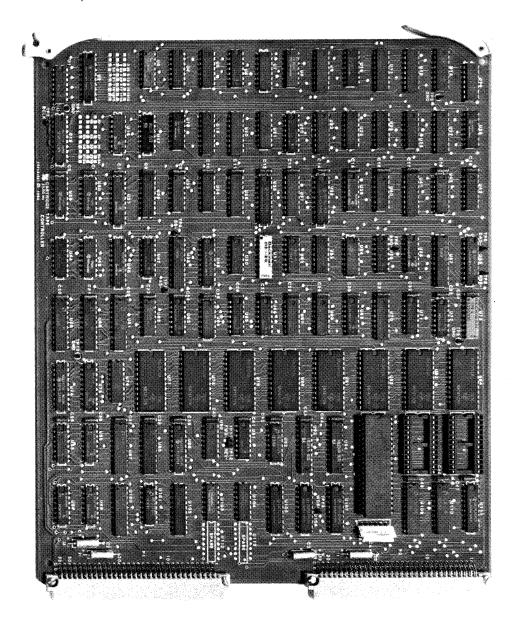

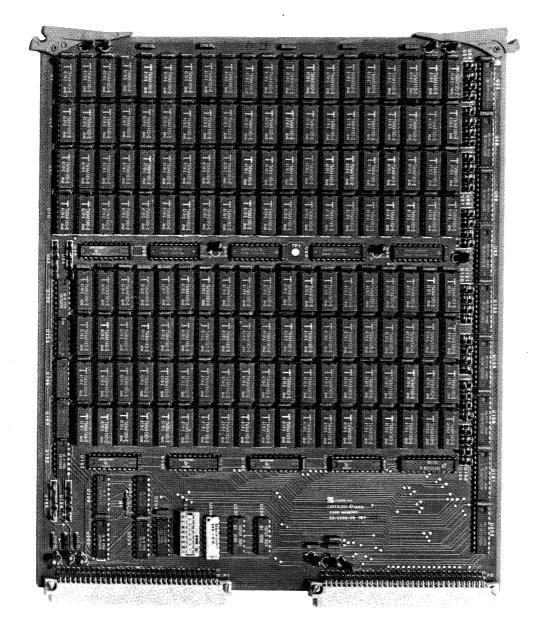

The basic system contains five printed circuit boards in the ten-slot card cage. These boards (Figures 1-2 through 1-6) are the CPU, the Winchester Disk Controller, the Cartridge Tape Controller, the Memory Subsystem Controller, and the 256K Byte ECC Memory. The lower five slots of the card cage are dedicated to memory; with the addition of three more memory boards, the basic 256-kilobyte system can have a physical memory space of 1 megabyte, not including the small bootstrap memory on the CPU board.

#### 1.2 Functional Relationships

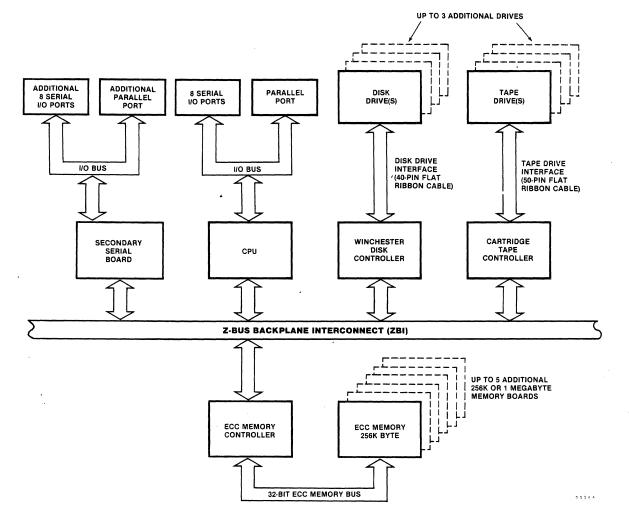

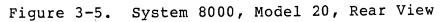

The block diagram in Figure 1-7 shows the functional relationships of the major elements (boards) that make up the basic system. These elements communicate with one another over Zilog's Z-Bus Backplane Interconnect (ZBI), a highspeed, 32-bit, semisynchronous bus. The following paragraphs briefly describe the functions of each element on the bus.

]

Figure 1-1. System 8000

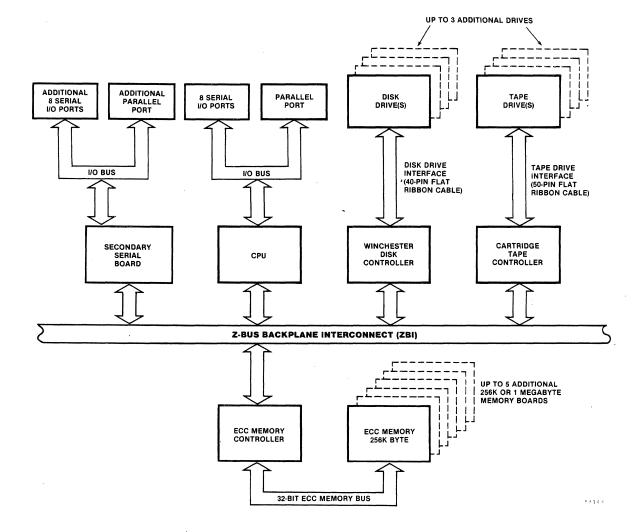

#### 1.2.1 CPU Board

The CPU is the host of the System 8000; it controls the ZBI and terminal communications into and out of the system. As shown in Figure 1-7, the CPU supports eight serial I/O ports and a parallel I/O port. The serial ports are compatible with both the RS232-C and the RS423 standards. The parallel port, with the appropriate jumpers inserted, is compatible with the line printer standards of either Centronics or Data Products.

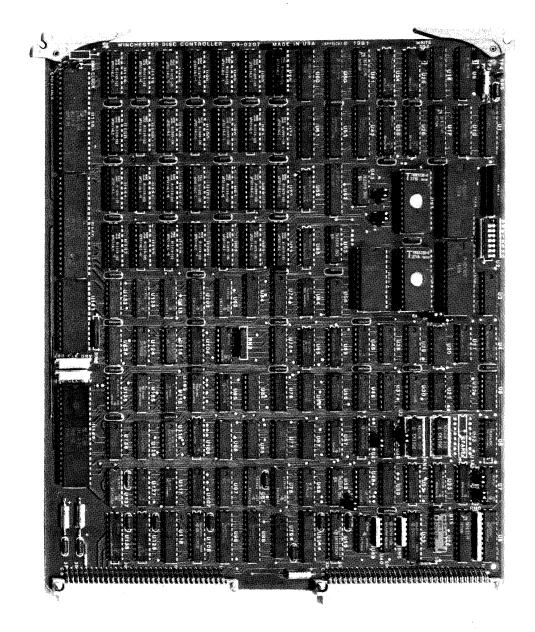

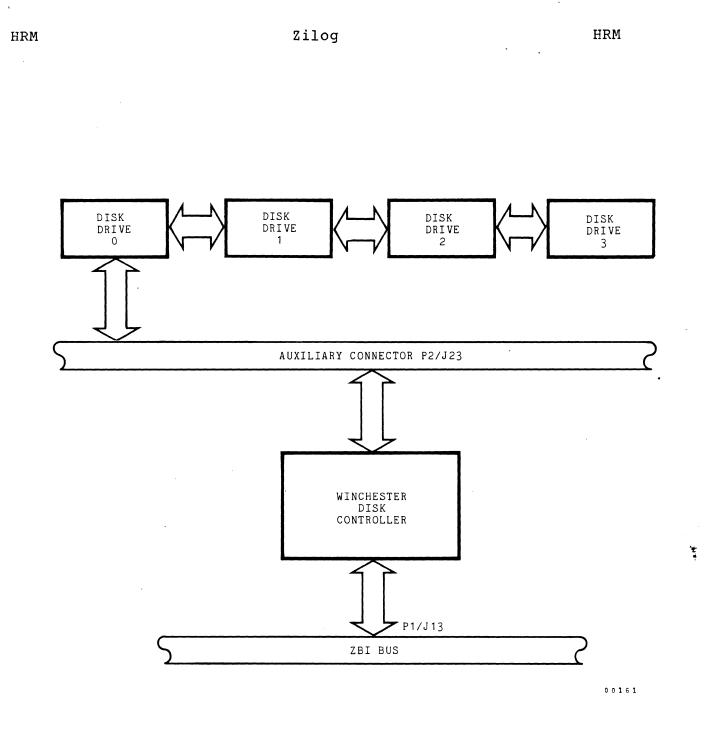

#### 1.2.2 Winchester Disk Controller

The disk controller enables the CPU to communicate with up to four Winchester disk drives. An intelligent bus module with an on-board Z80B microprocessor, the controller can be polled or interrupt-driven by the CPU. The appropriate jumper arrangement determines the controller's mode of operation. The disk is organized into 512-byte sectors. A single command can cause the transfer of up to 128 512-byte sectors. In addition, the disk controller uses a full-track buffer which permits the transfer of 24 512-byte sectors in one disk revolution.

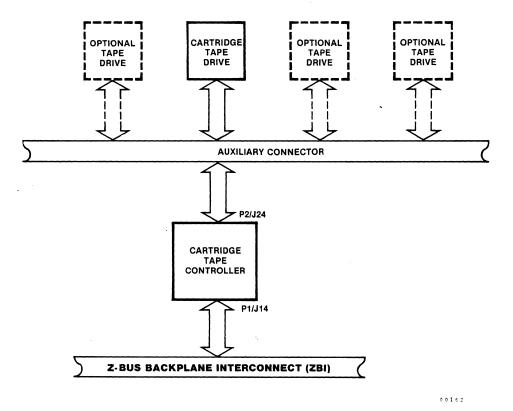

#### 1.2.3 Cartridge Tape Controller

The tape controller is the intelligent interface between the CPU and up to four cartridge tape drives. A Zilog Z80B microprocessor controls the operation of the controller. The controller uses direct-memory access (DMA) to transfer data between the cartridge tape drive and the CPU. When the CPU wants to initiate an operation, it sends a command to the controller. The controller completes the specified operation and then interrupts the CPU to notify it that the operation is complete.

#### 1.2.4 Memory Subsystem Controller

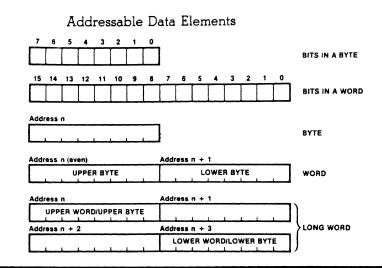

The memory controller can control the operation of up to 16 megabytes of dynamic read/write memory. The data can be transferred as bytes (eight bits), words (16 bits), or long words (32 bits); the controller translates the width of the data and places the data in the proper locations. The controller transparently corrects all single-bit errors and detects all double-bit errors. The controller uses a softerror logging system that counts soft errors in each 64K-byte block of memory.

HRM

ine - se

All and a

5

Figure 1-3. System 8000 Winchester Disk Controller

Figure 1-4. System 8000 Cartridge Tape Controller

Alternation of

7

|                                                                    |                                                                      | Ma + 3.0 |

|--------------------------------------------------------------------|----------------------------------------------------------------------|----------|

|                                                                    | و دودوده<br>ال<br>ال<br>ال<br>ال<br>ال<br>ال<br>ال<br>ال<br>ال<br>ال |          |

| 101<br>101<br>101<br>101<br>101<br>101<br>101<br>101<br>101<br>101 |                                                                      |          |

|                                                                    |                                                                      |          |

|                                                                    |                                                                      |          |

|                                                                    |                                                                      |          |

|                                                                    |                                                                      |          |

|                                                                    |                                                                      |          |

|                                                                    |                                                                      |          |

|                                                                    |                                                                      |          |

|                                                                    |                                                                      |          |

Figure 1-5. System 8000 Memory Subsystem Controller

Zilog

Figure 1-6. ECC Memory Array, 256 Kilobytes

#### 1.2.5 Memory Array

HRM

The ECC (error checking and correcting) Memory Array contains storage space for 256 kilobytes of data; in addition, it has storage for the syndrome bits used by the error checking and correcting logic. All data during memory transactions passes through the memory controller; the memory has no direct connection to the system bus (ZBI) (Figure 1-7). Instead, a high-speed, 32-bit bus connects the memory to the memory controller.

#### 1.3 System Expansion

The System 8000 can be expanded by adding up to three additional 24-megabyte or 40-megabyte disk drives, three additional cartridge tape drives, up to six megabytes of ECC RAM, and a Secondary Serial I/O Board that can support an additional eight serial I/O ports and one additional parallel printer port.

Figure 1-7. System 8000, Functional Relationships

#### SECTION 2

#### SYSTEM SPECIFICATIONS

#### 2.1 Introduction

This section contains the electrical, performance, physical, and environmental specifications for the System 8000, Model 20.

#### 2.2 Electrical Specifications

Table 2-1 lists the power requirements of systems that are installed in the U.S. (domestic). Table 2-2 lists the power requirements of systems that are installed outside of the U.S.; these requirements are the international requirements.

Table 2-1. Electrical Requirements, Domestic

| ITEM | REQUIREMENT |

|------|-------------|

|      |             |

Voltage 117 Vac nominal (range: 105 to 128 Vac)

Phase Single

| Frequency | 7 60 | Hertz |

|-----------|------|-------|

|           |      |       |

| Current | Sustained: |   | d: | 5 ampe: | res maximum |

|---------|------------|---|----|---------|-------------|

|         | Surge      | : | 8  | amperes | maximum     |

Table 2-2. Electrical Requirements, International

| ITEM      | REQUIREMENT                                                |  |  |

|-----------|------------------------------------------------------------|--|--|

| Voltage   | 220 Vac (range: 198 to 242 Vac)                            |  |  |

| Phase     | Single                                                     |  |  |

| Frequency | 50 Hertz                                                   |  |  |

| Current   | Sustained: 2.5 amperes maximum<br>Surge: 4 amperes maximum |  |  |

2.3 Performance Specifications

Tables 2-3 and 2-4 define the performance characteristics of the disk and tape drives.

Table 2-3. Winchester Disk Performance Characteristics

| ITEM                     | CHARACTERISTIC           |

|--------------------------|--------------------------|

| Rotational speed         | 3,600 RPM                |

| Power-on to ready time   | 15 seconds               |

| Average positioning time | 42 milliseconds          |

| Number of surfaces       | 3 or 5                   |

| Tracks per surface       | 600                      |

| Sectors per track        | 24                       |

| Bytes per sector         | 512                      |

| Rate of data transfer    | 801 kilobytes per second |

Table 2-4. Cartridge Tape Drive Performance Characteristics

| ITEM                | CHARACTERISTIC             |  |  |

|---------------------|----------------------------|--|--|

| Read/Write speed    | 30 inches per second (ips) |  |  |

| Rewind/Search speed | 90 inches per second (ips) |  |  |

| Tracks              | 4                          |  |  |

| Recording density   | 6400 BPI                   |  |  |

#### 2.4 Physical Specifications

This paragraph defines the specifications for the modules, boards, card cages, and connectors that make up the System 8000. Table 2-5 lists the basic specifications of an assembled system.

## Table 2-5. Physical Specifications

ITEM

| Height | 84 centimeters (33 inches)               |

|--------|------------------------------------------|

| Width  | 48 centimeters (19 inches)               |

| Depth  | 61 centimeters (24 inches)               |

| Weight | 60 kilograms (132 pounds)<br>approximate |

SPECIFICATION

### 2.4.1 Modules

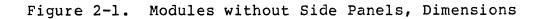

The modules, with their side panels removed, can be mounted in standard 19-inch racks. In stand-alone configurations, the modules can be stacked. The dimensions of the module with its side panel removed are shown in Figure 2-1.

13

13

HRM

.

TOP VIEW SIDE VIEW 20.5" -17.5"--7.25"-FRONT VIEW CARD CAGE

00165

•

Zilog

Figure 2-2 identifies the I/O connectors on the rear panel of the CPU Module. Table 2-6 lists the required mating connectors and sources; Table 2-7 lists the pin assignments of the serial (TTY) I/O connectors. Table 2-8 lists the pin assignments of the parallel (PRINTER) connectors.

#### NOTE

When serial I/O uses only the transmit and receive data lines, connect:

a) pin 4 (RTS) to pin 5 (CTS) b) pin 6 (DSR) to pin 20 (DTR)

on the connector to avoid intermittent operation of serial lines.

15

HRM

## Table 2-6. I/O Connectors

Zilog

| DESIGNATION                      | DESCRIPTION                   | VENDOR/PART NUMBER                                |  |

|----------------------------------|-------------------------------|---------------------------------------------------|--|

| Printer                          | 25-pin D Connector            | ITT Cannon<br>DBUE25SBB                           |  |

| TTY0-TTY7                        |                               | TRW Cinch<br>DBUE25SBF                            |  |

| Terminal<br>Expansion<br>l and 2 | 37-pin D Connector            | ITT Cannon<br>DCUE37SBB<br>TRW Cinch<br>DCUE37SBF |  |

| Disk Drive                       | 40-wire flat<br>ribbon socket | 3M<br>3417-6040                                   |  |

| Tape Drive                       | 50-wire flat<br>ribbon socket | 3M<br>3425-6050                                   |  |

Table 2-7. TTY Connector, Pin Assignments

SIGNAL NAME

PIN

| Ground | 7  |

|--------|----|

| DTR    | 20 |

| RTS    | 4  |

| TXD    | 2  |

| DSR    | 6  |

| CTS    | 5  |

| RXD    | 3  |

## HRM

## Table 2-8. Printer Connector, Pin Assignments

## Data Products Interface

| Signal Name                                                                                                                                                                         | P2 Backplane                                                                                                                          | Printer Port<br>Connector<br>Pins                                                    | Printer<br>Connector<br>Pins                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| DATA 0<br>DATA 1<br>DATA 2<br>DATA 2<br>DATA 3<br>DATA 4<br>DATA 5<br>DATA 6<br>DATA 7<br>DATA 5<br>DATA 7<br>DATA STROBE<br>INPUT PRIME<br>DATA DEMAND<br>FAULT<br>READY<br>ONLINE | P2-1C<br>P2-2C<br>P2-3C<br>P2-5C<br>P2-6C<br>P2-8C<br>P2-9C<br>Not Used<br>P2-12C<br>Not Used<br>P2-16C<br>P2-20C<br>P2-17C<br>P2-21C | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>Not Used<br>9<br>Not Used<br>11<br>12<br>23<br>24 | B<br>F<br>L<br>R<br>V<br>Z<br>n<br>Not Used<br>j<br>Not Used<br>E<br>C<br>cc<br>Y |

| SIGNAL GROUND                                                                                                                                                                       | P2-19C                                                                                                                                | 22                                                                                   | Х                                                                                 |

Centronics Interface

| Signal Name                                                                                                                                                                                                                                                                                                            | P2 Backplane                                                                                                                                                                  | Printer Port<br>Connector<br>Pins                                                                      | Printer<br>Connector<br>Pins                                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>DATA 0</li> <li>DATA 1</li> <li>DATA 2</li> <li>DATA 3</li> <li>DATA 4</li> <li>DATA 5</li> <li>DATA 6</li> <li>DATA 6</li> <li>DATA 7</li> <li>DATA STROBE</li> <li>INPUT PRIME</li> <li>ACKNOWLEDGE</li> <li>FAULT</li> <li>GROUND</li> <li>GROUND</li> <li>GROUND</li> <li>BUSY</li> <li>SELECT</li> </ul> | P2-1C<br>P2-2C<br>P2-3C<br>P2-5C<br>P2-6C<br>P2-8C<br>P2-9C<br>Not Used<br>P2-12C<br>Not Used<br>P2-16C<br>P2-20C<br>P2-32C<br>P2-32B<br>P2-32A<br>P2-32A<br>P2-17C<br>P2-21C | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>Not Used<br>9<br>Not Used<br>11<br>12<br>18<br>19<br>20<br>23<br>24 | 2 84<br>3 6<br>4 7<br>5<br>6<br>7<br>7<br>8<br>8<br>Not Used<br>10<br>32 4 6 2 (2)<br>24<br>25<br>26<br>11 / 228 /<br>13 |

17

#### 2.5 Environmental Specifications

The System 8000 can be expected to perform reliably provided the environmental specifications listed in Table 2-9 are maintained.

Table 2-9. Environmental Specifications

Operating temperature:

10 degrees C (50 degrees F) minimum 40 degrees C (104 degrees F) maximum

Relative humidity:

80% noncondensing

Noise level:

48 dba

2.6 Backplane (ZBI) Pin Assignments

Figure 2-3 shows the backplane into which the circuit boards are plugged. The view is from the front of the card cage. Only the connectors designated Jll through J20 (on the right) connect to the system bus, known as the Z-Bus Backplane Interconnect (ZBI). The connectors designated J21 through J30 (on the left) are auxiliary connectors. The pin assignments of all ZBI connectors are the same; Table 2-10 lists these ZBI pin assignments. Table 2-10. Backplane Connector, Jll through J20 (ZBI), Pin Assignments

| PIN                                                                                                                                                                      | Row A  | Row B  | Row C  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|

|                                                                                                                                                                          | SIGNAL | SIGNAL | SIGNAL |

| $ \begin{array}{c} 1\\ 2\\ 3\\ 4\\ 5\\ 6\\ 7\\ 8\\ 9\\ 10\\ 11\\ 12\\ 13\\ 14\\ 15\\ 16\\ 17\\ 18\\ 19\\ 20\\ 21\\ 22\\ 23\\ 24\\ 25\\ 26\\ 27\\ 28\\ 29\\ \end{array} $ |        |        |        |

| 30                                                                                                                                                                       | +12v   | +12v   | +12v   |

| 31                                                                                                                                                                       | -12v*  | -12v*  | -12v*  |

| 32                                                                                                                                                                       | GND    | GND    | GND    |

-l2v is allocated space on the ZBI backplane, but is not used nor generated by the S8000 system.

HRM

and the second

\*

The pin assignments of the connectors J21 to J30 differ from slot to slot; the bottom 5 connectors are the same. Figure 2-3 shows how the slots are dedicated; the following list indicates the tables that have the pin assignments for the different J2 connectors.

- 1) Table 2-11: connector J21, CPU board

- 2) Table 2-12: connector J22, Extended Serial I/O board (optional)

- 3) Table 2-13: connector J23, Winchester Disk Controller board

- 4) Table 2-14: connector J24, Cartridge Tape Controller board

- 5) Table 2-15: connector J26 through J30, memory bus: Memory Subsystem Controller and Memory boards

\* EXTENDED SERIAL I/O

00163

21

Figure 2-3. Backplane of Card Cage in CPU Module, Slot Assignment (Viewed from front of Card Cage)

HRM

| Table 2-1 | l. CPU | Board, | Connector   | P2/J21, | Slot | 1 |

|-----------|--------|--------|-------------|---------|------|---|

|           |        | 200101 | 00111100001 |         |      | - |

| PIN                                  | Row A<br>SIGNAL                                                | Row B<br>SIGNAL                                              | Row C<br>SIGNAL                                                  |

|--------------------------------------|----------------------------------------------------------------|--------------------------------------------------------------|------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | TXRTNO<br>TXDO<br>RTSO<br>DSRO<br>TXD1<br>RTS1<br>DSR1<br>TXD3 | RXD0<br>CTS0<br>DTR0<br>RXD1<br>CTS1<br>DTR1<br>RXD2<br>CTS2 | DATAO<br>DATA1<br>DATA2<br>GND<br>DATA3<br>DATA4<br>GND<br>DATA5 |

| 9<br>10<br>11                        | RTS2<br>DSR2                                                   | DTR2<br>RXD3                                                 | DATA6<br>DATA7                                                   |

| 12                                   | TXD3<br>RTS3                                                   | CTS3<br>DTR3                                                 | GND<br>DATA STROBE/DATA<br>STROBE\                               |

| 13<br>14<br>15                       | DSR3<br>TXD4<br>RTS4                                           | RXD4<br>CTS4<br>DTR4                                         | N.U./INPUT PRIME<br>TXRTN1<br>GND                                |

| 16<br>17<br>18                       | DSR4<br>TXD5<br>RTS5                                           | RXD5<br>CTS5<br>DTR5                                         | D.D./ACKNOWLEDGE\<br>BUSY\<br>TXRTN2                             |

| 19<br>20                             | DSR5<br>TXD6                                                   | RXD6<br>CTS6                                                 | GND<br>IFVALID/FAULT\                                            |

| 21<br>22                             | RTS6<br>DSR6                                                   | DTR6<br>RXD7                                                 | ON-LINE/SELECT<br>F.P BUSACK<br>INDICATOR                        |

| 23<br>24                             | TXD7<br>RTS7                                                   | CTS7<br>DTR7                                                 | F.P. POWER-ON<br>INDICATOR (GND)<br>F.P. NORMAL                  |

| 25                                   | DSR7                                                           | TXRTN5                                                       | INDICATOR<br>NMI SWITCH<br>(NORMALLY CLOSED)                     |

| 26                                   | TXRTN3                                                         | TXRTN6                                                       | NMI SWITCH<br>(NORMALLY OPEN)                                    |

| 27<br>28                             | TXRTN4<br>+5v                                                  | TXRTN7<br>+5v                                                | SW RESET<br>F.P. INDICATOR V+<br>(+5v)                           |

| 29<br>30<br>31<br>32                 | -5v<br>+12v<br>-12v<br>GND                                     | -5v<br>+12v<br>-12v<br>GND                                   | -5v<br>+12v<br>-12v<br>GND                                       |

22

Zilog

|       | P2/J   | 22, Slot 2 |                   |

|-------|--------|------------|-------------------|

| 5.7.1 | Row A  | Row B      | Row C             |

| PIN   | SIGNAL | SIGNAL     | SIGNAL            |

| 1     | TXRTN0 | RXD0       | DATA0             |

| 2     | TXD0   | CTS0       | DATAl             |

| 3     | RTS0   | DTR0       | DATA2             |

| 4     | DSR0   | RXD1       | GND               |

| 5     | TXDl   | CTSl       | DATA3             |

| 6     | RTS1   | DTR1       | DATA4             |

| 7     | DSR1   | RXD2       | GND               |

| 8     | TXD3   | CTS2       | DATA5             |

| 9     | RTS2   | DTR2       | DATA6             |

| 10    | DSR2   | RXD3       | DATA7             |

| 11    | TXD3   | CTS3       | GND               |

| 12    | RTS3   | DTR3       | DATA STROBE/DATA  |

|       |        |            | STROBE            |

| 13    | DSR3   | RXD4       | N.U/INPUT PRIME   |

| 14    | TXD4   | CTS4       | TXRTN1            |

| 15    | RTS4   | DTR4       | GND               |

| 16    | DSR4   | RXD5       | D.D./ACKNOWLEDGE\ |

| 17    | TXD5   | CTS5       | BUSY\             |

| 18    | RTS5   | DTR5       | TXRTN2            |

| 19    | DSR5   | RXD6       | GND               |

| 20    | TXD6   | CTS6       | IFVALID/FAULT\    |

| 21    | RTS6   | DTR6       | ON-LINE/SELECT    |

| 22    | DSR6   | RXD7       |                   |

| 23    | lXD7   | CTS7       | GND               |

| 24    | RTS7   | DTR7       | N.V./LP. CONT     |

| 25    | DSR7   | TXRTN5     |                   |

| 26    | TXRTN3 | TXRTN6     |                   |

| 27    | TXRTN4 | TXRTN7     | _                 |

| 28    | +5v    | +5v        | +5v               |

| 29    | -5v    | -5v        | -5v               |

| 30    | +12v   | +12v       | +12v              |

| 31    | -12v   | -12v       | -12v              |

| 32    | GND    | GND        | GND               |

Table 2-12. Secondary Serial I/O, Connector P2/J22, Slot 2

23

23

P

| Т                               | able 2-13. Winc<br>P2/J2                   | hester Disk<br>3, Slot 3                       | Controller,        | Connector |

|---------------------------------|--------------------------------------------|------------------------------------------------|--------------------|-----------|

| PIN                             | Row A<br>SIGNAL                            | Row B<br>SIGNAL                                | Row C<br>SIGNAL    |           |

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | CBO<br>CB2<br>CB3                          | CB1                                            |                    |           |

| 4<br>5                          | CB5<br>CB6                                 | CB4                                            | GND                |           |

| 6<br>7<br>8                     | DIRECTION\<br>CWD0\                        | CB7<br>CWD1\                                   | GND                |           |

| 9<br>10                         | $CYACK \setminus INDEX \setminus$          |                                                |                    |           |

| 11<br>12<br>13                  |                                            | SECTOR\<br>SEEKEND\                            | GND                |           |

| 13<br>14<br>15<br>16            | SYSTEMCLK<br>UNITACK0\                     | WRITE-CLK<br>ATTACK<br>SYSTEMCLK\<br>UNITACK1\ | GND                |           |

| 17<br>18                        | UNITACK2\<br>READ-ENABLE\<br>MASTER RESET\ | BI-DATA<br>UNITACK3\                           | GND                |           |

|                                 | WRITE ENABLE                               |                                                |                    |           |

| 23<br>24<br>25                  |                                            |                                                | GND                |           |

| 26<br>27                        |                                            |                                                |                    |           |

| 28<br>29<br>30                  | +5v<br>-5v<br>+12v                         | +5v<br>-5v<br>+12v                             | +5v<br>-5v<br>+12v |           |

| 31<br>32                        | -12v<br>GND                                | -12v<br>GND                                    | -12v<br>GND        |           |

HRM

.

| Table 2-14. | Cartridge Tape Controller, Connector P2/J | 24, |

|-------------|-------------------------------------------|-----|

|             | Slot 4, Pin Assignments                   |     |

| PIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            | Row A<br>SIGNAL | Row B<br>SIGNAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Row C<br>SIGNAL                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>6<br>7<br>8<br>9<br>0<br>112<br>14<br>5<br>8<br>9<br>0<br>112<br>14<br>5<br>14<br>14<br>15<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14<br>14 |                            |                 | SLD<br>RDY<br>WND<br>FLG<br>LPS<br>FUP<br>BSY<br>EWS<br>RWD<br>REV<br>FWD<br>HSP<br>WEN<br>SL1<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL2<br>SL4<br>SL4<br>SL2<br>SL4<br>SL4<br>SL4<br>SL4<br>SL4<br>SL4<br>SL4<br>SL4<br>SL4<br>SL4 | GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND |

| 25<br>26<br>27<br>28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | +5v                        |                 | TRl\+5v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | GND<br>+5v                                                         |

| 28<br>29<br>30<br>31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | +5V<br>-5V<br>+12V<br>-12V |                 | -5v ·<br>+12v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | +5v<br>-5v<br>+12v<br>-12v                                         |

| 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | GND                        | ,               | GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | GND                                                                |

Zilog

25

25

Second and

Table 2-15. System 8000 Memory Bus, Connector P2/J26-30, Slots 6 through 10

| PIN                                  | Row A                        | Row B                   | Row C  |

|--------------------------------------|------------------------------|-------------------------|--------|

|                                      | SIGNAL                       | SIGNAL                  | SIGNAL |

| 1                                    | MD38\                        | MD37\                   |        |

| 2                                    | MD36\                        | MD35\                   |        |

| 3                                    | MD34\                        | MD33\                   |        |

| 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8 | MD32<br>MD30<br>MD28         | MD31<br>MD29<br>MD27    | GND    |

| 7                                    | MD26\                        | MD25\                   | GND    |

| 8                                    | MD24\                        | MD23\                   |        |

| 9                                    | MD22\                        | MD21\                   |        |

| 10                                   | MD20\                        | MD19\                   | GND    |

| 11                                   | MD18\                        | MD17\                   |        |

| 12                                   | MD16\                        | MD15\                   |        |

| 13                                   | MD14\                        | MD13\                   | GND    |

| 14 -                                 | MD12\                        | MD11\                   |        |

| 15                                   | MD10\                        | MD09\                   |        |

| 16                                   | MD08\                        | MD07\                   |        |

| 17<br>18<br>19                       | MD08<br>MD06<br>MD04<br>MD02 | MD05\<br>MD03\<br>MD01\ | GND    |

| 20                                   | MD00\                        | MA16                    | READ   |

| 21                                   | MA17                         | MA18                    |        |

| 22                                   | MA19                         | MA20                    |        |

| 23                                   | MA21                         | MA22                    | GND    |

| 24                                   | MA23                         | RCO\                    | RAS\   |

| 25                                   | RC1\                         | RC2\                    | REF\a  |

| 26                                   | RC3\                         | RC4\                    | CAS\   |

| 27                                   | RC5\                         | RC6\                    | WRITE\ |

| 28                                   | +5v                          | +5v                     | +5v    |

| 29                                   | -5v                          | -5v                     | -5v    |

| 30                                   | +12v                         | +12v                    | +12v   |

| 31                                   | -12v                         | -12v                    | -12v   |

| 32                                   | GND                          | GND                     | GND    |

26

HRM

#### SECTION 3

#### INSTALLATION

### 3.1 Introduction

This section provides information to enable easy installation of the System 8000. It contains receiving inspection, unpacking, system locations, interconnection, and turn-on information.

#### 3.2 Receiving Inspection

The system has been pre-tested by factory specialists prior to being packed and installed in the shipping containers. However, during shipment mishandling may have occurred that will affect the operational capability of the system.

Visually inspect the exterior of the shipping carton. If visual inspection reveals the presence of unusual shipping carton damage, fill out a Shipping Damage Report for the shipping agent.

#### 3.3 Unpacking

The system has been carefully packed in individual shipping containers with styrofoam retaining supports that absorb shock and prevent movement within the packing carton during normal shipping and handling procedures. During unpacking procedures, carefully remove and keep all styrofoam retaining supports and other packing materials as required to allow access to the system enclosure. Save all styrofoam supports and other packing material until the performance verification procedures have been completed. Proceed with the unpacking instructions as follows:

Unpacking Procedure

- 1. Place the carton in an upright position.

- Remove styrofoam and other packing materials from each carton as required, to allow for removal of the contents.

- 3. Remove the system components from the shipping carton.

# 3.4 System 8000 Console Inspection

Visually inspect the system console for dents or evidence of mishandling. Make notations of any mishandling evidence in the Shipping Damage Report.

# 3.5 Internal Inspection

Unusual shipping and handling damage that is not obvious from packing carton or external cabinet visual inspections may have caused the printed circuit cards in the peripheral module to become displaced from connector sockets. If this condition is found, replace the PC cards in their appropriate slots as shown in Figure 2-3. The 256K Memory Array boards are inserted starting at slot ten (bottom) of the card cage, i.e., if one 256K Memory is included in the system, it is inserted in slot 10, if two 256K memories are included, they are inserted in slots 9 and 10. After all components have been inspected and any defective conditions have been corrected, proceed with the System 8000 assembly instructions beginning at paragraph 3.6.

The Peripheral Module is packed with foam packing material above, below, and on both sides of the module. This packing material should be removed before proceeding further. The disk and tape drives should not be powered up with the packing material in place because it will interfere with proper cooling of the module. The BASF Winchester disk drive is packed with the lockscrew for the linear voice-coil motor in the locked (IN) position as shown in Figure 3-2. If the lockscrew is in the unlocked (OUT) position, shipping damage has probably occurred. Record on the Shipping Data Report. Repackage for return to Zilog in the same carton.

#### CAUTION

The lockscrew should never be disengaged prior to assembly, nor before applying power to the drive.

#### 3.6 Assembly Instructions

The basic system assembly consists of stacking and attaching the Processor and Peripheral Modules on the Storage Compartment base. The separate modular units are stacked vertically to form the System 8000 (Figure 3-3). A double Storage Compartment is shown for the Model 20.

Zilog

The Model 30 consists of an additional Peripheral Module and a single Storage Compartment.

# 3.6.1 Assembly and Interconnecting

Remove front panels of the Processor and Peripheral Modules, and the Storage compartment by pulling the panels forward.

- Locate on the top front corners of the storage compartment the two aluminum guide posts. At the bottom front corners of each of the modules are two U-shaped slots. These slots will slide into the guides and align a rear key hole when stacking each module. Remove the front panels from the processor and peripheral modules.

- 2. With the Peripheral Module placed approximately one inch behind the Storage Compartment guide posts, slide the module forward until alignment guides are fully inserted in slots. Lift the module slightly from the rear making sure the key is engaged.

- 3. Loosen thumb screws and open cable ducts at rear of the Peripheral Module.

- 4. Loosen thumb screws of clamps stored at rear of module and attach at top of Storage Compartment.

- 5. Repeat the above procedures and attach the processor or next module to the top of the Peripheral Module. (Model 30 includes two Peripheral Modules.)

- 6. Locate card cage at front of processor and ensure that PC boards are firmly mounted. This may be done by lifting board levers and reinserting boards.

- 7. Ensure that all packing material has been removed from the disk and tape drive units.

- 8. Replace front covers on modules.

- 9. Connect wider ribbon cable jumper to the tape connection on the Processor and Peripheral Module. The red stripe on the edge of the cable must be oriented on the right side looking from rear.

- Connect the smaller ribbon cable and jumper between the disk connections with the red stripe to the right.

- 11. Install AC output power cable at rear of Processor Module and jumper to Periphral Module. In the case of the Model 30, install a second AC power cable between the two Peripheral Modules.

- 12. Install AC power cord at AC input of Processor Module.

- 13. Turn AC power with the power switch at the rear of the Processor Module (wait approximately 30 seconds).

- 14. Check cartridge tape slot for illumination to verify that power is applied to the disk and tape drive units.

- 15. Turn off AC power.

- 16. Connect the CRT interface cable to the CONSOLE port on back of Processor Module. If a printer is included with the system, connect the printer to the PRINTER port.

- 17. Replace cable duct and tighten thumb screws.

- 18. Unlock the voice-coil actuator on the disk drive through an access hole shown in Figure 3-5. Refer to Section 3.10 for voice-coil unlocking procedure.

## 3.6.2 Disassembly

During disassembly, and before removal of the Peripheral Module, power must be removed from the module and the voice-coil actuator lockscrew must be locked on the BASF Winchester disk drive. Refer to Section 3.10 and Figures 3-2 and 3-5.

Procedure:

- 1. Open cable ducts by removing thumb screws.

- 2. Remove interconnecting cables between the Processor and Peripheral Modules.

- 3. Remove top cover.

- 4. Remove the clamp screws attaching the Processor Module to the Peripheral Module and store.

- 5. Remove front covers from modules.

30

HRM

- 6. Remove Processor Module by lifting and sliding back from guideposts.

- Apply AC power to the Peripheral Module and wait until the disks (disk drive) are rotating at nominal speed (at least 20 seconds).

#### CAUTION

Before the Peripheral Module can be dismounted, the BASF Winchester disk drive voice-coil actuator lockscrew must be in the locked position (refer to Figure 3-2).

- 8. If the system is using a rev. 8 BASF Winchester disk drive, proceed as follows:

- a. Loosen thumb screws attaching the module to the storage compartment.

- b. Elevate the front of the module approximately six (6) inches. This will cause the headcarriage assembly to move toward track 00 (outer diameter of the disk).

- c. Gently engage the voice-coil actuator lockscrew in a clockwise direction using light pressure with a small blade screwdriver.

- d. Remove AC power from the module and remove it from the Storage Compartment.

- 9. If the system is using a rev. 15 BASF Winchester disk drive, proceed as follows:

- a. Loosen the thumb screws attaching the module to the Storage Compartment.

- b. Remove the module front panel.

- c. Switch the head retract toggle switch on the Servo PCA. This will cause the head-carriage to move toward track 00 (outer diameter at the disk).

- d. Gently engage the voice-coil actuator lockscrew in a clockwise direction using light pressure with a small blade screwdriver.

- Return the toggle switch to its normal operating position and remove AC power from the module.

- f. Remove the module from the Storage Compartment.

- 10. If another Peripheral Module is used (Model 30), follow the same removal procedure.

Side Panels on Modules

Side panels are removed by removing four screws on each panel.

Front Panels on Modules

Front panels are secured by spring fasteners, and pull away from the module.

Base Plate

HRM

The Storage Compartment is attached by four screws which secure it to the base plate.

3.7 System Location

The choice of a location for the System 8000 should conform to the guide-lines described in paragraphs 3.7.1 through 3.7.4.

3.7.1 System Enclosure Location

The System 8000 contains internal air circulating fans that exhaust through ports located on the sides of the enclosure. To allow normal system ventilation, the enclosure sides should be at least three inches from an adjacent wall or other object that could interfere with proper exhaust air circulation.

# 3.7.2 Operating Temperature

The System 8000 has been designed to operate within an ambient temperature range of 50 to 104 degrees Fahrenheit (10 to 40 degrees Celsius).

Zilog

## 3.7.3 Relative Humidity

Acceptable humidity conditions are from 0 to 80 percent noncondensing.

# 3.7.4 Access

Access to internal components is required periodically for maintenance. To allow access to the enclosure for the purpose of removal or replacement of peripherals or components, place the system in a location that will allow it to be easily rolled away from nearby walls or other objects.

#### 3.8 Electrical Power Requirements

System input power requirements are nominally 117 volts alternating current (Vac), 60 Hertz at 5 amps (sustained) maximum or 220 Vac, 50 Hertz at 2.5 amps (sustained) maximum, single phase. Ranges of 105 to 129 Vac and 198 to 242 Vac respectively, are acceptable input power voltage ranges.

#### 3.9 System Interconnection