# This document is for Xerox internal use only DRAFT - DRAFT - DRAFT - DRAFT

# NoteTaker System Manual

BY Douglas G. Fairbairn

December 1978

SSL-78-1xxx

# **ABSTRACT**

This manual describes the NoteTaker computing system. The NoteTaker is a portable computer of considerable power useful for a wide range of computational and simulation-oriented functions.

XEROX

PALO ALTO RESEARCH CENTER

3333 Coyote Hill Road / Palo Alto / California

94304

#### **PREFACE**

The NoteTaker is a very powerful portable computer intended for a wide variety of applications. Its intended users are "children of all ages": five-year-olds and high school students, as well as writers, researchers, artists, managers, and engineers. NoteTaker offers the capability of a general-purpose minicomputer, and allows it to be used without even plugging it into an AC power outlet.

This manual describes the hardware components of the system in three levels of detail. The introduction summarizes the main features of the NoteTaker hardware. Section 2 gives an overview of the architecture. Section 3 offers the detail required to program the system and to interface other devices to it.

The NoteTaker has its roots in the long-time desire of the Learning Research Group at the Xerox Palo Alto Research Center (Xerox PARC) to have a portable system on which to experiment with its ideas concerning personal computers. The architecture of the machine was defined by Douglas Fairbairn of the LSI Systems Area at PARC in conjunction with LRG. The design of the system was handled largely by the Special Programs Group in the Electronics Division of Xerox. This group is headed by Douglas Stewart. The principal electronics designers were James Leung, and Ron Freeman(SPG) and Ben Sato of the Advanced Systems Department. Dick Resnick of SPG offered crucial help by writing the system maintenance and checkout diagnostics as well as programming the keyboard controller. The mechanical design and documentation were done or coordinated by Bob Nishimura (SPG). The successful and timely completion of the project is due largely to the way this group worked together and carried out their respective tasks with skill and thoroughness. Larry Tesler, Dan Ingalls, and Ted Kaehler of LRG played key roles in helping to define the needed hardware functions and they plus Bruce Horn offered invaluable aid in the debugging of the system. The project was managed by Doug Fairbairn. Special thanks is due Bert Sutherland, manager of the Systems Science Lab (PARC) and Lynn Conway, manager of the LSI Systems Area, who so actively supported the project.

#### 1.0 Introduction

The decisions about the form and capabilities of the NoteTaker were based on a wide range of often conflicting desires. The system had to offer a computing capability in the class of the Alto computer and it had to be packaged in a form which allowed it to be carried home, on airplanes, or wherever its owner desired to take it. There was a very strong feeling that the user should not have to "pack it up" to take it somewhere. That is it should go from being used to being carried in only a few seconds, and it should not be necessary to carry it in some additional case which would have to be stored somewhere when the unit was being used.

The capabilities offered by NoteTaker had to be sufficient such that the user did not always have to plug in external interfaces to make the machine useful. We therefore included all of the basic peripherals we felt were necessary. Because no current technology offered a secondary storage medium suitable for swapping operations, it was decided to include the maximum amount of random-access memory the package would allow. The minifloppy disk was included as a non-volatile storage device because the proximity of suitably fast and reliable communications facilities could not be guaranteed. The 7" CRT was chosen because it offers the largest number of viewable dots of any display device which met the size and power limitations of the package.

The current system is laid out on 7 small printed circuit boards. There is space for one additional board. This board will be designed in the near future and will likely include an Ethernet interface and possibly a modem. Communications capabilities are an important aspect of any personal computing system and we intend to look at a wide variety of them with the NoteTaker.

The hardware components which make up a NoteTaker system are as follows:

- 256K bytes of main memory with single-bit error correction and double-bit detection.

- General purpose processor consisting of an Intel 8086 CPU (a 16 bit microprocessor) and 8K bytes of local memory with byte parity.

- An I/O processor (also an Intel 8086) for controlling a variety of I/O devices described below. This processor has the same access to the central memory as the above processor but has only 4K bytes of local EPROM. This processor is

available for general purpose computing tasks when it is not involved in I/O operations.

- · An EIA interface for general purpose communications needs.

- · An 10-bit analog-to-digital converter with an 8 input analog multiplexer and sample/hold on the input.

- · A two channel, 12-bit digital-to-analog converter with preamp output.

- A double-density, double-sided, minifloppy disk capable of storing about 340K bytes of data. [The current model is single-sided and will only store 170K bytes.]

- A 7" diagonal CRT displaying 640 dots horizontally and 480 dots in the vertical direction. This provides a resciution of 118 dots/inch. The I/O processor handles the setup of the display controller but a display refresh controller with the display logic handles the transfer of data from the memory to the display.

- · A standard keyboard, identical to the Alto I keyboard layout. The keyboard is interfaced to the I/O processor over a serial data link. The keyboard has within it a single-chip microprocessor for controlling power on the keyboard, keeping track of the mouse and serializing the data which is transferred to the I/O processor.

- · A mouse. The mouse is actually interfaced to the single-chip microprocessor in the keyboard and its state is transmitted along with the keyboard state.

- · A transparent overlay tablet for pointing on the screen

- A small 2" speaker for audio output.

- A power system capable of supplying 100 watts. The peak demand of the system is about 80 watts. The power supply can get its primary power from the Ac line (120 or 240 VAC) or from a battery pack (28.8 VDC)which is included within the NoteTaker. It is expected that the system can be operated on the batteries for about 2 hours at a time. A recharging system is built into the power supply as well.

- There are several I/O connections on the rear panel which the user may find useful:

- An external 8086 bus interface which allows other devices to be connected to the NoteTaker.

- A connector for interfacing to two more external floppy disks.

- A connector to plug in an external CRT. This CRT may be driven at a higher line rate than the 525 rate used by the internal monitor. The display controller is programmable and could be set to run at about 875 lines if required.

- Three of the inputs to the analog multiplexer (multiplexed into the analog-to-digital converter) are available on the rear panel.

- The two digital-to-analog converter outputs (preamp levels) are available on the front panel in a standard phone jack.

- The architecture of the system is such that up to 16 processors can be operated in parallel. Although these extra processors may not fit within the package, the system will offer a useful test-bed for experimenting with multi-processor architectures.

- The package is about 21" wide, 14" deep, and 7" high. The total weight without batteries is about 40 lbs. With batteries the system weighs about 48 lbs.

### 2.0 System Architecture

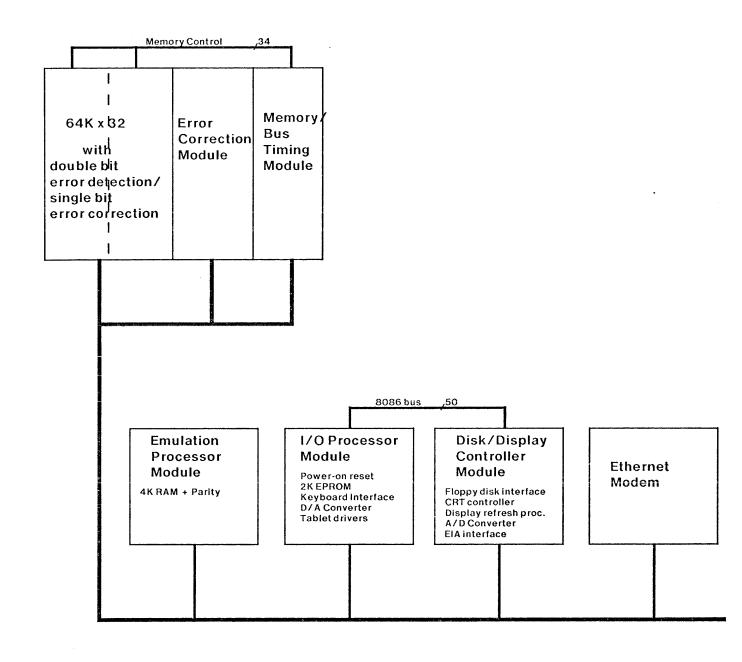

A block diagram of the NoteTaker system is shown in Fig. 1. The computer offers a multiprocessor architecture based around a single system bus. Each of the processors and the main memory are connected to the system bus. The processors do not communicate directly with each other but rather do so by passing messages in main memory. The system bus is synchronous with the main memory. Each of the processors run asynchronously from each other and from the system bus. The basic NoteTaker configuration allows for 16 processors. The processors do not have to be of the same type. In the current configuration, there are two Intel 8086 processors for general purpose computation and one display refresh processor.

### 2.1 System bus

The system bus links the processors with memory and includes 16 information lines and 21 control lines. The information lines carry both data and addresses. Control functions on the bus include a bus clock for synchronizing transfers, a parallel hardware priority system for controlling access, and capability for any processor to interrupt, reset, or boot any other processor.

These last three functions are implemented by writing the target processor's address and the desired function code into a reserved memory location. The memory system then takes care of generating the appropriate reset, boot, or interrupt signals.

Bus arbitration is handled in a distributed fashion. When a processor wants control of the bus it sets an internal access request signal which is synchronized by the next *BusSync* signal to produce a *BusReqn* signal. There are 8 parallel bus request lines on the backplane, each of which is assigned to a processor. Each of the processors monitors the request lines of higher priority than themselves. A processor assumes control of the bus when it is requesting control and no other processors of a higher priority are doing so also.

There is a bus lock capability implemented on the system bus to allow any of the processors to prohibit access of the shared memory during a critical section. A processor can set an internal bit which indicates that the bus is to be locked the next time that processor gets control. When a processor gains bus control and asserts <code>BusLock</code>, all other processors capable of doing <code>write operations</code> to the memory are forced to disable their bus request signals and leave them disabled until the locking processor resets the <code>BusLock</code> signal. Note that a processor such as the display refresh processor is allowed continued access to the memory because it can in no way modify the memory's contents.

Table I summarizes the signals on the bus. There are a total of 52 devoted to system wide functions. Of these, 16 are information, 21 are control, and 13 are power. The bus is implemented on a backplane of 100 pin connectors, leaving 50 pins available for I/O device interfacing.

# 2.2 Main memory

The main memory is organized as 64K 32-bit words with an additional 7 bits with each word for double-bit error detection and single-bit correction. Although all data is accessed 32 bits at a time, the memory can be byte addressed. The information path on the system bus

is 16 bits wide and transfers bytes, words or double words in a synchronous fashion between the processors and the memory. Both addresses and data are transferred on the information path.

A normal read operation takes 560 ns. plus about 80 ns of bus arbitration overhead. This assumes no conflicting requests from higher priority devices. A write operation takes 880 ns for the memory to complete but the processor is allowed to proceed after 320 ns of the cycle. In block transfer mode, the memory can transfer data at the rate of 1 doubleword every 320ns. The peak bandwidth available on the bus is thus 100 Mbs. The hardware will allow any device to make up to 128 consecutive double-word transfers although because of refresh requirements on the dynamic memories, the real limitation is about 46 double-words.

The main memory is constructed of special 32Kx1 hybrid dynamic RAMs. These chips are two standard 16K RAMs on a single package. Memory capacity will grow to 512K bytes when 64Kx1 chips become available and could grow to 1 M byte if the 64K chips can be placed in a hybrid package. The address space of the Intel 8086 processors is 20 bits or 1M byte.

#### 2.3 Emulation processor

The emulation processor subsystem consists of an 8086 processor with 8K bytes of local memory. When running Smalltalk, this local memory holds the machine code interpreter for the Smalltalk language. The Smalltalk byte codes and data are held in the main memory.

This subsystem also has the ability to trap attempted accesses to memory locations  $\mathsf{FFFC0}_\mathsf{H}$  to  $\mathsf{FFFDF}_\mathsf{H}$ . An access to any of these locations will cause an interrupt and vector the processor to the appropriate routine. This interrupt can be disabled in software as can the others described below.

The other interrupts available on the EP are local parity error, main memory parity error, system interrupt, vertical sync (60 Hz.), and the above mentioned trap. The priority of these interrupts is as listed here.

#### 2.4 Input/Output processor

The fourth important building block of the NoteTaker is the I/O subsystem. Here we make use of many standard LSI components. The I/O subsystem is controlled by an Intel 8086 processor. This I/O processor handles much of the overhead associated with setting up and completing I/O transfers. The communication between the I/O section and the emulation processor is handled through main memory and the system interrupts.

The I/O processor communicates with the controllers for the display, keyboard, and floppy disk. It acts as a controller for the tablet, a 10-bit A/D converter with 8 analog inputs, a dual output 12-bit D/A converter, and an EIA line interface.

The display refresh processor is a semi-independent processor within the I/O system. It gets its initialization from the I/O processor but handles transfer of data between the memory and display independently. There is no hardware cursor in the display controller and the 8086 must reset the bit map starting address at the beginning of each frame. The display bit map must be contiguous in main memory and the two fields of the frame are *not* interlaced in memory as they are on the Alto.

The keyboard has the same layout as the Alto I keyboard. Within the keyboard is a single-chip microprocessor (Intel 8748) which receives requests for data from the I/O processor and sends back the state of the keys and the mouse. All communications take place over a serial path between the keyboard and the I/O processor. The keyboard processor is continuously monitoring the state of the mouse direction signals and keeping track of the change in mouse coordinates from the last time the I/O processor polled the keyboard. The power to the keyboard keys is normally off. When the I/O processor sends a request to the keyboard, the keyboard processor turns on the power to the keys, samples the state of each of the keys, and transmits one bit to the I/O processor for each key in the array. Also reported at this time is the state of the mouse switches and the relative coordinates since the last poll.

The minifloppy disk controller is a Western Digital 1791 capable of handling double density floppies or minifloppies. There is additional logic which allows up to 3 drives to be controlled. The extra drives can be attached to the connector on the rear panel. Each drive may be single or double sided.

The tablet is a transparent device which fits over the front of the NoteTaker screen. It allows the CRT to be touch sensitive for use in a variety of user interface experiments. The I/O processor can sample the coordinates where the panel is touched by reading two of the inputs of the A/D converter.

The A/D converter can sample the state of the tablet as mentioned above. It can also monitor the state of the battery voltage, and the +5 volt and +12 volt supplies for the NoteTaker. The last three outputs are brought to a rear connector for the user. The converter can sample at a rate up to 12 Khz and can be programmed to sample at slower rates.

The D/A converter is a single 12-bit converter with two sample and hold circuits on the output. The input to the converter is fed by a 16 word FIFO which is loaded by the processor. The rate at which the samples are clocked out of the FIFO and into the converter is set by software and can be a maximum of 16 Khz..

The EIA interface implements standard RS-232 type protocols operating at a speed of 300 baud.

[Section 3 is in preparation]

Figure 1 - NoteTaker System Block Diagram

# Table 1 - NoteTaker System Bus Signals

| Signal                                                                                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Originates in processor (P) or Memory(M)                                |

|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| Information Bus                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                         |

| MData00(MSB) - MDa                                                                                                         | ta15(LSB) Data and Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                     | P/M                                                                     |

| Control Bus                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                         |

| PageMode' GoMem' BusLock' BusClkDly' ProcBoot' ProcInt' BusReq0-7 MemComp ParErr DataReady ProcReset' CorrOn' BusClk Reset | Current processor wants to access memory is ready - processor may processor access of any other process Delayed version of basic bus clock Boot the addressed processor Interrupt the addressed processor Bus request lines for each processor Indicates memory is finished with cur The main memory has detected as each the data requested from memory is a Stop the addressed processor Enable error correction circuitry Basic System Clock for synchronizing Power on reset | occeed with request Moor P M M M rrent request M rror M available M M P |

| Power                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                         |

| + 5 volts<br>+ 12 volts<br>-20 volts<br>+ 28.8 volts<br>+ 15 volts                                                         | 8.5 amps 4.0 Amps 400 ma. Battery Output: 4 amp-hours < 50 ma derived from + 30 volts < 50 ma derived from -20 volts                                                                                                                                                                                                                                                                                                                                                             |                                                                         |

Raw output of power supply inverter - unregulated Charging voltage for batteries

+30 volts +42 volts