2985 KIFER ROAD = SANTA CLARA, CA 95051 = (408) 988-2550 = TWX 910-338-0130

XDF-50

OPERATION AND MAINTENANCE

MANUAL -

#### **XEBEC SPECIFICATION NO. 200105**

#### **XEBEC MOVING HEAD DISK**

#### FORMATTER

### MODEL NO. XDF-50

#### **OPERATION & MAINTENANCE MANUAL**

The information contained herein is Xebec Proprietary and is not to be reproduced or disseminated in any form without prior "approval of Xebec Systems, Inc. Specifications and configurations are current as of date shown above, and are subject to change without prior notification.

Copyright (C) 1975 XEBEC SYSTEMS INCORPORATED

Revision "B" June 9, 1976

#### TABLE OF CONTENTS

#### 1.0 INTRODUCTION

- 1.1 General

- 1.2 Specifications

### 2.0 SYSTEM DESCRIPTION

- 2.1 Introduction

- 2.2 Functional Description

- 2.3 Mechanical Packaging

- 2.4 Power Supply

- 2.5 Sector Format

- 2.6 For matter Commands

- 2.7 Write Protection

- 2.8 Controls and Displays

- 2.9 Environment

### 3.0 FUNCTIONAL OPERATION

- 3.1 Introduction

- · 3.2 Disc Command

- 3.3 Formatter Commands

- 3.3.1 Command Register

- 3.3.2 Word Count Register

- 3.3.3 Status Register

### TABLE OF CONTENTS (Continued)

### 4.0 DETAILED CIRCUIT DESCRIPTION

- 4.1 General

- 4.2 Registers

- 4.2.1 Cylinder Address Register

- 4.2.2 Word Count Register

- 4.2.3 Command Register

- 4.2.4 Status Register

- 4.2.5 Shift Register

- 4.3 Control Logic

- 4.3.1 State Counter

- 4.3.2 Sector Length Counter

- 4.3.3 Sector Counter

- 4.3.4 Bits Word Counter

- 4.3.5 Comparator Circuits

- 4.3.6 Timing Circuits

- 4.3.7 Double Frequency Write Data Generation

- 4.3.8 Read Gate

- 4.3.9 Read Clock

- 4.3.10 Write Enable

- 4.3.11 Data Flag

Rev. A, 2-6-73

### TABLE OF CONTENTS (Continued)

#### 4.4 Status Bits

- 4.4.1 Rate Error

- 4.4.2 Preamble Compare Error

- 4.4.3 Write Protect Error

- 4.4.4 Bad Sector Flag

- 4.4.5 Format Error

- 4.4.6 Time Out Error

- 4.4.7 Cylinder Address Error

- 4.4.8 Not Operational

- 4.5 Busy

- 4.6 Done

- 4.7 Format & Disk Options

- 4.7.1 Format Options

- 4.7.2 Disk Options

- 4.8 CRC Register

#### 5.0 INSTALLATION/SHIPPING

- 5.1 Unpacking

- 5.2 Inspection

- 5.3 230 Volt Operation

- 5.4 Preliminary Test

- 5.4.1 DC Voltage Adjustment

- 5.4.2 Current Limiting Adjustment

### TABLE OF CONTENTS (Continued)

- 5.5 Rack Mounting

- 5.6 Interconnecting Cabling

- 5.6.1 XEBEC Supplied Coupler/Drive

- 5.6.2 Customer Supplied Coupler/Drive

- 5.7 Packing Instructions

#### 6.0 INTERFACE REQUIREMENTS

- 6.1 Introduction

- 6.2 Interface Signals

- 6.2.1 Register Selection

- 6.2.2 Coupler Output Bus

- 6.2.3 Coupler Input Bus

- 6.2.4 DMA Data Control

- 6.2.4.1 Data Flag

- 6.2.4.2 Data In/Out

- 6.2.5 Basic Formatter Status

- 6.2.5.1 Busy

- 6.2.5.2 Done

- 6.2.6 Master Clear

- 6.3 Input/Output Connectors

- 6.4 Cable Design

#### ILLUSTRATIONS

- 1.1 Photo XDF-50

- 2.1 Sector Format

- 3.1 Command Sequence Flow Chart

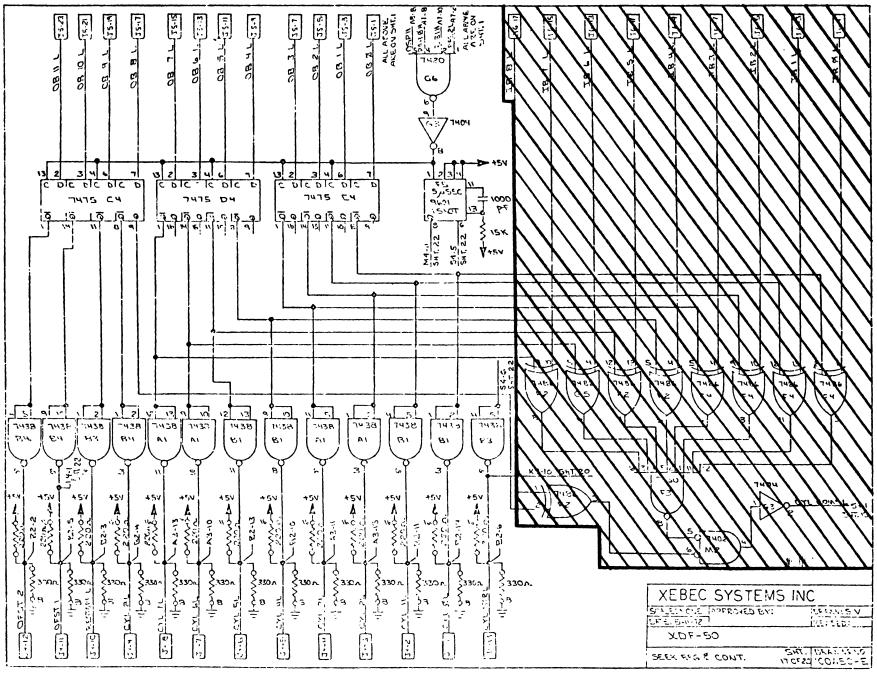

- 4.1 Cylinder Address Register (Logic)

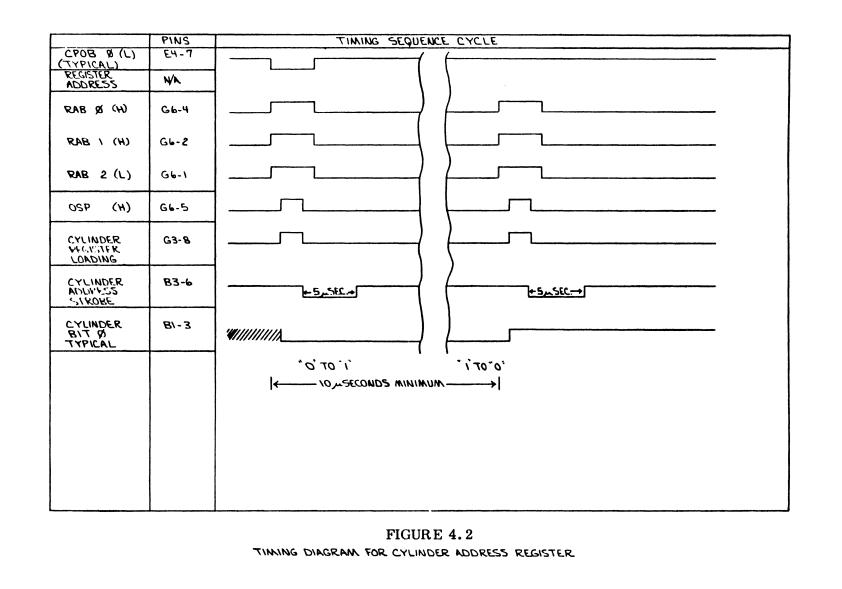

- 4.2 Cylinder Address Register (Timing)

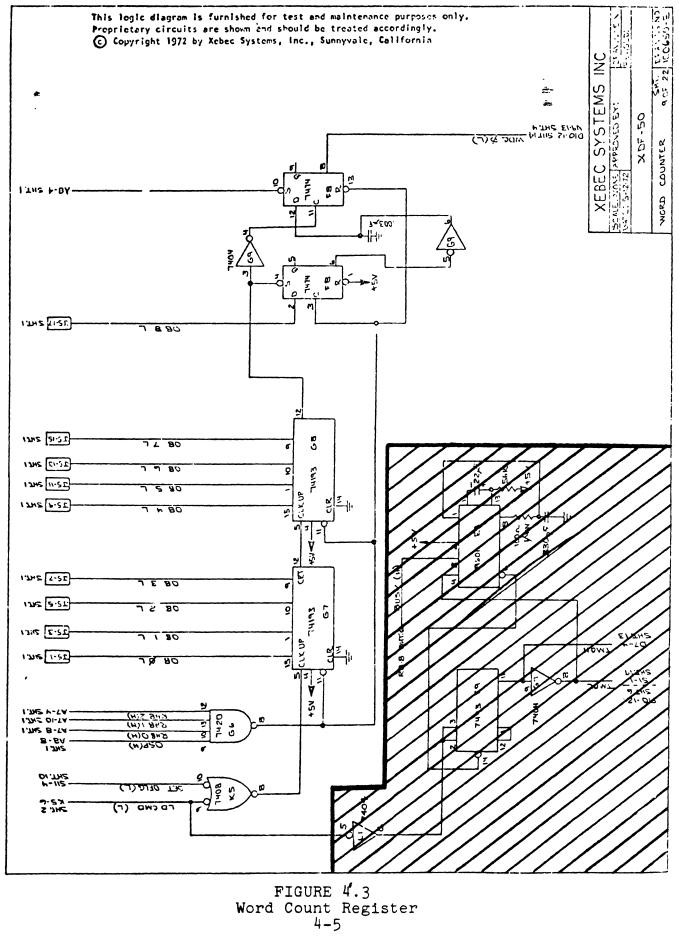

- 4.3 Word Count Register (Logic)

- 4.4 Word Count Register (Timing)

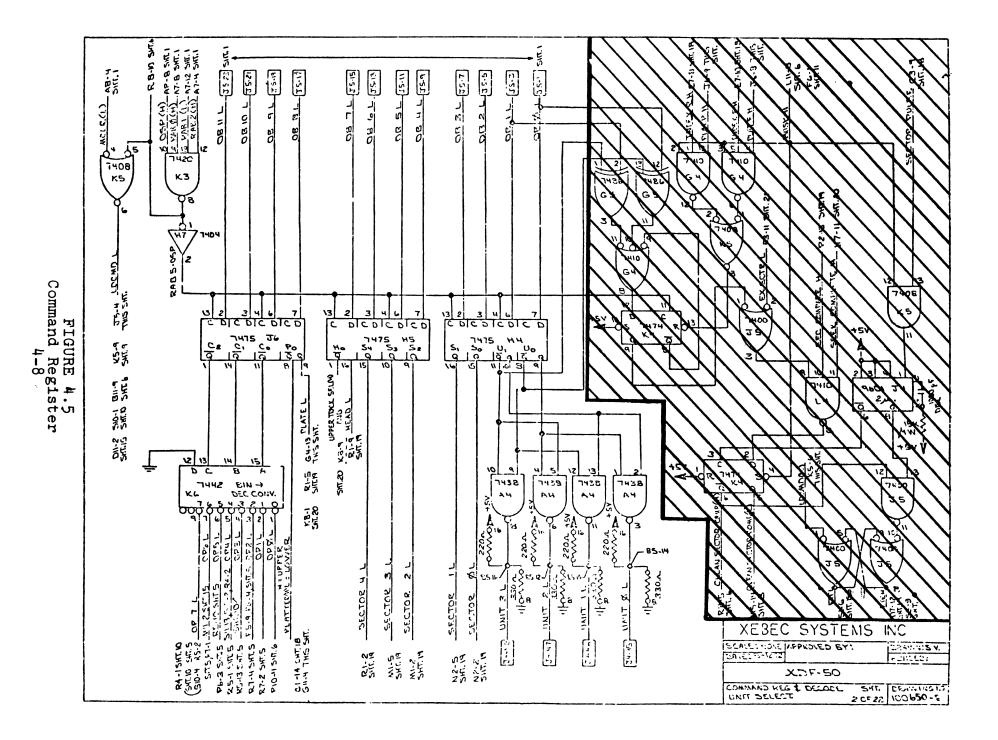

- 4.5 Command Register (Logic)

- 4.6 Command Register (Timing)

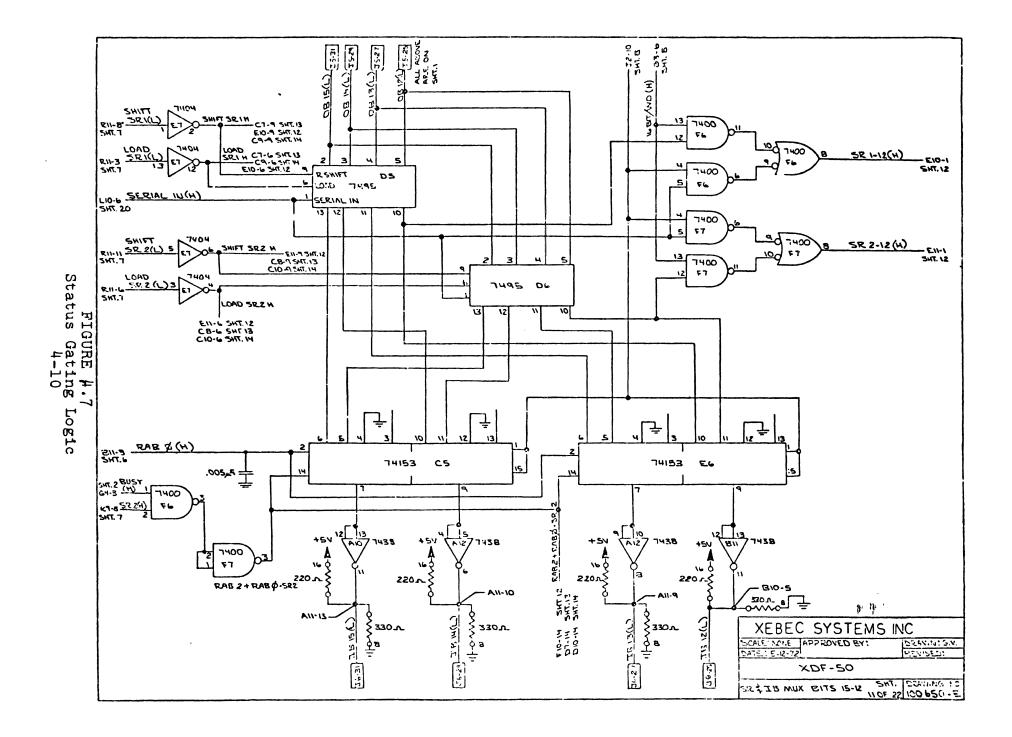

- 4.7 Status Gating (Logic)

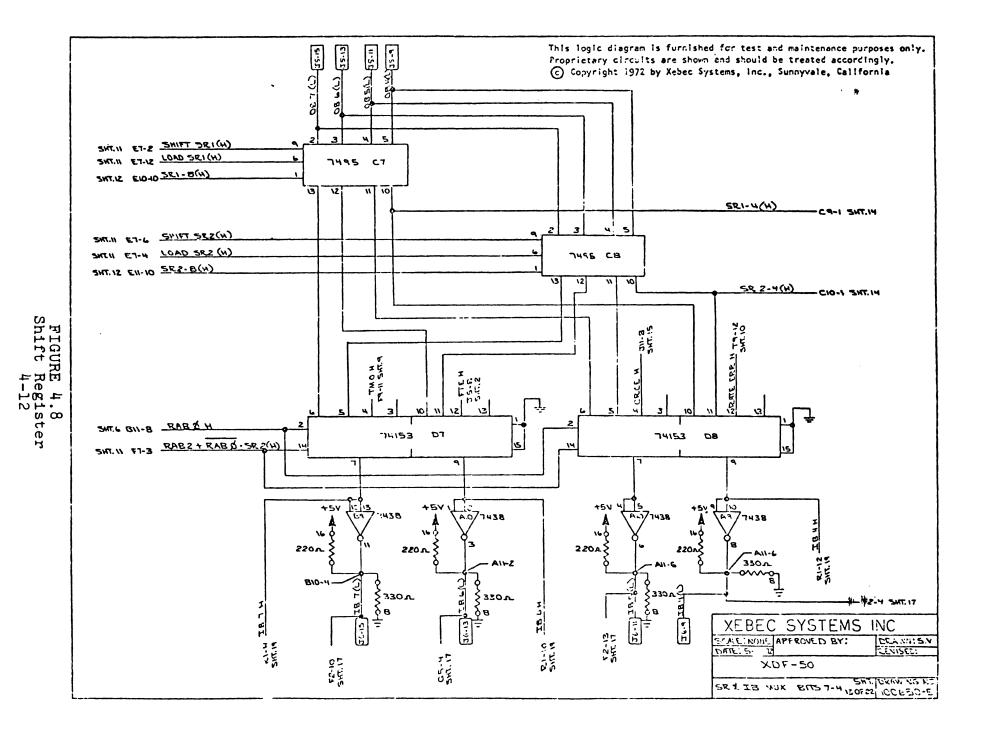

- 4.8 Shift Register (Logic)

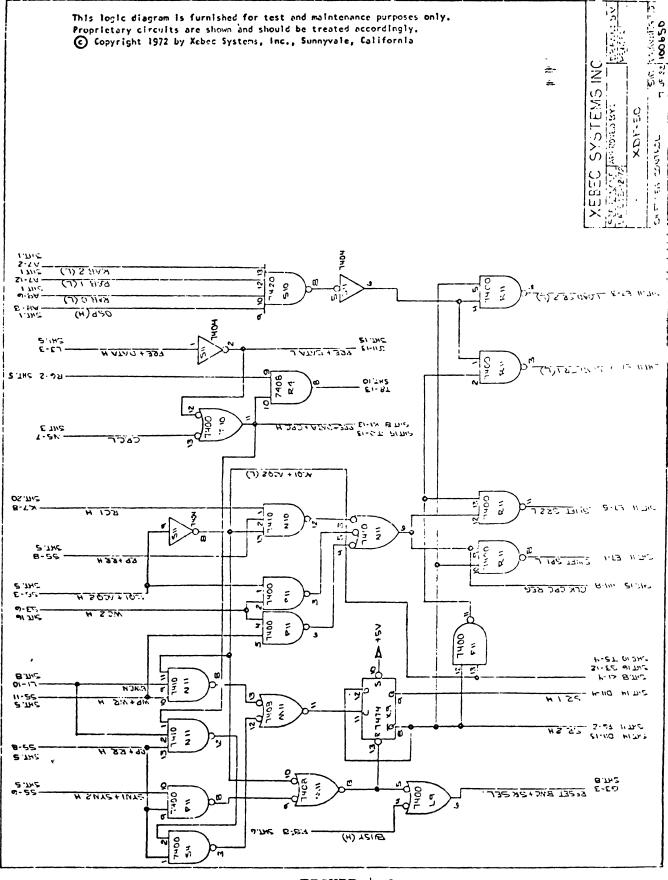

- 4.9 Steering Flip Flop (Logic)

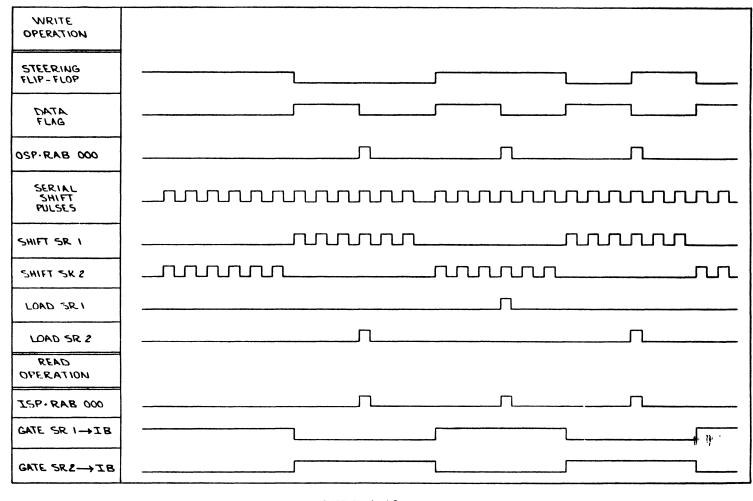

- 4.10 Shift Register (Timing)

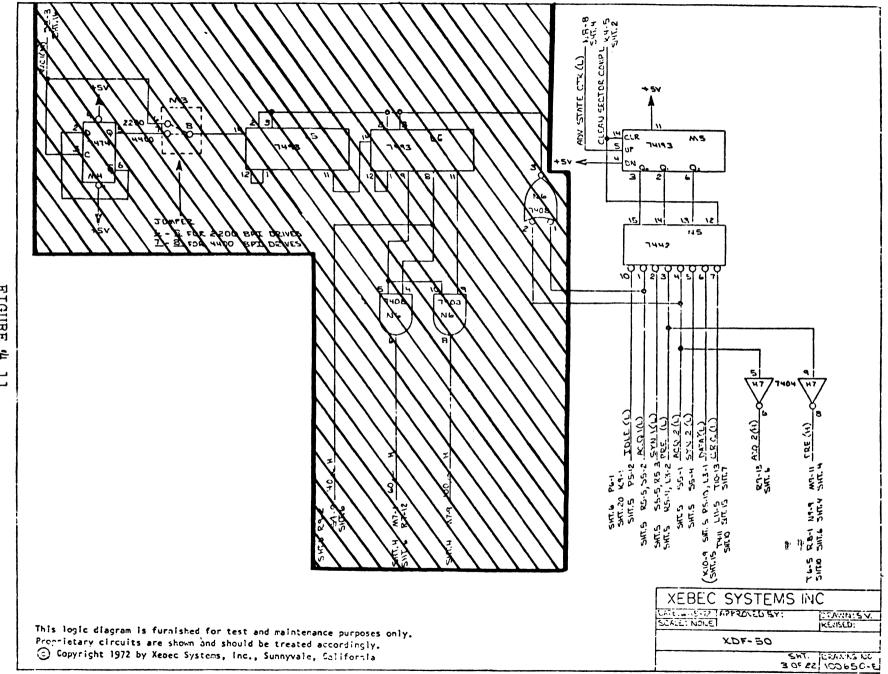

- 4.11 State Counter (Logic)

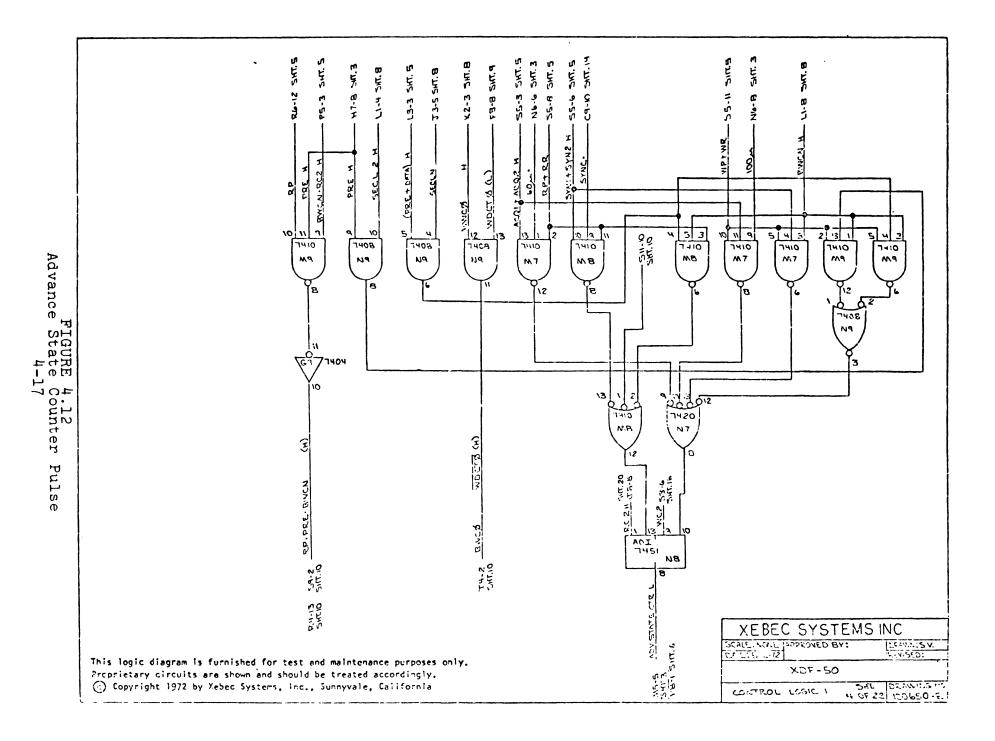

- 4.12 State Counter Control (Logic)

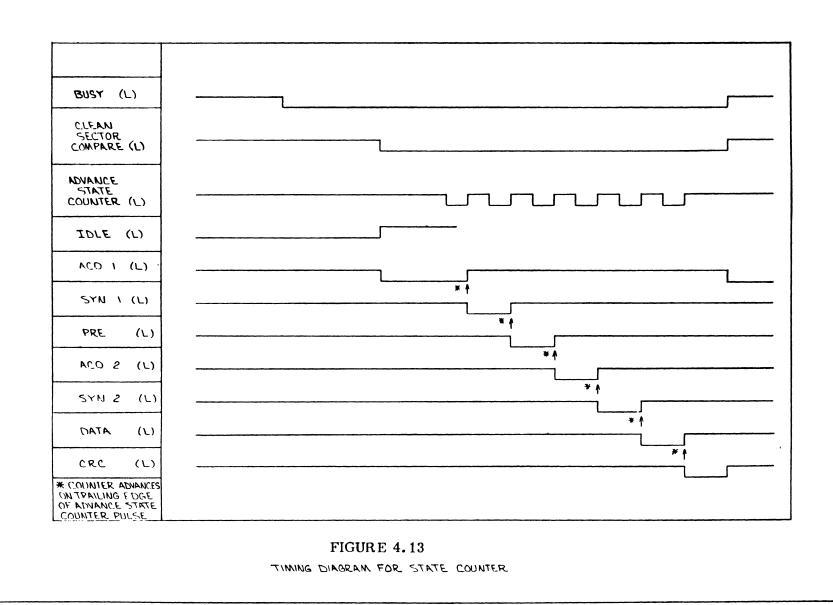

- 4.13 State Counter (Tin ing)

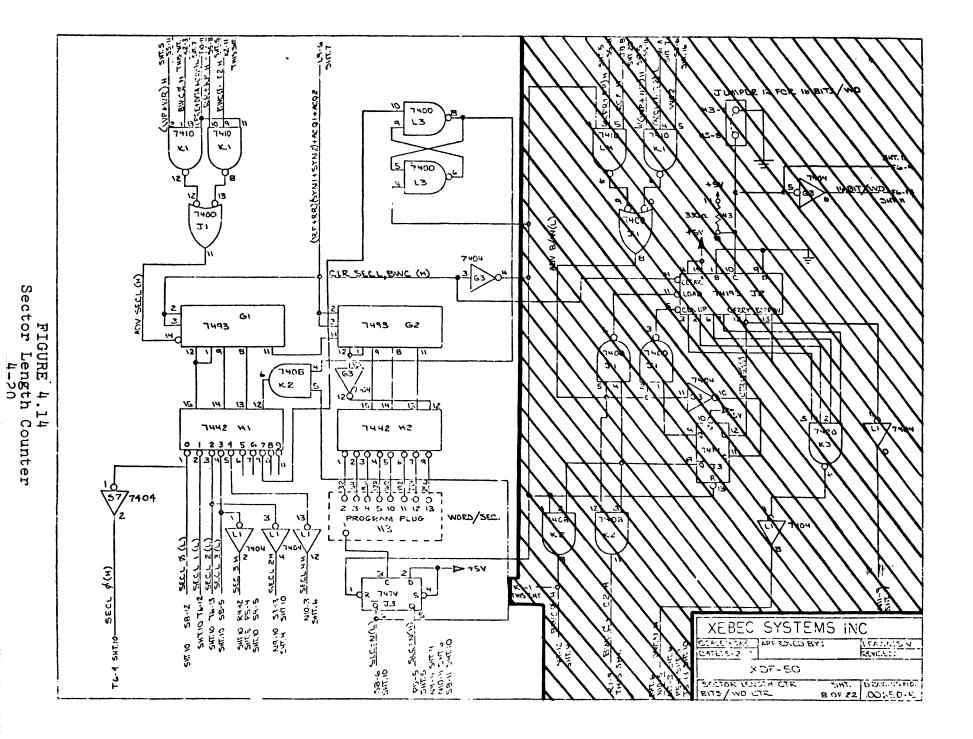

- 4.14 Sector Length Counter (Logic)

- 4.15 Sector Length Counter (Timing)

- 4.16 Sector Counter (Logic)

- 4.17 Sector Counter (Timing)

### ILLUSTRATIONS (Continued)

- 4.18 Bits/Word Counter (Logic)

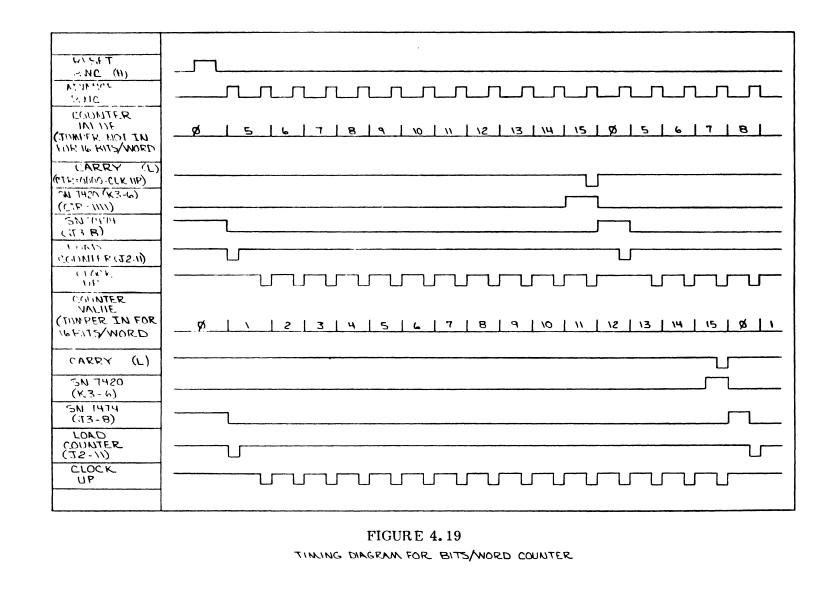

- 4.19 Bits/Word Counter (Timing)

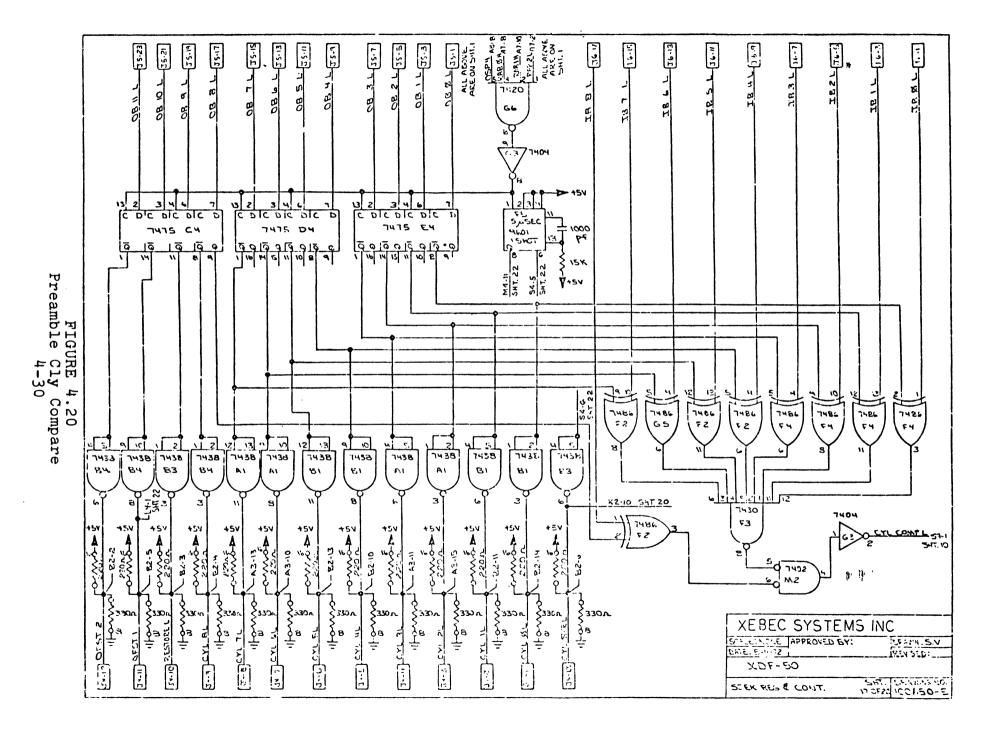

- 4.20 Cylinder Compare (Logic)

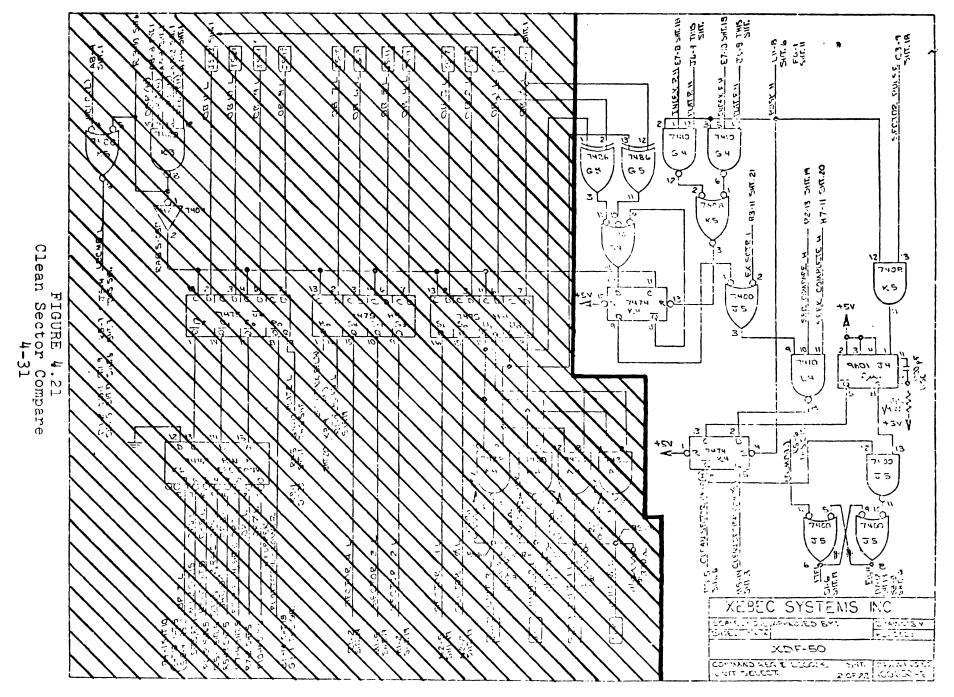

- 4.21 Sector Compare Flip Flop (Logic)

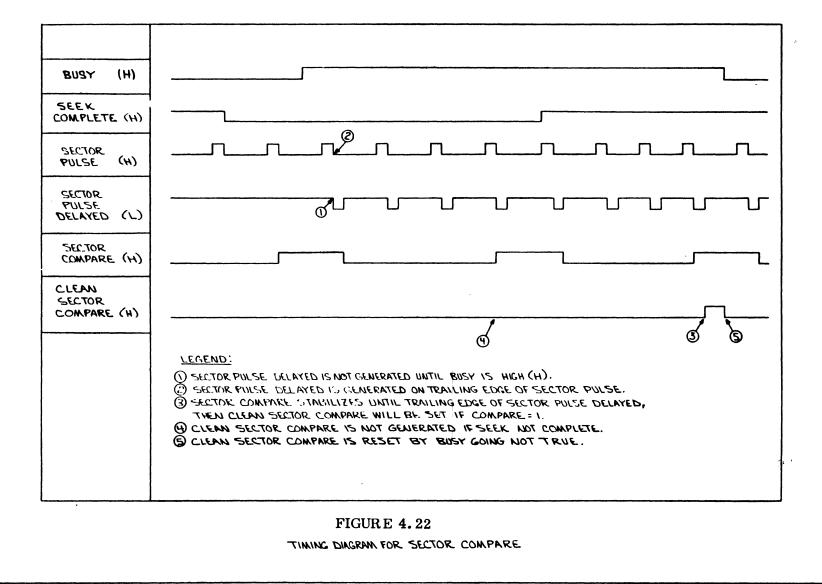

- 4.22 Sector Compare (Timing)

- 4.23 Sector Comparator (Logic)

- 4.24 Sector Preamble Compare (Logic)

- 4.25 Timing Counter (Logic)

- 4.26 Write Oscillator & Double Frequency Write Data Generation (Logic)

- 4.27 Write Oscillator & Double Frequency

- Write Data Generation (Timing)

- 4.28 Read Gate (Logic)

- 4.29 Read Clock (Logic)

- 4.30 Write Enable (Logic)

- 4.31 Data Flag (Logic)

- 4.32 Status Flip Flops (Logic)

- 4.33 Status Flip Flops (Logic)

- 4.34 Busy & Done (Logic)

- 4.35 CRC Register (Logic)

### ILLUSTRATIONS (Continued)

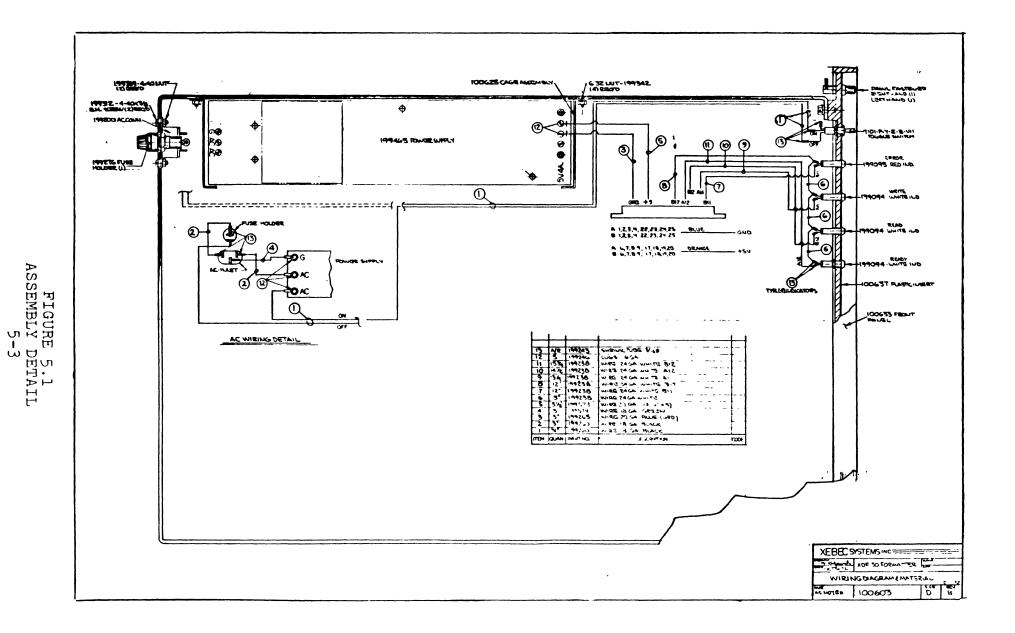

- 5.1 XDF-50 Assembly

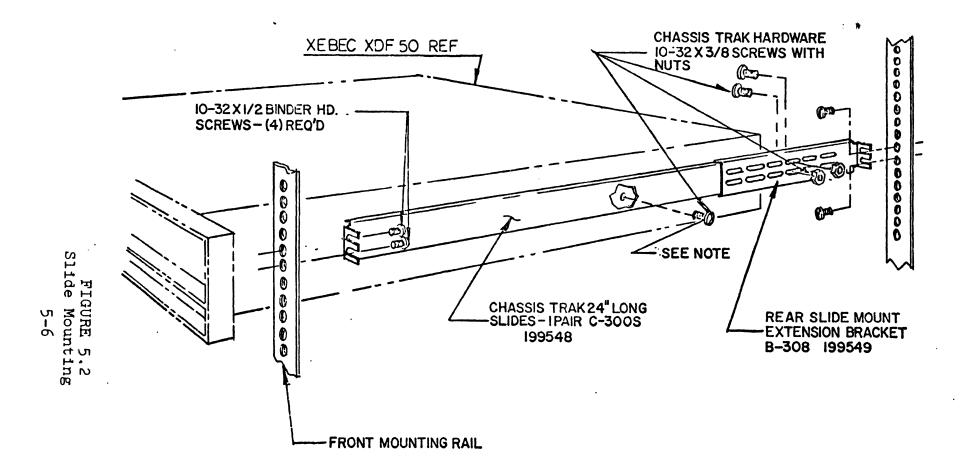

- 5.2 Slide Mounting Assembly

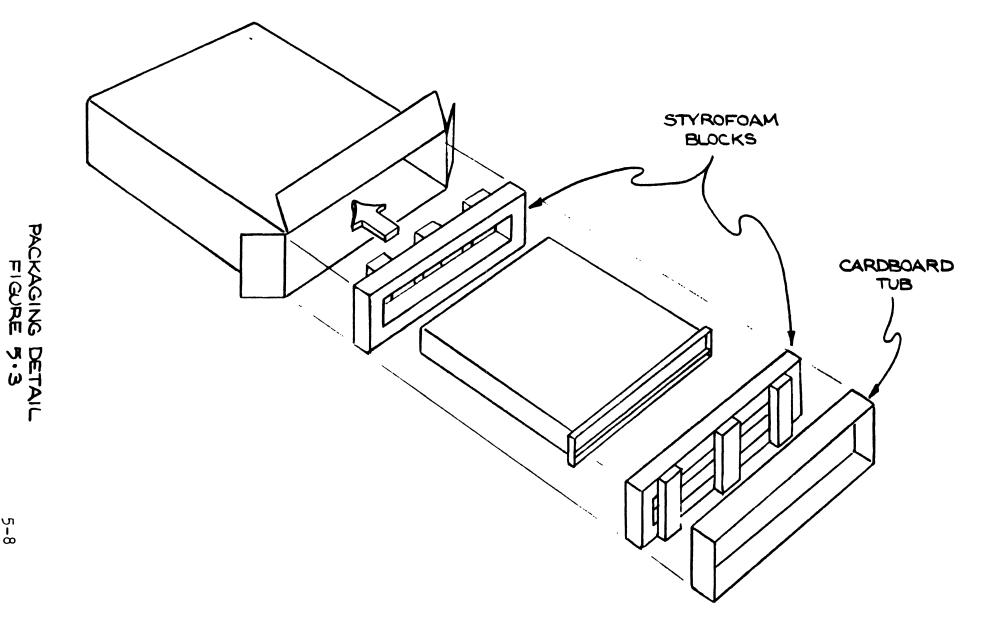

- 5.3 Packing for Shipment

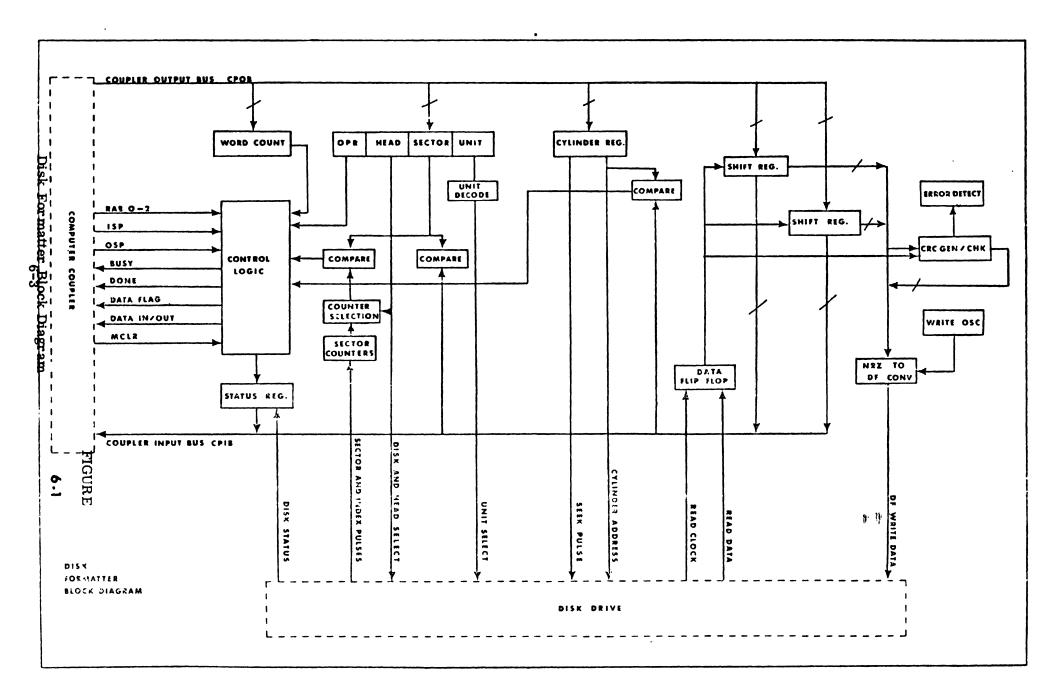

- 6.1 XDF-50 Block Diagram

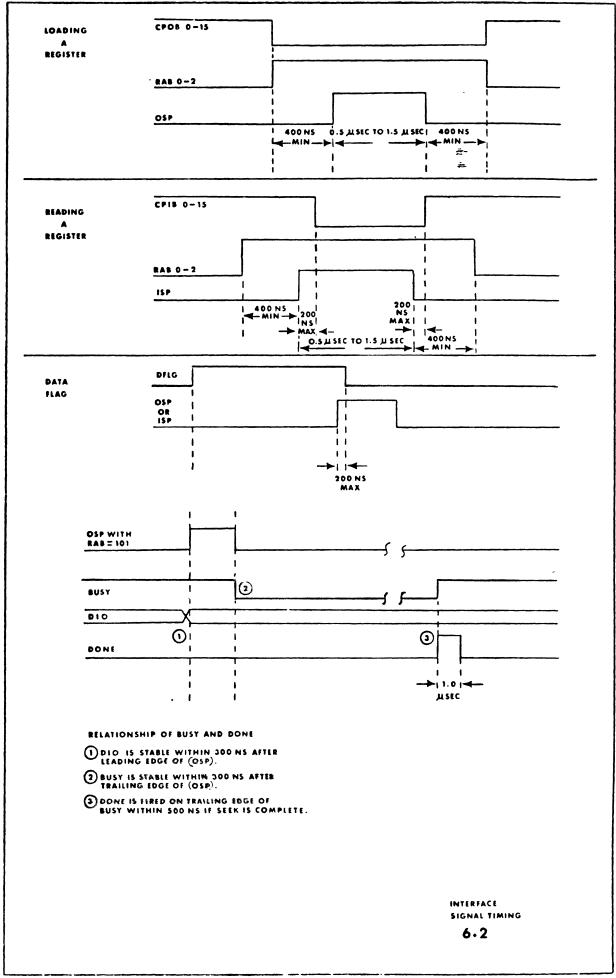

- 6.2 Interface Signal Timing

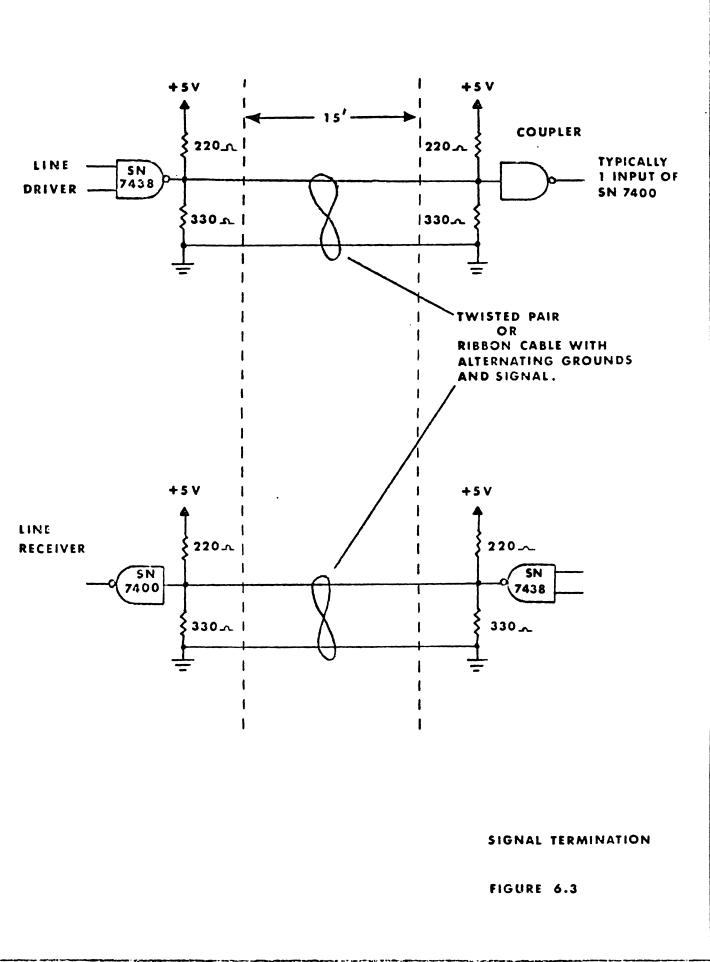

- 6.3 Signal Termination

### SECTION I INTRODUCTION

### 1.1 GENERAL

The Xebec Moving Head Disk Formatter (XDF-50) see Figure 1, described in this manual has been designed to be used with a wide variety of moving head disk drives manufactured by Microdata, CDC, Pertec and others.

The data conversion and control logic functions of this disk formatter significantly simplifies the logic design that is normally required to interface these Disk Drives to any modern mini-computer.

The XDF-50 design extensively utilizes medium scale integration (MSI) integrated circuits and incorporates conservative printed circuit design practices to produce a highly reliable, low cost piece of peripheral equipment.

### 1.2 SPECIFICATIONS

The specifications for the disk formatter are shown in Table 1.1.

XDF-50 XEBEC DISK FORMATTER FIGURE 1.1

# TABLE 1.1 DISK FORMATTER SPECIFICATION

| Para | ameter                                        | Unit                                                                                              | Selected By                                                   |

|------|-----------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 1.   | Word Length                                   | 12 Bit Word<br>16 Bit Word                                                                        | 14 Pin DIP<br>Program Plug                                    |

| 2.   | Sector Size                                   | 32 Words<br>64 Words<br>96 Words<br>128 Words<br>160 Words<br>192 Words<br>224 Words<br>256 Words | 14 Pin DIP<br>Program Plug                                    |

| 3.   | Sectors/Revolution                            | 12 Sectors<br>16 Sectors<br>24 Sectors<br>32 Sectors                                              | Automatically uses<br>number of sector slots<br>on disk pack. |

| 4.   | Size of Cylinder Address Register             | 9 Bits                                                                                            |                                                               |

| 5.   | Size of Command Register                      | 12 Bits                                                                                           |                                                               |

| 6.   | Size of Status Register                       | 12 Bits                                                                                           |                                                               |

| 7.   | Size of Word Count Register                   | 9 Bits                                                                                            |                                                               |

| 8.   | Number of Disk Drives which may be connected. | 4 Maximum                                                                                         |                                                               |

| 9.   | Spindle Speed                                 | 1500 RPM<br>or<br>2400 RPM                                                                        |                                                               |

| 10.  | Packing Density                               | 2200 BPI                                                                                          |                                                               |

| 11.  | Words/Sector                                  | 12 16 24 32                                                                                       | Number of Sectors                                             |

|      |                                               | - 256 160 96                                                                                      | 12 Bit Word                                                   |

|      |                                               | <b>256</b> 192 128 64                                                                             | 16 Bit Word                                                   |

# TABLE 1.1 DISK FORMATTER SPECIFICATION (Continued)

### Parameter

12. Words/Disk Drive (Single Platter) (Based on 207 Cylinders)

| 12        | 16        | 24          | 32        | # of Sectors |

|-----------|-----------|-------------|-----------|--------------|

|           | 1,695,744 | 1, 589, 760 | 1,271,808 | 12 Bit Word  |

| 1,271,808 | 1,271,808 | 1,271,808   | 1,271,808 | 16 Bit Word  |

13. Words/Disk Drive (Dual Platter) (Based on 203 Cylinders)

| 12          | 16          | 24          | 32          | # of Sectors |

|-------------|-------------|-------------|-------------|--------------|

| _           | 3, 325, 952 | 3, 118, 080 | 2, 494, 464 | 12 Bit Word  |

| 2, 494, 464 | 2, 494, 464 | 2, 494, 464 | 2, 494, 464 | 16 Bit Word  |

14. Bit Transfer Rate

1588.5 KHz at 1500 RPM\* 2500.0 KHz at 2400 RPM

\* A crystal change is required to change frequencies.

### SECTION 2 SYSTEM DESCRIPTION

### 2.1 INTRODUCTION

When used in conjunction with various moving head drives, the XDF-50 provides all control and timing necessary to form a data storage/retrieval system suitable for use in small-to-medium scale data processing applications. Compatibility and interchangeability of disk packs is provided between disk drives and formatters.

#### 2.2 FUNCTIONAL DESCRIPTION

The XDF-50 is designed to operate over a wide range of parameters. These variable parameters are:

- 1) 12 Bit or 16 Bit Word Lengths.

- 2) Number of Sectors per Revolution.

- 3) Number of Words per Sector.

- 4) 1500 RPM or 2400 RPM Disk Speed.

- 5) Manufacturer of Disk Drive.

- 6) Number of Disk Drives.

A maximum of four disk drives can be attached to each formatter. They must be of the same type with respect to the first five variable parameters, but may be any combination of single or dual platters.

### 2.3 MECHANICAL PACKAGING

#### 2.3.1 Disk Formatter

The disk formatter is rack mountable in a standard EIA relay rack. Front access is accomplished by use of slides. Physical dimensions are as follows:

| a) | Overall Depth: | 29.0 Inches<br>(includes cable bends and air flow) |

|----|----------------|----------------------------------------------------|

| b) | Unit Height:   | 3.5 Inches maximum                                 |

| c) | Unit Width:    | 19.0 Inches maximum                                |

| d) | Weight:              | 30.0 Pounds maximum                                           |

|----|----------------------|---------------------------------------------------------------|

| e) | Mounting:            | 19 Inch EIA Rack Mounting Utilizing both Front and Back Rails |

| f) | Rack Space Required: | 3.5 Inches maximum                                            |

#### 2.4 POWER SUPPLY

The AC power requirements for the formatter are as follows:

$115 \pm 10\%$  VAC, Single Phase 47 - 63 Hz, Fused at 1.5 Amperes 230 VAC Optional

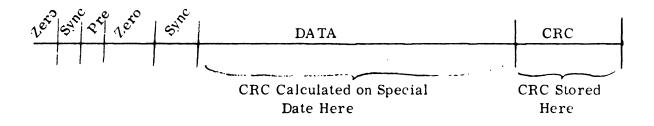

### 2.5 SECTOR FORMAT

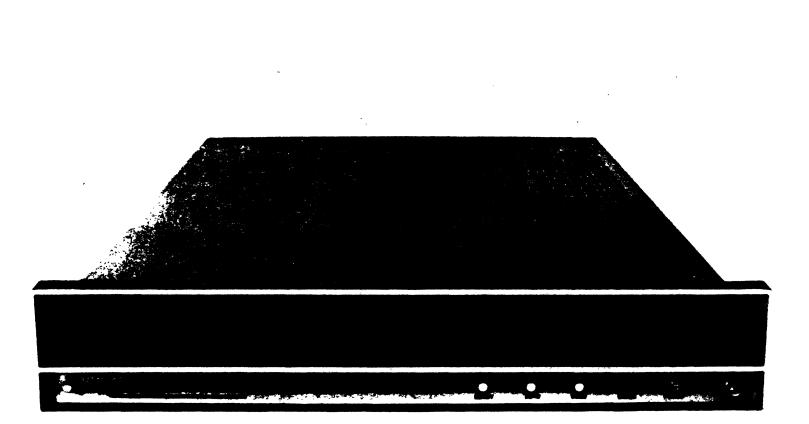

Each sector is divided as shown in Figure 2.1. As can be seen by this figure these divisions are as follows:

| a) | Zeros Field 1 - used for bit synchronization                    |

|----|-----------------------------------------------------------------|

| b) | Sync Word 1 - used for word synchronization                     |

| c) | Preamble - identifies cylinder /sector/write protect/bad sector |

| d) | Write Amplifier Turn-On Gap                                     |

| e) | Zeros Field 2 - used for bit synchronization                    |

| f) | Sync Word 2 - used for word synchronization                     |

| g) | Data Field                                                      |

| h) | Cyclic Redundancy Checkwords                                    |

- i) Write Amplifier Turn-Off Gap

- j) Spare

The sector format is designed in this manner for the following reasons:

- 1) Positive checking of cylinder position.

- 2) Positive checking of sector and head selection.

- 3) Positive means of programming write protection into each individual sector.

- 4) A method of flagging bad sectors.

The write amplifier turn-on gap which follows the preamble allows time for the amplifiers to be turned on after the preamble has been read. This technique eliminates the need for rewriting the preamble each time a sector is updated, and also eliminates the need to wait one extra revolution to write a sector after checking the preamble.

The size of the initial gap has been chosen to allow full interchangeability between disk drives and disk drives between formatters.

### 2.6 FORMATTER COMMANDS

The formatter and disk commands that are available to the user are summarized below. A detailed description of these commands is contained in Section 3.

- A. Load Cylinder Address Register

- B. Load Microprogrammed Command Word Register

- 1. Select Unit

- 2. Select Sector

- 3. Select Head

- 4. Perform Operation

- a. Write preamble and 1 sector

- b. Check preamble and write 1 sector

- c. Check preamble and read 1 sector

- d. Read diagnostic mode

- e. Ignore write protect and write 1 sector

- f. Write diagnostic mode

- g. Ignore Preamble and read 1 sector

- C. Load Word Count Register

- D. Read Status Register

#### 2.7 WRITE PROTECTION

Two levels of write protection are provided by the disk formatter. These are as follows:

- 1. Programmable write protection by use of a flag bit in the preamble, and

- 2. Absolute write protection by switch.

### 2.7.1 Write Protection Switch Location

On dual platter models the write protection switches located on the disk drive are sensed by the disk formatter.

The write protection switches are located behind the front panel of the formatter when the option is installed.

### 2.8 CONTROLS AND DISPLAYS

- 2.8.1 Controls

- A. **Power ON/OFF** Switches

A toggle ON/OFF switch is provided on the front panel of the formatter. This toggle switch controls the AC power to the formatter power supply.

B. Write Protect Switches

Four write protect switches one for each drive unit are located behind the front panel of the formatter. These switches are provided when option is installed only.

# 2.8.2 Displays

### A. Indicators

As can be seen by Figure 1.1, the front panel of the formatter has four indicators. These are:

| 1. | Read Indicator    | The formatter is processing a read type instruction.        |

|----|-------------------|-------------------------------------------------------------|

| 2. | Write Indicator   | That the formater is processing a write type instruction.   |

| 3. | Error (Red Light) | The formatter has found an error during the last operation. |

| 4. | Ready             | The selected disk unit is on and ready to read or write.    |

### 2.9 ENVIRONMENT

2.9.1 Operating

Temperature:+50° to +104°F, ambientHumidity:10% to 80% RH, 85° maximum wet<br/>bulb temperature.

### 2.9.2 Non-Operating and/or Storage

| Temperature: | $-40^{\circ}$ F to $+150^{\circ}$ F |

|--------------|-------------------------------------|

| Humidity:    | 10% to 95% RH, non-condensing       |

### SECTION 3 FUNCTIONAL OPERATION

### 3.1 INTRODUCTION

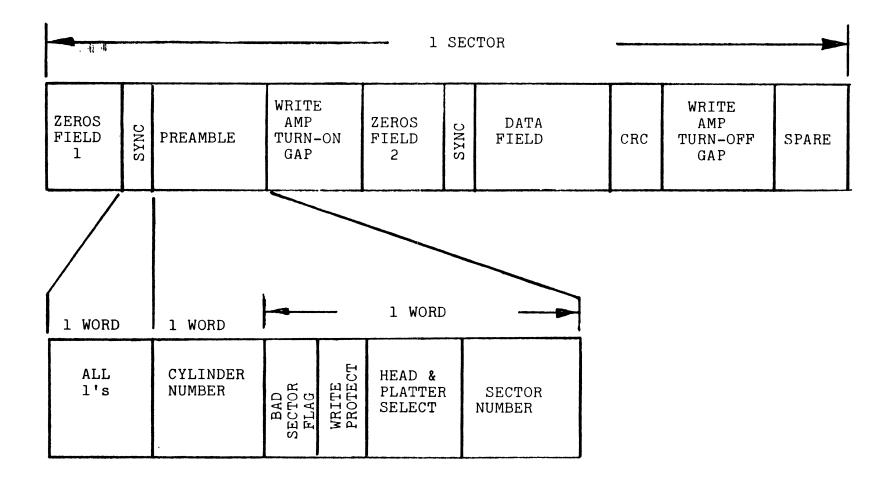

In this section there is a more detailed description of the commands which may be issued to the formatter. These commands are divided into two types:

- 1) <u>Disk Commands</u> which cause the disk to position to a specified cylinder, and

- 2) <u>Formatter Commands</u> which load or read registers in the formatter.

Neither disk commands nor formatter commands should be issued to the Formatter when it is Busy. See Figure 3-1 for a description of the proper sequence for issuing disk and formatter commands.

### 3.2 DISK COMMAND

The disk command, SEEK Cylinder, is routed through the formatter cylinder address register to the selected disk drive unit. This causes the positioner to move to the required cylinder address. This command does not cause the formatter to go Busy.

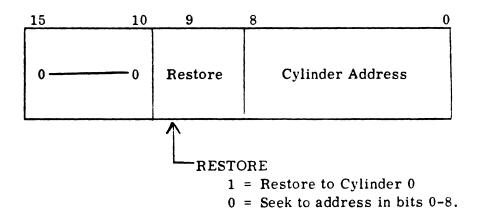

When an Output Strobe Pulse (OSP) is issued with the Register Address Bus (RAB)=011, the 9 bit formatter cylinder address register, Figure 3-2, is loaded from the Coupler Output Bus (CPOB) 0-8 lines. Loading this register causes a SEEK (on the drive unit selected by last command issued) to the Cylinder number loaded into the register. The disk drive performs a validity check on the address. A valid address causes the positioner to move to the required cylinder address.

After the SEEK has been initiated by the loading of this register, any <u>other</u> command (except SEEK) may be issued to the formatter immediately. Another SEEK cylinder command may be issued to a different disk unit after ten (10) microseconds. The 10 microseconds wait time is necessary to allow the disk drive to accept the SEEK address. On disk formatters which have more than one disk drive attached, the SEEK commands can be overlapped between drive units, i.e., two or more drive units may be seeking simultaneously while at the same time data transfers are taking place on another disk unit.

The cylinder address register must not be loaded if BUSY = 1, or if the SEEK bit of the status word = 1. Loading the cylinder address register leaves BUSY unchanged and does not effect DONE.

### CYLINDER REGISTER

# Figure 3.2

.

If the drive unit number has been changed since a SEEK command was initiated, the cylinder address register must be reloaded before the data transfer command can be issued. This is necessary so that the cylinder address portion of the preamble compares correctly.

Bit 9 of the cylinder address register is called the restore bit. A "1" in this bit causes the drive to seek to cylinder 0 without regard to the value of the bits in the rest of the register.

#### 3.3 FORMATTER COMMANDS

These commands involve the transfer of data and control words to or from the disk and can be executed in either a single seek or seek overlap mode. As stated before, they may be issued while the disk is still engaged in a SEEK.

There are three basic formatter commands. All control functions and data conversion of signals from the disk are handled by these formatter commands. The user communicates with the disk formatter by sensing BUSY and DONE status and loading or reading registers.

#### 3.3.1 Command Register

Issuing an OSP with the RAB=101 loads the 12 bit formatter command register from CPOB 0-11 lines. Loading this register causes BUSY to be set and initiates an operation. When the operation has been completed and BUSY goes off, a DONE pulse is issued.

NOTE: The register must not be loaded when BUSY = 1.

The format of the Command Register is as follows:

| CPOB | 15  | 14_ | 13 | 12             | 11 | 10    | 9  | 8  | 7    | 6 | 5    | 4    | 3    | 2    | 1 | 0   |

|------|-----|-----|----|----------------|----|-------|----|----|------|---|------|------|------|------|---|-----|

|      |     |     |    |                |    |       |    | He | ad   |   |      |      |      |      | U | nit |

|      | 0 - |     |    | <del>-</del> 0 | Ор | erati | on | Se | lect | S | ecto | or A | \dd1 | ress | N | br. |

|      |     |     |    |                |    |       |    | Ac | ldr. |   |      |      |      |      |   |     |

|      |     |     |    |                |    |       |    |    |      |   |      |      |      |      |   |     |

Bits

| 15 - 12 Not U | sed = | 00 |

|---------------|-------|----|

|---------------|-------|----|

$11 - 9 \qquad OPR - Operation Code = Shown in Table 3.1.$

#### TABLE 3.1

|     | OPERATION                                                                          | ACCEPTABLE<br>WORD COUNT | ERROR WHICH TERMINATED<br>OPERATION BEFORE DATA<br>TRANSFER OCCURS | ERROR WHICH MAY<br>OCCUR AFTER DATA<br>TRANSFER | COMMENTS                                                                                                                                                                                                                                                                                                                                     |

|-----|------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 000 | No-Operation                                                                       | N. A                     | NRDY, CAE                                                          | NONE                                            | No operation is performed. BUSY goes off<br>immediately, DONE is generated. This operation<br>is used to change the unit number without perform-<br>ing a data transfer.                                                                                                                                                                     |

| 001 | Write Preamble<br>and 1 Sector                                                     | 2–(N+2)<br>Inclusive     | NRDY, WPE, CAE, TMO,                                               | RATE, WCE, FTE                                  | Write Preamble and Data up to 1 Sector in length<br>depending upon value in word count register. The<br>first two words transferred specify the preamble to<br>be recorded as shown in Table II.                                                                                                                                             |

| 010 | Check Preamble<br>and Write 1 Sector                                               | 0 – N<br>Inclusive       | NRDY, WPE, CAE, PCE, BSEC,<br>TMO, FTE                             | RATE, WCE                                       | The previously recorded preamble is checked by the<br>formatter, and data up to 1 sector in length is<br>written on the disk. WC may be 0 N inclusive. If<br>WC is less then N, the remaining words in the sector<br>are filled with zeros.                                                                                                  |

| 011 | Check Preamble<br>and Read 1 Sector                                                | 0-N+2                    | NRDY, CAE, PCE, BSEC, TMO<br>FTE                                   | CRCE, RATE, WCE                                 | The preamble previously recorded is checked by the<br>formatter and data up to 1 sector in length are read<br>from the disk.<br>If WC is in the range 0 N inclusive, WC words will be<br>transferred.<br>If WC is N+1 or N+2, the entire data portion of<br>sector is transferred plus the CRC word(s) will<br>be input as the last word(s). |

| 100 | Read Diagnostic                                                                    | N+4                      | NRDY, CAE, TMO, FTE,                                               | CRCE, RATE, WCE                                 | The preamble, 1 sector of data and the Cyclic<br>Redundancy Check (CRC) words are read from the<br>disk and tranferred through the formatter.<br>The preamble words are the first two words input<br>followed by N Data Words followed by two CRC words.                                                                                     |

| 101 | Check Preamble &<br>Write a Sector but<br>Ignore Write Protect<br>Bit in Preamble. | 0 – N                    | NRDY, WPE, CAE, PCE, BSEC,<br>TMO, FTE                             | RATE, WCE                                       | This operation is identical to 010 except the trans-<br>fer is not terminated if the write protect bit in<br>the preamble is set. If write protect switch is on,<br>or if the rest of the preamble does not check, writing<br>will not occur.                                                                                                |

| 110 | Write Diagnostic                                                                   | N+4                      | NRDY, WPE, CAE, TMO, FTE                                           | RATE, WCE                                       | The preamble 1 sector of data and the CRC words are<br>transferred through the formatter and written on<br>the disk. This instruction differs from 001 because<br>the CRC words are transferred as data and are not<br>generated by the formatter                                                                                            |

| 111 | Ignore Preamble<br>and Read a Sector                                               | 0 - N<br>Inclusive       | NRDY, CAE, TMO, FTE                                                | CRCE, RATE, WCE                                 | The preamble is not checked and up to 1 sector of data is read.                                                                                                                                                                                                                                                                              |

| Bits  |                                                                                                                                                                                    |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 - 7 | Head - Head Select Address                                                                                                                                                         |

|       | The head selected to be used for reading or writing is assigned as follows:                                                                                                        |

|       | Single Platter Drive                                                                                                                                                               |

|       | 00 Upper Head<br>01 Lower Head                                                                                                                                                     |

|       | Dual Platter Drive                                                                                                                                                                 |

|       | <ul> <li>00 Upper Head - Removable Disk</li> <li>01 Lower Head - Removable Disk</li> <li>10 Upper Head - Non Removable Disk</li> <li>11 Lower Head - Non Removable Disk</li> </ul> |

| 6 - 2 | Sector - Sector Address                                                                                                                                                            |

|       | Data transfer will occur on the sector specified by this<br>5 bit number. The acceptable range is from 0-S <sub>8</sub> where:                                                     |

|       | $S_8$ is 37 <sub>8</sub> for 32 sector disks<br>27 <sub>8</sub> for 24 sector disks<br>17 <sub>8</sub> for 16 sector disks<br>13 <sub>8</sub> for 12 sector disks                  |

| 1 - 0 | <u>Unit – Unit Number</u>                                                                                                                                                          |

|       | Unit selected for use by the formatter.                                                                                                                                            |

|       | Code Selected Unit                                                                                                                                                                 |

|       | 00         0           01         1           10         2           11         3                                                                                                  |

|       | 11 3                                                                                                                                                                               |

#### TABLE 3.2

#### PREAMBLE DATA FORMAT

Cylinder Values ( $0_8 - 624_8$ )

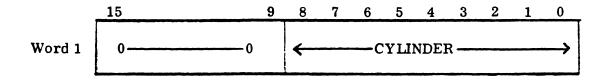

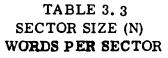

### 3.3.2 Word Count Register

Issuing an OSP with the RAB=111 loads the 9 bit formatter word count register from CPOB 0-8 lines. The word count register is used to determine how many words of data to transfer through the formatter for READ or WRITE operations. Although the word count register is a 9 bit register, the actual maximum number of bits that may be loaded into the register is a function of the sector size (N) hardwired into the disk formatter. See Table 3.3. If the specified word count is too large, an error flag is set in the Status Register at the end of the data transfer operation. This error flag indicates that the Word Count Register did not count down to zero.

Note: This register must not be loaded when BUSY=1. Loading the word count register leaves BUSY unchanged and does not affect DONE.

| Decimal           | N Octal          |

|-------------------|------------------|

| <sup>32</sup> 10  | 40 <sub>8</sub>  |

| <sup>64</sup> 10  | 1008             |

| 96 <sub>10</sub>  | 140 <sub>8</sub> |

| 128<br>10         | 200 <sub>8</sub> |

| 160 <sub>10</sub> | 240 <sub>8</sub> |

| 192<br>10         | 300 <sub>8</sub> |

| <sup>224</sup> 10 | 340 <sub>8</sub> |

| <sup>256</sup> 10 | 4008             |

### 3.3.3 Status Register

Issuing an Input Strobe Pulse (ISP) with RAB=011 causes the status word of the formatter to be placed on Coupler Input Bus (CPIB) 0-11 lines.

NOTE: This register must not be accessed while BUSY=1.

The format of Status Register is as follows:

| 15 - 12 | 11   | 10  | 9   | 8            | 7                 | 6                 | 5                  | 4                                 | 3        | 2      | 1    | 0       |

|---------|------|-----|-----|--------------|-------------------|-------------------|--------------------|-----------------------------------|----------|--------|------|---------|

| 0-0     | NRDY | WPE | CAE | PCE          | тмо               | FTE               | CRCE               | RATE                              | BSEC     | WCE    | 0    | SEEK    |

|         | Bits |     |     |              |                   |                   |                    |                                   |          |        |      |         |

|         | 15 - | 12  |     | Not          | Used =            | 00                |                    |                                   |          |        |      |         |

|         | 11   |     |     | NRD          | <u>Y - D</u>      | rive N            | ot Read            | ly                                |          |        |      |         |

|         |      |     |     |              |                   | -                 | elected<br>up to s | unit is r<br>peed.                | not conn | ected, | no   | t       |

|         | 10   |     |     | WPE          | <u> - Wr</u>      | ite Pr            | otect E            | rror                              |          |        |      |         |

|         |      |     |     |              | -                 |                   |                    | ittempte<br>transfe               |          | -      | orot | ected   |

|         | 9    |     |     | CAE          | - Cyl             | inder             | Addres             | s Error                           |          |        |      |         |

|         |      |     |     | sele         | cted d            | rive u            | nit was            | ch excee<br>loaded i<br>lata trar | into the | cylind | ler  | the     |

|         | 8    |     |     | PCE          | - Pre             | amble             | Check              | Error                             |          |        |      |         |

|         |      |     |     |              |                   |                   |                    | tor port<br>er did no             |          | -      | eam  | ble did |

|         | 7    |     |     | TMC          | ) - Tir           | ne Out            | Error              |                                   |          |        |      |         |

|         |      |     |     | data<br>by s | transi<br>electir | er oco<br>Ig a se | curred.            | BUSY<br>This e<br>mber w          | error is | usual  | ly c | aused   |

| Bits |                                                                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6    | <u>FTE - Format Error</u>                                                                                                                                                                                                                    |

|      | Either a sector size too large for the disk drive<br>connected to the formatter has been selected or no<br>sync word was found in the specified sector indicating<br>that the disk is not formatted. Data transfer may not<br>have occurred. |

| 5    | <u>CRCE - CRC Error</u>                                                                                                                                                                                                                      |

|      | The CRC word recorded at the end of the sector did<br>not compare with the one calculated on the data in the<br>sector. All specified data transfers occurred.                                                                               |

| 4    | RATE - Rate Error                                                                                                                                                                                                                            |

|      | The user did not clear the Data Flag within the specified length of time (by sending or accepting a new word.)                                                                                                                               |

|      | Data transfer occurred up through the end of the sector<br>but some words were missed.                                                                                                                                                       |

| 3    | BSEC - Bad Sector                                                                                                                                                                                                                            |

|      | The Bad Sector Flag was set to 1. Data transfer did not occur.                                                                                                                                                                               |

| 2    | WCE - Word Count Error                                                                                                                                                                                                                       |

|      | The word count was greater than zero at the completion<br>of the last operation. A full sector of data may have<br>been transferred.                                                                                                         |

| 1    | Not Used = $0$                                                                                                                                                                                                                               |

| 0    | SEEK - Unit Seeking                                                                                                                                                                                                                          |

|      | The disk unit last selected by a UNIT command is still<br>executing a SEEK cylinder. If the user wishes to change<br>the cylinder address on this unit, this bit must first go                                                               |

to zero.

### SECTION 4 THEORY OF OPERATION

### 4.1 GENERAL

The heart of the Disk Formatter is the registers. All communications between the mini-computer and the Disk Formatter are accomplished by loading and reading of these registers. These registers are selected by a group of three lines called Register Address Bus (RAB) which address uniquely one of the registers to be loaded or read. In conjunction with RAB lines, there is an Output Strobe Pulse (OSP) or an Input Strobe Pulse (ISP) which strobes the data into registers or reads the data from register, respectively. In this manner, the registers are accessed.

The data is transmitted from the computer to the registers on Coupler Output (CPOB) lines, and from the registers back to the computer by means of Coupler Input Bus (CPIB) lines.

All diagrams shown in this section are provided as reference for the text which describes logic operation. In some cases, logic not pertinent to the discussion is blocked out of the drawing. A complete, up to date set of logics is included with each XDF-50 formatter. The user should refer to these logics for maintenance of his system since these prints describe the configuration of the XDF-50 as shipped.

#### 4.2 REGISTERS

Before any data READ/WRITE operations can begin, the Disk Formatter registers must be loaded with data that describe cylinder positioning, number of data words to transfer, and what operations must be performed. The registers that must be loaded to perform these functions are in order of their loading sequence.

- A. Cylinder Address Register

- B. Word Count Register

- C. Command Register

The mini-computer coupler transmits four signals to the formatter which are used to select the registers for loading. These are the three RAB signal lines mentioned previously which are decoded by the Disk Formatter and strobed by an Output Strobe Pulse. This loads the selected register. The balance of this section is concerned with a fuller explanation of these registers and their timing sequence.

## 4.2.1 Cylinder Address Register

The cylinder address register is shown in Figure 4.1. As can be seen by this figure, the cylinder address register is a 12-bit register. It is composed of three Quad Latches (SN7475) which drive a series of SN7438 power drivers. The SN7438 power drivers are used to drive the terminated cylinder address lines.

### 4.2.1.1 Loading Cylinder Address Register

The timing sequence for the loading of the cylinder address register is as shown in Figure 4.2. The pin numbers shown on Figure 4.2 refer to Figure 4.1.

Loading the cylinder address register causes a cylinder address strobe (CYL STROBE) to be generated to the disk unit. This strobe transfers the cylinder number from the cylinder register in the Disk Formatter to a like cylinder register in the disk drive. The disk unit performs a validity check on the address. A valid address causes the disk positioner to move to the required cylinder address. In case of an invalid address, a cylinder address error bit is returned by the disk unit.

After the SEEK has been initiated by the loading of this register, any other command (except SEEK) may be issued to the Disk Formatter. However, another SEEK command may be issued to a different disk drive within ten microseconds. As can be seen by Figure 4.2, this means that in a daisy chained disk configuration the Disk Formatter can cause SEEK's to be overlapped between disk drives.

### 4.2.2 Word Count Register

The word count register is shown in Figure 4.3. As can be seen by this Figure, the word count register is composed of two SN74193 up/down counter chips and two SN7474 D type flip flops, creating a 9 bit register. The purpose of this register is to tell the Disk Formatter how many words within a sector are to be transferred

FIGURE 4:1 Cylinder Address Register 4-3

4-4

| 0 <sup>*</sup>   דדר  176   375   400   401-<br>173   176   177   400   401- |

|------------------------------------------------------------------------------|

| ///²   ///²   ///²                                                           |

|                                                                              |

|                                                                              |

|                                                                              |

| -                                                                            |

#### FIGURE 4-4

TINNING DIAGRAM FOR WORD COUNT REGISTER

4-6

•

### 4.2.2.1 Loading Word Count Register

The timing sequence for the loading of the word count register is as shown in Figure 4.4. The timing sequence shown is for a word count of "403 $_8$ ".

Since the data on the CPOB is carried as low true, the "1's" complement of "4038", is loaded into the word count register as a high true state. To change the "1's" complement into a "2's" complement, an initial advance of the word count register is accomplished by incrementing the counter when the command register (K5-9) is loaded. This assumes that the command register will only be loaded once following the loading of the word count register.

Therefore, each subsequent advance of the word count register is accomplished on the trailing edge of the Set Data Flag Pulse. When the word count register reaches "0" flip flop (F8-?) is set. This causes the Disk Formatter to quit generating Data Flag pulses.

As can be seen by Figure 4.4 the word counter "0" flip flop is not set on the first overflow of the Carry Out Signal in the example of " $403_8$ " shown but is set on the second overflow. Whether F8-9 is set on first overflow or second overflow depends upon the value set in F8-5. Since F8-5 acts as the MSB of the counter it controls the setting of the word counter "0" flip flop.

The word counter "0" flip flop will remain set until a new value is loaded into the word count register.

### 4.2.3. Command Register

The command register is shown in Figure 4.5. As shown by this figure, the command register is a 12 bit register being composed of three SN7475 bistable latches. The register is loaded by data on the CPOB (0-11) lines. The register selection is accomplished by a RAB address of 101 and an OSP.

The most significant 3 bit outputs are decoded by the SN7442 binary decoder into 8 possible operations (0-7). Two bits go to a head select address (1 bit for platter select and 1 bit for head select), and 5 bits go to a comparator circuit where they are compared against a Sector Counter. The least significant 2 bits are decoded by a set of SN7438 drivers. These drivers are used to select 1 out of 4 possible disk units whose address are 0-3.

|                                                      | PINS     | TIMING SEQUENCE CYCLE |

|------------------------------------------------------|----------|-----------------------|

| CPOB Ø (L)<br>(TYPICAL)                              | 44-7     |                       |

| REGISTER<br>AGURESS                                  |          |                       |

| RAB Ø (H)                                            | K3-9     |                       |

| RABI (L)                                             | K3-13    |                       |

| RAB 2 (H)                                            | K3-12    |                       |

| 05P (H)                                              | K3-10    |                       |

| LDADING (H)<br>(DMMAND<br>VIGUITR                    | H7-2     |                       |

| HATTER (H)<br>TYPICAL OF<br>OTHER RITS OF<br>COMMAND | 8 - ما 1 |                       |

| COMMAND                                              |          |                       |

| OPERATION (L)<br>THREE(3)                            | X6-4     |                       |

| UNIT 3 (L)<br>SELECT                                 | A4-8     |                       |

16

FIGURE 4.6

TIMING DIAGRAM FOR COMMAND REGISTER

4-9

#### 4.2.3.1 Loading the Command Register

The timing sequence for loading the command register is as shown in Figure 4.6. The timing sequence is an example of " $3403_8$ " being loaded into the command register. Any time the command register is loaded with anything other than 000, the Disk Formatter unit goes BUSY, and the BUSY flip flop is set. For further discussion of BUSY, see paragraph 4.5.

#### 4.2.4 Status Register

The status register is a 12 bit register. The status bits are placed on the CPIB lines any time that the formatter is not busy and RAB 0 = 1.

See figure 4-7 for logic of status gating. Detail descriptions of each of the status register bits is found in Section 3.3.3 and Section 4.4.

### 4.2.5 Shift Registers

A typical section of the shift register is shown in Figure 4.8. Each group of the SN7495 registers are four bit right shift registers that are loaded in parallel and shifted serially. They are not loaded from the mini-computer executed programs, but normally from the DMA channel only.

The shift registers have a RAB address of 000, and this address with an OSP causes the data on the CPOB lines to be loaded into the shift registers. The loaded shift registers are shifted serially and are used to provide the write data for the disk memory unit.

To determine which shift register is to be loaded in parallel and which shift register is to be shifted serially, the control logic steers the data by use of steering flip flop (K9 - Pin 8 & 9). See Figure 4.9. Initially, the control logic is set to select shift register 2 to be loaded in parallel and shift register 1 for data to be shifted serially. The timing of the shift registers and the steering logic is shown in Figure 4.10.

FIGURE 4.9 Steering Flip Flop 4-13

FIGURE 4.10

TIMING DIAGRAM FOR SHIFT REGISTER

#### 4.3 CONTROL LOGIC

#### 4.3.1 State Counter

The state counter is shown in Figure 4.11. It is composed of a SN74193 simultaneous advance counter and a SN7442 decoder. The output from the SN74193 counter is decoded by the SN7442 decoder into 1 of a possible 8 states.

The initial state as shown by Figure 4.11 is IDLE. The first signal input to the state counter is a Clean Sector Compare (H) signal which resets the state counter. This forces the counter to decode the output as  $10_8$  which is output on pin 10 (Idle State).

As soon as the Disk Formatter finds a sector compare the operation begins. The input on pin 12 of the SN7442 decoder is low so the counter is not advanced. This is decoded as "000" by the decoder, and a "0" on N5-12 forces the decoder to output the signal on N5-1 which is the ACQ-1 state.

Subsequent advances of the state counter are caused by an advance state counter pulse which comes from the SN 7451 AOI gate shown in Figure 4.12. This increment pulse causes the state counter to advance through its states which are decoded as ACQ1, SYN1, PRE, ACQ2, SYN2, DATA, CRC. The CRC state is the last state entered by the state counter. This state is terminated by resetting the BUSY flip flop. Resetting the BUSY flip flop also resets the Clean Sector Compare flip flop, which is decoded as the Idle State, terminating the Disk Formatter operation. See the Timing Diagram on Figure 4.13. The logic equation for the signals which advance the State Counter is shown in Table 4.1.

#### 4.3.2 Sector Length Counter

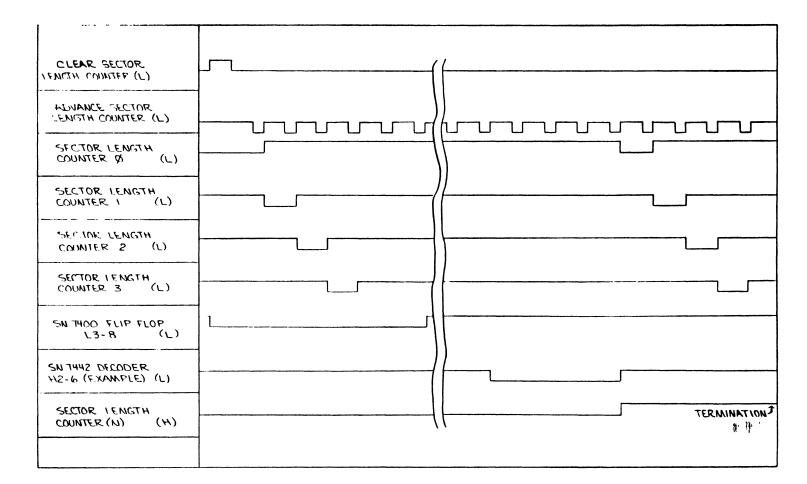

The sector length counter is as shown on Figure 4.14. Initially, the sector length counter is in the zero state (SECL 0), it goes up through SECL 1, SECL 2, SECL 3, etc. up to SECL 7. When it reaches that point, the control logic sets the L3 flip flop. The setting of that flip flop prevents any further decodes from the SN 7442 decoder until the L3 flip flop is reset by SLC=N, indicating that the counter has counted one full sector. Sector length counter=N and SECL 0, SECL 0, SECL 1, SECL 2, and SECL 3 is used to decode into N+0, N+1, N+2, N+3.

The logic equations for the sector length counter as shown in Table 4.2, and the Timing Diagram is as shown in Figure 4.15.

# TABLE 4.1LOGIC EQUATIONS FOR ADVANCING STATE COUNTER

| MODE OF OPERATION                                                                             | LOGIC EQUATION                                         |

|-----------------------------------------------------------------------------------------------|--------------------------------------------------------|

| READ PREAMBLE (RP)                                                                            | ACQ1•40µ•WC2+SYN1•SYNC•RC2<br>+PRE•SECL 3•BWCN•RC2     |

| READ RECORD (RR)                                                                              | ACQ2•69u•WC2+SYN2•SYNC•RC2<br>+DATA•SECL(N)•BWCN•RC2   |

| CRC MODE TO IDLE (READ TERMINATIO<br>RESET BUSY (NORMAL TERMINATION)<br>CRC BACK TO IDLE MODE | N)<br>RR•(SECL N+3) • BWCN                             |

| WRITE PREAMBLE (WP)                                                                           | ACQ1•100u•WC2+SYN1•BWCN•WC2<br>+PRE•SECL 2•BWCN•WC2    |

| WRITE RECORD (WR)                                                                             | ACQ2•100µ•WC2+SYN2•BWCN•WC2<br>+DATA•SECL (N)•BWCN•WC2 |

| CRC MODE TO IDLE (WRITE<br>TERMINATION)<br>RESET BUSY (NORMAL TERMINATION)                    | WR•(SECL N+4)•BWCN                                     |

.

-

#### FIGURE 4.15

TIMING DIAGRAM FOR SECTOR LENGTH COUNTER

4-21

TABLE 4.2LOGIC EQUATIONS FOR SECTOR LENGTH COUNTER

| OPERATION MODE      | LOGIC EQUATION TO INCREMENT<br>COUNTER |

|---------------------|----------------------------------------|

| READ PREAMBLE (RP)  | PRE•BWC 0•RC2                          |

| READ RECORD (RR)    | DATA•BWC 0•RC2 + CRC•BWC 0•RC2         |

| WRITE PREAMBLE (WP) | PRE•BWC 0                              |

| WRITE RECORD (WR)   | DATA•BWC 0 + CRC•BWC 0                 |

## RESET SECTOR LENGTH COUNTER

RP (ACQ1 + SNY1) + WP (ACQ1) RR (ACQ2 + SYN2) + WR (ACQ2)

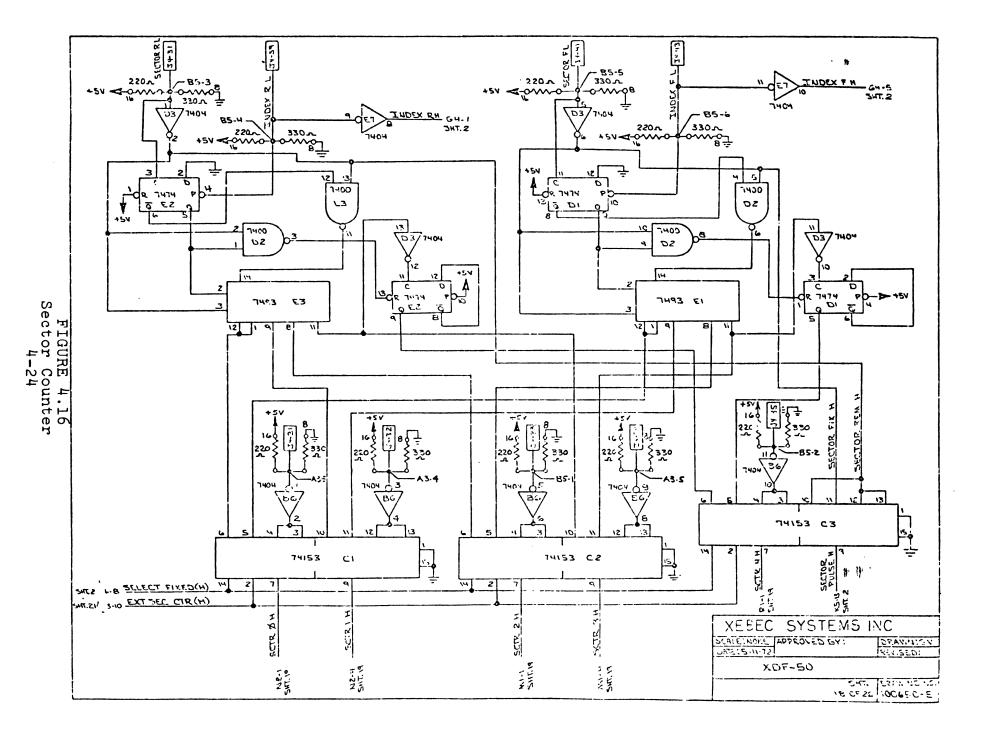

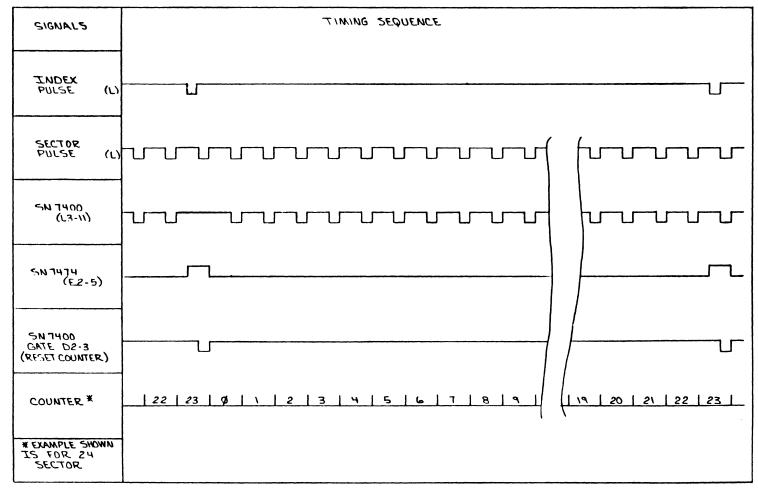

### 4.3.3 Sector Counter

The sector counters are shown in Figure 4.16. Sector pulses and index pulses come in from the disk, the index pulse once/revolution and sector pulse once/sector. The SN7474 E2 flip flop is used to determine when to reset the counter. If it gets set by the index pulse, then on the next sector pulse the counter will get reset.

When E2 is set, a pulse is generated on D2-3 which resets E2-13, an extension of the sector counter, to make the sector counter a 5 bit counter. Internally to the SN7493 sector counter on pins 2 and 3, an equivalent circuit is used. Pins 2 and 3 are inputs that will reset the counter when they are both high (H).

The sector pulse (E3-14) is inhibited when E2-5 is not set high. Therefore, no advance pulses enter the counter when it is being reset by index pulses. The timing diagram is shown in Figure 4.17.

The above describes the operation of the Sector Counter for the removable disk. An identical counter for the fixed disk is shown on the right hand side of Figure 4-24. The operation of this counter is the same. It should be noted, however, that entirely separate sets of pulses are used to drive the other sector counter, and the relationship of the value of the counters depends upon the orientation of the index mask on the fixed disk to the index mask on the removable disk.

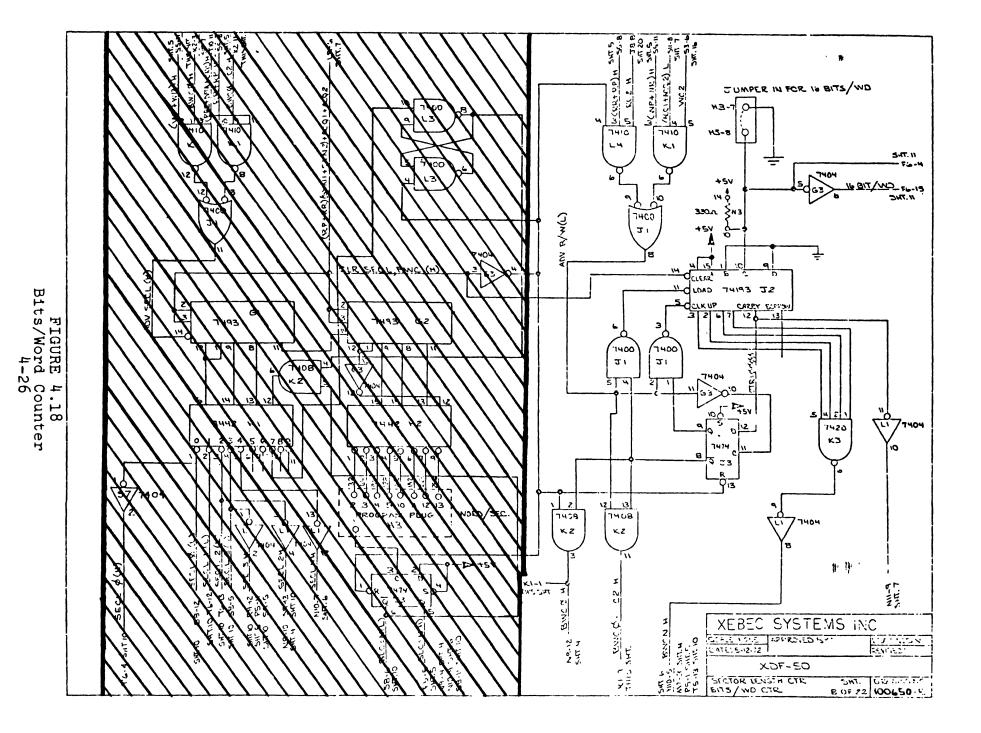

#### 4.3.4 <u>Bits/Word Counter</u>

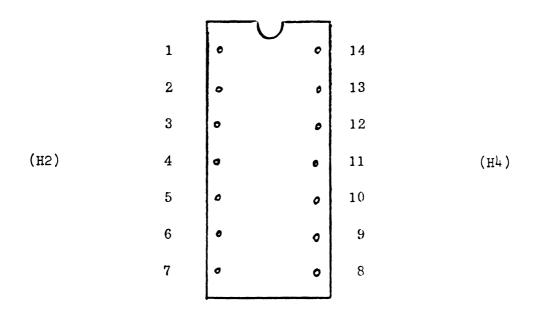

The bits/word counter is shown in Figure 4.18. The bits/word counter can be configured to divide by 12 bits or 16 bits depending upon the jumper between H3-7 to H3-8.

When a 12 bits/word mini-computer is attached to the disk formatter, a "load pulse" is generated after count "0" to load a value of five into the counter.

When the counter reaches a value of 15, (BWCN), it resets itself automatically back to zero (BWC0) since it is a four bit counter. After count zero it jumps back to 5 as before. The net result is that 12 counter states are used.

In the case of a 16 bits/word mini-computer, the disk formatter generates a "load pulse" after count zero to load a value of "1" into the counter. The counter counts up to 15 (BWCN), and on the next count back to zero (BWC0) again. All 16 states of the counter are used.

The Timing Diagram for the bits/word counter is shown in Figure 4.19, and the logic equations for the operational modes are shown in Table 4.3.

•

FIGURE 4.17 TIMING DIAGRAM FOR SECTOR COUNTER

4-25

\*\*

4-27

TABLE 4.3LOGIC EQUATION FOR BITS/WORD COUNTER

~

| FUNCTION                        | OPERATION MODE                                                                     | LOGIC EQUATION                                                                                                |

|---------------------------------|------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| RESET<br>BITS/WORD<br>COUNTER   | READ PREAMBLE (RP)<br>WRITE PREAMBLE (WP)<br>READ RECORD (RR)<br>WRITE RECORD (WR) | (SYN1 + ACQ1) + $(ACQ1)$ + $(SYN2 + ACQ2)$ + $(ACQ2)$                                                         |

| ADVANCE<br>BITS/WORD<br>COUNTER | READ PREAMBLE (RP)<br>WRITE PREAMBLE (WP)<br>READ RECORD (RR)<br>WRITE RECORD (WR) | $\overline{(SYN1 + ACQ1)} RC2$ $\overline{(ACQ1 WC2)}$ $\overline{(SYN2 + ACQ2)} RC2$ $\overline{(ACQ2 WC2)}$ |

,

#### 4.3.5 Comparator Circuits

There are three (3) comparator circuits in the disk formatter. These are:

- 1) Cylinder Compare

- 2) Sector Compare

- 3) Preamble Sector Compare

These are briefly discussed in the balance of this section.

#### 4.3.5.1 Cylinder Compare

Cylinder Compare circuit is shown in Figure 4.20. As can be seen by this girue, it is composed of SN7486 exclusive /OR gates feeding into an 8-input NAND flip flop. The output of this compare circuit is used to determine if the cylinder register matches the first preamble word (which identifies the cylinder address currently read).

#### 4.3.5.2 Sector Compare

The sector compare flip flop is shown in Figure 4.21. When the command register is loaded, the BUSY flip flop is set. The disk formatter waits until SEEK is complete and then waits until the sector counter value is equal to the sector value loaded into the command register. This equality along with SEEK complete enables the sector pulse. The sector pulse is delayed approximately 2.0 microseconds to allow the counters to stabilize before comparison.

When these events have occurred the clean sector compare flip flop is set. This indicates the beginning of an operation in the addressed sector. The timing of these events is shown in Figure 4.22.

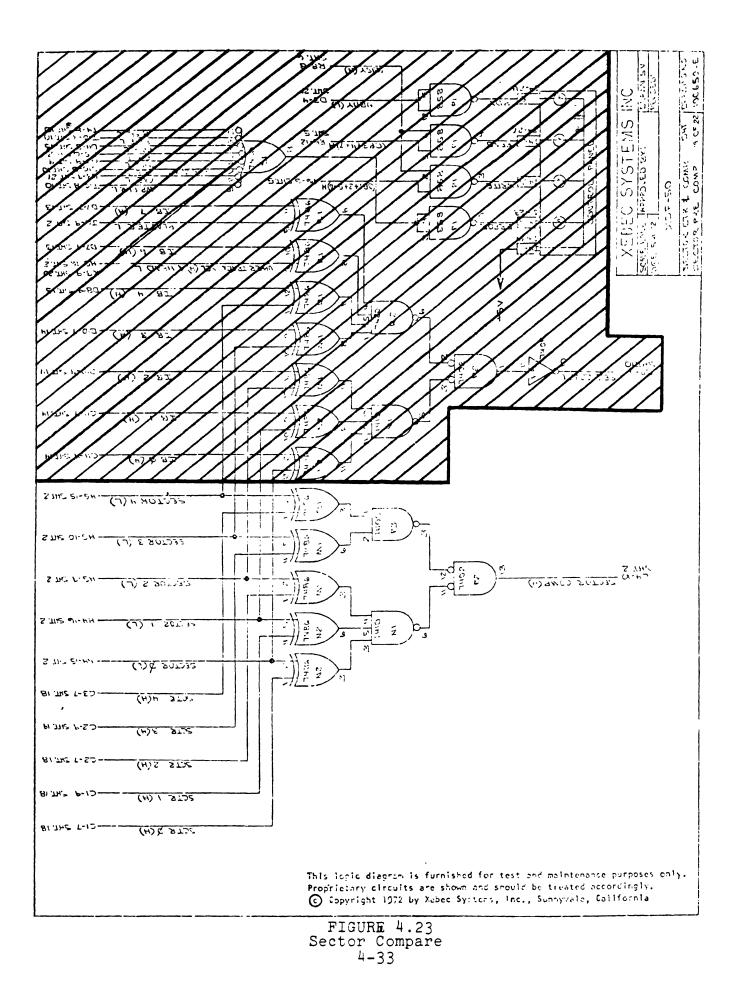

The comparison of the value in the sector register to the current value of the sector counter is shown in Figure 4.23. It is a series of SN7486 exlusive/OR gates whose output P2-13, is used to determine whether the sector counter value equals the command register sector value.

.

4-32

#### 4.3.5.3 Preamble Sector Compare

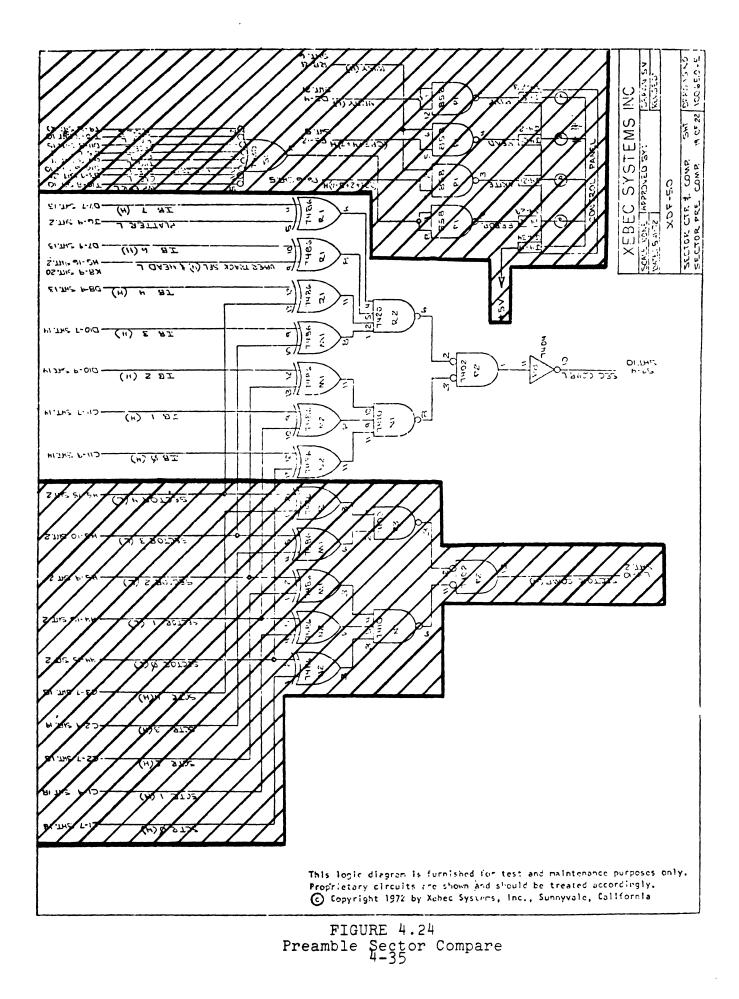

The preamble sector compare circuit is shown in Figure 4.24. It is composed of a series of SN7486 Exclusive /OR gates. The output of this compare circuit is used to determine if the sector register matches the 2nd word of the preamble (used to identify the sector currently being read.)

#### 4.3.6 <u>Timing Circuits</u>

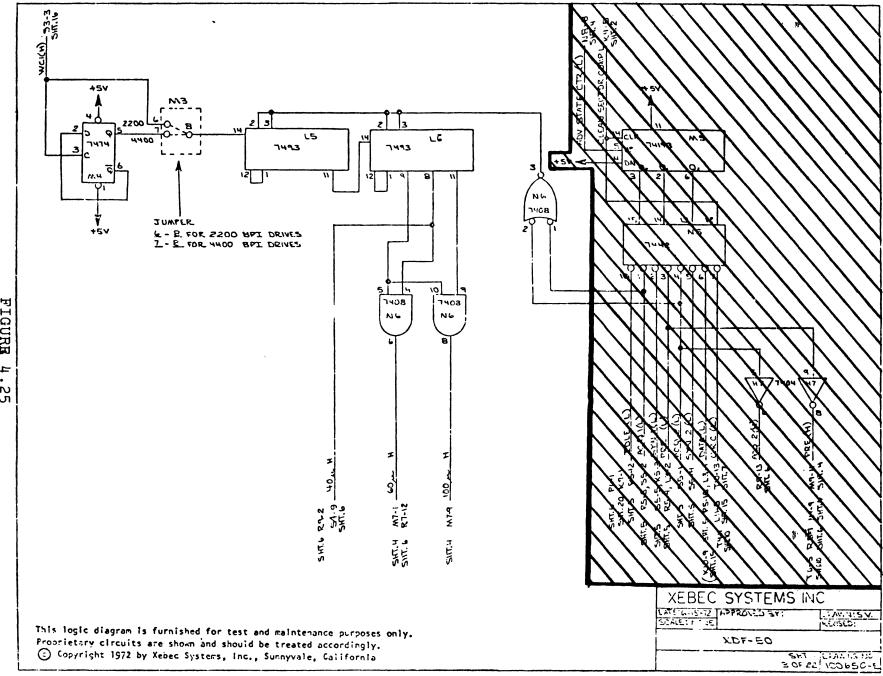

The timing circuit for the disk formatter is shown in Figure 4.25. This circuit is composed of two SN7493 4-bit binary counters, one SN7474 flip flop, and a series of SN7408 gates. The timing circuit shown utilizes jumpers between pins 6 and 8 for 2200 BPI density.

The outputs of the timing circuit are 40 microseconds, 60 microseconds, and 100 microseconds from the zero state of the counter. The logic equations for resetting and advancing the timer are as follows:

| RESET TIMER   |                                   |

|---------------|-----------------------------------|

|               | ACQ1 + ACQ2                       |

| ADVANCE TIMER | WC1, $(ACQ1 + ACQ2)$              |

|               | (Implied by reset, not actually   |

|               | in the logic for advancing timer) |

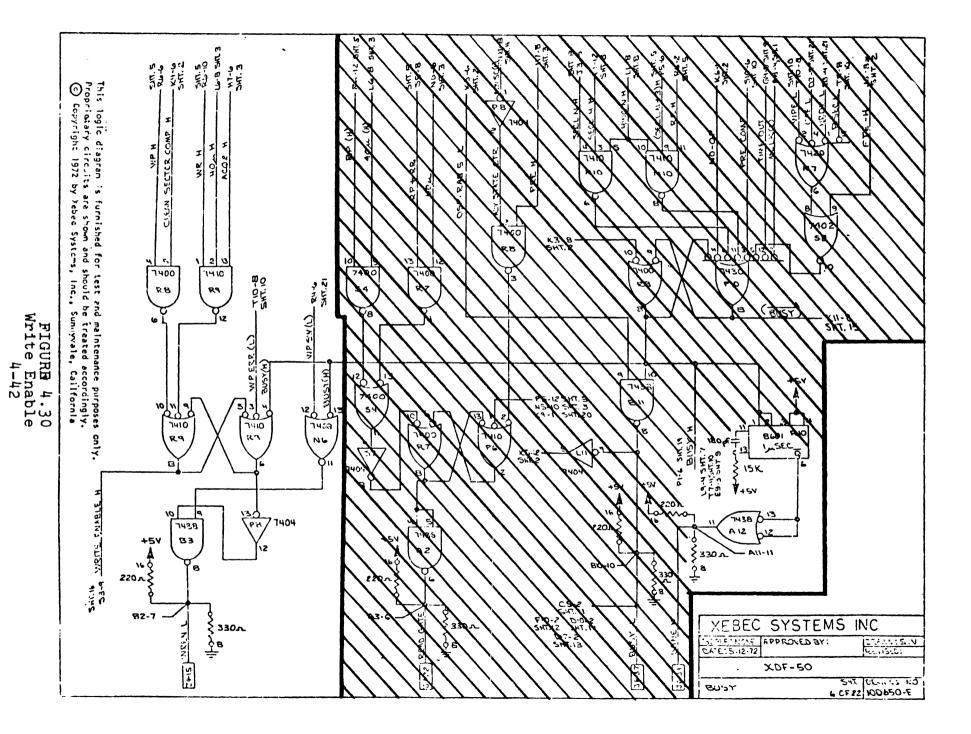

#### 4.3.7 Write Clock and Double Frequency Write Data Generation

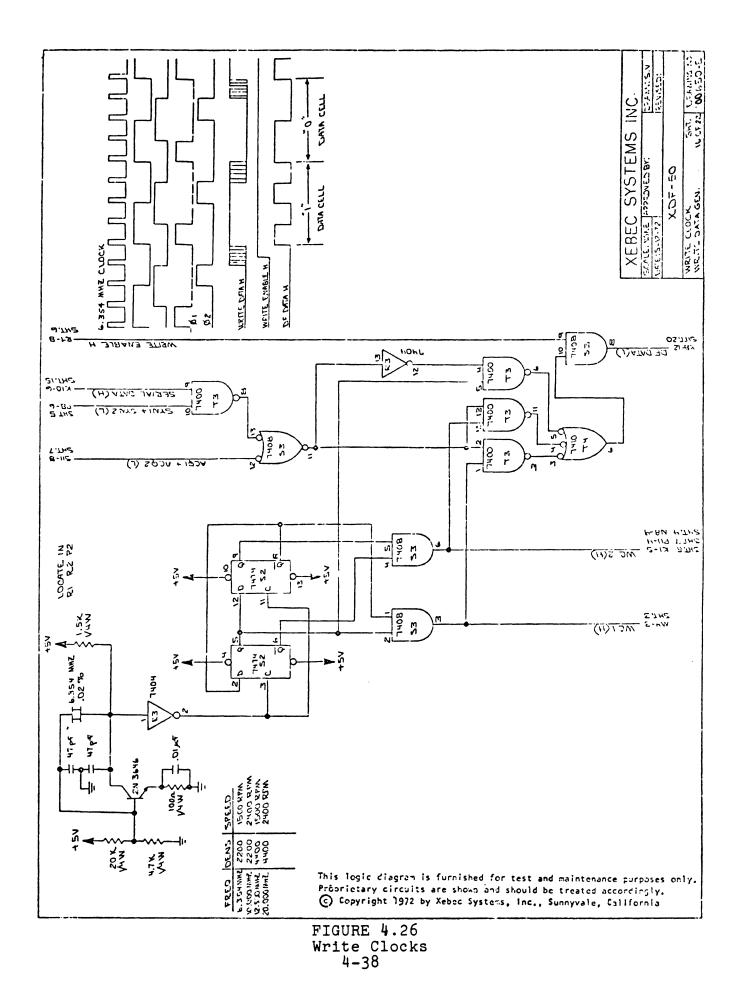

The write clock circuit is shown in Figure 4.26. It is composed of two SN7474 counters and SN7408 decoders. These generate the write clocks used to create double frequency write data.

The write oscillator is the basic timing source and runs at one of the crystal controlled frequency values shown on Figure 4.26. The R3 inverter shapes the signal to a TTL compatible pulse

The TTL compatible signal is used to drive the SN7474 counter which is then decoded by the SN7408 gate. Two states of the counter are decoded as write clock 1 and write clock 2.

The disk formatter has thus generated a two (2) phase clock which are a quarter cell in duration and are spaced 1/2 cell apart. See Timing Diagram on Figure 4.27.

FIGURE 4.25 Timing Counter 4-36 The write clocks that are generated are used to create a double frequency (DF) encoded signal from the NRZ wirte data that is received from the shift registers. The timing for the DF signal is shown in Figure 4.27.

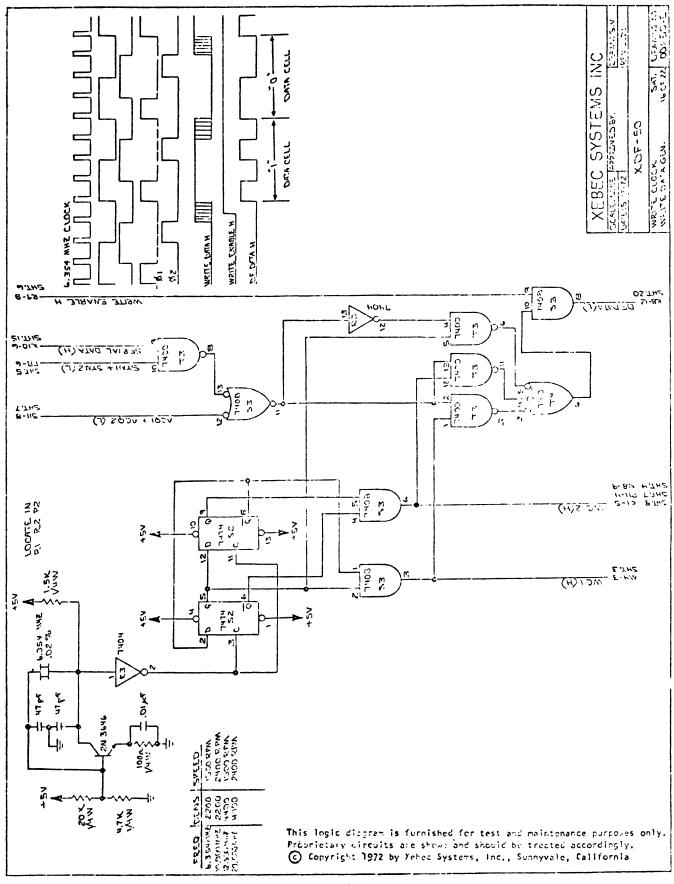

#### 4.3.8 Read Gate

The read gate circuit is as shown in Figure 4.28. When a read operation is selected, the read gate circuit is enabled. This enables data from the disk memory unit to be read into the disk formatter.

The read gate flip flop is controlled as follows:

- A) Set read gate =  $(RP \cdot 40 \mu + RR \cdot 60 \mu)$

- B) Reset read gate = OSP RAB5 + PRE ADV STATE CTR + MCLR

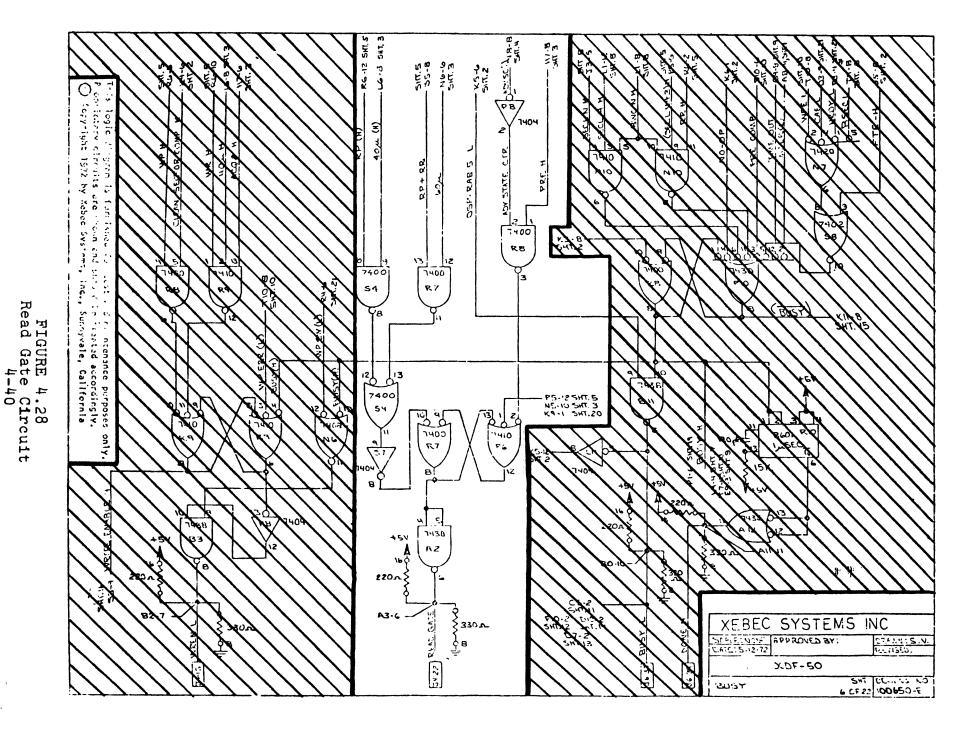

#### 4.3.9 Read Clock Circuit

The read clock circuit is shown in Figure 4.29. A two phase set of internal read clocks is generated from the incoming read clock from the disk (Read CLKI).

| Read Clock 1: | SHIFT-SHIFT REGISTERS                                                         |

|---------------|-------------------------------------------------------------------------------|

| Read Clock 2: | CLOCK SECTOR LENGTH COUNTER<br>CLOCK BITS/WORD COUNTER<br>CLOCK STATE COUNTER |

Read clock 1 and read clock 2 are pulses 50-100 NS wide, separated by a delay of 70 to 100 NS.

SRIN is generated from the read data input RDATA 1 and forms the serial read data input to the shift registers.

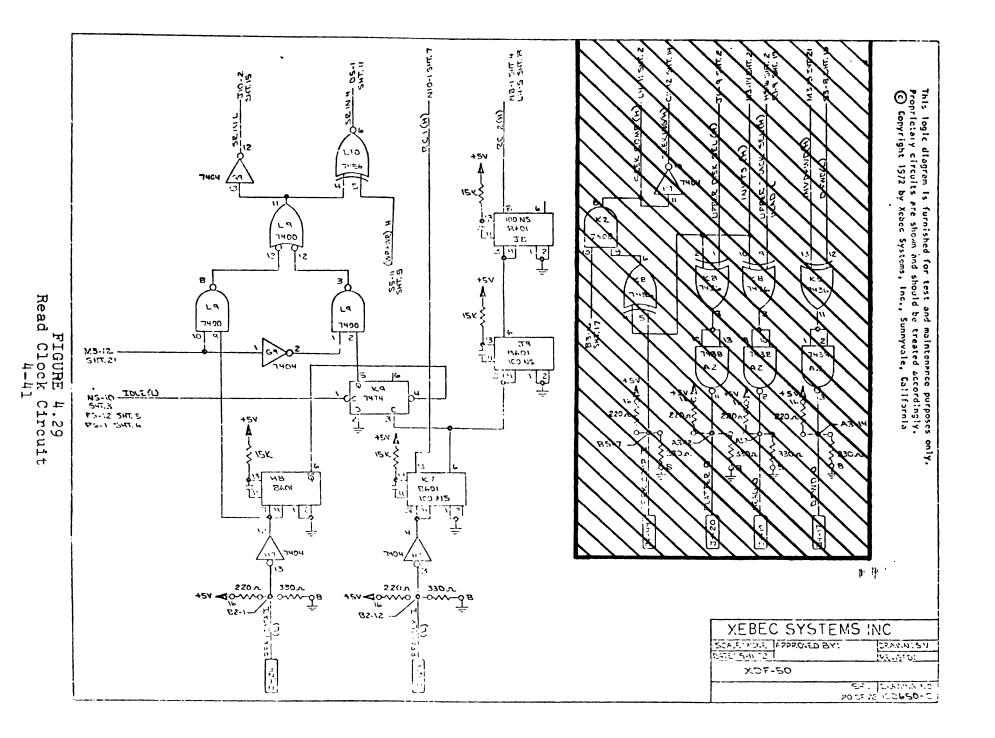

#### 4.3.10 Write Enable

The write enable circuit is shown in Figure 4.30. The write enable flip flop is set when the clean sector compare signal pulse is enabled and write preamble operation is being performed, or when a write record operation is being performed. The write enable flip flop will remain set until 1) a write protect error is detected, or 2) until BUSY flip flop goes off indicating data transfer has been completed.

When the disk formatter detects a write protect error, the write enable flip flop is reset immediately. With a set and reset condition on the flip flop simultaneously, the disk formatter logic is designed so that signals enabling the reset side of any flip flop have first priority. The write enable circuit would be turned off, and an error bit would be returned to the status register.

#### FIGURE 4.27 Write Clock/Data Timing 4-39

The logic equations for the write enable circuit are:

Set Write Enable FF = WP•CLEAN SECTOR COMPARE + WR• ACQ2 40 u Reset Write Enable FF = WPERR + BUSY WREN = Write Enable FF•Busy•WP<sub>sw</sub>

#### 4.3.11 Data Flag

The data flag circuit is shown in Figure 4.31. Data Flag (DFLG) is used to tell the mini-computer coupler that the formatter is ready to receive or send a word of data. DFLG is a flip flop controlled as follows:

| Function   | During<br>Operation     | Logic Equation                                                      |

|------------|-------------------------|---------------------------------------------------------------------|

| SET DFLG   | READ PREAMBLE           | RP•OP4•(SECL1+SECL2)•BWC0•<br>WDCT0                                 |

| SET DFLG   | READ RECORD             | $\frac{RR \bullet (SEC L0 + SEC LN3) \bullet BWC0 \bullet}{WDC T0}$ |

| SET DFLG   | WRITE PREAMBLE          | WP• (SYN+PRE)• BWC0• WDCT0                                          |

| SET DFLG   | WRITE RECORD            | $\frac{WR \bullet (SYNC+DATA+CRC) \bullet BWC0 \bullet}{WDCT0}$     |

| RESET DFLG | ALL WRITE<br>OPERATIONS | OSP                                                                 |

| RESET DFLG | ALL READ<br>OPERATIONS  | ISP                                                                 |

| RESET DFLG | ALL OPERATIONS          | BUSY                                                                |

#### 4.4 STATUS BITS

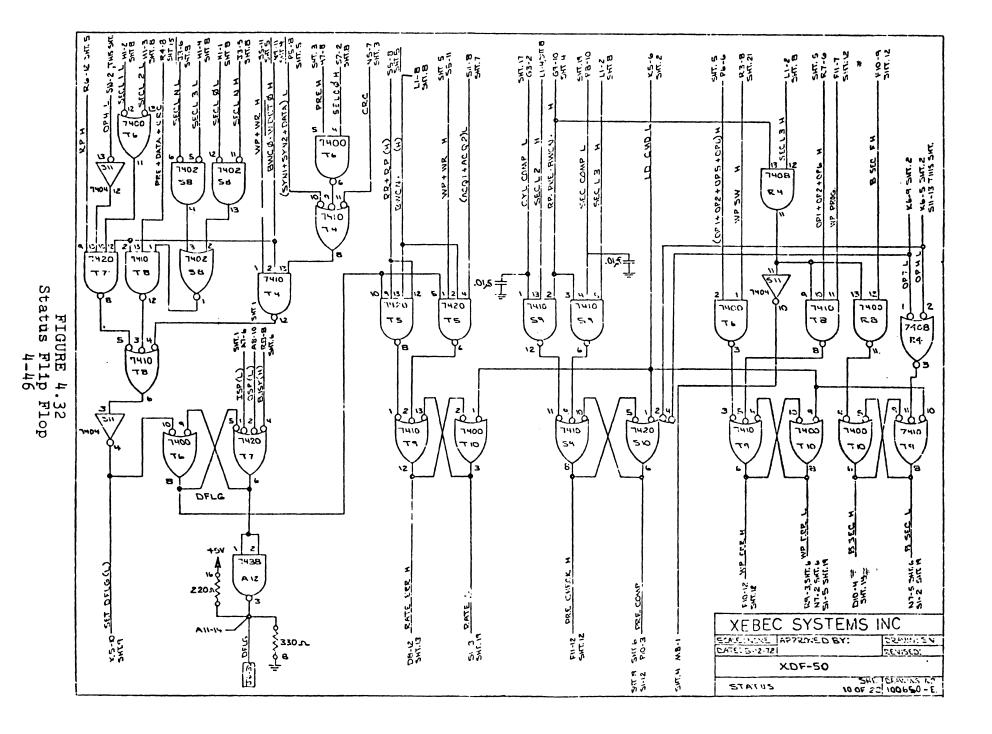

The status bits are shown in Figures 4.32 and 4.33. These status bits indicate the following error conditions within the disk formatter:

- A) Rate Error

- B) Preamble Compare Error

- C) Write Protect Error

- D) Bad Sector Flag

- E) Format Error

- F) Time Out Error

- G) Cylinder Address Error

- H) Not Operational

In addition, there is also a CRC error bit input to the status register, but that error condition is discussed under the CRC Register section of this manual.

## 4.4.1 Rate Error

A Rate Error is generated when the disk formatter does not receive a response to a data flag within one word time. If the reset signal is not received within the specified time, the disk unit will have missed a word and an error bit will be input to the status register. A Rate Error will not terminate the operation. The logic equations are:

| Set Rate Error   | All Read Operations  | (RP+PR)•DFLG•<br>BWCN                                            |

|------------------|----------------------|------------------------------------------------------------------|

|                  | All Write Operations | $\frac{(WP+WR) \bullet (ACQ1+}{ACQ2}) \bullet DFLG \bullet BWCN$ |

| Reset Rate Error | All Operations       | OSP•RAB5 + MCLR                                                  |

<sup>4-47</sup>

## 4.4.2 Preamble Compare Error

A preamble compare error is generated when the cylinder or sector portion of the preamble do not compare with the values loaded into the cylinder address and command registers. This error terminates the operation. The logic equation for operation of this flip flop is as follows:

SET PREAMBLE COMPARE ERROR

CYL COMP•SEC L2• RP•PRE•BWCN +

SEC COMP•SEC L3• RP PRE•BWCN

**RESET PREAMBLE COMPARE ERROR**

MCLR + LD CMD + OP4 + OP7

In case of simultaneous set and reset, reset has priority.

4.4.3 Write Protect Error

The write protect error flip flop is enabled when a write operation is attempted on a write protected sector or disk unit. The logic equation for the setting or resetting of this flip flop is as follows:

SET WRITE PROTECT ERROR

WPSW•(OP1 + OP2 + OP5 + OP6) + WPROG• (OP1 + OP2 + OP6)\$ SEC L3•RP•PRE•BWCN

RESET WRITE PROTECT ERROR

MCLR + LD CMD

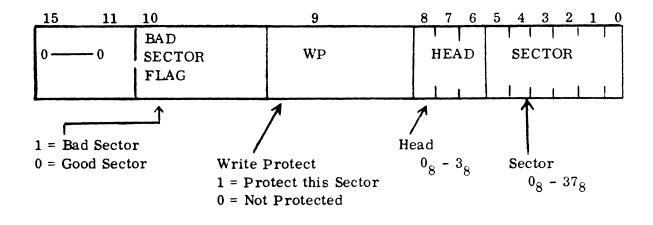

#### 4.4.4 Bad Sector Flag

A bad sector flag is generated when the bad sector flag bit is set in bit 10 of the second word of the preamble. An error bit is generated in the status register but the disk formatter operation is not terminated. The logic equation for the operation of this flip flop is as follows:

> SET BAD SECTOR FLAG = BSECF·SECL3·RP·PRE·BWCN RESET BAD SECTOR FLAG = OP7 + OP4 + LD CMD + MCLR

The bad sector flag logic is designed so that when a set and reset condition is on the flip flop simultaneously, the reset side has priority over the set side.

## 4.4.5 Format Error

A format error is generated anytime the clean sector compare flip flop is still set when the next sector pulse is generated. See Figure 4.21.

This is usually caused by reading a sector with no data written on it or having a pack in the disk with smaller sectors than the formatter is configured for (e.g., putting a 24 sector<sub>pack</sub> in a drive tied to a 16 sector formatter). A format error terminates operation in the formatter.

The logic equation for the set and reset condition of this flip flop is as follows:

| SET FORMAT ERROR   | BUSY•SEC PULSE•CLEAN<br>SECTOR COMPARE |

|--------------------|----------------------------------------|

| RESET FORMAT ERROR | MCLR + LD CMD                          |

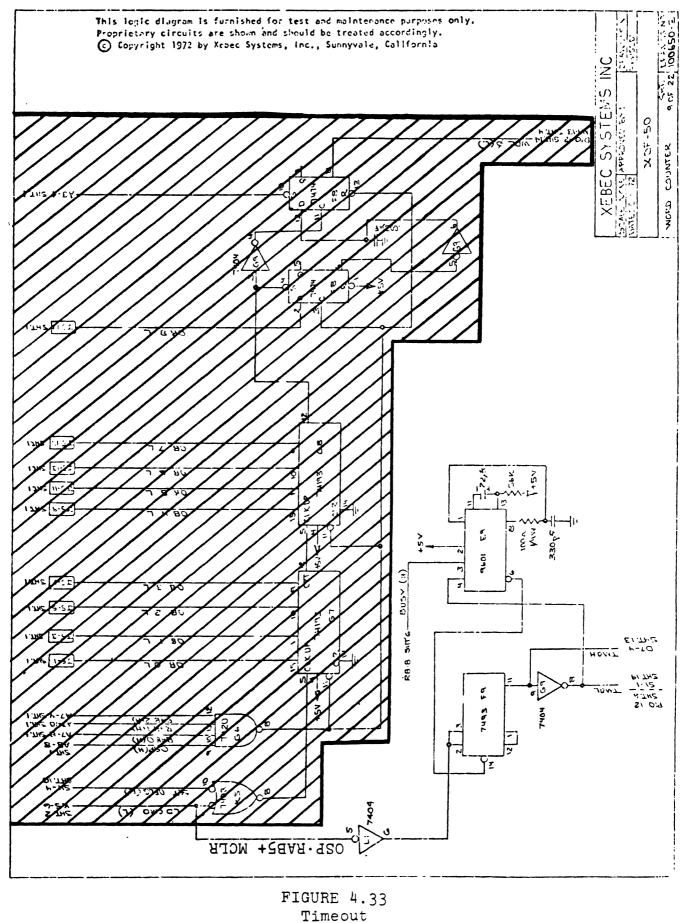

## 4.4.6 <u>Time Out Error</u>

A time out error is generated when an invalid sector number is selected or when the disk formatter does not go NOT BUSY within about two seconds and the operation is not complete. An error bit is input to the status register and the operation is terminated. The logic for the time out error is shown in Figure 4.33.

#### 4.4.7 Cylinder Address Error

A cylinder address error is generated in the <u>disk drive</u> when a cylinder address that exceeds the selected disk unit is loaded into the cylinder address register. This error is gated through the formatter, and terminates the current operation. The only way this error can be cleared is by:

- 1) Unloading the disk drive with the load/unload switch, or

- 2) Issuing a legitimate cylinder address to the drive.

## 4.4.8 Not Operational

A not operational status is generated in the disk drive when 1) the unit is not selected, 2) not on, 3) not up to speed, or 4) malfunctioning. This error is gated through the formatter and terminates the current operation.

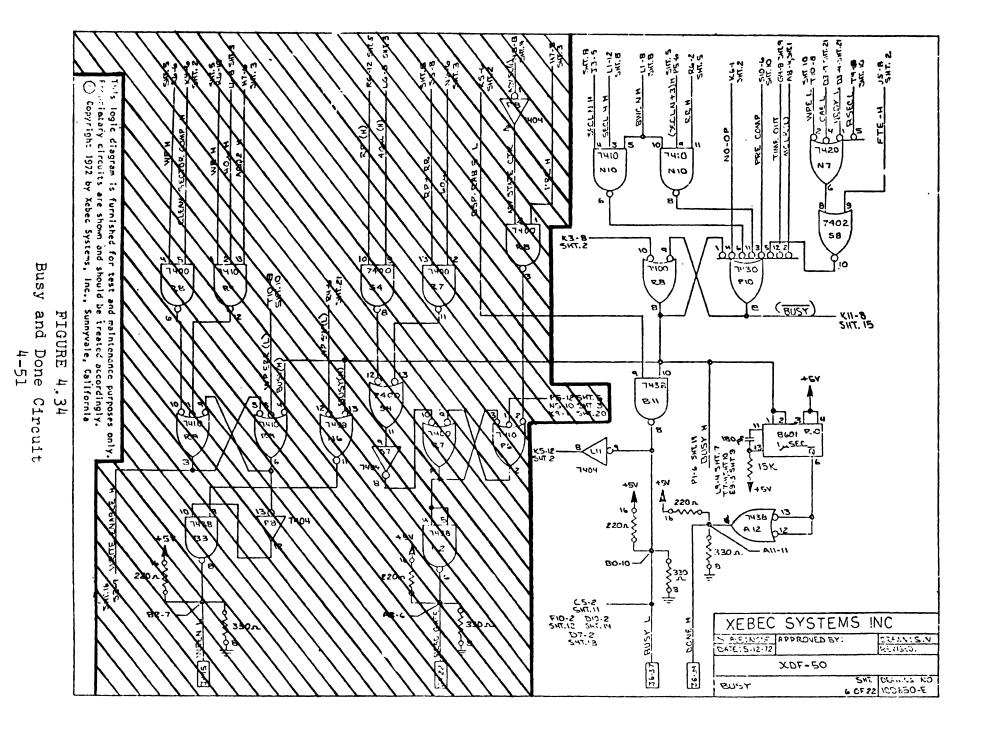

#### 4.5 BUSY

The BUSY circuit is shown in Figure 4.34. The loading of the Command Register sets the BUSY flip flop. The setting of this flip flop causes the Disk Formatter to wait until SEEK is complete, then the operation begins.

The BUSY signal indicates that the Disk Formatter is busy with an operation. When BUSY=1 there can be no transfers other than data over the CPOB or CPIB data busses.

| Function   | Operation                                        | Equation                                |

|------------|--------------------------------------------------|-----------------------------------------|

| Set BUSY   | All Operations                                   | LD CMD                                  |

| Reset BUSY | Read Operations                                  | RR•SECLN3•BWCN                          |

| Reset BUSY | Write Operations                                 | SECLN4 • BWCN                           |

| Reset BUSY | Premature Ter-<br>ininations caused<br>by Errors | PRECOM+CAE+NRD Y+<br>BSEC+WPROT+IIMEOUT |

| Reset BUSY | All Others                                       | MCLR+NO-OP                              |

#### LOGIC EQUATIONS FOR BUSY FLIP FLOP

#### 4.6 DONE

The DONE circuit is also shown in Figure 4.34. The DONE pulse is approximately 1 microsecond in duration, and indicates that the Disk Formatter has completed an operation. DONE occurs when BUSY goes from 1 to 0.

## 4.7 FORMAT AND DISK OPTIONS

## 4.7.1 Format Options

The sector format of the number of words of data on the disk can be modified by placing jumpers on a program plug located in H3. The format parameters are:

# of Bit Per Word. (12 or 16)

# of Words Per Sector

The allowable number of words per sector is a function of the number of sectors per revolution and the number of bits per word.

|                                 | Max. # of Words per Sector |     |     |     |    |

|---------------------------------|----------------------------|-----|-----|-----|----|

| Sector<br>Bits Size<br>Per Word | 8                          | 12  | 16  | 24  | 32 |

| 12                              | 256                        | 256 | 256 | 160 | 96 |

| 16                              | 256                        | 256 | 192 | 128 | 64 |

## 4.7.2 <u>Disk Options</u>

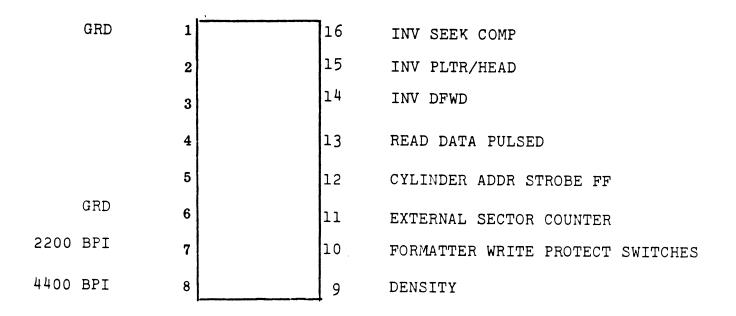

Various parameters of the disk interface signals are selectable by jumpers placed on program plugs located in M3.

These parameters are:

Output to Disk:

Polarity of disk select signal Polarity of head select signal Polarity of double frequency write data

Orientation of Jumpiers on Program Plug. Located in H3.

| Function               |                                                   | Jumper                                                                   |

|------------------------|---------------------------------------------------|--------------------------------------------------------------------------|

| Bits per<br>Word       | 12<br>16                                          | No jumper from pin 7-8<br>Jumper in from pin 7-8                         |

| Words<br>per<br>Sector | 32<br>64<br>96<br>125<br>160<br>192<br>224<br>256 | 1 - 2<br>1 - 3<br>1 - 4<br>1 - 5<br>1 - 10<br>1 - 13<br>1 - 12<br>1 - 13 |

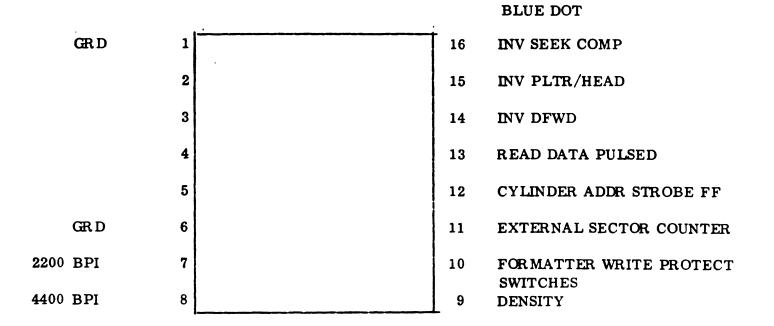

# DISK OPTIONS (XDF-50 Artwork Revision E and Above)

## ORIENTATION OF JUMPERS ON PROGRAM PLUG LOCATED DN-M 3

FUNCTION

JUMPERS

| Disk Packing Density        | 6-8 Must Be On All XDF-50 |

|-----------------------------|---------------------------|

| Seek Select                 |                           |

| H=                          |                           |

| L=                          |                           |

| Platter/Head Select         |                           |

| H=Upper                     | 2-15                      |

| L=Lower                     |                           |

| Double Freq. Write Data     |                           |

| Pos. Edge                   | 3-14                      |

| Neg. Edge                   |                           |

| External Sector Counter     | 6-11                      |

| Internal Sector Counter     |                           |

| Read Data Pulsed            | 4-13                      |

| Read Data Level             |                           |

| Cyl Addr Strb Pulse         |                           |

| Cyl Addr Strb FF (Addr Ack) | 5-12                      |

| Formatter Write Protect Sw  | 7-10                      |

Input from Disks:

Polarity of SEEK complete Select internal or external sector counter Select type of read data - (Pulse or Level) Type of cylinder address strobe (Pulse or flip flop)

Disk Speed - 1500 RPM or 2400 RPM - Selected by crystal frequency 6.354 Mhz = 1500 RPM 10.000 Mhz = 2400 RPM

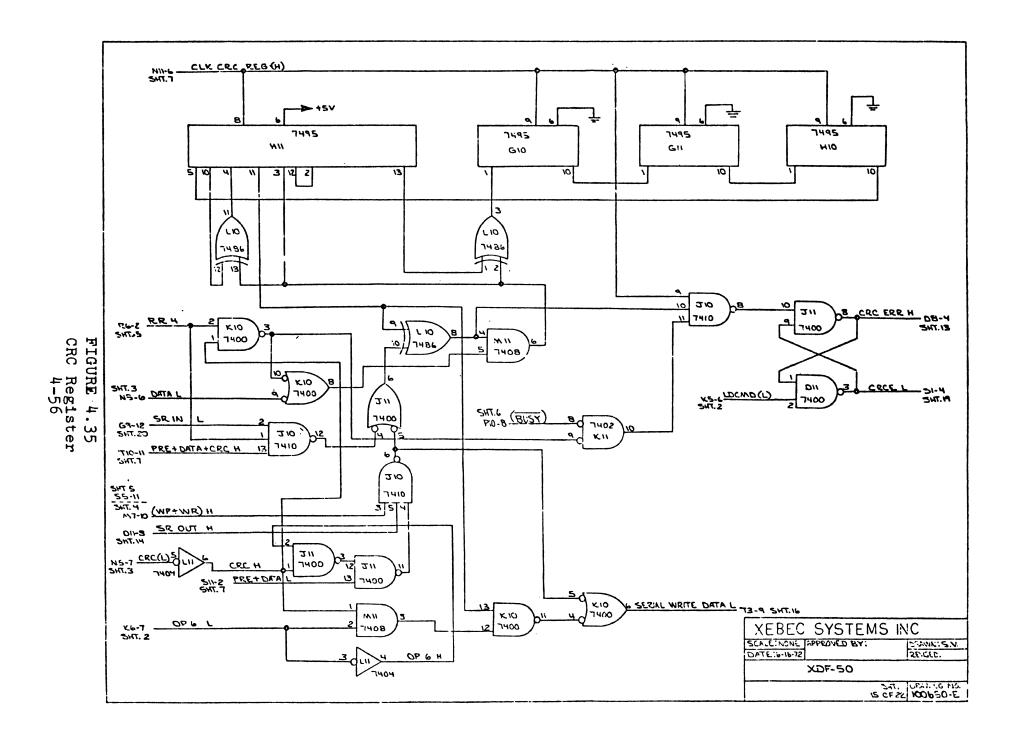

#### 4.8 CRC REGISTER

The Cyclic Redundancy Check (CRC) logic used to detect data errors within the XDF-50 Formatter is shown in Figure 4.35.

The CRC used is accumulated in a 16 bit shift register and is calculated on all data bits in the record portion of the sector. Note that the zero's fields, sync words, and preamble are excluded from the CRC calculation. It should also be noted that the CRC is maintained in a 16 bit register even if the data word is set to 12 bits or 16 bits in length. The CRC is actually calculated on the collection of serial data recorded on the disk and the resulting CRC stored serially after the data field.

The checking polynomial used is  $1+x^2+x^{15}+x^{16}$ .

For encoding, the serial data is entered at the high order end of the CRC register while the contents of the register is shifted toward the high order end. When the last bit of the serial data is entered, the calculated CRC is contained in the shift register. The data is shifted through the CRC register and then recorded on the disk.

When the data is read back, the CRC is calculated on the serial data from the disk as before. When the last data bit has been entered, the calculated CRC is again contained in the CRC register. The next 16 bits to be entered are the CRC calculated during the write cycle. As they are entered into the CRC register, the bits are compared one at a time to verify equality of the previously calculated and stored CRC to the currently calculated CRC. If equality exists, the CRC error flip flop is not set. If any set of bits differ, the CRC error flip flop is set and the error status reported through the status word.

## Table 4.4

Logic Equation For CRC Register

Condition (Figure 4.35)

.

Serial Write Data

$(WP + WR) \cdot PRE + DATA) + (OP6 \cdot CRC)$

SR OUT + CRC Register (OP6. CRC)

## SECTION 5 INSTALLATION/SHIPPING

This section describes the procedures for unpacking, setting up and connecting the XDF-50 Formatter. Also described is the procedure for packing the unit if it is to be shipped.

#### 5.1 UNPACKING

- A. Cut tape securing top end of box with a knife, being careful not to cut any deeper than is required to cut tape.

- B. Remove and save manual which is taped to top of inner box.

- C. Cut tape securing top of inner box with knife, being careful to cut only the tape and not the box.

- D. Remove and save foam pad inside inner box.

- E. Pull XDF-50 Formatter chassis by grasping edges of front panel casting and pulling straight up. It may be necessary to have someone else hold the box while the chassis is being removed.

- F. Replace all foam pads, cardboard laminations, plastic sheets and other packing materials in the box and save. If unit is to be shipped again such as for factory service it must be shipped in this container to avoid shipping damage. See Section 5.7 for packing instructions.

#### 5.2 INSPECTION

- A. Remove formatter from plastic sack and visually inspect for shipping damage. If any shipping damage is noted, contact <u>Shipping Carrier</u> immediately to file insurance claim.

- B. Remove top cover from formatter chassis by loosening screws on both sides. It is not necessary to remove these screws to lift cover.

- C. Check inside of formatter to see that screws and standoffs securing P.C. card are snug that dc power connector is in place.

D. If unit is to be used on 115 VAC, the unit has been properly configured at factory. Replace cover and proceed to paragraph 5.4.

If unit is to be used on 230V, change power strapping per paragraph 5.3.

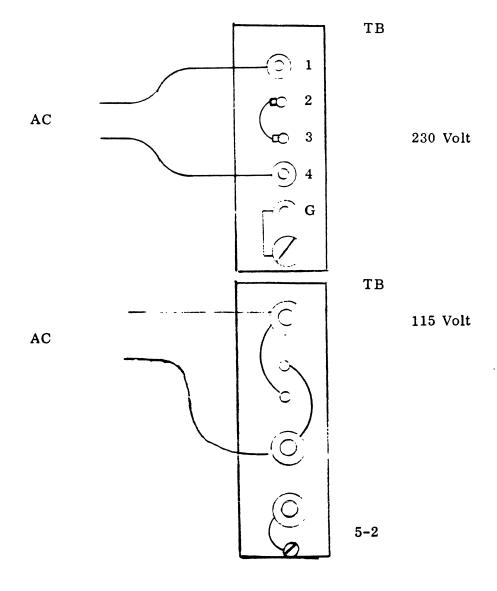

## 5.3 230 VOLT OPERATION

The formatter is normally set for 115 volt operation at the factory. If 230 volt operation is required, the transformer taps must be changed. The diagrams below indicate the proper settings.

The procedure for setting transformer taps is:

- A. Remove top cover of formatter.

- B. Remove P.C. card(s) by removing screws and unplugging dc power connector.

- C. Remove AC filter mounted over TB at rear of power supply.

- D. Set jumpers on AC input connector at rear of power supply as below:

- E. Replace P.C. Card(s) and DC Power Connector (s), tighten screws securing P.C. Card(s) finger tight.

- F. Replace top cover.

## 5.4 PRELIMINARY TEST

This test verifies that the power supply is operational and that the DC is connected to the logic card.

After it has been ascertained that the power supply is configured for the correct AC voltage, plug in the power cord at the back of the formatter chassis, and connect the power plug to the appropriate AC outlet. Do not connect any other cables to the formatter. Switch on the AC power switch located on the front panel. The red error light should come on indicating that the power supply is operational. If the light does not come on, either:

- A. AC fuse is blown (rear of chassis)

- B. DC fuse is blown (internal to power supply)

- C. DC connector not plugged onto card.

- D. Lamp is defective.

- E. Power supply is defective.

- F. Power supply is out of adjustment (See 5.4.1 below)

#### 5.4.1 DC Voltage Adjustment

The DC power output should be set to  $5.0 \pm .2$  volts. A potentiometer which adjusts DC voltage is located on the regulator card. The voltage should be set initially with the connector disconnected from the card and the voltage measured at the DC terminal block.