# Tape Dimension IV Tape Controller User's Manual

# Tape Dimension IV Tape Controller User's Manual

14511 New Myford Road Tustin California 92680

Phone: (714) 730-6250 Telex: 4720629 WESPER Cable: WESPER

PRINTED IN U.S.A.

P91001164 09/13/84

(This page intentionally left blank.)

#### PREFACE

This User's Manual provides information necessary for the installation and operation of the Western Peripherals TAPE DIMENSION IV Tape Adapter, used with the DEC PDP-11 and VAX-11 family of Unibus-equipped computer systems.

The manual is divided into the following sections:

Section II Installation

Section III Programming

Section IV Computer Interface

Section V Pertec-Compatible

Formatter Interface

Section VI STC & Telex

Formatter Interfaces

Section VII NRZI and PE Tape Formats

Section VIII GCR Tape Format

# RELATED DOCUMENTS

| ANSI X3.22          | American National Standard:<br>Recorded Magnetic Tape for Information<br>Interchange (800 CPI, NRZI)                                        |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| ANSI X30.39-1973    | American National Standard:<br>Recorded Magnetic Tape for Information<br>Interchange (1600 CPI, Phase Encoded)                              |

| ANSI X3.40-1973     | American National Standard:<br>Unrecorded Magnetic Tape for Information<br>Interchange (9-track 200 and 800 CPI, NRZI;<br>and 1600 CPI, PE) |

| ANSI X3.54-1976     | American National Standard:<br>Recorded Magnetic Tape for Information<br>Interchange (6250 CPI, GCR)                                        |

| DEC                 | Unibus Protocol                                                                                                                             |

| DEC EK-OTS11-UG-001 | TS-11 Subsystem User's Guide                                                                                                                |

## SECTION I

# GENERAL DESCRIPTION

(This page intentionally left blank.)

# SECTION I - GENERAL DESCRIPTION

## TABLE OF CONTENTS

| ARAGRAPH PA                       | AGE |

|-----------------------------------|-----|

| NTRODUCTION                       | 1-1 |

| MULATION - SOFTWARE COMPATIBILITY | 1-1 |

| ARDWARE COMPATIBILITY             | 1-1 |

| APE UNIT OPERATION AND INTERFACE  | 1-1 |

| ACHE BUFFER                       | 1-2 |

| RROR HANDLINR                     | 1-2 |

| APE FORMATS                       | 1-3 |

| ATA BLOCK SIZE                    | 1-3 |

| PECIFICATIONS                     | 1-4 |

(This page intentionally left blank.)

## SECTION I

## GENERAL DESCRIPTION

## INTRODUCTION

The Western Peripherals TAPE DIMENSION IV Tape Controller emulates Digital Equipment Corporation (DEC) Model TS-11 Tape Subsystems. This Group Code Recording tape controller/coupler, containing 64K bytes of on-board data buffering to facilitate start/stop functionality on streaming tape drives. Contained on a single standard-sized hex-wide printed circuit board, the Tape Dimension-IV is compatible with the DEC PDP-11 and VAX-11 family of computer systems and interfaces with these processors via a standard Unibus slot.

The Tape Dimension IV provides the interface for a tape subsystem using industry-compatible formatted start/stop and streaming drives with dual density (NRZI/PE) or tri-density capavility, which includes the 6250 bit per inch (bpi) Group Code Recording (GCR) format. The on-board data buffer allows the TD-IV to emulate operation of the the DEC TS-11 start/stop tape subsystem, while fully supporting streaming tape drives. It also takes advantage of bus speeds without concern for data late conditions, even at fast data rates on a highly populated peripheral bus, while remaining transparent to standard DEC software.

## EMULATION - SOFTWARE COMPATIBILITY

The Tape Dimension IV is compatible with DEC operating systems that can support TS-11 tape subsystems. The controller uses these standard TS-11 registers and vector to simplify the system interface, and since the controller is fully buffered, it is immune to data late conditions, even when operating with high speed disk drives. Alternate TS-11 register addresses and vectors are also available via simple switch selection.

## HARDWARE COMPATIBILITY

The Tape Dimension IV interfaces the DEC PDP-11 or VAX-11 system processor via the Unibus. The hex-wide TD-IV board mounts inside the cabinet of the host computer and plugs directly into an available SPC slot in its Unibus.

## TAPE UNIT OPERATION AND INTERFACE

The Tape Dimension IV supports the industry-standard tape drive interface as well as the special interfaces and other requirements to run GCR and other formats on STC and Telex tape drives.

Standard 50-conductor "A" and "B" formatter interface cables are used to connect Pertec-compatible tape drives to the controller through two connectors at the top edge of the controller board. Two additional connectors are also available for the STC/Telex interface. Various drive types are supported, including drives operating in the PE, NRZI and/or GCR format. Contact your Western Peripherals representative or the Western Peripherals Marketing department for a list of drives which are compatible with the TD-IV.

## CACHE BUFFER

The 64 KByte data buffer contained on the TD-IV board acts as a cache for data being transmitted between the host and the formatter in the tape drive. After fetching the first record, the controller initiates a write operation on the drive and waits for the next command from the host. If the next command is also a Write, the controller will fetch and store the next block of data in its buffer. The controller will continue to accept data until the 64 KByte data buffer is full.

As data is written to tape, space becomes available in the buffer, and the controller will accept more data. Should data transfer operations be suspended momentarily, data in the buffer will maintain the drive in the streaming mode, reducing the amount of repositioning activity required by the drive. The maximum transfer rate for streaming operations is 750 KBytes per second.

Because data is always transferred as complete blocks through the buffer, the controller remains immune to data late conditions. This provides flexibility in assigning priorities on the bus without regard to bus grant late errors no matter how busy the host bus may be.

#### ERROR HANDLING

A switch-selectable feature allows the Tape Dimension IV to handle Write errors on the controller board. Any routine Write errors resulting from bad tape are corrected by automatic retries. No host computer intervention is required, saving valuable computer time.

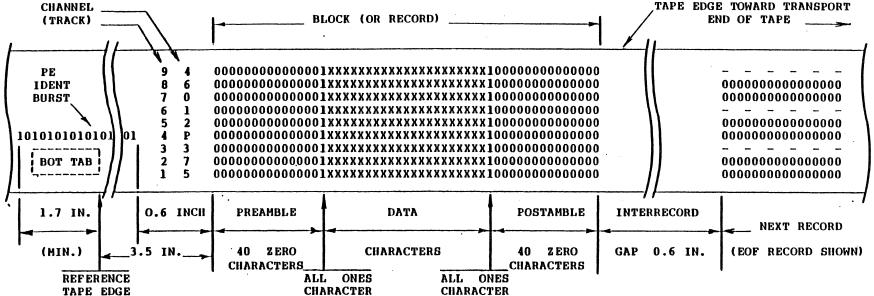

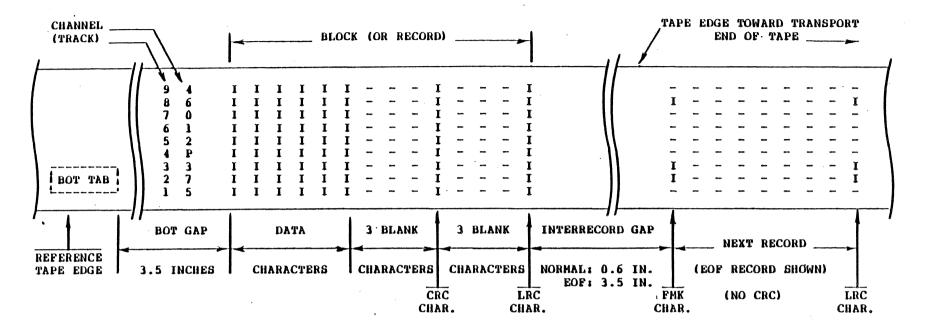

## TAPE FORMATS

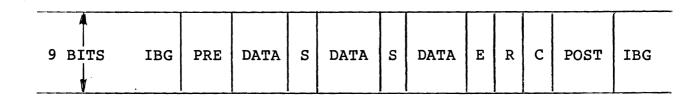

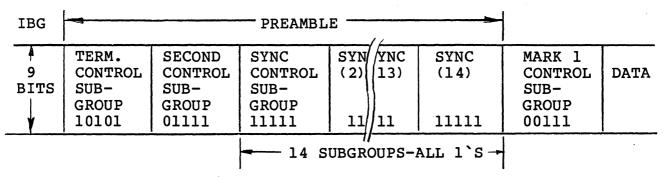

Group Code Recording (GCR) is featured by the TD-IV, allowing the user to take advantage of this modern high density recording technology. All data and control characters are recorded in groups and subgroups. Data groups contain error correcting characters for high data reliability. Each tape block contains preamble and postamble groups as well as ending data, control, and CRC groups. Resynchronization groups are also provided if the data block is longer than 1112 bytes.

The controller also uses the standard nine track 1600 bit per inch (bpi) phase encoded and 800 bpi NRZI tape formats. In PE, each tape block contains a 41 character preamble of 40 tape characters with all-zero bits followed by one character of all-one bits. The preamble is followed by the data field which also contains an odd parity bit for each data character. Following the data field is the postamble, which is the mirror-image of the preamble.

Like PE, the data field of the NRZI format contains an odd parity bit for each data character. Following the data field are the Cyclic Redundancy Check (CRC) and Longitudinal Redundancy Check (LRC) characters to ensure data integrity.

## DATA BLOCK SIZE

Although the recommended maximum is 2K to 4K, the maximum data block size is only limited by the Byte/Record Count word to a full 64K byte block. While the controller can handle a single-byte tape block, the minimum recommended data block size can vary from system to system where the generated tapes will be used.

## **SPECIFICATIONS**

## COMPUTER INTERFACE - SOFTWARE

PDP-11 Interface Protocol -

DEC TS-11

Emulation -

One DEC TS-11 subsystem

Unibus Register Addressing Assignments -

Standard =  $772520_8$ ,  $772522_8$  (TSDB/TSBA, TSSR)

Optional= 7700008-7777608 (TSDB/TSBA register, in modulo 408 increments, via option switches).

Unibus Interrupt Vector -

Standard = 224 (octal)

Optional = 0 - 377 (via option switches).

PDP-11 Bus Level -

Bus level 4, 5, 6, or 7; (level 5 is standard).

## COMPUTER INTERFACE - HARDWARE

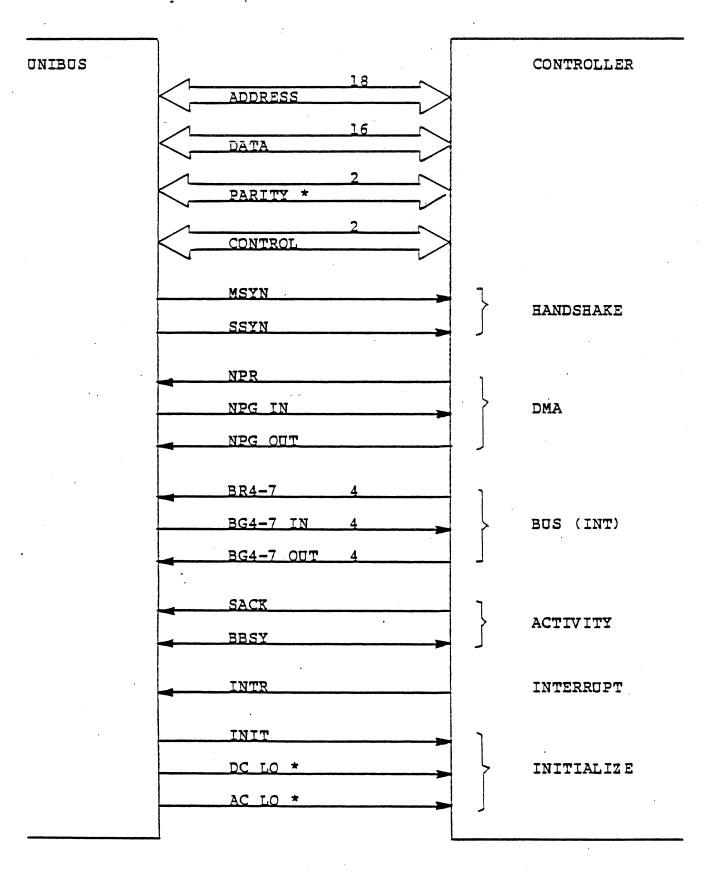

Unibus interface -

(fits in a standard Unibus SPC slot).

Bus Loading -

One standard Unibus load.

DMA Addressing -

18 bits

Buffering -

64 Kbytes (read and write)

DMA Unibus Transfer Time (bus efficiency) -

Averages 1 us/word Read and Write (BBSY time).

## TAPE DRIVE INTERFACE

Formatter Interface (Start-Stop or Streaming operation) -

Pertec-compatible NRZI/PE/GCR Formatter (Pertec, CDC, Kennedy, Cipher, Ampex, etc.) or STC/Telex-compatible formatter.

Formatted Tape Drive Protocol -

Industry (Pertec) Standard for formatted drive. STC/Telex drives have a different interface, described later.)

Number Of Drives -

One tape drive

Tape Interface Cabling -

Two 50 cond. 3M-type ribbon cables (Pertec-compatible)

Two 60 conductor 3M-type ribbon cables (STC/Telex)

Telex drives require a special cable adapter board

Recording Formats -

6250 BPI per ANSI X3.54 1600 BPI per ANSI X3.39 800 BPI per ANSI X3.22

Tape Transfer Rate -

Over 1 mb/sec. with single-record buffering. Operation with Cache Buffer. - 0.75 mb/sec.

## SELF-TEST FEATURE

Provides a full basic test of controller's internal processor and storage to assure reliable operation every time power is applied to the system.

SIZE One Standard PDP-11 Hex-wide PC Board

POWER +5 volts (5% tolerance) @ 7.0 amps power consumption (maximum).

## **ENVIRONMENT**

Operating temperature 0 to 55 degrees Celsius

Storage temperature -10 to 70 degrees Celsius

Relative humidity 10% to 90% (without condensation)

(This page intentionally left blank.)

# SECTION II

## INSTALLATION

(This page intentionally left blank.)

# SECTION II - INSTALLATION

# TABLE OF CONTENTS

| PARAGRAPH                               | PAGE |

|-----------------------------------------|------|

| INTRODUCTION                            | 2-1  |

| JNPACKING AND INSPECTION                | 2-1  |

| PREPARATION                             | 2-1  |

| CONFIGURATION SELECTIONS                | 2-3  |

| Jnibus Address Selection                | 2-3  |

| Vector Address Selection                | 2-4  |

| Bus Level Selection                     | 2-5  |

| Orive-Type Switch Settings              | 2-6  |

| Multiple Subsystems                     | 2-6  |

| Additional Feature Selection            | 2-7  |

| TAPE DIMENSION IV BOARD INSTALLATION    | 2-7  |

| INTERCONNECTIONS                        | 2-8  |

| Telex Adapter Installation Instructions | 2-8  |

| SELF-TEST                               | 2-13 |

| CHECKOUT                                | 2-13 |

# LIST OF ILLUSTRATIONS

| FIGUR | <u>PAGE</u>                                                              |

|-------|--------------------------------------------------------------------------|

| 2-1   | Tape Dimension IV Board Illustration 2-2                                 |

|       | LIST OF TABLES                                                           |

| TABLE | PAGE                                                                     |

| 2-1   | Standard Unibus Address Selection (Switch Module 8B) 2-3                 |

| 2-2   | Standard Interrupt Vector Selection (Switch Module 1B) 2-4               |

| 2-3   | Bus level Selection 2-5                                                  |

| 2-4   | Drive-Type Switch Settings (Switch Module 16E) 2-6                       |

| 2-5   | Unit Select (Switch Module 6B) 2-6                                       |

| 2-6   | Feature Selection 2-7                                                    |

| 2-7   | Pin Assignments for Pertec-compatible Formatter Interface (Connector J3) |

| 2-8   | Pin Assignments for Pertec-compatible Formatter Interface (Connector J4) |

| 2-9   | Pin Assignments for STC/Telex Interface (Connector J1) 2-11              |

| 2-10  | Pin Assignments for STC/Telex Interface (Connector J2) 2-12              |

| 2-11  | Self-Test Indications 2-13                                               |

| 2-12  | Failing Memory Chip Look-Up Table 2-13                                   |

## SECTION II

## INSTALLATION

## INTRODUCTION

This section provides information required to configure and install the Western Peripherals TAPE DIMENSION IV Magnetic Tape Controller in a DEC VAX/PDP-11 computer system. The TD-IV consists of one standard hex-wide printed circuit board which plugs into a standard SPC backplane in the computer mainframe or expansion chassis. One cable set is provided for interconnecting the controller to the drive's formatter. (An adapter is provided to interface the Telex formatter.) An optional diagnostic tape is available (P/N P68000280) and a A User's Manual is included with each controller.

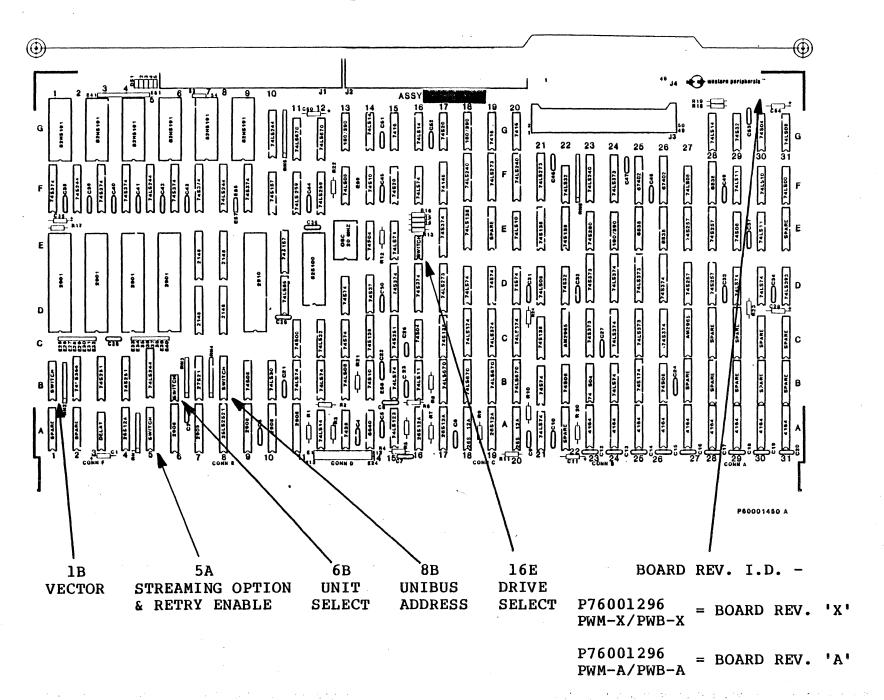

The installation information in this section applies to standard TAPE DIMENSION IV assembly number P60001450-010, Revision 'X' or 'A'. If your board has a different part number, contact Western Peripherals for information concerning the proper installation of your controller board.

## UNPACKING AND INSPECTION

After removal of the controller board and associated components from the shipping container, visually inspect them for physical damage. Check off each item on the enclosed packing list. In case of damage, retain all packaging material and notify the carrier to make a report. Always ensure all minor parts and small items are accounted for before discarding any shipping material.

## PREPARATION

Determine the position in the computer where the controller is to be installed. Remember that its physical location in the system determines its bus priority within the specified bus level. You may subsequently want to adjust the position of the devices on the bus to take advantage of the priority structure of the bus to minimize or eliminate bus grant late errors in the other various devices in the system. The TD-IV remains immune to data late errors.

Refer to the appropriate tape drive manual to install the tape drive. The drive must be prepared and the processor checked out before the controller can be expected to operate properly.

Figure 2-1 Tape Dimension IV Board Illustration

Assembly Number P60001450 Layout

INSTALLATION

## CONFIGURATION SELECTIONS

## Unibus Address Selection

Unibus address bits 4 through 11 for the controller registers are switch selectable. These bits are controlled by switch toggles 1 through 8 of the switch module at location 8B on the controller board. Placing a switch toggle in the ON position selects a binary 0 while placing it in the OFF position, selects a binary 1 in its respective bit position.

The switch settings required to set up the standard Unibus addresses (772520 and 772522) are illustrated in Table 2-1. The switches are arranged differently for board revisions 'X' and 'A', so check your board revision (upper right-hand corner of board). The table has instructions for both versions.

| OCTAL              | 7      |        | 7 7 |    | 2  |    | 5  |    | 2  |         | 0-2 |            |       |    |    |    |    |    |

|--------------------|--------|--------|-----|----|----|----|----|----|----|---------|-----|------------|-------|----|----|----|----|----|

| BIT                | 17     | 16     | 15  | 14 | 13 | 12 | 11 | 10 | 09 | 08      | 07  | 06         | 05    | 04 | 03 | 02 | 01 | 00 |

| BINARY             | 1      | 1      | 1   | 1  | 1  | 1  | 0  | 1  | 0  | 1       | 0   | 1          | 0     | 1  | 0  | 0  | X  | 0  |

| SWITCH #<br>REV. A |        |        |     |    |    |    | 5  | 4  | 6  | 3       | 7   | 2          | 8     | 1  |    |    |    |    |

| SWITCH #<br>REV. X |        | D7117D |     |    | 1  | 8  | 2  | 7  | 3  | 6       | 4   | 5          | rini. | rm |    |    |    |    |

| "ON"               | FIXED  |        | Х   |    | Х  |    | Х  |    | X  | 1 1 - 1 |     | *          |       |    |    |    |    |    |

| "OFF"              | VALUES |        |     | ,  | Х  |    | X  |    | X  |         | Х   | LECT<br>** |       |    |    |    |    |    |

<sup>\*</sup> Register-determined Values

Table 2-1 Standard Unibus Address Selection (8B)

<sup>\*\*</sup> See Table 2-5

## Vector Address Selection

The interrupt vector address for the drive is selected by positioning the switch toggles of the switch module at location 1B on the controller board. Switch toggles 1 through 6 control bits 02 through 07. (Bits 00 & 01 are allways 0) Placing a switch toggle in the ON position selects a binary 1 while placing it in the OFF position selects a binary 0 in its respective bit position.

The switch settings required to set up the standard drive interrupt vector address (224) are illustrated in Table 2-2.

| OCTAL    | 2 |   |   | 2 |   |   | 4 |   |

|----------|---|---|---|---|---|---|---|---|

| BINARY   | 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 |

| SWITCH # | 6 | 3 | 2 | 1 | 4 | 5 |   |   |

| ON       | X |   |   | Х |   | Х |   |   |

| OFF      |   | Х | Х |   | Х |   |   |   |

Table 2-2 Standard Interrupt Vector Selection (1B)

## Bus Level Selection

By placement of jumpers in accordance with Table 2-3, any of bus levels 4, 5, 6 or 7 can be selected. Level 5 is standard. These jumpers are located at the bottom of the board near Connector D.

| JUMPER      |         | BUS LEVEI |         |         |

|-------------|---------|-----------|---------|---------|

| CONNECTIONS | 4       | 5         | 6       | 7       |

| E01-E13     | INSTALL | REMOVE    | REMOVE  | REMOVE  |

| E02-E14     | INSTALL | REMOVE    | REMOVE  | REMOVE  |

| E03-E15     | REMOVE  | INSTALL   | REMOVE  | REMOVE  |

| E04-E16     | REMOVE  | INSTALL   | REMOVE  | REMOVE  |

| E05-E17     | REMOVE  | REMOVE    | INSTALL | REMOVE  |

| E06-E18     | REMOVE  | REMOVE    | INSTALL | REMOVE  |

| E07-E19     | REMOVE  | REMOVE    | REMOVE  | INSTALL |

| E08-E20     | REMOVE  | REMOVE    | REMOVE  | INSTALL |

| E09-E21     | INSTALL | REMOVE    | REMOVE  | REMOVE  |

| E10-E22     | REMOVE  | INSTALL   | REMOVE  | REMOVE  |

| E11-E23     | REMOVE  | REMOVE    | INSTALL | REMOVE  |

| E12-E24     | REMOVE  | REMOVE    | REMOVE  | INSTALL |

| E13-E14     | REMOVE  | INSTALL   | INSTALL | INSTALL |

| E15-E16     | INSTALL | REMOVE    | INSTALL | INSTALL |

| E17-E18     | INSTALL | INSTALL   | REMOVE  | INSTALL |

| E19-E20     | INSTALL | INSTALL   | INSTALL | REMOVE  |

Table 2-3 Bus level Selection

## Drive-Type Switch Settings

The switch module on the controller at location 16E must be set according to the type of drive connected to the controller and the mode of operation. Table 2-4 identifies the correct switch settings for each drive-type.

|                              |           | witch Pach Togg |       |            |

|------------------------------|-----------|-----------------|-------|------------|

| Drive/Interface Type:        | 1         | 2               | 3*    | 4          |

| STC Drive<br>Telex Drive     | On        | Off             |       | Off<br>Off |

| Pertec-type Start/Stop Drive | On<br>Off | On<br>Off       |       | On         |

| Pertec-type Streaming Drive  | Off       | Off             | ***** | Off        |

<sup>\*</sup> Location 5A, Switch 3 is explained in Table 2-6.

Table 2-4 Drive-Type Switch Settings (16E)

## Multiple Subsystems

When more than one TS-11 subsystem must be installed in the computer system, the TD-IV can be addressed as UNIT-0, UNIT-1, UNIT-2, or UNIT-3 by switch settings, via a 4 position switch labeled 6B. See Table 2-5; (only one unit may be selected).

|        | Swi        | tch P     | ositi     | on: |

|--------|------------|-----------|-----------|-----|

| Unit # | 4          | 3         | 2         | 1   |

| 0      | ON         | OFF       | OFF       | OFF |

| 1<br>2 | OFF<br>OFF | ON<br>OFF | OFF<br>ON | OFF |

| 3      | OFF        | OFF       | OFF       | ON  |

Switch Pack 6B

Table 2-5 Unit Select (6B)

## Additional Feature Selection (Switch 5A)

The switch pack at location 5A is used to configure the controller for additional features. The Cache Buffer feature (Switch 5A-3 and Switch 16E-3) optimizes operation with streaming tape drives. Table 2-6, below, lists the features and their appropriate switch settings.

| Switch               | Feature                                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------|

| 5A-1 OFF*<br>5A-1 On | Internal Automatic Retries (on hard errors only). Retries Disabled.                                                  |

| 5A-2 Off<br>5A-2 ON* | CDC Keystone drives (disables automatic speed selection). Normal operation (enables automatic speed selection).      |

| 5A-3 Off<br>5A-3 ON* | Single-block buffering enabled (Switch 16E-3 must also be off). Cache buffer enabled (Switch 16E-3 must also be on). |

| 5A-4 OFF*<br>5A-4 On | Internal Automatic Retries (on correctable errors only). Retries Disabled.                                           |

<sup>\*</sup> Recommended standard switch settings.

Table 2-6 Feature Selection

## TAPE DIMENSION IV BOARD INSTALLATION

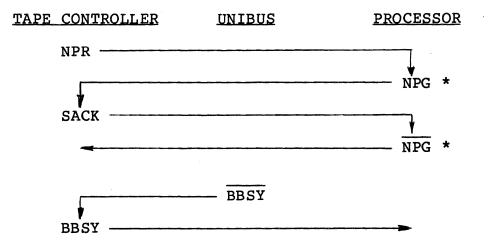

The DMA Non-Processor Grant and Bus Grant lines are daisy-chained from one backplane connector to the next. To maintain continuity, unused backplane connector slots are usually jumpered with a jumper card and/or a jumper wire.

The Bus Grant jumper card is installed in the D connector of unused slots. Western Peripherals supplies part number P01310093 for this purpose. The DMA Non-Processor Grant jumper is connected between pins Al and Bl on the backside of the "C" connectors of unused slots.

Any open slots between the controller and the processor must have these jumpers installed. Be sure to check for (by continuity test) and remove the DMA Non-Processor Grant jumper wire from the backplane connector of the slot selected for controller installation.

Place the controller board into the selected slot in the backplane, being careful to insure that it seats properly. Check that the computer Unibus is properly terminated.

## INTERCONNECTIONS

Connections between the TD-IV and the formatter are completed via two cables supplied with the controller. When connecting the cables, be sure pin 1 (the triangle or arrow) on each plug is oriented to the triangle on the socket. You should check the manual for the tape drive to ensure proper connection at the drive.

For the <u>Pertec-compatible</u> formatter interface, these cables plug into 50-pin socket connector J3 and 50-pin edge connector J4 on the controller board. The pin assignments for these two connectors are listed in Tables 2-7 and 2-8. When connecting the cable to J3, be sure pin 1 (the triangle or arrow) on the plug is oriented to the triangle on the socket. When connecting the cable to edge-connector J4, be sure the red stripe on the cable is oriented to pin 1 (printed on the board next to the connector).

For an <u>STC or Telex</u> formatter interface, the ribbon cables plug into two 60-pin socket connectors, Jl and J2 on the controller board. The pin assignments for the two connectors Jl and J2 on the controller are listed in Tables 2-9 and 2-10. These tables also list the the pin assignments for the Telex formatter I/O connectors.

For an <u>STC</u> drive, the cable from Jl connects to connector B4 on the drive and the cable from J2 connects to connector A4 on the drive.

## Telex Adapter Installation Instructions

For a <u>Telex</u> formatter interface, a Telex/TD-IV Cable Adapter (assembly P60001245) is also supplied. The ribbon cables from Jl and J2 on the TD-IV plug into two 60-pin connectors on the Cable Adapter assembly and the connectors of the three 50-pin cables coming from the Cable Adapter assembly plug into three I/O connectors at the Telex formatter.

Installation of the Telex cable adapter is not difficult if you follow these simple steps. Be sure that the stripe on the cable and the arrow on the plugs match the pin 1 arrow on the board connectors. The cables to the Telex electronics are self-orienting and cannot be connected backwards.

- 1. Open the back door of the tape drive unit.

- 2. Mount the Telex Adapter Board on the cabinet rails using the hardware provided.

- 3. Connect the cables:

| TAPE | <b>DIMENSION</b> | IA | TELEX | <u>CABLE</u> | ADAPTER | <b>BOARD</b> |

|------|------------------|----|-------|--------------|---------|--------------|

|      |                  |    |       |              |         |              |

CABLE P1 CONNECTOR J1 CABLE P2 CONNECTOR J2

## TELEX CABLE ADAPTER BOARD TELEX DRIVE ELECTRONICS

| CABLE | P101 | CONNECTOR | I.O1 |

|-------|------|-----------|------|

| CABLE | P102 | CONNECTOR | I.O2 |

| CABLE | P103 | CONNECTOR | I.O3 |

Table 2-7 Pin Assignments for Pertec-compatible Formatter Interface (Connector J3)

| Signal<br>Pin      | Ground<br>Pin | TD-IV<br>Mnemonic | Formatter<br>Mnemonic |

|--------------------|---------------|-------------------|-----------------------|

| 2                  | 1             | FBSY              | FBY                   |

| 4                  | 2             | LBYT              | LWD                   |

| <b>4</b><br>6<br>8 | 5             | WRD03             | W4                    |

| 8                  | 7             | CMDCLK            | GO                    |

| 10                 | 9             | WRD07             | WO                    |

| 12                 | 11            | WRD06             | Wl                    |

| 18                 | 17            | CMD1              | REV                   |

| 20                 | 19            | REW               | REW                   |

| 22                 | 21            | WRDP              | WP                    |

| 24                 | 23            | WRD00             | W7                    |

| 26                 | 25            | WRD04             | W3                    |

| 27                 | 26            | WRD01             | W6                    |

| 30                 | 29            | WRD05             | W2                    |

| 32                 | 31            | WRD02             | <b>W</b> 5            |

| 34                 | 33            | CMD2              | WRT                   |

| 36                 | 35            | DS0               | LGP                   |

| 38                 | 37            | DSl               | EDIT                  |

| 40                 | 39            | CMD4              | ERASE                 |

| 42                 | 41            | CMD3              | WFM                   |

| 46                 | 45            | TA0               | TAD0                  |

| 48                 | 47            | RD05              | R2                    |

| 50                 | 49            | RD04              | R3                    |

Table 2-8 Pin Assignments for Pertec-compatible Formatter Interface (Connector J4)

| Signal<br>Pin | Ground<br>Pin | TD-IV<br>Mnemonic | Formatter<br>Mnemonic |

|---------------|---------------|-------------------|-----------------------|

| 1             | 5             | DP                | RP                    |

| 2 3           | 5<br>5        | RD07              | R0                    |

|               |               | RD06              | Rl                    |

| 4             | 5             | LP                | LDP                   |

| 6             | 5<br>5<br>7   | RD03              | R4                    |

| 8             |               | RD00              | R7                    |

| 10            | 9             | RD01              | R6                    |

| 12            | 11            | ERR               | HER                   |

| 14            | 13            | FM                | FMK                   |

| 16            | 15            | IDB               | IDENT                 |

| 18            | 17            | FEN               | FEN                   |

| 20            | 19            | RD02              | R5                    |

| 22            | 21            | EOT               | EOT                   |

| 24            | 23            | ESC1              | UNL                   |

| 28            | 27            | RDY               | RDY                   |

| 30            | 29            | RW                | RWD                   |

| 32            | 31            | FP                | FPT                   |

| 34            | 33            | RSTR              | RSTR                  |

| 36            | 35            | WSTR              | WSTR                  |

| 38            | 37            | DBSY              | DBY                   |

| 40            | 39            | ER1               | SPD                   |

| 42            | 41            | CERR              | CER                   |

| 44            | 43            | ONL               | ONL                   |

| 46            | 45            | TAl               | TADL                  |

| 48            | 47            | TA2               | TAD2                  |

| 50            | 49            | CMD0              | HISP                  |

Table 2-9 Pin Assignments for STC/Telex Interface (Connector J1)

TD-IV CONNECTOR J1

TELEX I/O CONNECTORS

|               |               |                   |                 |                   |                  | danadan dan dan dan dan dan dan dan dan |

|---------------|---------------|-------------------|-----------------|-------------------|------------------|-----------------------------------------|

| SIGNAL<br>PIN | GROUND<br>PIN | TD-IV<br>MNEMONIC | STC<br>MNEMONIC | TELEX<br>MNEMONIC | TELEX<br>ADAPTER | TELEX<br>CONNECTOR                      |

| Al            | Bl            | _                 | _               | _                 | _                |                                         |

| A2            | B2            | ER0               | ERMX-0          | ERROR 0           | PIO3-3           | IO3-2                                   |

| A3            | В3            | ERl               | ERMX-1          | ERROR 1           | PIO3-5           | 103-3                                   |

| A4            | B4            | ER2               | ERMX-2          | ERROR 2           | PIO3-7           | IO3-4                                   |

| A5            | B5            | ER3               | ERMX-3          | ERROR 3           | PIO3-9           | IO3 <b>-</b> 5                          |

| A6            | В6            | ER4               | ERMX-4          | ERROR 4           | PIO3-11          | 103-6                                   |

| A7            | В7            | ER5               | ERMX-5          | ERROR 5           | PIO3-13          | IO3-7                                   |

| A8            | B8            | ER6               | ERMX-6          | ERROR 6           | PIO3-15          | IO3-8                                   |

| A9            | в9            | ER7               | ERMX-7          | ERROR 7           | PIO3-17          | IO3-9                                   |

| Al0           | B10           | FBSY              | BUSY            | BSY               | PIO1-23          | 101-12                                  |

| All           | Bll           | DREQ              | TREQ            | DRQ               | PIO2-23          | IO2-12                                  |

| A12           | B12           | -                 | -               |                   | -                | _                                       |

| Al3           | B13           | IDB               | ID BURST        | IDS               | PIO2-37          | 102-19                                  |

| Al4           | B14           | OPI               | OPINC           | REV               | PIO1-41          | IO1-21                                  |

| A15           | B15           | DBSY              | ENDATP          | DBZ               | PIO2-21          | 102-11                                  |

| Al6           | B16           | FMT               | TMS             | FMK               | PIO2-43          | IO2-22                                  |

| Al7           | B17           | RJS               | REJECT          | REJ               | PIO1-27          | IO1-14                                  |

| A18           | B18           | OVR               | OVRNS           | OVR.              | PIO2-31          | IO2-16                                  |

| A19           | B19           | EM                | DATA CHK        | EM                | PIO1-49          | IO1-25                                  |

| A20           | B20           | RPE               | ROMPS           | RPE               | PIO1-39          | IO1-20                                  |

| A21           | B21           | CERR              | CRERR           | COR               | PIO2-35          | 102-18                                  |

| A22           | B22           | BLK               | BLOCK           | IBEN              | PIO2-19          | 102-10                                  |

| A23           | B23           | DD0               | NRZI            | DDS0              | PIO2-39          | 102-20                                  |

| A24           | B24           | DPE               | BUPER           | DPE               | PIO2-47          | 102-24                                  |

| A25           | B25           | ONL               | ONLS            | ONL               | PIO1-33          | IO1-17                                  |

| A26           | B26           | DD1               | HDENS           | DDS1              | PIO2-41          | 102-21                                  |

| A27           | B27           | RDY               | RDYS            | RDY               | PIO1-35          | 101-18                                  |

| A28           | B28           | -                 | -               | -                 | _                |                                         |

| A29           | B29           | CMD0              | _               | CMD0              | PIO1-7           | IO1-4                                   |

| A30           | B30           | TA2               | -               | TA2               | PIO1-5           | 101-3                                   |

Table 2-10 Pin Assignments for STC/Telex Interface (Connector J2)

TD-IV CONNECTOR J2

TELEX I/O CONNECTORS

| · · · · · · · · · · · · · · · · · · · |               |                   |                 |                   |                    |                    |

|---------------------------------------|---------------|-------------------|-----------------|-------------------|--------------------|--------------------|

| SIGNAL<br>PIN                         | GROUND<br>PIN | TD-IV<br>MNEMONIC | STC<br>MNEMONIC | TELEX<br>MNEMONIC | TELEX -<br>ADAPTER | TELEX<br>CONNECTOR |

| Al                                    | Bl            | TAO               | AD0             | TA0               | PIO1-1             | 101-1              |

| A2                                    | B2            | TAl               | ADl             | TAl               | PIO1-3             | IO1-2              |

| A3                                    | в3            | CMD1              | CMD0            | CMD1              | PIO1-9             | IO1-5              |

| A4                                    | B4            | CMD2              | CMD1            | CMD2              | PIO1-11            | IO1-6              |

| A5                                    | B5            | CMD3              | CMD2            | CMD3              | PIO1-13            | IO1-7              |

| A6                                    | В6            | CMD 4             | CMD3            | CMD4              | PIO1-15            | IO1-8              |

| A7                                    | в7            | DS0               | DS0             | -                 | GROUND             | IO1-9              |

| A8                                    | в8            | CMDCLK            | START           | CMD.CLK           | PIO1-25            | IO1-13             |

| A9                                    | в9            | LBYT              | STOP            | LBY               | PIO2-27            | 102-14             |

| A10                                   | B10           | DACK              | TRAK            | DAK               | PIO2-25            | 102-13             |

| All                                   | Bll           | WRDP              | DATA-P          | DP                | PIO2-17            | 102-9              |

| A12                                   | B12           | WRD07             | DATA-0          | D0                | PIO2-1             | 102-1              |

| A13                                   | B13           | WRD06             | DATA-1          | Dl                | PIO2-3             | 102-2              |

| Al4                                   | B14           | WRD05             | DATA-2          | D2                | PIO2-5             | 102-3              |

| A15                                   | B15           | WRD04             | DATA-3          | D3                | PIO2-7             | 102-4              |

| Al6                                   | B16           | WRD03             | DATA-4          | D4                | PIO2-9             | IO2-5              |

| A17                                   | B17           | WRD02             | DATA-5          | D5                | PIO2-11            | 102-6              |

| A18                                   | B18           | WRD01             | DATA-6          | D6                | PIO2-13            | IO2-7              |

| A19                                   | B19           | WRD00             | DATA-7          | D7                | PIO2-15            | IO2-8              |

| A20                                   | B20           | SRST              | RESET           | SYSRST            | PIO2-45            | 102-23             |

| A21                                   | B21           | ESC1              | SLXl            | ESC1              | PIO3-21            | 103-11             |

| A22                                   | B22           | ESC0              | SLX0            | ESC0              | PIO3-19            | 103-10             |

| A23                                   | B23           | DSl               | DSl             | DS1               | GROUND             | 101-10             |

| A24                                   | B24           | ESC2              | SLX2            | -                 | -                  | -                  |

| A25                                   | B25           | ERR               | SSC             | ERR               | PIO2-33            | 102-17             |

| A26                                   | B26           | OSC               | OSC             | OB                | PIO2-49            | 102-25             |

| A27                                   | B27           | EOT               | EOTS            | EOT               | PIO1-31            | 101-16             |

| A28                                   | B28           | LP                | BOTS            | $\mathtt{BOT}$    | PIO1-29            | 101-15             |

| A29                                   | B29           | FP                | FPTS            | $\mathtt{FPT}$    | PIO1-37            | 101-19             |

| A30                                   | B30           | RW 0              | REWS            | RWG               | PIO1-47            | IO1-24             |

## SELF-TEST

The TAPE DIMENSION IV uses its internal self-test firmware to verify the controller every time power is applied to the system. If no problem is detected, the LED indicators on the top edge of the board will be OFF. Table 2-11 lists other indications which define specific failures.

|     | LED | NUM | BER: |     |     |                             |

|-----|-----|-----|------|-----|-----|-----------------------------|

| 5   | 4   | 3   | 2    | 1   | HEX | TEST RESULT                 |

| -   |     |     |      |     |     |                             |

| OFF | OFF | OFF | OFF  | OFF | 0   | Self Test OK                |

| OFF | OFF | OFF | OFF  | ON  | 1   | Sequencer Failure           |

| OFF | OFF | OFF | ON   | OFF | 2   | ALU Test Condition Failure  |

| OFF | OFF | OFF | ON   | ON  | 3   | DBUS Test Condition Failure |

| OFF | OFF | ON  | OFF  | OFF | 4   | Static Memory Failure       |

| OFF | OFF | ON  | ON   | OFF | 6   | ALU Address Failure         |

|     | OFF |     | ON   | ON  | 7   | FIFO Failure                |

| ON  | X   | X   | X    | X   |     | Dynamic Memory Failure      |

|     |     |     |      |     |     | (See Table 2-12)            |

Table 2-11 Self-Test Indications

|     | LED | NUME | BER: |     |     |          |

|-----|-----|------|------|-----|-----|----------|

| . 5 | 4   | 3    | 2    | 1   | HEX | LOCATION |

|     |     |      |      |     |     |          |

| ON  | OFF | OFF  | OFF  | OFF | 10  | 30A      |

| ON  | OFF | OFF  | OFF  | ON  | 11  | 29A      |

| ON  | OFF | OFF  | ON   | OFF | 12  | 28A      |

| ON  | OFF | OFF  | ON   | ON  | 13  | 27A      |

| ON  | OFF | ON   | OFF  | OFF | 14  | 26A      |

| ON  | OFF | ON   | OFF  | ON  | 15  | 25A      |

| ON  | OFF | ON   | ON   | OFF | 16  | 24A      |

| ON  | OFF | ON   | ON   | ON  | 17  | 23A      |

|     |     |      |      |     |     |          |

Table 2-12 Failing Memory Chip Look-Up Table

## CHECKOUT

With your tape system installed, you may now power-up the system and test the installation. To check the controller installation and the connection of the cables to the drive, examine the Control/Status Register of the controller. The Off-Line status bit (bit 6) should change when the drive is placed on-line.

You may then run the ZTSHCO test program contained in the diagnostic tape supplied with the controller. An operational test should also be performed, such as performing a tape back-up from disk.

# SECTION III

**PROGRAMMING**

(This page intentionally left blank.)

# SECTION III - PROGRAMMING

# TABLE OF CONTENTS

| PARAGRAPH PA                                        | <u>.GE</u> |

|-----------------------------------------------------|------------|

| INTRODUCTION 3                                      | -1         |

| GENERAL 3                                           | -1         |

| PACKET BUFFER PROTOCOL 3                            | -2         |

| PDP-11 PROGRAM-CONTROLLED INPUT/OUTPUT OPERATIONS 3 | -4         |

| COMMAND PACKET 3                                    | -7         |

| CHARACTERISTICS DATA BUFFER 3-                      | 11         |

| TAPE DATA BUFFERS 3-                                | 11         |

| MESSAGE PACKET                                      | 13         |

## LIST OF ILLUSTRATIONS

Figure 3-1 Command Packet Formats ...... 3-8

Figure 3-2 Characteristics Data Buffer ...... 3-11

**PAGE**

FIGURE

| Figu  | re 3-3  | Order of Characters                        | 3-12   |

|-------|---------|--------------------------------------------|--------|

| Figur | re 3-4  | Message Packet Format                      | 3-14   |

|       |         |                                            |        |

|       |         |                                            |        |

|       |         | LIST OF TABLES                             |        |

| TABLE | 2       |                                            | PAGE   |

| 3-1   | PDP-11  | Program-Controlled Input/Output Operations | 3-5    |

| 3-2   | TSSR F  | ormat                                      | 3-6    |

| 3-3   | Termina | ation Class Codes                          | 3-7    |

| 3-4   | Command | d Packet Header Word Format                | 3-9    |

| 3-5   | Command | d Summary                                  | . 3-10 |

| 3-6   | Charact | teristics Mode Byte Format                 | 3-12   |

| 3-7   | Message | e Packet Header Word Format                | . 3-14 |

| 3-8   | Extende | ed Status Word Formats                     | . 3-15 |

#### SECTION III

#### **PROGRAMMING**

#### INTRODUCTION

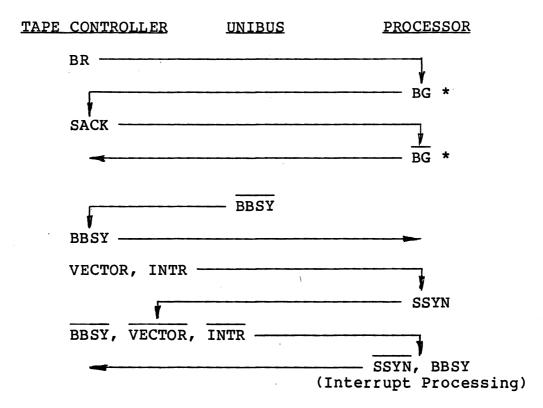

This section contains machine-level programming reference information which describes the registers of the TAPE DIMENSION IV. Also contained in this section is information on the operation of the controller including register transfers, packet transfers, data transfers, and interrupts.

## **GENERAL**

Communication between the PDP-11 program and the controller involves program-addressable registers in the controller and various classes of buffer space in PDP-11 main memory.

Two switch-selectable register addresses are assigned to the controller. The first address is shared by the write-only TSDB register and the read-only TSBA register. The second address is assigned to the read/write TSSR register.

To implement any transport command, two packet buffers in PDP-11 memory must be assigned to that transport. These packet buffers include the Command Packet Buffer in which the PDP-11 program writes command information and the Message Buffer in which the controller writes transport status information.

After writing a command packet in a command buffer, the PDPll program then writes the command buffer address in the TSDB register associated with the transport to which the command is addressed. This causes the controller to read the command packet and, if possible, execute the command. Upon completion or rejection of the command, the controller writes the appropriate transport status information in the TSSR register and in the message packet buffer. If the interrupt-enable bit is set in the command packet, it also interrupts the PDP-11 program to inform it of the ending status.

A separate command, the Set Characteristics command, points to a characteristics data buffer in PDP-11 main memory. The PDP-11 program writes the address and length of the message buffer to be assigned to the transport in the characteristics data buffer and also writes a characteristics mode byte. The write characteristics command causes the controller to access the characteristics data buffer and obtain this information. Once a

message buffer address has been obtained, the message buffer continues to be assigned to the transport until initialization occurs. Since a message packet buffer is required to complete each command transaction, it follows that the first command to a transport following initialization must be a write Characteristics command.

The controller uses non-processor direct memory accesses to obtain information from the command buffer and the characteristics data buffer and to write status information in the message buffer. During a tape read or write operation, the controller uses non-processor direct memory transfers to access a tape data buffer in PDP-11 memory.

The TSBA register holds the 16 least significant bits of the PDP-11 memory address for each direct memory access. The two most significant bits of the PDP-11 memory address are held in the TSSR register.

The two least significant bits of each command packet buffer address are always 0s. Thus, the PDP-11 can specify the command packet buffer address by means of a single 16-bit transfer to the TSDB register. Bits 0 and 1 of the word transferred to the TSDB are the two most significant bits of the command packet buffer address. Bits 2 through 15 represent bits 2 through 15 of the command packet buffer address.

In addition to holding the two most significant bits of PDP-11 memory addresses, the TSSR register hold 13 bits of transport status. Although the TSSR register is defined as a read/write register, a DATO operation addressed to the TSSR register has the effect of resetting five of the status bits held in it rather than transferring information to it. Such an operation also results in transport initialization during which a load sequence returns the tape to the BOT position if the transport is on line.

## PACKET BUFFER PROTOCOL

There is a specific protocol for accessing packet buffers and this protocol is defined in terms of buffer ownership. In general, ownership of both buffers belongs to the PDP-11 program at the time that a command transaction begins and passes to the controller when the PDP-11 program writes the command packet buffer address in the TSDB register with the Acknowledge bit set in the Command Packet header word. Ownership of the two buffers then passes back to the PDP-11 program after the command has been completed when the controller updates status and (if the Interrupt-Enable bit in the command packet is set) interrupts the PDP-11 program.

Since only the current owner is allowed to access a buffer, the controller cannot report a change of status occurring during an idle period after it has returned ownership to the PDP-11

program. If a change between on-line and off-line status occurs when the controller does not own the message buffer, it waits until the next command is received. This gives it the message buffer ownership required to update the message buffer so as to reflect the change in status. In this case, it does not accept ownership of the command buffer. If the attention-interrupt bit was set in the characteristics mode byte obtained during the most recent write-characteristics command transaction, then an attention interrupt occurs following the status update. This interrupt is independent of the state of the interrupt-enable bit of the command which returns message buffer ownership to the controller allowing the status update.

Because the controller has not accepted command buffer ownership, the transaction (which would normally have resulted in the processing of a command) in this case has resulted only in the reporting of a change in on-line/off-line status. If the command is still appropriate after this status change, the PDP-ll must restart the transaction by writing the command buffer address in the TSDB register in order to obtain command execution.

There is a message-buffer-release command whose only purpose is to leave ownership of the message buffer to the controller so that a subsequent change of on-line/off-line status can be reported immediately under transport-idle conditions. The controller updates the TSSR but not the message buffer during the message-buffer-release command transaction. If the release-interrupt-enable bit was set in the characteristics mode byte obtained during the most recent write-characteristics command transaction, then an interrupt is generated at the end of the message-buffer-release command transaction. This occurs independently of the state of the interrupt-enable bit of the message-buffer-release command.

If a change of on-line/off-line status occurs following the execution of the message-buffer-release command, then the message buffer is updated immediately to report this change of status. This update returns ownership of the message buffer to the PDP-ll program. If the attention-interrupt-enable bit was set in the characteristics mode byte obtained during the most recent write-characteristics command transaction, then an interrupt is generated at the time of the message buffer update. (This interrupt is also independent of the state of the interrupt-enable bit of the message-buffer-release command.)

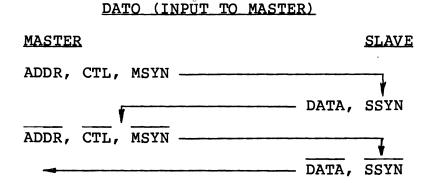

## PDP-11 PROGRAM-CONTROLLED INPUT/OUTPUT OPERATIONS

Two consecutive word addresses are assigned to the transport interfacing with the controller. The address assignments are established by setting toggle switches on the controller board. Standard addresses are as follows:

| Unit # | Registers         | <u>Address</u>   | (Octal) |

|--------|-------------------|------------------|---------|

| 1      | TSDB/TSBA         | 772520           |         |

| 2      | TSSR<br>TSDB/TSBA | 772522<br>772524 |         |

| 3      | TSSR<br>TSDB/TSBA | 772526<br>772530 |         |

| J      | TSSR              | 772532           |         |

| 4      | TSDB/TSBA<br>TSSR | 772534<br>772536 |         |

Table 3-1 summarizes the PDP-11 program-controlled input and output transfer operations associated with each register.

The format of the TSDB and TSBA register is defined in the description of the input and output operations. The format of the TSSR is summarized in Table 3-2.

Table 3-1

PDP-11 Program-Controlled Input/Output Operations

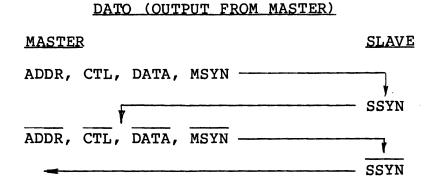

| Transfer Class<br>and Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DATO, TSDB                     | Sixteen bits of command buffer address information from Unibus are accepted by the controller. Bits 15 through 02 from Unibus are stored in corresponding bit positions of TSBA and bits 01 and 00 from Unibus (MSBs of command buffer address) are stored in bit positions 09 and 08 of TSSR. SSR bit in TSSR is reset. Controller fetches command information from buffer and processes command without further program intervention if the ACK bit is set. |

| DATOB,<br>TSDB,<br>Upper Byte  | Upper byte from Unibus is loaded into both bytes of TSBA and bits 09 and 08 from Unibus are loaded into corresponding bit positions in TSSR. Used to test integrity of controller Unibus addressing function for transport n. After this operation, DATO to TSSR must be performed to provide necessary initialization before command for transport n can be accepted.                                                                                        |

| DATOB, TSDB,<br>Lower Byte     | Lower byte from Unibus is loaded into lower byte of TSBA and lower byte of TSSR. Used for diagnostic purposes. After this operation, DATO to TSSR must be performed to provide necessary initialization before command for transport n can be accepted.                                                                                                                                                                                                       |

| DATI, TSBA                     | Sixteen least significant bits of current Unibus address pointer for transport n are placed on Unibus.                                                                                                                                                                                                                                                                                                                                                        |

| DATO or DATOB,<br>TSSR         | SPE, UPE, RMR, NXM, and SSR bits of TSSR are reset. Any transport n operation currently in progress is aborted. If transport n is on-line, a rewind-to-loadpoint operation is executed. SSR bit of TSSR is then set to indicate that transport n is ready to accept a command.                                                                                                                                                                                |

| DATI TSSR                      | Contents of TSSR are placed on Unibus.                                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 3-2 TSSR Format

| Bit(s) | Mnemonic | Meaning When Set                                                                                                                                                                                                                                                                                                                                            |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | sc       | A special condition was detected during execution of last command. More information is contained in the termination class code (bits 04-01)                                                                                                                                                                                                                 |

| 14     | UPE      | Unibus parity error                                                                                                                                                                                                                                                                                                                                         |

| 13     | SPE      | Not used by the controller. Always 0.                                                                                                                                                                                                                                                                                                                       |

| 12     | RMR      | Register modification refused. The PDP-11 program has loaded a command packet address into the TSDB when SSR (bit 07) is reset. This can occur if the last command was a message buffer release command and the controller is updating the message buffer to report a change in on-line/off-line status at the time that the PDP-11 program loads the TSDB. |

| 11     | NXM      | The controller has attempted to access a non-<br>existent memory location. The attempted<br>access may involve a command, message, or<br>data buffer.                                                                                                                                                                                                       |

| 10     | NBA      | The controller needs a message buffer address. A write characteristics command has not been executed since the last TSSR initialization.                                                                                                                                                                                                                    |

| 09, 08 | A17, A16 | Bits 17 and 16 of the Unibus address for non-<br>processor direct memory access                                                                                                                                                                                                                                                                             |

| 07     | SSR      | The transport is not busy and another command addressed to it can be accepted.                                                                                                                                                                                                                                                                              |

| 06     | OFL      | The transport is off line.                                                                                                                                                                                                                                                                                                                                  |

| 05, 04 | FC1, FC0 | Fatal termination class code. Not supported.                                                                                                                                                                                                                                                                                                                |

| 03-01  | TC2-TC0  | Termination class code. See Table 3-3.                                                                                                                                                                                                                                                                                                                      |

| 00     |          | Not used.                                                                                                                                                                                                                                                                                                                                                   |

Table 3-3 Termination Class Codes

| C | ode | e Valu | e                                 |                                                                                                                                                |

|---|-----|--------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| T | C2  | ,1,0   | Class                             | Description                                                                                                                                    |

| 0 | 0   | 0      | Normal                            | No special condition detected.                                                                                                                 |

| 0 | 0   | 1      | Attention                         | Transport has gone off line or come on line.                                                                                                   |

| 0 | 1   | 0      | Tape Status<br>Alert              | Tape status having program significance detected. Further information in TMK, RLS, RLL, EOT, or BOT bit of XSTATO word of message packet.      |

| 0 | 1   | 1      | Function<br>Reject                | Command has been rejected. Further information in VCK, BOT, WLE, LLC, or ILA bit of XSTATO word of message packet or in OFL bit of TSSR.       |

| 1 | 0   | 0      | Recoverable error, tape moved     | An uncorrected error has been detected, and tape has moved one record position. Recommended procedure is to log error and issue retry command. |

| 1 | 0   | 1      | Recoverable error, tape not moved | Not used by the controller.                                                                                                                    |

| 1 | 1   | 0      | Unrecoverable error               | Tape position has been lost. No valid recovery procedure is available.                                                                         |

| 1 | 1   | 1      | Fatal error                       | Not used by the controller.                                                                                                                    |

### COMMAND PACKET

Figure 3-1 illustrates command packet formats. Every packet contains a command packet header word. For some commands, additional information is required. Packets for commands which require access to a data buffer in main memory have two address words and a count word. The first address word contains the 16 least significant bits of the address. The second address contains the two most significant address bits, right justified. The count word specifies the data buffer length in positive byte count format. Packets for position commands contain a count word which specifies the number of records or file marks to be spaced over. For other commands, the header word contains all the required information.

Table 3-4 summarizes the information contained in the command packet header word. Two fields of the header word, the command mode field and the command code field, specify the operation to be performed. The decoding of these fields is summarized in Table 3-5.

|     | HEADER WORD |     |     |     |     |     |     |     |     |     |     |     |     |     |     |   |

|-----|-------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---|

| A15 | Al 4        | A13 | A12 | All | A10 | A09 | 80A | A07 | A06 | A05 | A04 | A03 | A02 | A01 | A00 | * |

| 0   | 0           | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Al7 | Al6 | * |

|     | COUNT WORD  |     |     |     |     |     |     |     |     |     |     |     |     |     |     |   |

\* Address Words

A. Read, Write, Write Characteristics Command Packet Format

HEADER WORD

COUNT WORD

B. Position Command Packet Format

HEADER WORD

NOT USED

C. Control or Format Command Packet Format

Figure 3-1 Command Packet Formats

Table 3-4 Command Packet Header Word Format

| Bit(s) | Mnemonic/<br>Name           | Meaning When Set                                                                                                                                                                                                                                                                                                                                                                           |

|--------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15     | ACK                         | Indicates the PDP-11 program has read message buffer. Is normally set for all commands except those occurring when the controller owns message buffer due to execution of a message-buffer-release command.                                                                                                                                                                                |

| 14-12  | Device-<br>Depend.<br>Field | (Individual bits described below)                                                                                                                                                                                                                                                                                                                                                          |

| 14     | CVC                         | Clears volume check bit of XSTATO word.                                                                                                                                                                                                                                                                                                                                                    |

| 13     | OPP                         | Alters read retry commands so that the read occurs in the opposite direction (Reread previous record is executed by reading in reverse and then spacing forward. Reread next record is executed by reading forward and then backspacing.)                                                                                                                                                  |

| 12     | SWB                         | When this bit is reset, the order of data buffer byte addresses is the same as the order in which the characters appear on tape with the character associated with the lowest byte address being closest to the BOT. Setting this bit swaps the positions of the two bytes of each word so that the upper byte appears closer to the BOT on the tape. (See paragraph: "TAPE DATA BUFFERS") |

| 11-8   | Command<br>Mode             | In conjunction with command code (bits 4-0) these bits specify the operation to be performed as summarized in Table 3-5.                                                                                                                                                                                                                                                                   |

| 7-5    | Packet<br>Format:           | (Individual bits described below)                                                                                                                                                                                                                                                                                                                                                          |

| 7      | IE                          | Interrupt enable                                                                                                                                                                                                                                                                                                                                                                           |

| 6,5    | -                           | These bits always have value 00, specifying one word header.                                                                                                                                                                                                                                                                                                                               |

| 4-0    | Command<br>Code             | In conjunction with command note bits (11-8), these bits specify the operation to be performed as summarized in Table 3-5.                                                                                                                                                                                                                                                                 |

Table 3-5 Command Summary

| <u>Command</u><br><u>Value</u> | Code<br>Command              | Command M<br>Value                   | ode<br>Operation                                                                                                                                                                                                                                                                       |

|--------------------------------|------------------------------|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00001                          | Read                         | 0000<br>0001<br>0010                 | Read one record forward. Read one record reverse. Reread previous record (backspace over record and then read forward). Reread next record (Space forward one record and then read reverse).                                                                                           |

| 00100                          | Write<br>character<br>istics | _0000                                | Get message buffer address and characteristics byte from characteristics data buffer.                                                                                                                                                                                                  |

| 00101                          | Write                        | 0000<br>0010                         | Write one data record. Retry to write one data record (Backspace over record and the erase and write record).                                                                                                                                                                          |

| 00110                          | Write<br>Subsystem<br>Memory | 0000                                 | Not supported.                                                                                                                                                                                                                                                                         |

| 01000                          | Position                     | 0000<br>0001<br>0010<br>0011<br>0100 | Space forward n records, where n is specified by count word.  Space reverse n records, where n is specified by count word.  Skip n tape marks forward, where n is specified by count word.  Space reverse n tape marks, where n is specified by count word.  Rewind tape to loadpoint. |

| 01001                          | Format                       | 0000<br>0001<br>0010                 | Write tape mark. Erase forward 3 inches of tape. Retry to write tape mark (Space reverse, erase, and write tape mark).                                                                                                                                                                 |

| 01010                          | Control                      | 0000                                 | This constitutes a message buffer release command. It leaves ownership of the message buffer with the controller so as to allow immediate reporting of transport on-line/off-line status change.                                                                                       |

|                                |                              | 0001                                 | Rewind tape completely onto supply reel (unload). Clean tape (not supported).                                                                                                                                                                                                          |

| 01111                          | Get<br>status<br>immediate   | 0000                                 | Update message buffer.                                                                                                                                                                                                                                                                 |

## CHARACTERISTICS DATA BUFFER

The information contained in the characteristics data buffer includes the message buffer address and the characteristics mode byte. The location and length of the characteristics data buffer are specified in the address and count words of the write characteristics command packet. The controlleruses non-processor direct memory accesses to obtain the information from the characteristics data buffer.

Figure 3-2 illustrates the characteristics data buffer format. Table 3-6 summarizes the information contained in the characteristics mode byte.

| A15 | A14 | A13 | A12 | All | A10 | A09 | A08 | A07 | A06   | A05  | A04  | A03  | A02  | A01  | A00 | *  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|------|------|------|------|------|-----|----|

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0     | 0    | 0    | 0    | 0    | À17  | Al6 | *  |

| 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0     | 0    | 0    | 1    | 1    | 1    | 0   | ** |

|     |     |     |     |     |     |     |     |     | CHARA | ACTE | RIST | CS I | MODE | ВУТІ | Ξ   |    |

- \* Message Buffer Address

- \*\* Message Buffer Length

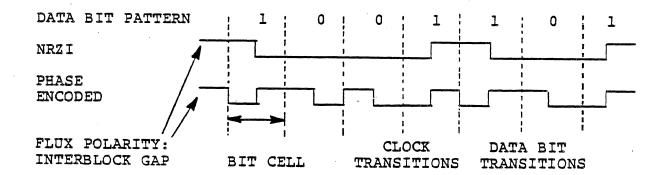

Figure 3-2 Characteristics Data Buffer