## MODEL TC-131 TAPE CONTROLLER HARDWARE MANUAL

PUBLICATION NUMBER

91000471

PRELIMINARY

# western peripherals

14321 MYFORD ROAD TUSTIN, CALIFORNIA 92680

© 1980 by Western Peripherals, Inc. All Rights Reserved

PRINTED IN U.S.A.

NOVEMBER, 1980

## SECTION I

2

## GENERAL DESCRIPTION

## TABLE OF CONTENTS

| SECTION |         |                          | PAGE |

|---------|---------|--------------------------|------|

| I       | GENERAI | L DESCRIPTION            |      |

|         | 1.1     | DESCRIPTION OF EQUIPMENT | 1-1  |

|         | 1.3     | DRIVE COMPATIBILITY      | 1-1  |

|         | 1.6     | OTHER FEATURES           | 1-2  |

|         | 1.12    | SPECIFICATIONS           | 1-4  |

#### SECTION I

### GENERAL DESCRIPTION

### 1.1 DESCRIPTION OF EQUIPMENT

1.2 The Western Peripherals Model TC-131 is a magnetic tape controller/formatter which is hardware and software compatible with the DEC PDP-11 family of computer systems, providing both NRZI and phase encoded (PE) format capability in an embedded controller. Only the NRZI format capability is provided with model TC-131N. Mounted in any standard Small Peripheral Controller (SPC) slot in a standard backplane system unit, the controller consists of a single standard hex-wide board and contains a microprocessor plus all interface, control, status, and formatting electronics to emulate the TM-11/TU-10 tape subsystem. The controller installs directly into any available location in the computer or expansion chassis. Three ribbon cables interconnect the controller with the tape drives through cable adapters, which also provide daisy-chaining capabilities for multiple drive installations.

1.3 DRIVE COMPATIBILITY

1.4 The controller will handle up to eight industry-compatible (IBM/ANSI) read-after-write (dual gap) tape drives. The controller is capable of handling tape drives in varying combinations of speeds, densities, and formats. The controller can select either of two switch selectable speeds in the range from 25 to 125 inches per second (ips).

1.5 Single or dual density NRZI and PE tape drives may be used with densities of 800 bits per inch (bpi) NRZI 9-track, and 1600 bpi PE 9-track. Software density control is available for dual density operation. The controller is compatible with all industrystandard tape drives.

1.6 OTHER FEATURES

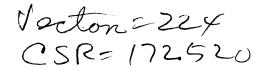

1.7 The controller is compatible with the Unibus and with existing magnetic tape software, utilizing the standard TU-10/TM-11 magnetic tape controller registers. Enhancements of the standard registers provide other features which add to the usefulness of the controller. Transfers of register information between the tape controller and the computer are made using standard register addresses 772520 through 772532 with 224 as the standard interrupt vector. Alternate addresses and vectors may be used for a second tape system if over eight tape drives are used or if other system requirements are such that a second controller must be used. The address and vector may be changed by moving jumpers. Data transfers are in a 16-bit word or 8-bit byte format via the Unibus.

1.8 Both DEC (normal) and standard IBM (selectable) byte packing modes are available. This bit-selectable IBM packing mode allows reading and writing IBM/industry-compatible tapes. Accomplished without special software, the "automatic read and write on-the-fly" feature allows non-stop operation when doing consecutive read or write operations. The controller writes and recognizes IBM/ANSI compatible end-of-file tape marks. The controller provides an "EDIT" feature which allows a record anywhere on a previously

91000471 4/81

GENERAL DESCRIPTION

recorded tape to be replaced with an updated record. (widow)

1.9 65 bytes of data buffering provide flexibility in assigning priorities when programming data transfers to the computer. The tape motion control, Cyclic Redundancy Check character (CRC) and the Longitudinal Redundancy Check character (LRC) generation and checking, inter-record gap generation and status reporting are included. No screwdriver adjustments are required or provided. While the controller can read or write only in the forward direction, it can space (or move to a new position) in both directions.

1.10 The controller may address up to eight drives but can only read, write or space one drive at a time, except for the Rewind Command. This function requires only initiation by the controller. That transport can then be left to rewind while the controller services another drive.

1.11 Programmed instructions are used to specify the starting address in computer memory, the number of bytes to transfer, the drive number, and the function to be performed. Programmed instructions are also used to transfer status, address, byte count and other information from the tape controller to the computer. Data transfers during read and write operations are accomplished by the controller, which becomes "bus master" to accomplish these transfers.

91000471 4/81

## 1.12 SPECIFICATIONS

1.13 The following information summarizes the specifications of the tape controller.

- 1. Computer Interface

- a. Compatibility The controller is fully hardware and software compatible with the DEC PDP-11 computer system family and all other systems emulating the Unibus.

- b. Emulation The controller emulates the standard TM-ll/TU-l0 tape subsystem.

- c. The controller interfaces directly with the Unibus through any standard SPC board slot.

- d. Bus Loading One bus load.

- e. Tape Commands\*:

Off line

Read

Write

Write EOF

Space Forward

Space Reverse

Write with Extended Record Gap

Rewind

f. Other Mode Controls:

Density Selection \*

Byte Mode Selection \*

Controller Clear

Unit Selection \*

91000471 4/81

|    | Interrupt Enable *                              |

|----|-------------------------------------------------|

|    | Command Execution (GO) *                        |

|    | Edit Mode *                                     |

|    | Byte Count *                                    |

|    | Memory Address *                                |

|    | For Diagnostics:                                |

|    | Check Character Read Selection *                |

|    | Bad Tape Error Simulation *                     |

| g. | Controller Status:                              |

|    | Status of the above-mentioned commands marked   |

|    | with an asterisk (*) may be checked in addition |

|    | to the following:                               |

|    | Illegal Command                                 |

|    | End of File                                     |

|    | Parity/Format Error                             |

|    | Bus Grant Late                                  |

|    | End of Tape                                     |

|    | Record Length Excessive (Read Mode)             |

|    | Bad Tape Error                                  |

|    | Non-Existent Memory                             |

|    | Drive On-Line                                   |

|    | Beginning of Tape                               |

|    | Write-Protected                                 |

|    | Drive Rewinding                                 |

|    | Drive Ready                                     |

|    | Error Summary                                   |

|    | Controller Ready                                |

91000471 4/81

Correctable Parity Error (Read)

PE Identification

For Diagnostics:

Tape Stopping After Rewind

10 KHz Clock

Gap Shutdown

Read/LRC Bits

CRC/LRC Character

- h. Register Addresses: 772520 thru 772532

(standard for TM-11). Alternate addresses

are jumper selectable.

- Interrupt Vector: 224 (standard for TM-11). Alternate vectors are jumper selectable.

- 2. Format Compatibility

Fully compatible with the industry-standard IBM/ANSI digital tape recording format as described in ANSI specifications X3.22-1973 and X3.39-1973. Both DEC (normal) and standard IBM (selectable) byte packing modes are available.

3. Drive Compatibility

a. Designed to be compatible with the industry standard drives

b. Read-after-Write only (dual gap head)

c. Single or dual density (operator or software switchable)

4. Tape Speed

25 ips, 37.5 ips, 45 ips, 75 ips, 125 ips

- 5. Format and Density

- a. NRZI 9-Track 800 BPI

b. PE 9-Track - 1600 BPI

6. Data Transfers

a. 9-Track (1) DEC - compatible byte packing mode,

(least significant byte first) - standard

operating mode

(2) IBM - compatible byte packing mode(most significant byte first).

- Bus transfers consist of 16-bit word transfers

with 8-bit byte transfers for odd bytes at the

beginning and/or end of the transfer.

- 7. Drive Configuration

- a. Up to eight drives in daisy chain configuration

- b. One or two tape drive speeds.

c. Single or dual densities on the daisy-chain.

- 8. Hardware

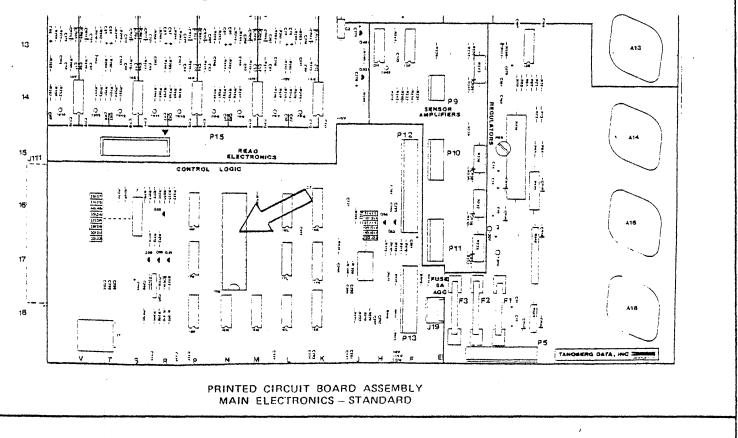

- a. One hex-wide printed circuit board mounted within the computer chassis (or expansion cabinet), containing a 2900 microprocessor and other advanced technology microcircuits.

- b. Three interface cables and adapter boards per tape drive

91000471 4/81

## 9. Other Features

a. Edit mode for correcting pre-recorded tapes

- b. Crystal controlled clocks

- c. Phase-locked loop read tracking in the PE mode

- d. No screwdriver adjustments

- 10. Error Handling

- Generates and checks vertical parity, CRC,LRC

preambles and postambles

- b. Detects dead track errors

- c. Corrects PE single channel dropouts

## 11. Data Buffering

The internal buffer between the CPU and the tape

drive provides 65 bytes of buffering to allow for transfers between the controller and the tape drive during the time when the computer bus is unable to service the controller. All data contained in the buffer will automatically be transferred before the operation is aborted. During read operations, the buffer allows a check of false preambles in 9-track PE mode when a single dead track occurs. During read operations, the buffer must be emptied within the maximum times specified below, otherwise a data late error condition is reported.

91000471 4/81

## Maximum Time After End of Record

| Tape Speed | 9-Track NR | ZI <u>9-Track PE</u> |

|------------|------------|----------------------|

| 25.0 ips   | 1.50 ms    | 2.05 ms              |

| 37.5 ips   | 1.00 ms    | 1.37 ms              |

| 45.0 ips   | 0.83 ms    | 1.14 ms              |

| 75.0 ips   | 0.50 ms    | 0.68 ms              |

| 125.0 ips  | 0.30 ms    | 0.41 ms              |

12. Non-Stop "On-the-Fly" Tape Operation

This feature provides continuous tape motion when consecutive tape commands require tape motion in the same direction on the same tape drive. Under these conditions, the controller will time through the inter-record gap (IRG) in the read mode, or will write the IRG in the write mode and execute the next command without stopping the tape.

- 13. Power Requirements

- a. Source CPU or Expansion Chassis power supply

- b. +5VDC <u>+</u> 5% @ 9.0 amps

- 14. Physical Specifications

- a. Size

- (1) One Standard DEC Hex-sized board

b. Weight (approximate)

- (1) Controller board 22 oz. (0.62 kg)

- (2) Cables & Adapters 26 oz. (0.74 kg) per drive

## 91000471 4/81

c. Environment

(1) Operation Temperature 0 to 55 degrees C

(2) Storage Temperature 10 to 70 degrees C

(3) Relative Humidity 1

,

- 10 to 90 percent

- (without conden-

sation)

## SELF-TEST SEQUENCE AND DESCRIPTION

| LEDS<br>#5 4321 | TEST-<br>DESCRIPTION       | LISTING<br>PAGE |

|-----------------|----------------------------|-----------------|

| lF              | 2910 LOOP CNTR, Q REG      | 3               |

| lE              | INCR/DECR Q REG, CARRY OUT | 4               |

| lC              | SHIFT Q REG, LITERALS, XOR | 5               |

| 18              | POWER UP CONDITION TEST    | б               |

| 10              | REG FILE SHIFT TEST        | 7               |

| 07              | 2901 REG. ADDRESSING       | 8               |

| Ol              | REGISTERS - MOVING ZERO    | 9               |

| 02              | CARRY CONTROL TEST         | 10              |

| 03              | FIFO OPERATION TEST        | 11.             |

| 04              | WRITE FIFO TEST            | 12              |

| 05              | READ FIFO TEST             | 13              |

| 06              | PARITY TEST                | 14              |

| 08              | MICRO-INTERRUPT TEST       | 15              |

| 00              | PASS                       | 16              |

## SECTION II INSTALLATION

.

## TABLE OF CONTENTS

|                                        | PAGE                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INTRODUCTION                           | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| UNPACKING AND INSPECTION               | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SYSTEM COMPONENTS                      | 2-2                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PREPARATION                            | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SY\$TEM SET-UP                         | 2-3                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TAPE SPEED SELECTION                   | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CONTROLLER JUMPERS                     | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ADDRESS JUMPERS                        | 2-4                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| VECTOR JUMPERS                         | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| NPG JUMPER REMOVAL/BUS LEVEL SELECTION | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PRIORITY JUMPERS                       | 2-7                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| BUS LEVEL SELECTION                    | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONTROLLER INSTALLATION                | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONTROLLER BOARD INSTALLATION          | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONTROLLER CABLE CONNECTIONS           | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TAPE DRIVE INSTALLATION                | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TERMINATORS                            | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CONFIGURATION SWITCHES                 | 2-13                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DRIVE SELECT JUMPERS                   | 2-16                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TAPE DRIVE INTERCONNECTIONS            | 2-16                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| INSTALLATION CHECKLIST                 | 2-22                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                        | UNPACKING AND INSPECTION<br>SYSTEM COMPONENTS<br>PREPARATION<br>SYSTEM SET-UP<br>TAPE SPEED SELECTION<br>CONTROLLER JUMPERS<br>ADDRESS JUMPERS<br>VECTOR JUMPERS<br>NPG JUMPER REMOVAL/BUS LEVEL SELECTION<br>PRIORITY JUMPERS<br>BUS LEVEL SELECTION<br>CONTROLLER INSTALLATION<br>CONTROLLER CABLE CONNECTIONS<br>TAPE DRIVE INSTALLATION<br>TERMINATORS<br>CONFIGURATION SWITCHES<br>DRIVE SELECT JUMPERS<br>TAPE DRIVE INTERCONNECTIONS |

## LIST OF ILLUSTRATIONS

| FIGURE |                                         | PAGE |

|--------|-----------------------------------------|------|

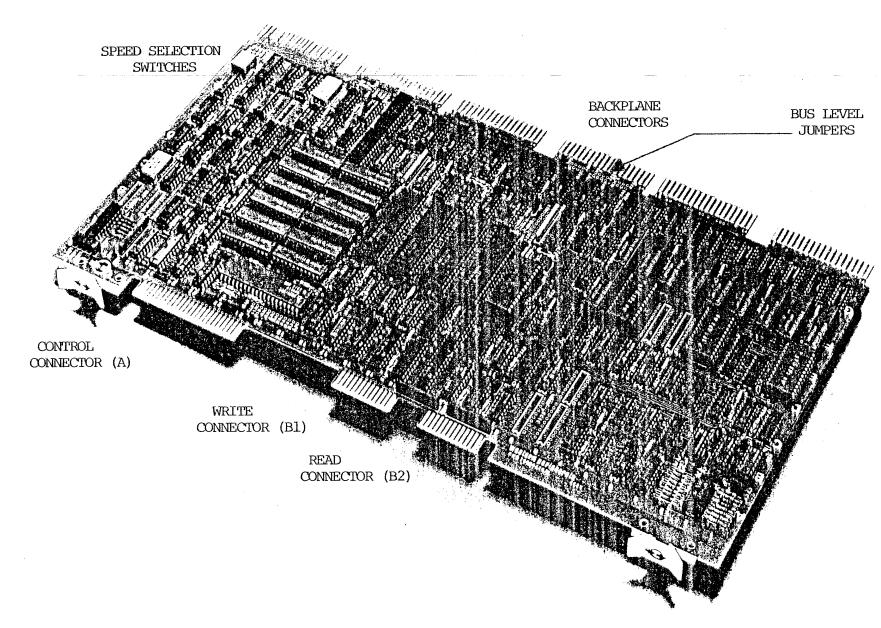

| 2.1    | CONTROLLER INSTALLATION FEATURES        | 2-5  |

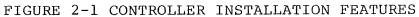

| 2.2    | EXAMPLE OF TYPICAL SYSTEM INSTALLATION  | 2-6  |

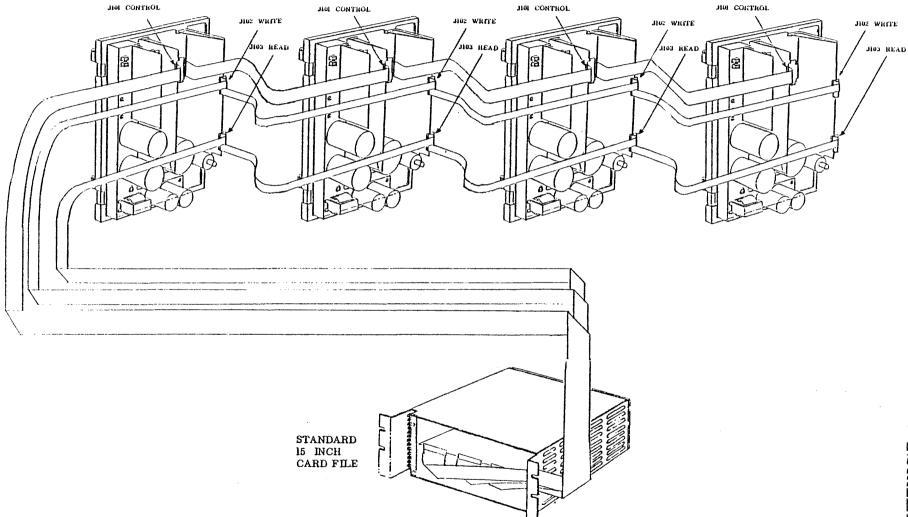

| 2.3    | BACKPLANE JUMPERS                       | 2-9  |

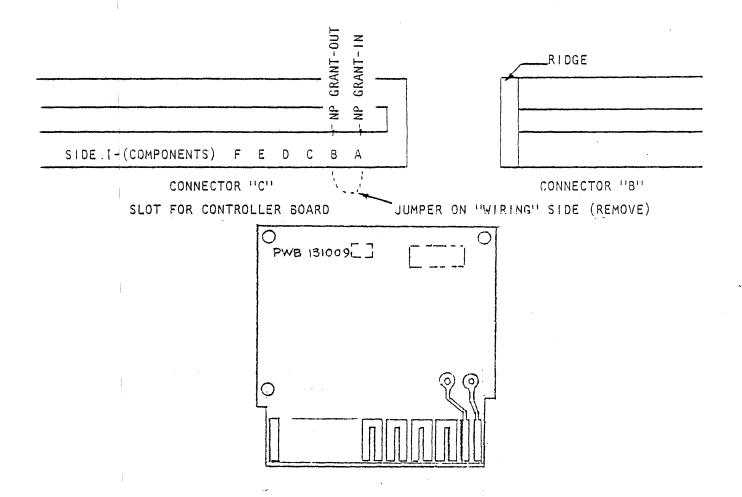

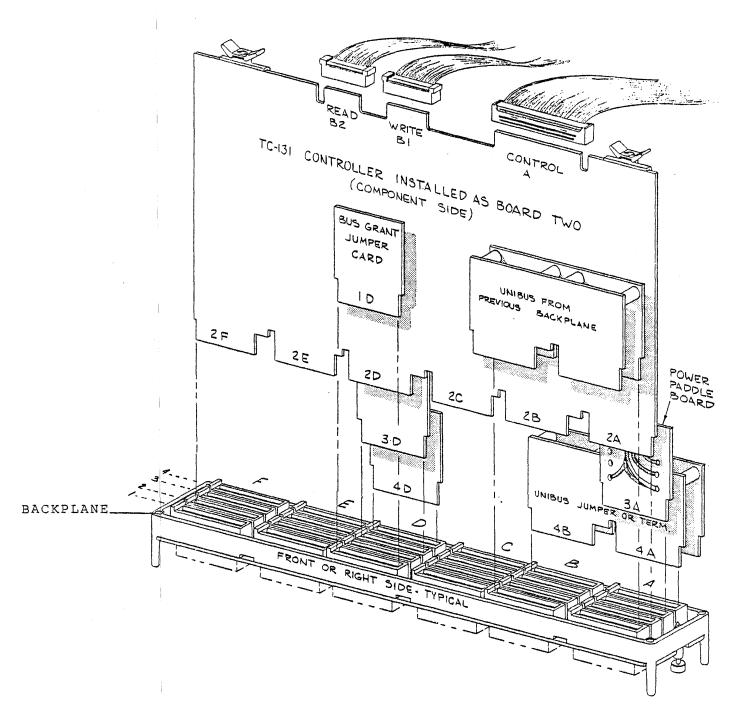

| 2.4    | SYSTEM CONFIGURATION                    | 2-12 |

| 2.5    | DETAILS OF ADAPTER INSTALLATION         | 2-14 |

| 2.6    | DRIVE SELECT JUMPERS                    | 2-17 |

| 2.7    | SINGLE TAPE DRIVE CONNECTIONS           | 2-20 |

| 2.8    | TAPE DRIVE DAISY-CHAIN CONNECTIONS      | 2-21 |

|        |                                         |      |

| TABLE  |                                         | ·    |

| 2.1    | SPEED SELECTION SWITCHES                | 2-7  |

| 2.2    | ADDRESS JUMPERS                         | 2-8  |

| 2.3    | VECTOR JUMPERS                          | 2-8  |

| 2.4    | BUS LEVEL SELECTION                     | 2-11 |

| 2.5    | CONFIGURATION SWITCHES                  | 2-15 |

| 2.6    | CONTROL ADAPTER SELECT OPTIONS          | 2-18 |

| 2.7    | CONNECTOR LEGENDS AND CABLE CONNECTIONS | 2-18 |

| 2.8    | IBM AND DENSITY SELECT JUMPERS          | 2-24 |

### SECTION II

## INSTALLATION

## 2.1 INTRODUCTION

2.2 This section provides information necessary to successfully set up and install the TC-131 Tape Controller into the DEC PDP-11 computer system. This information is essential for the initial installation and will also be valuable when the controller is reinstalled after repair.

2.3 The controller consists of a single printed circuit board which plugs directly into a slot in a standard SPC-wired system unit (backplane) in the computer mainframe or in an expansion chassis. Cable Adapter Paddleboards are provided to match the universal controller interface cables to the specific connector requirements of each drive (to be specified by the customer at the time of purchase). All DC power required for the operation of the controller is received from the power supply of the host computer or chassis via the backplane connector.

2.4 UNPACKING AND INSPECTION. After removal of the controller components from the shipping containers, visually inspect them for physical damage. Check off each item on the enclosed packing list. In case of damage, retain all packaging and notify the carrier to make a report. Be sure all minor parts and small items are found before discarding any shipping material.

91000471 6/81

2.5 SYSTEM COMPONENTS. Check the equipment supplied to ensure that all necessary items are included:

1. Controller Board

2. Drive Cables (3), one set per drive:

Control cable

Write cable

Read cable

3. Adapter Paddleboards (3), one set per drive:

Control Adapter Paddleboard

Write Adapter Paddleboard

Read Adapter Paddleboard

Including:

Terminators (on the Write and Control Paddleboards)

Drive Select Jumpers (on the Control Paddleboard)

See Figure 2-6 for part identification.

4. Program tapes:

- a. Diagnostic program tape

- b. Reliability program tape

5. Documentation:

- a. Hardware manual

- b. Logic manual

- c. Diagnositc manual

6. Other items which should be available:

- a. Computer

- b. Tape drives

- c. Standard SPC backplane system unit and associated power cable.

91000471 6/81

- d. Unibus terminator, cables/jumpers

- e. Unibus repeater, if required

- f. Loading device for diagnostics

## 2.6 PREPARATION

2.7 Locate the position in the computer where the controller will be installed. Remember that the position of the system unit determines priority for DMA and interrupt activity. The tape controller usually works well if placed anywhere in the system. Check the cabling distance to the first drive and to each daisychained drive, verifying that all cable lengths will be adequate. Refer to your tape drive manual to install the tape drives. The computer and the tape drives must be prepared for operation before the controller can be expected to operate properly.

> WARNING: INCORRECT INSTALLATION WILL CAUSE DAMAGE TO THE SYSTEM WHEN POWER IS APPLIED.

### 2.8 SYSTEM SET-UP

2.9 The tape system must be set up properly either when installing the system or after servicing. Proper set-up includes: (1) Setting the speed switches to the speed of the drives, (2) Setting the Address, Vector, and Interrupt Bus Level as required by software and (3) Removing the backplane jumper for the NPG signal. Each set of Tape Drive Adapter Paddleboard must have the proper termination (on the last drive), a Drive Select Jumper (except single drive installations), and Configuration Switch selections.

### 91000471 6/81

INSTALLATION

Installation is complete when the system components are plugged in and interconnected. A recheck and inspection of the installation ensures that no item is overlooked. The procedures to set the controller features and to install the controller are in the paragraphs that follow. Locations of setup items on the controller board are shown in Figure 2-1. A complete installation is shown in Figure 2-2. Also, check at the rear of the manual and this section for any special information which may be pertinent to your installation.

2.10 TAPE SPEED SELECTION. Tape drive speed is selected on the controller by the setting of four switches located by the setting of four switches located in a switch pack at location 28G. Speed selection provides two tape speeds for both the NRZI and PE modes. Table 2-1 provides the required speed settings for various combinations, (if only one speed is used, it may be selected on either speed A or speed B.)

2.11 CONTROLLER JUMPERS

2.12 ADDRESS JUMPERS. Normally, the controller is assigned to the standard TM-11 Unibus addresses, 772 520-772 532<sub>8</sub>. An alternate address may be assigned to the controller when a second controller is used, or when required for any other reason. An alternate address as well as the standard one are shown in Table 2-2. Check the jumpers to ensure that the controller will operate properly. These jumpers are located near IC 13F.

## 91000471 6/81

91000471

6/81

2-5

INSTALLATION

Figure 2-2 Example of Typical System Installation

INSTALLATION

| 3  | 4              |

|----|----------------|

| 1  |                |

| ON | ON             |

|    | ON             |

|    |                |

|    |                |

| ON |                |

|    | ON             |

|    | ON             |

| ON |                |

| ON |                |

| ON | ON             |

|    | ON<br>ON<br>ON |

ON = CLOSED; ALL OTHERS OFF (OR OPEN) TABLE 2-1 SPEED SELECTION SWITCHES

2.13 VECTOR JUMPERS. Normally, the controller is assigned to the standard TM-11 Unibus vector, 224<sub>8</sub>. An alternate vector may be assigned to the controller when a second controller is used, or when required for any other reason. An alternate vector as well as the standard one are shown in Table 2-3. Check the jumpers to ensure that the controller will operate properly. These jumpers are located near IC 19F.

2.14 NPG JUMPER REMOVAL/BUS LEVEL SELECTION

2.15 PRIORITY JUMPERS. The Direct Memory Access Non-Processor Grant lines are daisy-chained to the I/O devices. As shown in Figure 2-3, each device receives this signal on pin CAl and sends this signal from pin CBl to the next device.

91000471 6/81

Kanned

| BIT NO.                                | 17 | 16  | 15    | 14     | 13  | 12                                                                                                             | 11                    | 10               | 9                     | 8                | 7                     | 6                | 5                     | 4                | 3 | 2     | 1 | 0 |

|----------------------------------------|----|-----|-------|--------|-----|----------------------------------------------------------------------------------------------------------------|-----------------------|------------------|-----------------------|------------------|-----------------------|------------------|-----------------------|------------------|---|-------|---|---|

| STANDARD<br>ADDRESS<br>772520          | 1  | 1   | 1     | 1      | 1   | 1                                                                                                              | 0                     | 1                | 0                     | 1                | 0                     | 1                | 0                     | 1                | x | x     | x | x |

| DESIRED<br>ADDRESS<br>(FILL-IN)        | 1  | 1   | 1     | 1      | 1   | 1                                                                                                              |                       |                  |                       |                  |                       |                  |                       |                  | x | x     | x | x |

| INSTALL<br>JUMPER<br>FOR<br>Ø -<br>BIT |    | (N0 | OT AL | TERABI | LE) | an de la companya de | E20<br>TO<br>E28<br>* | E19<br>TO<br>E27 | E18<br>TO<br>E26<br>* | E17<br>TO<br>E25 | E16<br>TO<br>E24<br>* | E15<br>TO<br>E23 | E14<br>TO<br>E22<br>* | E13<br>TO<br>E21 |   | REGIS |   |   |

\* STANDARD ADDRESS PROVIDED IN ETCHED JUMPERS.

JUMPERS ARE LOCATED ON SCHEMATIC PAGE 2 AND ON BOARD NEAR IC 13F.

| BIT NO.                                | 7                | 6                     | 5                     | 4                | 3                     | 2                | 1                     | 0 |

|----------------------------------------|------------------|-----------------------|-----------------------|------------------|-----------------------|------------------|-----------------------|---|

| STANDARD<br>VECTOR<br>224              | 1                | 0                     | 0                     | l                | 0                     | 1                | 0                     | 0 |

| DESIRED<br>VECTOR<br>(FILL-IN)         |                  |                       |                       | , <b>2</b>       |                       |                  | 5                     |   |

| INSTALL<br>JUMPER<br>FOR<br>Ø -<br>BIT | E34<br>TO<br>E40 | E33<br>TO<br>E39<br>* | E32<br>TO<br>E38<br>* | E31<br>TO<br>E37 | E30<br>TO<br>E36<br>* | E29<br>TO<br>E35 | F<br>I<br>X<br>E<br>D |   |

## TABLE 2-2 ADDRESS JUMPERS

\* STANDARD VECTOR PROVIDED IN ETCH JUMPERS. JUMPERS ARE LOCATED ON SCHEMATIC PAGE 2 AND ON BOARD NEAR IC 19F.

TABLE 2-3 VECTOR JUMPERS

91000471 6/81

### FIGURE 2-3 BACKPLANE JUMPERS

There can be no break in the chain throughout the I/O devices. A previously unused card connector will have jumpers across these pins. When installing the controller, remove the priority jumpers from across the connector pins of the card slot for the controller board and ensure that the priority lines are daisy-chained from the CPU through the devices.

91000471 6/81

INSTALLATION

2.16 The interrupt - bus grant lines are also daisy-chained to the I/O devices. When installing the controller, remove the priority jumper card from the "D" connectors of the card slot to be occupied by the controller and check that these lines are daisy-chained through the devices or jumper cards from the CPU.

2.17 BUS LEVEL SELECTION. Interrupts on the Unibus are selectable among four bus levels. The controller is normally operated on Interrupt Bus Level 5. Verify the tape controller bus level of the operating system to select the proper bus level. However, when operating the Reliability test program Bus Level 5 must be used. Install the bus level jumpers according to Table 2-4. These jumpers are located at IC rows 10 through 14 near bus connector "D".

2.18 CONTROLLER INSTALLATION

2.19 CONTROLLER BOARD INSTALLATION. Referring to Figure 2-4, place the controller boards into any convenient location of the system unit. Ensure the boards are oriented correctly (notches on the board connectors must fit the ridges of the system unit), and are seated fully.

WARNING: INCORRECT INSTALLATION WILL CAUSE DAMAGE TO THE SYSTEM WHEN POWER IS APPLIED.

|                        |                               | BUS LEVEL                     |                               |                               |

|------------------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|

| FUNCTION               | 4                             | 5*                            | б                             | 7                             |

| BUS REQUEST            | E49-E61                       | E50-E62                       | E51-E63                       | E52-E64                       |

| GRANT IN<br>GRANT OUT  | E42-E54<br>E41-E53            | E44-E56<br>E43-E55            | E46-E58<br>E45-E57            | E48-E60<br>E47-E59            |

| BUS<br>GRANT<br>BYPASS | E56-E55<br>E58-E57<br>E60-E59 | E54-E53<br>E58-E57<br>E60-E59 | E54-E53<br>E56-E55<br>E60-E59 | E54-E53<br>E56-E55<br>E58-E57 |

\* STANDARD BUS LEVEL 5 JUMPERS ARE PROVIDED IN ETCH. JUMPERS E41 THRU E64 ARE LOCATED AT IC ROWS 10 THRU 14, NEAR BUS CONNECTOR "D".

TABLE 2-4 BUS LEVEL SELECTION

91000471 6/81

SYSTEM CONFIGURATION

(TYPICAL)

INSTALLATION

2.20 CONTROLLER CABLE CONNECTIONS. Locate the following cables:

Controller-End

| Description        | Conductors | Marking |

|--------------------|------------|---------|

| Tape Read Cable    | 26         | Top B2  |

| Tape Write Cable   | 26         | Top Bl  |

| Tape Control Cable | 50         | Top A   |

The ribbon cables are keyed to prevent incorrect connections. Check the ribbon cable connectors to assure that all keys are in place.

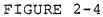

2.21 Install the Read, Write, and Control cables (in that order) onto the controller connectors as shown in Figure 2-4. The cables will exit toward the solder side of the boards.

### 2.22 TAPE DRIVE INSTALLATION

2.23 ADAPTER PADDLEBOARD SETUP. Locate a set of three Adapter Paddleboards for each tape drive. The Adapter Paddleboards for each drive require proper setup before installation. Setup includes proper termination, switch settings, and installation of drive selection jumper plugs.

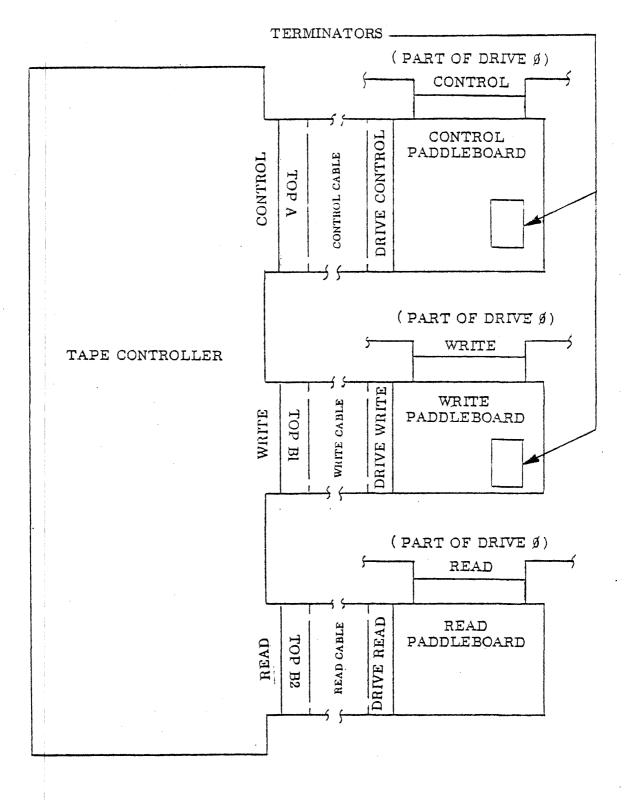

2.24 **TERMINATORS.** Consulting the tape manuals for details, remove all termination devices from each drive. Remove the terminators from the Write and Control Adapter Paddleboards, except the Adapter Paddleboards on the drive located farthest from the controller. See Figure 2-5. Ensure that the last Adapter Paddleboards have the terminators installed as shown.

2.25 **CONFIGURATION SWITCHES.** Set the switch module on each Control Paddleboard according to the configuration requirements of the tape drive. Switch settings are given in Table 2-5.

Figure 2-5. Details of Adapter Installation

91000471 6/81

21  $\vdash$ 4

INSTALLATION

| SWITCH<br>NUMBER | SETTING ·                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------|

| l                | "ON" for normal operation<br>"OFF for H.P. drives and for some Pertec<br>models                                 |

| 2                | OFF                                                                                                             |

| 3                | OFF                                                                                                             |

| 4                | ON - For HIGH SPEED drive<br>(Controller speed B)<br>OFF - For LOW SPEED drive<br>(Controller speed A)          |

| 5                | ON                                                                                                              |

| 6                | "ON" for 9-track NRZI-only drives<br>"OFF" for all other drives                                                 |

| 7                | "ON" for either dual density or PE drives<br>made by Kennedy, Digidata, or Qantex<br>"OFF" for all other drives |

| 8                | "OFF"                                                                                                           |

Reference Schematic Number 122036 Table 2-5 Configuration Switches

INSTALLATION

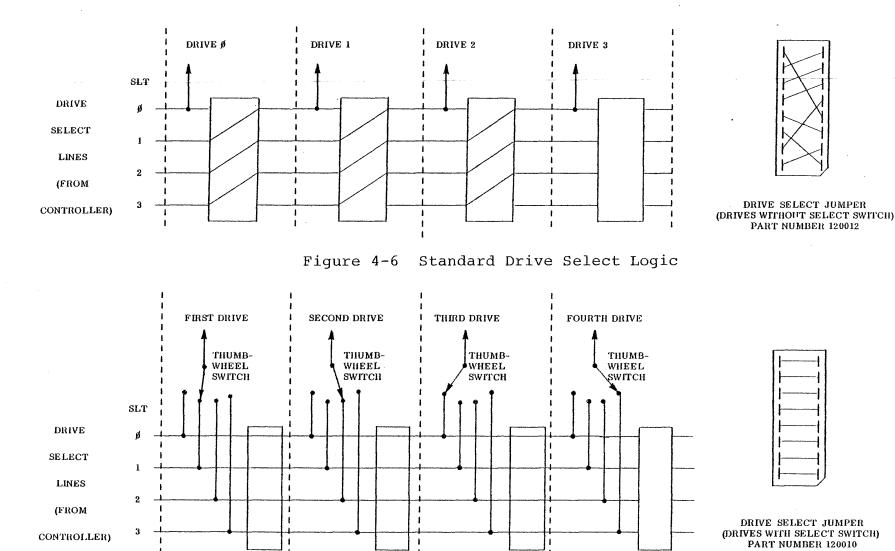

2.26 DRIVE SELECT JUMPERS. Ensure that the correct Drive Select Jumper is installed in the Control Paddleboards. The last drive does not require a Drive Select Jumper (leaving one installed will have no effect).

1. For tape drives without front panel unit select switches, use jumper part number 122012 as shown in Figure 2-6.

2. For tape drives with front panel unit select switches:

- a. Use jumper part number 122010 as shown in Figure 2-6.

- b. On drives with Unit Select Switches that receive the select lines from J101, ensure Control Paddleboard Jumpers are installed from P to R (factory etch), N to M, E to F, and G to H. See Table 2-6.

- c. On drives with externally connected Unit Select Switches, connect as shown in Table 2-6.

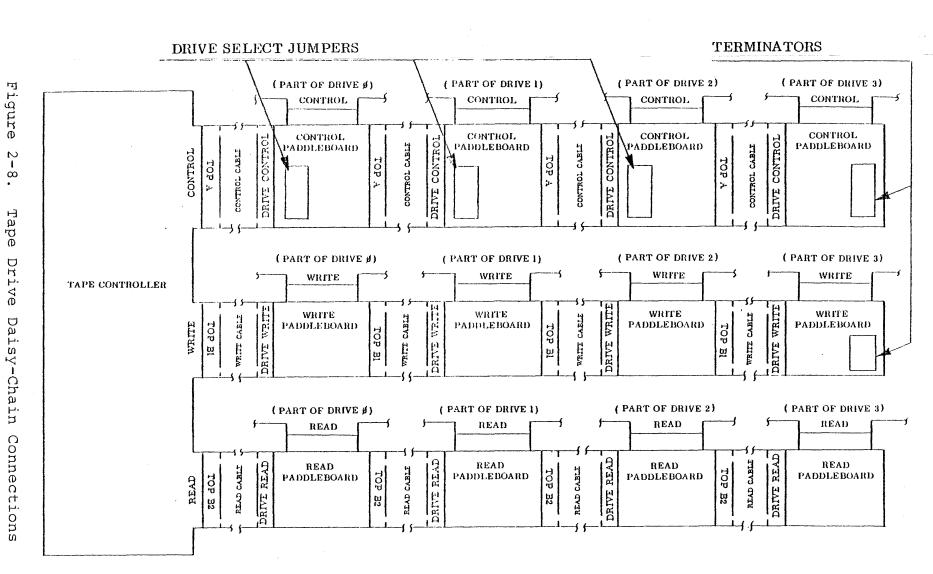

2.27 **TAPE DRIVE INTERCONNECTIONS.** Locate a set of three ribbon cables for each drive (one set is connected to the controller). Check that each connector has its key in place and connect the cables as shown in Table 2-5 and Figures 2-7 and 2-8.

NON-SELECT JUMPER (PN 122012) For daisy-chained drives Without front panel Unit Select switches.

UNIT SELECT JUMPER (PN 122010) For daisy-chained drives with Unit Select switch (Except fourth tape unit)

UNIT SELECT JUMPER (PN 122011) For daisy-chained drives with unit select switches (Install in fourth tape unit)

NOTE: No jumper plug is required on the last tape unit or for single drive installations. However, it should remain in the board for future expansion of the system.

Figure 2-6 Drive Select Jumpers

| Drive<br>Select<br>Line: |   | Add<br>Jumper: | To<br>Activate<br>J101<br>Pin: | Connect<br>External<br>Switch<br>To: |  |

|--------------------------|---|----------------|--------------------------------|--------------------------------------|--|

| Select                   | ø | P-R<br>(Etch)  | J                              | А                                    |  |

| Select                   | 1 | N-M            | A                              | В                                    |  |

| Select                   | 2 | E-F            | 18                             | D                                    |  |

| Select                   | 3 | G-H            | v                              | С                                    |  |

|                          |   |                |                                | L (return line<br>from switch)       |  |

NOTE: APPLIES TO DRIVE SELECT THUMBWHEEL OPTION ONLY.

Table 2-6 Control Adapter Select Options

| (Sequence is repeated for each drive) |                  |                   |                    |                   |                  |  |  |

|---------------------------------------|------------------|-------------------|--------------------|-------------------|------------------|--|--|

| Cables                                |                  | Paddleboards      |                    | Cables            |                  |  |  |

| Controller<br>End                     | Drive<br>End     | Controller<br>End | Daisy Chain<br>End | Controller<br>End | Drive<br>End     |  |  |

| Тор А                                 | Drive<br>Control | Drive<br>Control  | Тор А              | Тор А             | Drive<br>Control |  |  |

| Top B1                                | Drive<br>Write   | Drive<br>Write    | Top B1             | Top B1            | Drive<br>Write   |  |  |

| Тор В2                                | Drive<br>Read    | Drive<br>Read     | Тор В2             | Top B2            | Drive<br>Read    |  |  |

Table 2-7 Connector Legends and Cable Connections

INSTALLATION

2.28 Connect the Control, Write and Read Adapter Paddleboard connectors to J101, J102, and J013, respectively, on the tape transport. (Reference the tape drive manual for details.) Connect the paddleboards to the drive with care. The green connectors are not keyed to the drive connectors. Therefore, it is possible to (1) install the connector backwards or (2) to place the Adapter Paddleboard on the wrong drive connector (e.g., Read and Write Connectors reversed.) Avoid incorrect connection by (1) verifying the function of each drive connector and (2) physically checking the pin orientation of the mating connectors. If possible, secure the paddleboard connectors to the drive connectors with screws. Neatly dress and tie all cables so the installation appears neat and professional.

### INSTALLATION

Figure 2-7. Single Tape Drive Connections

91000471 6/81

91000471 6/81

2-21

INSTALLATION

INSTALLATION

### 2.29 INSTALLATION CHECKLIST

2.30 The installation of the controller is now complete. Doublecheck your installation before testing and operation.

### CHECKLIST

- () Were all items supplied?

- () Did you choose a location for the controller which

- will provide the desired bus priority?

- () Do all cables reach with adequate service loops?

- () Are the computer and tape drives ready?

- () Did you properly set up tape speed including setting Speed A, Speed B, and using the correct VCO Speed Chip?

- () Did you check the address, vector, and bus level

- jumpers?

- ( ) Did you check the jumpers for the priority lines on the computer backplane?

- () Did you install the controller correctly?

- () Did you connect the cables properly?

- ( ) Did you set up the Adapter Paddleboards for proper operation, including:

- 1. Removing termination devices from each tape drive

- Removing terminator chips from the Control and Write Adapter Paddleboards, except the last paddleboards in the daisy-chain

- 3. Setting the configuration switches

- 4. Ensuring that the correct drive jumpers and options are installed?

- () Did you connect the ribbon cables to the Adapter Paddleboards at each drive?

- ( ) Did you connect the Adapter Paddleboards to the tape drives?

# WARNING: BEFORE POWERING THE SYSTEM, BE SURE THAT ALL PARTS ARE PROPERLY CONNECTED

The tape system is now ready for testing and operation.

NOTE: Refer to the supplementary information at the back of the manuals for additional advice.

|    | IBM PACK                                                    | REMOTE DENSITY SELECT                               |

|----|-------------------------------------------------------------|-----------------------------------------------------|

| 1. | STANDARD - Bit 10 in MTRD                                   | 1. STANDARD - Drive Density Switch                  |

| 2. | OPTION 1 - Use of Drive Select-<br>Bit 10 in MTC            | 2. OPTION 1 - Use of Drive Select-<br>Bit 10 in MTC |

| 3. | OPTION 2 - Customer installed<br>jumper or remote<br>switch |                                                     |

When using OPTION 1 either IBM Pack OR Remote Density Select can be opted, NOT both. In order for a customer to have both options, the following are the different combinations.

| IBM PACK    | REMOTE DENSITY SELECT    |

|-------------|--------------------------|

| . Standard  | Standard and/or Option 1 |

| 2. Option 1 | Standard                 |

| 3. Option 2 | Standard and/or Option 1 |

.

|         | ІВМ РАСК | REMOTE DENSITY SELECT | JUMPERS                               |

|---------|----------|-----------------------|---------------------------------------|

| Standar | d        | Standard              | E82 to E83, E84 to E85                |

| Standar | d        | Option 1              | E83 to E85, E82 to E84                |

| Option  | 1        | Standard              | E83 to E85, E84 to E85,<br>E80 to E81 |

| Option  | 2        | Standard              | E82 to E83, E84 to E85,<br>E78 to E79 |

| Option  | 2        | Option 1              | E83 to E85, E82 to E84,<br>E78 to E79 |

# TABLE 2-8 IBM AND DENSITY SELECT JUMPERS

91000471 7/81

# SECTION III PROGRAMMING

# TABLE OF CONTENTS

| PARA-<br>GRAPH |                                                 | PAGE |

|----------------|-------------------------------------------------|------|

| 3.1            | GENERAL                                         | 3-1  |

| 3.3            | PROGRAMMED OPERATIONS                           | 3-1  |

| 3.5            | OPERATION AS A SLAVE DEVICE                     | 3-1  |

| 3.6            | OPERATION AS A MASTER DEVICE                    | 3-2  |

| 3.7            | CONTROLLER REGISTERS                            | 3-2  |

| 3.8            | REGISTER ADDRESSING                             | 3-2  |

| 3.9            | STATUS REGISTER (MTS) 772 520                   | 3-2  |

| 3.10           | COMMAND REGISTER (MTC) 772 522                  | 3-6  |

| 3.11           | BYTE/RECORD COUNT REGISTER (MTBRC) 772 524      | 3-11 |

| 3.14           | CURRENT MEMORY ADDRESS REGISTER (MTCMA) 772 526 | 3-12 |

| 3.15           | DATA BUFFER (MTD) 772 530                       | 3-12 |

| 3.16           | TU-10 READ LINES (MTRD) 772 532                 | 3-12 |

# LIST OF ILLUSTRATIONS

| FIGURE |                                   | PAGE |

|--------|-----------------------------------|------|

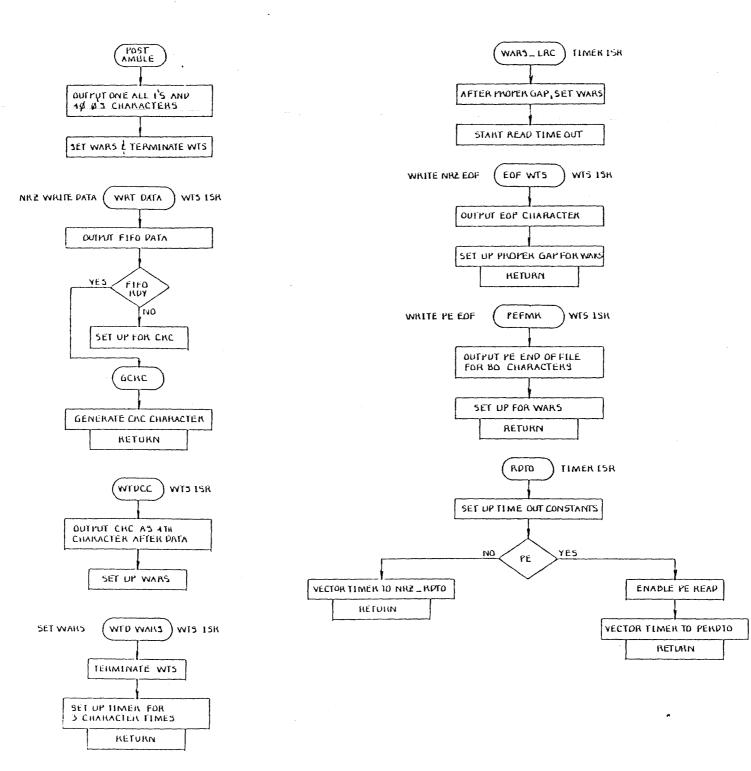

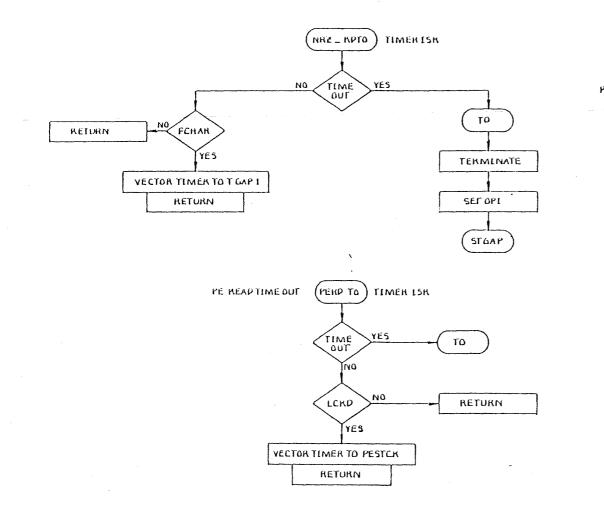

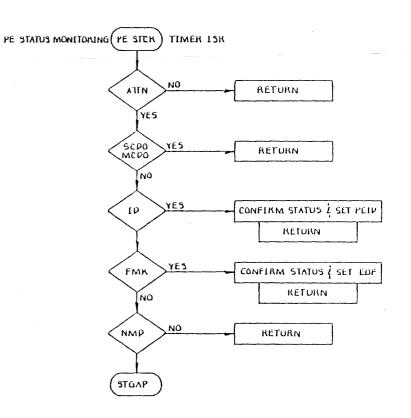

| 3.1    | "WRITE" FLOWCHART                 | 3-15 |

| 3.2    | "WRITE END OF FILE" FLOWCHART     | 3-16 |

| 3.3    | "READ" FLOWCHART                  | 3-17 |

| 3.4    | "SPACE FORWARD/REVERSE" FLOWCHART | 3-18 |

| 3.5    | "REWIND" FLOWCHART                | 3-19 |

|        |                                   |      |

#### SECTION III

#### PROGRAMMING

#### 3.1 GENERAL

3.2 This section contains machine-level programming reference information which describes the registers of the controller. Also contained in this section is information on the operation of the controller, addressing, data transfers, and interrupts. This information will be useful in understanding the operating systems as well as the diagnostic programs. A working knowledge of machine-level programming, along with reference to the information contained in this section, will allow the Customer Engineer to create small diagnostic programs for testing specific functions of the controller.

### 3.3 PROGRAMMED OPERATIONS

3.4 The DEC computer controls devices differently than most other

computer systems. Since registers in peripheral devices are assigned addresses on the bus similar to memory, all instructions that address memory locations are, in effect, I/O instructions. Registers in devices can take advantage of all the arithmetic power of the processor. There is no limit to the number of registers that a device may have, providing great flexibility in the design and control of peripheral equipment.

**3.5 OPERATION AS A SLAVE DEVICE.** All command and status information is transferred with the CPU acting as the master device and the controller acting as the slave. The individual bits within the Command Register control the operations of the device. For example, the command to make the tape

system read a block from tape is provided by properly setting bits 1 through 3 in the Command Register. Status conditions are also handled by the assignment of bits within the registers. All command and status information is written or read by program instructions. Indications of operation complete can be through examination of the status and command registers or by utilizing the system interrupts.

3.6 OPERATION AS A MASTER DEVICE. Once a function command has been issued to the controller, the operation is executed by the controller, utilizing DMA bus transfers to move the data to or from the memory. The Byte/Record Counter Register and the Current Memory Address Register are updated throughout the DMA activity. At the conclusion of an operation, completion is indicated to the CPU through the status bits and also an interrupt (if enabled). The standard interrupt vector (224 octal) is used.

### 3.7 CONTROLLER REGISTERS

**3.8 REGISTER ADDRESSING.** The registers of the tape controller occupy bus address locations 772 520 through 772 532 and are addressed by the CPU with the controller being the slave device. These addresses are placed on the bus in the same way that memory is addressed. The controller latches the address until the completion of the transfer.

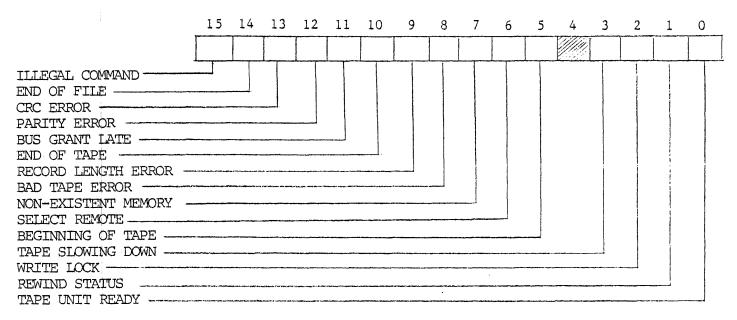

3.9 STATUS REGISTER (MTS) 772 520. The status register contains only read bits, providing the CPU with status indications from both the tape drive and the controller.

91000471 6/81

### REGISTER BIT ASSIGNMENTS:

- 1. <u>MTS BIT 15 ILLEGAL COMMAND (ILL COM)</u> When an illegal command is received, the CU RDY bit remains true, and the command is disregarded. The Illegal Command bit is set for any of the following conditions and sets the ERR bit in the Command Register:

- Any tape command initiated during a tape operation (CU RDY bit is false)

- b. Any tape command where the selected drive is not on-line (Select Remote bit is false).

- c. Any write command on a drive which is file protected.

- d. The drives Ready status line going false during an operation.

- 2. <u>MTS BIT 14 END OF FILE (EOF)</u> The EOF bit is set when a file mark character is detected during a Read, Space Forward or Space Reverse operation. The EOF bit sets the ERR bit in the Command Register.

- 3. <u>MTS BIT 13 CRC ERROR</u> This bit is set when the CRC check fails during, Write, or Write with Extended Record Gap. This bit will

91000471 6/81

set the ERR bit in the Command Register.

- 4. <u>MTS BIT 12 PARITY ERROR (PAE)</u> The Parity Error bit is set when the controller detects a parity error, LRC error, or Postamble error during a Read, Write, or write with Extended Record Gap operation. The PAE bit does not affect the transfer of data. During a Write operation, the entire record will be transferred onto tape or in a Read operation, the entire record will be transferred to memory. The PAE error bit will set the ERR bit in the Command Register.

- 5. <u>MTS BIT 11 BUS GRANT LATE (BGL)</u> The Bus Grant Late bit is set when the controller overflows (or empties) its internal buffer and information is lost during an operation. This bit will also be set during a Read operation when the internal buffer of the controller is not emptied before the tape begins to stop. The ERR bit in the Command Register will be set when the BGL bit is true.

- 6. <u>MTS BIT 10 END OF TAPE (EOT)</u> The End of Tape bit is set when the EOT marker is encountered while the tape is moving in the forward direction. The bit will be reset when the EOT marker is passed while performing a Rewind or Space Reverse operation. The ERR bit in the Command register will be set when the EOT bit is true.

- 7. <u>MTS BIT 9 RECORD LENGTH ERROR</u> (RLE) The Record Length Error bit will be set during a Read operation when the length of the record being read exceeds the memory allocation as indicated by the Byte/Record Counter. When the Byte/Record Counter indicates the

end of the memory allocation, data transfer will stop and the controller will continue to advance the tape to the next interrecord gap. A Record Length Error stops the incrementing of the Byte/Record Counter and the Current Memory Address Register and sets the ERR bit in the Command Register.

- 8. <u>MTS BIT 8 BAD TAPE ERROR (BTE)</u> The Bad Tape Error bit sets when a character is detected (read strobe) during the gap shut-down (or the slowing down) for all operations (except rewind). When a Bad Tape Error is detected, the ERR bit in the Command Register is set.

- 9. <u>MTS BIT 7 NONEXISTENT MEMORY NXM</u>) The Nonexistent Memory bit is set during direct memory operations (when the controller is bus master and is performing data transfers with the bus) and the controller does not receive a Slave Sync response within 14 microseconds after it issues the Master Sync signal. When the Nonexistent Memory error bus time-out is detected, the Read or Write operation is terminated, stopping the tape in the interrecord gap, and setting the ERR bit in the Command Register.

- 10. <u>MTS BIT 6 SELECT REMOTE (SELR)</u> The Select Remote bit is set when the addressed tape drive is on line and cleared when the addressed tape unit is off line, powered off, or disconnected.

- 11. <u>MTS BIT 5 BEGINNING OF TAPE (BOT)</u> The Beginning of Tape bit is set when the tape drive detects the Load Point mark at the beginning of the magnetic tape.

- 12. MTS BIT 4 7 CHANNEL (7 CH) The seven channel bit is not used and is always a  $\emptyset$ .

91000471 6/81

- 13. <u>MTS BIT 3 SLOWING DOWN (SDWN)</u> The Tape Slowing Down (or Settle Down) bit is set whenever the tape unit is stopping after a rewinding operation.

- 14. <u>MTS BIT 2 WRITE LOCK (WRL)</u> The Write Lock bit is set to prevent the software from attempting to write information on the tape when the operator has removed the write-enable ring from the supply reel on the tape drive.

- 15. <u>MTS BIT 1 REWIND STATUS (RWS)</u> The Rewind Status bit is set by the selected drive when it receives a Rewind command from the controller or operator panel and is cleared by the selected drive when the tape arrives at BOT, completing the Rewind operation.

- 16. <u>MTS BIT Ø TAPE UNIT READY (TUR)</u> The Tape Unit Ready bit is set when the selected tape unit is stopped and is cleared when the controller begins to execute a function command.

- 3.10 COMMAND REGISTER (MTC) 772 522. This register receives operational commands from the CPU and provides status information from the con-troller and the tape drive.

COMMAND REGISTER BIT ASSIGNMENTS:

|        |                                                                |                                                                                             | 15                   | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|--------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| Binary | bit                                                            | weights:                                                                                    |                      |    |    |    |    | 4  | 2 | 1 |   |   |   |   |   |   |   |   |

|        | ENSI<br>OWER<br>ATER.<br>RIVE<br>ONTR<br>NTER.<br>XTEN<br>UNCT | TY/PACKING<br>CLEAR<br>AL PARITY<br>SELECT -<br>OLLER REAT<br>RUPT ENAB<br>DED ADDRE<br>ION | DY -<br>LE -<br>SS - |    |    |    |    |    |   |   |   |   |   |   |   |   |   |   |

91000471 6/81

PROGRAMMING

- 1. <u>MTC BIT 15 ERROR (ERR)</u> Set as a function of bits 7-15 of the Status Register (MTS) being set. This bit is cleared as the result of an Initialize or a Go command to the tape unit.

- 2. MTC BITS 14, 13 (DEN 8, DEN 5)

Bit 14 (DEN 8) is used to specify the desired density, as follows:

| (DEN<br>BIT |   | N 5)<br>T 13 |                                 |

|-------------|---|--------------|---------------------------------|

| l<br>Ø      | 2 |              | 800 bpi - NRZI<br>1600 bpi - PE |

- 3. <u>MTC BIT 12 POWER CLEAR (PCLR)</u> This bit provides the means for the processor to clear the controller and the tape drives without clearing other devices in the system. The PCLR bit is always read back by the processor as zero.

- 4. <u>MTC BIT 11 LATERAL PARITY (PEVN)</u> This bit, when set, selects even lateral parity if required for 7-track operations. Otherwise, odd parity is generated and checked during all data transfer operations.

- 5. <u>MTC BITS 10-8 DRIVE SELECT (SLT 1, 2, 4)</u> These bits specify one of the eight possible tape units. All operations defined in the MTC register and all status conditions defined in the MTS register refer to the unit indicated by these bits.

PROGRAMMING

|       |                          |             | DRIVE SELECT LINES |              |

|-------|--------------------------|-------------|--------------------|--------------|

| DRIVE | LOGICAL DRIVE<br>ADDRESS | SL1 (Bit 8) | SL2 (Bit 9)        | SL4 (Bit 10) |

| l     | ø                        | False       | False              | False        |

| 2     | 1                        | True        | False              | False        |

| 3     | 2                        | False       | True               | False        |

| 4     | 3                        | True        | True               | False        |

| 5     | 4                        | False       | False              | True         |

| 6     | 5                        | True        | False              | True         |

| 7     | 6                        | False       | True               | True         |

| 8     | 7                        | True        | True               | True         |

|       |                          |             |                    |              |

- 6. <u>MTC BIT 7 CONTROLLER READY (CUR)</u> This bit is cleared at the start of a tape operation and is set at the end of a tape operation to indicate that the controller is ready to accept a new command.

- 7. <u>MTC BIT 6 INTERRUPT ENABLE (INT ENB)</u> When this bit is set, an interrupt occurs whenever either the Controller Ready bit or the ERR bit goes true or whenever a rewinding tape unit arrives at BOT. In addition, an interrupt occurs for an instruction that sets the INT ENB bit but does not set the GO bit.

- 8. <u>MTC BITS 5, 4 EXTENDED BYTE ADDRESS (YBA 17, XBA 16)</u> These bits access the two most significant bits of Current Memory Address Register, providing an 18-bit memory addressing capability.

| 9. | MTC | BITS  | 3   | -  | 1   | FUNCTION | BITS | - | These | bits | select | one | of | eight |

|----|-----|-------|-----|----|-----|----------|------|---|-------|------|--------|-----|----|-------|

|    | com | and f | unc | ti | ons | •        |      |   |       |      |        |     |    |       |

| Bit 3 | Bit 2 | Bit 1 | OCTAL |               |

|-------|-------|-------|-------|---------------|

| 0     | 0     | 0     | 1     | Off Line      |

| 0     | 0     | 1     | 3     | Read          |

| 0     | 1     | 0     | 5     | Write         |

| 0     | 1     | 1     | 7     | Write EOF     |

| 1     | 0     | 0     | 9     | Space Forward |

| 1     | 0     | 1     | 11    | Space Reverse |

| 1     | 1     | 0     | 13    | Write/E.R.G.  |

| 1     | 1     | 1     | 15    | Rewind        |

- a. <u>Off Line Command.</u> This command, which places the selected drive off-line, is usually preceded by a rewind command after completing all operations on the reel of tape. The controller does not go Busy, leaving it free for use with other drives in the system.

- b. <u>Read Command.</u> The program must specify a byte count (in twos complement or negative form) and an initial address. The controller reads a single record from tape and sends the data via DMA operations to the locations specified by the Address Register until the EOR gap is encountered or the Byte Counter overflows, whichever occurs first. For operations with variable length records, a large byte count ensures that the entire record will be read. The length of the record of unknown size can then be determined after it is read by comparing the Byte Counter at the end of the operation to its initial setting. The setting of BGL status during the record indicates that information has been lost, but data transfers

PROGRAMMING

continue until the byte counter overflows or the EOR gap is detected.

- c. <u>Write Command.</u> The program must specify a (negative) byte count and an initial bus address. If Write Lock is true, GO sets Illegal Command, and the controller rejects the operation. Otherwise, the Controller makes an immediate data request for the first word, and writes the data it receives from the locations specified by the address counter onto the magnetic tape until either the byte counter overflows or a BGL or NXM error occurs, at which time the controller terminates the record.

- d. <u>Write End of File Command.</u> Unless Write Lock is set, GO starts the controller into operation to write a file mark. With Write Lock true, the command is rejected.

- e. <u>Space Forward Command.</u> The program must specify a (negative) byte count equal to the number of records to be spaced. The controller spaces forward over the given number of records unless it encounters a file mark or the end of tape. To space over a file, the program can simply give a zero (maximum) byte count.

- f. <u>Space Reverse Command.</u> The program must specify a (negative) byte count equal to the number of records to be spaced. The controller spaces reverse over the given number of records, but it stops the tape automatically upon encountering a file mark or the Load Point. To space over a file, the program can simply specify a zero (maximum) byte count.

91000471 6/81

- g. <u>Write with Extended Record Gap Command.</u> The operation of this command results in a three and one-half inch length of tape being erased before the data is written. This provides a method of erasing a bad record from a damaged portion of tape before rewriting the data farther down on the tape. A Space Reverse One Record operation generally precedes this command.

- h. <u>Rewind Command.</u> This command initiates a rewind operation in the addressed tape drive, which rewinds the tape onto the supply reel at high speed, and stops at BOT. The controller does not go Busy, leaving it free for further use by the program during the rewind operation.

3.11 BYTE/RECORD COUNT REGISTER (MTBRC) 772 524. The MTBRC is a 16-bit binary counter which is used to count bytes of memory during Read or Write operations, or to count records in a Space Forward or Space Reverse operation. When used in a Write or Write with Extended Record Gap operation, the MTBRC is initially set by the program to the 2's compliment of the number of bytes to be transferred from memory to tape. The MTBRC increments by one immediately after each byte memory access or by two after each word transfer. The MRBRC overflows to zero after the last byte of the record has been read from memory. Bus transfers are terminated by this byte count zero condition.

3.12 When the MTBRC is used in a Read operation, it is set to the 2's complement of a number equal to or greater than the maximum expected record length, indicating the memory allocation for the read data. A Record Length Error (RLE) occurs when the actual record length is greater than the allocated memory, as indicated by the MTBRC overflowing before the EOR gap is detected.

91000471 6/81

PROGRAMMING

3.13 When the MTBRC is used in a Space Forward or Space Reverse operation, it is set to the 2's compliment of the number of records to be spaced over. It is incremented by one each time a record passes the head whether the tape is moving in the forward or reverse direction.

3.14 CURRENT MEMORY ADDRESS REGISTER (MTCMA) 772 526. The MTCMA register contains 18 memory address counter bits. It is used in DMA operations to provide the memory address for data transfers in Read Write and Write with Extended Record Gap operations. Prior to issuing a command, the MTCMA is set to the memory address to be used for the first data transfer. The MTCMA is incremented by one immediately after each byte transfer and by two after each word transfer. Thus, at any instant of time, the MTCMA points to the next higher address than the one which had most recently been accessed. When the entire record has been transferred, the MTCMA contains the address of the word following the final transfer for the record. After Bus Grant Late (BGL) and Non-Existent Memory (NXM) error conditions, the MTCMA contains the address of the location in which the failure occurred.

**3.15 DATA BUFFER (MTD) 772 530.** The data buffer is a register which is used for diagnostic purposes. After the completion of an operation, the 9-bits of the CRC or LRC are placed into the data register and made available to the program, depending upon the TU-10 Register bit 14.

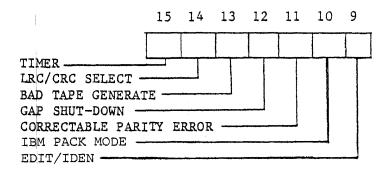

3.16 TU-10 READ LINES (MTRD) 772 532. In addition to its use for diagnostic purposes, this register receives additional command bits from the CPU and provides additional status information from the controller and from the tape drive.

TU-10 READ LINES REGISTER BIT ASSIGNMENTS:

- 1. <u>MTRD BIT 15 TIMER (10KHz)</u> This read-only bit provides the diagnostic program with the output of a 10 KHz timer. This timer bit, having a 50% duty cycle, is used by the diagnostic program for measuring the time duration of tape operations.

- 2. <u>MTRD BIT 14 LRC/CRC SELECT (LRCS)</u> This write/read bit, when set, disables the CRC word from remaining in the data register at the conclusion of an operation, replacing it with the LRC character.

- 3. <u>MTRD BIT 13 BAD TAPE GENERATE (BTG)</u> If set during an operation in progress this write-only diagnostic bit simulates a bad tape error by prematurely setting end-of-record status.

- 4. <u>MTRD BIT 12 GAP SHUT-DOWN BIT (GSB)</u> This bit indicates the controller's post-record positioning time period (Main Sequence 2 or 3) to the diagnostic program.

- 5. <u>MTRD BIT 11 CORRECTABLE PARITY ERROR (CPE)</u> This bit is true in the Read Mode when a phase encoded tape is being corrected because of a single channel dropout.

- 6. <u>MTRD BIT 10 IBM PACK MODE</u> - When this Write/Read bit is set by the CPU, the IBM Pack mode is set, enabling the controller's internal byte swapping circuitry. IBM/industry-compatible tapes may then be read or written by the controller.

7. <u>MTRD BIT 9 EDIT MODE/P.E. IDENTIFICATION (EDIT/IDEN)</u> - When this bit is set by the CPU, the Edit Mode is enabled, issuing the Overwrite command to the tape drive. When read, this bit is true to indicate the Identification Burst of a phase encoded tape is being read by the controller.

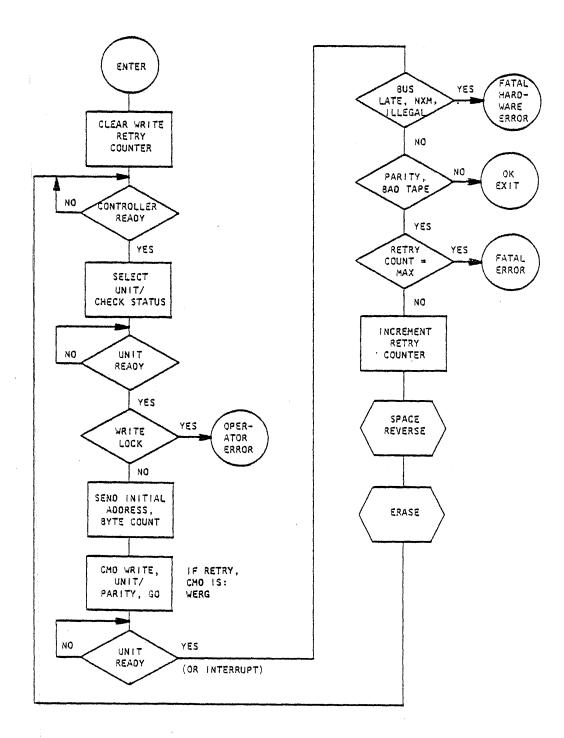

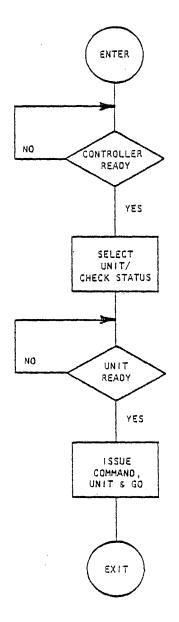

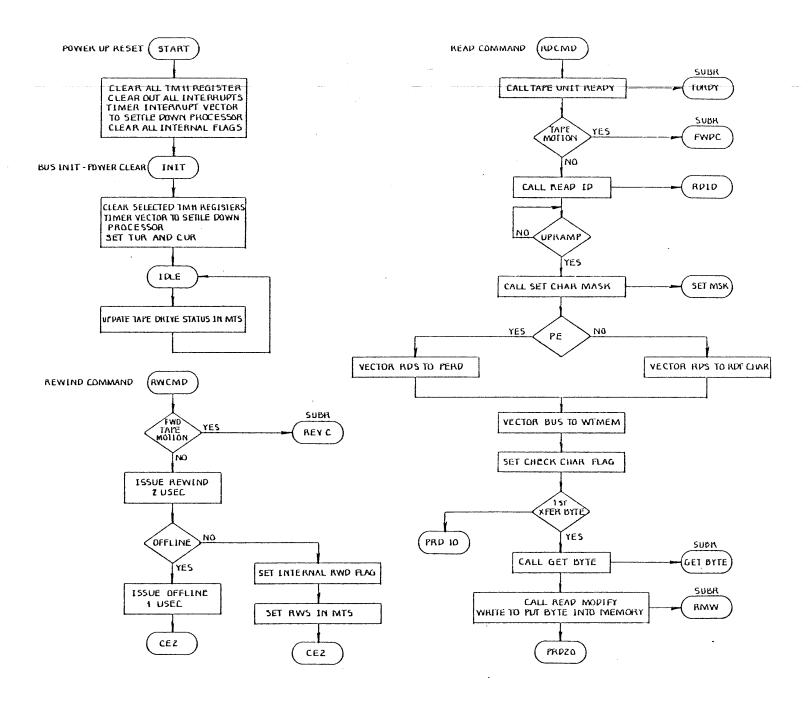

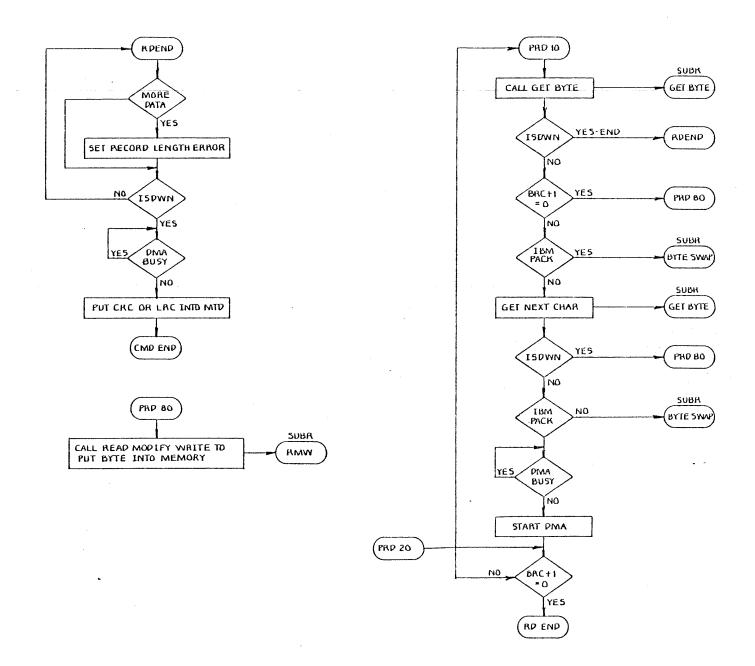

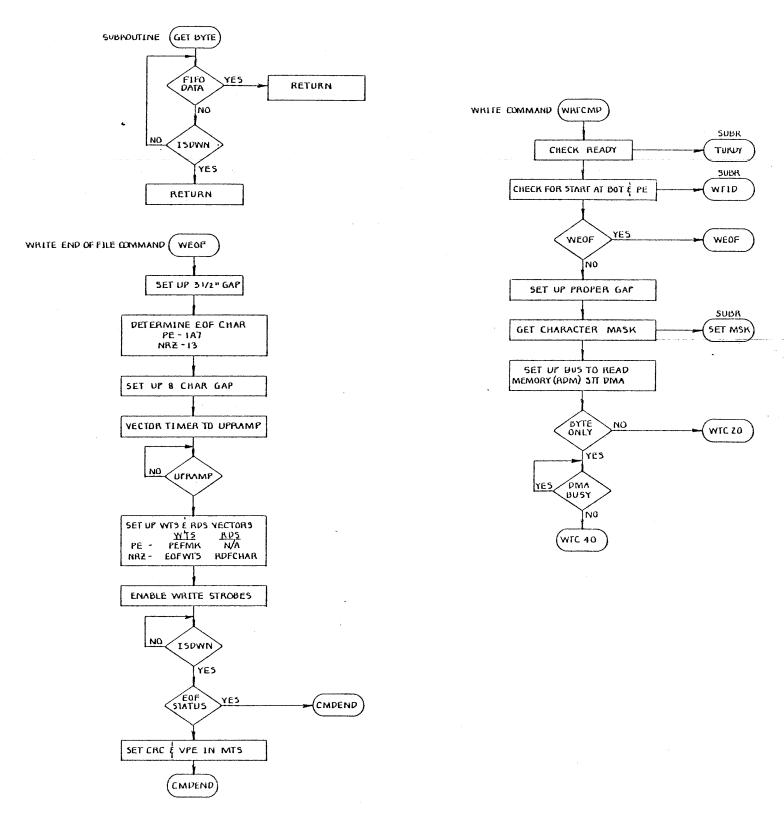

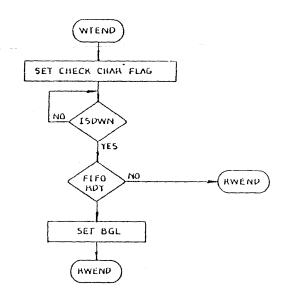

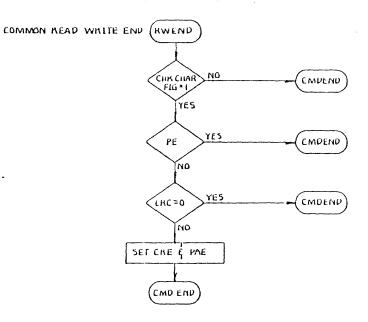

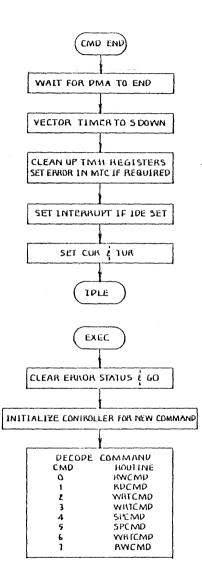

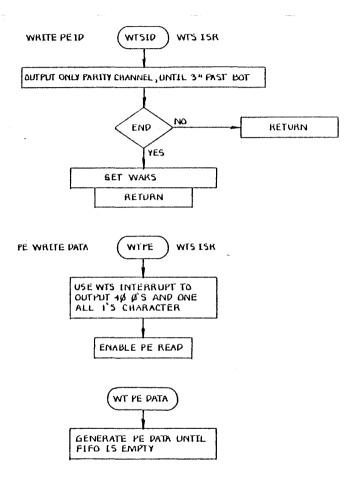

Figure 3-1. "WRITE" Flow Chart

91000471 6/81

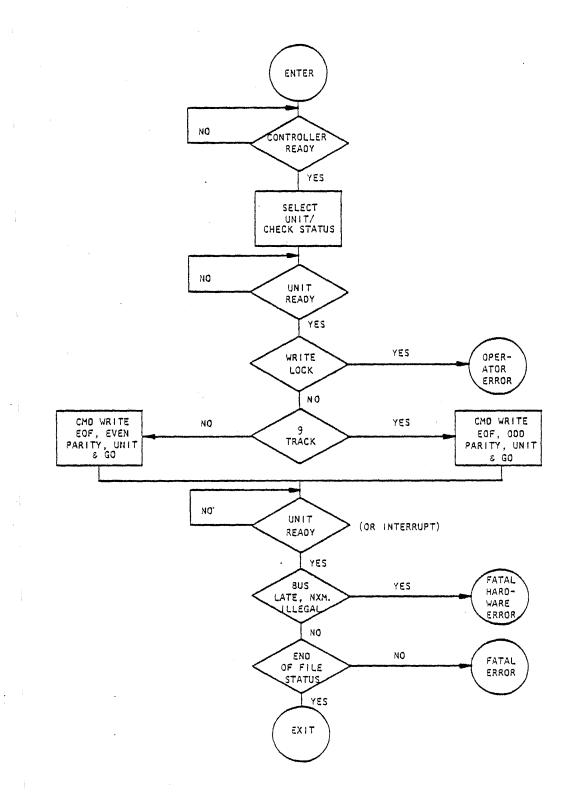

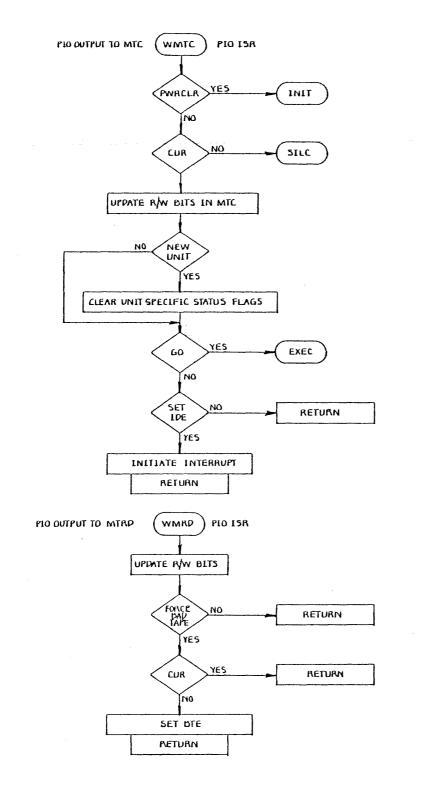

Figure 3-2. "WRITE END OF FILE" Flow Chart

91000471 6/81

1

.

### PROGRAMMING

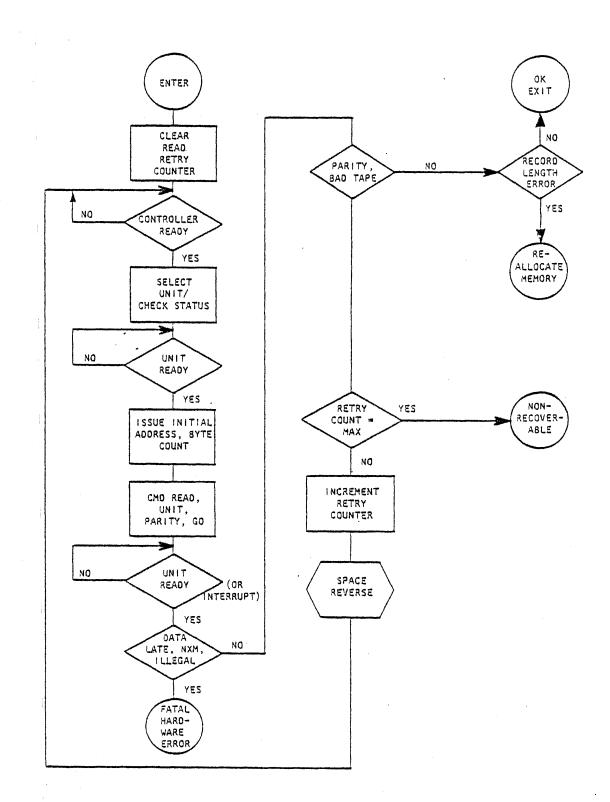

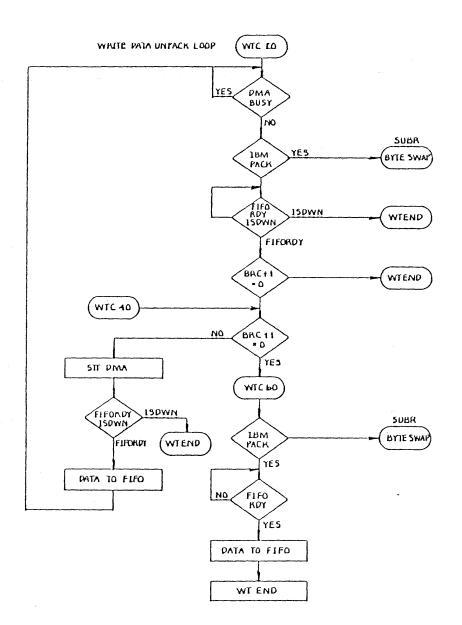

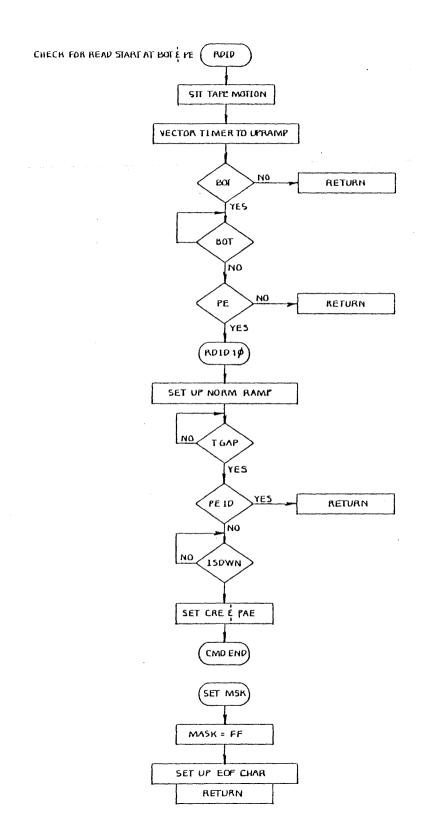

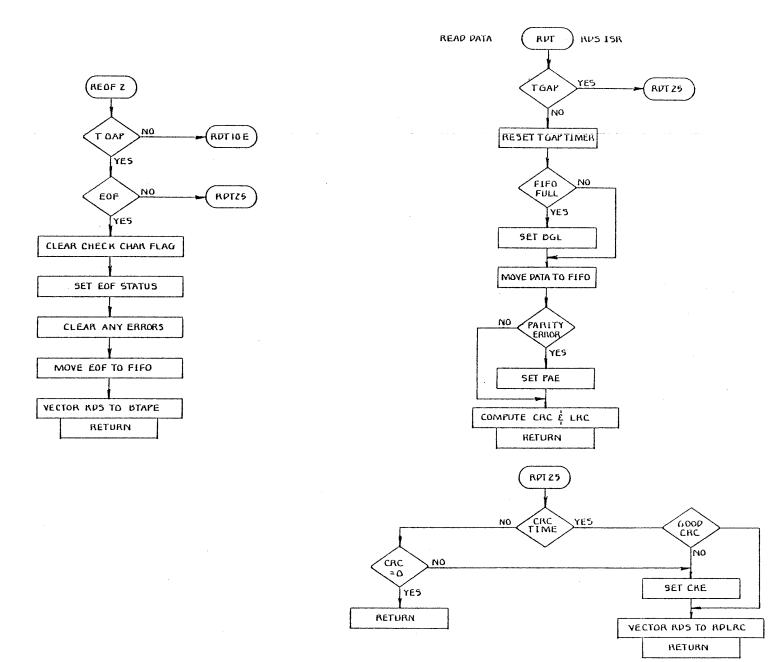

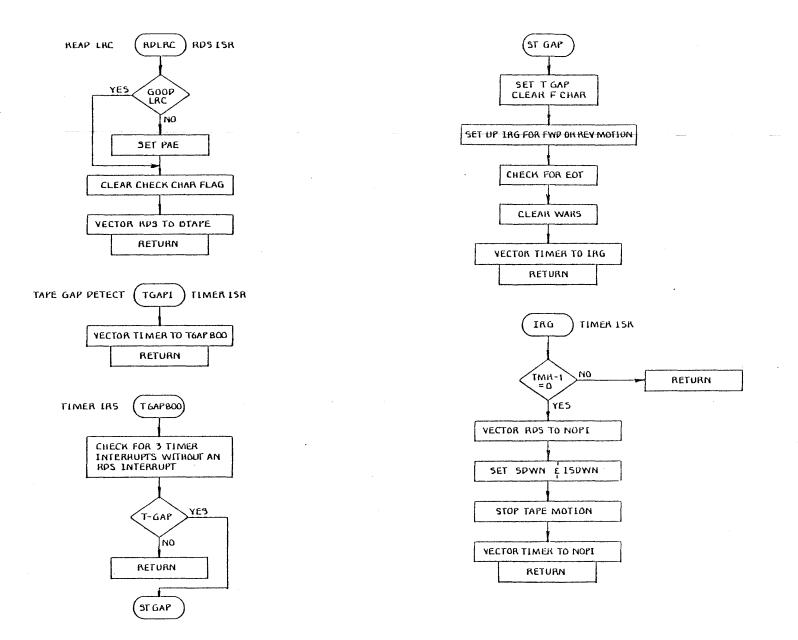

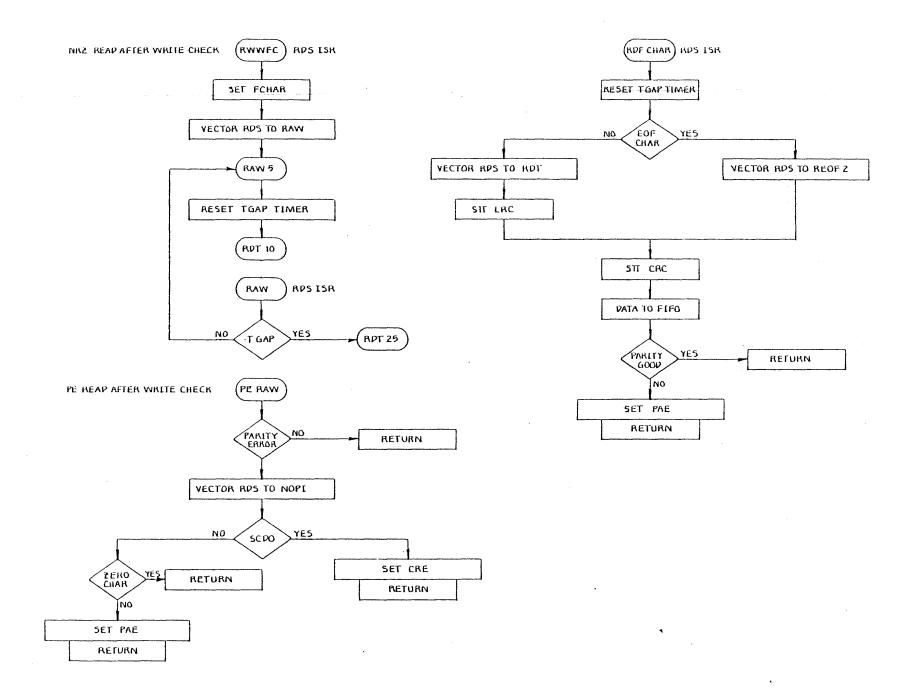

### Figure 3-3. "READ" Flow Chart

### 91000471 6/81

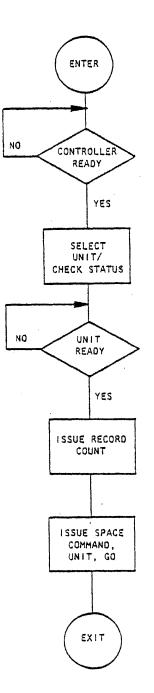

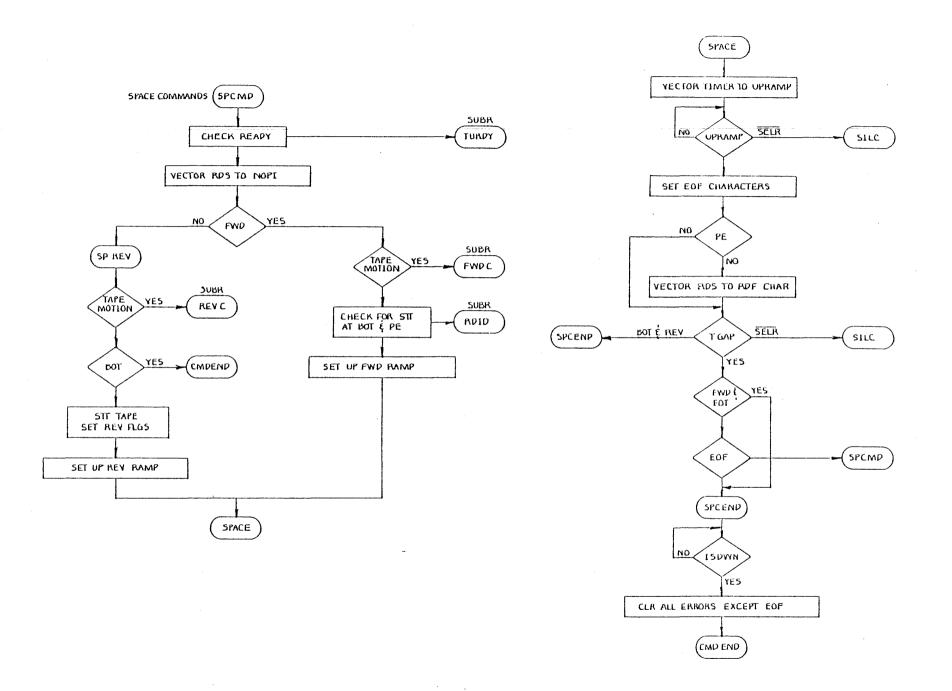

Figure 3-4. "SPACE FORWARD/REVERSE" Flow Chart

91000471 6/81

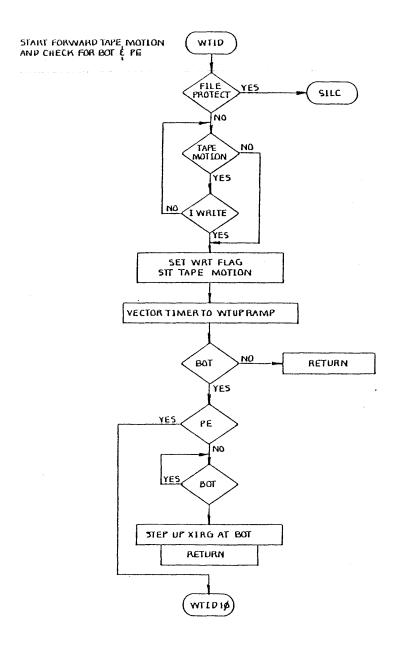

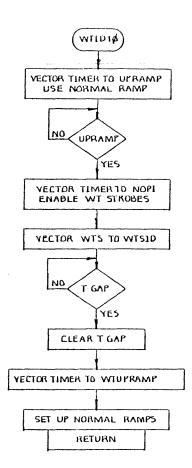

# Figure 3-5. "REWIND" Flow Chart

91000471 6/81

# SECTION IV

# THEORY OF OPERATIONS

Ì

### TABLE OF CONTENTS

| PARA-<br>GRAPH |                                    | PAGE |

|----------------|------------------------------------|------|

| 4.1            | TAPE FORMAT                        | 4-1  |

| 4.3            | NINE-TRACK NRZI FORMAT             | 4-1  |

| 4.5            | NINE-TRACK PE FORMAT               | 4-3  |

| 4.9            | MISSING CHARACTERS                 | 4-5  |

| 4.10           | END-OF-FILE MARK                   | 4-5  |

| 4.11           | TAPE-END MARKERS                   | 4-6  |

| 4.13           | RECORD LENGTH                      | 4-6  |

| 4.14           | EFFECTIVE TRANSFER RATE            | 4-6  |

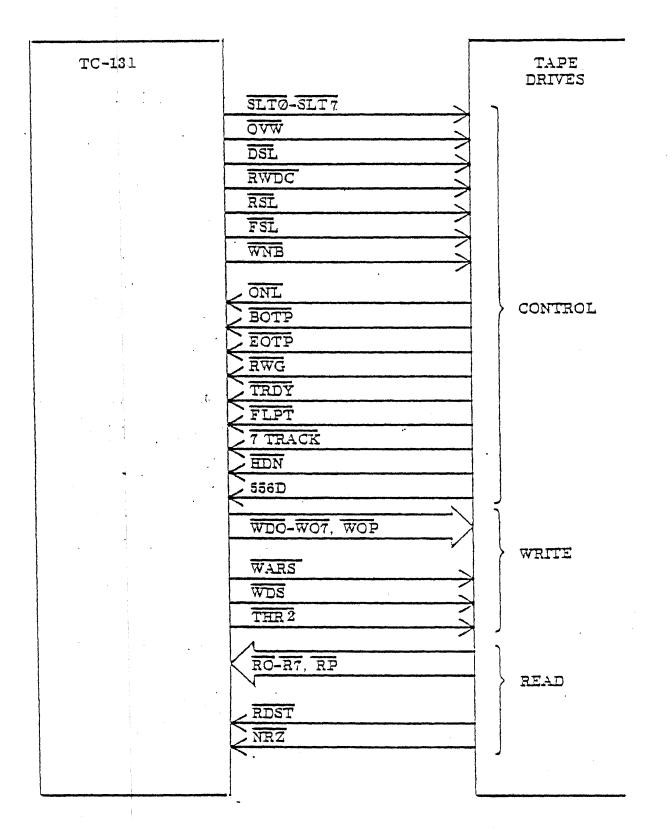

| 4.15           | TAPE DRIVE INTERFACE               | 4-7  |

| 4.16           | INTERFACE SIGNALS                  | 4-7  |

| 4.17           | INTERCONNECTIONS                   | 4-7  |

| 4.18           | DRIVE SELECT LOGIC                 | 4-8  |

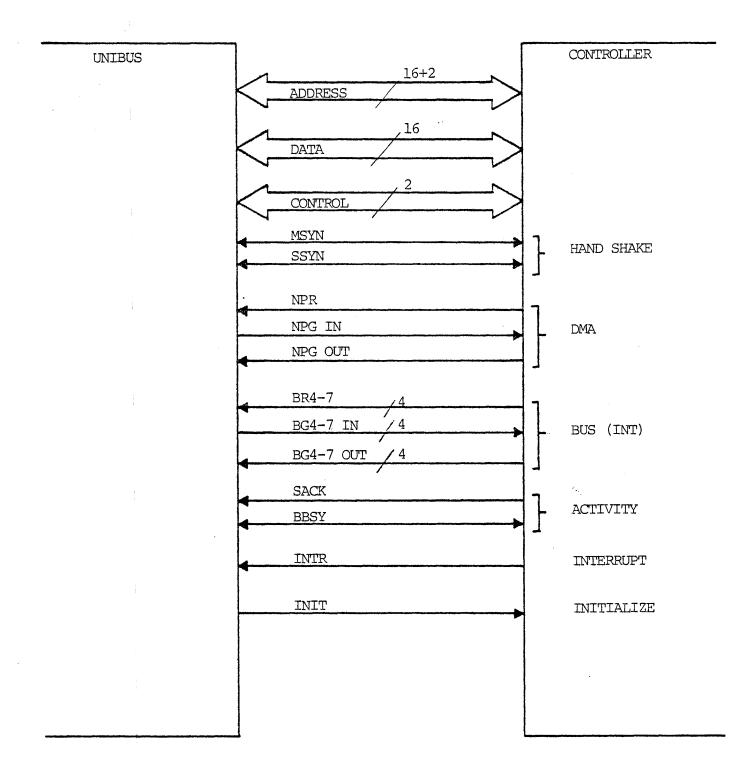

| 4.20           | COMPUTER INTERFACE                 | 4-14 |

| 4.22           | BUS INTERFACE SIGNALS              | 4-14 |

| 4.23           | BUS OPERATIONS                     | 4-17 |

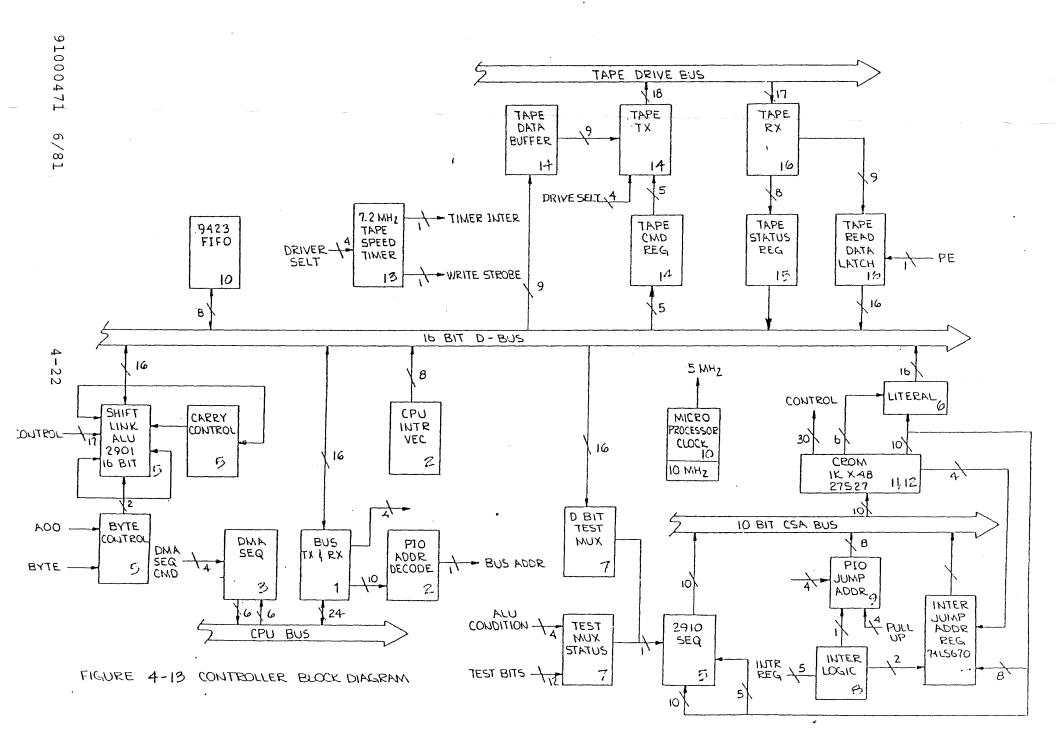

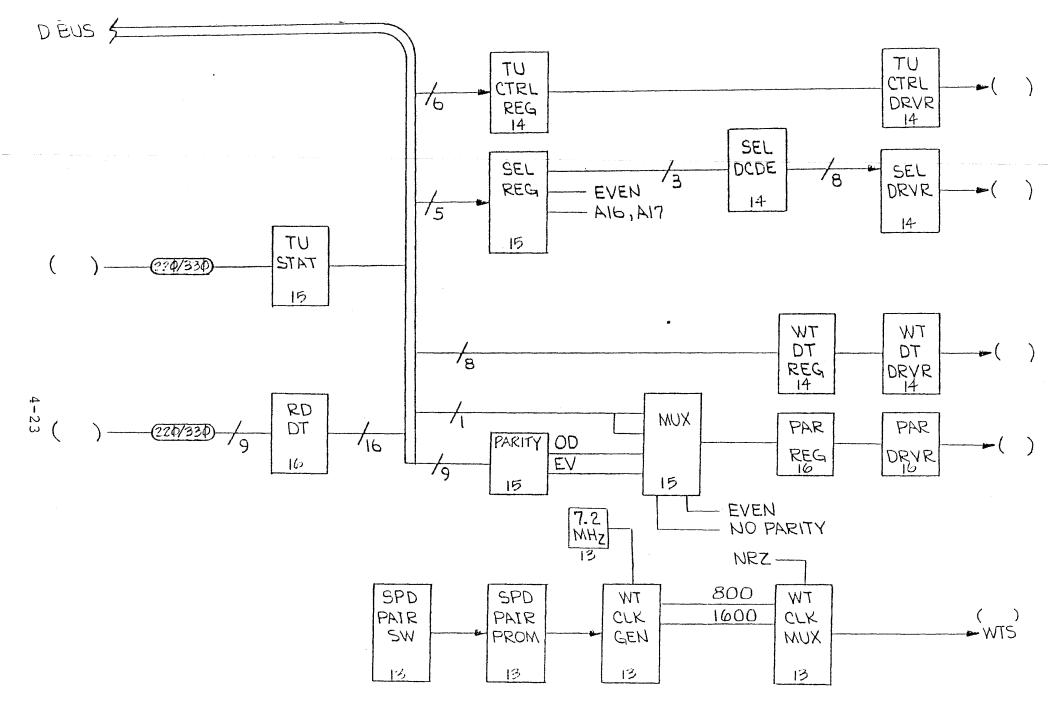

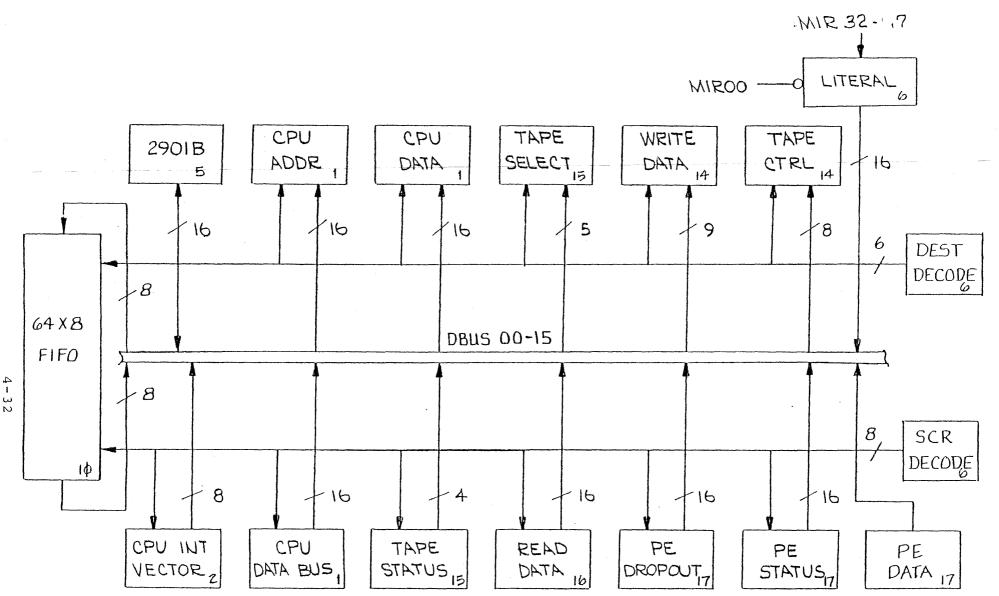

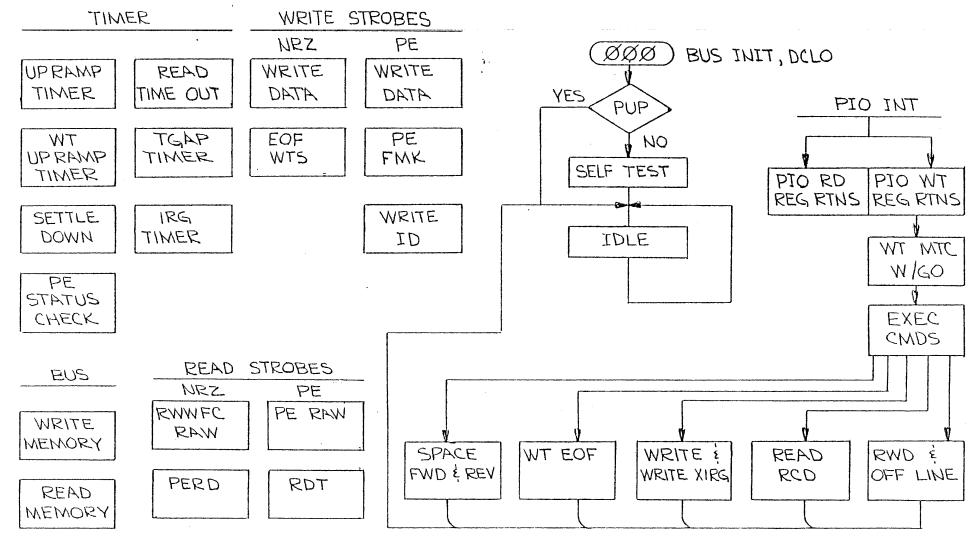

| 4.27           | FUNCTIONAL CONTROLLER ORGANIZATION | 4-21 |

| 4.29           | TAPE DRIVE INTERFACE               | 4-21 |

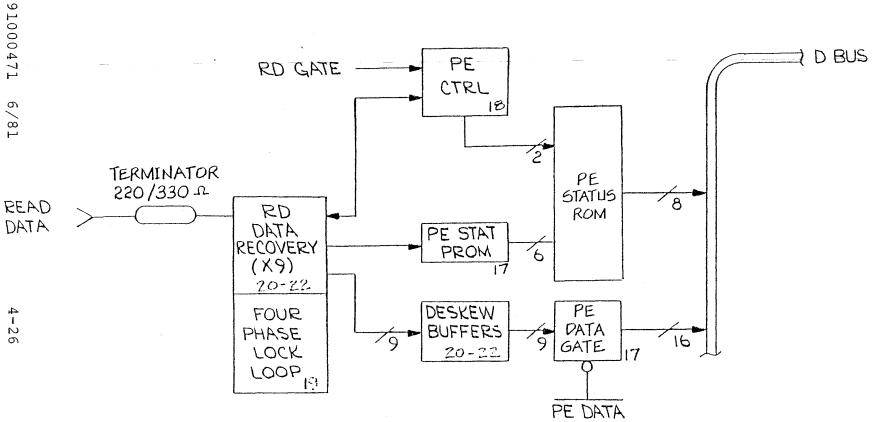

| 4.33           | PHASE ENCODED DATA RECOVERY        | 4-24 |

| 4.35           | PE ACTIVE CONTROL                  | 4-25 |

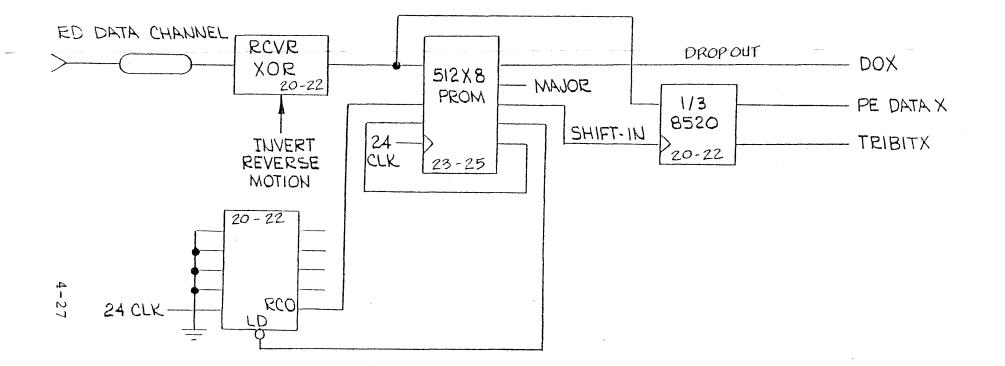

| 4.36           | PE DATA CHANNEL                    | 4-25 |

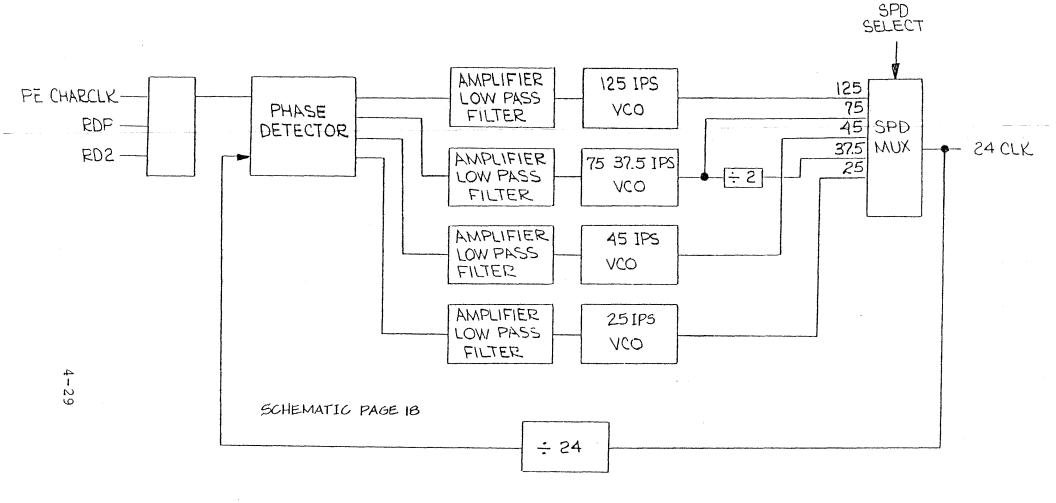

| 4.37           | PHASE LOCK LOOP                    | 4-28 |

| 4.38           | PE STATUS                          | 4-30 |

### TABLE OF CONTENTS

| PARA-<br>GRAPH |                                   | PAGE |

|----------------|-----------------------------------|------|

| 4.39           | MICROPROCESSOR                    | 4-30 |

| 4.41           | DATA PROCESSOR                    | 4-31 |

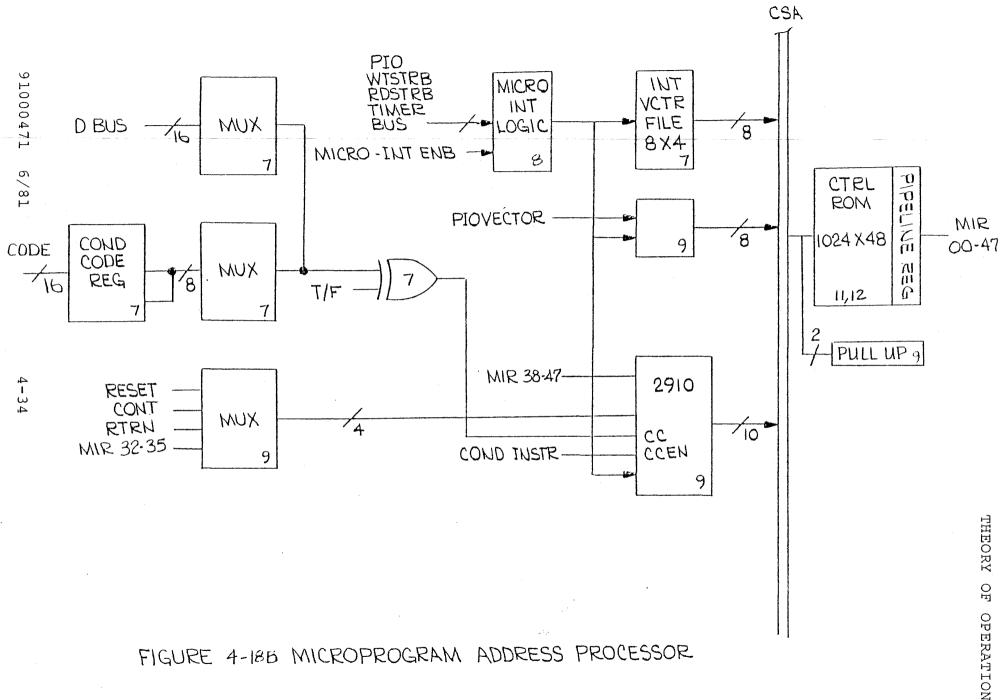

| 4.43           | MICROPROGRAM ADDRESS PROCESSOR    | 4-33 |

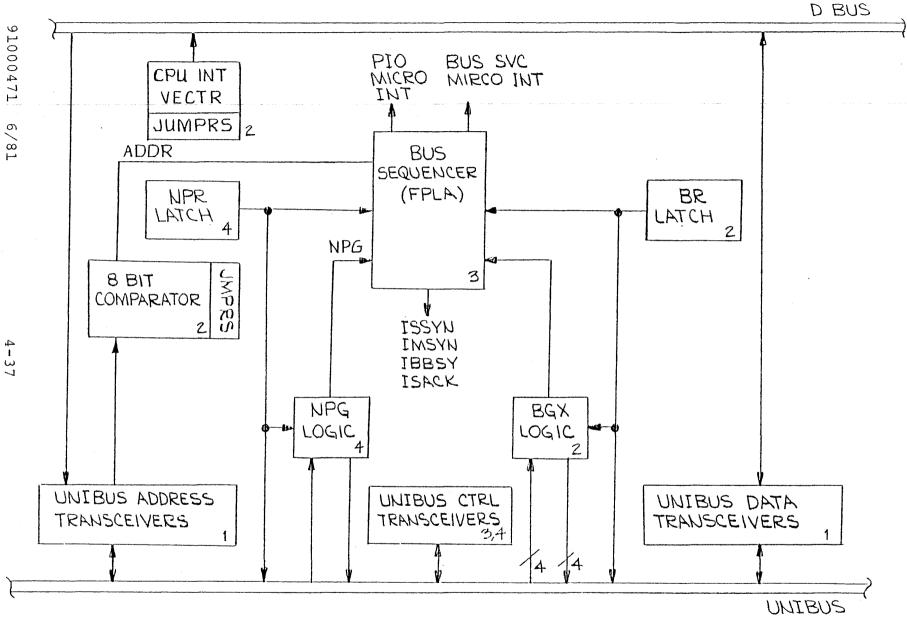

| 4.49           | UNIBUS INTERFACE                  | 4-36 |

| 4.51           | ADDRESS TRANSCEIVERS AND DECODING | 4-36 |

| 4.52           | DATA TRANSCEIVERS                 | 4-38 |

| 4.53           | NON-PROCESSOR REQUESTS (DMA)      | 4-38 |

| 4.54           | BUS REQUEST (INTERRUPT)           | 4-39 |

# LIST OF ILLUSTRATIONS

| FIGURE |                                                                  | PAGE |

|--------|------------------------------------------------------------------|------|

| 4.1    | 9-TRACK NRZI TAPE FORMAT                                         | 4-2  |

| 4.2    | 9-TRACK PE TAPE FORMAT                                           | 4-4  |

| 4.3    | PE AND NRZI RECORDING COMPARISON                                 | 4-5  |

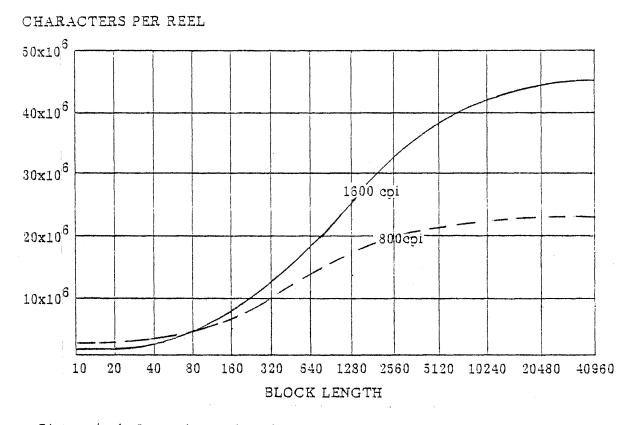

| 4.4    | COMPARISON OF PACKING DENSITY, PHASE ENCODED AND<br>NRZI FORMATS | 4-7  |

| 4.5    | TÀPE DRIVE INTERFACE                                             | 4-9  |

| 4.6    | STANDARD DRIVE SELECT LOGIC                                      | 4-13 |

| 4.7    | DRIVE SELECT LOGIC USING SELECT SWITCHES                         | 4-13 |

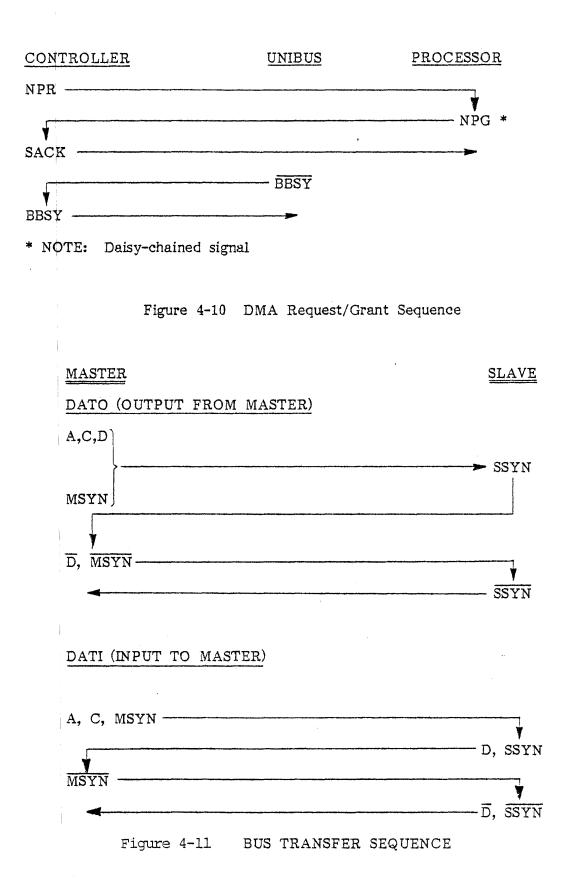

| 4.10   | DMA REQUEST/GRANT SEQUENCE                                       | 4-18 |

| 4.11   | BUS TRANSFER SEQUENCE                                            | 4-18 |

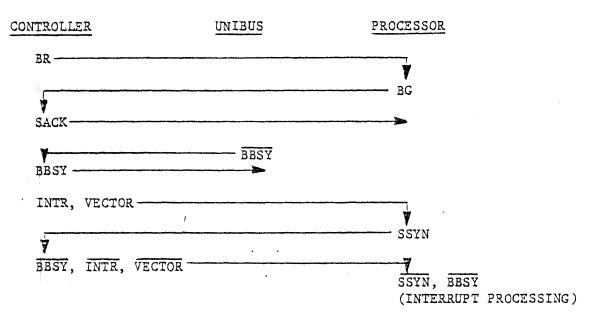

| 4.12   | BUS REQUEST/INTERRUPT SEQUENCE                                   | 4-20 |

#### SECTION IV

#### THEORY OF OPERATION

### 4.1 TAPE FORMAT

4.2 The Western Peripherals Tape Controller interfaces to industry-standard tape drives which write nine or seven bit characters laterally across the tape. The density of the characters written on the tape is determined by the type of tape drive, the density selection made on the tape drive, and (in some cases) the density selection made in the command issued by the CPU. A data block (record) written on tape consists of data characters and error checking characters (or a preamble and postamble). Every data character consists of the data byte plus a parity bit that is generated by the controller to conform with odd or even parity as specified by the program or the format. A record (or block) of data on tape represents the data transferred to or from a block of memory in one Read or Write operation. The controller separates adjacent records by automatically erasing a 0.6 inch (0.75 inch in 7-track) segment of tape to form an interrecord gap (IRG) between them. The controller always stops and starts the magnetic tape in an interrecord gap.

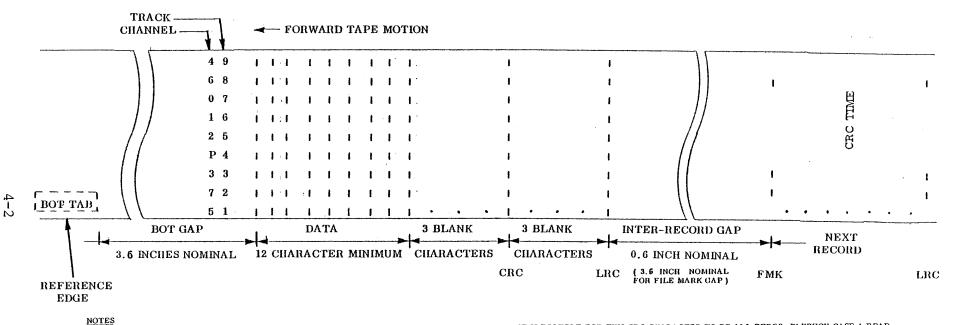

4.3 NINE-TRACK NRZI FORMAT. As shown in Figure 4-1, each data character contains eight data bits and one odd vertical parity bit. Following the last data character, the End of Record gap (three blank characters) is written, followed by a Cyclic Redundancy Check (CRC) character, followed by three more blank characters, concluded by a Longitudinal Redundancy Check (LRC) character. Following the LRC character, a 0.6 inch IRG is written, in which all nine tracks are erased. The LRC character produces an even longitudinal parity in each of the tracks along the length of the tape. Reading or writ-

- 1. TAPE SHOWN WITH OXIDE SIDE UP.

- 2. CHANNELS 0 THROUGH 7 CONTAIN DATA BITS IN DESCENDING ORDER OF SIGNIFICANCE.

- 3. CHANNEL P (PARITY) ALWAYS CONTAINS ODD DATA PARITY.

4. EACH BIT OF THE LRC IS SUCH THAT THE TOTAL NUMBER OF "1" BITS IN THAT TRACK (INCLUDING THE CRC AND THE LRC) IS EVEN. IN THE 9-TRACK FORMAT THE LRC WILL NEVER BE AN ALL-ZEROS CHARACTER.

- 5. IT IS POSSIBLE FOR THIS CRC CHARACTER TO BE ALL ZEROS, IN WHICH CASE A READ DATA STROBE WILL NOT BE GENERATED.

- 6. A FILE MARK IS A SINGLE CHARACTER RECORD HAVING "1" BITS IN CHANNELS 3, 6, AND 7 FOR BOTH THE DATA CHARACTER AND THE LRC. THE CRC CONTAINS ALL ZEROS. THIS RECORD IS SEPARATED BY 3.5 INCHES FROM THE PREVIOUS RECORD AND BY A NORMAL ING (0.6 INCH) FROM THE FOLLOWING RECORD.

- 7. DATA PACKING DENSITY IS FIXED AT 800 BITS PER INCH.

Figure 4-1 9-Track NRZI Tape Format

ing, the controller checks to ascertain that the lateral parity of every data character is odd and that every track has even longitudinal parity.

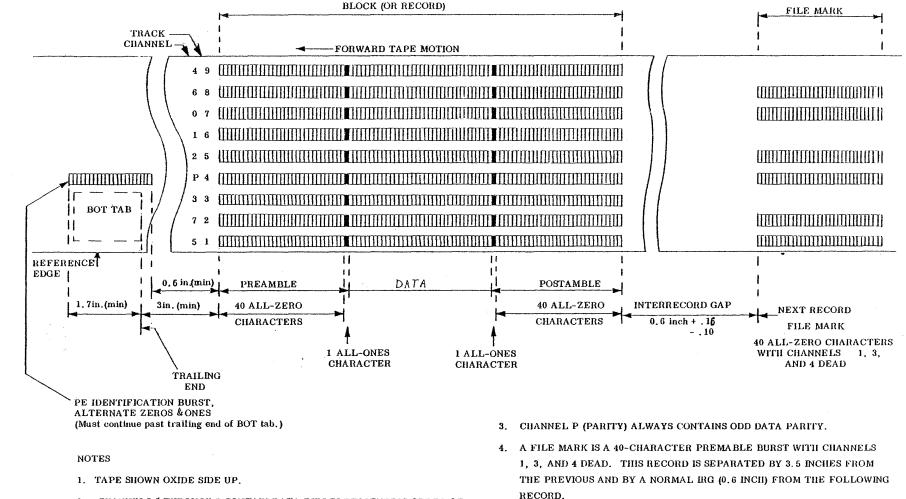

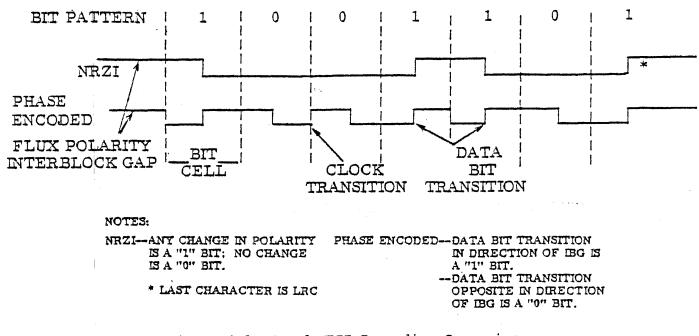

4.4 The 9-track file mark consists of a single character record with a one-bit in channels 3, 6, and 7; the remaining channels contain zeros. The CRC character is left blank, but an LRC character is written which is identical to the file mark character.