# MODEL TC-120/128 TAPE CONTROLLER HARDWARE MANUAL

### 3

# MODEL TC-120/128 TAPE CONTROLLER HARDWARE MANUAL

PUBLICATION NUMBER

01200146 C

### western peripherals

14321 MYFORD ROAD TUSTIN, CALIFORNIA 92680

© 1981 by Western Peripherals, Inc. All Rights Reserved

#### PREFACE

This manual provides information necessary for the installation and maintenance of the Western Peripherals Model TC-120/128

Tape Controller, used with Data General or Data General-emulating computers.

The manual is divided into the following sections:

Section I General Description

Section II Installation

Section III Programming

Section IV Theory of Operation

### SECTION I GENERAL DESCRIPTION

#### TABLE OF CONTENTS

| PARAGR | APH                      | PAGE |

|--------|--------------------------|------|

| 1.1    | DESCRIPTION OF EQUIPMENT | 1-1  |

| 1.3    | DRIVE COMPATIBILITY      | 1-1  |

| 1.6    | OTHER FEATURES           | 1-2  |

| 1.12   | SPECIFICATIONS           | 1-4  |

#### SECTION I

#### GENERAL DESCRIPTION

#### 1.1 DESCRIPTION OF EQUIPMENT

1.2 The Western Peripherals Model TC-120/128 is a universal magnetic tape controller/formatter which is hardware and software compatible with the Data General family of computer systems, providing both NRZI and phase encoded (PE) format capability in a single embedded printed circuit board. The controller is also compatible with all other computers emulating the Data General computer family, using the standard-sized 15 inch x 15 inch circuit boards. The controller contains all interface, control, status, and formatting electronics to emulate the Data General tape subsystem and installs directly into any available card slot in the computer or expansion chassis. The controller board interfaces with the standard backplane and, using a special connector, interfaces to the tape drives through the rear of the computer. Three ribbon cables interconnect the controller with the tape drives through cable adapters, which also provide daisy-chaining capabilities for multiple drive installations.

#### 1.3 DRIVE COMPATIBILITY

1.4 The controller will handle up to eight industry-compatible (IBM/ANSI) read-after-write (dual gap) tape drives. The controller is capable of handling tape drives in varying combinations of speeds, densities, and formats. The controller can select either

of two switch selectable speeds in the range from 6.25 to 125 inches per second (ips).

1.5 Single or dual density NRZI and PE tape drives may be used with densities of 200, 556, or 800 bits per inch (bpi) NRZI 7-track,800 bpi NRZI 9-track, and 1600 bpi PE 9-track (PE mode not available in Model TC-128. Software density control is available for dual density operation. The controller is compatible with all industry-standard tape drives.

#### 1.6 OTHER FEATURES

- 1.7 The controller is compatible with the I/O bus and with existing magnetic tape software, utilizing the standard magnetic tape controller registers. Enhancements of the standard registers provide other features which add to the usefulness of the controller. Transfers of register information between the tape controller and the computer are made under I/O transfer control via device code #22. Device code #62 may be used for a second tape system if over eight tape drives are used or other system requirements are such that a second controller must be used. The device code may be changed by moving a jumper. Data transfers are in a 16-bit word format via the bus.

- 1.8 In 7-track, 4-6-6 bit packing allows a full 16-bit word memory dump transfer to and from magnetic tape. Accomplished without special software, the automatic read and write on-the-fly feature allows non-stop operation when doing consecutive read or write operations. The controller writes and recognizes IBM/ANSI-compatible end-of-file tape marks.

The controller provides an "EDIT" feature which allows a record anywhere on a previously recorded tape to be replaced with an updated record.

- 1.9 66 bytes of data buffering provide flexibility in assigning priorities when programming data transfers to the computer. The tape motion control, Cyclic Redundancy Check character (CRC) and the Longitudinal Redundancy Check character (LRC) generation, LRC checking, inter-record gap generation and status reporting are included. All write clocks and delay times are derived from a crystal-controlled oscillator. No screwdriver adjustments are required or provided. While the controller can read or write only in the forward direction, it can space (or move to a new position) in both directions.

- 1.10 The controller may address up to eight drives but can only read, write or space one drive at a time, except for the Rewind Command. This function requires only initiation by the controller. That transport can then be left to rewind while the controller services another drive.

- 1.11 Programmed I/O transfer instructions are used to specify the starting word address in computer memory, the number of words to transfer, the drive number, and the function to be performed. Programmed I/O transfer instructions are also used to transfer status and address data from the tape controller to the computer. Data word transfers during read and write operations are accomplished by the controller, using the computer's data channel process.

#### 1.12 SPECIFICATIONS

1.13 The following information summarizes the specifications of the tape controller.

#### 1. Computer Interface

- a. Compatibility The controller is fully hardware and software compatible with the Data General computer family and all other computers emulating Data General computers.

- b. Emulation The controller emulates the standard Data General tape subsystem.

- c. The controller interfaces directly with the I/O bus through a standard board slot.

- d. Controller Bus Location The controller may be located in the bus in any slot after the Processor, Memory, and Terminal I/O boards. Bus priority signals must be available to the controller.

- e. Bus Loading One bus load, using DG-compatible interfacing circuitry.

- f. Tape commands:

Write

Read

Rewind

Space Forward

Space Reverse

Write End-of-File Mark

Erase

g. Other Mode Controls and Registers:

Memory Address

Word Count

Select Threshold Two

Select Edit Mode

Select Density

Select Pack Mode (7 track 4-6-6 memory dump mode)

Select Even Parity (7 track only)

Select Unit Number

Select Test Mode

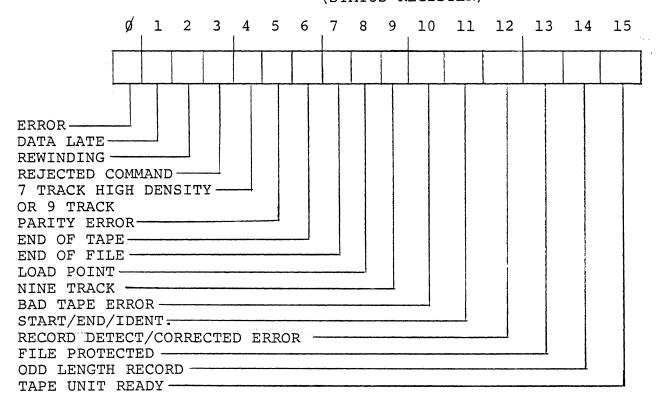

h. Controller status:

Error Flag

Data Late

Rewinding

Illegal

High Density

Parity Error

End-of-Tape

End-of-File

Load Point

9-track

Bad Tape

Start-End/Identification Status

First Character Detected

File Protected

Odd-Length Record

Tape Unit Ready

Memory Address

Maintenance Register (CRC-LRC)

i. Device Code:

Standard - 22

Alternate - 62

2. Format Compatibility

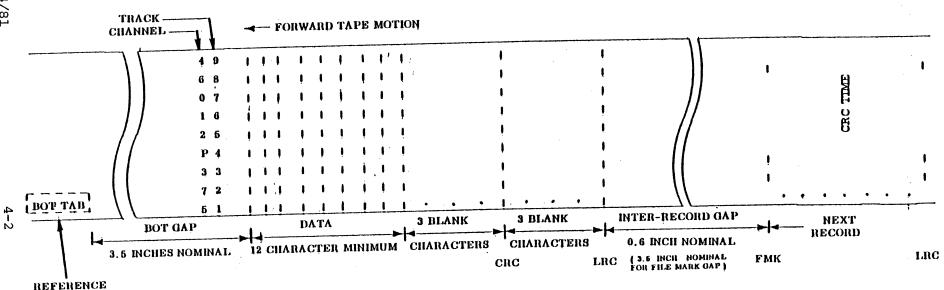

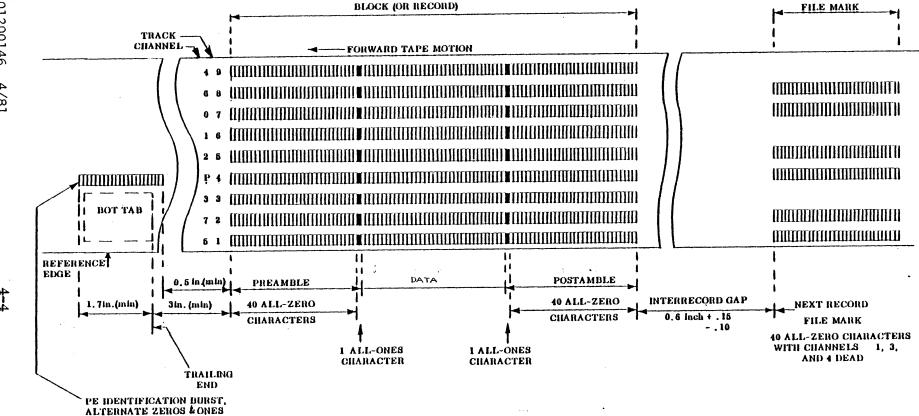

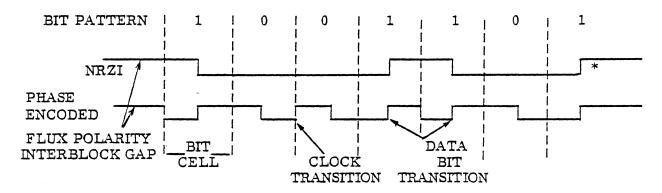

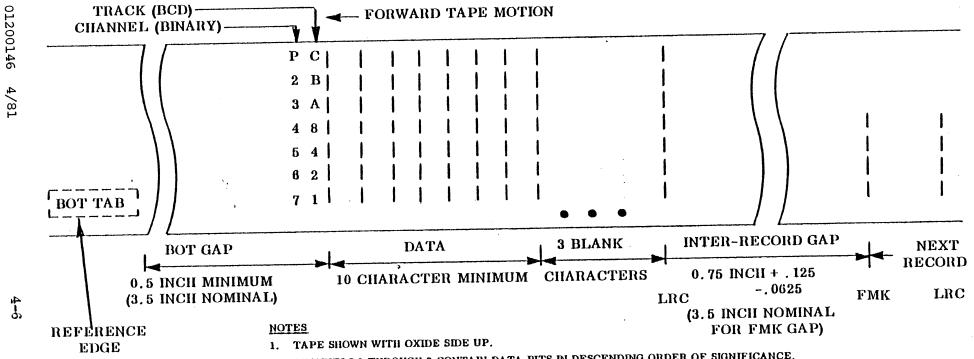

Fully compatible with the industry-standard IBM/ANSI digital tape recording format as described in ANSI specifications X3.22-1973 and X3.39-1973.

- 3. Drive Compatiblity

- a. Designed to be compatible with the industry standard drives

- b. Read-after-Write only (dual gap head)

- c. Single or dual density (operator or software switchable)

- 4. Tape Speed

- 6.25 ips, 12.5 ips, 18.75 ips, 25 ips, 37.5 ips, 45 ips, 75 ips, 125 ips. Any two speeds may be set through switches on the controller board. For the P.E. format, the speed difference is limited to: 6.25-18.75 ips, 12.5-37.5 ips, 12.5-45 ips, 18.75-45 ips, 25-75 ips, or 75-125 ips.

- 5. Format and Density

- a. NRZI 7-Track 200/556/800 BPI

- b. NRZI 9-Track 800 BPI

- c. PE 9-Track 1600 BPI (Not available in Model TC-128)

#### 6. Data Transfers

a. 9-Track

The eight data bits of each tape character are transferred to or from the bus as a 16-bit computer word.

#### b. 7-Track

- (1) Unpacked (normal mode)

Tracks B, A, 8, 4, 2 and 1 contain the 6-bit tape characters. Two tape characters are transferred to the CPU for each computer word.

- (2) Packed (4-6-6 memory dump mode)

One 4-bit and two 6-bit tape characters are transferred for each computer word.

- c. Bus transfers for register information or tape data consist of 16-bit word transfers.

- 7. Drive Configuration

- a. Up to eight drives in daisy chain configuration

- b. One or two tape drive speeds. (All 7-Track drives must be assigned to Speed "A".)

- c. Single or multiple formats and densities on the daisy-chain.

#### 8. Hardware

a. Single standard-sized printed circuit board mounted within the computer's card cage (or expansion cabinet)

- b. Computer backplane adapter/connector board (Eclipse computers require a special backplane adapter because of limited space)

- c. Three interface cables and adapter boards per tape drive

#### 9. Other Features

- a. Edit mode for correcting pre-recorded tapes

- b. Crystal controlled clocks

- c. Phase locked loop read tracking in the PE mode

- d. No screwdriver adjustments

#### 10. Error Handling

- a. Generates and checks vertical parity, LRC, preambles and postambles

- b. Generates CRC characters

- c. Detects dead track errors

- d. Corrects PE single channel dropouts

#### 11. Data Buffering

The internal buffer between the bus and the tape drive provides 66 bytes of buffering to allow for transfers between the controller and the tape drive during times that the computer bus is unable to service the controller. All data contained in the buffer will automatically be transferred before the operation is aborted. During read operations, the buffer allows a check of false postambles in 9-track PE mode when a single dead track occurs. During read operations, the buffer must be emptied within the maximum times

specified below, otherwise a data late error condition is reported.

Maximum Time After End of Record

| Tape  | Speed | 7-Track  | 9-Track NRZI | 9-Track PE |

|-------|-------|----------|--------------|------------|

| 12.5  | ips   | 15.00 ms | 3.00 ms      | 4.10 ms    |

| 25.0  | ips   | 7.50 ms  | 1.50 ms      | 2.05 ms    |

| 37.5  | ips   | 5.00 ms  | 1.00 ms      | 1.37 ms    |

| 45.0  | ips   | 4.17 ms  | 0.83 ms      | 1.14 ms    |

| 75.0  | ips   | 2.50 ms  | 0.50 ms      | 0.68 ms    |

| 125.0 | ips   | 1.50 ms  | 0.30 ms      | 0.41 ms    |

#### 12. Non-Stop "On-the-Fly" Tape Operation

This feature provides continuous tape motion when consecutive tape commands require tape motion in the same direction on the same tape drive. Under these conditions, the controller will time through the interrecord gap (IRG) in the read mode, or will write the IRG in the write mode and execute the next command without stopping the tape.

#### 13. Power Requirements

- a. Source Computer or Expansion Chassis power supply

- b. + 5VDC + 5% @ 4.8 amps

+15VDC + 10% @ 50 milliamps (backplane pin Al0)

#### 14. Physical Specifications

a. Size 15-inch square (standard DG-sized) single printed circuit board fits standard Data

General I/O bus card slot

- b. Weight (approximate)

- a. Controller Board 30 oz. (0.85 kg)

- b. Cables and Adapters 26 oz. (0.74kg) per drive

- c. Environment

- (1) Operational Temperature 0 to 55 degrees C

- (2) Storage Temperature 10 to 70 degrees C

- (3) Relative Humidity 10 to 90 percent

(without condensation)

# SECTION II INSTALLATION

#### TABLE OF CONTENTS

| PARA-<br>GRAPH |                                                   | PAGE |

|----------------|---------------------------------------------------|------|

| 2.1            | GENERAL INFORMATION                               | 2-1  |

| 2.4            | Unpacking and Inspection                          | 2-1  |

| 2.5            | System Components                                 | 2-2  |

| 2.6            | PREPARATION                                       | 2-3  |

| 2.8            | SYSTEM SET-UP                                     | 2-3  |

| 2.10           | Tape Speed Selection                              | 2-5  |

| 2.11           | Configuring the System for Dual Speed Operation   | 2-5  |

| 2.12           | Configuring the System for Single-Speed Operation | 2-5  |

| 2.13           | VCO Speed Chip (For PE Operation)                 | 2-7  |

| 2.14           | Extended Address Feature                          | 2-8  |

| 2.15           | Expanded Word Count Feature                       | 2-9  |

| 2.16           | Device Code Selection                             | 2-9  |

| 2.17           | CONTROLLER INSTALLATION                           | 2-9  |

| 2.19           | Priority Jumpers                                  | 2-9  |

| 2.20           | Other Backplane Considerations                    | 2-10 |

| 2.21           | Cabling                                           | 2-10 |

| 2.22           | Controller Cable Connections                      | 2-18 |

| 2.23           | TAPE DRIVE INSTALLATION                           | 2-18 |

| 2.24           | Adapter Paddleboard Set-Up                        | 2-18 |

| 2.25           | Terminators                                       | 2-18 |

| 2.26           | Configuration Switches                            | 2-18 |

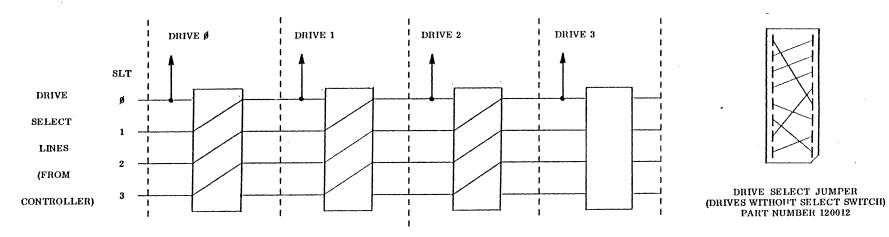

| 2.27           | Drive Select Jumpers                              | 2-21 |

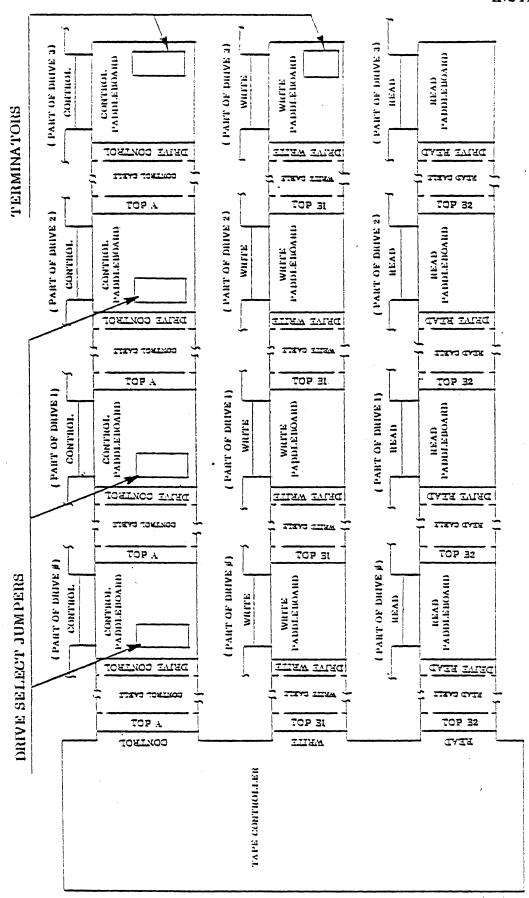

| 2.28           | Tape Drive Interconnections                       | 2-21 |

| 2.30           | INSTALLATION CHECKLIST                            | 2-27 |

#### LIST OF ILLUSTRATIONS

| FIGURE |                                                                                  | PAGE     |

|--------|----------------------------------------------------------------------------------|----------|

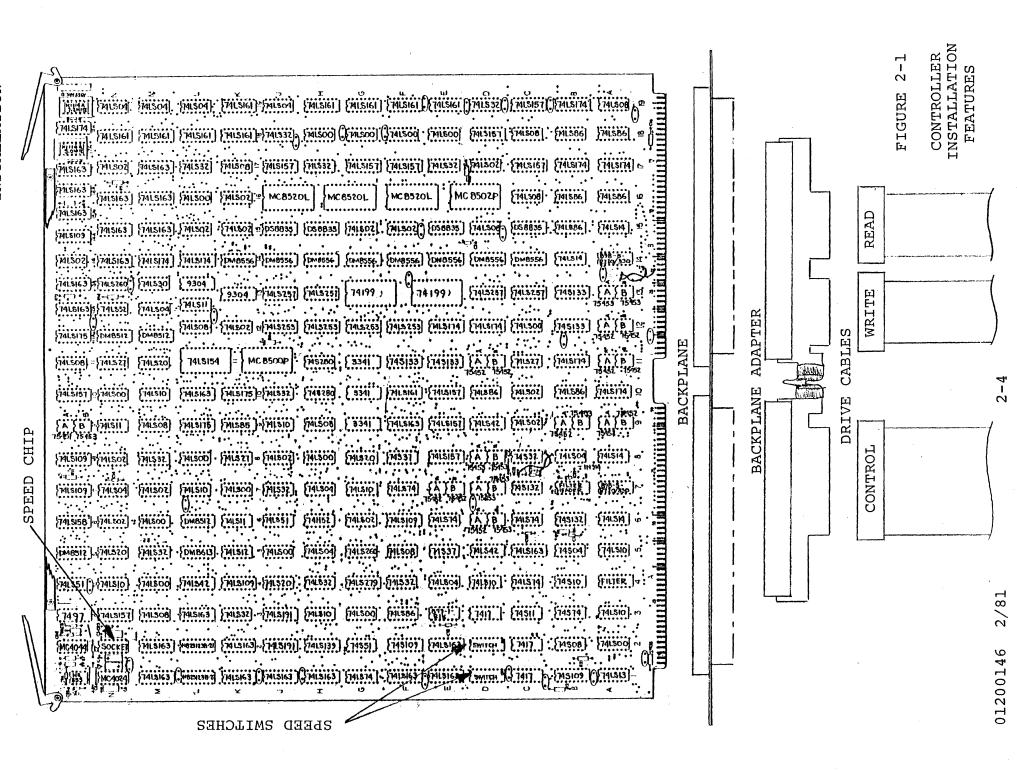

| 2.1    | Controller Installation Features                                                 | 2-4      |

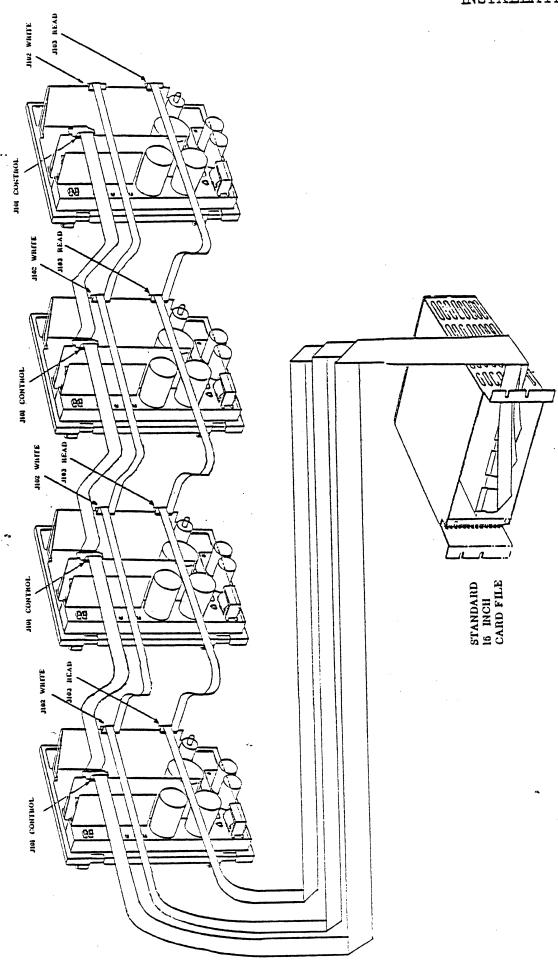

| 2.2    | Example of Typical System Installation                                           | 2-6      |

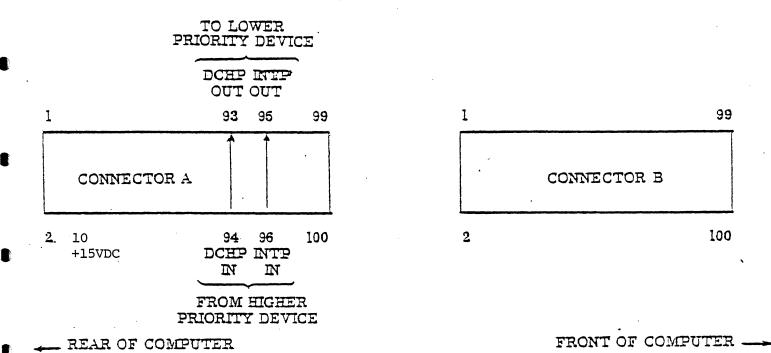

| 2.3    | Computer Backplane Connector                                                     | 2-10     |

| 2.4    | Standard Backplane Adapter                                                       | 2-16     |

| 2.5    | Eclipse Cables                                                                   | 2-17     |

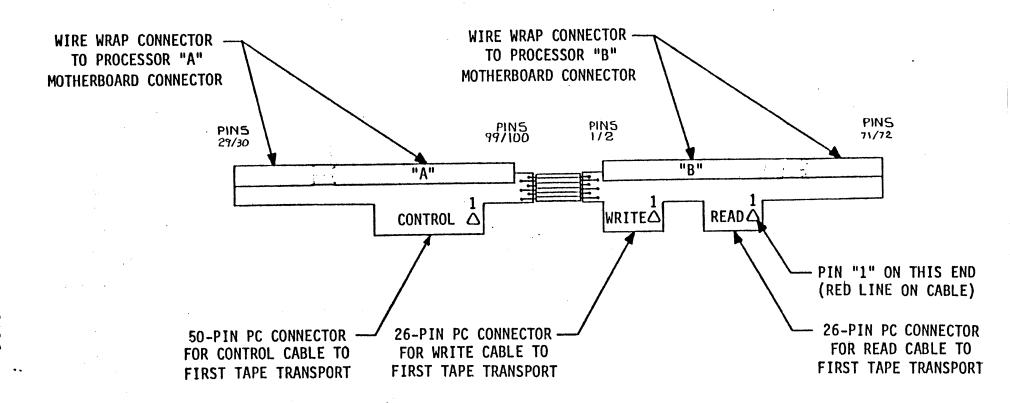

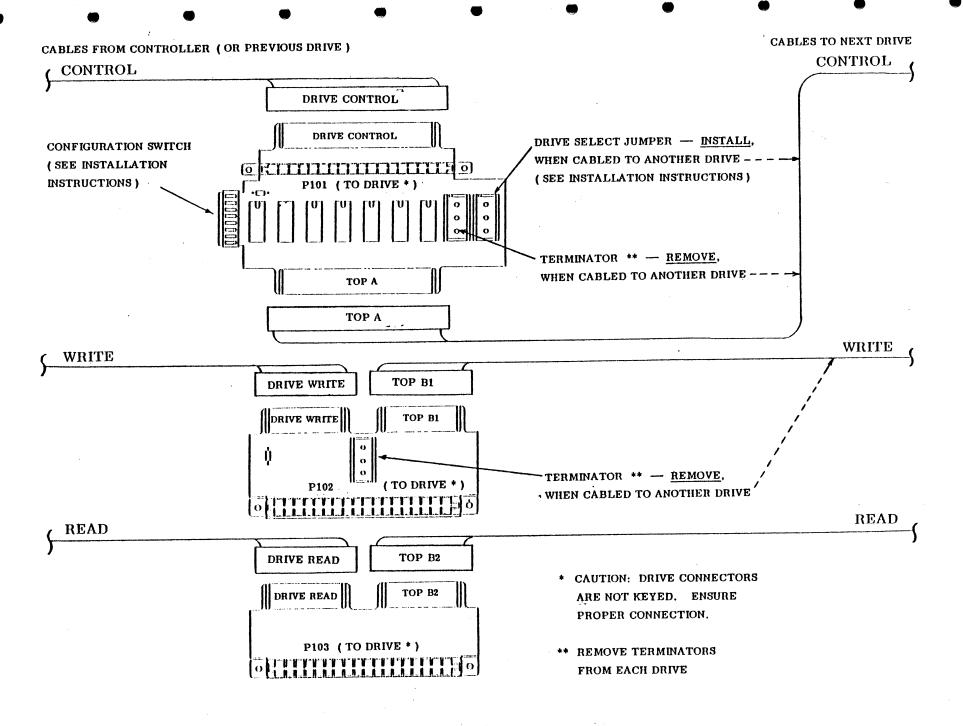

| 2.6    | Details of Adapter Installation                                                  | 2-19     |

| 2.7    | Drive Select Jumpers                                                             | 2-22     |

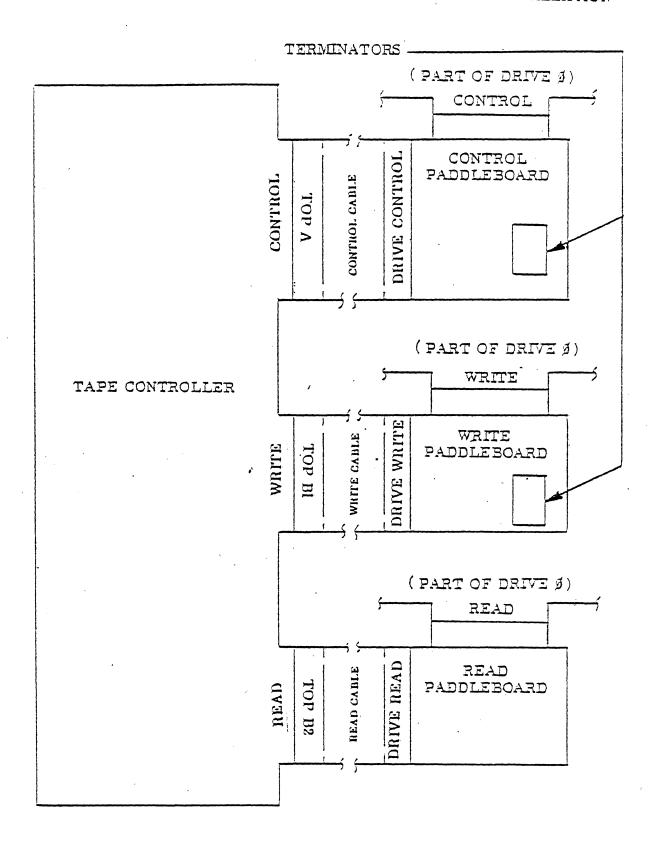

| 2.8    | Single Tape Drive Connections                                                    | 2-25     |

| 2.9    | Tape Drive Daisy-Chain Connections                                               | 2-26     |

|        |                                                                                  |          |

|        |                                                                                  |          |

| TABLE  |                                                                                  | PAGE     |

| 2.1    | Speed Selection                                                                  | 2-7      |

| 2.2    | Speed Chips                                                                      | 2-8      |

| 2.3    | Nova Tape Interface For Nova, Nova 1200, Nova 800, Super Nova, and Super Nova SC | 2-12, 13 |

| 2.4    | Nova Tape Interface for Nova 1210, Nova 1220, and Nova 820                       | 2-14, 15 |

| 2.5    | Configuration Switches                                                           | 2-20     |

| 2.6    | Control Adapter Select Options                                                   | 2-23     |

| 2 7    | Connector Legends and Cable Connections                                          | 2-23     |

#### SECTION II

#### INSTALLATION

#### 2.1 GENERAL INFORMATION

- 2.2 This section provides information necessary to successfully set up and install the TC-120 Tape Controller into the Data General-type computer system. This information is essential for the initial installation and will also be valuable when the controller is reinstalled after repair.

- 2.3 The controller is a single printed circuit board that plugs directly into a standard I/O bus card slot in the computer mainframe or in an expansion chassis. Cable assemblies and adapters are provided for interfacing the controller with the drives.

(Interface to be specified by the customer at the time of purchase). All dc power required for the operation of the controller is received from the power supply of the host computer system via the backplane connector.

- 2.4 UNPACKING AND INSPECTION. After removal of the controller components from the shipping containers, visually inspect them for physical damage. Check off each item on the enclosed packing list. In case of damage, retain all packaging and notify the carrier to make a report. Be sure all minor parts and small items are found before discarding any shipping material.

- 2.5 SYSTEM COMPONENTS. Check the equipment supplied to ensure that all necessary items are included:

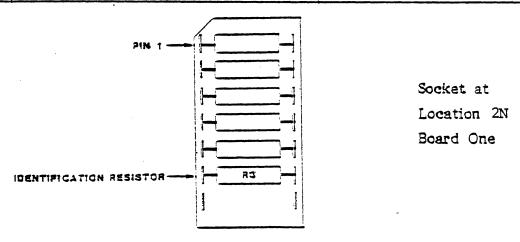

- 1. Tape controller board

Including proper VCO Speed Chip at location 2N

(for PE operation).

See Table 2-2 for part identification.

- 2. Backplane connector adapter.

- 3. Drive Cable(s), one set per drive.

For control, write, and read functions.

- 4. Adapter Paddleboards (3), one set per drive:

Control Paddleboard

Write Paddleboard

Read Paddleboard

Terminators (on the Write and Control

Paddleboards)

Drive Select Jumpers (on the Control

Paddleboard)

See Figure 2-7 for part identification.

5. Program Tapes:

Diagnostic Program Tape

Reliability Program Tape

Instruction Reference Card

6. Documentation:

Hardware Manual

Logic Manual

Diagnostic Manual

Including:

7. Other items which should be available:

Computer

Tape drives

Loading device for

diagnostics

#### 2.6 PREPARATION

2.7 Locate the position in the computer where the controller will be installed. Remember that the location in the system determines the priority for data channel and interrupt activity. The tape controller usually works well if placed anywhere in the system. Check the cabling distance to the first drive and to any daisy-chained drives, verifying that all cable lengths will be adequate, allowing for proper service loops. Refer to the drive manual to install the drives. The computer and drives must be prepared and checked-out before the controller can be expected to operate.

#### 2.8 SYSTEM SET-UP

2.9 The tape system must be set up properly either when installing the system or after servicing. Proper set-up includes:

(1) setting the Speed Switches to the speed of the drives, (2) installing the correct VCO Speed Chip, and (3) checking the backplane priority jumpers. (4) Each set of Tape Drive Adapter Paddleboards must have the proper termination (on the last drive), a Drive Select Jumper (except single drive installations), and Configuration Switch selections. Installation is complete when the system components are plugged in and interconnected. A recheck of the installation ensures that no item is overlooked. The procedures to set-up and install the controller are in the paragraphs that follow. Locations of installation features of the controller board are shown in Figure 2-1. A complete system

installation is shown in Figure 2-2. Also, check at the rear of the manual for special information which may be pertinent to your installation.

- 2.10 TAPE SPEED SELECTION. Tape drive speed information is provided to the controller by the code placed in the two speed switches and, for PE, the speed chip placed in the socket at location 2N. Two speed switches are provided for dual speed operation. The switches are located at D1 and D2 as shown in Figure 2-1. The switch module at location D1 selects the primary speed (Speed A) and the switch module at location D2 selects the alternate speed (Speed B). Table 2-1 provides the switch settings for each speed.

- 2.11 CONFIGURING THE SYSTEM FOR DUAL SPEED OPERATION. 9-track drives of one speed may be assigned to Speed A and 9-track drives of a second speed may be assigned to Speed B. However, all 7-track tape drives must operate at the speed selected for Speed A. A switch on the Control Adapter Paddleboard in each 9-track drive will be set to select either Speed A or Speed B. Set the speed switches as shown in Table 2-1 and record your Speed A and Speed B selections to avoid confusion when setting up the tape drives.

- 2.12 CONFIGURING THE SYSTEM FOR SINGLE-SPEED OPERATION. For systems using only one tape speed, set both speed switches identically, as shown in Table 2-1. In this configuration, the speed selection switch on the Control Adapter Paddleboard cannot be set wrong for 9-track drives.

Figure 2-2 Example of Typical System Installation

2-6

|           | TAPE SPEED |      |       |     |      |     |     |     |

|-----------|------------|------|-------|-----|------|-----|-----|-----|

| SWITCH    | 6.25       | 12.5 | 18.75 | 25  | 37.5 | 45  | 75  | 125 |

| POSITIONS | IPS        | IPS  | IPS   | IPS | IPS  | IPS | IPS | IPS |

| 1         | ON         | ON   | ON    |     | ON   |     |     |     |

| 2         | ON         |      | ON    |     |      |     | ON  |     |

| 3         |            | ·    |       | ON  | ON   |     | ON  |     |

| 4         |            | ON   | ON    | ON  | ON   | ON  | ON  | ON  |

| 5         | ON         | ON   | ON    |     | ON   | ON  |     |     |

| 6         | ON         |      | ON    | ON  |      |     |     |     |

| 7         |            | ON   |       |     |      |     |     |     |

| 8         | ON         |      |       |     |      |     |     |     |

SPEED A: LOCATION D1 SPEED B: LOCATION D2

Note: All other switches are "OFF"

Table 2-1 Speed Selection

2.13 VCO SPEED CHIP (FOR PE OPERATION). In addition to proper speed switch settings, proper PE operation requires insertion of the correct speed chip for the read tracking oscillator (VCO). Table 2-2 provides the part number of each speed chip. The speed chip supplied with each controller when shipped is for the speed specified by the customer at the time of purchase. (Other speed chips are available from the factory). Ensure that the correct part is properly installed in location 2N of the controller. When operating with two PE tape speeds, ensure that both tape speeds are within the limits of the selected speed chip.

| NOM.<br>SPEED | SPEED RANGE<br>(IPS) | SPEED CHIP<br>PART NO. | SPEED CHIP IDENTIFICATION (SEE R3) |

|---------------|----------------------|------------------------|------------------------------------|

| 12.5          | 6.25 - 18.75         | 120023-01              | RED - VIO - RED                    |

| 25            | 12.5 - 37.5          | 120023-02              | BRN - ORG - RED                    |

| 37.5          | 12.5 - 45            | 120023-03              | WHT - BRN - BRN                    |

| 45            | 18.75 - 45           | 120023-04              | VIO - GRN - BRN                    |

| 75·           | 25 - 75              | 120023-05              | YEL - ORG - BRN                    |

| 125           | 75 - 125             | 120023-06              | ORG - BLK - BRN                    |

Table 2-2 Speed Chips (for PE Operation only)

2.14 EXTENDED ADDRESS FEATURE. For programs which require expanded addressing, jumpers on the controller extend the addressing ragne of the controller from 32K to 64K, but preclude operation in the test mode. To implement this feature, cut the etch which connects A to B (located between 2C and 3C). Also, cut the etch between F and G and add a jumper from F to H (located between 14K and 15K). Note: The Reliability program will not operate on device code 62. Reinstall the jumper to run the Reliability program or patch the program to run device code 62. (This change is not compatible with some programs.)

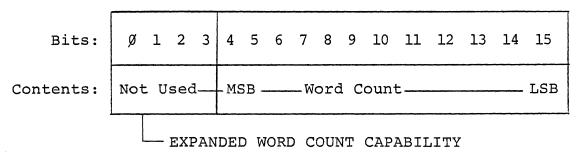

- 2.15 EXPANDED WORD COUNT FEATURE. For programs which require expanded word count capability, jumpers on the controller extend the word count register from 12 bits to 16 bits. To implement this feature cut the etch connecting C to D (located between 14J and 15J) and add a jumper from C to E (located between 14K and 15K). (This feature is not compatible with some programs.)

- 2.16 DEVICE CODE SELECTION. Normally, the Tape Controller is assigned to device code 22, (Mnemonic MTA). A second Tape Controller, if used is assigned to alternate device code 62. To make this change, cut the etch (or remove the jumper) between jumper points "M" and "N". This jumper may be found between location 3F and 4F.

#### 2.17 CONTROLLER INSTALLATION

- 2.18 Ensure that any keys in the selected backplane connector match the keying slots in the controller. Remove all extra keys from the slot. Place the controller board into the assigned card slot in the computer, assuring that the board seats properly and makes good connection.

- 2.19 PRIORITY JUMPERS. The data Channel Priority and the Interrupt Priority lines are daisy-chained to the I/O devices. As shown in Figure 2-3, each device receives these signals on pins A94 and A96 and sends these signals from pins A93 and A95 to the next device. There can be no break in the chain throughout the I/O devices. A previously unused card connector may have jumpers across these pins. Remove these jumpers from across the controller's backplane connector pins and check that the priority lines are daisy-chained from the CPU through the devices.

#### SOLDER PIN SIDE OF BACKPLANE

Figure 2-3 Computer Backplane Connector

- 2.20 OTHER BACKPLANE CONSIDERATIONS. Be certain that the backplane supplies +15VDC on backplane connector pin Alo. On some processors this voltage is not supplied to the upper slots and must be wired-in for operation of the tape controller in these locations. Solder this connection as close to the board as possible. The computer's I/O bus must also have proper termination.

- 2.21 CABLING. A connector adapter assembly provides the interface from the CPU backplane connector to the tape cables and may be installed as follows:

- Remove or relocate any wires located on the backplane connector pins for the tape controller including wires placed there as a tie point and wires used for a device

which previously occupied that slot. The controller uses all unassigned backplane pins, therefore, no other connections to these pins should be wired to the card slot assigned to the controller. (See Table 2-3 and 2-4) If +15 volts has to be wired to Pin AlO, it should be soldered close to the computer backplane. Remove any excess solder from the pins and straighten any bent pins.

- 2. Attach the adapter connectors to the pins of the backplane connectors, carefully observing pin assignments marked on the connectors. (See Figure 2-4 and 2-5) Seat the connectors firmly on the backplane pins.

- 3. Neatly dress and tie all cables so that the installation appears orderly and professional.

TABLE 2-3

NOVA TAPE INTERFACE FOR

NOVA, NOVA 1200, NOVA 800, SUPER NOVA, AND SUPER NOVA SC

|                                                                                                                          |                                 | •                                    |                                                                                         | _                                                         |

|--------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------|

| Signal                                                                                                                   | Level<br>*                      | Direction *                          | Panel<br>Pin                                                                            | External<br>Bus Pin                                       |

| GND<br>CLR<br>DATAO<br>DATA1<br>DATA2<br>DATA3<br>DATA4<br>DATA5<br>DATA6<br>DATA7<br>DATA8<br>DATA9<br>DATA10<br>DATA11 |                                 |                                      | A50<br>B62<br>B65<br>B82<br>B73<br>B61<br>B57<br>B95<br>B55<br>B60<br>B63<br>B75<br>B58 | Bus Pin  1 2 3 4 5 6 7 8 9 10 11 12 13 14                 |

| DATA12 DATA13 DATA14 DATA15 DATIA DATIB DATIC DATOA DATOB                                                                | L<br>L<br>L<br>H<br>H<br>H      | B<br>B<br>B<br>D<br>D<br>D<br>D      | B59<br>B64<br>B56<br>B66<br>A44<br>A42<br>A54<br>A58                                    | 15<br>16<br>17<br>18<br>19<br>20<br>21<br>22              |

| DATOC DCHA DCHI DCHMO DCHM1 DCHO DCHP IN DCHP OUT DCHR DSO                                                               | H<br>L<br>H<br>L<br>L<br>L<br>L | D<br>D<br>P<br>D<br>D<br>D           | A48<br>A60<br>B37<br>B17<br>B21<br>B33<br>A94*)<br>A93*)<br>B35<br>A72                  | 24<br>25<br>26<br>27<br>28<br>29<br>30<br>31<br>32        |

| DS1 DS2 DS3 DS4 DS5 INTA INTP IN INTP OUT INTR IOPLS IORST                                                               | L<br>L<br>L<br>H<br>L<br>H<br>H | D<br>D<br>D<br>D<br>D<br>D<br>P<br>D | A68<br>A66<br>A46<br>A62<br>A64<br>A40<br>A96*)<br>A95*)<br>B29<br>A74<br>A70           | .33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42 |

TABLE 2-3 (Continued)

|          | Level | Direction | Pane1 | Externa1 |

|----------|-------|-----------|-------|----------|

| Signal   | *     | *         | Pin   | Bus Pin  |

| MSKO     | L     | D         | A38   | 43       |

| OVFLO    | H     | , D       | в39   | 44       |

| RQENB    | L     | D         | B41   | 45       |

| SELB     | L     | P         | A82   | 46       |

| SELD     | L     | P         | A80   | 47       |

| STRT     | H     | D         | A52   | 48       |

| POWER ON | Н     | D         |       | 49       |

| NOT USED |       |           |       | 50       |

\*For the two pairs of priority-determining signals, the in signal comes from the processor or the preceding device; the out signal goes to the next device. If the computer is operated with an interface board removed (or a slot is not used), Jumper Pin A93 to A94 and A95 to A96 to maintain bus continuity.

Pin 1 of the external bus is grounded and the groud wires from all twisted pairs are connected to it. The Power-On line cannot be used to supply power to any external device; it is available only for picking up relays for remote power turn-on. Pin 50 is not used.

\*\*LEGEND: H = HIGH B = BI DIRECTIONAL P = FROM DEVICE

L = LOW D = FROM PROCESSOR TO PROCESSOR

TO DEVICE

TABLE 2-4 NOVA TAPE INTERFACE FOR NOVA 1210, NOVA 1220, AND NOVA 820

| GND  GND  CLR  H  D  A50  K  9  DATAO  L  B  B62  W  41  DATA1  L  B  B65  Z  44  DATA2  L  B  B73  AB  46  DATA4  L  B  B73  AB  46  DATA5  L  B  B73  AB  46  DATA5  L  B  B73  AB  46  DATA4  L  B  B73  AB  46  DATA6  L  B  B73  AB  46  DATA7  L  B  B73  AB  46  DATA6  L  B  B73  AB  46  DATA6  L  B  B73  AB  46  DATA7  L  B  B  B57  T  36  DATA6  L  B  B  B57  AC  47  DATA8  L  B  B  B60  U  39  DATA9  L  B  B63  X  42  DATA10  L  B  B63  X  42  DATA11  L  B  B55  T  AC  47  DATA11  L  B  B55  T  AC  47  DATA12  L  B  B55  T  AC  47  DATA12  L  B  B56  B59  L  B  B66  AA  45  DATA15  L  B  B66  AA  45  DATA16  DATA15  L  B  B66  AA  45  DATA16  DATOA  H  D  A44  F  B  DATOC  H  D  A44  E  D  DATOC  H  D  A48  J  B  DATOC  H  D  A48  J  B  BOCHM  L  D  DATOC  H  D  A48  J  B  DOHA  D  DATOC  H  D  A48  J  B  DOHA  D  DOHA  L  D  DATOC  H  D  D  A48  J  B  DOHA  D  DATOC  H  D  D  A48  J  B  D  DOHA  L  D  DATOC  H  D  A48  J  B  D  DOHA  D  DATOC  H  D  A46  R  14  DCHI  DCHI  DCHI  D  DATOC  H  D  A48  J  B  BOCHP  D  D  A46  R  14  DCHI  DCHI  D  D  DCHP  D  D  A46  R  14  DCHI  D  D  DCHP  D  D  A66  U  17  DS3  L  D  A66  U  17  DS3  L  D  A66  U  17  DS4  L  D  A66  D  A72  X  20  DS1  L  D  A66  U  17  DS5  L  D  A66  D  A66  D  A77  D  A66  D  A77  D  A66  D  A77  D  A78  D  D  D  D  D  D  D  D  D  D  D  D  D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |            | <b>-</b>       | _ 1          | Exte       |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|----------------|--------------|------------|------------|

| CLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Signal   | Level<br>* | Direction<br>* | Panel<br>Pin | Bus<br>SIG | Pin<br>GND |

| CLR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | CND      |            |                |              | ΔΕ         | 50<br>-    |

| DATAO L B B62 w 41 DATA1 L B B65 z 44 DATA2 L B B85 z 44 DATA3 L B B82 AD 48 DATA3 L B B73 AB 46 DATA4 L B B61 v 40 DATA5 L B B61 v 40 DATA5 L B B57 r 36 DATA6 L B B95 AE 49 DATA7 L B B55 n 34 DATA8 L B B60 u 39 DATA9 L B B60 u 39 DATA9 L B B60 u 39 DATA9 L B B75 AC 47 DATA11 L B B75 AC 47 DATA11 L B B75 x 37 DATA12 L B B75 x 37 DATA12 L B B59 t 38 DATA13 L B B64 y 43 DATA14 L B B56 P 35 DATA15 L B B66 AA 45 DATA16 H D A44 F 6 DATIB H D A44 F 6 DATIB H D A44 F 6 DATIC H D A54 M 11 DATOC H D A56 N 12 DATOC H D A56 N 12 DATOC H D B37 k 31 DCHA L D A60 R 14 DCHA L D A60 R 14 DCHA L D A94*) b DCHP OUT L D A93*) DSO L D A72 X 20 DS1 L D A66 U 17 DS3 L D A66 U 17 DS3 L D A66 I 16 INTA H D A46 H 7 DS4 L D A66 I 17 DS3 L D A66 I 17 DS4 L D A66 I 17 DS5 L D A66 I 17 DS3 L D A66 I 17 DNTP IN L D A96*) C 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          | н          | ח              | A 50         |            |            |

| DATA1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |                |              |            |            |

| DATA2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |                |              |            |            |

| DATA3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |                |              |            |            |

| DATA4 L B B61 V 40 DATA5 L B B57 r 36 DATA6 L B B57 r 36 DATA6 L B B55 n 34 DATA7 L B B55 n 34 DATA8 L B B60 u 39 DATA9 L B B60 u 39 DATA9 L B B63 x 42 DATA10 L B B58 s 37 DATA11 L B B58 s 37 DATA11 L B B58 s 37 DATA12 L B B59 t 38 DATA13 L B B64 y 43 DATA14 L B B66 AA 45 DATA15 L B B66 AA 45 DATA16 H D A44 F 6 DATIB H D A44 F 6 DATIB H D A42 E 5 DATIC H D A54 M 11 DATOA H D A58 P 13 DATOC H D A58 P 13 DATOC H D A60 R 14 DCHA L D A60 R 14 DCHA L D A60 R 14 DCHA L D A93*) DCHMO L P B17 d 26 DCHMO L P B17 d 26 DCHMO L P B17 d 26 DCHMO L P B21 e 27 DCHO H D A93*) DCHP OUT L D A93*) DCHR L P B35 j 30 DSO L D A66 U 77 DS3 L D A66 U 77 DS3 L D A66 T 16 INTA H D A46 T 16 INTA H D A40 D 4 INTP IN L D A96*) L D A96*                                                                       |          |            |                |              |            |            |

| DATA5 L B B57 r 36 DATA6 L B B95 AE 49 DATA7 L B B855 n 34 DATA8 L B B60 u 39 DATA9 L B B63 x 42 DATA10 L B B75 AC 47 DATA11 L B B75 AC 47 DATA11 L B B75 AC 47 DATA12 L B B75 AC 47 DATA12 L B B75 C 38 DATA13 L B B64 y 43 DATA14 L B B56 P 35 DATA15 L B B66 AA 45 DATA16 H D A44 F 6 DATIB H D A44 F 6 DATIB H D A44 F 6 DATIC H D A54 M 11 DATOA H D A58 P 13 DATOC H D A56 N 12 DATOC H D A60 R 14 DCH1 H D B37 k 31 DCHA L D A60 R 14 DCH1 H D B37 k 31 DCHMO L P B17 d 26 DCHM1 L P B21 e 27 DCHO H D B33 h 29 DCHP IN L D A94*) b 24 DCHP OUT L D A93*) DCHR L P B35 j 30 DSO L D A72 X 20 DS1 L D A66 U 17 DS3 L D A66 T 16 INTA H D A40 D 4 INTP IN L D A96*) c 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |            |                |              |            |            |

| DATA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |                |              |            |            |

| DATA7 L B B B55 n 34 DATA8 L B B B60 u 39 DATA9 L B B B60 u 39 DATA10 L B B B63 x 42 DATA11 L B B B75 AC 47 DATA11 L B B B58 s 37 DATA12 L B B B59 t 38 DATA13 L B B B64 y 43 DATA14 L B B B66 AA 45 DATA14 L B B B66 AA 45 DATA15 L B B B66 AA 45 DATIA H D A444 F 6 DATIB H D A42 E 5 DATIC H D A58 P 13 DATOB H D A56 N 12 DATOC H D A58 P 13 DATOB H D B37 k 11 DCHMO L D B37 k 31 DCHMO L P B17 d 26 DCHM1 L P B21 e 27 DCHO H D B33 h 29 DCHP IN L D A68 V 18 DS2 L D A66 U 17 DS3 L D A66 U 17 DS3 L D A66 T 16 INTA H D A40 D 4 INTP IN L D A40 H INTP IN L D A96*) INTP OUT L D A96* INTP IN L D A96*) INTP IN L D A40 H INTP IN L D A4 |          |            |                |              |            |            |

| DATA8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |                |              | ·          |            |

| DATA9  DATA10  L  B  B B63  X  42  DATA10  L  B B75  AC  47  DATA11  L  B B858  S  37  DATA12  L  B B859  L  B DATA13  L  B B64  Y  43  DATA14  L  B B66  AA  45  DATA15  L  B B66  AA  45  DATA16  L  B B66  AA  45  DATA16  DATIA  H  D A444  F  6  DATIB  DATOC  H  D A558  DATOC  H  D A48  DATOC  H  D A48  DATOC  H  D A60  R  14  DCH1  DCHA  DCHA  L  D B37  R  31  DCHMO  L  DCHMO  L  P B17  DCHO  H  D A93*)  DCHP IN  L  D A60  R  14  DCHP OUT  L  D A93*)  DCHR  L  D A66  U 17  DS3  L  DS0  L  D A66  U 17  DS3  L  D A66  U 17  DS3  L  D A66  U 17  DS3  L  D A66  L  D A66  U 17  DS3  L  D A66  L  D A66  U 17  DS3  L  D A66  L  D A66  U 17  DS3  L  D A66  L  D A66  U 17  DS3  L  D A66  L  D A66  U 17  DS3  L  D A66  D A67  E  D A67  E  D A67  E  D A67  E  D A67  D A6  |          |            |                |              |            |            |

| DATA10  L  B  B  B75  AC  47  DATA11  L  B  B  B58  S  37  DATA12  L  B  B  B59  L  38  DATA13  L  B  B59  L  38  DATA13  L  B  B64  Y  43  DATA14  L  B  B  B66  AA  45  DATA15  L  B  B66  AA  45  DATIA  H  D  A444  F  6  DATIB  H  D  A442  E  5  DATIC  H  D  A54  M  11  DATOA  H  D  A58  P  13  DATOB  DATOC  H  D  A56  N  12  DATOC  H  D  A60  R  14  DCH1  H  D  B37  k  31  DCHA  DCHA  L  D  B37  k  31  DCHMO  L  P  B17  d  26  DCHMI  L  P  B33  h  29  DCHP IN  L  D  A94*)  D  CHP OUT  L  D  A66  L  D  A68  V  18  DS2  L  D  A66  L  D  A66  L  D  A66  T  DS3  L  D  A66  L  D  A66  T  DS3  L  D  A66  T  DS3  L  D  A66  T  D  A67  DS4  L  D  A66  T  DS5  L  D  A66  T  D  A67  DS6  L  D  A66  D  A77  DS7  DS7  DS7  DS7  DS7  DS7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |            | _              |              |            |            |

| DATA11  L B B58 S 37 DATA12 L B B59 t 38 DATA13 L B B64 y 43 DATA14 L B B66 A A 45 DATA15 L B B66 AA 45 DATIA DATIA H D A444 F 6 DATIB H D A442 E 5 DATIC H D A54 M 11 DATOA H D A56 N 12 DATOC H D DATOC H D DA56 N 12 DATOC H D DA60 R DCHA L DCHI H D B37 k 31 DCHMO L P B17 d 26 DCHMI L P B21 e 27 DCHO H D B33 h 29 DCHP DCHP IN L D DA93*) DCHP DCHR L P B35 j 30 DSO L D A66 U 17 DS3 L D A66 I I D A66 I I D A66 I I D D A66 I I D D D D D D D D D D D D D D D D D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |            |                |              |            |            |

| DATA12  DATA13  L  B  B  B59  C  38  DATA13  L  B  B64  DATA14  L  B  B56  P  35  DATA15  L  B  B66  AA  45  DATIA  DATIA  H  D  A44  F  6  DATIB  H  D  A42  E  5  DATIC  H  D  A54  M  11  DATOA  H  D  A58  P  13  DATOB  DATOC  H  D  A48  J  B  DCHA  DCHA  L  D  A60  R  14  DCH1  H  D  B37  k  31  DCHMO  L  P  B17  d  26  DCHM1  L  P  B21  E  7  DCHO  H  D  B33  h  29  DCHP IN  L  D  A94*)  D  CHP OUT  L  D  A93*)  DCHR  L  D  A66  U  T  DS3  L  D  A66  U  T  DS3  L  D  A66  U  T  DS4  L  D  A66  U  T  DS5  L  D  A66  D  A72  X  20  DS1  DS3  L  D  A66  U  T  DS4  L  D  A66  U  T  DS5  L  D  A66  U  T  DS5  L  D  A66  U  T  DS5  L  D  A66  D  A60  D  A70  D  A60  D  A70  A70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |            |                |              |            |            |

| DATA13  DATA14  L  B  B  B64  y  43  DATA15  DATA15  L  B  B66  AA  45  DATIA  DATIA  H  D  A44  F  6  DATIB  H  D  A44  F  6  DATIC  H  D  A54  M  11  DATOA  H  D  A58  P  13  DATOC  H  D  DATOC  H  D  A48  J  8  DCHA  DCHA  DCHI  H  D  B37  k  31  DCHMO  L  P  B17  d  26  DCHMI  L  P  B21  E  7  DCHO  H  D  A94*)  D  CHP OUT  L  D  A68  V  18  DS2  L  D  A66  U  17  DS3  L  D  A66  U  17  DS3  L  D  A62  S  15  DS5  L  D  A64  T  T  D  A96*)  INTP IN  L  D  A96*)  INTP OUT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |                |              |            |            |

| DATA14  L B B B56 P 35 DATA15 L B B66 AA 45 DATIA H D A44 F 6 DATIB H D A42 E 5 DATIC H DATOA H D A54 M 11 DATOA H D A58 P 13 DATOB H D A56 N 12 DATOC H D A60 R 14 DCHA L D A60 R 14 DCHI H D B37 k 31 DCHMO L P B17 d 26 DCHMI L P B21 e 27 DCHO H D B33 h 29 DCHP IN L D CHP OUT L D A93*) DCHR L P B35 j 30 DSO L D A68 V 18 DS2 DS1 L D A66 U 17 DS3 L D A66 U 17 DS3 L D A66 L D A66 U 17 DS4 L D A66 L D A66 T INTA H D A96*) L D L D L D L D L D L D L D L D L D L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |            |                |              |            |            |

| DATA15  DATIA  DATIA  H  D  A444  F  6  DATIB  H  D  A42  E  5  DATIC  H  D  A54  M  11  DATOA  H  D  A58  P  13  DATOB  DATOC  H  D  A56  N  12  DATOC  H  D  A60  R  14  DCHA  L  D  A60  R  14  DCHI  H  D  B37  k  31  DCHMO  L  P  B17  d  26  DCHM1  L  P  B21  e  27  DCHO  H  D  A94*)  D  CHP IN  L  D  A93*)  DCHR  L  P  B35  J  30  DSO  L  D  A68  V  18  DS2  L  D  A66  U  17  DS3  L  D  A64  L  D  A64  T  D  A64  T  D  A62  S  15  DS5  L  D  A64  T  D  A40  D  4  INTP IN  L  D  A96*)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |          |            |                |              | P          |            |

| DATIA       H       D       A444       F       6         DATIB       H       D       A42       E       5         DATIC       H       D       A54       M       11         DATOA       H       D       A58       P       13         DATOB       H       D       A56       N       12         DATOC       H       D       A48       J       8         DCHA       L       D       A60       R       14         DCHA       L       D       A60       R       14         DCHA       H       D       B37       k       31         DCHA       H       D       B37       k       31         DCHMO       L       P       B17       d       26         DCHMI       L       P       B21       e       27         DCHO       H       D       B33       h       29         DCHP IN       L       D       A94**)       b       24         DCHP OUT       L       D       A68       V       18         DS2       L       D       A66       U       17 </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |            |                |              |            |            |

| DATIB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DATIA `  |            |                |              |            |            |

| DATIC H D A54 M 11 DATOA H D A58 P 13 DATOB H D A56 N 12 DATOC H D A48 J 8 DCHA L D A60 R 14 DCH1 H D B37 k 31 DCHMO L P B17 d 26 DCHM1 L P B21 e 27 DCHO H D B33 h 29 DCHP IN L D A94*) b 24 DCHP OUT L D A93*) DCHR L P B35 j 30 DSO L D A68 V 18 DS2 L D A66 U 17 DS3 L D A66 U 17 DS3 L D A66 T 16 INTA H D A40 D 4 INTP IN L D A96*) INTP OUT L D A95*) c 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DATIB    |            |                | A42          |            |            |

| DATOA H D A58 P 13 DATOB H D A56 N 12 DATOC H D A48 J 8 DCHA L D A60 R 14 DCH1 H D B37 k 31 DCHMO L P B17 d 26 DCHM1 L P B21 e 27 DCHO H D B33 h 29 DCHP IN L D A94*) b 24 DCHP OUT L D A93*) DCHR L P B35 j 30 DSO L D A72 X 20 DS1 L D A68 V 18 DS2 L D A66 U 17 DS3 L D A66 U 17 DS3 L D A66 T 16 INTA H D A40 D 4 INTP IN L D A95*) c 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DATIC    |            |                | A54          |            |            |

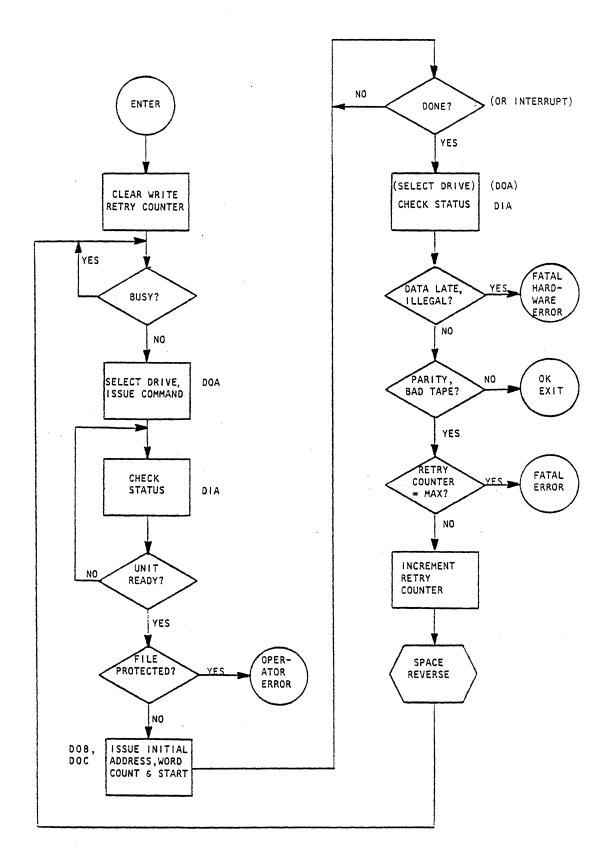

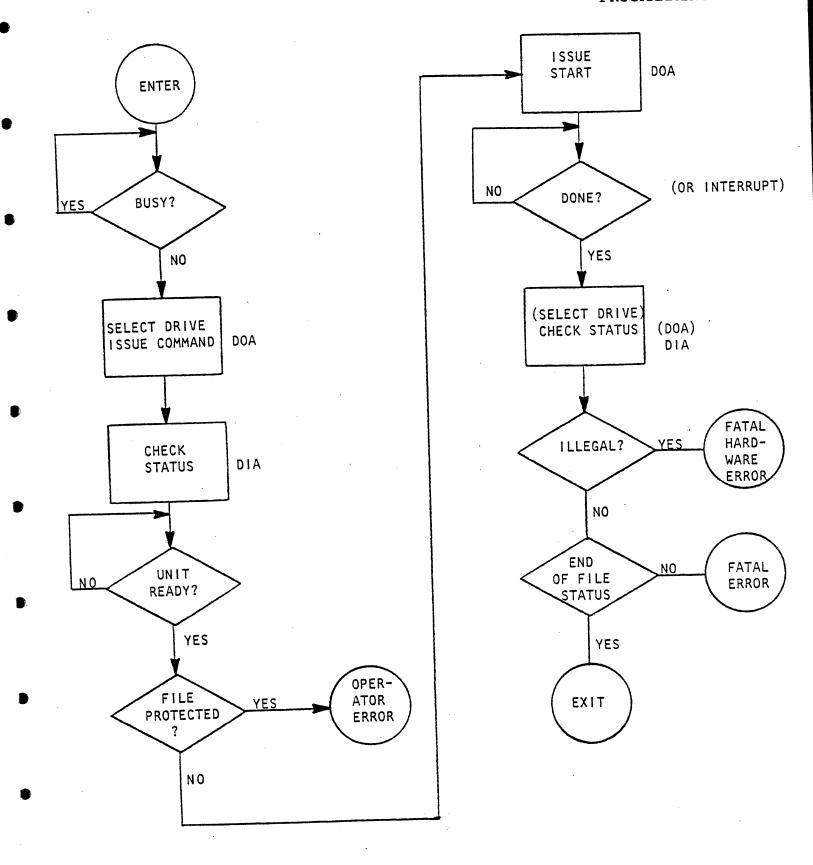

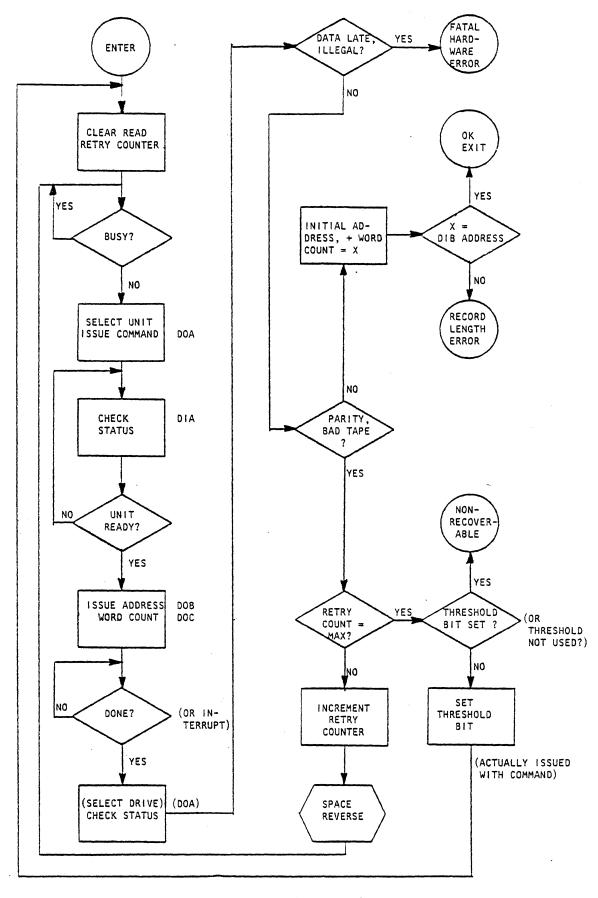

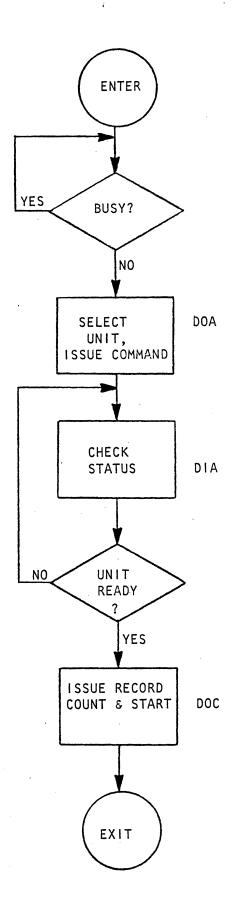

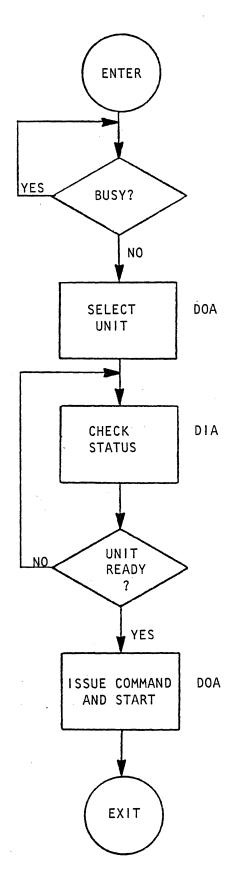

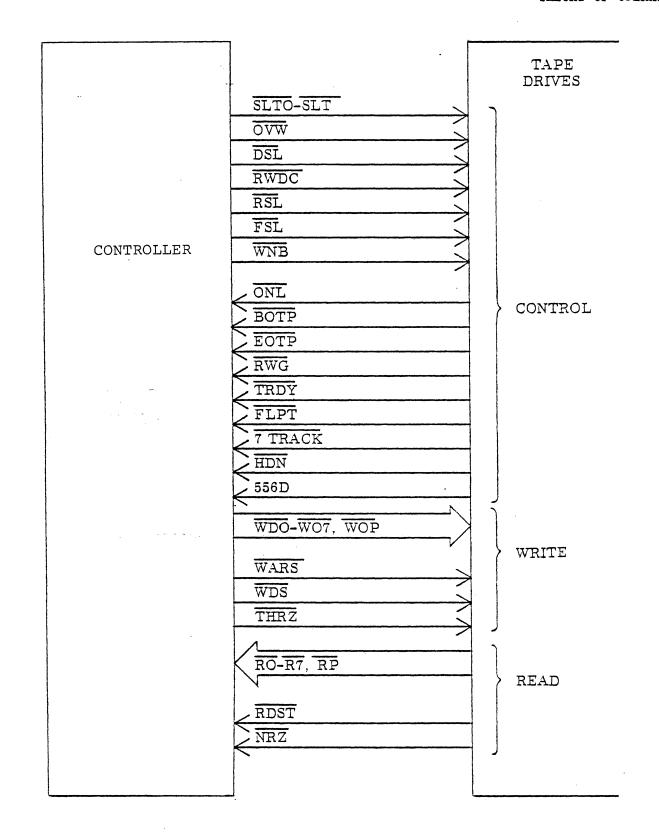

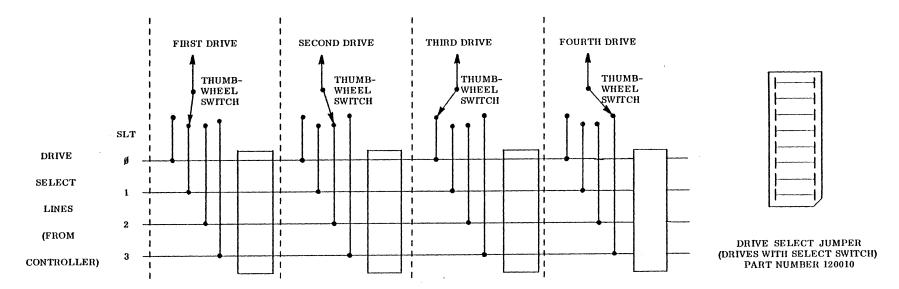

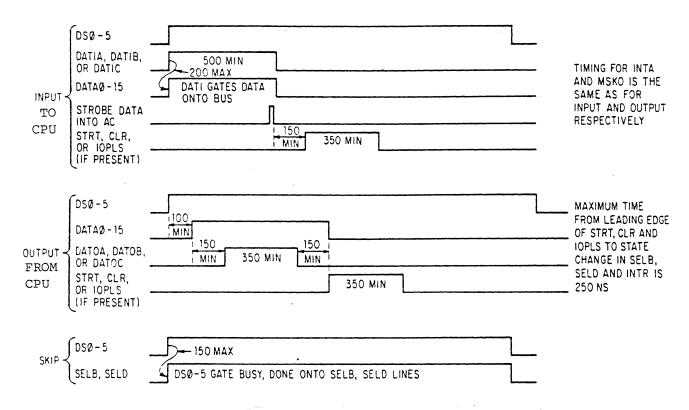

| DATOB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |            |                |              |            | 13         |