BIL/WE microcomputer symposium.

## Prepared and Published by the Technical Publication Department

## NOTICE

Not for use or disclosure outside the Bell System except under written agreement.

#### ACKNOWLEDGMENTS

Symposium Sponsor

The Microprocessor Steering Committee

W. E. Danielson - Chairperson

- R. M. Allen (WE)

- R. C. Fletcher

- G. L. Hermansen (WE)

- J. W. Schaefer

- D. G. Thomas

- R. L. Wagner

Symposium Chairperson

R. B. Hawkins

Symposium Assistant Chairperson

C. L. Semmelman

**Technical Program Chairperson**

J. R. Mc Eowen

Session Chairpersons

C. R. Baugh A. H. Bobeck F. H. Henig W. N. Toy C. D. Weiss

**Technical Arrangements**

M. J. Krumm

D. Manolio

Graphic Arts

**Technical Publication Department**

J. A. Walker - Coordinating Editor

# CONTENTS

## SESSION 1 - INTRODUCTION

# SESSION 2 - IN-HOUSE MICROCOMPUTERS

| A MAC-8 Status Report                                                      | 1-1  |  |

|----------------------------------------------------------------------------|------|--|

| MAC-8 Device Description                                                   | 2-1  |  |

| Design and Fabrication of the MAC-8 Microprocessor Chip                    | 3-1  |  |

| Testing and Debugging of MAC-8 Systems                                     | 4-1  |  |

| The MAC-8 in a User Environment                                            | 5-1  |  |

| MAC-4                                                                      | 6-1  |  |

| SESSION 3 - SUPPORT FACILITIES                                             |      |  |

| The Programming Languages of MAC-8                                         | 7-1  |  |

| A Support System for the Intel 8080                                        | 8-1  |  |

| UNIX on the LSI-11                                                         | 9-1  |  |

| Manufacturing Microcomputer-Based Systems                                  | 10-1 |  |

| SWAT - A Debugging System for the $\text{DIMENSION}^{\textcircled{R}}$ PBX |      |  |

| SESSION 4 - APPLICATIONS I                                                 |      |  |

| The Loop Switching System                                                  | 12-1 |  |

| TASI-E Software Development                                                | 13-1 |  |

| A Microcomputer Test Facility for a<br>Mobile Telecommunications System    | 14-1 |  |

| The Design of a Self-Checking Microcomputer                                | 15-1 |  |

| Design of an LSI Microprocessor                                            | 16-1 |  |

# CONTENTS (Continued)

# SESSION 5 - APPLICATIONS II

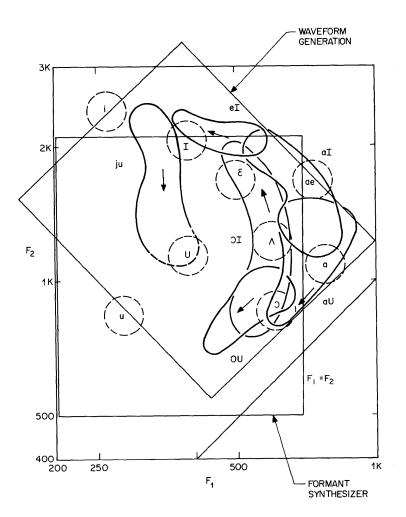

| Speech Output From a Microprocessor                                                         |      |  |

|---------------------------------------------------------------------------------------------|------|--|

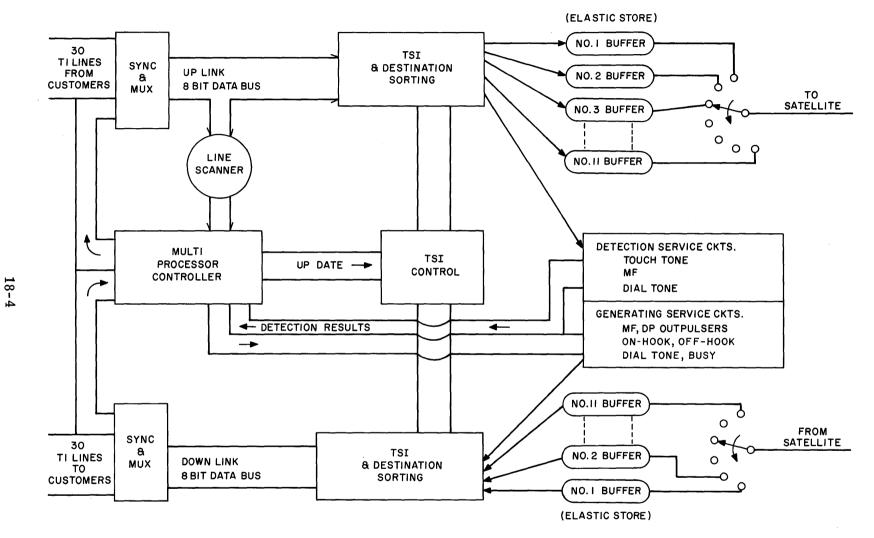

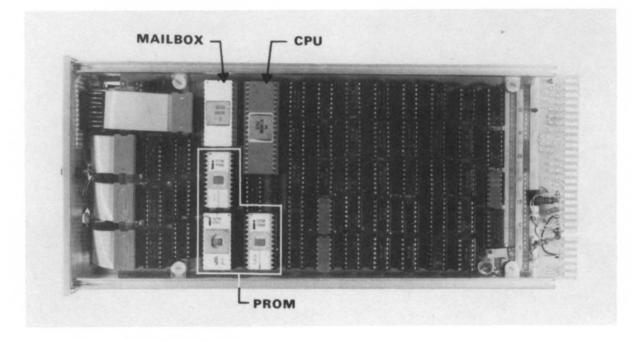

| A Small Digital Time Division Switch Using Microprocessor Control                           | 18-1 |  |

| A Microprocessor-Controlled Switching System for L5E -<br>Designs, Lessons, and Experiences | 19-1 |  |

| The 32A Communication System                                                                | 20-1 |  |

| The Business Switching System                                                               | 21-1 |  |

| A PROCON-Based Peripheral Controller                                                        | 22-1 |  |

| A Microcomputer-Controlled Single-Line Telephone System                                     | 23-1 |  |

| SESSION 6 - PERIPHERAL TECHNOLOGY                                                           |      |  |

| Some Power Considerations for Microprocessor Systems                                        | 24-1 |  |

| A Survey of Small Tape Peripherals                                                          | 25-1 |  |

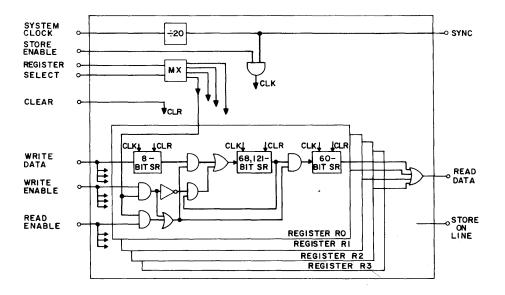

| Serial Bubble Store                                                                         | 26-1 |  |

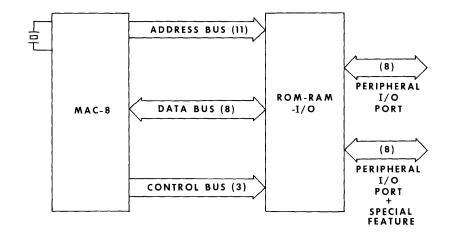

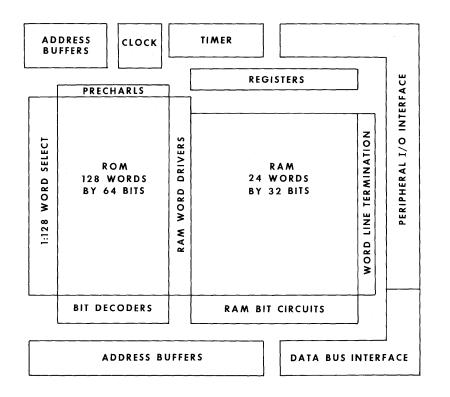

| A ROM-RAM-I/O Device for the MAC-8                                                          |      |  |

| A 4K Random-Access Memory                                                                   |      |  |

## INTRODUCTION

Speaker: I. M. Ross Executive Vice President

## Microcomputer Symposium

The intent of the symposium is to present the latest Bell System experience and expertise in microcomputer applications, to encourage communication among microcomputer users, and to stimulate engineers and designers with the potential of this new technology.

-

#### **IN-HOUSE MICROCOMPUTERS**

#### A MAC-8 STATUS REPORT

L. C. Thomas, BTL Dept 4391, HO, NJ

### ABSTRACT

This report describes the current status and future direction of the components of the MAC-8 development project: the devices, support software and hardware, and user training. The Symposium presentation of this paper will include current schedules and pricing information. This information has not been included here because of the publication deadline.

## INTRODUCTION

The purpose of this paper is to describe the development and interaction of the components that are essential for providing a Bell System microprocessor capability. These components are: the MAC-8 microprocessor, software support, hardware interfaces, and user education and application support.

## MAC-8 MICROPROCESSOR

Complementary metal oxide semiconductor (CMOS) technology has been used to implement the MAC-8 chip. One of the advantages of this technology is that p-channel and n-channel devices can be used on the same chip. The combination of these devices has produced a variety of innovative circuit configurations that provide the MAC-8 chip n-channel density (about 8000 transistors on a 220- by 220-mil chip) with the low-power dissipation associated with CMOS (less than 150 mW). The details of this design approach are covered in the paper by Cooper and Krambeck.<sup>1</sup> Another reason for the choice of CMOS technology involves its track record in previous development projects. In a company whose large scale integration (LSI) experience is limited, judgments of track records must be extremely subjective. However, after a 1-1/2 year involvement with the MAC-8 project, we in the Systems Area continue to feel that we have chosen a technology and circuit implementation that promise to become industry standards.

#### SOFTWARE SUPPORT

In the software development for the MAC-8 microprocessor, two aspects have been emphasized. The first of these is the development of an efficient high-level language to describe applications to the MAC-8. The second item of emphasis is to develop debugging tools in this same high-level language. Possibly a hardware analogy is appropriate here. Obviously, it is much simpler to design logic circuits with medium scale integration (MSI) devices, such as counters and multiplexers, rather than quad gates. A high-level language brings the same advantages to software development. Similarly, a system designed with MSI devices would be difficult to debug on a gate-by-gate basis. Thus, a high-level language should be debugged in its own symbolic, human-oriented terms, not at a lower level. As obvious as these concepts appear, they have not been incorporated into commercial support software. While the high-level language PL/M has been implemented for some commercial microprocessors, it is notoriously inefficient in byte processing and execution time. Its usefulness is restricted to those cases that must emphasize short schedules. The design philosophy regarding software aids, emphasized in papers by Kirby and Rovegno<sup>2</sup> and Shupe, Johnson, and Hofmann.<sup>3</sup> translates directly to reduced development costs and an increased ability to respond to competitive pressures in minimum time. Maintenance and current engineering costs should also be substantially reduced.

#### HARDWARE INTERFACES

The hardware interface between the MAC-8 dual in-line package (DIP) and the outside world is described in the papers by Blahut<sup>4</sup> and Torres.<sup>5</sup> In these papers, instruction timing, control signal timing, and the utilization of commercially available memories and peripheral devices have been emphasized. The only in-house peripheral device being specifically developed for the MAC-8 is a device

containing read-only memory (ROM), random-access memory (RAM), and input/ output (I/O) on a single DIP. This device is described in a paper by Ukeiley and Slemmer.<sup>6</sup> With the exception of this device, emphasis has been placed on developing the central processing unit (CPU) and the user support facilities described in this paper. The demand for any additional members of a MAC-8 family of devices will be determined by system requirements over the next 12 to 24 months. The successful development of a MAC-4<sup>7</sup> device would provide an ideal building block for MAC-8 peripheral devices of all types.

## USER EDUCATION AND APPLICATION SUPPORT

The MAC-8 project is confronting the user education and application support problems in a variety of ways.

- Users Manual: A Users Manual will be written by the various hardware and software designers involved in the project and edited by E. J. Angelo. This manual will be available originally in a looseleaf format; when documentation on all phases of the project becomes complete, a hard-bound version will be published.

- <u>Conventional Courses</u>: MAC-8 courses will be presented in-hours, out-of-hours, in short-course format, and in self-teaching formats beginning in the spring of 1977.

- User Group Application Notes: A MAC-8 user group will be formed and supported. This group will facilitate the exchange of information among MAC-8 users via specific application notes, as well as hardware and software exchanges.

- The MAC-TUTOR: The hardware keystone of the MAC-8 education and applications support effort will be the MAC-TUTOR apparatus. This apparatus will consist of a complete MAC-8 microcomputer system at an objective cost of \$350. This system will include a MAC-8 CPU, RAM, a programmable ROM (PROM) debug monitor system coupled with a 20-button keyboard, and I/O capability. The power supply will be included with the apparatus as well as an RS-232 connection for more elaborate program development. A self-teaching booklet will accompany the MAC-TUTOR. The MAC-TUTOR apparatus will be supplied to each student in in-hours, out-of-hours, and short courses to be given at Bell Laboratories. The apparatus will be

considered as the textbook for these courses, and will be paid for by the student's department. For self-teaching purposes, they may be purchased separately. Initial availability of the MAC-TUTOR is expected in the spring semester 1977, with full production quantities expected in June 1977.

#### REFERENCES

- J. A. Cooper and R. H. Krambeck, 'Design and Fabrication of the MAC-8 Microprocessor Chip, ' paper presented at Microcomputer Symposium, Bell Telephone Laboratories, Holmdel, New Jersey, 1976.

- D. B. Kirby and H. D. Rovegno, "The Programming Languages of MAC-8," paper presented at Microcomputer Symposium, Bell Telephone Laboratories, Holmdel, New Jersey, 1976.

- B. B. Hofmann, K. W. Johnson, and C. F. Shupe, "Testing and Debugging of MAC-8 Systems," paper presented at Microcomputer Symposium, Bell Telephone Laboratories, Holmdel, New Jersey, 1976.

- 4. D. E. Blahut, "Mac-8 Device Description," paper presented at Microcomputor Symposium, Bell Telephone Laboratories, Holmdel, New Jersey, 1976.

- 5. F. B. Torres, "The MAC-8 in a User Environment," paper presented at Microcomputor Symposium, Bell Telephone Laboratories, Holmdel, New Jersey, 1976.

- R. L. Ukeiley and W. C. Slemmer, 'A ROM-RAM-I/O Device for the MAC-8, "paper presented at Microcomputer Symposium, Bell Telephone Laboratories, Holmdel, New Jersey, 1976.

- D. C. Stanzione, "MAC-4," paper presented at Microcomputer Symposium, Bell Telephone Laboratories, Holmdel, New Jersey, 1976.

- ,

#### IN-HOUSE MICROCOMPUTERS

### **MAC-8 DEVICE DESCRIPTION**

D. E. Blahut, BTL Dept 4391, HO, NJ

#### ABSTRACT

The MAC-8 microprocessor is a single-chip, bus-structured, 8-bit microprocessor. A single 16-bit address bus accesses memory and input/output (I/O), including the sixteen 16-bit working registers and the pushdown stack contained in the random-access memory (RAM). Other features include interrupt, direct memory access (DMA), and reset capabilities.

This paper provides a review of the internal MAC-8 architecture and a detailed description of various input and output signals that will be useful to the hardware designer when interconnecting the 40-pin MAC-8 dual in-line package (DIP) with memory and I/O and peripheral hardware in general.

The Symposium presentation of this paper will include final electrical characteristics and timing waveforms. This information has not been included here because of the publication deadline.

#### INTRODUCTION

With its innovative architecture, the MAC-8 microprocessor is a powerful device when compared to outside alternatives; however, a detailed description of this structure, its salient and powerful capabilities, and the generous set of instructions and memory accessing modes will not be presented here.<sup>1</sup> The purpose of this paper is to provide a device description primarily for the hardware system designers. Only a brief review of the architecture will be presented in order to more easily describe the interaction between the MAC-8 and its peripherals.

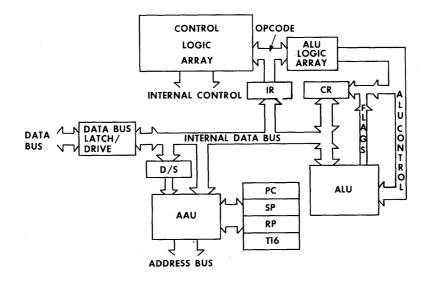

### ARCHITECTURE

The MAC-8 is partitioned into four major functional blocks. See Figure 2-1. The control logic array is the nucleus of the microprocessor. It performs the task of directing the circuitry through the sequence of states required to execute each of its instructions and functions. A second logic array controls the function to be performed by the arithmetic and logic unit (ALU), if called upon during the course of each sequence. It also controls the operation of the condition register in latching the flags generated by the ALU. A separate address arithmetic unit (AAU) is provided to expedite the many required address calculations. The last major portion of the microprocessor contains four 16-bit pointers: the program counter (PC), the stack pointer (SP), a temporary register (T16), and the register pointer (RP). The RP points to the location in the 65K memory space allocated to working registers.

One of the advantages of off-chip registers is that a large number of registers (16 in the case of the MAC-8) may be used. Other advantages are not so obvious. For example, a time-critical routine might push the RP and load a new RP value, which, in essence, pushes all registers in one operation. Upon completion of the routine, popping RP returns the original registers to the main program, leaving the registers of the routine untouched until next called upon. Also, a new RP might be selected that partially overlaps the previous set, providing a convenient

Figure 2-1 - MAC-8 Block Diagram

method for passing parameters and a simplified procedure for deep nesting of calls. The point to be noted is that both the RP and SP might vary over a large range, the extremes of which might be difficult if not impossible to predict. Offchip knowledge of these pointer values might be fundamental to the administration of proper memory allocation.

A typical MAC-8 instruction consists of two bytes: the first byte defines the instruction; the second byte provides the four bits required to specify the source register and the four bits that specify the destination. These 4-bit nibbles and the RP are combined by the AAU to form the appropriate memory pointers.

### PINOUTS

The MAC-8 is capable of accessing 65K of memory or I/O via its 16-bit address bus and its 8-bit data bus. Table 2-1 shows the pinouts. The microprocessor is equipped with DMA, one interrupt, and a reset. Two clock inputs are provided, and a resonator connected between them will activate an internal clock. One of the pins serves as the clock input if an external clock is used. A third pin (clock output) provides a clock for use by peripheral hardware. The data ready lead is instrumental in providing wait states for accessing slow memory or I/O. Finally, three status outputs determine the status of internal components of the chip, such as the values of RP and SP. These status signals are described in more detail in a subsequent section of this paper.

#### ELECTRICAL CHARACTERISTICS

The MAC-8 is a static microprocessor capable of operating at clock frequencies in the 0 to 2 MHz range. All pins are transistor-transistor logic (TTL) compatible, with each output capable of driving one standard TTL load. Total power consumption is below 200 mW at 2 MHz.

#### TIMING

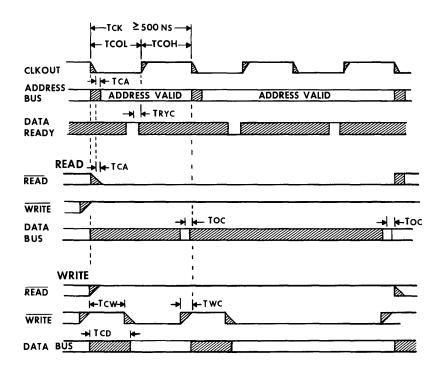

Preliminary timing waveforms are shown in Figure 2-2. The address bus and read signal are updated at the start of each machine cycle, which for sufficiently fast memory is a single clock cycle. The read signal specifies the direction of data flow on the data bus and, therefore, remains low for two successive read cycles. The data bus is strobed at the end of each read cycle.

# TABLE 2-1

# MAC-8 DIP PINOUT

|         | Function                                 | Pin No.                         |

|---------|------------------------------------------|---------------------------------|

| Address |                                          | 12                              |

|         | a14                                      | 11                              |

|         | a13                                      | 10                              |

|         | a12                                      | 9                               |

|         | a11                                      | 8<br>7<br>6<br>4<br>3<br>2<br>1 |

|         | a10<br>a09                               | l<br>B                          |

|         | a09<br>a08                               | 4                               |

|         | a07                                      | 3                               |

|         | a06                                      | 2                               |

|         | a05                                      | ī                               |

|         | a04                                      | 40                              |

|         | a03                                      | 39                              |

|         | a02                                      | 38                              |

|         | a01                                      | 37                              |

|         | a00                                      | 36                              |

| Data    | d7                                       | 14                              |

|         | d6                                       | 15                              |

|         | d5                                       | 16                              |

|         | d4                                       | 17                              |

|         | d3                                       | 18                              |

|         | d2                                       | 19                              |

|         | d1<br>d0                                 | 20<br>21                        |

| !Read C |                                          | 21<br>22                        |

| !Write  |                                          | 23                              |

| Data R  |                                          | 35                              |

| Data R  |                                          | 33                              |

|         | cknowledge                               | 34                              |

| Interru | pt Request                               | $2\overline{4}$                 |

| !Reset  | Teo 700 1                                | 25                              |

| Clock   | Out                                      | $\overline{32}$                 |

| Clock   | Resonator Pin 0                          | 31                              |

| Clock   | Resonator Pin 0<br>Resonator Pin 1 or In | 30                              |

| Status  | s2                                       | 28                              |

| Status  | s1                                       | 29                              |

| Status  | s0                                       | 27                              |

| Vcc     | +5V                                      | 5                               |

| Vdd     | +12V                                     | 26                              |

| Vss     | 0V                                       | 13                              |

! is logical negation, indicating active low signal.

Figure 2-2 - Preliminary Timing Waveforms

A write access cycle includes a write pulse that is activated after the address has stabilized and returns high 50 ns (nominal) before the end of the cycle. Both write and nonaccess cycles have a high-logic level on the read pin, indicating that the on-chip data bus drivers are activated.

Slow memory or I/O ports are accessed via the data ready input. Prior to each midcycle, the data ready input is strobed by the chip. Detection of a low-logic level causes the machine cycle to be extended until a high level is strobed. The machine cycle is terminated during the second half of that clock cycle. It should be noted that the data ready input is ignored during nonaccess clock cycles.

DMA, interrupt, and reset inputs can be changed at any time, and are appropriately strobed into the MAC-8. Interrupt and reset inputs are strobed at the start of the last machine cycle of each instruction or function. A low level on either input begins a sequence of states that pushes the control register (CR) and PC onto the stack, clears the interrupt enable flip-flop, and applies address X(FFFF) to the address bus. If interrupting, the peripheral hardware should respond to this address with a vector on the data bus that, when combined with a high byte of X(00), forms the pointer to the interrupt handler. Reset automatically vectors to address X(0000). The similarity of the reset and interrupt operations is intentional, allowing the reset to be used as a nonmaskable interrupt.

The logic level on the DMA request lead is monitored at the beginning of each machine cycle. If a request is detected, a low-going DMA acknowledgment is generated as the read and write drivers and the address bus and data bus drivers are switched to their high-impedance states.

## STATUS

The remaining MAC-8 pins are the status outputs. These signals indicate when the address and/or data bus contains information about internal status (such as RP and SP) or if an internal condition of special significance exists. Since the above situations cannot always exist, one of the status indications represents "no other reportable status." Seven other independent internal events are each assigned a 3-bit status code. See Table 2-2.

#### TABLE 2-2

## STATUS ASSIGNMENTS

| Function             | Status<br>(S2, S1, S0) |

|----------------------|------------------------|

| PCT Opcode Fetch     | 000                    |

| PC Opcode Fetch      | 001                    |

| RP Change            | 010                    |

| PCF Opcode Fetch     | 011                    |

| No Reportable Status | 100                    |

| Halt                 | 101                    |

| SP Change            | 110                    |

| Тгар                 | 111                    |

|                      |                        |

The RP and SP codes indicate that, during the next machine cycle, the RP or SP, respectively, will appear on the address bus. Each instruction that can result in

a change in either pointer will contain at least one appropriate status signal. The last SP or RP status signal of any instruction or function will correspond to the final correct internal pointer value.

Similarly, status signals PCT, PC, and PCF indicate that an operation code (opcode) fetch is scheduled for the next cycle. As mentioned previously, this is also the cycle in which the interrupt and reset inputs are strobed. If the machine cycle following one of these status indications is a read access cycle, the following statements are true.

- A new instruction has begun.

- The address bus contains the pointer (PC) to the opcode.

- The data bus contains the opcode.

If it is not a read access cycle, the beginning of an interrupt-reset sequence is indicated.

The PCT signal differs from the other two indications because it indicates when the fetch causes a discontinuity in the program flow. This makes it useful for program tracing. The PC and PCF signals correspond to in-line fetches (i.e., no discontinuity). The PCF signal is unique in that it indicates when the otherwise idle data bus is used to output the condition register.

One of the MAC-8 instructions is the HALT instruction, which switches the bus drivers to the high-impedance state and puts out the halt status indication. The status signal remains as long as the state is maintained. The halt state can be terminated only by a reset or an interrupt.

The final status output is trap. The signal is generated when the control logic array gets lost in the execution of an instruction. The only predictable use is when an unassigned or illegal opcode is encountered. A trap results in the chip going through the same sequence of states as an interrupt or reset (the CR and PC are pushed) until the interrupt acknowledge. At this point, control is transferred to address X(0008). Interrupt-reset acknowledge is not generated. The interrupt enable flip-flop, however, is reset.

The unassigned opcodes, of which there are 53, can be used with their functions defined by the trap handler. For example, one-byte calls can be implemented

easily. One application already in use is the insertion of one-byte break points. It should be noted that the value of PC pushed on the stack is two past the location of the invalid opcode.

#### SUMMARY

The MAC-8 is a bus-structured microprocessor having access to a 65K 8-bit memory space. The simple bus structure makes the accessing of commercially available medium and large scale integration (MSI and LSI) peripherals, including memories, straightforward. The microprocessor is equipped with DMA, interrupt, and reset features. In addition, power-on reset, static operation, low power, and a single-phase internal clock make the microprocessor a viable candidate for a broad spectrum of applications. The memory accessing modes and instructions are generous compared to outside alternatives.<sup>2</sup> A convenient set of status outputs is not only attractive from a hardware point of view for applications such as trace tables, memory allocation administration, sanity logic, and usable unassigned opcodes; but also contributes significantly to the testability (in reasonable detail) of the chip.

## REFERENCES

- 1. D. E. Blahut and R. C. Brainard, <u>MAC-8 Microprocessor</u> <u>Hardware Manual</u>, TM-76-4391-3, TM-76-1353-7, June 17, 1976.

- 2. S. T. Campbell, MAC-8 Microprocessor Summary, Memorandum for File, Case 38565-2, March 8, 1976.

### IN-HOUSE MICROCOMPUTERS

### DESIGN AND FABRICATION OF THE MAC-8 MICROPROCESSOR CHIP

J. A. Cooper, Jr., and R. H. Krambeck, BTL Dept 2261, MH, NJ

#### ABSTRACT

The MAC-8 microprocessor chip was designed and fabricated using silicon-gate complementary metal oxide semiconductor (CMOS) technology. However, many of the circuits are not CMOS, but n-channel metal oxide semiconductor (NMOS) with p-channel load devices. These circuits, called pseudo-NMOS, dissipate more power than CMOS but have layout advantages for gates having more than four inputs. The performance characteristics of CMOS versus pseudo-NMOS as used in the MAC-8 are discussed first.

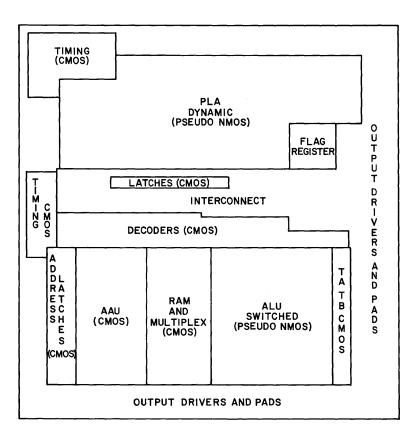

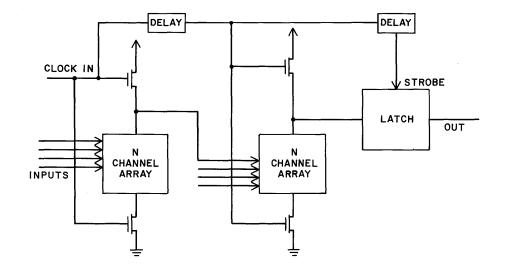

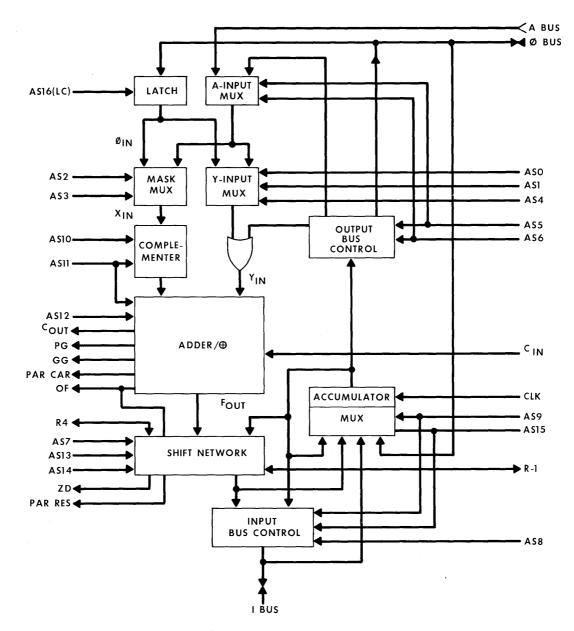

Next, an overview of the major circuits in the MAC-8 is presented. Internal timing waveforms are derived from CMOS delay elements which partially compensate for processing variations. Control is accomplished primarily by a programmed logic array (PLA), implemented in dynamic pseudo-NMOS. The PLA sequences the microprocessor through the state diagram and provides internal control signals. The control signals produced by the PLA are encoded and must be decoded by CMOS gates which control the register, arithmetic, and logic unit (RALU) section. The RALU contains an 8-bit arithmetic logic unit (ALU), implemented in static pseudo-NMOS, a 4- by 16-bit static CMOS random-access memory (RAM), a 16-bit CMOS address arithmetic unit (AAU), and a master multiplexer implemented with complementary transmission gates.

## INTRODUCTION

The object of the MAC-8 microprocessor program is to produce a microprocessor uniquely suited to Bell System needs. The development of the architecture and proposed program set, therefore, involved inputs from many parts of the Bell System. Similarly the choice of a technology to implement the MAC-8 was based upon inputs from several Bell Laboratories departments.

The technology that was chosen was CMOS. The main reason for this choice is the great flexibility in circuit design that is possible when both p- and n-channel transistors are present on the same chip. For example, simple one- and twoinput gates, such as those found in the latches and on-chip registers, are made with complementary circuitry. Thus a great advantage in power consumption, compared with NMOS, is gained without using significantly more area. Meanwhile, highly complex combinational gates found in the ALU and PLA are implemented using pseudo-NMOS, just as in NMOS except that the load transistors are p-channel. As a result the areas of these circuits are also comparable to those of their NMOS counterparts. Moreover, since the outputs of these circuits are transferred to static latches, they need not consume static power. Therefore, overall chip power is still comparable to the power consumed by an all-CMOS chip.

Consequently, the gate density of the chip is comparable to NMOS but has a power consumption more typical of CMOS. Flexibility in supply voltages is also typical of CMOS. The chip is expected to operate at 2 MHz with a supply of 12V and with supply voltages of between 4.5 and 13V. A second 5V power supply is required to operate the on-chip transistor-transistor logic (TTL) interface circuitry. Some special features of the chip are TTL-compatible inputs and outputs and a crystal oscillator circuit.

## CIRCUIT DESIGN

The flexibility of CMOS permits the use of different kinds of circuits for different parts of the microprocessor. Figure 3-1 shows how the area of the chip is occupied and the kind of circuit used in each section. There are three: CMOS for registers and simple gates, dynamic pseudo-NMOS for the PLA, and static switched psuedo-NMOS for the ALU. These circuits have been chosen for the following reasons.

Figure 3-1 - Block Diagram of Chip

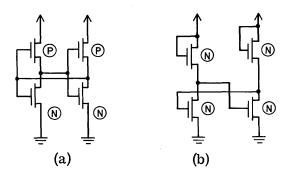

A substantial part of the chip area holds registers for storing data and drivers for providing buffering. Figure 3-2(a) shows the circuit used for a pair of crosscoupled inverters using CMOS. The corresponding circuit for NMOS is shown in Fig. 3-2(b). As can be seen, both require four transistors and would take about the same area. However, although both are static, only the NMOS circuit requires significant current to hold its data. It is therefore advantageous to use CMOS for making inverters and registers. There is little penalty in area and negligible static power consumption. For most of the random logic in the control part of the chip, CMOS is also used. A two-input NAND or NOR gate uses four transistors in CMOS, compared with three in NMOS, so some additional area is used, but overall impact on chip area is slight. CMOS is also used for the AAU where most of the gates are also relatively simple.

The gates in the ALU were not well suited to CMOS because of their great complexity. Figure 3-3(a) shows a typical ALU gate using CMOS and Figure 3-3(b) the corresponding circuit using pseudo-NMOS. The CMOS has almost twice as many transistors and would take about twice the area. However, the pseudo-NMOS circuit has two important disadvantages. First, it consumes power when its output is low. Second, the requirement that the output be low when any nchannel path is in use forces the choice of a poorly conducting load transistor. As a result pullups are much slower than pulldowns. The static NMOS circuit would therefore be relatively tardy.

To alleviate the first problem, a switch was added to the pseudo-NMOS circuit so that it could be turned off when not being accessed. An n-channel transistor

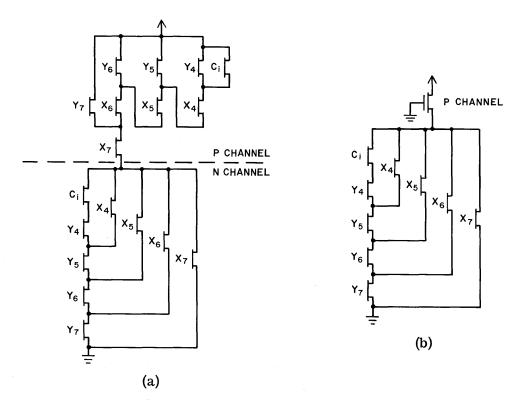

Figure 3-2 - CMOS and NMOS Memory Elements

Figure 3-3 - CMOS ALU and Pseudo-NMOS Gates

was used between the circuit and ground. Since the ALU is accessed only once about every six cycles, most of the power drain has been eliminated in this way. The problem of slow pullups is handled by arranging the circuit so that all pseudo-NMOS nodes are precharged high during the intervals between accesses and no pullups ever occur during access. Such an arrangement is illustrated in Figure 3-4. The first stage is turned on only after all inputs are stable. Therefore, its output either stays high or is pulled down. The CMOS inverter driven by the first stage converts the output to a rising signal. (CMOS pullups are fast so this pullup does not significantly increase access time.) As a result, the imputs to the second stage are either fixed or make a low-to-high transition. Therefore, the second-stage output, like the first, stays high or is pulled down. The inputs to the third stage make high-to-low transitions. Therefore, third-stage turnon is delayed until all of its inputs are stable. Finally, the output of the third stage is buffered by a CMOS circuit for delivery to other parts of the chip. The result is a circuit with the area of NMOS but with a small power drain and speed considerably faster than a standard NMOS circuit.

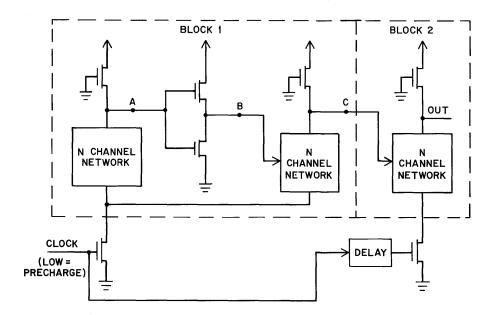

The PLA presents a somewhat different problem. It must be accessed every cycle, so the circuit used for the ALU would not be suitable. Its gates are quite complex, so CMOS would waste considerable area. For the PLA the slow pull-up problem was eliminated by the clocking arrangement shown in Figure 3-5. The p-channel

Figure 3-4 - ALU Block Diagram

load is on only when the n-channel switch is off. Each stage is precharged by a low clock signal and accessed by a high clock signal. The delay in access of the second stage is necessary to ensure that its inputs are stable before access begins. The result is a circuit with the area of NMOS but with no static power drain. As in the ALU, speed is maximized by the elimination of pullups during access. Since the outputs are dynamic, each is fed into a latch which is strobed after the second-stage outputs are correct and before precharge for the next cycle begins.

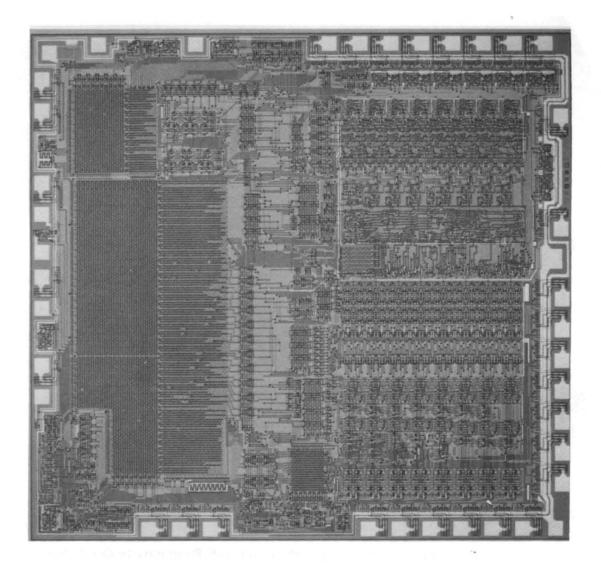

### CHIP REALIZATION

The chip was fabricated on the Murray Hill CMOS line. A photograph is shown in Figure 3-6. The chip is 5.9 by 5.55 mm and contains approximately 7500 transistors of which over 80 percent are n-channel. It is shipped in a 40-pin dual in-line package (DIP).

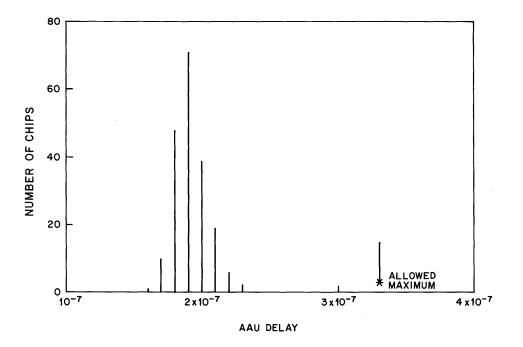

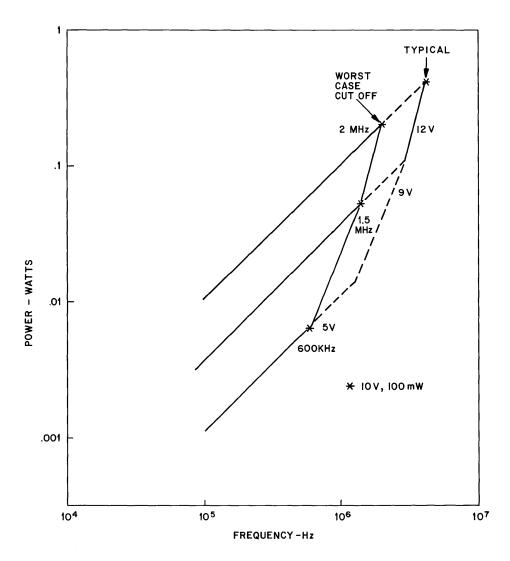

The chip and its constituent parts were tested extensively both on the bench and on the Murray Hill automatic test system, the Sentry 600. Data on access times of various circuits were gathered as an example. Figure 3-7 is a histogram of AAU access time for 16-bit increment. The maximum allowed value is also shown. A sequence of test vectors developed by R. Gallant is also part of the Sentry test and, when complete, will exercise all transistors on the chip. The oscillator circuit has been successfully operated with crystals of 1, 2, 3, and 6 MHz, showing wide margins with respect to actual demands. The power re-

Figure 3-5 - PLA Block Diagram

Figure 3-6 - The MAC-8 Microprocessor Chip

quirements as a function of frequency and applied voltage are presented in Figure 3-8. Packaged samples are now available or soon will be, and Bell Laboratories design information (LDI) transmittal is scheduled for January, 1977.

Figure 3-7 - AAU Delay for 16-Bit Increment for 196 Functionally Good Chips

Figure 3-8 - Power vs. Frequency, Showing Worst Case and Typical Frequency Cutoffs

.

## IN-HOUSE MICROCOMPUTERS

## **TESTING AND DEBUGGING OF MAC-8 SYSTEMS**

C. F. Shupe, BTL Dept 8623, HO, NJ

K. W. Johnson, BTL Dept 4391, HO, NJ

B. B. Hofmann, BTL Dept 4393, HO, NJ

Testing shows the presence, not the absence, of bugs.

E. W. Dijkstra

A debugged program is one for which you have not yet found the conditions that make it fail.

J. Ogdin

Debugging is an art.

E. Yourdon

#### ABSTRACT

The main objective in designing the MAC-8 microprocessor software testing tools was to give the MAC-8 user the ability to test at the source code, as opposed to the object code, level. The goal was achieved by using modern software testing techniques from the data processing industry.

The MAC-8 software testing tools are (1) the MAC-8 software simulator (m8sim) and (2) the program logic aid (PLAID) development system. This paper describes the high-level functional design of m8sim/PLAID and its implications for the MAC-8 user. An important aspect of the design is the compatibility between m8sim and PLAID in spite of the differences in their host environments.

### INTRODUCTION

The testing of any piece of software is apt to be slowed by the discovery of an error. The discovery of the error's cause (the bug) is termed debugging. Correcting the bug allows testing to resume.

Testing, debugging, and correcting are facts of life in any software project. The confusing aspect of microprocessor software is the obvious hardware nature of the processor itself. After all, when we program a large computer in a high-level language we don't worry about the interrupt pending bit or other real-time considerations. We also tend to think of a microprocessor plus software in terms of its hardware equivalent. But the reality remains that to have a microprocessor perform useful work, we must write, test, debug, and correct software. Any real-time aspects of the application only make these tasks more challenging.

This paper describes the high-level techniques and capabilities that have been designed for the testing, debugging, and correcting of software for the MAC-8 microprocessor. Some features will not be implemented by the time of publication.

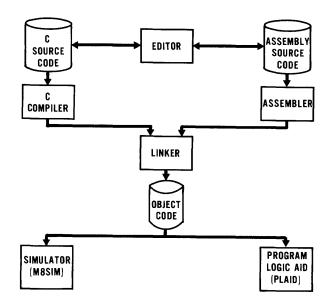

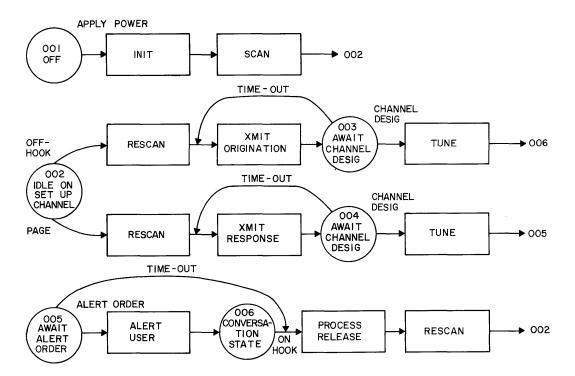

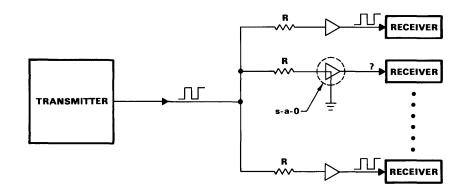

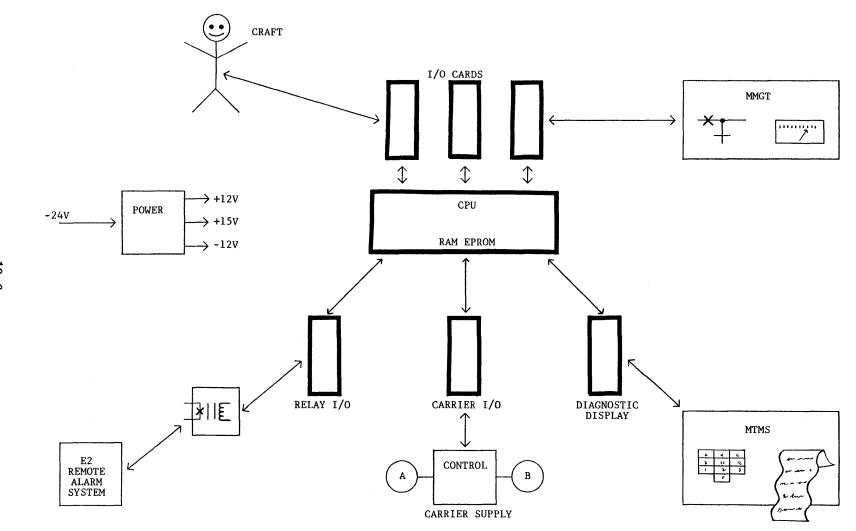

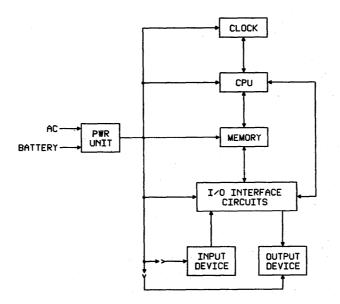

In the MAC-8 support system (see Figure 4-1), software source code is first written in the C and/or assembly language and is then compiled and linked into object code. An example of source code is "A=B;" and its corresponding object code is a numerically coded MAC-8 move instruction which includes the absolute addresses for symbols A and B. MAC-8 object code is tested interactively by the software simulator m8sim<sup>1</sup> or, in a hardware environment, by PLAID. The m8sim and PLAID are the MAC-8 debugging aids and the components of the simulator/PLAID (S/P) subsystem for the MAC-8.

Software testing consists of varying certain conditions (such as input data), observing how the software reacts, and comparing this behavior with the expected behavior. With m8sim all inputs to the program are contrived by the user, and the behavior of the program is monitored solely through the output that m8sim provides. In PLAID the user program runs in its intended real-time environment in which the user can modify the inputs and monitor the behavior of the program. The user by means of either debugging aid seeks the cause of erroneous software behavior. Once the cause is found and a cure is devised, the user makes the correction at the source level and obtains new object code. Testing then resumes

Figure 4-1 - MAC-8 Support System

on the now-modified program. It is important to note that the user software is exercised at the object code level whereas the user is thinking in source code throughout the process.

## THE ASPECTS OF HIGH-LEVEL DEBUGGING

Our knowledge of high-level debugging, developed and refined in the large-computer environment, has been applied to the MAC-8 microprocessor.  $^2$

## The Source Code Philosophy

Early in the development of the MAC-8 support system (see Figure 4-1), the source code of the user was defined as the basic unit of the system. This philosophy resulted in the following features.

- The editor, which is used to enter and change the source code, is line-number driven as well as context driven.

- Compiler and assembler diagnostics reference the line number of offensive source code.

- All user software changes are made at the source code level, ensuring that source and object are always in agreement.

- The m8sim and PLAID allow the user to debug using the symbolic names in the source code, in addition to providing a line-number mapping between source and object.

### The Command Language

The second aspect of high-level debugging is the necessity for a command language with the following characteristics. First, interactive aids, which require a command language for communication of requests, are necessary for efficient debugging. Second, when there is more than one debugging aid (as is common in microprocessor applications) a single command language is desirable for the sake of user sanity. And finally, the high-level command language for the debugging aid must be consistent with the environment in which it is used.

Of these three requirements, matching the command language to the user's needs as well as to the operating environment is the most difficult. The user acquires a working knowledge of the C language, used in both the MAC-8 C compiler and the assembler and of the UNIX operating system, host of the MAC-8 support system (auxiliary support for PLAID). As m8sim and PLAID are in a UNIX/C environment with which the user is familiar, we deduce that the command language for these debugging aids must somehow be consistent. But since neither the C language nor the UNIX command language alone was suitable as a debugging aid command language, an S/P command language was purposely designed to incorporate the best features of each: the conventions for entering m8sim and PLAID commands, plus the underlying command syntax, are in agreement with UNIX; the C influence appears most obviously in the expressions and value assignments as written in the command language.

Let's consider the C language text "A=B+2\*D;", which in English reads: "Assign the value of the expression B+2\*D to the symbol A." This is a typical C statement which a user might write for a MAC-8 application in which A, B, and D are symbols known to the C compiler. However, expressions and value assignments are also essential for displaying and changing values in the debugging process. As a result of the S/P command language design, the statement "A=B+2\*D;" is also a valid command for both m8sim and PLAID and has the same meaning for them as it does for the C compiler. Thus a MAC-8 user need know only one way of expressing "A=B+2\*D;" to be immediately able to evaluate proposed source-level changes in either m8sim or PLAID.

The S/P command language allows the user to enter explanatory comments in C syntax, along with the commands themselves. Comments are as useful in the debugging process as in the writing of source code and the command language is consistent in this respect with C.

By providing a generalized based-number representation which permits the user to express quantities in any reasonable number base the S/P command language has surpassed even the C language. There are additional important similarities, which we will not discuss, between C and the command language. In summary the consistency of the S/P command language with the source languages and operating system is an important aspect of high-level debugging.

## Functions

The third and most significant aspect of high-level debugging is the collection of functions which the debugging aid can perform for the user. In this regard the techniques of large-computer debugging can serve the particular needs of the microprocessor user.

In practice the user enters a command which causes m8sim or PLAID to perform a particular function, the selection and sequence of which must always be under user control. The m8sim and PLAID functions fall into one of the following categories: basic, simulation/execution, or auxiliary functions.

> • <u>Basic Functions</u>: The underlying power of m8sim and PLAID is derived from the user's ability to converse symbolically, as well as in absolute terms. The symbols are defined in the source code of the user, by the MAC-8 architecture (including the on-chip registers, such as the program counter, and the user registers in random-access memory [RAM]), or by the user within m8sim or PLAID. The latter type of symbol includes timers and pseudovariables, which are treated like user program symbols but reside outside of the program memory space; the actual use of timers and pseudovariables will be

discussed later. Numerical quantities may be expressed using a based-number convention, which is supported for bases 2 through 36.

Symbols and numbers may be combined into expressions using a subset of the C language arithmetic operators. Examples are the familiar addition and subtraction, the logical operators, and the everuseful "address of" and "pointed to" operators. In fact, m8sim and PLAID are great based-number calculators because of their expression-evaluation capability, but their power and flexibility really become evident during the simulation (in m8sim) or execution (in PLAID) phase of a user program.

There is, of course, the necessary function for displaying values of symbols, registers, and expressions. Just as important is the value assignment, mentioned previously, by which the user can change the registers, symbols, or pseudovariables. Another function lists all registers.

• <u>Simulation/Execution Functions</u>: The simulation/execution monitoring functions for a user program are concerned with (1) memory management, (2) simulation/execution control, (3) breakpoints, and (4) timers.

Memory management functions allow the user to define the memory space, i.e., to specify read-only addresses and input/output (I/O) ports, and to load user programs into the simulated or real memory. The control functions cause actual simulation or execution to begin. Breakpoint functions allow the user to define and remove interruptions of simulation/execution. Breakpoint definitions are classified as conditions and actions. Conditions are written as expressions, with the ability to specify user memory read and/or write accesses as operands. The actions are sets of S/P commands, to be executed whenever the conditional expression is true. In addition to the traditional breakpoint sequence in which control is always returned to the user, simulation/execution may continue automatically if the user desires. A pseudovariable, for example, can be automatically incremented into a subroutine; the user may later interrogate this quantity as an indication of subroutine usage. There are two types of timers: range timers, which are active only when the program counter is in a specified address range, and extent timers, which are turned on or off under explicit user control. Range timers are particularly useful for measuring code efficiency, whereas extent timers are more useful for real-time debugging and critical path evaluation.

A noteworthy feature of the simulation/execution function is the ability to inform the user of how simulation/execution is progressing by printing out the source code which corresponds to the simulated/ executed instructions. This code is extracted from the original source file of the user and includes comments made in the source language.

Traces, the past history of simulation/execution, are most useful in PLAID where a program may be run in real time, stopped, and then diagnosed. There are two types of traces. One is a list of recently simulated/executed instructions, and the other gives a history of program control transfers.

• <u>Auxiliary Functions</u>: A high-level function lets the user avoid the typing of repetitious command sequences. The user defines a named set (a block) of S/P commands; instead of a regular command, the user can then enter the block name to execute the set of commands.

Another high-level feature allows the user conditionally to execute an S/P command. This option is useful for establishing a decision sequence within breakpoint actions. The presence of a conditional in the command language, incidentally, is another similarity to the C language.

The help function, as its name implies, is designed to give the user reference information about the S/P on demand. It is essentially a built-in reference manual which can easily be updated to make the latest information available to the user.

Other functions offer the user the ability to: (1) interrupt, and later resume, a debugging session with no loss of effort; (2) exercise control over the content and format of the m8sim/PLAID output; and (3) draw command input from a file. There are other functions which we will not discuss here.

### THE SIMULATOR AND PLAID ENVIRONMENTS

The high-level debugging features, just described, are available in both the MAC-8 simulator m8sim and PLAID (when connected to UNIX). The rationale for using both m8sim and PLAID is, of course, based on (1) the wide availability and low cost of m8sim and its utility in debugging logical programming errors, and (2) the ability of the PLAID user to diagnose real-time, software, and hardware problems and to verify real-world operation. Of necessity, then, there are some differences in the environments and uses of m8sim and PLAID.

### The MAC-8 Simulator (m8sim) Environment

The host for the MAC-8 support system (see Figure 4-1) is the UNIX operating system, which provides time-shared computing for multiple users. Each user accesses UNIX through a remotely located ASCII terminal à la modem. In preparing a software program for the MAC-8 the user builds a source code file using the UNIX text editor. The source code is compiled, assembled, and linked, resulting in an object code file. At this point the user may invoke m8sim and evaluate the functioning of the application program. Initially, in the testing phase the incidence of bugs is high, requiring numerous iterations of debugging and correcting the source. Although the user leaves m8sim to make source corrections and to construct a new object file the overhead time involved is minimal. At some later point the user becomes confident that the m8sim testing has revealed most logical programming errors and is thus ready to test in the hardware environment.

#### The PLAID Environment

,

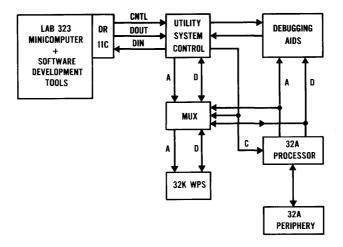

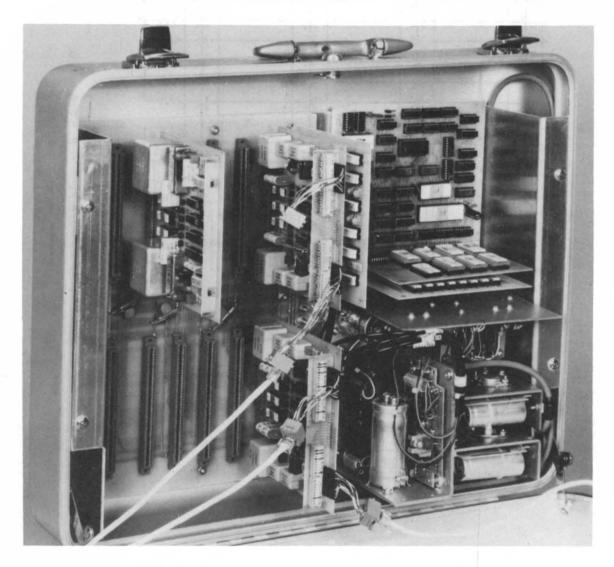

Before actually discussing the PLAID environment we first need to mention its architecture and options. PLAID is itself a hardware unit to which the user connects a standard ASCII terminal in order to communicate with PLAID and, through PLAID, with UNIX. There is a built-in modem for establishing the phone line tie with UNIX. Although PLAID may be operated with reduced capabilities without UNIX, we assume in the following discussion that the PLAID-UNIX connection has been established. An external microprocessor access and control (MAC) cable enables connection to be made with the user application system hardware. (The free end of the cable clamps onto the processor dual in-line package [DIP] socket in that system.) Finally, as an option a floppy disc may be attached for the local storage of object code and object code symbol tables. The user may thus minimize the transmission time of new object code from the UNIX system and utilize the local linker for the object software.

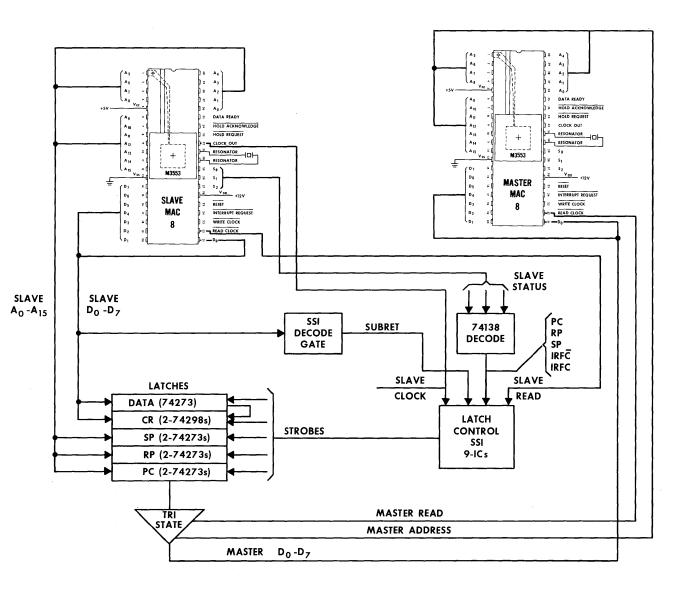

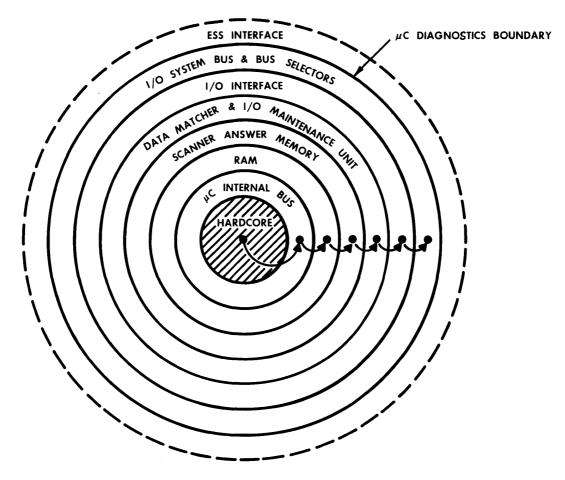

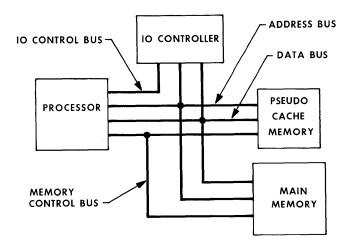

PLAID has an internal master subsystem, which performs executive and command processing functions, and a slave subsystem, which can be used in a variety of useful ways. The slave has a bus to which are connected the MAC cable, a MAC-8 microprocessor, a 65K RAM, and 36 I/O ports. Any combination of 1K RAM segments can be overlaid by 1K programmable read-only memories (PROMs), the procedure followed in the later stages of the development of an application. The slave I/O ports can be enabled or disabled in groups of 12.

PLAID may be operated in the basic mode in which case it functions very much like m8sim. With the slave processor executing the user program from the slave RAM and the program I/O directed through the slave I/O ports, the user will find few functional differences between m8sim and PLAID. The basic mode is typically employed during the initial implementation of a system when hardware development and software development are proceeding simultaneously. The fact that the three components of the slave - the processor, memory, and I/O ports can be independently substituted for the user processor, memory, and I/O ports gives the user very powerful hardware prototyping capabilities. In a typical situation the user program in slave RAM will be executed by the user processor with a mixture of slave and user I/O ports, while execution is monitored by the PLAID master via the MAC cable. As the user hardware grows during development, less and less of the slave hardware is used, until such time as the system is complete. After completion PLAID is also quite useful in monitoring system operation and diagnosing hardware and software failures. Consequently, throughout the life of the user system, PLAID allows the user to test in real time (with the possible exception of breakpoints) with real I/O activity.

## SUMMARY

The MAC-8 support system has proven the initial assumption that state-of-the-art techniques drawn from the large-computer environment can be successfully applied

to microprocessors. Specifically, the high-level facilities in m8sim and PLAID are designed to ease the testing, debugging, and correcting burden by providing the necessary interfaces between the user and the user object code. We emphasize the advantages of a single command language for both m8sim and PLAID. In addition the combination of m8sim for simulation and PLAID for execution monitoring and hardware prototyping gives the user maximum flexibility in the testing and debugging of MAC-8 systems.

We would like to acknowledge the many people who, through their suggestions and criticisms, have contributed to the design and implementation of both m8sim and PLAID. Steve Campbell, in particular, deserves recognition for his participation in the original design process.<sup>2</sup>

# REFERENCES

- 1. C. F. Shupe, <u>MAC-8 Simulator (m8sim) User Manual, Version 1.2,</u> Memorandum for File, Case 39898-14, June 30, 1976.

- 2. S. T. Campbell and C. F. Shupe, <u>MAC-8 Simulator/PLAID Design</u> Specification, Memorandum for File, Case 39898-14, June 30, 1976.

.

### IN-HOUSE MICROCOMPUTERS

# THE MAC-8 IN A USER ENVIRONMENT

F. B. Torres, BTL Dept 4391, HO, NJ

## ABSTRACT

The first bona fide application of MAC-8 in a true working environment is the PLAID console. A wire-wrap version of PLAID, which has been built and tested, demonstrates the relative ease with which MAC-8 works with a variety of peripheral devices, including the following:

- Intel 2116, 16K by 1 dynamic random-access memory (RAM) with associated 3242 address multiplexer/refresh counter.

- Intel 2708, 1K by 8 programmable read-only memory (PROM).

- Intel 8255, programmable peripheral interface.

- Intel 8251, universal synchronous/asynchronous receivertransmitter (USART).

- Intel 8253, programmable interval timer.

- Intel 8259, programmable interrupt controller.

- Vectron external clock oscillator.

PLAID has also shown that MAC-8 functions harmoniously with external circuits providing such features as direct-memory access (DMA) capability, programmable wait state generation for slow memories, write protection for selected RAM locations, and overlay of RAM locations by PROM and input/output (I/O). In addition it has been demonstrated that MAC-8 can indeed be used in a multiprocessor environment.

Other characteristics of the MAC-8 which have been brought to light by PLAID are the ability to latch the contents of the on-chip registers from the address and data buses, to recognize when the off-chip registers are being accessed, and to snapshot the old and new values of the program counter (PC) in cases of such PC discontinuities as JUMP or CALL.

The purpose of this paper is to present selected circuits used in PLAID which illustrate some of these features.

#### INTRODUCTION

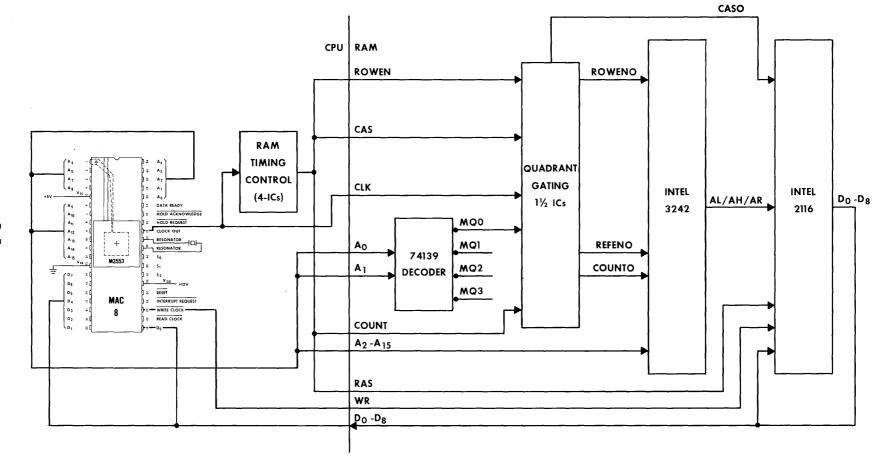

The PLAID console contains two MAC-8 microprocessors and numerous peripheral circuits. The processors work together as master and slave. The peripheral circuits perform functions such as dynamic RAM, PROM, I/O, wait states, write protection, DMA, interrupt priority, user system monitoring, and links to a terminal and UNIX. PLAID demands that the MAC-8 be capable of functioning with a wide variety of peripheral devices, including another MAC-8. The wirewrap version of PLAID demonstrates that these demands have been met with relative ease.

This paper discusses several circuits controlled by MAC-8 which are used in PLAID.

## RAM

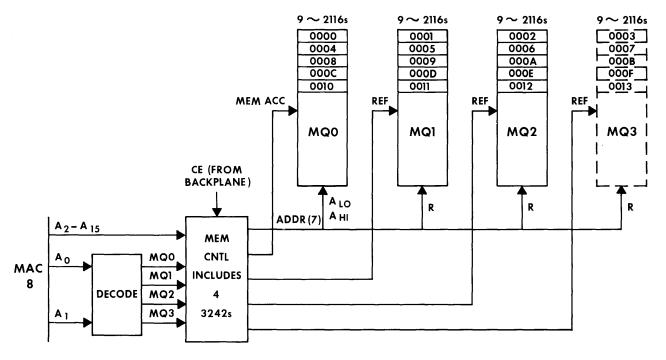

The RAM circuit uses the Intel 2116, 16K dynamic RAM and the Intel 3242 address multiplexer and refresh counter. Since timing constraints at a 2-MHz clock rate prohibit both memory refresh and access in the same cycle, another method of refresh had to be used. Because it slows down the processor, cycle stealing was ruled out in favor of memory quadrant rotation, a scheme which causes the MAC-8 to access successive quadrants of memory on incremental PC values (see Figure 5-1). While one quadrant is being accessed, the other three are being refreshed. Address bits  $A_0$  and  $A_1$  are decoded to indicate to the four Intel 3242s which quadrant is being accessed. The Intel 3242s apply address bits  $A_2$  through  $A_{15}$  in two groups of seven bits to the quadrant being accessed and the internal counter addresses to the quadrants being refreshed. During

### 65K OF READ-WRITE MEMORY

Figure 5-1 - Memory Quadrant Rotation

clock cycles when RAM is not being accessed, all four quadrants are refreshed. This method of refresh control permits operation of the MAC-8 at frequencies well below 2 MHz without danger of losing RAM data. We recognize the fact that successive PC values are not always continuous, and occasionally the same quadrant may be accessed several times in succession. The chip enable (CE) input to the memory control allows RAM to be placed in a high impedance state, permitting PROM and I/O to overlay portions of the 65K available memory space.

Figure 5-2 shows one quadrant of the actual circuit used in PLAID for RAM control. Row address select (RAS), column address select (CAS), row enable (ROWEN), and COUNT are derived from the MAC-8 clock on the central processing unit (CPU) board. The write pulse (WR) is taken directly from the MAC-8. The memory quadrant 0 (MQ0) being accessed is derived from the two least significant address bits. These signals provide the Intel 3242 with the information it needs to control the RAM devices in quadrant 0 in either a memory access or refresh operation.

## PROM

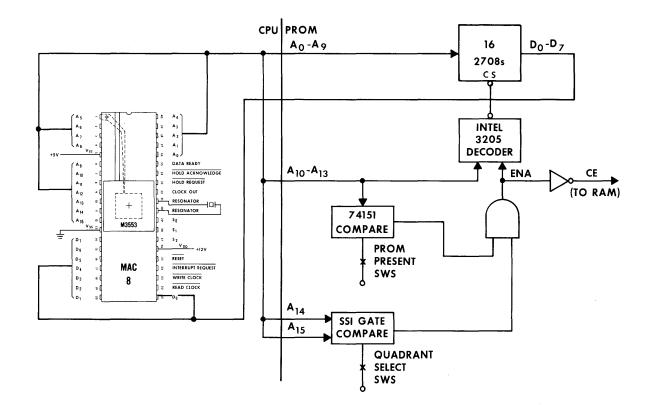

The PROM circuit (see Figure 5-3) uses the Intel 2708, 1K by 8 PROM. Address bits  $A_0$  through  $A_9$  select the appropriate word in PROM, bits  $A_{10}$  through  $A_{13}$  select which of the 16 PROMs to access, and bits  $A_{14}$  and  $A_{15}$  are compared with the quadrant select switches to determine if, in fact, PROM is being accessed. The PROM present switches are also checked to see if the desired PROM is in its socket and not turned off. If all conditions are met, the PROM circuit is given access to the MAC-8 data bus, and the CE signal is forced low to keep the RAM circuit turned off.

### WAIT STATE GENERATOR

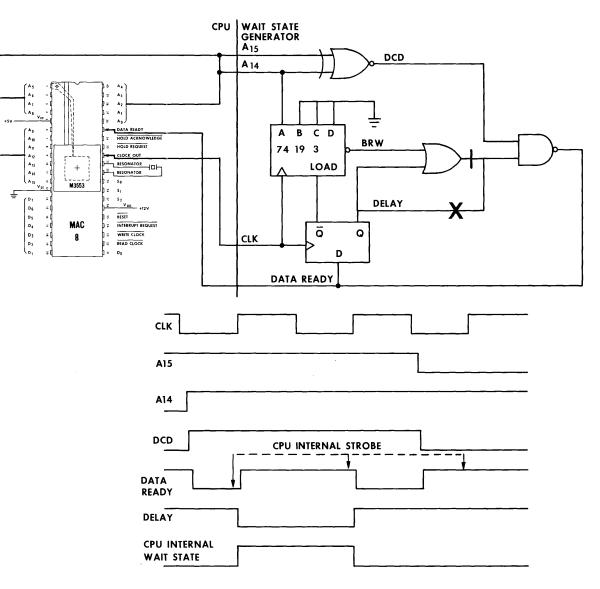

Figure 5-4 illustrates a wait state circuit that can be used with MAC-8. The decoder selects the addresses at which wait states are required. In this example a single wait state is provided by the DELAY flip-flop when the address falls in quadrant 0 or quadrant 3.

Assume that, prior to cycle N,  $A_{15}$  is high and  $A_{14}$  is low. This arrangement forces DCD low and the DATA READY signal high. DELAY is high since the

Figure 5-2 - RAM Control

5-5 -5

Figure 5-3 - PROM Control

Figure 5-4 - Fixed Wait States

5-7

value of DATA READY is clocked into the flip-flop. After the start of cycle N, assume that  $A_{14}$  goes high, for cing DCD high and DATA READY low. At midcycle the MAC-8 strobes the DATA READY signal, finds it low, and sets its internal wait level. DELAY is cleared at the positive clock transition, and DATA READY goes high again. During cycle N+1 the strobe finds DATA READY high and clears its internal wait level. DELAY is again set, for cing DATA READY low. If, in cycle N+2, the new address falls in quadrant 1 or 2, as depicted in this example, DATA READY is restored to its high state and remains there until the next time a wait state is required. If the new address is still in quadrant 0 or 3, the cycle is repeated. In this example the memory access called for by the MAC-8 in cycle N was delayed until cycle N+1, hence a single wait state.

If more than one wait state is required for slower memory applications, a counter may be inserted into the circuit. Here the number of wait states is determined by the value loaded into the counter, plus one for the DELAY flip-flop. The example shows two wait states being generated, but larger values may be used. The number of wait states may be variable for different address locations and may indeed be under program control.

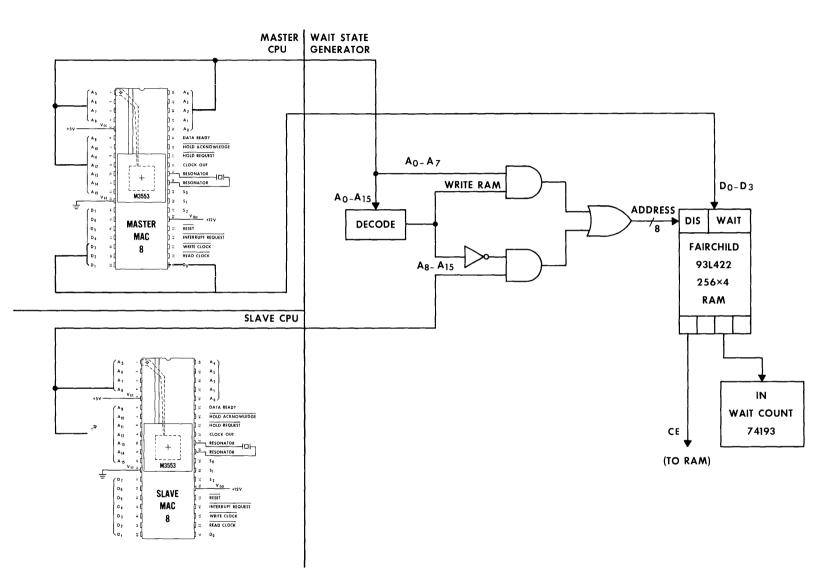

PLAID uses a wait state generator which is under program control. The circuit shown in Figure 5-5 uses a Fairchild 93L422, 256 by 4 RAM. Three of the four bits are used to provide from zero to seven wait states for each of the 256 locations and are loaded into the counter discussed above. Since the control RAM locations are accessed by the slave MAC-8 with its eight high-level address bits, each location represents a page (block of 256 bytes) of MAC-8 memory locations. The control RAM, which is initialized by the master MAC-8 under control of software, also contains a memory disable bit which is used to turn off preselected pages of slave memory. This feature can be used to implement write protection or to allow the user to simply replace part or all of the slave memory with that of the user's own.

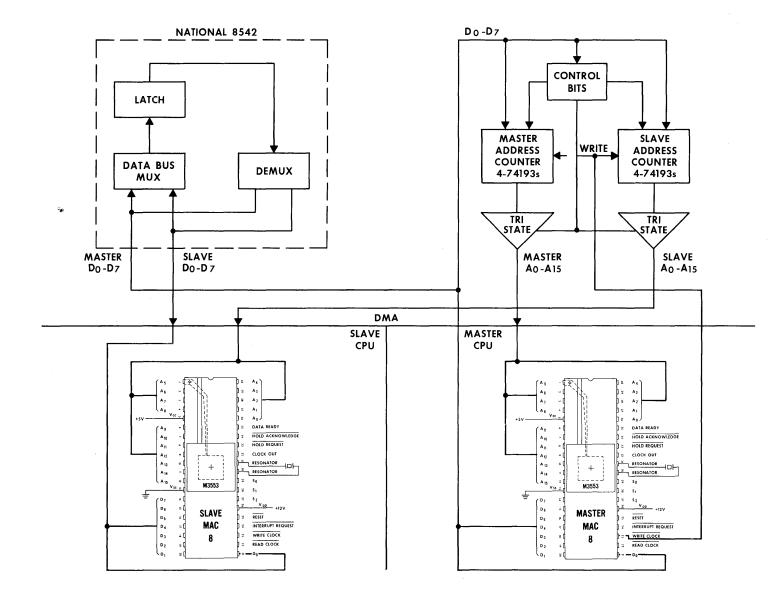

### DMA

DMA in PLAID is mainly used for the exchange of data between master and slave memories. The circuit, illustrated in Figure 5-6, makes use of the National DM8542 I/O register and two counters. The counters, preloaded by the master with the starting addresses of master and slave, may be allowed to autoincrement

Figure 5-5 - Programmable Wait States

5-9

Figure 5-6 - DMA Control

5-10

with each transfer, or one may be held stationary while the other is incremented. Having these operations under program control permits the user a large degree of flexibility. For instance, by holding the slave address fixed at an I/O port, data transfer between the master and the I/O device can take place.

Data transfer occurs through the multiplexer-demultiplexer-latch circuitry of the DM8542. The latch is necessary since timing constraints require two clock **cy**cles per word transfer between master and slave. Control signals are decoded in a 74139 device to direct the mode of operation and to generate the appropriate master and slave write and read signals.

# **MONITORING MAC-8 REGISTERS**

The contents of the on-chip registers appear on the data and address buses at certain times during MAC-8 operation. In order to know what is present on the buses at any given time, it is necessary to know the status of the CPU during the current clock cycle when the operation is under control of the interrupt handler (IH) and a subroutine return (SUBRET) instruction is being executed. In the circuit illustrated in Figure 5-7, CPU status is determined by decoding the three status bits from the MAC-8. IH control begins when the expected read signal from the CPU is not received in the cycle following an IR fetch status. IR fetch without condition register (IRFC), and IR fetch without condition register (IRFC'). IH control ends with the reception of the next PC status. A SUBRET is detected by decoding each instruction that appears on the data bus during the cycle following an IR fetch status. The instruction ends with the next PC or IRFC status indication.

The contents of the RP or SP registers appear on the address bus during the cycle following the RP or SP change status indication. The contents of the PC register appear on the address bus during the cycle following an IR fetch status, provided control has not been transferred to the IH. The contents of the condition register are present on the data bus under the following conditions:

- During the same cycle that an IRFC status is received.

- During the same cycle that a PC status is received, provided that control is not transferred to IH and a SUBRET is not being executed.

- During the cycle preceding that in which a PC status has been received if a SUBRET is being executed.

Figure 5-7 - Snapshotting MAC-8 Registers

5-12

In order to handle the last condition the data bus is latched at each clock cycle. One other operation affects the condition register monitor: each time an IH operation is detected, the interrupt enable (INTE) bit must be cleared.

The monitor registers are updated each time a change is indicated in the on-chip registers and, if enabled, the circuit interrupts the master when a change occurs. The contents of the monitor registers can be read by the master at any time.

# CONCLUSION

I would like to acknowledge the work of D. E. Blahut, R. L. Ferch, and H. B. Greene with whom I shared the circuit design for the PLAID console. Clearly, there are many other interesting circuits in PLAID not covered in this paper. Please call upon us at any time for further discussion of PLAID circuitry. It is our feeling that the MAC-8 microprocessor is not only a device with powerful capabilities but also one that is interesting and enjoyable to work with.

### IN-HOUSE MICROCOMPUTERS

MAC-4

D. C. Stanzione, BTL Dept 4391, HO, NJ

### ABSTRACT

As the sophistication of our microprocessor technology increases and our skill in the use of that technology matures, we are finding that the benefits of memory-based large scale integration (LSI), customized with software, are applicable to a wide range of Bell System products. In particular, applications which require relatively few semiconductor devices and have previously been considered either too cost sensitive or lacking the complexity to justify use of a microprocessor are now candidates for a single-chip microprocessor system - a single-chip device containing central processing unit (CPU), memory, and input/ output (I/O).

The internal structure and characteristics of such a system containing CPU, program memory, data memory, and a sophisticated I/Ostructure are discussed in this paper.

## INTRODUCTION

A phenomenal growth in the development of integrated circuit technology has occurred over the last several years. A familiar statistic is the yearly doubling of the number of components on a single silicon chip and the forecast that this rate of growth will be maintained for at least the next five years.<sup>1</sup> Confronted with this capability in LSI, system designers are pressing to define functional blocks which will utilize it. The identification of the blocks is not simple. The high developmental expense for LSI circuits requires that there be substantial justification for a particular device. Development of a device for a specific customer, usually referred to as custom LSI, normally offers an implementation which provides the lowest device cost for a given function, but it is accompanied by lengthy development times and changing system specifications. These problems become more acute as improved technology provides the opportunity for even greater circuit complexity. Ideally, an LSI circuit would be catalog or off-theshelf, rather than custom, so that it might have a wider market base and be more adaptable to changes in device requirements. Some early examples of successful catalog LSI were memory components and calculator devices.

## ENTER THE MICROPROCESSOR

As integrated circuit technology evolved, a revolutionary, rather than evolutionary, phase in the utilization of the technology occurred. The advent of the microprocessor solved the LSI dilemma of lengthy development times versus changing system requirements and also permitted the use of cost-effective LSI in products with relatively low production volumes. The devices used in a microprocessor system were still customized but based on an entirely different concept: softwareas opposed to hardware-customized LSI. The microprocessor system was now tailored to a particular function by altering its program memory instead of configuring hardware. Designs could be rapidly implemented and easily changed.

With the change in design technique to software-customized systems, real innovation in hardware development shifted from the design of controller logic to that of sophisticated I/O interfaces to the processor and system memory. Most of the difficult problems in microprocessor design involve the application of sequential, stored-program logic in areas where we have traditionally used parallel logic. Most of the solutions to these problems are found in innovative I/O interfaces.

### SINGLE-CHIP SYSTEMS

As LSI maintained its seemingly unimpeded rate of growth, processors became more complex; memory sizes continued to increase; and I/O devices gained in sophistication. As the capability of the technology increased, it became apparent that an entire system (CPU, read-only memory [ROM], random-access memory [RAM], and I/O) could be combined on a single chip. The first devices of this type, available about mid-1975, were revisions of existing calculator chips. Instruction sets had a strong orientation toward binary coded decimal (BCD) arithmetic with little emphasis on program control and I/O capability. The I/O structures of these devices were slanted toward keyboard input and light-emitting diode (LED) output. We are beginning to see newer systems with strong emphasis on increased processor capability but with still fairly simple I/O structures. The trends in commercial, single-chip systems are toward increased processor capability (more efficient instruction sets, higher speed, etc.) and larger program and/ or data memory, but I/O architecture continues to be neglected despite the significance of I/O in system implementation. The importance of I/O in single-chip systems additional devices will significantly impact system cost.

The solution to the I/O probem is not an obvious one. While systems may have commonality in the controller implementation of the system (CPU, ROM, RAM), the I/O interfaces normally differ from system to system. The customization that has been obtained through programmability for controller logic has not been achieved for I/O interfaces.

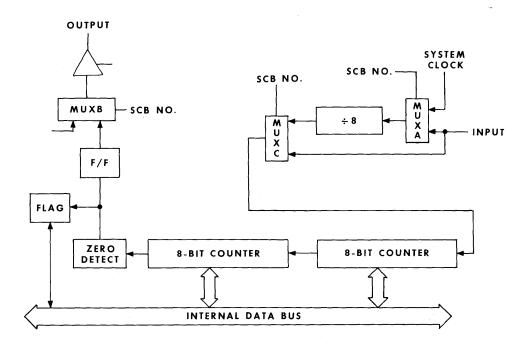

# MAC-4

The MAC-4 is a single-chip microprocessor device and is designed to extend the design commonality of the microprocessor beyond controller architecture and into the I/O structure of a system. The I/O structure of the MAC-4 provides a wide range of flexibility and programmability which has not previously been achieved. This capability is coupled with a powerful CPU and an instruction set which is optimized for memory efficiency in control-intensive applications. (In the preliminary description of the MAC-4 device and architecture which follows, the target specifications which were available when this paper was written are discussed. The paper is based upon work done by the Low End Microprocessor Study Group.<sup>2</sup>)

## CHARACTERISTICS

The MAC-4 architecture is structured around a 4-bit internal bus and 4-bit memories. However, data operands may be any widths which are multiples of 4-bit nibbles. Arithmetic and logic operations are performed in nibble-serial fashion within the processor. The operand length is determined by an internal register which is set by the user program.

The MAC-4 instruction set is optimized for I/O- and control-intensive applications. Particular attention has been given to memory efficiency since memory space is an especially critical parameter in single-chip systems. Memory efficiency is enhanced by various memory address modes, including several memory-to-memory operations. The standard device has a 2K by 4 program memory and a 64 by 4 data memory, excluding internal registers. The total available address space is 4K by 4 bits.

The MAC-4 will be fabricated in Si gate, Al metal, complementary metal oxide semiconductor (CMOS) technology. Target characteristics for the device include a required supply voltage of 3 to 10V; an operating power of approximately 6 mW to permit line powering of the device; a standby current (for retention of RAM data) of 50 nA at 2V; and a clock rate of 2 MHz at 10V operation and 400 kHz at 3.5V operation. The standard MAC-4 device will be packaged in a 40-pin dual in-line package (DIP).

## I/O ARCHITECTURE

The I/O architecture of the MAC-4 is designed to permit a wide range of flexibility and to minimize package count in many types of applications. Features within the I/O subsystem make possible data rates in the megabit range and allow responses to input stimuli to occur in less than a microsecond. The capability of the MAC-4 I/O subsystem impacts significantly on applications which previously would have required either discrete logic or custom LSI.

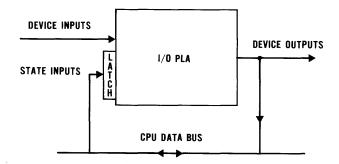

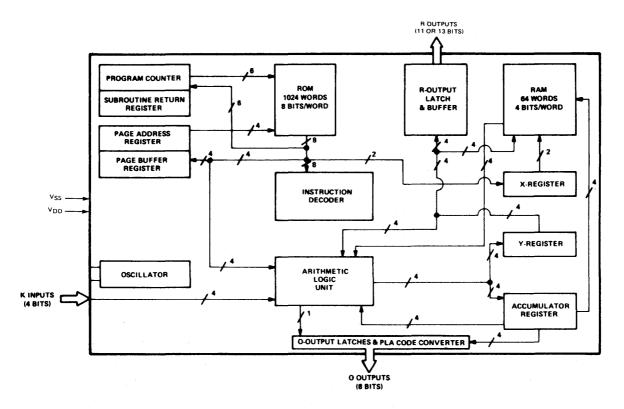

One of the most innovative features of the MAC-4 is a programmable logic array (PLA) (see Figure 6-1). In this configuration the state of the PLA is determined by the user program and is a part of the PLA inputs. The other inputs are clocked directly from device input pins. PLA outputs are latched every clock cycle, thereby achieving submicrosecond response times to input signals. The contents of the

Figure 6-1 - MAC-4 I/O PLA Structure

PLA are programmed when the device is fabricated in the same mask step that determines the contents of the system ROM.

Since a PLA may be used to implement specific logic functions (the CPU controller logic is implemented with a PLA), a user may program custom combinatorial logic for a specific I/O function. This feature may then be coupled with the state input provided by the CPU to achieve complex sequential logic functions tailored to a specific application under program control.

A direct-memory access (DMA) capability is also provided in the I/O subsystem. The ability to perform DMA operations allows the MAC-4 to send and receive bursts of data at megabit rates with no external hardware. The interrupt feature on the MAC-4 is implemented using the system DMA capability.

I/O transfers may also be made under program control. These transfers can be accomplished in either of two ways: special bit manipulation instructions provide I/O capability at the bit level, or data may be moved in parallel using standard data transfer instructions.

## APPLICATIONS: SHORTCUT TO CUSTOM LSI

It is anticipated that in most applications the standard MAC-4 device will be used. Those in which high-volume production is expected will also use the standard device for prototyping, field trial, and initial production. However, the MAC-4 has been designed so that it may be optimized for cost-sensitive products with highproduction volumes, a course which may be followed with relatively small, additional development effort.

Since approximately one-half of the standard chip is occupied by program and data memory, reduction of memory for simpler applications is an excellent area for possible cost reduction. Other areas include changes in I/O circuitry, the use of smaller packages when changes in the I/O make this appropriate, and even optimization of the CPU instruction set. These cost reduction techniques, coupled with the flexible system architecture of the MAC-4, compare favorably with device costs achievable with custom LSI. However, the problems of extensive chip development and changing system requirements, associated with the latter, have been dispensed with.

### SUMMARY

As LSI technology continues to evolve, complete microprocessor systems are becoming single chips. The tailoring of a catalog LSI device by means of software, rather than hardware, offers a number of substantial advantages. The MAC-4 is a single-chip microprocessor system which provides an extremely sophisticated, flexible I/O structure not previously available. This structure is combined with a powerful CPU which has been optimized for memory efficiency and is especially well-suited for I/O- and control-intensive applications. The introduction of this and similar devices into Bell Laboratories will allow designers to take full advantage of the rapidly advancing LSI technology.

### REFERENCES

- 1. Gordon E. Moore, "Progress in Digital Integrated Electronics," Proceedings of ELECTRO 76, Boston, Massachusetts, May 11, 1976.

- Final Report of the Low End Microprocessor Study Group (D. E. Blahut, I. A. Cermak, W. F. Chow, J. A. Copeland, D. H. Copp, J. I. Frederick, R. C. Hansen, V. K. L. Haung, C. A. Merk, J. R. McEowen, D. R. Morgan, P. O. Schuh, D. C. Stanzione, and L. C. Thomas), Bell Telephone Laboratories, Holmdel, New Jersey, May 28, 1976.

## SUPPORT FACILITIES

## THE PROGRAMMING LANGUAGES OF MAC-8

H. D. Rovegno and D. B. Kirby, BTL Dept 4393, HO, NJ

#### ABSTRACT