## CUSTOMER ENGINEERING DIVISION

## MODEL 928 SYSTEMS 10/20/30

## FIELD-LEVEL MAINTENANCE MANUAL

## PRELIMINARY VOLUME 3 THEORY OF OPERATION

© Wang Laboratories, Inc., 1978

#### NOTICE:

This document is the property of Wang Laboratories, Inc., Information contained herein is considered company proprietary information and its use is restricted solely to the purpose of assisting you in servicing Wang products. Reproduction of all or any part of this document is prohibited without the consent of Wang Laboratories.

WANG

LABORATORIES, INC.

ONE INDUSTRIAL AVENUE, LOWELL, MASSACHUSETTS 01851, TEL (617) 851-4111, TWX 710 343-6769, TELEX 94-7421

#### TABLE OF CONTENTS

SECTION 1 INTRODUCTION

| 1.1 | SCOPE                | 1-1      |

|-----|----------------------|----------|

| 1.2 | PURPOSE              | 1-2      |

| 1.3 | DESCRIPTION          | 1-2      |

| 1.4 | BLOCK DIAGRAMS       | 1-2      |

| 1.5 | TIMING DIAGRAMS      | · 1-4    |

| 1.6 | SCHEMATICS           | 1-4      |

| 1.7 | APPENDICES           | 1-5      |

| 1.8 | "BARRED"/LOW SIGNALS | 1-5      |

|     |                      | ,<br>1-0 |

SECTION 2 MASTER THEORY OF OPERATION

| 2.1 | MASTER | MEMORY (7201)                             | 2-1  |

|-----|--------|-------------------------------------------|------|

|     | 2.1.1  | GENERAL DESCRIPTION                       | 2-1  |

|     |        | 8080 ADDRESS BUS - PROM                   | 2-1  |

|     |        | 8080A ADDRESS BUS - RAM                   | 2-3  |

|     |        | 8080/DMA ADDRESS MULTIPLEXER              | 2-3  |

|     |        | PRIORITY FUNCTION DECODER                 | 2-4  |

|     |        | DMA ADDRESS BUS                           | 2-6  |

|     | 2.1.7  | ROW REFRESH CIRCUIT                       | 2-7  |

|     |        | FIFO CONTROL                              | 2-7  |

|     |        | 2.1.8.1 FIFO CONTROL - 256 BYTE WRITE     | 2-7  |

|     |        | 2.1.8.2 FIFO CONTROL - 256 BYTE READ      |      |

|     | 2.1.9  | MASTER MEMORY DATA BUSSES                 | 2-11 |

| 2.2 | MASTER | CENTRAL PROCESSING UNIT (CPU) (7202)      | 2-14 |

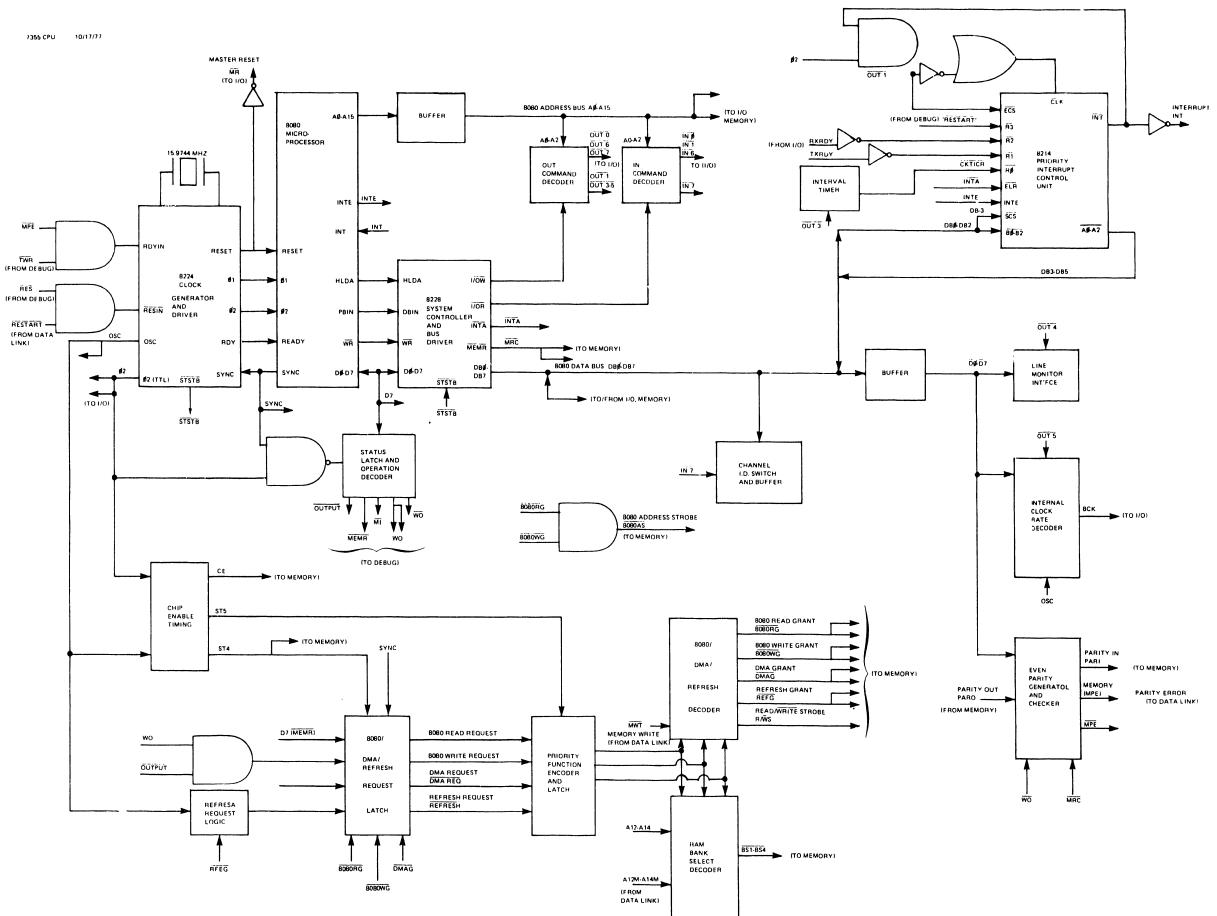

|     | 2.2.1  | GENERAL DESCRIPTION 8080A MICROPROCESSOR  | 2-14 |

|     | 2.2.2  | SYSTEM (MASTER CLOCK) TIMING              | 2-14 |

|     | 2.2.3  | STATUS REGISTER                           | 2-18 |

|     | 2.2.4  | IN/OUT COMMAND DECODERS                   | 2-19 |

|     | 2.2.5  | TRI-STATE DATA BUFFER                     | 2-22 |

|     | 2.2.6  | PROGRAM LEVEL SWITCHES                    | 2-22 |

|     | 2.2.7  | CHANNEL SELECT                            | 2-23 |

|     | 2.2.8  | PRIORITY INTERRUPT DECODER                | 2-23 |

|     | 2.2.9  | TCCLK-(10 MS TIMER-CLOCK TICK)            | 2-24 |

|     | 2.2.10 | REFRESH TIMING-(C4 CLOCK)                 | 2-25 |

|     | 2.2.11 | DMA, 1-BYTE, 256-BYTES CONTROL LOGIC      | 2-25 |

|     |        | 2.2.11.1 STATUS                           | 2-26 |

|     |        | 2.2.11.2 RESTART                          | 2-27 |

|     |        | 2.2.11.3 1-BYTE READ                      | 2-27 |

|     |        | 2.2.11.4 1-BYTE WRITE                     | 2-28 |

|     |        | 2.2.11.5 256-BYTE READ                    | 2-28 |

|     |        | 2.2.11.6 256-BYTE WRITE                   | 2-29 |

|     | 2.2.12 | DMA ADDRESS BUS AND PAGE ADDRESS COUNTER  | 2-29 |

|     | 2.2.13 | PARITY GENERATOR AND PARITY CHECK CIRCUIT | 2-29 |

|     | 2.2.14 | RESET AND READY/BUSY                                               | 2-30 |

|-----|--------|--------------------------------------------------------------------|------|

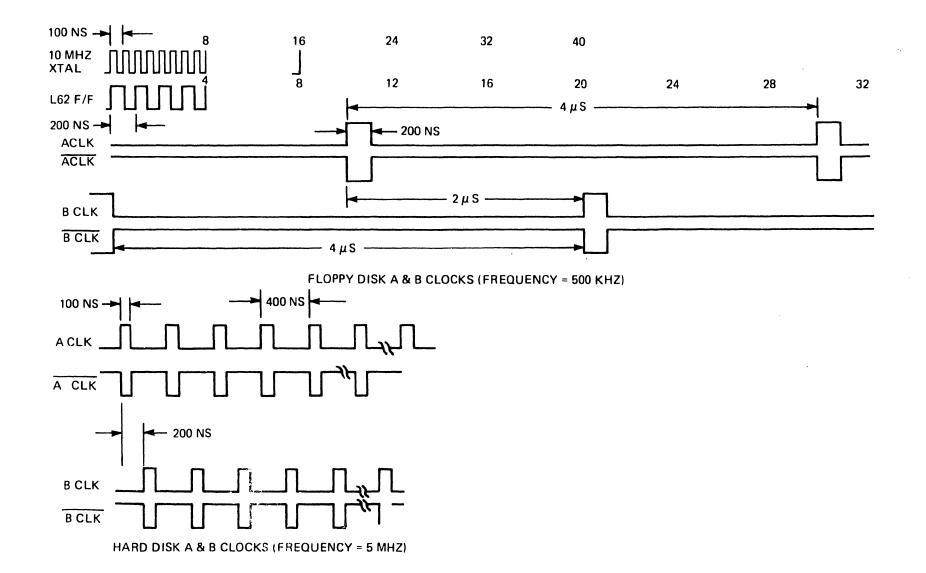

|     | 2.2.15 | A & B CLOCK GENERATOR FOR DISK<br>2.2.15.1 A & B CLOCKS FOR FLOPPY | 2-31 |

|     |        | 2.2.15.1 A & B CLOCKS FOR FLOPPY                                   | 2-31 |

|     |        | 2.2.15.2 A & B CLOCKS FOR THE HARD DISK                            |      |

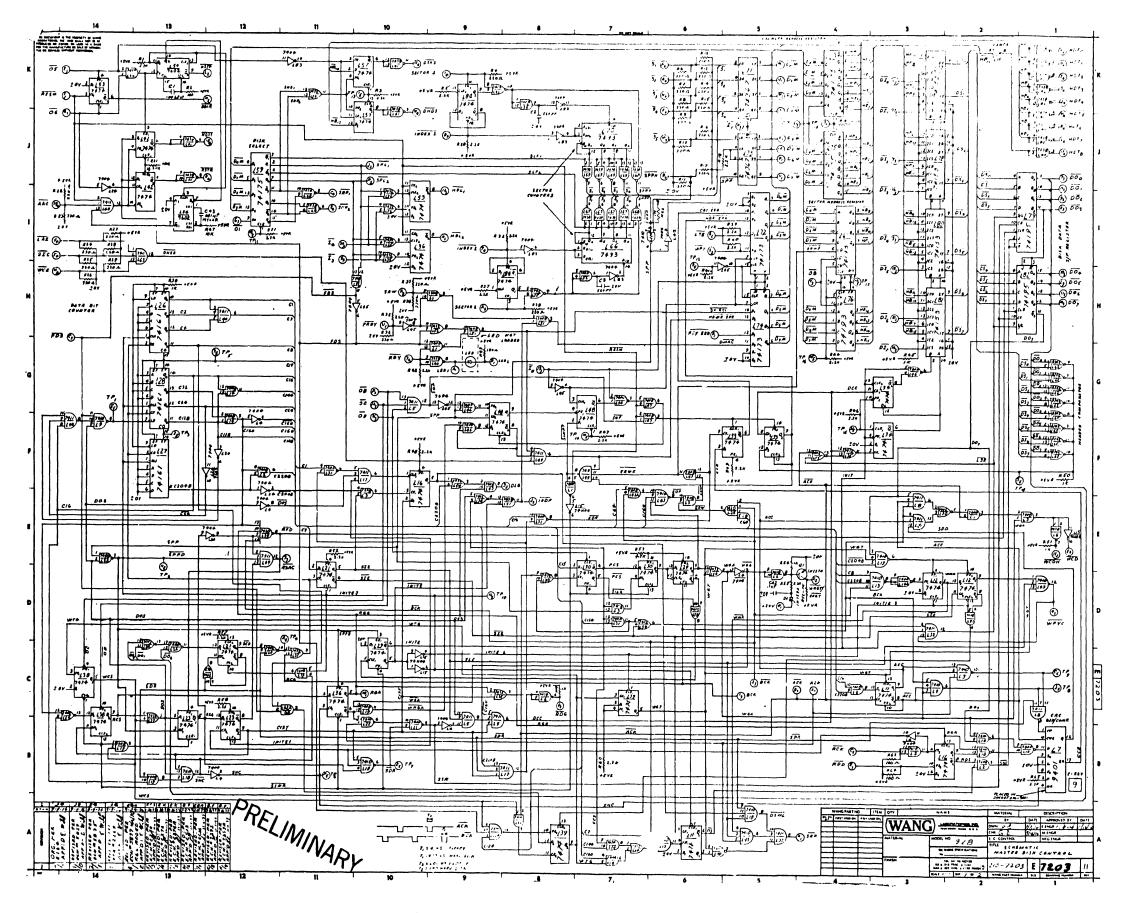

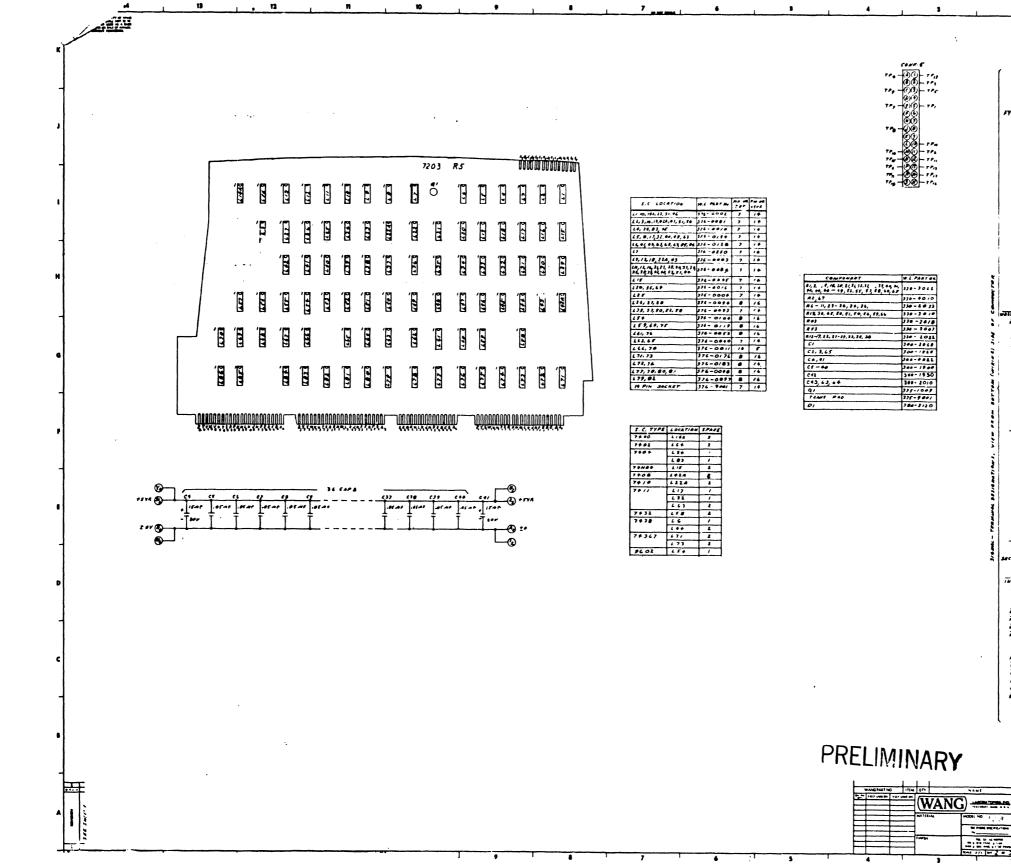

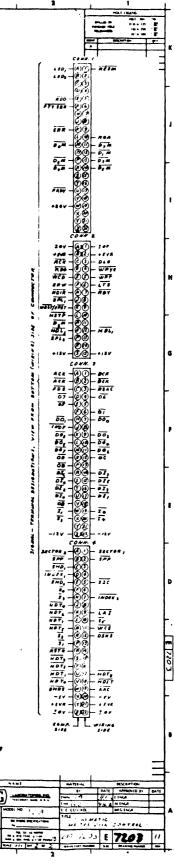

| 2.3 | MASTER | DISK CONTROLLER (7203)                                             | 2-36 |

|     | 2.3.1  | GENERAL DESCRIPTION                                                | 2-36 |

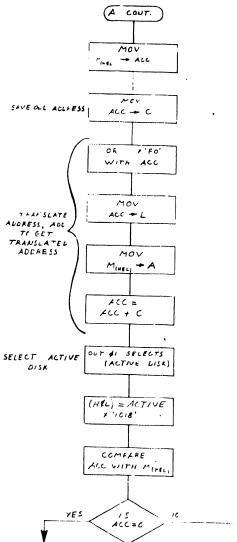

|     | 2.3.2  | DISK SELECT                                                        | 2-41 |

|     |        | 2.3.2.1 FLOPPY                                                     | 2-41 |

|     |        | 2.3.2.2 FIXED/REMOVABLE (HARD)                                     | 2-43 |

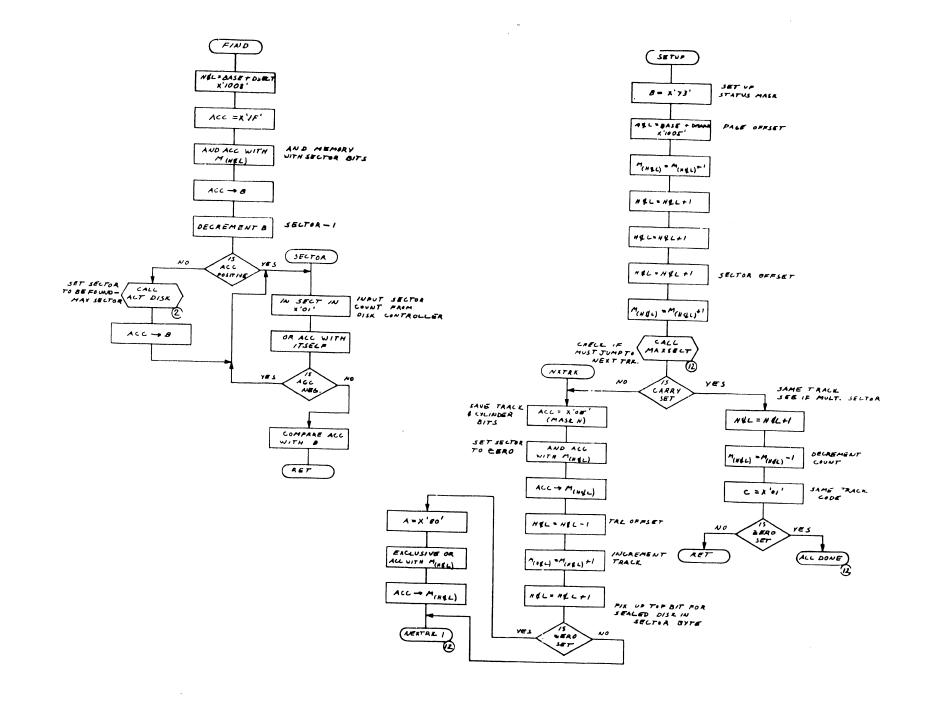

|     | 2.3.3  | SECTOR ADDRESS - HARD                                              | 2-45 |

|     | 2.3.4  | INPUT STATUS                                                       | 2-45 |

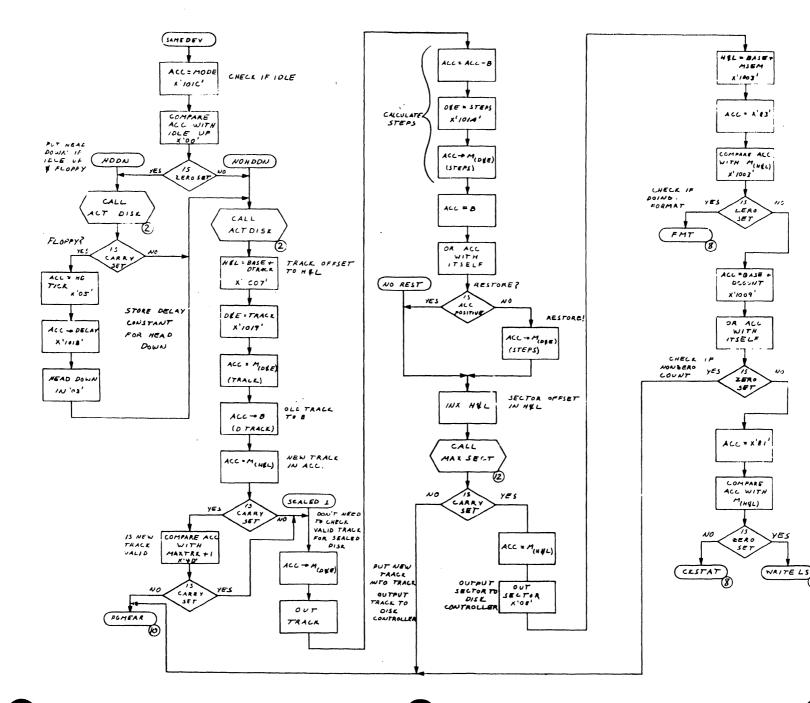

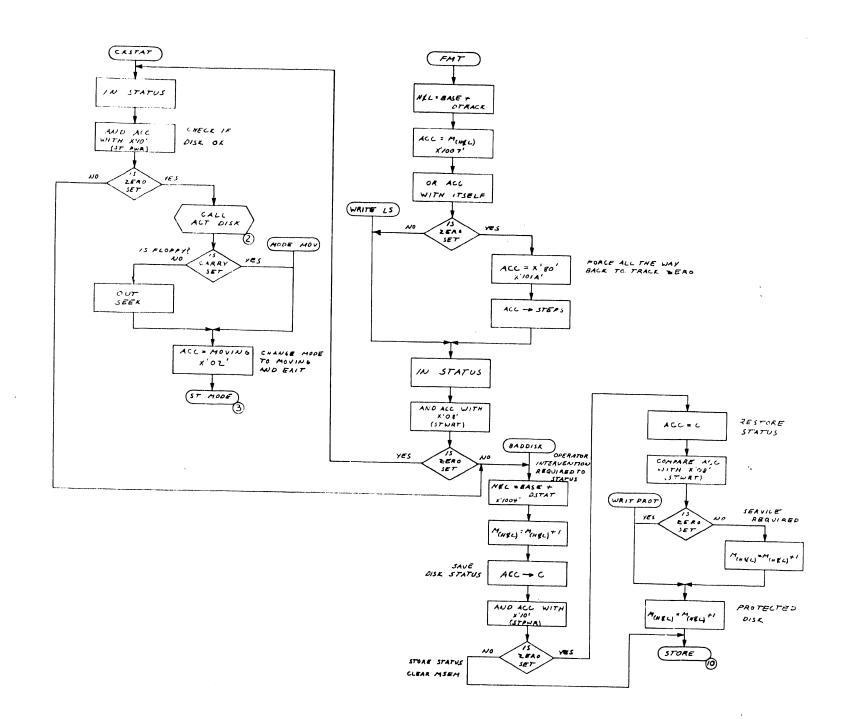

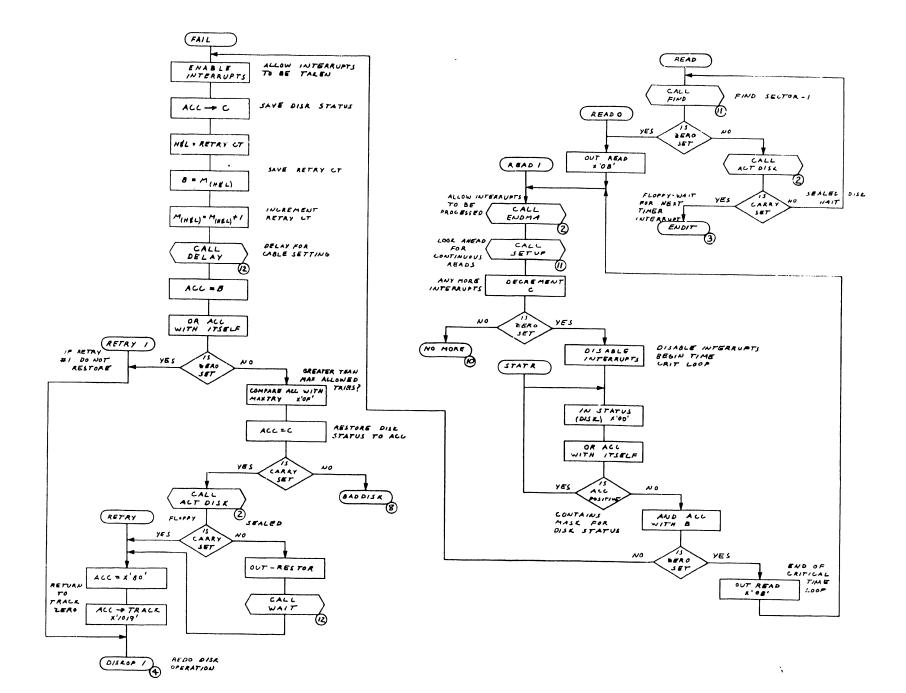

|     | 2.3.5  | READ OPERATION - FOR FLOPPY AND HARD DISKS                         | 2-46 |

|     |        | 2.3.5.1 OUT B - READ OPERATION                                     | 2-47 |

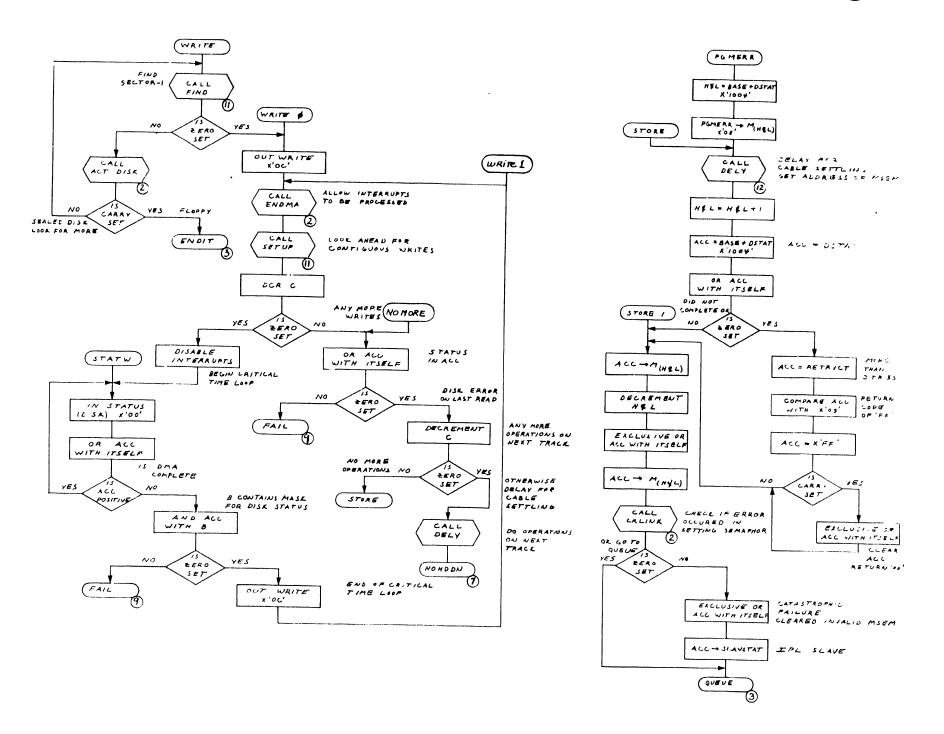

|     | 2.3.6  | WRITE OPERATION - FLOPPY AND HARD DISKS                            | 2-54 |

|     |        | 2.3.6.1 GENERAL INFORMATION                                        | 2-54 |

|     |        | 2.3.6.2 DECISION TO WRITE - START OF GAP                           | 2-54 |

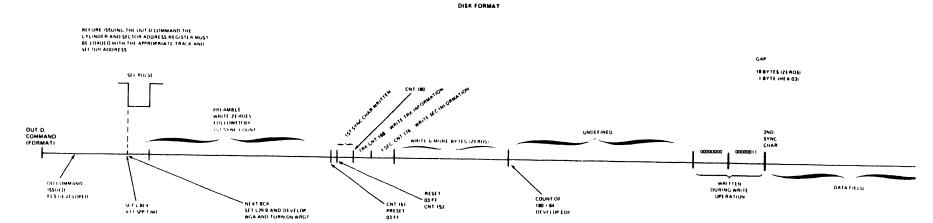

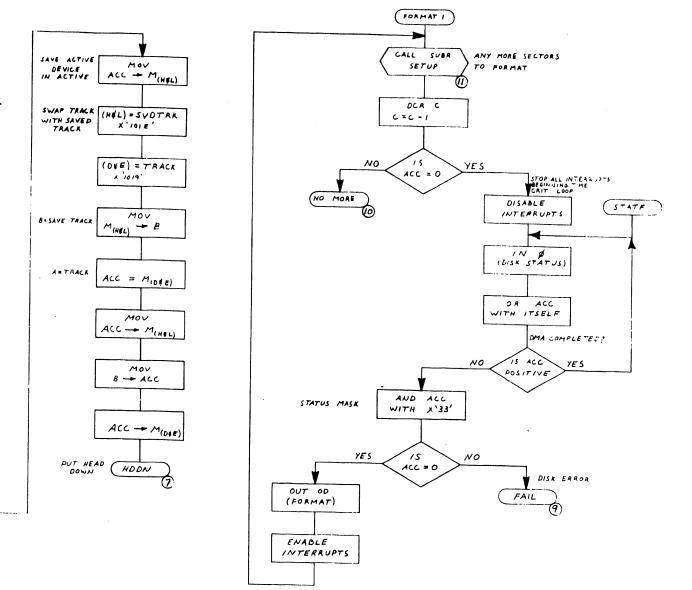

|     | 2.3.7  | FORMAT - FLOPPY/HARD                                               | 2-60 |

|     |        | 2.3.7.1 GENERAL INFORMATION                                        | 2-60 |

|     |        | 2.3.7.2 OUT OD - FORMAT COMMAND                                    | 2-62 |

| 2.4 | MASTER | MOTHERBOARD (7205)                                                 | 2-66 |

| 2.5 | MASTER | POWER SUPPLY/REGULATOR (7206)                                      | 2-68 |

| 2.6 | MASTER | DATA LINK - 7214                                                   | 2-70 |

|     | 2.6.1  | GENERAL DESCRIPTION                                                | 2-70 |

|     | 2.6.2  | DMA CONTROL                                                        | 2-70 |

|     |        | 2.6.2.1 IN STATUS (INST)                                           | 2-70 |

|     | 2.6.3  | 256 BYTE WRITE - MASTER DATA LINK                                  | 2-77 |

|     | 2.6.4  | 256 BYTE READ - MASTER DATA LINK                                   | 2-82 |

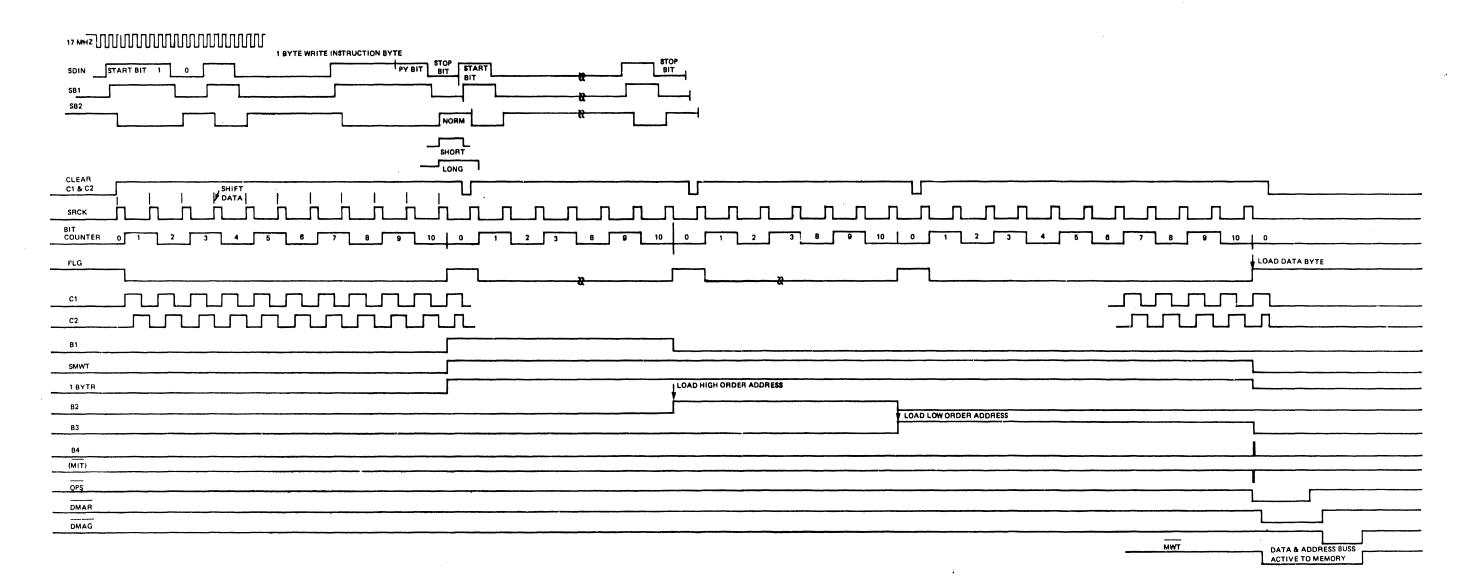

|     | 2.6.5  | 1 BYTE WRITE - MASTER CPU TO SLAVE MEMORY                          | 2-86 |

|     | 2.6.6  | 1 BYTE READ - SLAVE MEMORY TO MASTER CPU                           | 2-88 |

|     | 2.6.7  | RESTART - MASTER DATE LINK                                         | 2-89 |

|     |        |                                                                    |      |

SECTION 3 WORKSTATION THEORY OF OPERATION

| 3.1 | WANG MO | TOROLA MONITOR - REGULATOR (7067)              | 3-1  |

|-----|---------|------------------------------------------------|------|

|     | 3.1.1   | GENERAL DESCRIPTION                            | 3-1  |

| 3.2 | CRT CON | TROL (7225) - WITH WIDE PLATEN OPTION (7235)   | 3-3  |

|     | 3.2.1   | GENERAL DESCRIPTION                            | 3-3  |

|     | 3.2.2   | 8080 WORKSTATION PROCESSOR                     | 3-3  |

|     | 3.2.3   | CRT CONTROL - 7225                             | 3-3  |

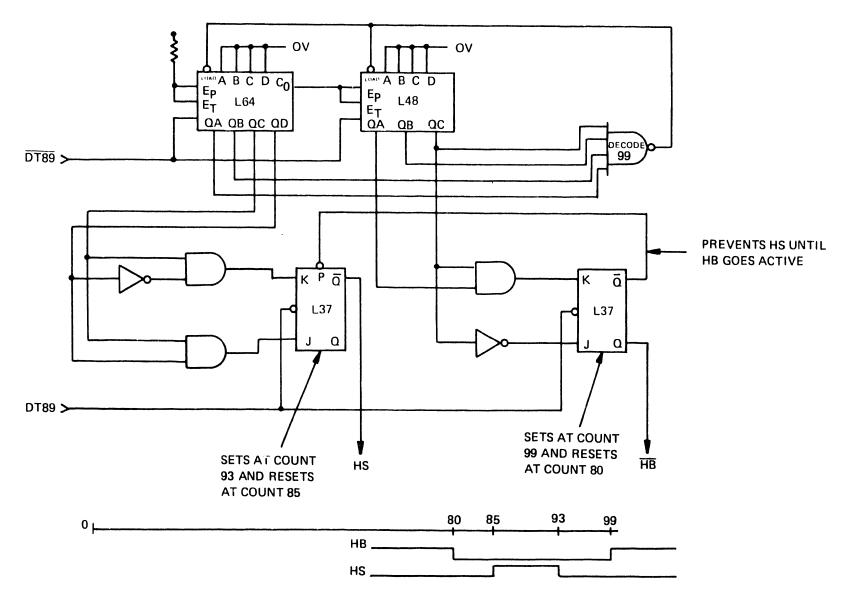

|     |         | CHARACTER COUNTER (HORIZONTAL COUNTER) - 60 HZ | 3-6  |

|     | 3.2.5   | ROW AND LINE COUNTERS - 60 HZ                  | 3-8  |

|     | 3.2.6   | CRT MEMORY ADDRESSING                          | 3-10 |

|     |         | 3.2.6.1 8080 WRITE CRT                         | 3-10 |

|     |         | 3.2.6.2 8080 READ CRT MEMORY                   | 3-12 |

|     |         | 3.2.6.3 CRT MEMORY READ FOR DISPLAY            | 3-12 |

|     | 3.2.7   | CHARACTER VIDEO AND CRT CONTROL BITS           | 3-13 |

|     |         | 3.2.7.1 CHARACTER VIDIO BITS                   | 3-15 |

|     |         | 3.2.7.2. UNDERLINE CONTROL BIT                 | 3-15 |

|     |         | 3.2.7.3. INTENSITY CONTROL BIT                 | 3-16 |

|     | 3.2.8   | KEYBOARD CONTROL LOGIC                         | 3-16 |

|     |         | OUT COMMANDS                                   | 3-18 |

|     | 3.2.10  |                                                | 3-18 |

|     |         |                                                | 7-10 |

|     | 3.2.11   | PARITY CHECKER AND GENERATOR                     | 3-20 |

|-----|----------|--------------------------------------------------|------|

|     | 3.2.12   | POWER UP F/F                                     | 3-20 |

|     | 3.2.13   | CRT CONTROL BOARD - 7235 WITH WIDE PLATEN OPTION | 3-20 |

|     | 3.2.14   | HORIZONTAL SCROLL                                |      |

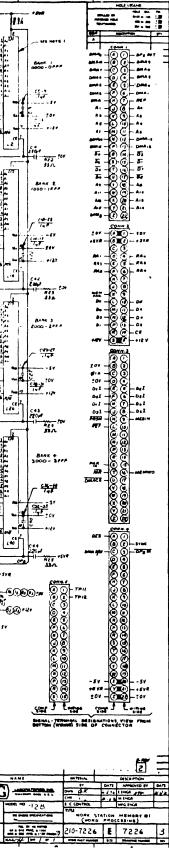

| 3.3 |          | ATION MEMORY $#1 - 7226$                         | 3-21 |

|     | 3.3.1    |                                                  | 3-27 |

|     |          | GENERAL DESCRIPTION                              | 3-27 |

|     |          |                                                  | 3-27 |

|     |          | MEMORY - 8080 READ                               | 3-29 |

|     | 3.3.4    | MEMORY - DMA WRITE                               | 3-30 |

|     |          | MEMORY - DMA READ                                |      |

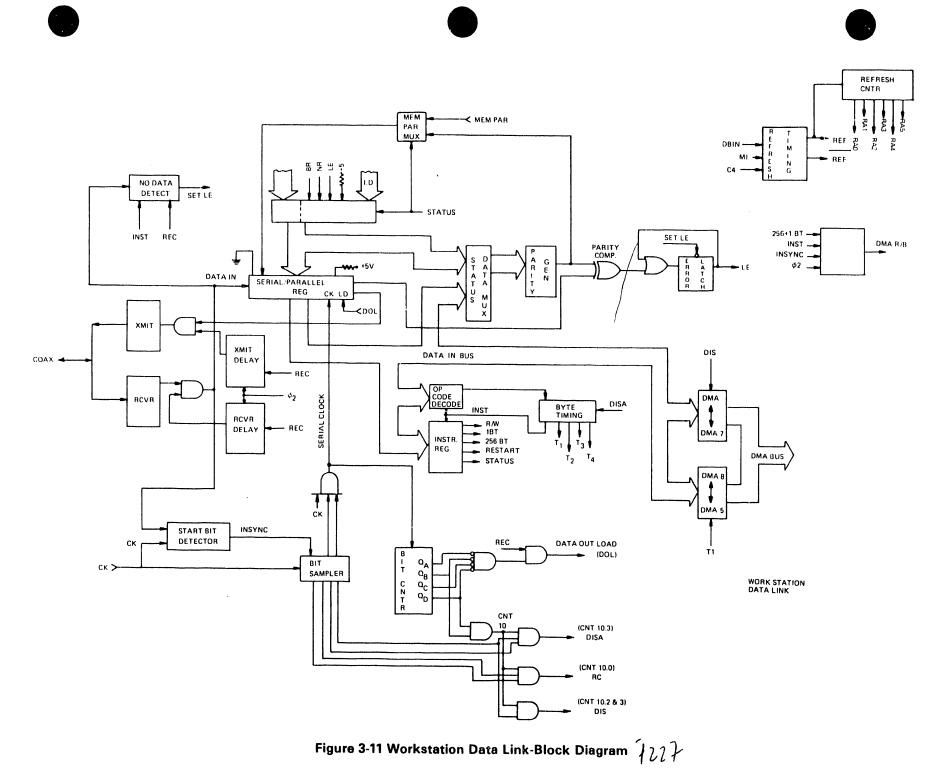

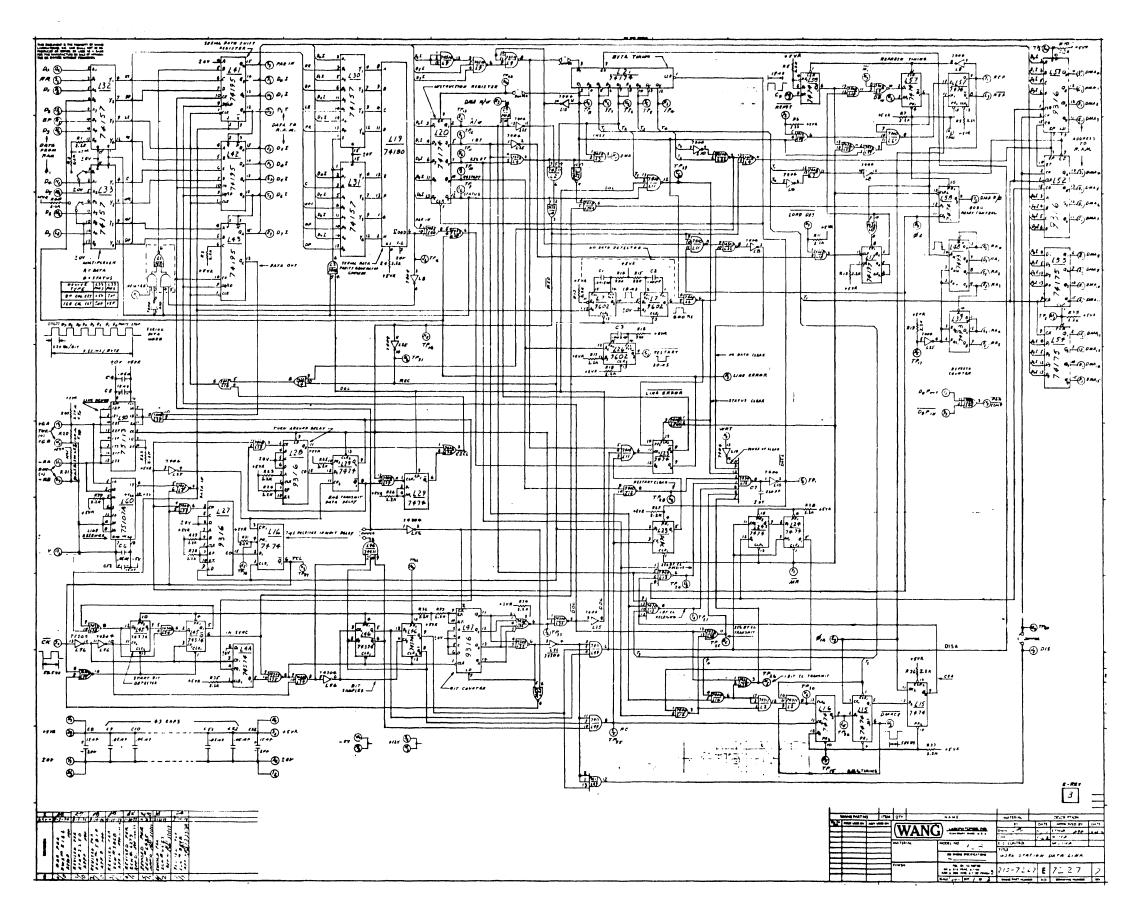

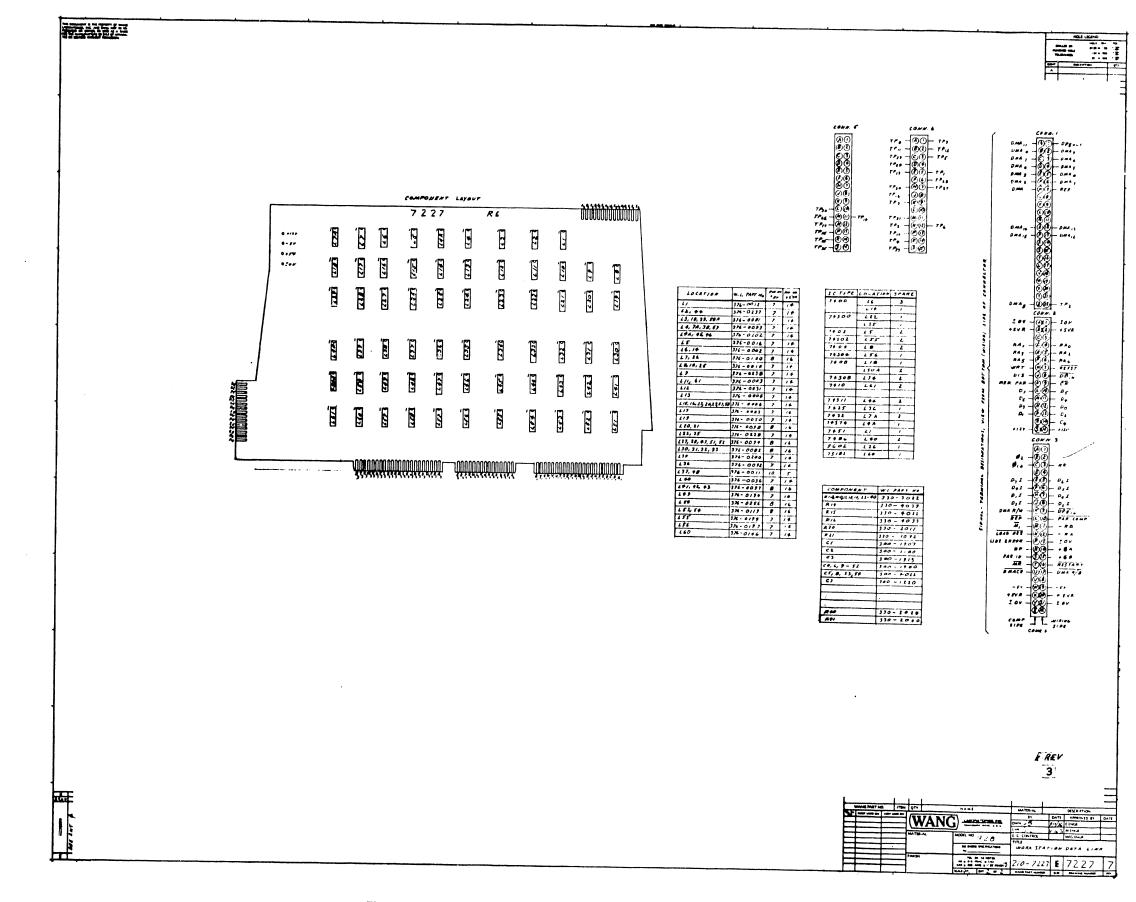

| 3.4 |          | FION DATA LINK - 7227                            | 3-31 |

|     | 3.4.1    |                                                  | 3-34 |

|     |          | GENERAL DESCRIPTION                              | 3-34 |

|     |          | HEADER BYTE                                      | 3-34 |

|     | 3.4.3    | HEADER/INSTRUCTION BYTE AND START BIT DETECTOR   | 3-38 |

|     | 3.4.4    | STATUS                                           | 3-39 |

|     | 3.4.5    | RESTART                                          | 3-41 |

|     |          | 256 BYTE WRITE                                   |      |

|     | 3.4.7    | 256 BYTE READ                                    | 3-42 |

|     |          |                                                  | 3-43 |

|     |          | WORKSTATION - 1-BYTE WRITE                       | 3-44 |

|     | 3.4.9    | WORKSTATION - 1-BYTE READ                        | 3-46 |

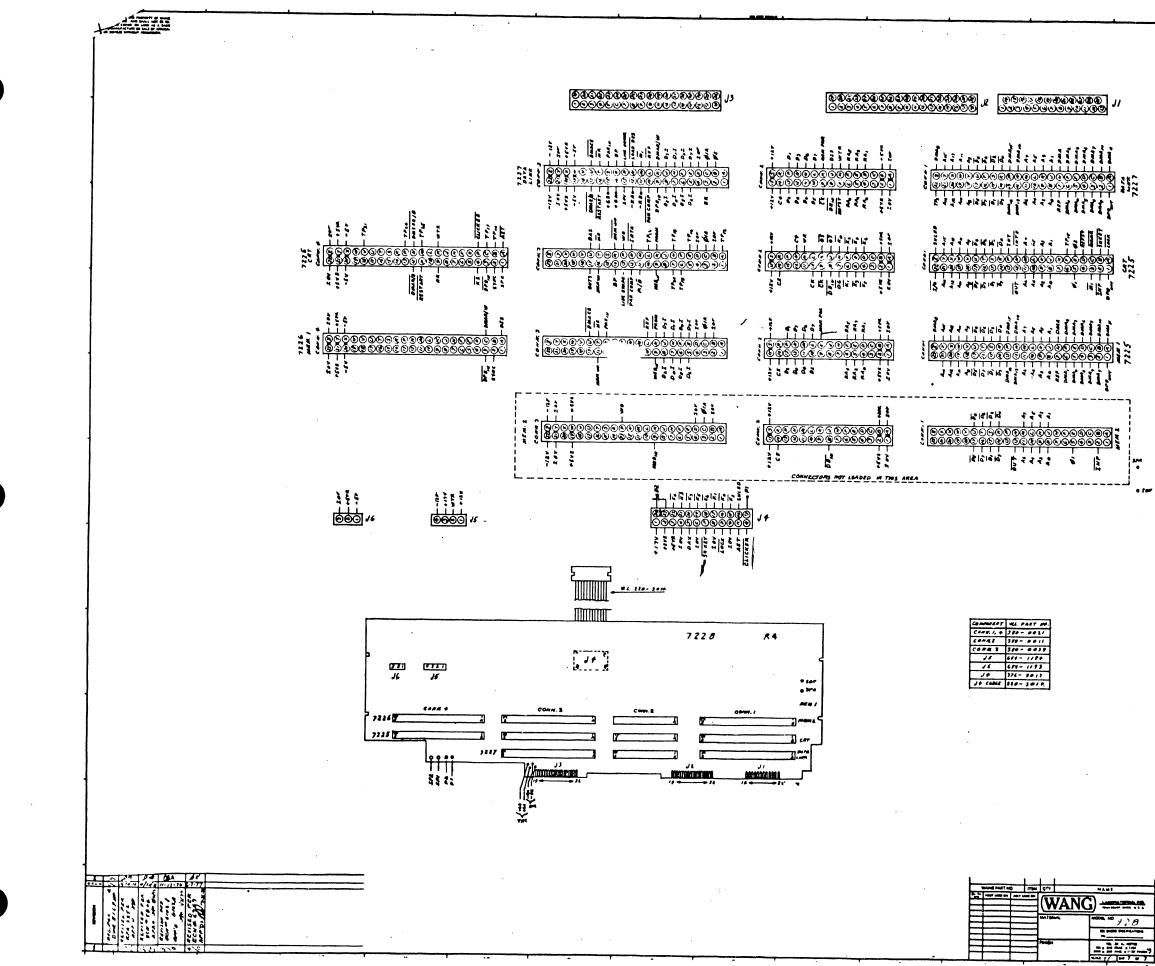

| 3.5 | MOTHERBO | DARD (7228)                                      | 3-50 |

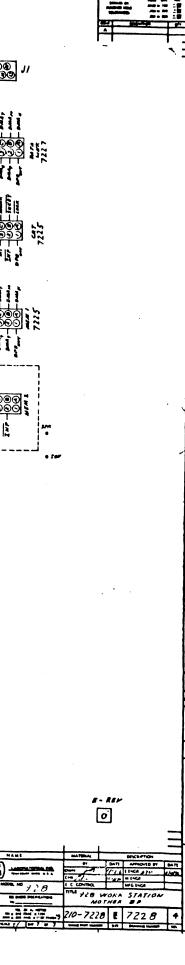

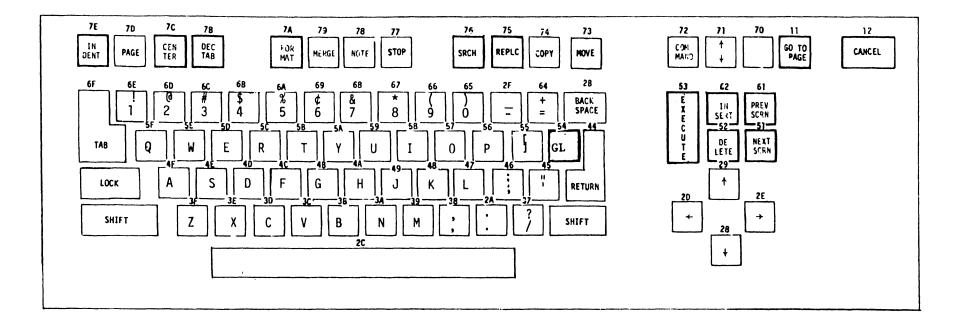

| 3.6 | KEYBOARI | ) (7229)                                         | 3-52 |

|     |          |                                                  | 3-32 |

SECTION 4 PRINTER THEORY OF OPERATION

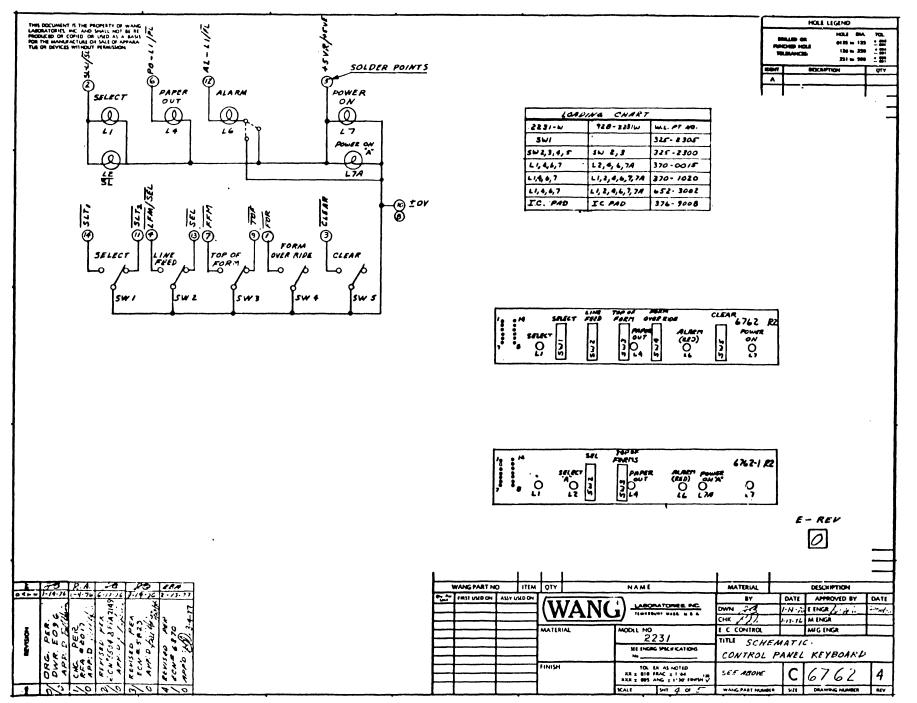

| 4.1 | FRONT CONTROL PANEL (6762-1)                         | 4-1  |

|-----|------------------------------------------------------|------|

| 4.2 |                                                      | 4-3  |

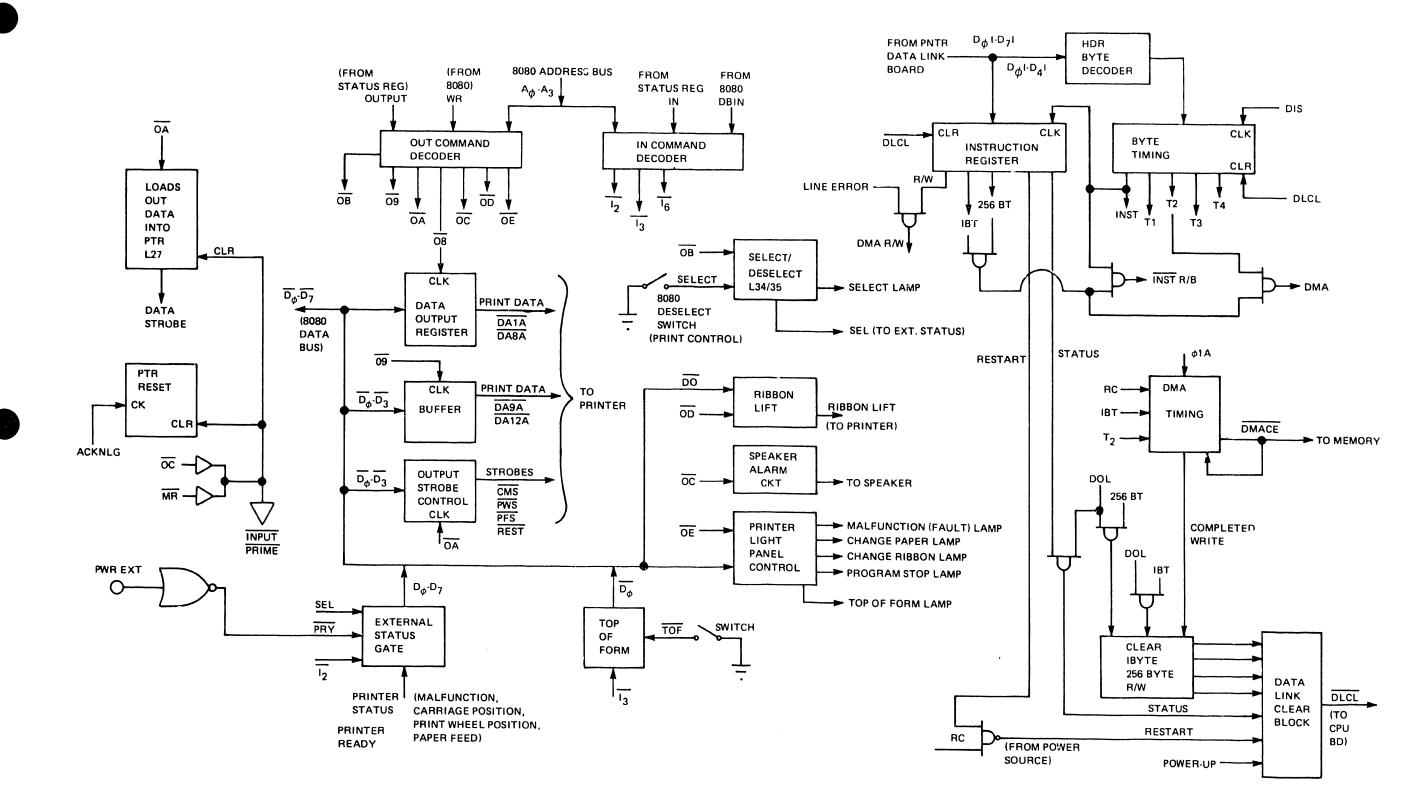

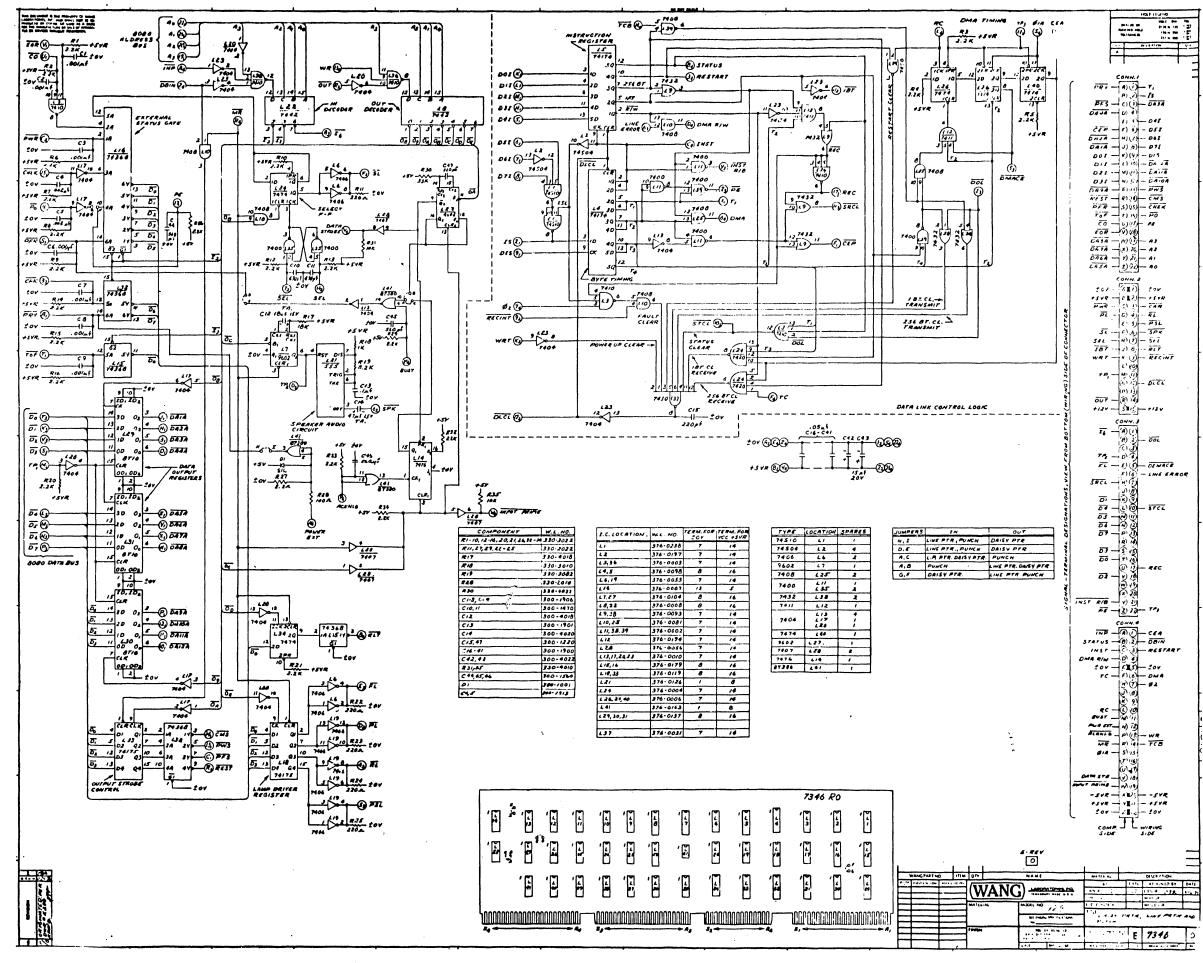

| 4.3 | I/O BOARD FOR 928 MATRIX & DAISY PRINTERS & PIO-7346 | 4-5  |

|     | 4.3.1 GENERAL DESCRIPTION                            |      |

|     | 4.3.2 PRINTER PROCESSOR IN/OUT COMMANDS              | 4-5  |

|     | 4.3.2 INTRIER FROCESSOR IN/OUT COMMANDS              | 4-5  |

|     | 4.3.3 DAISY PRINTER CONTROL                          | 4-5  |

|     | 4.3.4 MATRIX PRINTER CONTROL                         | 4-9  |

|     | 4.3.5 PHOTOCOMPOSITION INPUT OPTION                  | 4-9  |

| 4.4 | PRINTER/PIO MEMORY - 7347                            | 4-11 |

|     | 4.4.1 GENERAL DESCRIPTION                            | 4-11 |

|     | 4.4.2 PRINTER/PIO MEMORY - 8080 WRITE                | 4-11 |

|     | 4.4.3 PRINTER/PIO MEMORY - 8080 READ                 | 4-13 |

|     | 4.4.4 PRINTER/PIO MEMORY - DMA WRITE                 | 4-14 |

|     | 4.4.5 PRINTER/PIO MEMORY - DMA READ                  | 4-15 |

| 4.5 | PRINTER/PIO CPU BOARD - 7348                         | 4-18 |

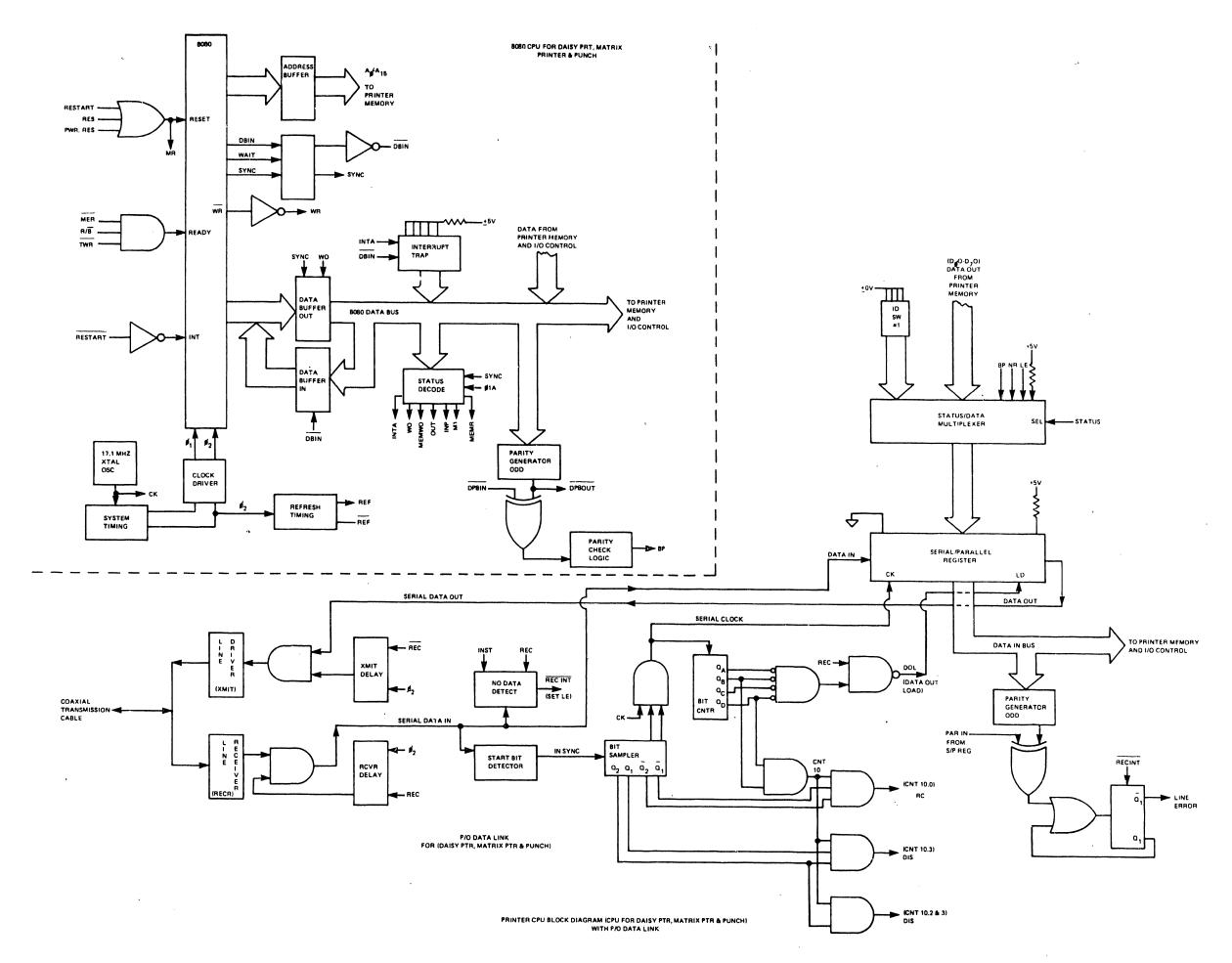

|     | 4.5.1 GENERAL DESCRIPTION                            | 4-18 |

|     | 4.5.2 DMA TRANSFER OPERATIONS - 1-BYTE STATUS        | 4-20 |

|     | 4.5.3 PRINTER RESTART                                | 4-23 |

|     | 4.5.4 PRINTER - 256 BYTE WRITE                       | 4-24 |

|     | 4.5.5 PRINTER – 256 BYTE READ                        | 4-25 |

|     | 4.5.6 PRINTER - 1-BYTE WRITE                         | 4-27 |

|     | 4.5.7 PRINTER - 1-BYTE READ                          | 4-29 |

|     | 4.5.8 PRINTEr - 8080 CPU                             | 4-31 |

SECTION 5 WANG OPTIONS

| INTRODU                               | DUCTION 5-                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LINE PRINTER OPTION (LPO) (5521/5531) |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.2.1                                 | 928 PRINT                                                                                             | ER INTERFACE ASSEMBLY (WL#270-0341)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| РНОТОСО                               | MPOSITION :                                                                                           | INPUT OPTION (PIO)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.3.2                                 | PIO DESCR                                                                                             | IPTION AND CODES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

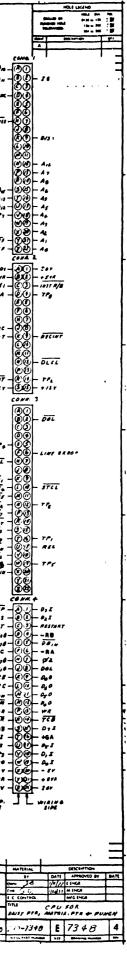

| 5.4.1                                 | GENERAL DI                                                                                            | ESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

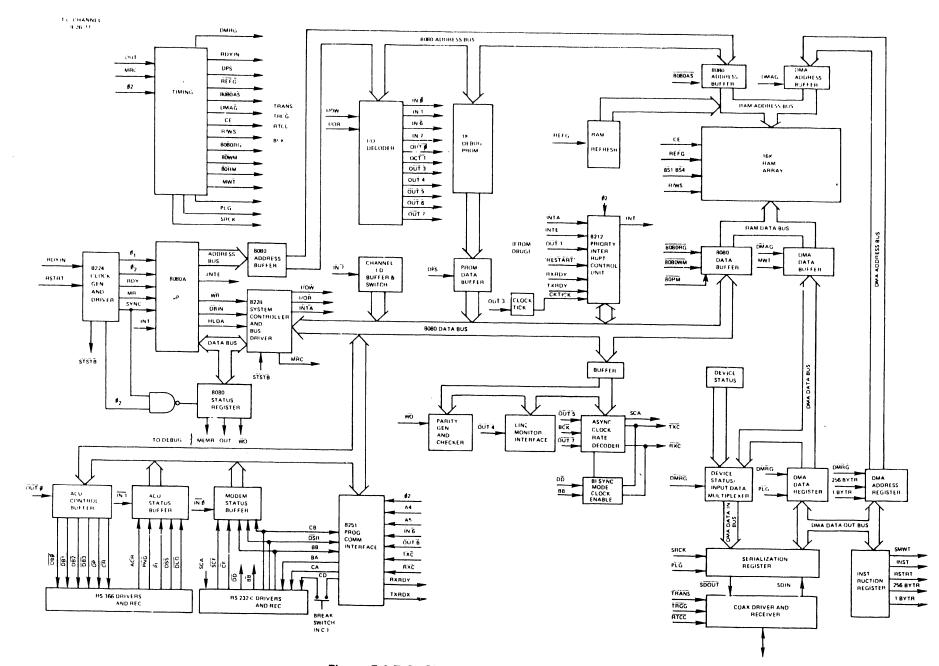

| 5.4.2                                 | INTERNAL                                                                                              | ARCHITECTURE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.4.3                                 | SYSTEM BUS                                                                                            | SES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5.4.4                                 | CPU BOARD                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       | 5.4.4.2                                                                                               | 8080 CONTROL AND TIMING LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                       | 5.4.4.3                                                                                               | OUT COMMAND DECODER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.4.4                                                                                               | IN COMMAND DECODER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.4.5                                                                                               | CHANNEL ID SWITCHES AND BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.4.6                                                                                               | LINE MONITOR INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.4.7                                                                                               | INTERNAL CLOCK RATE DECODER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.4.8                                                                                               | EVEN PARITY GENERATOR AND CHECKER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.4.9                                                                                               | INTERVAL TIMER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.4.10                                                                                              | 8214 PRIORITY INTERRUPT CONTROL UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

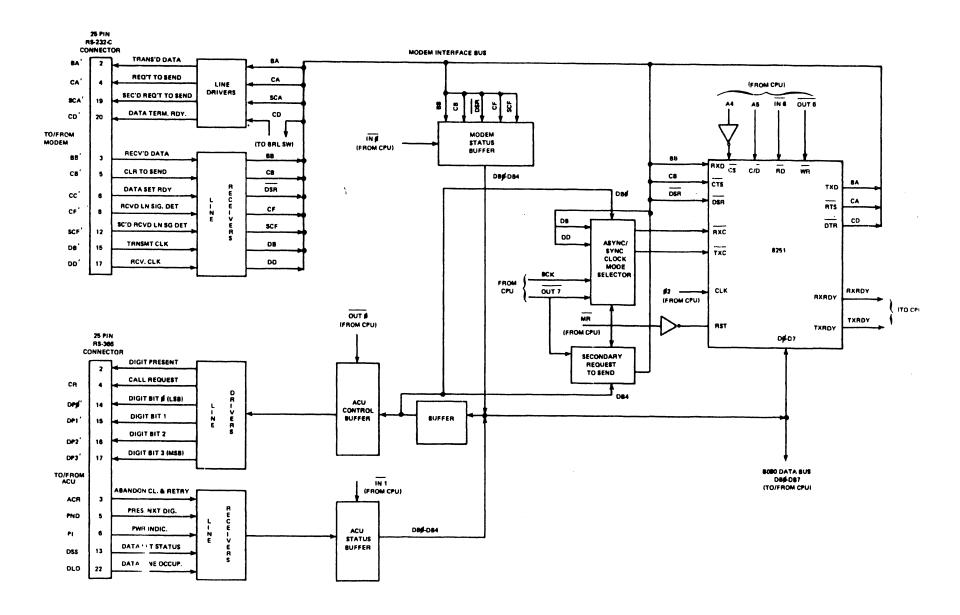

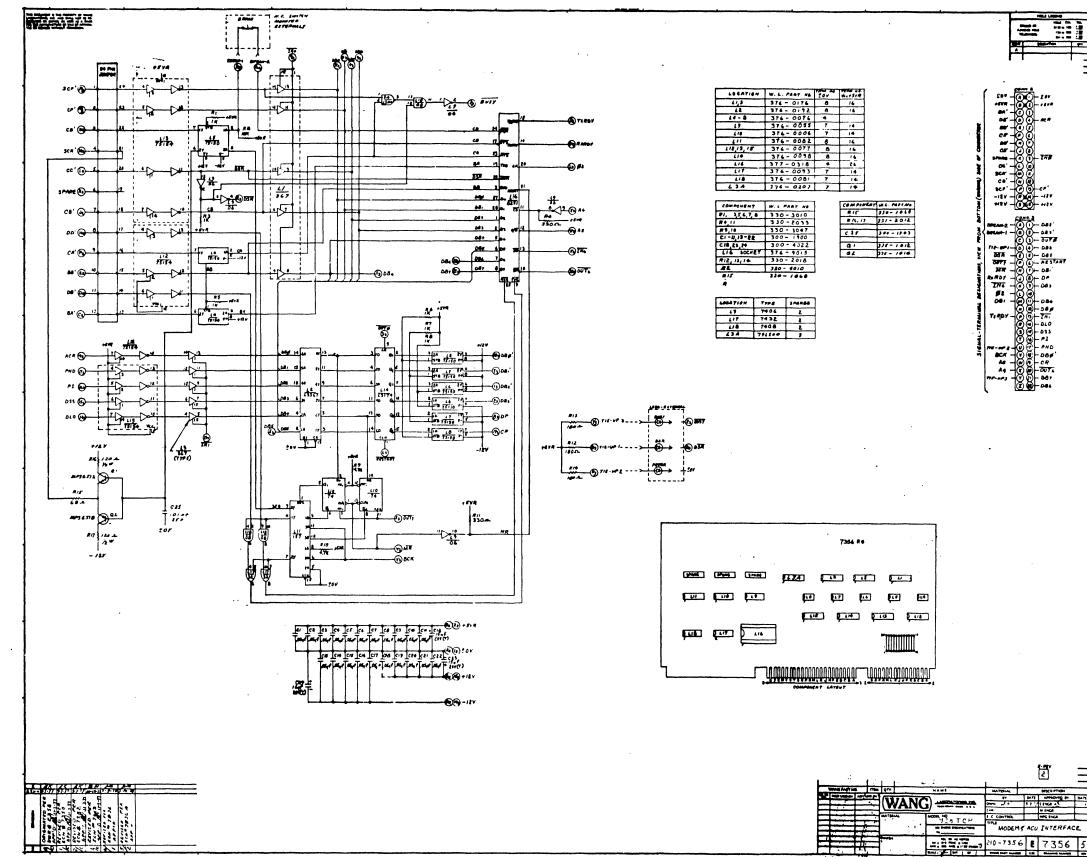

| 5.4.5                                 | MODEM AND                                                                                             | ACU INTERFACE BOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.5.1                                                                                               | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.5.2                                                                                               | 8251 (USART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.5.3                                                                                               | MODEM INTERFACE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.5.4                                                                                               | MODEM STATUS BUFFER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

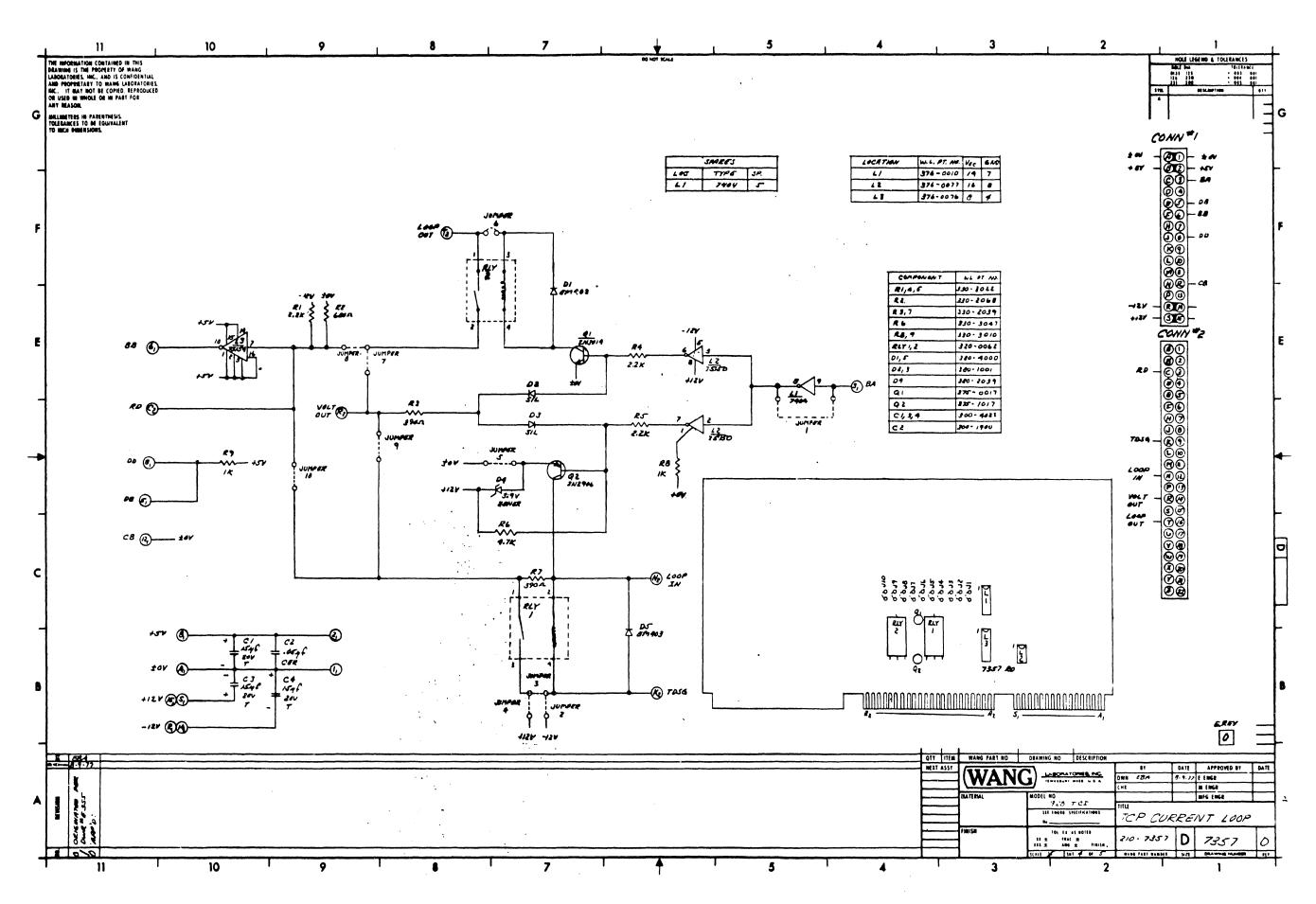

| 5.4.6                                 | MEMORY BOA                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.6.1                                                                                               | GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.6.2                                                                                               | RAM ADDRESS BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.6.3                                                                                               | RAM READ/WRITE AND CHIP SELECT LOGIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.6.4                                                                                               | RAM DATA BUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       |                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | 5.4.6.6                                                                                               | PROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                       | LINE PR<br>5.2.1<br>PHOTOCO<br>5.3.1<br>5.3.2<br>TELECOM<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.3<br>5.4.4 | 5.2.1 928 PRINT<br>PHOTOCOMPOSITION<br>5.3.1 GENERAL D<br>5.3.2 PIO DESCR<br>TELECOMMUNICATION<br>5.4.1 GENERAL D<br>5.4.2 INTERNAL<br>5.4.3 SYSTEM BU<br>5.4.4 CPU BOARD<br>5.4.4.1<br>5.4.4.2<br>5.4.4.3<br>5.4.4.4<br>5.4.4.2<br>5.4.4.3<br>5.4.4.4<br>5.4.4.5<br>5.4.4.6<br>5.4.4.7<br>5.4.4.8<br>5.4.4.8<br>5.4.4.9<br>5.4.4.10<br>5.4.4.10<br>5.4.5.1<br>5.4.5.1<br>5.4.5.2<br>5.4.5.1<br>5.4.5.2<br>5.4.5.3<br>5.4.5.4<br>5.4.5.5<br>5.4.6 MEMORY BOA<br>5.4.6.1<br>5.4.6.2<br>5.4.6.3<br>5.4.6.4<br>5.4.6.5 | LINE PRINTER OPTION (LPO) (5521/5531)<br>5.2.1 928 PRINTER INTERFACE ASSEMBLY (WL#270-0341)<br>PHOTOCOMPOSITION INPUT OPTION (PIO)<br>5.3.1 GENERAL DESCRIPTION<br>5.3.2 PIO DESCRIPTION AND CODES<br>TELECOMMUNICATIONS<br>5.4.1 GENERAL DESCRIPTION<br>5.4.2 INTERNAL ARCHITECTURE<br>5.4.3 SYSTEM BUSES<br>5.4.4 CPU BOARD<br>5.4.4.1 GENERAL<br>5.4.4.2 8080 CONTROL AND TIMING LOGIC<br>5.4.4.3 OUT COMMAND DECODER<br>5.4.4.4 IN COMMAND DECODER<br>5.4.4.5 CHANNEL ID SWITCHES AND BUFFER<br>5.4.4.6 LINE MONITOR INTERFACE<br>5.4.4.8 EVEN PARITY GENERATOR AND CHECKER<br>5.4.4.9 INTERVAL TIMER<br>5.4.4.10 8214 PRIORITY INTERRUPT CONTROL UNIT<br>5.4.4.11 MEMORY TIMING<br>5.4.5.1 GENERAL<br>5.4.5.2 8251 (USART)<br>5.4.5.3 MODEM INTERFACE |

2

#### ILLUSTRATIONS

| FIGURE # | TITLE                                              | PAGE |

|----------|----------------------------------------------------|------|

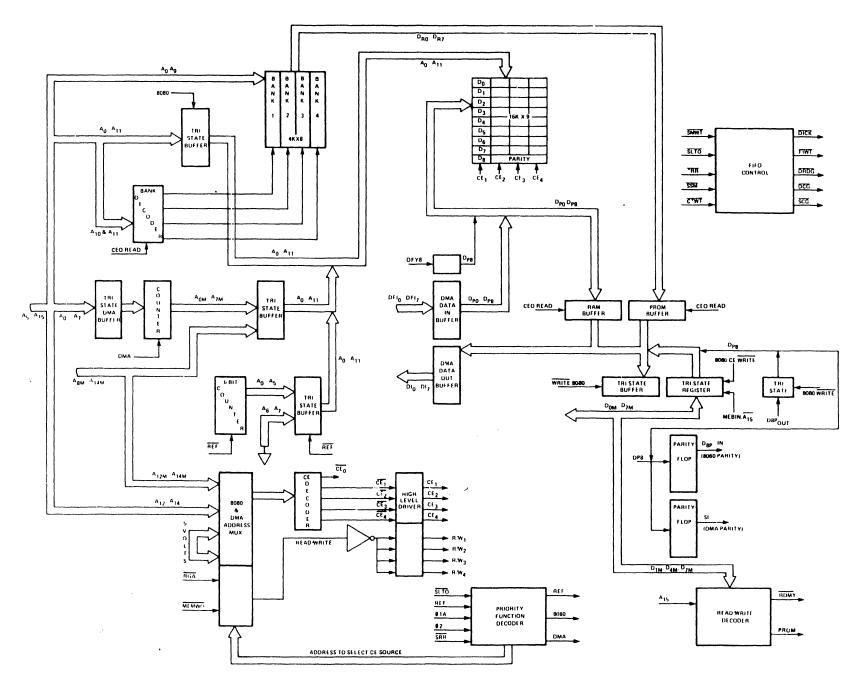

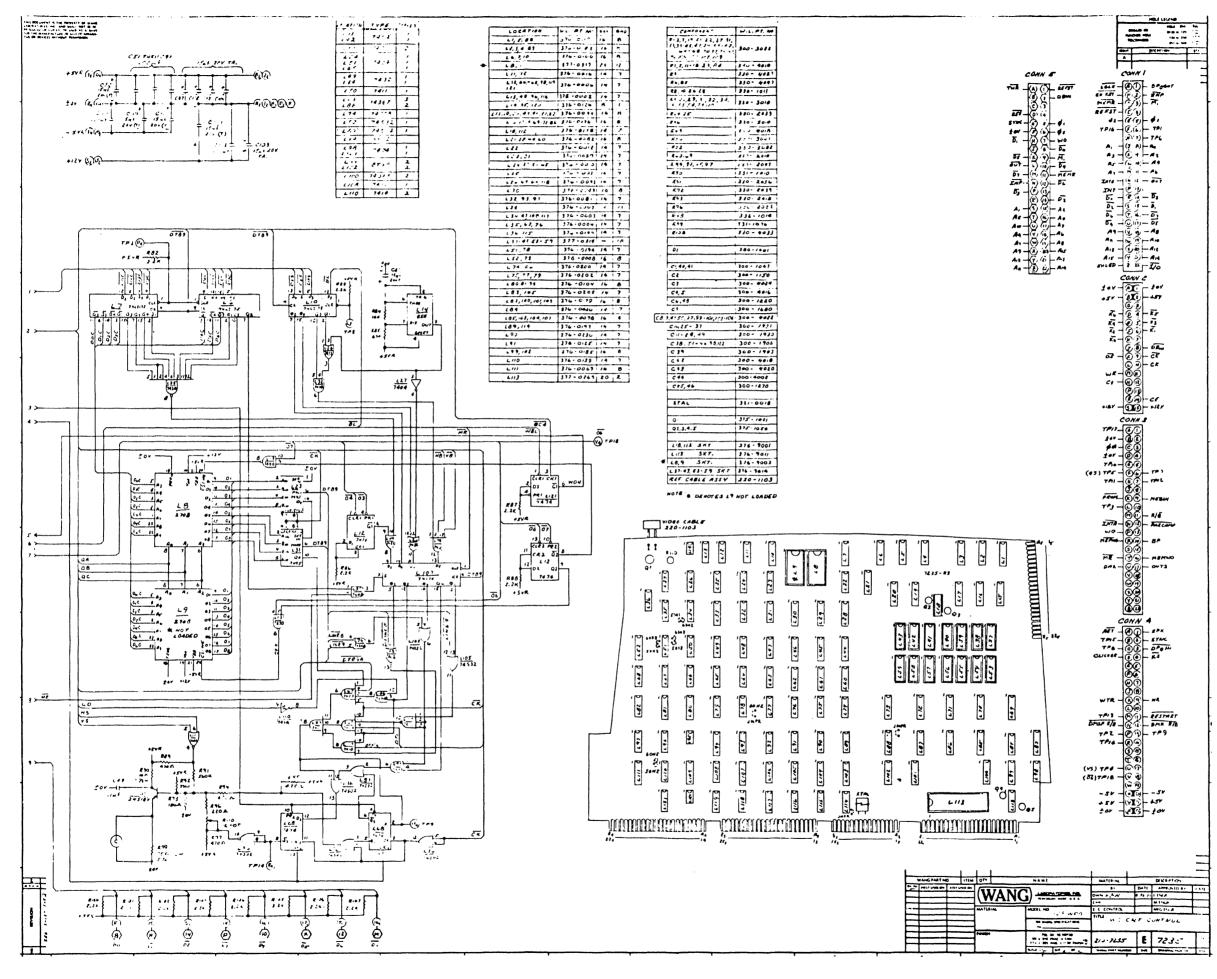

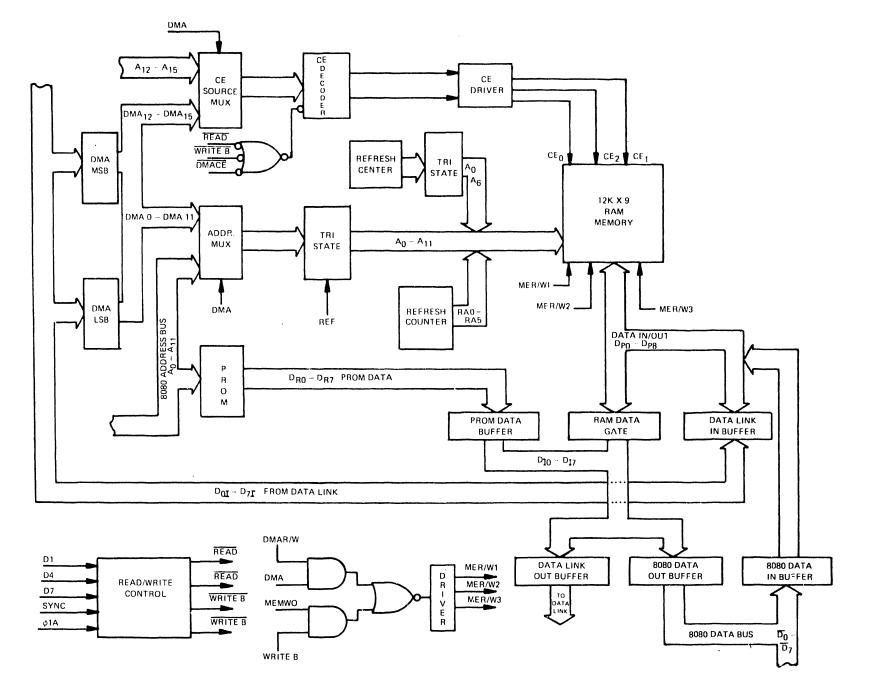

| 2-1      | Master Memory-Block Diagram                        | 2-2  |

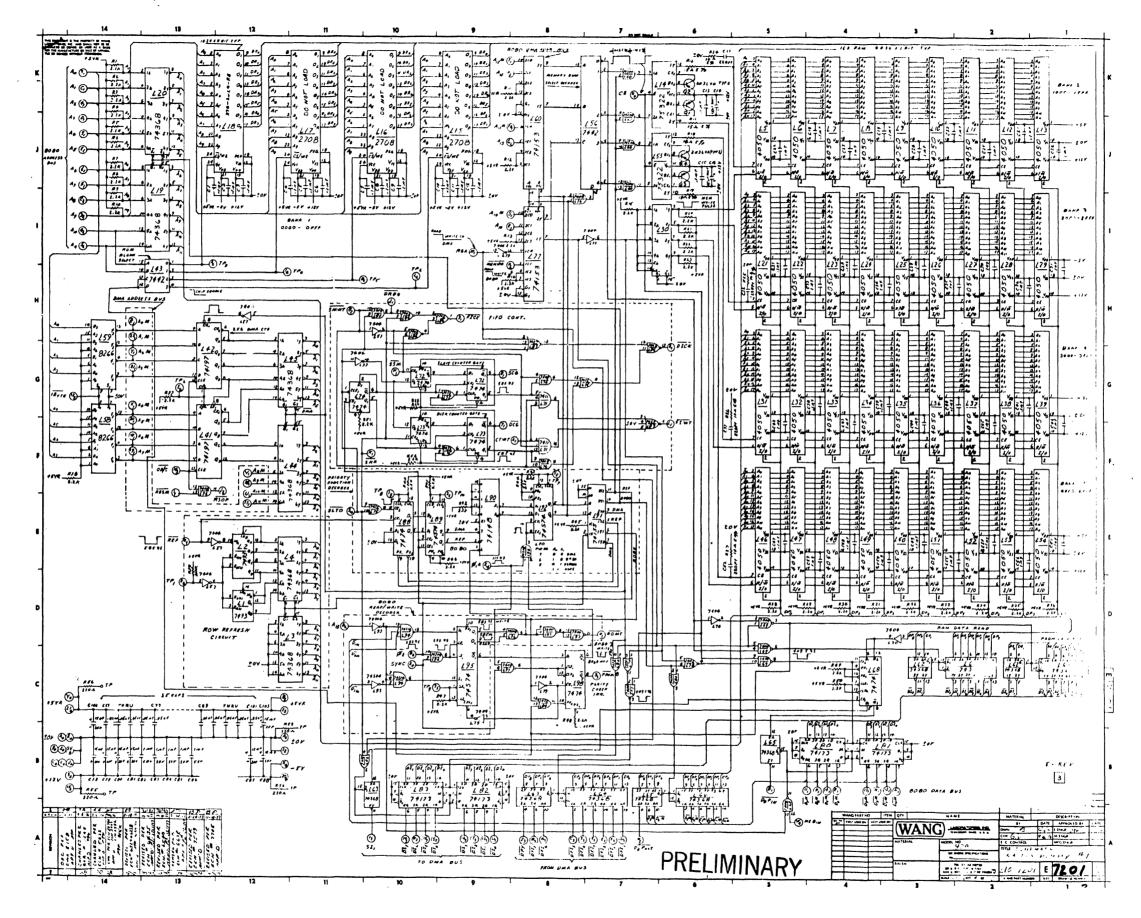

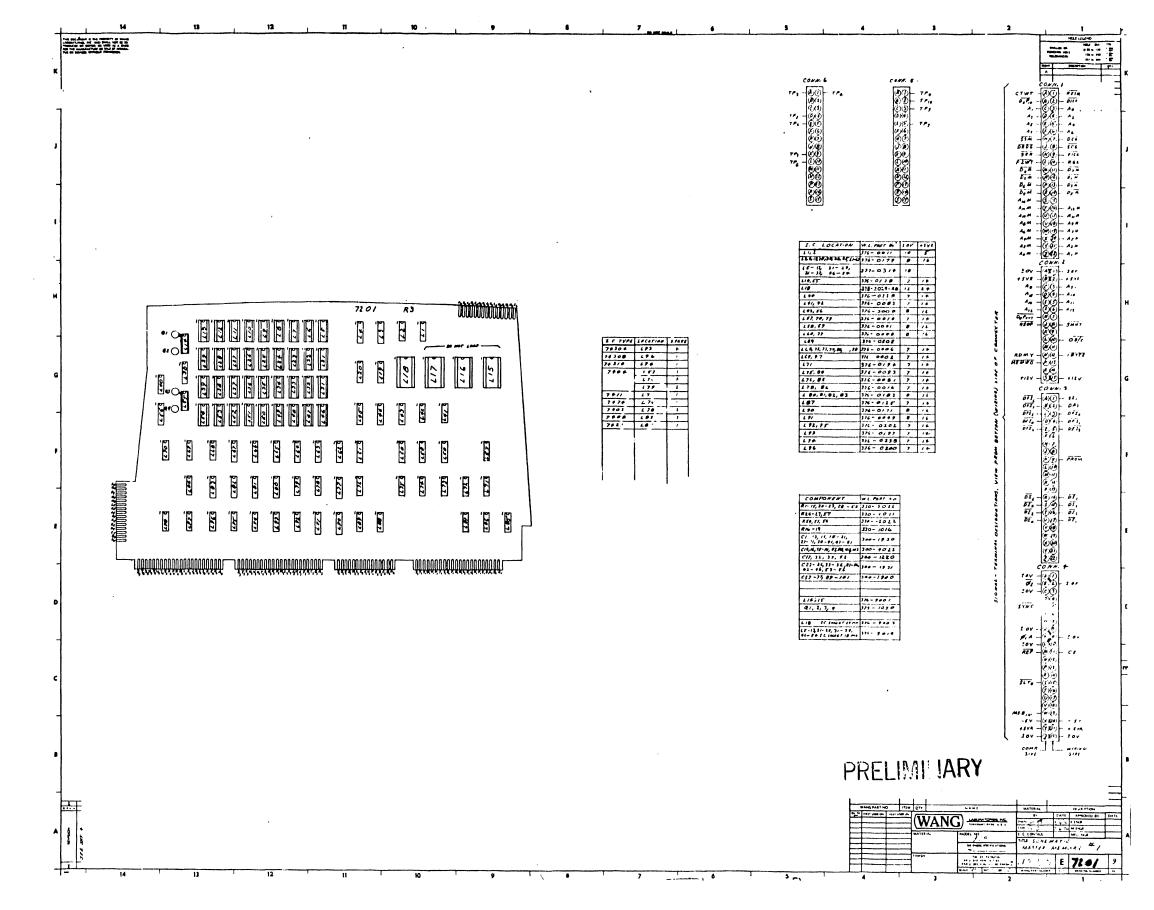

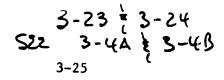

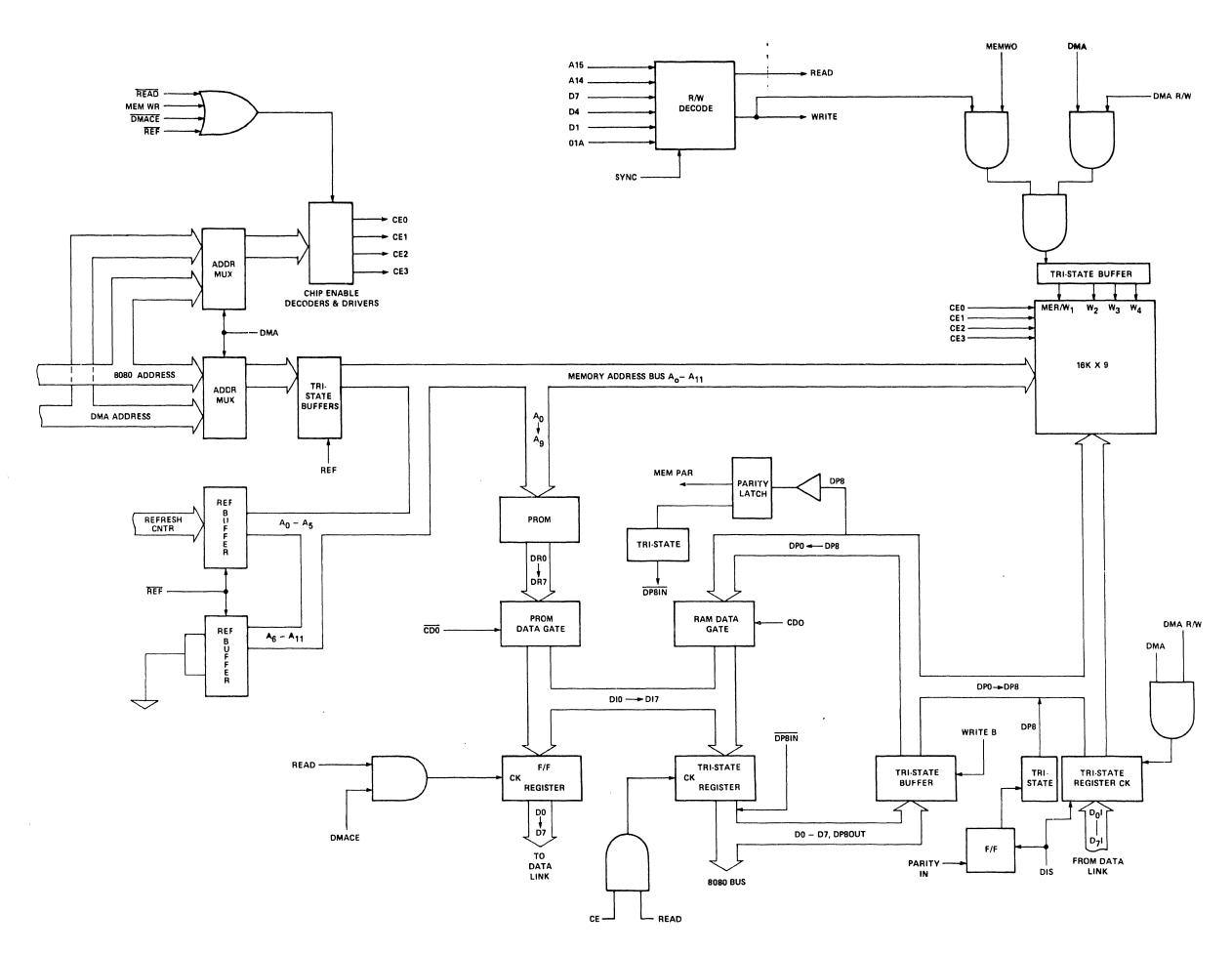

| 2-2      | Master Memory-Schematic Illustration Sheet 1       | 2-12 |

|          | Sheet 2                                            | 2-13 |

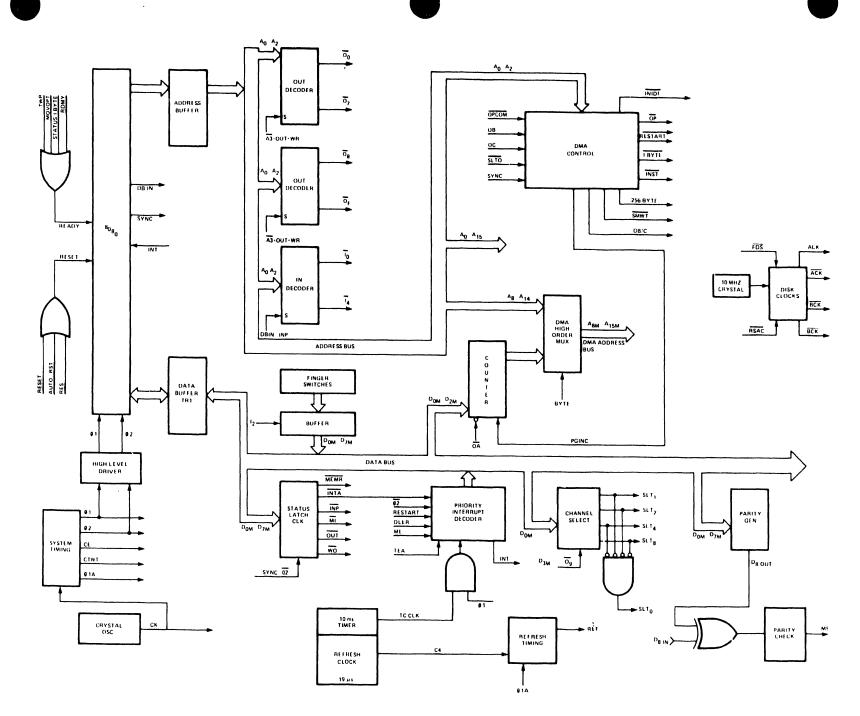

| 2-3      | Master CPU-Block Diagram                           | 2-15 |

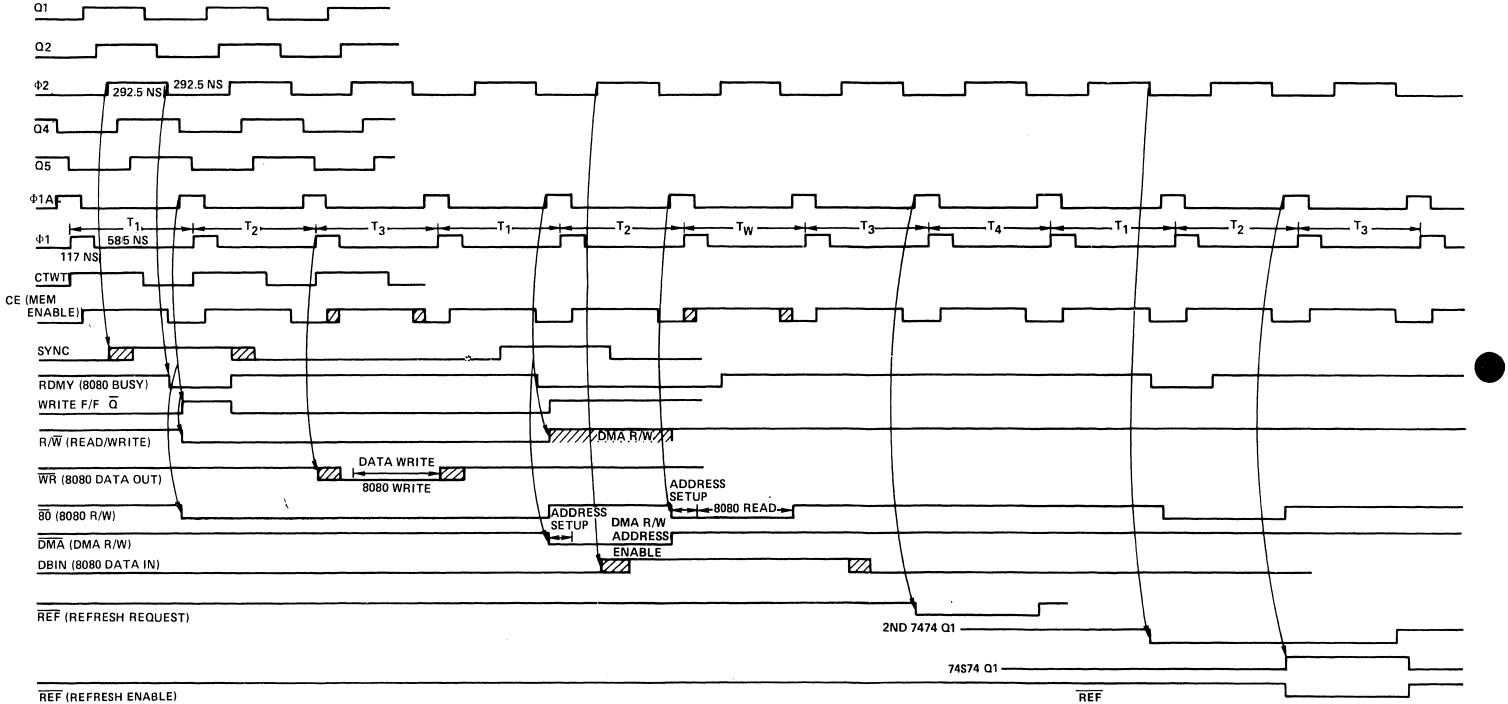

| 2-4      | Master CPU-Timing Diagram                          |      |

|          | (Includes Master Memory Timing)                    | 2-16 |

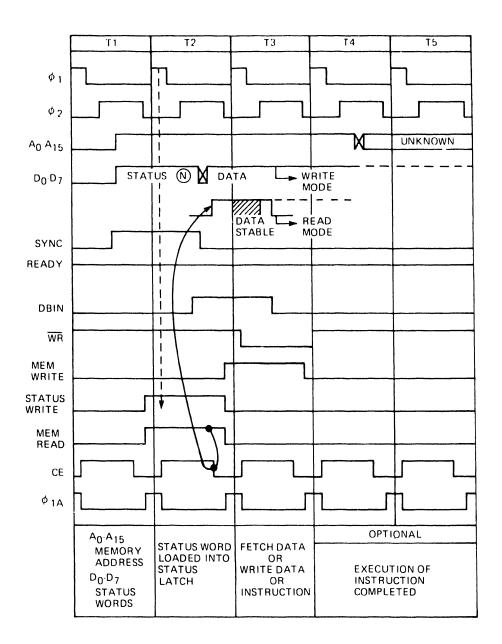

| 2-5A     | Basic 8080 Instruction Cycle                       | 2-17 |

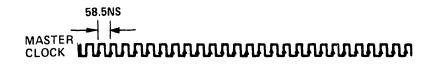

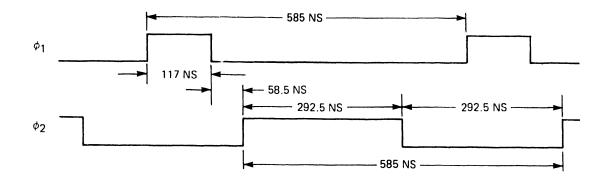

| 2-5B     | 01 and 02 Clock Timing                             | 2-17 |

| 2-6      | A & B Clock Generator-Timing Diagram               | 2-33 |

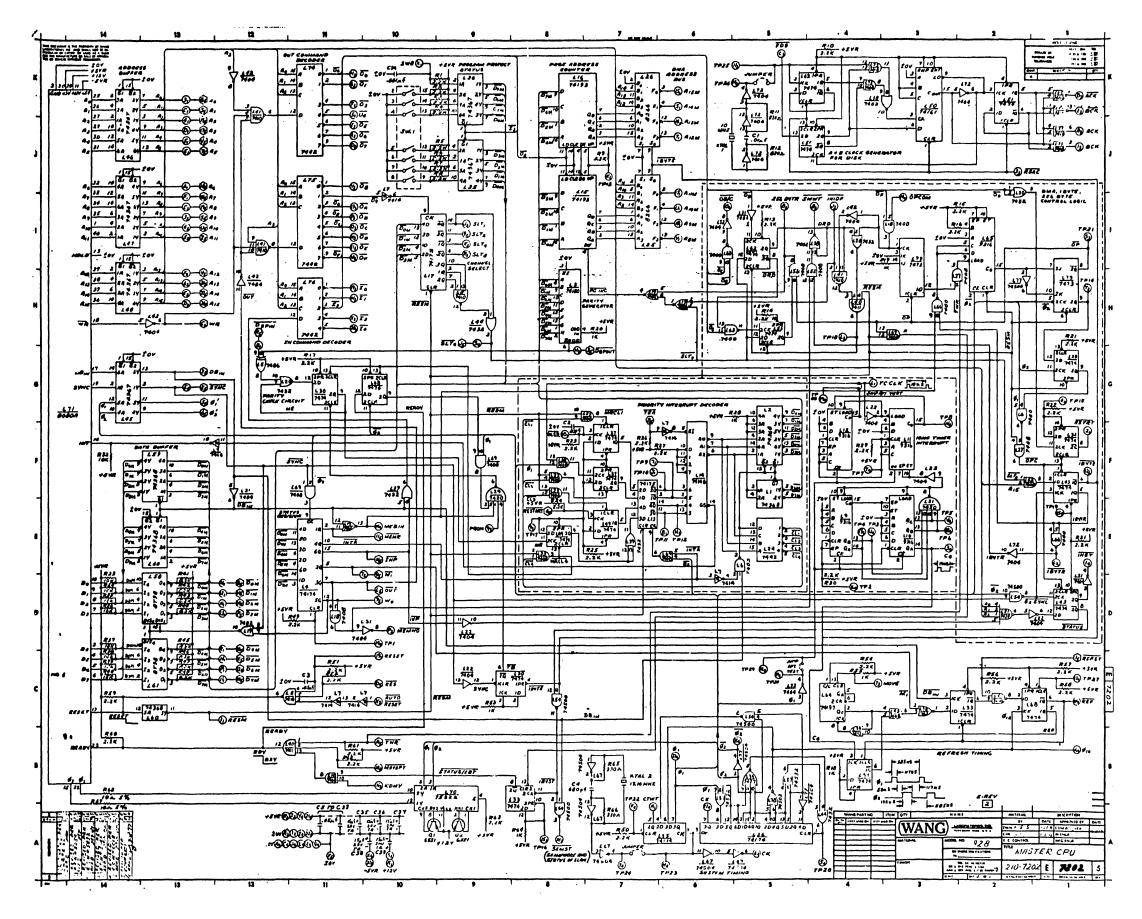

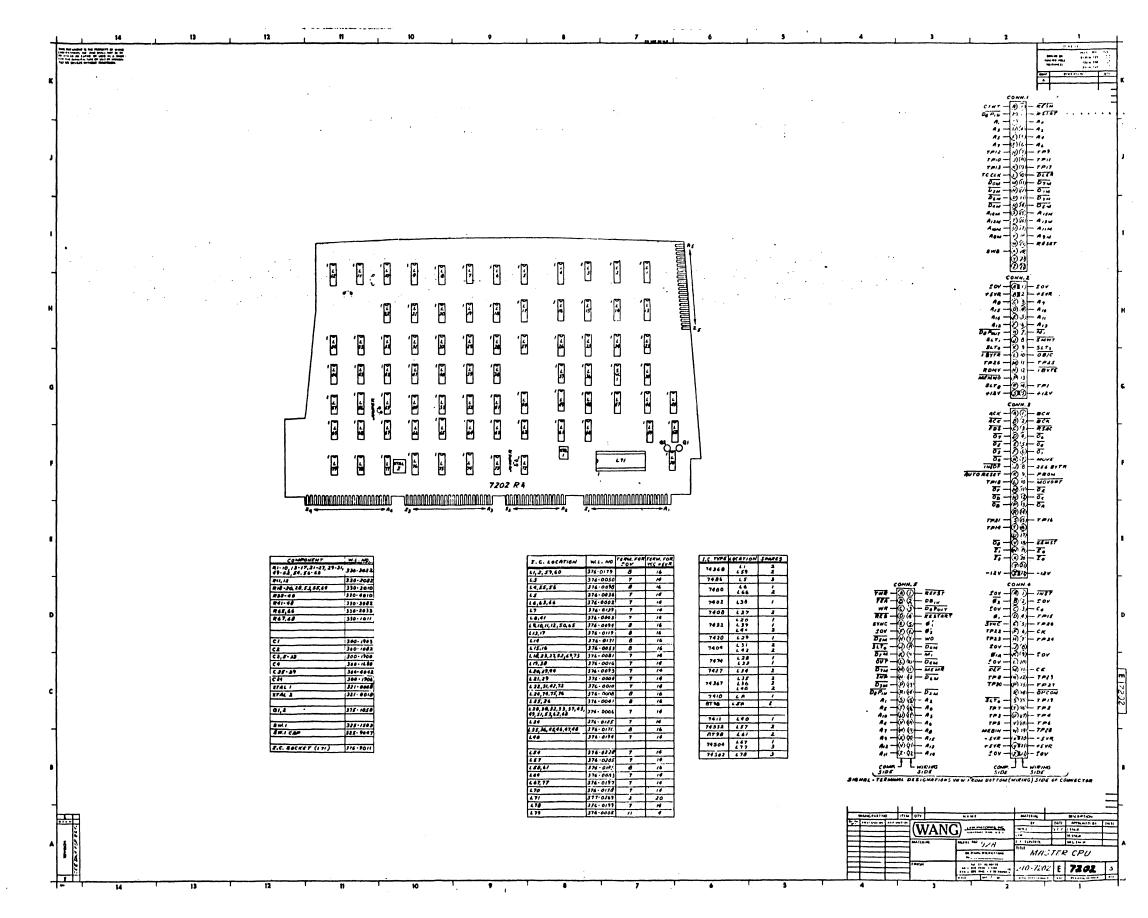

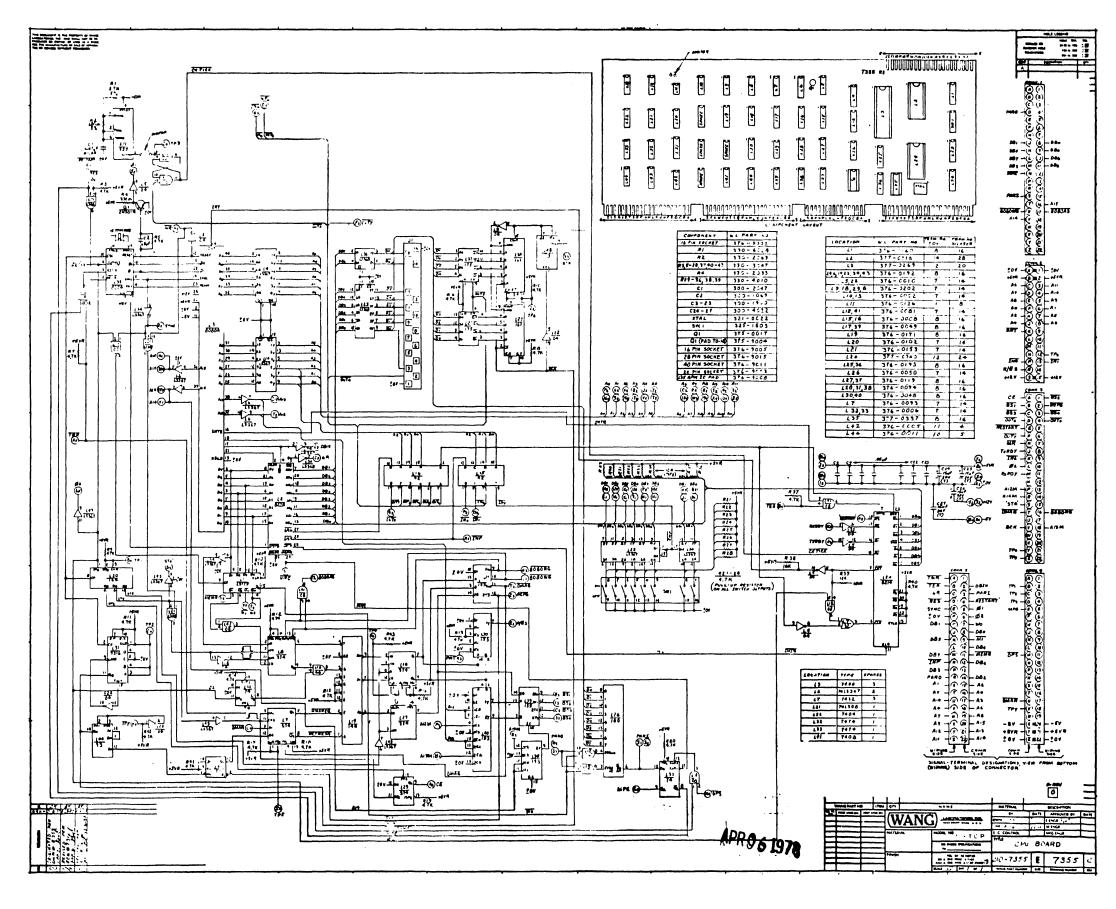

| 2-7      | Master CPU-Schematic Illustration Sheet 1          | 2-34 |

|          | Sheet 2                                            | 2-35 |

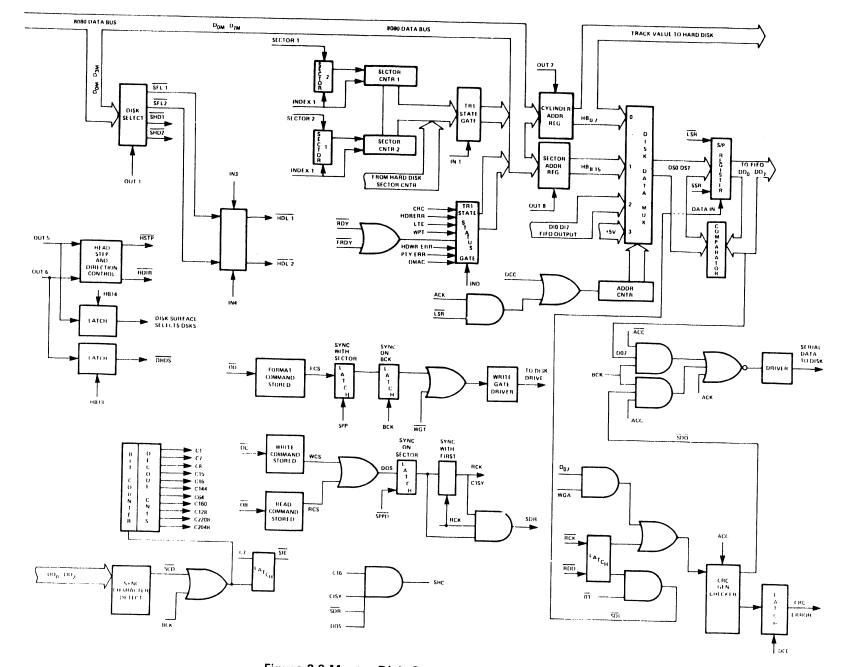

| 2-8      | Master Disk Controller-Block Diagram               | 2-37 |

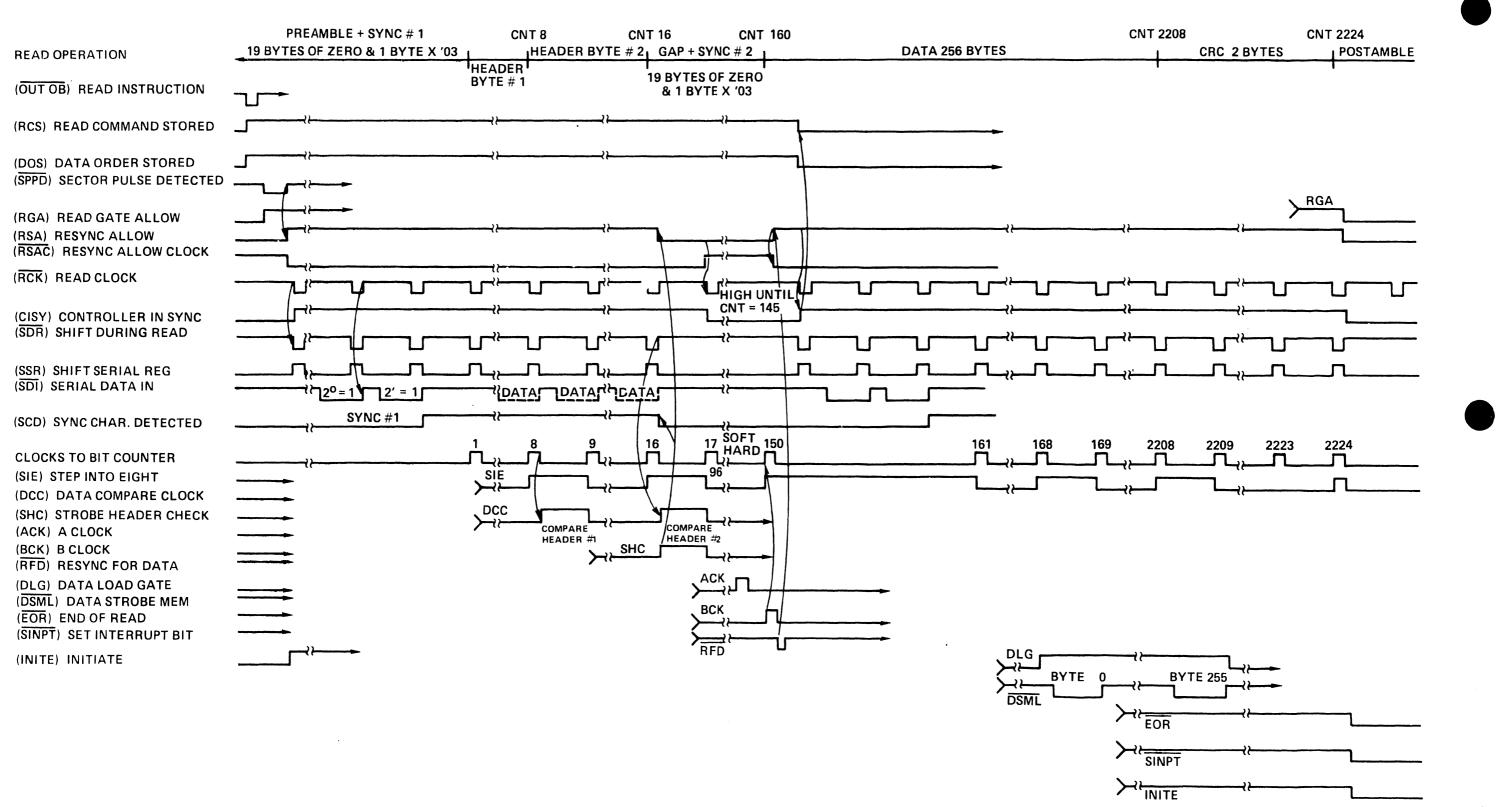

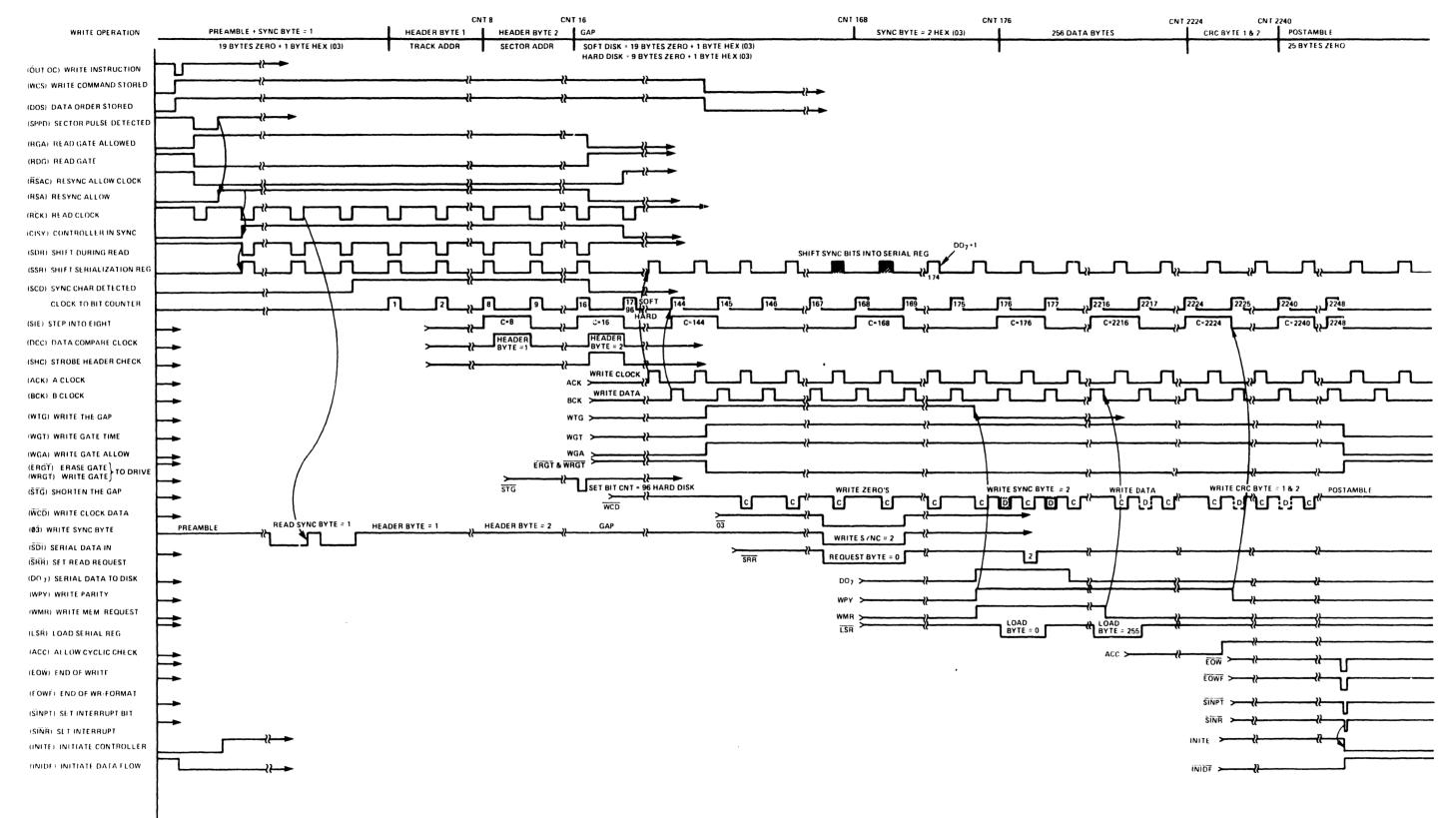

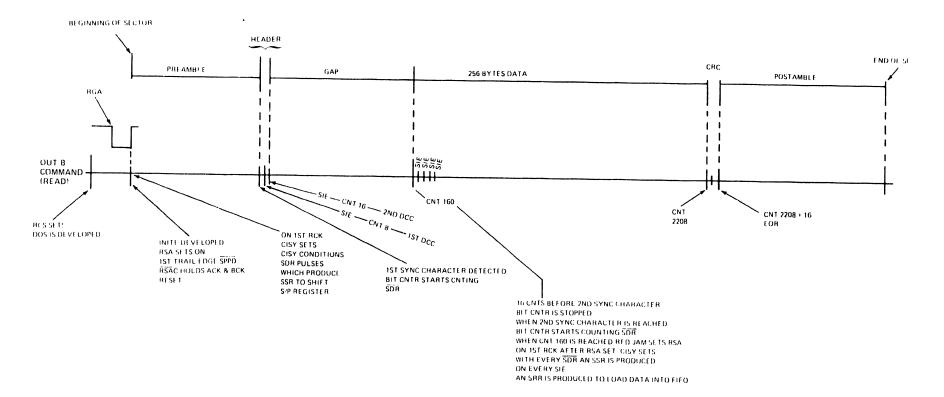

| 2-9      | Master Disk Controller-Timing Diagrams             |      |

|          | Read-Sheet 1                                       | 2-38 |

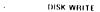

|          | Write-Sheet 2                                      | 2-39 |

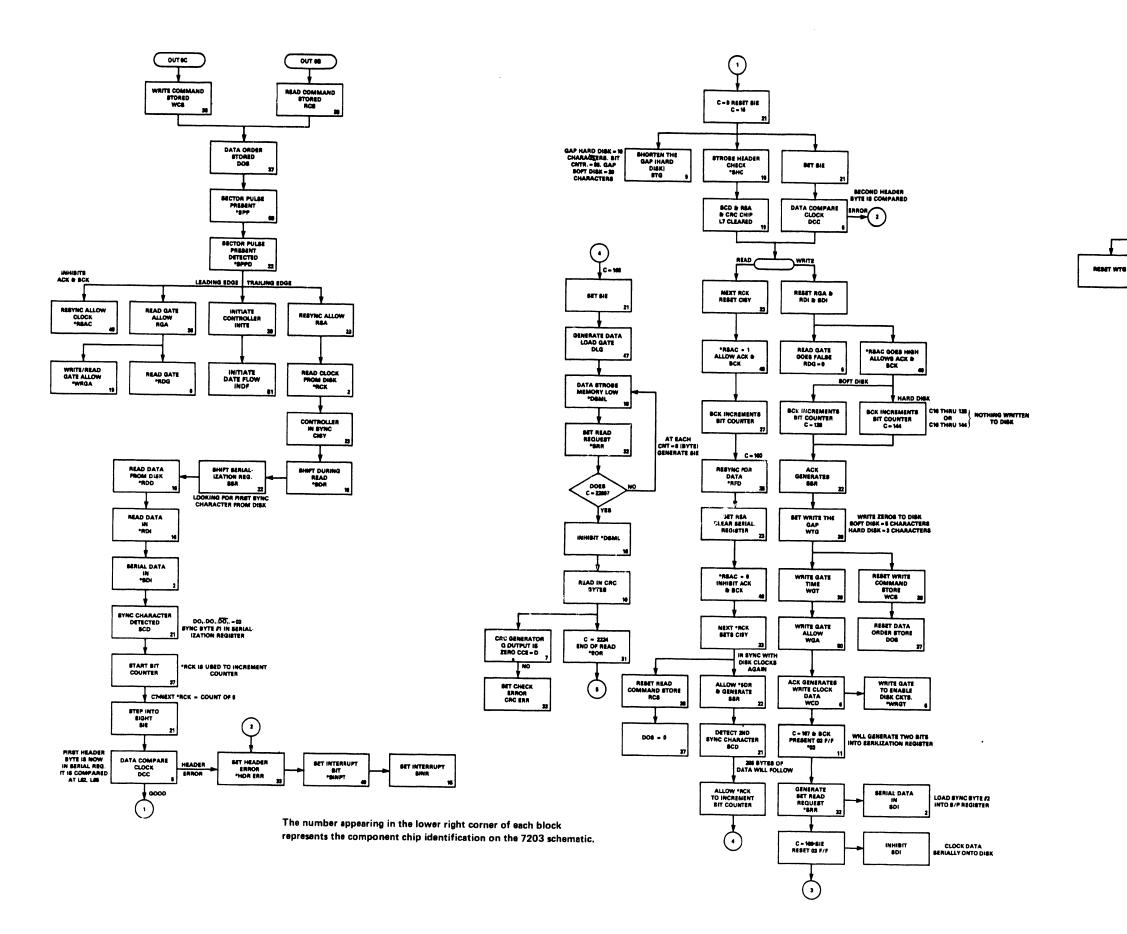

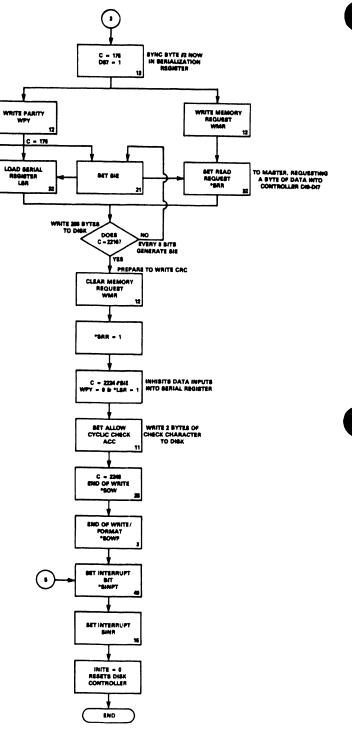

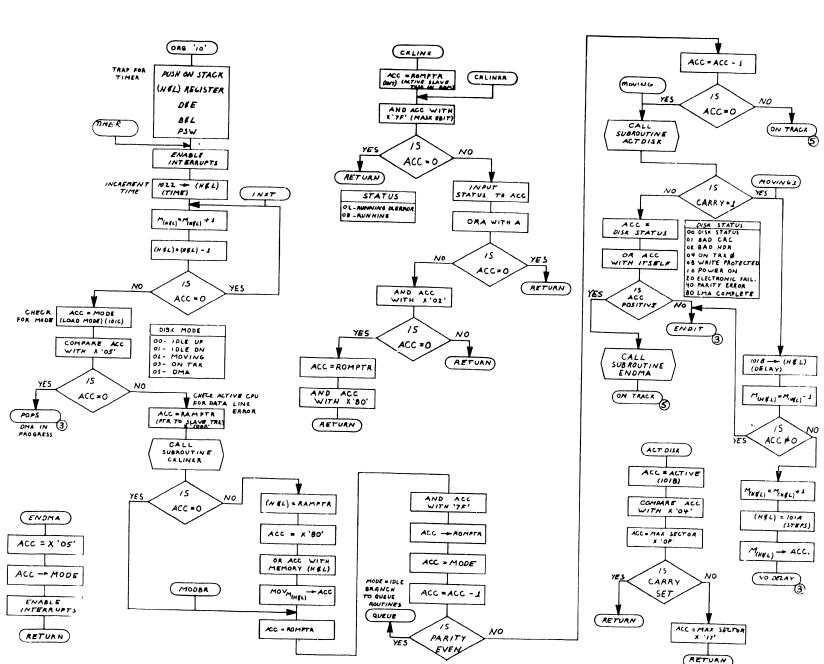

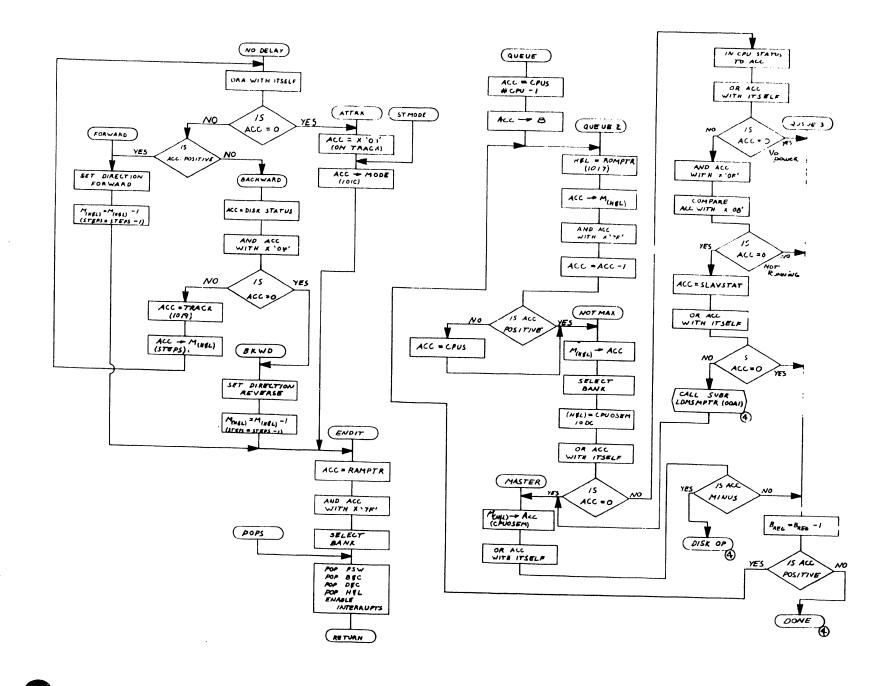

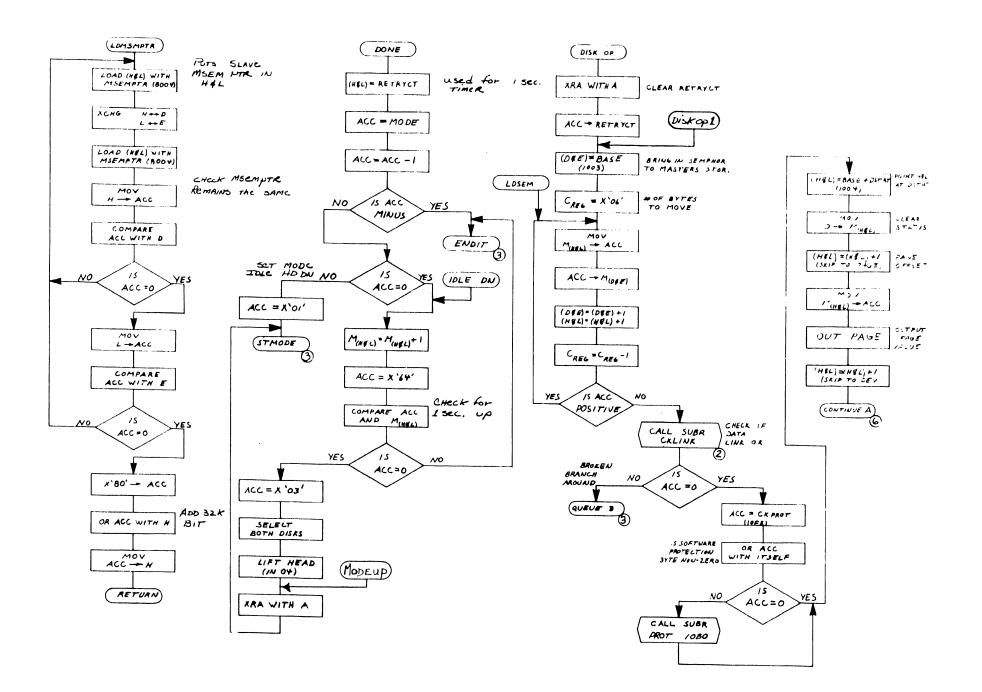

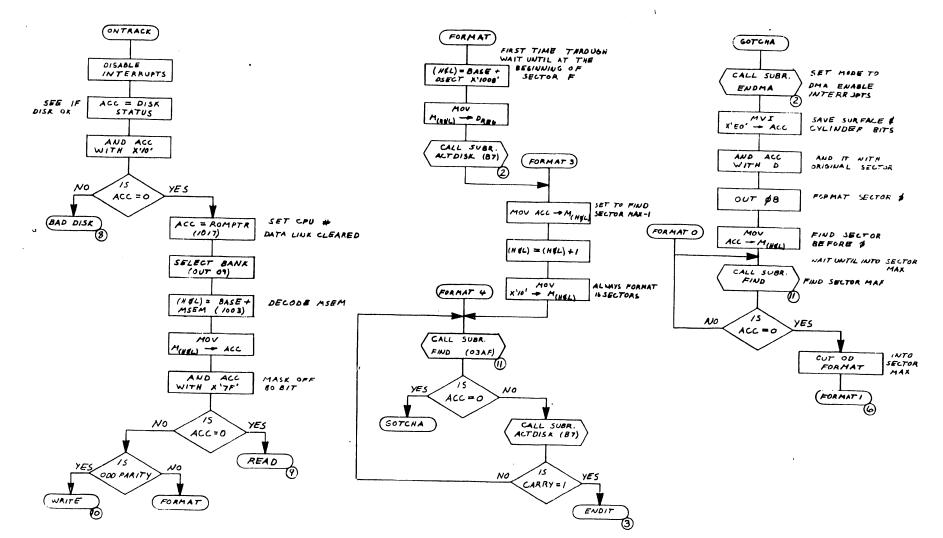

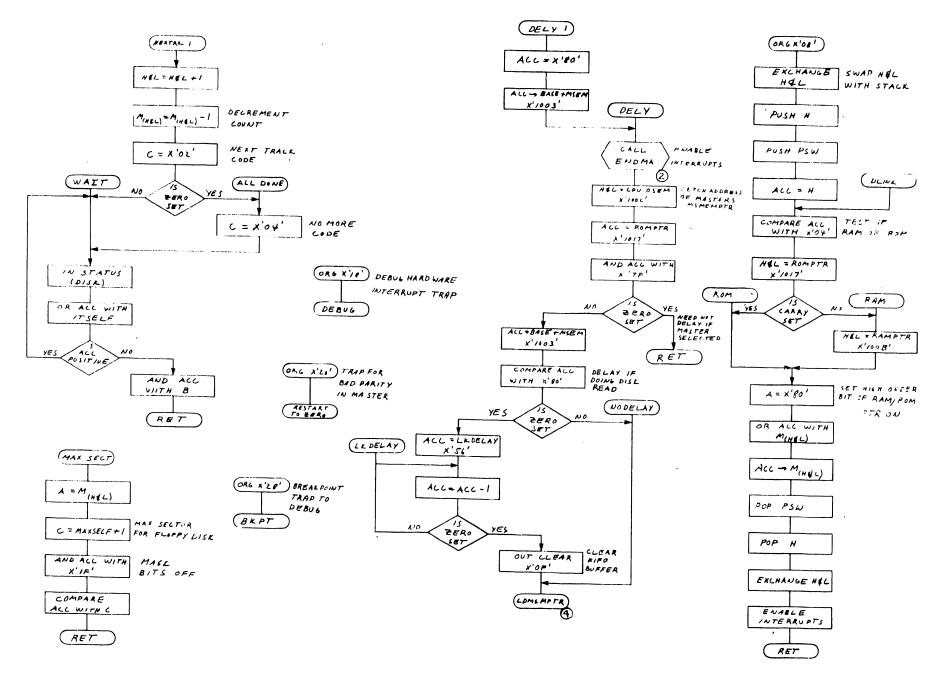

| 2-10     | Master Disk Controller-Flow Chart (Read/Write      |      |

|          | Operations)                                        | 2-40 |

| 2-11     | Master Disk Controller-Sector Read Event Chart     | 2-48 |

| 2-12     | Master Disk Controller-Sector Write Event Chart    | 2-55 |

| 2-13     | Master Disk Controller-Sector Format Event Chart 2 |      |

| 2-14     | Master Disk Controller-Schematic Illustrations     |      |

|          | Sheet 1                                            | 2-64 |

|          | Sheet 2                                            | 2-65 |

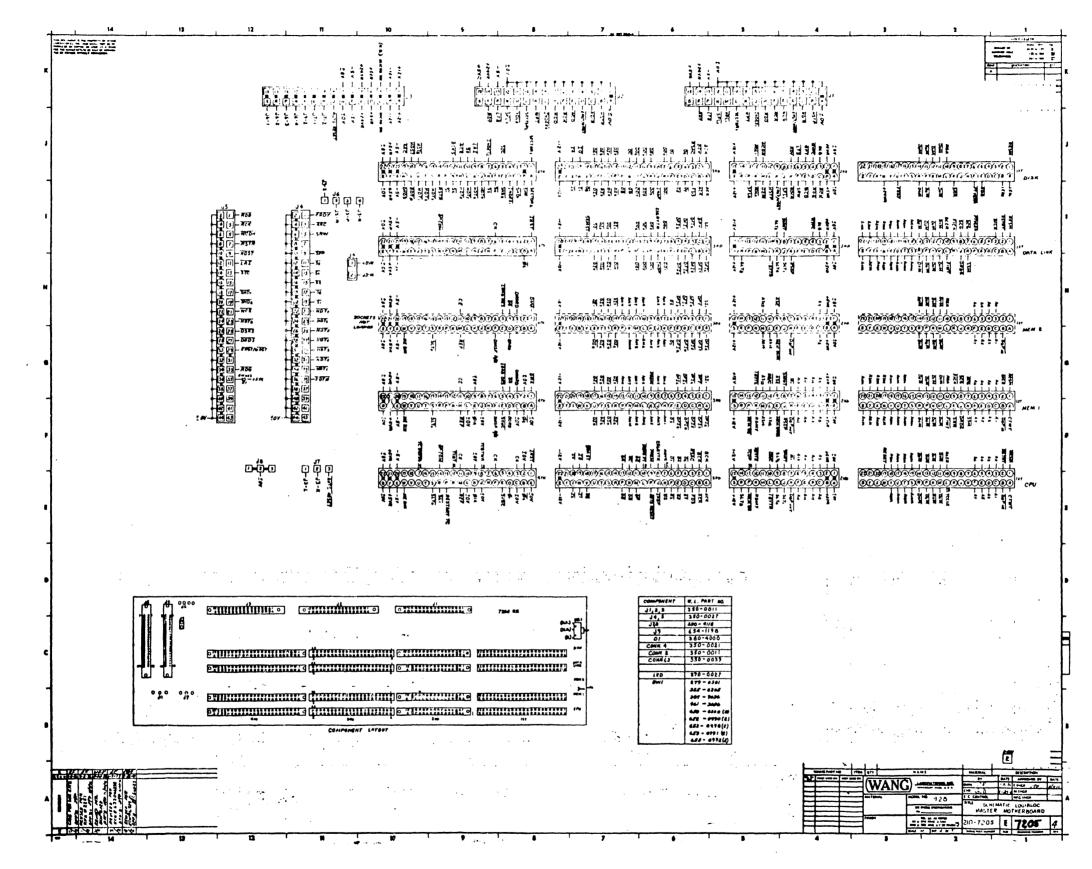

| 2-15     | Master Motherboard-Schematic Illustration          | 2-67 |

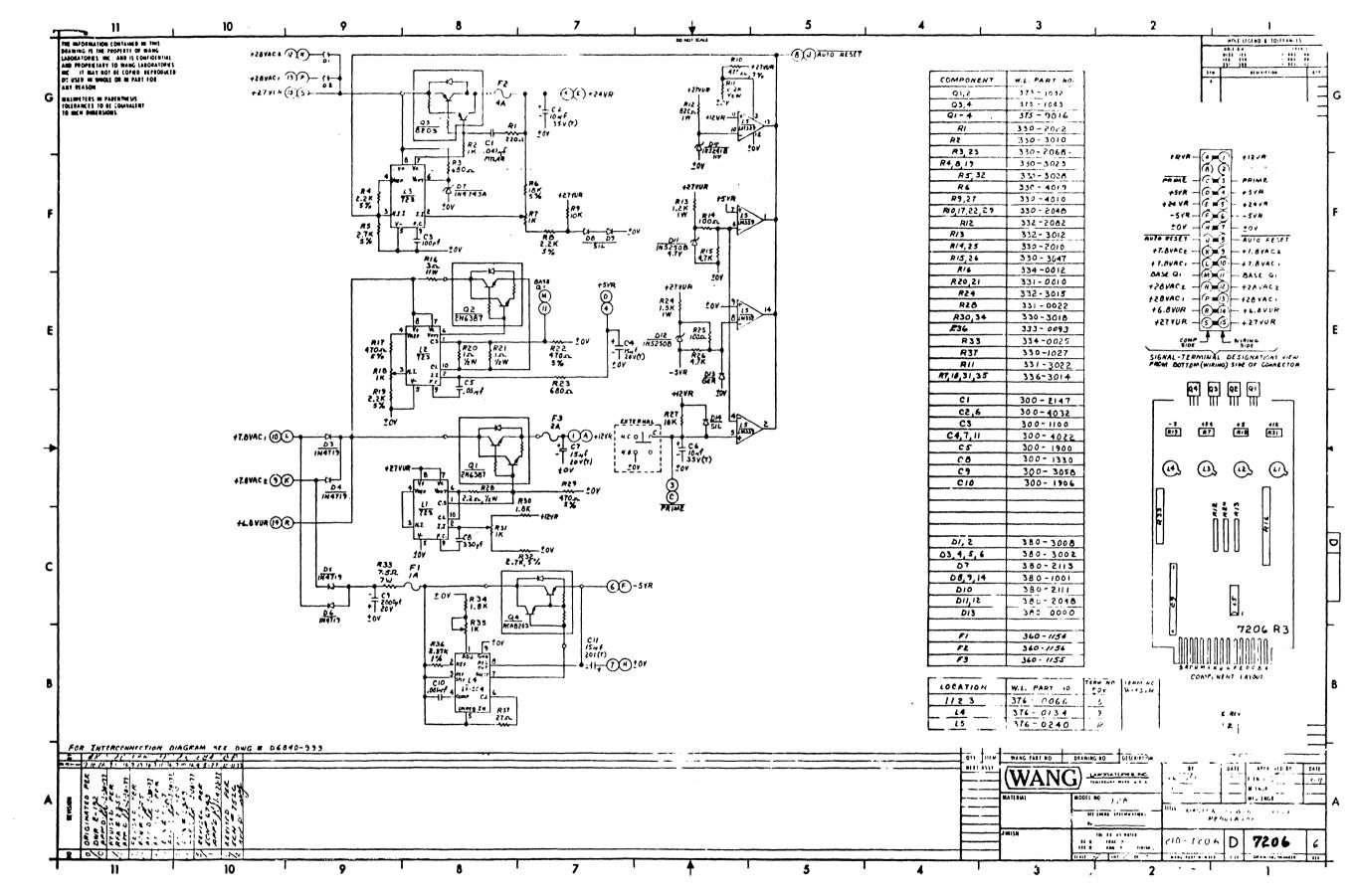

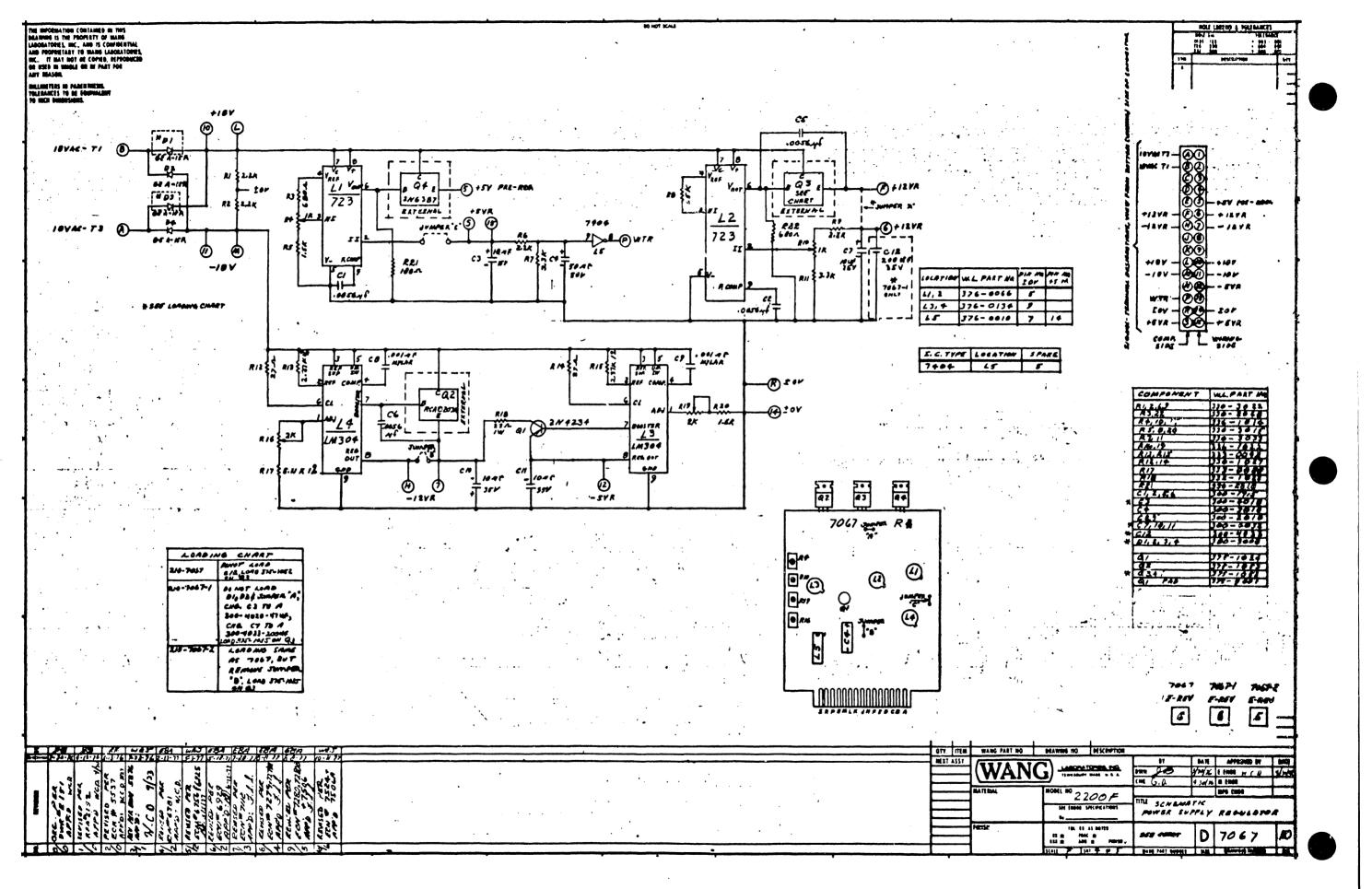

| 2-16     | Master Power Supply/Regulator-Schematic            |      |

|          | Illustration                                       | 2-69 |

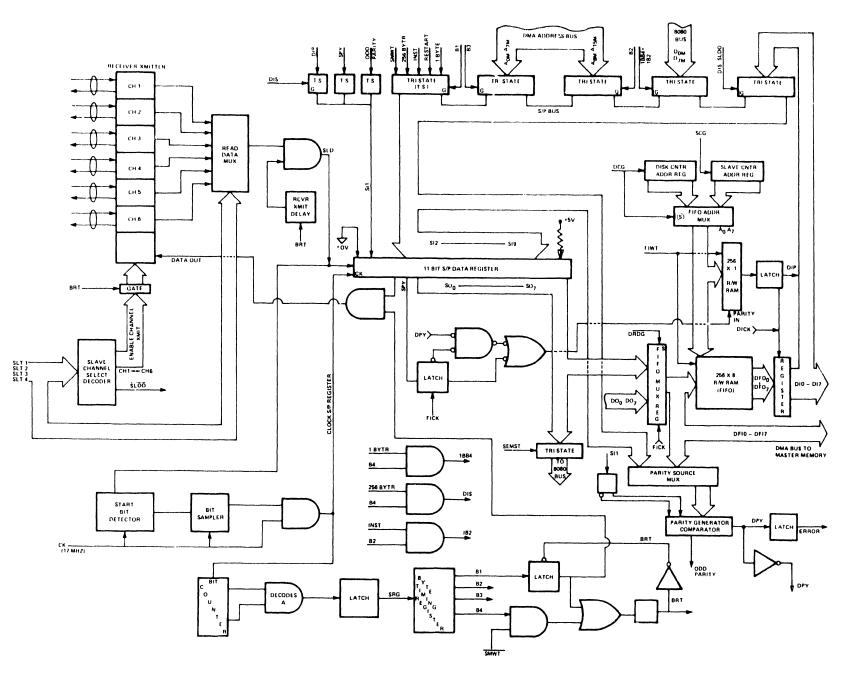

| 2-17     | Master Data Link-Block Diagram                     | 2-71 |

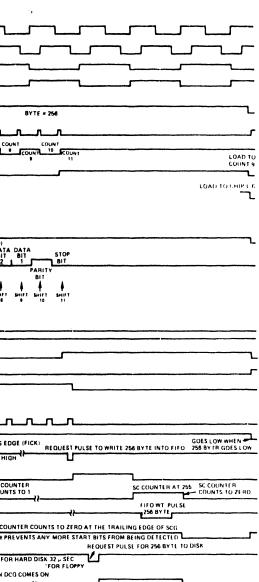

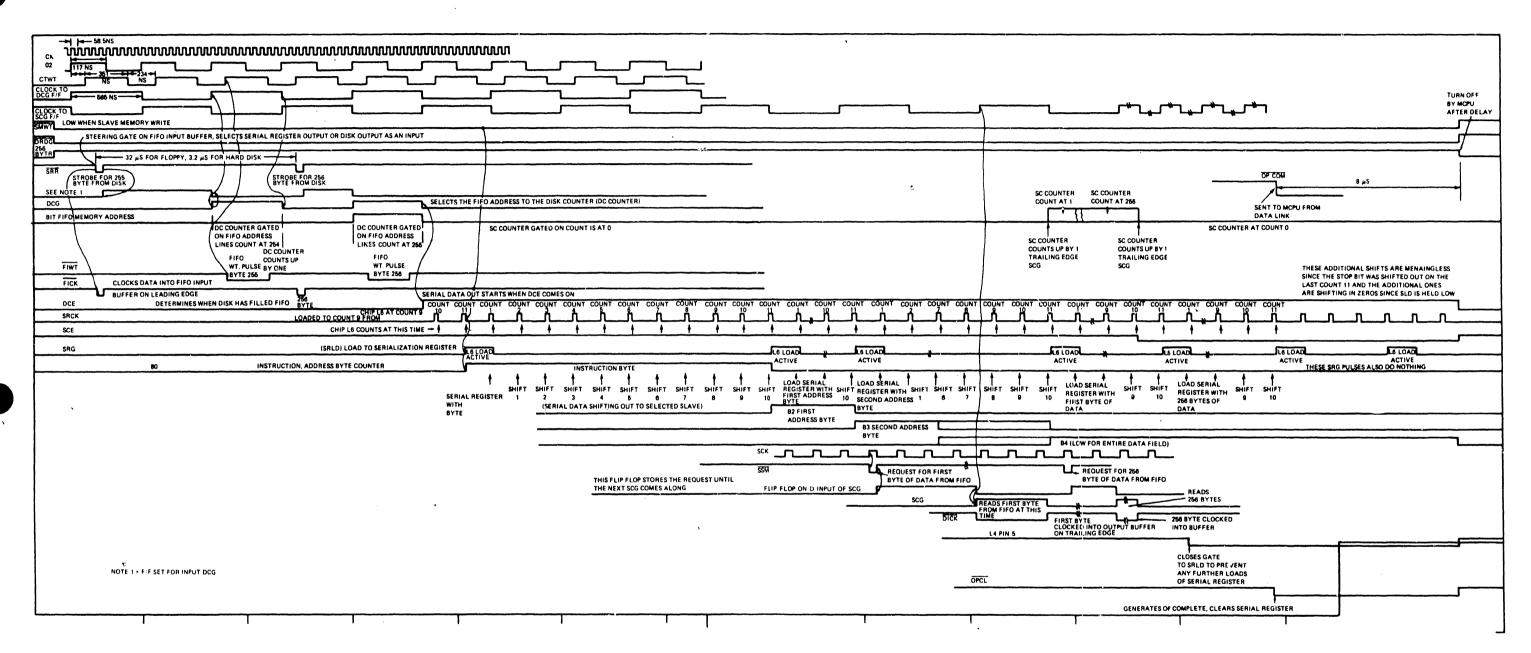

| 2-18     | Master Data Link-Timing Diagram Sheet 1            | 2-72 |

|          | Sheet 2                                            | 2-73 |

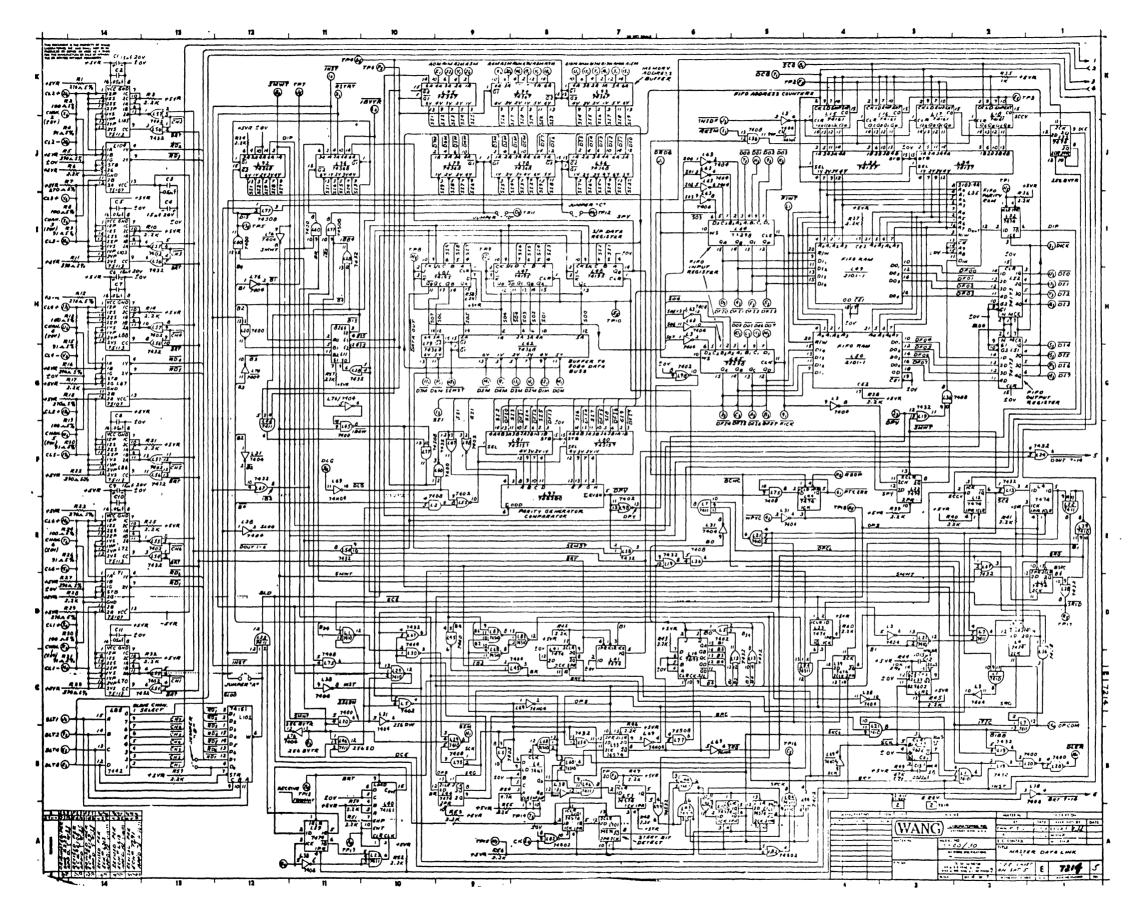

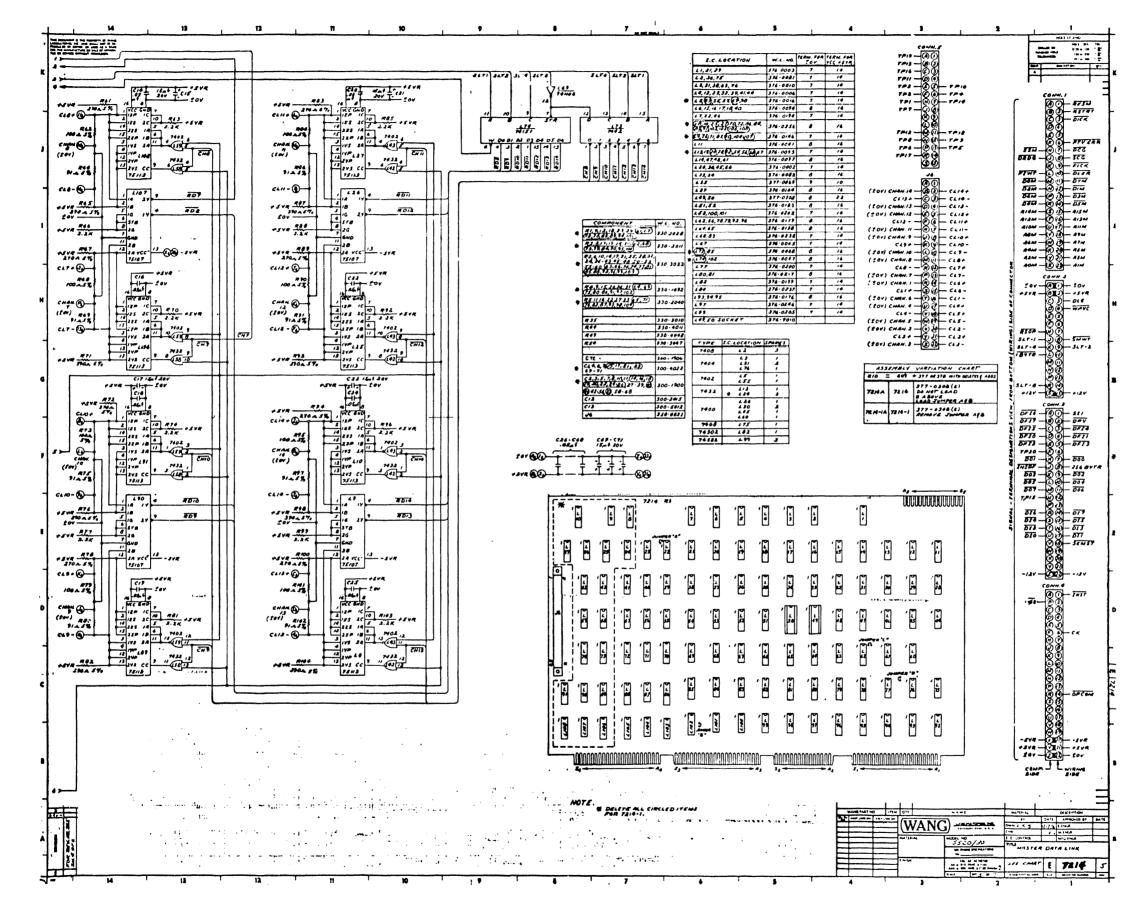

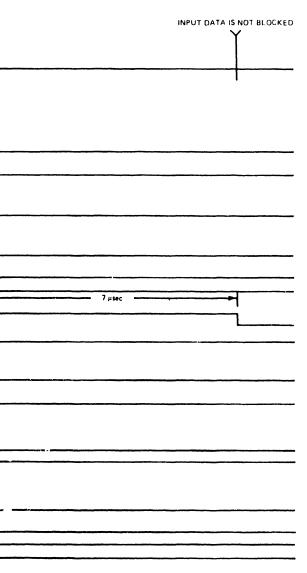

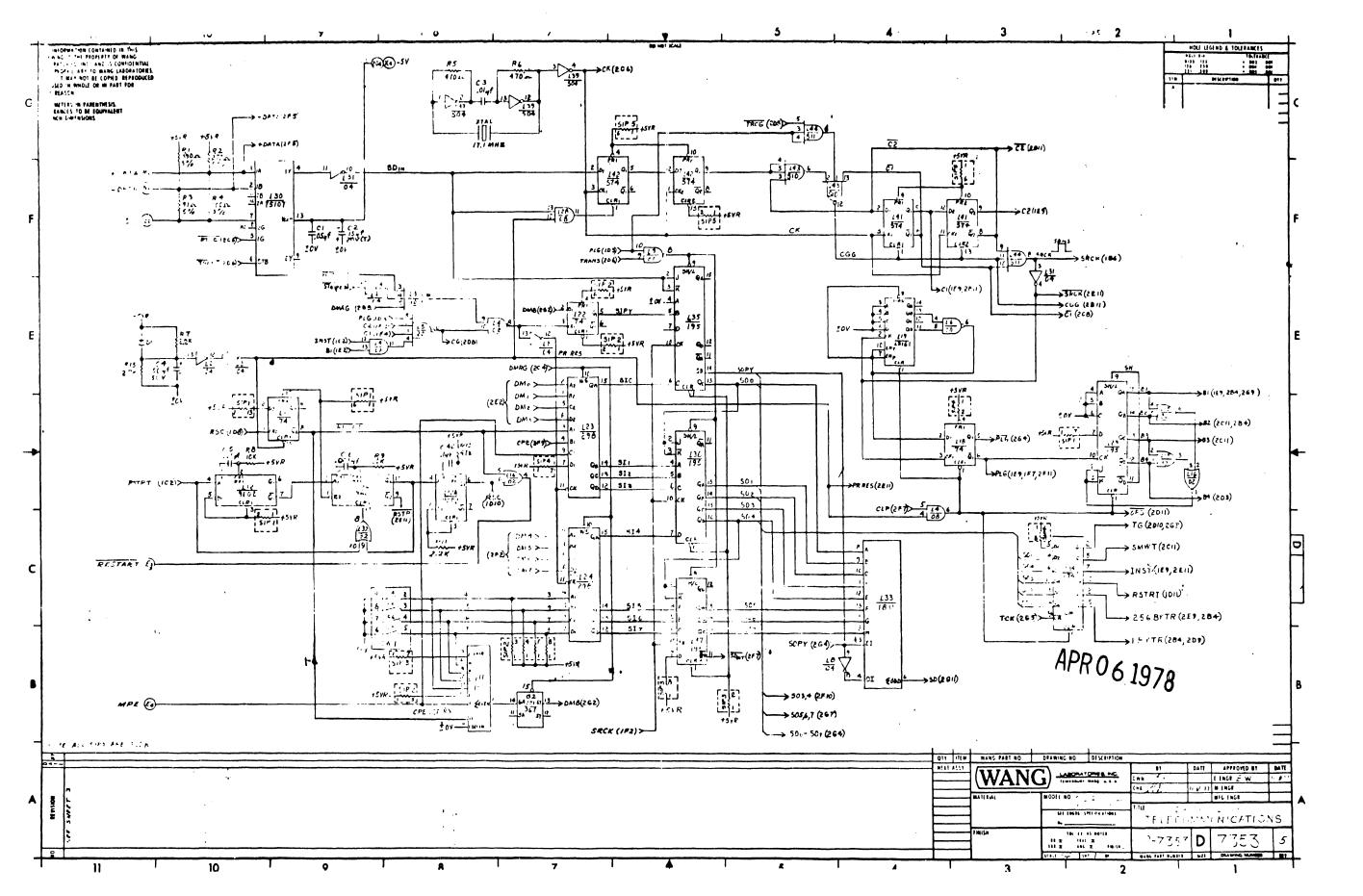

| 2-19     | Master Data Link-Schematic Illustration Sheet 1    | 2-92 |

|          | Sheet 2                                            | 2-93 |

v

#### FIGURE # TITLE

PAGE

| 3-1         | Workstation W/Motorola Monitor Regulator-                |

|-------------|----------------------------------------------------------|

|             | Schematic Illustration 3-2                               |

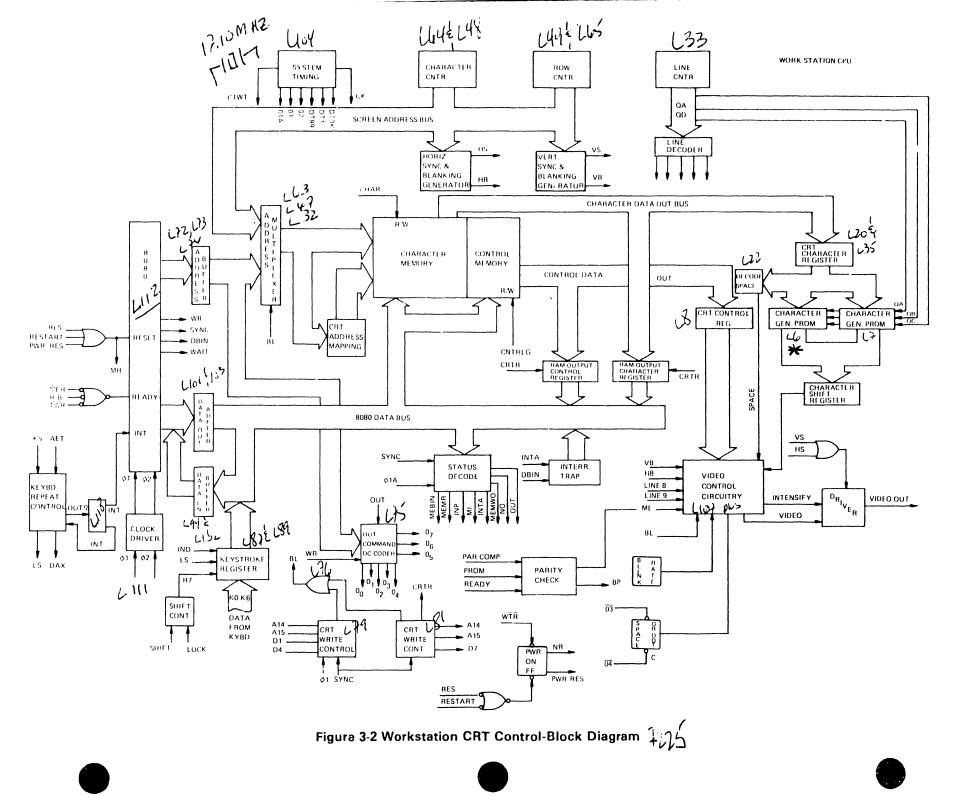

| 3-2         | Workstation CRT Control-Block Diagram                    |

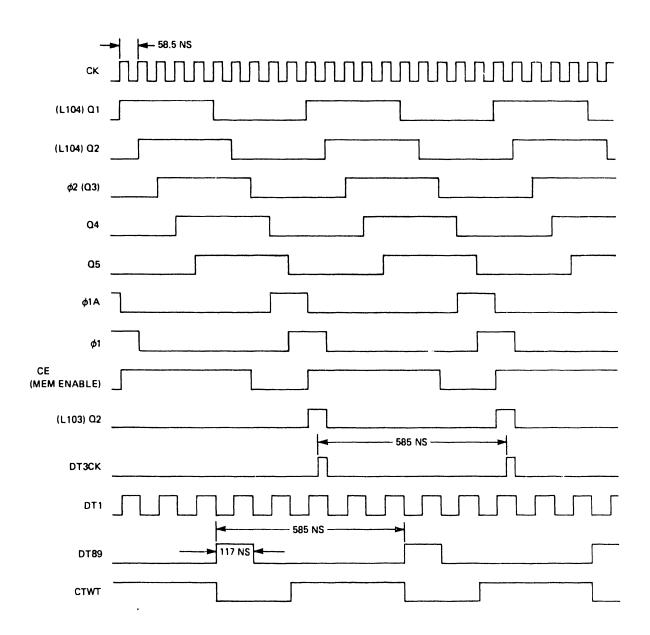

| 3-3         | Workstation CPU-Timing Diagram                           |

| 3-4         | Workstation CRT Character Counter-Block Diagram 3-7      |

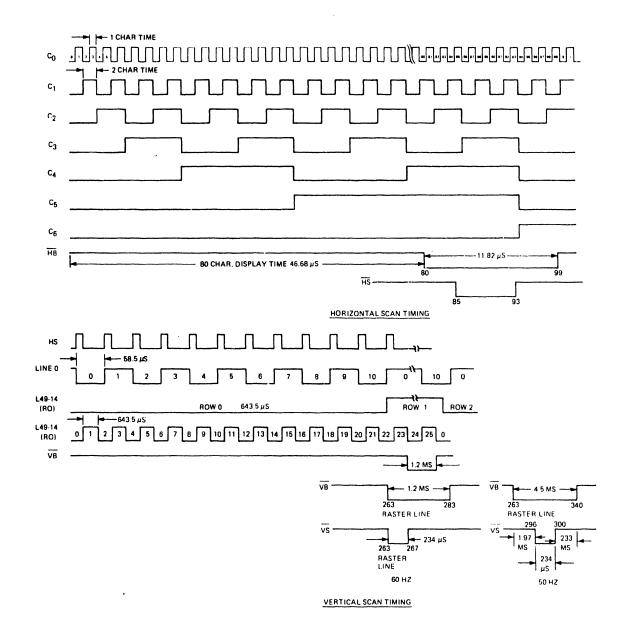

| 3-5         | Workstation CRT Horizontal and Vertical Scan-            |

|             | Timing Diagram 3-9                                       |

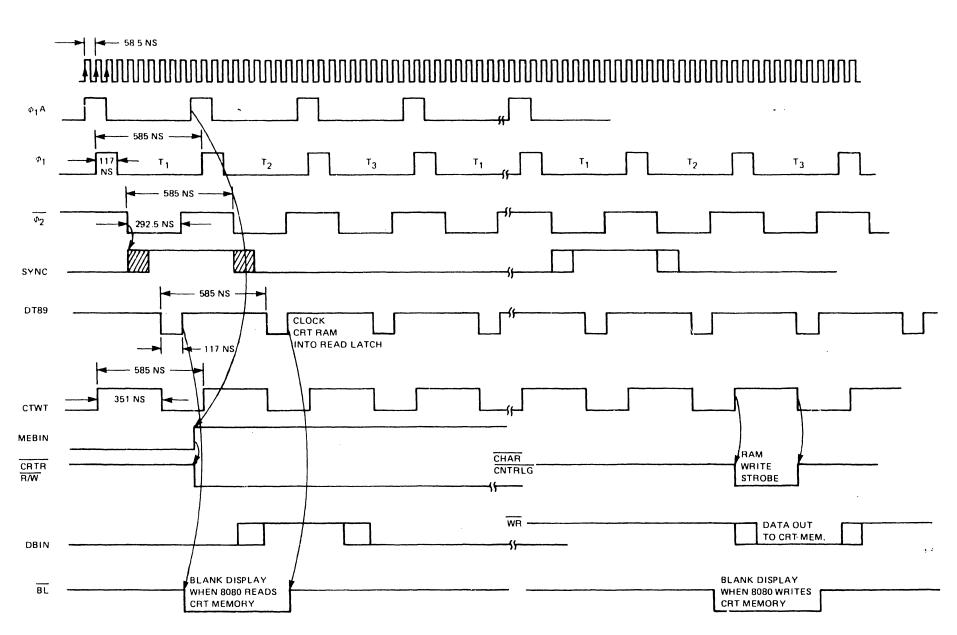

| 3-6         | Workstation CRT RAM Read/Write (by 8080)-                |

|             | Timing Diagram 3-11                                      |

| 3-7         |                                                          |

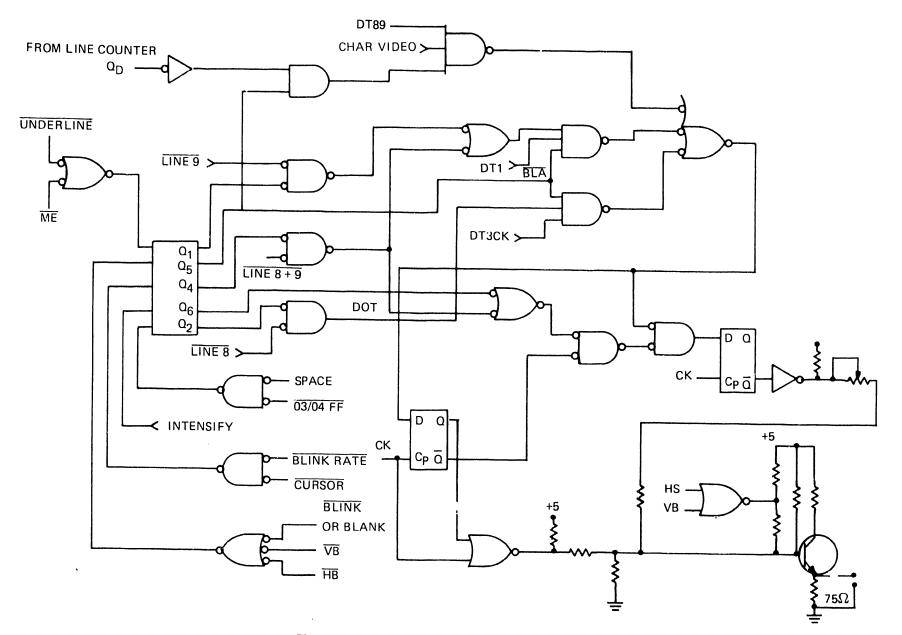

| 3-8         | Workstation CRT Video-Block Diagram                      |

|             |                                                          |

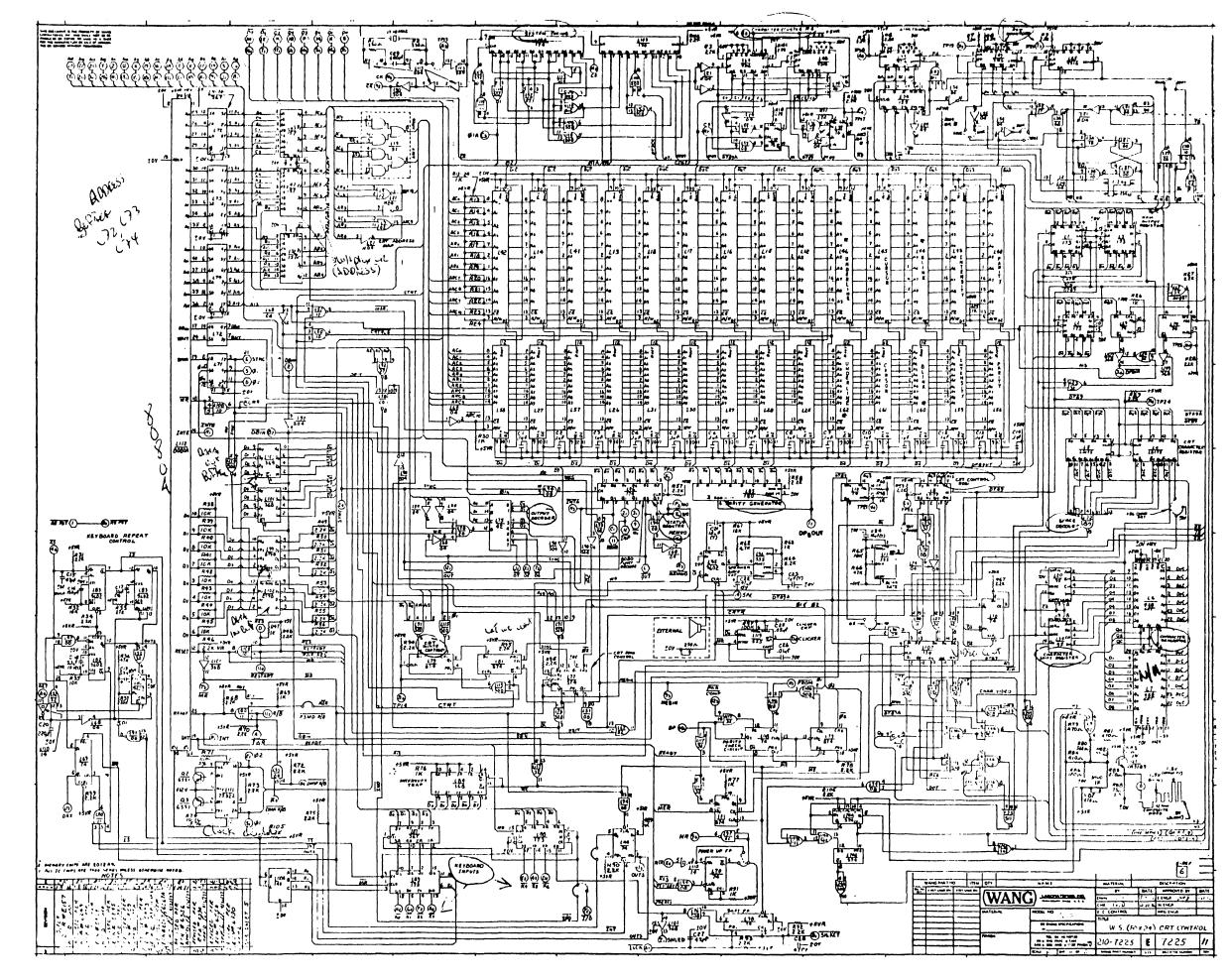

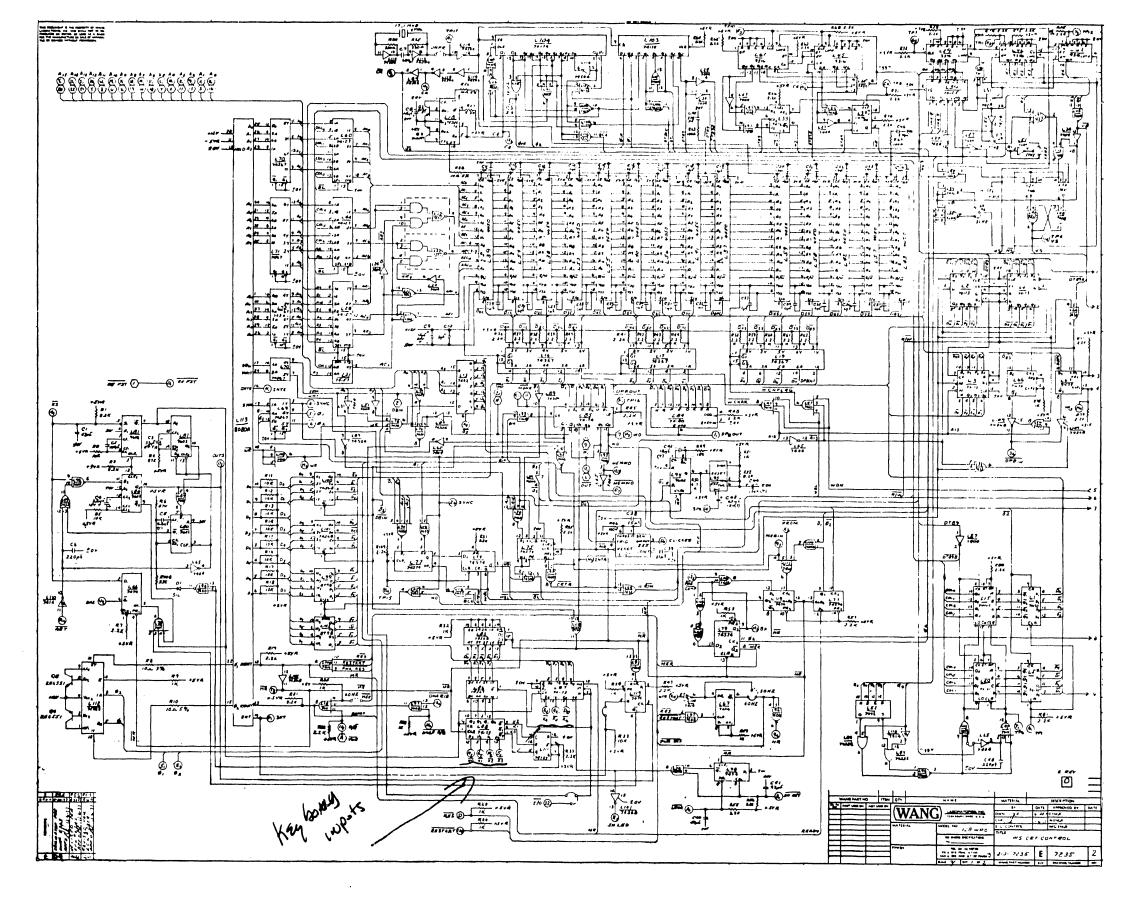

|             | Sheet 1 3-23                                             |

|             | Sheet 2 3-24                                             |

|             | Sheet 3 3-25                                             |

| 3-9         | Sheet 4 3-26                                             |

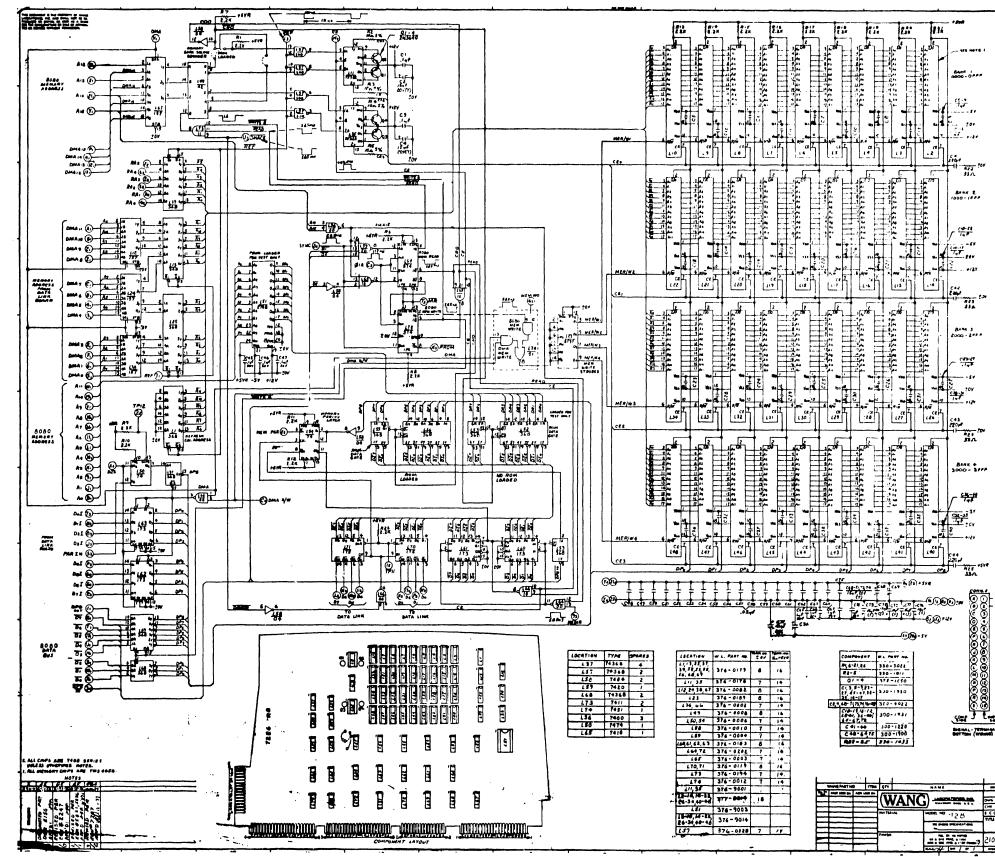

| 3-9<br>3-10 | Workstation Memory-Block Diagram 3-28                    |

| -           | Workstation Memory-Schematic Illustration 3-33           |

| 3-11        | Workstation Data Link-Block Diagram 3-35                 |

| 3-12        | Workstation Data Link-Timing Diagram                     |

| 3-13        | Workstation Data Link-Schematic Illustration             |

|             | Sheet 1 3-48                                             |

|             | Sheet 2 3-49                                             |

| 3-14        | Workstation Motherboard-Schematic Illustration 3-51      |

| 3-15        | 1260 American Keyboard 3-53                              |

| 3-16        | Workstation Keyboard-Schematic Illustration 3-58         |

| 4-1         | Printer Front Control Panel-Schematic Illustration . 4-2 |

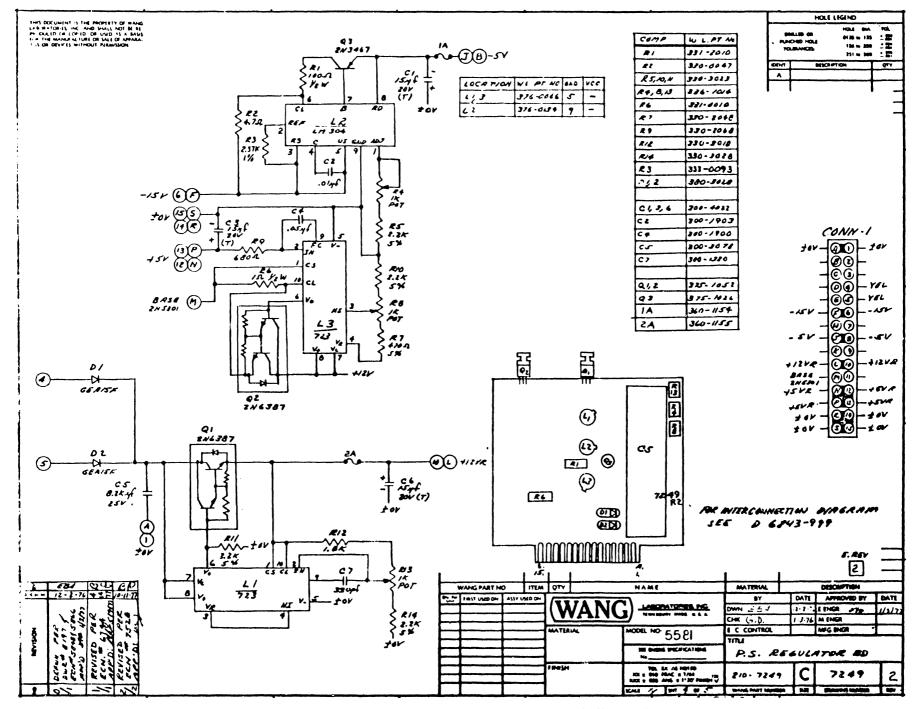

| 4-2         | Printer Power/Supply Regulator Schematic                 |

|             | Illustration 4-4                                         |

| 4-3         | Printer I/O Board-Block Diagram 4-7                      |

| 4-4         | Printer I/O Board-Schematic Illustration                 |

| 4-5         | Printer Memory-Block Diagram                             |

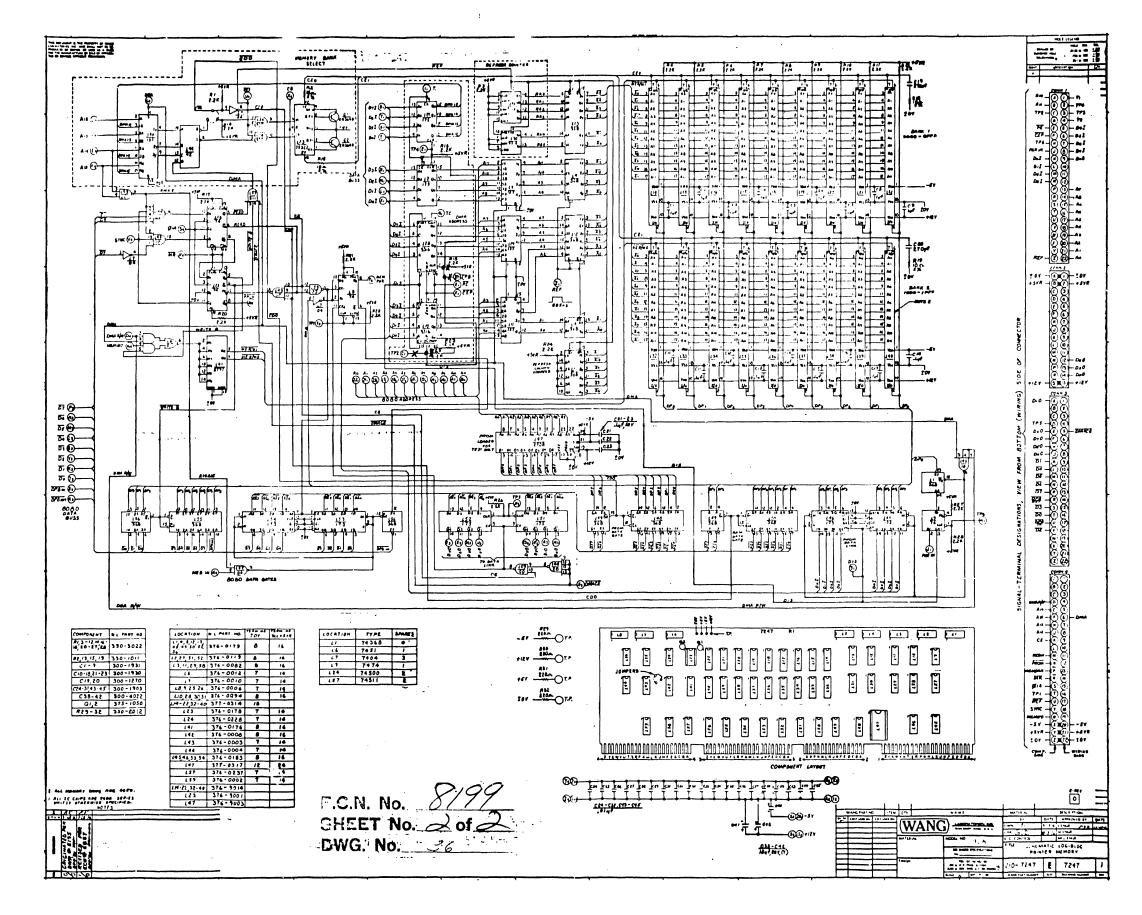

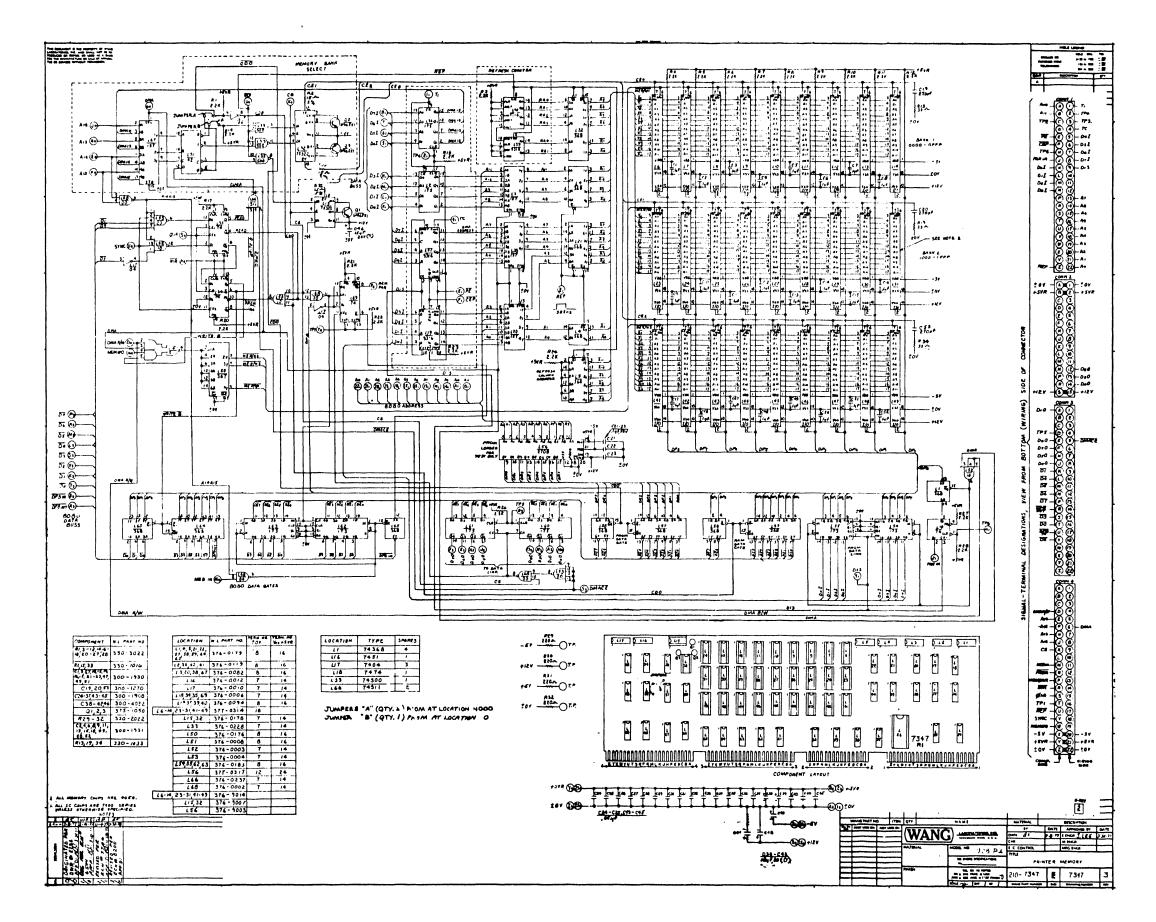

| 4-6         | Printer Memory-Schematic Illustration Sheet 1 4-16       |

|             | Sheet 2 4-17                                             |

| 4-7         | Printer CPU-Block Diagram 4-19                           |

|             |                                                          |

٠

| FIGURE # | TITLE                                         | PAGE |

|----------|-----------------------------------------------|------|

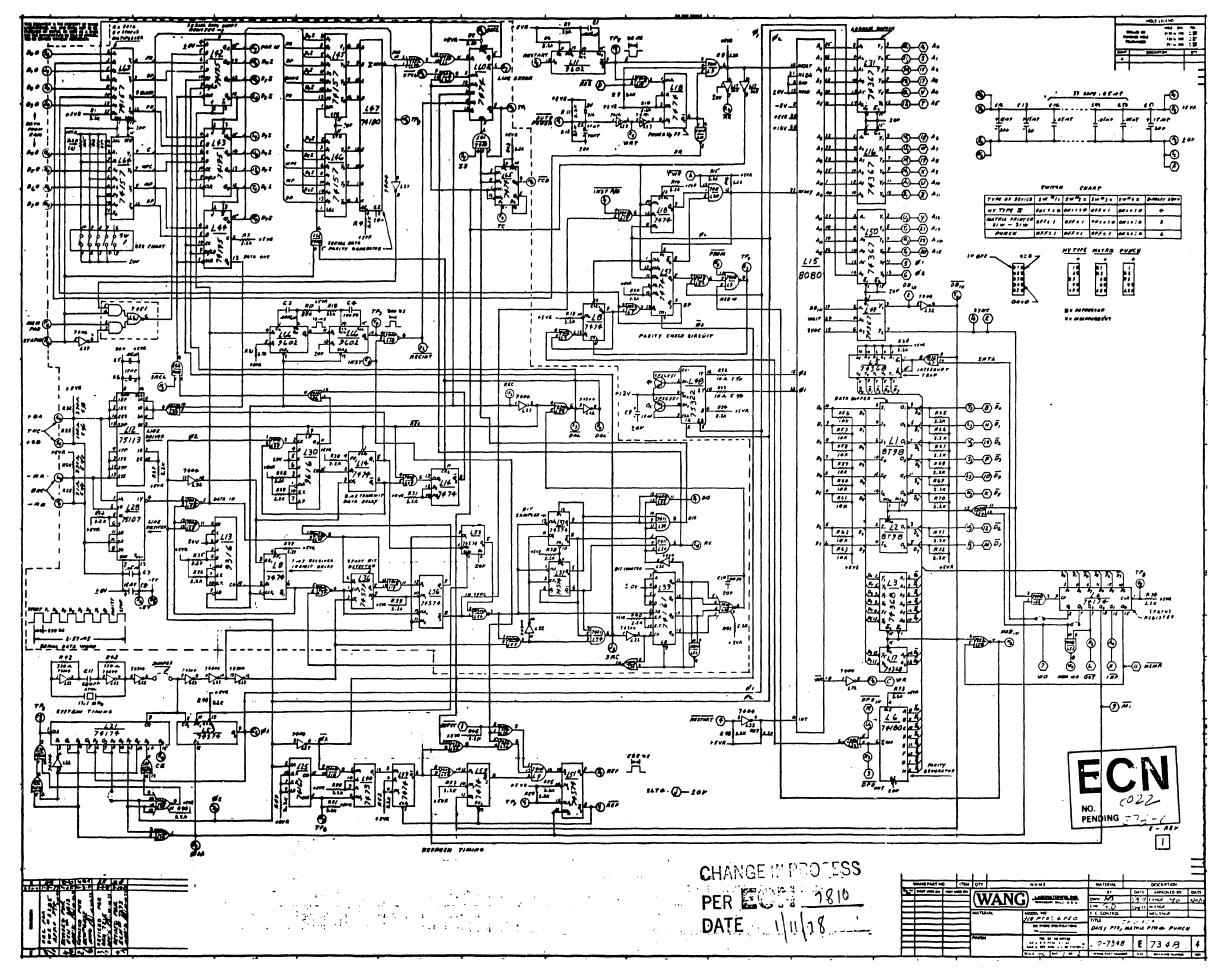

| 4-8      | Printer CPU-Schematic Illustrations Sheet 1   | 4-32 |

|          | Sheet 2                                       |      |

| 5-1      | T.C. Channel System-Block Diagram             | 5-4  |

| 5-2      | T.C. Channel Buses-Block Diagram              |      |

| 5-3      | T.C. CPU-Block Diagram                        |      |

| 5-4      | T.C. CPU-Schematic Illustration               |      |

| 5-5      | T.C. Modem Interface Bus-Block Diagram        |      |

| 5-6      | T.C. Model and ACU Interface-Schematic        | , 23 |

|          | Illustration                                  | 5-31 |

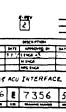

| 5-7      | T.C. Current Loop Interface-Schematic         | 5 51 |

|          | Illustration                                  | 5-32 |

| 5-8      | T.C. Memory-Schematic Illustration            |      |

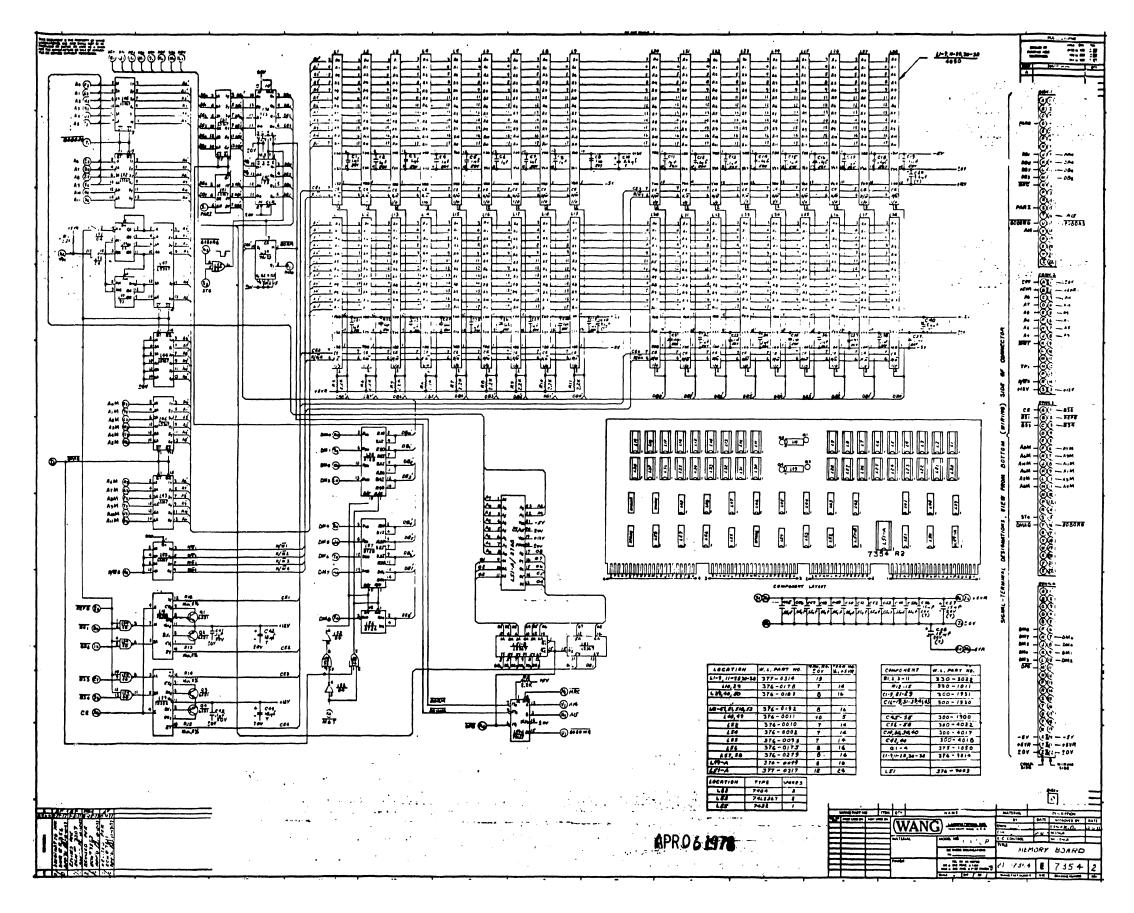

| 5-9      | T.C. Timing Diagrams -                        |      |

|          | 8080 "Cycle Steal" Scheme-Sheet 1             | 5-37 |

|          | 1 Byte Write Tele-Slave-Sheet 2               |      |

|          | IN-STATUS-OP, IN Tele-Slave-Sheet 3           |      |

| 5-10     | T.C. Data Link-Schematic Illustration Sheet 1 |      |

|          | Sheet 2                                       | 5-41 |

|          | Sheet 3                                       | 5-42 |

| 5-11     | T.C. Power Supply Regulator-Schematic         |      |

|          | Illustration                                  | 5-43 |

| 5-12     | T.C. Motherboard-Schematic Illustration       |      |

#### vii

TABLES

| TABLE | TITLE                                           | PAGE |

|-------|-------------------------------------------------|------|

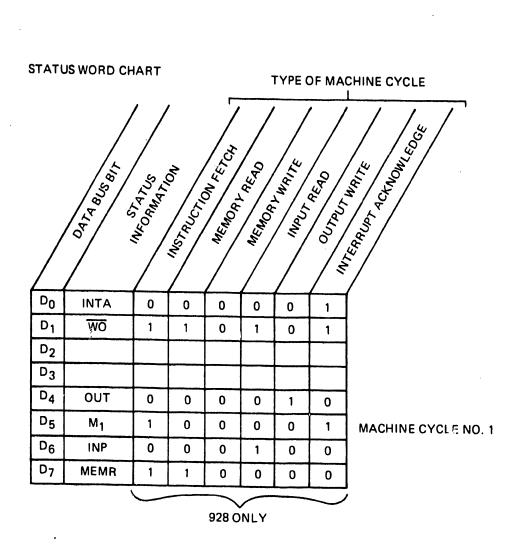

| 2-1   | 8080 Status Words and Definitions               | 2-20 |

| 2-2   | Input/Output Commands-Master CPU                |      |

| 2-3   | Header Bytes                                    | 2-44 |

| 3-1   | Input/Output Commands-Workstation               | 3-19 |

| 3-2   | Header Instruction Byte Description-Workstation | 3-37 |

| 3-3   | Translation Table-External to Internal Keycode  |      |

| 3-4   | 1260 Internal Keycode-(ASCII) Character Values  |      |

| 3-5   | Abbreviations-(Re: Table 3-4)                   |      |

| 3-6   | Special Screen Graphics                         | 3-57 |

| 4-1   | Processor IN/OUT Commands-Printer               |      |

| 5-1   | Clock Rate Selection Code-T.C                   |      |

| 5-2   | Data Link Board Mnemonics (7353)-T.C            |      |

#### APPENDICES

| APPENDIX | TITLE                | PAGE |

|----------|----------------------|------|

| A        | MNEMONIC CODE        | A-1  |

| В        | GLOSSARY             | B-1  |

| C        | RELATED PUBLICATIONS | C-1  |

| D        | R7 PROM FLOW DIAGRAM | D-1  |

# SECTION INTRO-DUCTION

#### SECTION 1 INTRODUCTION

#### 1.1 SCOPE

This preliminary maintenance manual is Volume 3, the last of three initial volumes planned for publication on Wang Model 928 Word Processing Systems 10, 20 and 30.

The contents of each volume will include the subject matter as listed below.

#### VOLUME I

A basic Service Manual that includes System Installation, Operation, Simplified Theory of Operation including block diagrams, system diagnostics and aspects of servicing and compatibility of system software and sub-units. This document will be made available to all service personnel.

#### VOLUME II

Will contain a complete set of schematics, ECNs, Bill of Materials (BOM), Mnemonics listings, Furniture, etc. This document will be made available to all service personnel.

#### VOLUME III

Detailed Theory of Operation for all 928 WP systems. This document will be distributed to Area, District and Subsidiary service offices. Copies will be available from Area offices to interested service personnel only on a request basis. 1.2 PURPOSE

The purpose of this volume is to provide a system theory of operation for interested field personnel. Its intended use is directed to those individuals which may now be able to direct field repairs of equipment which had heretofore been returned to the factory. This volume provides a ready reference to more fully understand the 928 system of operation.

1.3 DESCRIPTION

For purposes of this volume, the 928 word processing system has been divided into four major subdivisions as follows:

A. Master - (CPU, Storage, Floppy Disk, Hard Disk)

B. Workstation - (CRT, Keyboard)

C. Printer - (Daisy)

D. Options - (Matrix Printer, PIO, T.C., etc.)

The 10A, 20 and 30 systems are composed of various combinations of the above listed subdivisions.

The information contained in this volume is primarily concerned with the detailed theory of operation via the printed circuit boards used in the subdivisions mentioned above.

The theory is presented at the chip/component level.

Each subdivision is considered a separate information area within itself; i.e., all PCBs of Master, all PCBs of Workstation, all PCBs of Printer, Options (varied selection).

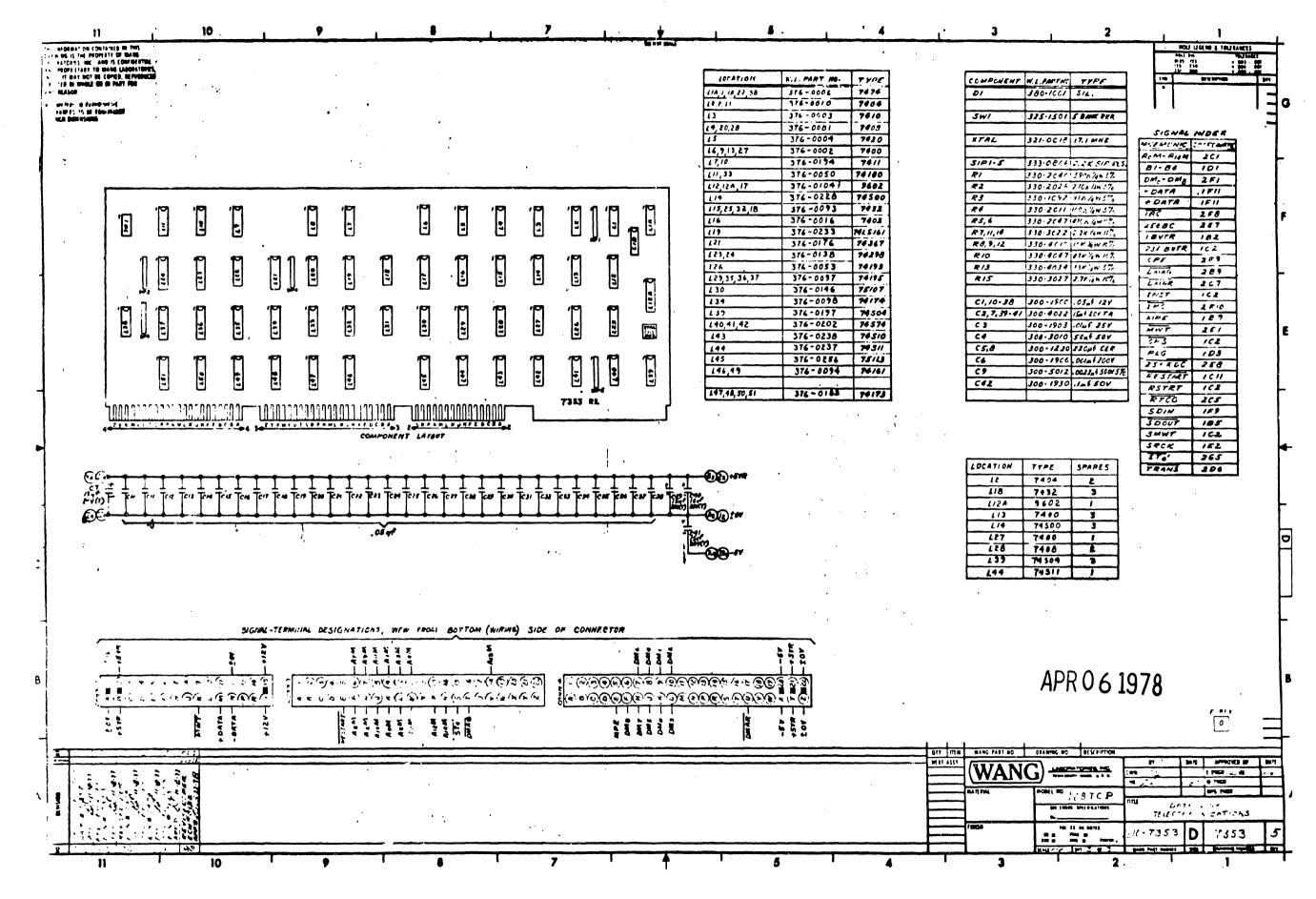

The topics of discussion (the PCBs) within each subdivision are arranged in numerical sequence according to the PCB part numbers within that section; e.g., Subdivision=Section 2=Master, the first topic is Master Memory (PCB  $\frac{#7201}{}$ ), the second topic is Master CPU (PCB 7202), the third topic is Master Disk Controller (PCB 7203), etc.

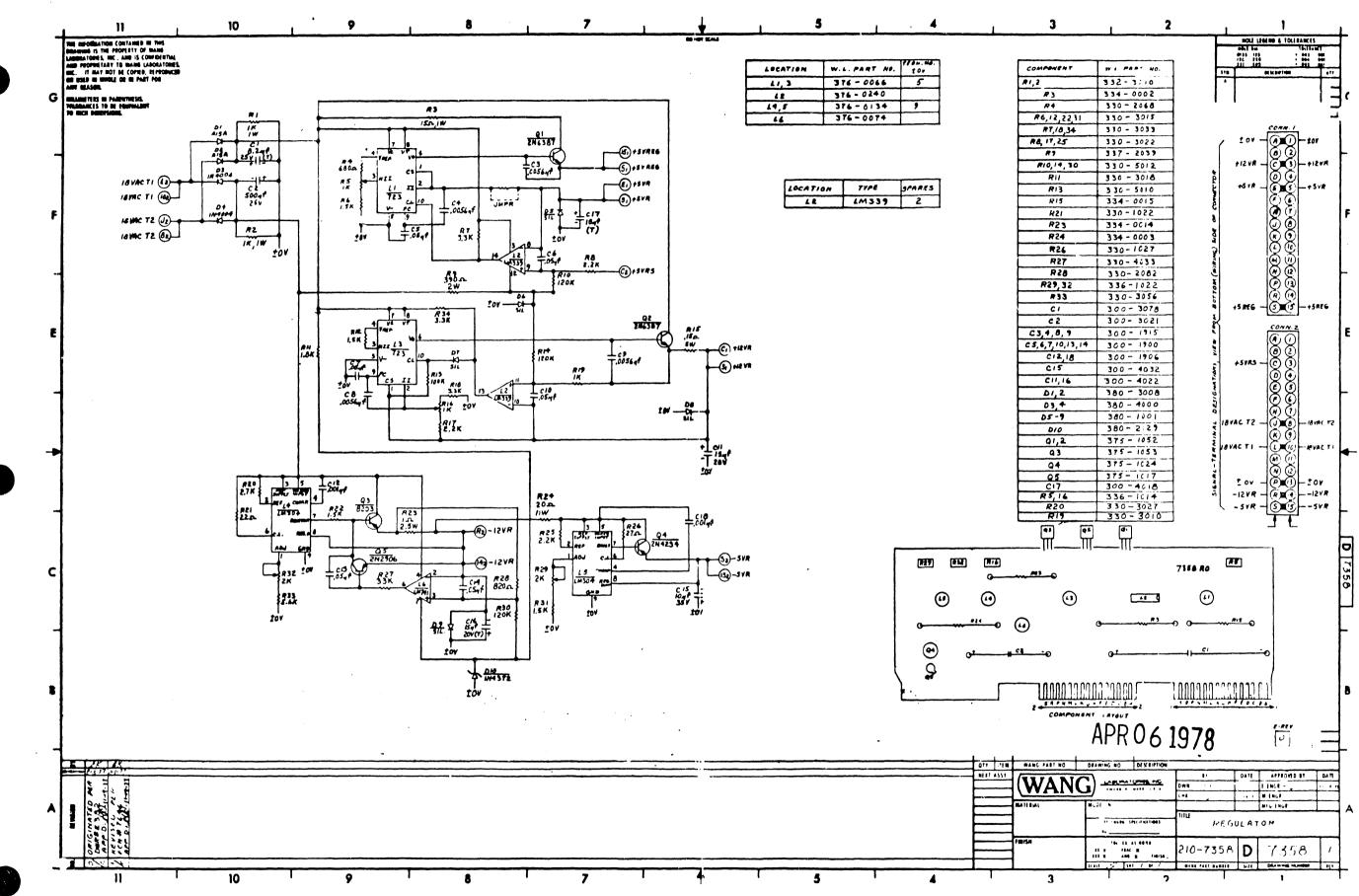

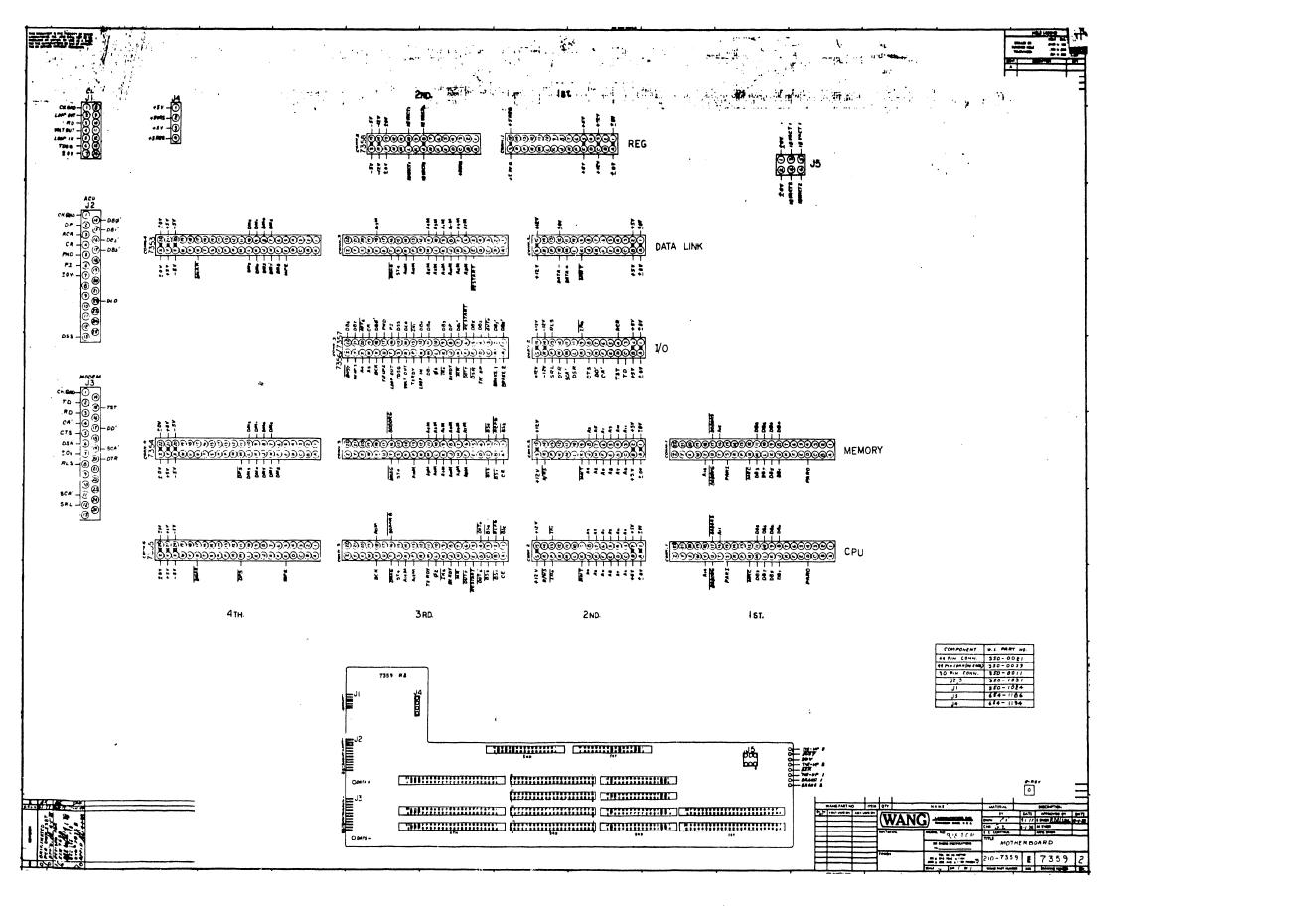

For common PCBs, such as power supplies/regulators and motherboards, only a brief statement and the schematic are provided.

If this volume is read from front cover to rear cover, it may be noticed that there are some information areas which appear repetitive. However, it is the basic philosophy of this volume to enable an individual to refer to any part for reference and information. Therefore, relative situations occur to many independent operations but this relatively must be expressed each time in order to fully explain the operation; hence the appearance of repetitive operations - (relative situations common to many opeations).

The following questions and subsequent answers can locate specific areas within this volume.

Which major subdivision do I wish to examine (choice of 4 areas)?

Once in the appropriate subdivision, which board do I wish to examine (paragraphs are numbered sequentially in relation to the PCB part number)?

What illustrations are available to me? (Each major paragraph has as a minimum the board schematics at the end of the paragraph. In most cases a block diagram and timing diagram are available at the beginning of each section - usually as the 2nd and 3rd page of that section.)

Are the appendices of any aid to me? (appendices, located at rear of volume contain relevant text/table material)

#### 1.4 BLOCK DIAGRAMS

Block diagrams are provided for each printed circuit board discussed in detail. The text of this volume is written directly to the block diagrams and schematics. The block diagram for each PCB gives a ready reference of operation and direct general tie-in to the schematic.

The block diagrams can be readily referenced to a specific page by examining the list of illustrations located in the front matter at the beginning of this volume.

#### 1.5 TIMING DIAGRAMS

In most cases, an overall timing diagram has been provided at the beginning of each major subdivision (usually as the 2nd or 3rd page of the section). For the Wang options subdivision, the timing diagrams are contained within the major paragraph being discussed. In some instances specific timing diagrams have been illustrated within the subparagraphs to permit a closer look at a major operational element.

Timing diagrams can be readily referenced to a specific page by examining the list of illuatrations located in the front matter at the beginning of this volume.

#### 1.6 SCHEMATICS

Schematic illustrations are provided for every printed circuit board. Therefore, in some cases such as power supplies/regulators and motherboards, only a brief statement may exist due to the simplicity of the intended operation. However, a schematic illustration will always be available as the last page(s) of that PCB discussion regardless of descriptive brevity. The schematic illustrations can be readily referenced to a specific page by examining the list of illustrations located in the front matter at the beginning of this volume.

1.7 APPENDICES

As an aid to understanding this theory of operation, four appendices are presented for easy reader reference.

1.7:1 APPENDIX A - Mnemonic Code

All the menmonics used in this volume and on the schematics are presented in Appendix A.

#### 1.7.2 APPENDIX B - Glossary

Because of the moot definitions of many words and phases, a glossary of terms is presented as Appendix B so that the reader will never be in question concerning a specific definition.

1.7.3 APPENDIX C - Related Publications

Where possible reference has been made to those documents which either initially explain on further enhance the contents of this volume; and these relevent publications have been listed in Appendix C.

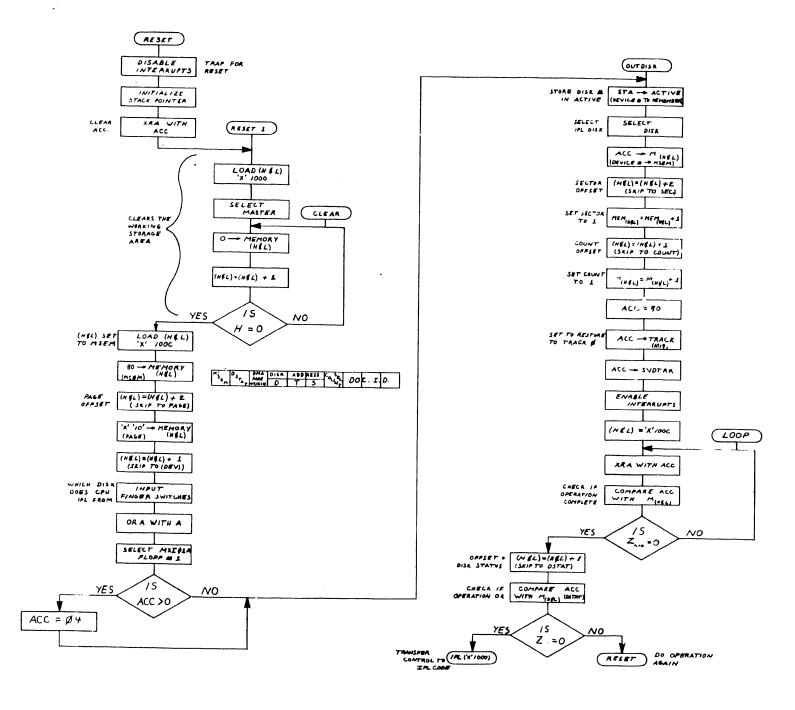

1.7.4 APPENDIX D - R7 Prom Flow Diagram

A flow diagram of the R7 Prom is presented in Appendix D to aid the reader in understanding the basic "start-up" sequence of the system. 1.8 "BARRED"/LOW SIGNALS

For ease of preparation and to aid reading clarity the typical "barred" signal symbol has been replaced by an asterisk.

e.g., SIE ("Barred" Signal) = \*SIE (Asterisk Signal)

## SECTION 2 MASTER THEORY **OF OPERATION**

#### SECTION 2 MASTER THEORY OF OPERATION

2.1 MASTER MEMORY - 7201

2.1.1 GENERAL DESCRIPTION (Figures 2-1 and 2-4)