# VS I/O STRUCTURE AND THE IOP MOTHERBOARD

**Models:**

209-7110 209-7810

### PREFACE

Every I/O interface on a VS 80, 85, 90 or 100 system consists of an IOP Motherboard (IOPMB) as a motherboard and a Device Adapter (DA) as a daughterboard. This manual covers the way in which the operating system and the peripheral device communicate with each other. Information about specific DA daughterboards is not provided here.

There are several other publications related to this document. The <u>VS Data Processing Field Guide</u>, part number 729-1265-A, is a handbook summarizing the operating system information which is covered here in chapter 2. The <u>VS 80 Reference Guide</u>, part number 741-0716, is a handbook containing <u>IOP part numbers</u> for VS 80 machines. The <u>VS Service Handbook</u>, part number 729-1098-A, is a handbook containing part number information for VS 85, 90 and 100 IOPs.

This manual obsoletes 729-0824 and its update 729-0941.

## Proprietary Notice

This document is the property of Wang Laboratories, Inc. Information contained herein is considered company proprietary information and its use is restricted solely to the purpose of assisting you in servicing Wang products. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories.

© Copyright Wang Labs, Inc. 1984

### REVISION STATUS

# DIAGNOSTICS HANDBOOK

# VS I/O STRUCTURE AND THE IOP MOTHERBOARD

| PAGES        | REVISION: DATE  |          |

|--------------|-----------------|----------|

| Front Matter | Original Issue: | 09/23/84 |

| 1-1 to 1-5   | Original Issue: | 09/23/84 |

| 2-1 to 2-17  | Original Issue: | 09/23/84 |

| 3-1 to 3-21  | Original Issue: | 09/23/84 |

| 4-1 to 4-6   | Original Issue: | 09/23/84 |

| A-1          | Original Issue: | 09/23/84 |

| B-1 to B-8   | Original Issue: | 09/23/84 |

# TABLE OF CONTENTS

# VS I/O STRUCTURE AND THE IOP MOTHERBOARD

| Chapter 1  | Overview            | 1-1 |

|------------|---------------------|-----|

| Chapter 2  | I/O Protocol        | 2-1 |

| Chapter 3  | IOPMB Block Diagram | 3-1 |

| Chapter 4  | Interface Control   | 4-1 |

| Appendix A | IOP Instruction Set | A-1 |

| Appendix B | Schematics          | B-1 |

### USER COMMENTS AND FEEDBACK

# VS I/O STRUCURE AND THE IOP MOTHERBOARD 741-0824

Please help us provide the best publication possible by using this comment sheet when you find things you'd like to see corrected, changed or added to this document. Attach copies of the marked-up pages, if possible, and mail to:

WANG LABORATORIES, INC. 437 South Union Street Lawrence, Massachusetts 01843 USA

Attention: Technical Training & Documentation mail stop 8237

| Your Name: |      |

|------------|------|

| Phone:     | RDB: |

| Address:   |      |

|            |      |

| Comments:  |      |

|            |      |

|            |      |

|            |      |

|            |      |

|            |      |

|            |      |

|            |      |

|            |      |

|            |      |

Same .

# CHAPTER 1 OVERVIEW

#### INTRODUCTION

The operating system of a computer is the entity which manages system resources and assigns those resources to the programs and applications running under it. One of the resources controlled by the operating system is the I/O subsystem. The I/O subsystem consists of all the devices attached to the system, of their interfaces and controllers, and of the manner in which they communicate.

This manual was written to help CE understand the the I/O subsystem in both intermediate and large VS systems. It explains the protocol used in communications between the CP and the I/O devices. It also provides an overview of the hardware involved in this information exchange. By discussing both software and hardware issues, this manual attempts to show a complete picture of I/O operations.

- Chapter 1 introduces the manual itself and provides an I/O overview.

- Chapter 2 describes how the operating system communicates with the I/O Processors (IOPs).

- Chapter 3 provides a block diagram description of the IOP Motherboard (IOPMB).

- Chapter 4 describes how the IOPMB communicates via each of its three interfaces.

- Appendix A provides the instruction set used in the PROMs on the IOP.

- Appendix B provides schematics for the two IOPMBs covered by this manual.

# ACRONYMS

The following acronyms are used for elements of the  $\ensuremath{\text{I}}/0$  subsystem of VS machines.

| Acronym | Definition                                        |

|---------|---------------------------------------------------|

| IOPMB   | IOP Motherboard.                                  |

| CIO     | Control I/O instruction (privileged).             |

| CP      | Central Processor.                                |

| CP3     | Central Processor of a VS 80 system.              |

| CP4     | Central Processor of a VS 85, 90 or 100 system.   |

| CP5     | Central Processor of a VS 15, 25 or 45 system.    |

| DA      | Device Adapter.                                   |

| DLI     | Device-Level Interface.                           |

| DLP     | Device-Level Processor, i.e., the microprocessor  |

|         | which is the intelligence of the device itself    |

|         | (often a Z80), not the IOPMB's Microprocessor     |

|         | logic.                                            |

| IOCA    | I/O Command Area or I/O Command Address.          |

| IOCT    | I/O Command Table.                                |

| IOCW    | I/O Command Word.                                 |

| IOP     | I/O Processor, a two-board assembly consisting of |

|         | an IOP Motherboard and a Device Adapter.          |

| IOPMB   | I/O Processor Motherboard.                        |

| IOSW    | I/O Status Word.                                  |

| HIO     | Halt $I/O$ instruction (privileged).              |

| PCB     | Processor Communications Bus.                     |

| SIO     | Start I/O instruction (privileged).               |

| XIO     | Execute I/O instruction.                          |

|         |                                                   |

1-2 741-0824

### IOP FUNCTIONS

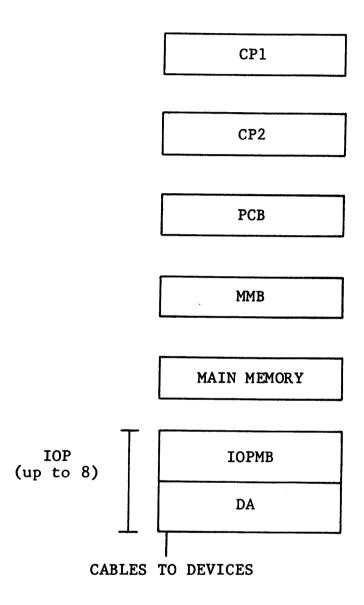

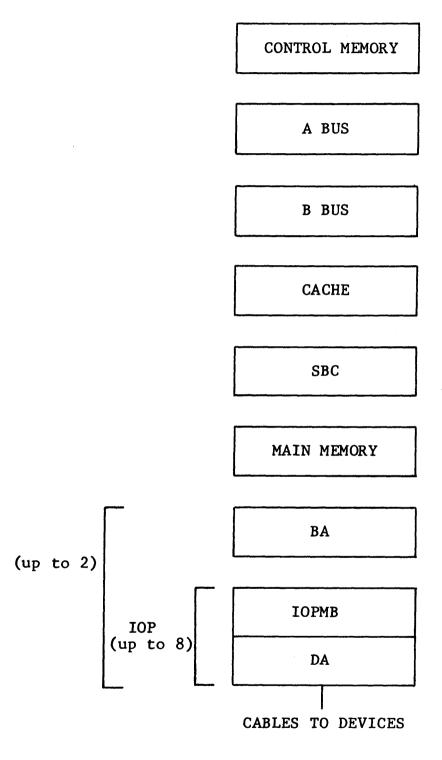

Input/Output Processors are used to control input/output requests to both serial and parallel devices in intermediate and large VS computer systems (VS 80/85/90/100). The position occupied by the IOP in the systems is shown in Figures 1-1 and 1-2.

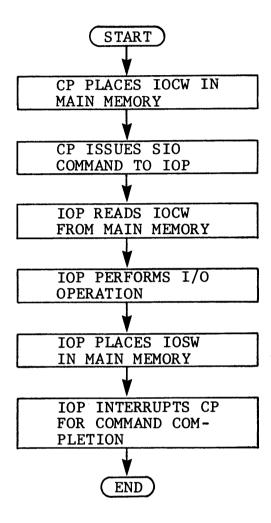

The operating system executing in the central processor (CP) starts an IOP's functions, but, once started, the IOP is able to perform the operation independently of the CP. Meanwhile, the CP places the program requiring I/O on hold and executes some other program. In this manner, the IOP and the CP perform concurrent processing.

Every IOP consists of a IOP Motherboard as a motherboard and a Device Adapter as a daughterboard. The IOPMB interfaces to the system buses and translates CP commands into functions for the DA. The DA furnishes the direct link to any attached devices.

There are two types of motherboards used in IOPs. The first model is the 209-7110 board. The second model is the 209-7810 board.

The difference between IOPMB models is in how many addresses each can handle. Both IOPMB boards handle up to 16 devices. On the 7110 IOPMB, these 16 devices may have only 16 different addresses. On the 7810 IOPMB, however, these 16 devices may have up to 32 addresses. This means that the 7810 may handle devices like archiving workstations which have separate addresses for the floppy disk drive and the workstation itself. The 7110 can handle only regular workstations which do not need a second address.

Figure 1-1 Printed Circuit Boards in a VS 80

Figure 1-2 Printed Circuit Boards in a VS 100

### CHAPTER 2 I/O PROTOCOL

#### **OVERVIEW**

The protocol of the I/O subsystem consists of two things:

- o the format in which commands and responses are communicated and

- o the order in which operations are performed.

This chapter concentrates on the format in which commands and responses are communicated. Chapter 4 discusses the order in which I/O operations are performed.

The protocol established between the VS operating system and the IOPs hinges on the I/O Command Word (IOCW) and the I/O Status Word (IOSW). The CP and all IOPs in the system use the same IOCW/IOSW structure when executing the I/O instructions.

This chapter discusses:

- o the format of the IOCWs,

- o the format of the IOSWs, and

- o the privileged I/O instructions.

#### REFERENCE DOCUMENTATION

- o VS Principles of Operation, part number 800-1100P0-04, describes the SIO, CIO and HIO instructions and the algorithms for memory addressing. (RR addressing is used.)

- o The VS Data Processing Field Guide, part number 729-1265-A, is a small handbook summarizing the operating system.

### IOCW

<u>IOCW Contents:</u> The IOCW is generated by the VS operating system to communicate to the IOP specific information about the requested I/O operation. This information consists of four fields of data. The four data fields are:

- o Command Code: the type of operation to be performed.

- o Data Address: the starting address for main memory data.

- o Data Count Field: the number of bytes of data to be transferred.

- o Device-Dependent Section: various types of information, depending on the device.

| BYTE | 0  | 1      | 2        | 3        | 4      | 5    | 6    | 7        | 8    |

|------|----|--------|----------|----------|--------|------|------|----------|------|

|      | CC | Da<br> | ta Addre | ess<br>I | Data C | ount | Devi | e-Depend | lent |

IOCW Storage: Once the operating system has generated an IOCW, it places the IOCW in main memory. To aid the IOP in locating the IOCW, the operating system then leaves this storage address at another place in main memory. This place is called the I/O Command Area or the I/O Command Address. Both are abbreviated as the IOCA.

The address of this address storage place is known to the IOP involved: it is a function of the device address. The IOP goes to this preliminary address to find the pointer to the actual I/O Command Word. The particular protocol about where to store the storage address depends on the CP in which the operating system is executing.

# DISK IOCW FORMAT

| 0    | 1                                                        | 2         | 3         | 4                                                    | 5                            | 6                    | 7                   | 8    |

|------|----------------------------------------------------------|-----------|-----------|------------------------------------------------------|------------------------------|----------------------|---------------------|------|

| CC   | Da                                                       | ata Addre | ess<br>L  | Data (                                               | Count                        | Se                   | l<br>ctor Addı<br>l | cess |

| Byte | Hex Va                                                   | lue       |           |                                                      | Des                          | cription             |                     | _    |

| 0    | Com                                                      | nand Code | <u>::</u> |                                                      |                              |                      |                     |      |

|      | 00<br>01<br>02<br>04<br>08<br>40<br>80<br>A0<br>C0<br>E0 |           | Data Ado  | le plate<br>addres<br>dress fi<br>s retry<br>gnostic | ssing is<br>ield.<br>on erro |                      | the                 |      |

| 1-3  | Data                                                     | a Address | 3:        |                                                      |                              |                      |                     |      |

|      | 0-5                                                      | 12K       | area. I   | If india<br>is conta                                 | ysical adrect addrains the   | ressing :<br>address | is in<br>of the     |      |

| 4-5  |                                                          | a Count:  | hexadect  | imal),                                               | s to be depends              | on the t             |                     |      |

|      | 100<br>800                                               |           |           |                                                      | , floppy<br>ves, 30/         |                      | g drives            | •    |

| 6-8  | Dev                                                      | ice-Deper | ndent: Se | ector A                                              | ddress                       |                      |                     |      |

|      |                                                          |           |           | from 0                                               | h transfe<br>to maxim<br>k.  |                      |                     |      |

# TAPE IOCW FORMAT

| BYTE | 0   | 1         | 2          | 3                      | 4                    | 5                    |                                                     |

|------|-----|-----------|------------|------------------------|----------------------|----------------------|-----------------------------------------------------|

|      | СС  | Dat       | a Addre    | <br>  S<br>            | Data                 | Count                |                                                     |

| Byte | Hex | k Value   |            |                        |                      | Descript             | tion                                                |

| 0    |     | Command   | Code:      |                        |                      |                      |                                                     |

|      |     | 01        |            |                        |                      |                      | es. Can be                                          |

|      |     | 02        | Se]<br>Ado | lects ind<br>Iress Fie | eld. Car             | dressing             | w.<br>g for Data<br>ed to other                     |

|      |     | 40        |            | lues belo<br>ad data.  | OW •                 |                      |                                                     |

|      |     | 80        |            | ite data.              | •                    |                      |                                                     |

|      |     | CO        |            | ise.                   |                      |                      |                                                     |

|      |     | D0<br>D4  |            | ise.<br>Lte tape       | mark                 |                      |                                                     |

|      |     | D8        |            |                        | ace block            | ζ.                   |                                                     |

|      |     | DC        | For        | ward spa               | ce file.             |                      |                                                     |

|      |     | EO        |            | ind.                   |                      |                      |                                                     |

|      |     | E4<br>E8  |            | vind and               |                      |                      |                                                     |

|      |     | EC        | Bac<br>Rac | k space                | file                 |                      |                                                     |

|      |     | FO        |            |                        | Set densi            | tv high              |                                                     |

|      |     |           |            |                        | PE mode              |                      |                                                     |

|      |     | F4        |            |                        | Set densi            |                      |                                                     |

|      |     | 70        | <u>Tel</u> | <u>ex:</u> Set         | NRZI mo              |                      |                                                     |

|      |     | F8        | Ker        | nedy: Set              | Set parit<br>GCR mod | y odd.               |                                                     |

|      |     | FC        | Ker        | nedy: S                | Set parit<br>drive-s | y even.              | mode.                                               |

| 1-3  | 1   | Data Add  | ress:      |                        |                      |                      | •                                                   |

|      |     | 0-512K    | are<br>use | ea. If i<br>e, this c  | indirect<br>contains | addressi<br>the addr | ss of data<br>ing is in<br>cess of the<br>ess List. |

| 4-5  | ;   | Data Cou  | nt:        |                        |                      |                      |                                                     |

|      |     |           | Nun        | ber of b               | ytes to              | be trans             | sferred.                                            |

| 6-8  | i   | Device-De | ependent   | : Not u                | sed for              | tapes.               |                                                     |

### SERIAL IOCW FORMATS

| BYTE | 0  | 1 | 2             | 3       | 4      | 5         | 6    | 7        | 8    |

|------|----|---|---------------|---------|--------|-----------|------|----------|------|

|      | сс | D | <br>ata Addre | ess<br> | Data ( | Count<br> | Devi | e-Depend | dent |

Description

| 0 | Command Code:  |

|---|----------------|

| U | dominana dode. |

Hex Value

Interpretation of this area by the IOP depends on whether it is passed to the IOP under an SIO or a CIO instruction. The two possibilities are listed separately below.

### 0 for SIO:

Byte

| 40 | Read data from the device.             |

|----|----------------------------------------|

| 44 | Read the tab settings.                 |

| 48 | Read the diagnostic code.              |

| 4C | 7810 IOPs: Interrogate.                |

| 50 | Read altered.                          |

| 80 | Write data to the device.              |

| 84 | Write the tab settings.                |

| 90 | Write selected.                        |

| CO | Control device. When this command is   |

|    | issued, the rest of the IOCW is passed |

|    | on to the device for use as an immedi- |

|    | ate operand. Do not use any DMA oper-  |

|    | ations when using the CO option.       |

## 0 for CIO:

| 40 | Read the Device Routing Table from the Device-Level Processor to main mem- |

|----|----------------------------------------------------------------------------|

|    | ory. 1024 bytes total.                                                     |

|    |                                                                            |

| 60 | Read the device's microcode.                                               |

| 80 | Load the Device Configuration Table                                        |

|    | from main memory into the Device-Level                                     |

|    | Processor. 64 bytes total.                                                 |

| 90 | Load the Device-Level Processor micro-                                     |

|    | code. This microcode resides not on                                        |

|    | the IOP but in the peripheral itself.                                      |

| A0 | Load device microcode.                                                     |

| A8 | Read the Device Routing Table from the                                     |

|    | Device-Level Processor to main mem-                                        |

|    | ory. 1024 bytes total.                                                     |

|    | ory. 1024 byccb cotar.                                                     |

| Byte    | Hex Value            | Description                                                                                                                                                                                                                            |

|---------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 Comma | nd Code for CI       | O, continued:                                                                                                                                                                                                                          |

|         | CO<br>DO<br>EO<br>FO | Reinitialize the Device-Level Process-<br>or and restart the IOP.<br>Restart the Device-Level Processor.<br>Restart the Device Processor.<br>Control resources.                                                                        |

| 1-3     | Data Address         | <u>s:</u>                                                                                                                                                                                                                              |

|         | 0-512K               | Main memory physical address of data area. If indirect addressing is in use, this contains the address of the start of the Indirect Address List.                                                                                      |

| 4-5     | Data Count:          |                                                                                                                                                                                                                                        |

|         |                      | Size of the valid data buffer for this I/O request. The device is allowed an unlimited number of accesses to this buffer. The only requirement is that it stay within the boundaries defined by this field and the Data Address field. |

| 6-8     | Device-Deper         | ndent:                                                                                                                                                                                                                                 |

|         |                      | mands: passed unaltered to device. Can anything desired.                                                                                                                                                                               |

For CIO commands: Device RAM Address.

#### IOSW

IOSW Contents: The IOP generates an IOSW to communicate to the CP the outcome of the I/O operation. Each IOSW can have up to 8 bytes of information. This information consists of five fields of data as follows:

- o General Status Byte: indicates whether the operation was successfully completed or if a hard or soft error occured.

- o Error Status Byte: indicates the type of error which occured.

- o <u>Device-Dependent Status Bytes:</u> vary according to device type.

- o Residual Byte Count: tells the operating system how much of the job remained to be done at the time the IOSW was logged.

- o Device-Dependent Extension: varies both in length and in meaning by device type.

| BYTE | 0  | 1  | 2  | 3       | 4    | 5     | 6      | 7       |

|------|----|----|----|---------|------|-------|--------|---------|

|      | GS | ES | Di | DS<br>I | Byte | Count | Dev-De | p. Ext. |

IOSW Storage: Once the operation is complete, the IOP stores the IOSW in main memory. The address at which it is stored depends on the type of CP in which the operating system is executing.

For a CP3-based system, the IOSW is written into main memory beginning at location 0000 0000.

For a CP4-based system, the IOSW is written into an operating system table. Then, as soon as the IOP notifies the operating system that the operation is completed, the operating system re-writes this IOSW into location 0000 0000.

# DISK IOSW FORMAT

| BYTE | 0   | 1                                      | 2     | 3                                                                                                                                          | 4                                                          | 5                                              | 6                                  | 7        |

|------|-----|----------------------------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|------------------------------------------------|------------------------------------|----------|

|      | GS  | ES                                     |       | DDS<br>L                                                                                                                                   | Byte                                                       | <br> <br> <br>                                 | Retry                              | Info.    |

| Byte | Нех | . Value                                |       |                                                                                                                                            |                                                            | Descrip                                        | tion                               |          |

| 0    |     | General                                | Statu | s:                                                                                                                                         |                                                            |                                                |                                    |          |

|      |     | 80<br>40<br>20<br>10<br>08<br>04, 02,  | 01    | IRQ: Intervolves NC: Normal of EC: Error Colored and EC are of EV and EC are of EV and EC: Unsolicity PC: IOP/DLP Reserved for ing system. | completiompletiset, a C is se ted int                      | ion. on. When soft erro t, the en errupt. ady. | n both NO<br>or occure<br>cror was | ed.<br>a |

| 1    |     | Error St                               | atus: |                                                                                                                                            |                                                            |                                                |                                    |          |

|      |     | 80<br>40<br>20<br>10<br>08             | 01    | IC: Invalid MPE: Memory MAE: Memory DM: Device DAM: Device damaged. Reserved for ing system.                                               | parity<br>addres<br>malfunc<br>memory                      | error. s error. tion. error, o                 |                                    |          |

| 2-3  |     | Device-D                               | epend | ent Status 1                                                                                                                               | Informa                                                    | tion:                                          |                                    |          |

| 2    |     | 80<br>40<br>20<br>10<br>08<br>04<br>02 |       | HDF: Header HDS: Header DIA: Diagnos OPT: Optimiz IDA: Invalio IDC: Invalio SO: Sector o SI: Seek inc                                      | skippe<br>stic mo<br>zation<br>d disk<br>d data<br>overrun | d.<br>de.<br>was used.<br>address.<br>count.   |                                    |          |

Disk IOSW Formats continued

| Byte | Hex Value                                                | Description                                                                                                                                                                                                                            |

|------|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2-3  | Device-Depe                                              | ndent Status Information continued                                                                                                                                                                                                     |

| 3    | 80<br>40<br>20<br>10<br>08<br>04<br>02                   | WP: Write-protected. NRO: Disk not ready. ST: Sector time-out. DCE: Data compare error. HDE: Header check. CRC: Cyclical redundancy check. O: Memory overrun. ISP: Short sector.                                                       |

| 4-5  |                                                          | is an error completion, these two bytes number of bytes of data that remain to                                                                                                                                                         |

| 6    | digit (n) s                                              | describes the retry set-up and second hows the error count.                                                                                                                                                                            |

|      | 0n<br>1n<br>2n<br>3n<br>4n<br>5n<br>6n<br>7n<br>8n<br>9n | Normal.  Data strobe early.  Data strobe late.  Offset minus.  Offset plus.  Data strobe early and offset plus.  Data strobe late and offset plus.  Data strobe early and offset minus.  Data strobe late and offset minus.  ECC used. |

# TAPE IOSW FORMAT

| BYTE | 0                                        | 1                                          | 2                                               | 3                                                                                                                                                                                                                                                                              | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5                                                  | 6                                   | 7                |  |

|------|------------------------------------------|--------------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------|------------------|--|

|      | GS                                       | ES                                         | DD<br>L                                         | S                                                                                                                                                                                                                                                                              | Byte C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ount                                               | Device                              | <br>-Depndnt<br> |  |

| Byte | Hex                                      | Value                                      |                                                 |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Descrip                                            | tion                                |                  |  |

| 0    |                                          | General                                    | Status:                                         |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                     |                  |  |

|      | 80<br>40<br>20<br>10<br>08<br>04, 02, 01 |                                            |                                                 | IRQ: Intervention required. NC: Normal completion. EC: Error Completion. When both NC and EC are set, a soft error occured. When only EC is set, the error was a hard error. U: Unsolicited interrupt. PC: IOP/DLP now ready. Reserved for future use by the operating system. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                     |                  |  |

| 1    |                                          | Error St                                   | atus:                                           |                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                     |                  |  |

|      |                                          | 80<br>40<br>20<br>10<br>08<br>04<br>02, 01 | MPE<br>MAE<br>DM:<br>DAM<br>dama<br>IL:<br>Resa | : Memory : Memory Device : Device aged. Incorre                                                                                                                                                                                                                                | d command y parity y address malfunct e memory ect lengt or future                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | error. error. ion. error, o                        |                                     |                  |  |

| 2-3  | ·                                        | Device-I                                   | ependent                                        | Status                                                                                                                                                                                                                                                                         | Informat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ion:                                               |                                     |                  |  |

| 2    |                                          | 80<br>40<br>20<br>10<br>08<br>04           | LRC:<br>CRC:<br>On v<br>On T                    | : Longit<br>: Cyclic<br>write or<br>read on!<br>DE: Inco                                                                                                                                                                                                                       | cal redunted redunted redunted redunted redunted redunted reduced redu | edundand<br>dancy ch<br>Skew ch<br>Noise bl<br>de. | cy check.<br>neck.<br>neck.<br>ock. |                  |  |

Tape IOSW formats, continued

| Byte | Hex Value                               | Description                                                                                                    |

|------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------|

| 2-3  | Device-Depend                           | dent Status Information continued                                                                              |

| 2    | 02                                      | Kennedy: DS1: Drive type (0 is for 9-track drives and 1 is for 7-track drives). Telex: 0.                      |

|      | 01                                      | Kennedy 7-Track only: DS2: Even Parity. All others: 0.                                                         |

| 1    | 80<br>40*                               | FP: File is write-protected.  Kennedy: DS3: Recording mode (0 is for PE and 1 is for NRZI).  Telex: see below. |

|      | 20*                                     | Kennedy: DS4: Density (0 is for high and 1 is for low). Telex: see below.                                      |

|      | 10                                      | LP: Load point.                                                                                                |

|      | 08                                      | TM: Tape mark detected.                                                                                        |

|      | 04                                      | EOT: End of tape detected.                                                                                     |

|      | 02                                      | O: FIFO overflow or underflow.                                                                                 |

|      | 01                                      | OFF: Offline.                                                                                                  |

|      | <u>*Telex:</u> bits                     | 40 and 20<br>00 PE.<br>01 NRZI.<br>10 GCR.<br>11 Drive selected mode.                                          |

| 4-5  | Residual Byt                            | e Count:                                                                                                       |

|      | When there is contain the be transferre | s an error completion, these two bytes number of bytes of data that remain to ed.                              |

| 6    | Error Retry                             | Count:                                                                                                         |

|      |                                         | mes IOP attempted unsuccessfully to I/O operation normally.                                                    |

| 7    | Reserved for                            | future use of the operating system.                                                                            |

# SERIAL IOSW FORMAT

| BYTE | 0  | 1  | 2  | 3  | 4    | 5     | 6      | 7        |

|------|----|----|----|----|------|-------|--------|----------|

|      | GS | ES | DI | os | Byte | Count | Device | -Depndnt |

| Byte | Hex Value   | Description                                                                                                  |

|------|-------------|--------------------------------------------------------------------------------------------------------------|

| 0    | General Sta | tus:                                                                                                         |

|      | 80          | IRQ: Intervention required.                                                                                  |

|      | 40          | NC: Normal completion.                                                                                       |

|      | 20          | EC: Error Completion.                                                                                        |

|      | 10          | U: Unsolicited interrupt.                                                                                    |

|      | 08          | PC: IOP/DLP now ready.                                                                                       |

|      | 04          | DAR: Data area early released. Means that the page in main memory is now released for use by other programs. |

|      | 02, 01      | Reserved for later use by the operat-<br>ing system.                                                         |

| 1    | Error Statu | <u>s:</u>                                                                                                    |

|      | 80          | IC: Invalid command.                                                                                         |

|      | 40          | MPE: Memory parity error.                                                                                    |

|      | 20          | MAE: Memory address error.                                                                                   |

|      | 10          | DM: Device malfunction.                                                                                      |

|      | 08          | DAM: Device memory error, or device damaged.                                                                 |

|      | 04          | IL: Incorrect length.                                                                                        |

|      | 02          | PP: Peripheral processor (Device-Level                                                                       |

|      | 01          | Processor) needs microcode.<br>DP: Device Processor needs microcode.                                         |

| 2-3  | Device-Depe | ndent Status Information:                                                                                    |

| 2    | All values  | Used by telecommunications controllers as the AID character.                                                 |

# Serial IOSW Formats, continued

| Byte | Hex Value                                                                         | Description                                                                                   |

|------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 3    | Device Infor                                                                      | mation:                                                                                       |

|      | <b>x</b> 0                                                                        | Value of first digit represents device type.                                                  |

|      | Note that the cations cont                                                        | e second digit is zero for telecommuni-rollers.                                               |

|      | 0x                                                                                | For non-TC controllers, the following                                                         |

|      | 01                                                                                | apply: DNR: Device Processor not running or                                                   |

|      | 02                                                                                | halted. IPL requested. DCE: Device cable error.                                               |

|      | 04                                                                                | DPE: Device parity error.                                                                     |

|      | 08                                                                                | DPO: Device is powered-on.                                                                    |

| 4-5  | Residual Byte                                                                     | e Count:                                                                                      |

|      | s an error completion, these two bytes number of bytes of data that remain to ed. |                                                                                               |

|      | In 22V27 SIO<br>byte 4 is 00<br>ing error co                                      | Ps operating in VS 100 machines, if , byte 5 can contain any of the follow-des:               |

|      | 00                                                                                | Invalid BA command.                                                                           |

|      | 01<br>02                                                                          | BCC error.                                                                                    |

|      | 03                                                                                | Memory address error. IOP/BA parity error.                                                    |

| 6-7  | Device-Depend                                                                     | dent: Extended Error Codes                                                                    |

|      | ial controlle                                                                     | lecommunications controllers. For serers, these two bytes pass unaltered IOP and main memory. |

## I/O INSTRUCTIONS

Whenever a program requires I/O, it calls on the operating system using the XIO instruction. It is the operating system which then actually orders the IOP to perform the I/O. The three instructions the operating system uses are privileged, i.e., only the operating system may use these three instructions. This means that the CP must be in supervisor state.

- o Start I/O (SIO) is the privileged instruction which institutes I/O operation.

- o <u>Control I/O (CIO)</u> is the privileged instruction which performs different types of operations with the device's intelligence.

- o <u>Halt I/O (HIO)</u> is the privileged instruction which immediately terminates an I/O operation.

All instructions use the RR addressing capabilities.

2-14 741-0824

#### START I/O

SIO R1

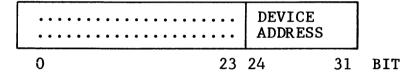

The operating system uses the SIO command to initiate an I/O operation for the I/O device whose address is in Rl. The instruction START I/O is executed only when the system is in the supervisor state.

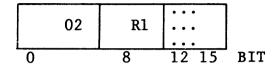

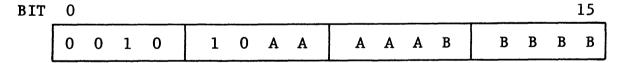

The register specified by Rl contains the I/O device address in the following format.

Before the SIO instruction is issued, the operating system stores the IOCW in memory then loads the pointer to the IOCW at the correct main memory address for the device in question.

After the SIO instruction is issued, the I/O operation will take place provided the addressed device and the IOP are available. Under any of the following conditions, the I/O operation will not take place:

- o The IOP is not connected or operational.

- o The IOP is busy.

- o The device is busy with a previous IOCW.

After the SIO instruction is executed, the operating system cannot change the IOCW until the completion interrupt is received from the IOP.

When the IOP receives the IOCW, it returns a condition code. The various condition codes which can result from this operation are:

- O SIO instruction is accepted by IOP and operation is proceeding.

- 1 The device is busy with a previous operation.

- 2 IOP BUSY is true.

- 3 The IOP is not operational.

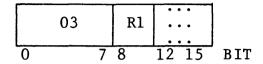

### CONTROL I/O

CIO R1

|   | 0C |   | R1 |       |     |

|---|----|---|----|-------|-----|

|   |    |   |    | • • • | j   |

| 0 |    | 7 | 8  | 12 15 | BIT |

CIO commands the IOP to perform its control function. In most cases, this means that the IOP loads microcode for the Device-Level Processor.

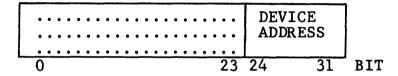

The register specified by Rl contains the I/O device address in the following format.

Before the CIO instruction is issued, the operating system stores the IOCW in memory then loads the pointer to the IOCW at the correct main memory address for the device in question. After the CIO instruction is issued, the I/O operation will take place provided the addressed device and the IOP are available. Under any of the following conditions, the I/O operation will not take place:

- o The IOP is not connected or operational.

- o The IOP is busy.

- o The device is busy with a previous IOCW.

Not all devices support CIO. When issued for a device for which control is not accepted, the O condition code is returned and program execution continues.

The various condition codes which can result from this operation are:

- 0 Means one of two things:

- o CIO instruction is accepted by IOP and operation is proceeding.

- o This device cannot accept a CIO instruction.

- l The device is busy with a previous operation.

- 2 IOP BUSY is true.

- 3 The IOP is not operational.

## HALT I/O

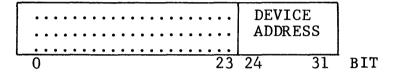

HIO R1

HIO commands the IOP to immediately terminate activities in the addressed device.

The register specified by Rl contains the I/O device address in the following format.

Not all devices support HIO. When issued for a device for which control is not accepted, the O condition code is returned and program execution continues.

HIO clears all interrupts that may be pending for the device. In addition, if any I/O operations are currently going on, HIO terminates them as well. If a current operation is terminated, a completion interrupt will be generated. The IOSW that the IOP places in main memory may or may not have the Error Completion and Incorrect Length bits set to 1.

The various condition codes which can result from this operation are:

- 0 Means one of two things:

- o HIO instruction is accepted by IOP and operation is proceeding.

- o This device cannot support the HIO instruction.

- 1 The device is busy with a previous operation.

- 2 IOP BUSY is true.

- 3 The IOP is not operational.

# CHAPTER 3 IOPMB BLOCK DIAGRAM

### INTRODUCTION

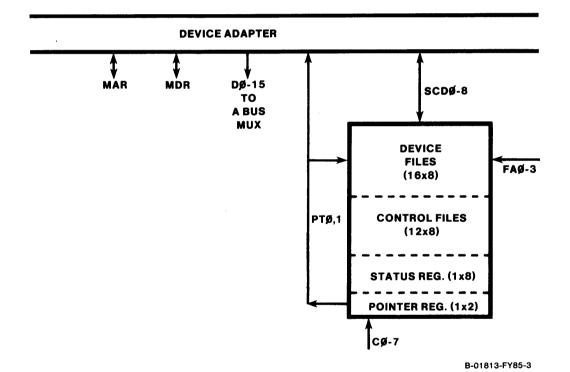

This chapter provides a block diagram of the IOPMB portion of an IOP assembly. The block diagram presents the logic at the functional level. Block diagrams for the DA portion are covered in the pertinent Product Maintenance Manuals.

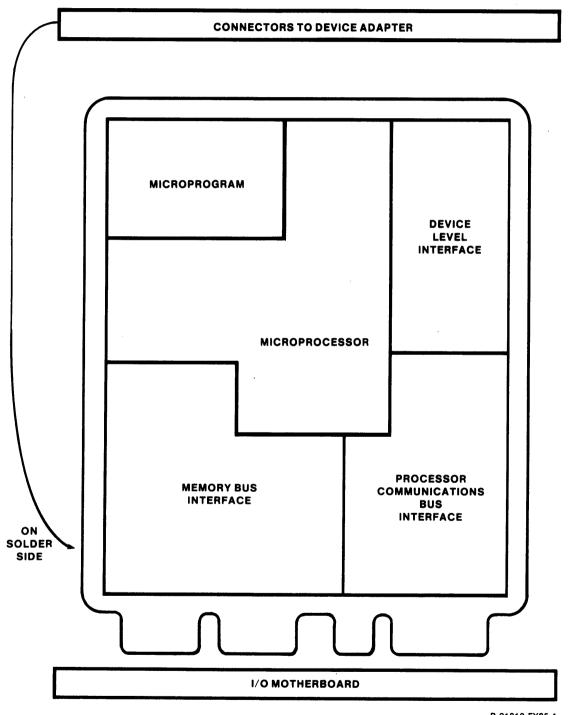

Overall, there are five major functional areas on the IOP Motherboard.

- o Intelligence:

- Microprogram

- Microprocessor

- o Interfaces:

- Memory Bus Interface

- Processor Communications Bus Interface

- Device Level Interface

Figure 3-1 presents a simple view of a IOP Motherboard. Each of these five functional blocks are discussed separately below.

Figure 3-1 Simple Block Diagram of IOPMB

B-01813-FY85-1

#### **MICROPROGRAM**

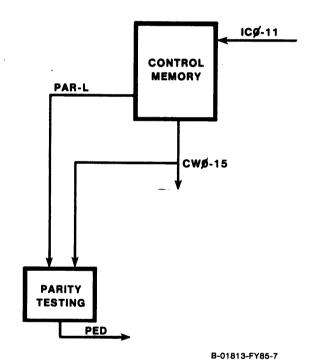

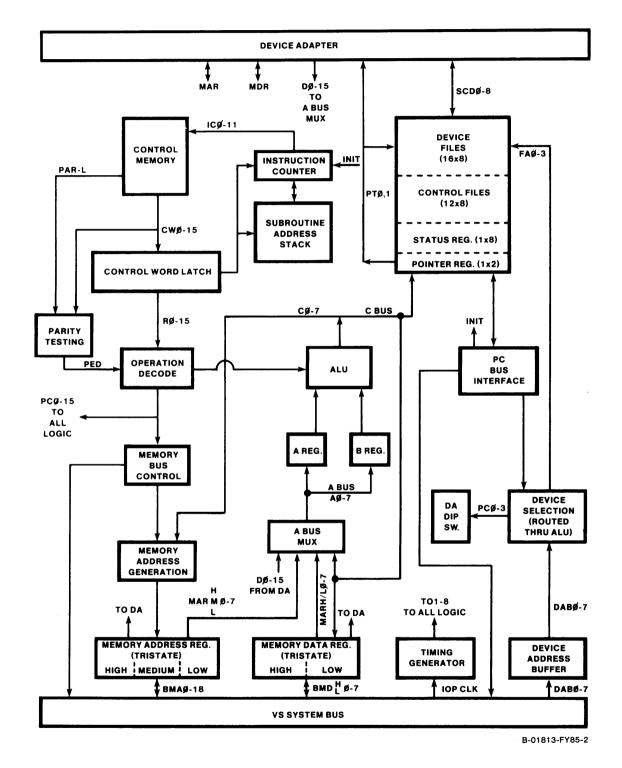

The Microprogram section of the IOPMB is diagrammed in detail in Figure 3-2. This function of the IOPMB consists of the Control Memory which stores the IOPMB microcode and of the Parity Testing Circuit which checks this microcode for errors.

The Control Memory consists of PROMs. The PROMs vary from one IOP to the next. Each set of PROMs contains the particular microcode program which drives the IOPMB for use in a specific environment. One set of PROMs makes the IOPMB run large disks; another set makes the IOPMB run workstations and printers.

Control Memory has 4 kilowords of 16 bits. It is the Microprocessor section which addresses the PROMs and latches the control word output.

The Parity Testing Circuit includes both a parity storage PROM and a parity generation chip. As each control word is read into the Microprocessor section, the parity generator creates the correct parity bit for the word. This bit is then checked against the stored parity bit from the PROM. If the two bits do not match, the Parity Testing Circuit generates an error signal called PED for Parity Error Detect.

Figure 3-2 Microprogram Detailed Block Diagram

3-4 741-0824

#### **MICROPROCESSOR**

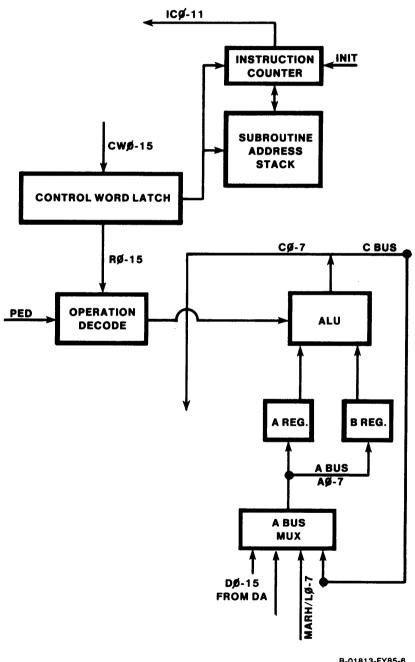

The Microprocessor function of the IOPMB is shown in the detailed block diagram of Figure 3-3. This section consists of the ALU, its input multiplexor and registers, the Control Word Latch, the Instruction Counter, a Subroutine Address Stack and Operation Decode circuitry.

The ALU is 8 bits wide and its multiplexor and registers are also 8 bits wide. The input bus to the ALU is the A bus. The output bus from the ALU is the C bus. Both eight-bit buses are used as board-wide communication paths. Most on-board communication happens via the ALU. Data from one storage area is gated through the ALU to the C bus and on to its destination buffer.

The ALU input multiplexor is called the A Bus Mux. One of its major tunctions is to select which parts of the wider buses will appear on the eight-bit A bus. Its inputs come separately from both the high and low sides of the latches in the Memory Bus Interface and the Device Level Interface.

The Microprocessor stores the current control word instruction in the Control Word Latch. The various bits of this instruction are decoded by the operation decode logic. Outputs of the Operation Decode logic select the ALU's functions and gate with many other signals on the IOPMB board.

To address the instructions in Control Memory, the Micro-processor includes an Instruction Counter. The Instruction Counter can be loaded from the previous control word or from a Subroutine Address Stack. The Subroutine Address Stack stores up to sixteen 12-bit Control Memory addresses. When necessary, the Microprocessor can force a low address into the Instruction Counter so that it can handle an emergency interrupt.

Figure 3-3

Microprocessor Detailed Block Diagram

B-01813-FY85-6

#### MEMORY BUS INTERFACE

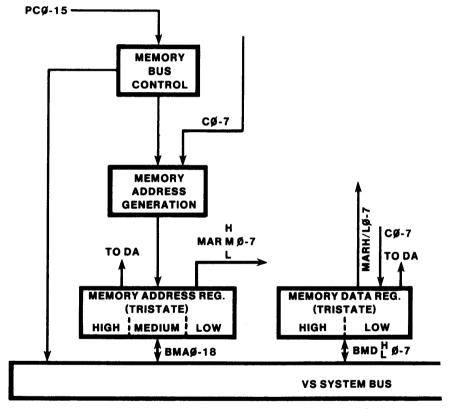

Figure 3-4 presents a detailed block diagram of the Memory Bus Interface of the IOPMB. This interface consists of the buffers for the memory data and address buses as well as memory address generation and memory control signals.

The Memory Data Buffer consists of tristate drivers which can send out data, strobe data in or stay at a high impedance so that other IOPs can drive signals on the bus unhindered. There are two parts to the Memory Data Buffer: one-half stores the low-order byte of data and one-half stores the high-order byte of data. From this buffer, data is bused to all parts of the IOPMB.

One important thing to note about the IOPMB's Memory Bus Interface is that it does not include any large-scale buffering for data en route from the device to main memory. As soon as the IOPMB receives a word of data from the device, it must get access to the memory bus in order to store that data in main memory. The amount of time which the IOPMB can take to clear the Memory Data Buffer before the next word comes from the Device Adapter logic depends on the type of device and on any buffering which may be present in the DA itself.

The Memory Address Buffer consists of tristate drivers which can send addresses out to the bus, strobe addresses in from the bus or stay at a high impedance so that other IOPs can drive signals on the bus unhindered. There are three parts to the Memory Address Buffer: one stores the low-order byte of the address, one stores the middle byte of addresses and the last stores the highest-order three bits.

In all, the IOP handles 19-bit addresses for a 512-kilobyte address space. This is okay for VS 80 machines. In VS 85, 90 or 100 machines, however, there is a maximum of 16 megabytes of memory, all of which is handled by a 24-bit address. In these machines, the BA handles the change from 19-bit to 24-bit addresses.

The Memory Bus Interface includes Memory Address Generation logic. This logic permits the IOP to sequence through all the memory addresses involved in block transfers between main memory and the devices it services. The Memory Address Generation logic can operate incrementally or it can be loaded directly from the ALU.

Figure 3-4

Memory Bus Interface Detailed Block Diagram

B-01813-FY85-5

Table 3-1 Main Memory Bus Interface Signals

| Signal Name | From   | То     | Function                                                                                                    |

|-------------|--------|--------|-------------------------------------------------------------------------------------------------------------|

| BMA0-18     | IOPMB  | Memory | Carry 19-bit main memory physical address.                                                                  |

| MM0-15      | Memory | IOP    | Carry data that has just been read from memory.                                                             |

| BMDH0-7     | IOP    | Memory | Carry the high-order byte of data.                                                                          |

| BMDLO-7     | IOP    | Memory | Carry the low-order byte of data.                                                                           |

| MRI         | IOP    | Memory | Requests use of the memory bus.                                                                             |

| MGS         | Memory | IOP    | Grants use of the memory bus.                                                                               |

| MMCB1-2     | IOP    | Memory | Indicates type of transfer:<br>00 No transfer.<br>01 Read 16 bits.<br>10 Write 16 bits.<br>11 Write 8 bits. |

| MCOS        | Memory | IOP    | Indicates when valid data is on<br>the bus so that the IOP can strobe<br>it into the memory data buffers.   |

| MMP         | Memory | IOP    | Indicates that a parity error oc-<br>cured when main memory was reading<br>the data.                        |

| IMA         | Memory | IOP    | Indicates that the address supplied to memory by the IOP was illegal.                                       |

#### PROCESSOR COMMUNICATIONS BUS INTERFACE

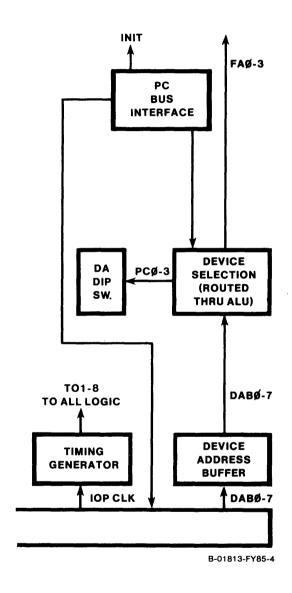

Figure 3-5 shows the Processor Communications Bus Interface. This interface consists of Device Selection Logic and PCB decode & control logic.

The Device Selection Logic determines if the device address on the system bus is the same as the device address range set into the dip switch. It consists of a Device Address Buffer, a dip switch and some routing logic. The system bus uses lines DABO-7 to send the device address out to the IOPs. The IOPMB stores this address in the Device Address Buffer. When the CP sends out the device address, the IOPMB Microprogram responds by comparing the Device Address Buffer to the device address dip switch settings. When the two match, the SEL SIXTN signal is generated.

The PCB decode & control logic looks at the discrete signals on the Processor Communications Bus. It decodes incoming signals to determine if any I/O functions are occuring. It also provides outgoing signal responses when required. It acts in conjunction with the Microprogram which determines the operating status of the IOPMB. Table 3-2 shows the various discrete PCB control signals and their functions.

#### TIMING GENERATOR

The IOP uses a crystal oscillator to produce timing cycles. A single bit is cascaded through the timing generator. This bit becomes, in turn, TO1, TO2, ..., TO8. Under two types of conditions this timing sequence is extended. To access on-board Control Memory, the IOP adds TO9 and a TO10. To access Main Memory, the IOP extends the duration of TO2.

Figure 3-5

Processor Communications Bus Detailed Block Diagram

Table 3-2 PCB Control Signals and Functions

| Signal Na | me From | То  | Function                                                                                                                                                |

|-----------|---------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------|