# **VS-25/45 Computer Systems**

**Customer Engineering Product Maintenance Manual**

741-1032

### PREFACE

This document is the Standard Maintenance (STD) Manual for the VS-25/45 Computer Systems. It is organized in accordance with the approved STD outline established at the Field/Home Office Publications meetings conducted on September 14th and 15th, 1982. The scope of this manual reflects the type of maintenance philosophy selected for this product (swap unit, printed circuit assembly, chip level or any combination thereof).

The purpose of this manual is to provide the Wang-trained Customer Engineer (CE) with instructions to operate, troubleshoot and repair the VS-25/45 Computer Systems. It will be updated on a regular schedule.

The last page before the back cover is a comment sheet. Please take the time to fill out the comment sheet and return it, via the Home Office mail pouch, addressed to:

Wang Laboratories, Inc. Customer Engineering Technical Documentation M/S 8237 437 South Union Street. Lawrence, Mass. 01843-9984

### Fourth Edition (October 1984)

This edition of the VS-25/45 Computer Systems STD manual obsoletes document(s) no. 729-1032-B/B-1. The material in this document may only be used for the purpose stated in the Preface. Updates and/or changes to this document will be published as Product Service Notices (PSN's) or subsequent editions.

This document is the property of Wang Laboratories, Inc. All information contained herein is considered company proprietary, and its use is restricted solely for the purpose of assisting the Wang-trained CE in servicing this Wang product. Reproduction of all or any part of this document is prohibited without the prior consent of Wang Laboratories, Inc.

© Copyright WANG Labs., Inc. 1982, 1983, 1984

# **PUBLICATION UPDATE BULLETIN**

DATE: 02/25/85

This PUB: 741-1032-1 VS-25/45 Computer Systems

Class Code: 6104

Base Document: 741-1032

Previous Notice(s): None

**REASON FOR CHANGE:**

This PUB provides installation, operation, checkout, and troubleshooting instructions for the 2-Megabyte Main Memory Option for the VS-25/45 Computer

\_\_\_\_\_

INSTRUCTIONS:

Remove pages and insert attached pages as follows:

|     | REMOVE        | INSERT        |

|-----|---------------|---------------|

| 1.  | Title Page/ii | Title Page/ii |

| 2.  | xiii/xiv      | xiii/xiv      |

| 3.  |               | Appendix D    |

| 4.  |               |               |

| 5.  |               |               |

| 6.  |               |               |

| 7.  |               |               |

| 8.  | <b>\</b>      |               |

| 9.  |               |               |

| 10. |               |               |

This page is to be used as a permanent record of revisions; place it directly following the title page.

LABORATOR ES INC

ONE INDUSTRIAL AVENUE LOWELL MASSACHUSETTS 01851 TEL (617) 459 5000 TWX 710 343 6769 TELEX 94 7421

# COMPANY PROPRIETARY STATEMENT

This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary, and its use is restricted solely to assisting you in servicing Wang products. Neither this document nor its contents may be disclosed, copied, revealed, or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang Laboratories, Inc.

### **CUSTOMER ENGINEERING**

# **PUBLICATION UPDATE BULLETIN**

DATE: 5/13/85

This PUB: 741-1032-2

Class Code: 6104

Base Document: 741-1032

Previous Notice(s):741-1032-1

REASON FOR CHANGE:

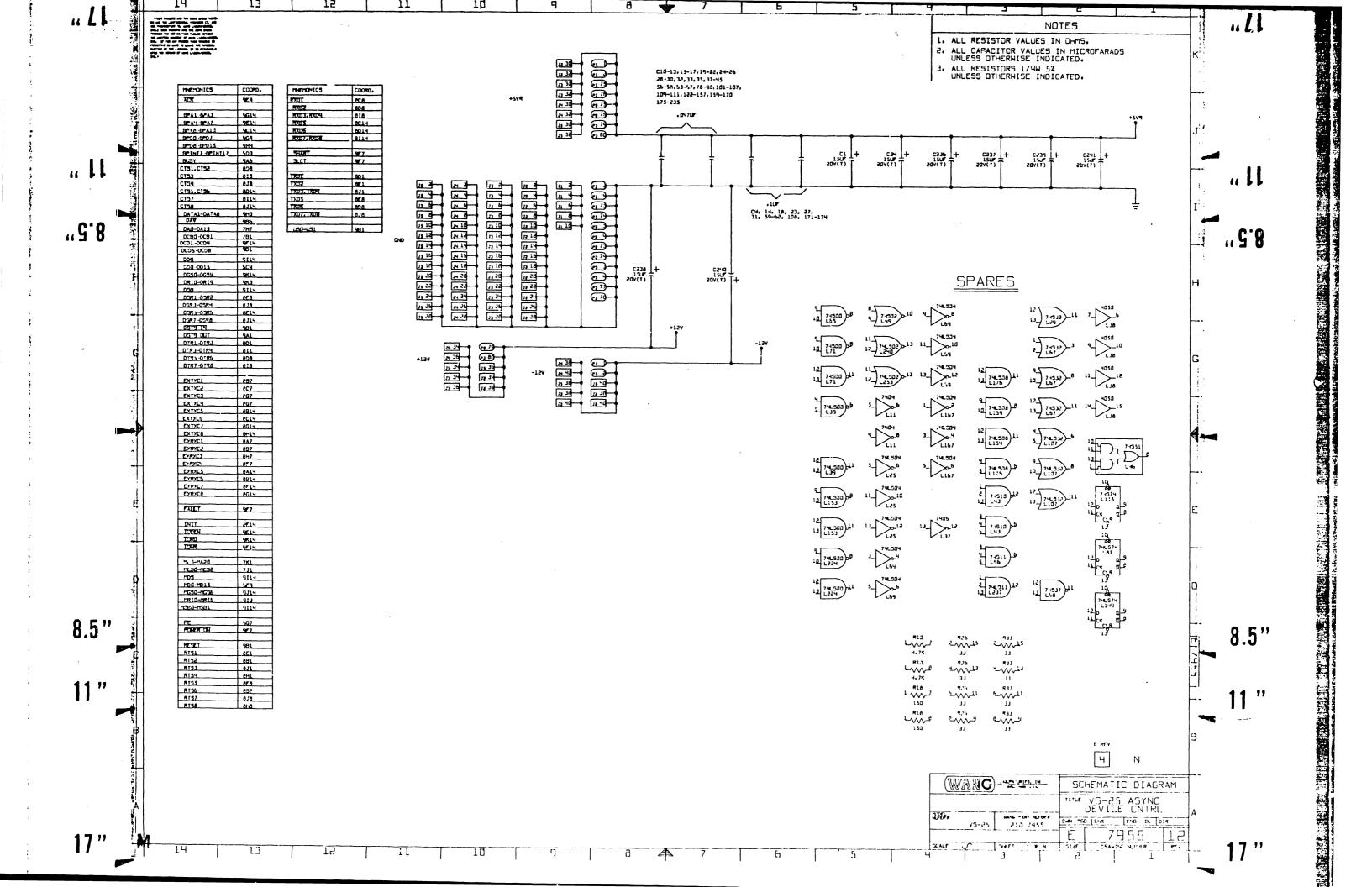

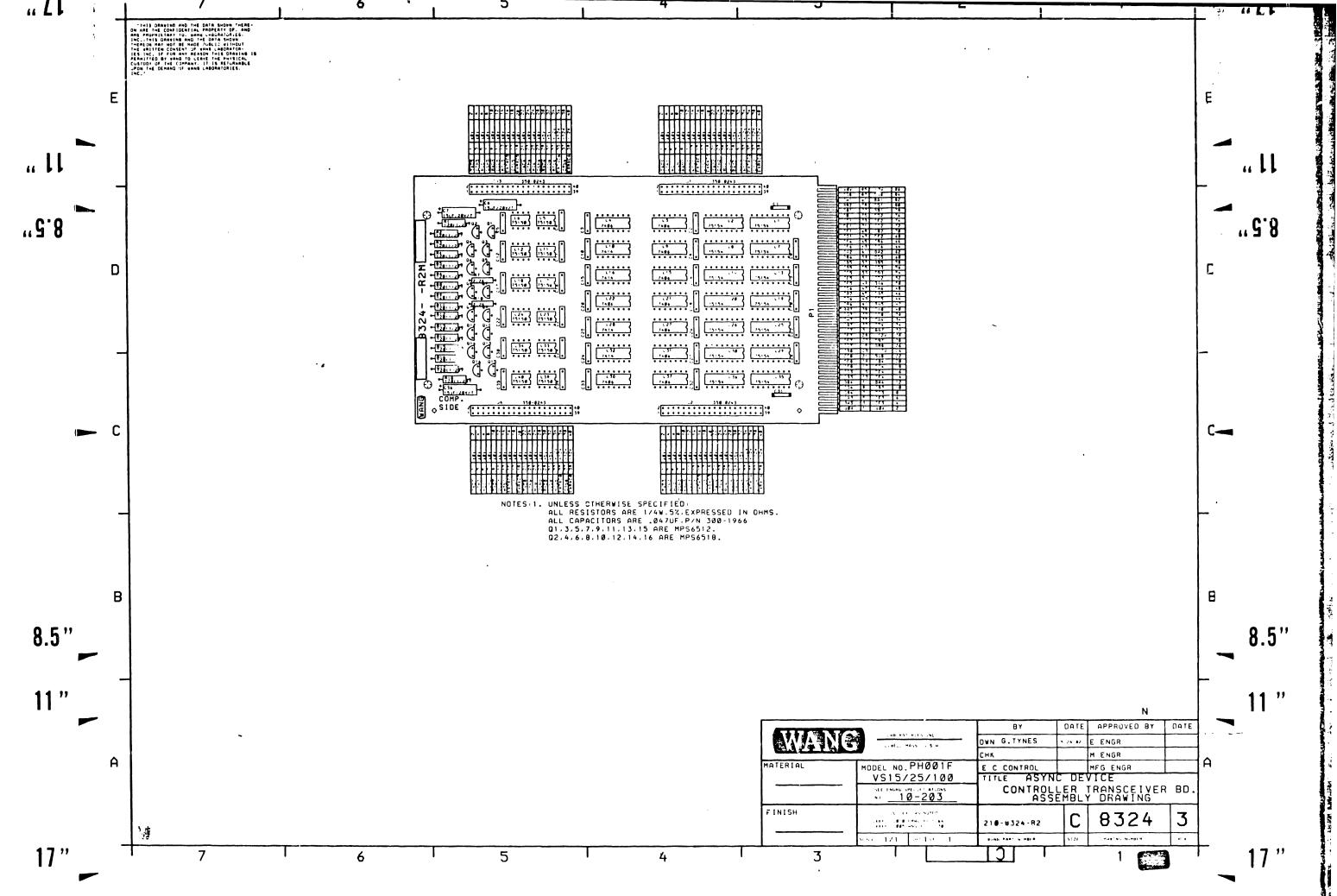

This PUB adds a description of the Async. Controller (Appendix E) to the VS-25/45 Product Maintenance Manual.

INSTRUCTIONS:

Remove pages and insert attached pages as follows:

|     | REMOVE   | INSERT     |

|-----|----------|------------|

| 1.  | xiii/xiv | xiii/xiv   |

| 2.  | Nothing  | Appendix E |

| 3.  | 1        |            |

| 4.  |          |            |

| 5.  |          |            |

| 6.  |          |            |

| 7.  | l.       |            |

| 8.  | 1        |            |

| 9.  | 1        |            |

| 10. |          |            |

This page is to be used as a permanent record of revisions; place it directly following the title page.

WANG

LABORATORIES. INC.

ONE INDUSTRIAL AVENUE, LOWELL. MASSACHUSETTS 01851 TEL (617) 459-5000 TWX 710 343 6769 TELEX 94 7421

# COMPANY PROPRIETARY STATEMENT

This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary, and its use is restricted solely to assisting you in servicing Wang products. Neither this document nor its contents may be disclosed, copied, revealed, or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang Laboratories, Inc.

### **CUSTOMER ENGINEERING**

# **PUBLICATION UPDATE BULLETIN**

DATE: 09/05/85

This PUB: 741-1032-3

Class Code: 6104

Base Document: 741-1032

Previous Notice(s):741-1032-1, 741-1032-2

### **REASON FOR CHANGE.**

Update Chapter 7, Illustrated Parts Breakdown

INSTRUCTIONS:

Remove pages and insert attached pages as follows:

This page constitutes a permanent record of revisions; place it directly following title page.

WANG

LABCRATORIES. INC

**COMPANY CONFIDENTIAL**

PRINTED IN U.S.A.

# COMPANY PROPRIETARY STATEMENT

This document is the property of Wang Laboratories, Inc. All information contained herein is considered Company Proprietary, and its use is restricted solely to assisting you in servicing Wang products. Neither this document nor its contents may be disclosed, copied, revealed, or used in whole or in part for any other purpose without the prior written permission of Wang Laboratories, Inc. This document must be returned upon request of Wang Laboratories, Inc.

### WARNING

| * |                                                       | * |

|---|-------------------------------------------------------|---|

| * | DO NOT OPEN THE SWITCHING POWER SUPPLY UNDER ANY      | * |

| * | CIRCUMSTANCE. EXTREMELY DANGEROUS VOLTAGE AND         | * |

| * | CURRENT LEVELS (IN EXCESS OF 300 VOLTS DC AND UN-     | * |

| * | LIMITED CURRENT) ARE PRESENT WITHIN THE POWER SUPPLY. | * |

| * |                                                       | * |

| * | DO NOT ATTEMP' TO REPAIR THE SWITCHING POWER          | * |

| * | SUPPLY; IT IS FIELD REPLACEABLE ONLY.                 | * |

| * |                                                       | * |

| * | AFTER POWERING THE UNIT DOWN AND DISCONNECTING THE AC | * |

| * | POWER CONNECTOR FROM THE POWER SOURCE RECEPTACLE,     | * |

| * | ALLOW ONE MINUTE BEFORE REMOVING THE POWER SUPPLY TO  | * |

| * | PROVIDE ADEQUATE TIME FOR ANY RESIDUAL VOLTAGE TO     | * |

| * | DRAIN THROUGH THE BLEEDER RESISTORS.                  | * |

| * |                                                       | * |

The last page before the back cover is a comment sheet. Please take the time to fill out the comment sheet and return it, via the Home Office mail pouch, addressed to:

> Wang Laboratories, Inc. Customer Engineering Technical Documentation M/S 8237 437 South Union Street. Lawrence, Mass. 01843-9984

ν

# TABLE OF CONTENTS

| CHAPTER 1  | INTRODUCTION                                  | Page |

|------------|-----------------------------------------------|------|

| 1.1<br>1.2 | Purpose<br>Scope                              | 1-1  |

| 1.3        | Related Publications                          | 1-1  |

| 1.4        | System Description                            | 1-2  |

| l.4.1      | Central Processor                             | 1-4  |

| 1.4.2      | Control Memory                                | 1-5  |

| 1.4.3      | Main Memory                                   | 1_5  |

| 1.4.4      | Bus Processor                                 | 1-5  |

| 1.5        | CPU Motherboard                               | 1-6  |

| 1.6        | Input/Output Device Adapters                  | 1-6  |

| 1.7        | System Diskette Drive                         | 1-8  |

| 1.8        | Front Panel                                   | 1-8  |

| 1.9        | Power Supply                                  | 1-8  |

| 1.10       | Software Description                          | 1-9  |

| 1.10.1     | User Convenience Features                     | 1-10 |

| 1.10.2     | Expanded Operating System Features            | 1-10 |

| 1.10.3     | Additional System Utilities                   | 1-10 |

| 1.10.4     | File Protection and Security                  | 1-12 |

| 1.10.4.1   | File Protection Codes                         | 1-13 |

| 1.10.4.2   | Special Protection Codes                      | 1-13 |

| 1.10.4.3   | User Access Rights                            | 1-13 |

| 1.11       | Error Detection and Correction                | 1-14 |

| 1.12       | Remote Diagnostic Facilities                  | 1-14 |

| 1.13       | Configurations                                | 1-14 |

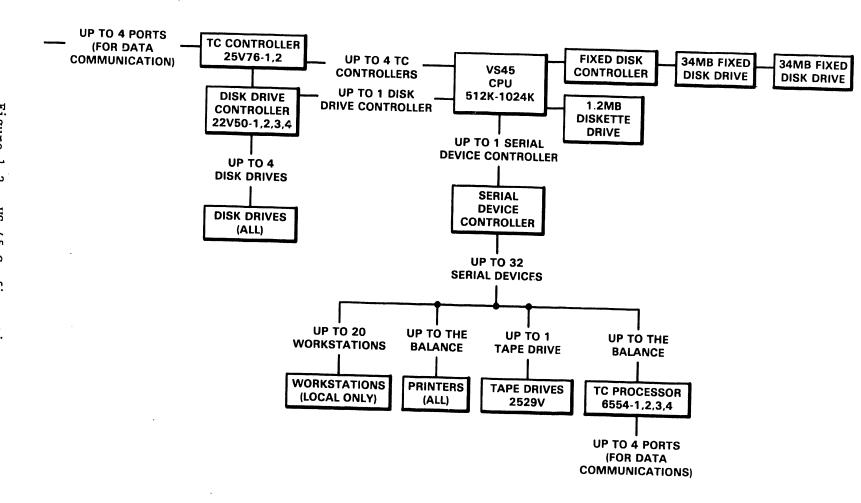

| 1.13.1     | Typical VS-25/45 System-Option Configurations | 1-16 |

| 1.14       | Associated Peripherals                        | 1-19 |

| 1.15       | Telecommunications                            | 1-20 |

| τ•τΟ       | System Specifications                         | 1-20 |

# CHAPTER 2 THEORY OF OPERATION

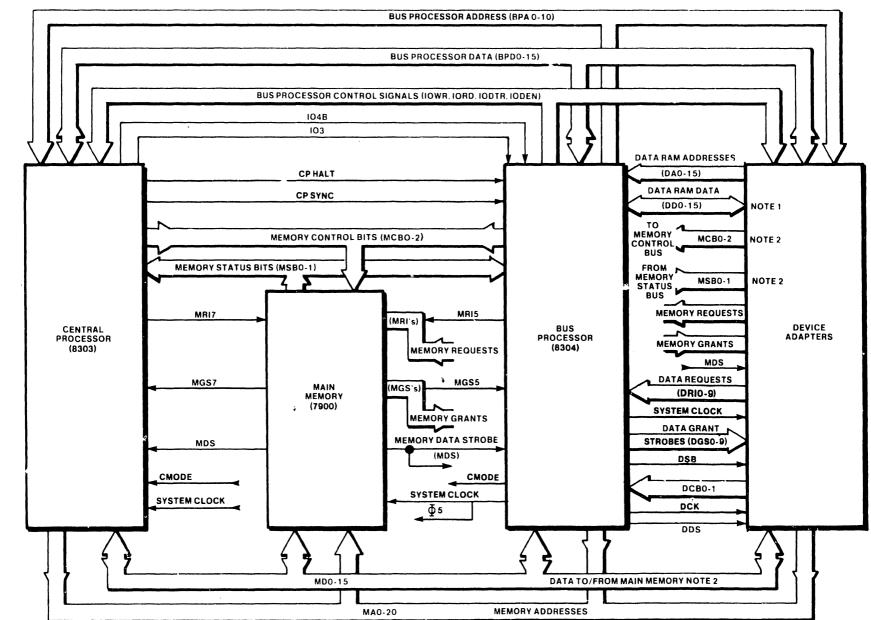

| 2.1     | VS-25/45 Overview 2-1                      |

|---------|--------------------------------------------|

| 2.1.1   | VS-25/45 Main Memory Bus 2-1               |

| 2.1.2   |                                            |

|         | VS-25/45 Bus Processor Bus 2-3             |

| 2.1.3   | VS-25/45 Data RAM Bus 2-4                  |

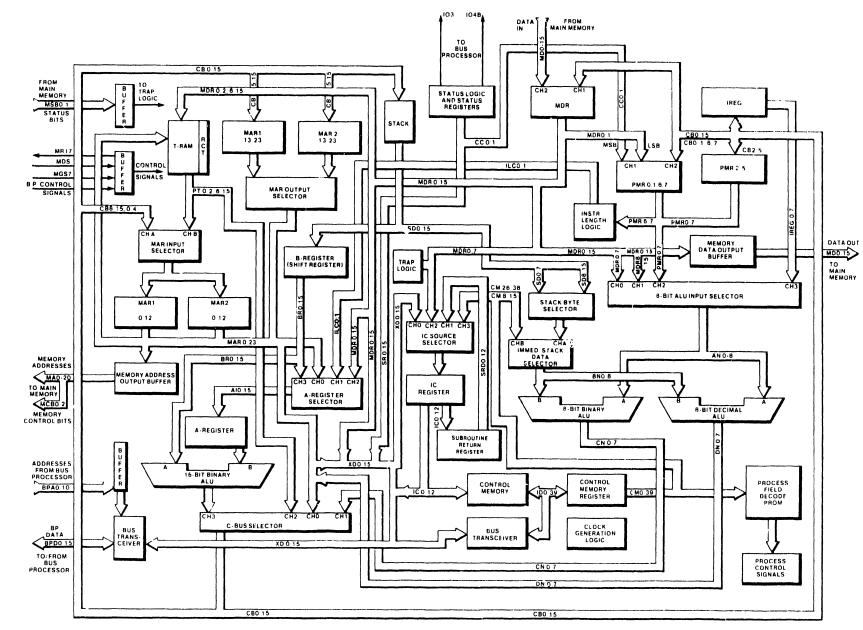

| 2.2     | VS-25/45 Central Processor 2-7             |

| 2.2.1   | CP Control Memory                          |

|         | CP Control Memory 2-7                      |

| 2.2.2   | General CP/Main Memory (MM) Operations 2-7 |

| 2.2.2.1 | Read and Write 2-8                         |

| 2.2.2.2 |                                            |

|         | Translation 2-8                            |

| 2.2.2.3 | Ripple 2-8                                 |

| 2.2.2.4 | Memory Address Registers 2-8               |

| 2.2.2.5      | Main Memory Data                               | 2-9  |

|--------------|------------------------------------------------|------|

| 2.2.3        | CP Address Translation                         |      |

| 2.2.4        | CP Stack                                       |      |

| 2.2.5        | CP Microtraps                                  |      |

| 2.2.6        | CP Status Register                             |      |

| 2.2.7        | General CP Hardware and Logic                  | 2-12 |

| 2.2.7.1      | 8-Bit Binary Arithmetic Logic Unit             |      |

| 2.2.7.2      | 8-Bit Decimal Arithmetic Logic Unit            |      |

| 2.2.7.3      | 16-Bit Binary Arithmetic Logic Unit            |      |

| 2.2.7.4      | Process Field Decoder                          |      |

| 2.2.7.5      | Indirect Register                              |      |

| 2.2.7.6      | Program Mask Register                          | 2-14 |

| 2.2.7.7      | Microinstruction Counter (MIC) Source Selector |      |

| 2.2.7.8      | Microinstruction Counter Register              |      |

| 2.2.7.9      | Subroutine Return Register                     |      |

| 2.2.7.10     | A-Register Source Selector, A-Register,        |      |

|              | and B-Register                                 | 2-15 |

| 2.2.7.11     | 8-Bit ALU Input Selector, Stack Byte Selector, |      |

|              | and Immediate/Stack Data Selector1             | 2-5. |

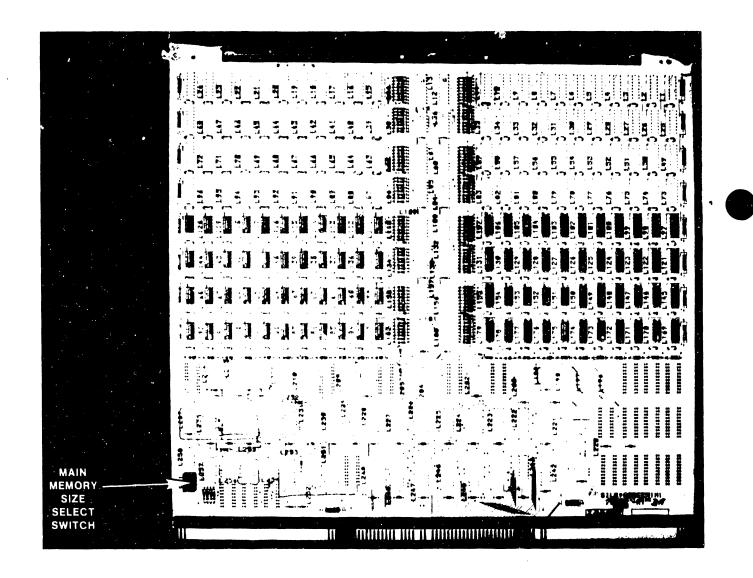

| 2.2.7.12     | System Identification PROM                     |      |

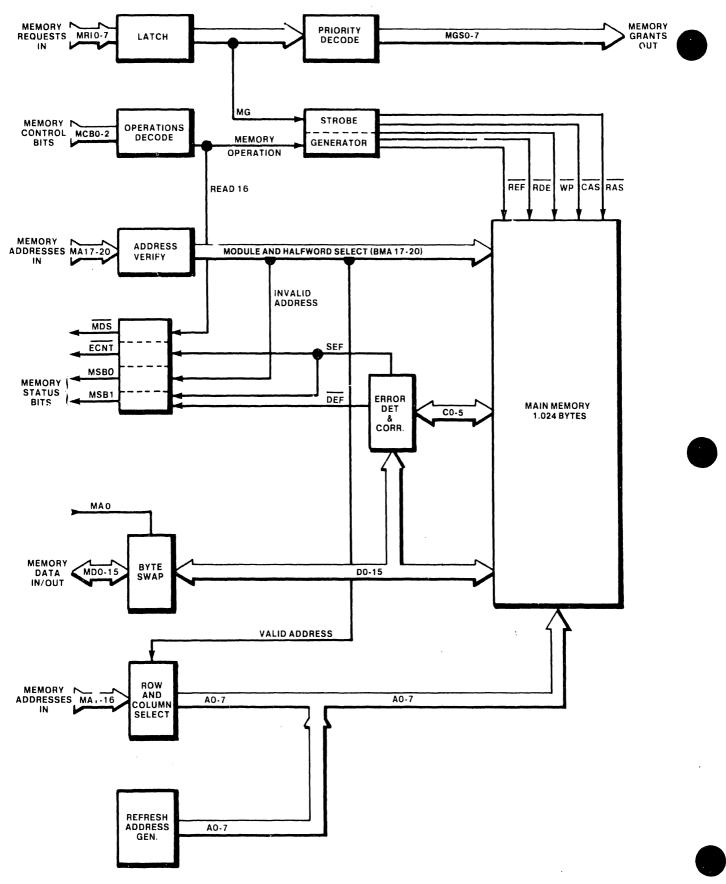

| 2.3          | VS-25/45 Main Memory                           |      |

| 2.3.1        | Main Memory Operations                         |      |

| 2.3.2        | Main Memory Control and Status                 |      |

| 2.3.3        | Main Memory Addressing                         |      |

| 2.3.4        | Main Memory Write                              |      |

| 2.3.5        | Main Memory Read                               |      |

| 2.3.6        | Main Memory Error Detection and Correction     |      |

| 2.3.7        | Main Memory Refresh                            |      |

| 2.4          | VS-25/45 Input/Output Section                  |      |

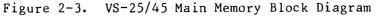

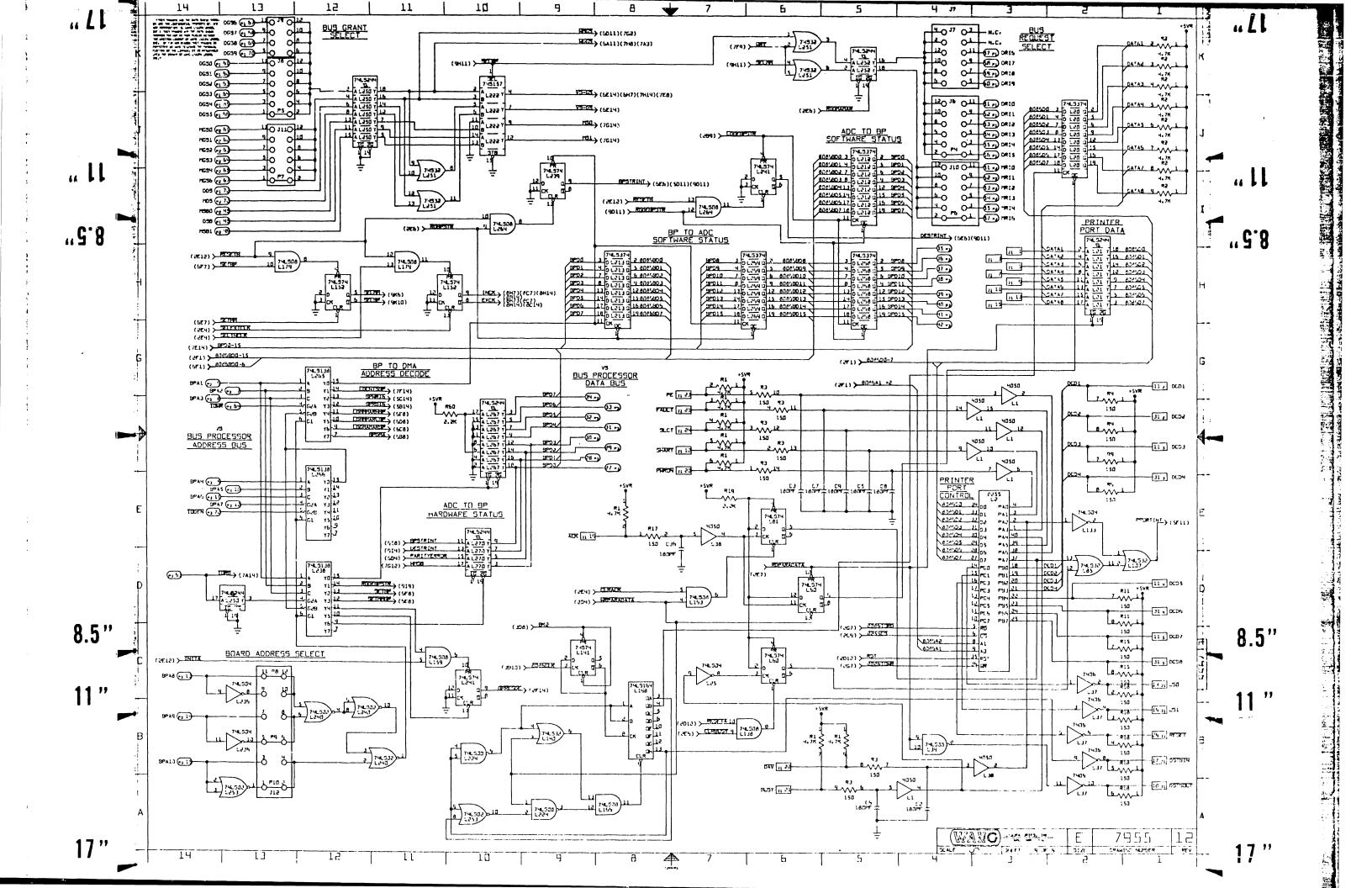

| 2.4.1        | Bus Processor                                  | 2-21 |

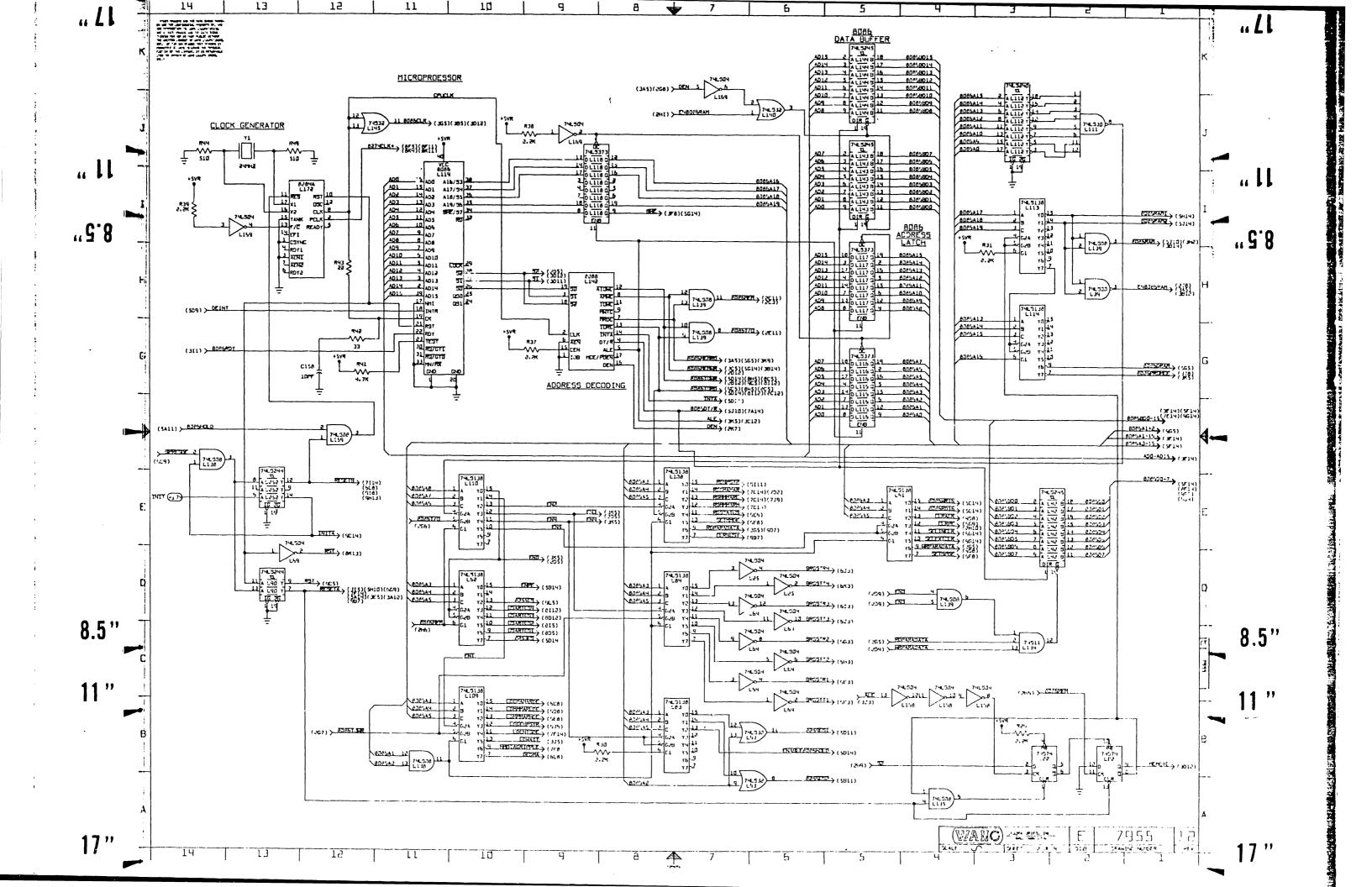

| 2.4.1.1      | BP Microprocessor Control Circuit              | 2-21 |

| 2.4.1.1.1    | BP Control Memory (PROM)                       |      |

| 2.4.1.1.2    | BP Code RAM (CRAM)                             | 2-22 |

| 2.4.1.1.3    | BP Addressing                                  | 2-22 |

| 2.4.1.1.4    | BP RAM Parity                                  | 2-26 |

| 2.4.1.1.5    | BP Status Register                             | 2-27 |

| 2.4.1.1.6    | BP Clock Generation Circuitry                  | 2-28 |

| 2.4.1.1.7    | BP Programmable Interrupt Timers (PITs)        |      |

| 2.4.1.1.8    | BP Battery Backup                              |      |

| 2.4.1.1.9    | BP Time-of-Day (TOD) Clock                     | 2-29 |

| 2.4.1.1.10   | BP Nonvolatile RAM (NVRAM)                     | 2-29 |

| 2.4.1.1.11   | BP Display                                     | 2-29 |

| 2.4.1.1.12   | BP Initialization                              | 2-30 |

| 2.4.1.1.13   | BP Interrupts                                  | 2-30 |

| 2.4.1.1.13.1 | BP/CP Interrupts                               | 2-30 |

,

-

| 2.4.1.1.13.2 | Additional BP Interrupts                    | 2-30 |

|--------------|---------------------------------------------|------|

| 2.4.1.1.14   | BP Wait States                              | 2-31 |

| 2.4.1.1.15   | BP Diagnostic Capabilities                  | 2-32 |

| 2.4.1.1.16   | BP Diagnostic Hardware Latch                | 2-33 |

| 2.4.1.1.17   | BP Software Switches                        | 2-34 |

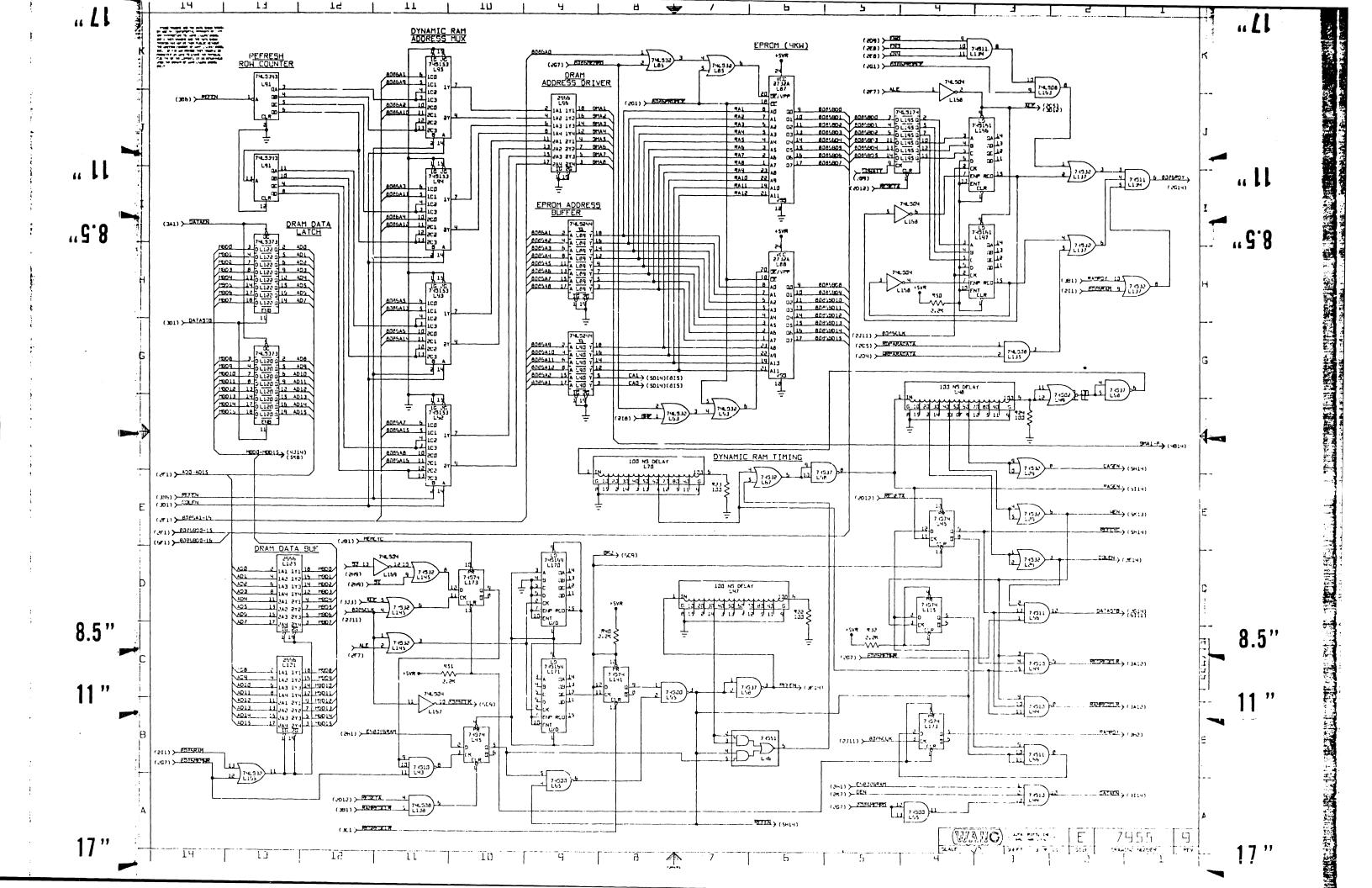

| 2.4.1.2      | BP Data RAM                                 | 2-34 |

| 2.4.1.2.1    | DRAM Control                                | 2-34 |

| 2.4.1.2.2    | DRAM Parity                                 | 2-36 |

| 2.4.1.2.3    | DRAM Timing                                 |      |

| 2.4.1.3      | BP Main Memory Direct Memory Access         | 2-36 |

| 2.4.2        | Floppy Diskette Drive Controller            | 2-36 |

| 2.4.2.1      | Floppy Diskette Drive Controller LSI Chip   | 2-36 |

| 2.4.2.2      | Phase Lock Loop                             | 2-37 |

| 2.4.2.2.1    | Phase/Frequency Detector                    | 2-37 |

| 2.4.2.2.2    | Loop Filter                                 | 2-37 |

| 2.4.2.2.3    | Voltage Controlled Oscillator (VCO)         | 2-39 |

| 2.4.2.3      | LSI-DMA Channel to the DRAM                 | 2-39 |

| 2.4.3        | Remote Diagnostic Telecommunication Channel | 2-39 |

| 2.5          | Serial I/O Device Adapter                   | 2-39 |

| 2.5.1        | SIO DA Data Link                            | 2-39 |

| 2.5.2        | SIO DA Buffering and DMA Path               | 2-40 |

| 2.5.3        | SIO DA Data Transfers                       | 2-40 |

| 2.5.3.1      | Write Dev One-Byte                          | 2-40 |

| 2.5.3.2      | Write Dev 256-bytes                         | 2-41 |

| 2.5.3.3      | Read Dev One-Byte                           | 2-41 |

| 2.5.3.4      | Read Dev 256-bytes                          | 2-42 |

| 2.5.4        | Addicional SIO DA Control Commands          | 2-43 |

| 2.5.4.1      | Restart                                     | 2-43 |

| 2.5.4.2      | Give Status                                 | 2-43 |

| 2.5.5        | SIO DA Data Overrun                         |      |

| 2.6          | Intelligent Serial (ISIO) Input/Output      |      |

|              | Device Adapter                              | 2-45 |

| 2.6.1        | Direct Memory Operations                    | 2-45 |

| 2.6.2        | Master Data Link (MDL)                      | 2-45 |

| 2.7          | Quantum Fixed Disk Drive Input/Output       |      |

|              | Device Adapter                              | 2-47 |

| 2.7.1        | Surface Operations                          | 2-47 |

| 2.7.1.1      | Disk Format                                 | 2-47 |

| 2.7.1.2      | Disk Write                                  |      |

| 2.7.1.3      | Dísk Read                                   |      |

| 2.7.1.4      | Read and Ignore Header                      |      |

| 2.7.1.5      | Verify                                      |      |

| 2.7.1.6      | Diagnostic Write                            |      |

| 2.7.1.7      | Diagnostic Read                             |      |

| 2.7.2        | Error Correction                            | 2-49 |

|              |                                             |      |

| 2.7.3    | Verify FIFO                                  | 2-40 |

|----------|----------------------------------------------|------|

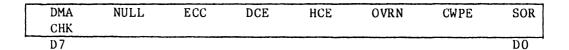

| 2.7.4    | Quantum Status Register                      | 2-49 |

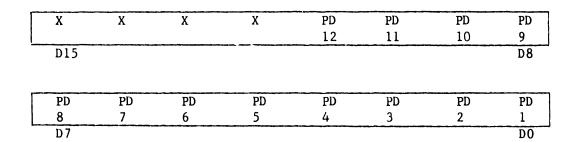

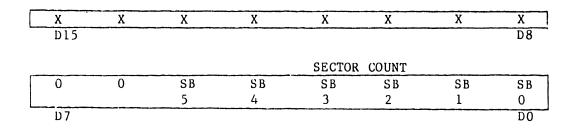

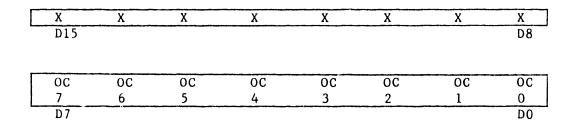

| 2.7.5    | Multisector Operation                        | 2-50 |

| 2.7.6    | Interrupts                                   | 2-50 |

| 2.8      | Storage Module Disk Drive Device Adapter     | 2-51 |

| 2.8.1    | Write Commands                               | 2-51 |

| 2.8.1.1  | Start (HEX 0100)                             | 2-53 |

| 2.8.1.2  | Load Command Register (HEX 0102)             | 2-55 |

| 2.8.1.3  | Load Tag Register (HEX 0104)                 | 2-53 |

| 2.8.1.4  | Load Track/Head Register (HEX 0106)          | 2-55 |

| 2.8.1.5  | Load Write Latch (HEX 0108)                  | 2-30 |

| 2.8.1.6  | Load Operation Counter (HEX 010A)            | 2-57 |

| 2.8.1.7  | Deselect (HEX 010C)                          | 2-57 |

| 2.8.1.8  | Reset (HEX 010E)                             | 2-57 |

| 2.8.1.9  | Set Tag Strobe (HEX 0110)                    | 2-5/ |

| 2.8.1.10 | Load RAM (HEX 0311)                          | 2-30 |

| 2.8.1.11 | Enable Seek End Interrupt (HEX 0114)         | 2-58 |

| 2.8.1.12 | MAR Clock (HEX 0118)                         | 2-60 |

| 2.8.1.13 | Load FIFO (HEX 011A)                         | 2-60 |

| 2.8.1.14 | Diagnostic Clock-1 (HEX 011C)                | 2-60 |

| 2.8.1.15 | Diagnostic Clock-2 (HEX 011C)                | 2-60 |

| 2.8.2    | Read Commands                                | 2-60 |

| 2.8.2.1  | Read Device Code (HEX 0100)                  | 2-61 |

| 2.8.2.2  | Read Disk Status (HEX 0102)                  | 2-61 |

| 2.8.2.3  | Read Operation Status (HEX 0102)             | 2-62 |

| 2.8.2.4  | Read ECC (HEX 0304)                          | 2-03 |

| 2.8.2.5  | Read Disk Type (HEX 0108)                    | 2-64 |

| 2.8.2.6  | Read Data (HEX 010A)                         | 2-65 |

| 2.8.2.7  | Read Sector (HEX 010C)                       | 2-65 |

| 2.8.2.8  | Read Operation Count (HEX 010E)              | 2-05 |

| 2.8.2.9  | Read MARL (HEX 030C)                         | 2-66 |

| 2.8.2.10 | Read MARH (HEX 030E)                         | 2-00 |

| 2.8.2.11 | Read FIFO (HEX 0114)                         | 2-66 |

| 2.8.2.12 | Read PROM (HEX 0312)                         | 2-07 |

| 2.8.2.13 | Read State Count (HEX 0118)                  | 2-67 |

| 2.8.2.14 | Read Tag Bus (HEX OIIA)                      | 2-09 |

| 2.8.3    | Surface Operation                            | 2-69 |

| 2.8.3.1  | Device Adapter Set Up for Surface Operations | 2-70 |

| 2.8.3.2  | Format (without data field)                  | 2-71 |

| 2.8.3.3  | Format (with data field)                     | 2-12 |

| 2.8.3.4  | Write                                        | 2-/3 |

| 2.8.3.5  | Write (in ECC diagnostic mode)               | 2-13 |

| 2.8.3.6  |                                              | 2-72 |

| 2.8.3.7  | Read (in ECC Diagnostic Mode)                | 2-13 |

| 2.8.3.8  | Verify                                       | 2-74 |

|          |                                              | 2-14 |

| 2.8.3.9  | Error Correction Procedure 2                 | 77         |

|----------|----------------------------------------------|------------|

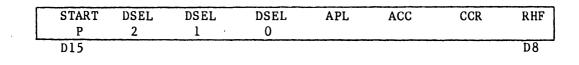

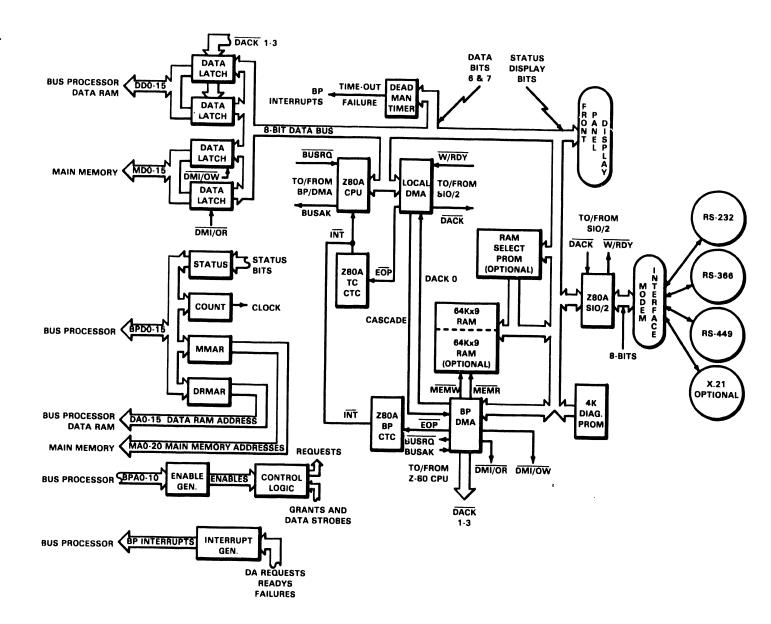

| 2.9      | Telecommunications Device Adapter 2          | -74        |

| 2.9.1    | TC General Description 2                     | 75         |

| 2.9.2    | TC/CPU Functions 2                           | -75        |

| 2.9.3    | Instruction space/Data Space Selector        | , ,<br>, , |

| 2.9.4    | Opcode Decode PROM                           | -//        |

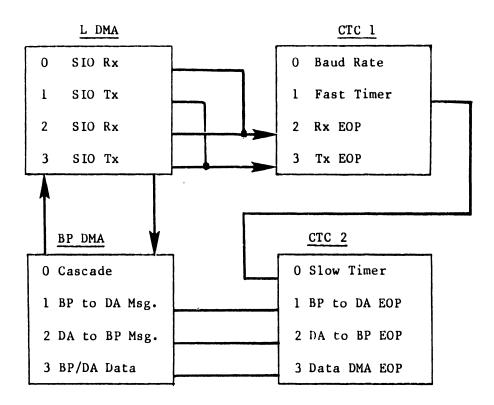

| 2.9.5    | 9517A Line DMA Controller 2                  | - 70       |

| 2.9.6    | 9517A BP DMA Controller 2                    | - 79       |

| 2.9.7    | SIO/2 Functions                              |            |

| 2.9.8    | CTC Functions 2                              | -00        |

| 2.9.8.1  | CTC 1 2-                                     | -01        |

| 2.9.8.2  | CTC 2 2-                                     | -81        |

| 2.9.9    | Deadman Timer Control Register 2-            | ~01        |

| 2.9.10   | Deadman Timer 2-                             | -82        |

| 2.9.11   | 25V76 Interrupt Handling 2-                  | -02        |

| 2.9.12   | TC-BP/DA DMA Transfers 2-                    | -82<br>-83 |

| 2.9.13   | Automatic Calling Unit 2-                    | -05        |

| 2.9.14   | Line Interface 2-                            | -04        |

| 2.9.15   | Address/Status Switches 2-                   | -04        |

| 2.9.16   | Diagnostic Functions 2                       | -05        |

| 2.9.17   | Status Display 2-                            | 20-        |

| 2.9.18   | TC-BUS Processor/Device Adapter Interface 2- | -00        |

| 2.9.18.1 | TC-BP to DA I/O Command 2-                   | -00        |

| 2.9.18.2 | TC Interrupt 2-                              | -00        |

| 2.9.18.3 | TC Handshake Procedure Between BP and DA 2-  | -00        |

| 2.9.18.4 | TC Diagnostic Termination                    | -0/        |

|          |                                              | · ()()     |

# CHAPTER 3 OPERATION

| 3.1   | General                             |

|-------|-------------------------------------|

| 3.2   | Switches                            |

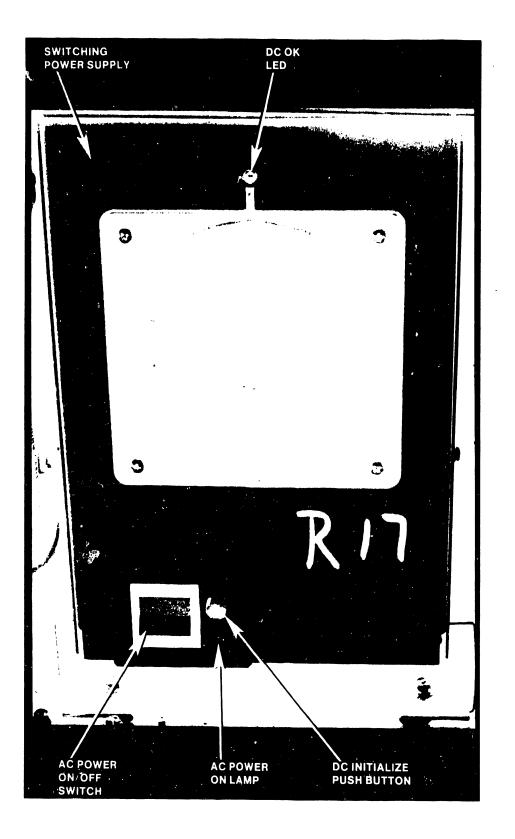

| 3.2.1 | Power Panel 3-1                     |

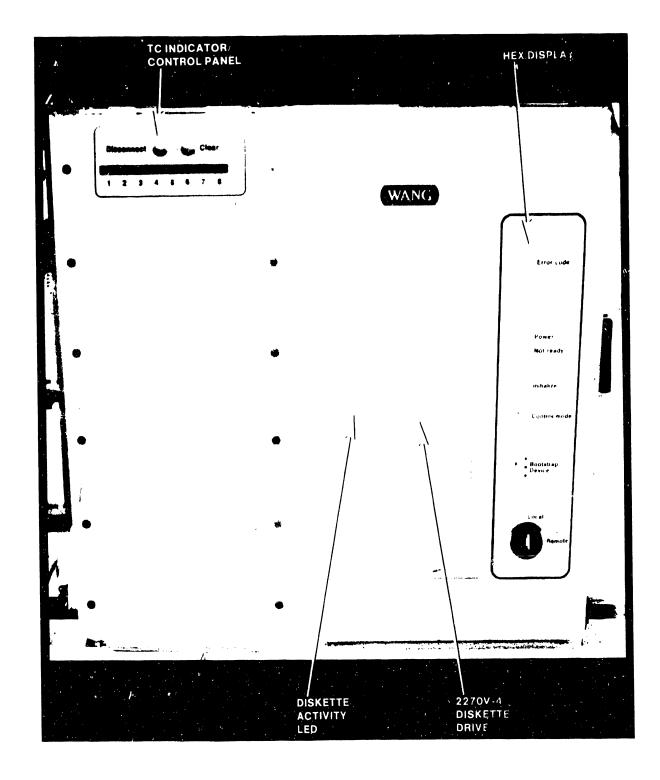

| 3.2.2 | Front Panel                         |

| 3.2.3 | TC DA Front Control/Indicator Panel |

| 3.2.4 | Control Mode Pushbutton 3-4         |

| 3.2.5 | Initialize Pushbutton 3-4           |

| 3.2.6 | Bootstrap Media Switch 3-5          |

| 3.2.7 | Local/Remote Switch 3-5             |

| 3.2.8 | Memory Size Selection               |

| 3.2.9 | BP Software Switch Settings 3-6     |

| 3.3   | Indicators 3-6                      |

| 3.3.1 | HEX Display 3-6                     |

| 3.3.2 | Power Supply Power On LED           |

| 3.3.3 | ISIO Diagnostic LED 3-7             |

| 3.4  | Support Materials               | 3-7 |

|------|---------------------------------|-----|

| 3.5  | Daily Power-Up Procedures       | 5-7 |

| 3.6  | Daily Verification Procedures   | 3-7 |

| 3.7  | Daily Power-Down Dress d        | 3-8 |

| 3.8  | Daily Power-Down Procedures     | 3-8 |

| 3.9  | Emergency Shut-Down Procedures  | 3-8 |

| J• 7 | Operator Preventive Maintenance | 3-8 |

### CHAPTER 4 INSTALLATION

| 4.1      | General                                          | -1         |

|----------|--------------------------------------------------|------------|

| 4.2      | Installation Site Check 4.                       | -1         |

| 4.3      | Tools and Test Equipment 4                       | -2         |

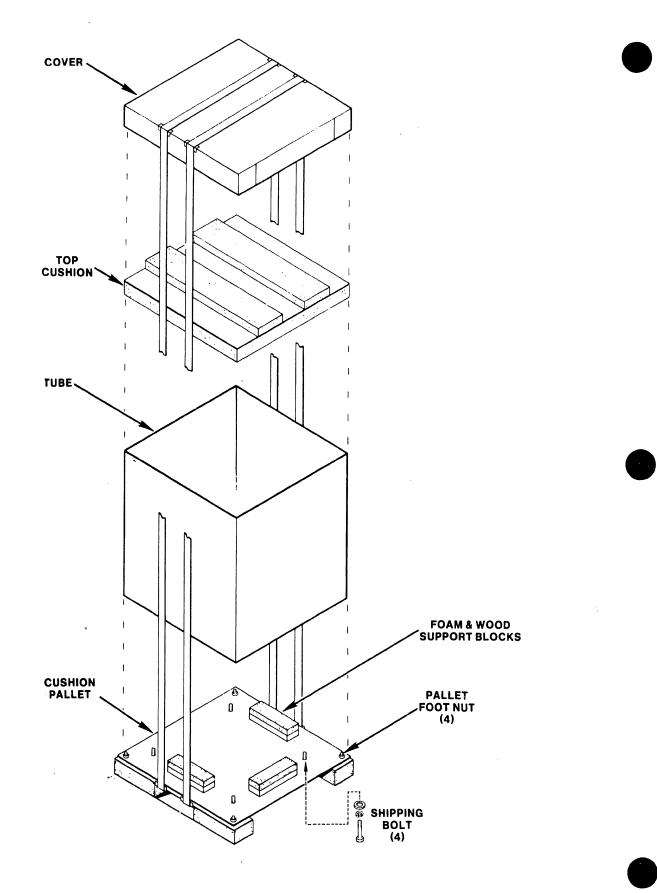

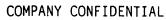

| 4.4      | Unpacking                                        | -2         |

| 4.4.1    | Claims Information                               | -2         |

| 4.4.2    | Telecommunications Adapter Upgrade Kit 4         | -3         |

| 4.4.3    | SMD Adapter Upgrade Kits 4-                      | -1         |

| 4.4.4    | Unpacking the Main Frame 4                       | -5         |

| 4.4.5    | Unpacking the Peripherals 4-                     | _0         |

| 4.5      | Main Frame Inspection 4-                         | -0<br>-8   |

| 4.5.1    | Peripheral Inspection 4-                         | Ω          |

| 4.6      | Minimum Requirements 4-                          | -0<br>-0   |

| 4.6.1    | Hardware                                         | 0          |

| 4.6.2    | Coldstart Package 4-                             | -9<br>_0   |

| 4.6.3    | Diagnostic Packages 4-                           | -10        |

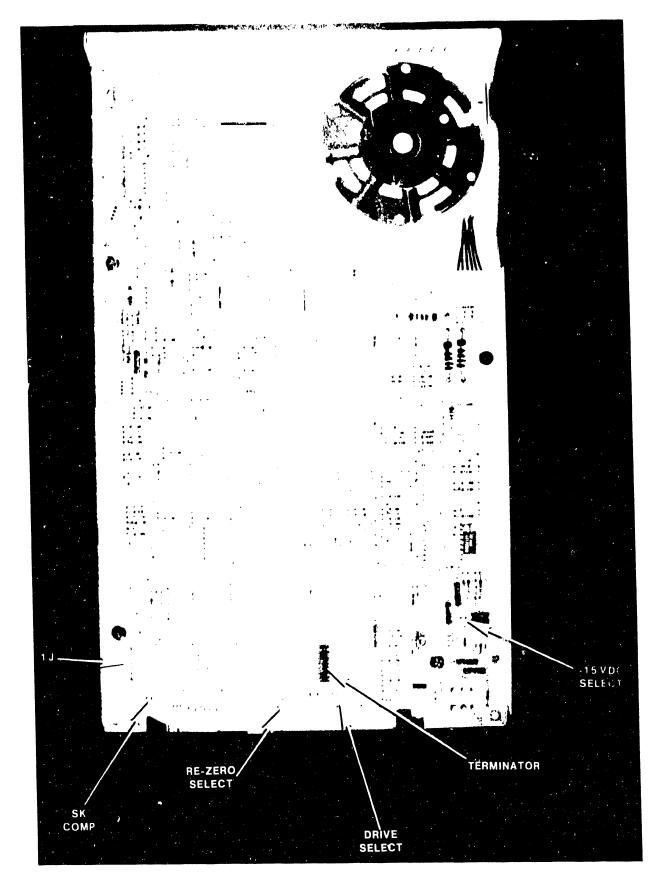

| 4.7      | Quantum Drive Installation 4-                    | -12        |

| 4.8.     | Main Frame Source-Power Check 4-                 | -15        |

| 4.8.1    | Initial Main Frame Power-Up 4-                   | -16        |

| 4.9      | Verify System Disk 4-                            | -10        |

| 4.10     | Coldstart Program 4-                             | -20        |

| 4.10.1   | Operating System 5.03.70 Coldstart Procedure 4-  | -20        |

| 4.10.2   | Operating System 6.10 Coldstart Procedure 4-     | -20<br>-23 |

| 4.10.2.1 | Operating System 6.10 Backup Procedure 4-        | 23         |

| 4.11     | Bootstrap Programs and IPL Process 4-            | -27        |

| 4.11.1   | IPL Procedure                                    | -29        |

| 4.12     | System Interconnection 4-                        | -29        |

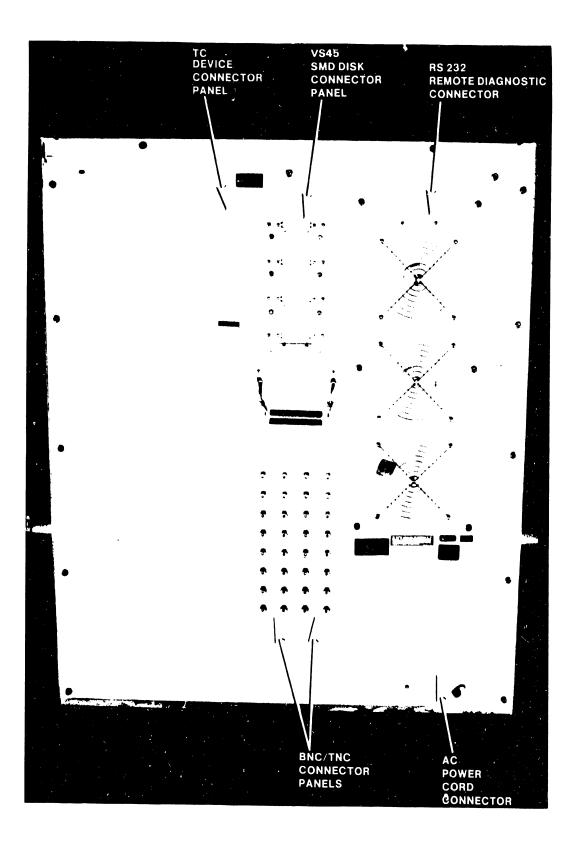

| 4.12.1   | Connector Plate-to-I/O Device Adapter Cabling 4- | - 30       |

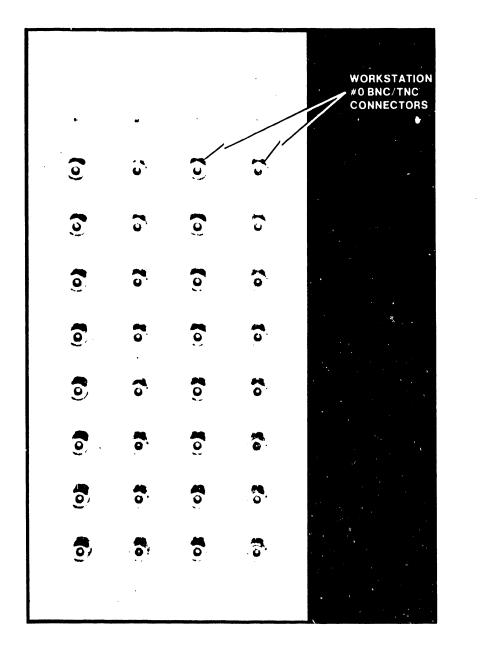

| 4.12.2   | BNC/TNC Connectors 4-                            | -31        |

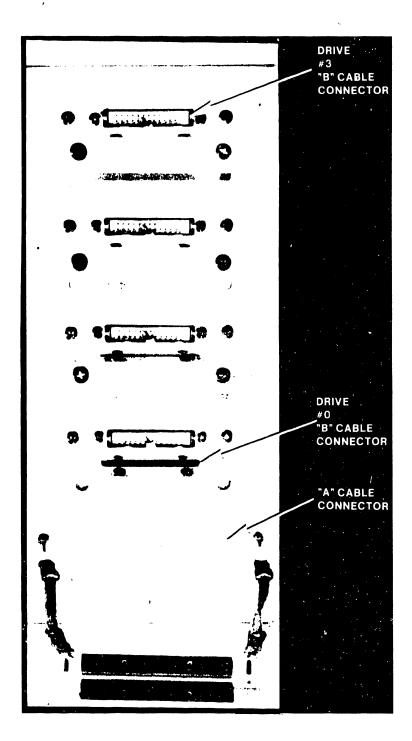

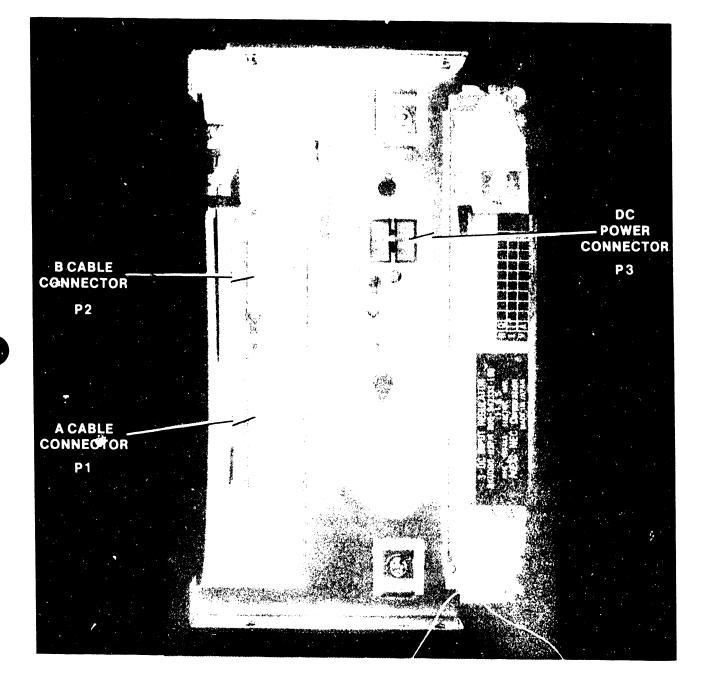

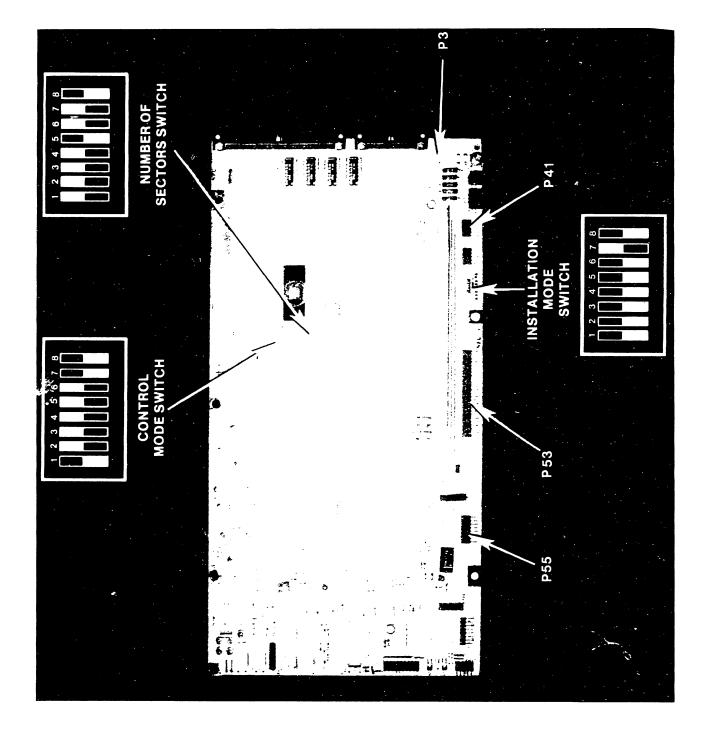

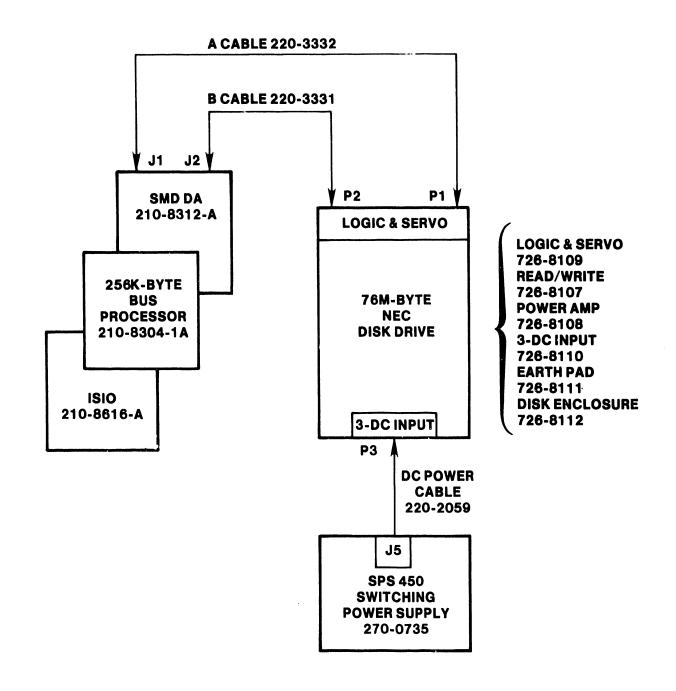

| 4.12.3   | SMD Disk Cable Connectors 4-                     | - 2 2      |

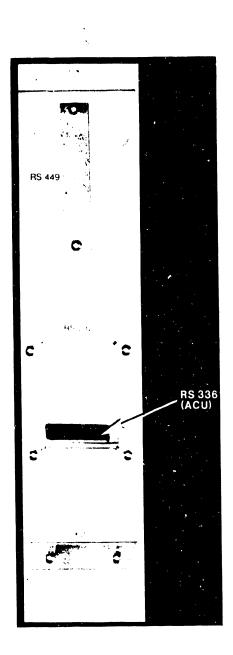

| 4.12.4   | Telecommunication Connectors                     | -34        |

| 4.13     | Preliminary System Checkout 4-                   | -20        |

| 4.13.1   | Daily Power-Up/Power-Down Procedures 4-          | ·3/        |

| 4.14     | System Turnover                                  | .3/        |

|          | · · · · · · · · · · · · · · · · · · ·            | - 28       |

I.

PREVENTIVE AND CORRECTIVE MAINTENANCE

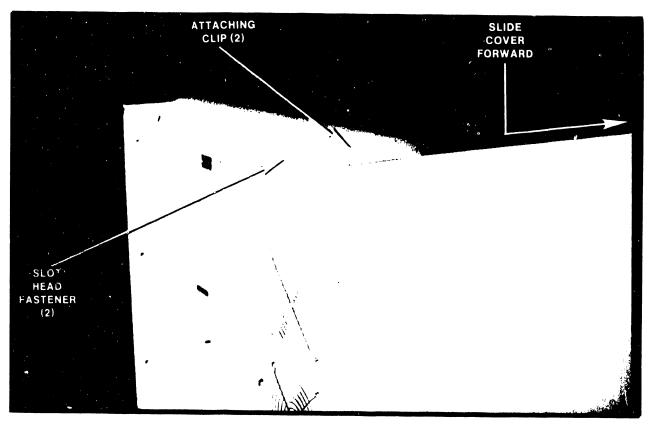

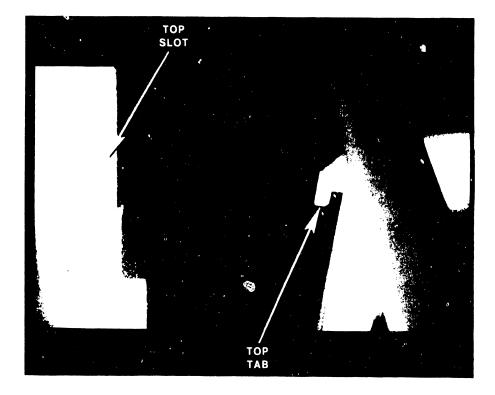

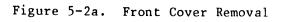

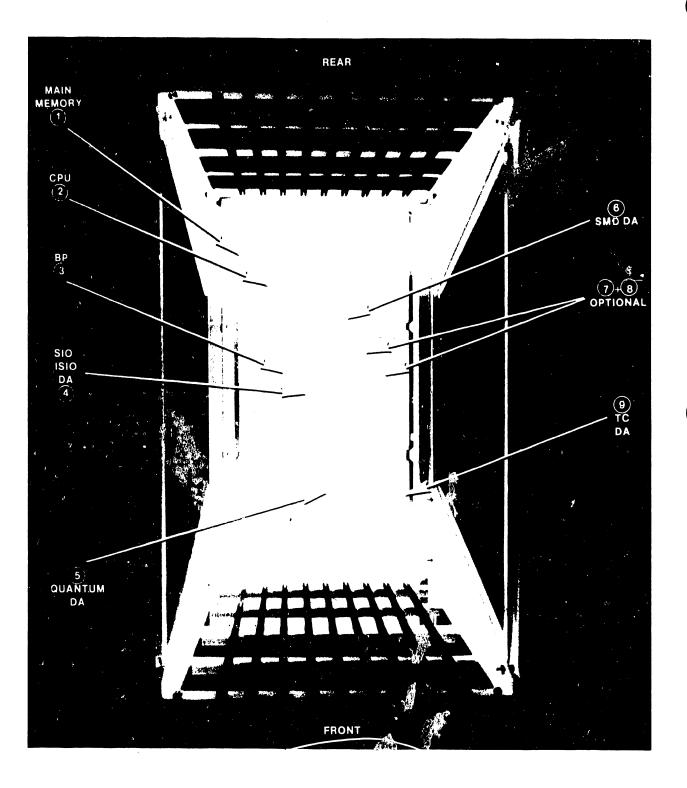

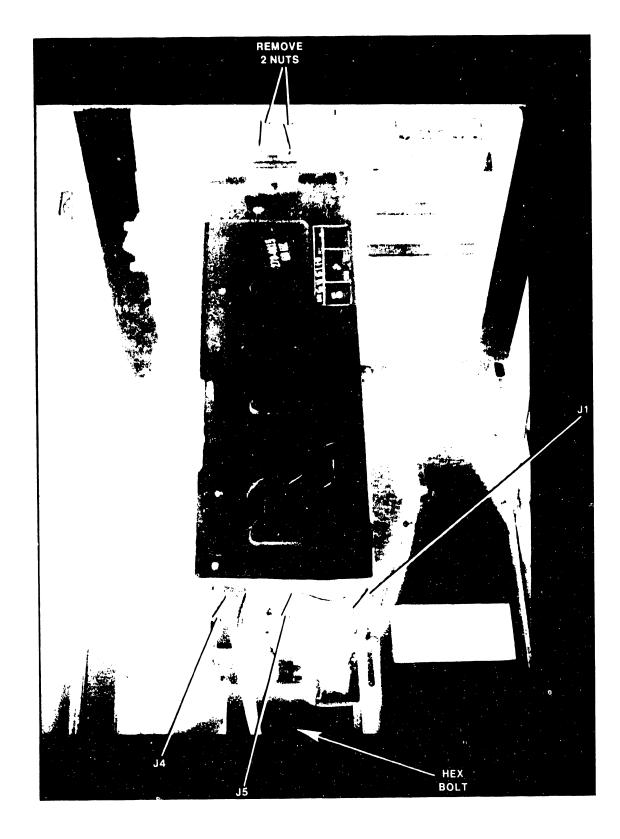

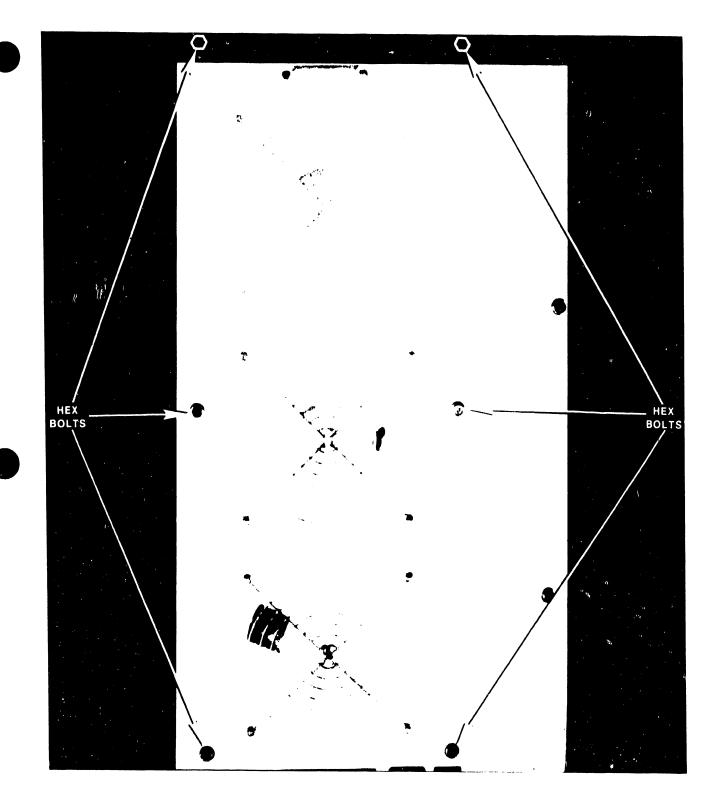

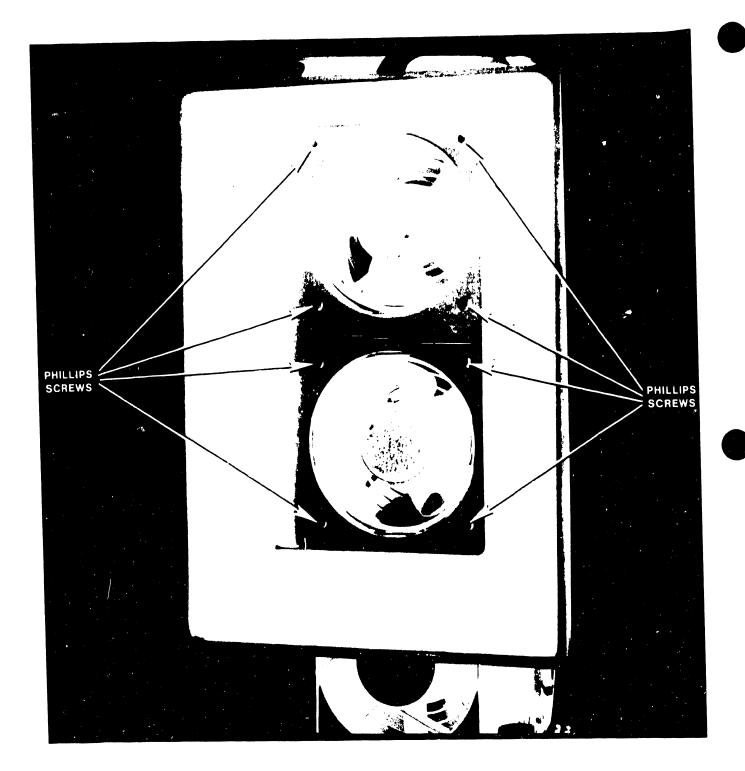

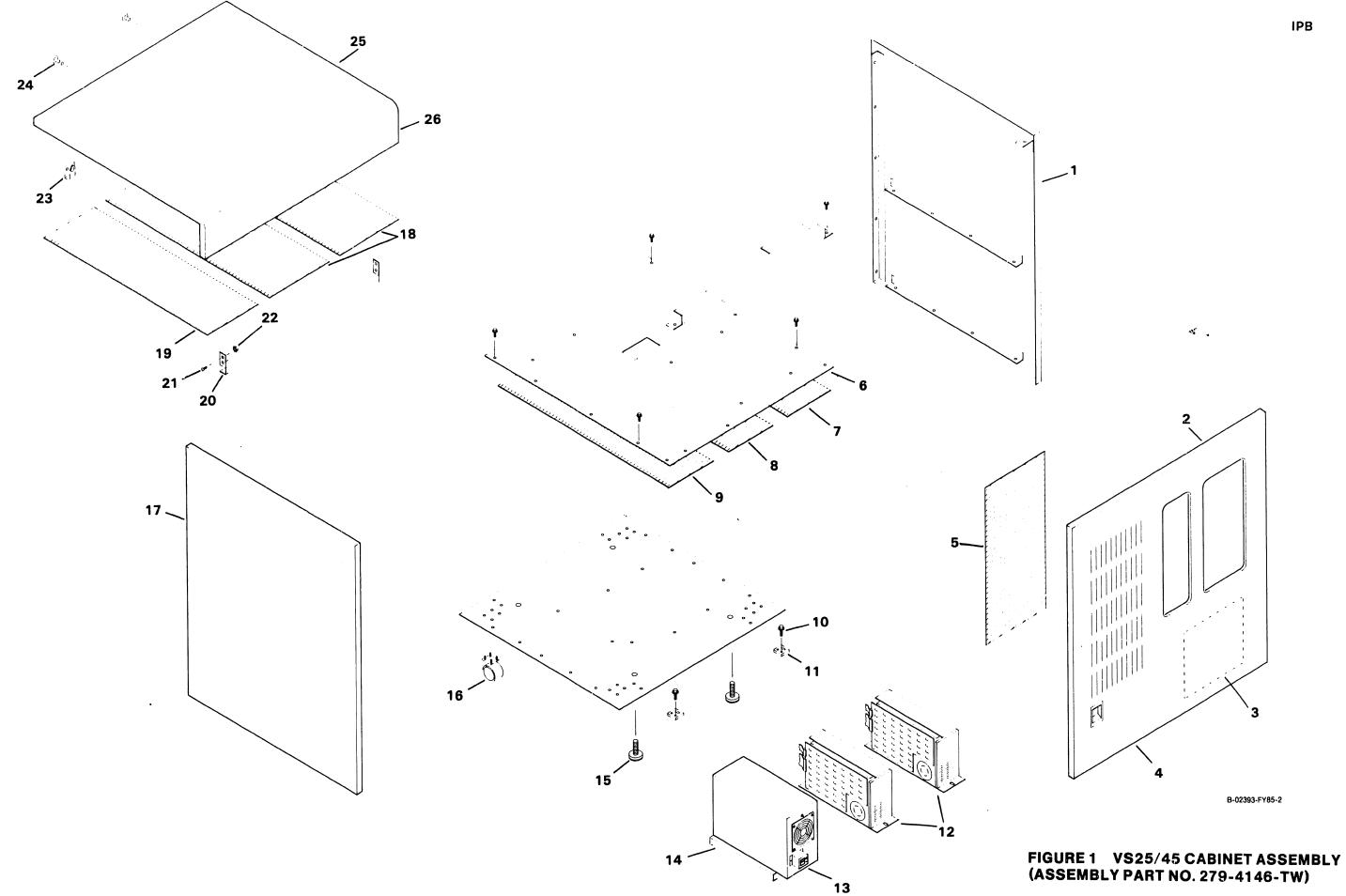

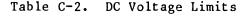

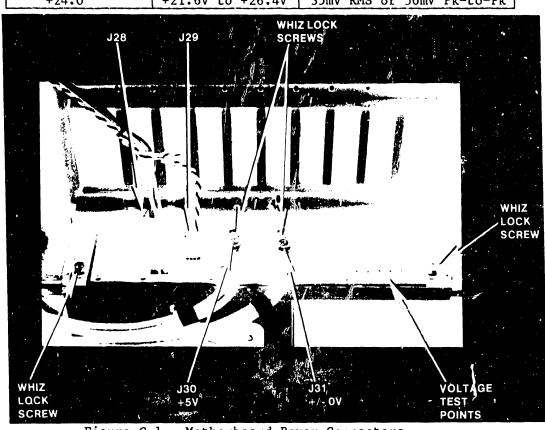

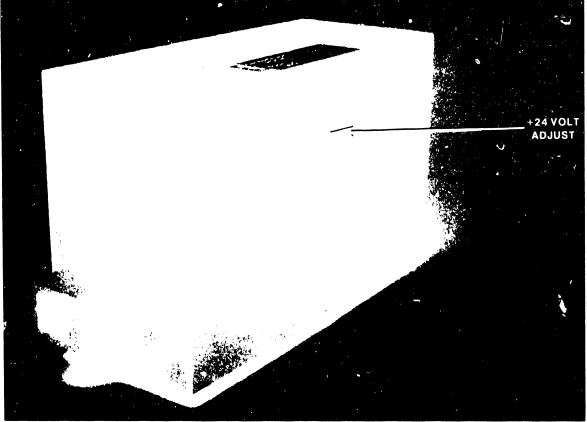

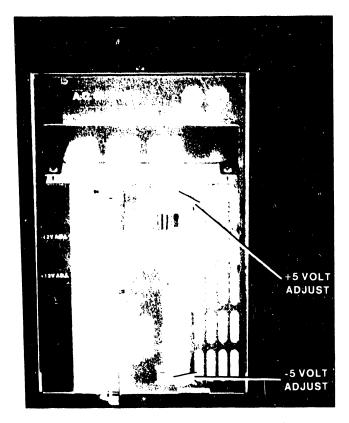

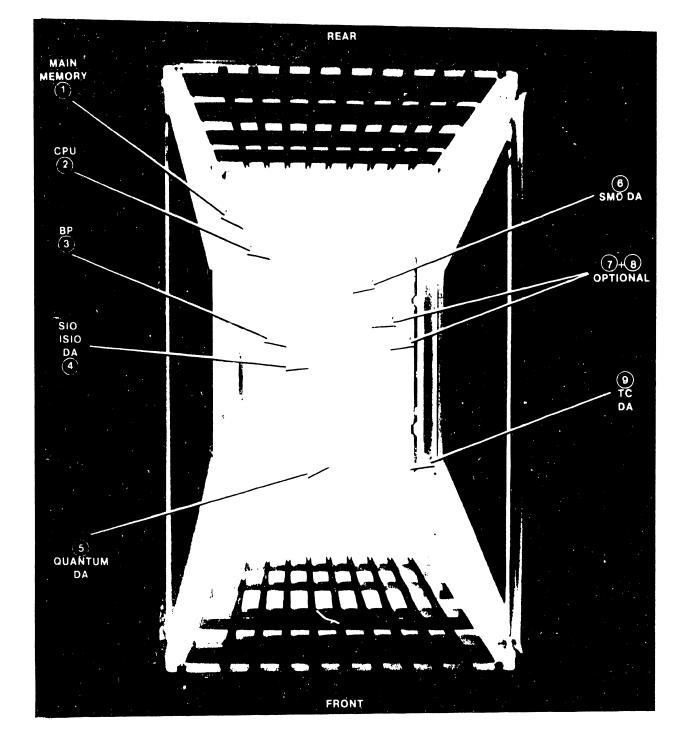

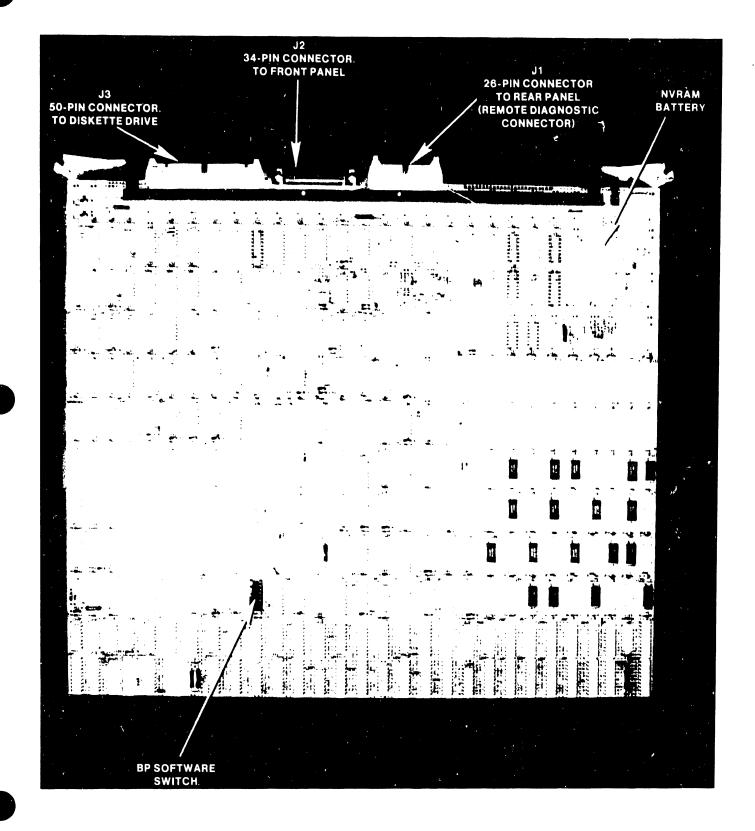

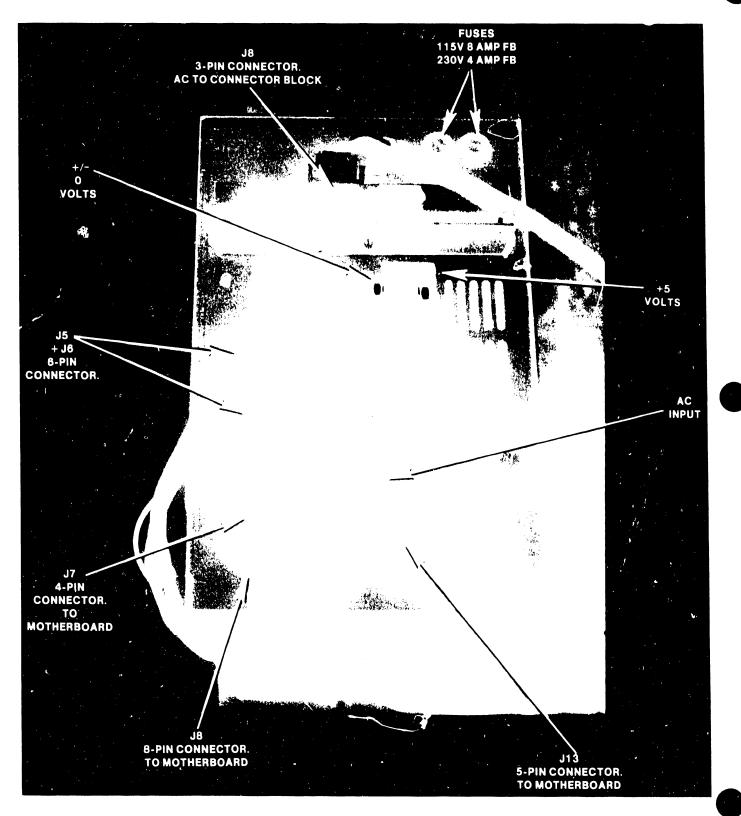

#### 5.1 General ..... 5 - 15.2 Preventive Maintenance ..... 5-1 5.2.1 5.2.2 Test Equipment ..... 5-1 5.2.3 5.2.4 Preventive Maintenance Schedule ..... 5-1 5.2.5 Main Frame Voltage Checks ..... 5-2 5.2.6 Peripheral Preventive Maintenance ...... 5-2 5.3 Corrective Maintenance ..... 5-2 5.3.1 5.3.2 5.3.3 5.3.4 5.3.4.1 Top Cover Removal ..... 5-3 5.3.4.2 Front Cover Removal ..... 5-3 5.3.4.3 CP Circuit Board Removal and Replacement ...... 5-7 5.3.4.3.1 210-7900 Main Memory Board Removal 5.3.4.3.2 210-8303 CPU Board Removal and Replacement ...... 5-9 5.3.4.3.3 210-8304 BP Board Removal and Replacement ...... 5-10 5.3.4.4 DA Circuit Board Removal and Replacement ...... 5-13 5.3.4.4.1 210-7906 SIO DA Removal and Replacement ...... 5-13 5.3.4.4.2 210-8616 ISIO DA Removal and Replacement ...... 5-16 5.3.4.4.3 210-8235 Quantum DA Removal and Replacement ..... 5-18 5.3.4.4.4 210-8312/13/14/15 SMD DA Removal and Replacement ..... 5-20 5.3.4.4.5 210-8337/8637 TC DA Removal and Replacement ..... 5-23 5.3.4.5 Front Panel Removal ..... 5-28 5.3.4.6 Front Panel Replacement ..... 5-28 5.3.4.7 TC DA Front Indicator/Control Panel Removal ..... 5-29 5.3.4.8 TC DA Front Indicator/Control Panel Replacement ..... 5-29 5.3.4.9 Motherboard Removal ..... 5-30 5.3.4.10 5.3.4.11 Power Supply Removal ..... 5-32 5.3.4.12 Power Supply Replacement ..... 5-32 5.3.4.13 Quantum Drive Removal ..... 5-34 5.3.4.14 5.3.4.15 Diskette Drive Removal ..... 5-38 5.3.4.16 Diskette Drive Replacement ..... 5-38 5.3.4.17 5.3.4.18 CHAPTER 6

CHAPTER 5

| 7.1                                                                                                                                                                                     | SCOPE                                                                                        | 7-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 8                                                                                                                                                                               | TROUBLESHOOTING                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

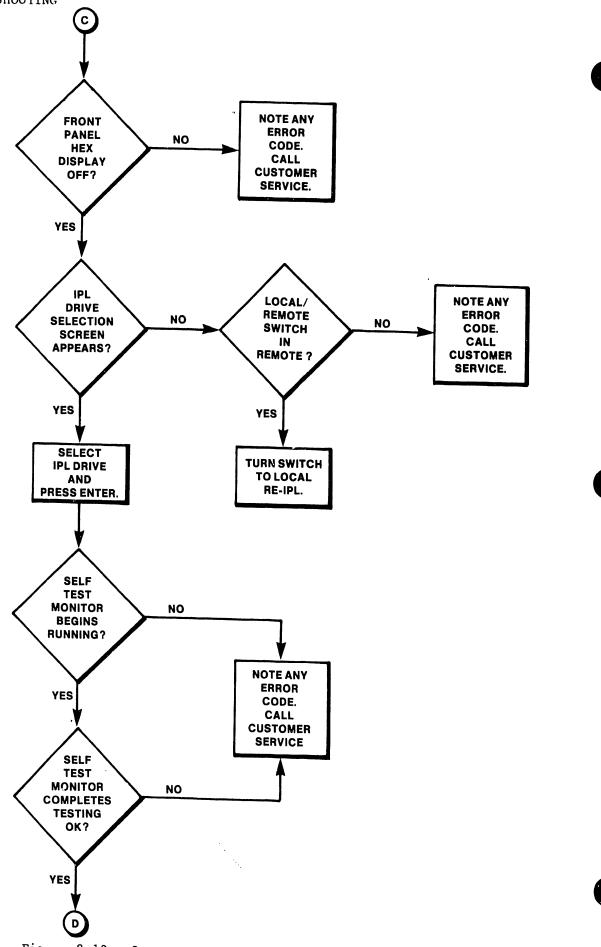

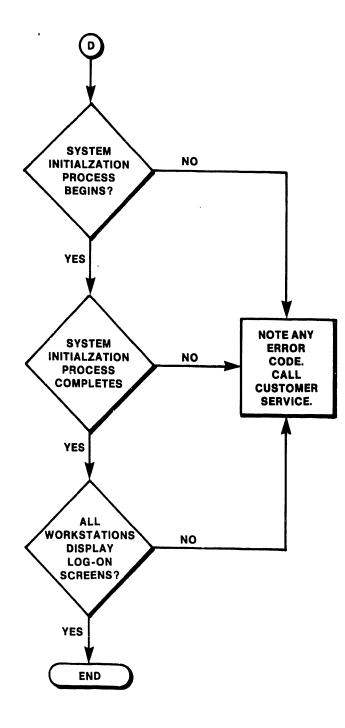

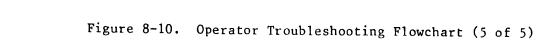

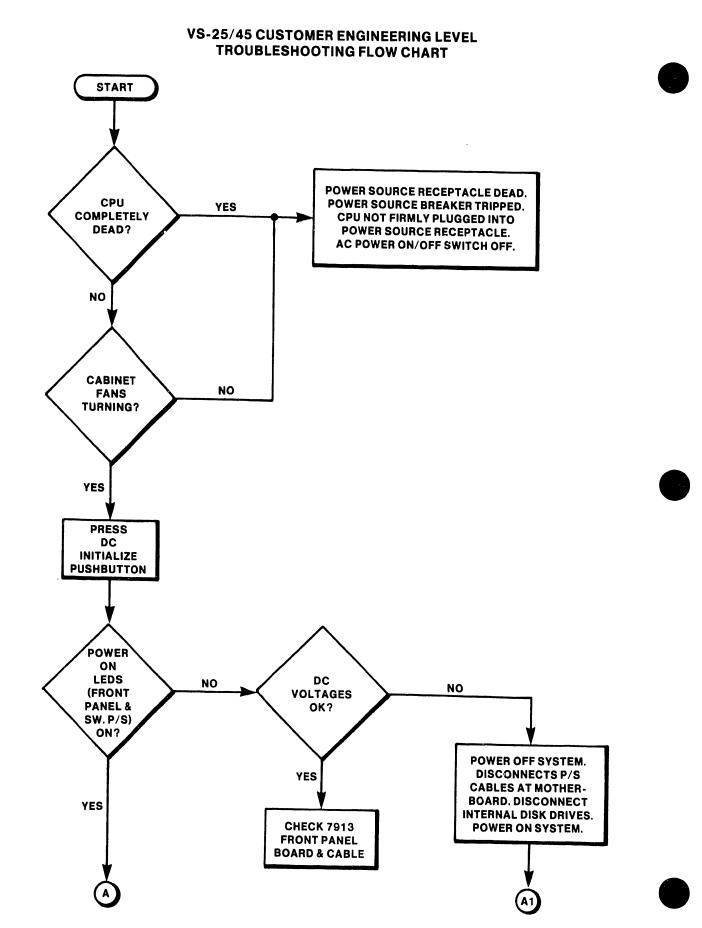

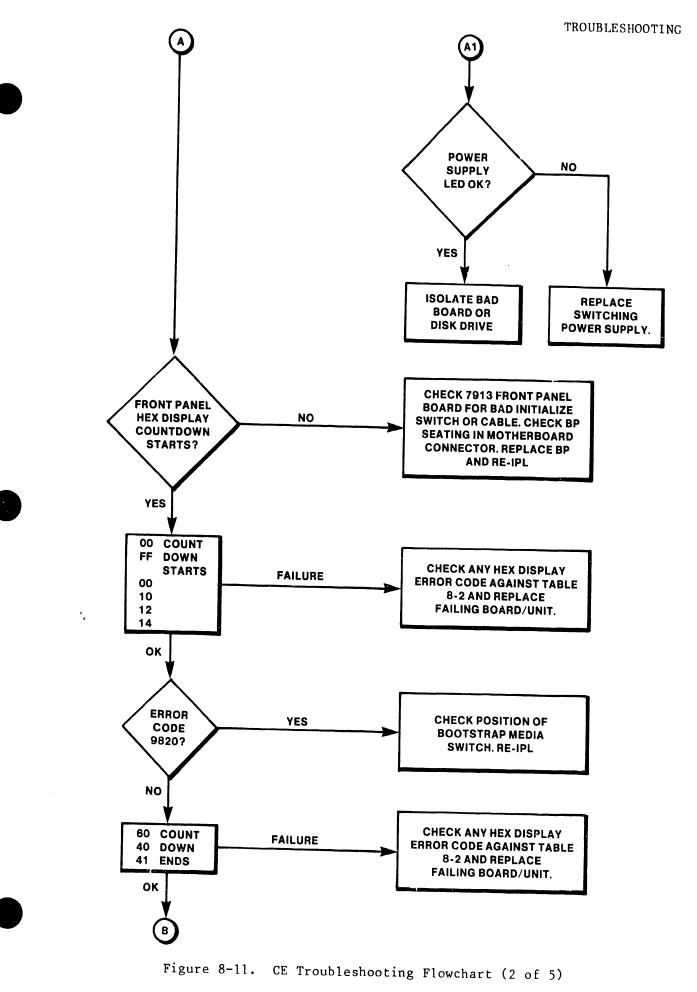

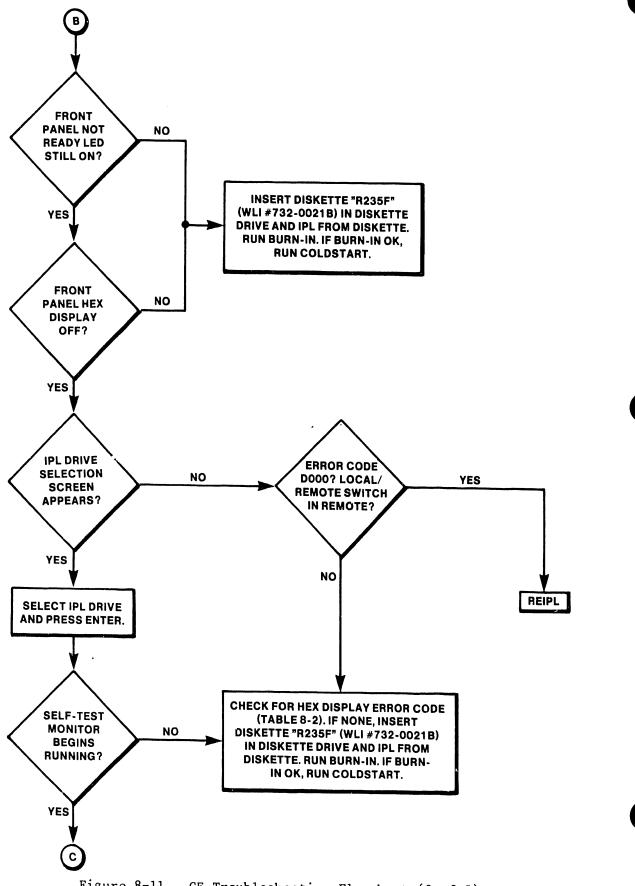

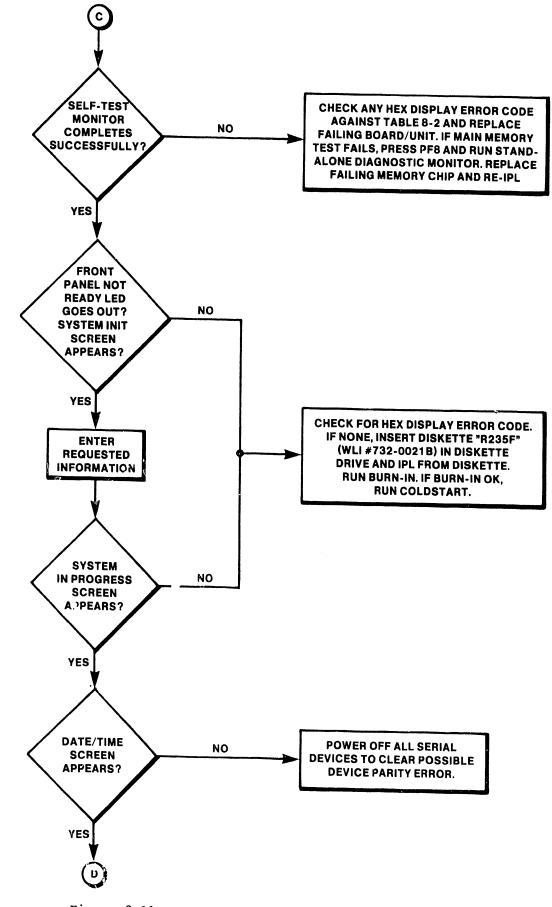

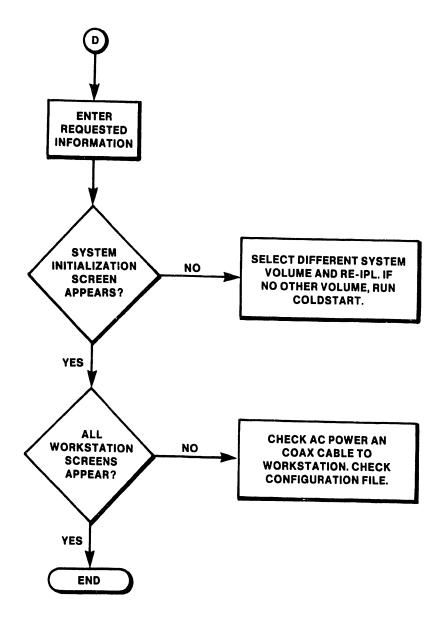

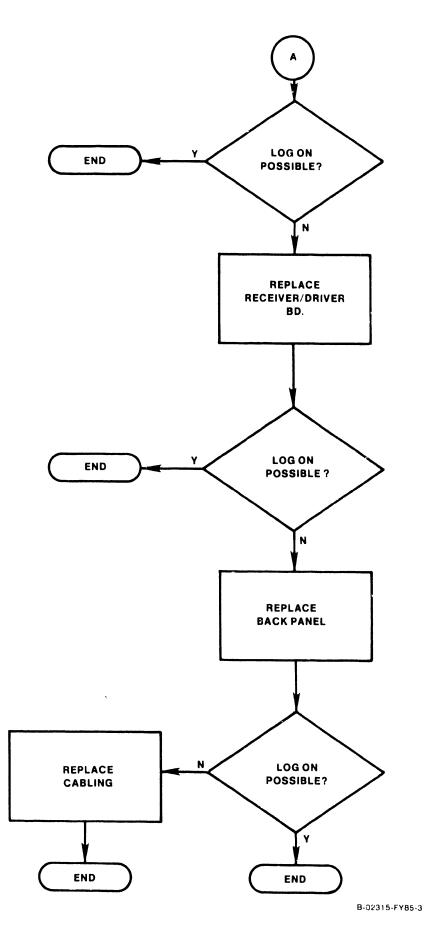

| 8.1<br>8.2<br>8.3<br>8.3.1<br>8.3.2<br>8.4<br>8.4.1<br>8.4.1.1<br>8.4.1.2<br>8.5<br>8.6<br>8.6.1<br>8.6.2.1<br>8.6.2.2<br>8.6.2.3<br>8.6.2.3<br>8.6.2.5<br>8.7<br>8.7.1<br>8.7.2<br>8.8 | General                                                                                      | 8-1<br>8-1<br>8-2<br>8-8<br>8-8<br>8-9<br>8-10<br>8-11<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-15<br>8-15<br>8-15<br>8-15<br>8-15<br>8-15<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-12<br>8-22<br>8-22<br>8-22 |

| APPENDIX A                                                                                                                                                                              | MNEMONICS, WORDS/PHRASES, MICROINSTRUCTIONS, AND<br>MISCELLANEOUS HARDWARE RELATED FUNCTIONS |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| APPENDIX B                                                                                                                                                                              | VS-25/45 SELF-TEST MONITOR DIAGNOSTIC ERROR CODES                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| APPENDIX C                                                                                                                                                                              | NEC DISK DRIVE                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

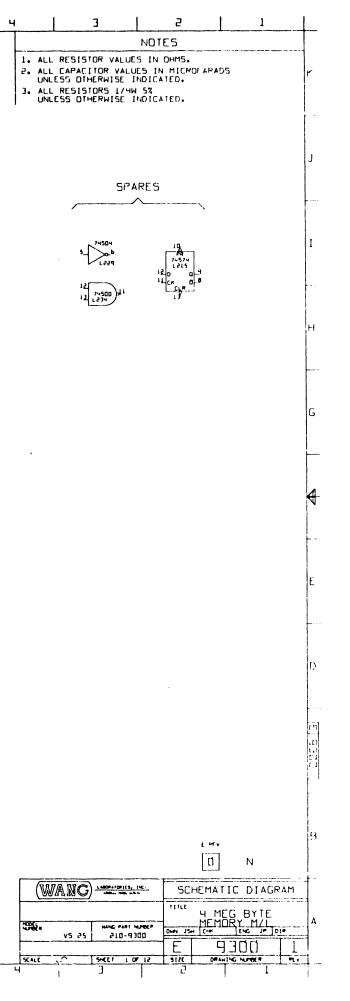

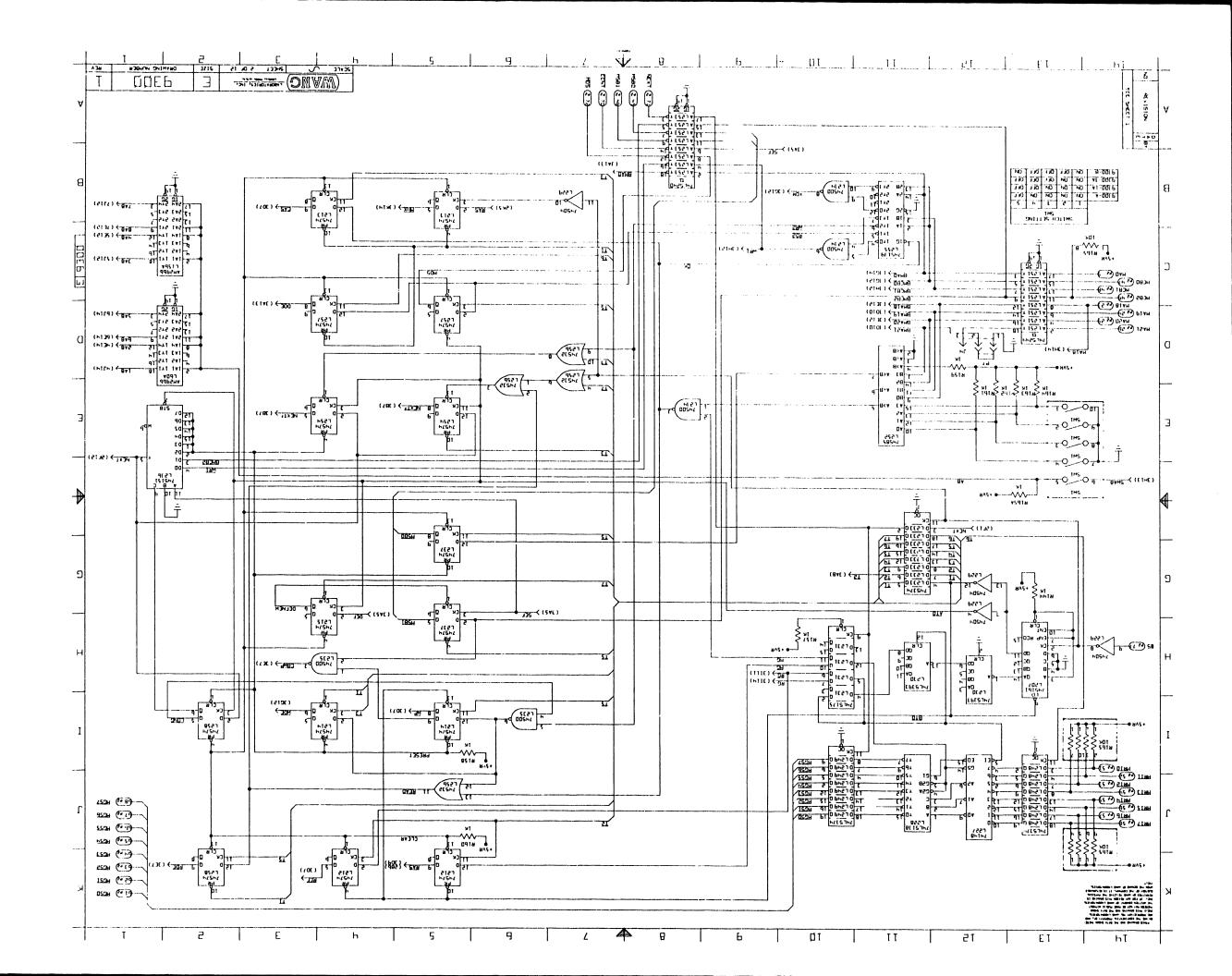

| APPENDIX D                                                                                                                                                                              | 2-MEGABYTE MAIN MEMORY OPTION                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

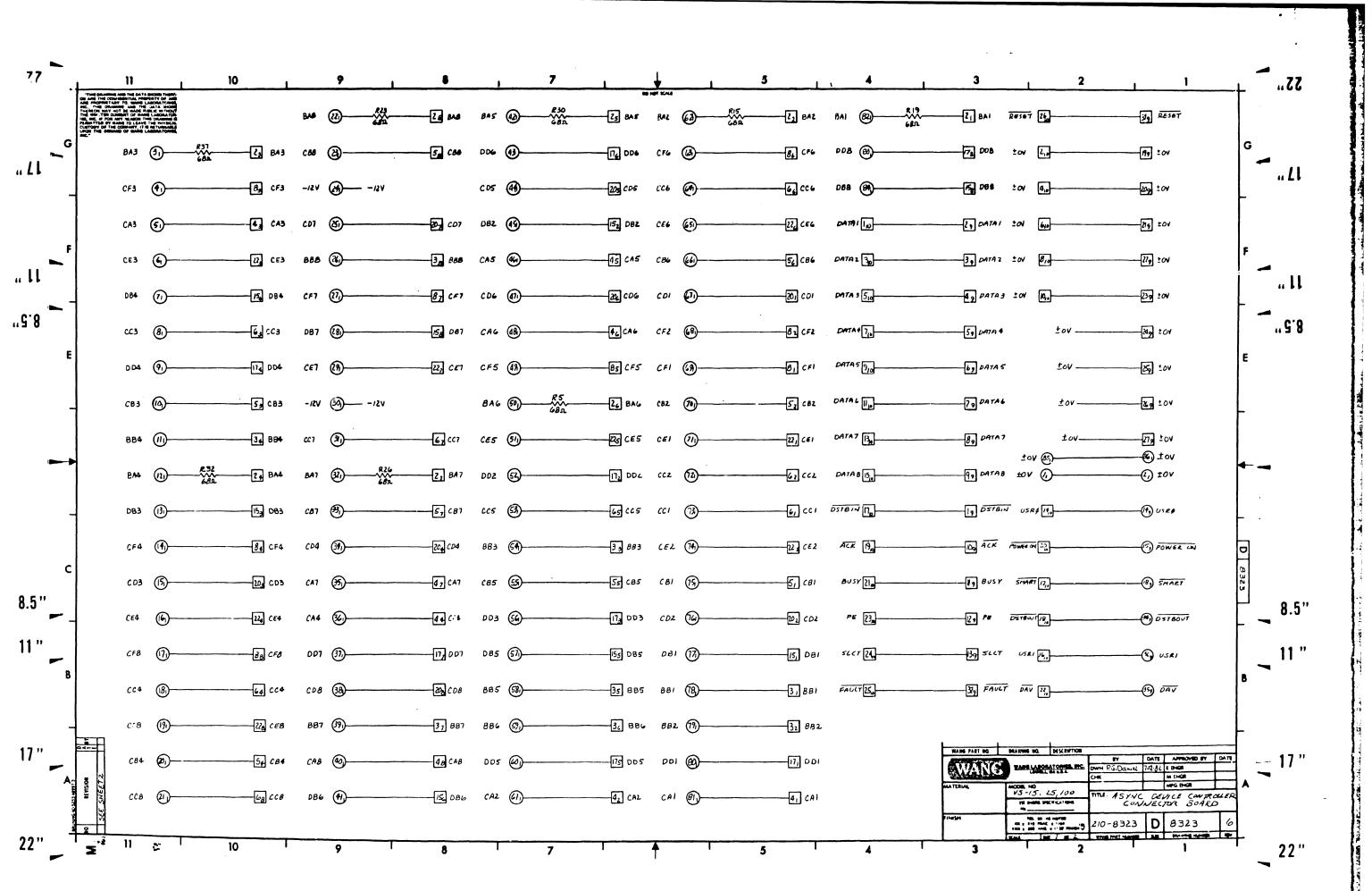

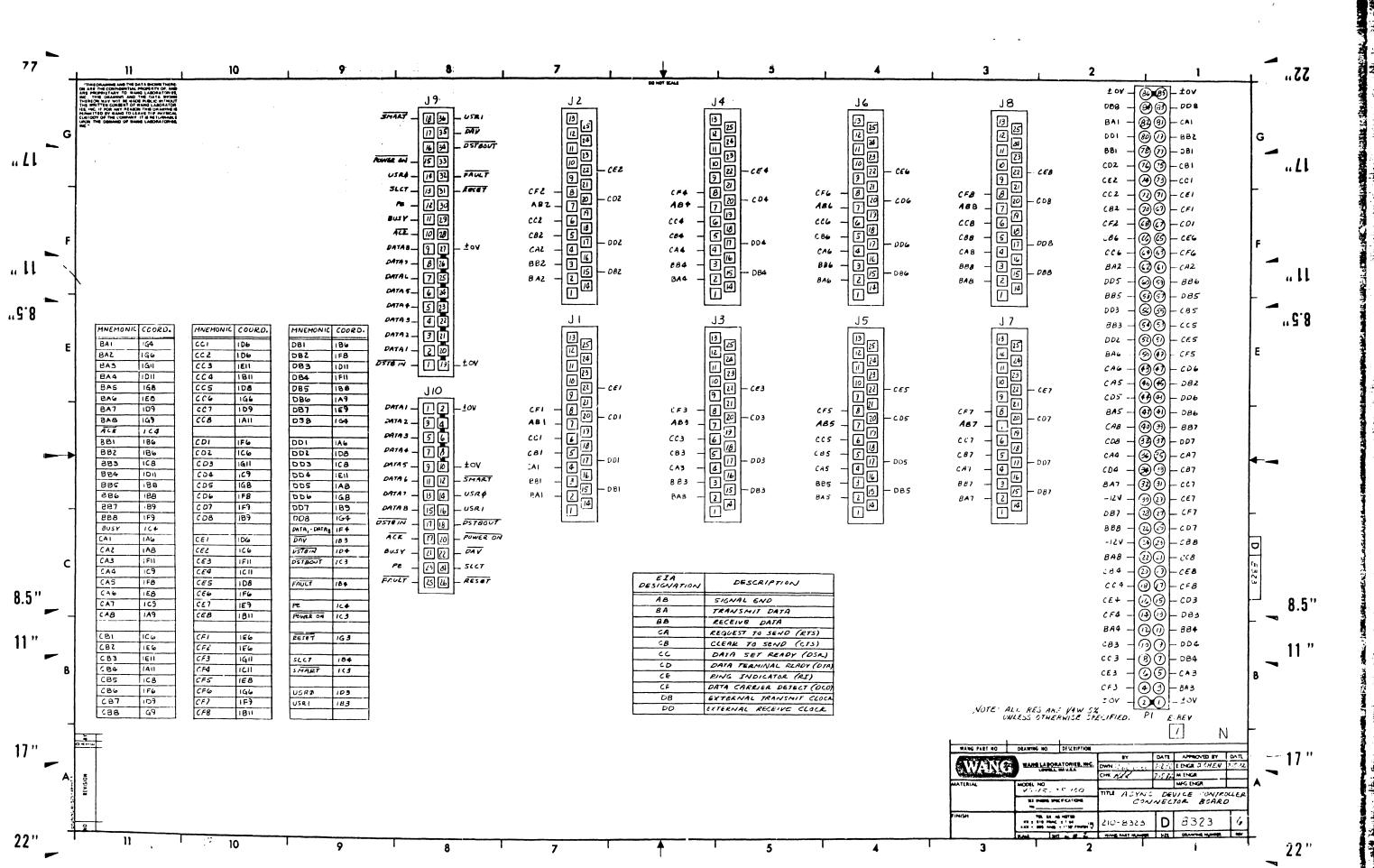

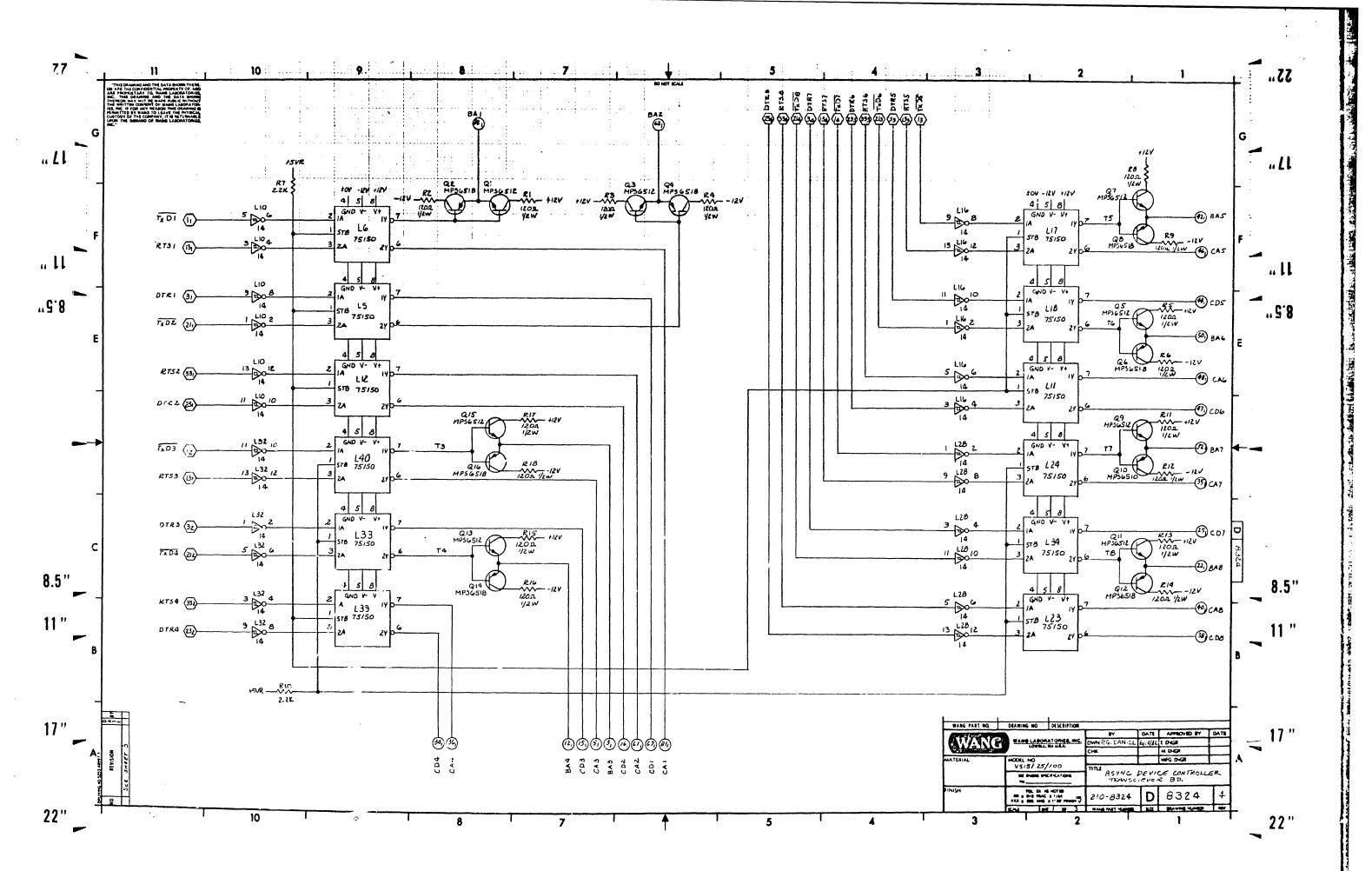

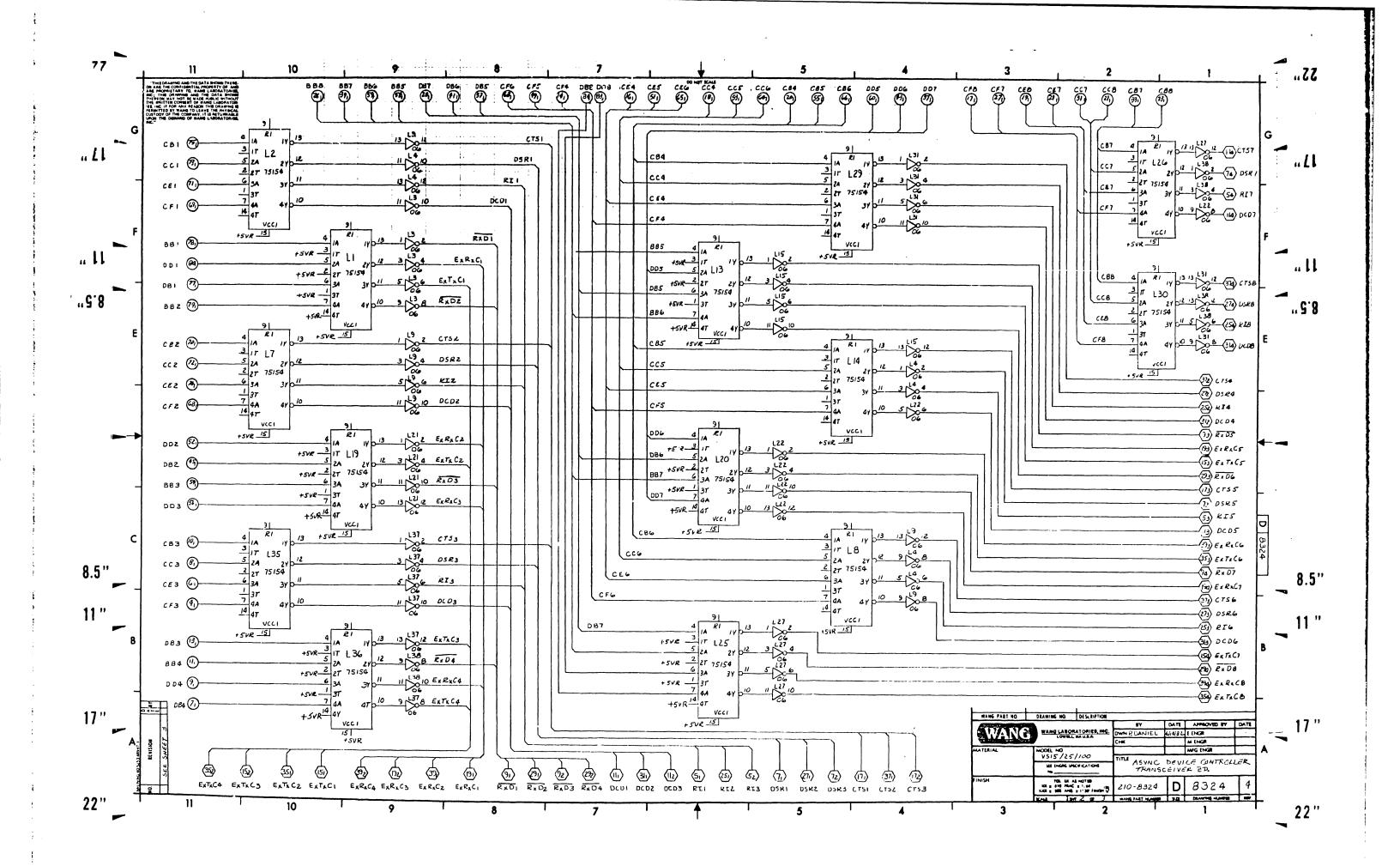

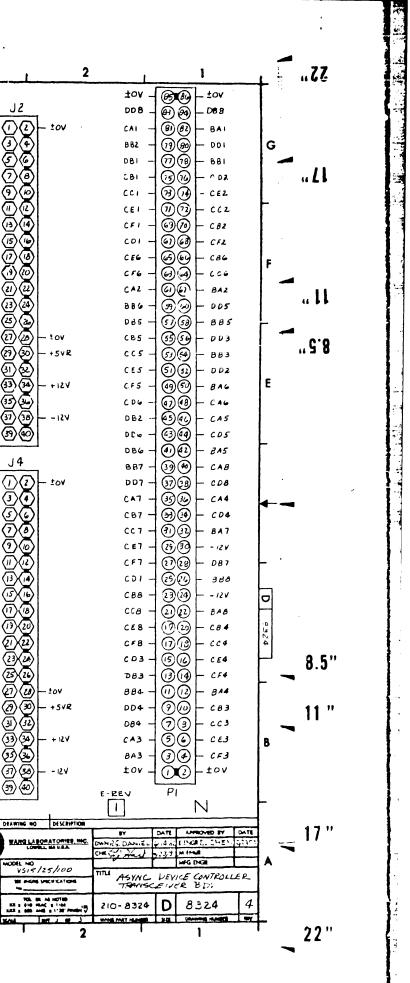

| APPENDIX E                                                                                                                                                                              | ASYNC. CONTROLLER BOARD                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

ĺ

.

.

CHAPTER 7 ILLUSTRATED PARTS BREAKDOWN

# LIST OF ILLUSTRATIONS

•

| Figure                                                                                                                             | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Page                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

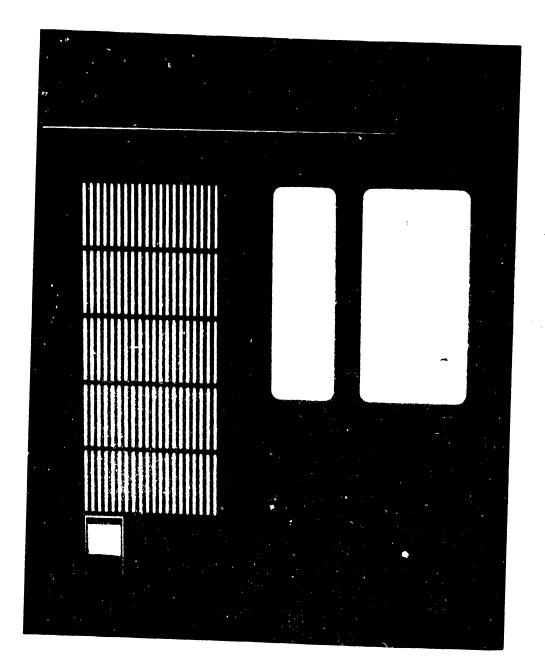

| 1-1<br>1-2                                                                                                                         | VS-25 Configurations<br>VS-45 Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                           |

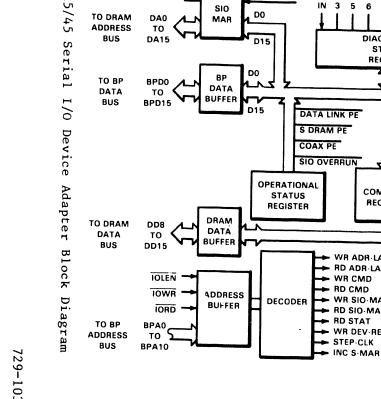

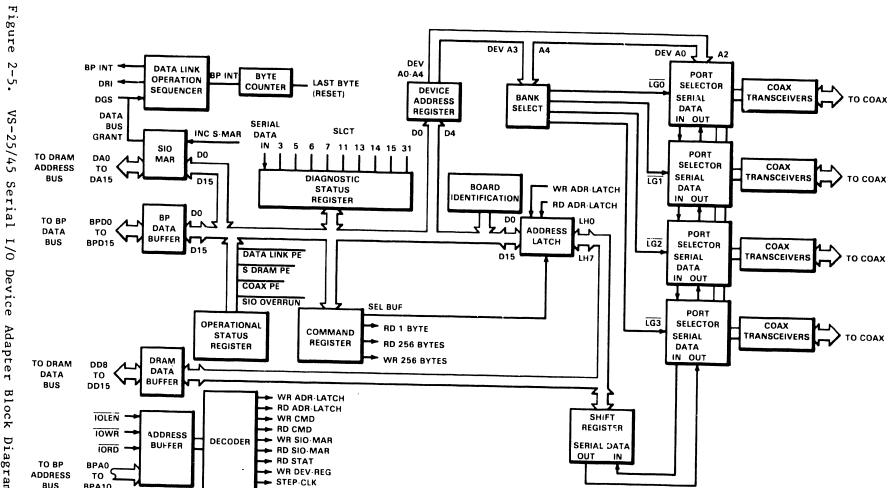

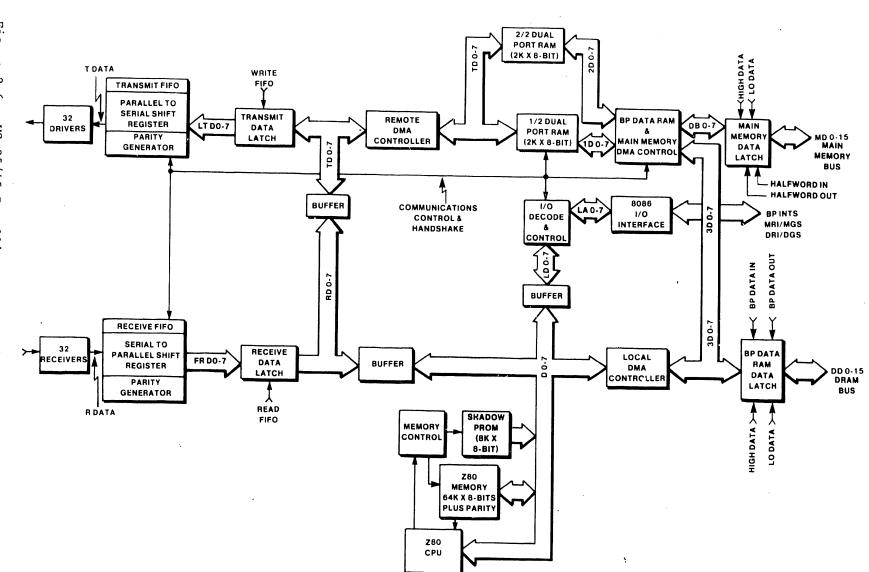

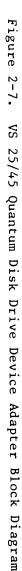

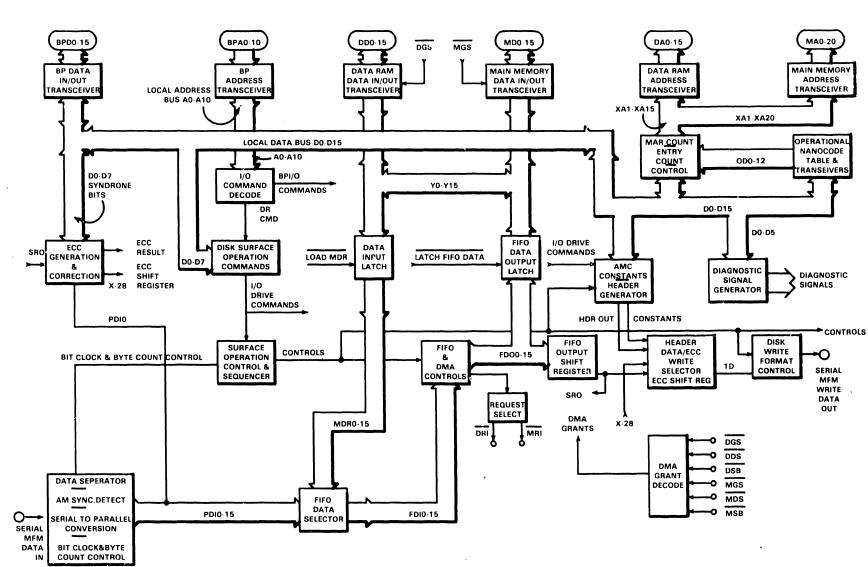

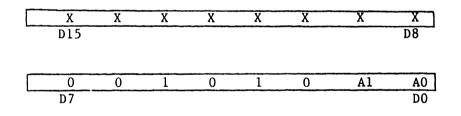

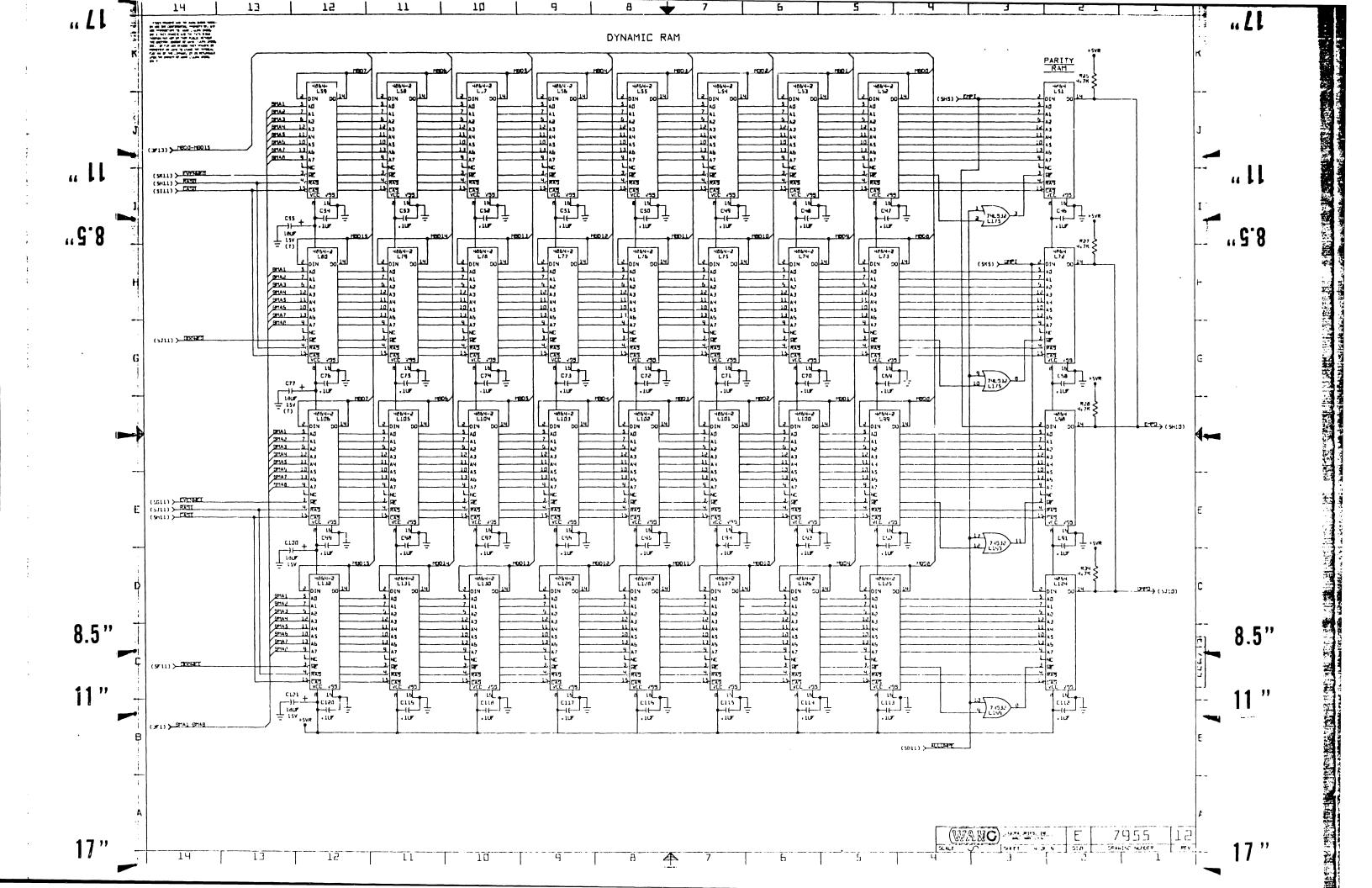

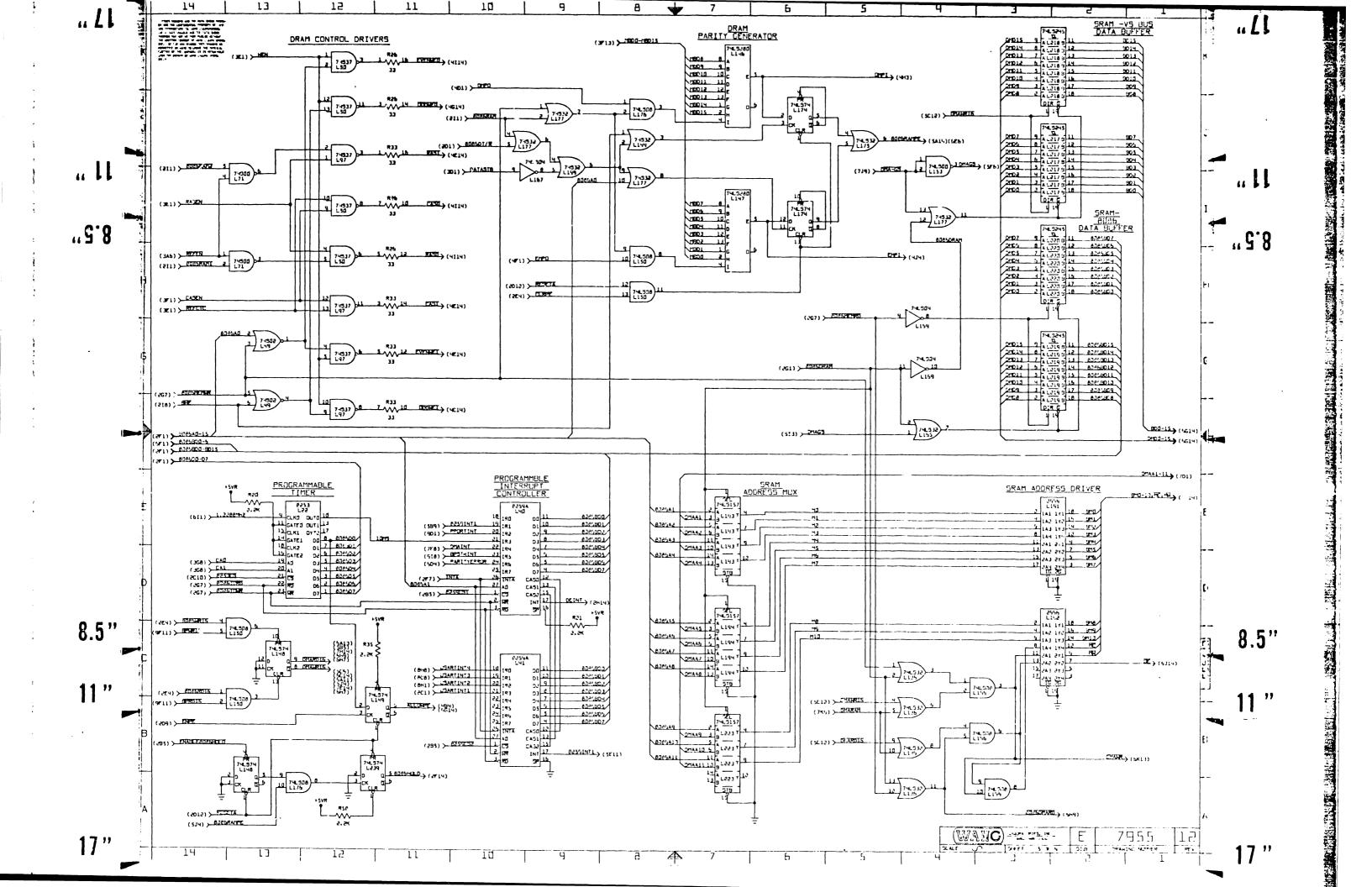

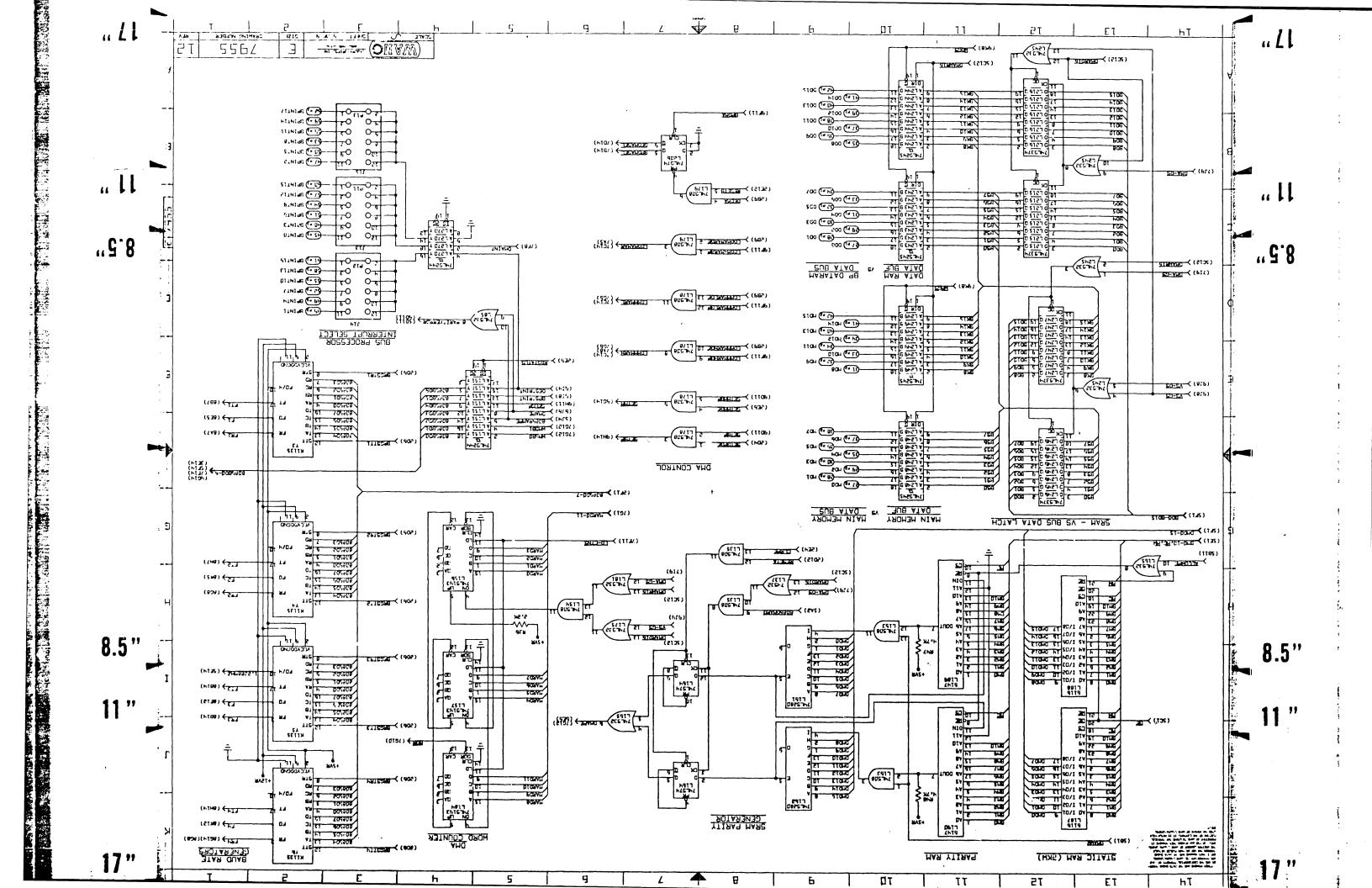

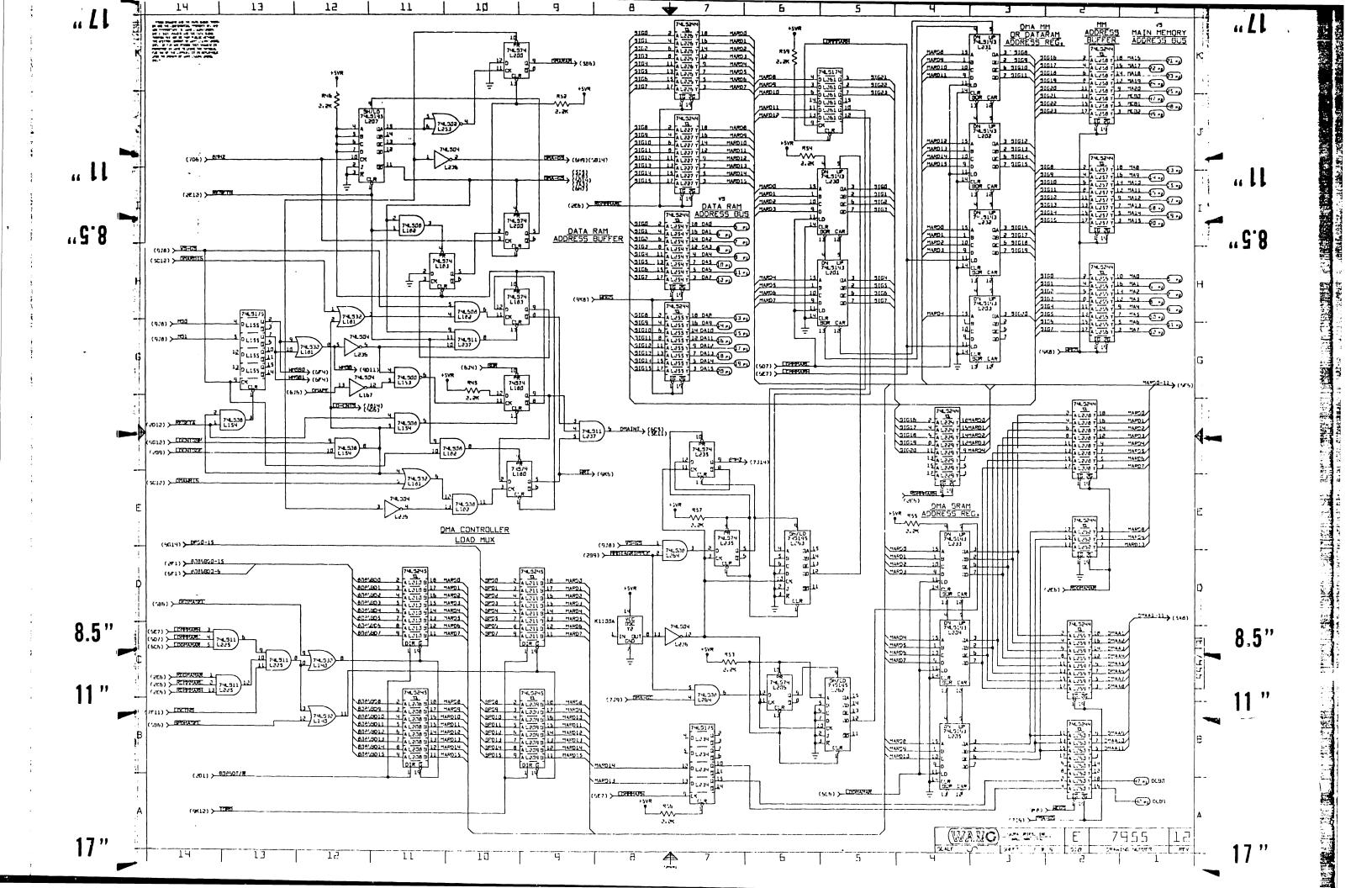

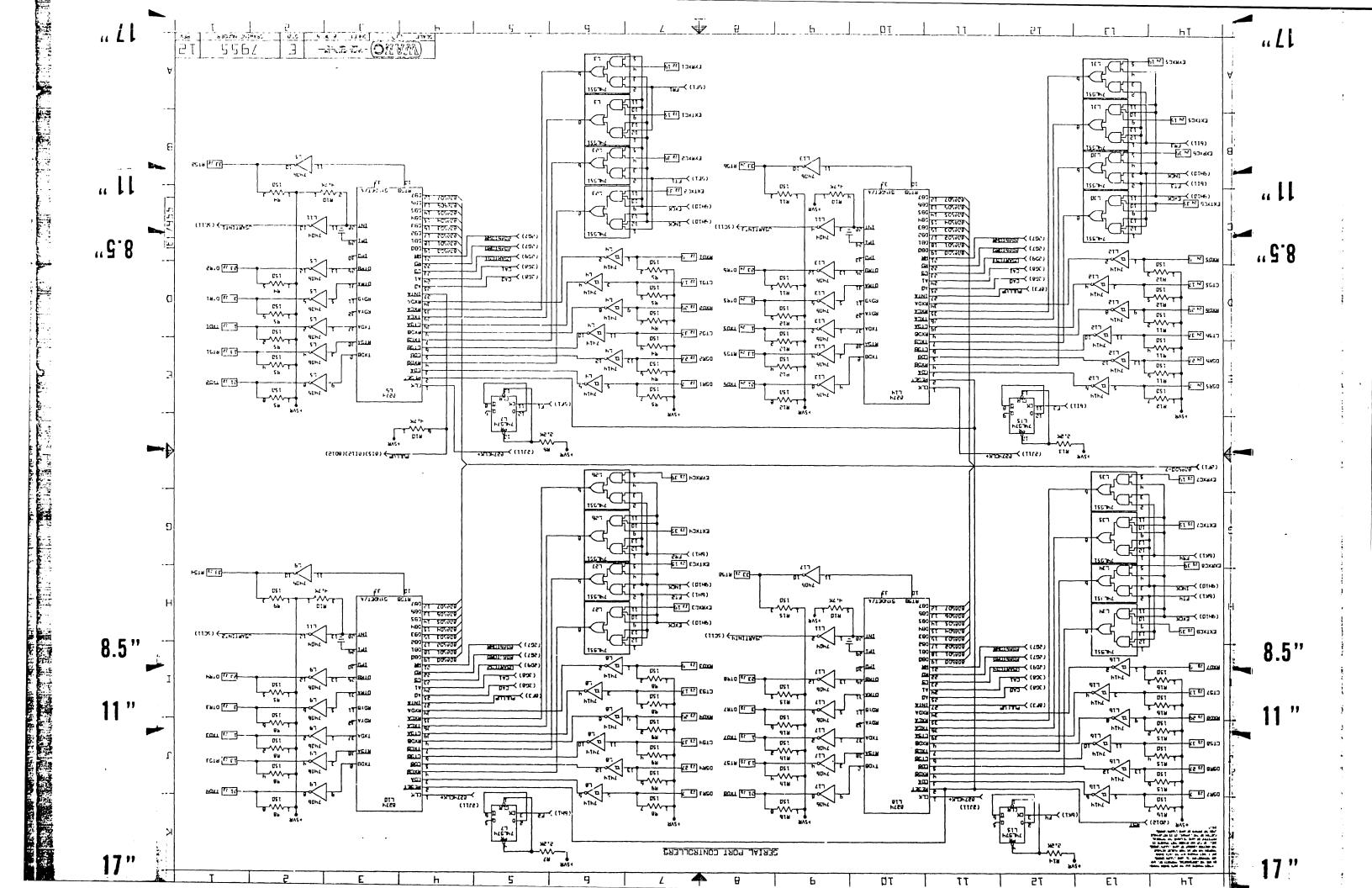

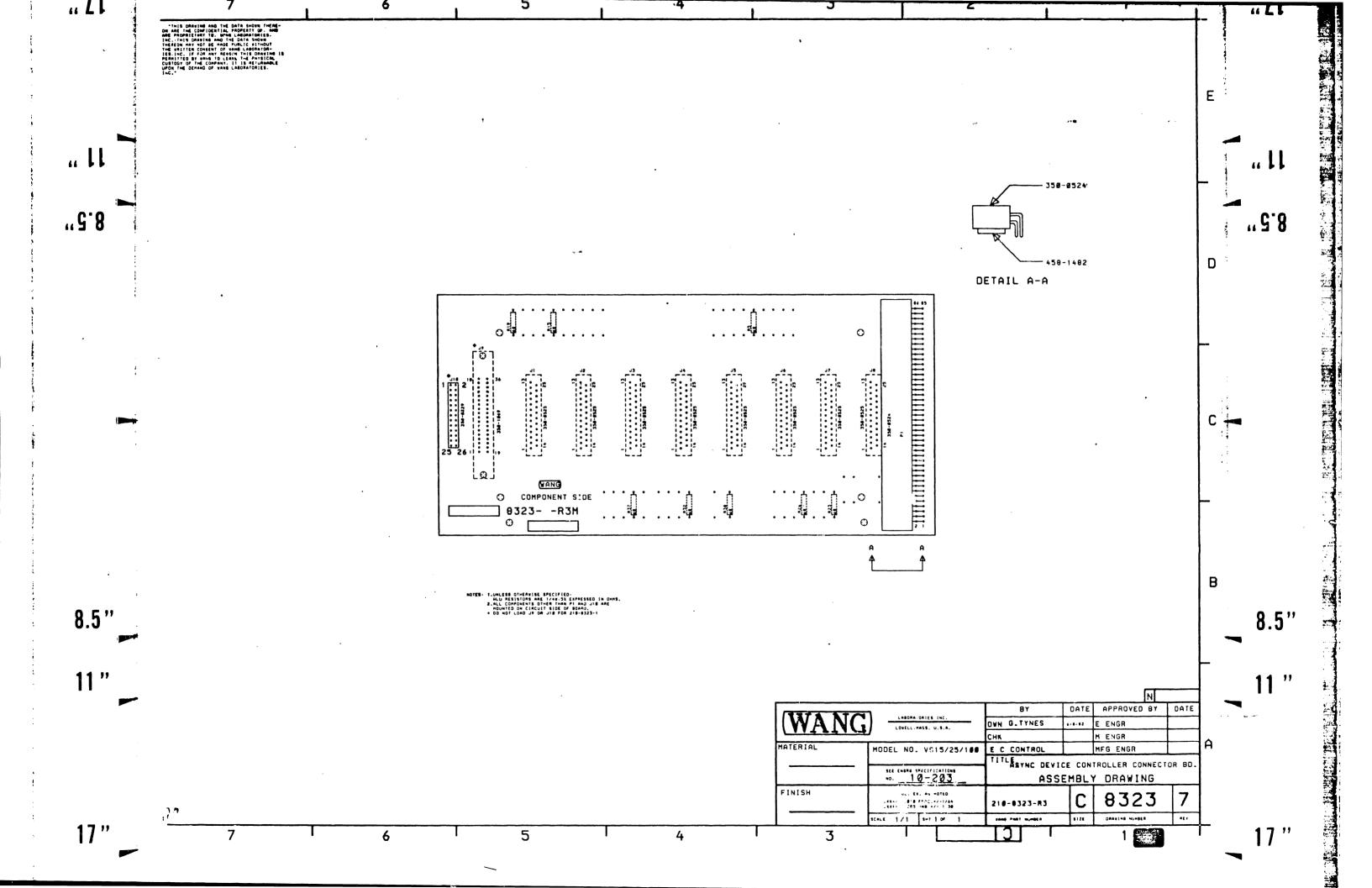

| 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-9                                                                        | VS-25/45 System Block Diagram<br>VS-25/45 CPU Block Diagram<br>VS-25/45 Main Memory Block Diagram<br>VS-25/45 Bus Processor Block Diagram<br>VS-25/45 Serial I/O DA Block Diagram<br>VS-25/45 Intelligent SIO DA Block Diagram<br>VS 25/45 Quantum Disk Drive DA Block Diagram<br>VS 25/45 SMD Disk Drive DA Block Diagram<br>VS-25/45 Telecommunications DA Block Diagram                                                                                                                                       | 2-6<br>2-16<br>2-23<br>2-38<br>2-44<br>2-46<br>2-52                                                                       |

| 3-1<br>3-2                                                                                                                         | Power Panel Switches and Indicators<br>Front Panel Switches and Indicators                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                           |

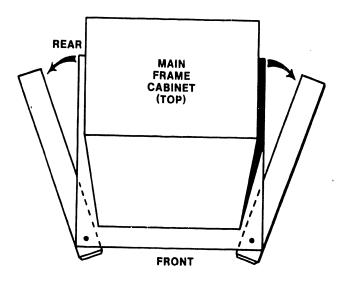

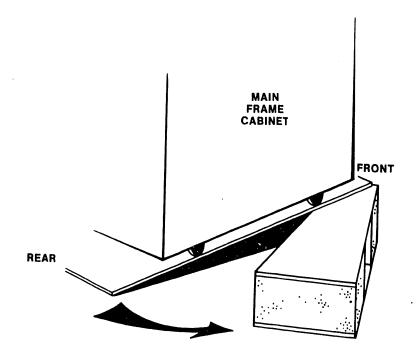

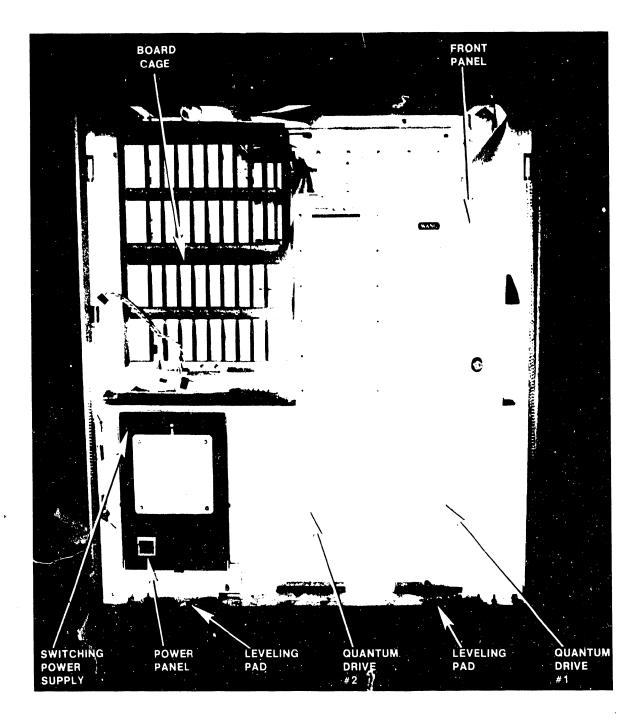

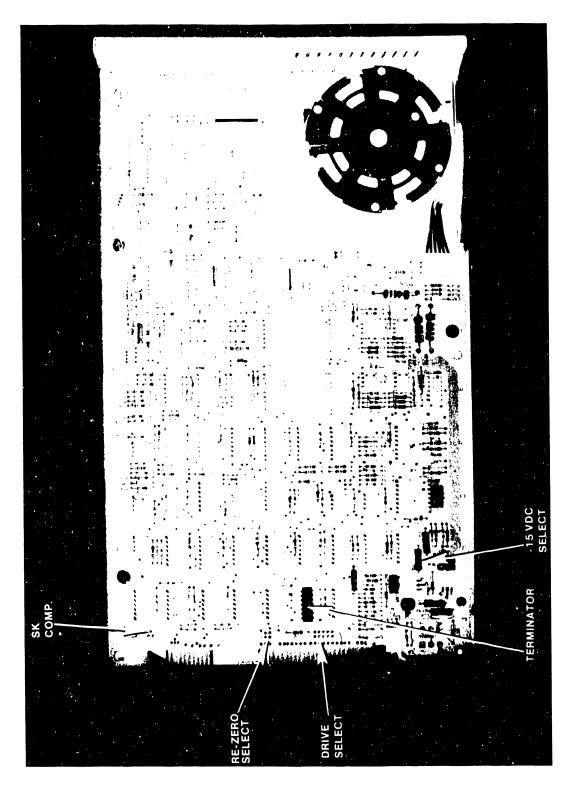

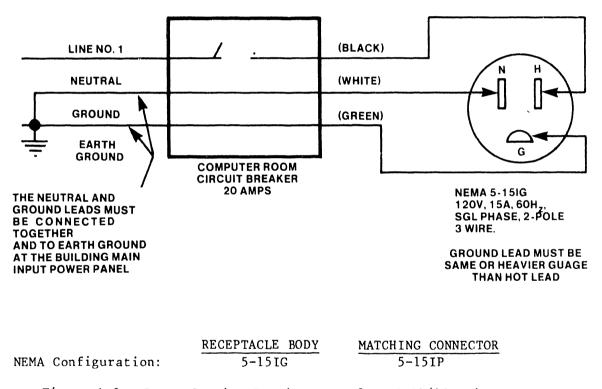

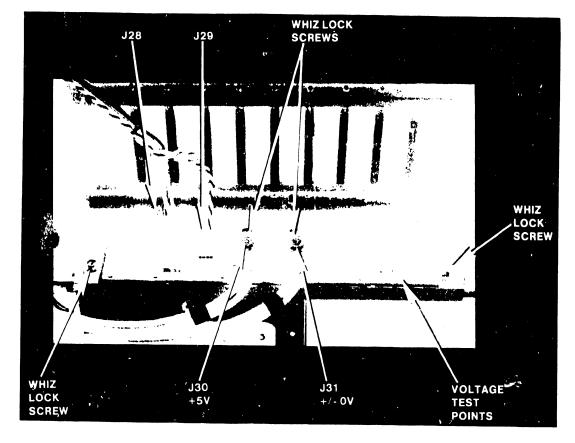

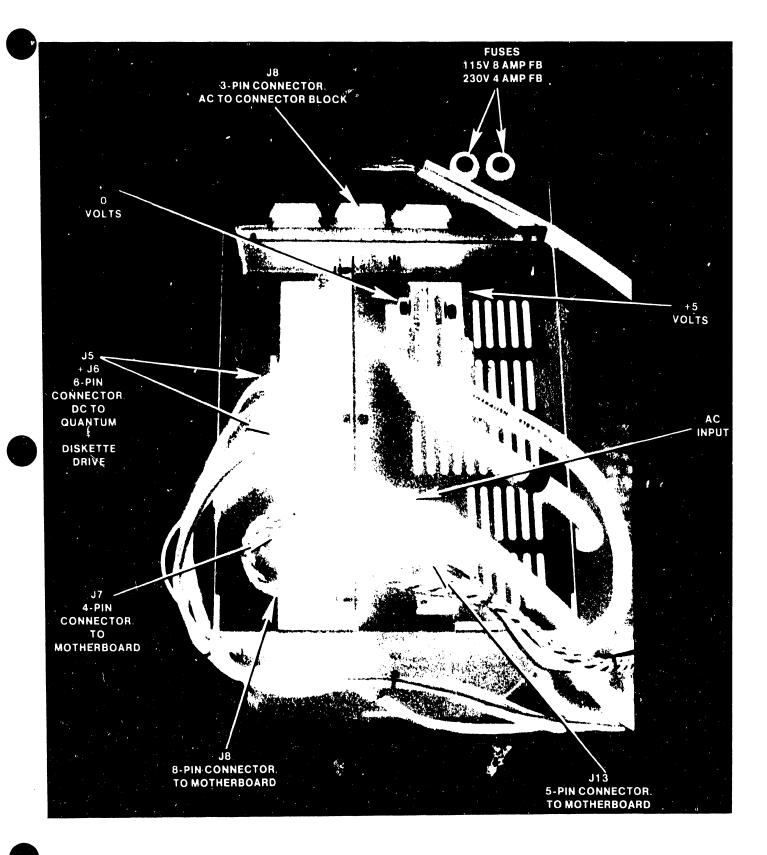

| $\begin{array}{r} 4-1 \\ 4-2 \\ 4-3 \\ 4-4 \\ 4-5 \\ 4-6 \\ 4-7 \\ 4-8 \\ 4-9 \\ 4-10 \\ 4-11 \\ 4-12 \\ 4-13 \\ 4-14 \end{array}$ | VS-25/45 Shipping Carton<br>Swinging Cushion Pallet Feet<br>Rolling Cabinet Off Cushion Palle<br>VS-25/45 With Top and Front Covers Removed<br>Quantum Drive Spindle Lock<br>Quantum Drive Actuator Lock<br>Quantum Drive Jumper Options<br>Power Service Requirements for VS-25/45 Main Frame<br>Motherboard Power Connectors<br>Motherboard Voltage Test Points<br>VS-25/45 Rear Panel Connector Plate Locations<br>SMD Disk DA Rear Cable Connector Panel<br>Telecommunications DA Rear Cable Connector Panel | $\begin{array}{r} 4-7 \\ 4-7 \\ 4-11 \\ 4-13 \\ 4-13 \\ 4-14 \\ 4-15 \\ 4-17 \\ 4-17 \\ 4-32 \\ 4-33 \\ 4-35 \end{array}$ |

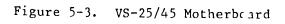

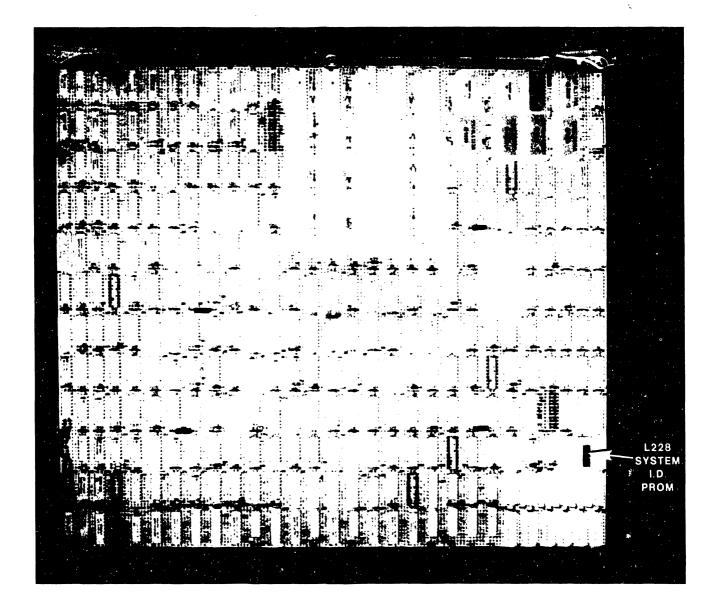

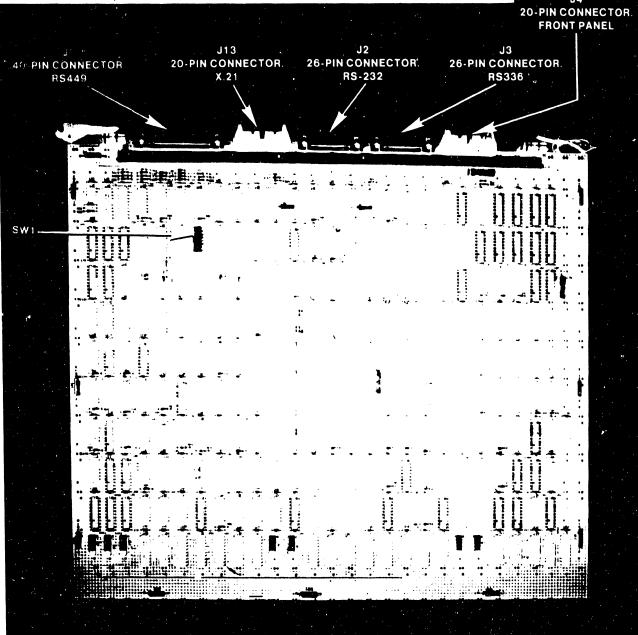

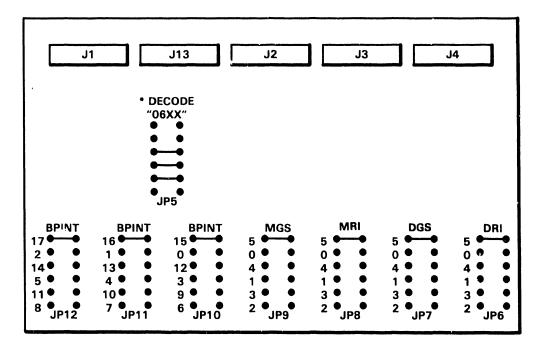

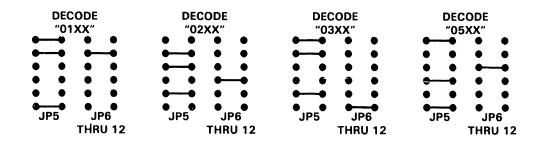

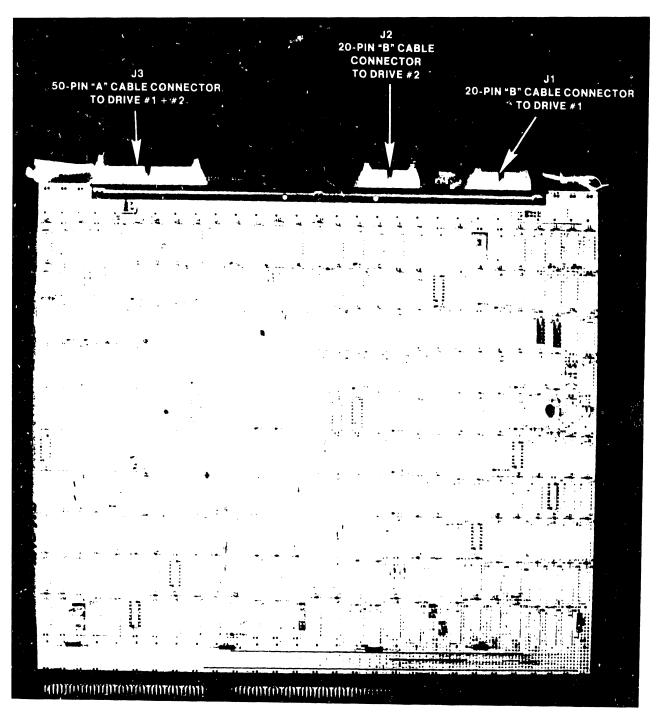

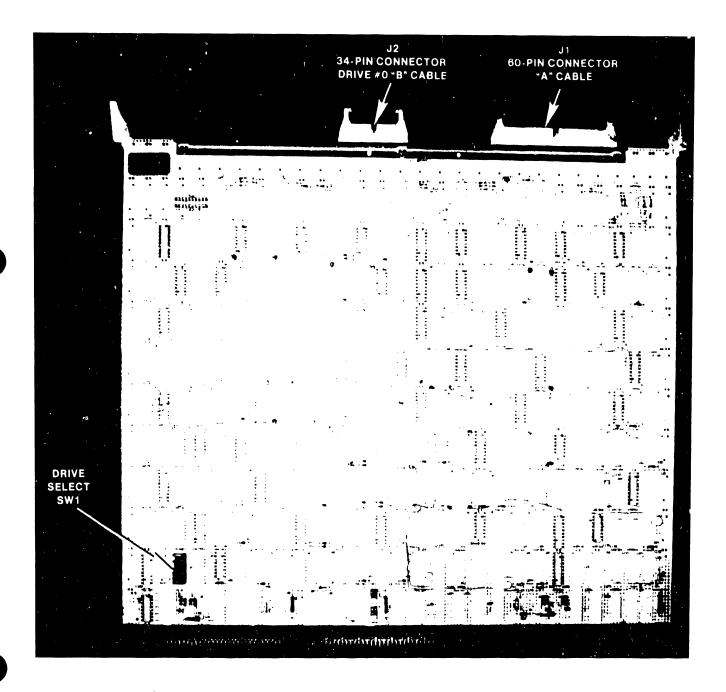

| 5-1<br>5-2<br>5-2<br>5-3<br>5-4<br>5-5<br>5-6<br>5-7<br>5-8                                                                        | Top Cover Removal<br>Top Cover Removal<br>Front Cover Removal<br>Front Cover Removal<br>VS-25/45 Motherboard<br>210-7900 Main Memory Board<br>210-8303 CPU Board<br>210-8304 Bus Processor Board<br>210-7906 Serial I/O Adapter<br>210-7906 Serial I/O Adapter Connector/<br>Jumper Locations                                                                                                                                                                                                                    | 5-4<br>5-5<br>5-6<br>5-8<br>5-9<br>5-11<br>5-14                                                                           |

••••

### LIST OF ILLUSTRATIONS (Cont'd)

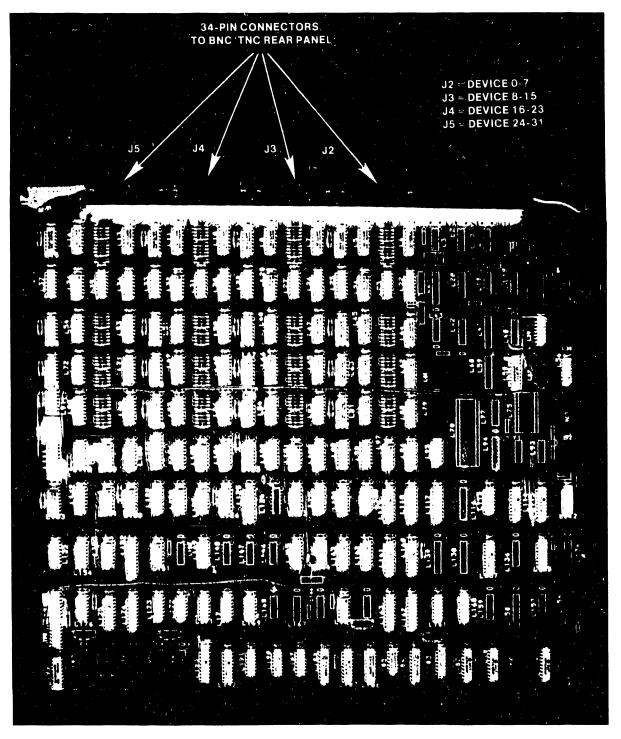

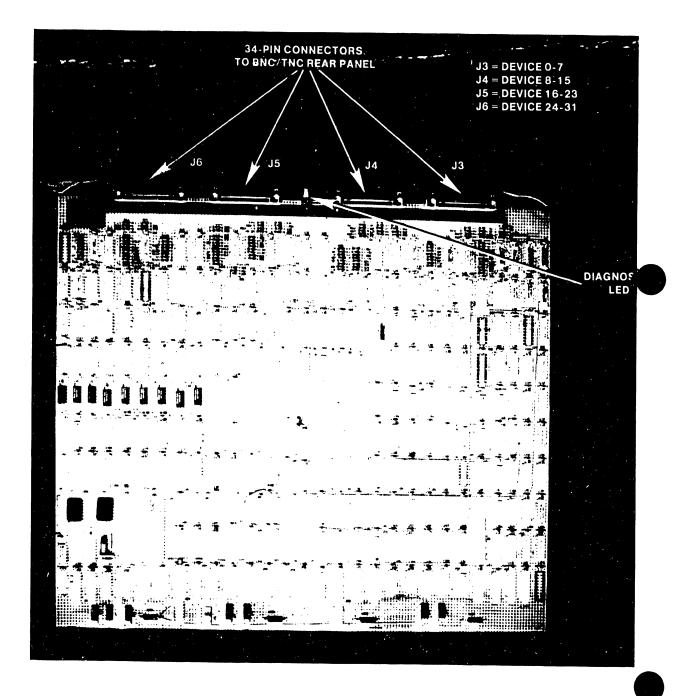

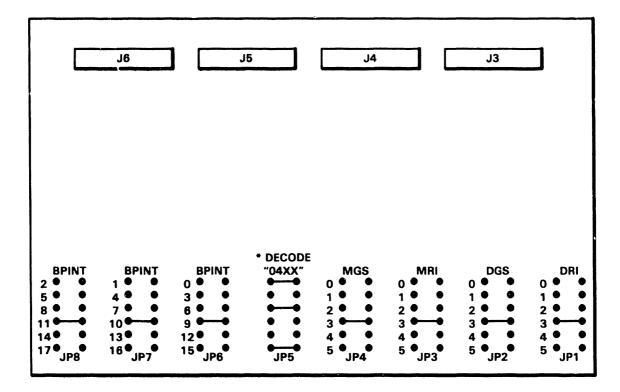

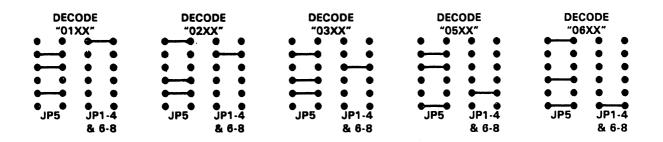

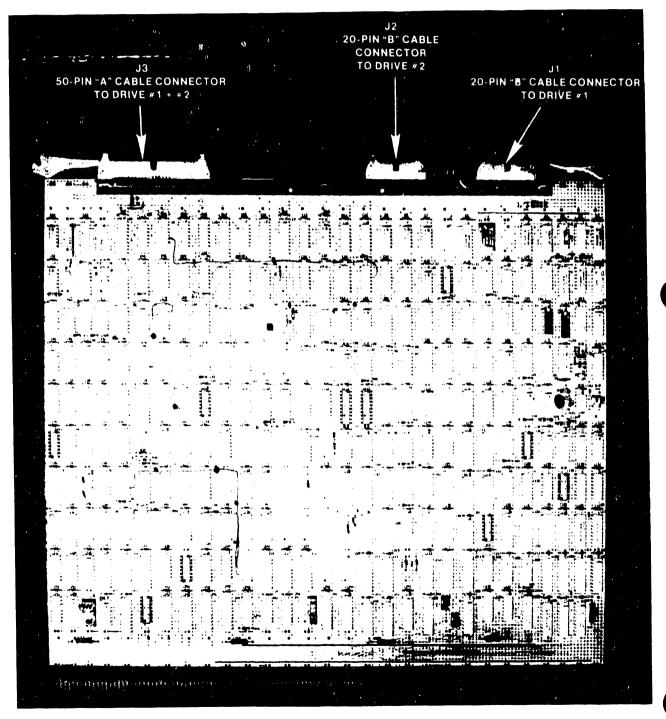

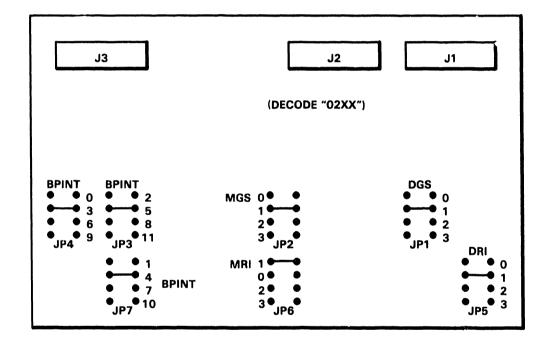

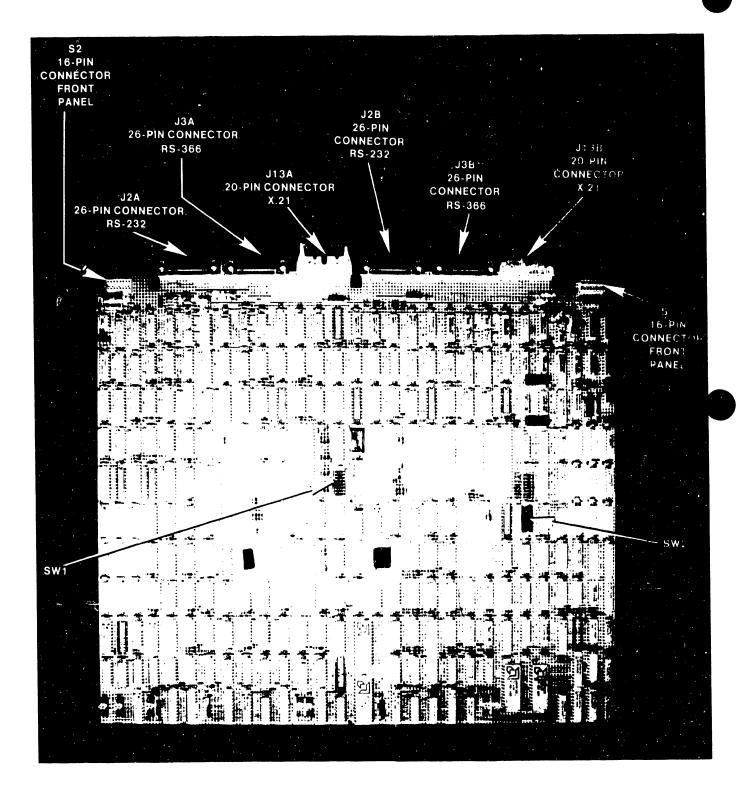

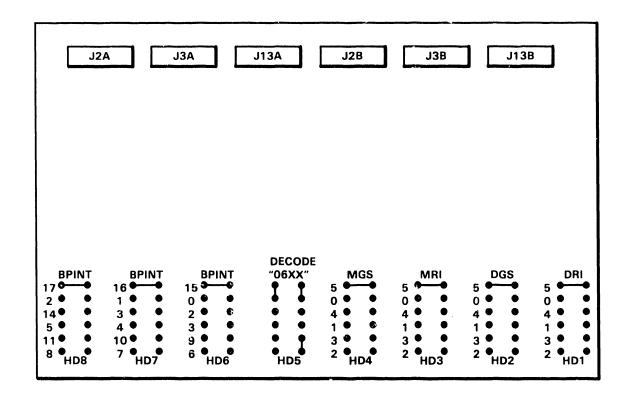

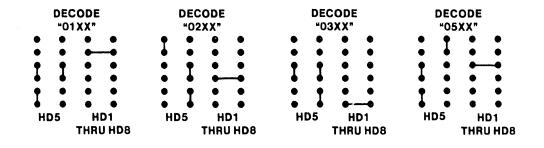

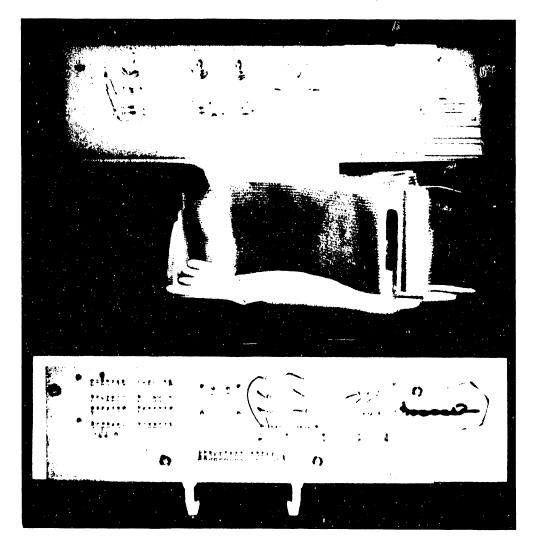

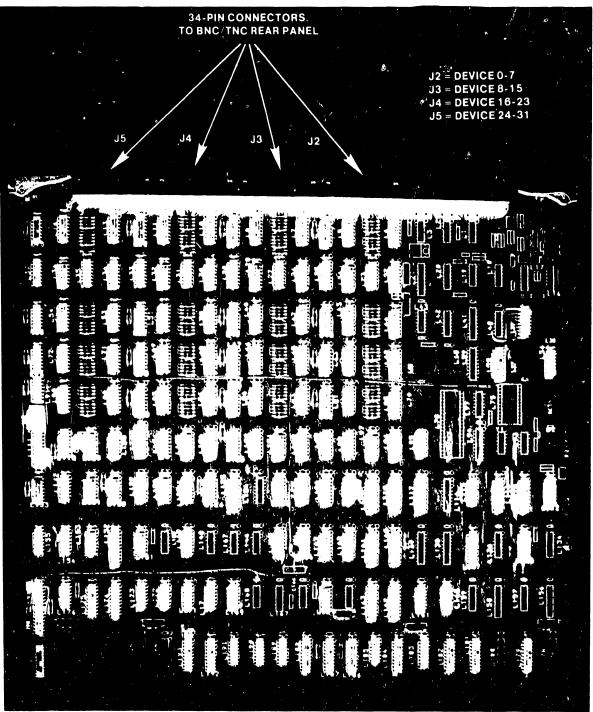

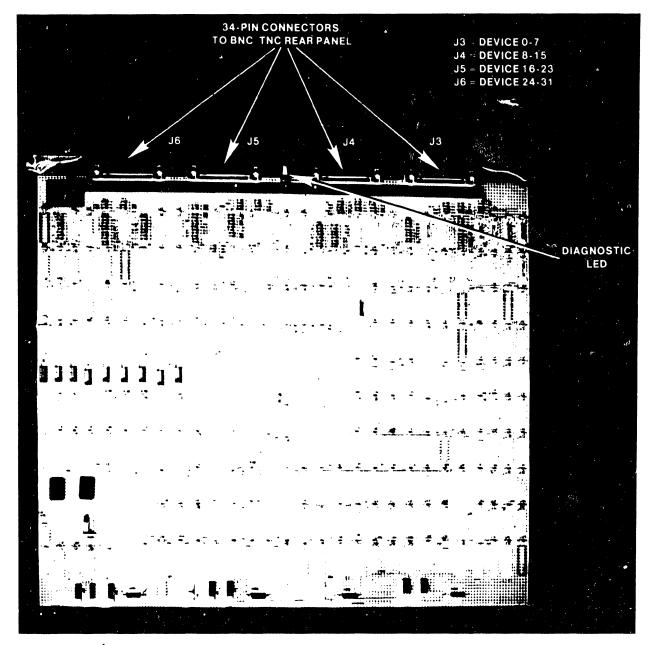

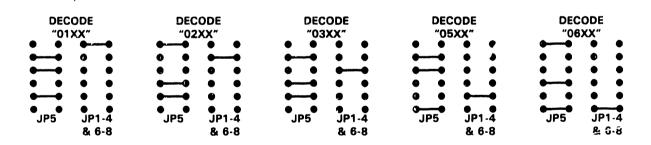

| Jumper Locations         5-17           210-8325 Quantum Dik DA         5-18           5-12         210-8313 2-Port SMD Disk DA         5-19           5-13         210-8313 2-Port SMD Disk DA         5-20           5-14         SMD Disk DA Connector/Jumper Locations         5-21           5-15         SMD Disk DA Connector/Jumper Locations         5-22           5-16         210-8337 1-Port Telecommunications DA         5-23           5-17         210-8637 2-Port Telecommunications DA         5-24           5-18         210-8337 1-Port TC DA Connector/Jumper Locations         5-25           5-19         210-8637 2-Port TC DA Connector/Jumper Locations         5-26           5-20         210-8637 2-Port TC DA Connector/Jumper Locations         5-27           (R1 Version)         5-23         5-17         5-28           5-20         210-8637 2-Port TC DA Connector/Jumper Locations         5-27           (R2 Version)         5-28         5-22         5-27           5-21         Front and Rear View of 210-7913 Front Panel Board         5-28           5-22         Front and Rear View of 200-8014 Telecommunications         5-30           5-24         Motherboard         5-33           5-25         Rear View of Power Supply         5-33 | 5-9<br>5-10 | 210-8616 Intelligent Serial I/O Adapter<br>210-8616 Intelligent Serial I/O Adapter Connector/ |       |

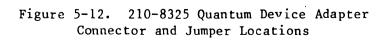

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------|-------|

| 5-12       210-8325 Quantum DA Connector/Jumper Locations       5-19         5-13       210-8313 2-Port SMD Disk DA       5-20         5-14       SMD Disk Da Connector/Jumper Locations       5-21         5-15       SMD Disk DA Connector/Jumper Locations       5-22         5-16       210-8337 1-Port Telecommunications DA       5-23         5-17       210-8637 2-Port Telecommunications DA       5-24         5-18       210-8337/8637 Telecommunications DA Address/       5-25         5-19       210-8637 2-Port TC DA Connector/Jumper Locations       5-25         5-20       210-8637 2-Port TC DA Connector/Jumper Locations       5-27         (R1 Version)       5-21       Front and Rear View of 210-7913 Front Panel Board       5-28         5-22       Front and Rear View of 210-7913 Front Panel Board       5-36         5-23       Motherboard       5-31         5-24       Motherboard       5-31         5-25       Rear View of Power Supply       5-33         5-26       Motherboard Voltage Test Points       5-34         5-27       Quantum Drive Actuator Lock       5-36         5-28       Quantum Drive Actuator Lock       5-37         5-30       Diskette Drive       5-37         5-32       Fan Baffle                                             |             | •                                                                                             |       |

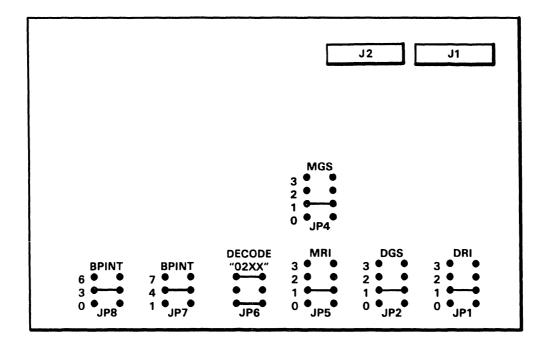

| 5-13       210-8313 2-Port SMD Disk DA       5-20         5-14       SMD Disk Device Type Switch Settings       5-21         5-15       SMD Disk Da Connector/Jumper Locations       5-23         5-16       210-8337 1-Port Telecommunications DA       5-23         5-18       210-8337 1-Port Telecommunications DA       5-24         5-18       210-8337 1-Port To Da Connector/Jumper Locations       5-26         5-19       210-8337 1-Port TC DA Connector/Jumper Locations       5-25         5-20       210-8637 2-Port TC DA Connector/Jumper Locations       5-27         (R1 Version)       5-21       Front and Rear View of 210-7913 Front Panel Board       5-28         5-21       Front and Rear View of 210-7913 Front Panel Board       5-28         5-22       Front and Rear View of 210-7913 Front Panel Board       5-28         5-23       Motherboard Power Connectors       5-30         5-24       Motherboard       5-31         5-25       Rear View of Power Supply       5-33         5-26       Motherboard Voltage Test Points       5-36         5-27       Quantum Drive Spindle Lock       5-36         5-28       Quantum Drive Jumper Options       5-37         5-30       Diskette Drive       5-37         5-31 <td></td> <td>•</td> <td></td>         |             | •                                                                                             |       |

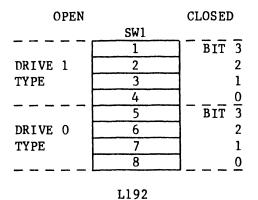

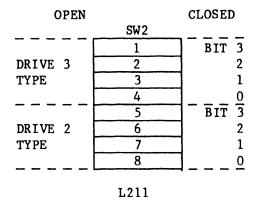

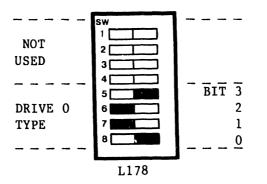

| 5-14       SMD Disk Device Type Switch Settings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-12        |                                                                                               |       |

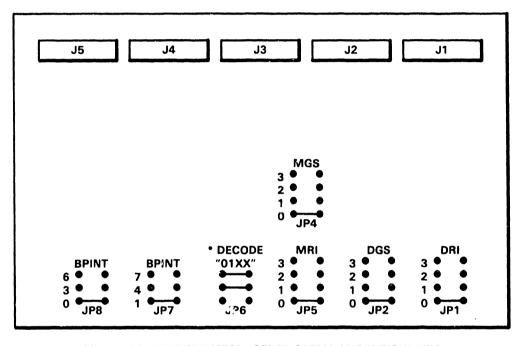

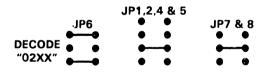

| 5-15       SMD Disk DA Connector/Jumper Locations       5-22         5-16       210-8337       1-Port Telecommunications DA       5-23         5-17       210-8337       2-Port Telecommunications DA       5-24         5-18       210-8337/2-Port Telecommunications DA       5-25         5-19       210-8337/2-Port TC DA Connector/Jumper Locations       5-25         5-20       210-8637       2-Port TC DA Connector/Jumper Locations       5-27.7         (R1 Version)       5-20       210-8637       2-Port TC DA Connector/Jumper Locations       5-27.7         5-20       210-8637       2-Port TC DA Connector/Jumper Locations       5-27.7         (R1 Version)       5-2       5-27.7       (R1 Version)       5-27.8         5-21       Front and Rear View of 210-7913 Front Panel Board       5-28         5-22       Front and Rear View of                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                                                               |       |

| 5-16       210-8337 1-Port Telecommunications DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-14        | SMD Disk Device Type Switch Settings                                                          | 5-21  |

| 5-16       210-8337 1-Port Telecommunications DA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 5-15        | SMD Disk DA Connector/Jumper Locations                                                        | 5-22  |

| 5-17       210-8637 2-Port Telecommunications DA Address/       5-24         5-18       210-8337/8637 Telecommunications DA Address/       5-25         5-19       210-8337 1-Port TC DA Connector/Jumper Locations 5-26         5-20       210-8637 2-Port TC DA Connector/Jumper Locations 5-27         (R1 Version)       5-20a         5-20a       210-8637 2-Port TC DA Connector/Jumper Locations 5-27a         (R2 Version)       5-21         5-21       Front and Rear View of 210-7913 Front Panel Board 5-28         5-22       Front and Rear View of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-16        |                                                                                               |       |

| 5-18       210-8337/8637 Telecommunications DA Address/<br>Status Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5–17        |                                                                                               |       |

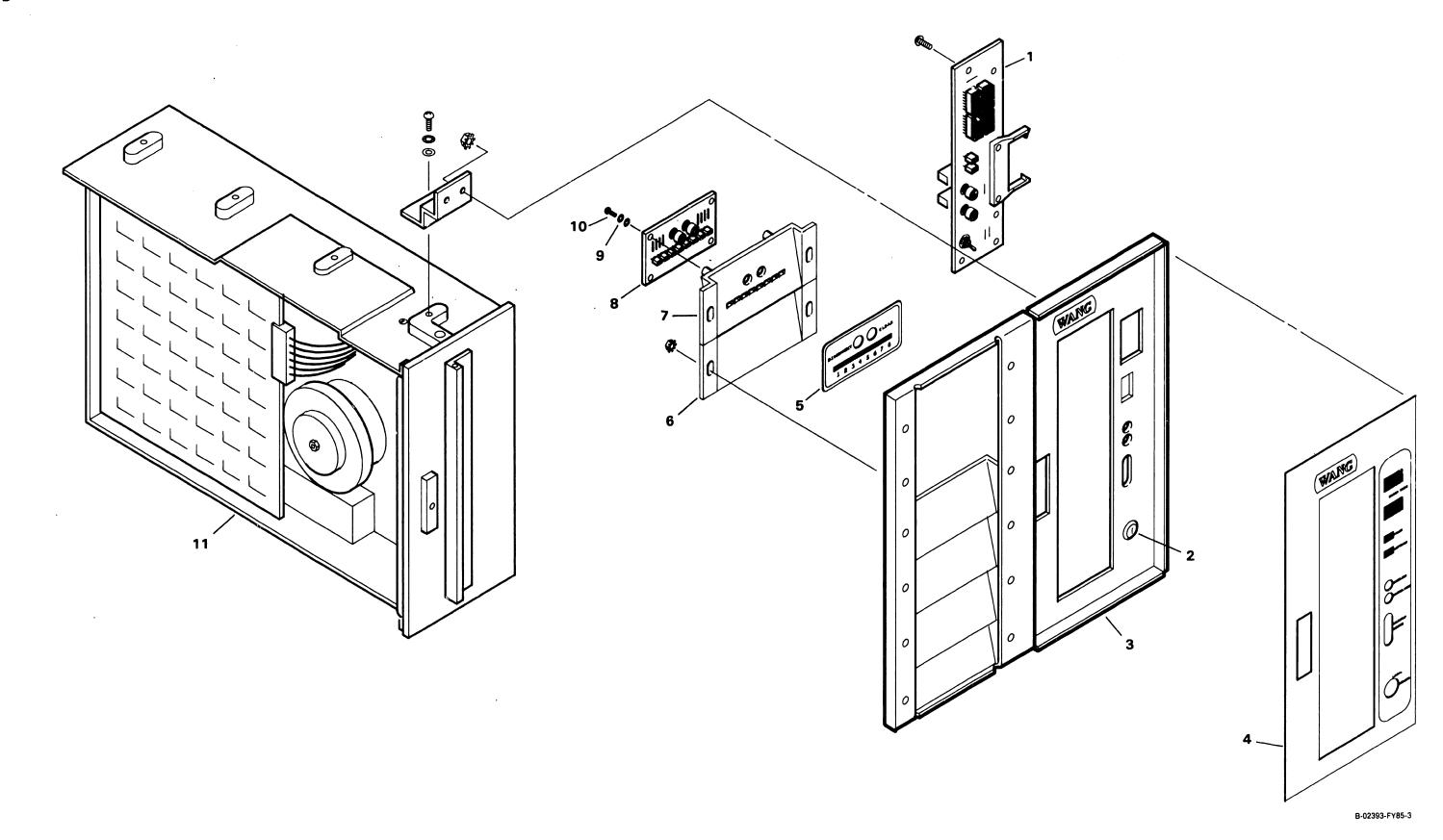

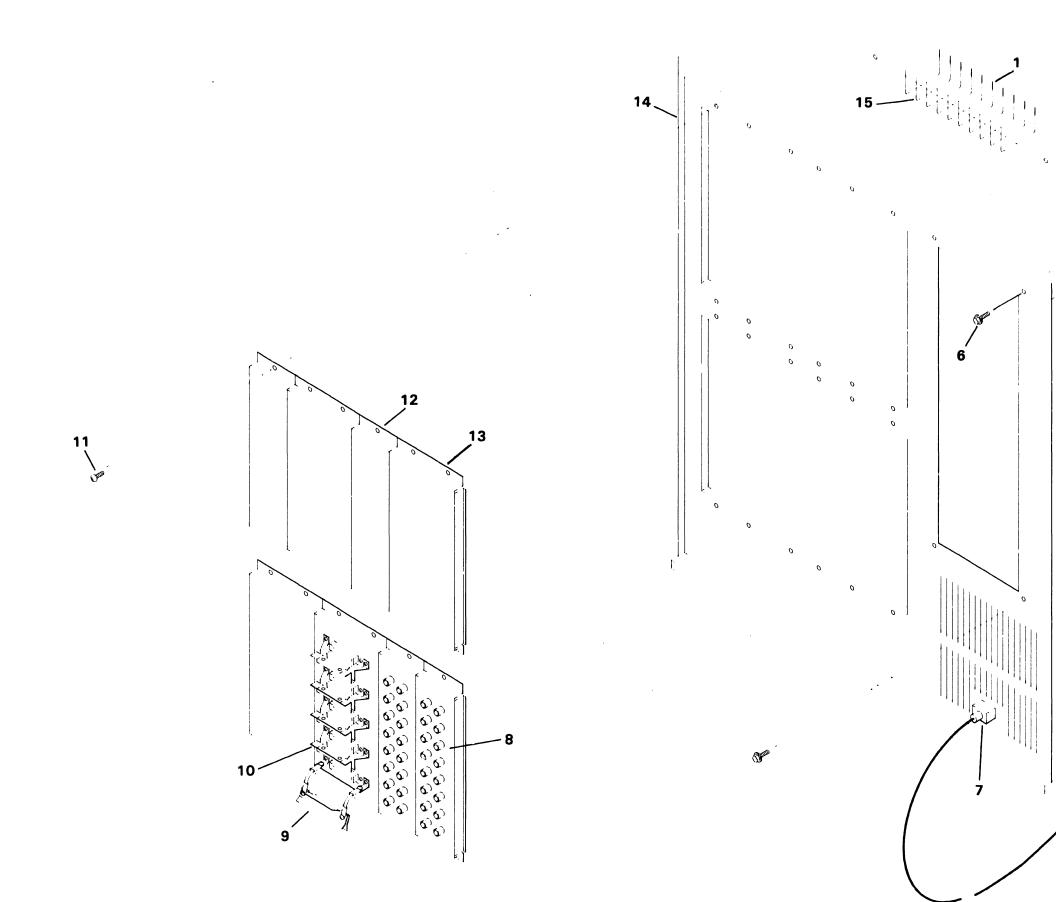

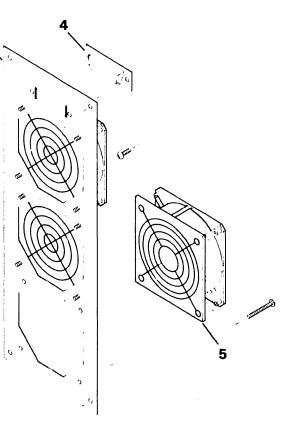

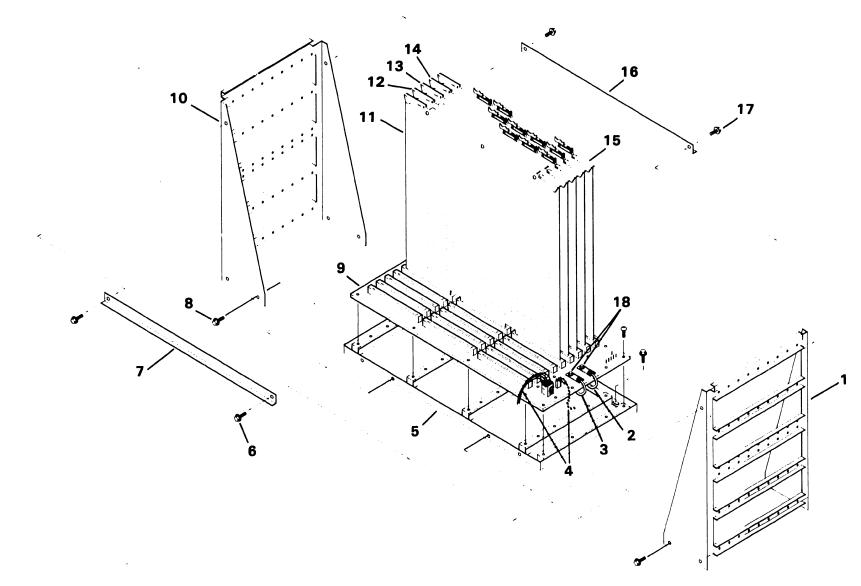

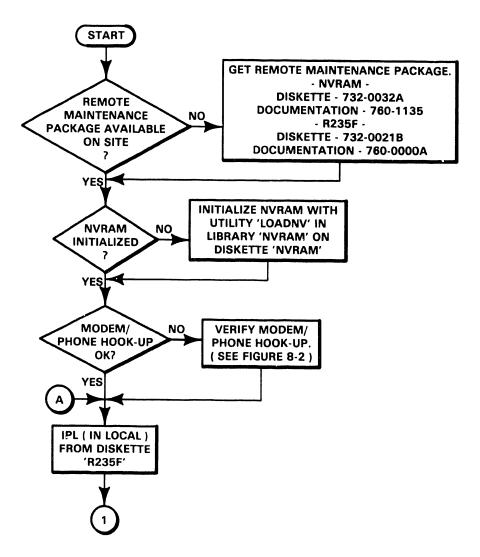

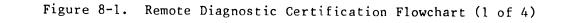

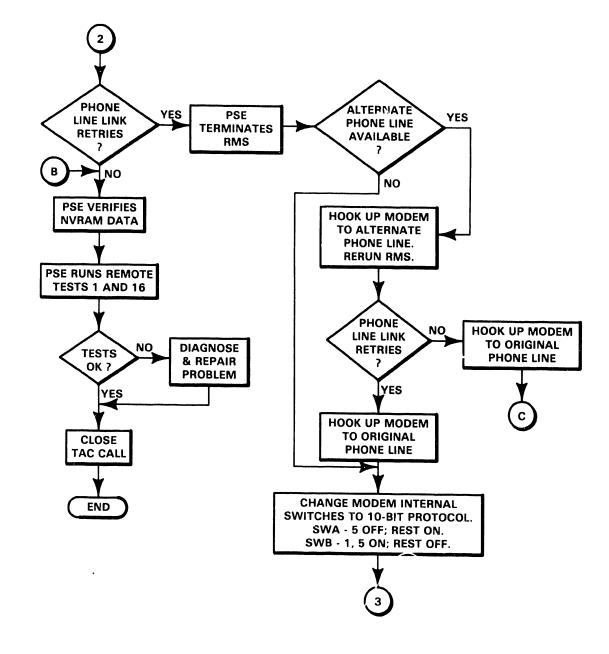

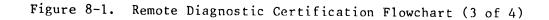

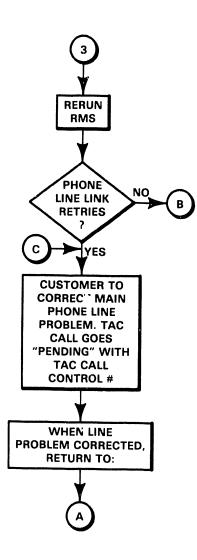

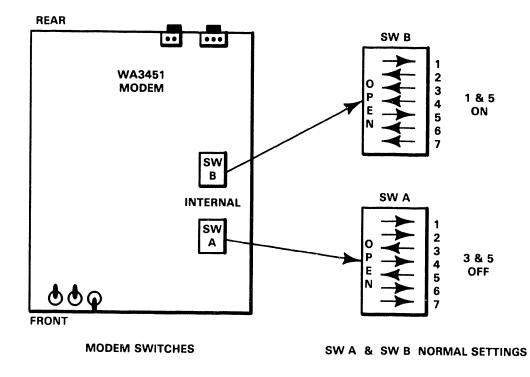

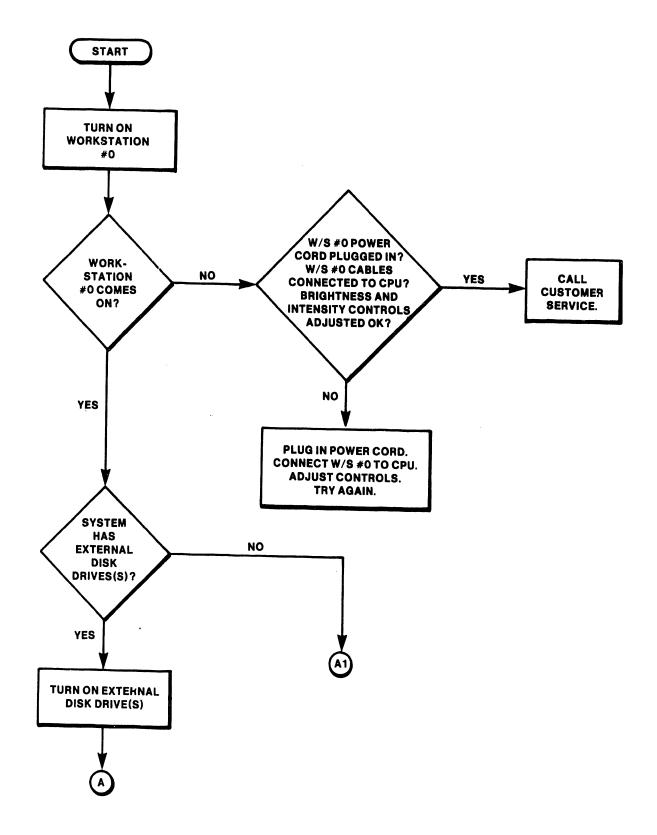

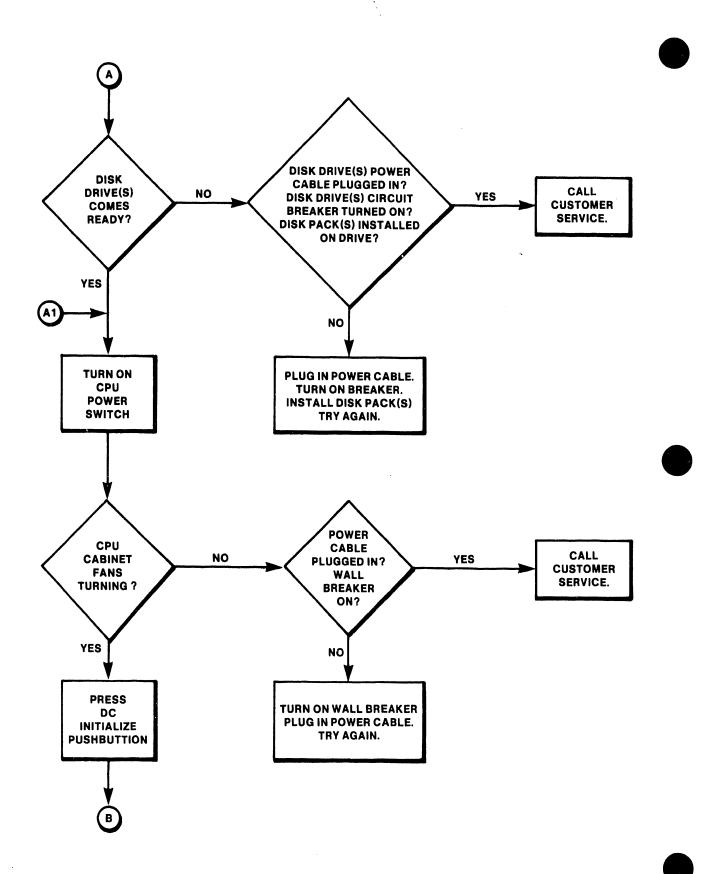

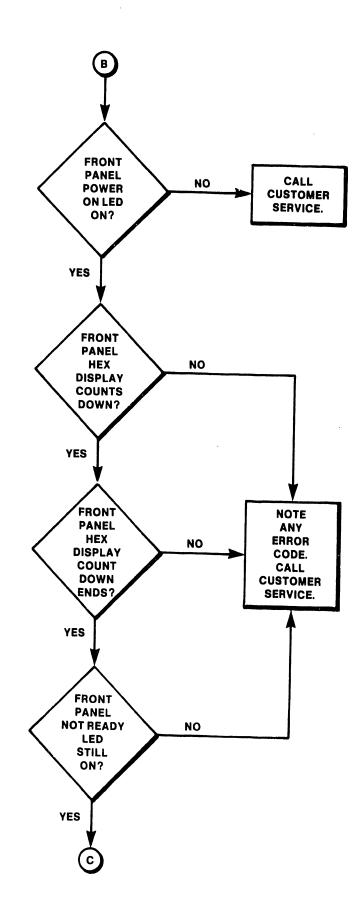

| 5-19210-8337 1-Port TC DA Connector/Jumper Locations5-265-20210-8637 2-Port TC DA Connector/Jumper Locations5-27(R1 Version)10-8637 2-Port TC DA Connector/Jumper Locations5-27a5-20a210-8637 2-Port TC DA Connector/Jumper Locations5-27a(R2 Version)5-21Front and Rear View of 210-7913 Front Panel Board5-285-22Front and Rear View of $\sqrt[4]{2}/0-0814$ Telecommunications5-285-23Motherboard Power Connectors5-315-24Motherboard5-315-25Rear View of Power Supply5-335-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-315-31Fan Panel Assembly7-55-32Fan Baffle7-77-3VS25/45 Cabinet Assembly7-97-4VS25/45 Notherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modme/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-168-5Standard Sequence Display Screen8-16                                                                                                                                                                                                            | 5–18        |                                                                                               |       |

| 5-20       210-8637 2-Port TC DA Connector/Jumper Locations       5-27         (R1 Version)       210-8637 2-Port TC DA Connector/Jumper Locations       5-27a         (R2 Version)       Front and Rear View of 210-7913 Front Panel Board       5-28         5-21       Front and Rear View of 2470-0814 Telecommunications       5-29         5-22       Front and Rear View of 2470-0814 Telecommunications       5-49         5-23       Motherboard Power Connectors       5-30         5-24       Motherboard       5-31         5-25       Rear View of Power Supply       5-33         5-26       Motherboard Voltage Test Points       5-36         5-27       Quantum Drive Spindle Lock       5-36         5-28       Quantum Drive Jumper Options       5-37         5-30       Diskette Drive       5-37         5-31       Fan Panel Assembly       5-41         5-32       Fan Baffle       5-42         7-1       VS25/45 Cabinet Assembly       7-5         7-2       VS25/45 Rear Panel Assembly       7-9         7-4       VS25/45 Rear Panel Assembly       7-9         7-4       VS25/45 Motherboard Certification Flowchart (1 of 4)       8-3         8-1       Remote Diagnostic Certification Flowchart (2 of 4)       8-4                                             |             |                                                                                               |       |

| S-20a(R1 Version)5-20a210-8637 2-Port TC DA Connector/Jumper Locations5-27a(R2 Version)Front and Rear View of 210-7913 Front Panel Board5-285-21Front and Rear View of 210-7913 Front Panel Board5-285-22Front and Rear View of 200-814 TelecommunicationsDA Indicator/Control Pagel5-23Motherboard Power Connectors5-305-24Motherboard Power Connectors5-335-25Rear View of Power Supply5-335-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-375-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-97-4VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-158-4IPL Drive Selection8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                             | 5-19        | 210-8337 1-Port TC DA Connector/Jumper Locations                                              | 5-26  |

| 5-20a210-8637 2-Port TC DA Connector/Jumper Locations5-27a<br>(R2 Version)5-21Front and Rear View of 210-7913 Front Panel Board5-285-22Front and Rear View of 270-0814 Telecommunications<br>DA Indicator/Control Page15-295-23Motherboard Power Connectors5-305-24Motherboard5-315-25Rear View of Power Supply5-335-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle7-47-1VS25/45 Cabinet Assembly7-57-2VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-68-2Moder/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-158-4IPL Drive Selection8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                  | 5-20        |                                                                                               | 5-27  |

| (R2 Version)5-21Front and Rear View of 210-7913 Front Panel Board 5-285-22Front and Rear View of .270-0814 Telecommunications<br>DA Indicator/Control Pagel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | (R1 Version)                                                                                  |       |

| 5-21Front and Rear View of 210-7913 Front Panel Board5-285-22Front and Rear View of $\sqrt{2}70-0814$ Telecommunications<br>DA Indicator/Control Panel5-295-23Motherboard Power Connectors5-305-24Motherboard5-315-25Rear View of Power Supply5-335-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle7-57-2VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-68-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-158-4IPL Drive Selection8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                          | 5–20a       |                                                                                               | 5-27a |

| 5-22Front and Rear View of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | • •                                                                                           |       |

| DA Indicator/Control Pagel5-295-23Motherboard Power Connectors5-305-24Motherboard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             |                                                                                               | 5-28  |

| 5-23Motherboard Power Connectors5-305-24Motherboard5-313-25Rear View of Power Supply5-335-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Rear Panel Assembly7-97-3VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (4 of 4)8-58-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-168-6Error Log Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-22        |                                                                                               |       |

| 5-24Motherboard5-313-25Rear View of Power Supply5-335-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-77-3VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (3 of 4)8-58-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-158-4IPL Drive Selection8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | DA Indicator/Control Papel                                                                    | 5-29  |

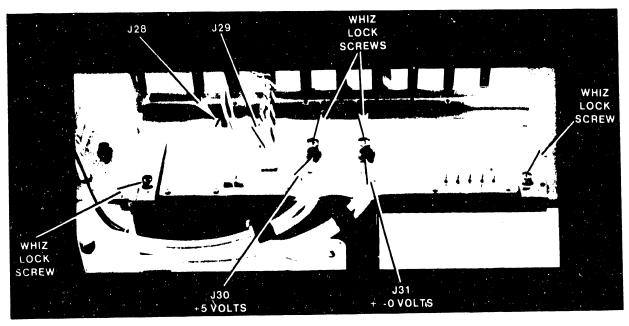

| 5-25Rear View of Power Supply5-335-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-77-3VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (3 of 4)8-58-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | Motherboard Power Connectors                                                                  | 5-30  |

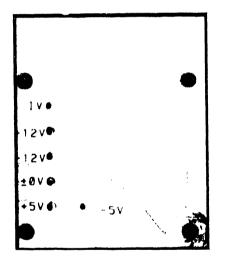

| 5-26Motherboard Voltage Test Points5-345-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-77-3VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (3 of 4)8-58-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5–24        | Motherboard                                                                                   | 5-31  |

| 5-27Quantum Drive Spindle Lock5-365-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-77-3VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (3 of 4)8-58-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5–25        | Rear View of Power Supply                                                                     | 5-33  |

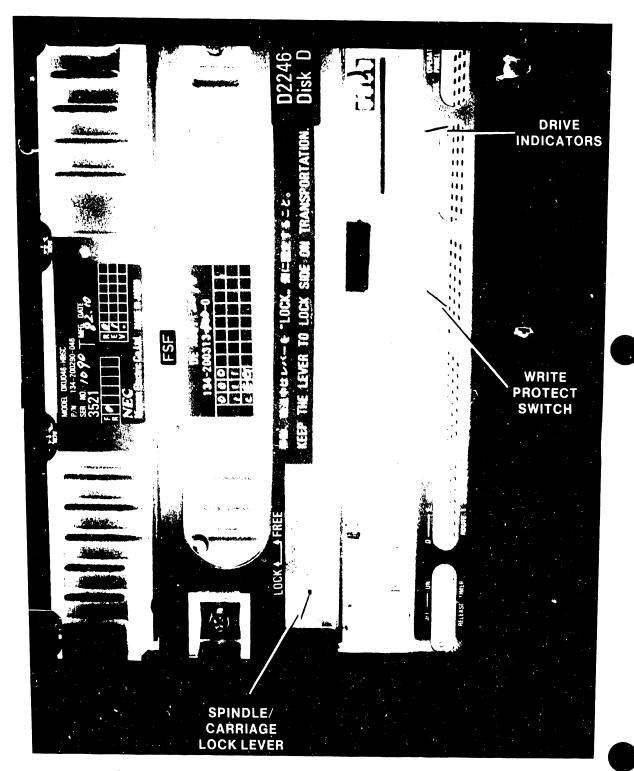

| 5-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-77-3VS25/45 Rear Panel Assembly7-77-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (4 of 4)8-58-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-158-4IPL Drive Selection8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-26        | Motherboard Voltage Test Points                                                               | 5-34  |

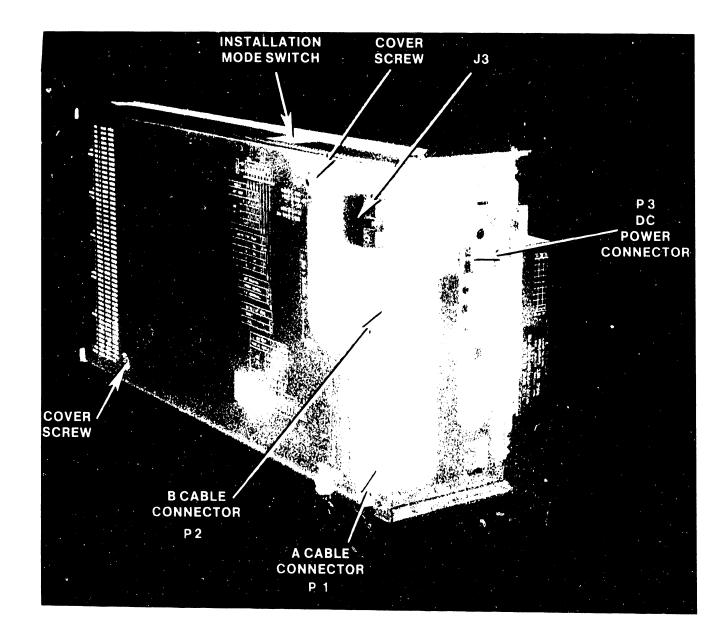

| 5-28Quantum Drive Actuator Lock5-365-29Quantum Drive Jumper Options5-375-30Diskette Drive5-395-31Fan Panel Assembly5-415-32Fan Baffle5-427-1VS25/45 Cabinet Assembly7-57-2VS25/45 Front Panel Assembly7-77-3VS25/45 Rear Panel Assembly7-97-4VS25/45 Motherboard and Card Cage Assembly7-98-1Remote Diagnostic Certification Flowchart (1 of 4)8-38-1Remote Diagnostic Certification Flowchart (2 of 4)8-48-1Remote Diagnostic Certification Flowchart (4 of 4)8-58-1Remote Diagnostic Certification Flowchart (4 of 4)8-68-2Modem/Phone Connections and Modem Switches8-78-3Stand-Alone Diagnostic Monitor Screen8-158-4IPL Drive Selection8-168-5Standard Sequence Display Screen8-18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5–27        | Quantum Drive Spindle Lock                                                                    | 5-36  |