# HARD DISK SUBSYSTEM

## COPYRIGHT

(c) 1983 by VICTOR (R).

All rights reserved. This publication contains proprietary information which is protected by copyright. No part of this publication may be reproduced, transcribed, stored in a retrieval system, translated into any language or computer language, or transmitted in any form whatsoever without the prior written consent of the publisher.

For information contact:

VICTOR Publications 380 El Pueblo Road Scotts Valley, Ca. 95066 (408) 438-6680

#### TRADEMARKS

VICTOR is a registered trademark of Victor Technologies, Inc. XEBEC is a registered trademark of Xebec, Inc. and is used under their expressed written consent. TANDON is a registered trademark of Tandon Corporation, and is used under their expressed written consent. SEAGATE is a registered trademark of Seagate Technology, and is used under their expressed written consent.

First VICTOR printing November, 1983

Printed in U.S.A.

## PREFACE

The purpose of this manual is to provide a source of technical information on the V9000/Sl Microcomputer Hard Disk Subsystem. Although intended for Service Engineers, anyone interested in specifications, architecture, functional theory or maintenance practices will find this manual helpful.

Sections of this manual cover:

- \* Introduction to Winchester Technology

- \* Overview of Hard Disk Subsystem

- \* Winchester Drive Handling Precautions

- \* Host Interface

- \* Winchester Drive Interface

- \* Winchester Disk Drives

- \* Module Replacement Guide

- \* Diagnostic Software

- \* Hard Disk Subsystem Error Reporting

Familiarity with the V9000/S1 microcomputer operation, hardware configuration, and comprehension of the MS/DOS Operating System is recommended before proceeding with this manual.

Logic conventions used throughout this manual may vary as follows; High (true) signals will always be written as in the following example (CLK, WR, RD, DMA-ON, etc.), Low (true) signals might vary as in the following example (CLK/ or CLK or -CLK).

## CONTENTS

## PREFACE

## 1. GENERAL INFORMATION

| 1.1 | Introduction To Winchester Technology |     |

|-----|---------------------------------------|-----|

| 1.2 | Overview of Hard Disk Subsystem       | 1-4 |

| 1.3 | Winchester Drive Handling Precautions | 1-5 |

## 2. HOST INTERFACE

| 2.1 | DMA Boa | ard                                          | L  |

|-----|---------|----------------------------------------------|----|

|     | 2.1.1   | Physical Description 2-1                     |    |

|     | 2.1.2   | Functional Description of DMA Transfer 2-2   | 2  |

|     | 2.1.3   | Theory of Operation 2-2                      | 2  |

|     |         | 2.1.3.1 Host Bus Interface                   | 2  |

|     |         | 2.1.3.2 Controller Interface                 |    |

|     |         | 2.1.3.3 DMA Timing Generator                 |    |

|     |         | 2.1.3.4 Controller Acknowledge Logic 2-5     | 5  |

|     |         | 2.1.3.5 Bus Request Logic 2-5                | ;  |

|     |         | 2.1.3.6 Interrupt Request Latch 2-6          | 5  |

|     |         | 2.1.3.7 Bus Arbitration Logic 2-6            | ;  |

|     |         | 2.1.3.8 Address Counter 2-8                  | •  |

|     | 2.1.4   | DMA Board Schematic and Assembly Drawing 2-1 | .1 |

# 3. WINCHESTER DRIVE INTERFACE

| 3.1 | Xebec | S1410 Dis | k Controller Board 3-1        |

|-----|-------|-----------|-------------------------------|

|     | 3.1.1 |           | al Organization 3-2           |

|     |       | 3.1.1.1   | Host Interface 3-2            |

|     |       | 3.1.1.2   | Processor 3-2                 |

|     |       | 3.1.1.3   | State Machine 3-2             |

|     |       | 3.1.1.4   | SERDES 3-2                    |

|     |       | 3.1.1.5   | Data Separator 3-3            |

|     |       | 3.1.1.6   | Sector Buffer 3-3             |

|     | 3.1.2 | Specific  | ations                        |

|     |       | 3.1.2.1   | Electrical Specifications 3-3 |

|     |       | 3.1.2.2   | Enviromental Specifications   |

|     |       | 3.1.2.3   | Connectors                    |

|     |       | 3.1.2.4   | Connector Pin Assignments 3-4 |

|     | 3.1.3 | Board Se  | tup 3-6                       |

|     |       | 3.1.3.1   | Board Jumpers 3-6             |

|     |       | 3.1.3.2   | Connecting Cables 3-6         |

|     |       | 3.1.3.3   | Address Jumper Group 3-7      |

| 3.1.4 | Theory of Operation                      | 3-8  |

|-------|------------------------------------------|------|

|       | 3.1.4.1 Signal Definitions               | 3-8  |

|       | 3.1.4.2 Detailed Description             |      |

|       | (Handshaking and Timing)                 | 3-11 |

| 3.1.5 | Programming Information                  | 3-14 |

|       | 3.1.5.1 Commands                         | 3-15 |

|       | 3.1.5.2 Control Byte                     | 3-16 |

|       | 3.1.5.3 Logical Address                  | 3-17 |

|       | 3.1.5.4 Request Sense Status             | 3-17 |

|       | 3.1.5.5 Initialize Drive Characteristics | 3-22 |

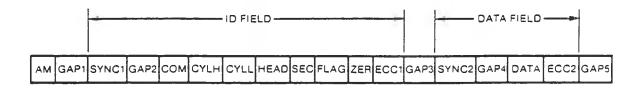

| 3.1.6 | Sector Format                            | 3-22 |

| 3.1.7 | Error Correction Philosophy              | 3-23 |

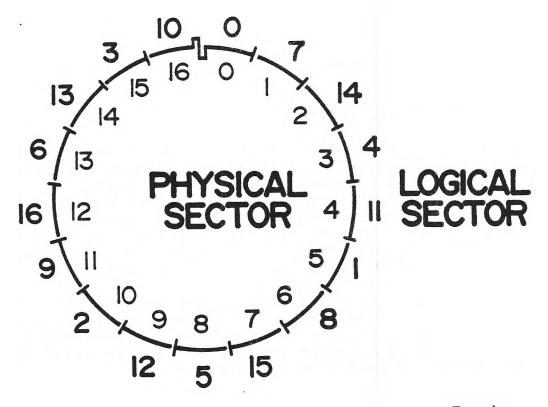

| 3.1.8 | Sector Interleaving                      | 3-24 |

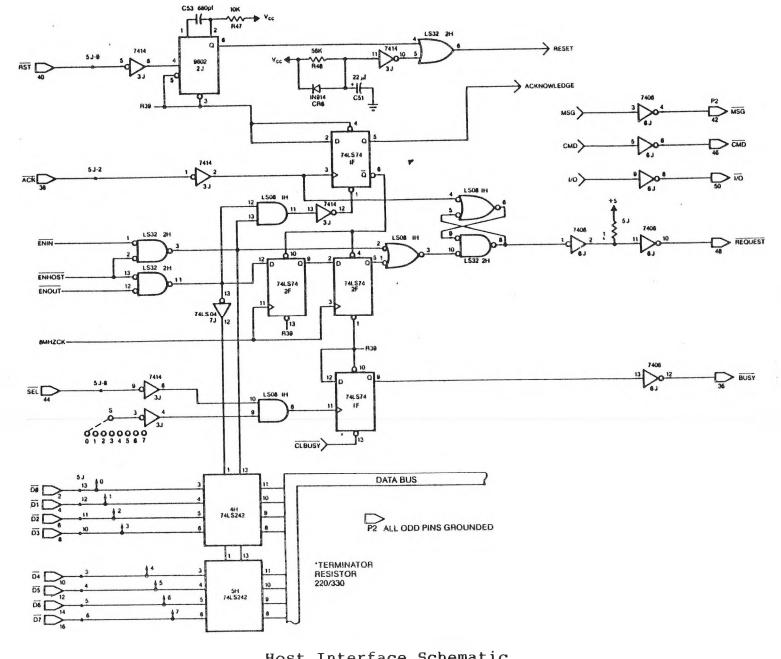

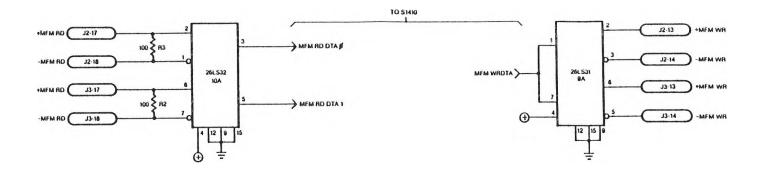

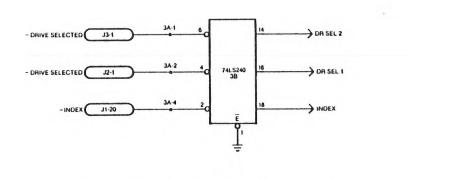

| 3.1.9 | Host and Drive Interface Schematics      | 3-25 |

# 4. MODULE REPLACEMENT GUIDE

| 4.1 | Winchester drive replacement | 4-1  |

|-----|------------------------------|------|

| 4.2 | Xebec Controller Replacement | 4-9  |

| 4.3 | DMA Board Replacement        | 4-10 |

# 5. DIAGNOSTIC SOFTWARE

| 5.1 | HDFIEL           | D Diagnostic Diskette 5-         | -1  |

|-----|------------------|----------------------------------|-----|

|     | 5.1.1            | Test Philosophy 5-               |     |

|     | 5.1.2            | SHOWSTAT                         |     |

|     |                  | 5.1.2.1 Operator Instructions 5- |     |

|     |                  | 5.1.2.2 Error Analysis 5-        |     |

|     | 5.1.3            |                                  |     |

|     |                  | 5.1.3.1 Operator Instructions    |     |

|     |                  |                                  | .10 |

|     | 5.1.4            | DMATEST                          | -   |

|     |                  | 5.1.4.1 Operator Instructions    |     |

|     |                  | 5.1.4.2 Error Analysis           |     |

|     | 5.1.5            | Serial Interrupt Test (SIOITRV3) | 10  |

|     |                  |                                  | 10  |

|     |                  | 5.1.5.2 Error Analysis           |     |

|     | 5.1.6            |                                  |     |

|     | 31210            | 5.1.6.1 Operator Instructions    |     |

|     |                  | 5.1.6.2 Error Analysis           |     |

|     | 5.1.7            | Attributes Test (ATRIB)          | 12  |

|     | J.1.1            | 5.1.7.1 Operator Instructions    |     |

|     |                  | 5.1.7.2 Error Analysis           |     |

|     | 5.1.8            | Floppy Drive Board Test (DBT)    |     |

|     | <b>J * T * O</b> | LIOPPY DIIVE DOGIG IESC (DBL)    | LZ. |

|                                 | 5.1.8.1 Operator Instructions                                    | 5-12 |

|---------------------------------|------------------------------------------------------------------|------|

|                                 | 5.1.8.2 Error Analysis                                           | 5-13 |

| 5.1.9                           | CPU Test (CPU)                                                   | 5-13 |

|                                 | 5.1.9.1 Operator Instructions                                    | 5-14 |

|                                 | 5.1.9.2 Error Analysis                                           | 5-14 |

| 5.1.10                          | Sine Wave Test (SINE)                                            | 5-14 |

| 512120                          | 5.1.10.1 Operator Instructions                                   | 5-14 |

|                                 | 5.1.10.2 Error Analysis                                          | 5-14 |

| 5 1 11                          | Serial Connection Test (SCONNECT)                                | 5-14 |

| <b>J</b> • <b>T</b> • <b>TT</b> | 5.1.10.1 Operator Instructions                                   | 5-15 |

|                                 | $5.1.10.1$ Operator instructions $\dots \dots \dots \dots \dots$ | 5-15 |

| 5 1 10                          | 5.1.10.2 Error Analysis                                          |      |

| 5.1.12                          | System Memory Test (RAMTEST)                                     | 5-15 |

|                                 | 5.1.12.1 Operator Instructions                                   | 5-15 |

|                                 | 5.1.12.2 Error Analysis                                          | 5-16 |

| 5.1.13                          | Timer Interrupt Test (TIMIT)                                     | 5-16 |

|                                 | 5.1.13.1 Operator Instructions                                   | 5-16 |

|                                 | 5.1.13.2 Error Analysis                                          | 5-17 |

| 5.1.14                          | Serial Port Test (SPT)                                           | 5-17 |

|                                 |                                                                  | 5-17 |

|                                 | 5.1.14.2 Error Analysis                                          | 5-17 |

| 5.1.15                          | Keyboard Test (KEYTEST)                                          | 5-17 |

|                                 |                                                                  | 5-18 |

|                                 | 5.1.15.2 Error Analysis                                          | 5-18 |

| 5 1 16                          |                                                                  | 5-18 |

| 2.1.10                          |                                                                  | 5-19 |

|                                 |                                                                  |      |

|                                 | 5.1.16.2 Error Analysis                                          | 5-20 |

| יסמפתמט                         | I Diagnostic Diskette *** Not Released ***                       |      |

| DDDEPU.                         | I Diagnostic Diskette *** Not Released ***                       |      |

5.3 Diagnostic Error Reporting (HDFIELD and HDDEPOT) ..... 5-21

5.2

# LIST OF FIGURES

.

# Page Number

.

.

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6                                                              | DMA Board (Direct Memory Access)<br>DMA Transfer, Block Diagram<br>DMA Board Functional Block Diagram<br>DMA Board Functional Timing<br>DMA Board Schematic<br>DMA PCB Assembly Drawing                                                                                                                                                                                                                                                                                                                                 | -2-2<br>2-3<br>2-6<br>2-11                                                        |

|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

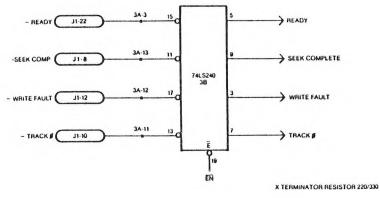

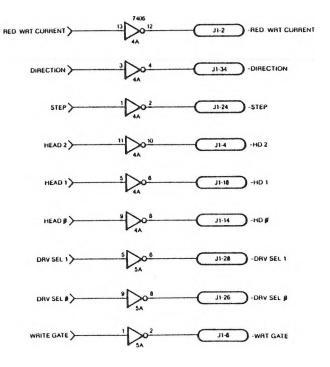

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11<br>3.12<br>3.13<br>3.14 | Xebec Sl410 Controller Board<br>Sl410 Controller, Functional Organization<br>Sl410 Cable, Connector, and Jumper Locations<br>Sl410 Normal (Factory Installed) Address Jumper<br>Sl410 Changed Address Jumper (Controller 1)<br>Controller Select Timing<br>Data Transfer From Host, Timing<br>Data Transfer To Host, Timing<br>Device Control Block (DCB) Format<br>Completion Status Bytes<br>Sector Format<br>Interleave Factor of 5, 17 Sectors<br>Sl410 Host Interface Schematic<br>Sl410 Drive Interface Schematic | 3-2<br>3-7<br>3-8<br>3-12<br>3-13<br>3-14<br>3-15<br>3-16<br>3-23<br>3-24<br>3-26 |

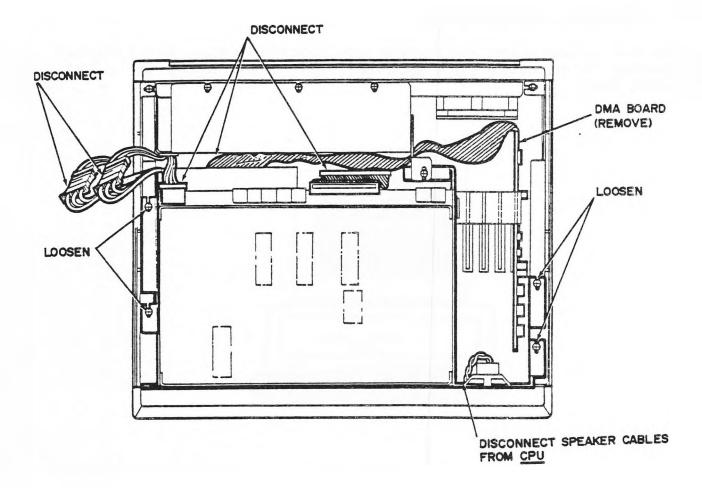

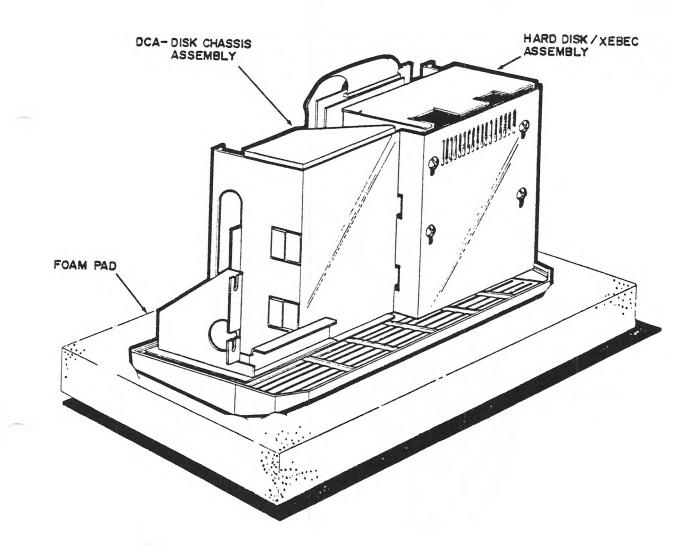

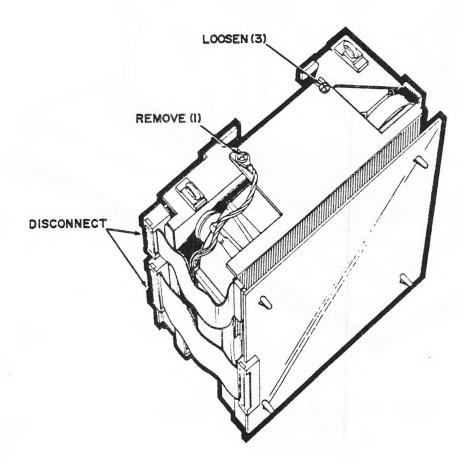

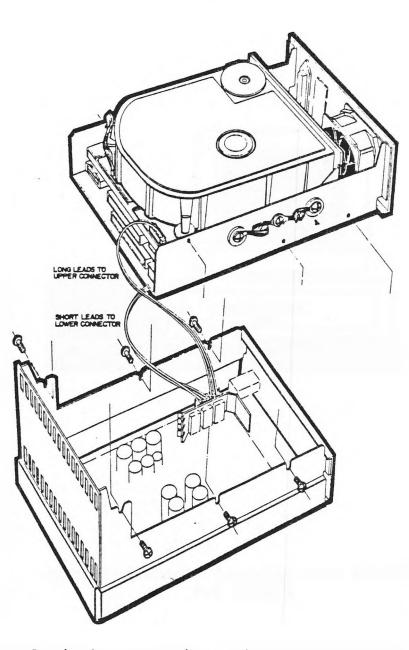

| 4.1<br>4.2                                                                                          | V9000/S1 With Internal Winchester Drive<br>Mainframe, Disk Chassis Assembly (DCA),                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                   |

| 4.3                                                                                                 | and Cables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-2                                                                               |

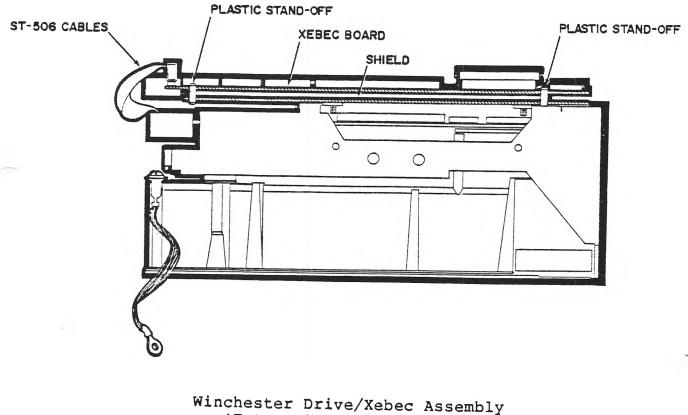

| 4.4                                                                                                 | Disk Chassis Assembly (DCA)<br>Winchester Drive/Xebec Board Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-3                                                                               |

|                                                                                                     | (Internal Configuration)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4 - 4                                                                             |

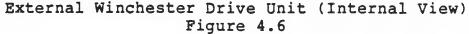

| 4.5                                                                                                 | V9000/S1 With External Winchester Drive<br>External Winchester Drive Unit                                                                                                                                                                                                                                                                                                                                                                                                                                               | 4-5                                                                               |

| 7.0                                                                                                 | (Internal View)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-6                                                                               |

| 4.7                                                                                                 | Winchester Drive/Xebec Board Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                   |

|                                                                                                     | (External Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-7                                                                               |

## LIST OF TABLES

# Page <u>Number</u>

| 3.1  | S1410 Electrical Specifications              |      |

|------|----------------------------------------------|------|

| 3.2  | S1410 Enviromental Specifications            | 3-3  |

| 3.3  | S1410 Controller Mating Connectors           | 3-4  |

| 3.4  | Connector Jl, Control Signals and            |      |

|      | Pin Assignments                              | 3-4  |

| 3.5  | Connectors J2 and J3, Data Signals and       |      |

|      | Pin Assignments                              | 3-5  |

| 3.6  | Connector P2, Host Interface Pin Assignments |      |

| 3.7  | Connector Pl, Power Supply Pin Assignments   | 3-6  |

| 3.8  | S1410 Jumper Locations                       | 3-6  |

| 3.9  | Host Bus Status Signals                      | 3-9  |

| 3.10 | Summary of Host Bus Status Signals           |      |

| 3.11 | Controller - Host Handshaking                | 3-10 |

| 3.12 | Host Bus Control Signals                     |      |

| 3.13 | Host Bus Data Signals                        |      |

| 3.14 | S1410 Controller/System Error Code Summary   |      |

| 3.15 | Sector Field Description                     |      |

|      |                                              |      |

## 1. GENERAL INFORMATION

#### 1.1 INTRODUCTION TO WINCHESTER TECHNOLOGY

The term Winchester comes not from an inventor's name, but from the code name IBM assigned to the development of the Model 3340 disk memory, which was introduced in 1973. The industry as a whole has borrowed the Winchester name and now generally uses it to describe any disk drive using similar technology. The key element of Winchester technology is that the head-to-disk assembly (HDA) is sealed from outside air and the disk is generally non-removable.

In some ways, Winchester technology is similar to conventional hard-disk drives. As with conventional hard disks, the read/write head floats over the recording medium on an air cushion that keeps the head from contacting the disk. In the case of the Winchester, however, the sealed and extremely clean enviroment of the HDA permits the disk designer to "fly" the read/write head closer to the disk surface. In typical removable-media hard-disk systems, the read/write head flies 60 to 70 microinches above the disk surface. The limitation on the distance the head flies above the disk is based on the minimum distance the head can fly safely above the disk and not risk contact with dust or any other contaminant on the disk. Any contact of this type causes the head to stop flying and crash on the disk surface. Such a crash normally ruins the read/write head and the surface of the disk medium, results in a complete loss of data, and necessitates an expensive repair job. Sealing the HDA in a Winchester drive provides a substantially cleaner environment than that of removable-media disks and allows the designer to fly the head about 20 microinches over the disk surface. This lower head altitude provides higher magnetic flux densities at the recording surface and thus higher recording densities on the disk.

During the read/write/seek operations, the Winchester head flies above the surface of the hard disk platter on an air bearing, supported by carefully balanced aerodynamic forces. As the disk starts or stops, the head takes off or lands from the siliconelubricated surface of the platter.

A Winchester drive has one or more rigid disks (or platters) typically 5 1/4 inches in diameter. Each disk is coated on both sides with a magnetic medium, usually iron oxide, so that two surfaces per disk are available for the storage of data. The platters are also coated with a silicon lubicant to allow takeoff and landing of the heads.

Each Winchester head has three rails, or raised surfaces. The trailing end of the middle rail holds a magnetic core with wire

coiled around for writing and reading the data. The two outer rails govern the flow of air. The force that results is sufficient to support a weight of 10 grams at a height of half a micrometer above the disk.

Winchester drives have a number of advantages over conventional hard-disk drives. First, they are very low cost both in absolute terms and in terms of cost per bit of storage capacity. In addition, the sealed enviroment of the HDA produces extremely high reliability with MTBF (mean time between failure) figures quoted in excess of 8000 hours. Winchester disk drives also require no preventive maintenance such as changing air filters or cleaning and aligning heads. The primary disadvantage comes from the fact that the storage medium (the actual disk platter) is not removable. This prevents us from backing up data files in the conventional way (that is, by making and storing an exact copy of the disk to be backed up). However, this problem is overcome in systems that have a floppy disk drive such as the V9000/S1 Hard Disk System. Important files may be periodically backed up and kept on floppies in the event of a crash or media failure.

## 1.1.1 UNDERSTANDING WINCHESTER DISK OPERATION

A Winchester disk is similar to any other disk system in terms of operation and organization. The disk (or platter) can be considered to be composed of concentric tracks of recorded information. Each track is further subdivided into sectors. A typical 5 1/4 inch Winchester drive system may contain upwards of 40,000 individual sectors, each containing its own sector address information and data-storage space. Each track is also contained in what is known as a cylinder. On a single platter Winchester drive a cylinder would contain two tracks, one from the upper surface and one from the lower surface. On a four platter drive the cylinder would contain four tracks, one from the upper and lower surface of each platter. When performing a read/write/ or seek operation the head mechanism, whether two or four heads, positions itself at a certain cylinder and then performs a read or write by turning on one of it's heads.

As the following discussion will show, the operation of a Winchester disk is very similar to that of standard floppy disk drives. The major difference is the speed of operation and the amount of data that a Winchester can hold.

Probably the easiest way to understand disk operation is to go through the steps involved in seeking and reading data on a particular sector of the disk. As the first step in the process, the controller moves the read/write head mechanism to the cylinder containing the desired track by sending control signals to the disk drive. When the read/write head stack is on the proper cylinder, the controller then waits for a specific portion of the disk called the index position (or mark) to pass under the head. This index position provides orientation information which identifies the start of all tracks. Through interpretation of the command from the controller the proper head is then activated to read a particular track once the index mark is found. The controller begins reading the serial data coming from the disk, looking at the sector address information for each sector until it locates the address indicating the desired sector. The data immediately following this address is then captured and the read is completed.

A disk write operation is performed similarly. The same sequence of events occurs until the controller locates the proper sector. At this point, instead of reading data from the disk, the controller sends new data to the disk for recording.

The final point to be covered is how the sector-address information is put on the disk in the first place. This process is called formatting. When a disk is formatted, the controller starts on track 0 and, following the index mark, writes the sector-address information for the first sector on the disk. It then fills the data area following the first address with nulls or other characters to reserve the data space for future use. As soon as it has filled the area, the controller begins the process over again for the next sector, writing the sector-address information and then reserving the data area. This process continues until all the sectors on the first track of the platter are formatted. The controller then formats the remaining tracks in this same manner.

## 1.2 OVERVIEW OF HARD DISK SUBSYSTEM

The V9000/S1 Hard Disk Subsystem consists of three major hardware components; The Winchester Disk Drive, Xebec S1410 Controller, and the Direct Memory Access Interface Board (DMA). The DMA Board resides in a slot of the System Expansion Bus. It connects to the controller via the SASI (Shugart Associates System Interface) cable. The controller connects to the disk via two short cables that comprise an ST506 style interface. ST506 refers to the Seagate Technology drive "model 506", which first used this interface. The disk drive is a 5 1/4 inch Winchester with a formatted capacity of approximately 10.6 megabytes. The disk controller is a Xebec S1410. It performs physical level control of the disk, e.g. move the heads, turn on write current, and return status to the host. It accepts sector oriented commands from the host, e.g. read 64 sectors of data starting at sector 100. The DMA board provides an interface from the host system onto the SASI bus and hence to the controller. The DMA board transfers data between system memory and the Hard Disk Subsystem without CPU intervention.

## 1.3 WINCHESTER DRIVE HANDLING PRECAUTIONS

Winchesters are delicate instruments that require proper care and handling. These units are expected to perform when needed, therefore misuse and/or mishandling will adversely affect the expected performance.

Even though a Winchester Drive is installed in a system it's succeptability to damage is still great. Systems should be given at least 15 seconds on power up or down before movement of the unit. Units should be packed in original shipping containers whenever possible and marked as extremely fragile.

Individual drives should be handled with extreme care. The Winchester Drive can be carried easily in one hand and thus taken for granted. This type of handling exposes the drive to unintentional shock forces and should be avoided. When individual drives are returned they must be packed in a single-pack shipping container (part #187125-01). If more than one drive is returned they must be packed four to a box using the proper shipping container (part #187125-02). When these containers are not readily available packing procedures must adhere to the following guidelines:

## SINGLE DRIVE SHIPPING REQUIREMENTS

Single drives must be protected by at least 4 inches of polyurathane foam on all sides (2072 foam), and placed in a cardboard box whose dimensions assure no movement of the drive. (cardboard box specifications: 175 lb test, RSC double wall, #3W, 2P/1C)

## MULTIPLE DRIVE SHIPPING REQUIREMENTS

When more than one drive is to be returned, no more than four drives are permitted per container. The drives may be placed next to each other but separated by a 200 lb test RSC single wall cardboard divider. The four drives must be tightly packed in no less than 6 inches of polyurathane foam (2072) on all sides and placed in a cardboard box whose dimensions assure no movement of the drives. (cardboard box specifications: 200 lb test, RSC double wall, #3W, 2P/1C)

The following is a list of do's and don'ts concerning Winchester Drives:

- \* Drives should be placed on a foam pad when not in a system or shipping container.

- Never stack drives, even if protected by foam.

- \* No moving parts should be moved, e.g. spindle hub or positioning mechanism.

- \* The sealed drive assembly should never be opened for any reason.

- \* If reformatting of the drive is necessary, allow at least 45 minutes of "power on time" before proceeding.

- Note: Refer to Technical Bulletin #581-228-SB31 for more information concerning returned drives.

#### 2. HOST INTERFACE

## 2.1 DIRECT MEMORY ACCESS BOARD (DMA)

The Direct Memory Access Board makes it possible to transfer large arrays of data between the hard disk and system memory without CPU intervention. This task would be very time-consuming, due to the amount of instructions needed to accomplish the transfer, if DMA were not used.

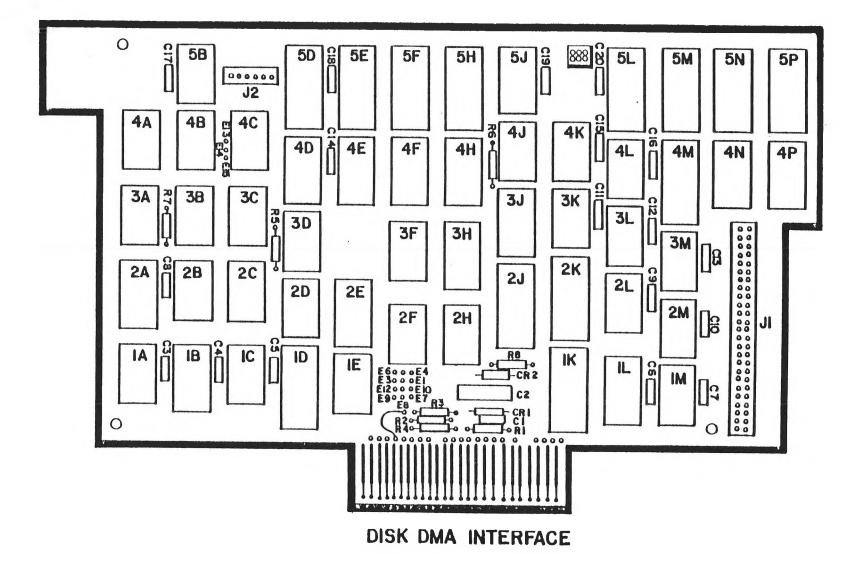

## 2.1.1 PHYSICAL DESCRIPTION

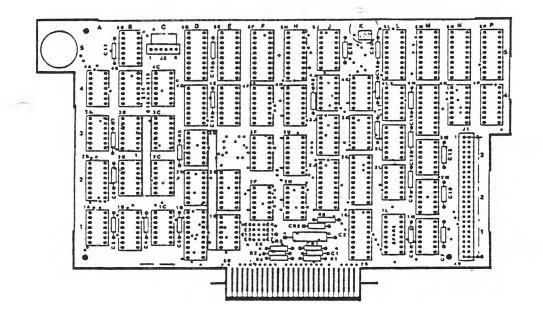

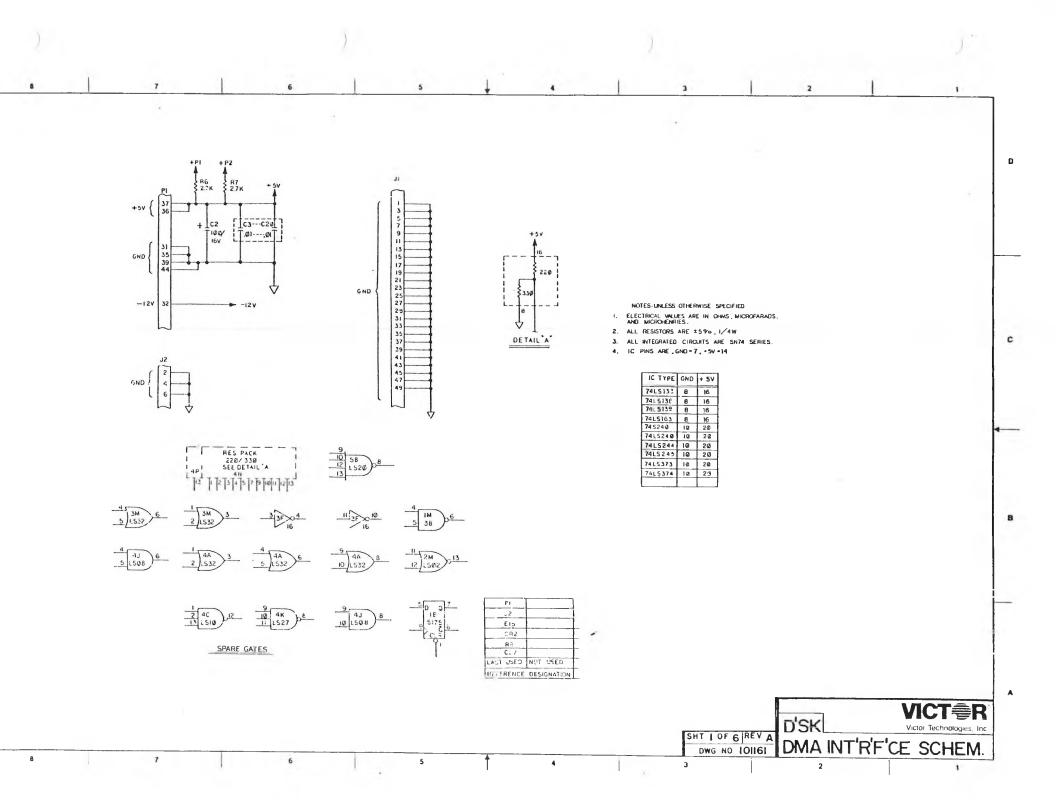

The DMA board shown in Figure 2.1, when installed in the system, may reside in any slot of the expansion bus. The board is keyed in such a way that the component side of the board is always facing the outside of the mainframe when installed.

There are three connectors on the board, Jl (50 pins), Pl (50 pins), and J2 (6 pins). Jl connects the DMA board to the hard disk controller via a 50 pin flat ribbon cable. When connecting this cable make sure pin one (red key of cable) is connected appropriately to pin one of the DMA board and Xebec Controller. Edge connector Pl is inserted into the system expansion bus. Connector J2 is the bus arbitration link if more than one DMA board is used on the expansion bus.

DMA BOARD (DIRECT MEMORY ACCESS) Figure 2.1

#### 2.1.2 FUNCTIONAL DESCRIPTION OF DMA TRANSFER

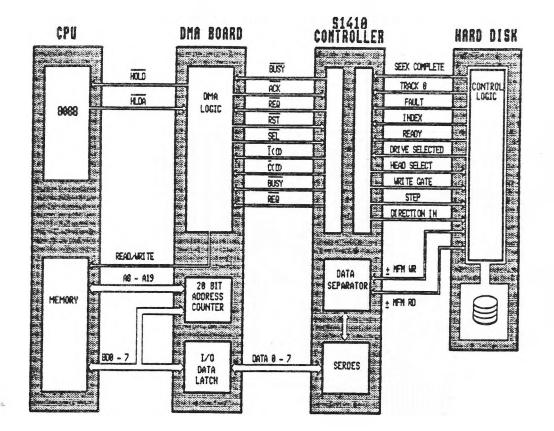

Before any transfer of data to or from the hard disk the DMA Board must be selected. The 8088 addresses the DMA Board at EF300. Once the DMA Board has been selected (DMA-ON), CSEL/ (Controller Select) is generated to the Xebec Controller. The hard disk controller responds with a Controller Request (CREQ) asking for what type of transfer is to take place (Command, Data, or Status). The DMA board recognizes CREQ, issues a HOLD to the 8088 and takes control of the bus for transfer of data to or from the hard disk through a handshake sequence (see section 3.1.4.2).

Control information is supplied to the DMA logic to specify an input or output (READ or WRITE) operation in memory. The address register is loaded with the starting address, and a data exchange between the memory and the hard disk is executed. Following each transfer, the address register is incremented to select the next memory location. When the information exchange is completed, the hard disk controller issues a control command which resets the Hold Request line to the processor. This allows the microcomputer to continue with a normal programmed sequence. (See Figure 2.2)

DMA Transfer Block Diagram Figure 2.2

## 2.1.3 DMA BOARD THEORY OF OPERATION

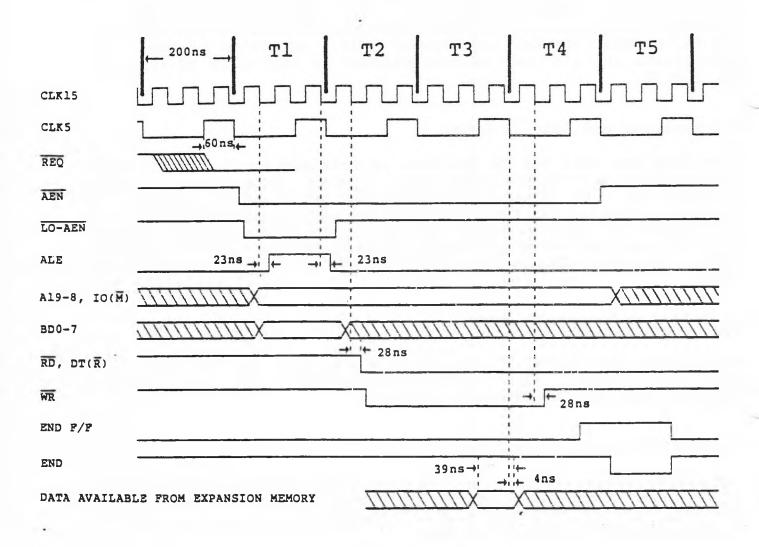

The following sections contain information which should be useful to the persons involved in component level repair of the DMA Board. Refer to Figure 2.3 (DMA Board Functional Block Diagram) shown below, and Figure 2.4 (DMA Board Functional Timing Diagram) on page 2-6, as needed.

DMA Board, Functional Block Diagram Figure 2.3

## 2.1.3.1 Host Bus Interface

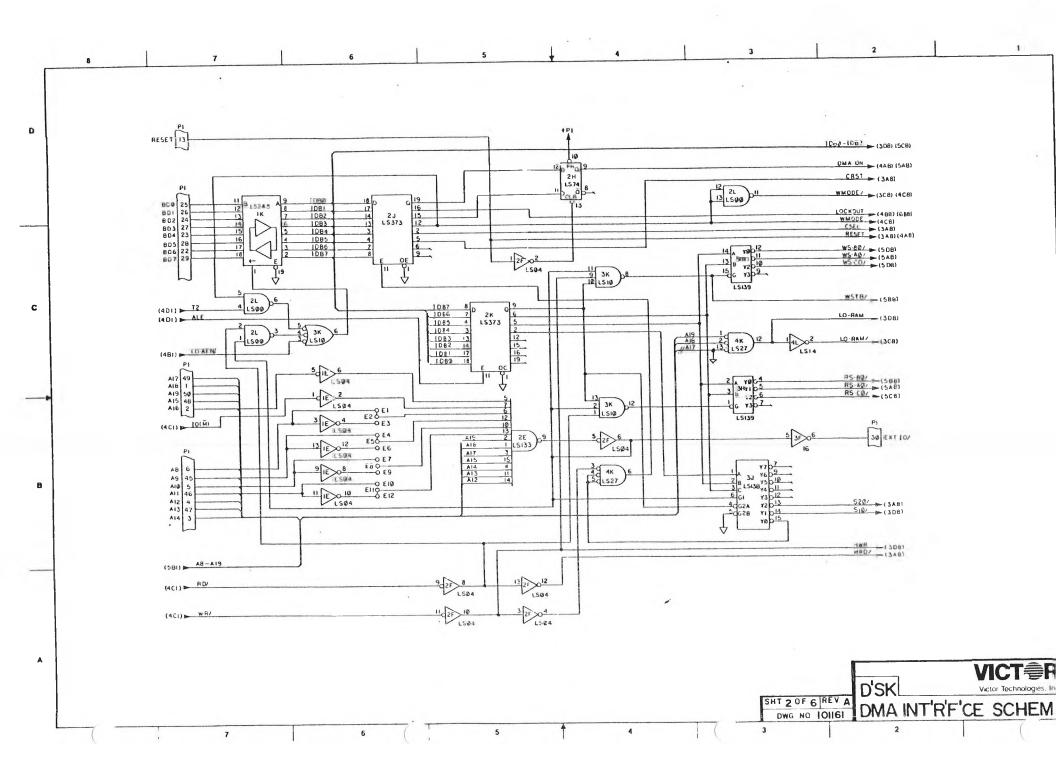

Refer to sheet 2 of the DMA Board Schematic, Figure 2.5, for the following discussion.

## Address Decoding

The lower half of sheet 2 shows the Host Bus Address Decoding Logic.

Address lines Al2 thru Al9, plus signal IO(M/) are decoded by IC's lE and 2E to produce a "Board select" signal. Board Select is used to enable further decoding of address lines to generate chip select signals. Board Select is also buffered by open-collector gate 3F to generate the EXT IO/ signal to the host. This signal disables the host's buffer for on-board I/O devices.

Octal latch 2K freezes the state of the multiplexed address/data bus (IDB0 thru IDB7) at ALE time to produce A4 thru A7. These address lines drive chip select decoding logic composed of IC's 3K, 3H, and 3J. One half of decoder 3H is enabled by board select and WR/, thus, it generates "Write Select" signals WS-80/, WS-A0/, and WS-CO/. The other half of 3H generates only "Read Select" signals in a similar manner. The outputs of decoder 3J are three chip select signals unqualified by RD/ or WR/.

Note that in this address decoding scheme, the default base address of the board is EF300. This is determined by the jumpers at El thru El2. The default (etched) jumper configuration is shown in the schematic. Note also that the chip select signal names indicate the value of A0 thru A7 that will generate the signal. Since A0 thru A3 are not decoded at all they are "don't cares". A4 is also a "don't care" for some signals. For example, the signal WS-80/ is generated by a write to any address in the range from EF380 to EF39F.

## Data Bus Buffer

IC lK is a bi-directional buffer between the host address/data bus and the DMA board. Most of the time lK's direction is driving the DMA board. When the CPU reads a register on the DMA board, and during the data phase (T2) of a DMA write operation, the direction of the buffer is reversed to drive the host bus.

## Control Register

Octal latch 2J is a write only register used to control various functions of the DMA board. Latch 2H conditions the output of 2J to enable/disable DMA mode. The primary function of 2H is ensure that following a system reset the DMA function is disabled.

## 2.1.3.2 Controller Interface

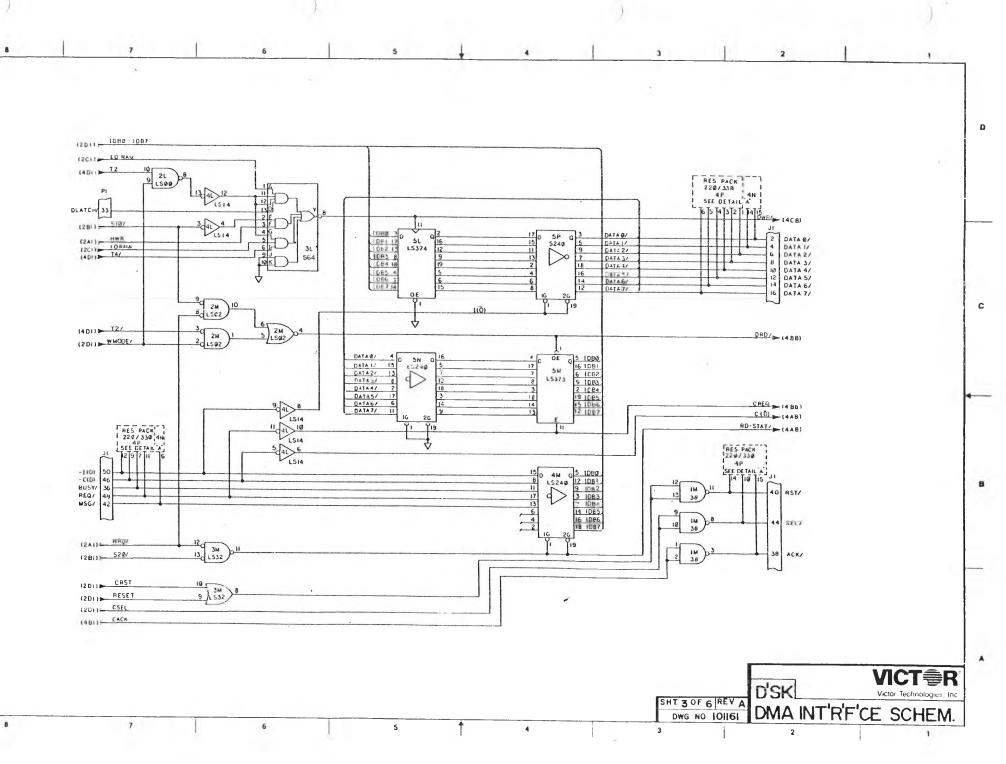

Refer to sheet 3 of the DMA Board Schematic, Figure 2.5, for the following discussion.

Data Out Latch and Bus Driver

Data from the host to the controller is latched by IC 5L and

driven onto the SASI Bus by the tri-state driver 5P. IC 5P is enabled only when the SASI Bus status line I(O/) is in the output state (low).

#### Write Strobe Selector

Data that is read from system memory during a DMA cycle must be latched into IC 5L at just the right moment during the read. If this is a read from "on-board" memory (lo-ram) then the correct moment is the falling edge of DLATCH/. If this is a read from expansion memory then the correct moment is the falling edge of T4/. If this is not a DMA cycle at all, i.e. the CPU is writing directly to the controller, then the correct time is the end of the WR/ strobe (the falling edge of HWR). Selection of the appropriate write strobe is accomplished by the logic of IC's 2L, 4L, and 3L.

## Bus Receiver and Data In Latch

Data from the SASI Bus to the host is received by IC 5N. This is an inverting buffer with PNP inputs to minimize loading on the bus. In addition it has hysterisis to provide extra noise immunity. To minimize ringing, resistor packs 4P and 4N terminate the bus in a resistance that approximates the characteristic impedance of the bus. The output of 5N is latched into 5M by the falling edge of CREQ. Data from the bus is guaranteed to be valid while CREQ is true.

## Read Strobe Enable

The output of tri-state latch 5M is driven onto the DMA data bus when DRD/ is true. DRD/ is true during T2 of a DMA write cycle or during a CPU read of the SASI Data Bus.

## Controller Status In Buffers

Inverting buffer 4M receives the controller status signals I/(0), -C(D), BUSY/, REQ/, and MSG/. The output of 4M is driven onto the DMA data bus during a CPU read of controller status, i.e. when IC 3M detects HRD/ and S20/ as true.

## Controller Reset, Select, and Acknowledge Lines

These three signals are driven onto the SASI bus by open collector buffer 1M. The reset signal (RST/) is caused by a hardware reset at 3M-9 or a programmed reset (CRST) at 3M-10. CRST can be activated by writing to the control register. The RST/ signal is

normally active only for a single pulse during system initialization.

Controller select (SEL/) is activated by writing to the control register. It is pulsed at the beginning of every controller command. Controller acknowledge (ACK/) is generated after the host has read or written a byte of data in response to the controllers request signal (REQ/). See Section 2.1.3.4 for a description of the Acknowledge Logic.

## DMA Board Functional Timing Diagram Figure 2.4

## 2.1.3.3 DMA Timing Generator

Refer to the top half of sheet 4, DMA Board Schematic (Figure 2.5), for the following discussion.

## Shift Register and End Flip-Flops

The five flip-flops contained in IC's lA and lB are wired as a shift register clocked by the falling edge of CLK5. A DMA cycle begins when a START/ pulse at OR Gate 2B is clocked into the first cell of the shift register. The output of this cell is fed back to OR gate 2B to hold the start signal. The start signal propagates into succesive cells with each falling edge of CLK5 until finally it is clocked into the END flip-flops with the rising edge of CLK5. The output of the END flip-flops ANDed with CLK5 low generates an END pulse that resets the shift register. The output of the shift register is five staggered timing signals: AEN (T1), T2, T3 (not used), T4, and T5 (END). AEN goes true first, followed by T2 200ns later and so on with T3, T4, and T5.

## Host Bus Control Decoding

The staggered timing signals from the shift register are decoded by NAND gates 1C and 2B to generate the host bus control signals; ALE, RD/, and WR/. These are latched by 1D on the falling edge of CLK15. This is to eliminate decoding transients. Latch 1D also provides tri-state bus driving capability. It is enabled onto the host bus during AEN. Pull-up resistors R2, R3, and R4 prevent RD/, WR/, and DT(R/) from floating during bus exchange between the CPU and DMA. Likewise, R1 and other components form a constant-current pull-down network to prevent ALE from floating to an active state.

## 2.1.3.4 Controller Acknowledge Logic

Refer to sheet 4 of the DMA Board Schematic, Figure 2.5, for the following discussion.

On sheet 4 of the schematic, zones (B thru C) by (6 thru 8) contains the Controller Acknowledge Flip-Flops. The Write Acknowledge Flip-Flop is set by DWR/. This happens whenever the CPU or DMA writes data to the SASI bus. The Read Acknowledge Flip-Flop is set whenever the CPU or DMA reads the SASI data bus.

## 2.1.3.5 Bus Request Logic

Refer to the bottom half of sheet 4, DMA Board Schematic (Figure 2.5), for the following discussion.

#### New Request Latch

New Request Latch, 3D, is set every time the controller asserts CREQ and with C(D/) in the data state, i.e. bus requests are not generated by controller requests for command or status byte transfer. In addition, DMA-ON must be true. When a DMA cycle is actually granted the New Request Latch will be cleared during T2. The output of the New Request Latch drives the DMA start logic on sheet 6 of the schematic, and Bus Request Latch, 3D.

## Hold Request Latch

The Bus Request Latch generates a hold request (HOLD/) to the CPU, synchronous with CLK5. Unlike the New Request Latch, this latch is not necessarily cleared by a DMA cycle. If CPU LOCKOUT mode is programmed then gates 2B and 2C form a feedback path to keep the bus request latch set until a RELEASE/ signal is applied to its clear input. RELEASE/ is caused by either a RESET signal or a controller request time out.

## Request Time-Out Counter

IC 2A counts the number of CLK5's between controller requests. If the count reaches 16 then a signal is generated to release the bus to the processor. This is to ensure that the bus is released between sector bursts of a multi-sector transfer.

#### 2.1.3.6 Interrupt Request Latch

Refer to sheet 4 of the DMA Board Schematic, Figure 2.5, for the following discussion.

When the controller requests the transfer of command or status bytes, Interrupt Request Latch 3C is set. Thus IR4 (optionally jumperable to IR5) is asserted to the Programmable Interrupt Controller on the CPU board. The interrupt latch is cleared by a CPU read of SASI bus status.

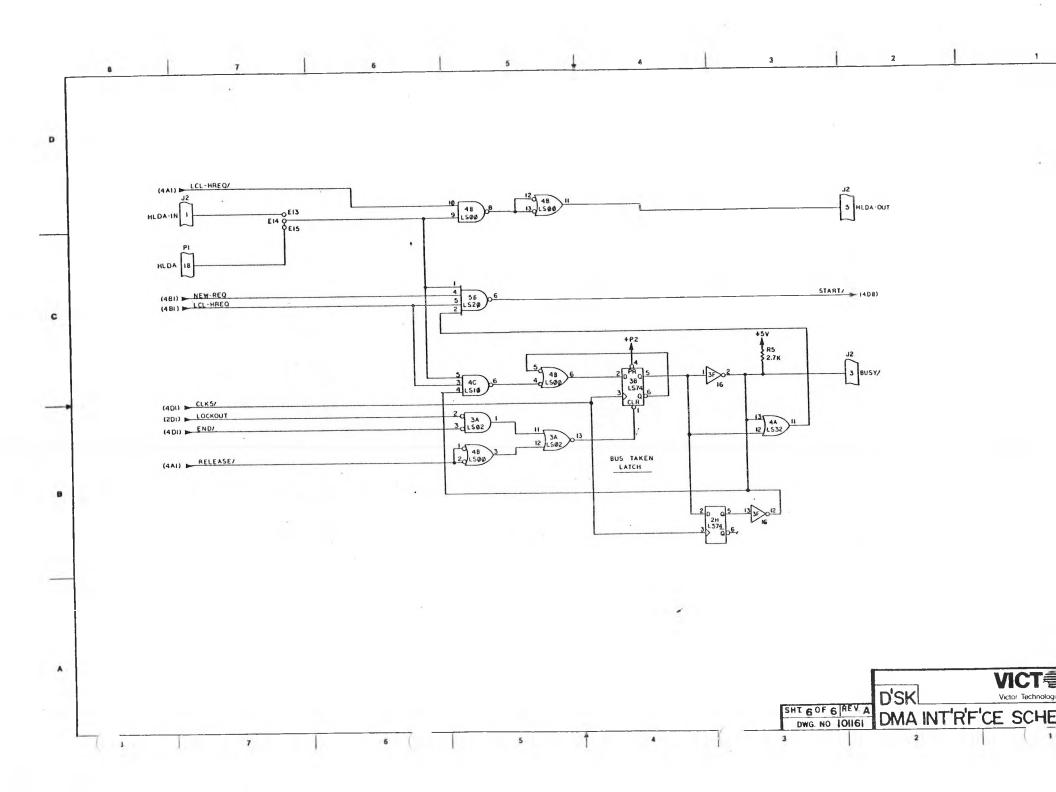

## 2.1.3.7 Bus Arbitration Logic

Refer to sheet 6 of the DMA Board Schematic, Figure 2.5, for the following discussion.

When more than one DMA board (or Bus Master) is used in the system the bus arbitration logic is used to prevent bus contention between the peripheral devices, their respective DMA board, and the host memory via the 6 pin connector "J2" located on the top edge of the board.

## Hold Acknowledge Chain

The jumper configuration in the upper left corner of sheet 6 allows HLDA (Hold Acknowledge) to be chained from the "primary" bus master board (DMA board for example) to another bus master board. The primary bus master board being the first in line to receive HLDA from the 8088 via the expansion bus. With the second DMA board strapped E14-E13 HLDA is asserted via the primary bus master board. If signal LCL-HREQ/ (Local Hold Request) is true HLDA is prevented from entering the next bus master board indicating the primary board is contolling the bus.

#### Start Logic

The START/ signal from nand gate 5B pin 6 is used by the DMA Timing Generator (sheet 4) to begin a DMA cycle. To accomplish this HLDA from the 8088 must be true at 5B pin 1, a request must have been generated by the controller to assert NEW-REQ at 5B pin 4, LCL-HREQ must be true at 5B pin 5, and the bus must have been taken by the active DMA board.

## Bus Taken Latch

Once the 8088 has acknowledged a controller request by asserting HLDA the active DMA board issues a BUSY/ signal to indicate it has taken control of the bus. Connector J2's BUSY/ line is bidirectional in operation so either board may respond with a BUSY/ signal. (device 3F is open collector)

Bus Taken Latch 3B generates an 800ns BUSY signal from the Q output pin 5. Once 3B is set the Q/ output pin 6 (feedback enable line thru 4B) assures the Bus Taken Latch remains enabled. Latch 3B is set as a result of HLDA true (4C pin 5), LCL-HREQ true (4C pin 3), and the bus must not be busy (4C pin 4).

## Busy Stretch Latch

BUSY at pin 5 of 3B is also routed to the latch at 2H known as the Busy Stretch Latch. This latch delays the BUSY signal by one CLK5 or 200ns. Open collector inverter 3F pins 2 and 12 inverts the BUSY signal from 3B pin 5 respectively and the wire-ored connection of 3F pins 2 and 12 results in a 1 us BUSY/ signal. This extra stretch assures a full DMA cycle.

## Bus Release Logic

Gate 3A and 4B make up the Bus Release Logic. Only two situations will cause the DMA board to release the bus. Either END/ is true

(indicated by the completion of a DMA cycle) or by RELEASE/ (caused by a system reset or controller timeout). Either of these situations will clear the Bus Taken Latch thus releasing the bus.

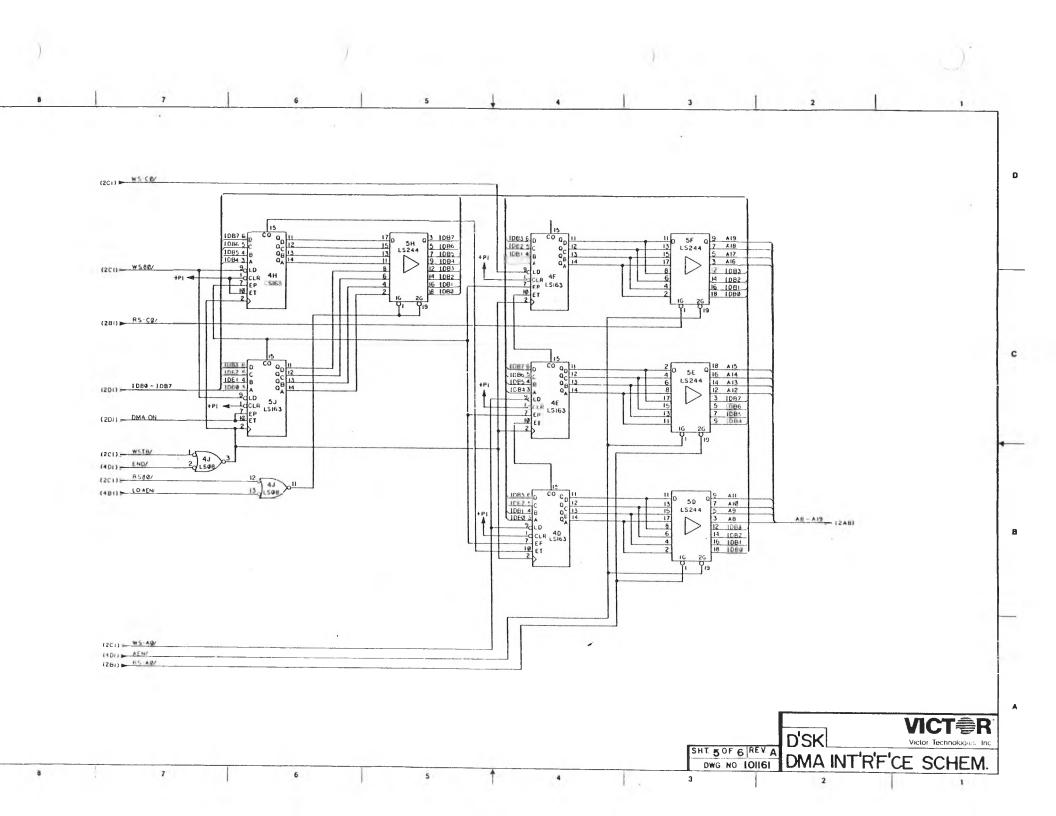

## 2.1.3.8 Address Counter

Refer to sheet 5 of the DMA Board Schematic, Figure 2.5, for the following discussion.

Located on sheet 5 is the 20 bit DMA Address Counter with tristate outputs. The Low Byte Counter consists of 4H and 5J (address EF380), Middle Byte Counter 4E and 4D (address EF3A0), and High Nibble Counter 4F (address EF3Co). Beginning a DMA transfer these counters are loaded with the starting address in system memory where data from the hard disk will be stored. Each DMA cycle increments the counter by one.

Address data is sent via the IDB0-7 Bus to the 20-bit counter. Signal DMA-ON enables the first half of the Low Byte Counter at 5J pin 7 and 10. Low Byte address is loaded into 4H and 5J by signal WS80/ (Write Select EF380) from the Write Select Decoder on sheet 2. Clocking for the Low Byte Counter as well as the Mid and High Counters is provided by signal WSTB/ (Write Strobe) at 4J pin 1. Signal END/, which is active at the end of the DMA cycle is used to increment the counters. The carry output of 5J pin 15 is used to enable the EP input of the other counters in the chain. Low Byte Counter carry out (pin 15 of 4H) enables the ET input of Mid Byte Counter 4D pin 10. (Input ET is fed forward "internally" to enable the carry output of each LS163 Counter)

Readback of the address counter is accomplished by the LS244's at 5H, 5F, 5E and 5D. Low Byte IDB0-7 is read via the 244 at 5H when RS-80/ (Read Select EF380) or LO-AEN/ (Low Address Enable) are true. Mid Counter 4E and 4D are read back via 5E and 5D respectively requiring RS-A0/ (Read Select EF3A0) and AEN/ (Address Enable) true. High Counter 4F is read back via 5F requiring RS-C0/ (Read Select EF3C0) and AEN/ true. A8-19 is fed directly to the expansion bus.

## 2.1.4 DMA BOARD SCHEMATIC AND ASSEMBLY DRAWING

Contained on the following pages is the schematic #104741 and assembly drawing #104740 of the DMA Board.

DMA Board Assembly Drawing #104740 (Sheet 1 of 1) Figure 2.6

## 3. WINCHESTER DRIVE INTERFACE

# 3.1 XEBEC S1410 DISK CONTROLLER BOARD

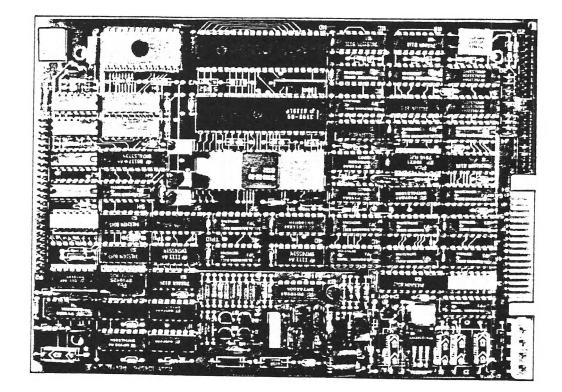

The S1410 Contoller, shown in Figure 3.1, boasts the following operating and design features:

- \* Interlocked data transfer through the Shugart Associates System Interface (SASI)

- \* Microprocessor-based architecture

- \* Full-sector buffer (256 or 512 bytes)

- \* Hardware 32-bit ECC polynomial with ll-bit burst correction

- \* Field proven data separator

- \* Seagate ST506 disk interface

- \* Automatic retries during disk access

- \* Internal Diagnostics

- \* Automatic burst error detection and correction

- \* Separate sector format for ID and data fields with individual ECC fields for both the ID and data fields

- \* High level command set

- \* Variable interleave

## XEBEC S1410 CONTROLLER BOARD Figure 3.1

#### 3.1.1 FUNCTIONAL ORGANIZATION

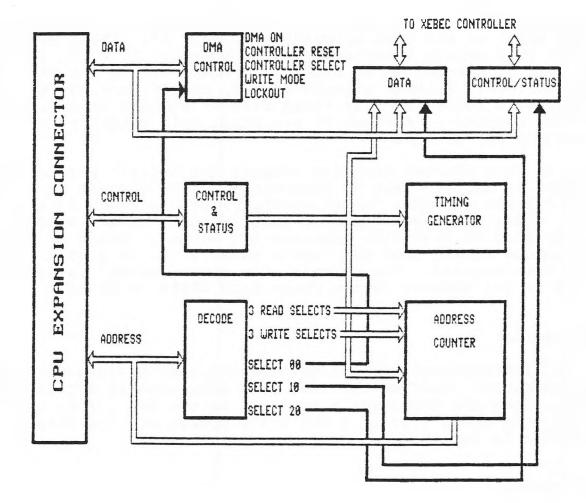

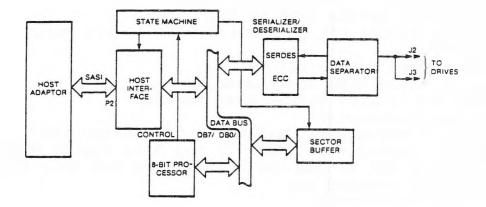

Major areas of the S1410 Controller are shown in the simplified block diagram of Figure 3.2.

## S1410 CONTROLLER, FUNCTIONAL ORGANIZATION Figure 3.2

## 3.1.1.1 Host Interface

The host interface connects the internal data bus of the S1410 Controller to the SASI Data Bus; the state machine controls the movement of data and commands through the S1410 host interface.

3.1.1.2 Processor

Considered a "smart" controller the S1410 utilizes an eight-bit processor to monitor and control its operation.

3.1.1.3 State Machine

The state machine contols and synchronizes the operation of the Host Adapter (DMA Board), SERDES, and sector buffer.

3.1.1.4 SERDES

The serializer/deserializer (SERDES) converts parallel data from the internal data bus to serial data for transfer to a selected disk drive. It converts serial data from the selected disk drive to parallel data which it places on the internal data bus.

## 3.1.1.5 Data Separator

The data separator converts serial NRZ data to MFM for transfer to the selected disk drive. It converts MFM data coming from the selected disk drive to serial NRZ data for the SERDES.

3.1.1.6 Sector Buffer

The sector buffer stages data transfers between the disk drive and the host to prevent data overruns.

## 3.1.2 SPECIFICATIONS

This section contains the overall specifications of the S1410 Controller.

3.1.2.1 Electrical

Note: All measurements are made on the controller printed circuit board at the power connector Pl.

## Table 3.1 Electrical Specifications

| Voltage   | Range            | Current                        |  |

|-----------|------------------|--------------------------------|--|

| +5.0 Vdc  | 4.75 to 5.25 Vdc | 2.5 Amp. Max<br>2.0 Amp. Typ.  |  |

| +12.0 Vdc | 10.8 to 13.2 Vdc | 66.0 ma. Max.<br>48.0 ma. Typ. |  |

Note: The maximum conducted power supply ripple must not exceed 0.10 volts rms, from 0.1 to 25MHz.

3.1.2.2 Enviromental

## Table 3.2 Enviromental Specifications

| Temperature       | 0 to 55 degrees Celsius         |

|-------------------|---------------------------------|

| Relative Humidity | 10 to 95 percent non-condensing |

| Altitude          | Sea level to 10,000 feet        |

## 3.1.2.3 Connectors

## Table 3.3 Controller Mating Connectors

| Designation | Function                         | Type/Source                    |  |

|-------------|----------------------------------|--------------------------------|--|

| Jl          | Drive Control Signals            | AMP 88373-3                    |  |

| J2,J3       | Drive Data Signals               | AMP 86904-1                    |  |

| J 4         | Test Connector                   | Not Applicable                 |  |

| Pl          | Power Supply (housing)<br>(pins) | AMP 1-480424-0<br>AMP 350078-4 |  |

| P2          | Host interface signals           | AMP 86916-1                    |  |

Note: No connection to J4 must be made. This is for manufacturing test use only.

## 3.1.2.4 Connector Pin Assignments

The following tables contain the pin assignments of the connectors on the controller board. The tables identify the signals on the pins. Connector P2 signals are defined under section 3.1.2, Theory of Operation.

## Table 3.4 Connector Jl, Control Signals, Pin Assignments

| <u>Signal</u> Pin                                                                         | Ground Return                                                                           | Signal Name                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2<br>4<br>6<br>8<br>10<br>12<br>14<br>16<br>18<br>20<br>22<br>24<br>-26<br>28<br>30<br>32 | 1<br>3<br>5<br>7<br>9<br>11<br>13<br>15<br>17<br>19<br>21<br>23<br>25<br>27<br>29<br>31 | Reduced Write Current<br>Head Select 2(2)<br>Write Select Gate<br>Seek Complete<br>Track 00<br>Write Fault<br>Head Select 2(0)<br>Reserved<br>Head Select 2(1)<br>Index<br>Ready<br>Step<br>Drive Select 1<br>Drive Select 2<br>Reserved<br>Reserved |

| 34                                                                                        | 33                                                                                      | Direction In                                                                                                                                                                                                                                         |

|            |    |     |     | Table | 3.5      |     |             |

|------------|----|-----|-----|-------|----------|-----|-------------|

| Connectors | J2 | and | J3, | Data  | Signals, | Pin | Assignments |

| <u>Signal</u> <u>Pin</u>         | Ground Return          | Signal Name                                                                                    |

|----------------------------------|------------------------|------------------------------------------------------------------------------------------------|

| 1<br>5<br>7<br>_<br>11           | 2<br>6<br>8<br>-<br>12 | Drive Selected<br>Spare<br>Reserved<br>Spares<br>Ground                                        |

| 13<br>14<br>15<br>17<br>18<br>19 | 16<br>20               | MFM Write Data +<br>MFM Write Data -<br>Ground<br>MFM Read Data +<br>MFM Read Data -<br>Ground |

Table 3.6Connector P2, Host Interface, Pin Assignments

| <u>Signal Pin</u> | Ground Return | Signal Name |

|-------------------|---------------|-------------|

| 2                 | 1             | Data O      |

| 4                 | 3             | Data 1      |

| 6                 |               | Data 2      |

| 8                 | 5<br>7        | Data 3      |

| 10                | 9             | Data 4      |

| 12                | 11            | Data 5      |

| 14                | 13            | Data 6      |

| 16                | 15            | Data 7      |

| 18                | 17            | Spare       |

| 20                | 19            | Spare       |

| 22                | 21            | Spare       |

| 24                | 23            | Spare       |

| 26                | 25            | Spare       |

| 28                | 27            | Spare       |

| 30                | 29            | Spare       |

| 32                | 31            | Spare       |

| 34                | 33            | Spare       |

| 36                | 35            | BUSY        |

| 38                | 37            | ACK         |

| 40                | 39            | RST         |

| 42                | 41            | MSG         |

| 44                | 43            | SEL         |

| 46                | 45            | <u>C/D</u>  |

| 48                | 47            | REQ         |

| 50                | 49            | Ī/O         |

Table 3.7 Connector Pl, Power Supply, Pin Assignments

| Pin | Number | Voltage                 |

|-----|--------|-------------------------|

|     | 1      | +12Vdc<br>Ground Return |

|     | 3      | Ground Return           |

|     | 4      | +5Vdc                   |

#### 3.1.3 BOARD SETUP

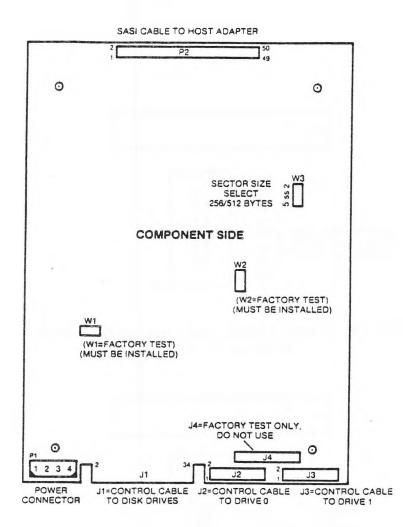

This section contains information used for setting up and installing the board for operation. Except for changing the address of the controller the other information provided is for reference only.

3.1.3.1 Board Jumpers

Jumpers on the S1410 board are listed in Table 3.8, and are shown in Figure 3.3.

#### Table 3.8 Jumper Locations

| Designation | Function               | Connection and Result                                                                        |

|-------------|------------------------|----------------------------------------------------------------------------------------------|

| Wl          | Factory Test           | Must be installed                                                                            |

| W2          | Factory Test           | Must be installed                                                                            |

| W3          | Selects Sector<br>Size | SS to 2: 256 byte sector<br>32 Sectors/Track<br>SS to 5: 512 byte sector<br>17 Sectors/Track |

Note: SS to 5 is the configuration used in the Victor System.

#### 3.1.3.2 Connecting Cables

The following cables must be in place for proper operation of the controller. Included is the maximum length recommended for each cable. Figure 3.3 shows the connector locations.

Jl Control Cable: maximum 20 feet

J2 Data Cable: maximum 20 feet

J3 Data Cable: maximum 20 feet

P1 Power Cable: Not applicable

P2 Host Interface Cable: maximum 15 feet

Cable, Connector, and Jumper Locations Figure 3.3

Note: No connection should be made to J4. Factory test only.

#### 3.1.3.3 Address Jumper Group

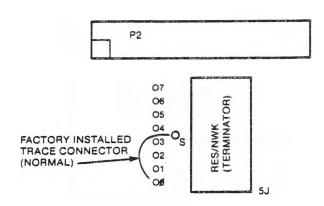

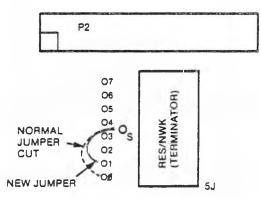

The controller supports one of eight unique device addresses. When more than one controller is used in a system, the address jumper on the controller must be changed. Figure 3.4 shows the address jumper group located next to the terminator at position 5J; it also shows that terminal (pad 0) is connected to terminal S. This is the factory-installed jumper, and sets the controller to address 0.

In order to change this address, the factory-installed jumper (trace) must be cut. Then, a new jumper must be connected between terminal S and the selected address terminal. Figure 3.5 shows that the factory-installed jumper has been cut, and a new jumper has been installed between terminal S and address terminal 1. The address of the controller is now 1.

Normal (Factory-Installed) Address Jumper Figure 3.4

Changed Address Jumper (Controller 1) Figure 3.5

#### 3.1.4 THEORY OF OPERATION

This section discusses the functional theory of operation of the S1410 Controller and how it is used in the Victor Hard Disk Subsystem.

#### 3.1.4.1 Signal Definitions

The following tables list and define the signals that appear on the SASI Bus lines between the DMA Board and controller. The following designations are used in the tables.

| Abbreviation | Definition                                                       |

|--------------|------------------------------------------------------------------|

| Drv          | Driver                                                           |

| Rcvr         | Receiver                                                         |

| OC           | Open Collector                                                   |

| Tri-State    | Line has three states: high,<br>low, and high impedance          |

| 220/330      | Line Termination: 220 Ohms to source voltage/ 330 Ohms to ground |

# Table 3.9 Host Bus Status Signals

| ~ | NAME | DRVR/ | RCVR | DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---|------|-------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | ī/o  | Drv   | oc   | Input/Output: The controller drives this<br>line. A low level on this line indicates<br>that the controller is driving the data<br>in (to the DMA Board) on the SASI Bus.<br>A high level on this line indicates that<br>the DMA Board is driving the data out on<br>the SASI Data Bus. The DMA Board<br>monitors this line and uses it to enable<br>and disable its data bus drivers. This<br>signal is qualified by signal REQ. |

|   | C/D  | Drv   | oc   | Command/Data: This signal line<br>indicates whether the information on the<br>data bus consists of command or data<br>bytes. A low means command bytes; a<br>high means data bytes. This signal is<br>qualified by signal REQ.                                                                                                                                                                                                    |

| ( | BUSY | Drv   | oc   | Busy: The controller generates this<br>active low signal in response to the SEL<br>signal and the address bit (DB0 to DB7)<br>from the DMA Board. The busy signal<br>informs the DMA Board that the<br>controller is ready to conduct<br>transactions on the SASI Bus.                                                                                                                                                            |

|   | MSG  | Drv   | OC   | Message: The controller sends this<br>active low signal to the DMA Board to<br>indicate that the current command has<br>been completed. When MSG is active, the<br>I/O signal line is always low so that<br>the controller can drive the bus data<br>lines. This signal is qualified by REQ.                                                                                                                                      |

Table 3.10 Summary of Host Bus Status Signals

| Ī/O  | <u>c/d</u> | MSG  | DEFINITION                                                                      |

|------|------------|------|---------------------------------------------------------------------------------|

| High | Low        | High | The Controller receives command from the DMA Board.                             |

| High | High       | High | The Controller receives data from the DMA<br>Board.                             |

| Low  | High       | High | The Controller sends data to the DMA Board.                                     |

| Low  | Low        | High | The Controller sends error status byte to the DMA Board.                        |

| Low  | Low        | Low  | The Controller informs the DMA Board that it has completed the current command. |

Table 3.11 Controller - Host Handshaking

| Name | Drv/Rcvr | Definition |

|------|----------|------------|

|      |          |            |

- **REQ** Drv OC **REQUEST:** The controller sends this active low signal to the DMA Board for each byte transferred across the interface. This signal qualifies signals I/O, C/D, and MSG.

- ACKRcvr<br/>220/230ACKNOWLEDGE: The DMA Board generates this<br/>active low signal in response to the REQ<br/>signal from the controller when the host is<br/>ready to receive or transmit a byte of<br/>data. In order to complete the handshake,<br/>the DMA Board must sen an acknowledge (ACK)<br/>in response to each request (REQ) from the<br/>controller.

Table 3.12 Host Bus Control Signals

Definition

Name Drv/Rcvr

RST

Rcvr,

220/220

RESET: The DMA Board sends this active low signal to the controller to force the controller to the idle state. After RST has become active, any controller status is cleared. RST also causes the deactivation of all signals to the drives. The time requirement for the RST signal is as

#### follows:

Minumum = 100 ns. Maximum = None

SEL

Rcvr, 220/330 Belief Select: The DMA Board sends this active low signal to the controller to initiate a command transaction. Along with SEL, the DMA Board must also send an address bit to select the controller (DB0 for controller). The controller must not be busy. The DMA Board must deactivate SEL before the end of the current command.

> Table 3.13 Host Bus Data Signals

#### Name Drv/Rcvr Definition

DB7-DB0 Rcvr, These are the eight data bits (lines) of the SASI Bus (DB0 = LSB). Each line is also used as address bits to select a controller in systems using multiple controllers. The normal connection (hardwired on the board) is to DB0, which is the address of controller 0. Any other connection requires cutting the existing trace on the board (or jumper) and adding a jumper.

The following list shows the bit assignments:

DB0 - Controller 0 DB1 - Controller 1 DB2 - Controller 2 DB3 - Controller 3 DB4 - Controller 4 DB5 - Controller 5 DB6 - Controller 6 DB7 - Controller 7

3.1.4.2 Detailed Description (Handshaking and Timing)

The following paragraphs describe the interaction between the controller and DMA Board.

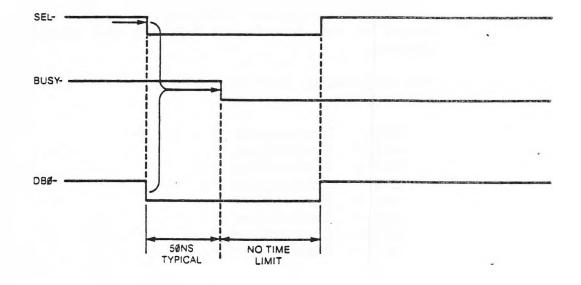

#### Controller Selection

Before the DMA Board can begin a transaction, it must select the controller. The DMA Board selects the controller by activating the SEL control signal and the address bit of the controller. Any bit, DB0 - DB7, can be the address bit in a system with multiple controllers. For the following discussion, the controller's address is 0.

The timing diagram in Figure 3.6 shows the basic timing requirements. Upon receiving both the SEL signal and DBO, the controller activates the BUSY signal. As shown in the timing diagram, both SEL and DBO must be active (low) before the controller can activate the BUSY signal. During the selection process, the host has control of the data bus as signified by the deactivation of the I/O line. Selection is complete when BUSY becomes active. The SEL signal must be deactivated by the host interface before the current controller operation has completed. The controller then enters command mode.

Controller Select Timing Figure 3.6

#### Command Mode

The controller receives commands from the DMA Board using a handshaking sequence. The controller places a low level on the C/D (COMMAND/DATA) line to indicate that it wants a command from the DMA Board and places a high level on the I/O line to indicate that the movement of information is from the host adapter out to the controller. The MSG line is high.

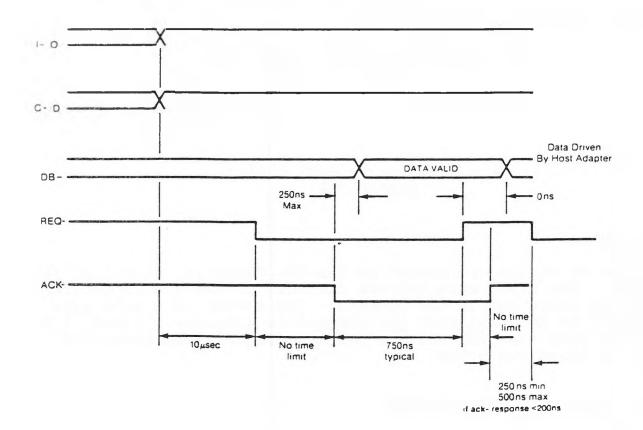

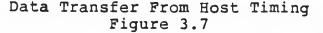

The controller activates the REQ line within 10 microseconds after signals I/O, C/D, and MSG have been placed at high, low, and high levels, respectively. The DMA Board responds by activating the ACK signal when a command byte is ready for the controller. The command byte placed on the data bus by the host must be stable within 250 nanoseconds after the ACK signal is activated. The command byte must be held stable until REQ is deactivated. The host deactivates ACK after REQ goes high. This completes the handshake for the first command byte. Each succeeding command byte from the DMA Board requires the same complete handshake sequence. Refer to Figure 3.7 for data bus, REQ and ACK timing.

#### Data Transfer

The timing diagrams in Figures 3.7 and 3.8 illustrate the required timing for data transfer.

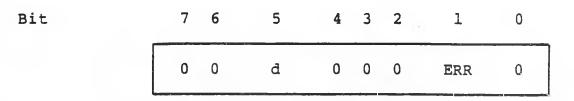

Data Transfer To Host Timing Figure 3.8

#### Status Bytes

Two bytes of status are passed to the DMA Board at the end of all commands. The first byte informs the host if any errors occurred during the execution of the command. The second is a zero byte. It signals to the host that the command is complete. Figure 3.8 shows the data bus, REQ and ACK timing. Figure 3.10 shows the format of these two bytes.

#### 3.1.5 PROGRAMMING INFORMATION

The following section discusses communications between the controller and host from the point of view of the codes that are passed. The host sends commands to the controller via the DMA Board. The controller then performs the commands and reports back to the host. For more information on this section the

reader may wish to obtain a copy of the Xebec S1410 Owner's Manual and Programming Guide by calling (408) 733-4200. Only certain significant commands will be discussed in this section.

#### 3.1.5.1 Commands

- · ·

The host sends a six-byte block to the controller to specify the operation. This block is the Device Control Block (DCB). Figure 3.9 shows the composition of the DCB. The list that follows Figure 3.9 defines the bytes that make up the DCB.

| Bit    | 7 6     | 5      | 4             | 3     | 2     | 1   | 0 |

|--------|---------|--------|---------------|-------|-------|-----|---|

| Byte O | Cmd Cla | Opcode |               |       |       |     |   |

| Byte l | LUN     |        |               | High  | Addr  | ess |   |

| Byte 2 |         | M:     | iddle Address |       |       |     |   |

| Byte 3 |         |        | Low Address   |       |       |     |   |

| Byte 4 | Int     | erlea  | ave or        | Block | c Cou | nt  |   |

| Byte 5 |         | Co     | ontrol        | Field | 1     |     |   |

Device Control Block (DCB) Format Figure 3.9

- Byte 0 Bits 7, 6, and 5 identify the class of the command. Bits 4 through 0 contain the opcode of the command.

- Byte 1 Bits 7, 6, and 5 identify the logical unit number (LUN). Bits 4 through 0 contain logical disk address 2.

- Byte 2 Bits 7 through 0 contain logical disk address 1.

- Byte 3 Bits 7 through 0 contain logical disk address 0 (LSB).

- Byte 4 Bits 7 through 0 specify the interleave or block count.

Byte 5 Bits 7 through 0 contain the control field.

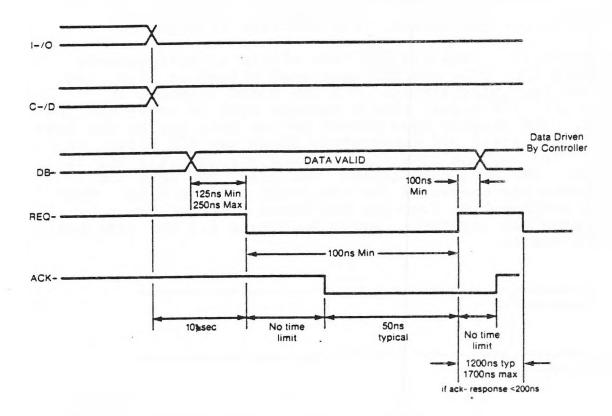

At the end of a command, the controller returns two completion status bytes to the host. The format of these bytes is shown in Figure 3.10.

#### NEXT TO LAST STATUS BYTE

Bits 0,2,3,4,6, and 7: Set to zero

Bit 1: When set, error occurred during command execution.

Bit 5: Logical unit number of drive, d=0 or 1.

#### LAST STATUS BYTE

| Bit | 7 | 6 | 5 | 4 | 3 | 2 | 1   | 0 |

|-----|---|---|---|---|---|---|-----|---|

|     | 0 | 0 | đ | 0 | 0 | 0 | ERR | 0 |

Bits 0-7: Set to zero.

#### Completion Status Bytes Figure 3.10

#### 3.1.5.2 Control Byte

The control field, byte 5, of the DCB allows the user to select options for several different types and makes of disk drives. The following list defines the bits of the control byte.

- Bit 0 Half-step option of Seagate and Texas Instrument drives.

- Bit 1 Half-step option for Tandon Drives.

- Bit 2 Buffer-step option for drives made by Computer

Memories, Inc. and Rotating Memories, Inc. (200 microsecond pulse per step).

Bit 3-5 Spare. Set to zero for future use.

- Bit 6 If one, during a read sector command, the failing sector is not re-read on the next revolution before attempting correction. This bit should be set to zero for normal operation.

- Bit 7 Disable the four retries by the controller on all disk access commands. Set this bit only during the evaluation of the performance of a disk drive.

This bit should be set to zero for normal operation.

Note: The step option bits (2-0) are mutually exclusive and only one option should be selected in any given configuration.

3.1.5.3 Logical Address (High, Middle, and Low)

The logical address of the drive is computed by using the following equation.

Logical Address = (CYADR \* HDCYL + HDADR) \* SETRK + SEADR

Where : CYADR = Cylinder Address HDADR = Head Address SEADR = Sector Address HDCYL = Number of Heads per Cylinder SETRK = Number of Sectors per Track

The commands fall into eight classes, 0 through 7; only classes 0 and 7 are used. Class 0 commands are data, non-data transfer, and status commands. Classes 1 through 6 are reserved. Class 7 are diagnostic commands.

Following is a description of two important Class 0 commands; Request Sense Status and Initialize Drive Characteristics. The description includes its class, opcode, and format. When a slash (/) represents a bit position, the slash indicates a don't care.

#### 3.1.5.4 Request Sense Status (Class 0, Opcode 03)

The host must send this command immediately after it detects an error. The command causes the controller to return four bytes of drive and controller status; the formats of these bytes are shown after the DCB. When an error occurs on a multiple sector data transfer, (read or write), the Request Sense Status command returns the logical address of the failing sector in bytes 1, 2, and 3. If the Request Sense Status command is issued after any of the Format commands or the Check Track Format command, then the logical address returned by the controller points to one sector beyond the last track formatted or checked if there was no error. If there was an error, then the logical address returned points to the track in error. The tables which follow the formats list the error codes as reported internal to the S1410 Controller.

#### d = drive, 0 or 1

Note: This parameter (d) would be used for indicating which drive receives the command when two drives are chained off one controller.

| Bit    | 7         | 6          | 5   | 4      | 3     | 2      | l | 0 |  |

|--------|-----------|------------|-----|--------|-------|--------|---|---|--|

| Byte O | 0         | 0          | . 0 | 0      | 0     | 0      | 1 | 1 |  |

| Byte l | 0         | 0          | đ   | 1      | 1     | 1      | 1 | 1 |  |

| Byte 2 | 1         | 1          | 1   | 1      | 1     | 1      | 1 | 1 |  |

| Byte 3 | 1         | 1          | 1   | 1      | 1     | 1      | 1 | / |  |

| Byte 4 | 1         | 1          | 1   | 1      | 1     | 1      | 1 | / |  |

| Byte 5 | 1         | 1          | 1   | 1      | 1     | 1      | 1 | 1 |  |

|        |           | i carro, l | SI  | ENSE B | YTE O | ****** |   |   |  |

| Bit    | 7         | 6          | 5   | 4      | 3     | 2      | 1 | 0 |  |

| Byte O | See Below |            |     |        |       |        |   |   |  |

| -      |           |            | _   | _      |       |        |   |   |  |

REQUEST SENSE STATUS FORMAT

Bits 0,1,2,3: Error Code (Hex 3 in example above) Bits 4,5: Error Type (Hex 0 in example above)

Bit 6: Spare, set to zero

Bit 7: Address valid, when set

0

/

0

/

/

Bit 7, the address valid bit in the error code byte (byte 0), is relevant only when the previous command required a logical block address; in which case it is always returned as a one otherwise it is set to zero.

đ

/

/

SENSE BYTES 1,2, and 3

/

/

High Address

/

/

/

/

/

/

/

/

Byte 1

Byte 2

Byte 3

| The following table (3.14) contains the error codes as reported |

|-----------------------------------------------------------------|

| by the controller when a Request Sense Status command is issued |

| by the host. The table is divided into four areas; Type 0 (Disk |

| Drive), Type 1 (Controller), and, Type 2 and 3 (Command and     |

| Miscellaneous). The Summary Error Table shows the hex code with |

| bit 7 (address valid) set and not set.                          |

Note: Present Winchester CPU Boot Roms report system boot errors from the controller with bit 7 set.

Example: X98, X92, X91, etc.

Future Universal CPU Boot Roms will report system boot errors from the controller with bit 7 not set.

Example: X18, X12, X11, etc.

# Table 3.14 S1410 Error Code Summary

Error Code (Hex)

| Bit 7<br>Set | Bit 7<br>Not Set | Meaning                                                                                                            |  |  |

|--------------|------------------|--------------------------------------------------------------------------------------------------------------------|--|--|

|              |                  | Type 0 (Disk Drive)                                                                                                |  |  |

| 80           | 00               | No error detected: The controller detected no<br>error during the execution of the previous<br>command.            |  |  |

| 81           | 01               | No index detected from disk drive                                                                                  |  |  |

| 82           | 02               | No seek complete from disk drive                                                                                   |  |  |

| 83           | 03               | The controller detected a write fault from the disk drive during the last operation.                               |  |  |

| 84           | 04               | After the controller selected the drive, the drive did not respond with a ready signal.                            |  |  |

| 85           | 05               | Not Used.                                                                                                          |  |  |

| 86           | 06               | After stepping maximum number of cylinders, the<br>controller did not receive track 00 signal from<br>the drive.   |  |  |

| 87-8F        | 07-0F            | Not Used.                                                                                                          |  |  |

|              |                  | Type 1 (Controller)                                                                                                |  |  |

| 90           | 10               | ID Read Error: The controller detected an ECC error in the target ID Field on the disk.                            |  |  |

| 91           | 11               | Data Error: The controller detected an<br>uncorrectable ECC error in the target sector<br>during a read operation. |  |  |

| 92           | 12               | Address Mark: The controller did not detect the target address mark (AM) on the disk.                              |  |  |

| 93           | 13               | Not Used.                                                                                                          |  |  |

| 94           | 14               | Sector Not Found: The controller found the correct cylinder and head, but not the target sector.                   |  |  |