## Hardware Reference Manual

### Hardware Reference Manual

Vic FOR Indexculters 160 E Pueblo Road Socta Inany, CA Indec

- VICTOR & regulational traditional of Victor Factoration

NOTICE

PICTOR realize no regime contract or property of any real of the second seco

We are a set of the se

Report VICTOR SIMILAR Area 1881

#### COPYRIGHT

ř

1.1

1.4

12.1

Sil

#### © 1983 by VICTOR.®

Portions reprinted by permission of Intel Corporation INTEL, © 1978 and 1981.

Portions reprinted by permission of Motorola, Inc., © 1978.

Portions reprinted by permission of Synertec, Inc., ©1980.

All rights reserved. This publication contains proprietary information which is protected by copyright. No part of this publication may be reproduced, transcribed, stored in a retrieval system, translated into any language or computer language, or transmitted in any form whatsoever without the prior written consent of the publisher. For information contact:

VICTOR Publications 380 El Pueblo Road Scotts Valley, CA 95066 (408) 438-6680

Processoury united beyreased her betaune

ett - elustabila P - seamen -

. Cale Galleomi ans?

Jemory Mt. specie 0

-- EC 229 504 564 28

Inceksis Addressing

String Addressing F 2 Por Addresunc

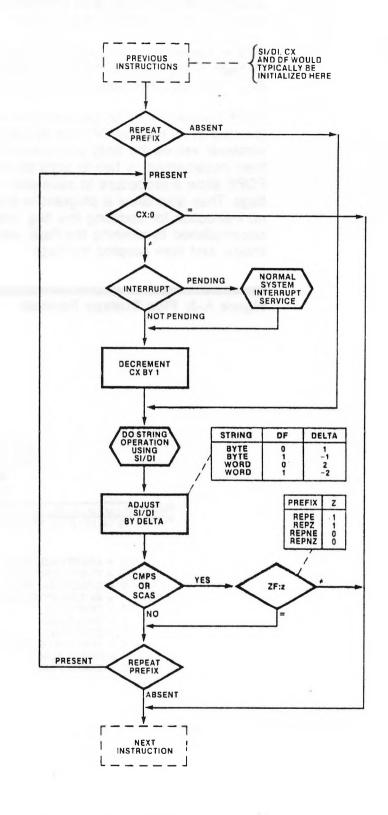

REPERDE DE AMA MARAR

#### TRADEMARKS

VICTOR is a registered trademark of Victor Technologies, Inc.

SE T THE SOUND

### NOTICE

£ ....

22

12

13

28

ES

9.7

43

59

45

20

86

VICTOR makes no representations or warranties of any kind whatsoever with respect to the contents hereof and specifically disclaims any implied warranties of merchantability or fitness for any particular purpose. VICTOR shall not be liable for errors contained herein or for incidental or consequential damages in connection with the furnishing, performance, or use of this publication or its contents.

VICTOR reserves the right to revise this publication from time to time and to make changes in the content hereof without obligation to notify any person of such revision or changes.

COF INCE

thti÷ loteb

thti÷ loteb

#### Second VICTOR printing April, 1983.

ISBN 0-88182-065-2

#### CONTENTS

.

· Para ·

TRACECO

|                                       | THE CONCERNING OF REAL AND                                                      |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------|

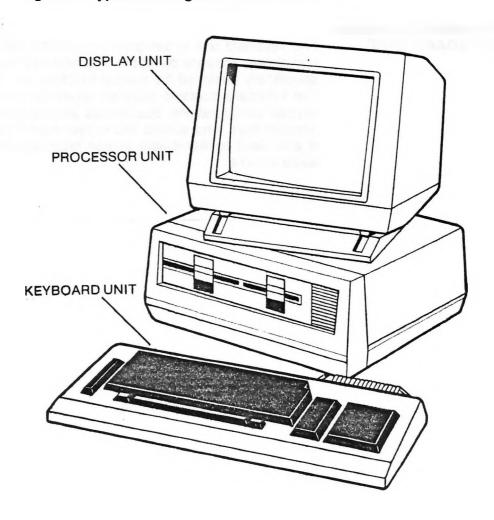

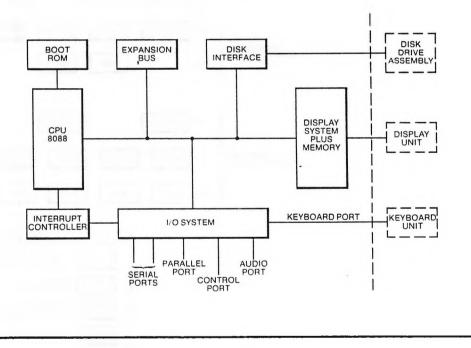

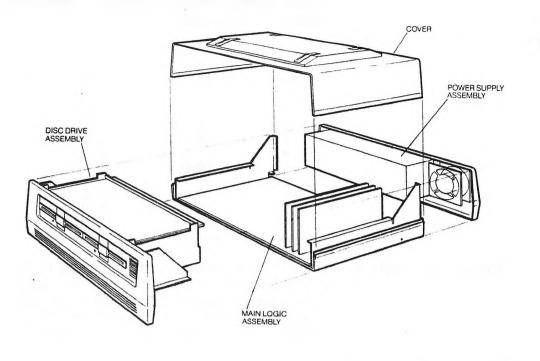

| System Description                    | Processor Unit                                                                                                      |

|                                       | Processor Unit                                                                                                      |

|                                       | Display Unit                                                                                                        |

|                                       | Display Unit<br>Keyboard Unit                                                                                       |

|                                       |                                                                                                                     |

| 14                                    | Main Logic Board                                                                                                    |

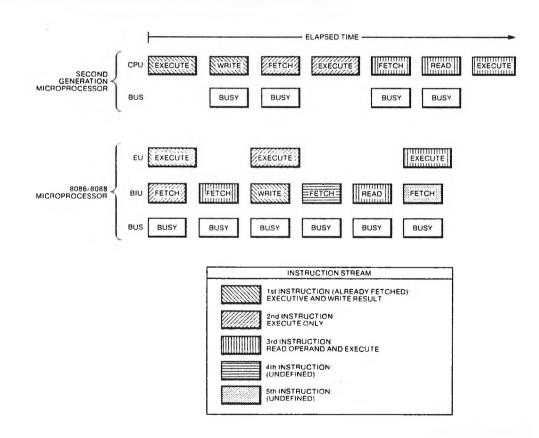

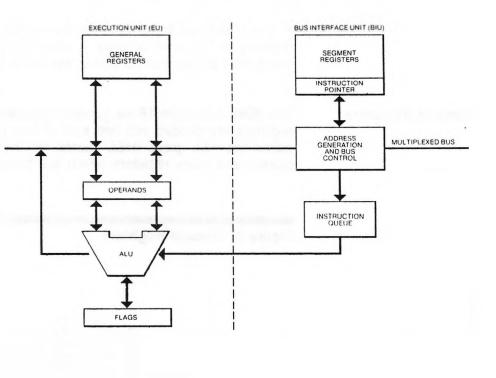

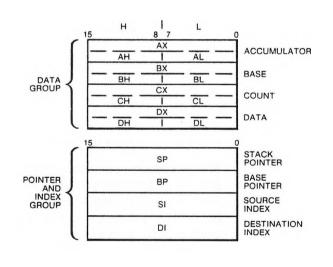

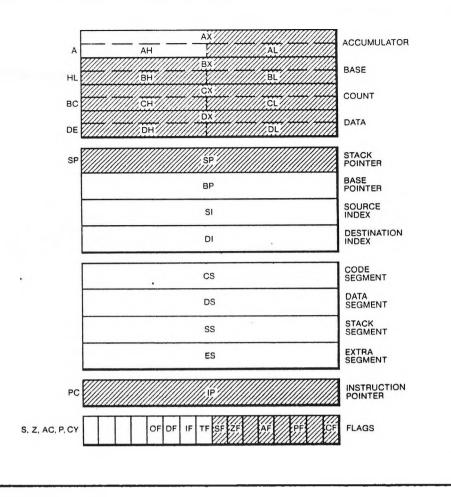

| Processor Unit                        | Main Logic Board<br>8088 Central Processing Unit (CPU)<br>Execution Unit<br>Bus Interface Unit<br>General Registers |

| ·                                     | 8088 Central Processing Unit (CPU)                                                                                  |

| The there are                         | Execution Unit name and a second s     |

| 15 8 2 14                             | Bus Interface Unit                                                                                                  |

| 18. 11 - May                          |                                                                                                                     |

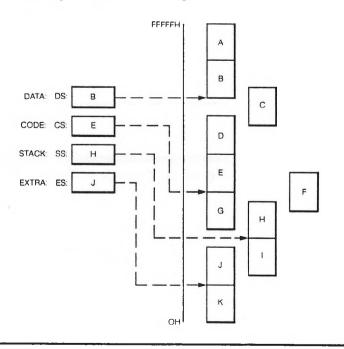

|                                       | Segment Registers                                                                                                   |

|                                       | Instruction Pointer                                                                                                 |

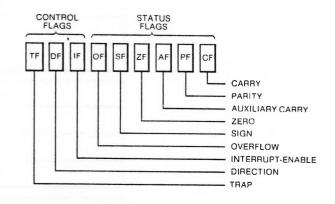

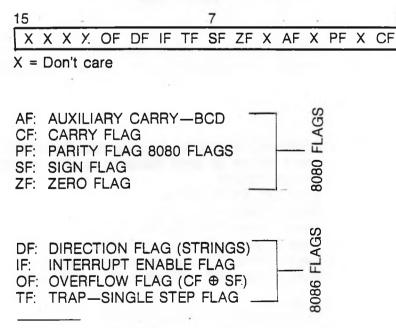

|                                       | Flags                                                                                                               |

|                                       | 8080/8085 Register and Flag Correspondence                                                                          |

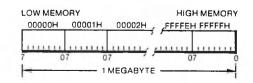

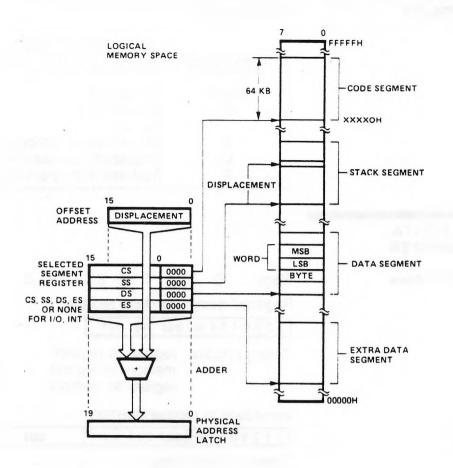

|                                       | Memory<br>Storage Organization<br>Segmentation<br>Physical Address Generation                                       |

|                                       | Storage Organization                                                                                                |

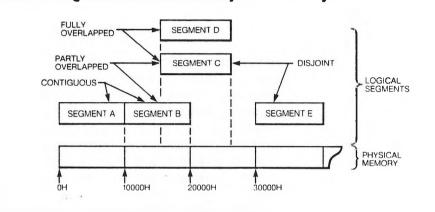

|                                       | Segmentation                                                                                                        |

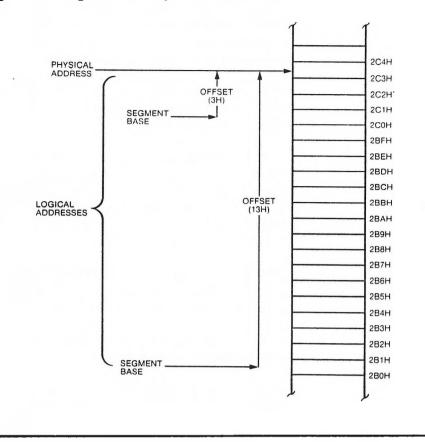

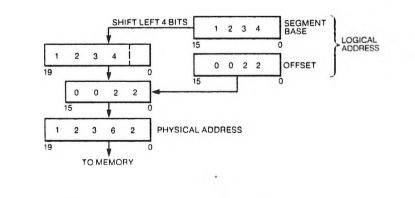

|                                       | Physical Address Generation                                                                                         |

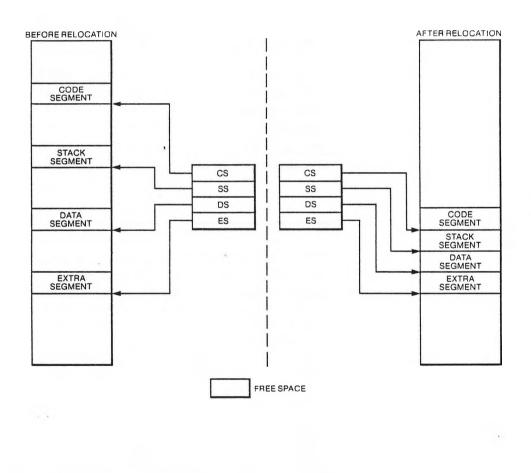

|                                       | Dynamically Relocatable Code 1                                                                                      |

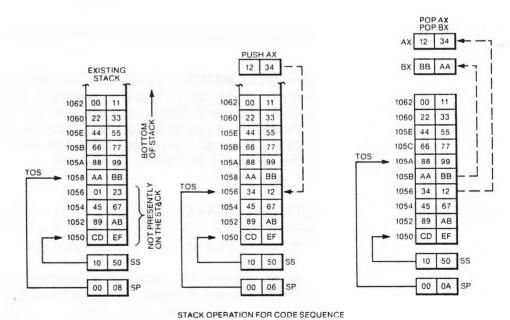

|                                       | Stack Implementation 1                                                                                              |

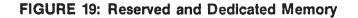

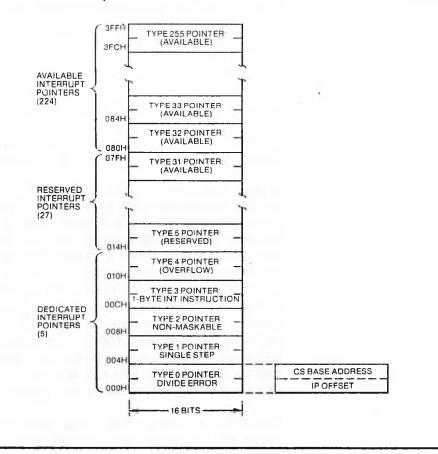

|                                       | Dedicated and Reserved Memory Locations 1                                                                           |

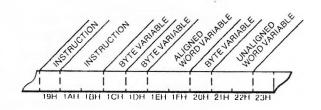

| · · · · · · · · · · · · · · · · · · · | 8086/8088 Memory Access                                                                                             |

|                                       | 8086/8088 Memory Access<br>Input/Output                                                                             |

|                                       | Memory Mapped I/O                                                                                                   |

|                                       | Direct Memory Access                                                                                                |

|                                       | Wait and Test                                                                                                       |

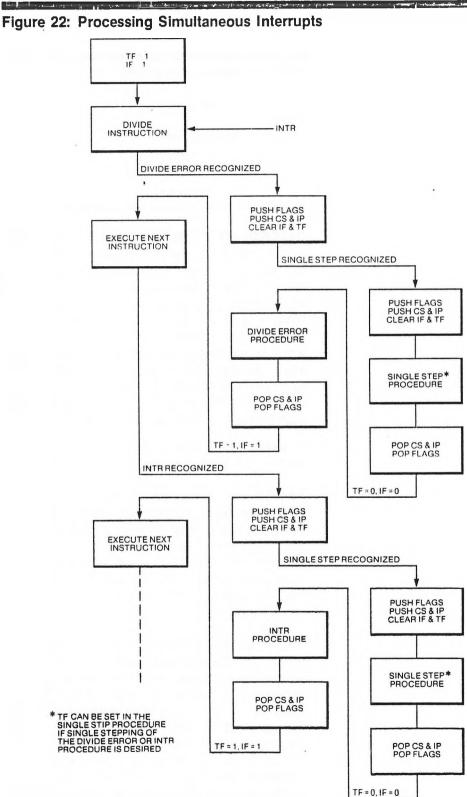

|                                       | Processor Control and Monitoring Interrupts                                                                         |

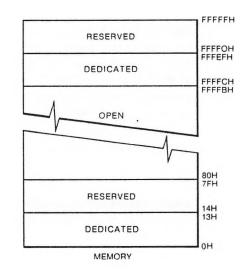

| ·                                     | External Interrupts                                                                                                 |

|                                       | Internal Interrunts                                                                                                 |

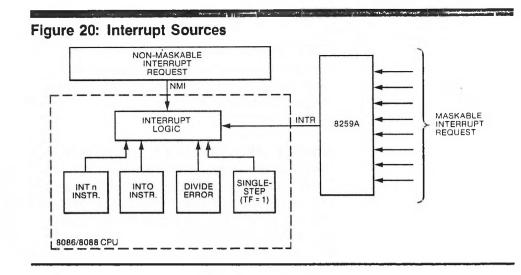

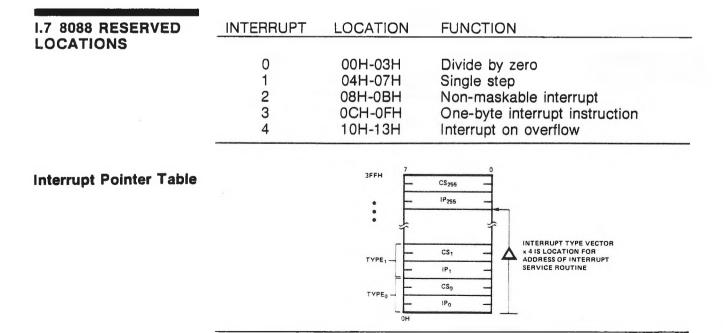

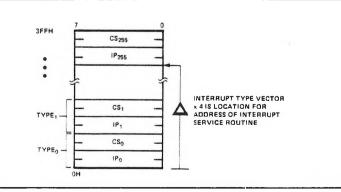

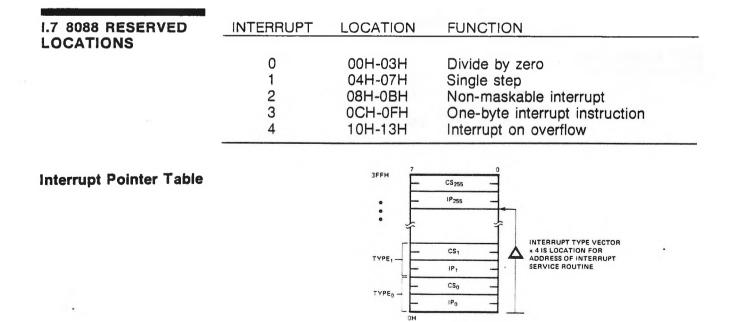

|                                       | Internal Interrupts<br>Interrupt Pointer Table<br>Interrupt Procedures                                              |

| 5                                     |                                                                                                                     |

|                                       | Breakpoint Interrupt                                                                                                |

|                                       | Breakpoint Interrupt<br>System Reset<br>Processor Halt                                                              |

|                                       | Processor Half                                                                                                      |

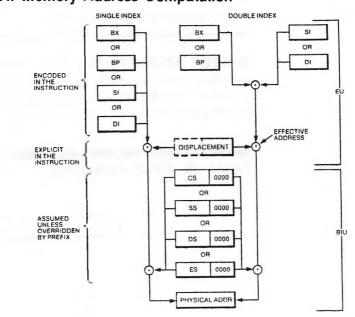

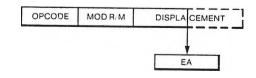

|                                       | Addressing Modes                                                                                                    |

|                                       | Addressing Modes<br>Register and Immediate Operands                                                                 |

| the second second                     | Momony Addressing Modes                                                                                             |

|                                       | Memory Addressing Modes                                                                                             |

|                                       | Direct Address                                                                                                      |

|                                       | Direct Addressing<br>Register Indirect Addressing                                                                   |

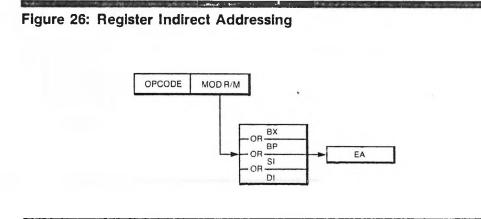

|                                       | Register Indirect Addressing                                                                                        |

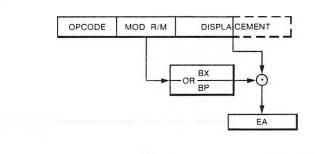

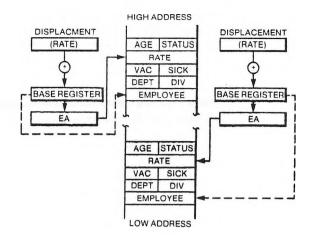

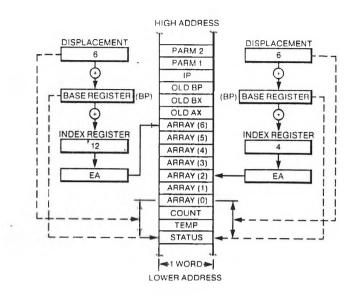

|                                       | Based Addressing                                                                                                    |

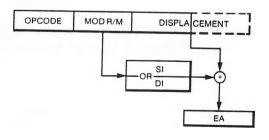

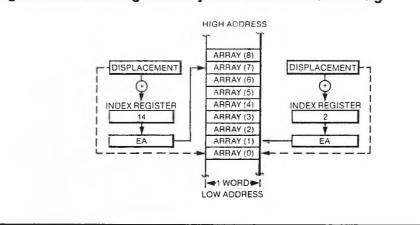

|                                       | Indexed Addressing                                                                                                  |

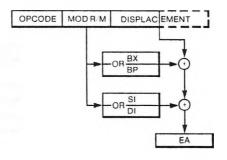

|                                       | Based Indexed Addressing                                                                                            |

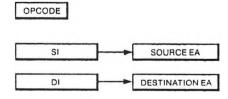

|                                       | String Addressing                                                                                                   |

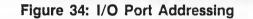

|                                       | I/O Port Addressing                                                                                                 |

|                                       | Boot ROM                                                                                                            |

|                                       | Input/Output (I/O) Functions                                                                                        |

|                                       | Serial Ports                                                                                                        |

|                                       | Parallel Port                                                                                                       |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 00   |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                  | Control Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

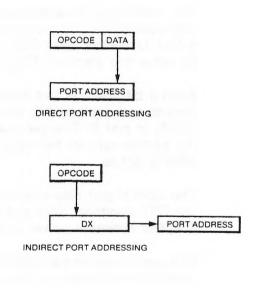

|                  | Audio Section                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

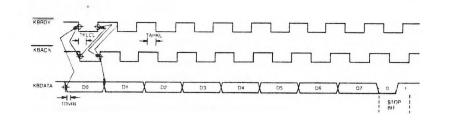

| 2.6              | Keyboard Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 38   |

|                  | Disk Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38   |

|                  | Disk intenace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20   |

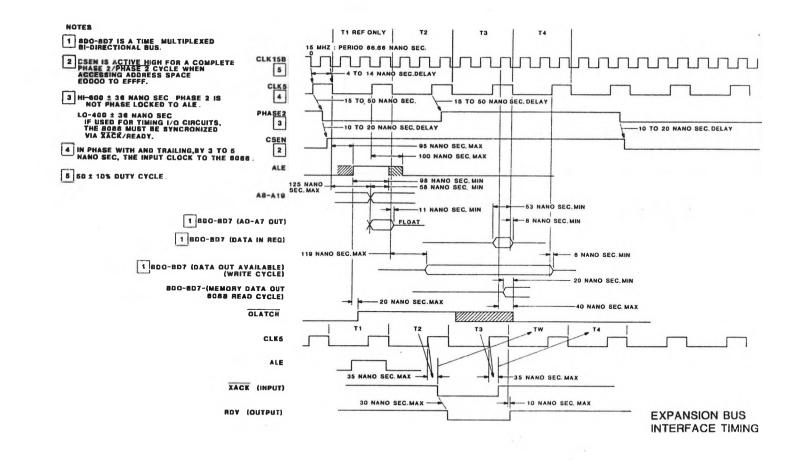

|                  | Expansion Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |

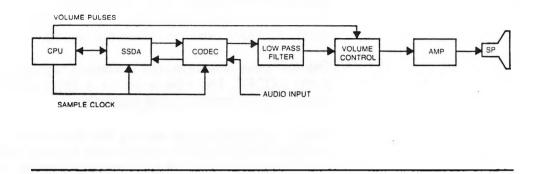

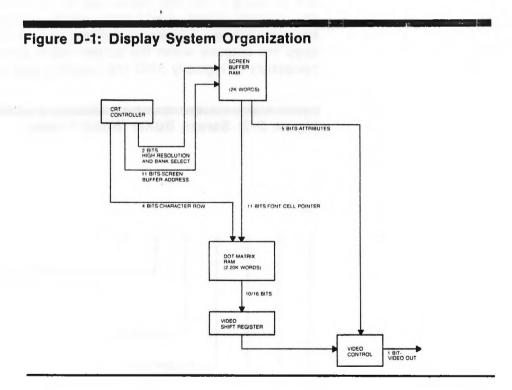

| T.C.             | Display                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

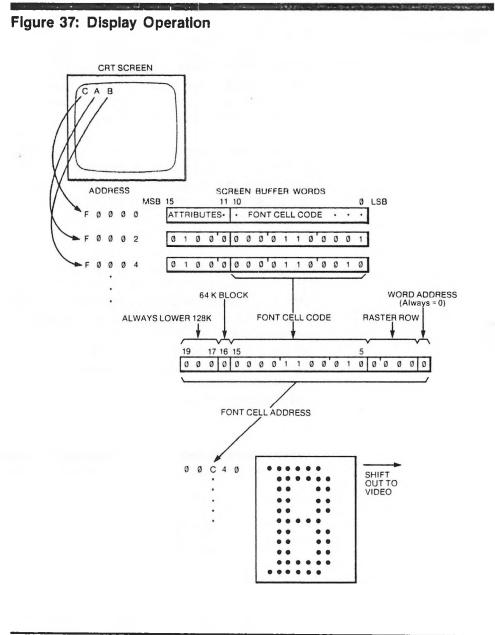

| 23               | Screen Buffer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 40   |

| 8.5              | Font Pointer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| ĉi               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A-1  |

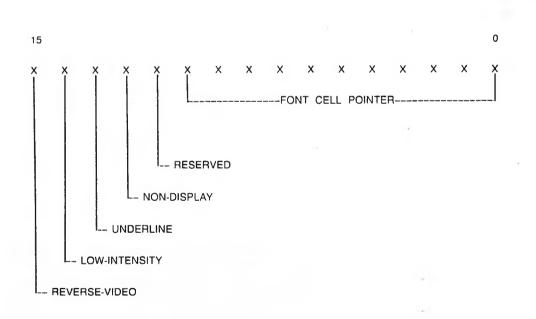

|                  | Attribute Bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |

| Ct.              | Reverse Video                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 41   |

| 5.5              | Display High/Low Intensity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 41   |

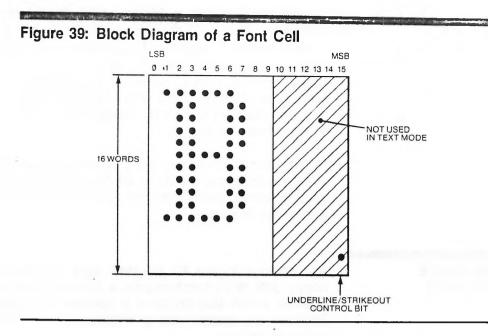

| 38               | Display Underline/Strikeover                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| Q.11             | Nondisplay Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 41   |

| 25               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | A 4  |

|                  | Software Attribute                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|                  | Font Cell                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

| <b>C</b> <0      | Display Brightness                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 43   |

| 2.5              | Display Contrast                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

| 3.0              | High Resolution Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43   |

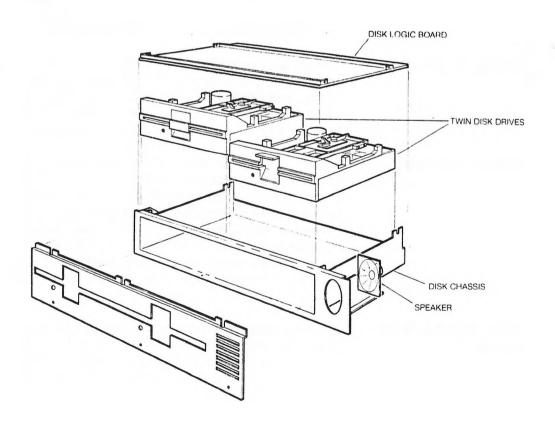

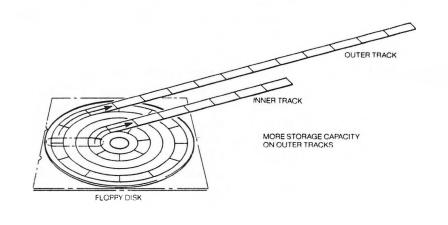

| 5.9              | Disk Drive Assembly                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| 5                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                  | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

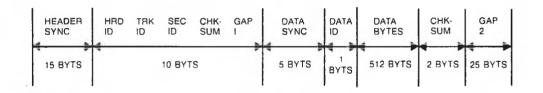

|                  | Reading Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 44   |

|                  | Header Search                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44   |

|                  | Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 44   |

| 12               | Writing Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.00 |

| ·/* ·            | Verification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46   |

|                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

|                  | Formatting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |