# ValidSIM<sup>TM</sup> REFERENCE MANUAL

#### Manual Number: MN224 Rev.A

15 July 1986

Valid Logic Systems, Incorporated 2820 Orchard Parkway San Jose, CA 95134 (408)945-9400 Telex 371 9004 FAX 408 262 2599

.

#### Copyright © 1986 Valid Logic Systems, Incorporated

This document contains confidential proprietary information which is not to be disclosed to unauthorized persons without the prior written consent of an officer of Valid Logic Systems Incorporated.

The copyright notice appearing above is included to provide statutory protection in the event of unauthorized or unintentional public disclosure.

# MANUAL REVISION HISTORY

| Rev | Date    | Software<br>Release     | Reason for Change |

|-----|---------|-------------------------|-------------------|

| A   | 7-15-86 | ValidSIM<br>Release 2.1 | Initial release.  |

• \*

# TABLE OF CONTENTS

| Section 1                               |     |

|-----------------------------------------|-----|

| Introduction                            |     |

| Theory of Operations                    | 1   |

| Signal States                           | 1   |

| Bidirectional Nets                      | 1   |

| Combination of States                   | 1   |

| Getting Started                         | . 1 |

| Selecting the Appropriate Simulation    | ]   |

| Window Sizes                            | ]   |

| Directives Files                        | J   |

| Starting Simulation                     | ]   |

| The Simulator Display                   | 1   |

| Status Lines                            | ]   |

| Echo Area                               | ]   |

| Display Area                            | ]   |

| Display Modes                           |     |

| Displaying Signal Values                | Ì   |

| Signal Values in Bus Mode               |     |

| Signal Values in Waveforms Mode         |     |

| Graphics for Signal Values              |     |

| Using Character Graphics                | •   |

| Working with Signal Values              |     |

| Opening Signals                         |     |

| Opening Memories                        | J   |

| Initialization of Signals and Memories  | ]   |

| Changing Signal Values                  | ]   |

| Changing Memory Values                  | ]   |

| Advancing Simulation Time               | ]   |

| Simulator Output                        | ]   |

| Listing File                            | ]   |

| Log File                                | ]   |

| Command File                            | ]   |

| Waveform Input File                     | ]   |

| File Names                              | ]   |

| Split-Screen Simulation                 | ]   |

| Differences from Full-Screen Simulation | 1   |

~ ...

| Section 2<br>Logic Simulator Directives     |     |

|---------------------------------------------|-----|

| Section 3                                   |     |

| Waveforms Mode                              |     |

| Waveform Commands                           | 3-2 |

| Section 4                                   |     |

| Breakpoints and Patching                    |     |

| Breakpoints                                 | 4-1 |

| Breakpoint Commands                         | 4-2 |

| Combining Breakpoint Commands               | 4-5 |

| Expression Syntax                           | 4-6 |

| Logic Patching                              | 4-7 |

| Section 5                                   |     |

| Tracing and Tabular I/O                     |     |

| Tracing                                     | 5-1 |

| Requirements for Standard Tracing           | 5-1 |

| Signal Mapping                              | 5-2 |

| Value Information for Tracing               | 5-2 |

| File Formats for Tracing                    | 5-2 |

| Signal Mapping File Format                  | 5-3 |

| Value File Format                           | 5-5 |

| Tabular I/O                                 | 5-6 |

| File Format for Tabular I/O                 | 5-6 |

| Stimulating Circuits with Tabular I/O Files | 5-7 |

| Sample Tabular I/O Use                      | 5-8 |

|                                             |     |

#### Section 6 Loading Memories

Section 7 Simulator Commands

#### Section 8 Delays

| Delays                                             |              |

|----------------------------------------------------|--------------|

| Delay Properties                                   | 8-1          |

| Delay Property                                     | 8-1          |

| Rise and Fall Properties                           | 8-2          |

| Pin-to-Pin Delay                                   | 8-2          |

| Rise_Fall Directive                                | 8-3          |

| Examples Using Delay Properties                    | 8-4          |

| Pin Delays with Rise/Fall Delays                   | 8-4          |

| Pin Delays without Rise/Fall Delays                | 8-5          |

| Delay Estimator                                    | 8-6          |

| Interaction of Wire Delays                         |              |

| with Delay Estimator                               | 8-7          |

| Computing Net Dependent Delays                     | 8-7          |

| Using the Delay Estimator                          | 8-10         |

| Expression Evaluator                               | 8-12         |

| Wire Delay Feedback                                | 8-15         |

| Wire Delay File                                    | 8-15         |

| Using a Wire Delay File                            | 8-17         |

| <b>c</b>                                           |              |

| Section 9                                          |              |

| Simulation Models                                  |              |

| Using Simulation Primitives                        | 9-1          |

| Simulator Primitives                               | 9-3          |

| Logic Gate Primitives                              | 9-3          |

| Buffer Primitives                                  | 9-5          |

| JK Primitive                                       | 9-6          |

| Latch Primitives                                   | 9-7          |

| Register Primitives                                | 9-9          |

| Multiplexer Primitives                             | 9-13         |

| Memory Primitive                                   | 9-14         |

| Counter/Shift Register Primitive                   | 9-16         |

| Arithmetic Primitives                              | 9-18         |

| Timing Checker Primitives                          | 9-20         |

|                                                    | 0 0 0        |

| Encoder and Decoder Primitives                     | 9-23         |

| Encoder and Decoder Primitives<br>Other Primitives | 9-23<br>9-24 |

|                                                    |              |

Section 10 Error Messages

| Appendix A                               |      |

|------------------------------------------|------|

| S-32/S-320 Additional Features           |      |

| Save and Restore Function                | A-1  |

| Save Command                             | A-1  |

| Restore Command                          | A-2  |

| Restore Directive                        | A-2  |

| Simulator Interruption                   | A-2  |

| User-Coded Primitives                    | A-3  |

| The Pascal Code for Systems Running UNIX | A-4  |

| The Pascal Code for Systems Running VMS  | A-5  |

| The Pascal Code for Systems Running CMS  | A-6  |

| Running a Simulator Containing UCPs      | A-8  |

| Running Your Simulator Under UNIX        | A-8  |

| Running Your Simulator Under VMS         | A-8  |

| Running Your Simulator Under CMS         | A-9  |

| Body Definition for UCPs                 | A-9  |

| UCP Pinout Descriptions                  | A-10 |

| User_Prim_Config Directive               | A-13 |

| Own Storage in UCPs                      | A-13 |

| Functions Provided for Use in UCPs       | A-13 |

| Example of a User-Coded Primitive        | A-18 |

| User Configuration File                  | A-19 |

| VMS Pascal Module Example                | A-20 |

|                                          |      |

# Appendix B

| Appendix B                |     |

|---------------------------|-----|

| PC AT Additional Features |     |

| Save and Restore Function | B-1 |

| Save Command              | B-1 |

| Restore Command           | B-2 |

| Restore Directive         | B-2 |

# Index

# SECTION 1 INTRODUCTION

The Logic Simulator represents a new approach to simulation of large digital systems. By separating timing verification from simulation, timing verification has been made more comprehensive and simulation has been made conceptually simpler and thus much faster. Optional timing analysis features in the Simulator also allow the user to perform some timing verification if desired.

First the design is entered using GED the Graphics Editor and the signals are named using the SCALD language. Buses can be drawn as a single wire by including a bit subscript in the signal name. The SIZE and TIMES properties can be used to let a one-bit section represent a multibitwide part. After the design is entered, you call the Simulator. The Simulator calls the Compiler to expand the design using the simulation models for each library part used in the design. The Compiler works on a design a page at-atime so that when a small change is made to a design, only a single page needs to be recompiled. For special purposes, the Compiler may also be called directly and a single large expansion file may be produced for a design. See the Compiler Reference manual for details.

Although designed primarily as an interactive tool, the Logic Simulator may also be run as a batch process. All used during a simulation be commands session mav single command file and the entered into a COMMAND FILE directive may be entered in the Simulator Directives file to direct the Simulator to use the commands in the specified file.

The designer may use command files to exercise a design in a way that is analogous to a diagnostic program. Since command files may be stored for repeated use, verification of a previously checked circuit can easily be repeated to ensure that it is still working correctly after design modifications.

## 1.1 THEORY OF OPERATIONS

The Logic Simulator initializes the system to a fixed state and waits for a command from the user. The user enters commands interactively (or through a command file) to OPEN the signals that need to be tracked, to DEPOSIT initial values to some signals, and to advance simulated time. It is frequently necessary to provide an external stimulus to a design, for example, a simulated disk data stream. Application of stimulus may be done through a command file, data file, or in many cases, by simulating an additional circuit specifically drawn to provide the stimulus.

After each SIMULATE command, the Simulator reports signal values for all OPENed signals. In Bus Mode simulation (useful for very large designs) instantaneous signal values are given for each signal. A history of previous signal values is not kept.

In Waveform Mode simulation, the signal value of each signal is recorded as a waveform. The previous signal values for each OPENed signal are kept for the amount of simulated time specified with the HISTORY command.

### SIGNAL STATES

Each bit of each signal in the Simulator assumes one of the 20 internal signal states used by the Simulator. These 20 internal states are mapped into 12 states that are used to report signal values to the user. The eight states that are not used to report signal values are special states that are used internally.

Each state is made up of two parts, a VALUE and a STRENGTH. The VALUE of a signal is its logical level. There are three possible signal values. These are:

| Signal Value | Meaning                                                |

|--------------|--------------------------------------------------------|

| 0<br>1<br>U  | Logical 0<br>Logical 1<br>Unknown<br>(could be 0 or 1) |

The STRENGTH of a signal describes the type of output or outputs that drive the signal to its VALUE. The possible STRENGTHs are:

| Signal Strength | Meaning                                                |

|-----------------|--------------------------------------------------------|

| HARD            | Driven to level                                        |

|                 | without resistance                                     |

| SOFT            | Driven to level<br>through resistance                  |

| MEMORY          | Driven to level and holding<br>(due to charge storage) |

| INDETERMINATE   | Could be HARD, SOFT<br>or MEMORY                       |

MEMORY STRENGTH signals maintain their VALUE for the period of time specified with the DECAY\_TIME directive. After this time they assume UNDEFINED VALUE. DECAY\_TIME is measured from the time the signal was last driven to the specified value. All signals in a design have the same decay time. The default value for DECAY TIME is infinite.

The combination of each of the three signal values with each of the four signal strengths gives the 12 signal states that are reported. The combination of INDETERMINATE strength and UNKNOWN value is interpreted as Z (highimpedance). The state names and abbreviations are:

| STATE NAME            | ABBREVIATION  |

|-----------------------|---------------|

| HARD_STATE_0          | hO            |

| SOFT_STATE_0          | $\mathbf{s0}$ |

| MEMORY_STATE_0        | m0            |

| INDETERMINATE_STATE_0 | iO            |

| HARD_STATE_1          | h1            |

| SOFT STATE 1          | sl            |

| MEMORY_STATE_1        | m1            |

| INDETERMINATE_STATE_1 | i1            |

| HARD_STATE_U          | hU            |

| SOFT_STATE_U          | ${ m sU}$     |

| MEMORY_STATE_U        | mU            |

| STATE_Z               | Z             |

#### BIDIRECTIONAL NETS

Bidirectional nets are nets that connect to the pins of a PASS TRANSISTOR or RES primitive. DEPOSITing into bidirectional signals is not recommended as the deposited value does not persist very long due to the bidirectional net evaluation scheme used by the Simulator. Unidirectional drivers should be connected to those bidirectional nets that the user wishes to force to certain levels.

#### COMBINATION OF STATES

When more than one output drives a net, the state of the net is determined by combining the states of the driving outputs. When more than two outputs drive a net, the output states are combined iteratively. The following tables list all combinations of two states.

Introduction

|            | hO | s0 | m0         | iO | h1 | <b>s1</b>  |

|------------|----|----|------------|----|----|------------|

|            |    |    |            |    |    |            |

| h0         | h0 | h0 | h0         | h0 | hU | h0         |

| s0         | h0 | s0 | s0         | iO | h1 | sU         |

| m0         | h0 | s0 | m0         | i0 | h1 | s1         |

| iO         | h0 | iO | i0         | i0 | hU | hU         |

|            |    |    |            |    |    |            |

| h1         | hU | h1 | h1         | hU | h1 | h1         |

| <b>s</b> 1 | hO | sU | <b>s</b> 1 | hU | h1 | <b>s</b> 1 |

| m1         | h0 | s0 | mU         | hU | h1 | s1         |

| i1         | hU | hU | hU         | hU | h1 | i1         |

|            |    |    |            |    |    |            |

| hU         | hU | hU | hU         | hU | hU | hU         |

| sU         | h0 | sU | sU         | hU | h1 | sU         |

| mU         | h0 | s0 | mU         | hU | h1 | s1         |

| Z          | h0 | s0 | m <b>0</b> | i0 | h1 | <b>s</b> 1 |

|            |    |    |            |    |    |            |

| [] | m1  | i1 | hU | sU | mU | Z  |

|----|-----|----|----|----|----|----|

| h0 | h0  | hU | hU | h0 | h0 | h0 |

| s0 | s0  | hU | hU | sU | s0 | s0 |

| m0 | mU  | hU | hU | sU | mU | m0 |

| i0 | hU  | hU | hU | hU | hU | i0 |

| h1 | h1  | h1 | hU | h1 | h1 | h1 |

| s1 | s1  | i1 | hU | sU | s1 | s1 |

| m1 | m1  | i1 | hU | sU | mU | m1 |

| i1 | i1  | i1 | hU | hU | hU | i1 |

| hU | hU  | hU | hU | hU | hU | hU |

| sU | sU  | hU | hU | sU | sU | sU |

| mU | mU  | hU | hU | sU | mU | mU |

| Z  | hm1 | i1 | hU | sU | mU | Z  |

### **1.2 GETTING STARTED**

This section describes the different ways you can invoke the Simulator: the split-screen Simulator and the full-screen Simulator. It also describes window sizes and explains the two methods of invoking the Compiler.

#### SELECTING THE APPROPRIATE SIMULATION

The Simulator can be run on any of Valid's supported hardware configurations.

The two most common ways to run the Simulator are in full screen simulation with graphics or under GED in split-Full screen simulation is used for screen simulation. medium to large designs because signal values for 48 signals can be viewed simultaneously on the display. Splitscreen simulation is useful for smaller designs and for opening signals. You enter split-screen simulation directly from GED and the schematic appears in the top portion of the screen while the lower portion is used for the simulation display. Signals can be specified by a puck press in the GED window, rather than typing a signal name. All of the GED commands are available to the user as well as all of the Simulator commands. Because part of the screen shows the schematic in split-screen simulation, a fairly large screen is required and only 12 signals can be viewed at one time in the simulation display (use the ROW command to see the others). See Split Screen Simulation later in this section for additional information.

In addition to these two methods of running simulations, the Logic Simulator can also be run on an IBM or VAX mainframe. Full screen simulation is available in both Waveforms and Bus mode. All commands that do not require a puck are available, and in Waveforms mode, waveforms appear in character-graphics (because of the limitations of the hosts). User-coded primitives (UCPs) may also be used during simulation on an IBM or VAX mainframe.

## WINDOW SIZES

If the Simulator is invoked in a partial screen window, the window must be at least a minimum size. Under GED, this size is  $48 \times 86$  characters. The Simulator with character-graphics can be run in any window at least  $12 \times 80$ ; with regular graphics, the minimum window size is  $22 \times 80$ . The user is prevented from running the Simulator in any window that is smaller than required.

#### DIRECTIVES FILES

First, use the Graphics Editor to create the design to be simulated. Then edit the Compiler Directives file. Here is an example of a Compiler Directives file:

> root\_drawing 'subtractor'; compile sim; library standard, sim, lsttl, tutorial; directory 'susan.wrk'; directory '/u0/lib/mylib/mylib.lib'; warnings on; oversights on; output list, expand, synonym; print\_width 80; suppress 196; end.

In this sample directives file, the drawing to be compiled is named "subtractor." This drawing resides in the SCALD directory "susan.wrk". The format of the Compiler directives file is the same whether the Compiler is called directly (with the compile command), or from within the Simulator (simulate command). Any errors reported during compilation must be corrected before the design is simulated.

Next, edit the Simulator Directives File. Include the ROOT\_DRAWING directive and any other required directives. Specify the same root\_drawing name as in the Compiler directives file. When the ROOT\_DRAWING directive is included, the Simulator can call the Compiler directly.

Directives may be entered in either upper or lower case. Comments may be included if enclosed in curly brackets. Each directive must be terminated with a semicolon (;) and the file must end with an END. statement. Here is a sample Simulator Directives File.

> ROOT\_DRAWING 'subtractor'; CLOCK\_PERIOD 100; CLOCK\_INTERVALS 5; OUTPUT LIST, command\_log; SESSION\_LOG ON; TERMINAL GRAPHICS; USE\_IF BATCH; { rest of directives for batch only } COMMAND\_FILE 'BATCH.CMD'; TERMINAL TTY; { terminal type for batch mode } END.

When the Simulator Directives file is correct, the Simulator can be invoked immediately. Type the command "simulate" at the system prompt.

### STARTING SIMULATION

The Simulator starts by reading the Simulator directives file (simulate.cmd). If the ROOT\_DRAWING directive is specified in this file, or the drawing name given on the simulate command line, the Simulator calls the Compiler directly if it needs to, and then starts the Simulator if no Compiler errors are found. A command line argument overrides any root drawing name in the directives file. The root drawing name should match that in the Compiler directives file.

When the ROOT\_DRAWING directive is used, the COMPILER\_OUTPUT and SYNONYM\_FILE directives are ignored and any existing Compiler expansion and synonyms files are also ignored. The Compiler does NOT generate the expansion and synonyms files.

The Compiler generates error messages if there are any errors during the compilation. If the specified root drawing name is not found or if compile errors are detected, the Simulator will exit and Comperr is run automatically to collect the error reports. Look in the Compiler listing file (cmplst.dat) for Compiler error messages.

The program COMPERR can also be invoked explicitly to collect all the Compiler error messages. Any errors reported during compilation must be corrected before the design is simulated.

When there are no Compiler errors, the Simulator display appears.

If the ROOT\_DRAWING directive is not used, the Simulator requires as input two Compiler output files: the expansion file (cmpexp.dat) and the synonym file (cmpsyn.dat). If the names of these files are not the default names, use the COMPILER\_OUTPUT and SYNONYM\_FILE directives to specify the file names. If, for backwards compatibility, you need to generate Compiler output files, see the Compiler Reference Manual.

### **1.3 THE SIMULATOR DISPLAY**

The Simulator display screen is divided into three parts: the status lines at the top, the display area in the middle, and the echo area, at the bottom.

- The status lines report current simulation parameters such as the current simulation time, the current radix (or base) and the current scale or resolution. The status lines are updated periodically by the Simulator.

- The display area shows the values of signals selected by the user and, in Waveforms mode, their history.

• The echo area echos the commands as they are selected from the menu, as they are typed from the keyboard, and as they are issued from a script file.

On platforms having multiple windows, the size of the Simulator display area in full-screen simulation varies with the size of the window in which the Simulator is invoked. Not only does the number of lines increase (for up to 48 waveforms in a full-screen window), but the width of the display area also grows as the size of the window is increased above the minimum. The additional width is used to increase the space available for waveforms in Waveforms mode and to increase the total amount of space available for signal names and values in Bus mode.

### STATUS LINES

The status lines display the following fields:

| Time  | Radix    |

|-------|----------|

| Clock | Top Row  |

| Scale | Mem path |

| Scope | -        |

Mem path and Scope are displayed only in Bus mode, and Top Row is displayed only in Waveforms mode. Scope appears in the status line in Bus mode and below the display field in Waveforms mode.

- Time is the current simulation time in nanoseconds.

- Radix shows the current radix value, which can be binary, octal, decimal, hexadecimal, or strength.

- Clock indicates the clock period in nanoseconds and the number of intervals into which the clock has been subdivided.

- Top Row indicates the row number of the top row on the display in Waveforms mode.

- Scale is the scale factor that is set with the RESO-LUTION directive.

- Mem path is a memory pathname that indicates the result of the last successful MEMPATH command.

- Scope shows the default path name that may be set with the SCOPE command.

#### ECHO AREA

The echo area is used for echoing command inputs and displaying Simulator output information. Most of this information consists of either error messages or query responses.

In Waveforms mode, the first line of the echo area has three fields: Trigger, Cursor, and Scale.

- **Trigger** is the time the most recent Breakpoint was encountered.

- Cursor shows the location of the cursor. The cursor advances with simulation and can also be moved with the CURSOR command. The CURSOR command is useful for determining the time of a transition. The cursor may be placed at any time between 0 and the current time. The values of the signals on the display at the time specified by the cursor are displayed on the right side of the screen.

- Scale is the Scale factor that is set with the RESO-LUTION directive.

When running under GED, if a command results in several lines of output, the Simulator displays a few lines and prints

\*\* Press <RETURN> to continue \*\*

The Simulator then waits for a < RETURN > and ignores all other input until a < RETURN > is entered.

# DISPLAY AREA

In Waveforms mode a time line appears across the bottom of the display area and matching tick marks across the top. The characters T, C, and B also appear along the top of the display area. The T character marks the time of the most recent Trigger. The C character marks the cursor. When the T and C are in the same location, a B (for both) is displayed.

## DISPLAY MODES

The Simulator has two display modes. These are BUS mode and WAVEFORMS mode. Bus mode displays instantaneous values of a large group of signals selected by the user. Bus mode is used for very large circuits. Waveforms mode displays signal values for each signal as a waveform over time. Signals (scalars or buses) are displayed one to a line. In Waveforms mode signal values for up to 200 signals can be maintained. The number of signals that can be simultaneously displayed on the screen is determined by the type of terminal, as shown in the following table.

| Terminal Type | Maximum Number<br>of Waveforms Displayed |

|---------------|------------------------------------------|

| S-320/S-32    | 48                                       |

| IBM PC AT/GX  | 48                                       |

| IBM PC AT/EG  | 17                                       |

| IBM PC AT/VG  | 42                                       |

| MicroVAX      | 48                                       |

| Ann Arbor     | 34                                       |

| VT100         | 12                                       |

| IBM 3270      | 14                                       |

In the Waveforms mode, both the current value and a history of transitions are maintained for each signal. The signal history is displayed as a waveform (similar to that produced by a standard logic analyzer) and can be written to a file (using the PLOT command) for subsequent input to the Plottime program. The Plottime program produces timing diagrams that are GED drawings. See the Plottime Reference Manual.

#### 1.4 DISPLAYING SIGNAL VALUES

Signal values are displayed in one of five radices: binary, octal, decimal, hexadecimal, or strength. Binary numbers are indicated by a trailing "b", octal by "o", decimal by "d", hex by "h", and strength by "s". On input, numbers are assumed to be in the current radix. Each bit of a value may be either 1, 0, U (unknown), or Z (high impedance).

In binary, these bits are displayed as "1", "0", "U" or "Z". Unknown or high-impedance bits in octal or hex values cause the digit to which they map to be reported as "Z" if all bits in the digit are high impedance, otherwise "U". Unknown or high-impedance bits in decimal values cause the entire value to be displayed as "U".

In strength radix, values are displayed and input using the state abbreviations shown above (page 1-4). For example, "U0010ZZZZb" represents a binary value with the most significant bit unknown and the four least significant bits in high impedance. In hex, this value would be displayed as "U2Zh". In strength radix, this value might be displayed as ".hU.hO.s0.s1.mO..Z..Z..Zs" if some of the bits were HARD, some SOFT, and some MEMORY strength. In Waveforms mode, "------" is output in the column of signal values if there is insufficient space to display the entire value.

# SIGNAL VALUES IN BUS MODE

In Bus mode many signals are displayed on each line. A signal might not fit if its name and value require too much room horizontally. If this happens, open the signal instead as several subranges. The value for each range of bits will be shorter than the total signal value.

## SIGNAL VALUES IN WAVEFORMS MODE

Waveforms mode uses graphics to display signal values whenever the terminal has graphics capabilities. When running simulation on a VAX or IBM mainframe, where graphics are not available, character graphics are used. On the SCALDSystem IV waveforms look slightly different than on other systems because they are formed using a graphical character set.

# **GRAPHICS FOR SIGNAL VALUES**

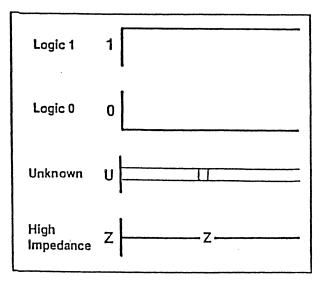

When standard graphics are being used, single bit signals (scalars) are represented as shown in Figure 1-1:

Figure 1-1. Graphics for Scalar Signals

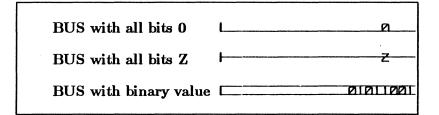

Multiple bit signals (buses) are represented as shown in Figure 1-2:

Figure 1-2. Graphics for Bus Signals

When using standard graphics, all signal transitions are indicated by a vertical line at the transition time; multiple transitions at a single time are indicated by a bold vertical line.

A typical scalar signal is shown in Figure 1-3:

Figure 1-3. Scalar Signal

This signal has the history: 0,1,U,0,Z.

A typical bus signal (vector) is shown in Figure 1-4:

BUS(15..0) 4301 A034 A0A

Figure 1-4. Bus Signal

This bus has the history: 43D1,?,AD34,0000,000U (where "?" indicates that the value is too large to fit in the display space). To view a signal value that is too large to fit in the display, use the WAVEFORM command to zoom in on the simulation time when that signal value occurred.

# USING CHARACTER GRAPHICS

When character graphics are being used single bit signals (scalars) are represented as follows:

| Logic 1            | ****** |

|--------------------|--------|

| Logic 0<br>Unknown | U      |

| High Impedance     | Z      |

Multiple bit signals (buses) are represented as follows:

| All bits 1                         | ^^val^^      |

|------------------------------------|--------------|

| All bits 0                         | 0            |

| All bits Z                         | Z            |

| With value xxx                     | <i>=xxx=</i> |

| With value too<br>large to display |              |

When character-graphics are being used, the following characters are used to indicate different transitions:

- / low-to-high transition

- high-to-low transition

- X multiple transitions mapping to same character

- > transition to Z

- all other transitions (including transition to U)

A multiple transition symbol is displayed only if some bit of the signal has changed two or more times during the time mapping to the display position. If a bus undergoes several transitions, but each bit changes only once, a multiple transition has not occurred.

## 1.5 WORKING WITH SIGNAL VALUES

### OPENING SIGNALS

When the user "opens" a signal name, that signal and its value appear in the main display. Signal names are in standard SCALD syntax, except that bit lists and step values are not permitted. Names are right-justified in Waveforms mode. The currently open signal is indicated by a "->" preceding the signal value. The value of the signal appears left-justified in the current radix. This value may be changed by "depositing" some other value. The last signal to be opened may be changed at any time in this fashion.

Any subrange of a signal may be displayed. If no bit range is given for a signal vector, then the entire vector is OPENed. A signal also may be displayed any number of times in different radices. A change made to the value of one version of the signal affects all the others. Introduction

Logic Simulator

A signal may be known by more than one name. A bit may be common to a group of signals. For example, the signal ADR BUS<31..0> may also be known as SYSTEM BUS<71..40> and also as CHIP SELECT<5..0>: MEMORY ADR<27..0>. The user may refer to the signal using any of its names.

#### **OPENING MEMORIES**

The contents of memories are displayed in a somewhat different fashion from signals. First, the pathname to the memory primitive is specified with the MEMPATH command (see the Commands section) and then the OPEN-MEMORY command is used to open the desired addresses. This sequence causes an entry to be made in the main display area. This entry displays on the left the memory pathname followed by the address (enclosed in parentheses). On the right the value stored in the memory at that address is displayed (right justified in the current radix). Bit ranges are not permitted in memory displays.

### INITIALIZATION OF SIGNALS AND MEMORIES

At the start of a simulation session, each signal is set to the undefined state U. The LOGIC\_INIT and MEM\_INIT commands are used to initialize all signals or all memories to a specific value. Signals and memories may be initialized to 0, 1, undefined (U), asserted (\*) or unasserted (-\*). If a signal has neither low assertion nor negation characters, or if it has both, then its asserted state is one; otherwise it is zero. For example, if - is the negation character and \* is the trailing low assertion character, then SIG A and -SIG B\* have an asserted state of zero. Memories with a bubbled output have an asserted state of zero; other memories have an asserted state of one.

# CHANGING SIGNAL VALUES

The user may change the value of any signal, whether driven or undriven. When the user changes the value of a signal that is driven, the signal value specified remains on the net until overridden by a driver. When a signal has a clock assertion (!P or !C) and is not driven by an output in the circuit, the signal generated by the Logic Simulator has the timing behavior specified by the clock assertion. Signal assertions with the prefixes !S and !D are ignored by the Simulator.

#### CHANGING MEMORY VALUES

The user may change the value of any memory location in the design by opening a location with the OPENMEMORY command and then DEPOSITing the desired value to that location. The location retains this value until a memory write is done to the matching address or until another DEPOSIT is done into that location.

### **1.6 ADVANCING SIMULATION TIME**

The user can cause the simulated time to advance by typing "SIMULATE C" (simulate for a clock period), "SIMULATE S" (simulate for the STEP time), or "SIMULATE value (simulate for value nanoseconds). Primitives are evaluated and values are changed as time advances until the designated simulation time elapses. When this time is reached, the status lines and the values of all the signals in the main display are updated appropriately. The command "SIMU-LATE 0" can be used to immediately cause the evaluation of any zero-delay parts.

The Simulator is able to detect zero-delay loops during simulation (except when using Realfast). This facility does not attempt to detect all the possible oscillations, but simply the loops that would otherwise cause the Simulator to enter an infinite loop. When a zero-delay loop is detected, a warning message appears and the SIMULATE command is terminated. You will typically want to exit from the Simulator and fix the error in the design.

# **1.7 SIMULATOR OUTPUT**

The Simulator produces four output files: a listing file (simlst.dat), a log file (simlog.dat), a command file (simcmd.dat), and a Waveform Input file (plotsig.dat).

File names for these files are slightly different when the Valid verification tools are run under different operating systems (UNIX, VMS, CMS). Under UNIX, the file names are:

| Simulator Listing File |      | $\mathbf{simlst.dat}$ |

|------------------------|------|-----------------------|

| Simulator Log File     |      | simlog.dat            |

| Simulator Command File | ==== | simcmd.dat            |

| Waveform Input File    |      | plotsig.dat           |

For file names under VMS and CMS, see File Names later in this section.

The log file is produced every time you run the Simulator. The OUTPUT directive regulates whether the listing file and the command file are produced. The Waveform Input file is produced when you use the PLOT command.

Each time the Logic Simulator is run from the same directory, the output files are overwritten. This saves considerable amounts of disk space. Here is a brief description of each of the Simulator output files.

### LISTING FILE

The Listing file **simlst.dat** contains a summary of the directives, process information on the Simulator run, and error information. The directive SESSION\_LOG ON causes a record of all terminal I/O for the Simulator session to be sent to the listing file. The SNAPSHOT command sends an image of the status lines and signal display window to the listing file. By using the SESSION\_LOG directive and the SNAPSHOT command a permanent record of a simulation session can be created. For more details, see the section on Logic Simulator Directives.

Introduction

# LOG FILE

The Log file **simlog.dat** is used primarily by internal personnel to track down Simulator errors. In addition to process and error information, this file contains statistics on the memory requirements of the Simulator run.

# COMMAND FILE

The Command file **simcmd.dat** is a list of all of the commands issued in a Simulator session. It is used to exactly duplicate a simulation session, or to run a batch simulation. Edit the simcmd.dat file as required and rename it. Then use the SCRIPT command or the COMMAND\_FILE directive to invoke the renamed file. See the SCRIPT command for more information on command files.

## WAVEFORM INPUT FILE

The Waveform Input File plotsig.dat is an ASCII file that serves as the input file to the program Plottime which produces waveform diagrams of the signals from the design verified. Plottime produces waveform diagrams from a Simulator output file as well as from a Timing Verifier output file. The PLOT command is used to produce the Waveform Input file. One or several Waveform Input files can be produced during a simulation session. By default the Waveform Input file is named plotsig.dat but another name or names can be specified. For more information on Plottime, see the Plottime Reference Manual.

### 1.8 FILE NAMES

The Simulator file names vary under different operating systems. The table below shows the file names under different operating systems for the Simulator's input and output files.

| File       | <b>UNIX</b>  | VMS          | CMS          |

|------------|--------------|--------------|--------------|

| Directives | simulate.cmd | SIMULATE.CMD | SIMULATE CMD |

| Expansion  | cmpexp.dat   | CMPEXP.DAT   | CMPEXP DATA  |

| Synonym    | cmpsyn.dat   | CMPSYN.DAT   | CMPSYN DATA  |

| Listing    | simlst.dat   | SIMLST.DAT   | SIMLST DATA  |

| Log        | simlog.dat   | SIMLOG.DAT   | SIMLOG DATA  |

| Waveform   | plotsig.dat  | PLOTSIG.DAT  | PLOTSIG DATA |

| Command    | simcmd.dat   | SIMCMD.DAT   | SIMCMD DATA  |

Table 1-1. Logic Simulator Input and Output Files

### **1.9 SPLIT-SCREEN SIMULATION**

The Graphics Editor SIMULATE command creates a splitscreen display (with GED in the top portion and the Simulator below) and invokes the Simulator. A sufficiently large window is required to run the split-screen Simulator; the minimum size is 48 x 86 characters.

Before simulating, the user MUST write out the drawing if any changes have been made during the current editing session and the changes are to be reflected during simulation. If Compiler errors are found, the Simulator exits and returns to the standard GED display.

### **Differences from Full Screen Simulation**

• The user may specify a signal visible in the upper (GED) window by pointing to it with the puck instead of typing the name. For example, to open a signal, select OPEN from the menu with the puck, point to the signal to be opened, and then point to the line of the Simulator display where you want the signal to be placed (or select; from the menu for default placement). To open an unnamed signal point to the wire.

- A command selected from the Graphics Editor window returns the user to the Graphics Editor and suspends the Simulator. A command selected from the Simulator menu, or selecting the SIMULATE command from the Graphics Editor menu, returns control to the Simulator.

- The Simulator command EXIT terminates the Simulator and causes the GED display to fill the entire window.

- If the Graphics Editor is used to change a drawing while the Simulator is running, simulation data will be inconsistent with the new version of the drawing. To simulate the modified drawing, you must EXIT the Simulator and restart simulation. It is not necessary to exit the Graphics Editor.

- "Softkeys" defined in the Graphics Editor can be used with the Simulator to save typing.

•

# SECTION 2 LOGIC SIMULATOR DIRECTIVES

Simulator directives are parameters that control the simulation session. These directives control error reporting, I/O, and the Simulator's interpretation of the input from the Compiler. You enter directives in the Simulator directives file (simulate.cmd).

Each of the directives is described below, along with an example where usage may not be obvious. The Logic Simulator directives and their parameters are not case sensitive; each directive must be on a separate line and must be terminated by a semicolon.

#### BINARY\_TRACE

Specifying BINARY\_TRACE ON causes the Value File to be output in binary. The default, BINARY\_TRACE OFF, causes the Value File to be an ASCII file. This directive is ignored for Tabular tracing.

#### CLOCK\_INTERVALS

This directive sets the number of evenly spaced sub-periods within the clock period. For example, if there are eight sub-periods and the period of the clock is 100 ns, then MASTER CLK !C 0-2 is high from time 0 ns to time 25 ns and low from 25ns to 100ns. The directive

#### CLOCK\_PERIOD 100;

sets the clock period to 100 ns and the directive

### CLOCK\_INTERVALS 20;

divides the clock into 20 intervals of equal length. With a clock period of 100 ns, each interval is 5 ns long.

For example, the signal MASTER CLK !C 0-10,15-20 is high for the first ten intervals, (that is, from 0 to 50ns) and then high again for the last five intervals, from 75 to 100 ns. The signal history for this clock is:

MASTER CLK !C 0-10, 15-20 = 1:0, 0:50, 1:75

If CLOCK\_INTERVALS is unspecified, the clock is divided into ten intervals.

### CLOCK\_ON\_DRIVEN

Specifies whether clock generators may be specified on driven signals. The default for the directive is OFF, which will only permit timing assertions to be specified on undriven signals. Thus, building a clock generator on a driven signal is not allowed unless this directive is specified as ON.

### CLOCK\_PERIOD

Sets the period of the clock used by the Simulator. This clock period is used defining the behavior of clock signals. Clock period is specified in nanoseconds. All signals with an "!C" or "!P" timing assertion (e.g., MASTER CLK !C 0-3) have their behavior specified relative to this period. The directive

### CLOCK\_PERIOD 56;

sets the clock period to 56 ns. If unspecified, the Simulator sets the period to 100 ns. The clock period must be an integer and may be changed during simulation using the PERIOD command.

## COMMAND\_FILE

Specifies the name of a command file to be invoked as soon as the Simulator starts. This directive lets you run the Simulator in batch mode. A command file can be quickly made from the Simulator output file simcmd.dat by editing it and renaming it. The file name must be enclosed in quotes. See the SCRIPT command for a description of command files.

COMMAND\_FILE 'mysetup.dat';

#### COMPILER\_OUTPUT

This directive is used with the SYNONYM\_FILE directive to run a simulation of a design from existing Compiler files when those files do not have the default names. This directive is used to specify the name of the Compiler expansion file of the design to be simulated. When this directive is not specified, the default filename 'cmpexp.dat' is used. The file name must be enclosed in quotes. This directive is ignored when the ROOT\_DRAWING directive is present.

#### DECAY\_TIME

This directive specifies the time at which MEMORY strength signals lose their value and assume an UNDEFINED value. The default value is infinite. This means that MOS signal strengths will not decay over time unless the user explicitly specifies a decay time. The directive takes an integer. The units are nanoseconds.

### DEFAULT\_DRIVE

This directive is used to specify default values for rise drive and fall drive. The directive takes two values separated by commas. The first value specifies rise drive, the second specifies fall drive. Values are given as real numbers and are used for all pins whose drive is not otherwise specified. See the section on the Delay Estimator and Expression Evaluator. Here is an example directive:

DEFAULT\_DRIVE 0.35,0.5;

# DELAY\_ESTIMATOR

This directive is used to turn the Delay Estimator feature on and off. The default value is OFF. The directive

# DELAY\_ESTIMATOR ON;

enables the Delay Estimator. See the section on the Delay Estimator and Expression Evaluator.

# DELAY\_MODE

Delays in simulation models may be specified as a series of three values in square brackets. When this notation is used, the first value is the minimum delay, the second is the typical delay, and the third value is the maximum delay. This directive is used to select which of the three values is to be used for the current simulation run. The directive takes the values MIN, TYP, or MAX. The default value is MAX.

When using this directive, the appropriate delay values must be specified for each part used in the design. All parts with non-zero delay values must use the RISE and FALL properties or the DELAY property to specify these values using the following syntax:

```

RISE=[min,typ,max]

FALL=[min,typ,max]

DELAY=[min,typ,max],[min,typ,max]

```

If the DRIVE property is being used, minimum, typical, and maximum values must also be specified using the following syntax:

DRIVE=[min,typ,max],[min,typ,max]

Note that the square brackets are required characters in the syntax for the above properties. The values given for min, typ, and max may be either integers or real numbers. See the Delay Estimator and Expression Evaluator section.

### EXP\_EVALUATOR

This directive is used to turn the expression evaluator feature on and off. The default value is OFF. To enable the expression evaluator, use the directive

#### EXP\_EVALUATOR ON;

See the Delay Estimator and Expression Evaluator section.

### MEM\_STATE

This directive selects between two-state memories and four-state memories. A four-state memory retains U's; a two-state memory does not. This directive takes the values 2 or 4. If not specified, memories are four-state (in fact, a misnomer since there are only three actual states). To use two-state memories use the directive

MEM\_STATE 2;

# OUTPUT [NO] { LIST , COMMAND\_LOG } ;

This directive determines which output files are produced by the Simulator. When no directive is given, no files are created. The output file specifiers are: LIST causes the listing file simlst.dat to be created. The contents of the list file are controlled by other directives.

COMMAND\_LOG is a file containing all of the commands that the Simulator processed. After renaming, this file can be used as an input command file (either using the COMMAND\_FILE . directive or the SCRIPT command).

#### PIN\_DELAY

This directive specifies whether pin-to-pin delays will be used by the Simulator. The values for this directive are ON and OFF. When ON is specified, the pin delay properties override the body delay properties; otherwise, the body delay properties override the pin delay properties. The default state for this directive is OFF. When pin delay values are not defined for a particular pair of input and output pins, the body delay values are assumed.

### **REALCHIP\_LIBRARY**

Specifies the name of the Realchip library file containing the full set of Realchip device definition blocks for primitives modeled by Realchip reference elements. This directive must be used if any Realchip models are used by the Simulator. Otherwise, this directive can be omitted. The file name must be enclosed in quotes. An example directive is

REALCHIP\_LIBRARY 'realchip.dat';

### REMOTE\_HOST

Specifies the name of the machine or machines on the network containing Realchip/Realmodel modeling hardware and the Networked Realchip Server software to serve as a remote host for simulation. This directive enables the NETWORKED mode of operation, in which patterns can be sent to remote modeling hardware over the network connection. If this directive is not specified, the HOSTED mode will be used, accessing local modeling hardware directly. Each host name must be enclosed in quotes. When several host names are given, they are separated by commas. Here is an example directive:

### REMOTE\_HOST 'vserver', 'hostsim';

### RESOLUTION

This directive specifies the time resolution to be used by the Simulator. The value of the directive is a real number that specifies nanoseconds. The default value is 1. Numbers smaller than 1 are used to specify finer resolution, numbers larger than 1 are used to specify coarser resolution. The resolution currently in use by the Simulator is indicated in the display area under the label "Scale". The directive

# RESOLUTION 0.05;

means that each tick on the time scale used in Waveforms mode no longer represents one nanosecond, but now represents 0.05 ns. Values specified in ns (clock period, delays, decay times, etc.) will remain in ns, but are scaled on the display (e.g., a clock period of 100 ns will appear on the display with a period of 2000 ticks; "DECAY\_TIME 5000" will cause memory signals to change value after 100000 ticks). Screen-oriented commands (SIM, WAVE, HISTORY, CURSOR, etc.) maintain their relation to ticks on the screen, although the "real" times associated with those ticks has changed. The command WAVEFORMS 0 1000 displays a time scale of 0 to 1000 ticks, but each tick now represents 0.05 ns.

Exercise caution when changing the resolution. Too fine a resolution will decrease execution speed (simulating for hundreds of ticks even when no events are scheduled) or generate massive amounts of signal histories. Before decreasing the resolution, ensure that the specification of other time values is correspondingly coarse (e.g., "RESOLUTION 50" probably will not make sense with a 20 ns clock period).

### RISE\_FALL

This directive specifies whether separate RISE/FALL delays will be used by the Simulator. When the RISE\_FALL directive is ON, simulations are performed using both the rise and fall delays specified for parts and between pins on parts. When RISE/FALL or PRISE/PFALL values are not specified, the values of the DELAY and PDELAY properties are used. When the RISE FALL directive is OFF, the values of the DELAY and PDELAY properties override. When the RISE FALL directive is OFF and neither DELAY nor PDELAY properties are used, delay values are derived from the delay time if only one value is given (RISE or FALL but not both, or PRISE or PFALL but not both) or using the greater of the rise and fall delays. The default state of this directive is ON.

The following table summarizes the delay values that are used. The notation "a:b" indicates that the value "b" is assumed if the value "a" is not defined.

| RISE_FALL | ON<br>RISE FALL | OFF<br>RISE FALL |

|-----------|-----------------|------------------|

| no DELAY  | r:0 f:0         | max(r,f):0       |

| DELAY=x   | r:x f:x         | хх               |

| DELAY=x,y | r:x f:y         | $\max(x,y)$      |

When the use of the separate rise/fall delay feature is specified, the part delay used for the various transitions is as follows (where X indicates any value):

| OLD VALUE | NEW VALUE | DELAY USED     |

|-----------|-----------|----------------|

| X         | 0         | fall           |

| X         | 1         | rise           |

| X         | U         | min(rise,fall) |

| 0         | Z         | rise           |

| 1         | Z         | fall           |

| U         | Z         | max(rise,fall) |

### **ROOT\_DRAWING**

This directive specifies the name of the drawing on which you wish to perform simulation. Using this directive, the Simulator calls the Compiler directly, and only as needed. The name of the drawing is enclosed in quotes, like this:

### ROOT\_DRAWING 'counter';

To run a simulation using an existing Compiler expansion file, omit this directive.

#### SESSION\_LOG

This directive specifies whether a copy of terminal I/O is to be output to the listing file. The directive takes the value ON or OFF. Note that SESSION\_LOG ON and OUTPUT NO LIST are incompatible.

#### SIGNAME\_CHARS

This directive defines the number of character columns dedicated to signal names on the left side of the screen in WAVEFORMS mode. The default value is 24. This directive can take the values 9 through 24 inclusive. Values outside the legal range will be rounded to the closest legal value. Here is an example directive

#### SIGNAME\_CHARS 18;

As the number of characters is decreased, the space available for waveforms is correspondingly increased; however, with fewer characters available for signal names, a greater number of characters will be truncated when the length of the signal names exceeds the space available. Use the PEEK command to see the full signal name.

### SYNONYM\_FILE

This directive is used in conjunction with the COMPILER\_OUTPUT directive to perform a simulation on a design from existing Compiler files when the Compiler files do not have the default names. This directive gives the name of the synonyms file. If no synonyms file is specified with this directive, the default filename 'cmpsyn.dat' is used. The file name must be enclosed in quotes. This directive is ignored when the ROOT\_DRAWING directive is present.

### TABULAR\_TRACE

This directive specifies the trace format. TABULAR\_TRACE OFF, the default, specifies standard trace format, while TABULAR\_TRACE ON specifies tabular trace format.

### TERMINAL

This directive specifies the terminal type. The allowed values are:

ANNARBOR CLUSTER GCLUSTER GRAPHICS VT100 3270 TTY

CLUSTER designates a SCALD system terminal running the Simulator locally or in transparent mode connected to the host computer.

GCLUSTER designates a SCALD system terminal with graphics capabilities.

GRAPHICS designates an IBM PC or a MicroVAX II.

ANNARBOR designates an Ann Arbor Ambassador terminal with 48 lines.

TTY designates any dumb video terminal or a teletype.

VT100 designates a DEC VT100 (or equivalent) with 24 lines.

3270 designates an IBM 3270 or equivalent.

If the Simulator is running in a Graphics Editor window, the TERMINAL directive is ignored.

### TIMING\_CHECK

This directive is used to enable timing checkers used in simulation models. The directive takes the values ON or OFF. When this directive is ON, the Simulator recognizes all the timing checker primitives used in the simulation models for the circuit and performs timing violation checking accordingly. When TIMING\_CHECK is OFF, the Simulator ignores all the timing checkers and performs no timing violation checking. For designs you are validating with both ValidTIME and ValidSIM, use TIMING\_CHECK OFF. The Simulator does not need to do timing analysis and this will speed simulation. The default value for this directive is OFF.

### TRACE\_RADIX

This directive specifies the radix to use for tabular tracing. The directive can take the values 2, 8, 10, or 16. The default value is 2. Here is an example directive.

### TRACE\_RADIX 16;

### USE\_IF

This directive is used to include two sets of directives in a single directives file: one set for batch simulation, one set for interactive simulation. The USE\_IF directive takes one of two values: BATCH or INTERACTIVE. The following directives are only used if the Simulator is run in the specified mode. The USE\_IF directive has effect until the next USE\_IF directive, or until the end of the directives file. The following example of the USE\_IF directive instructs the Simulator to use a command file, create a session log, and set the terminal type to TTY when the Simulator is run as a batch process. This directive is useful primarily on systems such as the VAX where programs can be run either interactively or as a batch process.

#### USE\_IF BATCH; COMMAND\_FILE 'BATCHSIM.CMD'; TERMINAL TTY; SESSION\_LOG ON;

#### USE\_REALFAST

This directive controls the use of the Realfast Simulation Accelerator and the Realmodel Modeling System. The directive takes the values ON or OFF. When enabled (USE\_REALFAST ON;), a simulation is aborted if the Simulator cannot access the Realfast hardware (Realfast currently can not be shared between work stations; simultaneous use by more than one work station is prohibited). Simulation results using Realfast are the same as without its use - Realfast simply increases the speed of simulation. If this directive is omitted, Realfast is not used.

### USE\_SYNONYM

This directive instructs the Simulator whether or not to read the Compiler's synonyms file. Not reading the synonyms file decreases simulation loading time; however, signals can then only be referenced by their base names. The default is ON (i.e., the synonyms file is read).

### USER\_EXPRESSION $expr_id$ (param...) = equation;

This directive is used with the Expression Evaluator. When the directive EXP\_EVALUATOR OFF; is used, this directive is ignored. This directive is used to define a user-defined delay equation for computing primitive delays. *expr\_id* is a name assigned by the user to the expression being defined. This is followed by a list of *params*, enclosed in parentheses, which are the variables used in *equation*. *equation* is some combination of boolean and arithmetic operations which describe an equation to be used in

#### Directives

computing the delay. See the Delay Estimator and Expression Evaluator section. Here is an example directive:

USER\_EXPRESSION BufDelay(Cof)= [load <= Cof]'drive \* load', [Cof < load <= 4 \* Cof]'1.5 \* drive \* Cof';

## USER\_PARAMETER $param_id = (x [, x ...]);$

This directive is used with the Expression Evaluator. When the directive EXP\_EVALUATOR OFF; is used, this directive is ignored. This directive is used to define user-defined parameters used in the delay equation specified with the USER\_EXPRESSION directive. x is a real number. Up to five real numbers may be specified and should be enclosed in parentheses. *param\_id* is a name assigned by the user to the set of parameters being defined. See the USER\_EXPRESSION directive and the Delay Estimator and Expression Evaluator section. Here is an example directive:

### USER\_PARAMETER INV1=18;

### WIRE\_DELAYS

This directive specifies the name of the wire delays file; the filename must be quoted. See the Delays section. Here is an example directive:

WIRE\_DELAYS 'wiredel.dat';

### WIRE\_ESTIMATE

This directive is used with the Delay Estimator. It allows the user to define a look-up table specifying equivalent loads of a net. The look-up table contains a list of values corresponding to the delays associated with incrementally increasing load. Up to 100 real values may be specified. The values are separated by commas, like this:

#### WIRE\_ESTIMATE 5.5,6,6.4,6.8,7.1,7.5;

The directive can also take a family name parameter, so that different look-up tables can be used for different families of parts. Here is an example:

#### WIRE\_ESTIMATE TTL 5.5,6,6.4,6.8,7.1,7.5;

The body property FAMILY is attached to all bodies for which the alternate look-up tables are to be used. See the Delay Estimator and Expression Evaluator section for more information. , .

# SECTION 3 WAVEFORMS MODE

This section describes how to use the Simulator in Waveforms mode. Waveforms mode displays the value of each signal as a waveform over time. Using Waveforms mode, you can see twelve signals at one time in the split screen Simulator under GED, or up to 48 signals at one time in the full screen Simulator.

A certain group of commands that are not appropriate for use in Bus mode, are used in Waveforms mode. These commands are:

| WAVEFORMS  | ROW     |

|------------|---------|

| HISTORY    | SCROLL  |

| CURSOR     | SPACING |

| DELTA_TIME |         |

Each of these commands are described below. In addition, the OPEN command is also described below because it works differently under Waveform Mode than it does under bus mode.

Many of these commands take a number argument that designates time in nanoseconds. These number arguments are all affected by the value of the RESOLUTION directive. When RESOLUTION = 1 (the default) each tick mark on the Waveforms display represents 1 ns and the number arguments represent nanoseconds. When RESOLUTION = 10, for example, each tick mark represents 10 ns and the number arguments represent tick marks. The command

#### CURSOR 100

moves the Cursor to the tick mark labeled 100, which actually represents 1000 ns.

# 3.1 WAVEFORM COMMANDS

The following commands are commonly used in the Waveforms mode and affect the signal display.

#### WAVEFORMS start\_time end\_time or WAVEFORMS pt1 pt2

This command has two separate functions: the first is to invoke Waveforms mode and define the range of time to be displayed; the second is to pan and zoom on displayed waveforms to get a better view. Because Bus mode is the default, the first time you give the WAVEFORMS command, it invokes Waveforms mode. Be sure that you give both a start time and an end time. The Waveforms display advances automatically with simulation.

While you are in Waveforms mode, the WAVEFORMS command is used to pan and zoom the display. Several different syntaxes are available for using the waveforms command to pan and zoom.

1. The most common form of the WAVEFORMS command is

### WAVEFORM 100 300

The two numbers designate real time in nanoseconds. The first number is the start time and the second is the end time. On systems with a puck or mouse, the times can be designated as points on the waveforms display (to zoom in) or as points on the time line in the echo area (to zoom out). If the end\_time or pt2 is omitted, the current display width (end\_time - start\_time) is used with the new start\_time. The screen pans to the right.

2. The times can also be given as *relative* times, by using this syntax:

WAVEFORM left 100 right 400 WAVEFORM right 100 right 50 In this syntax the start time (the first parameter) is relative to the existing start time, and the end time (the second parameter) is relative to the new start time.

#### HISTORY time

The History command is used to set the time period during which signal history for each opened signal is maintained. When Waveforms mode is entered, HISTORY is automatically set to 10000 for all OPENED signals. Setting HIS-TORY to a smaller number can improve performance. When HISTORY is 500, signal history is only kept for each OPEN signal for the 500 ns prior to the current time. The HISTORY command is affected by the RESOLUTION directive. When using a large number for resolution, you will probably want to set HISTORY to a smaller number.

The HISTORY command with no argument tells you the current value for HISTORY.

#### CURSOR time

This command moves the cursor to a new time. The *time* parameter may be specified by giving a number, or using a puck press on the waveforms display or on the time line in the echo area. When a number is given, the units are nanoseconds, and are affected by the value of the RESO-LUTION directive.

A relative time can be specified by using the syntax:

#### CURSOR LEFT 25 CURSOR RIGHT 100

Whenever the cursor is moved, the signal values on the right side of the screen are changed to indicate the signal values at the cursor time. The cursor may be set to any time between 0 and the current time, whether the new time is visible or not. In full-screen graphics mode, if the new time is visible, a vertical line is drawn through the entire waveform display area; this line is displayed on all empty

#### Waveforms

Logic Simulator

rows including the blank rows between waveforms when SPACING is greater than 1. When simulation is complete, the cursor is automatically moved to the current time.

In full-screen graphics mode a timeline appears in the echo area and the value for the CURSOR command can be given by a puck press on this line. The timeline does not appear when running split-screen simulation under GED.

### DELTA\_TIME pt1 pt2

The DELta\_time command is used to determine the time difference between two points on the current waveform display. The points are specified using the puck, so this command is only available on systems having a puck. The value appears in the echo area. Points can be specified anywhere in the current waveforms display.

**OPEN** signal [, row [, col]]

**OPEN** signal pt [ ( dest pt signal pt )... ] [ dest pt ]

The OPEN command adds a signal to the display, and in Waveforms mode it starts recording signal history for that signal.

In split-screen simulation, a signal can be opened by selecting it with the puck in the GED drawing, and either giving a destination point with the puck or ending the command.

When a destination point is given the signal is opened on that line of the display. When none is given, the signal is opened on the first available line (if the signal has not been opened before). You can open a maximum of 200 signals. The command must be terminated by a semicolon or carriage return. The user can replace an existing signal by opening a new signal and specifying *row*. Once a signal is OPENed in Waveforms mode, the history for the signal is maintained for the specified history period, even if the signal is not on the screen. To remove an OPEN signal, use the REMOVE command or OPEN another signal on the same row. This feature allows a user to OPEN more signals than can be displayed at once, simulate to calculate their signal behavior, and then view their behavior.

### ROW number

This command controls which signals are displayed on the screen. The *number* gives the row number for the row that is to be placed at the top of the screen. Relative row numbers may also be specified by preceding the number with a + or - sign, or by pointing to the row using the puck. The number of the top row currently displayed on the screen is shown as one of the fields on the status line. Note that when changing the top row, all signals previously displayed above the new top row are scrolled up and off of the screen.

### SCROLL

This command allows the user to control the automatic scrolling feature of the Simulator. The command takes the argument ON or OFF. In Waveforms mode, when you have a full-screen of signals, the Simulator normally scrolls the display to OPEN each additional new signal. If you have many signals to open, it is faster to turn SCROLL off, until OPEN and DEPOSIT is completed. Using SCROLL OFF allows the user to OPEN and DEPOSIT into signals that are not on the display.

### SPACING value

This command allows the user to specify single or double (or multiple) spacing between adjacent waveforms in Waveforms mode. *value* is an integer indicating the number of spaces between waveforms. The default is 1 (single spacing). The current SPACING value is displayed in the echo area. Whenever the value of SPACING is changed, the screen is redrawn using the new value of SPACING.

# SECTION 4 BREAKPOINTS AND PATCHING

Breakpoints are triggering conditions that cause the Simulator to stop simulating and accept commands from the user. The following are some important uses of breakpoints:

- Skipping to a point of interest; for example, when a shift register shifts to all zeros.

- Performing "background" tests while the user stimulates the design (such as stopping whenever the design enters an error condition).

The logic patching facility allows the user to make simple modifications to a design without recompiling. This facility is useful primarily for "tacking" bug fixes in before they are entered into the design, or for stimulating an incomplete design. Some example uses are:

- Patching a design by forcing signals to some state, such as forcing the PARITY ERROR signal to a 0 whenever some pattern is read that is incorrectly reported as an error.

- Generating test stimuli based on the state of the design, such as submitting instruction N+1 whenever instruction N has completed.

The Patch facility allows you to temporarily assign a particular signal value to a signal during a simulation session. The commands you use are similar to the breakpoint commands.

### 4.1 BREAKPOINTS

Breakpointing conditions are boolean expressions of signals present in the design (refer to expression syntax). A breakpoint is encountered (triggers) when the expression defining it changes value from false to true.

#### Breakpoints

In addition to the standard boolean operators AND, OR, XOR, and NOT, state information can be included in breakpoint expressions to allow the user to build a state machine that detects when to trigger a breakpoint. This general form of the trigger-enabling feature is used in most logic analyzers.

To simplify construction of complex breakpoints, a new class of signal called an ENABLE signal has been added to the Simulator. ENABLE signals never exist in a design, but are created by the user as partial products in expressions. ENABLE signal names follow the same rules as standard signal names, but they are always scalars.

Simulation halts to display a breakpoint expression, but the system remains in interactive mode. The user may perform other operations or may continue simulation using another SIMULATE command.

If a breakpoint is encountered during execution of a SIMU-LATE command in a command file, simulation time stops at the breakpoint and the next command in the script is executed. This allows the user to create scripts for circuits where it is unknown how long to simulate before a certain event will occur.

Note that breakpoints should not be used when operating REALFAST.

### 4.2 BREAKPOINT COMMANDS

This section contains a list of commands used with breakpoints. See the following section for a description of breakpoint syntax.

### SET ENABLE signal WHEN expr

Sets *signal* to 1 when *expr* is true. The signal is a "new" signal that is created the first time it is referenced by the user (i.e., the signal cannot already exist in the design).

# CLEAR ENABLE signal WHEN expr

Clears *signal* to 0 when *expr* is true. The signal is a "new" signal that is created the first time it is referenced by the user (i.e., the signal cannot already exist in the design).

### SAMPLE ENABLE signal GETS expr 1 WHEN expr 2

Equates signal to the value of expr 1 when expr 2 changes from a 0 to a 1. The signal is a "new" signal that is created the first time it is referenced and cannot already exist in the design.

### LATCH ENABLE signal GETS expression 1 WHEN expr 2

Equates signal to the value of expr 1 when expr  $2^{\circ}$  is a 1. The signal is a "new" signal that is created the first time it is referenced and cannot already exist in the design.

### EQUATE ENABLE signal TO expr

Continuously gives *signal* the value of *expr*. The signal is a "new" signal that is created the first time it is referenced and cannot already exist in the design.

### SET BREAKPOINT *expr*

Installs *expr* as a breakpoint. While this breakpoint is set, the Simulator ALWAYS stops when the function changes from false to true. When the simulator stops, it prints out the function to identify which breakpoint was encountered. The Simulator assigns numbers to breakpoints to allow a breakpoint to be specified either by number or function; simple breakpoints can be called by name, and complex breakpoints can be called by number.

Named breakpoints are a special case of ENABLE signals. A user can EQUATE an ENABLE signal to the desired breakpointing expression, and thereafter reference the breakpoint by the name of the ENABLE signal as follows:

### EQUATE ENABLE name to breakpoint\_condition SET BREAKPOINT name

### **SET BREAKPOINT # number**

Activates the indicated breakpoint. While this breakpoint is set, the Simulator ALWAYS stops when the function changes from false to true. When the simulator stops, it prints out the function to identify the responsible breakpoint. Breakpoints are given numbers by the Simulator, and complex breakpoints may be re-installed by number. (Note that when simulating under CMS, the # symbol prefix must be replaced by the % symbol).

#### CLEAR BREAKPOINT name or CLEAR BREAKPOINT # number

Deactivates the breakpoint. The breakpoint no longer affects simulation but it remains in the breakpoint list marked "inactive". Only breakpoints that are a single string containing no boolean expressions may be cleared by name; all others must be cleared by number. Breakpoints you can clear by name are usually those defined using the EQUATE ENABLE command.

### LIST BREAKPOINTS

Lists all breakpoints that have been created, whether they are active or have been CLEARed. Breakpoints are marked as active (SET) or inactive (CLEARed). This command also prints the breakpoint number assigned by the Simulator.

### LIST ENABLES

Lists all of the ENABLE signals that have been defined and their definitions.

### 4.3 COMBINING BREAKPOINT COMMANDS

Groups of SAMPLE, LATCH, SET, CLEAR, and EQUATE commands may be applied to any signal, with the following results:

- EQUATEing a signal generates a combinational function only; signals generated with the EQUATE command have no state of their own. EQUATEing a signal that has already been equated supersedes the old definition.

- SAMPLEing, LATCHing, SETting or CLEARing a signal generates a function containing state information. SETs and CLEARs may be added to a signal that is SAMPLEd or LATCHed. A SAMPLE or LATCH may be added to a signal that is SET and/or CLEARed. Defining a SAMPLE, LATCH, CLEAR, or SET for a signal that already has such a definition supersedes the old definition. Only one SAMPLE or LATCH definition applies at one time. Defining a SAMPLE or LATCH definition supersedes the other definition supersedes the existing definition.

- Only one EQUATE definition or one definition from the set {SAMPLE, LATCH, SET, CLEAR} applies at a time. EQUATEing a signal that was previously defined as SAMPLEd, LATCHed, SET, or CLEARed supersedes the existing definition. SAM-PLEing, LATCHing, SETting, or CLEARing a signal that was previously EQUATEd supersedes the existing definition.

# 4.4 EXPRESSION SYNTAX

The syntax for an *expression* is based on the SCALD standard expression syntax:

```

<expression> -> <expression> OR <boolean expression> { boolean

-> <expression > XOR <boolean expression > { boolean XOR

-> < boolean expression >

<boolean expression> -> <boolean expression> AND

<relational expression > { boolean AND }

-> < relational expression >

<relational expression> -> <term> <rel OP> <term>

-> < term >

<rel OP> -> <'='>

{equal }

-> <'<>'>

{ not equal }

-> <'>='>

{ greater than or equal }

-> <'<='>

{ less than or equal }

-> <'<<'>

{ less than }

-> <'>>'>

{ greater than }

-> <signal>

<term>

-> ( <expression> )

-> NOT <term >

{ boolean NOT}

\{ \text{constant } 0 \}

-> 0

{ constant 1 }

-> 1

```

-> & <constant> { any constant, given

in current radix }