# ValidPACKAGER™ REFERENCE MANUAL

Manual Number: MN223 Rev A

10 March 1986

Valid Logic Systems, Incorporated 2820 Orchard Parkway San Jose, California 95134 (408) 945-9400 Telex 371 9004

Copyright © 1986 Valid Logic Systems, Incorporated

This document contains confidential proprietary information which is not to be disclosed to unauthorized persons without the prior written consent of an officer of Valid Logic Systems Incorporated.

ValidPACKAGER is a trademark of Valid Logic Systems, Inc. ValidCOMPILER is a trademark of Valid Logic Systems, Inc. UNIX is a trademark of AT&T Bell Laboratories

# NEW PACKAGER FEATURES

This manual describes version 7.28 of the Packager program. You may be using version 7.25. When you run the Packager, the first line of your listing file (PSTLST) will show the version of the Packager:

## Valid Logic Systems, Inc. Packager 7.25:1June85

or

## Valid Logic Systems, Inc. Packager 7.28:1June85

If you are using version 7.25 of the Packager program, then several of the features described in this manual will not be available to you. These include the following:

- The GROUP property.

- The subdirectory (-s) option of the "package" command.

- These directives:

FREE\_GROUPING HARD\_GROUPING HARD\_LOC\_SEC LIBRARY PART\_TYPE\_LENGTH PRINT\_PIN\_LIST USE\_PIN\_GROUP D OCUMENT\_ERRORS

• The following output files:

PSTPCHG (physical changes file) PSTBCHG (binding changes file)

• The subtype suffix specification for physical part tables.

3/10/86

New Packager Features

- The verbose (-v) option for feedback diagnostic messages.

- Feedback: in the 7.25 Packager, if you don't list all pins for a section, the Packager ignores that section and doesn't do feedback on it. In the 7.28 Packager, if a pin isn't listed, the Packager assumes that the pin is not connected (i.e., it is connected to the 'NC' net).

- Compact PIN\_NUMBER syntax specification (see Appendix A).

# TABLE OF CONTENTS

| Overview                              |              |

|---------------------------------------|--------------|

| How to Use This Manual                | 1-1          |

| Introduction to the Packager          | 1-1          |

|                                       |              |

| Running the Packager                  |              |

| Initial Packager Run                  | 2-1          |

| Subsequent Packager Runs              | 2-7          |

| The Packager Listing File             | 2-9          |

| Error Messages in Listings            | $\bar{2}-12$ |

| Commonly-Used Directives              | 2 - 12       |

| Interfaces to Physical Design Systems | 2-14         |

| The Subdirectory Option               | 2-14         |

|                                       | 2-11         |

| State Files                           |              |

| Using State Files                     | 3-1          |

|                                       | 01           |

| Overview of Packager Functions        |              |

| Logical to Physical Assignments       | 4-1          |

| Creating Net and Parts Lists          | 4-2          |

| Creating the PSTCHIP File             | 4-3          |

| Expansion of Structured Parts         | 4-3          |

| Removing Phantom Bodies               | 4-4          |

| Load and Net Checks                   | 4-4<br>4-5   |

| Load and Net Checks                   | 4-0          |

| User Directions From the Schematic    |              |

| Location Property                     | 5-2          |

| Section Command                       | 5-2<br>5-3   |

| Pinswap Command                       | 5-3          |

| Group Property                        | 5-4          |

|                                       | 5-4<br>5-6   |

| Location_Class Property               |              |

| Flag Bodies and Interfaces            | 5-6          |

| Suggestions for Use                   | 5-7          |

|                                       |              |

| Feedback to the Packager              | 0.1          |

| Types of Feedback                     | 6-1          |

| Common Errors to Avoid                | 6-4          |

| Running the Packager with Feedback    | 6-4          |

| Feedback File Formats                 | 6-6          |

| Physical Part Designator Transformations<br>Physical Section Transformations<br>Feedback Net List<br>Physical Net Name Transformations                                                                                                                                                                                                                                 | 6-7<br>6-7<br>6-8<br>6-9                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| Back Annotation<br>When to Back Annotate<br>How to Back Annotate<br>Design Techniques and Annotation<br>Soft and Hard Properties<br>Special Uses of Properties                                                                                                                                                                                                         | 7-1<br>7-2<br>7-3<br>7-4<br>7-5                                                         |

| Packager Functions in Detail<br>Net and Part Name Assignment<br>Size Expansion<br>Times Expansion<br>Wire-Gate and Wire-Tie Expansion<br>Net Checks<br>Output Type Check<br>Output Type Check<br>Device Loading Calculations<br>Single State Pin Drive and Loading<br>No_Load_Check Property<br>Unknown_Loading Property<br>Tables Comparing Net/Load Check Properties | 8-1<br>8-2<br>8-4<br>8-6<br>8-9<br>8-10<br>8-11<br>8-12<br>8-14<br>8-15<br>8-16<br>8-17 |

| Librarries and Physical Part Tables<br>Library Files<br>Pin_Number and Power_Pins Properties<br>Pin Swapping<br>Physical Part Tables<br>How to Use the Physical Part Tables<br>Note on Scale Factors<br>Format of the Physical Part Table<br>Modified Part Types in Pysical Part Tables                                                                                | 9-1<br>9-3<br>9-3<br>9-4<br>9-7<br>9-8<br>9-9<br>9-16                                   |

| Timesavers/Troubleshooting                                                                                                                                                                                                                                                                                                                                             | 10-1                                                                                    |

| Advanced Topics                                                                                                                                                                                                                                                                                                                                                        | 11-1                                                                                    |

| Packager Directives<br>Annotate<br>Document_Errors                                                                                                                                                                                                                                                                                                                     | $12-2 \\ 12-3$                                                                          |

| Feedback_Order   | 12-3  |

|------------------|-------|

| Filter_Property  | 12-4  |

| Free_Grouping    | 12-5  |

| Hard_Grouping    | 12-5  |

| Hard_Loc_Sec     | 12-6  |

| Include_Io_List  | 12-6  |

| Library          | 12-7  |

| Library_File     | 12-8  |

| Max_Errors       | 12-8  |

| Net_Name_Length  | 12-9  |

| Output           | 12-9  |

| Oversights       | 12-10 |

| Part_Name_Length | 12-11 |

| Part_Table_File  | 12-11 |

| Part_Type_Length | 12-12 |

| Pass_Property    | 12-12 |

| Print_Pin_List   | 12-13 |

| Report           | 12-13 |

| Suppress         | 12-14 |

| Use_Pin_Group    | 12-14 |

| Use_State_Files  | 12-15 |

| Warnings         | 12-15 |

|                  |       |

# Packager Output Files

| General Notes on Output Format          | 13 - 2  |

|-----------------------------------------|---------|

| Cross Reference Files                   | 13-3    |

| Local Part Cross Reference Overview     | 13-4    |

| Global Signal Cross Reference Overview  | 13-4    |

| Global Part Cross Reference Overview    | 13-5    |

| Path Properties and Path Elements       | 13-5    |

| Controlling Cross Reference Generation  | 13-7    |

| Local Part Cross Reference File Format  | 13-8    |

| Global Signal Cross Reference Format    | 13-11   |

| Global Part Cross Reference File Format | 13-13   |

| Logical Changes Summary                 | 13-14   |

| Binding Changes List                    | 13 - 15 |

| Physical Changes List                   | 13 - 15 |

| Reports File                            | 13 - 15 |

| The Expanded Net List                   | 13 - 16 |

| The Expanded Part List                  | 13-20   |

| Glossary                                | 14-1    |

# Packager Error Messages

| Format of Messages                                                |     |

|-------------------------------------------------------------------|-----|

| Directives Affecting Error Messages<br>Special Messages Reporting |     |

| Summary of Messages by Number                                     |     |

| Index                                                             | I-1 |

# SECTION 1 OVERVIEW

## 1.1 HOW TO USE THIS MANUAL

This manual is a reference guide for the Packager. Sections 1 through 4 contain an overview of the Packager, an introduction to running the Packager, and some basic information on specific functions and concepts necessary to understand the Packager. Sections 5 through 11 describe important Packager features and cover important concepts in greater depth and detail. Sections 12 through 15 are strictly reference material: output file formats, error messages, directives, and a glossary.

Everyone should read sections 1 through 4. Most users will also need to read portions of Sections 5 through 11. The manual has a "top-down" design; the first few sections provide a global view of the Packager and contain forward references to later sections that describe particular functions in more detail.

## **1.2 INTRODUCTION TO THE PACKAGER**

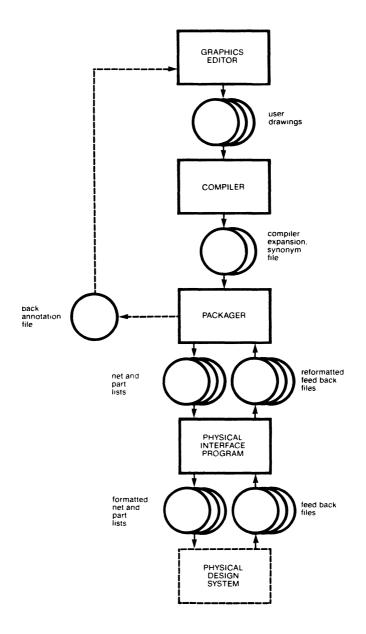

After a logical design is completed, it must be translated into a physical design. The logical design must be "packaged" into physical chips on a printed circuit board. The Packager is a bridge between the logical and physical designs, and information flows in both directions across this bridge. The Packager processes the compiled logic design and produces files for a physical design system. The Packager also accepts feedback files from a physical design system (to modify the Packager's original physical design) and produces a back annotation file that is used by the Graphics Editor to incorporate physical part numbers and physical pin numbers into the original logical design. During the packaging process, the Packager creates "state files" to maintain a consistent physical design for successive packaging runs. Figure 1 shows an overview of the Packager's relation to the Graphics Editor, the Compiler, and a physical design system.

The Packager performs the following functions:

- Logical to Physical Assignments

- Expansion of Structured Parts

- Removing Phantom Wire-OR and Wire-AND Bodies

- Checking Loading Constraints and Unconnected Signals

- Processing Feedback Files

- Creating Net and Parts Lists

- Preparing the Back Annotation File

Overview

Figure 1-1. Overview of Packager and Related Systems

3/10/86

#### Overview

## LOGICAL TO PHYSICAL ASSIGNMENTS

Each logical part, signal, and pin is given a physical name by the Packager. (These names can be changed by the user.)

## EXPANSION OF STRUCTURED PARTS

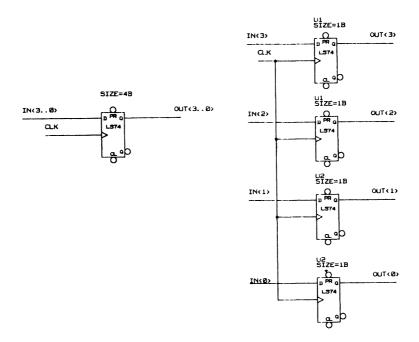

Parts with a SIZE property are expanded into the corresponding number of parts, and the vectored signals connected to the "sized" part are assigned to the expanded parts. The Packager also creates new versions of parts with TIMES properties.

# REMOVING PHANTOM WIRE-OR AND WIRE-AND BODIES

All wire-OR and wire-AND bodies in the design are replaced with explicit wire ties.

## NET AND LOAD CHECKS

The Packager checks each net to make sure that the loading specifications of the parts are not violated. The Packager also checks for unconnected signals on nets.

#### PROCESSING FEEDBACK FILES

The Packager processes feedback files from the physical design system to modify its original physical design.

## CREATING NET AND PARTS LISTS

The Packager creates a net list and part list which contain the information to be passed to a physical design system.

#### PREPARING THE BACK ANNOTATION FILE

The Packager creates a back annotation file for the Graphics Editor.

# SECTION 2 RUNNING THE PACKAGER

This section describes how to run the Packager and discusses the input and output files as well as the overall data flow. The Packager is an unusual program in that some of its output files are used as inputs to the next Packager run for the design. Thus, the initial Packager run differs from later runs.

## 2.1 INITIAL PACKAGER RUN

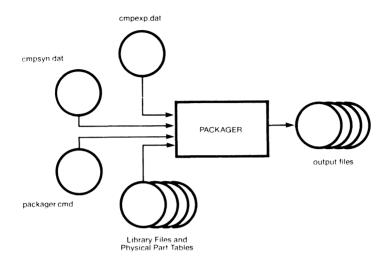

Figure 2 shows an overview of the input and output files for an initial run of the Packager. The files CMPEXP and CMPSYN are the expansion and synonym files from a Compiler run for logic. These files contain the logical design description. The file packager.cmd is a text file maintained by the user that contains directives (commands) from the user to the Packager. These commands control specific Packager functions. The library files and physical part tables contain physical information about the parts included in the logical design (e.g., pin numbers, number of sections per physical part, and electrical characteristics of the part). The Packager processes information from these input files and produces more than a dozen output files.

Figure 2-1. Overview of Initial Packager Run

Before running the Packager, you must compile your design for logic and prepare a Packager directives file. To run the Packager, enter this command after the prompt:

## package

When you enter this command, the Packager uses the current Compiler output files, the Packager directives file (packager.cmd), and the library files and physical part tables specified in the directives file. (The "package" command can also be used in the form "package [-s] [root drawing name]". This enables you to package different designs in the same directory but still maintain the design files separately. This option is discussed in more detail at the end of this section.)

While it is running, the Packager sends messages to the terminal reporting on the progress of activity. When the Packager finishes, the terminal shows the number of errors (if any) and CPU time. Here is an example of a simple

#### Packager

Packager directives file:

library\_file '/u0/lib/lsttl/lsttl.prt'; warnings on; oversights on; end.

The first three lines of the example file are directives. Each directive ends with a semicolon (;). The last line of the file is always "END." Directives allow you to specify certain choices for the Packager. For example, WARNINGS ON tells the Packager to print warning messages. Most directives are optional. If you omit them, the Packager uses a choice called default. However. preset a the LIBRARY FILE or LIBRARY directive is required to specify the library file(s) containing the physical information for the parts in your design. Some of the more commonly-used directives are discussed later in this sec-Section 12 contains a complete description of all tion. Packager directives. The directives are listed in that section in alphabetical order, with syntax and purpose fully defined.

> **NOTE:** The Packager directives file and the Compiler output files must be in your current directory when you enter the command "package". Libraries can be in a different directory, since the LIBRARY\_FILE directive includes the full path name for the library file.

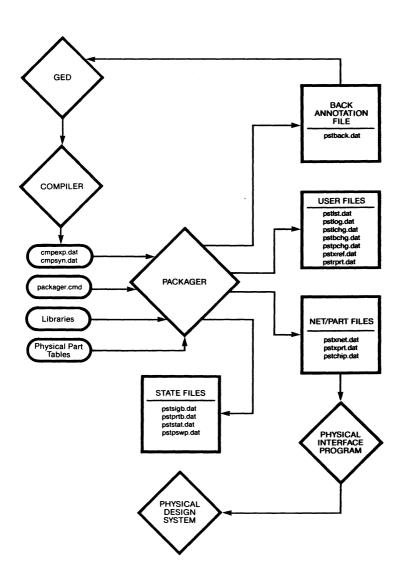

Figure 3 shows the input and output files from a first run of the Packager. All Packager output files have names beginning with the letters "pst" which stands for "post processing." You are now "post processing" your design for use with another system. This manual refers to output files by their logical name. The actual name depends on the particular operating system. The UNIX file name is the logical file name in lower case followed by the extension ".dat". For example, PSTLST becomes pstlst.dat. The output files are described below.

Figure 2-2. First Run of the Packager

#### Packager

Net/Part Files: to be processed by interface programs before going to physical layout.

- Expanded Net List (PSTXNET). Lists each net on your design (alphabetically by signal name) and the nodes connected to it (by U-number).

- Expanded Parts List (PSTXPRT). Lists each physical part in the design in order (by Unumber) and tells what logical part (by PATH property) is assigned to each section.

- New CHIPS File (PSTCHIP). Lists the physical information from the library chips files and physical part tables for each different library part that your design utilizes. This information is excerpted from the library chips files. Since this file is much shorter than the library chips files, it is passed on to subsequent programs for them to use.

User Files: documentation and statistics for the Packager run, for user's reference.

- Listing File (PSTLST). Provides process information and error messages for the user.

- Log File (PSTLOG). Provides process information and other data for use by Valid personnel.

- Cross References (PSTXREF). Lists, for cross reference purposes, signal names and the net names to which they correspond, and logical part names (library part names and PATH properties) and the physical assignment (U-number, section, and pin numbers) to which they correspond.

- Logical Changes Summary (PSTLCHG). Lists the logical parts that were added or deleted from the design since the last run of the Packager.

- Physical Changes Summary (PSTPCHG). Lists all physical parts that were added to the design or deleted from the design during this run.

- Binding Changes Summary (PSTBCHG). Lists all bindings that were added to the design or deleted from the design during this run. (A binding is a mapping of a logical part to its allocated physical section.)

- Reports File (PSTRPRT). Lists the remaining spare sections (if any), and how many packages of each physical part your packaged design requires.

Back Annotation File: for back annotation through GED.

• Back Annotation File (PSTBACK). Lists the information in the expanded net list and the expanded parts list ordered by body name and PATH property so that GED can write in physical part designators (e.g., U-numbers) and pin numbers for each body on the drawing.

Output Files for Use in Later Packager Runs (State Files)

- Logical Signal Name to Physical Net Name Binding (PSTSIGB) and Logical to Physical Part Designator Binding (PSTPRTB). These two files contain the information in the expanded net list and the expanded parts list, in a somewhat different format.

- State File (PSTSTAT). This brief file time-stamps the current Packager run and identifies the compilation run used for input.

- Pin Swap File (PSTPSWP). This file lists the pins swapped during the current Packager run. If no pins have been swapped, the file includes only a header and "end."

Section 13 contains detailed descriptions of Packager output files and includes a complete discussion of file format and syntax.

The back annotation file is used by the Graphics Editor (GED) to annotate the schematic with the physical part designators (e.g., U-numbers) and pin numbers. See Section 7 for a detailed discussion of back annotation.

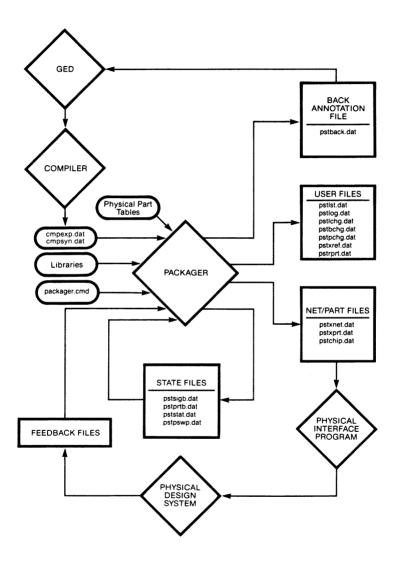

## 2.2 SUBSEQUENT PACKAGER RUNS

Figure 4 shows the overall data flow for subsequent Packager runs. Notice how the state files from the previous Packager run become input for the next run. The state files ensure consistency in the Packager's physical assignments from one run to the next. Section 3 discusses state files. The feedback files can come from the physical design system or can be created manually. Feedback files typically contain changes in U-numbers and pin assignments to optimize the design and shorten wire lengths. You can also change net names and swap sections. The Packager then incorporates these changes. See Section 6 for a detailed discussion of feedback files.

Figure 2-3. Subsequent Packager Runs

## 2.3 THE PACKAGER LISTING FILE

An example of a Packager listing file is shown in Figures 5A and 5B. The listing file is contained in PSTLST. The listing consists of several parts. The paragraph numbers below correspond to the "call out" numbers on Figure 5.

- 1. The first part of the listing file is the header. It tells you which version of the Packager you used, and the time and date of the Packager run.

- 2. The next part of the listing file is the directives list. It tells you every directive that was in effect for this run. This includes all the directives you entered in PACKAGER.CMD as well as the default settings for the directives you omitted.

- 3. The next part of the listing gives the drawing name and the date and time it was compiled. This information is taken from the Compiler expansion file.

- 4. The next several items on the listing file are process statements. As the Packager does its work, it reports at each stage. Errors are noted as they are found.

- 5. The listing file ends with a recap of the number of errors, oversights, and warnings found by the Packager, and the elapsed time and CPU time for this run.

Packager

```

Valid Logic Systems, Inc. Packager 7.25h:1June85

1

Packager run on Fri Jun 7 16:43:51 1985 at 16:43:51.00

* Starting to read directives

----- Directives ------

WARNINGS ON;

USE_PIN_GROUP ON;

SUPPRESS <none>;

OVERSIGHTS ON;

DOCUMENT_ERRORS ON;

OUTPUT EXPANDEDNETLIST

EXPANDEDPARTLIST.

LOGICALCHANGES.

LOCALPARTXREF .

GLOBALSIGNALXREF .

GLOBALPARTXREF .

BACKANNOTATION;

LIBRARY_FILE '/ug/lib/tutorial/tutorial.prt';

INCLUDE_IO_LIST OFF;

REPORT SPARES,

2

PARTSUMMARY:

ANNOTATE BODY,

PIN;

USE_STATE_FILES ON;

PART_NAME_LENGTH 16;

NET_NAME_LENGTH 24;

UNNAMED_CHANGES ON;

* Starting to read compiler output

----- Expansion file information ------

ROOT_DRAWING='SUBTRACTOR':

TIME=' COMPILATION ON FRI JUN 7 16:38:55 1985 ';

3

* Starting to read library description

*********************************

* Starting to read state file *

4

* Starting assignment of SIZE replicated parts *

**********************************

* Starting TIMES replication

******************************

```

Figure 2-4A. Packager Listing File

\* Starting to thread nets \* \* Starting to assign physical parts \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* Starting to evaluate nets \* \* Starting to check nodes \* ------Starting to assign physical part names \* Starting to assign physical net names \* Starting to assign physical group names \* \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* Starting to perform pin swaps \* Starting state files generation \* \*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\* \* Starting output list generation \* Packager run on Fri Jun 7 16:43:51 1985 at 16:43:51.88 Design name: SUBTRACTOR Design compilation: COMPILATION ON FRI JUN 7 16:38:55 1985 Library creation: COMPILATION ON THU JUN 6 11:87:86 1985 No errors detected 9 oversights detected 4 warnings detected Start time = 16:43:51.89 Ending time = 16:44:38.89 Elapsed time = 89:89:47.89 CPU time = 89:89:42.29

Figure 2-4B. Packager Listing File

3/10/86

5

## 2.4 ERROR MESSAGES IN LISTINGS

Packager error messages are also included in the listing file. Errors, oversights, and warnings are all listed together. An error is a serious problem which must be fixed before you can continue. An oversight is a less severe problem which should be fixed, but which does not halt progress. A warning is a minor problem which you may or may not choose to fix. Here is an example of a warning message:

## #2 WARNING(132): No input on net

In this example, "#2 WARNING" means that this is the second warning message from the Packager. Errors, oversights, and warnings are numbered separately. (For example, the third error would appear as "#3 ERROR".) The number "132" is the number of the warning message. The Packager has 229 different messages. The text "No input on net'' is the warning message itself. See Section 15 for more detailed information on error messages. It contains all messages in numerical order with a descriptive paragraph for each. These descriptions are also printed in the listing file as short paragraphs after the list of errors, one paragraph for each type of error, oversight, or warning. (To these paragraphs. directive omit use the DOCUMENT ERRORS OFF.)

## 2.5 COMMONLY-USED DIRECTIVES

The following directives are used frequently:

- FEEDBACK\_ORDER specifies the feedback files and the order in which the Packager will process them. This directive causes feedback to occur.

- LIBRARY\_FILE specifies the libraries containing physical information for parts in the design. This directive or the LIBRARY directive is always required.

- LIBRARY same function as LIBRARY\_FILE, but uses the short library name instead of the full path

name.

- OUTPUT this suppresses and enables selected output files.

- OVERSIGHTS if set to OFF, this suppresses all oversight messages in the listing.

- PART\_TABLE\_FILE specifies the files containing physical part tables to be referenced by the Packager.

- SUPPRESS this suppresses one or more warning or oversight messages.

- USE\_STATE\_FILES controls the generation of state files.

- WARNINGS if set to OFF, this suppresses all warning messages in the listing.

See Section 12 for detailed descriptions of the format and functions of all Packager directives.

Most Packager directives have default values. Here is the current set of default directives:

USE\_PIN\_GROUP ON; WARNINGS ON: SUPPRESS <none>; OVERSIGHTS ON: **DOCUMENT ERRORS ON:** OUTPUT EXPANDED NETLIST, EXPANDEDPARTLIST, LOGICALCHANGES, PHYSICALCHANGES, BINDINGCHANGES, LOCALPARTXREF, GLOBALSIGNALXREF, GLOBALPARTXREF, **BACKANNOTATION:** INCLUDE\_IO\_LIST OFF; REPORT SPARES, PARTSUMMARY;

ANNOTATE BODY, PIN; USE\_STATE\_FILES ON; PART\_NAME\_LENGTH 16; NET\_NAME\_LENGTH 24; UNNAMED\_CHANGES ON;

## 2.6 INTERFACES TO PHYSICAL DESIGN SYSTEMS

The following output from the Packager is sent to a physical design system:

- Expanded Net List (PSTXNET) lists each net and its attached nodes

- Expanded Part List (PSTXPRT) lists each physical part and shows the logical part assigned to each section.

- CHIPS File (PSTCHIP) physical characteristics of the parts in the design, extracted from the libraries and physical part tables.

These files must be reformatted by a physical interface program before they can be processed by a physical design system. Likewise, the output from the physical design system must be reformatted for feedback to the Packager. Section 6 discusses the feedback process and covers the format of feedback files.

## 2.7 THE SUBDIRECTORY OPTION

The "package" command which runs the Packager has a subdirectory option which allows you to package different designs in the same directory and keep separate sets of output files for each design. The subdirectory option can also be used to save the current state of the design by keeping a copy of the Compiler expansion file and a copy of the current Packager output files in a subdirectory. In this way, the subdirectory can provide a backup for a Packager run. The format of the "package" command with the subdirectory option is as follows: Packager

# package [-s] [root drawing name]

The option "-s" tells the Packager to save a copy of the output files from this run in a subdirectory. The name of the subdirectory is pack*i*, where *i* is an integer between 1 and 9. When you run the Packager with the "-s" option, it searches through all subdirectories for a Compiler Expansion file with the same *root drawing name* specified in the "package" command. If none is found, a new subdirectory is created. If the *root drawing name* was not specified, the Packager uses the name in the Compiler Expansion file in the directory. Here are some examples:

If you use the command "package -s" without the *root* drawing name, the Packager saves a copy of the Compiler Expansion file and all Packager output files in a subdirectory. The Packager first searches for an existing subdirectory containing a root drawing name which matches that in the Compiler Expansion file in the current directory. If there is none, then the Packager creates one to store the files.

If you use the command "package -s DESIGN1", the Packager searches for an existing subdirectory with a Compiler Expansion file that contains the root drawing DESIGN1. Note that if the root drawing name contains blanks, you must enclose it in double quotes.

The subdirectory "snapshot" of the design is overwritten every time the design is repackaged with the "-s" option. If you want to save several different copies of the same design, you must rename the drawing in GED so that the root drawing name is different from the previous Packager run.

# SECTION 3 STATE FILES

A small change in the logical design should cause only a small change in the physical design. This makes it possible to modify a design while physical design is in progress without redoing the physical layout. State files are used to keep Packager assignments consistent from one run to the next.

State files provide the Packager with the assignments from the previous run. Those assignments which are still legal in the current run are performed. Any new logical parts, nets, or pins are then assigned. (An assignment is legal if the parts, nets, or pins it references still exist in the logical design.)

The Packager generates and reads the part bindings (PSTPRTB), signal bindings (PSTSIGB), pin swap (PSTPSWP), and design information (PSTSTAT) state files. These files record the logical to physical part allocation, logical to physical net name assignment, logical to physical pin assignment, the pin swaps, and global design information for the last run of the Packager.

If the use of states files is enabled and these files exist when the Packager is run, they are used to guide logical to physical part allocation and logical to physical net name assignment, and logical to physical pin assignment. The Packager reports whether the state files are being used in the listing file (PSTLST) under the sections "Assign Physical Parts", "Assign Physical Net Names", and "Perform Pin Swaps".

#### 3.1 USING STATE FILES

When state files are enabled, the Packager reads them if they exist, and generates them after the logical to physical assignments have been completed. Since the state files for any design are named PSTPRTB, PSTSIGB, PSTPSWP,

3/10/86

and PSTSTAT, it is necessary to keep each design in a separate directory, or for IBM mainframe systems, a separate disk. This ensures that a state file for one design will not be applied to a different design.

If you want to disable the use and generation of state files, you must use the Packager directive USE\_STATE\_FILES OFF, since the default is ON. In general, you should use state files to preserve the consistency of the design from one run to the next.

Since the assignments specified in the state files are based on the history of the design, the component packing which they specify may not be as tight or as regular as that the Packager might generate from scratch. Deleting the odd bits of a bus might, for example, result in a set of buffers where every other section is used. If common pin usage allows, new logical parts will be allocated to the unused sections, but this may result in a physical design which is difficult to wire.

For these reasons, you may choose to delete the state files occasionally, to allow the Packager to repack the design in the most compact form. Deleting the state files WILL GREATLY CHANGE THE ASSIGNMENTS for a design, and may result in slightly different loading on nets connecting to common pins. Obviously, the state files should NEVER be deleted for designs which have already been built. Rather than deleting the state files, they should be SAVED so that they may be used if the new assignments are for some reason undesirable.

The state files should never be edited in order to change the physical design. Only the feedback files should be used to alter the design. Refer to Section 6 for more information on feedback.

# SECTION 4 OVERVIEW OF PACKAGER FUNCTIONS

This section contains a brief description of the following Packager functions:

- Logical to Physical Assignments

- Creating Net and Parts Lists

- Creating PSTCHIP File for Physical Design Systems

- Expansion of Structured Parts

- Removing Phantom Wire-OR and Wire-AND Bodies

- Load and Net Checks

These functions are covered here to provide a better overall understanding of the Packager. They are discussed in more depth later in the chapter.

#### 4.1 LOGICAL TO PHYSICAL ASSIGNMENTS

The Packager transfers a design from the logical realm to the physical realm. During this transfer, the Packager makes the following assignments:

| FROM LOGIC                       | CAL DESIGN TO I                    | PHYSICAL DESIGN                    |

|----------------------------------|------------------------------------|------------------------------------|

| logical parts<br>logical signals | are assigned to<br>are assigned to | physical sections<br>physical nets |

| logical nodes                    | become                             | physical pins                      |

The Packager assigns the logical parts to physical chips ("packages") which will be placed on a printed circuit board. A logical part is a body on the drawing created through the Graphics Editor. The Packager assigns logical parts to a section of a physical part. Physical parts are named by physical part designators (e.g., U1, U2, U3). Overview of Packager Functions

Note that logical part names and physical part designators have no correspondence. That is, there is no connection between the two names.

Physical net names are created from an abbreviation of the logical signal name for the net. (See Section 8 for a detailed description of the rules for abbreviating logical signal names.) If there are several signal names on one net, the Compiler picks one for the Packager to use.

The Packager assigns logical nodes to physical pins on a chip (e.g., A0 becomes pin 5, CE becomes pin 1). The Packager uses the library model of the logical part to determine the pin numbers. See Section 9 for more information on library models and pin number assignments.

## 4.2 CREATING NET AND PARTS LISTS

The Packager creates expanded net and parts lists which contain all the information about the physical design. These lists are organized by physical information, and they can be sent to a physical design system. (They are usually reformatted by a physical interface program before going to the physical design system.) The user cross reference file (PSTXREF) contains the same information in a more accessible form.

The Expanded Net List is ordered by physical net name and contains the properties for each net and the logical to physical binding of nets and nodes as well as node properties. The Expanded Part List is ordered by physical part name and contains the properties and logical to physical bindings of each part.

Section 13 has sample expanded net and parts listings and detailed explanations of the file format. It also contains a detailed description of the user cross reference file (PSTXREF).

## 4.3 CREATING THE PSTCHIP FILE

The Packager uses information from libraries and physical part tables to determine the physical characteristics of the various parts in a design. The Packager extracts information from these files for each part in the design and places it in the output file PSTCHIP. This output file can then be used by physical design systems.

Library files contain information attached to the body. This information includes the pin numbers for the part, the input and output loads for each pin, and the family of the part.

Physical part tables provide a way to create new part types from a basic part type. For example, you can create many different types of resistors and capacitors from a single basic resistor or capacitor. The various resistor types may have different resistance values, power dissipation, cost, reliability, etc. All of these characteristics can be specified in a physical part table. There is only one library definition for the part, and therefore only one copy of the models. The Packager uses the properties attached to the part to differentiate it from other instances of the same part.

Physical part tables thus allow you to attach new body properties to a part type without having to recreate or modify the library files containing the part type definitions. An important use of this capability is the addition of new properties to the libraries for certain interfaces to physical design systems. These properties describe to the interface the type and shape of each component.

## 4.4 EXPANSION OF STRUCTURED PARTS

The Packager expands any structured parts present in the logical design. A logical part with the SIZE property is expanded into the corresponding number of parts, and the vectored signals connected to the "sized" part are assigned to the expanded parts. The Packager also creates new versions of parts with TIMES properties.

Overview of Packager Functions

The SIZE property is used to generate a multiple-bit component and to connect it to a group of signals. The TIMES property is used to replicate an output that must drive many inputs. See Section 8 for more information on SIZE and TIMES.

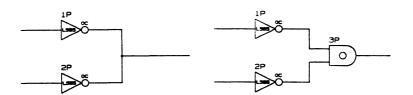

## 4.5 REMOVING PHANTOM BODIES

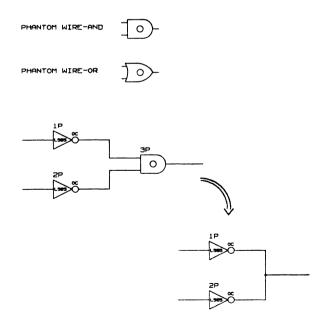

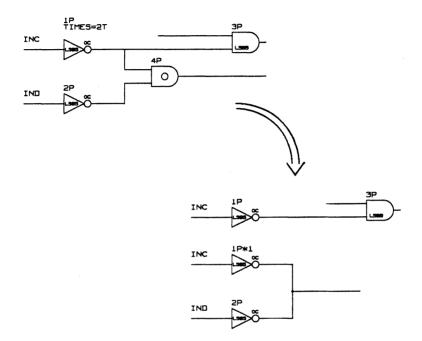

Figure 4-1 shows an example of "phantom" wire-OR and wire-AND bodies. These bodies are simply representations that you may use in your design to document the logical operation that is performed at a wire-tie. Phantom bodies may be accessed with the Graphics Editor by entering the command "library phantom." Of course, these are not "real" gates, and the Packager replaces them with wire-ties (also called "wire-gates"). For more information on this topic, see Section 8.

Figure 4-1. Wire-OR and Wire-AND Phantom Bodies

Packager

## 4.6 LOAD AND NET CHECKS

A net is a single bit signal and the nodes that are connected to it. The Packager performs the following net error checks:

- Output-Type Check: make sure that output pins connected together have the proper technology (e.g., open collector, open emitter, tri-state).

- I/O Check: make sure every net is connected to at least one input pin and at least one output pin.

The Packager calculates the loading for each net for both logic states ("0 state" and "1 state"). The Packager performs the following load checks:

- For each logic state, the input and output loads must have opposite signs.

- For each logic state, the absolute value of the smallest output load must be greater than or equal to the absolute value of the total input loads on that net.

See Section 8 for a complete description of the Packager's net and load checks. This section also discusses properties which suppress load checks in certain cases (e.g., unknown loading).

# SECTION 5 USER DIRECTIONS FROM THE SCHEMATIC

There are often cases where you need to direct the assignments made by the Packager. For example, you may want to assign four gates performing a particular function to the same package, and there is no guarantee that the Packager will make such an assignent. To solve this type of problem, there are several properties and commands you can use on your schematic which affect the Packager's assignment scheme. These include the following:

- LOCATION Property

- SECTION Command

- GROUP Property

- LOCATION\_CLASS Property

- PINSWAP Command

- FLAG Bodies and Interfaces

This section discusses each of the above properties and commands in the order listed above. This is followed by a paragraph containing suggestions for using these properties most effectively. You can use the above properties and commands on your logical design in the Graphics Editor. There are several other properties which are used at the "body" level when new parts are added to a library (e.g., PIN\_NUMBER, PIN\_GROUP). See Section 9 for more information on these properties and how they affect the Packager. The Graphics Editor reference chapter contains detailed instructions on the use of these commands and properties in GED.

The following properties do not affect the Packager assignment scheme but do affect load and net checks or physical part designators:

3/10/86

- UNKNOWN\_LOADING indicates that device loading is not known

- NO\_LOAD\_CHECK suppresses device loading calculations

- NO\_IO\_CHECK suppresses input and output net checks

- ALLOW\_CONNECT permits an output pin to be connected to a net regardless of other outputs on the net

- PHYS\_DES\_PREFIX specifies the prefix to use for the physical part designator. This can be defined in the library to set the default prefix for that part. This property does not affect the physical part designator if the part has already been named in a previous Packager run and if the current Packager run is using State files. If the part has already been named and you must use State files, then use the LOCA-TION property to change the physical part designator.

## 5.1 LOCATION PROPERTY

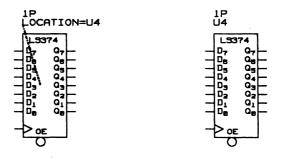

Use this property to assign a particular physical part name to a logical gate on a design. The LOCATION property always takes precedence over a physical part name assigned by the Packager. If you assign the same name to several gates, this has the effect of grouping them together; however, grouping is NOT the main purpose of this property. Use the GROUP property if you just want to group parts and don't have a particular physical part name to use. Figure 7 demonstrates the use of the LOCATION property. Note that it is an error to assign the same LOCATION name to more gates than will fit in the same physical part.

The LOCATION property can be attached only to physical part bodies. LOCATION properties attached to hierarchical drawings are errors and are ignored. The LOCATION property is not inherited as a body property.

# Figure 5-1. Use of the LOCATION Property

# 5.2 SECTION COMMAND

This command assigns a logical gate to a particular section within a physical part. The SECTION command does not specify the particular physical part; it simply assigns the gate to a particular section within a part of a given type. You can use the LOCATION property and SECTION command together.

Currently, the only parts that can be assigned to a particular section must have a SIZE of 1 or have the property HAS\_FIXED\_SIZE.

## 5.3 PINSWAP COMMAND

A swappable group of pins are those pins which are logically equivalent and belong to the same section. This means that if two nets are swapped between two pins that are in a swappable group, the logical function of the circuit is not altered. The PINSWAP command allows you to perform this operation on sectioned bodies. User Directions from Schematic

A common example of this occurs for the inputs of a NAND gate such as a 74LS00. The two input pins are physically equivalent in terms of loading and propagation delay from input to output. Thus, if the nets to the input pins are swapped, the behavior of the circuit is unchanged.

A set of pins on a given part that are swappable must have the same value for the PIN\_GROUP property attached to them. Any pin without the PIN\_GROUP property is not swappable with other pins. The value of the PIN\_GROUP property is not important, but all pins of a swappable group must have the identical value. If you want to swap pins which do not have the PIN\_GROUP property, use the directive PIN\_GROUP OFF to permit this.

The Packager and the section and pin assignment program used by the Graphics Editor recognize the PIN\_GROUP property on pins of parts in the CHIPS files. The property is used to assign the logical pins to pin equivalent and swappable groups so that the Packager can perform legal pin swaps.

## 5.4 GROUP PROPERTY

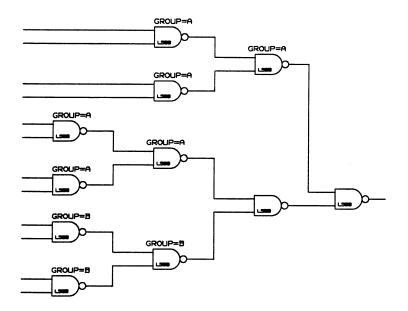

This property allows you to group logical parts together into the same set of physical packages. Logical parts with different GROUP properties (or no GROUP property) are placed in different physical packages. For example, in Figure 8 the NAND gates with GROUP = A will all be placed in the same set of physical packages, say U1 and U2, those gates with GROUP = B will be placed in U3, and those gates with no GROUP property will be placed in U4. Grouping allows you to force physical allocation yet not be concerned with specific physical part designators (e.g., Unumbers). The GROUP property applies to the entire design.

When using the GROUP property, you do not need to know the name of the physical package, and you also do not need to keep track of the number of gates in a group. If there are more gates in a group than will fit on a single part, the surplus gates automatically spill over to another part of the same type.

#### Packager

If you want to mix grouped parts with parts which are not grouped, use the directive FREE\_GROUPING ON. Otherwise, use the directive FREE\_GROUPING OFF (the default is ON). This ensures a tight placement, yet still keeps distinct groups on separate parts. For example, in Figure 5-2 FREE\_GROUPING ON would place the NAND gates with no GROUP property into either U2 or U3.

Figure 5-2. Use of the GROUP Property

Note that you can use LOCATION, GROUP, and SEC-TION on the same logical part, but you should be very careful in your assignments. For example, you cannot assign the same LOCATION to parts in different groups. However, parts in the same group can be in different physical packages. Note that you cannot use both GROUP and LOCATION\_CLASS in the same design. User Directions from Schematic

If the State files are used and some members of a group are deleted after their initial assignment, on subsequent runs the Packager will assign the remaining members of the group according to their previous assignments as recorded in the State files.

# 5.5 LOCATION\_CLASS PROPERTY

This property is similar to GROUP. The difference is that logical parts without the LOCATION\_CLASS property are always used to fill physical packages that contain parts with a LOCATION\_CLASS property. This capability is now replaced by using the GROUP property and the directive FREE\_GROUPING ON. Note that LOCATION\_CLASS works on a page of the design, whereas GROUP applies across the entire design. You cannot use both GROUP and LOCATION\_CLASS in the same design.

# 5.6 FLAG BODIES AND INTERFACES

Interfaces between a circuit and its external components must be defined in some manner. In board level designs this is normally done by implicitly defining interface signals through connectors spread throughout the design. Many gate array design systems, however, treat interface signals differently from internal signals. Often they must be declared in separate parts of the net list and must have extra information attached. For this reason, the Packager must be able to distinguish interface signals and treat them accordingly.

The Packager supports the use of FLAG bodies in the drawings to define the connection of interface signals in a root drawing to some external component such as a gate array chip carrier. To define a signal as an interface signal, attach a FLAG body to the signal. When the INCLUDE\_IO\_LIST ON directive is specified, the Packager will attach the IO\_NET property to the interface signals with the value INPUT, OUTPUT, or BID IRECTIONAL, as defined by the FLAG body. These properties are then output in the Expanded Net List.

Packager

# 5.7 SUGGESTIONS FOR USE

Here are some suggestions for effective ways to use these commands and properties:

- 1. Before the first Packager run, use the GROUP property to group related parts. If you are certain of the names for particular parts, use the LOCATION property. Likewise, if you are sure of the placement of certain sections within parts, use the SECTION command. Otherwise, don't use LOCATION and SEC-TION.

- 2.If you want to change your LOCATION or SECTION assignments during a feedback run. use the directive HARD LOC SEC OFF. Then be sure to back annotate and recompile the design to keep everything synchronized. Likewise, to move a section from one group's physical part to another group's physical part during feedback. use the directive HARD GROUP OFF and back annotate. Be sure to recompile before repackaging the design. Be very careful when you use these directives because they leave all LOCATION, SECTION, or GROUP assignments open to change. Inadvertent feedback errors can be very damaging in these circumstances. Also, note that if you change a location or section assignment in this way, the LOCATION and SEC properties are removed from the affected logical parts, while GROUP properties are changed according to the new assignments.

# SECTION 6 FEEDBACK TO THE PACKAGER

The physical design generated by the Packager may not be optimal for layout. The physical design system may rearrange parts, swap equivalent sections within parts, and swap equivalent pins on a section. Without feedback and back annotation, these changes will not appear on the schematic. Also, if there are further modifications to the logical design, the Packager and the physical design system will be "out of synch."

Feedback files inform the Packager of physical design changes. In this case, the files are usually generated automatically by the physical design system. Sometimes you may want to make manual changes to the Packager's physical design through feedback files. For example, you may want to make a small change without going through GED and recompiling. If you do this, remember that you must keep the Packager listings and physical design system files synchronized. It is also a good idea to back annotate the physical changes.

This section discusses the following topics:

Types of Feedback Warnings Running the Packager with Feedback Feedback File Formats

#### **6.1 TYPES OF FEEDBACK**

There are four types of changes that can be made through feedback files:

1. Physical part name changes

When a design is laid out, the physical part designators are often changed to include

3/10/86

position information. A typical scheme is to give a part a name of the form *letter number* where *letter* and *number* represent coordinates in two dimensions on a board. For example, G13 could represent row G, column 13.

2. Physical section reallocation

To simplify wiring, it is often desirable to group together those parts that connect to each other. Since the sections in a part may connect to different groups of parts, it is sometimes necessary to move a section from one part to another part of the same type. If all sections of the destination part are in use, then it is necessary to move one of them somewhere else. This process is often done by swapping two sections between different parts of the same type. Sections are sometimes reassigned within a single part to improve wiring.

3. Physical pin reallocation within a section

To simplify wiring even more, equivalent input pins of a section may be reassigned or swapped. This is frequently done to parts having many equivalent inputs.

4. Physical net name changes

Changing physical net names does not affect the layout or wiring of a design, but users may wish to rename nets for documentation or standardization reasons.

Note that you cannot change part types through feedback. You must use the Graphics Editor (GED) to change the part type on the logical design and then recompile and repackage. For example, you cannot swap a 74LS00 for a 54LS00 or 74LS32 through feedback; this change must be made on the logical design. If the directive HARD\_LOC\_SEC is set to OFF, then you can change section and location assignments through feedback files even if the assignments were attached as properties in the Graphics Editor. Also, if HARD\_GROUPING is OFF, you can reassign sections without regard to their groups. However, be sure to back annotate to keep the logical design in GED synchronized with the Packager's physical design. You must also recompile the design before running the Packager again.

The Packager currently can process four types of feedback files. You have the freedom to use any or all of the files as the situation requires. Only these files should be used to change the physical design. You should never edit the state files. The feedback files are as follows:

PSTPRTX - Physical part designator transformations file

Use this file to rename a physical part. The file contains a list of old physical part designator and new physical part designator pairs.

PSTSECX - Physical section transformations file

Use this file to reassign a logical part from an old physical section to a new physical section. The file contains a list of old-physical-section to new-physical-section pairs.

**PSTNETX - Physical net name transformations file**

Use this file to change physical net names. The file contains a list of old physical net name and new physical net name pairs.

PSTFNET - Feedback net list

Use this file for physical part designator changes, physical section swapping, and pin swapping. You cannot change physical net names with this file. The Feedback Net List file is frequently used by physical design systems to make several types of changes at one time. If you are generating feedback files manually, use the Feedback Net List file only if you are swapping pins. Otherwise, use the other feedback files, since they have simpler formats and are easier to use.

# 6.2 COMMON ERRORS TO AVOID

1. Never recompile a design between the time it was packaged for a physical design system and the time you use feedback from that system. The Packager uses the Compiler expansion and synonym files, the Library files, and State files during feedback processing. If any of these have changed since the previous Packager run, this will generate errors. You should save the following files for any design that is sent to a physical design system:

> Compiler output files Library files Physical part tables Packager state files

- 2. Never add or delete a part in the physical design system. Also, never change a net name. Many physical design systems are capable of making these changes, but the function of the design must be controlled from the Graphics Editor.

- 3. The directive NET\_NAME\_LENGTH should not be changed from the previous Packager run to the feedback run. This ensures that net names remain the same.

## 6.3 RUNNING THE PACKAGER WITH FEEDBACK

Feedback requires the state files from the previous Packager run. Be sure to include the directive USE STATE\_FILES ON in the directives file when you plan to do feedback on the next Packager run. This directive is also required for the feedback run.

The FEEDBACK\_ORDER directive specifies the type of feedback files to be used and the order in which the Packager will process them. When you include this directive in the directives file, you are telling the Packager to perform feedback. The format of this directive is as follows:

**feedback\_order** [-v] *filetype* [,*filetype*] ... ;

where *filetype* can be:

| part_trans | Physical part designator transformations |

|------------|------------------------------------------|

|            | file (pstprtx) - to change part names    |

- section\_trans Physical section reallocation file (pstsecx) - to change part names and section connections

- **feedback\_netlist** Feedback net list (pstfnet) to change pin connections, section connections, and part names

- **net\_trans** Physical net name transformations file (pstnetx) to change net names

For example,

FEEDBACK\_ORDER NET\_TRANS, FEEDBACK\_NETLIST;

specifies that physical net name feedback occurs first, followed by feedback net list changes.

The "-v" (verbose) option generates additional error information for certain errors found during feedback processing. For example, error #149 "Match not found for feedback section" generates a list of the closest partial matches for the entry. Normally, only the first three partial matches are Feedback to the Packager

listed. The "-v" option outputs all partial matches in the listing file (pstlst).

You should be careful to list the feedback files in the correct order. For example, if you refer to new net names in the Feedback Net List file, you should list NET\_TRANS before FEEDBACK\_NETLIST. In general, do part name changes first, section reallocations second, and pin connection changes third.

# 6.4 FEEDBACK FILE FORMATS

This section describes the formats of the four feedback files. These are text files that begin with a header and terminate with the marker "END.". The header lines identify the file and the name of the design. The form of the header lines is

FILE\_TYPE = file type ;

ROOT\_DRAWING = 'drawing name';

where *file type* specifies the file's type and '*drawing name*' (enclosed in single quotes) is the name of the root drawing of the expansion file. For example, a header for the Physical Part Designator Transformations file for the drawing SAMPLE would appear as:

FILE\_TYPE = PART\_TRANS; ROOT\_DRAWING = 'SAMPLE';

Comments may be placed in the files if enclosed in braces ({ }). A comment may appear anywhere a space may appear. Comments may cross line boundaries but cannot be nested.

If an item is too long to fit on a line (80 characters), it must be broken into more than one line. A tilde  $\binom{1}{2}$  is used as a continuation character to indicate that the current item is continued on the next line. A line break can appear between any two characters in the file. A tilde, however, is only significant if it occurs at the end of the line.

## PHYSICAL PART DESIGNATOR TRANSFORMATIONS (PSTPRTX)

Use this file to rename physical parts. The physical part designator identifies a particular occurrence of a physical part. The file type is PART\_TRANS, and it consists of a list of transformations in the form

## 'old physical part designator' 'new physical part designator'

where old physical part designator is the physical part designator assigned by the Packager during its last run and new physical part designator is the new physical part designator to be assigned. For instance, the physical part designator U31 can be changed to U32 as follows:

FILE\_TYPE = PART\_TRANS; ROOT\_DRAWING = 'SAMPLE'; 'U31' 'U32' END.

# PHYSICAL SECTION TRANSFORMATIONS (PSTSECX)

No layout knowledge is used during the initial Packager section assignment. When more reasonable section assignments are known, they can be given to the Packager which will use that information to reassign sections. The Physical Section Transformations file is used to specify section changes; its file type is SECTION\_TRANS.

The file contains a list of old physical pin designators (as assigned by the Packager during its last run) and new physical pin designators. A physical pin designator consists of a physical part designator and a UNIQUE pin number of the section (not a common pin). The Packager reassigns the sections as specified in this file.

Logical parts with the LOCATION and/or SEC properties cannot be reassigned unless you use the directive HARD\_LOC\_SEC OFF. This is also true for GROUPed sections unless you use the directive HARD\_GROUPING OFF. If you use these directives to make such changes, you

3/10/86

Feedback to the Packager

must back annotate the design so that the changes will be reflected on the schematic. Also, you must then recompile the design before running the Packager again. The only other way to change section assignments assigned through a property in the logical design is to change the logical design through GED.

The file consists of a list of transformations in the form

'old part name' old pin number 'new part name' new pin number

where old part name and old pin number specify the current section assignment, and new part name and new pin number specify the new section assignment. For example, given a 74LS00 (quad NAND gate), a swap of the first two sections on the part U31 might appear as follows:

FILE\_TYPE = SECTION\_TRANS; ROOT\_DRAWING = 'SAMPLE'; 'U31' 1 'U31' 4 'U31' 4 'U31' 1 END.

#### FEEDBACK NET LIST (PSTFNET)

You can use this feedback file to swap pins, reassign sections, and rename physical parts. Ycu CANNOT change net names or physical part types with this feedback file. If you are generating feedback files manually, use the Feedback Net List file only if you are swapping pins. Otherwise, use the other feedback files since they have simpler formats and are easier to use.

The file type is FEEDBACK\_NETLIST, and it consists of a list of nodes in the form

'physical part designator' 'physical part type' pin number 'physical net name';

where *physical part designator* is the new physical part designator, *physical part type* is the part type of the physical part, *pin number* is the new pin number of the node, and *physical net name* is the name assigned by the Packager to the net

Packager

where the node is connected.

The file MUST be sorted by physical part designator so that all the pins of a physical part appear together. The ordering of the pins on the part does not matter. An example of this file might appear as follows:

```

FILE_TYPE = FEED BACK_NETLIST;

ROOT_D RAWING = 'SAMPLE';

'U1' 'LS08' 1 'A0';

'U1' 'LS08' 2 'B0';

'U1' 'LS08' 3 'C0';

'U1' 'LS08' 4 'A1';

'U1' 'LS08' 5 'B1';

'U1' 'LS08' 6 'C1';

'U1' 'LS08' 8 'C2';

'U1' 'LS08' 9 'A2';

'U1' 'LS08' 10 'B2';

'U1' 'LS08' 11 'C3';

'U1' 'LS08' 12 'A3';

'U1' 'LS08' 13 'B3';

END.

```

NOTE: If you rename a part, you must enter all the pins for that part since omitted pins are assumed to be 'NC' (not connected). Also, if you reassign a section, you must list every pin in that section.

# PHYSICAL NET NAME TRANSFORMATIONS (PSTNETX)

This file is used to change the name of a physical net, and it has the file type NET\_TRANS. Each net is originally assigned a name by the Packager that can be changed with this file. The file consists of a list of transformations in the form

'old physical net name' 'new physical net name'

where old physical net name is the name assigned to the net by the Packager in the last run and new physical net name is the new name to be assigned to the net. For example, the Feedback to the Packager

net N00001 can be changed to XYZ as follows:

FILE\_TYPE = NET\_TRANS; ROOT\_DRAWING = 'SAMPLE'; 'N00001' 'XYZ' END.

# SECTION 7 BACK ANNOTATION

Information usually flows from the drawings of the logical design, through the Compiler and Packager, and on to a physical design system. However, there is an important class of information that flows from the end of this process to the beginning. The Packager and the physical design system add physical data to the design that you may wish to see reflected in the drawings, such as the physical part designator for each part and the pin number for each pin. The process of taking information created or added downstream in the design process and bringing it upstream is called "back annotation."

#### 7.1 WHEN TO BACK ANNOTATE

There are two different times in the design cycle when it is important to back annotate your GED drawing. The first of these is after the first error-free run of the Packager, and the second is after the design has been sent to a physical design system (producing feedback files) and the design has been repackaged to reflect the changes in physical assignments. The following shows the typical order of design steps from the Packager through a physical design system including back annotation.

> GED COMPILE PACKAGE BACKANNOTATE (physical interface program) (physical design system) PACKAGE BACKANNOTATE

The first time you back annotate your design is after your first error-free run of the Packager. After you have corrected any errors found by the Packager in your design,

3/10/86

and run the Packager on the corrected design, you want to record the physical assignments (the U-numbers and pin numbers) on your GED drawing for reference. Remember, however, that these physical assignments may be modified by your physical design system. That is why you will have to back annotate again later.

After this first back annotation, you send the Packager output to a physical interface program to format it for a physical design system, and then to a physical design system. The physical design system creates feedback files that are used as input files to the Packager. You may also create your own feedback files to force the Packager to make certain assignments. You then run the Packager again and it reassigns parts on the basis of the instructions in the feedback files. Now you want to update your GED drawing again so that it corresponds exactly with the physical design you have produced. This is the second time that you back annotate your design.

# 7.2 HOW TO BACK ANNOTATE

Back annotation brings physical design data from the Packager and adds it to the logical design drawings. The Packager generates a back annotation file that contains physical information grouped by drawing.

To generate this file, use the directive OUTPUT BACKAN-NOTATION when running the Packager. Backannotation can occur on three types of elements: bodies, pins, and nets. Use the ANNOTATE directive to select among these elements. If this directive is not specified, the default options are bodies and pins. If the net option is specified, the synonyms file from the compilation must be available. The back annotation information is written to the logical This file PSTBACK. file must be renamed to BACKANN.CMD to be used by the Graphics Editor. You can then use the GED command BACKANNOTATE to automatically add all the physical assignments made by the Packager to your drawing. Back annotation saves a lot of time and tedious work and ensures that the drawing accurately reflects the physical part assignments.

Packager

It is recommended that you keep a backup of all drawings before back annotation is performed. This will give you both non-annotated and annotated versions of the drawings that may be useful since it does take time to remove the annotated properties from a set of drawings. Figure 7-1 shows an example of a back annotated drawing.

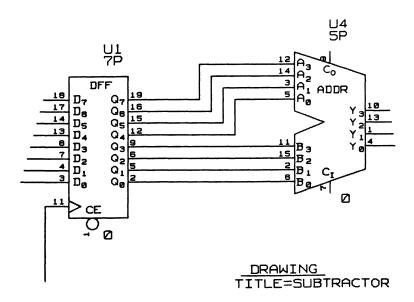

## Figure 7-1. Back Annotation of Schematic

#### 7.3 DESIGN TECHNIQUES AND ANNOTATION

If a logical design has structured elements such as SIZE and TIMES, back annotation may not show all the physical assignments on the drawing. Only non-structured elements are annotated. Back annotation cannot be done on structured elements because the physical and logical representations of the drawing are very different. A "flat" drawing has no structured elements and can be completely back annotated. If you have a design that is structured and you must have complete back annotation, you must re-enter

3/10/86

the finished design as a flat drawing.

Likewise, if you have a hierarchical design, you can only back annotate the "lowest" levels of the design. Remember that the top level of a hierarchy does not have a one-to-one correspondence to the physical design. For both hierarchical and structured designs, cross reference listings from the Packager (file PSTXREF) may be used to supply the complete set of physical information. These listings are organized such that all data can easily be tracked back to the design drawings. Cross reference listings and the design drawings may be used together for design troubleshooting when a fully backannotated print is not necessary.

## 7.4 SOFT AND HARD PROPERTIES

You may sometimes notice that certain parts may be updated with new physical information during successive back annotation runs. The properties which may change from one back annotation to the next are called "soft" properties. These are properties which are attached by the Packager program, and they may change from one run to the next.

Properties which you assign are called "hard" properties, and these are not altered by the Packager unless you use the directives HARD\_LOC\_SEC OFF and/or HARD\_GROUPING OFF and modify them through the feedback files. Thus, these properties do not change unless you specifically alter them through feedback or through the Graphics Editor.

For example, you may wish to attach the LOCATION property to a body to ensure that the part is assigned to a specific physical part designator. You would not want this to be changed by the Packager. Thus, LOCATION is a hard property. Other hard properties that you may use are:

> GROUP LOCATION\_CLASS SEC (you assign this with the SECTION command) PN (you assign this with the PINSWAP command)

### Packager

Soft properties, on the other hand, are added during back annotation, and they are subject to change on subsequent back annotation runs. You want these to be updated. The Graphics Editor differentiates between hard and soft properties so that it can update information correctly. Soft properties that may be added by the Packager include:

Note that soft properties are ALWAYS preceded with a "\$" in the property name. Also, soft properties do not force assignments in the Packager; only hard properties can control assignments.

# 7.5 SPECIAL USES OF PROPERTIES

Although users can assign soft properties, this is generally done by GED during back annotation. However, you may wish to attach a soft property to a .BODY drawing as a placeholder for back annotation purposes. The "\$" defines the property as "soft", and the "?" is a placeholder that is later substituted with a U-number.

# SECTION 8 PACKAGER FUNCTIONS IN DETAIL

This section contains detailed discussions of various Packager functions which were discussed more briefly earlier in this manual. This section covers the following topics in the order listed below:

> Net and Part Name Assignment SIZE Expansion TIMES Expansion Wire-Gate and Wire-Tie Expansion Net Checks Load Checks

#### 8.1 NET AND PART NAME ASSIGNMENT

The Packager assigns physical names to both signals and parts. Physical net names are created from the abbreviation of the logical signal name for the net. If there are several logical signal names on a net, the Compiler picks one for the Packager to use. The maximum length of net names is controlled by the NET\_NAME\_LENGTH directive. The path name portion of the logical signal name is not used in the abbreviation. The abbreviation is created as follows:

- 1. Remove all special characters. These are all characters except A-Z and 0-9.

- 2. If the signal is low asserted, add a trailing 'L'.

- 3. If the name starts with a digit, change it to a letter.

- 4. If the signal is vectored, append the offset as a number.

- 5. If the signal is versioned, append 'V' and the version number when the version number is not zero.

- 6. If the resulting name is greater than maximum net name length, remove all the vowels.

- 7. If the resulting name is still too long, then truncate the name to the maximum net name length.

- 8. If the resulting name is not unique, make it unique by incrementing the last non-numeric character of the name. This is to preserve the bit offset that was appended to the name.

For example, the logical net name "READ ADR B < 2 >" would become the physical net name "READADRB2". Physical part names are created by starting with the value of the PHYS\_DES\_PREFIX property found on the part type in the library or on the logical part in the design. If there is no prefix on the library part, the Packager uses the standard prefix 'U'. If the name is not unique, it is made unique by adding a number (e.g., U12, U14). The maximum length of the names is controlled by the PART NAME LENGTH directive. Note that the PHYS DES PREFIX property does not override the old part names from the last Packager run if the current run uses state files. That is, the Packager uses the prefix only if the part is new or if there are no state files.

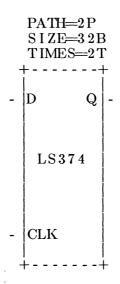

## 8.2 SIZE EXPANSION

The SIZE property is used to generate multiple components in one body representation and connect them to a group of signals (a bus). SIZE is used in the logical design to provide a concise means of representing many logical parts as one part together with bus notation. Figure 10 shows an example of a SIZEd part. The Packager generates SIZE number of expanded parts and assigns a new logical designator to each. A logical part can have pins common to all sections as well as pins unique for each section. Common pins are connected in parallel for all sections and the unique pins are connected to independent pieces of the signal connected to the original part. The PIN\_NUMBER property for each pin in the body definition specifies whether the pin is common or unique for each section. The PIN\_NUMBER property also specifies the width of the pin to which it is attached. The Packager allocates this number of bits from the original signal to each expanded part. The assignment of bits of a signal to physical parts is done sequentially so that adjacent bits are assigned to the same physical package if possible. Figure 8-1 shows an example of the packing of a SIZEd part. See the Library reference manual for more detail.

Figure 8-1. SIZE Expansion and Packaging

Packager Functions in Detail

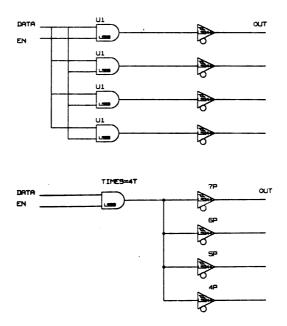

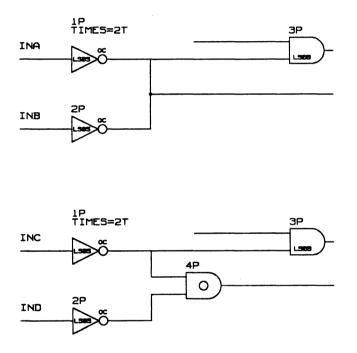

#### 8.3 TIMES EXPANSION

In digital designs, it is often convenient to have several different signals available which each have the same behavior. One such case is where a net has more input loads than the output is capable of driving. This fan-out error must be corrected if the circuit is to function as designed. A good way to fix this type of problem is to divide the inputs on the net into two or more groups, where each group presents a small enough load to be driven by one output. Each group is wired together and is said to connect to a "version" of the net. To keep the operation of the design unchanged, each version must have the same logical behavior. To avoid fan-out errors, each version of the net must have a different output driving it. This is accomplished by connecting each version of the net to a different version of the output, where each output version behaves the same. Figure 8-2 shows an example.

Figure 8-2. TIMES Expansion and Packaging

You can generate multiple versions of the outputs of any part by attaching the TIMES property to the part. The value of the TIMES property equals the number of versions to be generated. The outputs are generated by creating TIMES number of physical sections and, for all physical sections, connecting the inputs as shown in the drawings. Thus, since the inputs to each of the components are identical, each output signal will exhibit the same logical behavior over all the versions.

Replication by TIMES is useful where an output must drive many input loads. The Packager will divide the loads among the versions of an output so that the specified loading rules will be obeyed. In the process, the Packager generates one version of the net for each version of the output. When more versions of an output exist than are necessary to drive the net to which it is connected, the Packager will

3/10/86

Packager Functions in Detail

attempt to divide the loads evenly among all output versions. If loading rules require more output versions than are specified, the Packager determines the number of additional versions which are needed and flags the error.

When several outputs are connected to one net (wire-tied), and several versions of the net are desired, each output should have a TIMES value equal to the number of versions of the net desired. If several outputs on the same net have different TIMES values, the number of versions of the net generated is the minimum of the output TIMES values. Physical parts with no TIMES properties have a TIMES value of one. Figure 8-2 illustrates these rules.

## 8.4 WIRE-GATE AND WIRE-TIE EXPANSION