## SCALD LANGUAGE REFERENCE MANUAL

## Manual Number: MN221 Rev A

10 March 1986

Valid Logic Systems, Incorporated 2820 Orchard Parkway San Jose, CA 95134 (408)945-9400 Telex 371 9004

Copyright © 1986 Valid Logic Systems, Incorporated

This document contains confidential proprietary information which is not to be disclosed to unauthorized persons without the prior written consent of an officer of Valid Logic Systems Incorporated.

The copyright notice appearing above is included to provide statutory protection in the event of unauthorized or unintentional public disclosure.

# TABLE OF CONTENTS

| Overview                          |        |

|-----------------------------------|--------|

| Drawings                          | 1 - 2  |

| Signals and Interconnections      | 1-3    |

| Signal Naming and Syntax          |        |

| Signal Naming Conventions         | 2 - 1  |

| Signal Name Syntax                | 2-2    |

| Negation Symbol                   | 2-2    |

| Signal Name                       | 2-3    |

| Bit Subscripts                    | 2-5    |

| Assertion                         | 2-7    |

| Signal Properties                 | 2-7    |

| The Complete Signal Syntax        | 2-9    |

| Optional Ŝignal Name Ŝyntax       | 2 - 11 |

| Concatenated Signals              | 2 - 12 |

| Constant Signals                  | 2 - 12 |

| Path Name Syntax                  | 2 - 14 |

| Page                              | 2 - 15 |

| Abbreviation                      | 2 - 15 |

| Path                              | 2 - 15 |

| Size                              | 2 - 16 |

| Unique_Number                     | 2 - 16 |

| Path Element Name Examples        | 2 - 16 |

| Path Name                         | 2 - 17 |

| Signal Synonyms                   | 2-17   |

| Signals of Undetermined Width     | 2-18   |

| Signals of Undetermined Assertion | 2-19   |

| Advanced Signal Name Topics       | 2-20   |

| Unused Pin Names                  | 2-20   |

| NC Signals                        | 2-21   |

| Unnamed Signals                   | 2-22   |

| Special SCALD Bodies              |        |

| Plumbing Bodies                   | 3-1    |

| Bodies in the Standard Library    | 3-3    |

| SYNONYM                                    | 3-4  |

|--------------------------------------------|------|

| TAP                                        | 3-4  |

|                                            |      |

| Properties in the SCALD Language           |      |

| What is a Property                         | 4-2  |

| Specifying Properties                      | 4-3  |

| The Property Command                       | 4-3  |

| Properties Within Signals                  | 4-4  |

| Signal Properties                          | 4-4  |

| Pin Properties                             | 4-6  |

| Adding Pin Properties w/ Property Command. | 4-7  |

| Adding Pin Properties as Part of Pin Name  | 4-7  |

| Pin Properties Inherited From Signals      | 4-7  |

| Property Attributes                        | 4-7  |

| Parameter Attribute                        | 4-8  |

| Inherit Attribute                          | 4-11 |

| Permit Attribute                           | 4-13 |

| Filter Attribute                           | 4-14 |

| User Property Attribute File               | 4-14 |

| Default Property Attributes                | 4-15 |

| An Example Property Attributes File        | 4-16 |

| Drawing Properties                         | 4-16 |

| Text Macro Processing Within Properties    | 4-17 |

| Advanced Property Topics                   | 4-18 |

| \NAC Property                              | 4-18 |

| \NWC Property                              | 4-19 |

| Properties Recognized by the Compiler      | 4-20 |

| ABBREV                                     | 4-22 |

| ALLOW_CONNECT                              | 4-23 |

| BODY_TYPE                                  | 4-24 |

| BUBBLED                                    | 4-26 |

| EXPR                                       | 4-27 |

| HAS_FIXED_SIZE                             | 4-28 |

| NEEDS_NO_SIZE                              | 4-29 |

| NOASSERT                                   | 4-30 |

| NO_IO_CHECK                                | 4-32 |

| NOWID TH                                   | 4-33 |

| PART_NAME                                  | 4-35 |

| PATH                                       | 4-36 |

| REP                                        | 4-37 |

| SCOPE                                      | 4-38 |

| SIZE                                       | 4-39 |

| TERMINAL                                   | 4-40 |

| TIMES      | 4-41 |

|------------|------|

| TITLE      |      |

| WIRE_DELAY |      |

# Text Macro Facility

| What is a Text Macro               | 5-1    |

|------------------------------------|--------|

| Where to Define Text Macros        | 5 - 3  |

| Defining a Text Macro on a Drawing | 5-4    |

| How to Use Text Macros             | 5-4    |

| Use in Other Text Macros           | 5 - 5  |

| Use in Signal Names                | 5 - 5  |

| Use in Properties                  | 5-6    |

| Use in Parameters                  | 5-7    |

| Where Text Macros May Not be Used  | 5 - 8  |

| Drawing Names                      | 5-8    |

| Property Names                     | 5-8    |

| Text Macros With Parameters        | 5-8    |

| Multiple Parameters in Text Macros | 5-10   |

| Globally Defined Text Macros       | 5 - 11 |

# Selection Expressions

| Drawing Versions                        | 6-1 |

|-----------------------------------------|-----|

| Selection Expressions                   | 6-2 |

| How Selection Expressions Are Evaluated | 6-3 |

| Selection Expressions in Drawings       | 6-4 |

| Expression Evaluation                   | 6-5 |

| -                                       |     |

# Expressions

| Use of Expressions | 7-1 |

|--------------------|-----|

|                    | 7-3 |

# Index

# SECTION 1 OVERVIEW

Logic design is supported on the SCALD system and PC-AT with a unique set of software tools and a proven methodology. One of the most important aspects of SCALD technology is the SCALD language that is used to express the logical design of an electronic circuit. Within this manual, the signal and path name syntax is defined and the concepts of properties and text macros are explained.

As with any language, the SCALD language has been developed to provide clear and concise communication between system and designer and specifically to allow logic design concepts to be expressed in a predictable and consistent manner. The language is explicitly designed to allow the definition of complex logic circuits while still retaining its user-comprehensible nature. Since the language is understood by the system, error detection, circuit analysis, and physical descriptions can be generated automatically.

In the development of the SCALD language, the following eriteria were realized:

- The language is complete. That is, the language is capable of describing any logic circuit.

- The language is easy to understand. It is consistent, simple, and logical and includes no surprises.

- The language adapts to existing design conventions. Logic design conventions such as signal naming conventions and schematic layout are accommodated within the language – the language does not require the user to follow a specific design style.

- The language supports hierarchical and structured as well as flat designs.

- The language is error resistant. Constructs that are error-prone and that do not provide significant advantages in return are avoided.

- The language supports concise representations. Commonly encountered circuit elements are represented in as concise a manner as possible.

- The language does not require the addition of "special" information in a drawing that normally would not be placed on a vellum print. A drawing needs only enough information to describe the schematic.

#### 1.1 DRAWINGS

Logic designs are entered into the SCALD system as drawings. A drawing is nothing more than a graphical schematic – it is the same as a schematic drawn by hand on paper. The Graphics Editor is used to create all drawings in the SCALD system. Drawings are used to specify all information about a schematic throughout the SCALD system.

To describe a schematic, the components or "parts" are specified, positioned, and interconnected with wires. Components come from libraries that define sets of parts within a logic family. Valid offers a wide range of libraries that include the TTL, ECL, and CMOS technologies. A schematic drawing is complete when all components and wires have been entered and the drawing has been written to the disk.

The Graphics Editor creates two descriptions of each drawing; a graphical description that shows the shape and placement of all parts and wires, and a description of the circuit's electrical connectivity that describes how the parts are interconnected, but contains no graphical information. The Graphics Editor is the only SCALD system analysis tool that knows what the drawing "looks like" and is the only tool that reads the graphical descriptions. The remainder of the analysis tools use the electrical connectivity descriptions. The SCALD Compiler reads the drawings created by the Graphics Editor, performs error checking and hierarchical expansion, and outputs the connectivity files for use by the other analysis tools. A drawing is entered by the designer using the Graphics Editor, is compiled by the Compiler, and is packaged by the Packager into the net and parts lists required for circuit fabrication and documentation. The optional Timing Verifier and Logic Simulator analysis tools perform electrical verification of the design.

## 1.2 SIGNALS AND INTERCONNECTIONS

Every interconnection between two or more components represents a signal, and every signal has a name. Signal names can be assigned by the designer (using the Graphics Editor's SIGNAME command); unnamed signals automatically are given unique names by the Graphics Editor. Signal name assignment by the designer allows descriptive or mnemonic references to be used; signal names assigned by the Graphics Editor are more cryptic and are not as easily interpreted. A signal is referred to by name and can be referenced from many drawings.

The SCALD language recognizes interconnections in two ways: the direct connection of two (or more) points with a wire, or the designer's assignment of the same signal name to two or more wires (i.e., there is an implicit connection among wires of the same name). Implicit connections by signal name make it easy to interconnect components without having to use continuous wire connections that can add unnecessary complexity to a schematic. As an example, consider a clock signal that drives multiple components. While a single wire with multiple tie points can be used, labeling each clock input with the same signal name is logically and functionally identical and eliminates having to route the signal to each input.

# SECTION 2 SIGNAL NAMING AND SYNTAX

### 2.1 SIGNAL NAMING CONVENTIONS

Signals in the SCALD system represent interconnections of parts. These interconnections are given names that serve to identify and distinguish them. Signals have several attributes that are specified within the signal name. These attributes are:

- The name by which the signal is known

- Its assertion level (high or low)

- The number of bits the signal represents

- The properties it possesses

A signal's name is a string of characters chosen to provide some descriptive or mnemonic reference for the signal. The name is used to identify the signal, and all signals with the same name are interpreted as being the same signal.

The assertion level describes the active state of the signal when asserted. By convention, a signal is active high for positive logic and is active low for negative logic. Two signals with the same name, but with different assertion levels are NOT the same signal.

A signal that represents a single bit is called a "scalar" signal. Within SCALDsystem, signals can represent multiple bits (i.e., a bus). Multiple-bit signals are called "vector" signals; the bit subscript portion of the signal name specifies the number of bits (and which bits) the vector signal represents. Scalar signals do not have bit subscripts. Vector signals always have bit subscripts even when the signal represents only a single bit. A signal cannot be a scalar in one instance and a vector in another; the use of a signal must be consistent. Signal Naming and Syntax

Signals can be given properties that describe characteristics of the signal, control how the signal is interpreted by the Compiler, convey physical information, etc. Several properties are predefined by the Compiler and have special meanings. The designer can define additional properties that are passed through the Compiler to post processing programs to allow information to be added to the drawings that is not used by the other design tools, but has meaning in the user's design environment. Signals that have different properties, but are otherwise identical, are considered to be the same signal (except signals with different values for the SCOPE property; see Properties in section 3.

### 2.2 SIGNAL NAME SYNTAX

The complete signal name syntax can include the following parameters:

- negation symbol

- signal name

- bit subscript

- assertion symbol

- general properties

With the exception of the name, all of the other signal parameters are optional.

## NEGATION SYMBOL

The negation symbol indicates that the entire signal is the negated form of a corresponding "base" signal (i.e., the complement of the signal without the negation symbol). As an example, the signal -CLOCK A is the negated form or complement of the signal CLOCK A. The default negation symbol is the "-" character (see section 2.4 and the *Library Reference Manual* for optional symbols).

## SIGNAL NAME

The name portion of a signal is the "name" by which the signal is known. Within a name, a timing assertion may be included. A signal name may be made up of any characters except the following reserved characters:

bit subscript start character ('<') general property prefix character (' $\cdot$ ') assertion character ('\*') signal concatenation character (':')

The following additional characters have special meanings within the signal name:

- ' delimiter for a single quote string

- " delimiter for a double quote string

- {} delimiters for a comment

- ! prefix for a timing assertion

- **\$** signal class separator

A signal name is further divided into three parts: the signal class, the name string, and the timing assertion. The signal class and timing assertion are optional.

#### Signal Class

Signal class is an optional character string prefix that is used to identify groups or sets of related signals. As part of the signal name, signals with the same name string, but with a different signal class, are NOT identical. A signal class string must be separated from the name string by the \$ character. As an example, all signals in an ALU portion of a design would be placed in the same class (i.e., the "ALU" class) by prefixing each signal with "ALU."

ALU\$A=B ALU\$BUS ENABLE ALU\$CARRY IN

2-3

The signal class of a signal is ignored by the Compiler; it is interpreted as part of the name. Signal class can be used by the designer both to sort signals and to improve the readability of signal names. As will be explained later in this section, unnamed signals automatically are assigned signal class "UN."

## Name String

The name string is a string of characters that form the "name" of the signal; user-assigned names are usually descriptive or mnemonic. Names may be made up of any characters except for the special characters previous described (special characters can be used if enclosed in single or double quotes). For example, the name

A\*B enable

is illegal while the following names are legal:

'A\*B enable' "A\*B" enable A'\*'B enable

## **Timing Assertions**

Timing assertions are used to define the periodic behavior of a signal over a clock period. The most common use is in defining the behavior of clock signals. Timing assertions provide important data to the Timing Verifier and the Logic Simulator. They are passed on to these programs by the Compiler without being checked for syntax errors. Timing assertions are ignored by the Packager. The form of a timing assertion is described in detail in the *Timing Verifier Reference Manual.* The general form is

! assertion\_type time\_specifier

where '!' is the timing assertion prefix character, *assertion\_type* is C, P, D, or S, and *time\_specifier* is a clock interval or range of clock intervals.

Here are some examples:

CLOCK !S 4-6 CLOCK !C2-4

The Compiler ignores timing assertions because they are part of the name portion of the signal name. The two signals in the above example are NOT the same signal because they have unique signal names.

### BIT SUBSCRIPTS

Bit subscripts are part of the SCALD structured design methodology and are used with vector signals both to specify the number of bits that a signal represents (e.g., the bit range) and to identify the bits included. Bit subscripts can be of the following forms:

< bit> < bit .. bit> < bit .. bit : step> < bit : width> < bit : width : step> < bit list>

where bit is some bit number. The bit number must be equal to or greater than zero (negative bit numbers are not allowed). The '<' character marks the beginning of a bit subscript, and the '>' character marks the end. If a bit subscript does not appear in a signal name, the signal is a scalar.

## <bit> Subscript

Specifies a single bit of a vector signal. Note that although such a signal represents only a single bit, it is called a vector since it represents a specific bit of a multibit (vectored) signal. Some examples:

<31> <0> <6> <5334773>

### <br/> <bit1 .. bit2> Subscript

Specifies a subrange of bits from bit1 to bit2 inclusive. The order of the bits is determined by the signal syntax being used; the default bit order is from right to left (i.e., bit1 is greater than bit2). See also section 2.4 and the *Library* Reference Manual. Some examples:

<31..0> <9..2> <7..0>

### <br/><bit1 .. bit2 : step> Subscript

Specifies a subrange of bits beginning with bit2 and including every bit that is *step* bits apart up to bit1 (default rightto-left bit order). The *step* value is a positive integer (a negative integer can be specified to reverse the bit order signal syntax); a *step* value of "1" is equivalent to no step value. Some examples:

<31..0:2> results in 30 28 26 ... 6 4 2 0 <11..0:4> results in 8 4 0 <9..1:3> results in 7 4 1 <0..31:-1>results in 31 30 29 ... 3 2 1 0 <15..0:20> results in 0

#### <br/>bit: width> Subscript

Specifies a field of *width* bits using *bit* as the high-order bit (default right-to-left bit order) or low-order bit (left-toright bit order). Note that *width* must be a non-zero positive integer. Some examples:

<31:8> same as <31..24> <15:16> same as <15..0> <0:16> same as <0..15> (left-to-right bit order)

## <br/><bit: width : step> Subscript

Specifies a field of *width* bits using *bit* as the high-order bit (default right-to-left bit order) or low-order bit (left-toright bit order) and including only those bits that are *step* bits apart. Note again that *width* must be a non-zero positive integer, and *step* can be either a positive or negative non-zero integer. Some examples:

<31:8:2> same as <31..24:2>, results in 30 28 26 24 <0:16:3> same as <0..15:3> (left-to-right bit order), results in 0 3 6 9 12 15 <31:8:-1> same as <24..31>

## <br/>bit list> Subscript

A *bit list* is a list of any of the above forms of subscript specifiers. Each subscript specifier must be separated by a comma, and any number of specifiers may be included in the list. An example:

<1,7..4,19:8:2> results in 18 16 14 12 7 6 5 4 1

## ASSERTION

In the default signal syntax, the assertion level of a signal is determined by the presence or absence of the '\*' low assertion character (i.e., the presence of the low assertion character indicates that the signal is active in it low state). For a high assertion character that must be explicitly specified to define a signal that is active in its high state, see the alternate signal syntax formats described in section 4.4.

## SIGNAL PROPERTIES

Signal properties are used to add information to a signal that can be interpreted by the Compiler or Packager programs. A property is a name/value pair that is used to convey almost any kind of information. For a complete description of properties, see the Section 4. The form of a signal property when it appears in a signal name is:

## \ property name = 'property value'

The  $\$  is the property prefix character, property name is a character string identifier, and 'property value' is a string of characters enclosed in single quotes. Some common signal properties have been given abbreviations (with text macros) to make them easier to use. These abbreviations are:

| $\mathbf{L}$               | - | gives local scope to a signal              |

|----------------------------|---|--------------------------------------------|

| G                          | - | gives global scope to a signal             |

| Ι                          | - | identifies a signal as an interface signal |

| $\mathbf{R}\mathbf{n}$     | - | specifies signal replication               |

| NWC                        | - | no width check directive                   |

| NAC                        | - | no assertion check directive               |

| WD n                       | - | wire delay                                 |

| CD n                       | - | chip delay                                 |

| $\mathbf{E}\boldsymbol{n}$ | - | evaluation directive                       |

They are used as follows:

\L equivalent to \SCOPE='LOCAL' \WD 2.0-3.0 equivalent to \WIRE\_DELAY='2.0-3.0' \R 2 equivalent to \REP='2'

For a more complete description of text macros and their use, see Text Macro Facility, later in this manual.

## 2.3 THE COMPLETE SIGNAL SYNTAX

The signal name parameters are combined to form a complete signal name. To summarize, a signal name may include the following parameters:

- negation character

- name portion

- bit subscript

- assertion statement

- general properties

With the default signal name syntax, the order in which the signal name parameters must appear is as follows:

negation name subscript assertion properties

The negation, subscript, assertion, and properties parameters are optional; name must appear in every signal name. The following examples demonstrate the default signal syntax.

## CLOCK

Active high "CLOCK" scalar signal.

## -CLOCK

Negated (complementary) active high "CLOCK" scalar signal.

#### ENABLE\*

Active low "ENABLE" scalar signal.

## -ENABLE\*

Negated active low "ENABLE" scalar signal.

## -DATA IN <15..0>\*

Negated active low 16-bit DATA IN vector signal (DATA IN 0 through DATA IN 15).

Signal Naming and Syntax

### DATA OUT <2>\* \WD 2.0-3.0 \L

Active low "DATA OUT 2" single-bit vector signal with 2.0-3.0 nanosecond wire delay and "local" scope.

#### SYSINIT\* \G

Active low "SYSINIT" scalar signal with global scope.

#### ADDR <15..0,18> \I\WD 3.0-5.6

Active high 17-bit "ADDR" vector signal (ADDR 0-15, ADDR 18) with "interface" scope and 3.0-5.6 nanosecond wire delay.

#### CLK !C 0-4, 5-7

Clock signal high for intervals 0-4 and 5-7.

#### DATA !S 2-4

Data signal high for intervals 2-4.

Note that in the signal examples with properties, a space is required to separate the property name from its associated value and that a space also is required to separate a property value from a subsequent property name (the Compiler uses spaces to determine the beginning and end of a text macro parameter; a space is not required between the \I and \WD properties in the last example since the \I text macro does not have an associated property value).

## 2.4 OPTIONAL SIGNAL NAME SYNTAX

The default syntax for signal names described in the previbus sections is referred to as the Valid standard library fornat or "Library Format 1" and is defined as follows:

negation name subscript assertion general\_props

Four other formats for the signal name syntax are supborted. To use these formats, the component libraries nust be translated from the Valid format to the library fornat desired. Note that library translations normally are perormed by Valid field service personnel when the system is nstalled. The signal name syntax for each of the optional ibrary formats is as follows; the negation, assertion, and oit subscript order and subrange indicator for each format ure outlined in Table 2-1.

Library Format 2:

negation name subscript assertion general\_props

Library Format 3:

negation name subscript assertion general\_props

Library Format 4:

assertion name subscript general\_props

Library Format 5:

negation name assertion subscript general\_props

| 'ormat<br>lumber | Low Assertion<br>Character | High Assertion<br>Character | Bit<br>Order  | Subrange<br>Indicator |

|------------------|----------------------------|-----------------------------|---------------|-----------------------|

| 1*               | <sup>د</sup> *'            | none                        | right to left | · <b></b> '           |

| 2                | L                          | Н                           | right to left | ':'                   |

| 3                | L                          | н                           | right to left | ·'                    |

| 4                | <b>'_'</b>                 | '+'                         | left to right | ':'                   |

| 5                | L                          | н                           | left to right | <b>'</b> ••'          |

## Table 2-1. Optional Library Formats

/alid standard default format

Note that with the formats that use the 'L' and 'H' for assertion level, a space prefix is required to avoid signa name ambiguity with scalar signal names. Also note tha since Library Formats 2 and 4 use a ':' as the subrange indicator, two consecutive colons must be used to indicate a step argument for a bit subscript (e.g. < bit1:bit2::step>).

## 2.5 CONCATENATED SIGNALS

Signals can be concatenated (linked) to form signal bu structures by separating each signal name with the concate nation character (':') For example, the signals A and B ar concatenated as follows:

A:B

Concatenated signals are completely unrelated; concatenation is merely a shorthand notation for two or more signal that appear together and is the same as running the signal side by side. A concatenated signal is separated back int its individual signals with a "demerge" or "tap" body (se section 3).

## 2.6 CONSTANT SIGNALS

A constant is a special type of signal name. The SCALl language allows constant signals to be specified in binary octal, hexadecimal, and other number systems. The synta for a constant signal name is the same as for other sign names, except that bit subscripts are not allowed. Thes fields are allowed:

#### neg constant\_name assertion properties

Constants may have assertions although no assertion checking is performed on them unless explicitly enabled (see the *Compiler Reference Manual* for a discussion of assertic checking).

The syntax for *constant\_name* is

radix # constant\_value [(width)]

where *radix* specifies the number system (or base) used to specify *constant\_value*. Note that *radix* must be a base 10 integer between 2 and 16. If *radix* is not specified, binary (base 2) is assumed. The '#' character separates *radix* from *constant\_value*.

*Constant\_value* is a string of digits. The legal digits are determined by the radix specified as follows:

| Radix | Legal Digits     |  |  |

|-------|------------------|--|--|

| 2     | 0 1              |  |  |

| 3     | 012              |  |  |

| 4     | 0123             |  |  |

| 5     | 01234            |  |  |

| 6     | 012345           |  |  |

| 7     | 0123456          |  |  |

| 8     | 01234567         |  |  |

| 9     | 012345678        |  |  |

| 10    | 0123456789       |  |  |

| 11    | 0123456789A      |  |  |

| 12    | 0123456789AB     |  |  |

| 13    | 0123456789ABC    |  |  |

| 14    | 0123456789ABCD   |  |  |

| 15    | 0123456789ABCDE  |  |  |

| 16    | 0123456789ABCDEF |  |  |

Width explicitly specifies the number of bits used to express the constant (in the specified radix) and must be greater than zero. If width is omitted, it is calculated from the number of bits per digit (radix) and the number of digits in the constant. Note that width, if specified, must be enclosed in parentheses.

| Radix                  | Bits per Digit |

|------------------------|----------------|

| 2                      | 1              |

| 3 4                    | 2              |

| 5678                   | 3              |

| 9 10 11 12 13 14 15 16 | 4              |

#### Signal Naming and Syntax

Example constants:

| Constant                                                          | Value (base 10)                    | Number of Bits                   |

|-------------------------------------------------------------------|------------------------------------|----------------------------------|

| 0101<br>2#0000<br>0000(3)<br>10#0<br>16#FFFF<br>8#377<br>8#377(8) | 5<br>0<br>0<br>65535<br>255<br>255 | 4<br>4<br>3<br>4<br>16<br>9<br>8 |

#### 2.7 PATH NAME SYNTAX

Path names are used to uniquely identify every component within a design. Just as every wire has a signal name, every component appearing within a design has a unique path name. Since the same component can be used many times within a design, the component path name must be more specific than just the name of the component. Path names are assigned exclusively by the SCALD system based on the path followed from the root drawing down through the hierarchy to each individual component. Users may not specify their own path names. Path names are used by the Compiler (the Compiler listing file *cmplst.dat* references path names in its error reports), the Logic Simulator (opening signals with the same name within a design are resolved with path names), and by the Packager.

The path name itself is made up of path element names for each of the bodies encountered in the path from the root drawing to the component. A path element name is created by the Compiler for each body within a design. The path element name syntax is:

page abbreviation path [size] [unique\_number]

## PAGE

The number of the drawing page on which the body appears. If the page number is '1,' the *page* reference is omitted from the path element name.

## ABBREVIATION

An abbreviation for the drawing name. The abbreviation is normally assigned by the user by attaching the ABBREV property to the DRAWING body within the drawing. If an ABBREV property is not assigned to a drawing, the Compiler creates an abbreviation by truncating the drawing name. (Library components are preassigned an ABBREV property.) When *abbreviation* begins with a number, a period ('.') is prefixed to the abbreviation as a delimiter to separate *abbreviation* from *page* even if the page number is '1' (omitted). For example:

.1ALU = page 1 of drawing 1ALU2.1ALU = page 2 of drawing 1ALU2ALU = page 2 of drawing ALU

## PATH

The value of the PATH property attached to the body. Unique PATH properties are automatically assigned to each body in a drawing by the Graphics Editor when the drawing is written. PATH properties can also be assigned by the user with the Graphics Editor's PROPERTY command. When PATH is automatically assigned by the Graphics Editor, it takes the form

integerP

as in:

37P 85P 4P

If abbreviation ends with a number, a period ('.') is prefixed to path as a delimiter.

3/10/86

#### SIZE

The value of the SIZE property attached to the body for size replication. If the SIZE value is greater than 0, the value is included in the path element and prefixed by a '#' character; if the SIZE value is 0 or not specified (i.e., no size replication is to be performed), size is omitted.

### UNIQUE\_NUMBER

If the combination of the *page*, *abbreviation*, *path*, and *size* values does not form a unique path name element (e.g., vectored signals with size replicated components), an incrementing number, prefixed by a colon (':') is added following the *size* value to make each path name element unique.

### PATH ELEMENT NAME EXAMPLES

The path element name for a 74LS74 with an assigned PATH property of 34P that appears on page 3 of a drawing is:

#### 3LS74.34P

In the above example, note the period delimiter between LS74 (the abbreviation for an 74LS74 device) and the PATH property (34P). A more complex path element name is:

#### .2DAC8P#8:3

This path element name is for a body on page 1. Note the omission of a page number at the beginning; the leading period indicates that the body drawing abbreviation begins with a numeral (2DAC). The body has an assigned PATH property of 8P (a period delimiter is not required between the ABBREV and PATH properties since the ABBREV property ends with a character). The '#8' indicates a size replicated part, and the ':3' makes the path name element unique among the eight size-replicated bodies.

## PATH NAME

In a hierarchical design, the path name for any component within a design is constructed by concatenating each path element name for each body in the hierarchical path from the root drawing down to the component. Path names are enclosed in parentheses (). Each individual path element name is separated by a space. An example of a path name using the two path element names described above is:

## (CONVT .2DAC8P#8:3 3LS74.34P)

This example describes a 74LS74 that appears on page 3 of the drawing "2nd DAC stage" (abbreviated as 2DAC) which itself appears as a body on page 1 of the root drawing "converter" (abbreviated as CONVT). Note that since "CONVT" is the root drawing, there is no corresponding body and no page number or PATH or SIZE property.

## 2.8 SIGNAL SYNONYMS

When a signal has more than one signal name, the signal names are said to be synonymous (i.e., the names all reference the same signal). Synonyms are useful for creating locally-meaningful names for signals known throughout a design. Synonyms also provide a means of interconnecting nets. As an example, the two nets A and B can be connected together by simply synonyming the signals A and B.

The easiest way to create a synonym is to assign two signal names to a single wire. Synonyms also are created whenever more than one signal is connected to the same pin. A SYNONYM body is provided in the Standard Library (see the *Library Reference Manual*) that can be used to create a synonym. The SYNONYM body appears as three parallel lines; the center line has two common pins (one at each end). Every signal connected to the pins of the synonym body will be synonymed together. Signal Naming and Syntax

When two signals are synonymed, the Compiler selects one of the signal names as the "base" signal. The Compiler's expansion file (cmpexp.dat) contains only base signals. The synonyms file (cmpsyn.dat) lists all of the signals in the design and their corresponding base signal name. A signal is its own base signal if is is not synonymed to any other signals or if it is selected as the base signal. The rules for selecting a base signal are as follows. The rules are applied in the order listed; if base signal name selection cannot be determined by one rule, the next rule is applied.

- 1. Select the lower bit number of two signals with the same name (e.g., X < 0> is selected over X < 3>).

- 2. Select a constant signal over a non-constant signal.

- 3. Select a signal with name properties over a signal without name properties (e.g., CLOCK !C 0-4 is selected over CLOCK).

- 4. Select the signal with the most global scope.

- 5. Select the root-level interface signal.

- 6. Select a user-assigned signal name over an "unnamed" or 'NC' signal.

- 7. Select a scalar signal over a vector signal.

- 8. Select the signal that is lexicographically smaller (e.g., CLK is selected over CLOCK).

The synonyms file is described in detail in the Compiler Reference Manual.

## 2.9 SIGNALS OF UNDETERMINED WIDTH

Some signals in a design do not have an explicit width specification. The width of these signals must be determined from context; that is, the widths are determined by how they are used. The most common example of signals with undetermined widths are NC and unnamed signals. NC and unnamed signals are special signals. An NC signal is used to specify an unconnected pin. The use of this signal serves to make the drawing easier to understand. It is inconvenient to have to specify the width of an unconnected pin so the Compiler coerces the width of the signal NC to the width of whatever pin it is connected to. Unnamed signals are created by the Graphics Editor.

For both NC and unnamed signals, the Compiler determines the signal width from context. Most of the time, the Compiler sets the width of the signal to the width of the pin to which it is connected. In some cases, however, the pin itself has no width (as in the case of a MERGER or NOT body). In these cases, the Compiler must search further to find the width of the signal. Typically, all the "plumbing" bodies in a drawing must be processed before the widths of all the unnamed and NC signals can be determined. If the width of a signal cannot be determined, an error message is printed.

Signals with unknown widths are given the bit subscript  $\langle UNDEFINED \rangle$  when printed to indicate to the designer that the width could not be determined. In such cases, the designer can specify the width in one of the following ways:

- 1. Give the signal a name with the width specified (in the bit subscript).

- 2. Use a SLASH body to specify the width of the signal.

## 2.10 SIGNALS OF UNDETERMINED ASSERTION

The assertion of unnamed signals must be determined from context as is the width. The assertion of the signal is determined whenever the signal is connected to a pin with a known assertion or when the signal is synonymed to a signal with a known assertion. Some pins do not have known assertions. These pins have the NAC (no assertion check) property which causes the assertion of the pin to be inherited from the signals connected to it. The existence of the NAC property forces the Compiler to look at another body to find the assertion of a signal.

3/10/86

Signal Naming and Syntax

Most "plumbing" bodies have pins with the NAC property. For this reason, the Compiler processes all of the "plumbing" bodies first in order to determine the assertions of the unnamed signals in the design. If an unnamed signal is connected to pins of conflicting assertions, the Compiler generates an error message.

## 2.11 ADVANCED SIGNAL NAME TOPICS

All nets in a design are named. Many of these names are assigned by the user while others are assigned by the Graphics Editor. The Compiler uses the name given a net to refer to the net. If there is more than one name for a net, the Compiler selects one name for the net and outputs a list of synonyms (or aliases) for that name so that the other names are known. Special cases of signal names will be described below.

## UNUSED PIN NAMES

In a number of instances, a pin on a body will be intentionally left unconnected by design. Any unconnected pins are tied to the signal NC (no connect). There are cases where this can lead to problems. For instance, assume a drawing has two bodies connected with a signal that happens to also be an interface signal (a pin of the body corresponding to the drawing). Normally, the Compiler replaces the pin name as used in the drawing with the name of the signal connected to the pin. This means that a global signal name is propagated down into the design via the pins it is connected to. This makes it very easy to trace a signal and reduces confusion caused by preserving pin names (which aren't real signals in any case). In the case mentioned above, the real signal is NC (no connect). Substituting NC for the pin name in the drawing disconnects the two bodies since the signal is now a non-connected signal. To prevent this from happening, the Compiler creates a new signal name when it encounters an unconnected pin name.

The new signal name is created as follows:

- 1. Start with PINNAME\$.

- 2. Append the pin name.

- 3. If the name is not unique, make it unique by appending a number preceded by a '\$'.

For example, the pin name SETA would be transformed into the signal PINNAME\_\$SETA. This signal has the same scope as the pin name; that is, it is known throughout the subtree below the drawing.

## NC SIGNALS

Occasionally, a signal (or pin) is to be left unconnected. To make this clear in a drawing, it can be given the special signal name NC. The Compiler (and the rest of the SCALDsystem programs) understand that NC is a special signal name. It has the following characteristics:

- Unlike other signals, nets with the name NC are not connected together; each one is considered to be a unique net.

- The signal NC has no particular width: it assumes the width of whatever it is connected to.

- The signal NC has no particular assertion: it can be connected to bubbled as well as non-bubbled pins.

- NC can be given an explicit width through the use of the replication operator (R n).

If a pin is left unconnected, the Graphics Editor automatically assigns the signal NC to it. See the section on undetermined width signals for a complete discussion of NC signal width.

## UNNAMED SIGNALS

The Graphics Editor names each net that is not given a name by the designer. The name is selected as follows:

- 1. Start with UN\$.

- 2. Append the page number of the drawing in which the net is found followed by a '\$'.

- 3. Find all the bodies that the net connects to. Sort the names of the bodies alphabetically and select the first in the list. Append this name followed by a '\$'.

- 4. Append the value of the PATH property attached to the body (selected above) followed by a '\$'.

- 5. Append the name of the pin of the body (selected above) that the net connects to.

- 6. If the signal so constructed is not unique within the drawing, append a number, prefixed with a '\$', to make it unique.

For example, an unnamed signal on the third page of a drawing that is connected to an LS00, an LS138, a DAC1, and a MUX3 would be named as follows:

UN3\$DAC1\$

If the pin that the signal connects to on the DAC1 body is ENABLE and the DAC1 body has the PATH property 31P, the signal would be named as follows:

UN3\$DAC1\$31P\$ENABLE

Finally, if this signal name is not unique, it is made unique:

UN3\$DAC1\$31P\$ENABLE\$2

This is the complete form of the signal name. If the body name or the pin name have special characters (those with special meanings in signal names such as '<', '>', '\', ':') the body or pin name is placed in quotes. For instance, if the pin on the DAC1 body was ENABLE\1, the signal name would be formed as:

#### UN\$3\$DAC1\$31P\$"ENABLE\1"\$2

The Graphics Editor does not assign an assertion to the unnamed signal. This is because, in general, the assertion of a signal cannot be determined from the drawing alone; it can only be determined by processing the synonyms and "plumbing" bodies.

Unnamed signals have no particular width; they assume the width of the pins of the bodies to which they are connected. See the section describing signals of undetermined width for details.

## SECTION 3 SPECIAL SCALD BODIES

There are several special bodies that can be used in SCALD drawings for signal manipulation. These bodies are used to make it easier to express a design concisely. The bodies can be found in the SCALD Standard library in the *Library Reference Manual*. The SCALD system does not treat these bodies as special; each one is defined in terms of more basic concepts. The designer may create special bodies that behave in exactly the same manner as the ones provided.

#### **3.1 PLUMBING BODIES**

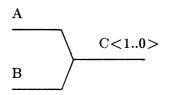

Plumbing bodies are used to combine (concatenate) signals into a single (vectored) signal or to separate a vectored signal into individual signals. A "plumbing" body looks like a wire or wires and simulates interconnections. For example, if two signals are to be combined into a bus, the user might draw a structure as follows:

The signals A and B are combined into the bus C < 1..0 >. Combining signals in this manner is called merging. If the above structure is drawn with wires, the result is the same as drawing:

A B

$$C < 1..0 >$$

#### Special SCALD Bodies

The signals A, B, and C < 1..0 > are synonymed together. This is not what was meant at all, and is an error besides (since the widths of the signals are different). The intended function could be drawn as:

A:B C<1..0>

In this example, the signal A:B (the concatenation of the signals A and B) is synonymed to the signal C < 1..0 >. This is precisely the function desired for merging.

The last example, however, does not give a good graphical representation of the function of merging. What is needed is to define a body that looks like the merge function and has the same function. This is done in a family of bodies called 2 MERGE, 3 MERGE, 4 MERGE, etc. that merge 2, 3, or 4 etc. signals into one signal. The definition of the MERGE is a synonym of the concatenation of all of the input signals to the output bus. MERGERs are described further below.

"Plumbing" bodies are special in that the Compiler processes them before processing other bodies in a drawing to resolve widths and assertions of signals whose widths or assertions are unknown (this is discussed in detail elsewhere). A "plumbing" body is identified by the presence of the NWC (no width check) property on a pin of the body. The NWC property indicates that the pin has no known width; the width of the pin is determined by the widths of the signals connected to it. Another method of specifying a "plumbing" body is the presence of the BODY\_TYPE="PLUMBING" body property. A "plumbing" body can not contain any primitives.

The designer may create "plumbing" bodies that follow design conventions already being used. In this manner, SCALD system drawings can be customized

# 3.2 BODIES IN THE STANDARD LIBRARY

The bodies in the following sections are included in the Standard Library; for additional information, see the Library Reference Manual.

### MERGERS

Mergers are used to combine several signals into one signal. The result of merging several signals is a single signal that is the concatenation of the input signals. An equivalent signal can be created by explicitly specifying the concatenation of the input signals. For instance, the signals A, B, and C can be merged together to form the signal A:B:C with a merger. The output signal is equivalent to A:B:C. If the output signal were named A:B:C, the merger would not be needed. The merger provides a graphical representation for combining signals. For a more detailed explanation, see under Plumbing Bodies below.

### DEMERGERS

Demergers are simply mergers turned around. The input signals are now output signals, and the output signal is now the input signal. A demerger is used to separate a signal into several pieces. In fact, a demerger is exactly the same as a merger. Its use determines its meaning; that is, if a merger is used to combine signals, it is a merger; but if it is used to separate signals, it is a demerger. For a more detailed explanation, see under Plumbing Bodies below.

# NOT

The NOT body is used to change the logic convention of a signal. If a signal is asserted low, it is considered to be a negative logic signal. If a signal is asserted high, it is considered to be a positive logic signal. The NOT body is used to change the logic convention of a signal without introducing an actual logical inversion. That is, the state of the signal is not changed, it is just considered to be of the opposite logic convention. The consistent use of logic

3/10/86

Special SCALD Bodies

conventions makes designs easier to read and understand. The NOT body is used as an escape in those cases where strict adherence to a logic convention is not possible. The NOT body is a notational assistance and does not affect the physical implementation of the circuit. The NOT body must be used if bubble checking is to be performed.

### SLASH

A SLASH body performs two useful functions. First, it is used to document the widths of signals. Normally, a signal's width is apparent from its bit subscript, but occasionally the signal name is not present or visible where the signal is used. In these cases, it may not be clear what the signal's width is. The SLASH body is used to remind the designer. The Compiler always checks the signal's actual width with that specified on the SLASH body.

The second use of the SLASH body is to specify signal widths that are not otherwise specified. NC and unnamed signals, for instance, have no particular widths. The Compiler assigns widths to these signals, but, when the Compiler is unable to determine the width, the SLASH body can be used to specify it.

### SYNONYM

The SYNONYM body is used to tell the Compiler that two signals with different names are to be considered the same signal. For more information, see below under Signal Synonyms.

# TAP

The TAP body is used to select a portion of a signal while leaving the original signal unchanged. In this fashion it is different from a merger which splits a signal into several pieces. A tap can be used to select either the most significant or least significant portion of the input signal. The number of bits selected by the tap is specified with a SIZE property attached to the TAP body.

# SECTION 4 PROPERTIES IN THE SCALD LANGUAGE

This section introduces the concept of a property. Properties serve important and varied functions in the SCALD system. They are used to convey a wide range of information about the design and to control analysis processes. A property is a name/value pair that can be attached to certain objects in a design to convey almost any information. A number of predefined properties are used by the SCALDsystem to record information needed by the Timing Verifier, the Simulator, and the Packager. Other properties can be defined by the user to convey information to design programs, or to be passed through the SCALD-system to other systems (such as simulators, physical design systems, etc.).

Properties also provide a mechanism for adding physical information to drawings (which represent only a logical design), that can be passed on to the Packager and other physical design systems. With the ability to define and use properties, the designer can customize the SCALD system to fit into an existing or evolving CAD system.

A property consists of a name by which the property is known (property name) and an associated value (property value). Properties can be attached to certain objects on any drawing in the Graphics Editor. Property name/value pairs can be attached to bodies, signals, and pins. Properties can also be attached to an entire drawing by attaching them to a DEFINE body or a DRAWING body on that drawing.

Properties are then passed along to the Compiler in the editor output files. From the Compiler they are passed to all the other SCALD system programs (as well as programs written by the user) in the Compiler expansion output file. (Some properties can be filtered out by the Compiler to reduce file size.)

# 4.1 WHAT IS A PROPERTY?

A property is a name/value pair assigned to a particular object. The property name is an identifier, that is,

a string of not more than 16 characters that includes letters, digits, and '\_'(underscores) and starts with a letter.

Some examples of property names are:

SIZE TIMES MY\_PROP\_NAME THE\_40TH\_NAME SATURD AY1027 COST\_OF\_PART PIN\_NUMBER PART\_NAME

Notice that the underscore is used instead of a space. Spaces are not allowed in property names because a space delimits a property name from a property value.

Many properties have been defined by Valid for use in the SCALD system and have a specific meaning. Each of these are described, one to a page, in alphabetical order, later in this section.

A property value is associated with each property name. The property value is a string of up to 255 printing characters. Property values can be empty. Property values should be enclosed in single quotes when a property is added to a signal name (and text macros are not used). Property values need no quotes when a property is added using the PROPERTY command.

Here are some representative property values:

1 25oct82 10:31:46.03 (SIZE + 4) / 5 + 35 MOD A This is a long property value Property value with special chars !@ #\$%\*()^}{[] > < A property always consists of the property name and its value.

### 4.2 SPECIFYING PROPERTIES

Properties are specified with the Graphics Editor. The Graphics Editor ignores double quotes ("), it does not pass them on to the Compiler. Where a double quote is needed, use two single quotes ('') instead.

There are basically two ways of adding properties to drawings; using the PROPERTY command or including the property in a signal name. The two methods are used in different situations. Body properties are always added using the PROPERTY command. Signal properties are usually included in a signal name, but can also be added to the signal using the PROPERTY command. Pin properties are usually included in the pin name, but can also be added using the PROPERTY command. A pin property can also be inherited by a pin from a signal connected to the pin.

The meaning of the properties is the same regardless of the method used to assign them.

### THE PROPERTY COMMAND

The PROPERTY command of the Graphics Editor is used to specify a property name and its value and to attach the property to an object in the drawing. Properties are attached to the origin of an object. Any property value can be entered, except one with leading spaces. Double quotes are ignored by GED.

A property specification appears as

name value

where *name* is the property name and *value* is the property value. When displayed on the drawing, the property appears as:

NAME=VALUE

# PROPERTIES WITHIN SIGNALS

The other method of specifying properties is to include them as part of signal names. Commonly used properties can be added to a signal name using predefined text macros. Other properties included in a signal name take the form:

\NAME='VALUE'

For more information on the exact syntax used for adding properties to signal names, see below under Signal Properties.

The user can define additional text macros to support other properties. See "Text Macro Facility," in Section 5.

# SIGNAL PROPERTIES

The syntax for a property in a signal name is

\NAME='VALUE'

where the backslash  $(\)$  denotes the start of a property. Note that the property value appears in single quotes. This is recommended to unambiguously identify the beginning and end of the property value. Do not use double quotes (GED restriction).

Text macros are used to make it easier to specify properties. For example, the property "SCOPE" specifies the scope of a signal. It can assume the values "LOCAL," "GLOBAL," or "INTERFACE." Instead of adding the property SCOPE='LOCAL' or SCOPE='GLOBAL' to a signal, text macros for each are predefined for the Compiler in a file. These text macros are:

> L = 'SCOPE="LOCAL"'G = 'SCOPE="GLOBAL"'I = 'SCOPE="INTERFACE"'

When used in a signal name, the text macros are expanded by the Compiler into the proper form. For example

CLOCK \* \I

is expanded to:

CLOCK \* \SCOPE="INTERFACE"

To define additional global text macros for property name/value pairs, see section 5. The designer may define additional text macros with a DEFINE body in a drawing (see section 5).

Text macro parameters can be used to create property name/value pairs whose values need to be assigned on an instance by instance basis. For example, assume a property called LENGTH which can take on many values. A global text macro definition of the property might be

LEN = 'LENGTH = "%1"

where %1 refers to the first text macro parameter (text macro parameters are separated by spaces). When used in a signal name, the value of the property is placed after the text macro as follows

LEN 2

which expands to:

$\LENGTH=2$

This is the manner in which Timing Verifier properties are supported. For example, a wire delay may be added to a wire as follows

SIGNAL\* \WD 2.0-5.6

which is equivalent to:

#### SIGNAL\* \WIRE\_DELAY='2.0-5.6'

This text macro is globally defined as follows

$WD = 'WIRE_DELAY = "\%1"'$

where %1 references the first parameter of the text macro.

Other standard signal name properties are supported with built-in, reserved text macros. See the text macro section for a complete description.

For a complete description of the syntax for a SCALD signal name, see section 2, Signal Naming and Syntax.

Properties on signal names are passed through the Compiler to the output expansion file. In this way, properties are available to the Packager, the Timing Verifier, the Logic Simulator, and any user provided programs.

Properties are associated with specific bits of the signal. Different bits of a multi-bit signal can have different properties.

### 4.3 PIN PROPERTIES

Properties can be attached to pins three ways. They may be attached by adding the property to the pin with the PRO-PERTY command of the Graphics Editor. They may be included as properties of the pin name for the pin. They may also be inherited from signals connected to the pin.

### ADDING PIN PROPERTIES WITH THE PROPERTY COMMAND

PIN properties can be added to pins of bodies with the Graphics Editor PROPERTY command. The user points to the pin and specifies the property name and value to be assigned to the pin. Default properties may be attached to pins in the body drawing. The most common example of a default pin property is PIN\_NAME which is used to specify the logical name of the pin.

### ADDING PIN PROPERTIES AS PART OF THE PIN NAME

Each pin of a body has a pin name which serves to identify that pin. A pin name can have signal properties just like any other signal; they are included in the signal name in exactly the same manner. Some examples of pin names with pin properties:

> DATA INPUT \NAC CLOCK\* \PIN\_NUMBER='2' OUTPUT \OUTPUT\_TYPE='(TS,TS)'

### PIN PROPERTIES INHERITED FROM SIGNALS

Properties can be inherited from the signals that are connected to them. The most common example of a property of this type is WIRE\_DELAY. This property is assigned as a signal property, but since it has a special inheritance attribute (see the section on property attributes), it is copied from the signal to the pin to which the signal is attached.

### 4.4 PROPERTY ATTRIBUTES

A property attribute is used to control property processing within the Compiler. Every property is given some attributes by default, and the user can modify or add to these. Attributes are assigned in property attributes files read by the Compiler. There is a Valid supplied attributes file that is always read by the Compiler to assign attributes to

standard SCALD properties. The user may supply an additional property attributes file specified by the PROPERTY\_FILE directive.

The attributes file contains a list of property names and associated attributes. The file has the following form

FILE\_TYPE = ATTRIBUTES; property name : attribute specification ;

END.

where property name is the name of the property, and attribute specification is a list of attributes for the property.

The attributes that can be assigned to properties are:

| parameter | $\rightarrow$ | used on body properties only       |

|-----------|---------------|------------------------------------|

| inherit   |               | controls property inheritance      |

| permit    | $\rightarrow$ | permission for property attachment |

| filter    | $\rightarrow$ | removes property from output files |

These are described in the following sections.

# PARAMETER ATTRIBUTE

The PARAMETER attribute is used to make the name and value of a body property known within the drawing corresponding to the body. Normally, body properties are attached to bodies and pass through the Compiler to other analysis tools. For example, the LOCATION property is used to specify the LOCATION name for a physical component. This property means nothing to the Compiler; it passes it through to the Packager, which uses it to guide its package allocation. SCALD Language

Some properties, however, are used to pass information into the drawing. The most common example of such a property is SIZE. This property is used to convey information about the number of bits the body represents. This information is needed by the drawing. To make it available, the SIZE property is given the PARAMETER attribute. This causes two things to happen. First, the name of the property, and its value, are available in the drawing. It can be used as though it were a text macro. Second, any text macros within the property value are expanded.

For example, assume the WIDTH=45\*X property is attached to the ELAN body. If the WIDTH property has the PARAMETER attribute, its value will be known within the ELAN.LOGIC drawing. It can be used, for example, in signal names:

#### SIGNAL\_WITHIN\_ELAN <WID TH-1..0>

Further, the value of the WIDTH property is expanded by the Compiler. Its value is '45\*X' where 'X' is some text macro (assume, for the purpose of example, that X=2). The WIDTH property value is expanded to be: "45\*2." The signal name shown above then becomes:

#### SIGNAL\_WITHIN\_ELAN <45\*2-1..0>

If the WIDTH property does not have the PARAMETER attribute, the Compiler will generate an error since WIDTH will be undefined.

Some properties that are to be parameters are used to pass information about a primitive component through to some analysis tool. For example, the TIMES property is attached to components to specify to the Packager that additional versions of the component should be generated. It may be necessary for the value of the TIMES property to be related to other design information; for example, the SIZE of the component:

TIMES=SIZE\*2

3/10/86

If the TIMES property has the PARAMETER attribute, the Compiler substitutes the value of the SIZE parameter (the SIZE property has the PARAMETER attribute by default). If SIZE=1, the TIMES property value becomes "1\*2." The Packager, on the other hand, is expecting the TIMES property to have an integer value; it won't accept "2\*1." The Compiler can be told to completely evaluate the property's value by giving it the PARAMETER(INTEGER) attribute. The Compiler expands text macros within the property value and evaluates the property value as an integer expression (an error is generated if the property value is a malformed integer expression). The TIMES property shown above is then output with the value "2." In all other respects, the PARAMETER(INTEGER) attribute behaves just like the PARAMETER attribute.

A property can be given the PARAMETER attribute in one of two ways: the property can be specified as a PARAME-TER when creating the body in the Graphics Editor, or the property can be given the PARAMETER attribute in the property attributes file. To give the property the PARAM-ETER attribute in a body drawing, append a \PARAME-TER to the end of the property value. For example, the following property (attached to a body) has the PARAME-TER attribute:

#### ELAN="value for ELAN\PARAMETER"

The property ELAN has the PARAMETER attribute only for this particular instance. If the property ELAN appears anywhere else (and does not have the \PARAMETER appended), it is not a PARAMETER. The second way to give a property the PARAMETER attribute is with the property attributes file. When given the attribute via the attributes file, the property has that attribute everywhere it is used (regardless of whether it has the \PARAMETER appended or not).

#### INHERIT ATTRIBUTE

A property may appear on an object automatically when objects become related or attached in some manner. This copying of properties from one object to another is called property inheritance. Inheritance can be controlled with the INHERIT attribute. Inheritance behavior for a particular property can be controlled for three independent contexts: BOD Ys (DRAWINGs), SIGNALs, and PINs. These will be discussed separately.

#### Body Property Inheritance

Inheritance of body properties is controlled with the INHERIT(BODY) attribute. When a property is attached to a body, it may be inherited down the hierarchy to appear on all of the bodies within the drawing corresponding to the body. For example, if the X property is attached to the ELAN body, and the X property has the INHERIT(BODY) attribute, every body within the ELAN.LOGIC drawing will have the X property. If the X property does not have the INHERIT(BODY) attribute, the X property only appears on the bodies to which it is attached (the ELAN body in this example).

Properties attached to the DRAWING body within the ELAN drawing will also inherit to every body within the drawing if the properties have the INHERIT(BODY) attribute. In this manner, properties attached to the body for ELAN and those attached DRAWING body within ELAN are processed in the same manner.

Care should be taken when using properties on bodies. If the properties all have the INHERIT(BODY) attribute (which all properties do by default), they all appear in the Compiler's output files. For example, if each drawing is given the property ENGINEER to specify the responsible engineer, and there are seven levels of hierarchy and five pages to every drawing, the primitives produced by the Compiler will each have 35 ENGINEER properties attached. This is probably not desirable. It can be corrected by removing the INHERIT(BODY) attribute from the property ENGINEER.

3/10/86

# Signal Property Inheritance

Inheritance of signal properties is controlled with the INHERIT(SIGNAL) attribute. When a property is attached to a signal, it may be inherited by other signals synonymed to it. For example, if the signal RESET has the X property and RESET is synonymed to the MCLEAR signal, the MCLEAR signal will get the X property if the X property has the INHERIT(SIGNAL) attribute. Since MERGERs, NOTs, and all other plumbing bodies are implemented with synonyms, this attribute allows properties to move along a net within a drawing.

Properties with the INHERIT(SIGNAL) attribute are considered to be properties of the net (since all of the signal names for the net will have the properties). These properties are output by the Compiler as properties of the net and are available for processing by the Packager, DIAL, etc. Properties without the INHERIT(SIGNAL) attribute are properties of a particular signal and not the entire net. These properties are not output from the Compiler. SCOPE is one such property. It is a property of a particular signal and should not be inherited by the entire net. In general, the user will never create a signal property without the INHERIT(SIGNAL) attribute.

All properties are given the INHERIT(SIGNAL) attribute by default.

# Pin Property Inheritance

Inheritance of pin properties is controlled with the INHERIT(PIN) attribute. When a property is attached to a pin, it becomes a property of that pin. If it has the INHERIT(PIN) attribute, it inherits to the interface signal for the pin. Once on a signal, an INHERIT(PIN) property copied other pins. property with is to Α the INHERIT(PIN) attribute is automatically given the INHERIT(SIGNAL) attribute.

For example, suppose the X property is attached to the A pin of the ELAN body. Within the ELAN.LOGIC drawing, the signal A\I appears and connects to the B pin of a EREG

SCALD Language

body. If the X property has the INHERIT(PIN) attribute, it will first appear as a property of the A\I signal and finally a property of the B pin of the EREG body.

The WIRE\_DELAY property has the INHERIT(PIN) attribute by default (assigned in the system-wide property attributes file). When used as a signal property (with the WD text macro) as follows:

#### CLOCK \WD 5.0-6.0

It appears as a signal property, but is copied to each pin connected to the CLOCK signal. It is then available as a pin property and can inherit deeper into the hierarchy. Properties with the INHERIT(PIN) attribute are stripped from all signals at the end of processing.

Properties are not assigned the INHERIT(PIN) property by default; this attribute must be assigned in the property attributes file.

#### Summary of the INHERIT Attribute

The INHERIT attribute is assigned as INHERIT(PIN), INHERIT(SIGNAL), and/or INHERIT(BODY). If a property can be inherited by more than one object, a list can be used:

INHERIT(PIN, SIGNAL)

INHERIT() can be used to remove all inheritance attributes for a property.

#### PERMIT ATTRIBUTE

The PERMIT attribute is used to control the objects to which a property may be attached. It is possible to accidentally attach a property to the wrong object. If the property does not have permission to be attached to that object, an error is generated by the Compiler. Permission can be granted for a property to be attached to a BODY, PIN, or SIGNAL (WIRE) with the PERMIT(BODY), PERMIT(PIN), or PERMIT(SIGNAL) attributes.

3/10/86

The SIZE property, for example, has the PERMIT(BODY) attribute since it is an error for it to be attached to any other object. The SCOPE property has the PERMIT(SIGNAL) attribute. By default, a property has all three attributes.

If a property is to be given permission to be attached to more than one object, the PERMIT attribute can be specified with a list:

PERMIT(PIN, SIGNAL)

Permission for a property to be attached to all objects can be removed with PERMIT(). Such a property cannot be attached to any object and is, therefore, useless.

#### FILTER ATTRIBUTE

The FILTER attribute prevents a property from appearing in the Compiler's output files. For example, the LAST\_MODIFIED property, which specifies the date on which the drawing page was last written, is filtered from the output by default since it is normally of no interest to analysis programs. The intent of supporting filtering is to reduce the size of design files and to reduce superfluous properties.

The FILTER attribute is assigned in the property attributes file. The user can override this attribute with the PASS\_PROPERTY directive (which causes the property to be output regardless of its attributes). The FILTER\_PROPERTY directive can be used to filter properties from the output even if they do not have the FILTER attribute.

#### USER PROPERTY ATTRIBUTE FILE

The user can supply a property attributes file by using the PROPERTY\_FILE directive in the Compiler command file. The attributes assigned in the user attribute file override the attributes assigned in the system-wide attributes file. Care should be taken to not override important attributes.

The only safe attribute is the FILTER attribute. All other attributes should be left unchanged; they are assigned as required for the SCALD system.

# DEFAULT PROPERTY ATTRIBUTES

The default attributes for a property are:

PERMIT(SIGNAL,PIN,BODY),INHERIT(SIGNAL,BODY);

These may be changed in the property attributes file. The following SCALD properties have attributes assigned (as shown) within the Compiler and cannot be changed by the user (if the property is normally used via a text macro, the text macro name appears as a comment):

| GIRD .              |                                            |

|---------------------|--------------------------------------------|

| SIZE:               | inherit(),permit(body),parameter(integer); |

| TIMES:              | inherit(),permit(body),parameter(integer); |

| PATH:               | inherit(),permit(body);                    |

| <b>REPLICATION:</b> | inherit(),permit(signal); { \R }           |

| TITLE:              | inherit(),permit(body);                    |

| EXPR:               | inherit(),permit(body);                    |

| VERSION:            | inherit(),permit(body);                    |

| ABBREV:             | inherit(),permit(body);                    |

| SCOPE:              | inherit(),permit(signal); { \I \L \G }     |

| PART_NAME:          | inherit(),permit(body);                    |

| TERMINAL:           | inherit(),permit(body);                    |

| NEED S_NO_SIZE:     | inherit(),permit(body);                    |

| HAS_FIXED_SIZE:     | inherit(),permit(body);                    |

| WIRE_DELAY:         | inherit(pin),permit(pin, signal);          |

| NOWID TH:           | inherit(),permit(signal), { \NWC } filter; |

| NOASSERT:           | inherit(),permit(signal), { \NAC } filter; |

| BODY_TYPE:          | inherit(),permit(body);                    |

| X:                  | inherit(),filter;                          |

| X_FIRST:            | inherit(),filter;                          |

| X_STEP:             | inherit(),filter;                          |

|                     |                                            |

# AN EXAMPLE PROPERTY ATTRIBUTES FILE

The following example is used to demonstrate the syntax and form for the property attributes file. The list of standard property attributes in the previous section is also, except for FILE\_TYPE, a legal attributes file.

$FILE_TYPE = ATTRIBUTES;$

CLOCK: inherit(signal); STABLE: inherit(signal); WIRE\_DELAY: inherit(pin); EVAL: inherit(pin); CHIP\_DELAY: inherit(pin);

END.

# 4.5 DRAWING PROPERTIES

Properties may be "attached" to an entire drawing by attaching them to a special body called DRAWING. These properties are used to convey standard information about the drawing itself. The Compiler understands a few standard property names. These properties are:

| TITLE     | = title of the drawing.                |

|-----------|----------------------------------------|

| ABBREV    | = abbreviation for the drawing.        |

| EXPR      | = selection expression (if the drawing |

|           | has $>1$ version).                     |

| PART_NAME | = name of the primitive part if this   |

|           | is a primitive drawing.                |

| TERMINAL  | = indicates that the drawing is a      |

|           | terminal drawing in the expansion      |

|           | but is not a primitive component.      |

These properties are discussed in detail later in this section.

Properties of the DRAWING are inherited by all bodies within the drawing if they have the INHERIT(BODY) attribute. Drawing properties behave exactly as body properties except they are common for all instances of the drawing.

#### 4.6 TEXT MACRO PROCESSING WITHIN PROPERTIES

It is convenient to be able to use text macros within property values. One mechanism for doing this was described above in the section about the PARAMETER attribute. The problems with this method are:

- 1. It only works for body properties.

- 2. The syntax of the property value must be severely restricted so that the text macros can be found.

- 3. If there is any text in the property value that coincidentally matches a text macro name, it is expanded. This can result in very strange results.

To solve these problems, another mechanism has been implemented that is much more flexible. Each of the problems above has been addressed as follows:

- 1. It works for all properties regardless of where they are attached.

- 2. The content of the property value can be whatever is desired since the text macros are clearly identified and are separate from the rest of the text.

- 3. The user has explicit control over what is expanded and what is not.

To use this feature, the property cannot be given the PARAMETER attribute. That is, the PARAMETER attribute mechanism and this mechanism are mutually exclusive.

Text macros need to be identified within the property with the '%' character. This character serves to mark the presence of the text macro and to prevent confusion between text macros and normal text. For example:

$$PARMS = "W = \% WID TH, L = \% LENG TH"$$

Note the presence of the two text macros (WIDTH and LENGTH) in the property value. They are flagged with the '%' character. By coincidence, the character 'L' is also a text macro, defined to be SCOPE="LOCAL". Without the use of the '%', the property value would be turned into garbage.