# PRIMARY HARDWARE MAINTENANCE MANUAL

Volume 1

Valid Logic Systems Incorporated 1395 Charleston Road Mountain View, CA 94043 (415) 940-4000

900-00020 Rev A

## CPU BOARD USER'S MANUAL

## VED-041582-2 Revision 5-14-82 (LCW)

## 02 Aug 84

## Copyright 1984 Valid Logic Systems Incorporated

This document contains confidential proprietary information which is not to be disclosed to unauthorized persons without the written consent of an officer of Valid Logic Systems Incorporated.

The copyright notice appearing above is included to provide statutory protection in the event of unauthorized or unintentional public disclosure.

## TABLE OF CONTENTS

| Section |                          |                                                                                                                                                                   | Page                                         |

|---------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

|         |                          | IONS                                                                                                                                                              | iii<br>v                                     |

| 1       | INTRODU                  | CTION                                                                                                                                                             | 1 – 1                                        |

|         | 1.1<br>1.2               | Purpose of Manual                                                                                                                                                 | 1-1<br>1-1                                   |

| 2       | M68000LE                 | B MICROPROCESSOR                                                                                                                                                  | 2-1                                          |

|         | 2.1<br>2.2               | General Features                                                                                                                                                  | 2-1<br>2-2                                   |

| 3       | LOCAL CO                 | OMMANDS                                                                                                                                                           | 3-1                                          |

|         | 3.1<br>3.2<br>3.3        | Purpose                                                                                                                                                           | 3-1<br>3-1<br>3-1                            |

| 4       | MEMORY                   |                                                                                                                                                                   | 4-1                                          |

|         | 4.1<br>4.2<br>4.3<br>4.4 | General                                                                                                                                                           | 4-1<br>4-1<br>4-4<br>4-4                     |

| 5       | CPU INTI                 | ERRUPTS                                                                                                                                                           | 5-1                                          |

|         | 5.1<br>5.2               | Interrupts/CPU Interface                                                                                                                                          | 5-1<br>5-1                                   |

| 6       | 796 BUS                  |                                                                                                                                                                   | 6-1                                          |

|         | 6.1<br>6.2<br>6.3        | 796 Bus InterfaceNon-Standard Bits796 Bus Description6.3.1Master-Slave Relationship6.3.2Bus Clock6.3.3Signal Interface6.3.4Data Transfers, Inhibit, and Interrupt | 6-1<br>6-4<br>6-5<br>6-5<br>6-5              |

|         |                          | Operations                                                                                                                                                        | 6-10<br>6-10<br>6-11<br>6-11<br>6-11<br>6-13 |

|         |                          | 6.3.6Address Decoding6.3.7Data Bus Drivers and Receivers                                                                                                          | 6-13<br>6-13                                 |

i

# TABLE OF CONTENTS (Continued)

| Section |                                                                                                                    | Page                            |

|---------|--------------------------------------------------------------------------------------------------------------------|---------------------------------|

|         | 6.3.8 Control Signal Logic                                                                                         | 6-14<br>6-14                    |

| 7       | 796 BUS COMMANDS                                                                                                   | 7-1                             |

|         | 7.1796 Bus Commands/CPU Interface7.2796 Bus Commands Detailed Description                                          | 7-1<br>7-1                      |

| 8       | BUS ARBITER                                                                                                        | 8-1                             |

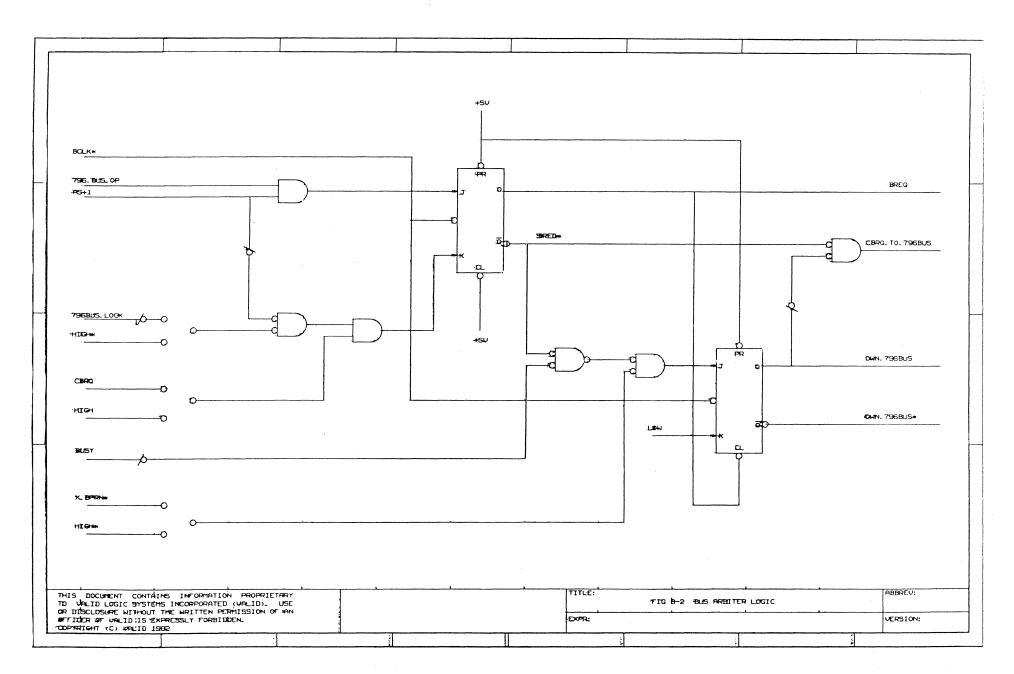

|         | 8.1Bus Arbiter/CPU Interface8.2Bus Arbiter Logic8.3Bus Arbiter Strapping                                           | 8-1<br>8-2<br>8-5               |

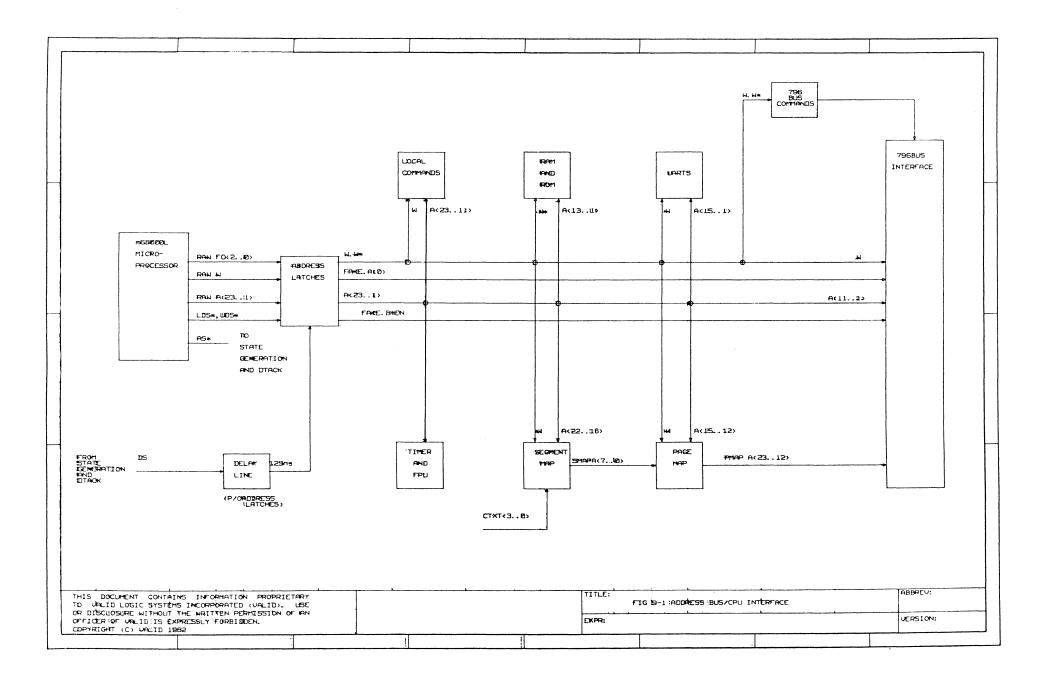

| 9       | CPU ADDRESSING                                                                                                     | 9–1                             |

|         | 9.1Address Bus/CPU Interface9.2Logical Address Space Structure9.2.1User Mode9.2.2Supervisor Mode9.3Local Resources | 9-1<br>9-3<br>9-3<br>9-3<br>9-5 |

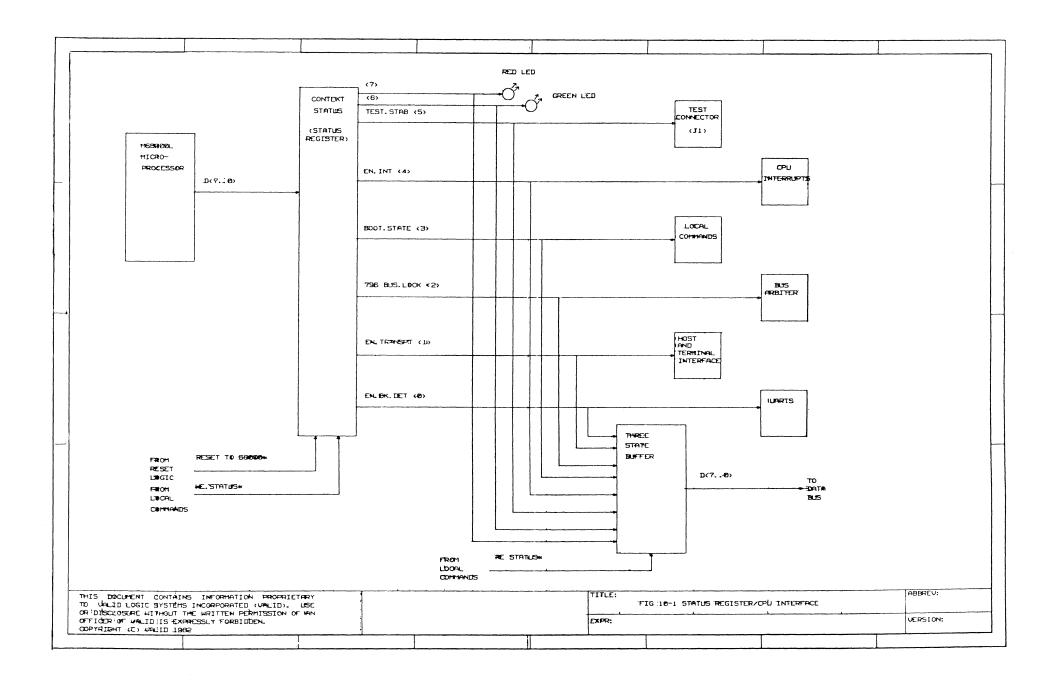

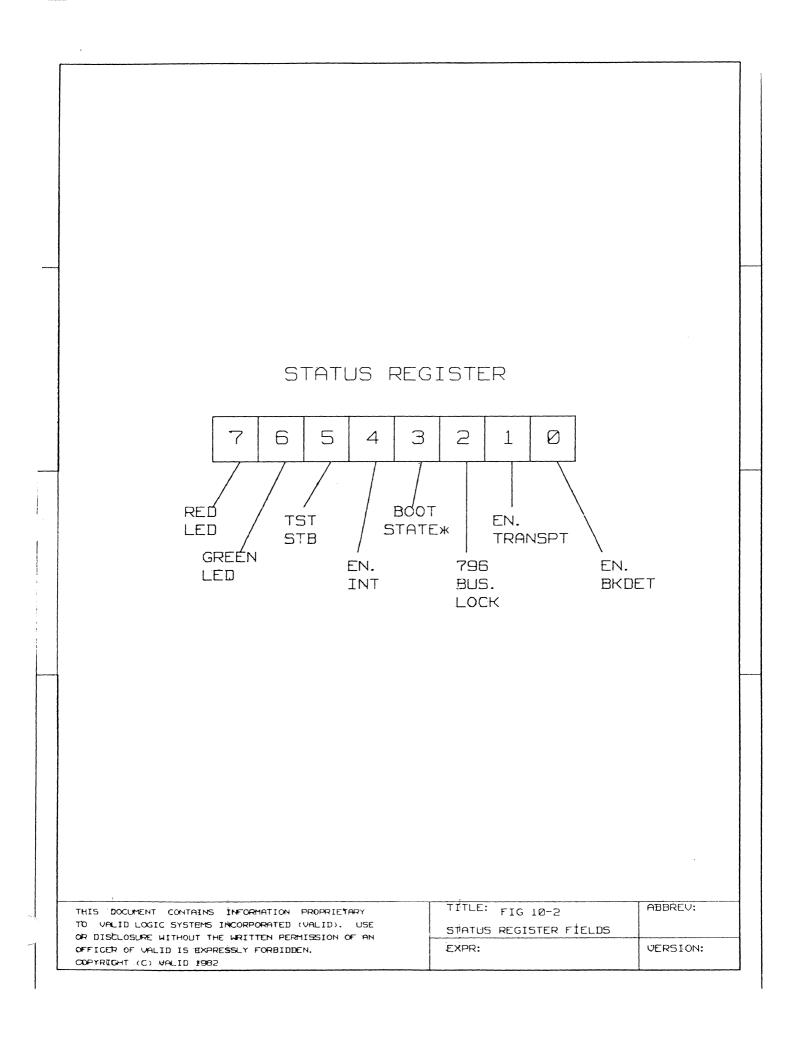

| 10      |                                                                                                                    | 10-1                            |

|         | 10.1Registers/CPU Interface10.2Status Register10.3Error Register10.4Context Register                               | 10-1<br>10-1<br>10-7<br>10-7    |

| 11      | ERRORS AND TIMEOUT                                                                                                 | 11-1                            |

|         | 11.1Errors and Timeout/CPU Interface11.2Errors and Timeout Detailed Operation                                      | 11-1<br>11-3                    |

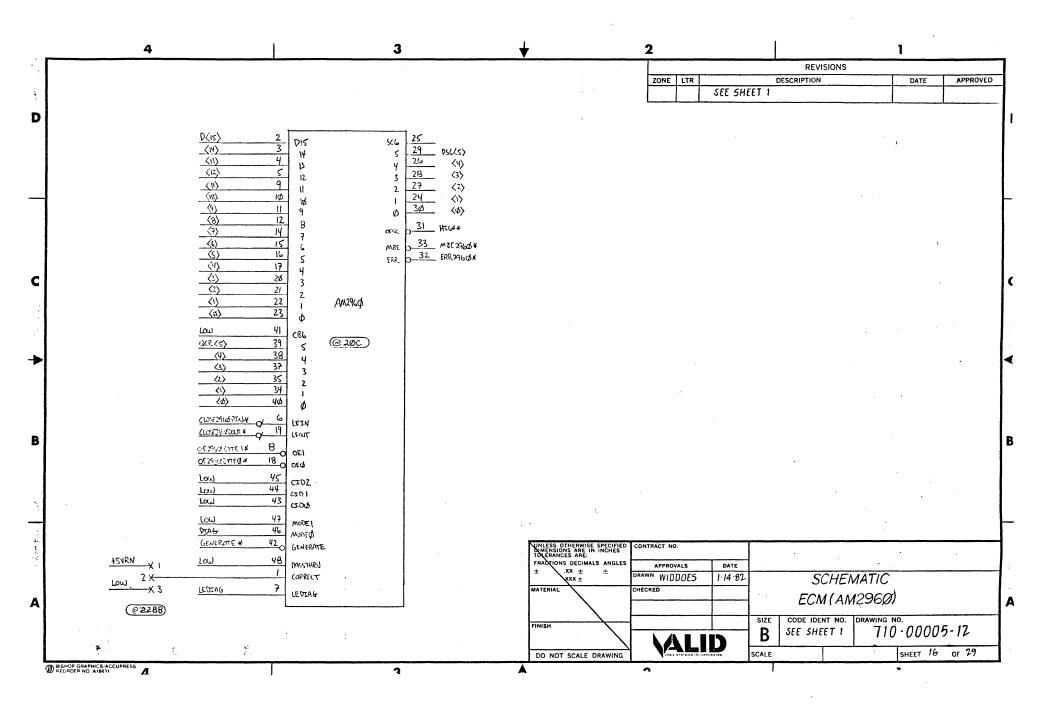

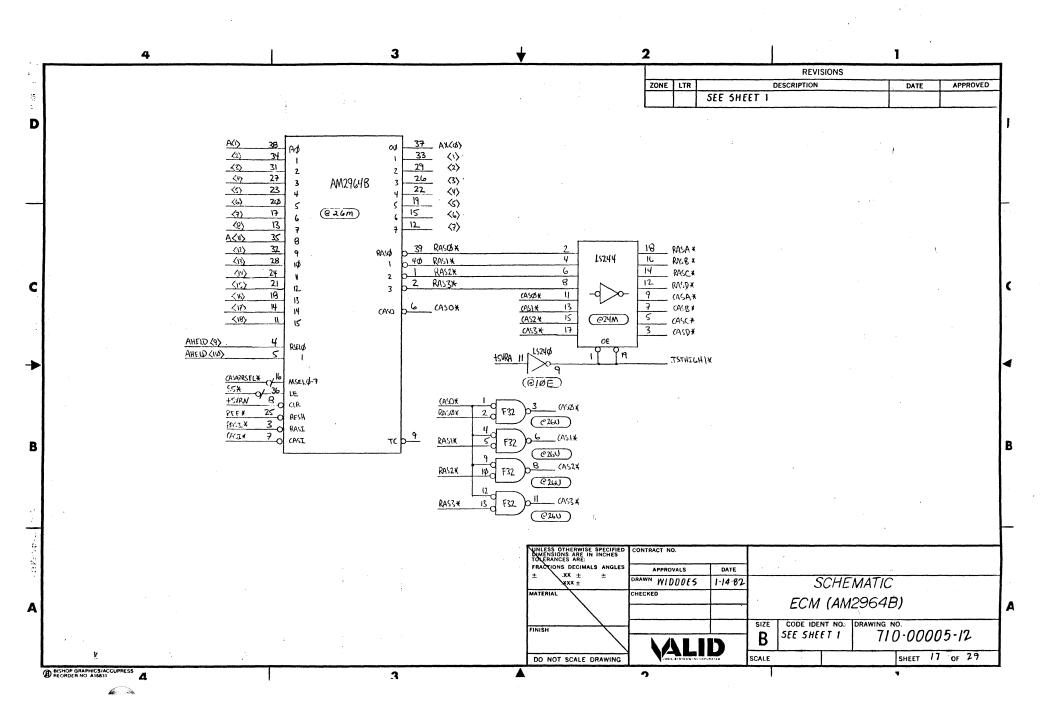

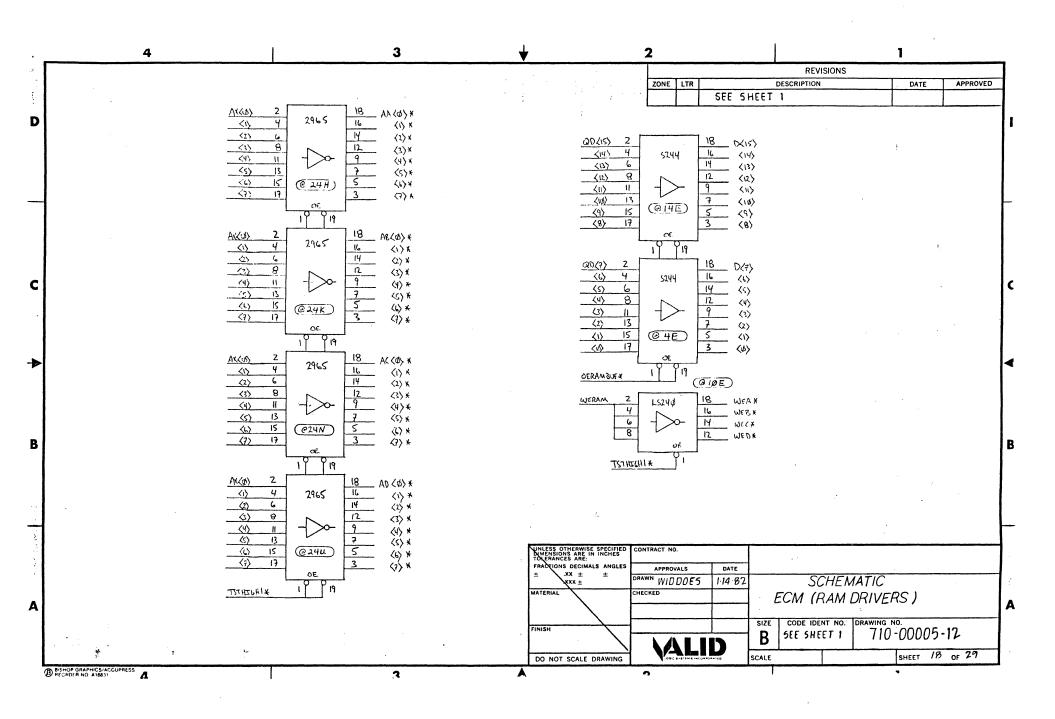

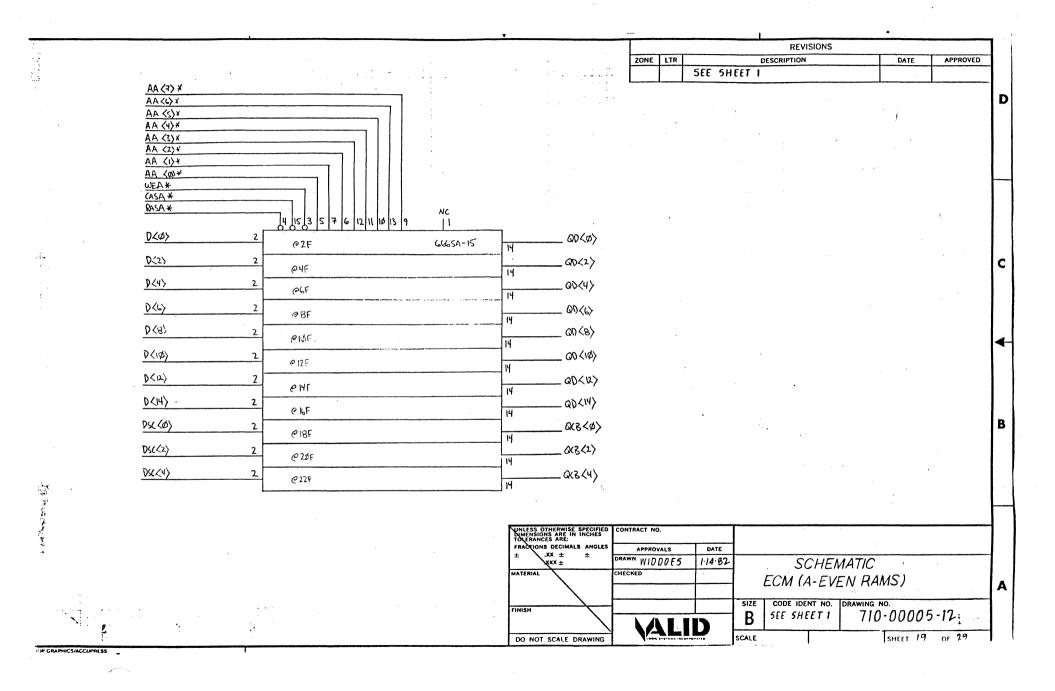

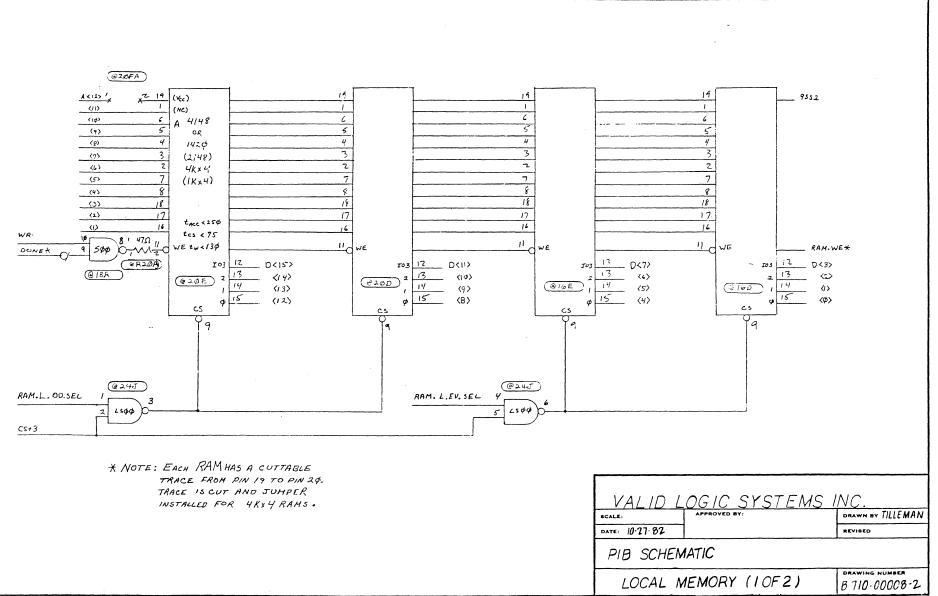

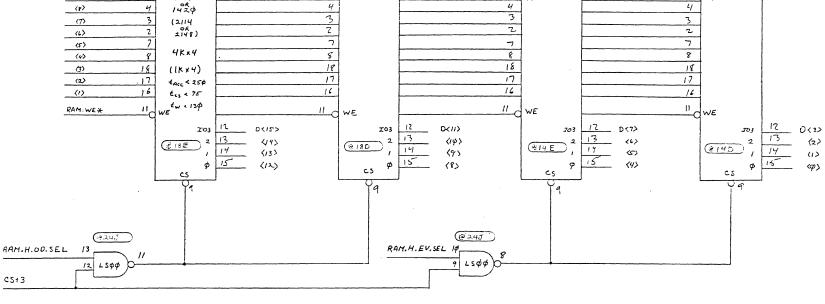

| 12      | RAM AND ROM MEMORIES                                                                                               | 12-1                            |

|         | 12.1Scratch Pad RAM/CPU Interface                                                                                  | 12-1<br>12-1                    |

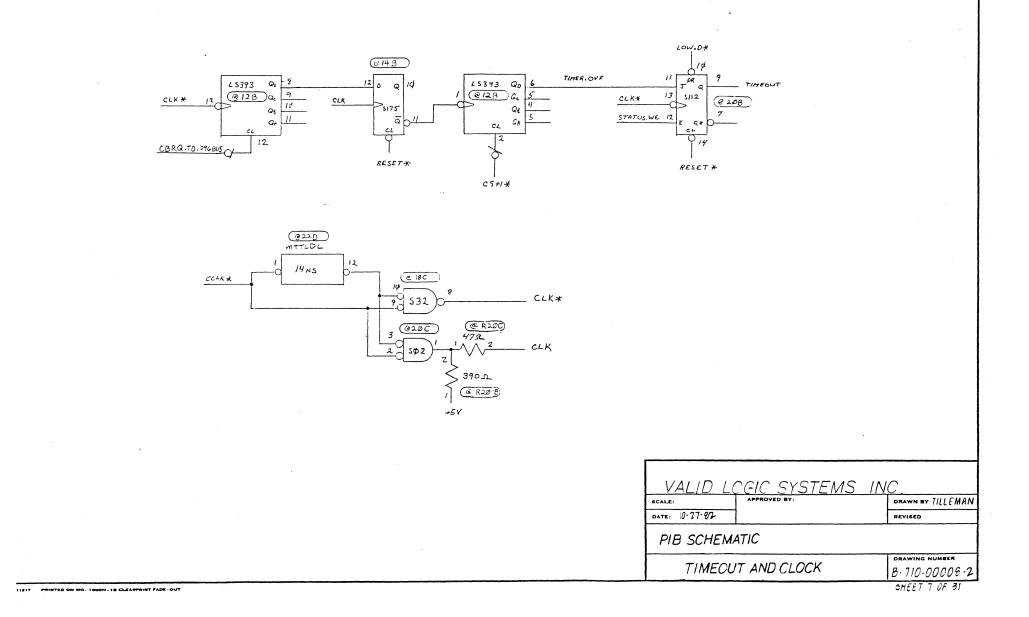

| 13      | INTERVAL TIMER                                                                                                     | 13-1                            |

|         | 13.1 Timer/CPU Interface                                                                                           | 13-1                            |

| 14      | STATE GENERATION AND DTACK                                                                                         | 14-1                            |

|         | 14.1State Generation/CPU Interface14.2State Signal Generation                                                      | 1 <b>4-1</b><br>14-3            |

s,

## TABLE OF CONTENTS (Continued)

| Section |                      |                                                                                                             | Page                                 |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------|--------------------------------------|

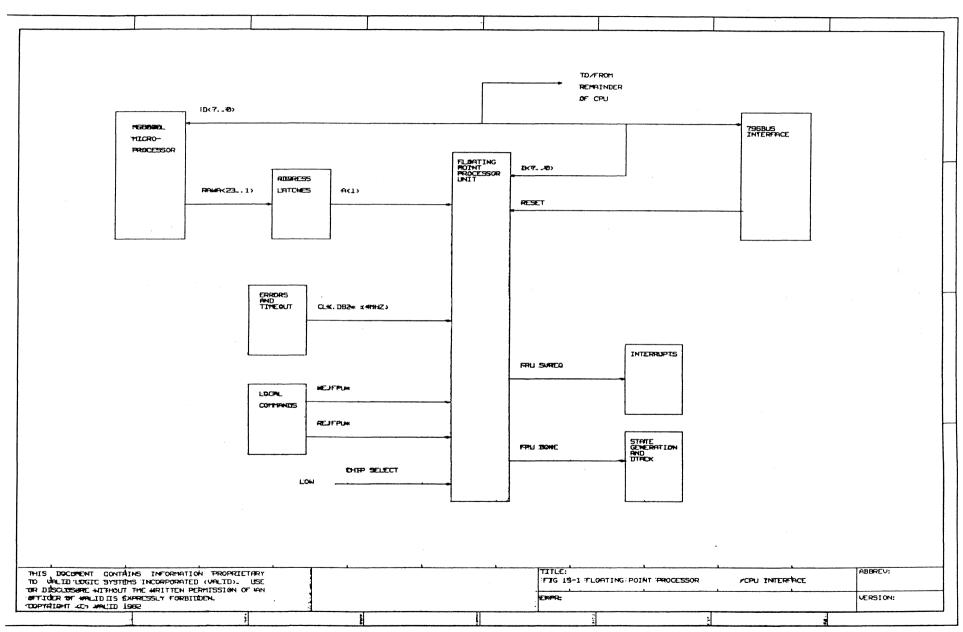

| 15      | FLOATIN              | IG PCINT PROCESSOR                                                                                          | 15-1                                 |

|         | 15.1                 | Floating Point Processor/CPU Interface                                                                      | 15-1                                 |

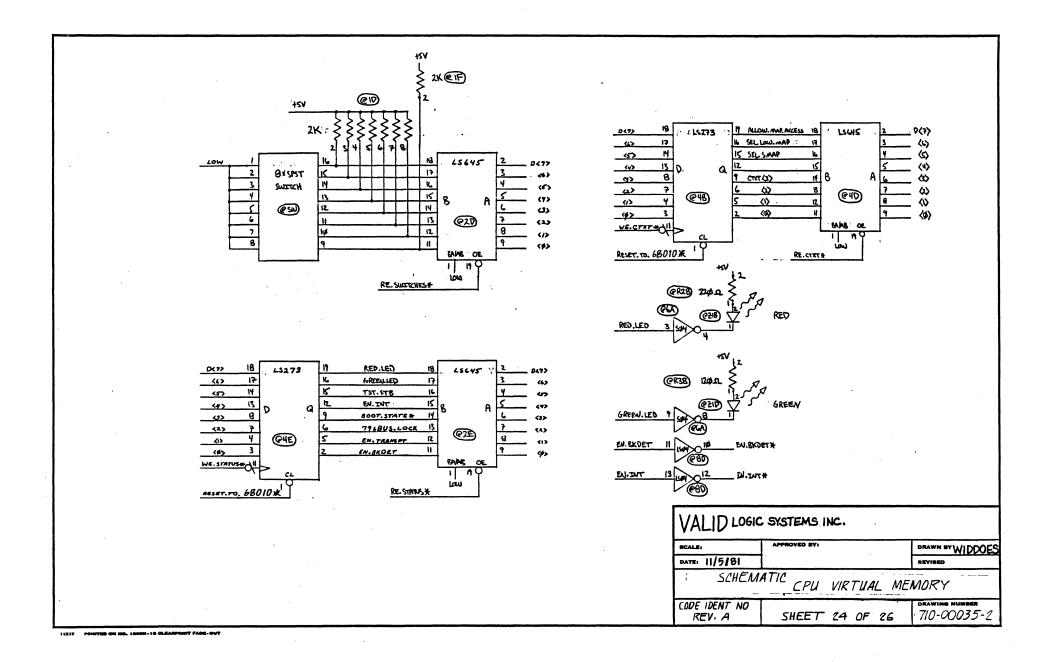

| 16      | SWITCHE              | S                                                                                                           | 16-1                                 |

|         | 16.1                 | Switches/CPU Interface                                                                                      | 16-1                                 |

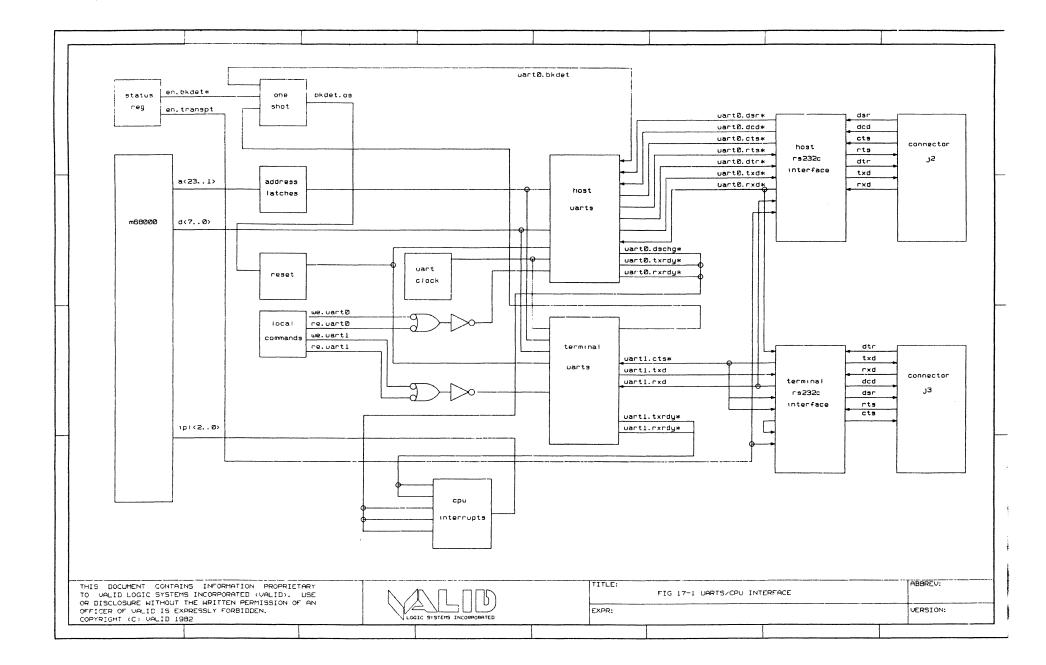

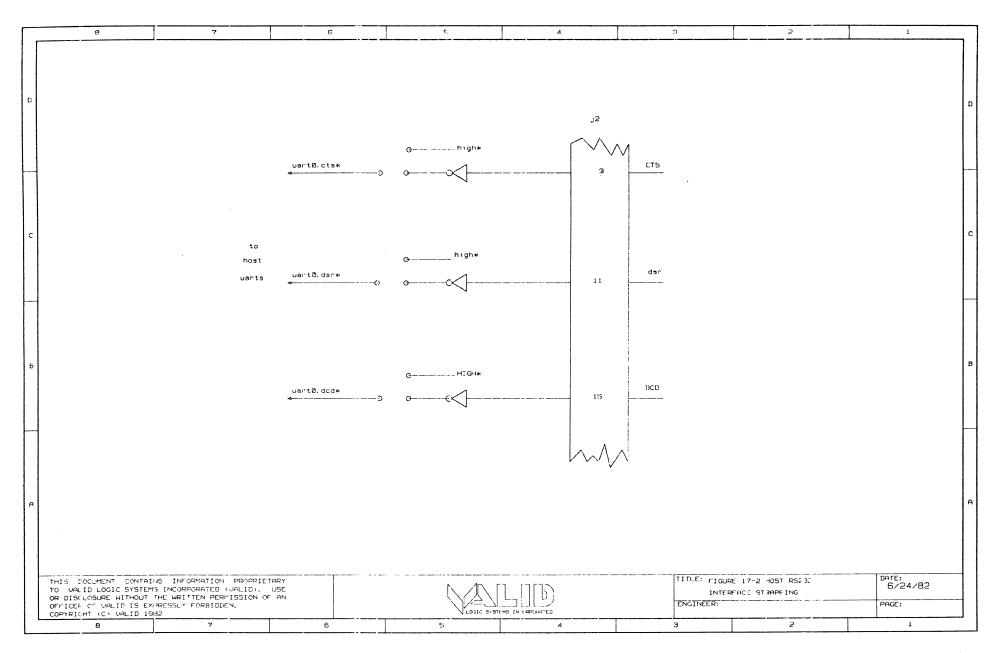

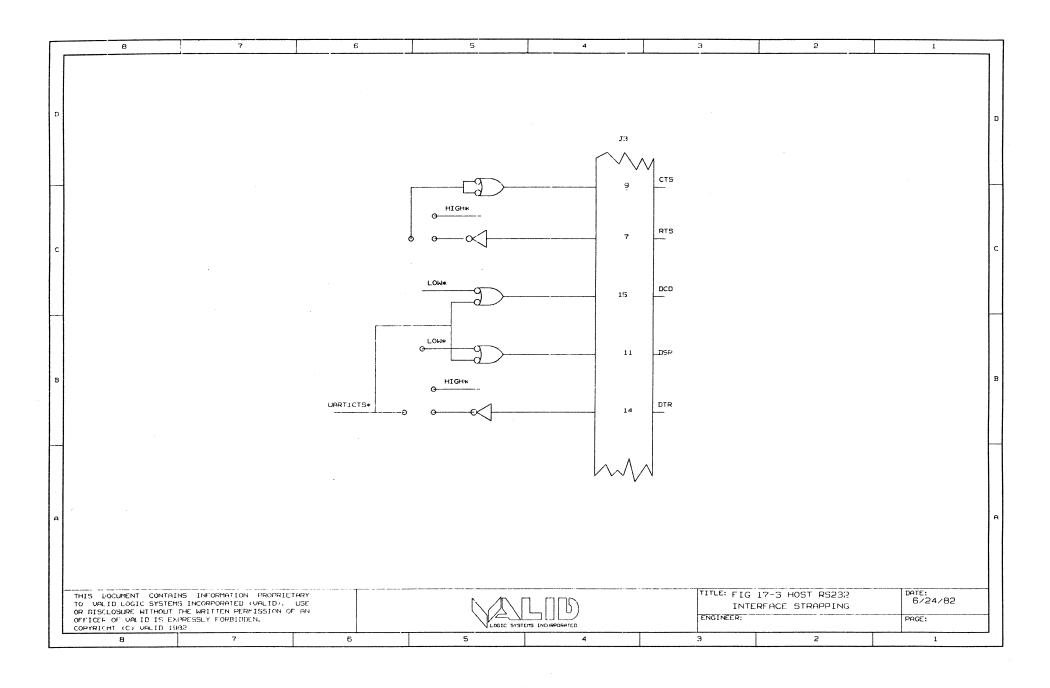

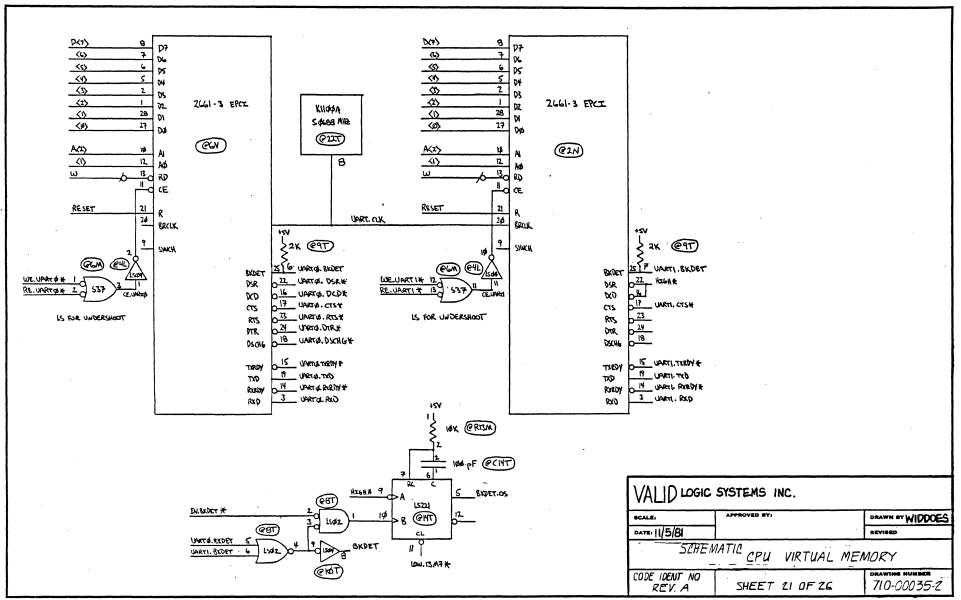

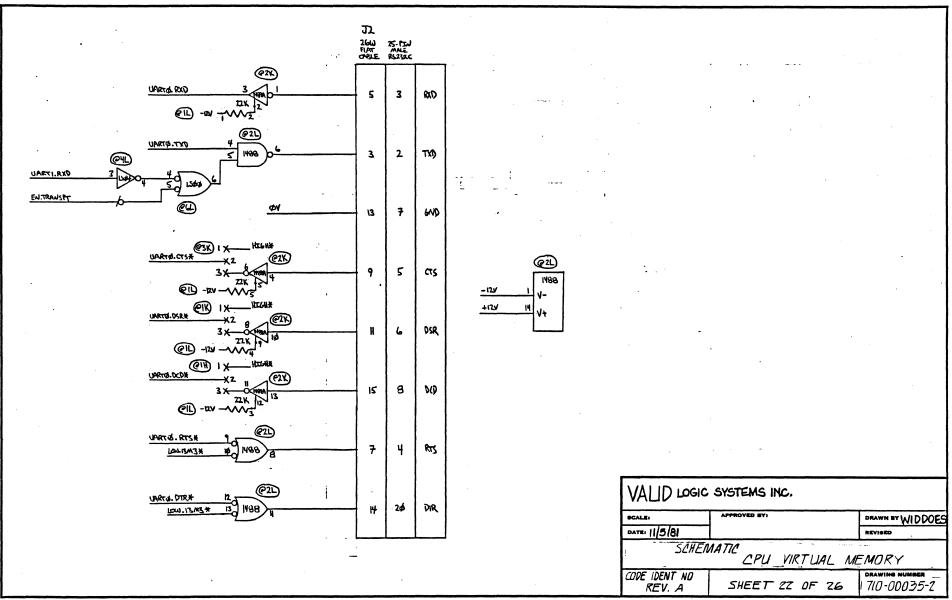

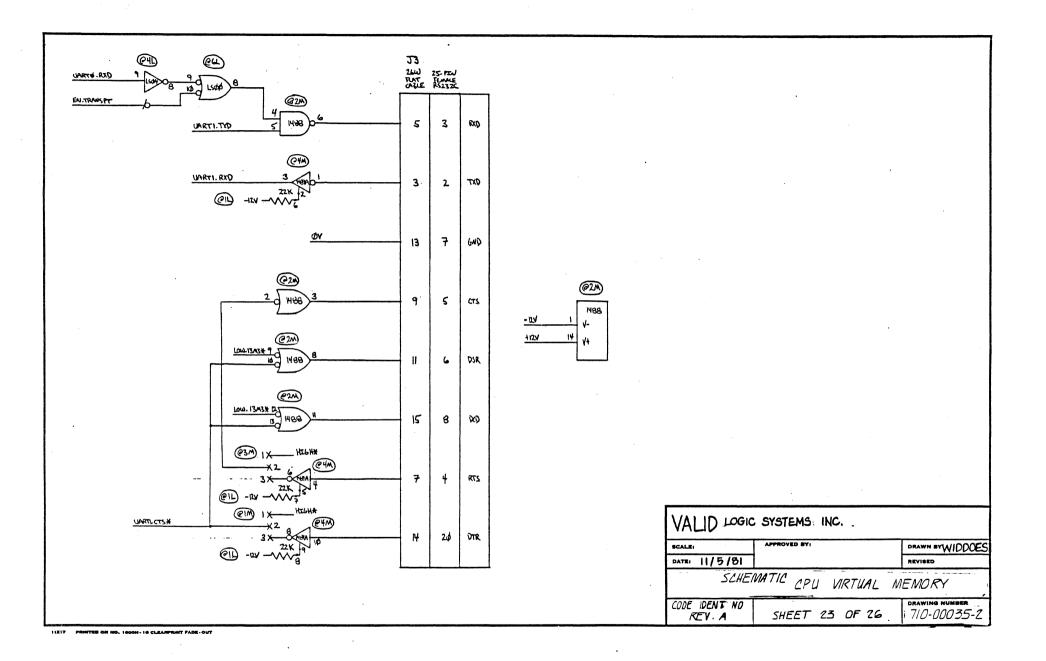

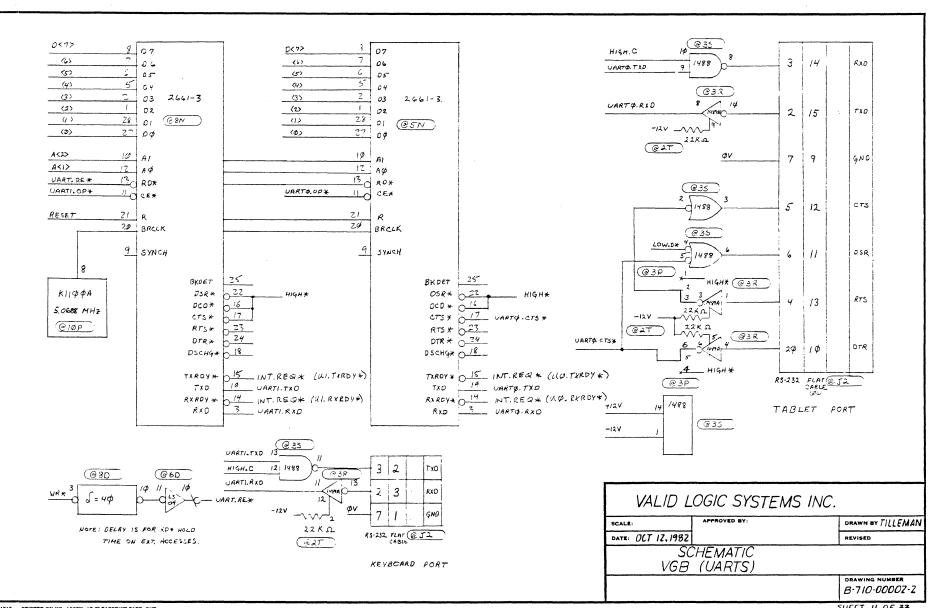

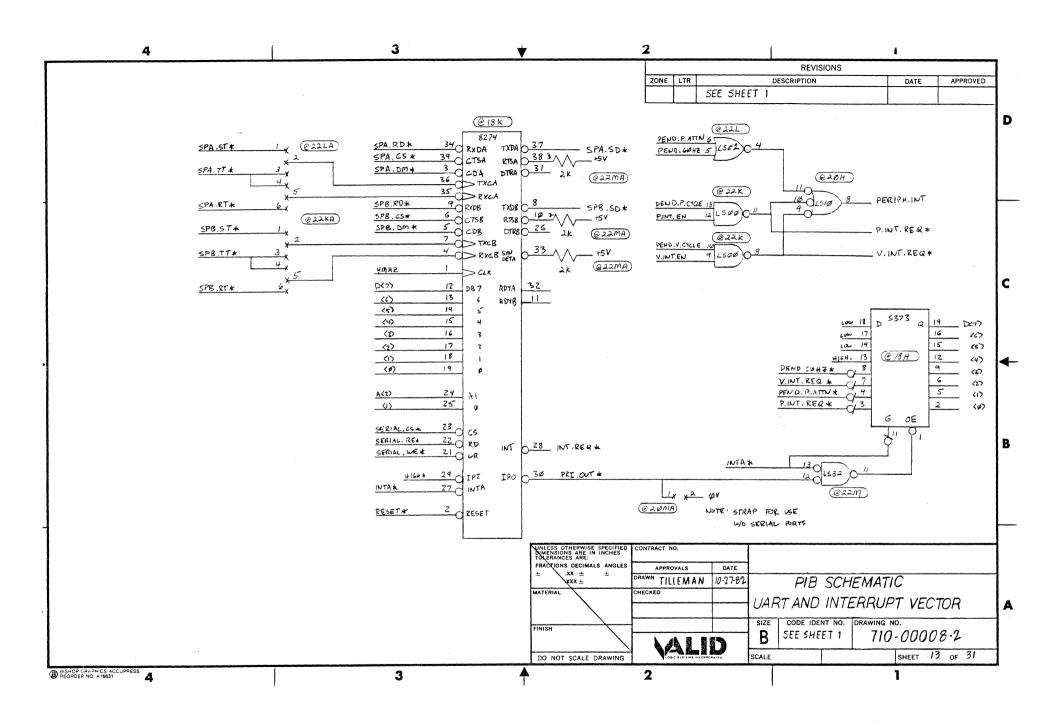

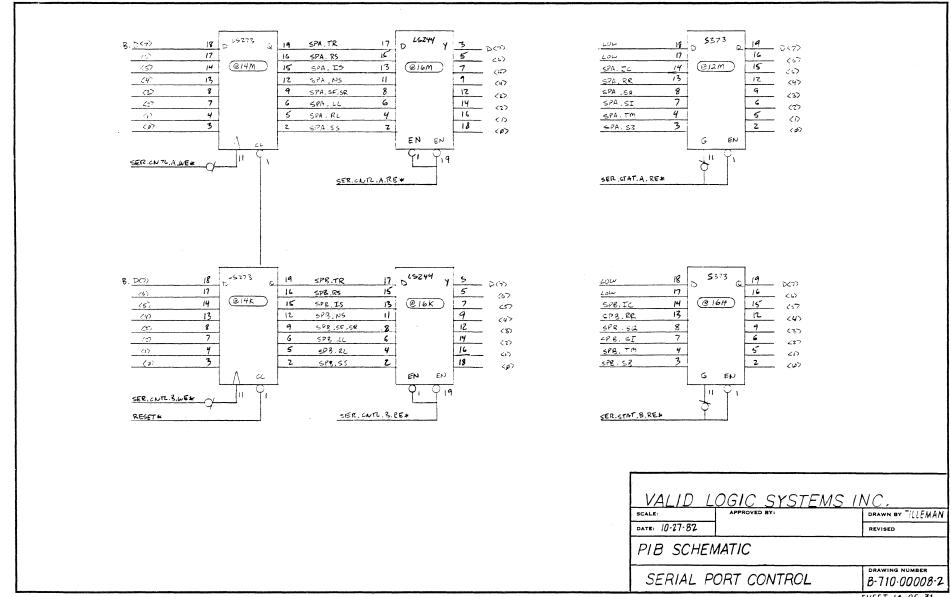

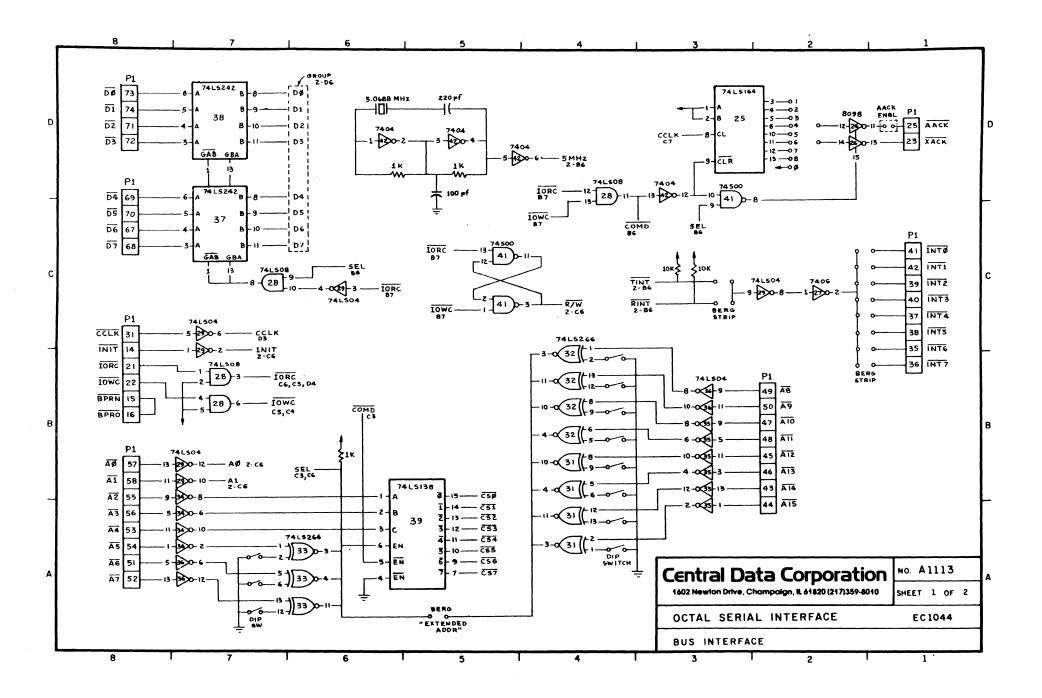

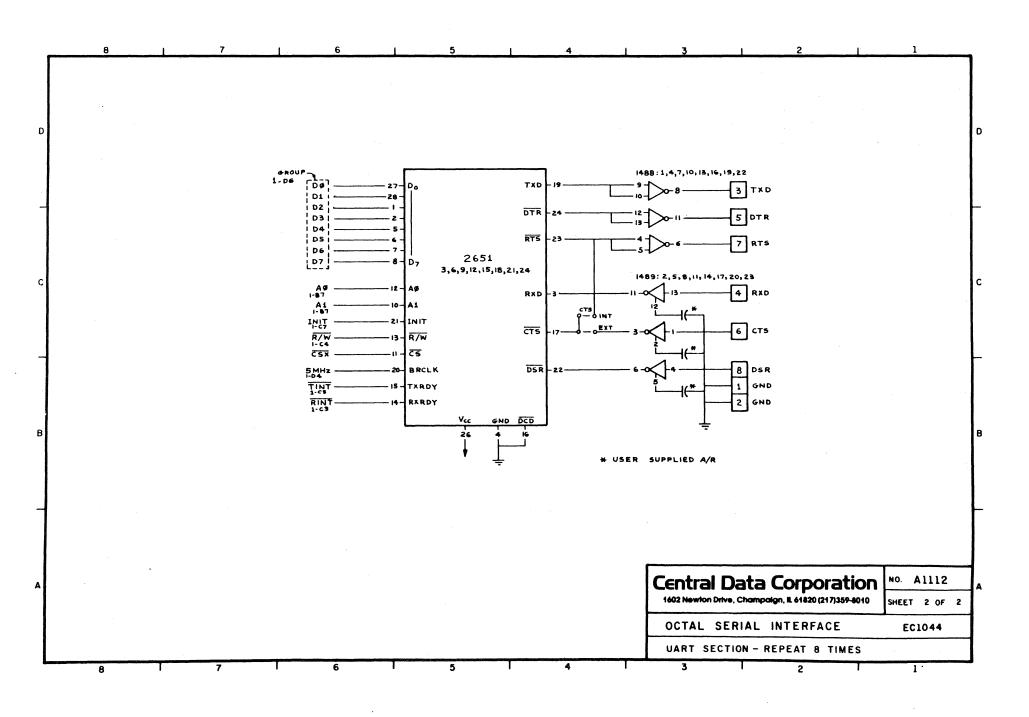

| 17      | UARTS                |                                                                                                             | 17-1                                 |

|         | 17.1<br>17.2<br>17.3 | UARTS/CPU Interface                                                                                         | 17-1<br>17-1<br>17-3                 |

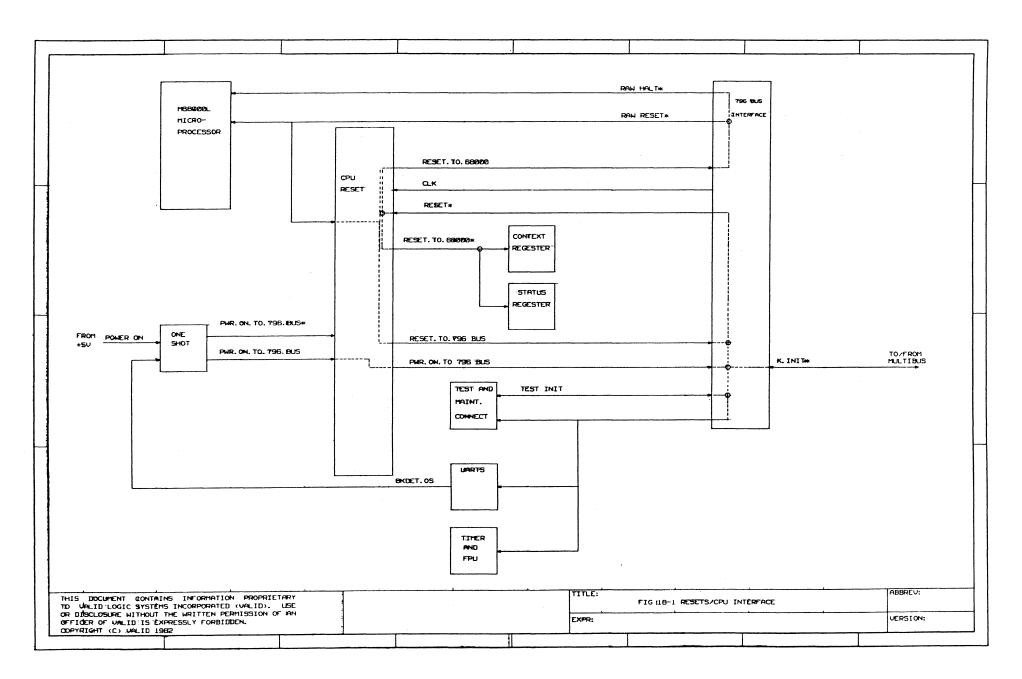

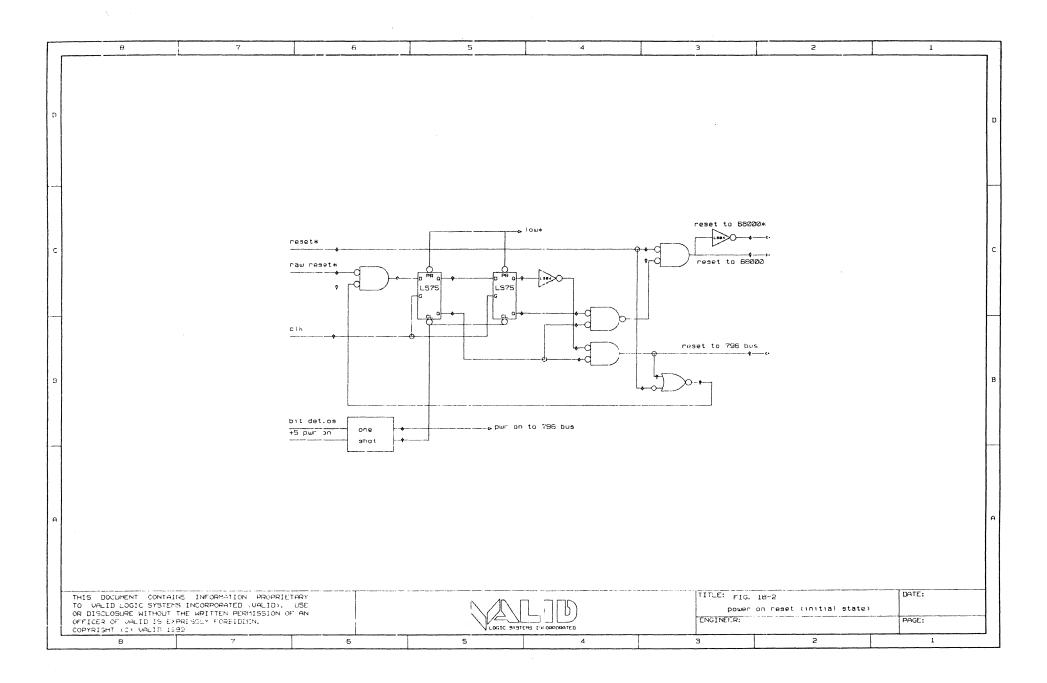

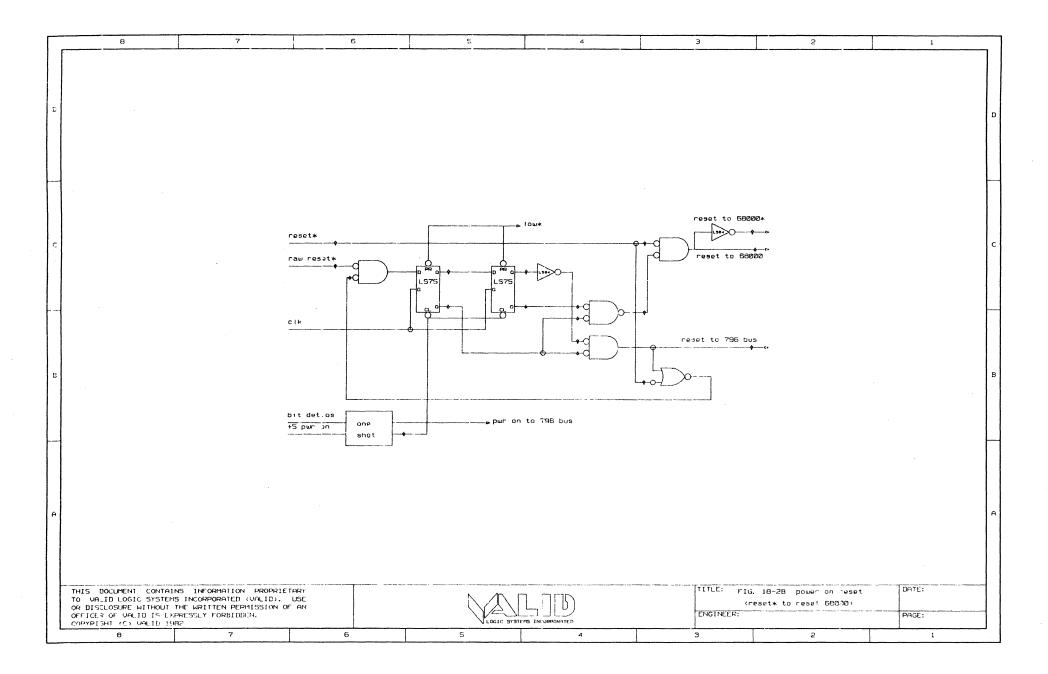

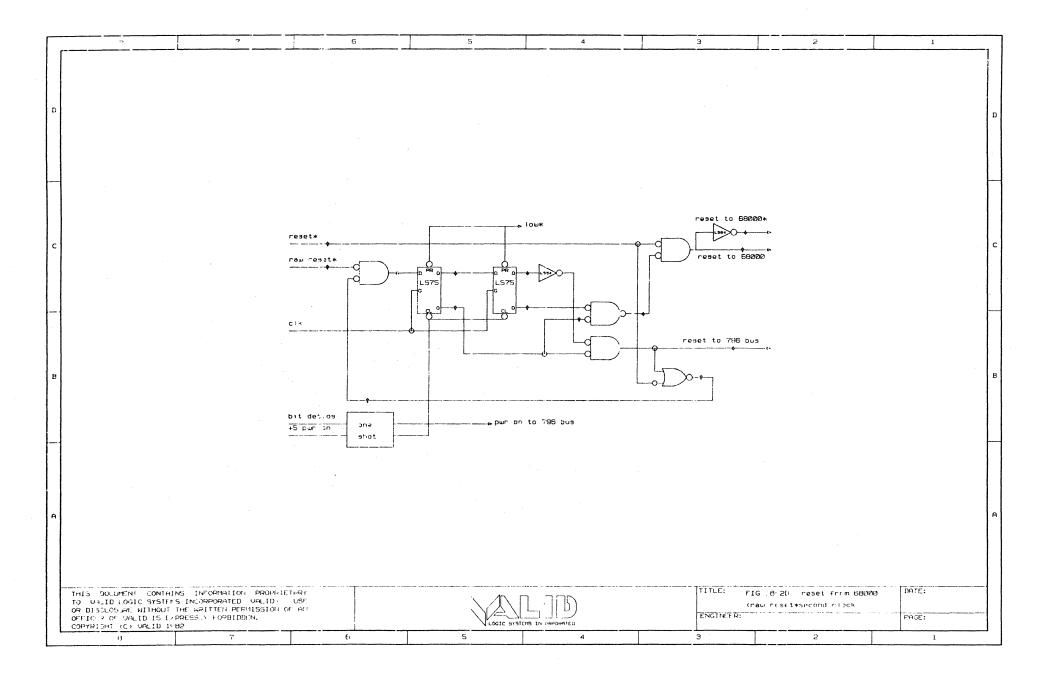

| 18      | CPU RES              | ETS                                                                                                         | 18-1                                 |

|         | 18.1<br>18.2         | Resets/CPU InterfaceResets Detailed Operation18.2.1Power On Reset18.2.2Reset From 6800018.2.3Reset From Bus | 18-1<br>18-1<br>18-3<br>18-3<br>18-3 |

| 19      | CLOCK G              | ENERATOR                                                                                                    | 19-1                                 |

|         | 19.1                 | Clock Generator/CPU Interface                                                                               | 19-1                                 |

| 20      | MAINTEN              | ANCE PORT                                                                                                   | 20-1                                 |

|         | 20.1                 | Maintenance Port/CPU Interface                                                                              | 20-1                                 |

## LIST OF ILLUSTRATIONS

| Number                   | Title                                 | Page                     |

|--------------------------|---------------------------------------|--------------------------|

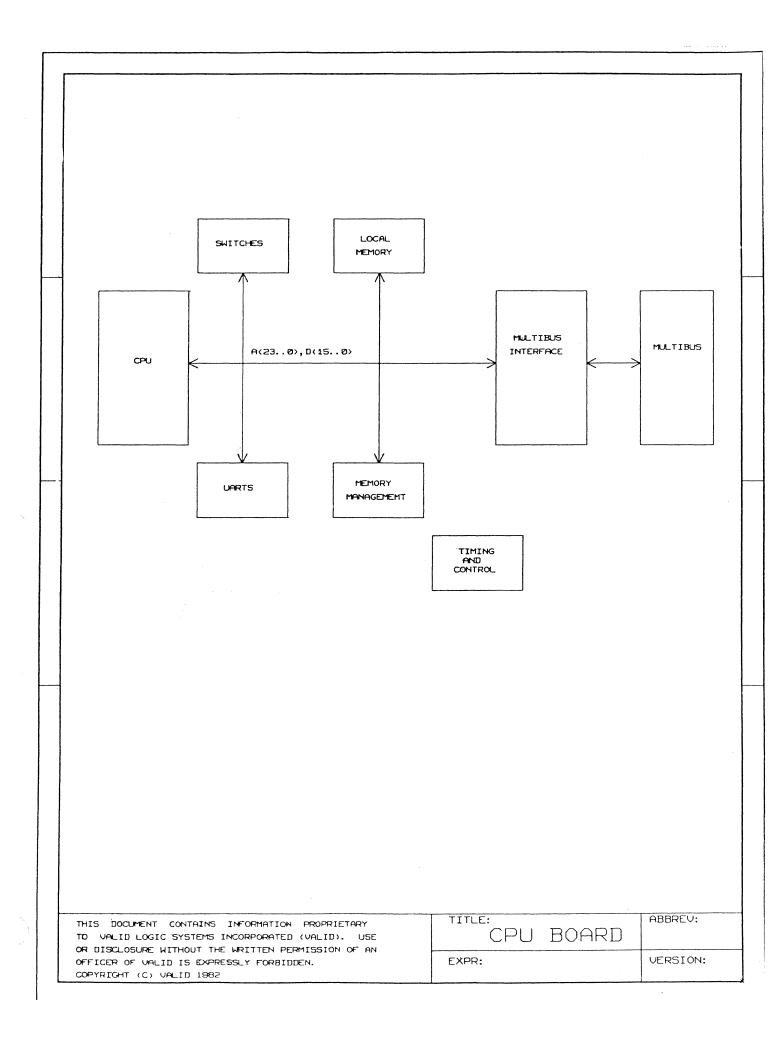

| 1-1                      | CPU Block Diagram                     | 1-3                      |

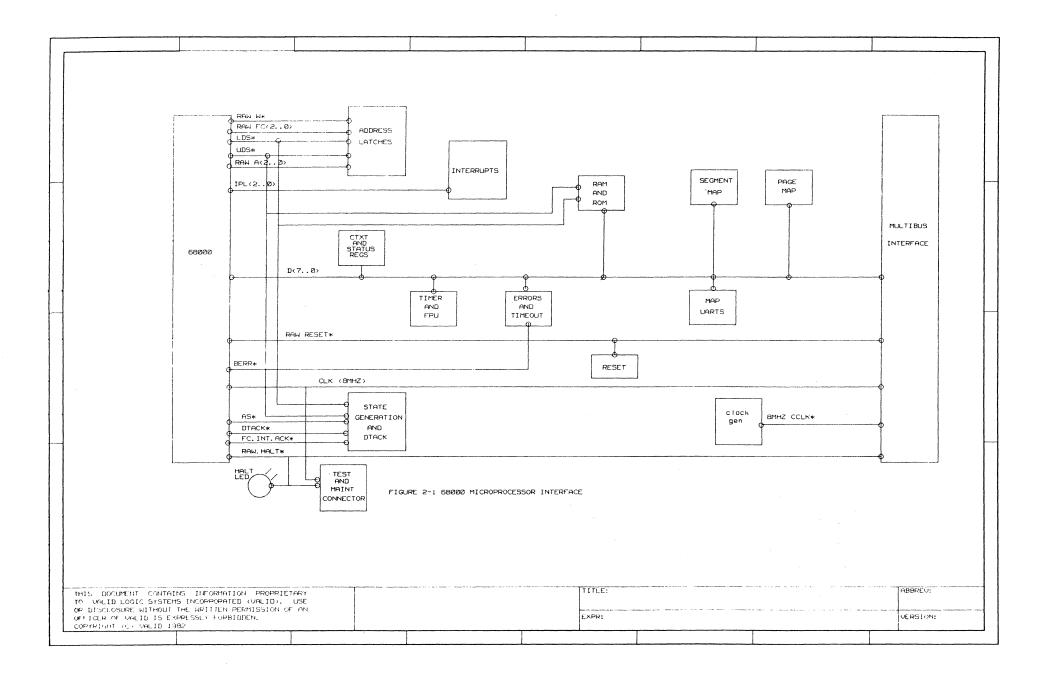

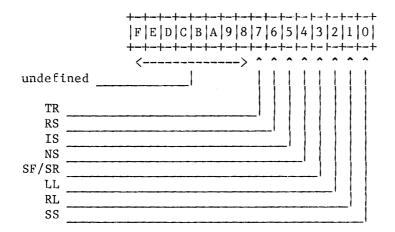

| 2-1                      | M68000LB Microprocessor/CPU Interface | 2-3                      |

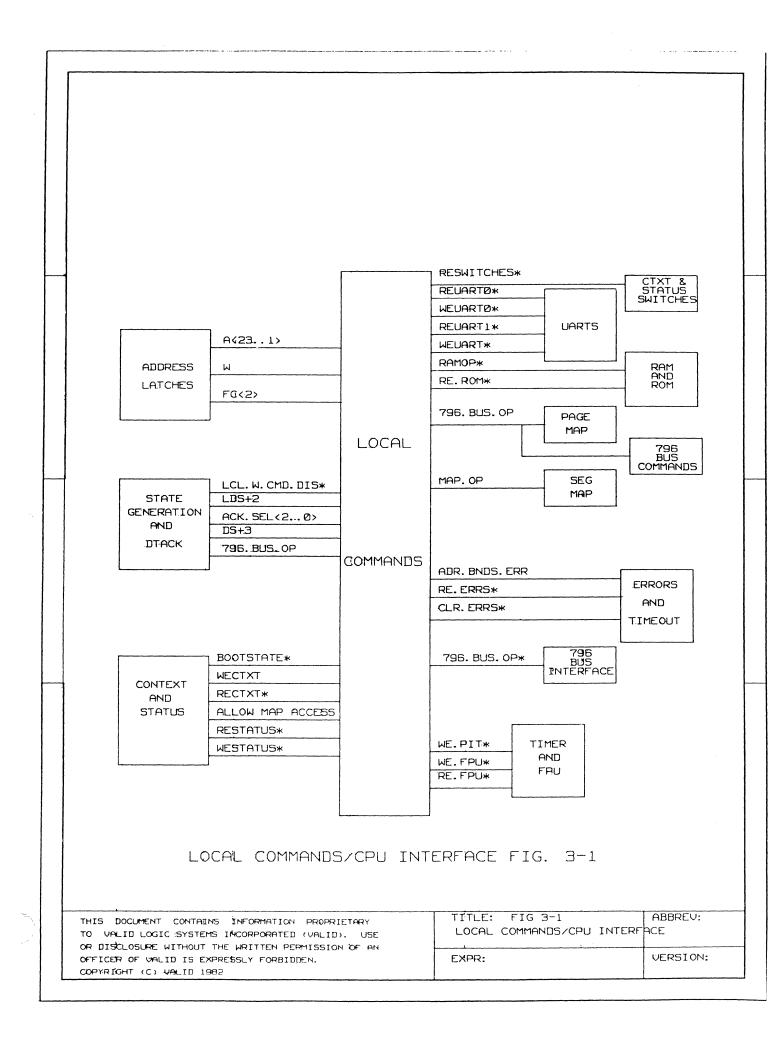

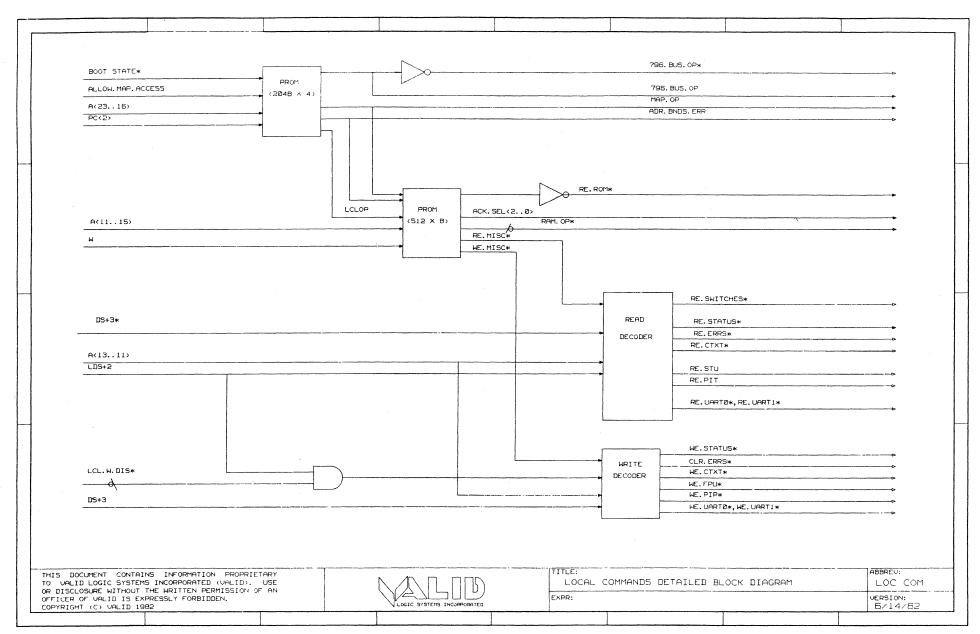

| 3-1<br>3-2               | Local Commands/CPU Interface          | 3-2<br>3-3               |

| 4-1<br>4-2<br>4-3<br>4-4 | Segment and Page Map/CPU Interface    | 4-2<br>4-3<br>4-5<br>4-7 |

# LIST OF ILLUSTRATIONS (Continued)

| Number                                               | Title                                                                                                                                                                            | Page                                           |

|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| 5-1<br>5-2                                           | Interrupts/CPU Interface                                                                                                                                                         | 5-2<br>5-3                                     |

| 6-1<br>6-2<br>6-3                                    | Multibus/CPU Interface                                                                                                                                                           | 6-2<br>6-3<br>6-12                             |

| 7-1<br>7-2                                           | 796 Bus Commands/CPU Interface                                                                                                                                                   | 7 <b>-</b> 2<br>7 <b>-</b> 3                   |

| 8-1<br>8-2                                           | Bus Arbiter/CPU Interface                                                                                                                                                        | 8-3<br>8-4                                     |

| 9-1                                                  | Address Bus/CPU Interface                                                                                                                                                        | 9-4                                            |

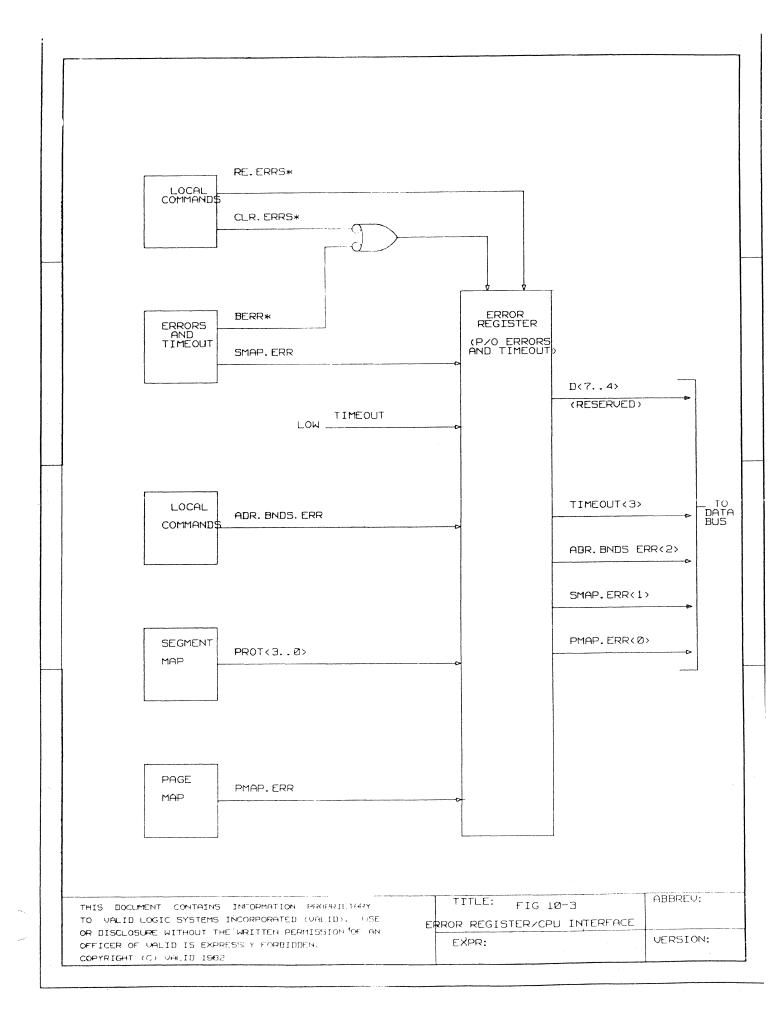

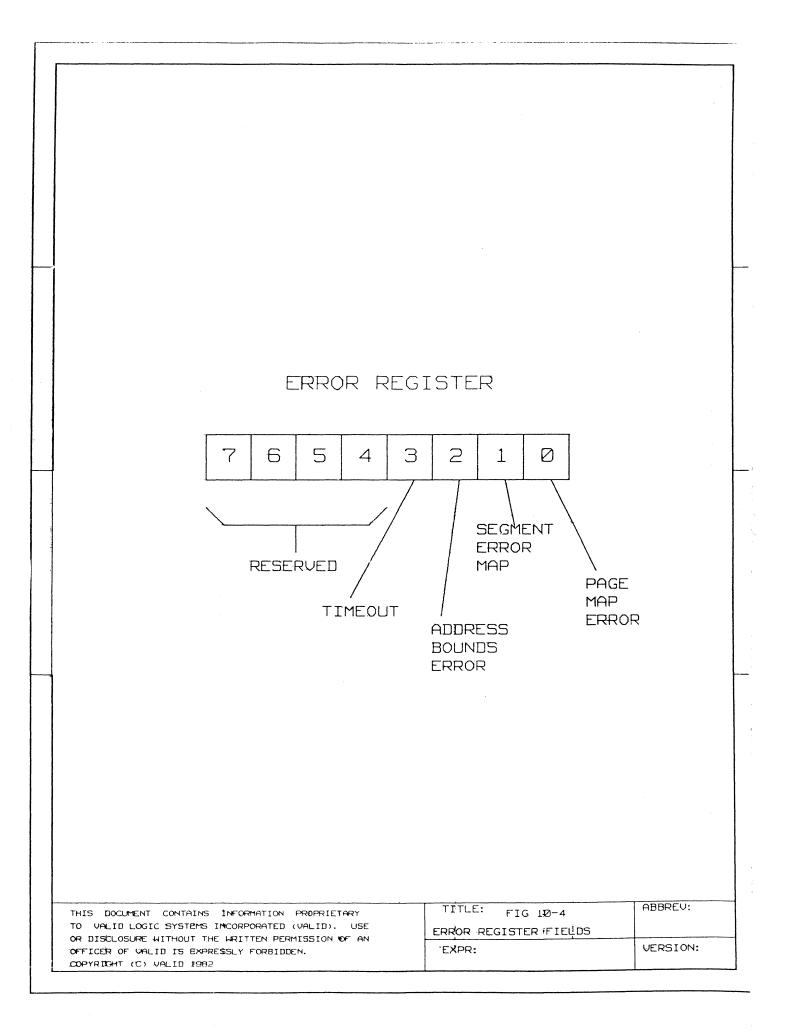

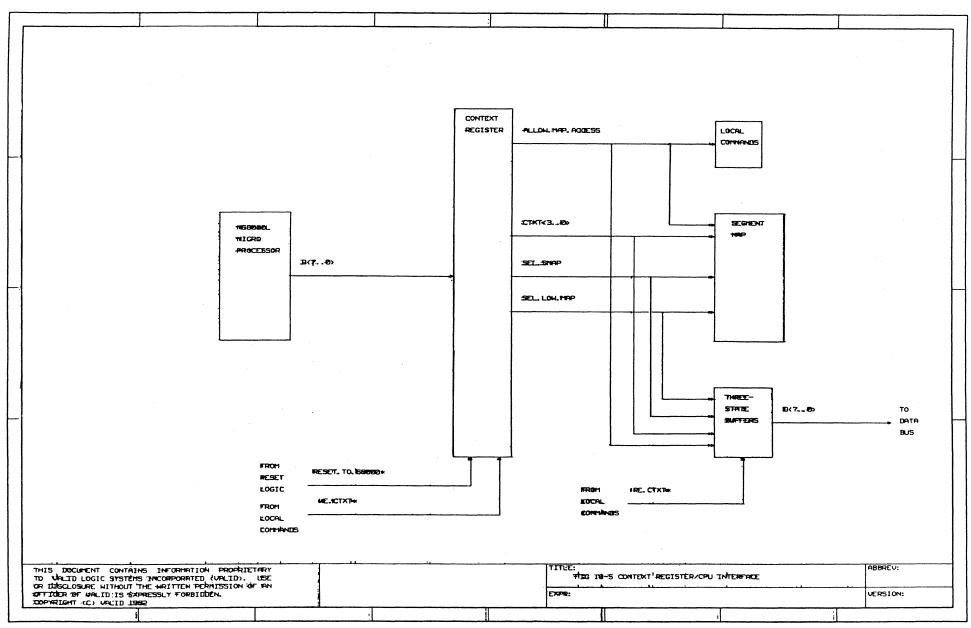

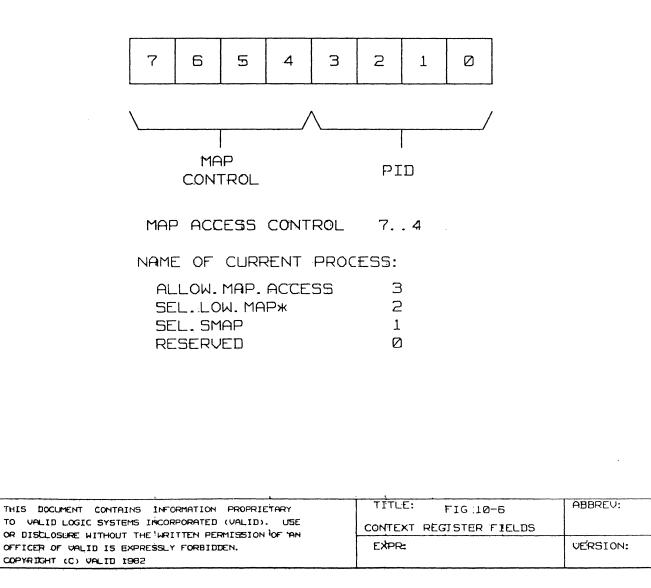

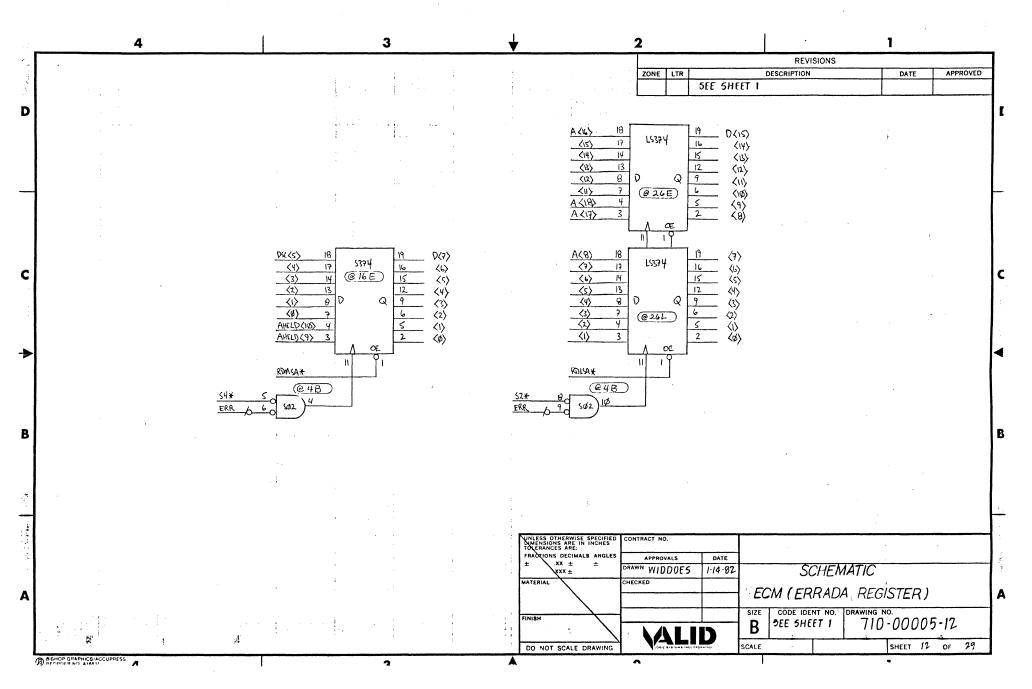

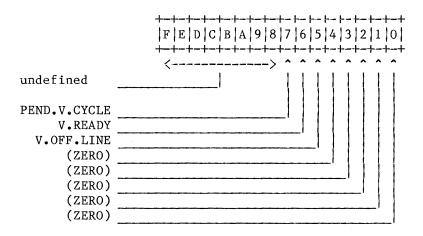

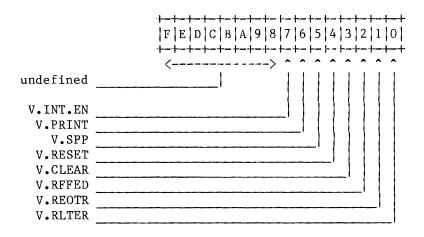

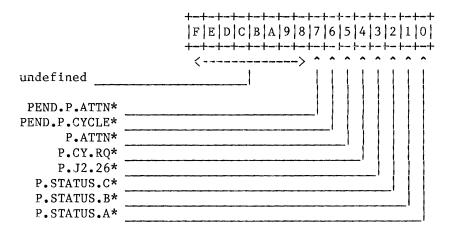

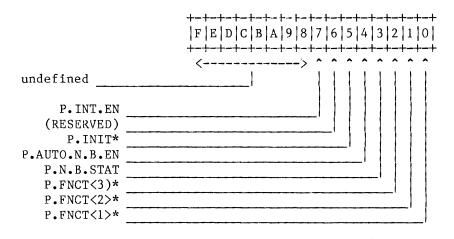

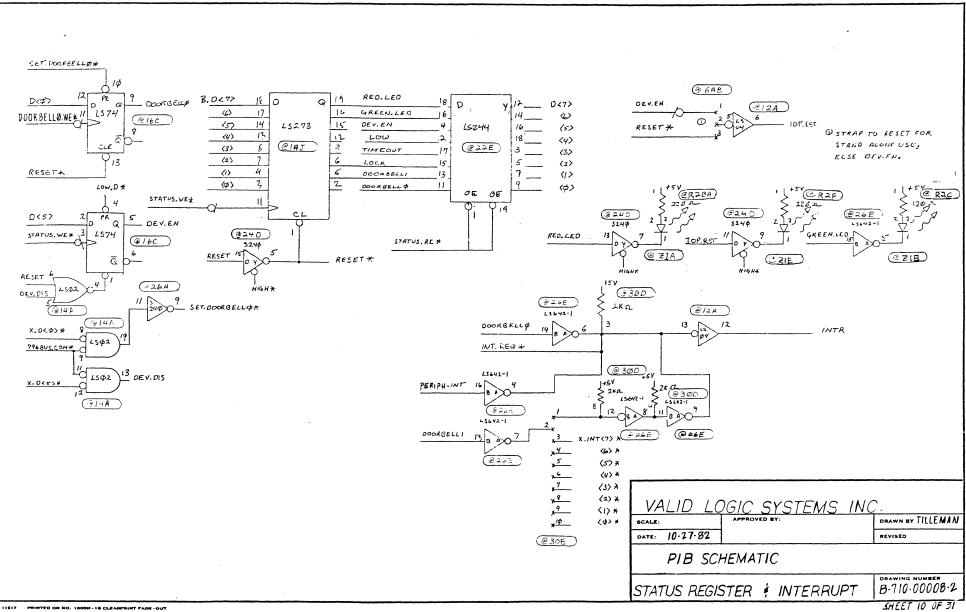

| 10-1<br>10-2<br>10-3<br>10-4<br>10-5<br>10-6         | Status Register/CPU InterfaceStatus Register FieldsError Register/CPU InterfaceError Register FieldsContext Register/CPU InterfaceContext Register FieldsContext Register Fields | 10-2<br>10-6<br>10-8<br>10-9<br>10-11<br>10-12 |

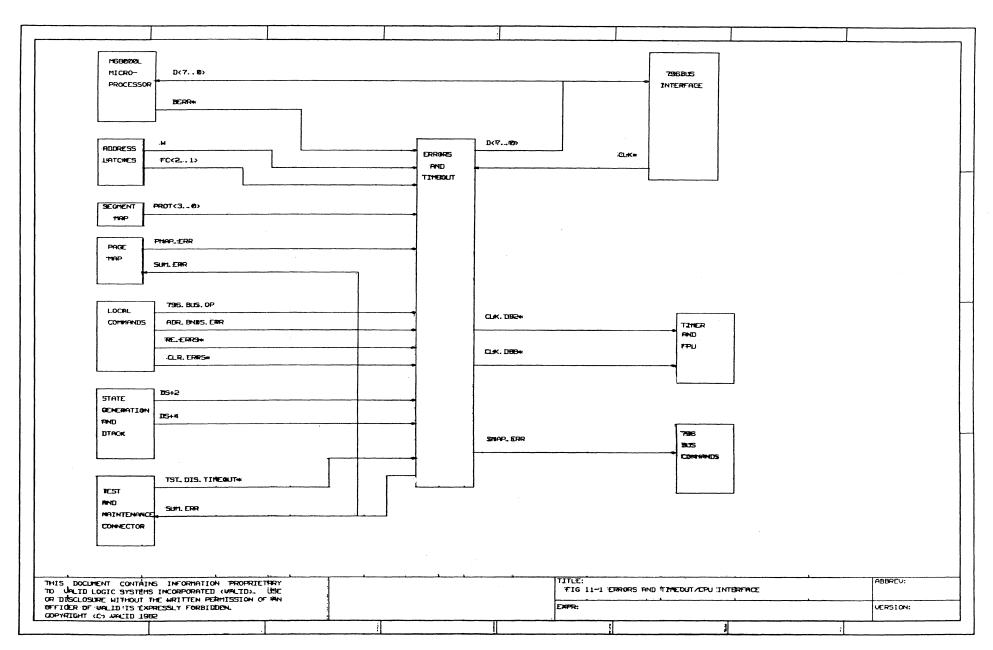

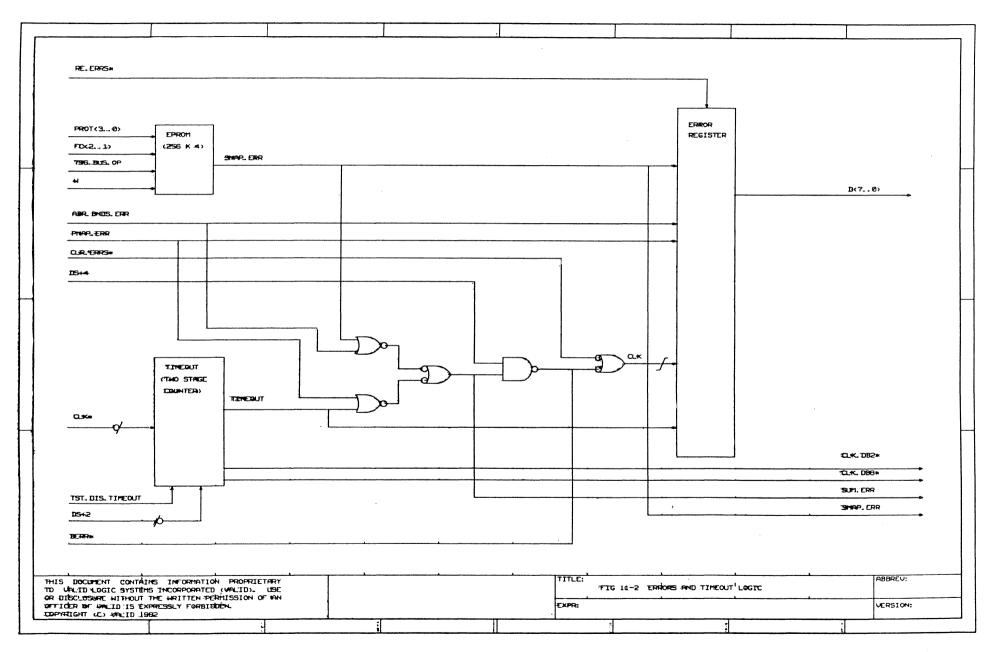

| 11-1<br>11-2                                         | Errors and Timeout/CPU Interface                                                                                                                                                 | 11-2<br>11-4                                   |

| 12 <b>-</b> 1<br>12 <b>-</b> 2                       | Scratch Pad RAM/CPU Interface                                                                                                                                                    | 12 <del>-</del> 2<br>12 <b>-</b> 3             |

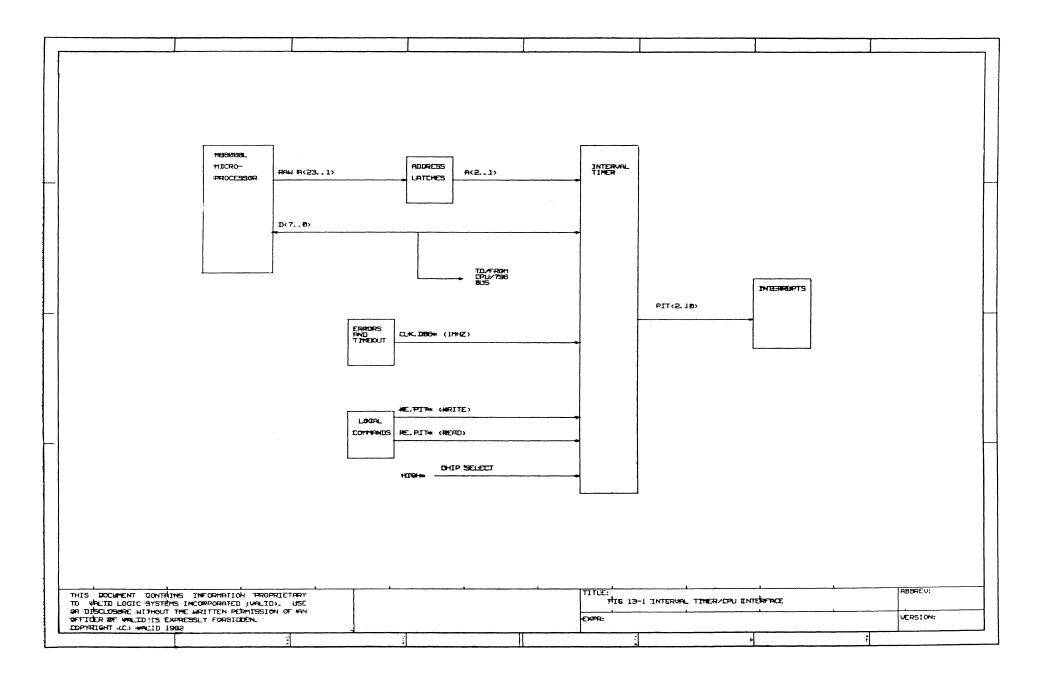

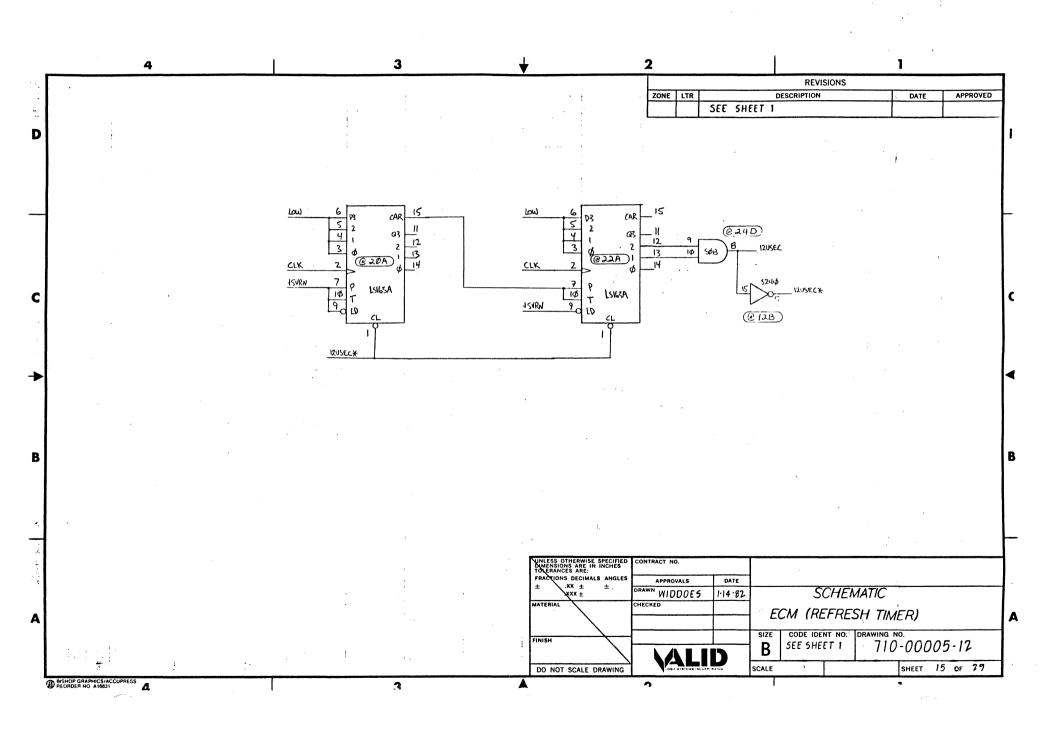

| 13-1                                                 | Interval Timer/CPU Interface                                                                                                                                                     | 13-2                                           |

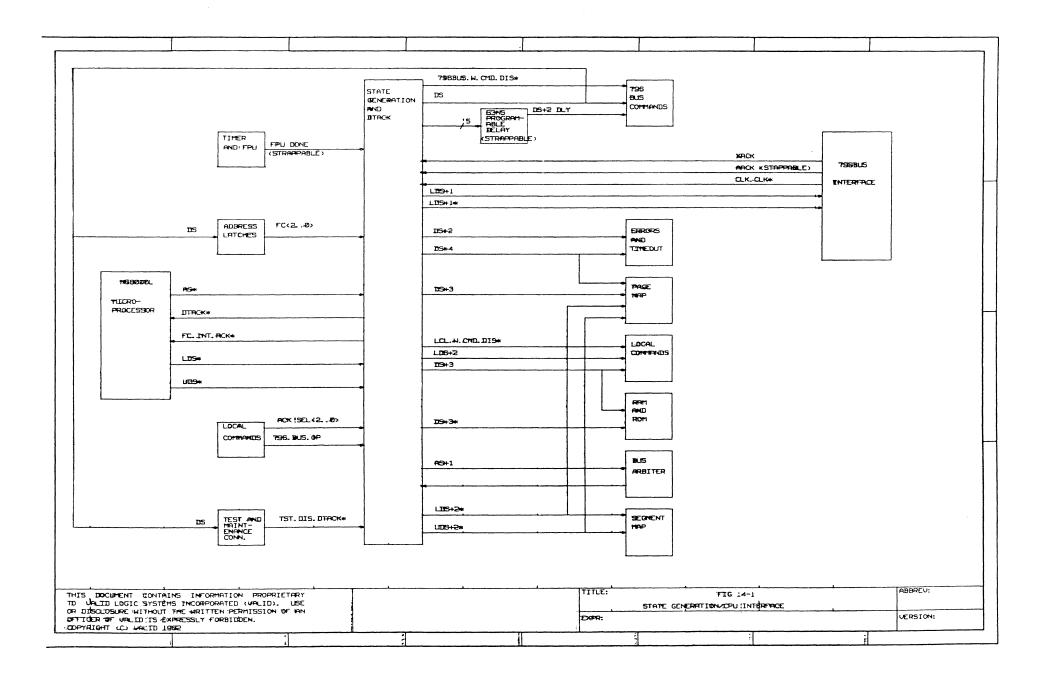

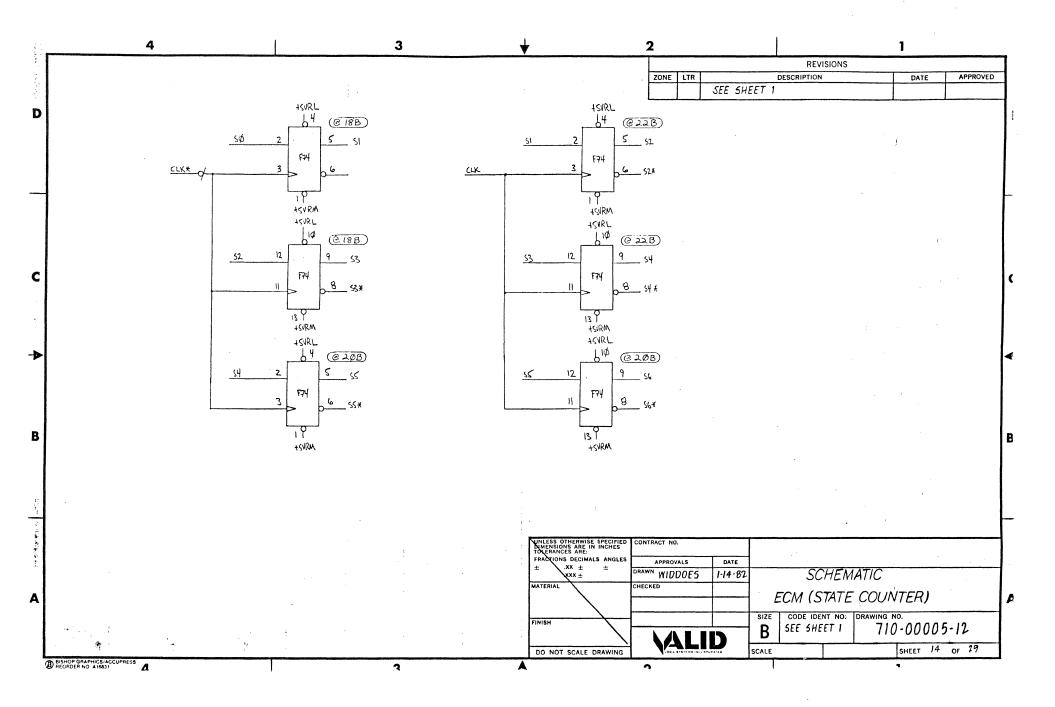

| 14-1                                                 | State Generation/CPU Interface                                                                                                                                                   | 14-2                                           |

| 15-1                                                 | Floating Point Processor/CPU Interface                                                                                                                                           | 15 <b>-</b> 2                                  |

| 16-1                                                 | Switches/CPU Interface                                                                                                                                                           | 16 <b>-</b> 2                                  |

| 17 <b>-</b> 1<br>17 <b>-</b> 2                       | UARTS/CPU Interface                                                                                                                                                              | 17-2<br>17-4                                   |

| 18-1<br>18-2<br>18-2<br>18-2<br>18-2<br>18-2<br>18-2 | Resets/CPU Interface                                                                                                                                                             | 18-2<br>18-5<br>18-6<br>18-7<br>18-8<br>18-9   |

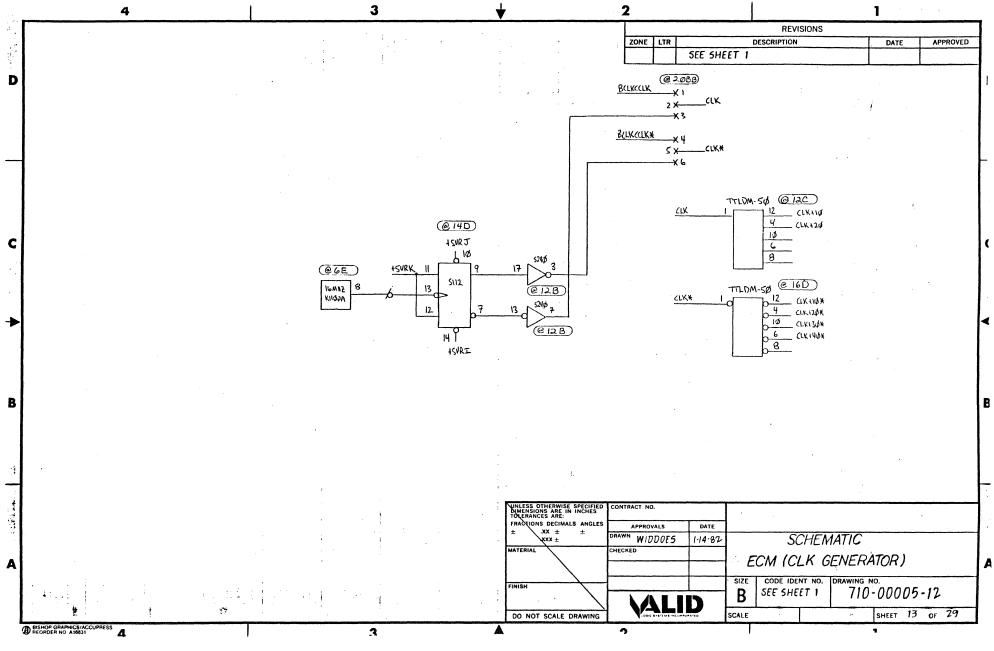

| 19-1                                                 | Clock Generator/CPU Interface                                                                                                                                                    | 19-2                                           |

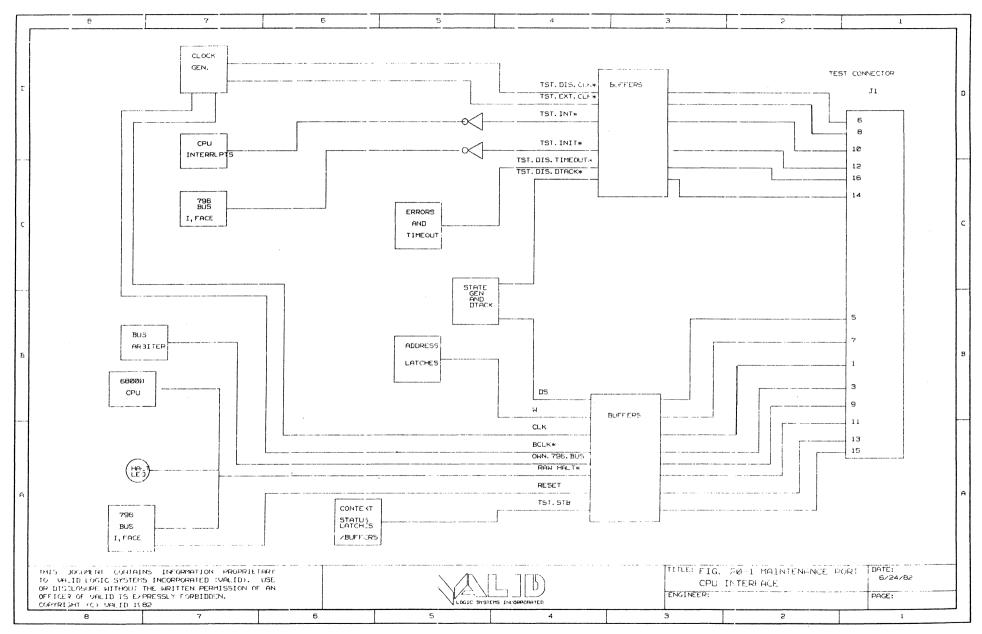

| 20-1                                                 | Maintenance Port/CPU Interface                                                                                                                                                   | 20-4                                           |

## LIST OF TABLES

| Number               | Title                              | Page                  |

|----------------------|------------------------------------|-----------------------|

| 2-1                  | M68000LB Interface Signals         | 2-5                   |

| 6-1<br>6-2           | 796 Bus Interface Signals (P1)     | 6-6<br>6-9            |

| 8-1                  | Bus Arbiter Interface Signals      | 8-1                   |

| 9-1                  | CPU Addressing Features            | 9-1                   |

| 10-1<br>10-2<br>10-3 | Status Register Fields             | 10-3<br>10-7<br>10-10 |

| 20-1                 | Maintenance Port Interface Signals | 20-1                  |

# SECTION 1 INTRODUCTION

## 1.1 Purpose of Manual

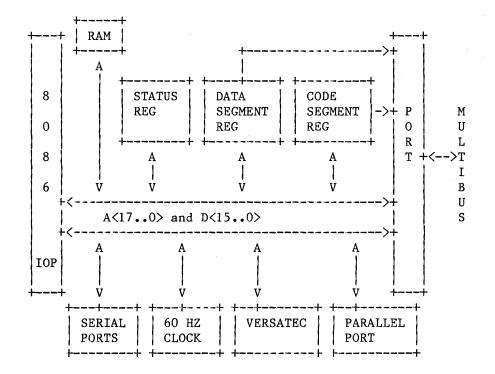

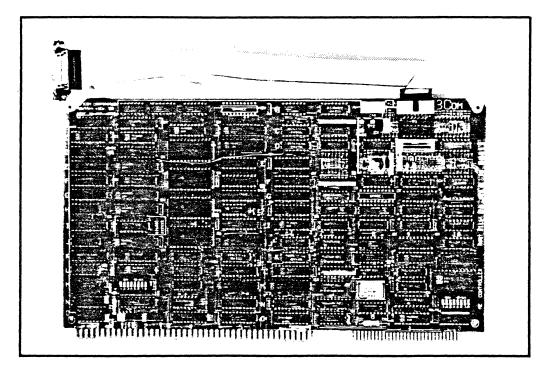

This manual provides a functional overview of the M68000LB CPU board. Included are descriptions of all functions contained on the CPU board as well as a block diagram of the overall board. The description of each function consists of explaining its interface with other functional areas within the CPU and a detailed description of the operation of that particular function. The overall block diagram shows the complete interconnection between all CPU functions described in this manual.

1.2 General Description

The CPU board provides a complete interface between the Motorola M68000LB Microproccessor running at an 8MHz rate and the IEEE-796 bus (Intel Multibus) referred to as the 796 bus in the remainder of this document. At the same time it provides the functions need in the CPU section of a high performance, large-memory, 796 bus based computer system. The board addresses the full 16 Mbyte 796 bus address space through a memory map which offers both relocation and protection for multiple simultaneous users. The board also provides fast serial bus arbitration allowing existence in a system with a large number of other bus masters. The CPU board consists of the following features:

R M68000LB is a registered trademark of Motorcla, Inc.R Multibus is a registered trademark of Intel.

- o Microprocessor running at 8MHz

- o Complete interface to a 16Mbyte 796 bus

- o Seven interrupt priority levels

- o Memory management utilizing segmentation and paging

- o Onboard status, error, and context registers

- o Eight software readable switches for configuration selection

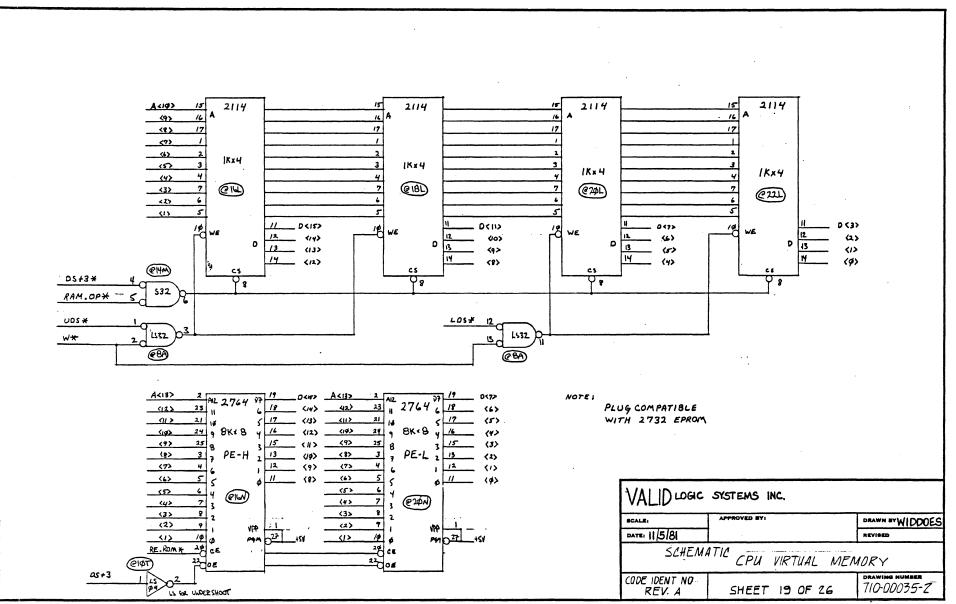

- o Sockets for up to 16Kbyte of local EPROM

- o 2Kbyte of local scratch-pad RAM

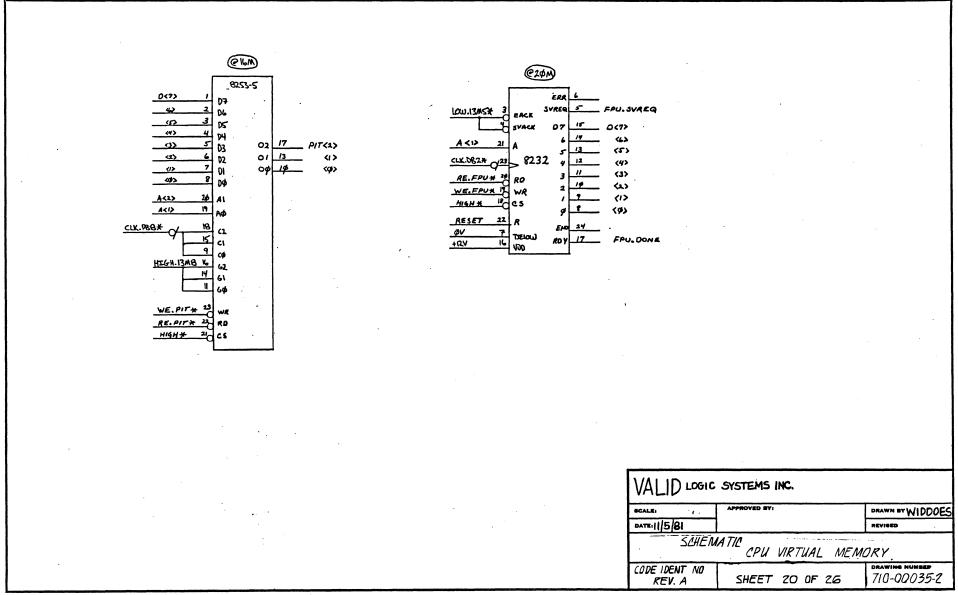

- o Three programmable 16-bit timers

- o Two programmable UARTS, one with full modem control

- o Full MACSBUG compatibility, including transparent mode

- o Optional IEEE format floating point processor.

- o Maintenance port for testing and diagnostic operations.

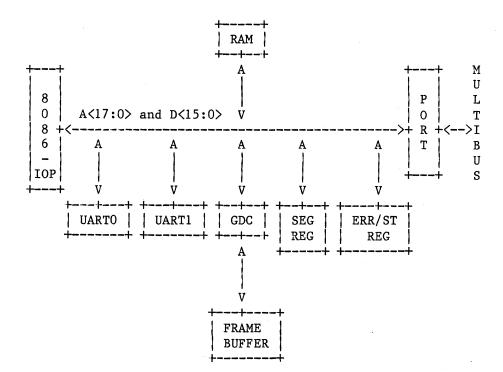

The CPU board consists of the functional areas shown in Figure 1-1. Each of these areas are described in the sections that follow. Interfaces to and from the CPU board include the UARTS ports, 796 bus, and maintenance connector. Certain strapping options are also provided on the board as explained in each functional description as applicable.

# SECTION 2 M68000LB MICROPROCESSOR

## 2.1 General Features

The M68000LB microprocessor is a high-performance, programmable, 16-bit processor containing a 32-bit architecture with the features listed below.

- o 8MHz operation

- o 16Mbyte direct addressing range

- o Eight 32-bit data registers

- o Seven 32-bit address registers

- o 56 instruction types

- o Five data types

- o 14 addressing modes

- o CPU driven at 8MHz

In addition, it incorporates such features as multi-level, vectored interrupts, privilege states, illegal instruction policing and bus-cycle abort.

The detailed operation of the M68000LB is discussed in publications supplied by the manufacturer of the device. Consult these as required for detailed information as to the specific features and operation of the M68000LB.

## 2.2 M68000LB/CPU/Multibus Interface

The interface of the CPU to the 796 bus as shown in Figure 2-1 are listed as follows:

- o Address Latches

- o State generation and data acknowledge (DTACK)

- o Local commands

- o UARTS

- o Timer and FPU

- o RAM and ROM

- o SMAP and PMAP

- o CPU interrupts

- o Errors and timeout

- o 796 bus interface

- o Clock generator

- o Test and maintenance interface

- o Context and status registers

Table 2-1 lists the name, category, and function of each signal to and from the M68000LB.

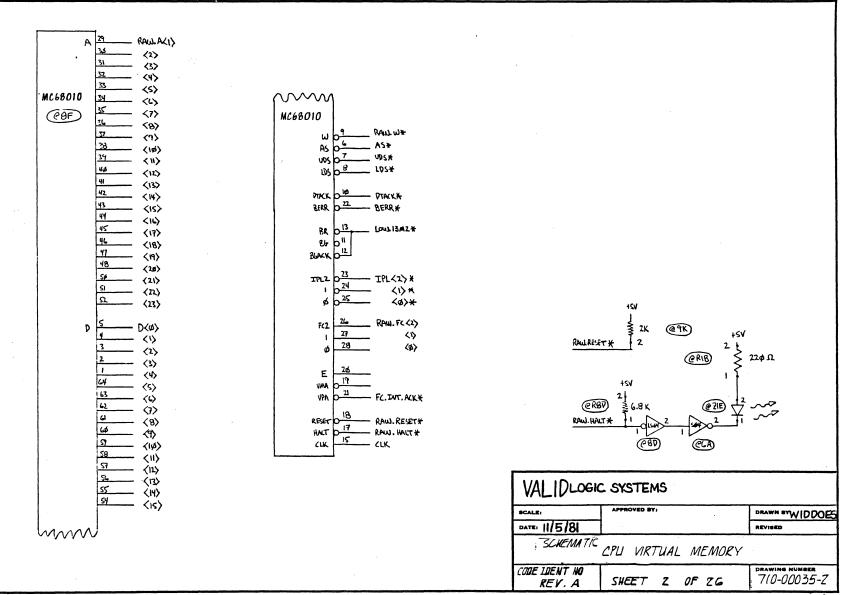

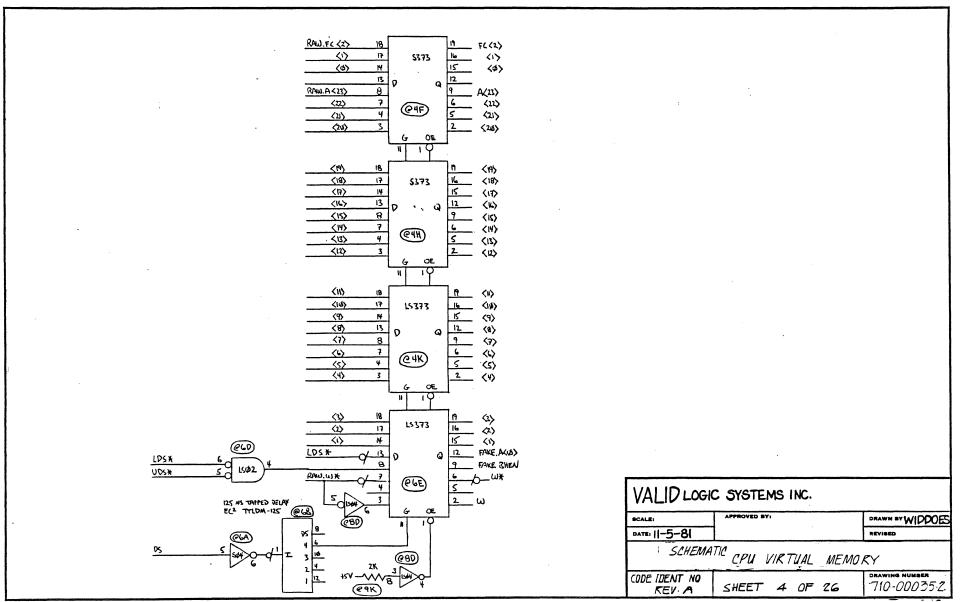

The M68000LB supplies address bits (RAW.A<23..1>), raw write (RAW.W\*), function code (RAW.FC<2..0>), and upper and lower data strobes (LDS\* and UDS\*) to the address latches. The latches in turn provide addressing, read/write commands, function codes, and upper and lower data byte selection as described in the addressing section of this manual.

LDS\* and UDS\* data strobes are supplied to the RAM and ROM memories and the state generation and DTACK logic. The strobes provide upper and lower byte selection for the operation of the RAM scratch pad memory. The strobes also generate data strobe outputs from the state generation logic to the CPU board. The function codes, all true, plus AS\* from the M68000LB generate FC.INT.ACK\* from the state generation logic to the M68000LB. Function code bits FC<2..1> are also supplied to the errors and timeout logic as inputs to the S.MAP ERR decoder.

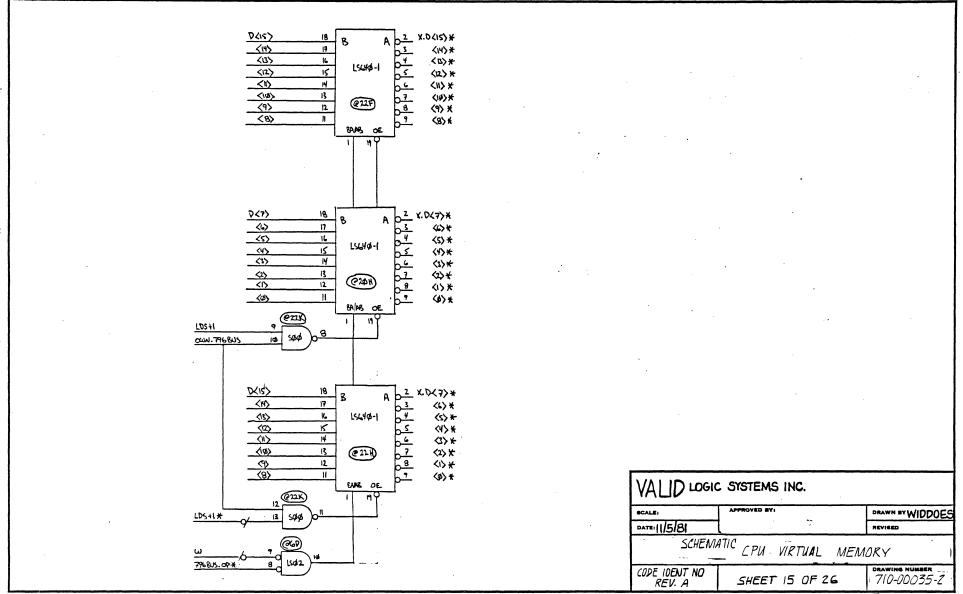

The M68000LB data bus provides an interface among the various functions on the CPU board. These are the context and status registers, timer, FPU, RAM and ROM, errors and timeout, segment and page maps, UARTS, and 796 bus interface. Data is exchanged between these functions and the 796 bus as controlled by the program (user or supervisor mode) and in turn as selected by the address bus, read/write selection, function code, and upper and lower data strobes.

# Table 2-1. M68000LB Interface Signals

| SIGNAL                      | CATEGORY                    | FUNCTION                                                                                                                              |

|-----------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| RAW A<231>                  | Address Data Lines          | Provides address for bus<br>operations during all<br>cycles except interrupt<br>modes (refer to CPU<br>Interrupts, Section 5).        |

| D<150>                      | Data Lines                  | Bi-directional data line<br>for word or byte length<br>data transfers (refer to<br>CPU Interrupts, Section<br>5).                     |

| AS*<br>(Address Strobe)     | Asynchronous Bus<br>Control | Indicates a valid address<br>is on the M68000LB<br>address bus.                                                                       |

| RAW W*<br>(Read/Write*)     | Asynchronous Bus<br>Control | Defines the data bus<br>transfer as a read or<br>write cycle. Also<br>operates in conjunc-<br>tion with the UDS* and<br>LDS* signals. |

| UDS*<br>(Upper Data Strobe) | Asynchronous Bus<br>Control | Controls upper byte of<br>data lines D<158><br>depending on condition<br>of RAW W*.                                                   |

| LDS*<br>(Lower Data Strobe) | Asynchronous Bus<br>Control | Controls lower byte of<br>data lines (D<70>)<br>depending on condition<br>of RAW W*.                                                  |

# Table 2-1. M68000LB Interface Signals (Continued)

| SIGNAL                                    | CATEGORY                    | FUNCTION                                                                                                                                                     |

|-------------------------------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DTACK<br>(Data Transfer<br>Acknowledge)   | Asynchronous Bus<br>Control | Indicates data transfer<br>is completed.                                                                                                                     |

| RAW FC<20><br>(Function Code)             | Processor Status            | Indicate the state (user<br>or supervisor) and the<br>cycle type currently<br>being executed. Function<br>code outputs are valid<br>only when AS* is active. |

| PL<20>)*<br>(Interrupt Priority<br>Level) | Interrupt Control           | Indicate the encoded<br>priority level of the<br>device requesting an<br>interrupt (refer to<br>CPU Interrupts,<br>Section 5).                               |

| FC.INT.ACK.*<br>(Valid Function<br>Code)  | Peripheral Control          | Indicates M68000LB<br>shculd use automatic<br>vectoring for an inter-<br>rupt.                                                                               |

| SIGNAL                | CATEGORY       | FUNCTION                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RAW RESET*<br>(Reset) | System Control | Bidirectional signal<br>resets the M68000LB<br>in response to an<br>external reset signal.<br>An externally genera-<br>ted reset (from CPU)<br>causes all external<br>devices to be reset<br>without affecting the<br>state of the pro-<br>cessor. A total<br>system reset as a<br>result of a HALT or<br>RESET, causes M68000LB<br>and all other devices<br>to be reset. |

| RAW HALT*<br>(Halt)   | System Control | Bi-directional signal.<br>When driven by M68000LB,<br>indicates to external<br>devices that processor<br>has stopped. When<br>driven by external<br>device, causes pro-<br>cessor to stop at<br>completion of current<br>bus cycle.                                                                                                                                       |

# Table 2-1. M68000LB Interface Signals (Continued)

| SIGNAL               | CATEGORY       | FUNCTION                                                              |

|----------------------|----------------|-----------------------------------------------------------------------|

| BERR*<br>(Bus Error) | System Control | Informs processor of<br>problem with current<br>cycle being executed. |

|                      |                | Works with RAW HALT*<br>to determine if excep-                        |

|                      |                | ticn processing should<br>be performed or cur-                        |

|                      |                | rent bus cycle retried.                                               |

| CLK                  |                | Provides 8MHz clock                                                   |

|                      |                | signal to operate the                                                 |

|                      |                | M68000LB.                                                             |

Table 2-1. M68000LB Interface Signals (Continued)

The 8MHz clock is generated by circuits on the CPU board and supplied to the 796 bus (see Clock Generator, Section 19) or can be received from the 796 bus from another source. Interrupts can originate either on the CPU board or the 796 bus. These result in a three bit code used by the M68000LB to select one of seven strappable interrupts. A bus error (BERR\*) is applied to the M68000LB after a timeout, an address bus error from the command logic, or a segment or page error. Reset (RAW RESET\*) is a bi-directional line between the 796 bus and the M68000LB. A reset from either source is provided to the CPU reset logic. The RAW.HALT line is a bi-directional signal used to halt M68000LB operations. The line illuminates a red light emitting diode (HALT LED) when activated. The reset and halt lines are also provided to the test and maintenance connector for fault isolation purposes.

# SECTION 3 LOCAL COMMANDS

## 3.1 Purpose

The purpose of the local commands is to generate command strobes for the CPU. The commands logic is odd-byte addressed and provides on board resources, map, and 796 bus access. The local commands interface within the CPU is shown in Figure 3-1. A detailed diagram of the commands logic is shown in Figure 3-2.

## 3.2 Local Commands/CPU Interface

The commands interface within the CPU, as shown in Figure 3-1, consists of receiving addressing, timing, and control signals from the address latches, state generation and DTACK, and context and status registers. The commands logic then provides command strobes to the various CPU functions as shown.

## 3.3 Commands Generation

The local commands logic consists of two programmable PROMs and two decoders. The PROMs (2048 x 4 and 512 x 8) are addressed from the CPU address latches over lines A<23..16> and A<15..11> respectively. Addressing to the decoders is over lines A<13..11>. In addition to the address lines, the PROMs are also addressed during the boot state controlled by one of the map access modes over function code line (FC<2>). The 512 x 8 PROM is addressed from the 2048 x 4 PROM, and the read.write line from the address latches. Commands generated from the PROMs include the following:

- o 796.BUS.OP\* to the 796 bus interface

- o MAP.OP to the segment map

- o ADR BNDS.ERR to the errors and timeout logic

- o RAM and ROM commands for local operation

- o Acknowledge lines to the state generation and DTACK

- o Read/write commands to the command decoders

The command decoders are operated by the data strobe (DS) and lower data strobe selection (LDS) lines from the state generation and DTACK logic. The write decoder can be disabled by the local write disable line (LCL.W.DIS\*) generated by the state generation logic. The decoders operate in either a read or write mode. The read decoder is selected by a read (RE.MISC\*) command from the 512 x 8 PROM, coupled with a true lower data strobe (LSD+2). The final read outputs are placed on the CPU lines as the DS+3\* pulse occurs to the read decoder. For a write operation, a WE.MISC\* line from the 512 x 8 PROM coupled with the LDS+2 selects the write decoder and the DS+3 pulse from the state generation logic places the write commands on the CPU lines.

# SECTION 4 MEMORY

## 4.1 General

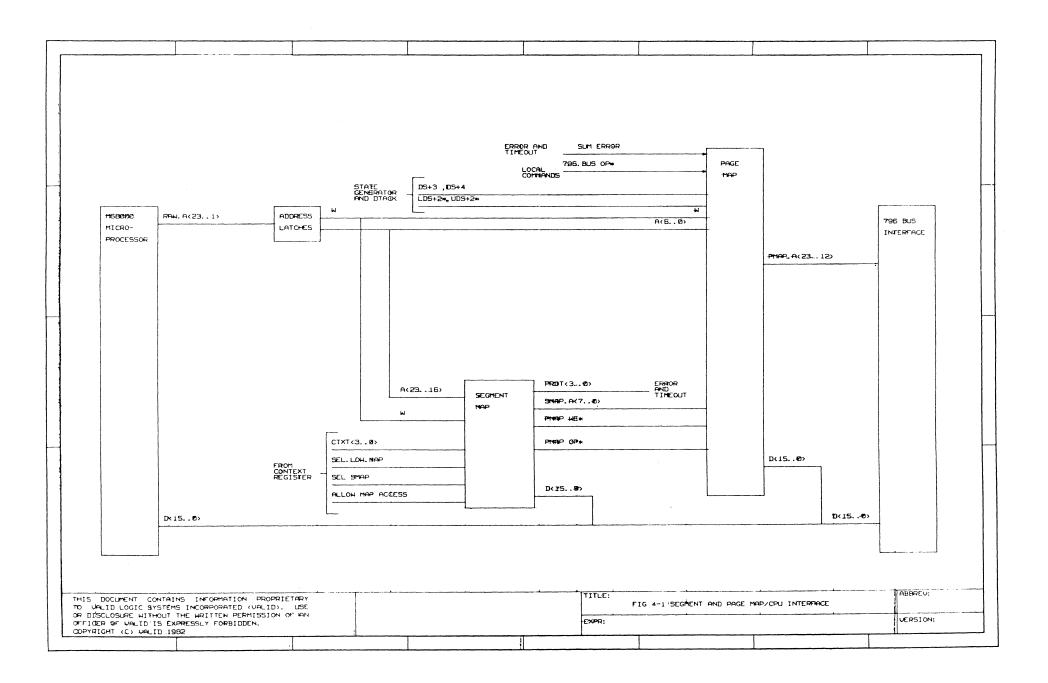

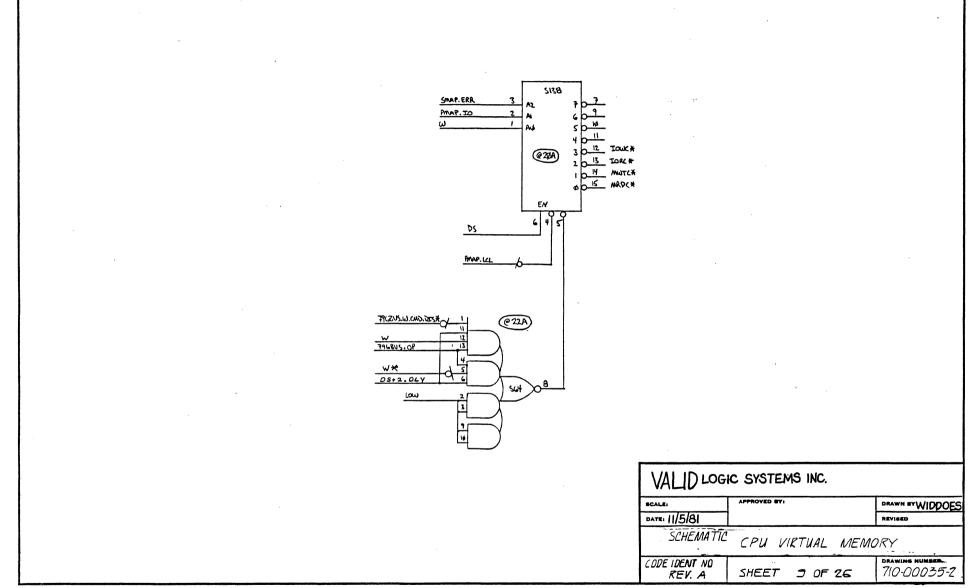

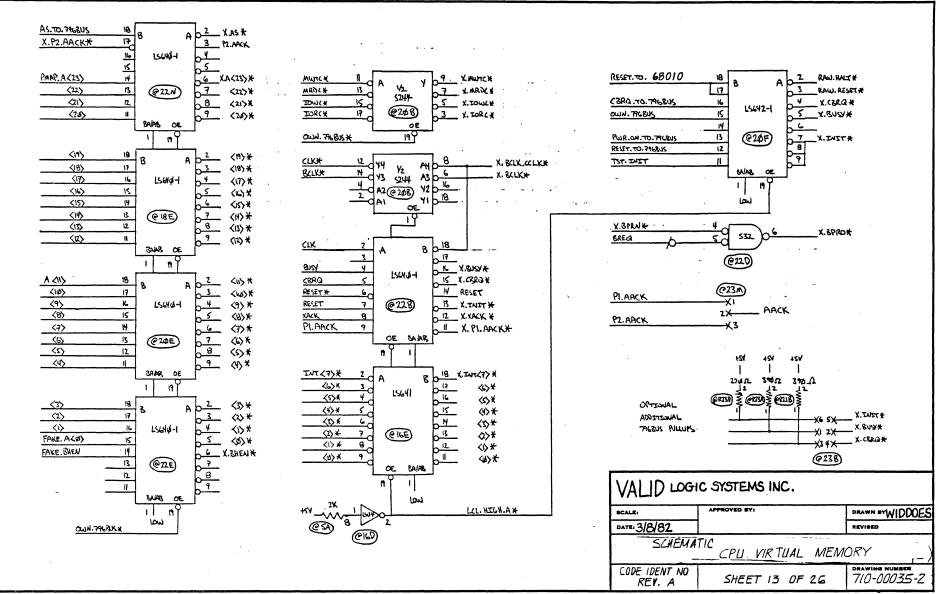

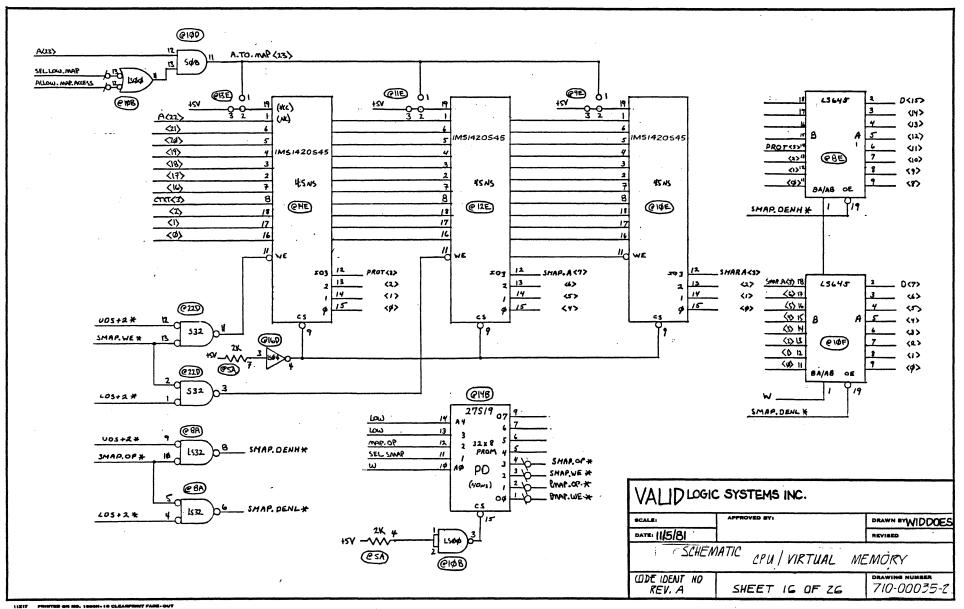

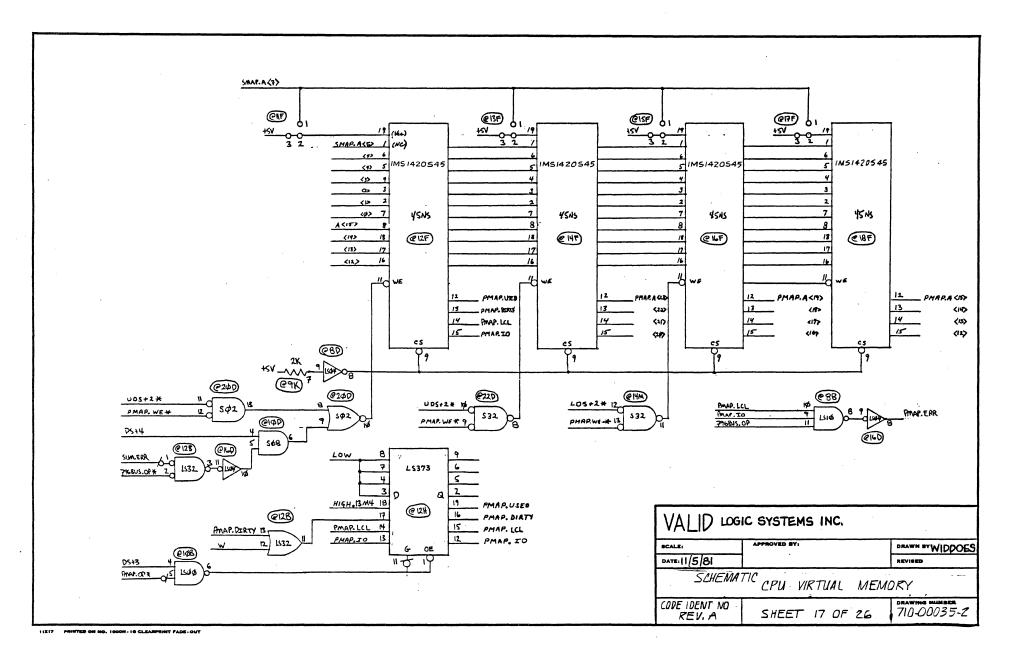

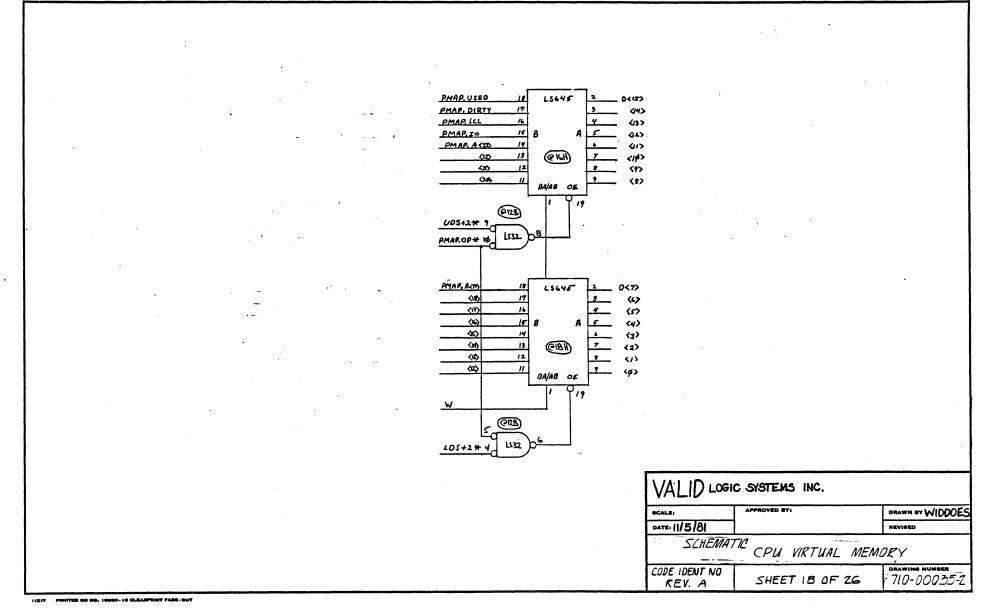

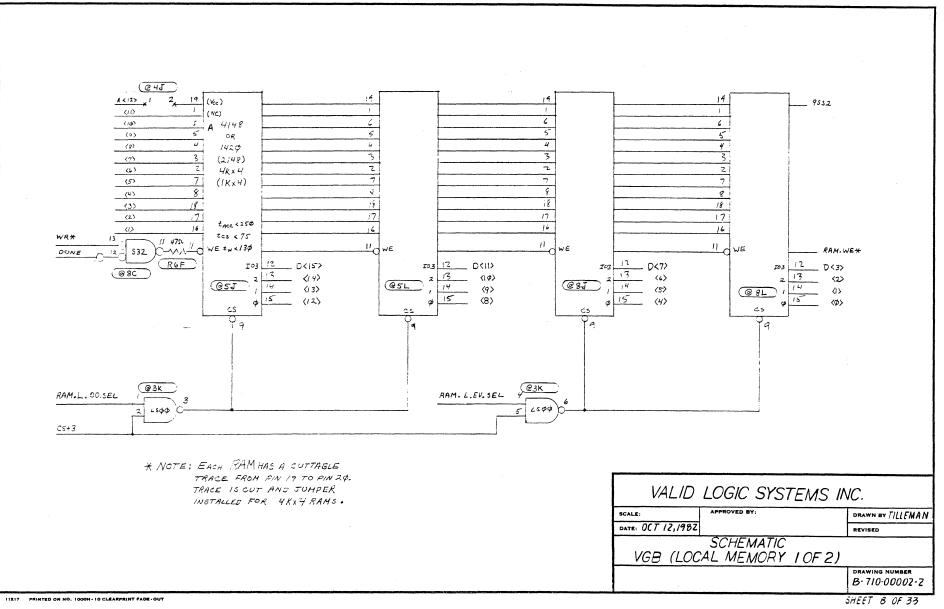

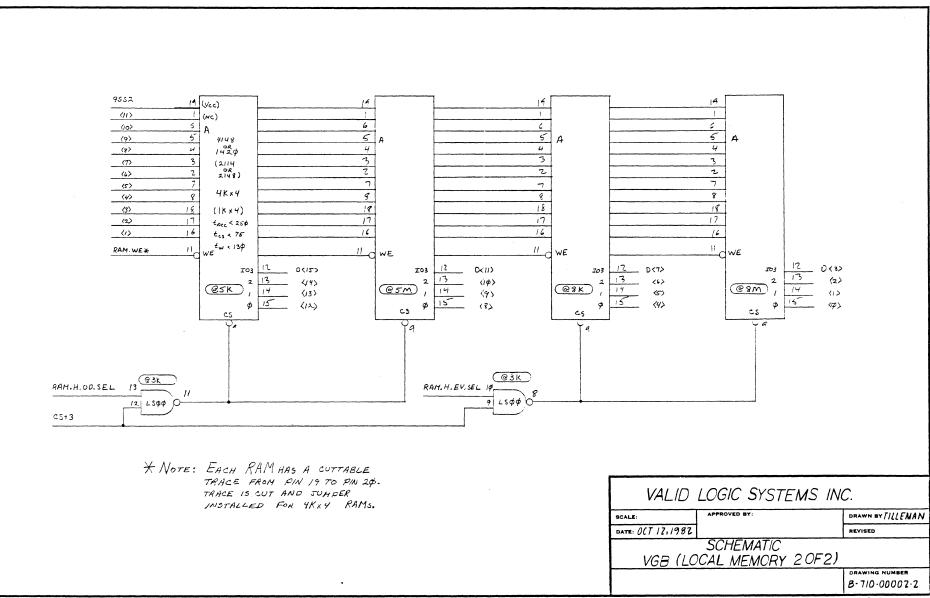

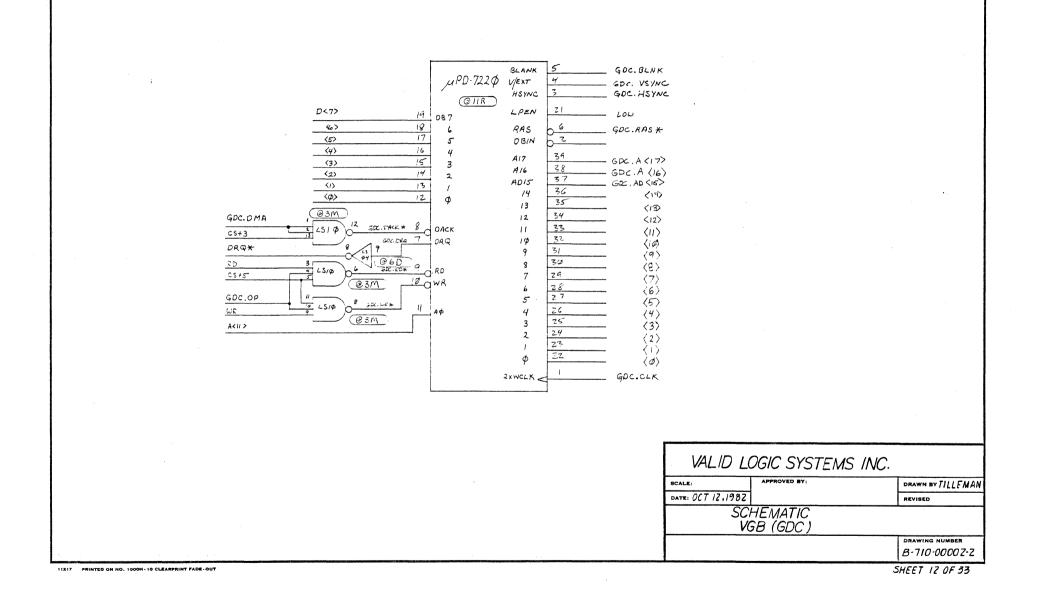

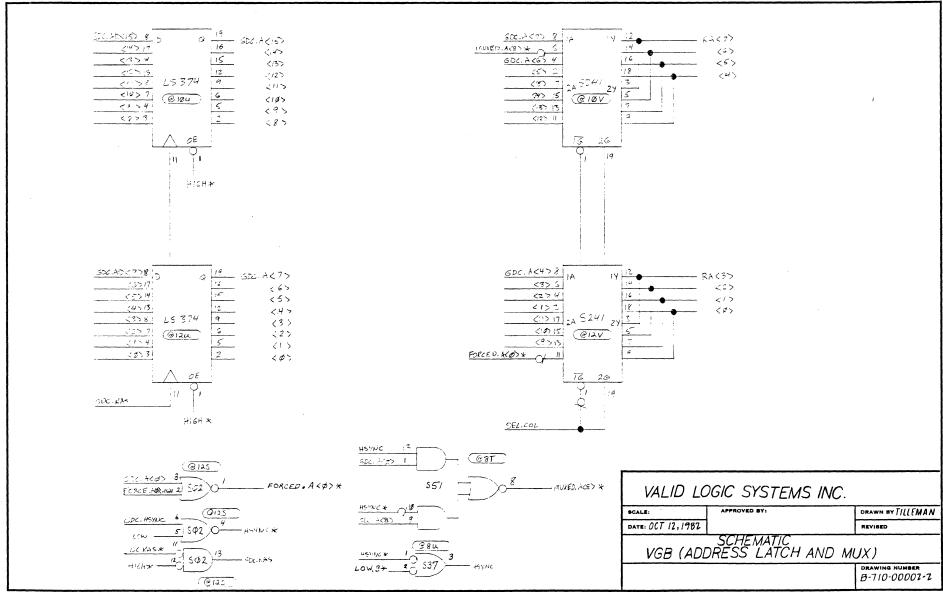

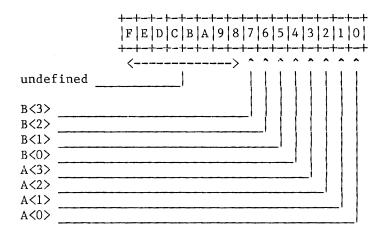

The CPU memory management consists of the M68000LB utilizing both segmentation and page mapping. The functions of the CPU board along with associated interfacing involved in the memory management task are shown in Figure 4-1. Shown are the segment map, page map, address, data, and select and control lines that interface with the various functions of the CPU board including the M68000LB, address latches, and 796 bus interface.

#### 4.2 Segment and Page Map Interface

Addressing and read/write commands for the segment map are received from the M68000LB via the address latches. Map selection and upper and lower data strobe (UDS+2\* and LDS+2\*) are supplied by the context register and state generator and DTACK respectively. Segment map addresses as well as control and selection signals are supplied to the page map. Segment map error signals (PROT<3..0>) to the errors and timeout logic are lines that provide inputs for the generation of the SMAP.ERR signal to the error register (see Registers, Section 10). An interface to the bi-directional data lines (D<15..0>) is also provided for reading and writing of segment map data as described in paragraphs that follow.

The page map supplies map addresses to the 796 bus (PMAP.A<23..12>) and interfaces with the data bus for read/write purposes. The map receives addresses and read/write commands (W) from the address latches and data strobe (DS+3 and DS+4), selection (796.BUS.OP\*), upper and lower byte selection (LDS+2\* and UDS+2), and error signals (SUM.ERROR) from the stage generation and DTACT local commands, and error and timeout logic.

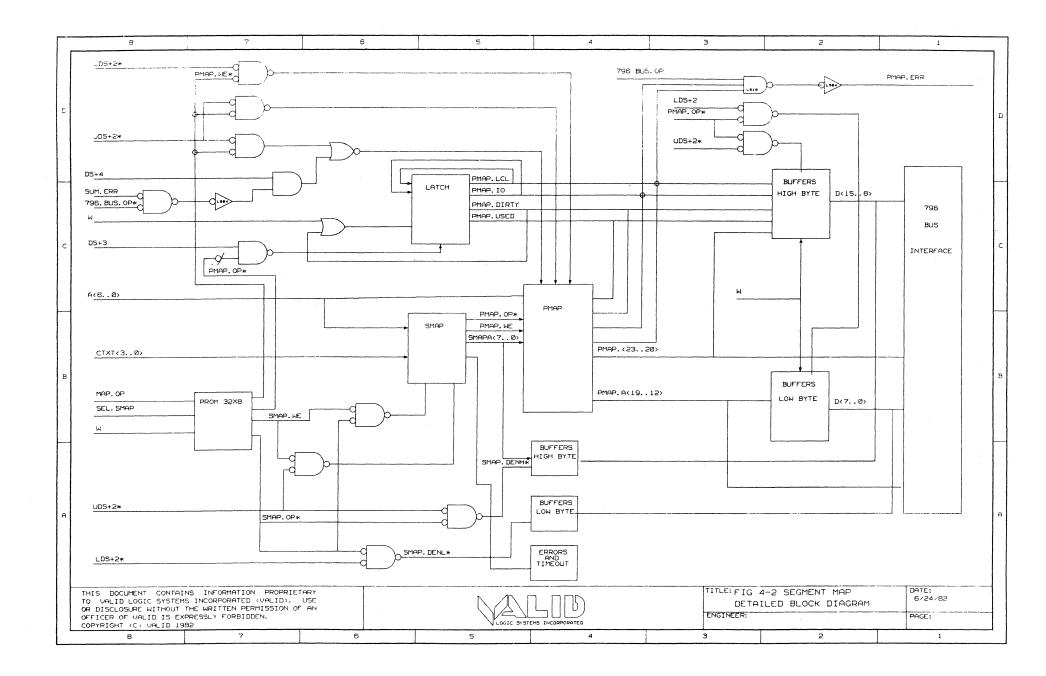

A detailed block diagram of the segment and page map is provided in Figure 4-2. In addition to the inteface diagram of the segment and page map described in the previous paragraphs, the detailed diagram shows gating of the

control and selection signals and bi-directional buffers used for reading and writing of data to and from the respective maps.

The selection logic shown in the case of both the segment and page map provides lower and upper byte selection based on the upper and lower data strobes and segment and page map selection signals. Also shown are the PMAP.USED, PMAP.DIRTY, PMAP, 10 and PMAP LCL which are discussed in the memory management paragraph.

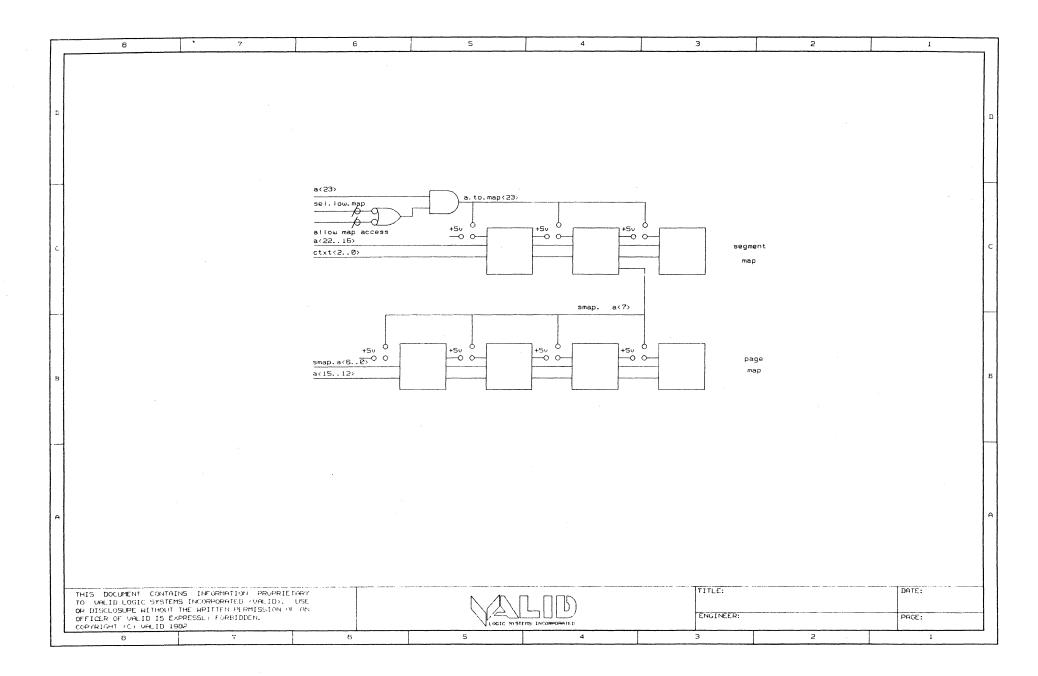

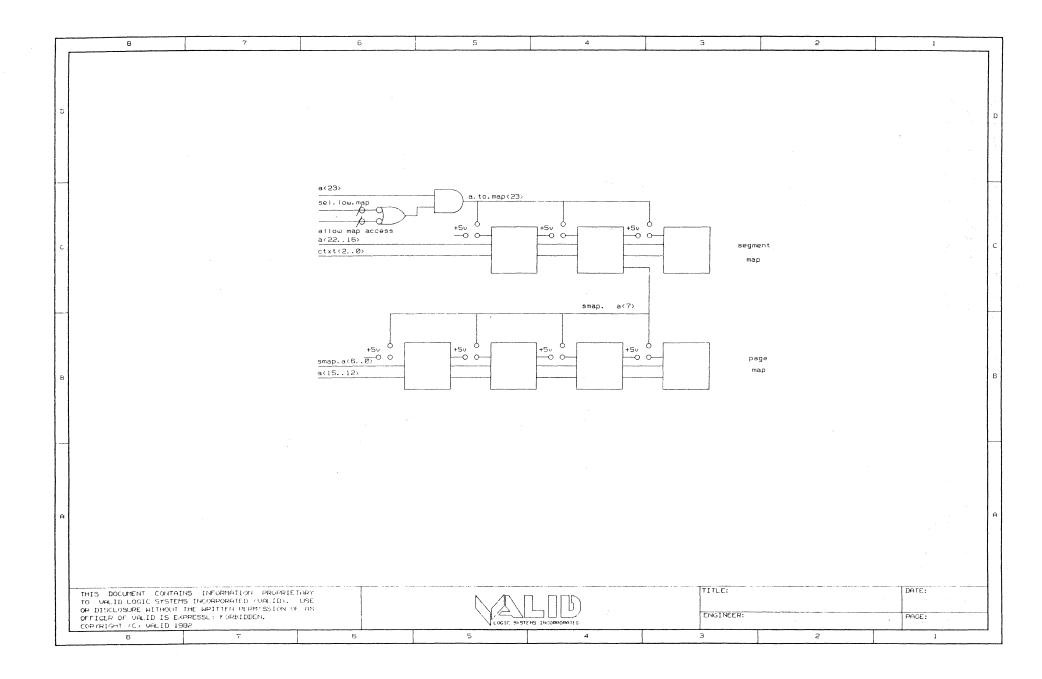

## 4.3 Segment and Page Map Strapping

The segment and page maps can be strapped to accept larger mapping RAMs. In that case, each of 16 processes can access a separate 16Mbyte logical address space containing 256 segments each of 16-4Kbyte pages. A diagram of the strapping configuration is shown in Figure 4-3. The strapping to a larger RAM mapping system involves using additional selection signals and address bit A<23> as shown instead of the +5V connection used for the VCC input of the smaller map. The segment map also provides the SMAP.A<7> bit for additional addressing space to the page map increased RAM size. This is also strapped to increase the addressing to the larger page map RAMs. The +5V input is then reconnected to the VCC input of the larger capacity RAMs.

## 4.4 Memory Management

The CPU board includes memory management sufficient to support a full capability multi-user operating system such as Unix runnning with 4Mbyte physical memory (16Mbyte using the 4K-map configuration. Each process can access to a separate 4Mbyte logical address space consisting of 64 pages of 64Kbyte each, which can be mapped anywhere within the 16Mbyte physical address space of the 796 bus.

As many as 16 processes can be mapped simultaneously. The low-order four bits of the context register (PID<3..0>) contains the process ID of the process currently being executed. In cases where there are more than 16 processes to be mapped, a process ID can be reused by reloading the appropriate section of the map.

100

As shown in Figures 4-1, 4-2, and 4-4, the segment table contains 1K entries and is addressed by the context 4-bit process ID concatenated with six logical address bits A<21..16> from the M68000LB. A segment table entry so addressed has the following format:

| FIELD  | NAME            | INTERPRETATION                    |

|--------|-----------------|-----------------------------------|

| <1512> | Undefined       |                                   |

| <118>  | ACCESS.MODE<30> | Per-segment legal access<br>modes |

| <76>   | Reserved        |                                   |

| <50>   | A<50>           | High crder page table<br>address  |

The high-order four bits of a segment table entry are undefined and can be neither read or written. The ACCESS.MODES<3..0> define the legal access modes for the segment which has the following structure:

| FIELD | NAME    | INTERPRETATION                   |

|-------|---------|----------------------------------|

| <3>   | USER    | User mode access<br>permitted    |

| <2>   | WRITE   | Writes permitted                 |

| <1>   | READ    | Data space reads<br>permitted    |

| <0>   | EXECUTE | Program space reads<br>permitted |

These bits have independent meanings. For example, a segment that is intended to have "supervisor-read or execute" access has ACCESS.MODES=3. Also note that all PC relative accesses are classified as "program space" accesses.

The page map table shown in Figure 4-4 contains 1K 16-bit entries and is addressed by concatenating the 6-bit field SMAP.A<5..0> from a segment table entry with the four logical address bits A<15..12> from the M68000LB. Each accessible segment requires 16 contiguous page table entries. However, not necessarily 16 pages of physical memory since page table entries can be marked "not present". A page table entry addressed in this manner has the following format:

| FIELD  | NAME         | INTERPRETATION                 |

|--------|--------------|--------------------------------|

| <1512> | PAGE.CONTROL | Per-page control bits          |

| <110>  | A<110>       | High-order physical<br>address |

Field A<11..0> is concatenated above the low-order 12 address bits from the M68000LB to form a full 24-bit 796 bus address. The PAGE CONTROL <3..0> field has the following format:

| FIELD | NAME  | INTERPRETATION                             |

|-------|-------|--------------------------------------------|

| <3>   | USED  | This page was accessed                     |

| <2>   | DIRTY | This page was written                      |

| <1>   | LOCAL | Accesses to this page<br>are not permitted |

| <0>   | 10    | I/O address                                |

The USED and DIRTY fields are updated by hardware when the page is accessed. The USED is set whenever the page is accessed and DIRTY is set whenever the page is written. The exception is USED and DIRTY are not changed if the access is illegal. If LOCAL = 1, then the access is not legal for example, the page does not exist in physical memory. Otherwise, if IO = 1, the access

is to 796 bus I/O space, and if IO = 0, then it is to 796 bus memory space. If either the segment or page table strobes are sent, USED and DIRTY are not updated, and the M68000LB is forced to execute a bus-error trap. The CPU error register captures the exact cause of the trap.

All 16 bits of a page table entry can be read or written using byte or word operations, as can all 12 defined bits of a segment table entry. To access either a segment table entry or a page table entry, the context register must be set up appropriately. The high-order address bit (A<23>) of the M68000LB must be set and the low-order 23 bits must be set as if the access were to some location within the segment or page concerned. The segment map can be accessed directly, but the page map is accessed by first setting up a location in the segment map and then addressing the page map through the segment map.

Since the high-order M68000LB address bit distinguishes map references, the M68000LB can do map operations interleaved with 796 bus operations, for example, copying from main 796 bus memory into the map. References with A<23> set are to the map, and references with A<23> clear are to the 796 bus.

Note that supervisor and user share a single logical-address space, allowing the supervisor direct access to user data structures.

If the map is strapped to accept larger mapping RAMs, each of 16 processes can access a separate 16Mbyte logical-address space containing 256 segments each of 16-4Kbyte pages.

# SECTION 5 CPU INTERRUPTS

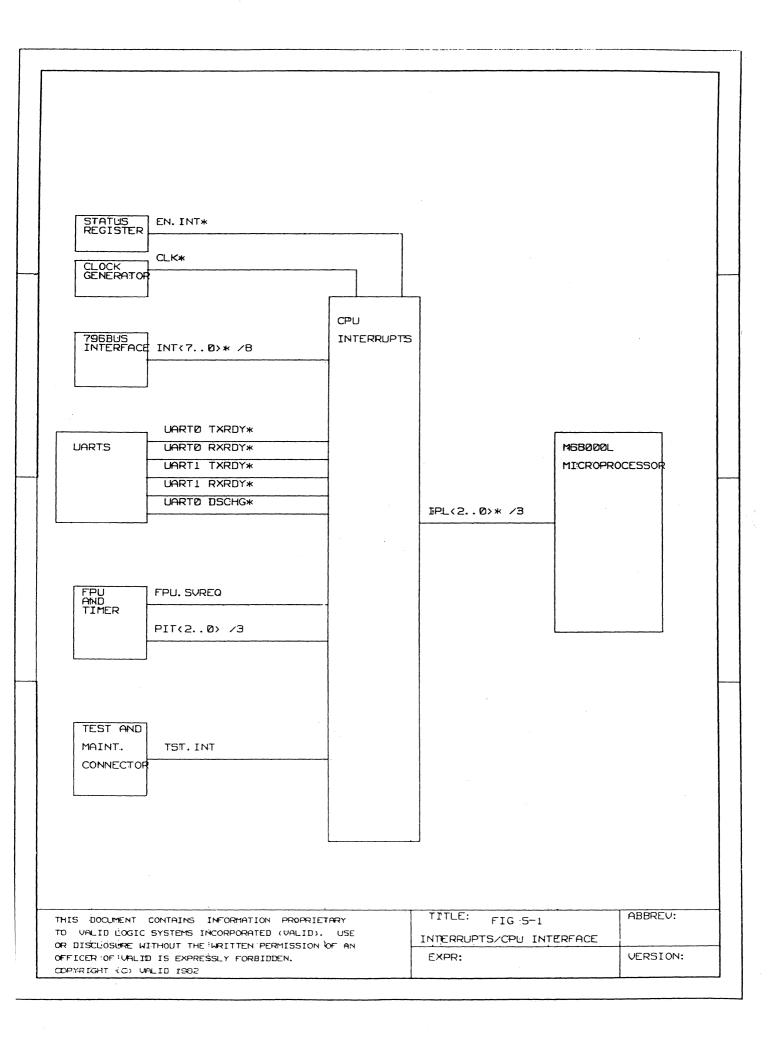

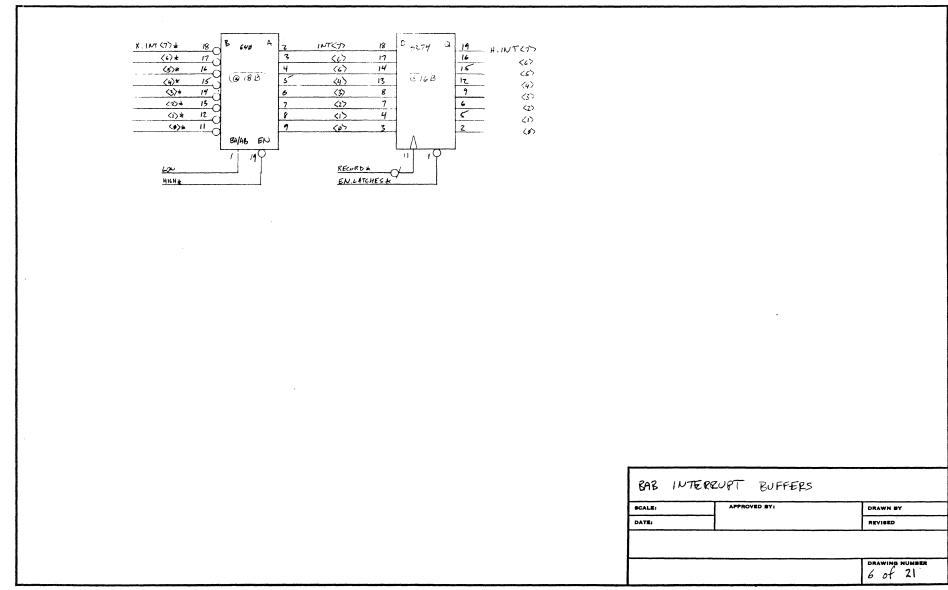

## 5.1 Interrupts/CPU Interface

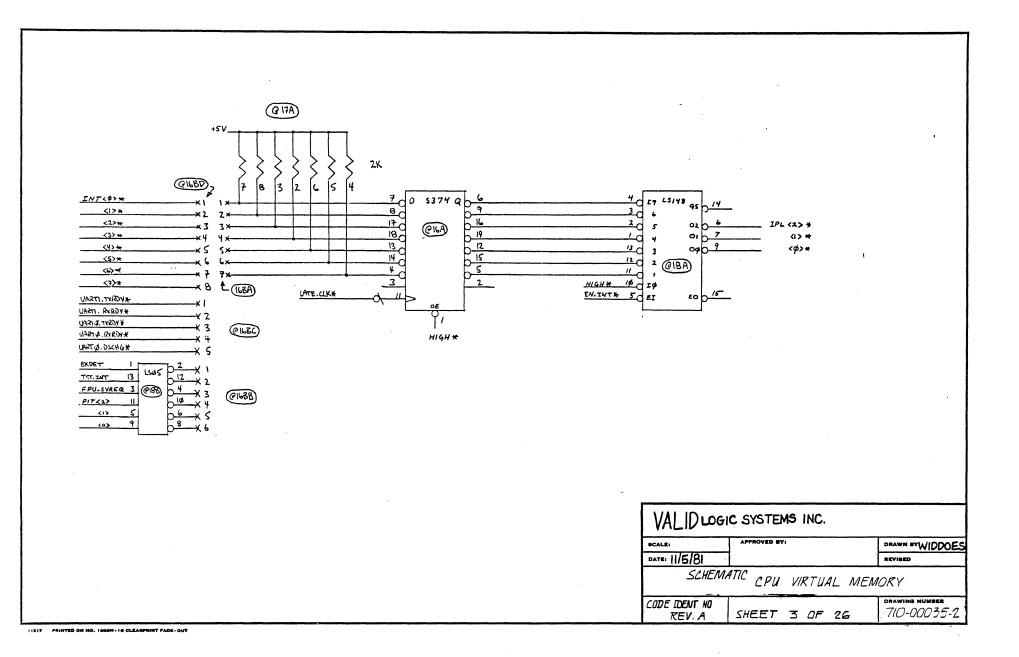

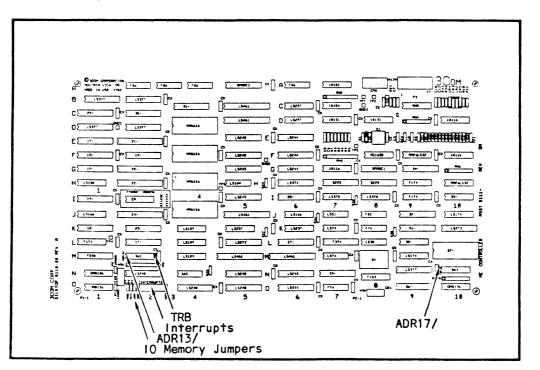

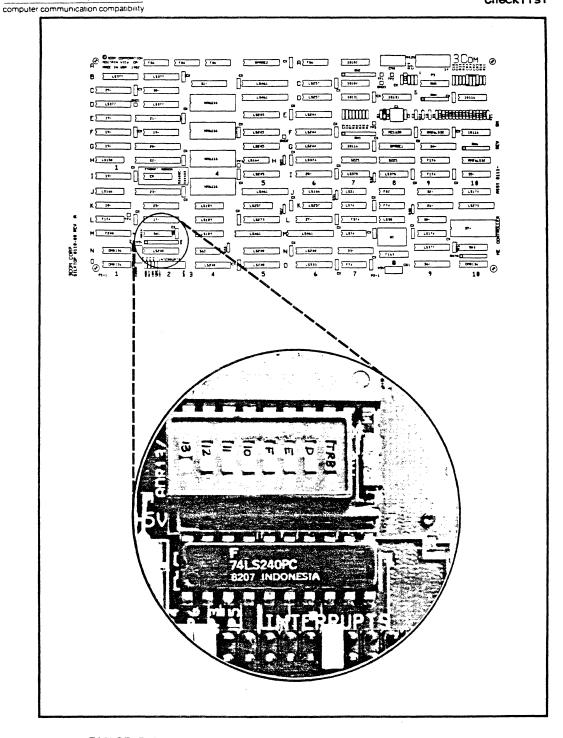

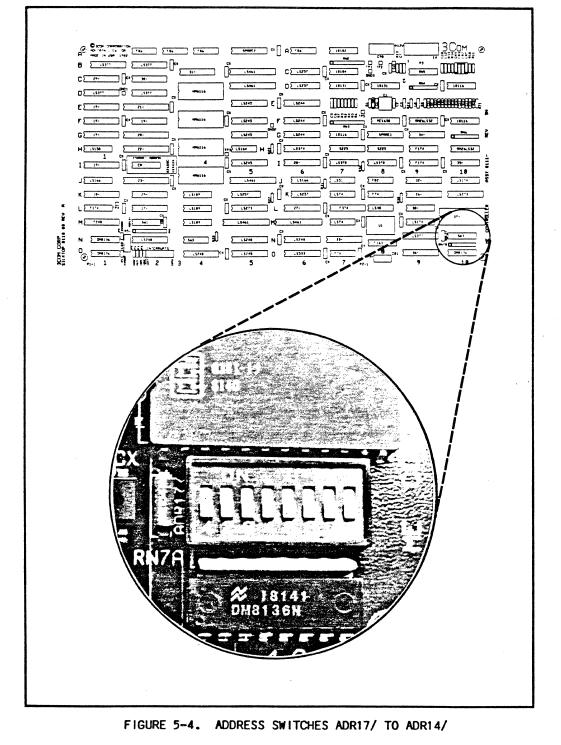

The CPU interrupts interface with the CPU as shown in Figure 5-1. Interrupts are received from the 796 bus interface, UARTS, FPU, and timer, and test and maintenance connector. The interrupts are strappable as described in the paragraphs that follow. The resulting interrupts to the M68000LB (3-bit code) are gated and clocked by EN.INT\* and CLK\* signals received from the status register and clock generator respectively.

The interupts operate asynchronously in auto-vector mode to deliver the three bits (IPL<2..0>\*) to the M68000LB. The bits track to one of seven fixed addresses. During interrupt cycles, the M68000LB address lines A<3..1> provide information about what level interrupt is being serviced while address lines A<23..4> are all set to logic high. During an interrupt acknowledge cycle, an external device supplies the vector number on data lines D<7..0>. Incoming interrupts are latched at the falling edge of the CLK\* pulse. During the time between clock pulses, the latches provide stability and settling time between the asynchronous priority inputs and the encoder. The 796 bus interrupts are further described in the discussion of the 796 bus in the sections that follow.

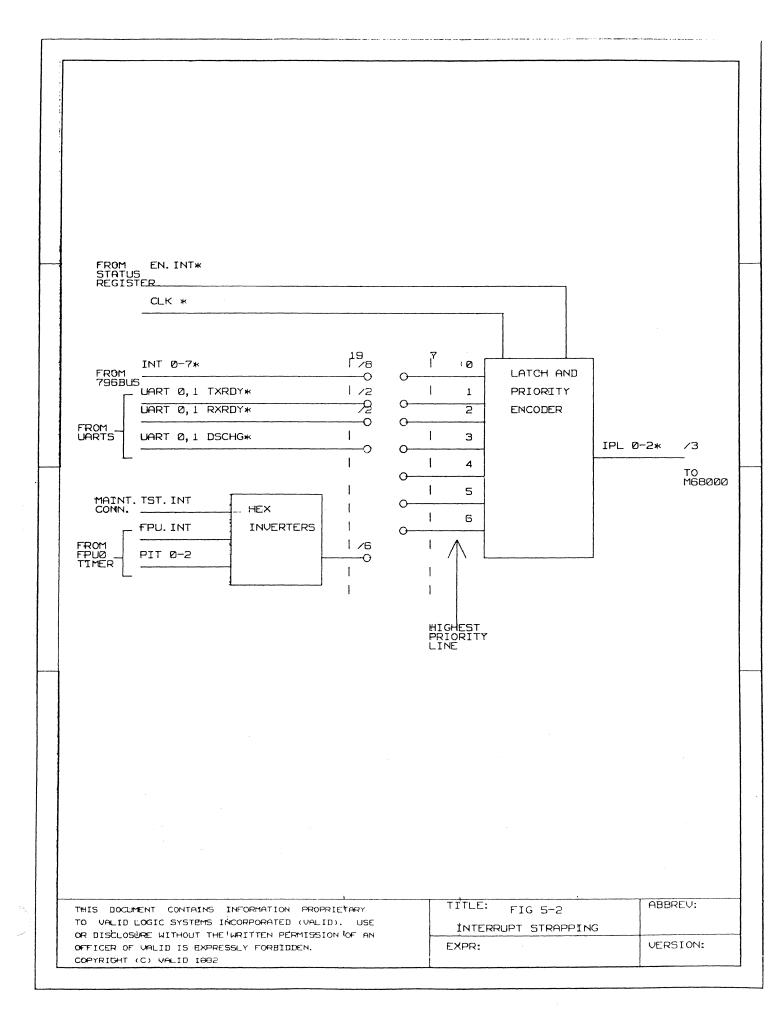

## 5.2 Interrupt Strapping

Any of the interrupts (19 total) can be strapped in any priority level to the seven inputs of the latches as shown in Figure 5-2. The seven latch cutputs are applied one-for-one to the priority encoder inputs and correspond to the priority scheme of the 796 bus (INT<7..0>) inputs as follows:

Line 7 = highest priority Line 1 = lowest priority Line 0 = no priority

# SECTION 6 796 BUS

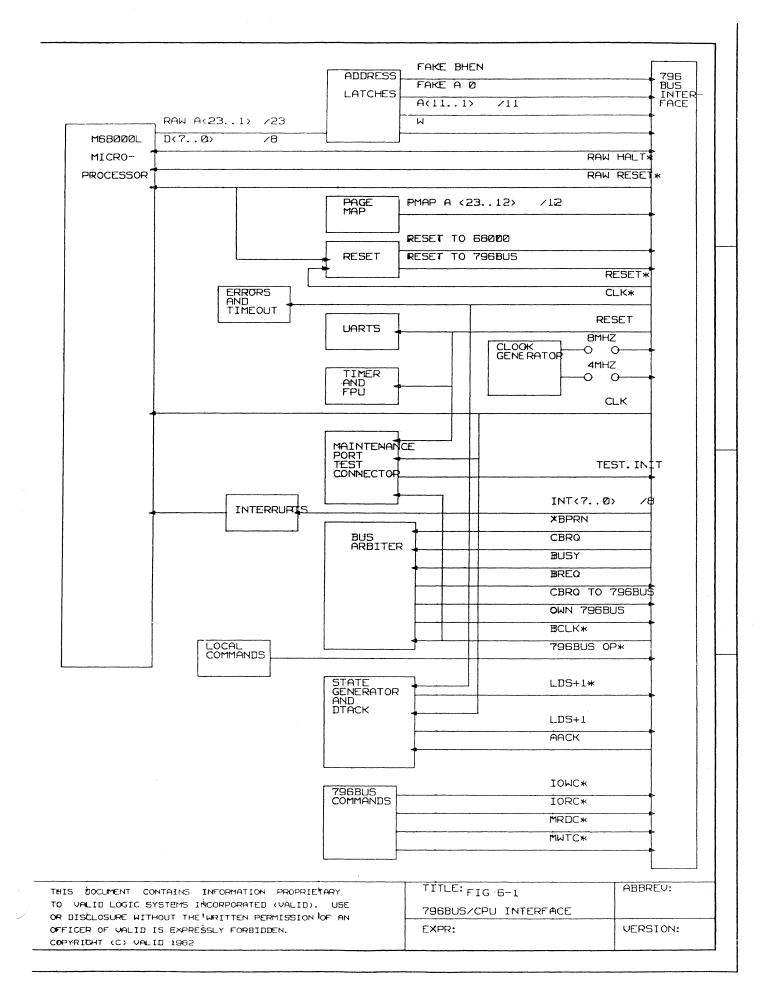

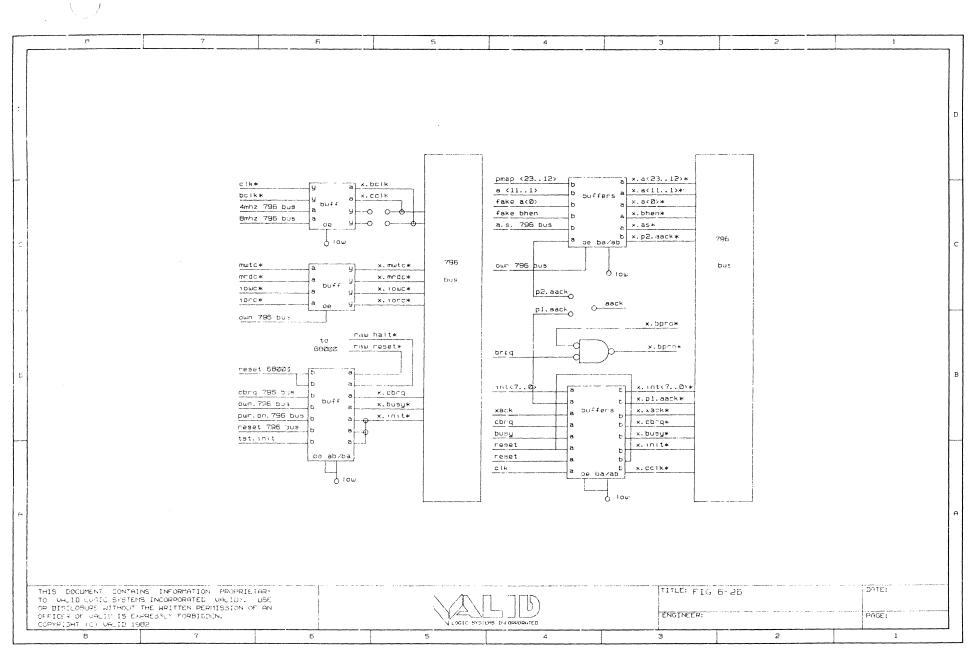

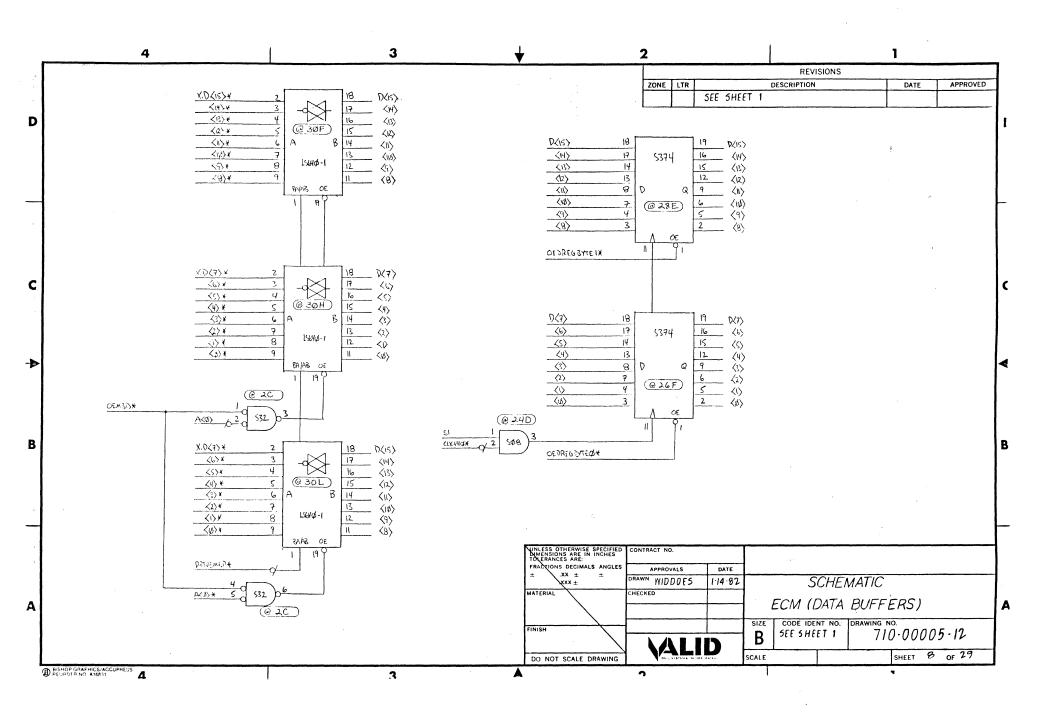

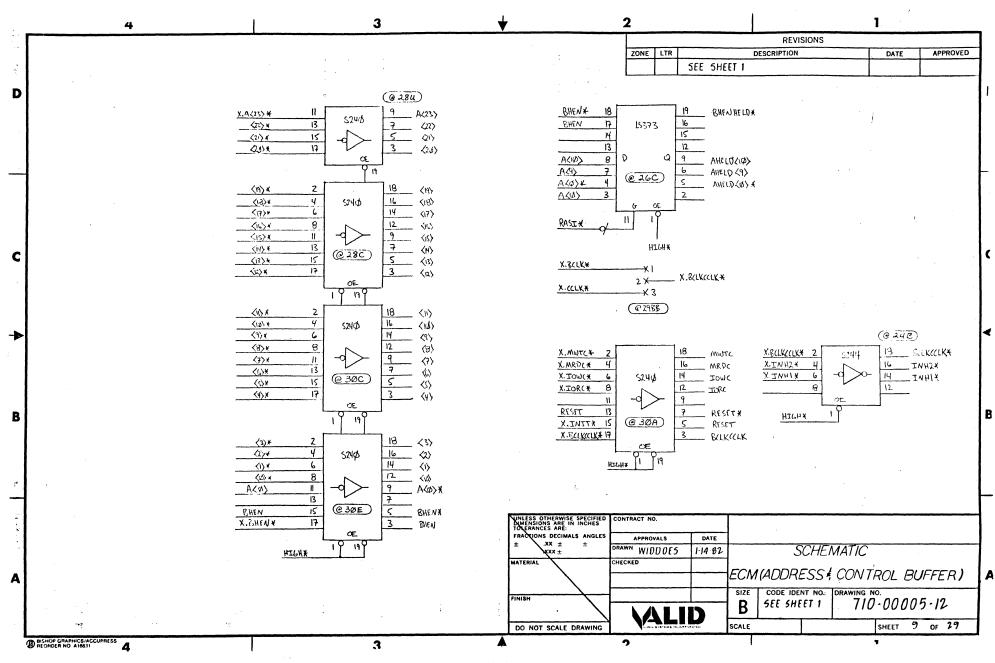

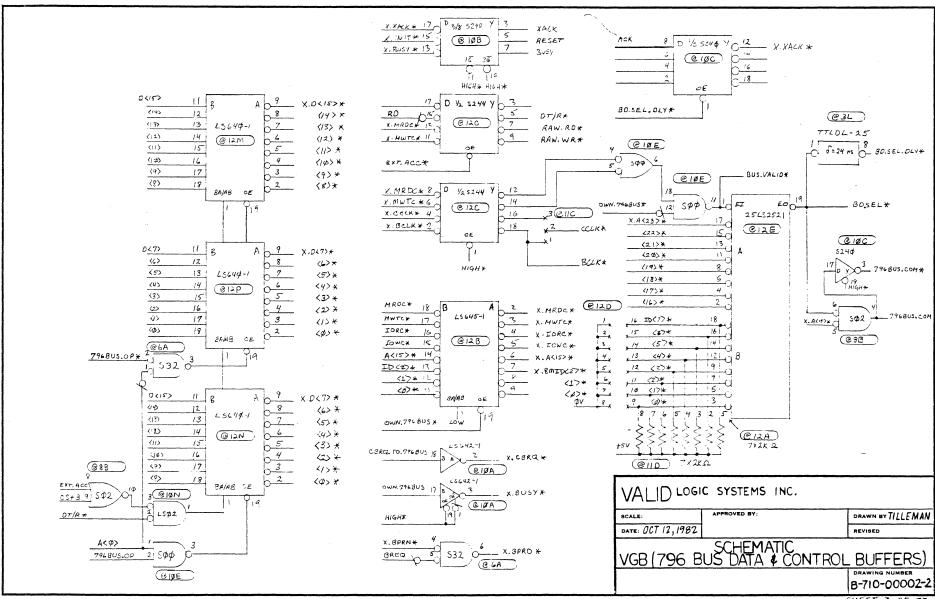

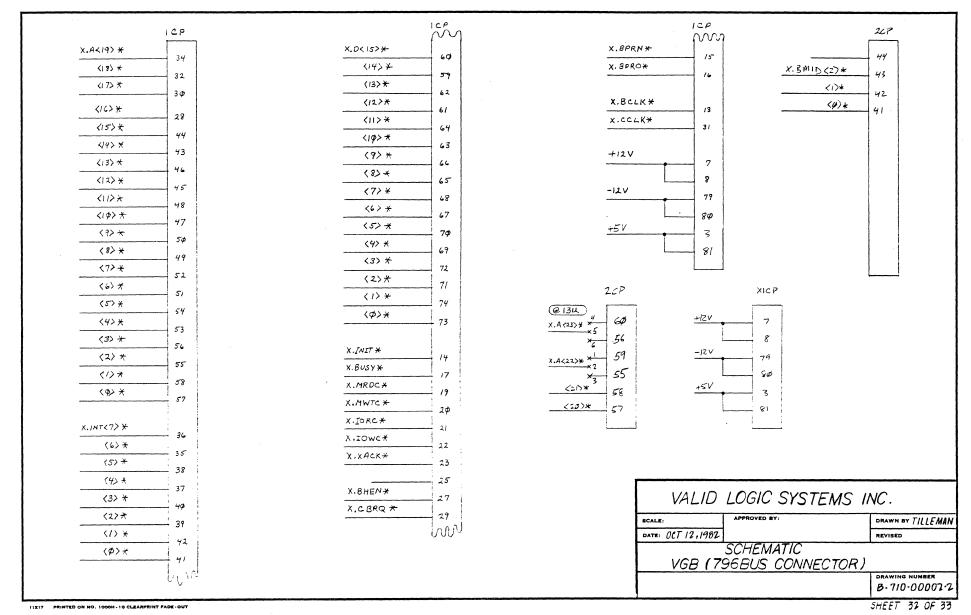

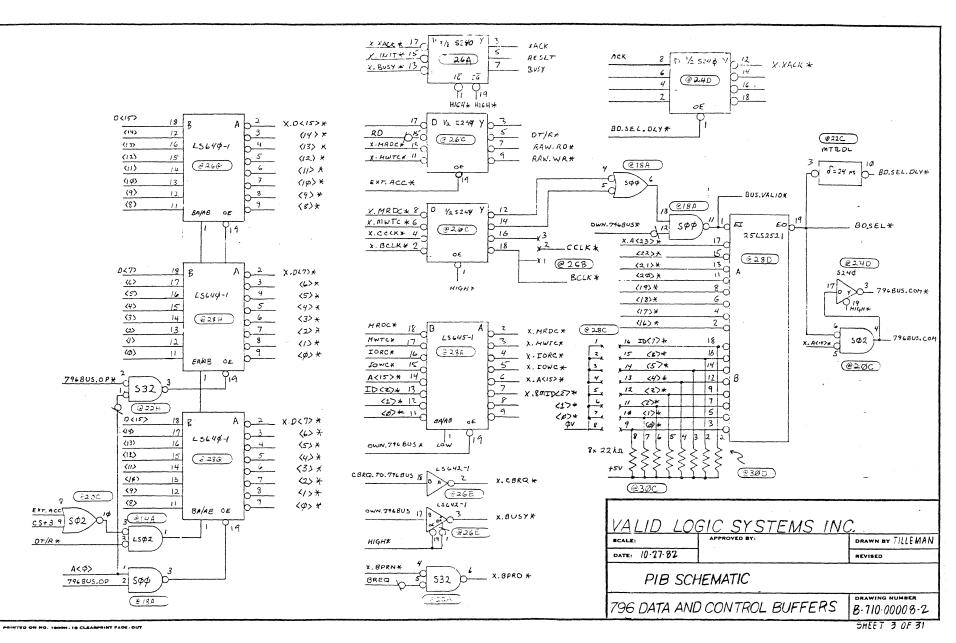

6.1 796 Bus Interface

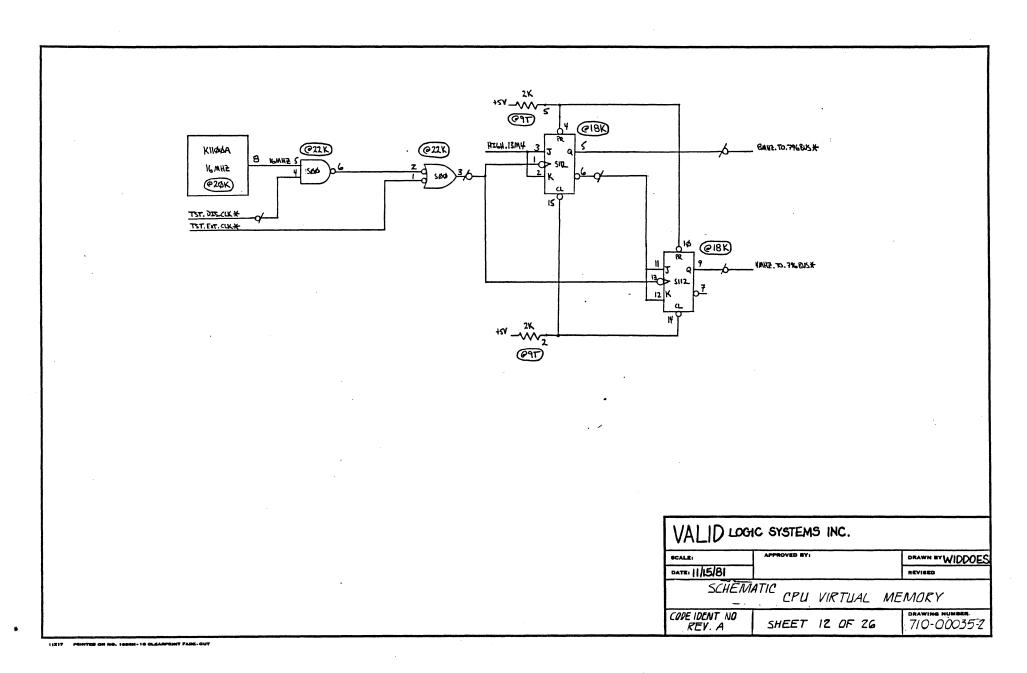

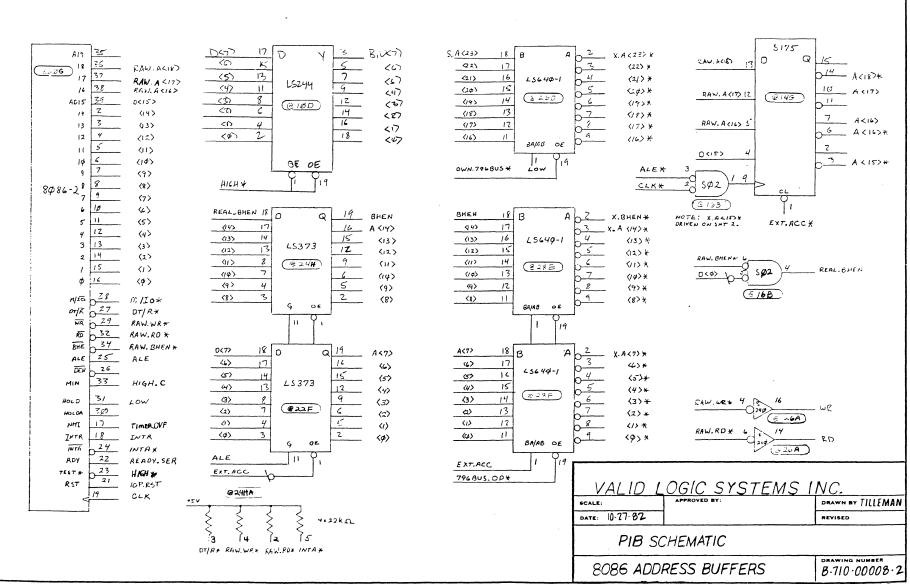

The CPU/796 bus interface with the M68000LB and various functions located on the CPU board is shown in Figure 6-1. A more detailed diagram of the internal 796 bus including gating and buffers is shown in Figure 6-2. The bus interface contained on the CPU board consists of the required number of buffers and control logic to completely interface the functions of the M68000LB CPU with the bus. The buffers provide gated bidirectional data paths for communication between the M68000LB and other devices attached to the bus. Synchronous, serial bus arbitration also allows a large number of bus masters to exist in a single system.

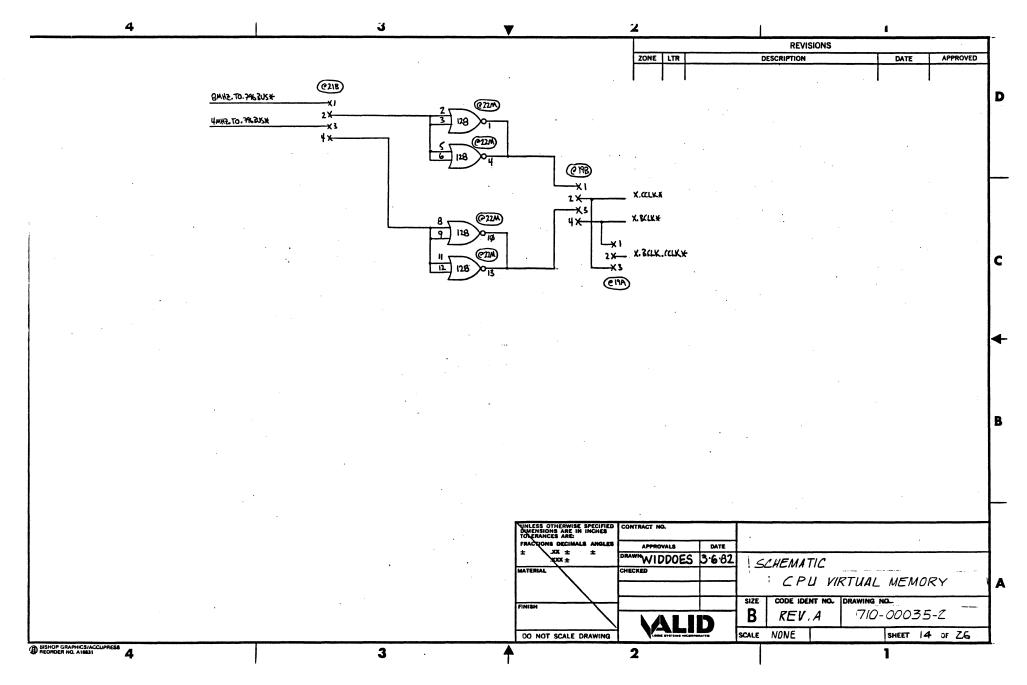

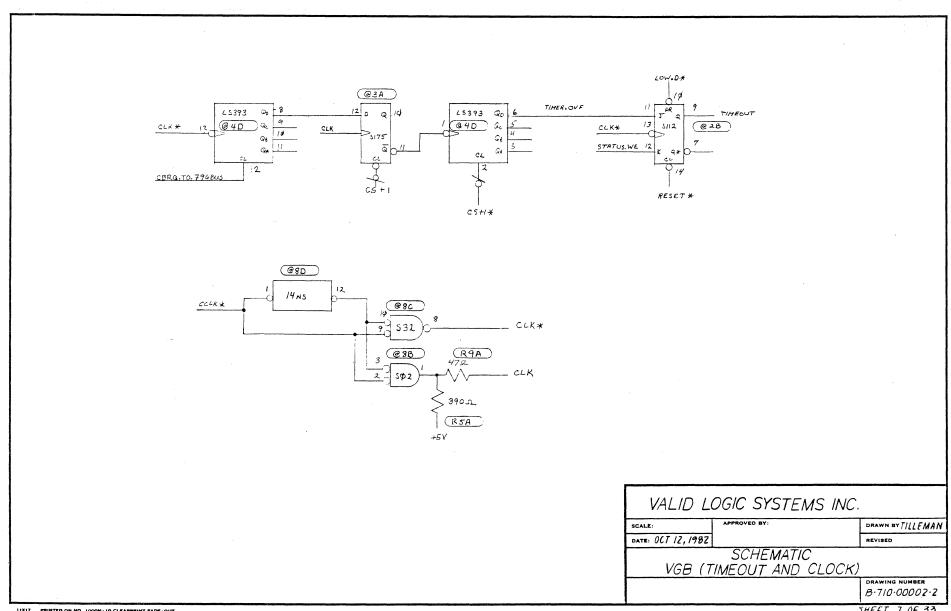

Straps are available to drive the CCLK\* and BCLK\* signals of the 796 bus at either a 4MHz or 8MHz synchronous rate with the M68000LB (BCLK\* at 4MHz allows a larger number of bus masters using serial arbitration). The XPU board drives the M68000LB from CCLK\* (CLK) received from the bus. Bus request logic is driven from BCLK\* also received from the 796 bus. In systems where more than one CPU exists, only one is strapped as a clock driver.

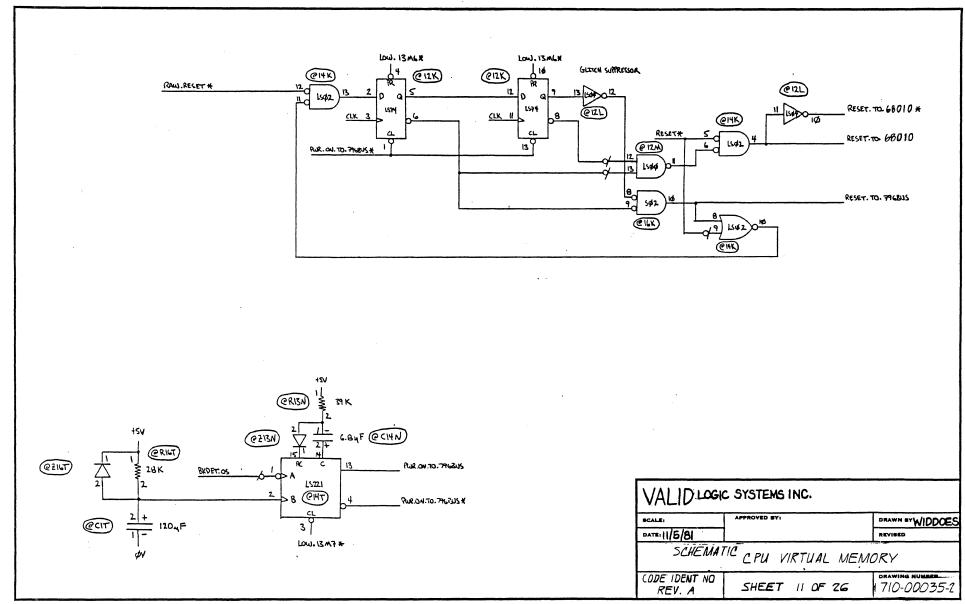

The CPU board both resets the bus or the board can be reset from the bus. The CPU devices are reset via an incoming X.INIT\* signal from the bus. The M68000LB executes a reset instruction to reset all on-board devices (except status and context registers and the M68000LB) and sends a RESET.TO.796 BUS pulse to generate X.INIT\* on the bus. A PWR.ON.TO 796 BUS pulse also resets the bus as well as a TST.INIT used during maintenance purposes.

Both byte and word bus operations are supported by this interface. In the M68000LB, low-order bytes of words have odd addresses, while on the 796 bus, high-order bytes of words have odd addresses. The interface therefore translates the low-order address bit of M68000LB addresses. The address sent over the 796 bus has the low-order address bit (A<0>) set when the M68000LB is doing an even byte access. The bit in turn is clear when the M68000LB is doing an odd byte access or a word access.

# 6.2 Non-Standard Bits

The non-standard 796 bus bits used in this system are shown below and are further described later in this section.

| CONNECTOR | PIN(s)         | SIGNAL     |

|-----------|----------------|------------|

| P1        | 25             | X.P1.AACK* |

| P2        | 40             | X.P2.AACK* |

| P2        | 39             | X.AS*      |

| P2        | 56,60          | X.A<23>    |

| P2        | 55 <b>,</b> 59 | X.A<22>    |

| P2        | 58             | X.A<21>    |

| P2        | 57             | X.A<20>    |

The 796 bus advanced acknowledge signal (X.AACK\*) is received on both connectors P1 and P2. The signal is strapped from one source or the other. The strapping of a tapped delay line minimizes the number of wait cycles the M68000LB executes while accessing 796 bus main memory.

The address strobe (X.AS\*) signal is driven on connector P2. The signal allows 796 bus main memory to start access before mapping is complete. This minimizes M68000LB wait cycles while accessing memory boards which use the AS\* signal.

Four high-order address bits (X.A<23..20>) are also driven on connector P2. Two different standards exist for the positions of X.A<22> and X.A<23> on P2. The bits are therefore driven according to both of these standards to allow the use of memory or peripheral board conforming to either standard.

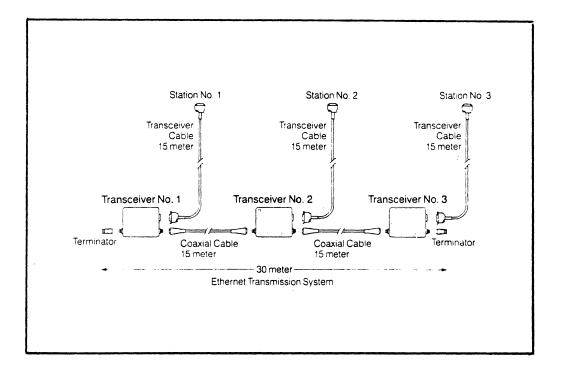

6.3 796 Bus Description

The following paragraphs provide a general overview of the 796 bus operations. For more information as to the specific timing and technical details, refer to IEEE 796 specifications and related technical reference data listed under "Related Documents" contained in this manual.

- o 20 address lines

- o 16 bi-directional data lines

- o 8 multilevel interrupt lines

- o 16 bus control lines

- o 1 bus clock

- o 8 interrupt lines to M68000LB

- o Power supply lines

The 796 bus connects to the CPU board by means of connectors P1 and P2. Connector P1 contains the signal groups listed above. Connector P2 contains optional signal lines.

The address and data lines are driven by three-state devices. The interrupt and other control lines are open-collector driven.

# 6.3.1 Master-Slave Relationship

The 796 bus provides for both 8 and 16-bit bus masters and slaves. A bus master module (such as the CPU board) drives the command and address lines and controls the bus. A bus slave cannot control the bus and only performs functions based on commands from the bus. A particular system may have a number of masters. In this case, bus arbitration results when more than one requests control of the bus.

6.3.2 Bus Clock

A bus clock is provided by one bus master and is derived independent of the processor clocks. The bus clock is placed on the bus then routed back into the providing bus master equally with other boards connected to the bus. This is to prevent skewing of the clock between the source and other users. The bus clock provides a timing reference for bus arbitration between bus masters in cases where multiple requests occur from more than one bus master. Once a bus request is granted, single of multiple read/write transfers occur. Actual transfers on the bus proceed asynchronously with respect to the bus clock.

The signals that make up the 796 bus interface for both connectors P1 and P2 are listed in table 1 and 2 respectively. The signal name and active logic level (\* = active low) is listed as well as the function for each signal.

Table 6-1. 796 Bus Interface Signals (P1)

**FUNCTION** SIGNAL X.INIT\* Resets the entire system to a known (Initialize) state. Driven from bus master or front panel reset switch. 20 address lines used to transmit X.ADRO\* - X.ADR9\* X.ADRA\* - X.ADRF\* address of memory location or 1/0 port to be accessed. X.ADRIO\* - X.ADR13\* (Address Lines) X.BHEN\* Address control line used to specify (Byte High Enable) that data will be transferred on the high byte (X.DAT8\*-- X.DATF\*) 796 bus data lines. X.INH1\* Prevents ROM memory from responding (Inhibit RAM) to the memory address on the system address bus. X.INH2\* Prevents ROM memory from responding (Inhibit ROM) to the memory address on the system address bus. X.DATO\* - X.DATF\* Bi-directional lines used to transmit (Data Lines) or receive information to or from a memory location or 1/0 port.

# Table 6-1. 796 Bus Interface Signals (P1) (Continued)

| SIGNAL                       | FUNCTION                                                                                                                                                                                                      |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X.BCLK*<br>(Bus Clock)       | X.BCLK is asynchronous to the processor<br>clock. Negative edge (high to low)<br>is used to synchronize bus priority<br>resolution circuits. May be slowed,<br>stopped, or single stepped for de-<br>bugging. |

| X.CCLK*<br>(Constant Clock)  | Provides a constant clock signal for<br>general use by modules on the system<br>bus.                                                                                                                          |

| X.BPRN<br>(Bus Priority-In)  | Synchronized with X.BCLK*. Indicates to<br>a particular bus master that no higher<br>priority module is requesting use of<br>the system bus.                                                                  |

| X.BPRO<br>(Bus Priority-Cut) | Synchronized with X.BCLK*. Supplied to<br>BPRN* input of the master module with<br>the next lower bus priority.                                                                                               |

| X.BUSY*<br>(Bus Busy)        | Synchronized with X.BCLK*. Open-<br>collector line driven by bus master<br>currently in control tc indicate<br>bus is currently in use.                                                                       |

| X.BREQ*<br>(Bus Request)     | Synchronized with X.BCLK*. Indicates<br>a particular bus master requires use<br>of the bus for one or more data<br>transfers.                                                                                 |

# Table 6-1. 796 Bus Interface Signals (P1) (Continued)

SIGNAL

# FUNCTION

X.CBRQ\*

Open-collector line driven by all

(Common Bus potential bus masters to inform

Request)

the current master that another

wishes to use bus. If high, indicates to bus master no other bus

master is requesting bus.

X.MDRC\*Asynchronous with respect to X.BCLK\*.(Memory ReadIndicates address of a memory loca-<br/>tion is placed on system address<br/>lines and specifies contents of the<br/>addressed location are to be read<br/>and placed on system data bus.

X.MWTC\* (Memory Write Command) Asynchronous with respect to X.BCLK\*. Indicated address of a memory location is placed on system address lines and that data is placed on the system data bus.

X.IORC\* Asynchronous with respect to X.BCLK\*.

(I/O Read Command) Indicates address of an input port is placed on system address bus and data is to be read and placed on system data bus.

X.IOWC\* (I/O Write Command) Asynchronous with respect to X.BCLK\*. Indicates address of an output port is placed on system address bus and contents of system data bus are output to the address port.

Table 6-1. 796 Bus Interface Signals (P1) (Continued)

| SIGNAL                                                 | FUNCTION                                                                                                                   |

|--------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| X.AACK<br>(Transfer<br>Acknowledge)                    | Asynchronous with respect to BCLK*.<br>Indicates specific slave board<br>read/write operation is complete.                 |

| X.INTO* - X.INT7*<br>(Asynchronous<br>Interrupt Lines) | Eight parallel interrupt lines used with interrupt resolution network.                                                     |

| X.INTA*<br>(Interrupt<br>Acknowledge)                  | Line driven by bus master transfer<br>of interrupt information onto bus<br>from slave priority interrupt con-<br>trollers. |

| Table 6-2.                                             | 796 Bus Interface Signals (P2)                                                                                             |

| SIGNAL                               | FUNCTION                                                                                                                                                                  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X.AACK                               | Same as P1.                                                                                                                                                               |

| X.ACLO<br>(AC Low)                   | Monitor AC line voltage. Goes true<br>when voltage drops below predefined<br>level. Goes false when all DC voltages<br>return to approximately 95% of<br>requested value. |

| X.AS*                                | Allows main memory to start accessing before mapping is complete.                                                                                                         |

| X.PFIN*<br>(Power Fail<br>Interrupt) | Interrupts processor when power failure occurs.                                                                                                                           |

| X.PFSN*<br>(Power Fail Sense)        | Latched output that indicates power failure has occurred.                                                                                                                 |

Table 6-2. 796 Bus Interface Signals (P2) (Continued)

| SIGNAL                                 | FUNCTION                                                                                           |

|----------------------------------------|----------------------------------------------------------------------------------------------------|

| X.A<2320>                              | Allows use of memory or peripheral boards.                                                         |

| X.PFSR*<br>(Power Fail<br>Sense Reset) | Used to reset power fail sense latch<br>(PFSN*)                                                    |

| X.MPRO*<br>(Memory Protect)            | Prevents memory operation during<br>period of uncertain DC power by<br>inhibiting memory requests. |

| X.ALE<br>(Address Latch<br>Enable)     | Generated by CPU to provide auxil-<br>liary address latch.                                         |

| X.HALT*                                | Indicates master CPU is halted.                                                                    |

| X.AUX RESET*                           | Initiates power up sequence.                                                                       |

| X.WAIT<br>(Bus Master Wait<br>State)   | Indicates processor is in wait state.                                                              |

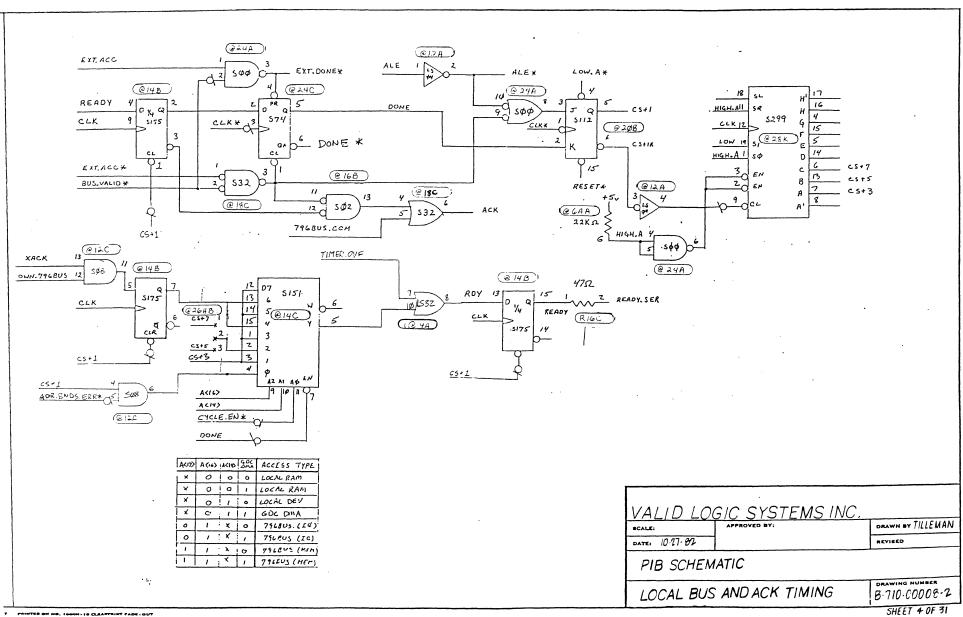

6.3.4 Data Transfers, Inhibit, and Interrupt Operations

Data transfer on the 796 bus consists of transferring read and write data. A typical data transfer occurs with a maximum bandwidth of 5MByte/sec for both single or multiple read/write transfers. Due to bus arbitration and memory access time, a typical maximum transfer rate is often on the order of 2MByte/sec.

6.3.4.1 Read Data. The read operation time is used by the 796 bus interface to decode the address and provide the required device selects. The device selects establish the data paths on the user system in anticipation of the

command strobe that follows. The read operation is initiated by the X.AS\* signal from the M68000LB followed by strobe command (X.IORC\* or X.MRDC\*). Valid data is driven onto the bus following the command and is not removed until the command is cleared. When the command is cleared, the X.ACK\* signal indicates the operation is complete.

6.3.4.2 Write Data. During a write data operation, valid data is presented simultaneously with a stable address. Stable data before and after X.IOWC or X.MWTC enables the bus interface to latch data on either the leading or trailing edge of the command. The X.ACK\* signal indicates the operation is complete.

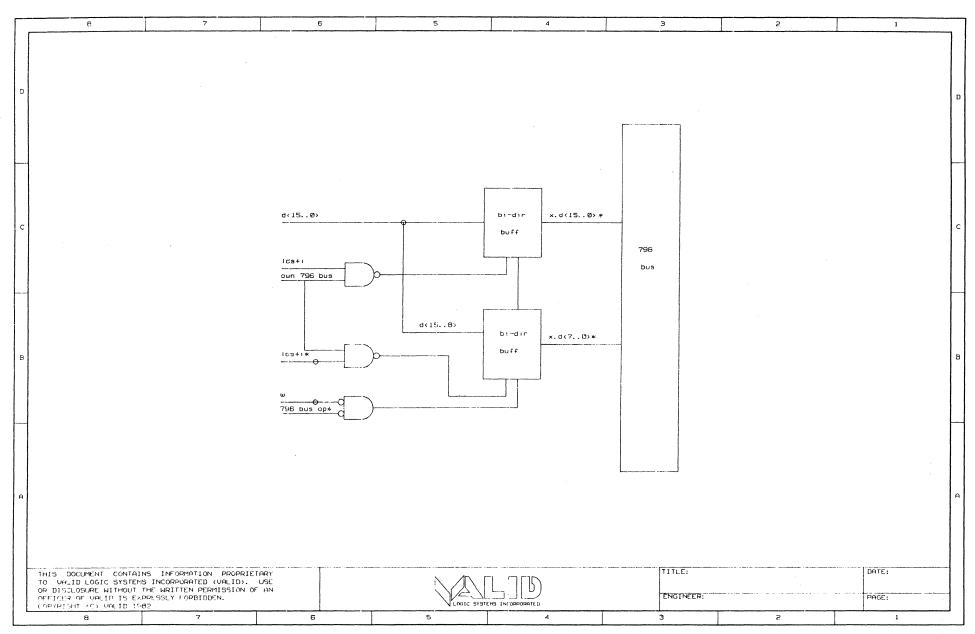

A 16-bit master transfers data on the data lines using 8-bit or 16-bit paths depending on whether byte or work (2-byte) operation is specified. A word transfer specified with an odd I/O or memory address is actually executed as two single byte transfers on the data lines.

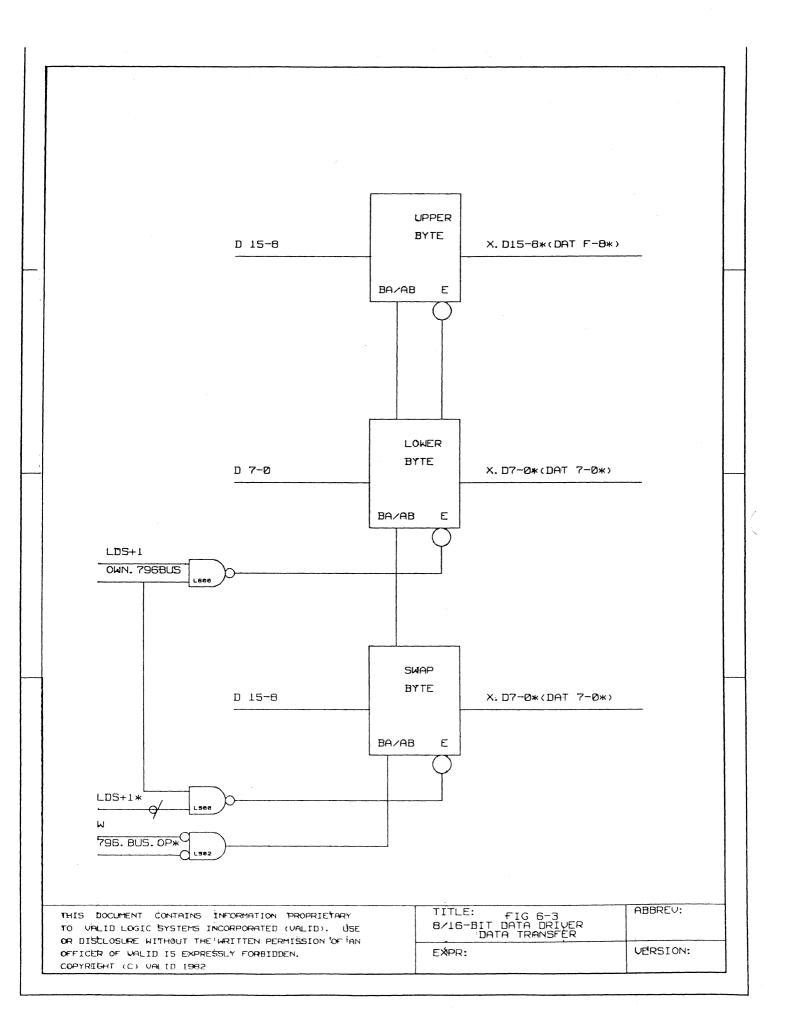

To adapt to both 8 and 16-bit devices, three buffers are used: lower, upper, and swap byte as shown in Figure 6-3. The lower byte buffer accesses X.DATO\* through X.DAT7\*, the upper accesses X.DAT8\* through X.DATF\*, and the swap buffer accesses 796 bus data lines X.DATO\* through X.DAT7\* and transfers the data from board data lines D8 through D15 and visa versa depending on the direction selected by the control logic. A read operation transfers low byte to high byte, a write transfers high to low.

6.3.4.3 Inhibit. Bus inhibit operations are required by bootstrap and memory mapped 1/0 configurations. The inhibit operation allows a combination of RAM/ROM memory mapped 1/0 to occupy the same memory address space. In the case of a bootstrap, it may be desirable to have both ROM and RAM occupy the same address space selecting ROM instead of RAM for low order memory only when the system is reset. Also, a system which has actual memory occupying the memory mapped 1/0 address space may need to inhibit RAM or ROM memory to perform its functions.

6.3.4.4 Interrupts. The interrupt lines (X.INTO\* through X.INT7\*) are used by a bus master to receive interrupts from bus slaves, other bus masters, or external logic such as power fail. The bus master may also contain external

interrupts (such as on the M68000LB CPU) which do not require the bus interrupt lines to interrupt the master.

There are two interrupt schemes used by bus interrupts: vectored and nonvectored. The M68000LB uses the vectored type of interrupts with the vector provided over the 796 bus address lines. The vectored interrupts are transferred from the slave to the bus master, when the master issues the X.INTA\* command signal in response to an interrupt. When an interrupt occurs, the interrupt control logic in the CPU interrupts the M68000LB.

In single board systems which use a CPU board capable of bus vectored interrupt operation, the X.BPRN\* pin must be grounded at master only if slave boards are to be accessed.

6.3.5 Slave Interface

The three basic elements of a slave bus interface are address decoders, bus drivers, and control logic.

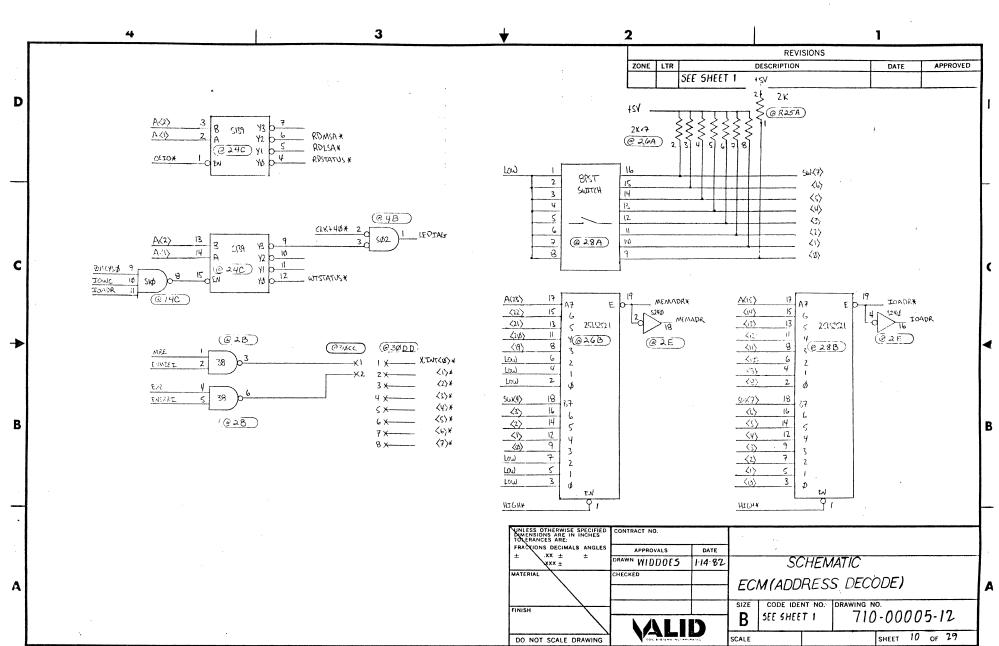

6.3.6 Address Decoding

The address decode logic decodes the appropriate 796 bus address bits into RAM or ROM requests, or 1/0 selects.

6.3.7 Data Bus Drivers and Receivers

For users which only receive data from the 796 bus, buffers are used to ensure that maximum allowable bus loading is not exceeded. In systems that place data onto the 796 bus data lines, three state drivers are required. For both read and write functions, bi-directional bus drivers are used.

# 6.3.8 Control Signal Logic

The control signal logic consists of circuits that forward I/O and memory read/write commands to their respective destinations, provide the bus with a transfer acknowledge response, and drive system interrupt lines.

# 6.3.9 Power Failures

Power failures are monitored by lines provided by connector P2. The power supply monitors the AC power level and when the power drops below an acceptable level, the supply raises the ACLO line. This tells the power fail logic that three milliseconds remain before the DC power falls below the regulated voltage levels. The power fail logic then sets a sense latch (X.PFSN\*) and generates an interrupt (X.PFIN\*) to the processor. After a 2.5 millisecond timeout, the memory protect signal (X.MPRO\*) is asserted by the power fail logic to prevent any memory activity. As power fails, the memory goes on standby power.

As the AC line revives, the logic voltage level is monitored by the power supply. After power returns to its operating level for one millisecond minimum. The power supply sets the X.ACLO\* signal to begin a restart sequence. This starts when the X.MPRO\* then the X.INIT\* become inactive. The bus master running then checks the power fail latch (X.PFSN\*). If the latch is set, the power up routine branches to reset the latch (X.PFSR\*), restore the environment, and resume execution.

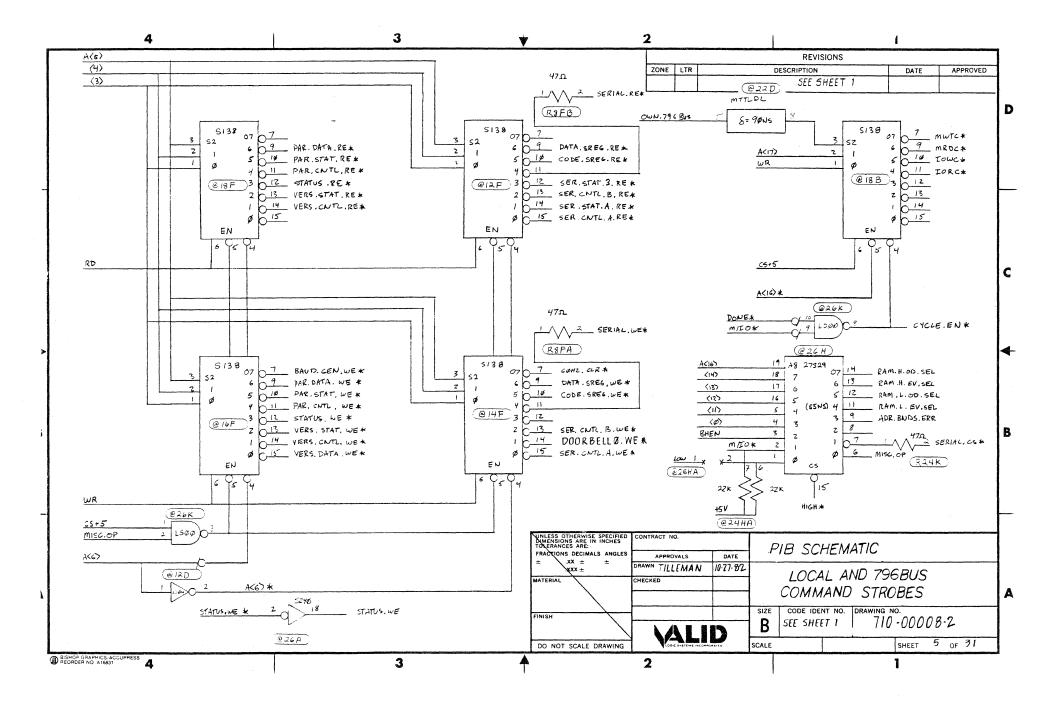

# SECTION 7 796 BUS COMMANDS

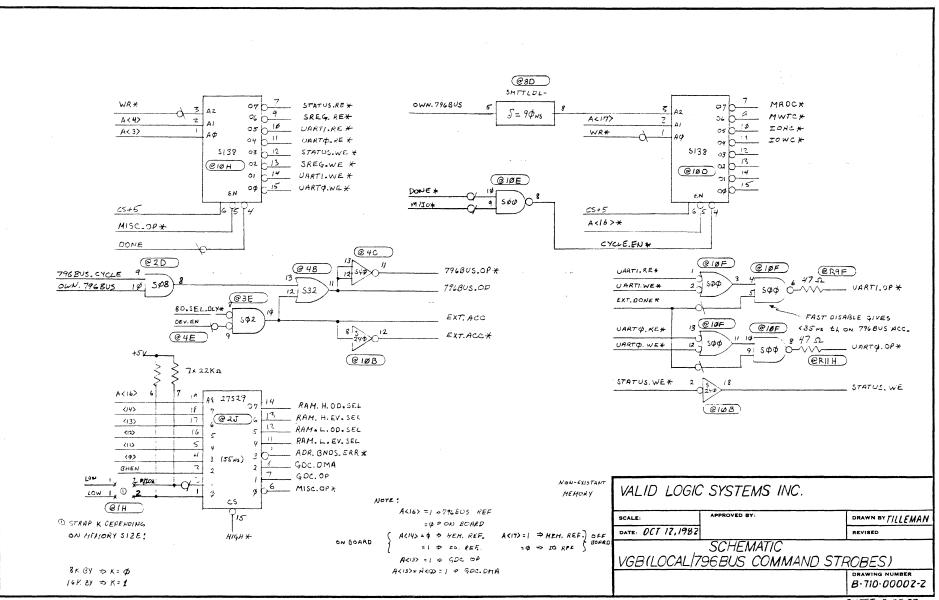

# 7.1 796 Bus Commands/CPU Interface

The 796 bus commands/CPU interface is shown in Figure 7-1. The 796 bus commands logic receives various enables, address lines, error inputs, and disables from the following CPU functions:

- o Address latches

- o Page map

- o Errors and timeout

- o Local commands

- o State generation and DTACK

Based on the configuration of the input signals (with no disables or errors), the command logic provides one of the following four commands to the 796 bus interface:

o IOWC\* : I/O write command

c IORC\* : I/O read command

o MWTC\* : Memory write command

c WRDC\* : Memory read command

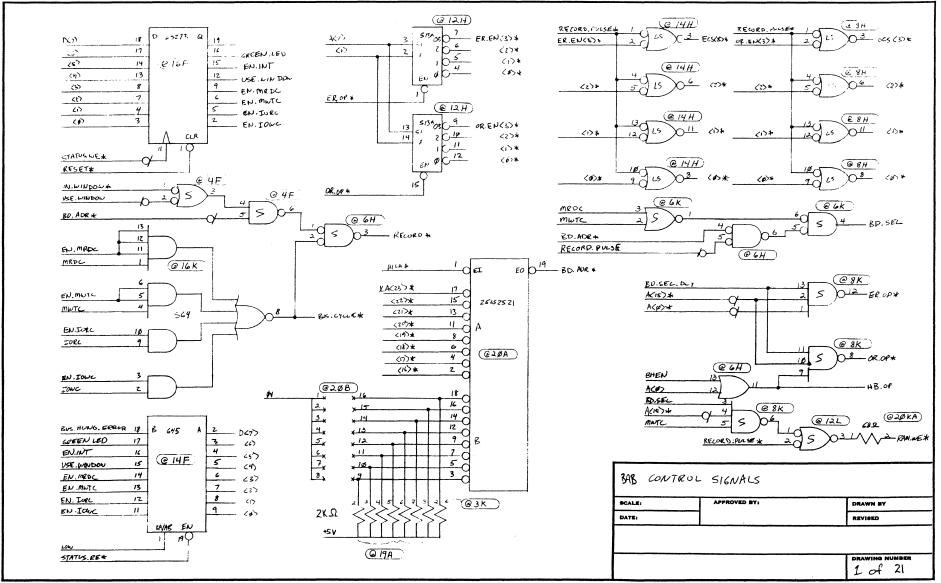

7.2 796 Bus Commands Detailed Description

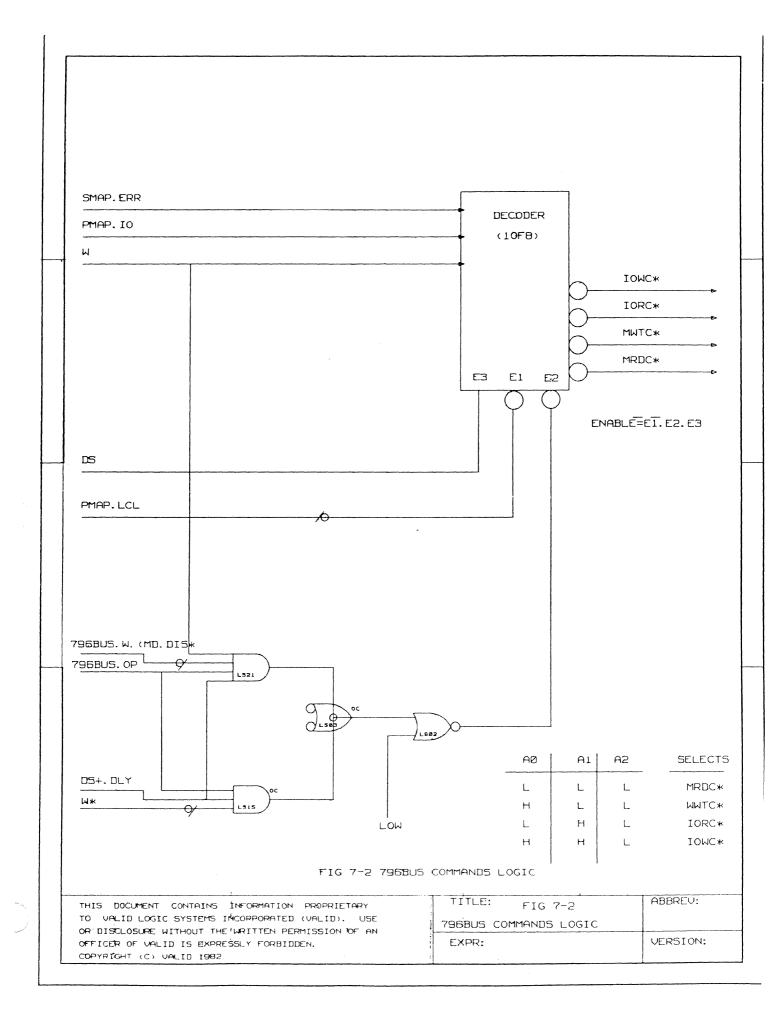

The 796 bus commands logic is shown in Figure 7-2. The logic consists of a one of eight decoder and associated enable gating. The decoder generates one of four outputs based on the address inputs (A0 through A2) when the decoder is enabled.

Either AND gate is enabled by a 796 BUS.OP true previous to a delayed data strobe (DS+2.DLY) occurring. The particular gate activated depends on the condition of the read/write selection lines (W and W\*). The read output enable can always be activated however, the write function can be disabled by a 796 BUS.W.CMD.DIS\* input. Without the disable or an SMAP.ERR present,

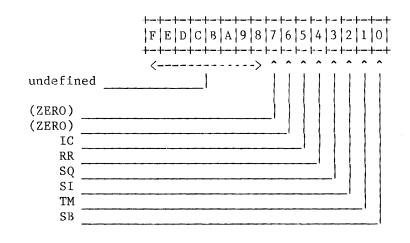

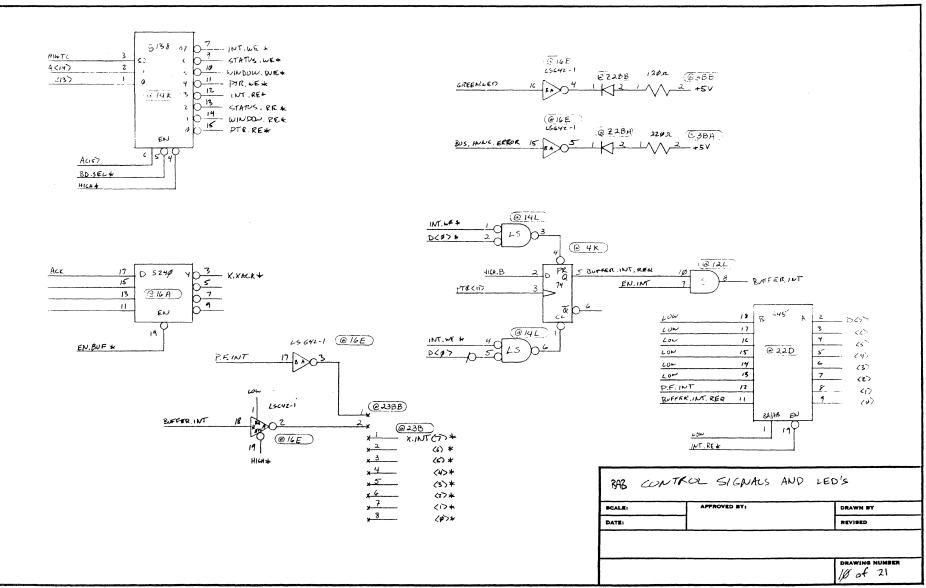

796BUS Μ COMMANDS ADDRESS LATCHES **₩**\* PMAP.LCL PAGE MAP PMAP. I/O IOWC\* 796BUS IORC\* INTERFACE ERRORS AND TIMEOUT SMAP.ERR MWTC\* MRDC\* LOCAL 7.968US. OP 796BUS. W. CMD. DIS\* STATE GENERATION DS AND DTACK DS DS+2. DLY FIG 7-1 796BUS COMMANDS/CPU INTERFACE ABBREV: TITLE: TLE: FIG 7-1 796BUS COMMANDS CPU INTERFACE THIS DOCUMENT CONTAINS INFORMATION PROPRIETARY / TO VALID LOGIC SYSTEMS INCORPORATED (VALID). USE OR DISCLOSURE WITHOUT THE WRITTEN PERMISSION OF AN EXPR: VERSION: OFFICER OF VALID IS EXPRESSLY FORBIDDEN. COPYRIGHT (C) VALID 1982

the enable decoder address inputs provide one of the four selected outputs as follows:

PMAP.IO W = IOWC\* PMAP.IO W = IORC\* PMAP.IO W = MWTC\* PMAP.IO W = MRTC\*

The SMAP.ERR signal sets all four I/O and memory output read/write selection lines to high therefore disabling the command function. After the error, a reset from the M68000LB to the errors and timeout logic resets the SMAP.ERR line thus re-enabling the command decoder.

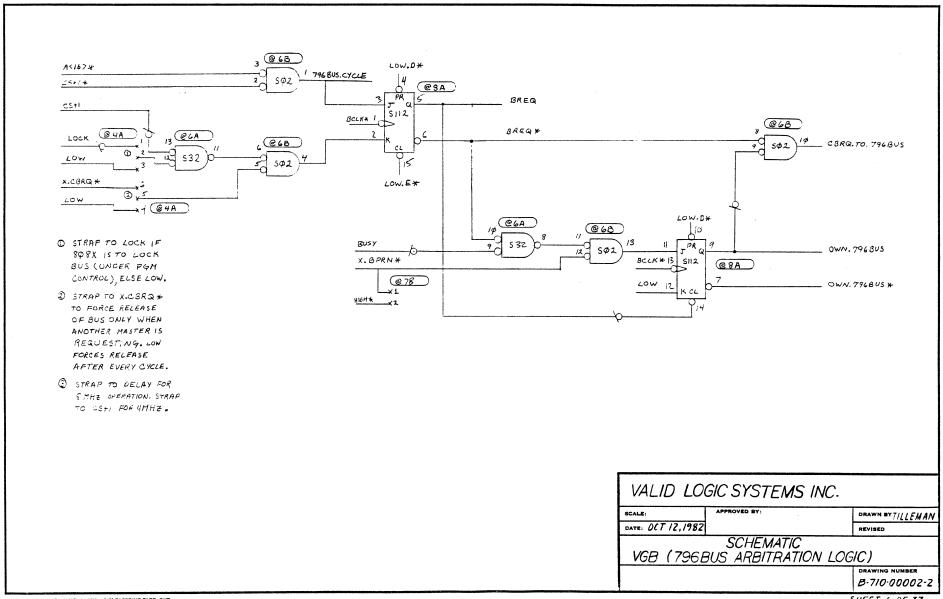

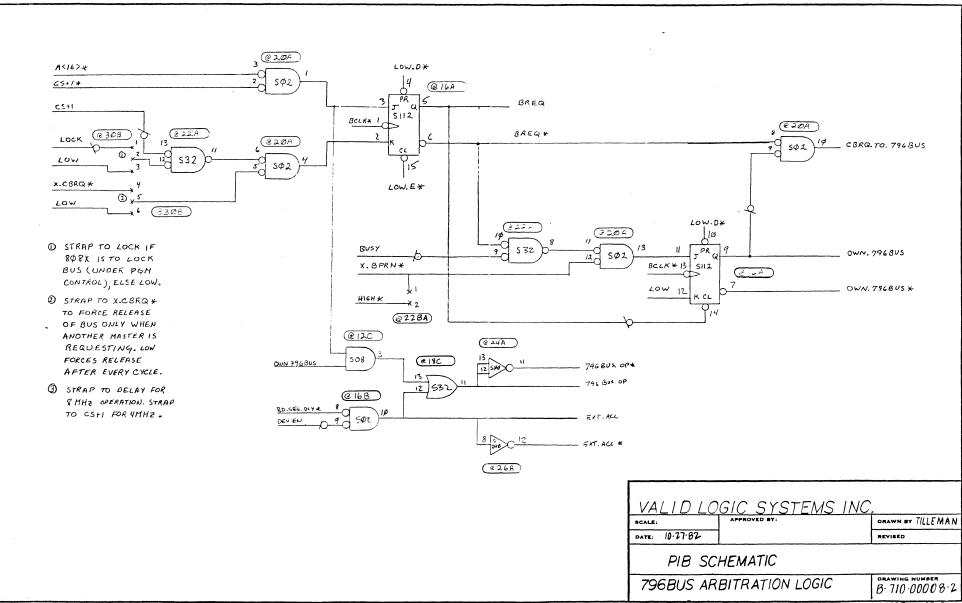

# SECTION 8 BUS ARBITER

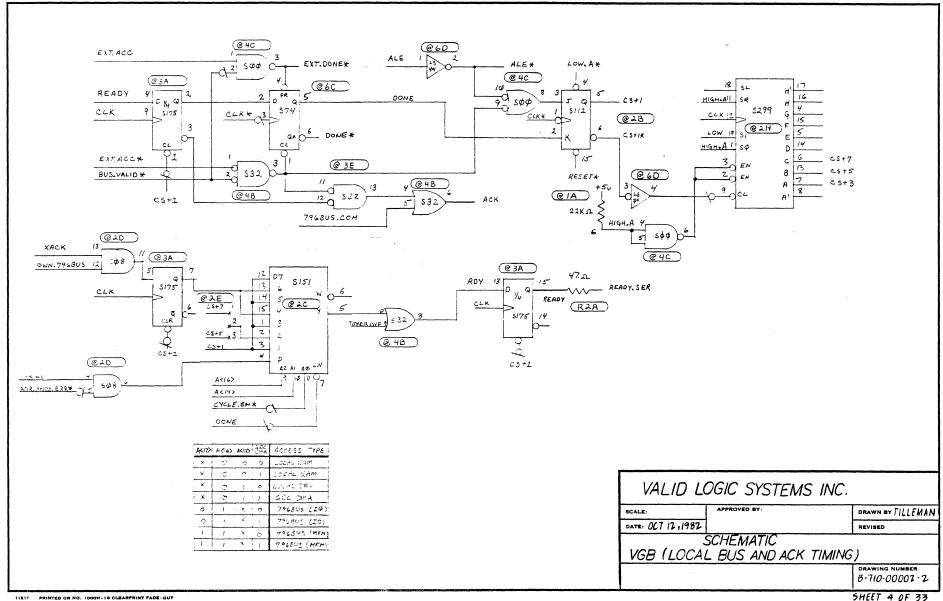

# 8.1 Bus Arbiter/CPU Interface

.

• • • • •

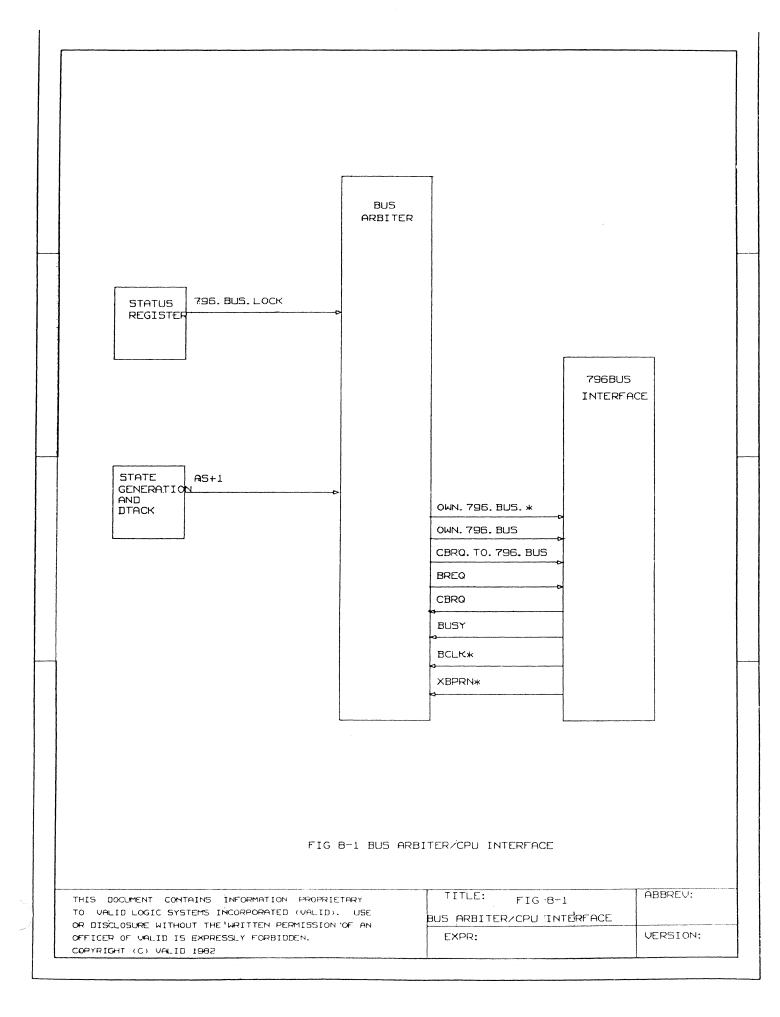

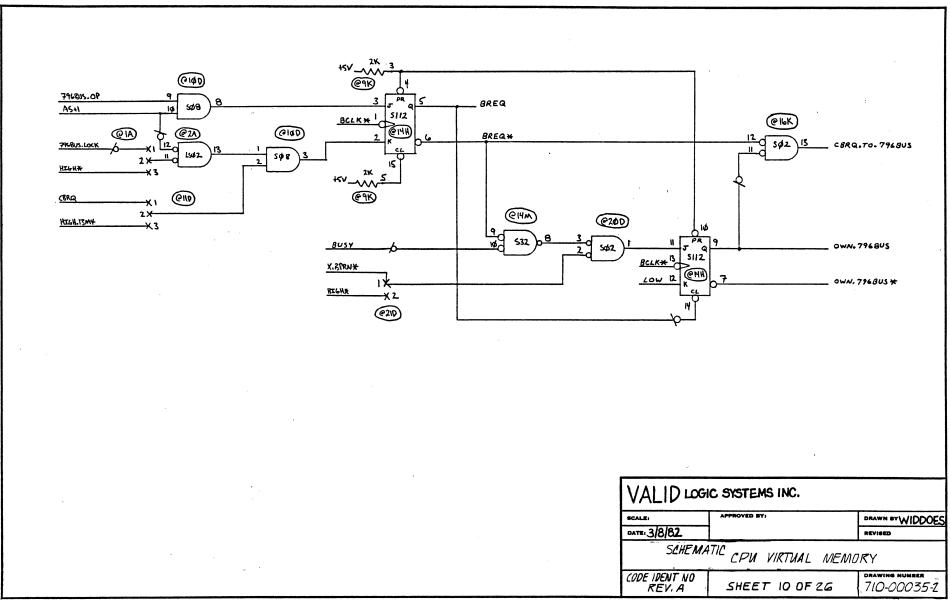

The bus arbiter/CPU interface is shown in Figure 8-1. The bus arbiter implements 796 bus protocol and provides fast bus exchange for the CPU in conjunction with other bus masters connected to the 796 bus. The arbiter receives signal inputs from the status register and state generation and DTACK, and to and from the 796 bus interface. The signals are listed and described in table 8-1.

Table 8-1. Bus Arbiter Interface Signals

| SIGNAL       | FUNCTION                                                                                                                                                                   |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 796 BUS.LOCK | Holds ownership of 796 bus and prevents BREQ<br>line from being reset.                                                                                                     |

| AS+1         | Address strobe used for setting BREQ true.                                                                                                                                 |

| OWN.796 BUS* | Activates 796 bus interface. Complementary<br>with CWN.796 EUS.                                                                                                            |

| OWN.796 BUS  | Activates 796 bus interface bus commands<br>buffer, generates X.BUSY* signifying bus is in<br>use, and provides enable to data bus buffers.<br>Complement to OWN.796 BUS*. |

Table 8-1. Bus Arbiter Interface Signals (Continued)

SIGNAL FUNCTION Generates X.CBRQ\* through 796 bus interface CBRQ.TO.796 BUS buffers to signify that another master wishes to use the bus. When false, indicates no other bus master is requesting bus. BREQ Indicates CPU requires use of 796 bus. CBRQ Common bus request informing CPU that another bus master wishes to use 796 bus. X.BPRN\* Indicates no higher priority module is requesting use of 796 bus. Synchronized with BCLK\*. BCLK\* Negative going edge sets current condition into bus arbiter logic. BUSY Indicates to bus arbiter that 796 bus is currently in use.

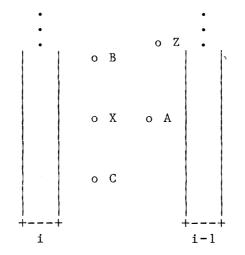

8.2 Bus Arbiter Logic

The bus arbiter logic is shown in Figure 8-2. The logic consists of two J-K flip-flops used to set and reset the 796 bus request and control lines as controlled by the bus selection inputs and related gating.

During operation, the BREQ is set by signals 796 BUS.OP, AS+1, and a low-going clock pulse to indicate the CPU wants the bus for the next or more cycles. At the same time, CBRQ.TO.796 BUS indicates to all bus masters that the CPU wishes to use the bus. If the bus is not busy and X.BPRN\* is not set, a high to the second flip-flop J input along with the next low-going clock pulse generates OWN.796 BUS and OWN.796 BUS\* to activate the bus interface buffers.

$Z^{m}$  >

If it is desired to lock the bus into a constant bus request situation, a 796 BUS.LOCK line can lock the flip-flop so the BREQ line cannot be reset. A low common bus request line (CBRQ) also disables the reset of BREQ as long as no other bus master desires to use the bus. A BUSY line from the bus indicates the bus is in use and disables the OWN.796 BUS outputs. These lines in turn disable the CPU 796 bus interface.

# 8.3 Bus Arbiter Strapping

Strapping of certain signals is used in situations where constant domination of the CPU on the 796 bus is desired (one example is where no other bus masters exist). These situations involve the strapping of the CBRQ or X.BPRN\* signals. The CBRQ feature can be constantly enabled by strapping the input true. The X.BPRN\* feature can be constantly enabled by strapping it false. The true CBRQ line then generates a constant bus request and the X.BPRN\* always simulates a bus priority request. The 796 BUS.LOCK feature can also be disabled by strapping it false.

# SECTION 9

# CPU ADDRESSING

# 9.1 Address Bus/CPU Interface

The address bus/CPU interface is shown in Figure 9-1. Addressing is provided on the address bus (RAW A<23..1>) from the M68000LB to the address latches.

The latches operate in an asynchronous manner (constantly enabled). Each address from the M68000LB is strobed onto the address bus lines (A<23..1>) by the data strobe (DS) along with the read/write command (W), upper and lower data strobes (UDS\* and LDS\*) which in turn generate FAKE.A<0> and FAKE.BHEN as required. Because the M68000LB is capable of updating the address lines in approximately 30 nanoseconds, a delay line is used to delay the data strobe by approximately 125 nanoseconds before placing a new address on the latch outputs. This allows time for the addresses to be used either by the CPU or 796 bus by keeping them available on the latch outputs for the correct amount of time.

The address bus interfaces various functions on the CPU board. These are each listed and described in detail in table 9-1. The FAKE.A<0> interfaces with 796 bus address bit X.A<0>\*. The bit is generated by the address latches LDS\* signal from the M68000LB. The bit is used to signify data is to be transfered on the lower byte 796 bus data lines. The FAKE.BHEN indicates data is to be transfered on the high byte 796 bus data lines. The AS\* signal is generated by the M68000LB to the state generation and DTACK logic to indicate a valid address is on the address bus.

Table 9-1. CPU Addressing Features

# FUNCTION

### DESCRIPTION

| Local Commands   | Decodes commands for all CPU functions.                                       |

|------------------|-------------------------------------------------------------------------------|

| 796 Bus Commands | Uses W and W* with other commands and control signals to generate one of four |

|                  | bus commands depending on the CPU mode.                                       |

# Table 9-1. CPU Addressing Features (Continued)

| FUNCTION    | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Segment Map | Addresses (A<2216>) and context<br>register CTXT<30> address the seg-<br>ment map to generate map addresses to<br>the page map. The signal along with<br>other control signals is used to<br>address a PROM which in turn gener-<br>ates segment and page map status sig-<br>nals. The W signal also controls bi-<br>directional buffers which allow either<br>segment map data onto the data bus or<br>lines from the data bus directly to the<br>page map and errors and timeout logic. |

| Page Map    | Address A<1512> along with segment<br>map addresses SMAP<70> are used to<br>generate page map addresses to the<br>796 bus and status signals to other<br>CPU functions. The W signal is used<br>in the generation of PMAP.DIRTY (see<br>memory management). The W signal also<br>controls bi-directional buffers which<br>allow addressing and generation of<br>status signals directly from the<br>data bus to the 796 bus.                                                              |

| RAM and ROM | Address bit A<101> provides addres-<br>sing to the RAM memory. Address bits<br>A<131> provide addressing to the<br>ROM memory. The W* signal along with<br>the UDS* and LDS* select the read<br>and write operations of the RAM.                                                                                                                                                                                                                                                          |

# Table 9-1. CPU Addressing Features (Continued)

# FUNCTIONDESCRIPTIONTIMER and FPIAddress bits A<2..1> selects the<br/>interval timer when the CPU selects<br/>it for use. The floating point<br/>processor is addressed by address<br/>bit A<1> when CPU selected.UARTSAddress bits A<2..1> selects the<br/>UARTS internal function for use

### 9.2 Logical Address Space Structure

The 16 megabyte logical address space of the M68000LB is divided into 256-64K bytes segments. Logical addressing operates in both the user and supervisor modes.

when selected for use by the CPU.

# 9.2.1 User Mode

In the user mode, accesses within the lowest 64 segments (4Mbytes from \$000000 through \$3FFFF) are mapped and checked for correct access mode as specified in the map. Correct accesses map to either the I/O space or memory space of the 796 bus. All others cause an address bounds bus-error trap. The user cannot access on-board RAM or other local resources.

# 9.2.2 Supervisor Mode

In the supervisor mode, the second segment (64Kbyte from \$010000 through \$01FFFF) is reserved to access local resources such as on-board RAM and ROM. Accesses in this segment are not mapped. All other supervisor mode accesses within the lowest 64 segments are mapped and checked for correct access mode as specified in the map.

In general, supervisor references to other than the lowest 64 segments cause an address-bounds bus-error trap. However, the context register contains a field which controls reading and writing the map. If the context register contains a value which allows access to the map, then (supervisor mode only) addresses in segments 128 through 191 (4Mbyte from \$800000 through \$BFFFF) are not mapped through to the 796 bus, but reference the map itself.

When the CPU is in the boot state (see status register), supervisor mode accesses to the first segment are unmapped and forced to local resources.

9.3 Local Resources

The CPU board contains certain local resources. These include ROM, RAM, UARTS, timer, floating point processor, and various status registers. The software running in supervisor mode accesses these local resources by generating addresses in the second segment (64Kbytes from \$010000 through \$01FFFF). First segment addresses (64Kbytes from \$000000 through \$00FFFF) also access these resources if the CPU is in the boot state.

# NOTE

Accesses to local resources are not mapped since some local register control the mapping function itself. Local resources are not accessible by other 796 bus masters.

The second segment, low-order 16-bits select the local resources as follows:

Address Range

Size

Function

| 16Kbytes |

|----------|

| 16Kbytes |

| 2Kbytes  |

| 14Kbytes |

| 16Kbytes |

|          |

Local ROM (reserved, timeout) Local RAM (reserved, timeout) Local Devices

# Local devices are selected by the low-order 14-bits as follows:

| Base Address | Device                           |

|--------------|----------------------------------|

| 01C001       | Host UART                        |

| 01C801       | Terminal UART                    |

| 01 D001      | 8253 Programmable Interval Timer |

| 01D801       | 8232 Floating-Point Processor    |

| 01E001       | Context Register                 |

| 01 E801      | Error Register                   |

| 01 F001      | Status Register                  |

| 01F801       | Switches (Context)               |

All devices in region \$01C000 through \$01FFFF are byte devices. Odd byte addresses should be used to access these devices. For a device with internal addressable functions, the bare address for the device must be odd, and the low-order ten word address bits (A<10..1>) select the function within the device. Byte accesses on even addresses within this area do not activate any device, and only the odd byte is read or written during a word access within this area.

# SECTION 10 REGISTERS

### 10.1 Registers/CPU Interface

The CPU includes status, error, and context registers contained as part of the context and status switches and errors and timeout logic functions of the board. The purpose of the registers is to have available certain conditions of the CPU for monitoring and information purposes when required. The registers may be written-into and read-from during CPU operations. The registers interface with various functions of the CPU board and the data bus as shown in Figures 10-1, 10-3, and 10-5. A description of each register and its particular functions are included in the paragraphs that follow.

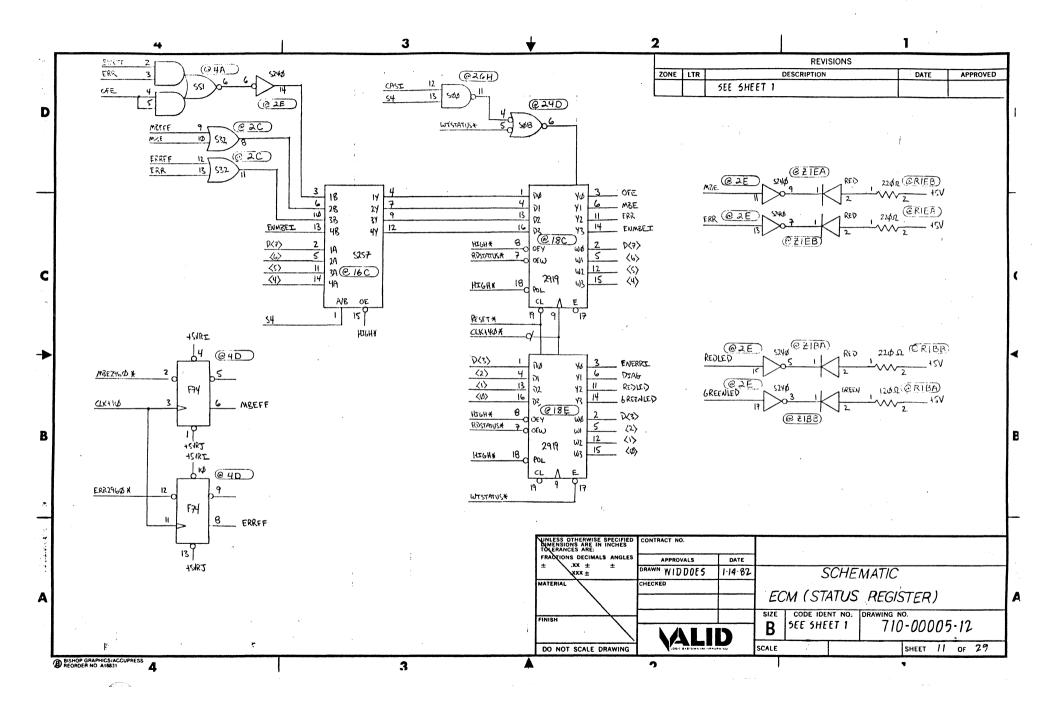

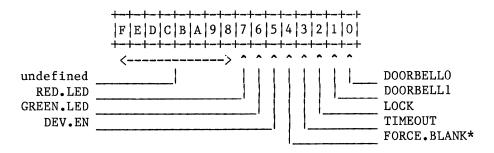

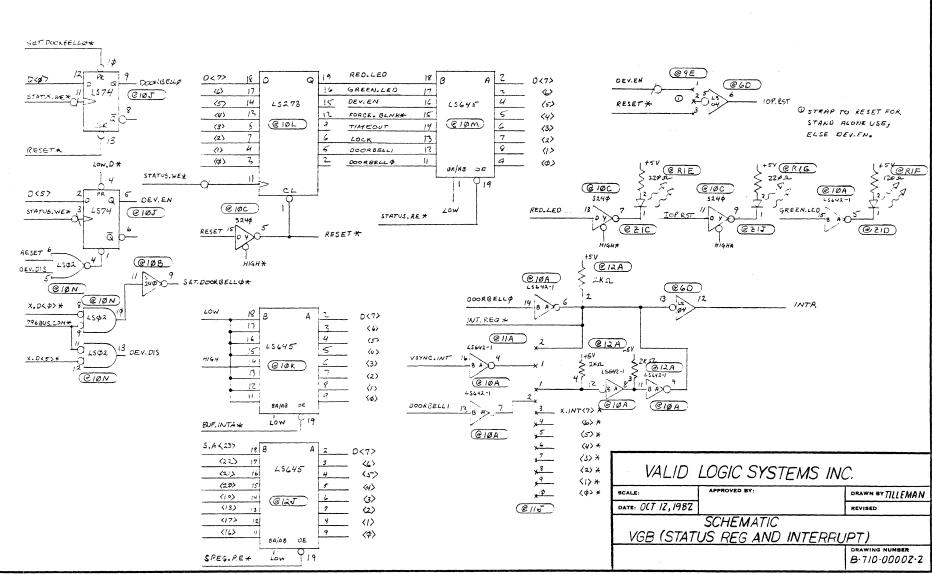

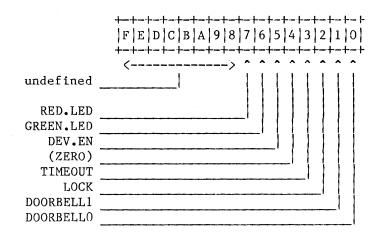

10.2 Status Register

The status register interface is shown in Figure 10-1. The purpose of the status register is to light the red and green LEDs based on the results of CPU diagnostics and provide control signals to varicus functions on the CPU board as well as place the status of the bits onto the M68000LB data bus.

The register can be either written-into or read-from using M68000LB byte or word operations. The register can also be cleared by reseting all bits (using RESET TO 68000\*) during a 796 bus or power-up reset. The effects of writing into the status register is observed after the write is completed (before the beginning of the next instruction). The register is written into from the data bus by a WE STATUS\* signal generated from the local commands logic.

The data written into the register is made available on the register output lines to the CPU board functions depending on the CPU operation being performed. The same data is also made available to the three state interface buffers for gating onto the M68000LB data bus. This is accomplished by generating a RE.STATUS\* signal to the buffers from the local commands logic.

The register contains fields related to each bit position as shown in Figure 10-2. These correspond to bit lines on the data bus. The fields are also listed in table 10-1 as well as each name and definition.

Table 10-1. Status Register Fields

| FIELD    | NAME                  | DEFINITIONS                                                                                                                                                                                                                                                                                                            |