Packager Overview

#### CHAPTER 8

#### PACKAGER

#### Overview of the Packager

# 8.1 INTRODUCTION

The Packager provides the interface between the SCALDsystem and the user's physical design environment. The files output by this program are intended to supply all the information needed by physical design systems. The Packager reads the expansion file created by the Compiler and produces files for the user's physical design system. These output files include net lists, part lists, etc.

State files can be generated to maintain a consistent description of the design from one Packager run to another. The Packager can also read files created by the user's physical design system that specify changes in the physical design or additions to it that need to be reflected in the output files. These changes are then made to the state files during the next execution of the Packager.

#### 8.2 A SUMMARY OF THE PACKAGER'S FUNCTIONS

The Packager performs several functions. These are summarized below with a short description. A complete description of each will be presented later in this section.

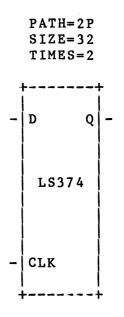

1. Expand parts with SIZE properties.

Parts with SIZE properties need to be expanded into (possibly) several parts. The signals connected to the original part are assigned to the expanded parts.

2. Create versions of parts that have TIMES property.

New versions of those parts that have TIMES properties are created. The signal versions (the outputs of versioned parts) are allocated as needed in the rest of the design.

3. Remove phantom WIRE-OR and WIRE-AND bodies.

All WIRE-OR and WIRE-AND bodies used in the design are removed and replaced with explicit wire tying. New versions of signals are used to implement wire

8-3

tying (see the section on WIRE-ORs and WIRE-ANDs).

4. Logical to physical mapping.

Each logical part, signal, and pin is given a physical name. These names are originally created by the Packager but can be changed by the user.

5. Loading calculations.

<sup>to</sup> The Packager checks each net to make sure that the loading specifications of the parts are not violated.

6. Input and output checks.

The Packager checks that there is at least one input and one output pin connected to each net. This detects the cases where there are dangling inputs or outputs. a 1.

7. Output file creation.

The Packager creates several files containing the results of the run. These files include a net list, parts list, logical design change summary, etc. v i tangi Karan

282 2. 28.0 8. Feedback of physical design changes.

The physical design created by the Packager may differ from the design created by the physical design system. All of these changes can be fed back into the Packager to modify its understanding of the actual physical design.

TETER (DOS): N Star Francis

The Packager also provides preliminary support for engineering changes. The treatment of ECOs in general will be addressed at a later date; the current Packager is not intended to be a solution to those problems.

062 .05 8.3 PACKAGER INPUT FILES

The following files are read by the Packager. Some of them are created by the Packager, some are created by the Compiler, and some are created by the designer (or the designer (s. physical design system). The specific formats of these files sisedescribed later in this section.

1. Packager Directives File

This file contains commands used to direct the execution of the Packager and is created by the designer with a text editor.

2. Compiler Expansion File

This is the output file from the Compiler and contains a body ordered description of the design. All user defined properties and signals are found here.

3. CHIPS File

This file contains descriptions of the physical part types used in the design. Each entry contains the physical part type, pin numbers, section descriptions, default properties, current loading values for both input and output pins, and family specification. This file is generated by the Compiler from a special set of library drawings.

4. Physical Part Tables

These files contains tables describing how new part types can be created from existing part definitions on an instance by instance basis. This is useful for discrete parts such as resistors and capacitors. These files are created by the designer with a text editor.

5. Logical Signal Name to Physical Net Name Bindings

This file contains bindings of logical signal names to physical net names. Each logical signal name is in cannonical form. It also contains a path name specifying the signal instance. The physical net name is a physical name string. Each signal name pair represents a single bit. This file is maintained by the Packager and is not to be written or changed in anyway by the user.

6. Physical Net Name Transformations

formpry

to for and

This file is used to change the physical net names assigned by the Packager. It consists of a list of

por chig and

physidad

Packager Overview

pstpirk.dat

petpit x. dat

fat.

200

55-23 B

old physical net names and new physical net names. It is created by the user or the user's physical design system.

7. Logical to Physical Part Designator Bindings

This file contains a list of logical to physical designator bindings. Each entry consists of a logical part designator and its corresponding physical part designator. Each entry also contains a section specification which binds logical pin designators to physical pin designators. This file is maintained by the Packager and is not to be written or changed in any way by the user.

8. Physical Part Designator Transformations

This file contains changes of old physical part designators (the ones assigned by the Packager during the last run of the program) to new physical part designators (as assigned, possibly, by some layout program). This file provides a means by which the physical part designators assigned by the Packager can be changed. This file is generated by the user or the user's physical design system.

#### 9. Physical Section Transformations

This file contains changes of old physical sections (the ones assigned by the Packager during the last run of the program) to new physical sections (as assigned, possibly, by some layout program). This file provides a means by which physical sections assigned by the Packager can be changed. This file is generated by the user or the user's physical design system.

10. Feedback Net List

This file contains a net list sorted by physical part designator of the current physical design. The only restriction is that the physical net names must not have changed or the new physical net names have already been fedback before performing a net list feedback. The Packager will detect and perform all physical part designators changes, physical section swapping, and pin swapping from the feedback net list. The file is generated by the user or the user's physical design system.

11. Signal Synonyms File

This file is produced by the Compiler and lists all aliases for each signal that has a synonym in the design.

12. State file

This contains information about the last run of the Packager. It is used to ensure that the Packager produces the same output for the same inputs.

13. Pin Swap File

$f^{st} f^{sy} f^{st} d\vec{r}$  This file contains the pin swap information generated from a previous run of the Packager. This file is maintained by the Packager and is not to be written or changed in any way by the user.

## FILES WRITTEN BY THE PACKAGER

The following files are created by the Packager. Some of them may be selectively disabled should the file not be needed. Some of these files are read by the Packager in subsequent runs of the program.

1. Execution Summary

A summary of the Packager execution showing execution times, statistics, error messages, etc.

2. Cross References

This file contains several cross references intended to provide information about the design that is not readily available in the drawings. These cross references include both physical and logical information and how they correspond. They are organized to provide access to the design as a whole or to a particular drawing. 3. Logical Signal Name to Physical Net Name Bindings

This file contains bindings of logical signal names to physical net names. Each logical signal name is in SCALD format. It also contains a path name specifying the signal instance. The physical net name is a physical name string. Each signal name pair represents a single bit. This file is maintained by the Packager and is not to be written or changed in any way by the user.

4. Logical to Physical Part Designator Bindings

This file contains a list of logical to physical designator bindings. Each entry consists of a logical part designator and its corresponding physical part designator. Each entry also contains a section specification which binds logical pin designators to physical pin designators. This file is maintained by the Packager and is not to be written or changed in any way by the user.

5. Expanded Net List

A net list consisting of the physical net name, properties of that net, physical part type, physical part designator, physical pin name, and properties of the logical pins. Properties from the chips file are not output.

6. Expanded Parts List

A part list consisting of physical part designators, logical to physical bindings, and the body properties of the logical parts. Properties from the chips file are not output.

7. Logical Changes Summary

A list of the changes in the logical design from the last run of the Packager. Any changes in logical part to physical part assignments are listed to this file.

8. State File

This contains information about the last run of the

Packager. It is used to ensure that the Packager produces the same output for the same inputs.

## 9. Pin Swap File

This contains the pin swap information generated by the Packager during a feedback net list. This file is maintained by the Packager and is not to be written or changed in any way by the user.

## 10. Log File

This file contains assertion check error messages, run time statistics, internal debug information, etc. used by Valid personnel when searching for information about program bugs. The user does not normally need to look at this file.

#### 11. Back Annotation File

This file contains information added to the design by the Packager or the physical design system which the user may wish to see reflected in the drawings. The Graphics Editor reads this file and adds this information to the user's drawings.

#### 12. Reports

This file contains several user reports generated by the Packager. These reports includes a part summary of the design and a list of spare physical sections.

#### 13. New CHIPS file

This file contains the new part definitions that were created from processing physical part tables. This file can be used by other programs such as DIAL to differentiate the newly created part types.

8-9

### 8.4 INTRODUCTION

The following sections describe the various functions of the Packager.

## 8.5 SIZE EXPANSION

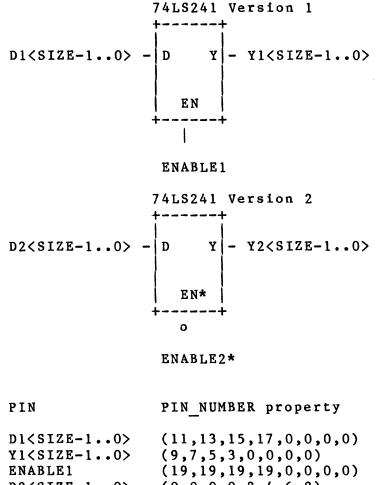

The SIZE property is used to generate a multiple-bit component, and connect it to a group of signals. The Packager generates SIZE number of logical parts and assigns a new logical part designator to each. A logical part can have pins common to all sections as well as pins unique for each section. Common pins are connected in parallel for all sections and the unique pins are connected to independent pieces of the signal connected to the original part. The PIN NUMBER property for each pin in the body definition specifies whether the pin is common or unique for each section. The PIN NUMBER property specifies the width of the pin it is attached to. The Packager allocates this number of bits from the original signal to each logical part. If the original signal is not wide enough for all logical parts, the Packager begins allocating from the beginning of the signal again. See the documentation describing the construction of physical libraries for more detail.

The assignment of bits of a signal to physical parts is done sequentually so that adjacent bits are assigned to the same physical package if possible.

## 8.6 TIMES EXPANSION

In digital designs, it is often convenient to have several different signals available which each have the same behavior. One such case is where a net has more input loads than the output is capable of driving. This fan-out error must be corrected for the product to function as designed. A good way to fix this type of problem is to divide the inputs on the net into two or more groups, where each group presents a small enough load to be driven by one output. Each group is wired together, and is said to connect to a version of the net. To keep the operation of the design unchanged, each version of the net must have the same logical behavior. To avoid fan-out errors, each version of the net must have a different output driving it. This is accomplished by connecting each version of the net to a different version of the output, where each output version behaves the same.

Any part may have multiple versions of its outputs generated by attaching the TIMES property to the instance of the part. The number of versions of each output that will be generated is the value of the TIMES property. The outputs are generated by creating TIMES number of physical sections and, for all physical sections, connecting the inputs as shown in the drawings. Thus, since the inputs to each of the components are identical, each output signal will exhibit the same logical behavior over all the versions.

Replication by TIMES is useful where an output must drive many input loads, and the Packager will divide the loads among the versions of an output so that the specified loading rules will be obeyed. In the process, it will generate one version of the net for each version of the output. When more versions of an output exist than are necessary to drive the net to which it connects to, the Packager will attempt to divide the loads evenly among all output versions. If loading rules require more output versions than are specified, the excess number required will be determined and flagged as an error.

When several outputs are connected to one net (wire-tied), and several versions of the net are desired, each output should have a TIMES value equal to the number of versions of the net desired. If several outputs on the same net have different TIMES values, the number of versions of the net generated is the minimum of the output TIMES values. Physical parts with no TIMES properties have a TIMES value of one.

Pins with the BIDIRECTIONAL property (see the section describing current loading) are considered to be output pins when versions of the part are created because of a TIMES property.

## 8.7 WIRE-GATE AND WIRE-TIE EXPANSION

In SCALD III, outputs of appropriate technologies may be connected together in two different ways:

- o An explicit wire-tie.

- o A wire-gate.

Wire-ties are simply the connection of two or more outputs to the same signal and are used primarily for connection of several drivers to a common bus. The signal present on the outputs is exactly that signal which is present on the bus, since the outputs are connected to the bus.

8-11

Wire-gates are used whenever signals are wired together to form the logical-or or logical-and of the signals (depending on the technology), and the signals are also used elsewhere in the design. In these cases, simply connecting to the same net (wire-tying) the outputs driving each signal is not acceptable, since it results in all the signals assuming the value of the logical-or or logical-and. The correct way to wire these signals together is to wire-gate the signals by connecting versions of the outputs which are used nowhere else in the design. By doing this, a signal is generated which has the required behavior, and the behavior of the other versions of the constituent signals remains unchanged wherever else they are used. This allows the designer to treat wire-gates the same as "real" gates, which makes complex wire-gate designs understandable.

TIMES properties on wire-gates function exactly the same as on physical parts. Several versions of a net are generated, each with different output versions. For each version of the wire-gate output net, one version of each of the wire-gate input nets is used. If a net connects to a wire-gate input, then enough versions of the net must exist to drive the "real" loads on the net plus the "induced" loads on the output net of the wire-gate. If a wire-gate has no TIMES property, it is ignored when determining the number of versions of the output net, and assumes the TIMES value required by the net. Each version of the output net will use one version of each input net, whether the wire-gate has a TIMES property or not. The Packager indicates any extra versions of outputs which are required, making it simple to arrive at the correct TIMES values for outputs driving even a complex combination of "real" and wire-gate inputs.

After a number of versions of a net have been generated (by use of the TIMES property), the number of versions required by wire-gate inputs is first used. The "real" loads on the net are then divided among the remaining versions of the net. Therefore, a net with 10 versions which gives 3 versions to wire-gate inputs will have 7 versions left to drive "real" inputs.

The constant signals '0' and '1' may be applied to the inputs of wire-gates, and function as they would on "real" gates. If a wire-and has an input connected to the '1' net, that input is ignored, since the other inputs will determine the value of the output. If a wire-and has an input connected to the '0' net, then all loads on the output net are connected to the '0' net, since 0 AND anything is 0. The outputs driving the remaining inputs to the wire-and are not used. The same is true for wire-or's, with '0' and '1' reversed.

## 8.8 NET CHECKS PERFORMED BY THE PACKAGER

A net is a single bit signal and the nodes (parts and the specific pin) that are connected to it. There are several consistency checks performed for nets. These are:

- 1. Make sure every net is connected to at least one input pin and at least one output pin.

- If a net is connected to more than one output pin, make sure all those pins have the proper technology (OC, OE, TS, etc.).

- 3. Make sure loading rules are not violated.

Each of the checks above is discussed below. Loading rules will be discussed in the next section.

## INPUT AND OUTPUT PIN CHECKS

Each net is checked to make sure that it connects to at least one input as well as one output pin. If this is not the case, a message is printed indicating the condition detected and the net for which it was detected. The presence of the OUTPUT\_LOAD property on a pin indicates that the pin is an output and the presence of the BIDIRECTIONAL property indicates that the pin is both an input and output.

These input and output checks can be suppressed on a pin by pin, body by body, or net by net basis. The NO IO CHECK property is used for this purpose.

The NO\_IO\_CHECK property can be given one of three values as follows:

LOW This causes the "O state" I/O check to be suppressed. The "l state" check is performed.

HIGH This causes the "1 state" I/O check to be suppressed. The "O state" check is performed.

BOTH or TRUE This causes both the "O state" and the "1 state" I/O checks to be suppressed.

The NO\_IO\_CHECK property may appear on a library part (as in the case of a standard connector) or can appear on an instance by instance basis in the drawings.

If the NO\_IO\_CHECK property is used as a net property, it applies to all the pins on the net. When used as a body property, NO\_IO\_CHECK applies to all pins of the body. When used as a pin property, NO\_IO\_CHECK applies only to the pin to which it is attached.

## MULTIPLE OUTPUT CHECKS

Outputs can only be tied together if they are given explicit permission to do so. Permission is given by the OUTPUT TYPE property attached to the output pins. The OUTPUT TYPE property serves three purposes. First, it gives permission to the pin to be connected to other outputs. Second, it specifies the type of output so that only compatible outputs may be connected together. Third, it specifies the logic function created by tying the outputs together. When the Packager detects outputs tied together that do not have the OUTPUT TYPE property or outputs tied together that hav incompatible OUTPUT TYPE properties, it produces an error message indicating the output pins as well as the net name.

Each output pin that can be connected to other output pins must have the OUTPUT TYPE property. The property value specifies the pin type and also the logic function created by tying the outputs together. The form of the OUTPUT\_TYPE property value is:

( <output type> , <logic function>)

where <output type> is the output type name and can be any identifier (string of letters, digits, or ' ' starting with a letter). The <logic function> is optional and specifies the logic function of outputs tied together and may be either AND, OR, or TS. See the Timing Verifier documentation for a description of how multiple output nets are simulated in the presence and absence of the logic function portion of the OUTPUT TYPE property.

Outputs can be connected together only if they have the OUTPUT TYPE property and the property values are the same. The parts in the Valid libraries have the following standard OUTPUT TYPE property values:

OC,AND { open collector; AND logic function } OE,OR { open emitter; OR logic function } TS,TS { TRI-STATE; logic function handled specially }

Other property values can be used. The value is only used to match output pin types and has no other meaning to the Packager. Occasionally, there is a need to connect outputs of different types. The ALLOW CONNECT property can used to allow multiple outputs to be connected together by specifying which outputs are to be "ignored" during the check.

The ALLOW CONNECT property may appear on a library part (as in the case of a standard connector) or can appear on an instance by instance basis in the drawings.

If the ALLOW CONNECT property is used as a net property, it applies to all the output pins on the nets. When used as a body property, ALLOW CONNECT applies to all the output pins of the body. When used as a pin property, ALLOW CONNECT applies only to the pin to which it is attached.

# 8.9 DEVICE LOADING CALCULATIONS

Once a design has been expanded into physical components, and the interconnection between them is complete, it is necessary to check that loading rules have been obeyed. The loading values are unitless quantities and need not represent any physical values.

The loading for each part is specified in the SCALD library defining the part. The loading for each pin of the part is specified by a property attached to the pin. The property has the following form:

(<low value>, <high value>)

where <low value> is the DC load the pin presents when in the "O state" (the most negative voltage state). <high value> is the DC load the pin presents when in the "l state" (the most positive voltage state). The actual value is an integer or a real number (of the form n.m) that specifies the load in some consistent units.

The values used for some Valid libraries (such as the LSTTL library) is the amount of current which an output may source or sink, and the amount of current required to set an input to each of its states. Theses loading values are specified in mA (Amps x 0.001) and by convention, current flowing into a pin is positive and current flowing out of a pin is negative. Some libraries (such as the 100K library) use values which has no physical meaning but instead describe the maximum fan-out for an output pin.

There are two properties used to specify loading: INPUT\_LOAD and OUTPUT\_LOAD. INPUT\_LOAD is used to specify the load a pin presents when it is used as an input or when

not driving the signal. An input pin should always have an INPUT\_LOAD property. An output pin is given an INPUT\_LOAD property whenever that pin can also place an input load on the signal. For instance, a TRI-STATE or an open collector output also presents a load when not driving the signal. This load needs to be considered when calculating the loading of the entire net. The OUTPUT\_LOAD property is used to specify the load presented by a pin when used as an output pin.

By definition, the presence of the OUTPUT LOAD property indicates that the pin is an output pin. If a pin does not have the OUTPUT LOAD property, it is assumed to be an input pin. When a pin is both an output and an input (as, for instance, in the case of a transceiver pin), both the INPUT LOAD and OUTPUT LOAD properties must be present. In addition, the BIDIRECTIONAL property must be used to indicate that the pin is both an input and an output.

The Packager calculates the loading for each net. There are two loading calculations performed: "O state" loading and "l state" loading. The "O state" loading calculation proceeds as follows:

- 1. Find the minimum "O state" value found in all the OUTPUT LOAD properties of pins connected to the net.

- 2. Add up the "O state" value found in all the INPUT LOAD properties of pins connected to the net.

- 3. Calcuate the net loading by adding the minimum OUTPUT LOAD to the INPUT LOAD totals.

- If the result has a different sign than the sign of the OUTPUT\_LOAD value, report a loading error for the net.

For example, consider a net with four nodes (pins) with the following loading properties:

OUTPUT LOAD = (3.0, -1.8)INPUT LOAD = (-1.2, 0.2)INPUT LOAD = (-1.2, 0.2)INPUT LOAD = (-1.2, 0.2)INPUT LOAD = (-1.2, 0.2)

The "O state" net loading value is -0.6. Since this value has a different sign than the value given in the OUTPUT\_LOAD (3.0), the net violates loading rules; there are too many inputs for the given output drive capability. The calculation of the "1 state" loading proceeds similarly. In the example used above, the "1 state" loading for the net would be -1.0 which is not an error (the sign of the value for the entire net is the same as the value for the output).

If a net loading error exists and may be fixed by the use of more versions of the net, the Packager will flag the net as having a loading error, and will try to generate more versions of the net to correct the error. This may, in turn, cause errors if not enough versions of the outputs exist. If a net has a loading error which cannot be fixed by more versions (such as an output which cannot drive even a single input), the Packager will flag this error and not try to generate more versions of the net.

#### LOADING FOR PINS THAT DRIVE OR LOAD ONE STATE ONLY

Some output pins can only drive to one state. For example, an open collector pin can only drive to the "O state". For these pins, it is meaningless to specify a loading for the opposite state. Further, the I/O and loading checks for the net for the other state should not assume that this pin is an output.

Likewise, some input pins only present a load for one state. Thus the I/O and loading checks for the net for the other state should not assume that this pin is an input.

To support this, the Packager allows loading for either the "O state" or the "l state" to be specified with an '' to indicate that the pin does not drive or load the net.

For example, the output loading for an open collector pin might be specified as:

OUTPUT LOAD = (-2.0, \*)

indicating that it can drive a 2.0 load in the "O state" but does not drive the net in the "1 state".

## SUPPRESSION OF DEVICE LOADING CALCULATIONS

Device loading calculations may be suppressed on a pin by pin or body by body basis. The NO\_LOAD\_CHECK property is used for this purpose.

The NO LOAD CHECK property can be given one of three values as follows:

LOW This causes the "O state" loading check to be suppressed.

The "1 state" check is performed.

HIGH This causes the "1 state" loading check to be suppressed. The "0 state" check is performed.

BOTH or TRUE This causes both the "O state" and the "1 state" loading checks to be suppressed.

The NO\_LOAD\_CHECK property may appear on a library part (as in the case of a standard connector) or can appear on an instance by instance basis in the drawings.

If the NO LOAD CHECK is used as a net property, it applies to all the pins on the net. When used as a body property, NO LOAD CHECK applies to all pins of the body. When used as a pin property, NO LOAD CHECK applies only to the pin to which it is attached.

# SPECIFICATION OF UNKNOWN LOADING

Occasionally there are parts in a design that have pins with unspecified or unknown loading such as the pins of a connector. The Packager makes it possible to include such components in a design without causing net loading or I/O check errors.

The property UNKNOWN LOADING is used to inform the Packager that loading is unknown and to suppress loading and I/O checks on the entire net if it appears on any pin of the net.

The UNKNOWN LOADING property may appear in on a library part (as in the case of a standard connector) or can be used on an instance by instance basis in the drawings.

If the UNKNOWN LOADING is used as a body property, it applies to all the pins of the body. When used as a pin property, UNKNOWN LOADING applies only to the pin to which it is attached.

If one attaches the NO LOAD CHECK to a pin with either UNKNOWN LOADING on the pin or body, load checking will not be suppressed for the entire net, but only for this pin as specified by the value of the NO LOAD CHECK. Likewise, attaching the NO IO CHECK to a pin will only suppress I/O checking only for the pin as specified by the value of the NO IO CHECK. This mechanism allows the user to "suppress" the effects of the UNKNOWN LOADING property on a pin by pin basis which is useful in the case of the UNKNOWN LOADING property attached to the body of a library part.

## 8.10 ASSIGNING LIBRARY PIN NUMBERS

Library parts must be given PIN\_NUMBER properties so the Packager will know how to assign pin numbers, swap sections, etc. The PIN\_NUMBER property is attached to each pin of the body (except for bus through pins) and conveys the following information:

o The pin number for the pin.

o How many sections of the part are in a package.

o What the pin numbers are for each section.

The Packager will print an error message if a pin is found with no PIN NUMBER property.

The basic form for a PIN NUMBER property is:

PIN NUMBER = ( <pin number> )

where <pin number> is a positive integer. If the pin represents a vector (multiple bits) rather than a scalar (single bit), the pin numbers for the pin are specified as:

PIN NUMBER = ( < <pin number>, <pin number>, ... > )

The enclosing '<' and '>' serve to indicate that the pin represents multiple bits. The pin numbers in the list must separated by commas. For example, a four bit pin might be specified as:

PIN NUMBER = (<1,2,4,5>)

If a part has multiple sections, the PIN NUMBER must specify the pin numbers for each section. The form of the PIN NUMBER property for specifying sections is:

PIN NUMBER = ( <pin number>, <pin number>, ... )

where <pin number> specifies the pin number for the same pin but for different sections. For example, the output pin of a 74LS00 (a quad NAND) would be specified as:

PIN NUMBER = (3, 6, 8, 11)

There must be four pin numbers specified since the part has four sections. All pins of the part must be assigned the same number of pin numbers (indicating the number of sections). The Packager will print an error message if this is not so.

8-19

If a pin is common to each of 4 sections, it must be given 4 pin numbers as well; the pin numbers are all identical. For example, the clock and Q pins of a 74LS273 (an octal register) would be specified as follows:

> PIN\_NUMBER = (2,5,6,9,12,15,16,19) Q pin PIN\_NUMBER = (11,11,11,11,11,11,11,11) clock

Note that the clock pin has 8 identical entries because it is common (has the same pin number) for each section of the part.

Care must be taken to ensure that the pin numbers are consistent for all pins of each section. Each number in the list specifies a different section. The Packager expects the second number in the list, for example, to correspond to the second section for every pin of the part.

If a sectioned part has a vectored pin, its pin numbers are specified in a similar manner. For instance, a 3 bit pin in a part with 2 sections might be specified as:

PIN NUMBER =  $(\langle 1, 2, 3 \rangle, \langle 5, 6, 7 \rangle)$

## 8.11 THE LOCATION PROPERTY

The LOCATION property is attached to a body in a drawing to assign its physical part designator. LOCATION properties can be attached only to physical part bodies. LOCATION properties attached to higher level drawings are errors and ignored. The LOCATION property is not inherited as a body property.

The LOCATION property always takes precedence over a physical part designator assignment in the physical part designator transformations file. An attempt at reassignment is flagged as an error. This error is classified as a FATAL ERROR. The Packager outputs a list of such discrepancies so that the drawings can be altered.

The LOCATION property is to be used only for flat drawings or wherever there is a one to one correspondence between a body in a drawing and a physical part. Since the LOCATION property specifies the physical part designator, care should be taken to make sure that layout has been considered.

Several parts may be given the same LOCATION property as long as they may all be assigned (as sections) to the same physical part. If this is not the case, an error message is produced.

## 8.12 THE LOCATION CLASS PROPERTY

The LOCATION CLASS property is used to control the assignment of logical parts to physical part by the Packager. If two logical parts have different LOCATION CLASS properties, they will not be assigned to the same physical part. However a logical part without a LOCATION CLASS may be assigned to a physical part that already has a logical part with a LOCATION CLASS. LOCATION CLASS properties are attached as body properties in the drawings.

# 8.13 MANUAL SECTION ASSIGNMENTS

The user can manually assign sections to logical parts in the drawings and have the Packager perform the specified assignments. Sections are assigned through the Graphics Editor SECTION command and works much like the VERSION command by pointing to the body or pin of the logical part.

Currently, the only parts that can be assigned to a particular section are either SIZE wide parts with a size of 1 or HAS\_FIXED\_SIZE parts. Assigning sections to a HAS\_FIXED\_SIZE part is accomplished by pointing to the pin of the section to be assigned. It is an error to point to the body of a HAS\_FIXED\_SIZE part.

If the logical part selected can be assigned to a section, the pin numbers for the selected section will be back annotated to the part in the drawing. If the same logical part is selected again, the next section will be selected and the new pin numbers will be back annotated to the part. Thus by pointing to the same logical part, one can step through all the different possible sections for the logical part.

The actual implementation for section assignment is done through the use of the SEC property which is assigned by the Graphics Editor to the logical part. If the Packager finds this property on a logical part, it will assign the logical part to the desired physical section. The user should not use or change the SEC property assigned by the Graphics Editor.

# 8.14 MANUAL PIN ASSIGNMENTS

The user can manually assign pins of a logical part in the drawings and have the Packager perform the specified assignments. The pins are assigned through the Graphics Editor command PINSWAP.

Currently, the only parts that can have pin assignments are those which already have been assigned to a section through the Graphics Editor command SECTION. It is an error to try and PINSWAP pins of a part which has not been SECTIONEd.

In addition, only pins in the same swap group are permitted to be swapped. A swappable group of pins are those pins which are logically equivalent and belong to the same section. This means that if two nets are swapped between two pins which are in a swappable group, the logical function of the circuit is not altered.

A common example of this occurs for the inputs of an NAND gate like a 74LSOO. The two input pins are physically equivalent in terms of loading and propagation delay from input to output. Thus, if the nets to the input pins are swapped, the behavior of the circuit is unchanged.

To define a swappable group, the library files must have the PIN\_GROUP property defined. Any set of pins that is swappable must have the PIN\_GROUP attached to it with the same value. Any pin without the PIN\_GROUP property is considered not swappable with any other pins. The value of the PIN\_GROUP property is not important, only that all pins of a swappable group have the identical value.

Once pin swaps have been performed on a part, further section assignments are no longer allowed for the part. This means that if the user wishes to assign a part to a different section after performing pin swaps, the part must first be de-assigned by using the REPLACE command. The user can then assign the new part to the desired section.

The actual implementation for pin assignment is done through the use of the PN property which is assigned by the Graphics Editor to the pins of the logical part. If the Packager finds this property on a pin, it will assign the nodes to the desired physical pin. The user should not use or change the PN property assigned by the Graphics Editor.

## 8.15 THE CREATION OF PHYSICAL NAMES

The Packager assigns physical names to both signals and parts the first time through. The algorithms are described below.

## CREATION OF SIGNAL NAMES

Physical net names are created from the abbreviation of the logical signal name for the net. The maximum length of the names is controlled by the NET NAME LENGTH directive always. The path name portion of the logical signal name is not used in the abbreviation. The abbreviation is created as follows:

- Remove all special characters. These are all characters except A-Z and 0-9.

- 2. If the signal is low asserted, add a trailing 'L'.

- 3. If the name starts with a digit, change it to a letter.

- 4. If the signal is vectored, append the offset as a number.

- 5. If the signal is versioned, append 'V' and the version number when the version number is not zero.

- 6. If the resulting name is greater than maximum net name length, remove all the vowels.

- 7. If the resulting name is still too long, then truncate the name to the maximum net name length.

- 8. If the resulting name is not unique, make it unique by incrementing the last non-numeric characters of the name. This is to preserve the bit offset that was appended to the name.

# CREATION OF PHYSICAL PART DESIGNATORS

Physical part designators are created by starting with the value of the PHYS DES PREFIX property found on the part type in the library, or if no such property is found, the standard prefix 'U'. If the name is not unique, it is made unique by suffixing a number. The maximum length of the names is controlled by the PART NAME LENGTH directive.

### 8.16 FEEDBACK PROCESSING

The Packager converts a logical design into a format suitable for physical design. This design as output by the Packager may not be optimal for layout, and the physical design system may rearrange parts and swap equivalent sections within a part and equivalent pins on a section. Since users need documentation of the completed physical design and may make modifications which require changes to the physical design, any changes to the physical design made during layout and wiring must be fed back into the Packager state files.

There are 4 types of changes which are commonly made during physical design:

1. Physical part name changes.

When a design is laid out, the physical part designators are often changed to include position information. A typical scheme is to give a part a name of the form <letter> <number>, where <letter> and <number> represent coordinates in two dimensions on a board. Example G13 is row G column 13.

2. Physical section reallocation.

To simplify wiring, it is often desirable to group together those parts which connect to each other. Since the sections in a part may connect to different groups of parts, it is sometimes necessary to move a section from one part into another part of the same type. If all sections of the destination part are in use, then it is necessary to move one of them somewhere else. This process is often done in the form of swaps of two sections between different parts of the same type. Sections are sometimes reallocated within a single part to improve wiring.

- 3. Physical pin reallocation within a section. To simplify wiring even more, equivalent input pins of a section may be reallocated. This is done primarily to parts having many equivalent inputs such as a 13 input NAND gate.

- 4. Physical net name changes. Changing physical net names does not affect the layout or wiring of a design, but users may wish to rename nets for documentaion or standardization reasons.

The Packager currently can process four types of feedback files. The user has the freedom to use any or all of the files as the situation requires. Only these files should be used to change the physical design. The state files should never be edited by the user. These files are as follows:

PSTPRTX - Physical part designator transformations file

This file contains a list of old physical part designator and new physical part designator pairs.

8-24

- PSTSECX Physical section transformations file This file contains a list of old physical section to new physical section pairs.

- 3. PSTNETX Physical net name transformations file This file contains a list of old physical net name to new physical net name pairs.

- 4. PSTFNET Feedback net list This file contains a net list sorted by physical part designator of the current physical design. The only restriction is that the physical net name must not have changed or the new physical net names have already been fedback before performing a net list feedback. The Packager will detect and perform all physical part designator changes, physical section swapping, and pin swapping from the feedback net list.

The FEEDBACK ORDER directive is used to specify which files and order of feedback processing for the Packager. The file types allowed are as follows:

PART TRANS

This specifies the physical part designator transformations file (PSTPRTX).

SECTION TRANS

This specifies the physical section reallocation file (PSTSECX).

NET TRANS

This specifies the physical net name transformations file (PSTNETX).

FEEDBACK NETLIST

This specifies the feedback net list (PSTFNET).

An example of this directive is as follows:

FEEDBACK ORDER NET TRANS, FEEDBACK NETLIST;

which specifies that physical net name transformations occur first followed by a feedback net list transformation.

Feedback of physical design changes can only occur when state files generation have been enabled, otherwise the changes being fedback cannot be saved. The Packager will generate an error if the FEEDBACK ORDER directive is used without enabling the use of state files through the USE STATE FILES ON; directive.

Due to the current implementation, feedback processing will only work if the logical design (the compiler expansion file) has not changed since the design was last packaged to generate a physical design from which the changes are derived and the design now being processed for feedback changes. This means the compiler expansion file, library files, and all Packager generated state files should be saved for a design that is sent to a physical design system. By saving these files, the Packager will be able to feedback the physical changes made by the physical design system.

## 8.17 BACK ANNOTATION

Information in the SCALDsystem usually flows from the drawings, through the Compiler and Packager, and on to physical design systems. However, there is an important class of information that flows from the end of the SCALD process to the beginning. The Packager and the physical design system add information to the design which you may wish to see reflected in the drawings. Most typical of this information is the physical part designator for each part and the pin number for each pin. This process of taking information created or added downstream in the design process and bringing it upstream is called back annotation.

The most common form of back annotation is bringing information from the Packager (physical design information) and adding it to the drawings. The Packager generates a back annotation file that contains physical information grouped by drawing. To generate this file, the directive OUTPUT BACKANNOTATION; should appear in the directive file. Backannotation can occur on three types of elements: bodies, pins, and nets. In order to select among these elements, the ANNOTATE directive should be used. If this directive is not specified, the default options will be bodies and pins. If the net option is specified, the synonym file from the compilation must be available. The back annotation information is written to the logical file PSTBACK.

The back annotation file can then be read by the Graphic Editor with the BACKANNOTATE command. This will add all the physical information in the file to the drawings. It is recommended that you copy all the drawings to another directory before back annotation is performed. This will give you both non-annotated and annotated versions of the drawings which may be useful since it is not easy to remove the annotated properties from a set of drawings.

## 8.18 OUTPUT FILE FORMATS

This section describes the formats of each of the output files created by the Packager. All output files are text files.

# STATE FILES

The Packager generates several state files to maintain the physical assignments through several runs of the Packager. The state files are written to the logical files PSTPRTB, PSTSIGB, PSTPSWP, and PSTSTAT. They are described in the section "Packager State Files" later in this chapter.

#### **CROSS REFERENCES**

The Packager generates several cross references to the logical file PSTXREF. A complete description of these files and their use is described in the "Packager Cross References" section later in this chapter.

# EXPANDED NET AND PART LISTS

The expanded net and part lists produced by the Packager contain logical to physical net and part bindings, as well as all the properties attached to pins and bodies. These files are intended for use in interfacing to unsupported physical design systems. These list are written to the logical files "PSTXNET" and "PSTXPRT" respectively. They are described in the "Packager Expanded Lists" section later in this chapter.

## LOGICAL CHANGES LIST

This file consists of a list of the changes in the logical design between the current input and the last run of the Packager. The changes are essentially add and delete lists of logical parts.

The Packager compares the Compiler expansion file and the Packager state files to find the following:

- 1. Any logical parts that were not present during the last run of the Packager.

- 2. Any logical parts present during the last run of the Packager and are not present during the current run. Each of these parts has a corresponding physical part designator.

The Packager lists each of the parts found to give a summary of the changes made. The form of the list is:

where <list of logical part designators> lists each logical part designator separated by ';'. The second list consists of a logical part designator followed by a physical part designator separated by ' ' and terminated with a ';'.

An example Logical Changes file:

LOGICAL CHANGES LIST - 1 12-AUG-1982 13:18:10.21 LOGICAL PARTS ADDED TO DESIGN: (FG1 .HH 1.TTT .00)74LS00; (ABC XYZ .253)74LS253; LOGICAL PARTS DELETED FROM DESIGN: (ABC XYZ .122)74LS122 U31; (REG .04)74LS04 U76; END LOGICAL CHANGES LIST

#### 8.19 POWER AND GROUND PIN ASSIGNMENTS

Power and ground pin assignments for each part are specified with the POWER PINS property attached to the part within the libraries. The POWER PINS property is used to specify both the names of the power rails as well as the pin numbers. The form of the PIN NUMBER property value is:

( <power rail> : <pin list> ; ... )

where <power rail> is the name of the power supply rail and must be an identifier (a string of letters, digits, or '' starting with a letter). The <pin list> is a list of the pin numbers of the part (separated with commas) that connect to the power rail. The ';' is used to separate the power rail specifications.

For example, a TTL part has two power pins: VCC and GND. The 74LS00 would have the property:

\$

POWER PINS = (VCC:14; GND:7)

The TMS4050 RAM would have the following property:

POWER PINS = (VBB:1;VDD:10;VSS:18)

The 100123 bus driver would have the following property:

POWER PINS = (VCC:6; VCCA:7,9,11,5,3,1; VEE:18);

The order of the values is not important. The POWER PINS property only applies to parts found within the libraries and is ignored if found elsewhere.

8.20 DESCRIPTION OF THE CHIPS FILE

The CHIPS file contains a description of every physical part in the libraries. It is generated by the Compiler from a drawing that uses every physical part exactly once. The Valid supplied libraries have such drawings. See, for example, the LSTTL LIBRARY drawing in the LSTTL library.

The CHIPS file contains information attached to the body as well as the .PART drawing describing the part. The following information is expected for each part:

- 1. PIN NUMBER property on every pin.

- 2. INPUT LOAD or OUTPUT LOAD properties on every pin.

- 3. POWER PINS property for the part. This may be attached to the body or to the .PART drawing (attached to the DRAWING body within the .PART drawing).

- 4. FAMILY property for the part. This may be attached to the body or to the .PART drawing (attached to the DRAWING body within the .PART drawing).

Other properties recognized by the Packager but not required:

- 1. BIDIRECTIONAL pin property if the pin is both an output and an input.

- 2. UNKNOWN LOADING pin or body property indicating that device loading is not known.

- 3. NO LOAD CHECK pin or body property used to suppress device loading calculations.

- 4. NO\_IO\_CHECK pin or body property used to suppress input and output net checks.

8-29

- 5. WIRE GATE body property indicating that the body is a phantom wire gate (such as a WIRE-OR).

- 6. WIRE\_GATE\_OUTPUT pin property indicating that this is an output pin of a wire gate.

- 7. OUTPUT TYPE pin property which specifies whether other outputs can be connected to the pin and what type they must be.

- 8. ALLOW CONNECT pin property to permit an output pin to be connected to a net regardless of whether there are other outputs on the net.

- 9. PHYS DES PREFIX body property which specifies the prefix to use for physical part designator creation.

- 10. PIN\_GROUP pin property which specifies whether a pin belongs to a group of swappable pins or not.

The CHIPS file is generated with the Compiler by compiling the library description drawings with the OUTPUT CHIPS; directive specified. The Compiler produces a chips file in the file CHIPS which is read by the Packager. The library manager has the responsibility to see that the CHIPS files used by the the designers are up to date. The CHIPS file must be recreated whenever the libraries are modified.

The libraries are described, for the purpose of creating the CHIPS file, in drawings of the form: <library> LIBRARY where <library> is the name of the particular library. For example, the LSTTL library is described in the drawing LSTTL LIBRARY. The library description drawing contains exactly one instance of each of the parts in the library. Only one version of parts with multiple body versions is permitted in the library description drawing. If the part has body versions that are asymmetrical (for example if the two versions describe sections of the part that have different function) both versions of the part must appear.

## 8.21 FORMATS FOR USER GENERATED FILES

This section describes the formats of the files you can generate. The Packager reads these files. All input files for the Packager are text files. Every file is terminated by an 'END.' which serves to mark the end of the file as well as provide a method for determining whether the file is complete. The header lines in the file serves to identify the file and the name of the design. The form of the header lines are:

FILE\_TYPE = <file type> ;

ROOT DRAWING = '<drawing name>' ;

where <file type> specifies the file's type (see below for each file described) and <drawing name> is the name of the root drawing of the expansion file. The header for the Physical Part Designator Transformations file would appear as:

> FILE\_TYPE = PART\_TRANS; ROOT\_DRAWING = 'RISC/E II';

Comments may be placed in the files if enclosed in '{' and '}'. A comment may appear anywhere a space may appear. Comments may cross line boundaries. Comments may not be nested.

If an item is too long to fit on a line (80 characters), it must be broken into more than one line. A tilde ('~') should be used as a continuation character to indicate that the current item is continued on the next line. A line break can appear between ANY TWO CHARACTERS in the file. A tilde is only significant if it occurs at the end of the line.

# PHYSICAL PART DESIGNATOR TRANSFORMATIONS

This file is used to change a physical part designator assigned by the Packager to one determined by the user. The physical part designator is used to identify a particular instance of a physical part. Each physical part is (usually) a real, purchaseable, wireable, tangible entity (unlike Viming Verifier or Simulator primitives).

The file type for this file is PART TRANS. The file consists of a list of transformations. Each transformation is of the form:

'<old part designator>' '<new part designator>'

where <old part designator> is the physical part designator assigned by the Packager during its last run and <new part designator> is the new physical part designator to be assigned. For instance, the physical part designator U31 can be changed to U32 as follows:

> FILE TYPE = PART TRANS; ROOT DRAWING = 'RISC/E II';

> 'U31' 'U32' END.

# PHYSICAL NET NAME TRANSFORMATIONS

This file is used to change the name given a physical net. Each net is originally assigned a name by the Packager. That name can be changed with this file. The file type for this file is NET TRANS. The file consists of a list of transformations. Each transformation is of the form:

'<old physical net name>' '<new physical net name>'

where <old physical net name> is the name assigned to the net by the Packager in the last run and <new physical net name> is the new name to be assigned to the net. For example, the net N00001 can be changed to XYZ with the transformation:

> FILE\_TYPE = NET\_TRANS; ROOT\_DRAWING = 'RISC/E II'; 'N00001' 'XYZ' END.

#### PHYSICAL SECTION TRANSFORMATIONS

The Packager assigns sections during the first run of a design. Sections of parts are assigned sequentially so that individual bits of a signal will be connected to the same package. No layout knowledge is used during this assignment. When more reasonable section assignments are known, they can be given to the Packager which will use that information to reassign sections. The Physical Section Transformations file is used to specify section changes.

The file contains a list of old physical pin designators (as assigned by the Packager during its last run) and new physical pin designators where a physical pin designator consists of a physical part name and a unique pin number of the section (not a common pin). The Packager will reassign the sections as specified in this file. If a section is reassigned that was already assigned in the drawings (through section assignment), the Packager will NOT change the assignment. An error message is printed in this case. This error is classified as a FATAL ERROR. The only way to change section assignments assigned in the drawings is to change the drawings.

The file type for this file is SECTION TRANS. The file consists of a list of transformations. Each transformation is of the form:

'<old part>' <old pin> '<new part>' <new pin>

where <old part> and <old pin> specify the current section assignment and <new part> and <new pin> specify the new section assignment. For example, given a 74LS00 (quad NAND), a swap of the first two sections on the part U31 might appear as follows:

```

FILE TYPE = SECTION TRANS;

ROOT DRAWING = 'RISC/E II';

'U31' 1 'U31' 4

'U31' 4 'U31' 1

END.

```

FEEDBACK NET LIST

If a physical design system can generate a net list which specifies part types and represents a physical design differing from the design produced by the last run of the Packager only by physical part designator changes and physical section reallocation, then the Packager can extract these changes and perform these transformations. The Feedback Net List is used by the Packager to extract these transformations of physical designators and section assignments.

The file type for this file is FEEDBACK NETLIST. The file consist of a list of nodes of the design. Each node entry is of the form:

'<physical part name>'

'<physical part type>'

<pin number>

'<physical net name>';

where <physical part name> is the new physical part designator, <physical part type> is the part type of the physical part, <pin number> is the pin number of the node and <physical net name> is the name assigned to the net by the Packager to which the node is connected.

The file MUST be SORTED by physical part name, so that all the pins of a physical part appear together. The ordering of the pins on the part does not matter. An example of this file might appear as follows:

FILE TYPE = FEEDBACK NETLIST; ROOT\_DRAWING = 'RISC/E II'; 'U1' 'LSO8' 1 'A0'; 'U1' 'LSO8' 2 'B0'; 'U1' 'LSO8' 3 'CO'; 'U1' 'LSO8' 4 'A1';

| 'Ul' | 'LS08' | 5  | 'B1'; |

|------|--------|----|-------|

| 'Ul' | 'LS08' | 6  | 'C1'; |

| ′U1′ | 'LS08' | 8  | ′C2′; |

| 'Ul' | 'LS08' | 9  | 'A2'; |

| ′U1′ | 'LS08' | 10 | ′B2′; |

| 'U1' | 'LS08' | 11 | ′C3′; |

| ′U1′ | 'LS08' | 12 | 'A3'; |

| ′U1′ | 'LS08' | 13 | ′B3′; |

| END. |        |    |       |

## 8.22 INTERFACE SIGNALS

Interfaces between a circuit and the external components it connects to must be defined in some manner. This is normally done in board level designs by implicitly defining interface signals through connectors spread throughout the design. Many gate array design systems, however, treat interface signals (those which connect to the chip carrier and hence go off the chip) as different from internal signals. Often they must be declared in separate parts of the net list, and must have extra information attached. For this reason, the Packager must be able to distinguish interface signals and treat them specially.

The Packager supports the use of FLAG bodies in the drawings to define the connection of interface signals in a root drawing to some external component such as a gate array chip carrier. To define a signal as an interface signal, attach a FLAG body to the signal. When the INCLUDE IO LIST ON; directive is specified, the Packager will attach to the interface signals the IO NET property with either the values INPUT, OUTPUT, or BIDIRECTIONAL, as defined by the FLAG body. These properties are then output in the Expanded Net List.

## Packager Directives Summary

### 8.23 PACKAGER DIRECTIVES

The Packager directives are used to specify input and output files, control message generation, and direct the Packager execution. The directives are placed in a text file and given to the Packager as the logical file INFILE which is bound to the file PACKAGER.CMD (PACKAGER CMD in CMS) by default. Each of the directives is described below. The directives and their parameters are not case sensitive.

#### ANNOTATE

Used to specify the allowable schematic back annotation information to generate for the BACKANNOTATION output file. If more than one of these directives appears in the directive file, the Packager ignores all but the last one. The form of the directive is:

ANNOTATE <option> , <option> , ...;

The options for this directive are as follows:

BODY

When specified, allows the back annotation of physical part designators.

#### PIN

When specified, allows the back annotation of physical pin numbers.

#### NET

When specified, allows the back annotation of physical net names. Currently only scalar nets can be annotated. The synonym file from the compilation of the design must be available for the net option to be successful.

If directive is unspecified, the Packager will generate back annotation for BODY and PIN when the BACKANNOTATION output file is generated.

#### FEEDBACK ORDER

Used to specify which feedback files and their order to perform feedback processing for the Packager. This

## 8-35

Packager Directives Summary

directive can only be used in the directives file once. The form of the directive is: FEEDBACK ORDER <file type>, <file type>, ...; The allowable <file type> for this directive are as follows: PART TRANS This specifies the physical part designator transformations file (PSTPRTX). SECTION TRANS This specifies the physical section reallocation file (PSTSECX). NET TRANS This specifies the physical net name transformations file (PSTNETX). FEEDBACK NETLIST This specifies the feedback net list (PSTFNET). An example of this directive is as follows:

FEEDBACK ORDER NET TRANS, FEEDBACK NETLIST;

which specifies that physical net name transformations occur first followed by a feedback net list transformation. If this directive is unspecified, the Packager will not perform feedback processing.

### FILTER PROPERTY

Used to specify properties that are not to be included in the expanded net and part lists. A list of property names separated by commas is given. The Packager makes sure that these properties are not output to the expanded net and part lists. This directive has no impact on any other file. The properties FOO, GRBX, and PATH could be suppressed with the directive:

FILTER PROPERTY FOO, GRBX, PATH;

Any number of properties can be listed. The FILTER PROPERTY directive can be specified as many times as desired.

## INCLUDE IO LIST

Used to control whether the nets connected to the interface pins of the design are included in the Expanded Net List with the IO\_NET property. The value of the IO\_NET property is either INPUT, OUTPUT, or BIDIRECTIONAL as defined by the FLAG body. The directive is specified as follows:

| INCLUDE_IO_LIST ON;  | output the IO <u>NET</u> property<br>for the interface pins. |

|----------------------|--------------------------------------------------------------|

| INCLUDE_IO_LIST OFF; | do not output the IO_NET property for the interface pins.    |

If this directive is unspecified, the Packager will not output the interface pins.

## LIBRARY FILE

Used to specify the names of files containing library components. These files are produced by the Compiler using the OUTPUT CHIPS directive. Any number of libraries can be specifed with this directive. The names can be placed in a list separated by commas or listed individually with separate LIBRARY\_FILE directives. For example, the directive:

LIBRARY FILE '100k.prt', '1sttl.prt';

specifies two library files, 100k.prt and lsttl.prt, and is equivalent to the directives:

LIBRARY\_FILE '100k.prt'; LIBRARY\_FILE '1sttl.prt';

The Packager checks to make sure that a file is not specified more than once.

#### MAX ERRORS

Used to specify the maximum number of errors allowed before the Packager gives up and terminates. When this condition occurs, the Packager prints a message and terminates with a summary of the execution. The maximum number of errors can be set to 500 as follows:

MAX ERRORS 500;

Packager Directives Summary

If not specified, the Packager terminates after 1000 errors.

## OUTPUT

Used to control which output files are produced by the Packager. Each of the various output listings can be individually suppressed or enabled. All files are generated by default. The first OUTPUT directive encountered causes all output files to be turned off (so that they may be individually turned back on) unless the '-' option is used, in which case files are deleted individually. The 'ALL' identifier can be used to turn all files on or off. For example, the directive:

OUTPUT;

is equivalent to the directive

OUTPUT -ALL;

which turns off all output files.

The names of these files are listed separated by commas in a single OUTPUT directive or can be specified with multiple OUTPUT directives. For instance, the directive:

OUTPUT EXPANDEDNETLIST, EXPANDEDPARTLIST;

is equivalent to:

OUTPUT EXPANDEDNETLIST; OUTPUT EXPANDEDPARTLIST;

In both of the above examples, the only output files that will be generated are the expanded net list and the expanded part list.

Each of the OUTPUT files are listed below.

EXPANDEDNETLIST

Causes the expanded net list to be output to the file PSTXNET.

EXPANDEDPARTLIST Causes the expanded part list to be output to the file PSTXPART.

LOGICALCHANGES Causes the logical changes summary to be output to the

### file PSTLCHG.

### CROSSREFERENCES

Causes all of the cross references to be output to the file PSTXREF.

### LOCALPARTXREF

Causes the local part crossreference to be output to the file PSTXREF.

GLOBALSIGNALXREF

Causes the global signal crossreference to be output to the file PSTXREF.

#### GLOBALPARTXREF

Causes the global part crossreference to be output to the file PSTXREF.

#### BACKANNOTATION

Causes the back annotation file to be output to the file PSTBACK.

If no OUTPUT directive is specified, the Packager produces all files.

## OVERSIGHTS

Used to control whether oversight messages are displayed. Several conditions are detected during execution of the Packager that are considered to be more serious than a warning (see below) but not as serious as an error. The oversights should be corrected, but the design will probably work without first fixing them. The total number of oversights detected is always reported at the end of the program regardless of whether they were printed or not. This directive is used to turn off all oversight messages. The SUPPRESS directive can be used to turn off specific oversight message by message number. The directive is specified as follows:

| OVERSIGHTS ON;  | display all oversight messages<br>on the Packager's list<br>file. |

|-----------------|-------------------------------------------------------------------|

| OVERSIGHTS OFF; | display no oversight messages.                                    |

# PART NAME LENGTH

Used to control the maximum physical part name designator length to be generated by the Packager. The form of the directive is:

## PART NAME LENGTH <length>;

If this directive is unspecified, the Packager will use a default length of 16.

### PART TABLE FILE

Used to specify the names of files containing physical part tables. Any number of physical part table files can be specifed with this directive. The names can be placed in a list separated by commas or listed individually with separate PART\_TABLE\_FILE directives. For example, the directive:

PART TABLE FILE 'res.tab', 'cap.tab';

specifies two physical part table files, res.tab and cap.tab, and is equivalent to the directives:

PART TABLE FILE 'res.tab'; PART TABLE FILE 'cap.tab';

The Packager checks to make sure that a file is not specified more than once.

# PASS PROPERTY

Used to control whether a specific property appears in the expanded net and part lists. The PASS PROPERTY directive takes a list of properties like the FILTER PROPERTY directive above. If the directive is not specified, all the properties are defaulted to pass into the expanded lists. Once specified, only those explicitly selected properties are allowed to pass into the expanded lists. The pass operation is performed before filtering, thus those properties explicitly allowed to pass may then be suppressed by filtering them out. See also the FILTER PROPERTY directive.

# NET NAME LENGTH

Used to control the maximum physical net name length to be generated by the Packager. The form of the directive is:

NET NAME LENGTH <length>;

If this directive is unspecified, the Packager will use a default length of 24.

### REPORT

Used to control which user reports to generate. The syntax of this directive is the same as the OUTPUT directive and supports the '-' and 'ALL' options. All the reports are written to the logical file PSTRPRT. The available reports are as follows:

#### SPARES

This report contains the all the spare physical sections in the design. Spare physical sections are sections which have not been allocated to a logical part and are listed by physical part designator and a unique pin number of the section that is a spare.

### PARTSUMMARY

This report contains a summary of all the physical parts used in the design. It is a list of part types and the number of physical parts used for that part type. A grand total is also generated for all the physical parts used in the design.

If no REPORT directive is specified, the Packager produces all reports.

### SUPPRESS

Used to suppress specific warning and oversight messages. Warnings and oversights are used to grade the severity of error conditions detected by the Packager. Warnings are considered to be the least severe, followed by oversights, and then errors. Since neither warnings nor oversights are as severe as an "error", and since there may be many of these messages in a good design, this directive is supplied to suppress the message that would be produced. The design conventions assumed by the Packager Directives Summary

> Packager are conservative and rigorous. The user may choose to design in a more liberal style and may want to ignore certain messages. Warning 132 can be suppressed with the directive:

SUPPRESS 132;

A list of warning messages may be specified as, for instance:

suppress 132,133,134;

All warning messages can be suppressed with the WARNING directive (see below). Error messages cannot be suppressed. If unspecified, the Packager suppresses no warnings or oversights.

### USE STATE FILES

Used to control whether the Packager reads and generates state files. The directive is specified as follows:

| USE_STATE_FILES ON;  | use state files if present<br>and generate new state files. |

|----------------------|-------------------------------------------------------------|

| USE_STATE_FILES OFF; | do not use or generate any state files.                     |

If this directive is unspecified, the Packager will use and generate state files.

### WARNINGS

Used to control whether the Packager prints warning messages. Several conditions are detected that are not as severe as errors, but need to be brought to the attention of the designer. All warning conditions can be eliminated by adding the needed information (described in the warning message) to the drawings. This directive can be used to suppress all warning messages (though it is a good idea to add the information to the drawings - this info helps to more clearly document the design). The total number of warning conditions encountered is reported at the end of the program regardless of whether warnings are displayed or not. The directive is specified as follows:

WARNINGS ON; display all warning messages on

the Packager's list file.

WARNINGS OFF; display no warning messages.

If unspecified, the Packager prints all warning messages.

## 8.24 AN EXAMPLE OF A PACKAGER DIRECTIVES FILE

The Packager directives file can be created with a text editor. The Packager pays no attention to the end-of-line or to multiple spaces. The letter case of the directives is unimportant. This is true both for directive names as well as file names within strings. Comments may be placed in the file if enclosed with '{' and '}'. Note that all Packager directives must be separated by ';' and the file must end with an 'end.'.

|                   | • | output the expanded net list   | } |

|-------------------|---|--------------------------------|---|

| EXPANDEDPARTLIST; | Ł | output the expanded part list  | } |

| warnings on;      | { | display all warning messages   | } |

| end.              | { | this marks the end of the file | } |

HARD-LOC-SET OFF;

Packager PIN NUMBER Property

# The PIN NUMBER Property

### 8.25 INTRODUCTION

The Packager recognizes the PIN NUMBER property on pins of parts in the CHIPS files. The property is used to assign the physical pin numbers for each logical pin so that the Packager can do physical assignments. The Packager requires PIN NUMBER properties for every pin of every part. The absence of the property on any pin is considered fatal.

The PIN\_NUMBER property for scalar pins has the following form:

PIN NUMBER =  $(\langle pin \rangle, \langle pin \rangle, \dots)$

where <pin> is a pin number. A multiple section part has several pin numbers for a pin, one for each section.

A PIN\_NUMBER property on a vector pin has the following form:

PIN\_NUMBER = ( < <pin>, <pin>, ... >, < <pin>, ... >, ... )

where <pin> is a pin number which can be either an integer or an identifier consisting of letters, digits, or ' ' with a maximum length of 16 characters. The enclosing '<' and '>' are used to indicate that the list of pin numbers specifies individual bits of the pin and not different sections for the pin.

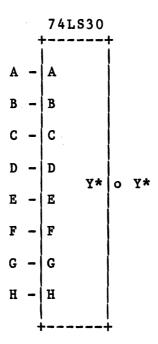

# 8.26 PIN NUMBERS FOR SINGLE SECTION SCALAR PINS

A scalar pin is a pin which corresponds to a one bit signal. This is different from a vector pin which corresponds to a several bit signal. The PIN NUMBER property for each pin of a simple one section part like a 74LS30 is a single positive integer enclosed by parentheses as follows:

| 74LS30 |    |   |    |   |    |  |  |  |  |

|--------|----|---|----|---|----|--|--|--|--|

|        | ++ |   |    |   |    |  |  |  |  |

| A      | -  | A |    |   |    |  |  |  |  |

| B      | -  | В |    |   |    |  |  |  |  |

| С      | -  | С |    |   |    |  |  |  |  |

| D      | -  | D | Y* | 0 | Y* |  |  |  |  |

| E      | -  | Е | 1  | U | 1  |  |  |  |  |

| F      | -  | F |    |   |    |  |  |  |  |

| G      | -  | G |    |   |    |  |  |  |  |

| H      | -  | н |    |   |    |  |  |  |  |

| <br>++ |    |   |    |   |    |  |  |  |  |

PIN PIN NUMBER property Α (1)B (2) С (3) D (4) Е (5) F (6) G (11)H (12)Y\* (8)

8-45

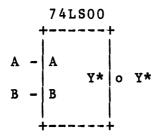

# 8.27 PIN NUMBERS FOR MULTIPLE SECTION SCALAR PINS

Some physical parts contain several equivalent sections which each correspond to the logical part of the given type. An example is the 74LS00, which contains 4 2-input NAND gates, and the logical part for a 74LS00 is a single 2-input NAND gate. The sections of a part are specifed by the PIN\_NUMBER property on a logical pin by logical pin basis. Each pin of the logical part has a PIN\_NUMBER property containing a list of pin numbers, one pin number for each section in the part. The sections are ordered, with all pins for the Nth section present in the Nth position in the PIN\_NUMBER property values. Each logical pin of a 74LS00 has 4 pin numbers, one for each section. The pin numbers for various sections within the PIN\_NUMBER property are separated by commas as follows:

PIN

PIN NUMBER property

| A  | (1,4,9,12)  |

|----|-------------|

| В  | (2,5,10,13) |

| Y* | (3,6,8,11)  |

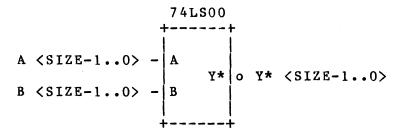

### 8.28 PIN NUMBERS FOR SIZE EXPANDED PARTS

A scalar pin may be defined as a SIZE wide pin on a SIZE replicated part, for which each bit of the attached bus connects to a different section of the part. The part definition for a SIZE wide part defines the SIZE wide pins as scalars, since for each section, those pins are only one bit wide. The 74LS00 shown above could (and probably would) be defined as a SIZE replicatable part as follows:

PIN PIN NUMBER property

| A $\langle SIZE-10 \rangle$ | (1,4,9,12)     |

|-----------------------------|----------------|

| B <size−10></size−10>       | (2, 5, 10, 13) |

| Y* <size-10></size-10>      | (3, 6, 8, 11)  |

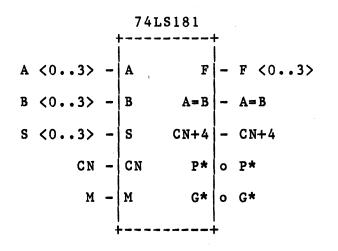

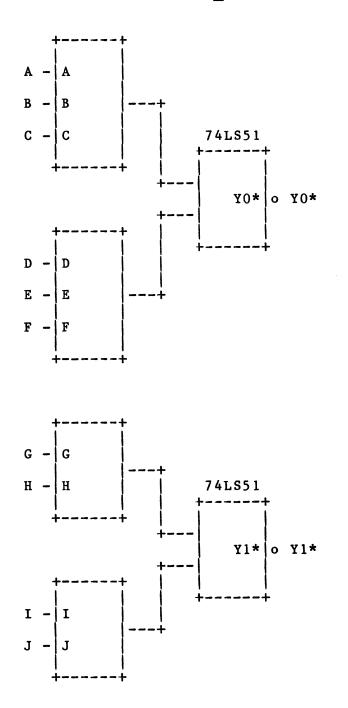

### 8.29 PIN NUMBERS FOR VECTOR PINS

A vector pin is a multiple bit pin having a fixed number of bits (not effected by the value of the SIZE property), where each bit of the vector connects to the same section of the part. Examples of vector pins are the data buses of a 74LS181 ALU. A vector pin has a PIN NUMBER property of the same form as a scalar pin, except that each logical pin number is generalized to include several physical pin numbers, enclosed between a less-than sign "<"

PIN

PIN NUMBER property

| A <03> | (<19,23,21,2>) |

|--------|----------------|

| B <03> | (<18,20,22,1>) |

| S <03> | (<3,4,5,6>)    |

| CN     | (7)            |