MAY 1 6 1985

## CHAPTER 6

### TIMING VERIFIER

### Reference Manual

## 6.1 INTRODUCTION

The Timing Verifier represents a new approach to verification of timing constraints of large digital systems. The Timing Verifier uses an algorithm which is computationally efficient and complete. Furthermore, the Timing Verifier does not require test inputs (such as a logic simulator) and works directly from the output of the Compiler. Thus, timing verification is done using only the designer's original set of drawings.

The Timing Verifier allows the verification of entire designs or of designs section by section. Verification of portions of a design means that small pieces of a design may be verified to save computation time. Similarly, a design need not be complete to be verified - verification can proceed on the finished sections. Designers can check their own pieces of a system on a daily basis, getting continuous feedback on its correctness as work proceeds. Verification of an entire system can be done when the pieces are known to be correct.

## WHAT IS TIMING VERIFICATION?

Digital systems are composed of components and their interconnections, or wires which convey <u>signals</u> from one component to another. In general, when a signal on the input of a component changes, some time later the signal on the output changes. The wire connected to this output then conveys the signal to the input of other components, again after some delay. Because of variations in construction, the delay time of components and wires varies.

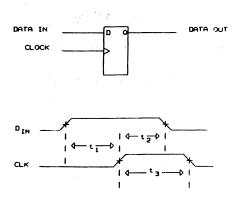

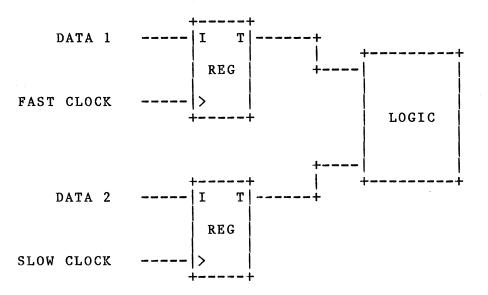

At certain places in a system - data inputs of registers, and external interfaces for example - a signal must assume its value at a certain time. Thus, if a path to such a place is too long or too short, the system may yield an incorrect result. For example, consider a circuit consisting of a D register:

For real devices, tl must be longer than some critical time - the setup time of the register ts - or the device may malfunction. If the data delay is long, tl may shrink below ts, violating the setup time spec of the register. Similarly, t2 must be longer than the hold time of the register, th. If the data delay is short, the hold time specification of the register may be violated. Finally, the width of the clock pulse, t3 must exceed some minimum time, or correct operation of the register is not guaranteed.

As a second example, consider a memory interface with a data bus and a data out valid signal:

| D<0> | <j21></j21> | D<4> | <j25></j25> |

|------|-------------|------|-------------|

| D<1> | <j22></j22> | D<5> | <j26></j26> |

| D<2> | <j23></j23> | D<6> | <j27></j27> |

| D<3> | <j24></j24> | D<7> | <j28></j28> |

DOVAL ----<J30>

There will typically be some specification that data must be ready some period of time before DOVAL becomes true. If this setup time is not met, systems connected to the memory may malfunction.

The Timing Verifier checks that there are no timing violations of these two types in the design. That is, at all points in a design:

- o Component constraints (setup, hold, pulse width, etc.) are observed.

- o All interface specifications provided by the designer are met.

Timing constraint verification is based on minimum and maximum propagation delays of circuit components, their set-up times, hold times and pulse width constraints, wire delays and interface specifications.

### 6.2 TIMING VERIFIER OPERATION

The Timing Verifier operates in two phases. First, it computes the value history of every signal in the system over one clock period. Then, it checks that the signals meet the timing constraints of the components and interfaces.

## 6.3 SIGNALS IN THE TIMING VERIFIER

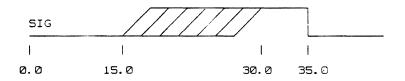

The Timing Verifier represents the behavior of a signal over time textually. For example, a signal SIG is shown as a waveform and in Timing Verifier text format:

SIG: 0:0.0, R:15.0, 1:30.0, F:35.0, 0:35.0

The evolution of a signal over a clock is called its <u>value</u> history.

A basic assumption of the Timing Verifier is that the circuit to be verified has periodic behavior. That is, given a circuit and a set of input stimulus, there is some state of the circuit S and some time T, such that starting the circuit in state S, applying the inputs and simulating for time T, the circuit returns to state S. (By state of a circuit, we mean the value history of each signal in the design.) Synchronous sequential circuits, and strictly combinational circuits both have this property.

In general, the design is simulated using an 8 value logic system:

1. 0 -- signal is 0 or false

2. 1 -- signal is 1 or true

3. S -- signal is stable, that is either 0 or 1

## Timing Verifier Reference Manual

- 4. R -- signal is rising going from 0 to 1

- 5. F -- signal is falling going from 1 to 0

- 6. C -- signal is undergoing a transition of unknown direction

- 7. U -- nothing is known about the signal

8. Z -- the signal is high impedance

The truth table for an AND gate in this logic system is:

| AND  0 1 S R F            | CUZ                                      |

|---------------------------|------------------------------------------|

| 0  0 0 0 0 0 0            | 000                                      |

| 1  0 1 S R F 0            | כ ט ט                                    |

| S  0 S S R F 0            | ט ט                                      |

| R   0   R   R   R   C   0 | ט ט                                      |

| F   O   F   F   C   F   C | ט   ט                                    |

| c  0 c c c c c            | ן ט   ט   כ                              |

| 10 0 0 0 0 U              | ט   ט                                    |

| z  0 u u u u              | <u>  ם</u>                               |

| 1                         | C. C |

The intent of this approach is to preserve the logic behavior of the circuit when actual values are known, and in other cases, to represent a signal as stable (0,1 or S), or undergoing a transition (R, F or C). In most cases, this information is sufficient for timing verification. For example, to verify the setup and hold time of a register, you only need to know when the D input is undergoing a transition and when it is stable with respect to the clock input. The actual value (0 or 1) on the D input is not important. Similarly, you do not need to know the output value (0 or 1) of the register. The output of a register changes only during a short interval after it is clocked and otherwise it is stable. Using S means that the contents of registers and memories do not have to be specified, greatly reducing the amount of time the designer has to spend preparing inputs for the verifier. Also, using S exponentialy reduces the number of states that must be simulated to verify the timing behavior of the circuit. For example, a k-bit counter that contains the value SSSSS....SS (k times) has only one state, not 2\*\*k states. Rarely does a circuit's timing depend on the actual value in the counter, but merely how long after the counter is clocked it takes for the outputs to stop undergoing transitions.

There are some cases where modelling the signals in a circuit as stable or undergoing a transition is not adequate, the actual (0,1) behavior is necessary. The Timing Verifier has a mechanism called <u>case analysis</u> for handling these situations.

In addition to the eight values described above, a signal may have one of three strengths, HARD, SOFT and UNDRIVEN. In effect the Timing Verifier does a kind of twenty-four state simulation. Signal strengths are discussed in detail in section "Signal Drive Strengths".

## 6.4 SCALD SIGNALS AND THE TIMING VERIFIER

The Timing Verifier needs certain kinds of information about signals in the system being checked. For example, interface specifications for those output signals that are to be checked must be provided. In general there are three kinds of information that the Timing Verifier extracts from signals - timing behavior, delays and special evaluation rules.

Timing Behavior (Signal Assertions)

The Timing Verifier initially sets all undriven signals of the circuit to "S" (stable) and all others to "U" (undefined). Often systems will have many undriven inputs set to "S" in this manner and consequently will not exhibit meaningful timing behavior. Some examples of this are:

- Primary inputs to the system. For example the design may be a controller which "talks" on some standard bus interface. If all the interface (input) signals are always stable, the controller will not operate.

- 2. Partial designs. One of the most important aspects of the Timing Verifier is the ability to verify the timing of partial designs. (A partial design may be either one that is incomplete, or a piece of an entire system that was extracted for separate timing verification.) In a partial design, signals that have not been generated yet will be undriven.

- 3. Clock Signals. In large systems it is often convenient to defer the design of the logic for complex multiphase clocks to near the end of the design cycle. These signals will therefore be undriven, even though their

Timing Verifier Reference Manual

> timing behavior is known. Furthermore, a synchronous system will not do anything unless these clock lines are driven.

For these signals <u>assertions</u>, which are simply part of the signal name, can be added. Assertions <u>define</u> the value history of signals when the history is not determined by a driving device. Assertions are discussed in detail below.

### DELAYS

Timing verification requires the modelling of both component and interconnect delays. Component delays are specified inside Timing Verifier library components. Interconnect delays on the other hand are specified as delays associated with wires.

A delay is associated with a wire in one of several ways:

- The designer may place a delay property on a signal. If this is done that particular instance of the signal has the specified delay.

- 2. The Timing Verifier will read a list of delays typically computed by some physical design subsystem. A list element associates a delay with an <u>input</u> pin. Thus the delay on each stub of a signal that drives multiple loads may be specified.

- 3. The Timing Verifier can use its delay estimator to calculate an estimated delay based on the number of loads and the size of the loads.

- 4. If none of these delays is specified, the Timing Verifier will use a default delay value that is specified when the Timing Verifier is run (which may be zero).

### TUNED SIGNALS AND GATED CLOCKS (EVALUATION DIRECTIVES)

High-speed digital system often use clocks which have been tuned in order to compensate for delays in the system. A means for describing signals that will be adjusted to have some particular timing behavior independent of circuit delays is necessary for complete timing verification. Evaluation Directives provide these descriptions.

A related complication occurs in systems that use gated clocks. The system functions correctly only if the gating signal properly "envelopes" the clock for all variations in circuit delays. Evaluation directives are used to direct the Timing Verifier checks for correct timing behavior of this type signal as well.

## 6.5 SIGNAL ASSERTIONS

In order for the Verifier to produce meaningful results, the designer must specify the value history of all input signals to the design and all interface signals that are to be checked.

Value histories are specified using <u>assertions</u> which are simply part of a SCALD signal name. The general form is:

<assertion type> ::= C | P | S | D

The assertions recognized by the Verifier are:

- C -- this indicates that the signal is a clock signal. Together with the <time specifier> and <explicit skew> this determines the 0, 1 behavior of the signal. If no <explicit skew> is given, this assertion will use the skew specified by the CLOCK\_SKEW directive.

- 2. P -- this indicates that the signal is a precision clock signal. The P assertion is identical to the C assertion except that when no <explicit skew> is given, it uses the skew specified by the PREC CLOCK SKEW directive.

- 3. S -- together with the <time specifier> and <explicit skew> this determines the stable, changing behavior of the signal. This is used to specify an initial value history for a signal. During the course of verification, should the computed value be different than the specified value, the computed value will replace it. If no <explicit skew> is given, then the <time specifier> is assumed to be exact, and no skew is added to the signal.

- 4. D -- together with the <time specifier> and <explicit skew> this determines the stable, changing behavior of the signal. This assertion is the same as the S assertion except that the value history specified is <u>never changed</u> during the course of verification. The use of the D assertion on signals in feed back paths which are broken by latches can significantly speed up the execution of the Timing Verifier.

Timing Verifier Reference Manual

<clock period> is a time (in nanoseconds). This overrides the CLOCK\_PERIOD in the directives file for a particular signal. The clock period has to be a sub-multiple of the system clock period. For example, with the CLOCK\_PERIOD and CLOCK\_INTERVALS set to 100, the following assertions can be given:

Signal Assertion Equivalent To

SIG!50P0-25SIG!P0-2550-75SIG!25C5-10SIG!C5-1030-3555-6080-85

A <time specifier> is used to describe time intervals. The <explicit skew> allows uncertainty or skew to be specified about the <time specifier>. The detailed syntax is:

<time period> ::= <time in clk units> - <time in clk units>

<pulse> ::= <time in clk units>+<time in nsec>

<explicit skew> ::= | ( <negative skew> , <positive skew> )

<negative skew> ::= -<time in nsec> | <time in nsec>

<positive skew> ::= +<time in nsec> | <time in nsec>

<time in clk units> ::= <integer> | <fixed point number>

<time in nsec> ::= <integer> | <fixed point number>

All three types of <time interval>s specify signal behavior in terms of evenly spaced sub-intervals of a global clock. A clock unit is equal to one of these sub-intervals. In the examples below the clock period is assumed to be 100 nsec and is divided into 8 even sub-periods of 12.5 nsec each. The CLOCK\_SKEW directive is -2 nsec to +2 nsec, and the PREC CLOCK SKEW directive is set to 0.

٦

1500

Each of the types of <time specifier>s is shown below: <time in clock units> This form specifies a pulse whose width is one sub period long. The signal is asserted the number of indicated sub-periods from the begining of the cycle. CLK!P 4 . 0:0.0, 1:50.0, 0:62.5 • CLK!P 4 (-2,5).0:0.0, R:48.0, 1:55.0, F:60.5, 0:67.5 1:0.0, F:23.0, 0:27.0, CLK!C 2,5\* . R:35.5, 1:39.5, F: 60.5, 0:64.5, R: 73.0, 1:77.0 CLK!P2.2,5.7 0:0.0, 1:27.5, 0:40.0, 1:71.3, 0:83.8 Note that low-asserted clocks, such as the third example above, take the value "O" when the signal is asserted.

<time period>

11 1991 188

A <time period> is a pulse whose leading and trailing edge is specified.

CLK!P 0-2.0 . . 1:0.0, 0:25.0 CLK!P 1-4,6.0-7 . 0:0.0, 1:12.5, 0:50.0, 1:75.0, 0:87.5 SIG!S1-4,6-7.3 . C:0.0, S:12.5, C:50.0, S:75.0, C:91.3 SIG !S2-4 (-1,5) . C:0.0, S:30.0, C:49.0

<pulse>

This form is used to specify a signal whose start time is specified relative to the clock sub-periods, but whose width is specified in absolute units.

SIG!S2+11.3 . . . C:0.0, S:25.0, C:36.3 -CLK!P3+9.0,4+10.0 . 1:0.0, 0:37.5, 1:46.5, 0:50.0, 1:60.0

The time before the plus symbol gives the time of the leading edge of the pulse in clock units, and the time after the plus symbol gives the width of the pulse in absolute time units (nanoseconds). This allows for pulses to be specified where the width doesn't scale with the cycle time of the circuit.

### ADVANCED USE OF ASSERTIONS

During simulation, if a driven signal does not meet its assertion specification, an error is reported in the Timing Verifier output file. Assertions have obvious uses as interface specifications of signals, and as pseudo-drivers in partially complete designs. They may also be used to create abstract models.

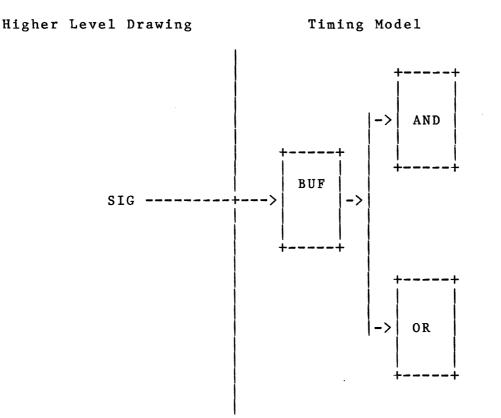

An abstract model of a part P consists of a body drawing and an abstract timing model. The abstract timing model is constructed soley of buffers -- all input signals are received by buffers and the output signals driven by buffers. The output of each receiver buffer has a local signal with a timing assertion on it matching the input timing spec of the corresponding pin of P. The input of each drive buffer has a local signal with a timing assertion on it matching the output timing spec of corresponding output pin of P. This approach can be expanded to have small amounts of logic in the abstract model to achieve more complex logic or timing behavior as required.

One capability of the Timing Verifier enhances the power of timing assertions. Assertions may be specified in the CASE analysis file rather than on the print. This facilitates experimenting with assertions. See the section on Timing Verifier Case Analysis for details.

### 6.6 DELAY PROPERTIES

Delay properties are used to model the delays of a circuit's interconnections. Delay properties are simply SCALD signal properties:

| <delay property=""></delay>                        | ::=   | \ <property name=""> <value></value></property>                     |

|----------------------------------------------------|-------|---------------------------------------------------------------------|

| <value></value>                                    | ::=   | = ' <time interval="" specifier=""> '</time>                        |

| <pre><time interval="" pre="" sp<=""></time></pre> | pecif | fier>                                                               |

|                                                    | ::=   | <delay range=""></delay>                                            |

|                                                    |       | <rising range=""> , <falling range=""></falling></rising>           |

| <rising range=""></rising>                         | ::=   | <delay range=""></delay>                                            |

| <falling range=""></falling>                       | ::=   | <delay range=""></delay>                                            |

| <delay range=""></delay>                           | ::=   | <delay></delay>                                                     |

|                                                    |       | <min delay=""> - <max delay=""></max></min>                         |

| <delay></delay>                                    | ::=   | <time></time>                                                       |

| <min delay=""></min>                               | ::=   | <time></time>                                                       |

| <max delay=""></max>                               | ::=   | <time></time>                                                       |

| <time></time>                                      | ::=   | <pre><integer>   <fixed number="" point=""></fixed></integer></pre> |

Verifier delay properties indicate that the signal is to be delayed (by the time indicated by the <time interval specifier>) with respect to the signal source. The most gene al form of a delay gives a minimum and maximum rising

delay and a minimum and maximum falling delay. If only one range is given, then the rising and falling delays are assumed to be the same.

The general delay properties recognized by the Verifier are:

- WIRE\_DELAY -- this type of delay is a simple wire delay property. It value may be over-ridden by the physical design subsystem, and also may be set to zero by certain evaluation directives.

- 2. CHIP\_DELAY -- this type of delay is used primarily with Verifier library models. It is just like the WIRE\_DELAY, except that it is not changeable by the physical design subsystem and a different set of evaluation directives set it to zero.

- 3. CLOCK DELAY -- this delay is not affected by any evaluation directives and cannot be overridden by the physical design subsystem. Its primary use is to describe a <u>tuned clock</u> which is adjusted to have some delay with respect to another logical version of the clock.

All delay properties are the same except in the way evaluation directives and the physical design subsystem operate on them.

To shorten signals and increase readability, the compiler has predefined text macros for these delay properties: the strings "WD", "CD", and "CKD" respectively. The user may of course use either the full property name or the associated text macro interchangeably. All examples will be in terms of the predefined macros. When using the predefined text macros the equal sign and quotes should be omitted, just giving the delay range after the macro name. Timing Verifier Reference Manual

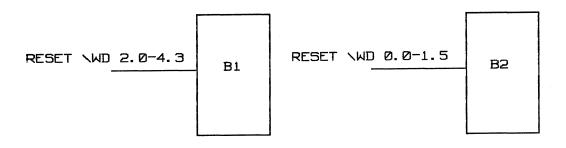

All Verifier delay properties are pin properties. That is, the delay is applied at each pin to which the wire with the signal name containing the delay property is attached. A pin connected to the same signal that lacks a delay property is not delayed. For example consider a drawing with two bodies that use a signal RESET:

| RESET \WD 2.0-4.3 | B1 | RESET ND 0.0-1.5, 1.0-2.5 | B2 |

|-------------------|----|---------------------------|----|

|                   |    |                           |    |

Then the behavior of RESET is:

| RESET | • | • | ٠ | 0:0.0, 1:10.0, 0:20.0    |

|-------|---|---|---|--------------------------|

|       |   |   |   | ( at the driver )        |

| RESET | • | • | ٠ |                          |

|       |   |   |   | F:22.0, 0:24.3 ( at B1 ) |

| RESET | • | • | • | 0.0.0, R:10.0, 1:11.5,   |

|       |   |   |   | F:21.0, 0:22.5 (at B2)   |

|       |   |   |   |                          |

Delay properties are handled this way so that systems where delays are different on different "stubs" of a net may be modelled.

## 6.7 EVALUATION DIRECTIVES

Evaluation directives are used for two purposes:

- 1. To facilitate the verification of designs that use tuned clocks. This is done by providing a description of how clock signals are tuned.

- 2. To facilitate the verification of designs that use "gated" clocks. Evaluation directives are defined that direct the Verifier to ensure that gating signals properly "envelope" clock signals.

## EVALUATION DIRECTIVES FOR CLOCK TUNING

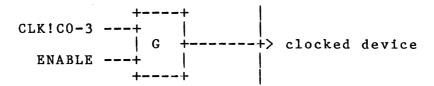

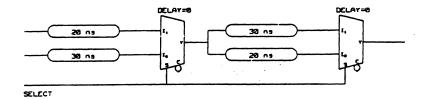

High performance designs often require the adjustment of clocks to compensate for circuit delays. A typical example is shown below:

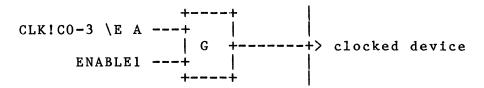

This is a typical circuit where a clocked device is conditionally clocked depending on whether the enable is asserted or not. Speed constraints may require that the signal CLK!CO-3 be generated so that the effective delay of the gate "G" and its top input wire is zero. An alternate way of viewing this situation is that the top input signal to gate G is generated so that the gates output signal is asserted from period 0 to 3 (when enabled). We indicate this to the Verifier using the evaluation directive "Z". A typical example is shown below:

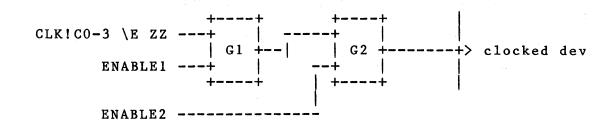

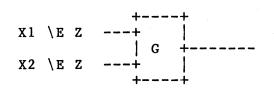

The second evaluation directive for tuning is 'W', which says to set the minimum wire delay to zero, and to substract the minimum delay from the maximum delay. The 'W' evaluation directive is just used to zero out the minimum wire delay of the last wire on a clock path. For example, evaluation directives may be composed:

> +----+ | CLK!CO-3 \E ZW ---+ | | G +----+> clocked device ENABLE ---+ | +----+

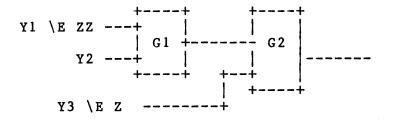

The 'ZW' means to treat the circuit as if the input wire delay, the delay of gate G and the minimum delay of the output wire delay is zero. Tuning directives may be combined to zero multiple levels of gating between the clocked signal and the clocked device:

If the clock is tuned with respect to the output of G2 the evaluation directive 'ZZ' is used -- the first "Z" sets the Gl and its input wire to zero, the second "Z" sets G2 and its input wire to zero. If the clock is tuned at the clock device's clock input the evaluation directive 'ZZW' should be used.

EVALUATION DIRECTIVES FOR CLOCK GATING

Correct performance of a digital system using gated clocks, requires that the gating signal be stable during the on-time (asserted time) of the clock. The evaluation directive 'A' is used to check this:

The 'A' indicates that ENABLE1 must be stable (S or 0 or 1) when that signal is controlling the gate:

- o If G is an AND gate, ENABLE1 must be stable when CLK!CO-3 is high.

- o If G is an OR gate, ENABLE1 must be stable when CLK!CO-3 is low.

- o If G is any other kind of logic element, it is ignored.

If the signals do not meet the conditions specified an error is generated in the Verifier output report.

The 'A' directive may be used only on AND and OR gates where one input of the gate is driven by a clock signal (a signal with a 'C' or 'P' assertion).

### TUNED AND GATED CLOCKS

Use the directive 'H' to verify designs with clocks that are both tuned and gated. The directive 'H' causes the Timing Verifier to zero the wire and the gate, and also to check that the enabling signal(s) is stable when the clock enables the gate.

### MULTILEVEL COMPONENT DEFINITION

When a component is defined with multiple levels of primitives, it is desired that the evaluation directives refer to the entire path through the component, rather than to a single primitive that the component is made up of. Ιf the component definition is a single level drawing, then the Timing Verifier automatically causes the evaluation directive string to count all of the primitives as one element. A user can also put the body property 'KEEPDIRECTIVE' on a primitive which will cause it to propagate the entire evaluation string through it, rather than taking the first evaluation letter off of it. This property is useful if a hierarchical definition for a component is used and the evaluation directives only want to increment once when going through the component.

### SUMMARY OF EVALUATION DIRECTIVES

Five evaluation directives are recognized by the Timing Verifier:

- o W -- sets the minimum delay of the wire to zero and subtracts the minimum delay from the maximum delay.

- o Z -- sets the wire delay and the gate delay to zero.

- A -- checks that the non-clock input(s) to a gate is stable when the clock input is enabling the gate.

Directs the Timing Verifier to ignore all the inputs to the gate except the one with the I assertion.

- o H -- sets the wire delay and the gate delay to zero and check that the non-clock input(s) to a gate is stable when the clock input is enabling the gate.

- I -- directs the Timing Verifier to ignore all the inputs to the gate except the one with the I assertion. The output of the gate is simply the input signal (with the assertion) delayed by the propagation delay of the gate. This directive may be used on any gate type but only one input to the gate may have an I assertion.

Timing Verifier Reference Manual

## RESTRICTIONS

An evaluation directive may be applied to only one input of a gate. The diagram illustrates an unacceptable condition.

### Timing Verifier Primitives

## 6.8 MODELLING COMPONENTS IN THE TIMING VERIFIER

Timing Verifier models are simply logic diagrams constructed from a specific set of parts called Timing Verifier primitives. Timing models may be hierarchical. If they are, the leaf drawings must be in terms of this parts set.

All Timing Verifier primitives may have an optional body property, TRANSITION, which takes the values SMOOTH or GLITCHY. The simulation of some primitives is modified based on this parameters. (Details are given below.) In addition, all Timing Verifier primitives have bubbleable pins. This feature allows negative edge triggering of latches, buffers to become inverters, etc.

The truth tables for the Timing Verifier primitives are given below. In the case where more than one entry applies to a given set of input conditions, the first entry will take precedence.

A complete list of the primitives is given below:

| 2  | OR  | 2-input | SIZE | wide | OR gate     |

|----|-----|---------|------|------|-------------|

| 3  | OR  | 3-input | SIZE | wide | OR gate     |

| 4  | OR  | 4-input | SIZE | wide | OR gate     |

| 5  | OR  | 5-input | SIZE | wide | OR gate     |

| 6  | OR  | 6-input | SIZE | wide | OR gate     |

| 7  | OR  | 7-input | SIZE | wide | OR gate     |

| 8  | OR  | 8-input | SIZE | wide | OR gate     |

|    |     |         |      |      | 0           |

| 2  | AND | 2-input | SIZE | wide | AND gate    |

| 3  | AND | 3-input | SIZE | wide | AND gate    |

| 4  | AND | 4-input | SIZE | wide | AND gate    |

| 5  | AND | 5-input | SIZE | wide | AND gate    |

| 6  | AND | 6-input | SIZE | wide | AND gate    |

| 7  | AND | 7-input | SIZE | wide | AND gate    |

| 8  | AND | 8-input | SIZE | wide | AND gate    |

|    |     | •       |      |      | 0           |

| 2  | CHG | 2-input | SIZE | wide | CHANGE gate |

| 3  | CHG | 3-input | SIZE | wide | CHANGE gate |

| 4  | CHG | 4-input | SIZE | wide | CHANGE gate |

| 5  | CHG | 5-input | SIZE | wide | CHANGE gate |

| 6  | CHG | 6-input | SIZE | wide | CHANGE gate |

| 7  | CHG | 7-input | SIZE | wide | CHANGE gate |

| 8  | CHG | 8-input | SIZE | wide | CHANGE gate |

| -  |     |         | . –  |      | 0.111       |

| XC | R   | 2-input | SIZE | wide | XOR gate    |

| BU |     | l-input | SIZE | wide | BUFFER gate |

|    |     |         |      |      | 0           |

| OR<br>AND<br>CHG                      | SIZE inputs to single bit output OR gate<br>SIZE inputs to single bit output AND gate<br>SIZE inputs to single bit output CHANGE gate |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| THRESHOLD<br>IDENTITY<br>RES          | l-input SIZE wide threshold gate<br>l-input SIZE wide identity gate<br>l-input SIZE wide resistor                                     |

| TS BUF                                | SIZE wide tri-state driver with enable                                                                                                |

| LATCH<br>LATCH RS                     | SIZE wide latch with enable<br>SIZE wide latch with enable and<br>asynchrous set and reset                                            |

| REG<br>REG RS                         | SIZE wide rising-edge triggered register<br>SIZE wide rising-edge triggered register with<br>asynchrous set and reset                 |

| 2 MUX<br>4 MUX<br>8 MUX               | SIZE wide 2-input multiplexer<br>SIZE wide 4-input multiplexer<br>SIZE wide 8-input multiplexer                                       |

| SETUP HOLD<br>SETUP RISE<br>HOLD FALL | SIZE wide rising-edge setup and hold checker<br>SIZE wide rising-edge setup and falling-edge<br>hold checker                          |

| EDGE TO EDGE                          | SIZE wide rising-edge to rising-edge skew<br>checker                                                                                  |

| TRANSMISSION                          | SIZE wide minimum pulse width checker<br>SIZE wide bi-directional transmission gate                                                   |

## AND, OR, CHANGE and XOR FUNCTIONS

The truth tables for the AND, OR, CHANGE(CHG), and XOR functions are given in the following tables:

| AND                        | 0 1 S R F C U Z                                                                               | OR                              | 0 1 S R F C U Z                                                                                                          |

|----------------------------|-----------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------|

| 0                          | 000000000000                                                                                  | 0                               | 0 1 S R F C U U                                                                                                          |

| 1                          | 0 1 S R F C U U                                                                               | 1                               |                                                                                                                          |

| S                          | 0 S S R F C U U                                                                               | S                               | S 1 S R F C U U                                                                                                          |

| R                          | 0   R   R   R   C   C   U   U                                                                 | R                               | R   1   R   R   C   C   U   Ŭ                                                                                            |

| F                          | 0 F F C F C U U                                                                               | F                               | F 1 F C F C U U                                                                                                          |

| С                          | 0 c c c c c u u                                                                               | С                               | C 1 C C C C U U                                                                                                          |

| U                          | 0 0 0 0 0 0 0 0                                                                               | U                               | ט   1   ט   ט   ט   ט   ט   ט                                                                                            |

| Z                          | 0 0 0 0 0 0 0 0                                                                               | Z                               | บ   1   บ   บ   บ   บ   บ   บ                                                                                            |

|                            |                                                                                               |                                 |                                                                                                                          |

|                            |                                                                                               |                                 |                                                                                                                          |

| CHG                        | 0 1 S R F C U Z                                                                               | XOR                             | 0 1 S R F C U Z                                                                                                          |

| CHG<br>0                   | 0 1 S R F C U Z <br> S S S C C C U U                                                          |                                 | 0 1 S R F C U Z <br> 0 1 S R F C U U                                                                                     |

|                            |                                                                                               | 0                               |                                                                                                                          |

| 0                          | s s s c c c u u                                                                               | 0                               | 0 1 S R F C U U                                                                                                          |

| 0<br>                      | s s s c c c u u <br> s s s c c c u u                                                          | 0<br>                           | 0 1 S R F C U U <br> 1 0 S F R C U U                                                                                     |

| 0<br>1<br>5                | s s s c c c u u <br> s s s c c c u u <br> s s s c c c u u                                     | 0<br>                           | 0 1 S R F C U U <br> 1 0 S F R C U U <br> S S S C C C U U                                                                |

| 0<br>1<br>S<br>R           | s s s c c c u u <br> s s s c c c u u <br> s s s c c c u u <br> c c c c c c u u                | 0<br>                           | 0 1 S R F C U U <br> 1 0 S F R C U U <br> S S S C C C U U <br> R F C C C C U U                                           |

| 0<br>1<br>S<br>R<br>F<br>C | s s s c c c u u <br> s s s c c c u u <br> s s s c c c u u <br> c c c c c c u u <br> c c c c c | 0<br>                           | 0 1 S R F C U U <br> 1 0 S F R C U U <br> S S S C C C U U <br> R F C C C C U U <br> F R C C C C U U                      |

| 0<br>1<br>S<br>R<br>F<br>C | s s s c c c u u <br> s s s c c c u u <br> s s s c c c u u <br> c c c c c c u u <br> c c c c c | 0<br>1<br>S<br>R<br>F<br>C<br>U | 0 1 S R F C U U <br> 1 0 S F R C U U <br> S S S C C C U U <br> R F C C C C U U <br> F R C C C C U U <br> C C C C C C U U |

These parts are simulated in the same way for TRANSITION = SMOOTH and TRANSITION = GLITCHY.

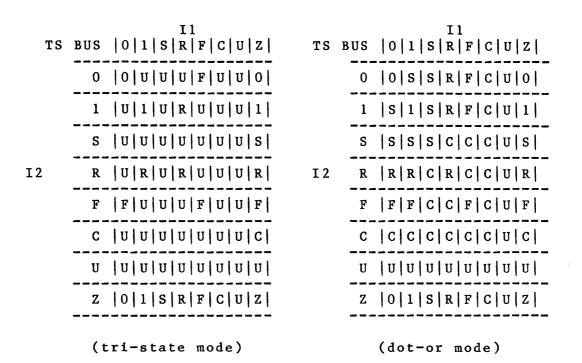

## TS BUF and TS BUS FUNCTIONS

The truth tables for the TS BUF primitive and related TS BUS are given in the following tables.

| TS    | ENABLE INPUT<br>BUF  0 1 S R F C U Z | ΤS            | ENABLE INPUT<br>BUF  0 1 S R F C U Z |

|-------|--------------------------------------|---------------|--------------------------------------|

|       | 0  z 0 u c c c u u                   | DATA<br>INPUT | 0  z 0 0 c c c u u                   |

|       | 1   Z   1   U   C   C   C   U   U    |               | 1  z 1 1 C C C U U                   |

|       | s  z s u c c c u u                   |               | s  z s s c c c u u                   |

| DATA  | R   Z   R   U   C   C   C   U   U    |               | R  Z R R C C C U U                   |

| INPUT | F  Z F U C C C U U                   |               | F  Z F F C C C U U                   |

|       | c  z c u c c c u u                   |               | c  z c c c c u u                     |

|       | u  z u u u u u u u                   |               | u  z u u u u u u u                   |

|       | z  z u u u u u u u                   |               | z  z u u u u u u u                   |

|       |                                      |               |                                      |

(dot-or mode)

(tri-state mode)

These parts are simulated in the same way for TRANSITION = SMOOTH and TRANSITION = GLITCHY.

### DOT GATES

The Timing Verifier simulates multiple driven nets (buses) by inserting a gate in the network. All the drivers of the bus are reconnected to the gate's inputs. The output of the gate drives all the inputs on the bus. If the bus is dot-or (dot-and), the inserted gate is an OR (AND) gate. If the bus is a tri-state bus, the inserted gate is a TS BUS with one of the two logic functions shown below.

Note that both the TS BUF and the TS BUS have two modes of operation. The mode used for simulation depends on whether the value of the TS BUS TYPE directive in the Verifier command file is "DOT TS" or "DOT OR". (See the Timing Verifier Directives Summary in this chapter of the manual).

## BUF AND THRESHOLD FUNCTIONS

The truth tables for the BUF and THRESHOLD primitives are given in the following tables:

|       | BUF | OUTPUT | THRESHO | LD | OUTPUT |

|-------|-----|--------|---------|----|--------|

|       | 0   | 0      |         | 0  | C      |

|       | 1   | 1      |         | 1  | 1      |

|       | s   | <br>S  |         | s  | С      |

| INPUT | R   | R      | INPUT   | R  | C      |

|       | F   | <br>F  |         | F  | C      |

|       | c   | С      |         | c  | C      |

|       | u   | <br>U  |         | U  | U      |

|       | Z   | <br>U  |         | z  | <br>U  |

|       |     |        |         |    |        |

These parts are simulated in the same way for TRANSITION = SMOOTH and TRANSITION = GLITCHY.

### **RES AND IDENTITY FUNCTIONS**

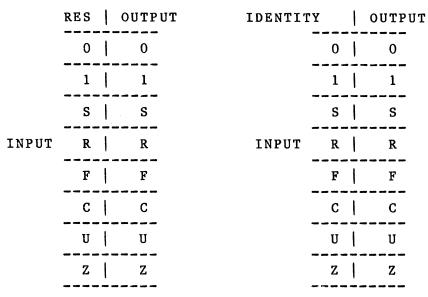

The truth tables for the RES and IDENTITY primitives are given in the following tables:

These parts are simulated in the same way for TRANSITION = SMOOTH and TRANSITION = GLITCHY.

### LATCH PRIMITIVE

The LATCH primitive has a DATA and EN input. Note: If EN is bubbled the iverse of the chart should be followed.

LATCH:

| EN |  | LASTOUTPUT                                   | DATA            | OUTPUT        |

|----|--|----------------------------------------------|-----------------|---------------|

| 0  |  | {0,1,S}                                      | X               | {0,1,S}       |

| 0  |  | {R,F,C,U,Z}                                  | X               | S S           |

| 1  |  | X                                            | {0,1,S,R,F,C}   | {0,1,S,R,F,C} |

| 1  |  | X                                            | {U,Z}           | {U,U}         |

| R  |  | = DATA                                       | {0,1,U,Z}       | {0,1,U,U}     |

| R  |  | = DATA<br>no input transit<br>latch is being |                 |               |

| R  |  | = DATA                                       | all other cond. | с<br>с        |

6-25

.

| R | <> DATA     | {U,Z}         | U             |

|---|-------------|---------------|---------------|

| R | 0           | {1,S}         | R             |

| R | 1           | {0,S}         | F             |

| R | {R,F,C,U,Z} | {0,1,S}       | C             |

| R | {R,1}       | R             | R             |

| R | {F,0}       | F             | F             |

| R | all other o | conditions    | C             |

| F | = DATA      | {0,1,S,U,Z}   | {0,1,S,U,U}   |

| F | = DATA      | {R,F,C}       | с             |

| F | X           | {U,Z}         | {U,U}         |

| F | 0           | {1,S}         | R             |

| F | 1           | {0,S}         | F             |

| F | С           | {0,1,S}       | {0,1,S}       |

| F | {R,1}       | R             | R             |

| F | {F,0}       | R             | F             |

| F | all other   | conditions    | с с           |

| S | = DATA      | x             | LASTOUTPUT    |

| S | <> DATA     | {0,1,S}       | S             |

| s | 1           | R             | R             |

| S | 0           | F             | F             |

| s | <> 1        | R             | С             |

| s | <> 0        | F             | c             |

| s | x           | С             | С             |

| S | all othe    | er inputs     | U U           |

| с | X           | {U,Z}         | {v,v}         |

| C | = DATA      | {0,1,S,R,F,C} | {0,1,S,R,F,C} |

6-26

(

| C |  | all | other | inputs |  | C |

|---|--|-----|-------|--------|--|---|

| Z |  | X   |       | X      |  | U |

| U |  | X   |       | X      |  | U |

If the INPUT undergoes a transition while the latch is closing, then a setup/hold time violation has occured. Under these conditions the latch is simulated in one of three ways depending on the value of LATCH-ERR-MODEL: LATCH\_ERR\_MODEL = OPEN; LATCH\_ERR\_MODEL = CLOSED or LATCH\_ERR\_MODEL = CONSERVATIVE;

LATCH ERR MODEL = OPEN:

| F       I       X $\{U,Z\}$ $\{U,U\}$ F       I       0 $\{0,1,S\}$ R         F       I       1 $\{0,1,S\}$ F         F       I       I $\{0,1,S\}$ F         F       I       I $\{0,1,S\}$ I       F         F       I       C       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I       I |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F               1         $\{0,1,S\}$         F         F               C         $\{0,1,S\}$   $\{0,1,S\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| F   C   {0,1,S}   {0,1,S}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $F   \{S, R, F, C, Z\}   \{0, 1, S\}   C$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| F   {R,1}   R   R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| F   {F,0}   F   F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| F   all other conditions   C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

LATCH ERR MODEL = CLOSED:

| LASTEN | LASTOUTPUT  |  | DATA |  | OUTPUT  |

|--------|-------------|--|------|--|---------|

| F      | {0,1,S}     |  | X    |  | {0,1,S} |

| F      | {R,F,C,U,Z} |  | X    |  | S       |

| LASTEN | LASTOUTPUT   | I    | DATA     | OUTPUT  |

|--------|--------------|------|----------|---------|

| F      | X            |      | {U,Z}    | { U, U} |

| F      | 0            |      | {0,1,S}  | R       |

| F      | 1            |      | {0,1,S}  | F       |

| F      | {S,R,F,C,,U} |      | {0,1,S}  | C       |

| F      | {R,1}        |      | R        | R       |

| F      | {F,0}        |      | F        | F       |

| F      | all othe     | r co | nditions | C       |

LATCH ERR MODEL = CONSERVATIVE:

The body property TRANSITION determines whether the output of the LATCH primitive should change when it is enabled, even if the input has not changed. When the body property TRANSITION = GLITCHY is attached to a LATCH primitive, the output of the LATCH will always change even if the input remains stable. If TRANSITION = SMOOTH is attached, or no TRANSITION property is attached, the output of the LATCH will not change if the input is always stable.

The LATCH RS primitive is the same as the LATCH except that it also has asynchrous RESET and SET inputs. First the LATCH output is computed for the current input values, then the SET RESET function is applied to the outputs. The SET RESET function is described in the next section.

### SET RESET FUNCTION

The SET RESET function is composed with the LATCH function to form a LATCH RS and the REG function to form a REG RS. It is not directly accessible as a Timing Verifier Primitive. The SET RESET function is different for TRANSITION = SMOOTH and GLITCHY. The function inherits its TRANSITION property from the LATCH RS or REG RS of which it is a part.

| R     | I    | S        | OLDOUTPUT  | NEWOUTPUT          |

|-------|------|----------|------------|--------------------|

| 0     |      | 0        | x          | OLDOUTPUT          |

| 0     |      | X        | 1          | 1                  |

| 0     |      | 1        | <> 1       | 1                  |

| 0     |      | <> {0,1} | <> 1       | CHG(OLDOUTPUT,S)   |

| x     |      | 0        | 0          | 0                  |

| 1     |      | 0        | x          | 0                  |

| <> {  | 0,1} | 0        | x          | CHG(OLDOUTPUT,R)   |

| <br>х |      | all o    | ther cases | CHG(OLDOUTPUT,R,S) |

GLITCHY:

where CH is the change function defined on Page 6-21.

| SMOOTH:<br>R | S        | OLDOUTPUT                    | NEWOUTPUT         |

|--------------|----------|------------------------------|-------------------|

| 0            | 0        | X                            | OLDOUTPUT         |

| 0            | <br>X    | 1                            | 1                 |

| 0            |          | X                            | 1                 |

| 0            | <br>R    | 0                            | R                 |

| 0            | <> {1,R} | X                            | CH(OLDOUTPUT,S)   |

| x            | 0        | 0                            |                   |

| <br>1        | 0        | x                            | 0                 |

| R            | 0        | 0                            | <br>  F           |

| <>{1,R}      |          | X                            | CH(OLDOUTPUT,R,S) |

| {1,R}        | <br>F    | {0,1,S}                      | {0,F,F,}          |

| {1,R}        | <br>F    | <pre></pre>                  | CH(OLDOUTPUT,R,S) |

| F            | {1,R}    | {0,1,S}                      | {R,1,R}           |

| F            | {1,R}    | <pre> &lt;&gt; {0,1,S}</pre> | CH(OLDOUTPUT,R,S) |

**REG FUNCTION**

The REG primitive implements a rising edge triggered register.

| CLOCK           | LASTCLOCK          | INPUT          | LASTOUTPUT         | NEXTOUTPUT         |

|-----------------|--------------------|----------------|--------------------|--------------------|

| 1               | 0                  | {0,1}          | {0.1}              | LASTOUTPUT         |

| 1               | 0                  | {1,R}          | {0,R}              | R                  |

| 1               | 0                  | {0,F}          | {1,F}              | F                  |

| l<br>If the     | 0<br>REG is SMOOTH | S<br>and there | S<br>were no input | S<br>transitions.  |

| 1               | 1                  | X              | <>{0,1,S}          | S                  |

| 1               | 1                  | x              | $= \{0, 1, S\}$    | LASTOUTPUT         |

| 1               | s                  | x              | x                  | LASTOUTPUT         |

| 1               | R                  | {0,1}          | S                  | LASTOUTPUT         |

| 1               | F                  | x x            | <>{0,1,S}          | s                  |

| 1               | {C,U,Z}            | INPUT :        | = LASTOUTPUT       | LASTOUTPUT         |

| 1               | {C,U,Z}            | INPUT          | <> LASTOUTPUT      | S                  |

| {C,R}           | x                  | [0,1]          | [0,1]              | LASTOUTPUT         |

| {C,R}           | x                  | {1,R}          | {0,R}              | R                  |

| {C,R}           | x                  | {0,F}          | {1,F}              | F                  |

| {C,R}<br>If the | X<br>REG is SMOOTH | S and there    | S<br>were no input | S<br>Stransitions. |

| {0,S,F}         | x                  | x x            | <>{0,1,S}          | s                  |

| {0,S,F}         | x                  | x              | ={0,1,S}           | LASTOUTPUT         |

| {U,Z}           | x                  | X              | x                  | u                  |

The body property TRANSITION determines whether the output of the REG primitive should change when it is clocked, even if the input has not changed. When the body property TRANSITION = GLITCHY is attached to a REG primitive, the output of the REG will always change even if the input remains stable. If TRANSITION = SMOOTH is

attached, or no TRANSITION property is attached, the output of the REG will not change if the input is always stable.

The REG RS primitive is the same as the REG except that it also has asynchrous R and S inputs. First the REG output is computed for the current input values, then the SET RESET function is applied to the output.

### THE 2, 4 AND 8 MUX FUNCTIONS

The 2 MUX, 4 MUX, and 8 MUX primitives implement 2-input, 4-input, and 8-input multiplexers. If any of the select inputs on these multiplexers has a known value of 0 or 1, then only the possibly selected data inputs will be looked at when calculating the output value. If more than one data input might be selected, the output value is calculated by using the CHANGE function on the set of selected data inputs.

If the N MUX has no TRANSITION property or TRANSITION = GLITCHY, then any input transition causes an output transition of the appropriate slope. If TRANSITION = SMOOTH, then if the output state before and after an input transition is the same, there is no output transition.

#### SETUP HOLD FUNCTION

The SETUP HOLD primitive has a clock and data input. It will generate an error message in the output listing if the data input is not stable from SETUP nsec's before the rising edge of the clock until HOLD nsec's after the rising edge of the clock. SETUP and HOLD are timing parameters given to this primitive. This primitive is normally used to check the set-up and hold times of registers and latches. This primitive has an optional enable input, which if specified, turns the checking on and off. If the enable input is any value other than ZERO, then checking is enabled. If checking is enabled anytime during the rising edge of the clock input, then checking will be done for that edge.

### SETUP RISE HOLD FALL FUNCTION

The SETUP RISE HOLD FALL primitive has a clock and data input. It will generate an error message in the output listing if the data input is not stable from SETUP nsec's before the rising edge of the clock, while the clock is rising, while the clock is true, during the falling edge of the clock, until HOLD nsec's after the falling edge of the clock. SETUP and HOLD are timing parameters given to this primitive. This primitive is normally used to check the set-up and hold times of data being written into memories.

. CEL

This primitive has an optional enable input which can be used to turn off checking. If the enable input is given, then any value other than ZERO will cause checking to be enabled. If checking is enabled anywhere between the beginning of the rising edge to the end of the falling edge, then checking will be done for that clock pulse.

### EDGE TO EDGE FUNCTION

The EDGE TO EDGE primitive has two clock inputs, CKl and CK2. It checks that the beginning of a RISING edge on CK2 is at least a minimum delay from the end of a RISING edge on CKl and that the end of a RISING edge on CK2 is no more than a maximum delay from the beginning of a RISING edge on CKl. The delay parameter is used to specify the minimum and maximum delays used. Only rising delays are used. If there is no edge on CK2, then no error message will be generated. This primitive has an optional enable input, which if specified, turns the checking on and off. If the enable input is any value other than ZERO, then checking is enabled. If checking is enabled anytime during the rising edge of CK1, then the checking will be done for that edge.

### MIN PULSE WIDTH

The MIN FULSE WIDTH primitive has one data input. It has two timing parameters LOW and HIGH. It checks that its data input has no pulses on it that are low for less than LOW nsec's, and that it has no pulses on it that are high for less than HIGH nsec's. This primitive has an optional enable input, which if specified, turns the checking on and off. If the enable input is any value other than ZERO, then checking is enabled. If checking is enabled anytime during a given pulse, then the width of that pulse is checked.

### TRANSMISSION GATE

The TRANSMISSION GATE primitive has an enable input EN, and two bi-directional pins Tl and T2. If the enable input is ZERO, then both Tl and T2 are set to high-impedence. If EN is ONE, then Tl and T2 are tied together using the same function as the tri-state bus (TS BUS), which is defined on Page 5-22.

### BUBBLING OF PRIMITIVE PINS

Each input and output of every primitive may be "bubbled" independently. (See Graphics Editor, BUBBLE command.) When this is done, it is as if an inverting buffer were inserted between the signal (input or output) and the primitive itself. The characteristics of the primitive

itself are not changed in any way. This is useful for creating inverting buffers (by bubbling the input or output of a BUF), nand gates. nor gates, negative edge triggered registers, etc.

The use of a bubbled input on a MIN PULSE WIDTH primitive is a good example of the statement that the primitive itself is unchanged. In order to check a low asserted signal (e.g., CK) to make sure that it is low for at least 20.0 nsec one may use a MIN PULSE WIDTH primitive with a bubbled input and a HIGH=20.0 property.

### 6.9 SIGNAL STRENGTHS IN THE TIMING VERIFIER

The output of a Timing Verifier primitive may assume one of three strengths, HARD, SOFT or UNDRIVEN. Strengths are required to correctly model circuit nodes that have multiple outputs on them when those outputs have different drive capabilities. A typical example of this is a tristate bus that is pulled-up with a resistor. When none of the tristate drivers are on, the bus should be in the one state. When a single driver drives the bus to zero, the bus should assume the zero state. Thus we need some way of modelling the fact that the resistor output is weaker than a bus driver output.

By default, the output of all devices except RES, IDENTITY and wire gates is HARD. The output of a resistor primitive is SOFT, unless the input to the resistor is UNDRIVEN, then the output is UNDRIVEN. The output of the IDENTITY primitive is the same as its input. The output strength of a wire gate is the same as the strongest input strength.

The default output strength of a primitive may be specified by attaching to it a body property STRENGTH which takes the values HARD, SOFT and UNDRIVEN. All primitives except the resistor and identity gate and wire gates ignore the strengths of their input signals. The function of a resistor and identity gate was described above. The functions of the dot gates are shown in the tables below.

The tables have four indices. Indices 1 and 3 are the strength and value of the first input, indices 2 and 4 are the strength and value of the second input.

DOT OR

| HARD, HARD, XO, XO | X0 | HARD,HARD,XO,X1    | X1 |

|--------------------|----|--------------------|----|

| HARD, HARD, XO, Xs | Xs | HARD, HARD, XO, Xz | X0 |

| HARD,HARD,X0,Xc    | Xc | HARD, HARD, XO, Xr | Xr |

| TARD, HARD, X0, Xf | Xf | HARD, HARD, XO, Xu | Xu |

| HARD, HARD, X1, X0X1HARD, HARD, X1, X1X1HARD, HARD, X1, XcX1HARD, HARD, X1, XzX1HARD, HARD, X1, XcX1HARD, HARD, X1, XzX1HARD, HARD, X1, XfX1HARD, HARD, X1, XzX1HARD, HARD, Xs, XsXsHARD, HARD, Xs, X1X1HARD, HARD, Xs, XsXsHARD, HARD, Xs, XzXsHARD, HARD, Xs, XsXsHARD, HARD, Xs, XzXzHARD, HARD, Xs, XfXfHARD, HARD, Xs, XzXzHARD, HARD, Xc, XsXcHARD, HARD, Xc, XzXcHARD, HARD, Xc, XsXcHARD, HARD, Xc, XzXcHARD, HARD, Xc, XsXcHARD, HARD, Xc, XzXrHARD, HARD, Xc, XsXrHARD, HARD, Xr, X1X1HARD, HARD, Xr, XcXcHARD, HARD, Xr, XzXrHARD, HARD, Xr, XcXcHARD, HARD, Xr, XzXrHARD, HARD, Xr, XsXfHARD, HARD, Xr, XzXrHARD, HARD, Xr, XsXfHARD, HARD, Xr, XzXrHARD, HARD, Xr, XsXfHARD, HARD, Xr, XzXrHARD, HARD, Xr, XsXsKfHARD, HARD, Xr, XzXrHARD, HARD, Xr, XsXsKfHARD, HARD, Xr, XzXzHARD, HARD, Xr, XsXsXsHARD, HARD, Xr, XzXzHARD, HARD, Xr, XsXsKARD, HARD, Xr, XzXzHARD, HARD, Xr, XsXsKARD, HARD, Xr, XzXzHARD, HARD, Xr, XsXsKARD, HARD, Xr, XzXzHARD, HARD, Xr, XsXsHARD                                                                                                                                                                                                      |                    |      |                    |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|--------------------|-----|

| HARD, HARD, X1, XcX1HARD, HARD, X1, XrX1HARD, HARD, X3, X0XsHARD, HARD, Xs, X1X1HARD, HARD, Xs, X0XsHARD, HARD, Xs, X1X1HARD, HARD, Xs, X0XsHARD, HARD, Xs, X1X1HARD, HARD, Xs, XcXcHARD, HARD, Xs, XrXsHARD, HARD, Xs, XfXfHARD, HARD, Xs, XrXuHARD, HARD, Xc, XsXcHARD, HARD, Xc, XrXcHARD, HARD, Xc, XsXcHARD, HARD, Xc, XrXcHARD, HARD, Xc, XsXcHARD, HARD, Xc, XrXcHARD, HARD, Xc, XsXrHARD, HARD, Xc, XrXrHARD, HARD, Xr, X0XrHARD, HARD, Xr, X1X1HARD, HARD, Xr, XcXcHARD, HARD, Xr, XrXrHARD, HARD, Xr, XsXrHARD, HARD, Xr, XrXrHARD, HARD, Xr, XsXfHARD, HARD, Xr, XrXrHARD, HARD, Xr, XsXfHARD, HARD, Xr, XuXuHARD, HARD, Xr, XsXfHARD, HARD, Xr, XuXuHARD, HARD, Xr, XsXsHARD, HARD, Xr, XuXuHARD, HARD, Xr, XsXsHARD, HARD, Xr, XuXuHARD, HARD, Xr, XsXsHARD, HARD, Xr, XuXuHARD, HARD, Xr, XsXfHARD, HARD, Xr, XuXuHARD, HARD, Xr, XsXuHARD, HARD, Xr, XuXu <td>HARD,HARD,X1,X0</td> <td>X1</td> <td>HARD,HARD,X1,X1</td> <td>X 1</td>                                                                                                                 | HARD,HARD,X1,X0    | X1   | HARD,HARD,X1,X1    | X 1 |

| HARD, HARD, X1, XfX1HARD, HARD, X1, XuX1HARD, HARD, Xs, XSXsHARD, HARD, Xs, X1X1HARD, HARD, Xs, XsXsHARD, HARD, Xs, XzXsHARD, HARD, Xs, Xs, XcXcHARD, HARD, Xs, XuXuHARD, HARD, Xc, XoXcHARD, HARD, Xs, XuXuHARD, HARD, Xc, XsXcHARD, HARD, Xc, X1X1HARD, HARD, Xc, XsXcHARD, HARD, Xc, XzXcHARD, HARD, Xc, XsXcHARD, HARD, Xc, XuXuHARD, HARD, Xc, XrXrHARD, HARD, Xc, XuXuHARD, HARD, Xc, Xr, XoXrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XoXrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XcXcHARD, HARD, Xr, XuXuHARD, HARD, Xr, XrXrKrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XcXcHARD, HARD, Xr, XuXuHARD, HARD, Xr, XrXrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XrXrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XrXrKrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XrXrKrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XrXrKrHARD, HARD, Xr, XuXuHARD, HARD, Xr, XrXrKrKrHARD, HARD, Xr, XrXrXuKrKrHARD, HARD, Xr, XrXrKrKrKrHARD, HARD, Xr, XrXrKrKrHARD, HARD, Xr, XrXrKrKr                                                                                                                                                                                                                                                        | HARD, HARD, X1, Xs | X1   | HARD, HARD, X1, Xz | X 1 |

| HARD, HARD, XS, X0XSHARD, HARD, XS, X1X1HARD, HARD, XS, XSXSHARD, HARD, XS, XZXSHARD, HARD, XS, X, XXHARD, HARD, XS, X, XXXHARD, HARD, XS, X, XXHARD, HARD, XS, X, XXUHARD, HARD, XC, X, XXCHARD, HARD, XC, X1X1HARD, HARD, XC, X, XSXCHARD, HARD, XC, X1X1HARD, HARD, XC, X, XSXCHARD, HARD, XC, X2XCHARD, HARD, XC, X, XSXCHARD, HARD, XC, XUXUHARD, HARD, XC, X, XSXCHARD, HARD, XC, XUXUHARD, HARD, X, X, XSXrHARD, HARD, XC, XIX1HARD, HARD, X, X, XSXrHARD, HARD, XT, XIX1HARD, HARD, X, X, XSXrHARD, HARD, XT, XUXUHARD, HARD, XT, X, XSXrHARD, HARD, XT, XUXUHARD, HARD, XT, X, XSXfHARD, HARD, XT, XUXUHARD, HARD, XT, X, XSXfHARD, HARD, XT, XUXUHARD, HARD, XT, XSXSHARD, HARD, XT, XUXUHARD, HARD, XT, XSXSKHARD, HARD, XT, XUXUHARD, HARD, XT, XSXSKARD, HARD, XZ, XZXZHARD, HARD, XZ, XSXSHARD, HARD, XZ, XZXZHARD, HARD, XZ, XSXSHARD, HARD, XZ, XZXZHARD, HARD, XZ, XSXUHARD, HARD, XZ, XZXZHARD, HARD, XZ, XSXUHARD, HARD, XZ, XZXZHARD, HARD, XZ, XSXUHARD, HARD, XZ, XZXZHARD, HARD, XZ, XZXZX                                                                                                                                                                           | HARD, HARD, X1, Xc | X 1  | HARD,HARD,X1,Xr    | X 1 |

| HARD, HARD, XS, XSXSHARD, HARD, XS, XZXSHARD, HARD, XS, XCXCHARD, HARD, XS, XXXTHARD, HARD, XS, XXXCHARD, HARD, XS, XXXXHARD, HARD, XS, XXXCHARD, HARD, XC, XZXCHARD, HARD, XC, XSXCHARD, HARD, XT, X1X1HARD, HARD, XT, XSXCHARD, HARD, XT, XZXTHARD, HARD, XT, XCXCHARD, HARD, XT, XZXTHARD, HARD, XT, XCXCHARD, HARD, XT, XZXIHARD, HARD, XT, XSXfHARD, HARD, XT, XZXIHARD, HARD, XT, XSXCHARD, HARD, XT, XZXIHARD, HARD, XT, XSXSHARD, HARD, XT, XZXIHARD, HARD, XT, XSXSHARD, HARD, XZ, XIXIHARD, HARD, XZ, XSXSHARD, HARD, XZ, XZXZHARD, HARD, XZ, XSXSHARD, HARD, XZ, XZXIHARD, HARD, XZ, XSXUHARD, HARD, XZ, XZXI <td>HARD, HARD, X1, Xf</td> <td>X1</td> <td>HARD, HARD, X1, Xu</td> <td>X1</td>                                                                                                            | HARD, HARD, X1, Xf | X1   | HARD, HARD, X1, Xu | X1  |

| HARD, HARD, XS, XCXcHARD, HARD, XS, XTXrHARD, HARD, XS, XfXfHARD, HARD, XS, XuXuHARD, HARD, XC, XSXcHARD, HARD, XC, XIX1HARD, HARD, XC, XSXcHARD, HARD, XC, XIX1HARD, HARD, XC, XSXcHARD, HARD, XC, XTXcHARD, HARD, XC, XFXcHARD, HARD, XC, XUXuHARD, HARD, XC, XFXcHARD, HARD, XC, XIX1HARD, HARD, Xr, XOXrHARD, HARD, Xr, XIX1HARD, HARD, Xr, XSXrHARD, HARD, Xr, XZXrHARD, HARD, Xr, XGXCHARD, HARD, Xr, XUXuHARD, HARD, Xr, XGXCHARD, HARD, Xr, XUXuHARD, HARD, Xr, XGXCHARD, HARD, Xr, XZXIHARD, HARD, Xr, XSXSHARD, HARD, XT, XZXUHARD, HARD, XF, XCXCHARD, HARD, XT, XZXUHARD, HARD, XF, XSXFHARD, HARD, XT, XZXIHARD, HARD, XZ, XOXOHARD, HARD, XZ, XZXIHARD, HARD, XZ, XCXCHARD, HARD, XZ, XZXUHARD, HARD, XU, XCXUHARD, HARD, XU, XZXUHARD, HARD, XU, XCXUHARD, HARD, XU, XZXUHARD, HARD, XU, XZXUHARD, HARD, XU, XZXUHARD, HARD, XU, XZXUHARD, HARD, XU, XUXUHARD, HARD, XU, XZXUHARD, HARD, XU, XUXUHARD, HARD, XU, XZXUHARD, HARD, XU, XUXUHARD, HARD, XU, XZXUHARD, HARD, XU, XUXU <td>HARD, HARD, Xs, XO</td> <td>Xs</td> <td>HARD,HARD,Xs,X1</td> <td>X 1</td>                                                                                                              | HARD, HARD, Xs, XO | Xs   | HARD,HARD,Xs,X1    | X 1 |

| HARD, HARD, XS, XfXfHARD, HARD, XS, XuXuHARD, HARD, XC, XOXcHARD, HARD, XC, XIX1HARD, HARD, XC, XSXcHARD, HARD, XC, XZXcHARD, HARD, XC, XSXcHARD, HARD, XC, XZXcHARD, HARD, XC, XGXrHARD, HARD, XC, XUXuHARD, HARD, Xr, XSXrHARD, HARD, Xr, XIX1HARD, HARD, Xr, XSXrHARD, HARD, Xr, XZXrHARD, HARD, Xr, XSXrHARD, HARD, Xr, XZXrHARD, HARD, Xr, XSXrHARD, HARD, Xr, XUXuHARD, HARD, Xr, XSXfHARD, HARD, XT, XUXuHARD, HARD, Xr, XSXSHARD, HARD, XT, XUXuHARD, HARD, XT, XSXSHARD, HARD, XT, XUXuHARD, HARD, XT, XSXSHARD, HARD, XT, XUXuHARD, HARD, XZ, XCXCHARD, HARD, XZ, XZXZHARD, HARD, XZ, XSXSHARD, HARD, XZ, XZXUHARD, HARD, XU, XCXuHARD, HARD, XU, XZXuHARD, HARD, XU, XCXuHARD, HARD, XU, XZXuHARD, HARD, XU, XZXUHARD, HARD, XU, XUXuHARD, HARD, XU, XCXUHARD, HARD, XU, XUXuHARD, HARD, XU, XCXUHARD, HARD, XU, XUXuHARD, HARD, XU, XCXUHARD, SOFT, XO, XZXU <td>HARD,HARD,Xs,Xs</td> <td>Xs</td> <td>HARD,HARD,Xs,Xz</td> <td>Xs</td>                                                                                                                  | HARD,HARD,Xs,Xs    | Xs   | HARD,HARD,Xs,Xz    | Xs  |

| HARD, HARD, Xc, XOXcHARD, HARD, Xc, X1X1HARD, HARD, Xc, X2XcHARD, HARD, Xc, X2XcHARD, HARD, Xc, X2XcHARD, HARD, Xc, X1XcHARD, HARD, Xc, X5XcHARD, HARD, Xc, X1X1HARD, HARD, Xr, X0XrHARD, HARD, Xr, X1X1HARD, HARD, Xr, X0XrHARD, HARD, Xr, X2XrHARD, HARD, Xr, X6XcHARD, HARD, Xr, X7XrHARD, HARD, Xr, X6XcHARD, HARD, Xr, X1X1HARD, HARD, Xr, X6XcHARD, HARD, Xr, X7XrHARD, HARD, Xr, X6XcHARD, HARD, Xr, X7X1HARD, HARD, X2, X8X8HARD, HARD, X2, X1X1HARD, HARD, X2, X6XcHARD, HARD, X2, X7X7HARD, HARD, X2, X6XcHARD, HARD, X2, X7X1HARD, HARD, X2, X6XuHARD, HARD, X2, X1X1HARD, HARD, X1, X0XuHARD, HARD, X2, X1X1HARD, HARD, X2, X6XuHARD, HARD, X2, X1X1HARD, HARD, X2, X6XuHARD, HARD, X2, X1X1HARD, HARD, X4, X0XuHARD, HARD, X4, X1X1HARD, HARD, X4, X0XuHARD, HARD, X4, X1X1HARD, HARD, X4, X0XuHARD, HARD, X4, X1X1HARD, HARD, X4, X6XuHARD, HARD, X4, X1X1 <td>HARD,HARD,Xs,Xc</td> <td>Xc</td> <td>HARD,HARD,Xs,Xr</td> <td>Xr</td>                                                                                                                  | HARD,HARD,Xs,Xc    | Xc   | HARD,HARD,Xs,Xr    | Xr  |

| HARD, HARD, XC, XSXCHARD, HARD, XC, XZXCHARD, HARD, XC, XGXCHARD, HARD, XC, XTXCHARD, HARD, XC, XGXCHARD, HARD, XC, XUXUHARD, HARD, XT, XSXTHARD, HARD, XT, XIX1HARD, HARD, XT, XSXTHARD, HARD, XT, XZXTHARD, HARD, XT, XSXTHARD, HARD, XT, XZXTHARD, HARD, XT, XSXTHARD, HARD, XT, XUXUHARD, HARD, XT, XSXfHARD, HARD, XT, XUXUHARD, HARD, XT, XSXfHARD, HARD, XT, XZXTHARD, HARD, XT, XSXfHARD, HARD, XT, XZXIHARD, HARD, XT, XSXfHARD, HARD, XT, XZXUHARD, HARD, XT, XSXSHARD, HARD, XT, XZXIHARD, HARD, XZ, XOXOHARD, HARD, XZ, XIXIHARD, HARD, XZ, XSXSHARD, HARD, XZ, XIXIHARD, HARD, XZ, XSXUHARD, HARD, XZ, XIXIHARD, HARD, XU, XOXUHARD, HARD, XU, XIXIHARD, HARD, XU, XCXUHARD, HARD, XU, XIXIHARD, HARD, XU, XCXUHARD, HARD, XU, XIXIHARD, SOFT, XO, XSXSHARD, SOFT, XO, XIXIHARD, SOFT, XO, XSXSHARD, SOFT, XO, XIXIHARD, SOFT, XI, XSXIHARD, SOFT, XI, XIXI <td>HARD, HARD, Xs, Xf</td> <td>Xf</td> <td>HARD,HARD,Xs,Xu</td> <td>Xu</td>                                                                                                               | HARD, HARD, Xs, Xf | Xf   | HARD,HARD,Xs,Xu    | Xu  |