# TYPE 7900 CENTRAL PROCESSOR 90 THEORY OF OPERATION Service Manual No. 1

Copy No.

# UNIVAC Solid – State COMPUTER

# TYPE 7900 CENTRAL PROCESSOR 90 THEORY OF OPERATION Service Manual No. 1

# "COMPANY CONFIDENTIAL

# REGISTERED CIRCULATION

The information contained in this manual is the property of the Sperry Rand Corporation and is Company Confidential. It is submitted in confidence and should not be disclosed to others unless so disclosed in confidence with the permission of Remington Rand Univac, Division of Sperry Rand Corporation, being first obtained. This copy is numbered and is so registered in your name in our records. The document is not to be reproduced or duplicated without express permission in writing from a duly authorized representative of the Sperry Rand Corporation. This manual is subject to recall."

# TABLE OF CONTENTS

| S | e | С | t | i | 0 | n |  |

|---|---|---|---|---|---|---|--|

|---|---|---|---|---|---|---|--|

**n**.

| Ι     | INTRODUCTION                 |                                |

|-------|------------------------------|--------------------------------|

| 1-1   | Functional Description       | 1-1                            |

| 1-2   | Processor                    | 1-2                            |

| 1-3   | Control Unit                 | 1-3                            |

| 1 - 4 | Storage Unit                 | 1-3                            |

| 1-5   | Arithmetic Unit              | 1-3                            |

| 1-6   | Card Reader                  | 1-4                            |

| 1-7   | Read-Punch Unit              | 1-4                            |

| 1-8   | Printer                      | 1-4                            |

| 1-9   | Computer Language            | 1-4                            |

| 1-10  | Computer Words               | 1-5                            |

| 1-11  | Data Word                    | 1-5                            |

| 1-12  | Instruction Words            | 1-6                            |

| 1-13  | System Codes                 | 1-6                            |

| 1-14  | UCT Code                     | 1-7                            |

| 1-15  | Remington Rand Card and Code | 1-8                            |

|       |                              | · Sector Control of the sector |

| II | LOGICAL | CIRCUITRY |

|----|---------|-----------|

|    |         |           |

| 2-1  | Introduction                        | 2-1               |

|------|-------------------------------------|-------------------|

| 2-2  | General                             | 2-1               |

| 2-3  | Signal Polarity                     |                   |

| 2-4  | Diode Circuits                      | $\frac{2-1}{2-2}$ |

|      |                                     | <u>, 4 – 4</u>    |

| 2-5  | Gates                               | <u>2-2</u><br>2-2 |

| 2-6  | Buffers                             | 2-2               |

| 2-7  | Differences                         | 2-3               |

| 2-8  | Connecting Diode                    | 2-3               |

| 2-9  | Magnetic Amplifiers                 | 2-3               |

| 2-10 | Electronic Differences              | 2-3               |

| 2-11 | Logical Difference                  | 2-4               |

| 2-12 | Decoding and Encoding Matrixes      | 2-4               |

| 2-13 | Decoding Matrix                     | 2-4               |

| 2-14 | Encoding Matrix                     | 2-5               |

| 2-15 | Computer Timing                     | 2-6               |

| 2-16 | Pulse Time                          | 2-6               |

| 2-17 | Word Time                           | 2-6               |

| 2-18 | Timing Signals                      | 2-7               |

| 2-19 | Relation Between Timing Signals and |                   |

|      | Word Time                           | 2-8               |

| 2-20 | Signal Notation                     | 2-8               |

| 2-21 | Function Signals                    | 2-8               |

| 2-22 | Control Signals                     | 2-9               |

| 2-23 | Information Signals                 | 2-9               |

|      |                                     |                   |

Section

| 2-24 | Logical Functions                           | 2-9    |

|------|---------------------------------------------|--------|

|      | Logical Functions                           | 2-10   |

| 2-25 | Making a Gate Permissive                    |        |

| 2-26 | Alerting a Gate                             | 2-10   |

| 2-27 | Blocking a Gate                             | 2-10   |

| 2-28 | Basic Logical Circuits                      | 2-11   |

| 2-29 | The Basic Flip-Flop                         | 2-11   |

| 2-30 | Setting the Flip-Flop                       | 2-11   |

| 2-31 | Restoring the Flip-Flop                     | 2-12   |

| 2-32 | The Set and Restored States                 | 2-12   |

| 2-33 | The Read Flip-Flop                          | 2-13   |

| 2-34 | Counters                                    | 2-13   |

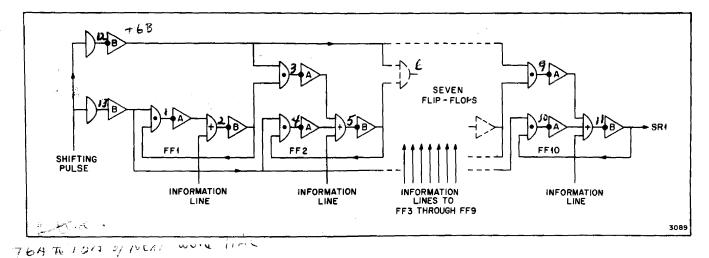

| 2-35 | Shift Register                              | 2-14   |

| 2-36 | Timing Reference                            | 2-16   |

| 2-37 |                                             | 2-16   |

|      | Circulating Registers                       |        |

| 2-38 | Input Gates                                 | 2 - 17 |

| 2-39 | Recirculating Gates of Register L           | 2-17   |

| 2-40 | Output Gates of Register L                  | 2-19   |

| 2-41 | Information Gating Circuit                  | 2-19   |

| 2-42 | Special Circuit Elements                    | 2-20   |

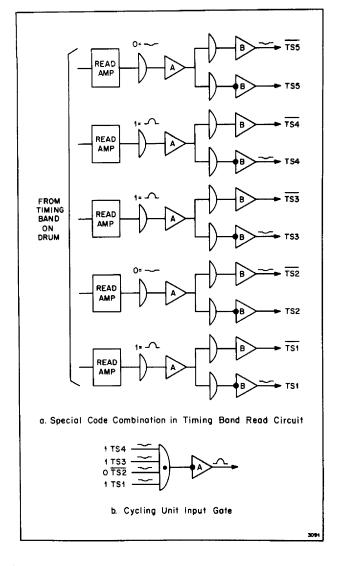

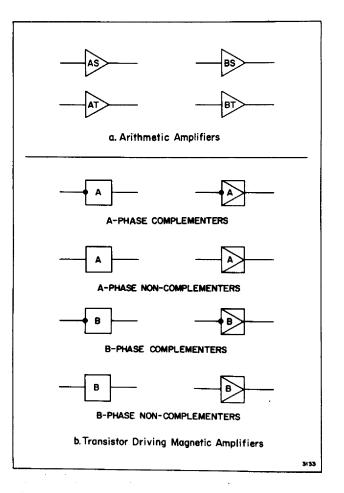

| 2-43 | Arithmetic Amplifiers                       | 2-20   |

| 2-44 | Transistor Driving Amplifiers               | 2-21   |

|      |                                             |        |

|      |                                             |        |

| III  | DESCRIPTION OF CENTRAL PROCESSOR COMPONENTS |        |

|      |                                             | •      |

| 3-1  | Introduction                                | 3-1    |

| 3-2  | Control Unit                                | 3-1    |

| 3-3  | Static Register                             | 3-1    |

| 3-4  | Static Register Flip-Flops                  | 3-2    |

| 3-5  | Stepping Gate                               | 3-2    |

| 3-6  | Ending Pulse Buffer                         | 3-3    |

| 3-7  | Block Read Flip-Flops                       | 3-3    |

| 3-8  | Run Flip-Flops                              | 3-4    |

| 3-9  | Instruction Decoder                         | 3-4    |

| 3-10 | Function Encod <u>er</u>                    | 3-6    |

| 3-11 | Register C                                  | 3-6    |

| 3-12 |                                             | 3-0    |

|      | Operator's Control Panel                    |        |

| 3-13 | Arithmetic Unit                             | 3-7    |

| 3-14 | Register A                                  | 3-8    |

| 3-15 | Input Gates                                 | 3-8    |

| 3-16 | Left Shift Gates                            | 3-8    |

| 3-17 | Right Shift Gates                           | 3-8    |

| 3-18 | Quotient Input Gates                        | 3-9    |

| 3-19 | Multiplier Sentinel Gate                    | 3-9    |

| 3-20 | LSD Complementer Gate                       | 3-9    |

| 3-21 | Recirculation Gates                         | 3-9    |

| 3-22 | Zero Suppress Gate                          | 3-10   |

| 3-23 | Remington Rand to UCT Translator            | ~ 17   |

|      | Gates                                       | 3-10   |

| 3-24 | UCT to RR Translator Gates                  |        |

| 3-25 |                                             | 3 - 10 |

| 3-25 | Circular Shift Gates                        | 3-11   |

|      | Sum Input Buffers                           | 3-11   |

| 3-27 | Output Display Gates                        | 3-11   |

| 3-28 | Output Circuits                             | 3-12   |

|      |                                             |        |

.

-

-

Page

| CLION | 11616                               | raye |

|-------|-------------------------------------|------|

| 3-29  | Register X                          | 3-12 |

| 3-30  | Input Gates                         | 3-12 |

| 3-31  | Right Shift Gates                   | 3-12 |

| 3-32  | Zero Suppress Gate                  | 3-13 |

| 3-32  | Comma Suppress Gates                | 3-13 |

|       |                                     | 3-13 |

| 3-34  | Recirculation Gates                 |      |

| 3-35  | Quotient-Complementing Gates        | 3-16 |

| 3-36  | Division Sentinel Gate              | 3-16 |

| 3-37  | Remainder Input Gates               | 3-16 |

| 3-38  | UCT to RR Translator Gates          | 3-16 |

| 3-39  | Check-Bit Storage Gate              | 3-16 |

| 3-40  | Check-Bit Computer Gates            | 3-17 |

| 3-41  | Circular-Shift Gates                | 3-17 |

| 3-42  | Output Display Gates                | 3-17 |

| 3-43  | Output Circuits                     | 3-17 |

| 3-44  | Register L                          | 3-18 |

| 3-45  | Recirculation Gates                 | 3-18 |

| 3-46  | M Gates                             | 3-18 |

| 3-47  | S Gates                             | 3-19 |

| 3-48  | Output Display Gates                | 3-19 |

| 3-49  | Output Gates                        | 3-19 |

| 3-50  | Outputs                             | 3-19 |

| 3-51  | S Buffers                           | 3-19 |

| 3-52  | M Buffers                           | 3-20 |

| 3-53  | Comparator                          | 3-20 |

| 3-54  | Quinary Equality Circuit            | 3-20 |

| 3-55  | Quinary Carry Circuit               | 3-21 |

| 3-56  | Force Decimal-Carry Gates           | 3-23 |

| 3-57  | Binary Equality Gates               | 3-24 |

| 3-58  | Initial Force Decimal-Carry Circuit | 3-25 |

| 3-59  | Binary-Carry Circuit                | 3-26 |

| 3-60  | Binary Adder Gates                  | 3-26 |

| 3-61  | Conditional Transfer Flip-Flop      | 3-26 |

| 3-61  |                                     | 3-28 |

| 3-63  | Time Selection Flip-Flop            | 3-29 |

|       | Complementer<br>Desimal CommunAdder |      |

| 3-64  | Decimal-Carry Adder                 | 3-30 |

| 3-65  | Quinary Adder                       | 3-31 |

| 3-66  | Sign and Control Circuit            | 3-31 |

| 3-67  | Register A Sign Flip-Flop           | 3-32 |

| 3-68  | Register L Sign Flip-Flop           | 3-33 |

| 3-69  | Register X Sign Flip-Flop           | 3-33 |

| 3-70  | Sign Display Circuit                | 3-33 |

| 3-71  | Complement Flip-Flop                | 3-34 |

| 3-72  | Overflow Flip-Flop                  | 3-35 |

| 3-73  | Overflow Delay Flip-Flop            | 3-36 |

| 3-74  | Multiplier/Quotient Counter         | 3-36 |

| 3-75  | MQC Flip-Flops                      | 3-37 |

| 3-76  | Countdown Circuit                   | 3-38 |

| 3-77  | Clear MQC Circuit                   | 3-40 |

| 3-78  | IER-OR Flip-Flops                   | 3-40 |

| 3-79  | Storage Unit                        | 3-41 |

| 3-80  | Storage Drum                        | 3-42 |

| 3-81  | Buffer Storage Areas                | 3-43 |

| 3-82  | Timing Band                         | 3-45 |

|       |                                     |      |

Section

# Title

Page

| 3-83  | Sprocket Track                      | 3-46 |

|-------|-------------------------------------|------|

| 3-84  | Timing Band Read Circuits           | 3-46 |

| 3-85  | Cycling Unit                        | 3-47 |

| 3-86  | Input-Output Sentinels              | 3-48 |

| 3-87  | Write Circuit                       | 3-50 |

| 3-88  | Write Pedestal Generator            | 3-50 |

| 3-89  | Write Input Circuits                | 3-50 |

| 3-90  | Check-Bit Circuit                   | 3-50 |

| 3-91  | Write Flip-Flop                     | 3-51 |

| 3-92  | Phase Modulation Coder              | 3-51 |

| 3-93  | Read Circuit                        | 3-52 |

| 3-94  | Read Flip-Flop                      | 3-53 |

| 3-95  | Read Output Circuit                 | 3-53 |

| 3-96  | Memory Selection Circuits           | 3-54 |

| 3-97  | Band Selection Flip-Flops           | 3-54 |

| 3-98  | Clear Band Selection Circuit        | 3-56 |

| 3-99  | Head Selection Flip-Flops           | 3-56 |

| 3-100 | Switch Selection Circuits           | 3-57 |

| 3-101 | Memory Switch                       | 3-57 |

| 0 101 | Memory Switcon                      | 0 0. |

|       |                                     |      |

| IV    | THEORY OF OPERATION                 |      |

| 1.    | THEORI OF OTERATION                 |      |

| 4-1   | Introduction                        | 4-1  |

| 4-2   | Basic Operation Cycle               | 4-1  |

| 4-3   | Search-for-Instruction Step         | 4-2  |

| 4-4   | Locating the Storage Address        | 4-2  |

| 4-5   | Comparison and Head Selection       | 4-8  |

| 4-6   | Band Selection                      | 4-13 |

| 4-7   | Staticize-Instruction Step          | 4-15 |

| 4-8   | Storing the p7 Digit                | 4-17 |

| 4-9   | Storing the Instruction Word        | 4-17 |

| 4-10  | Staticizing the Instruction         | 4-17 |

| 4-11  | Search-for-Operand Step             | 4-18 |

| 4-12  | Instruction Code Characteristics    | 4-18 |

| 4-13  | Locating the Operand                | 4-19 |

| 4-14  | Execute-Instruction Step            | 4-20 |

| 4-15  | Instructions with Two Execution     | - 20 |

|       | Steps                               | 4-20 |

| 4-16  | Timing of the Basic Operation Cycle | 4-21 |

| 4-17  | Processing a Typical Instruction    | 4-21 |

| 4-18  | Search for Operand                  | 4-27 |

| 4-19  | Execute the H(60) Instruction       | 4-28 |

| 4-20  | Memory Write Operation              | 4-29 |

| 4-21  | Arithmetic Operations               | 4-30 |

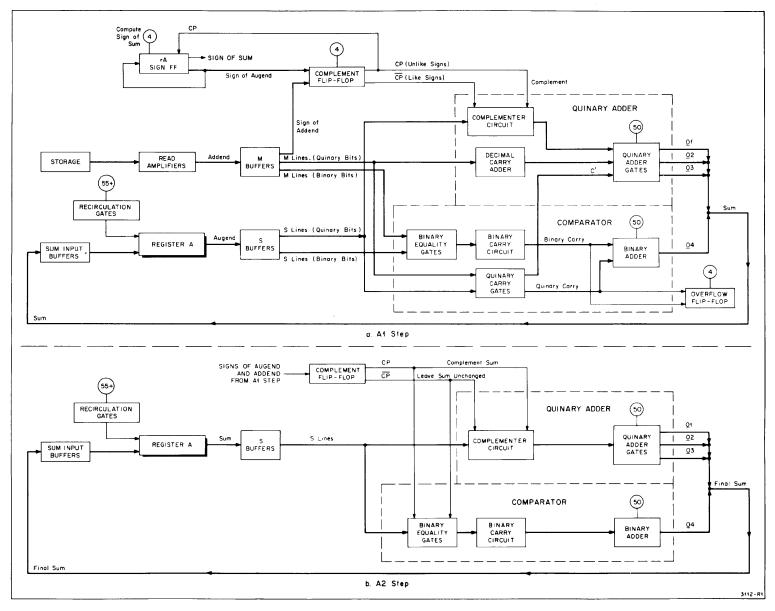

| 4-22  | Addition and Subtraction            | 4-30 |

| 4-23  | Add Instruction                     | 4-30 |

| 4-24  | Subtract Instruction                | 4-37 |

| 4-24  | Sample Problems                     | 4-38 |

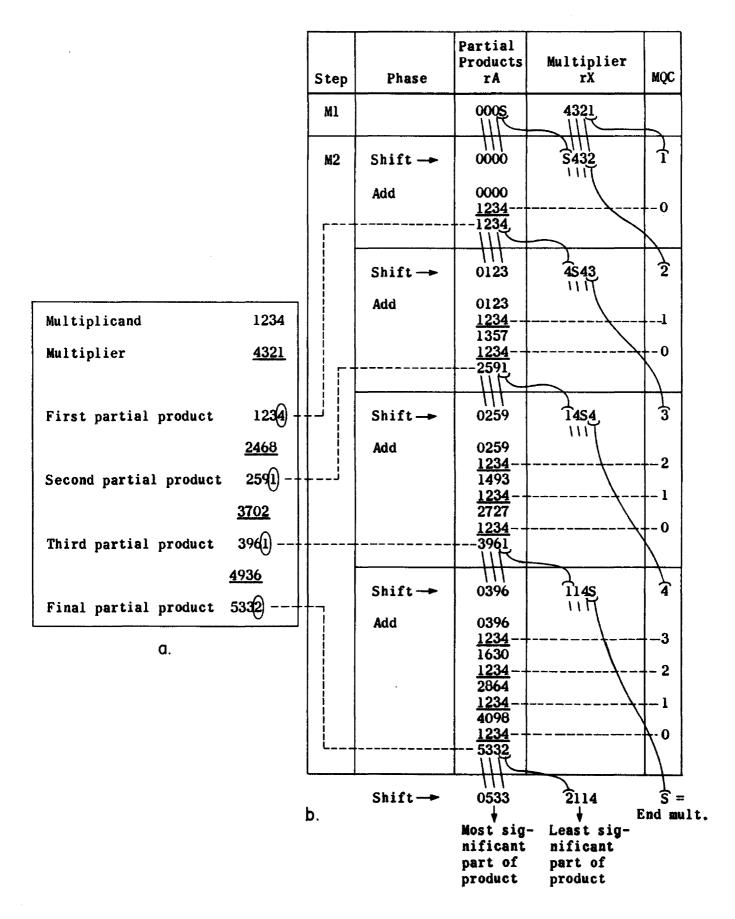

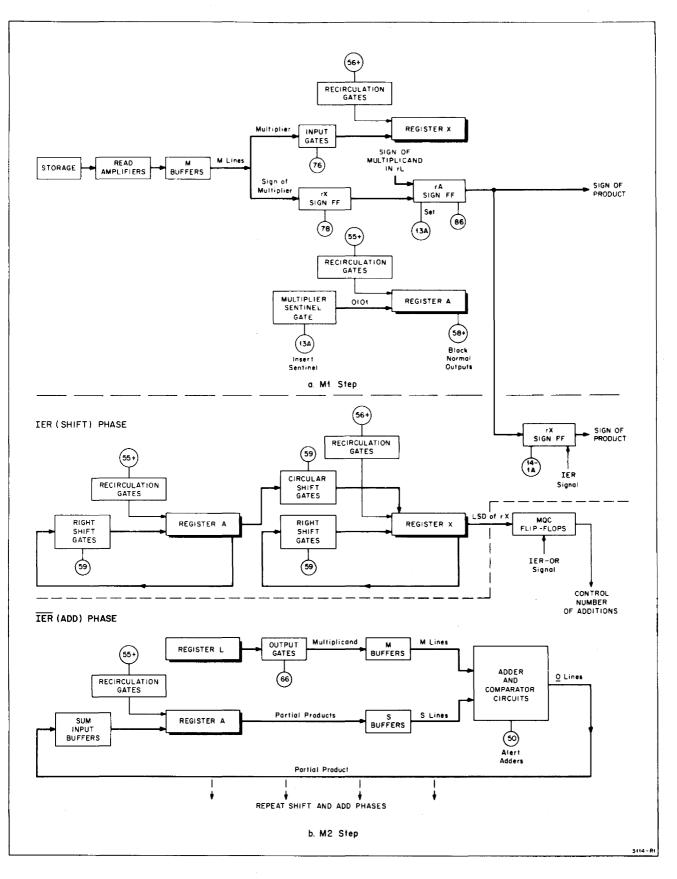

| 4-25  | Multiplication                      | 4-30 |

| 4-20  | General Description                 | 4-41 |

| 4-27  | Initial Conditions                  | 4-45 |

| 4-20  | Ml Step                             | 4-45 |

| 4-67  | MT Steh                             | 4-40 |

|       |                                     |      |

Ì,

.

| P | а | α | e |

|---|---|---|---|

|   |   |   |   |

V

|      |                                                  | 3 -  |

|------|--------------------------------------------------|------|

| 4-30 | M2 Step                                          | 4-46 |

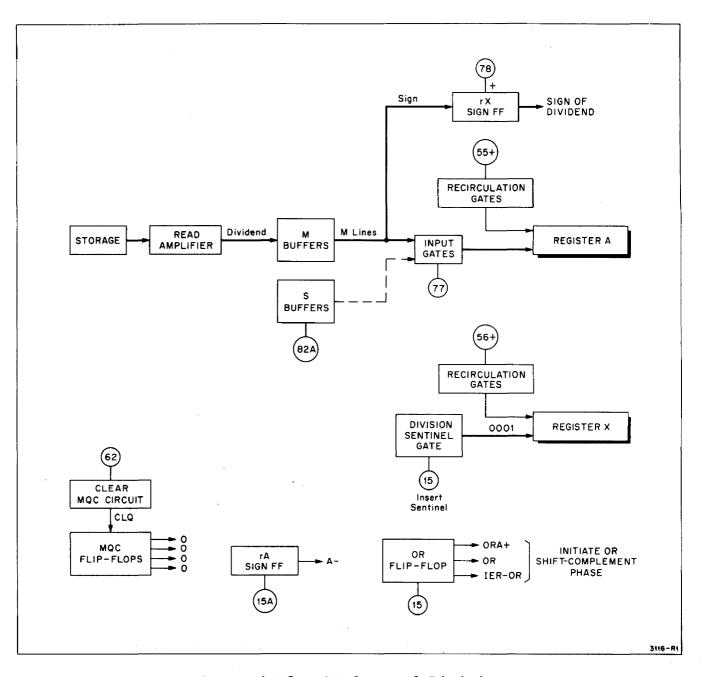

| 4-31 | Division                                         | 4-48 |

| 4-32 | General Description                              | 4-48 |

| 4-33 | Initial Conditions                               | 4-52 |

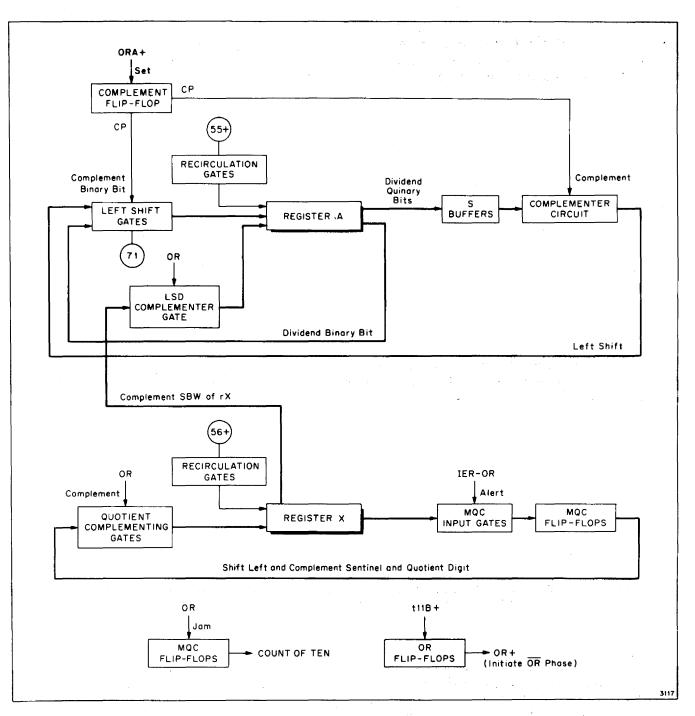

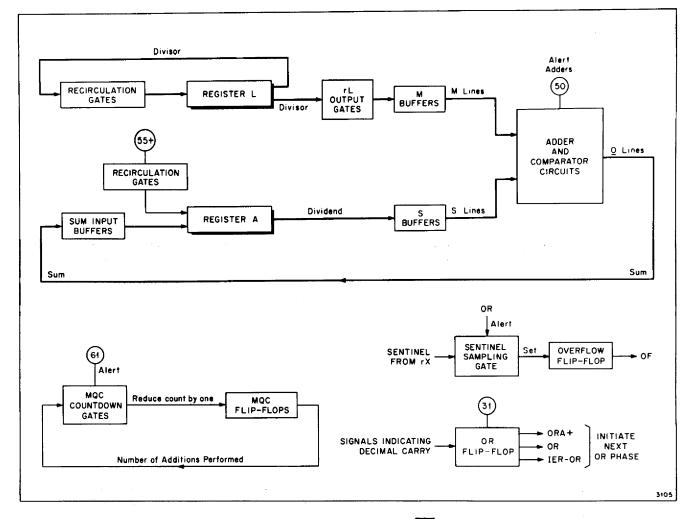

| 4-34 | Dl Step                                          | 4-54 |

| 4-35 | D2 Step                                          | 4-54 |

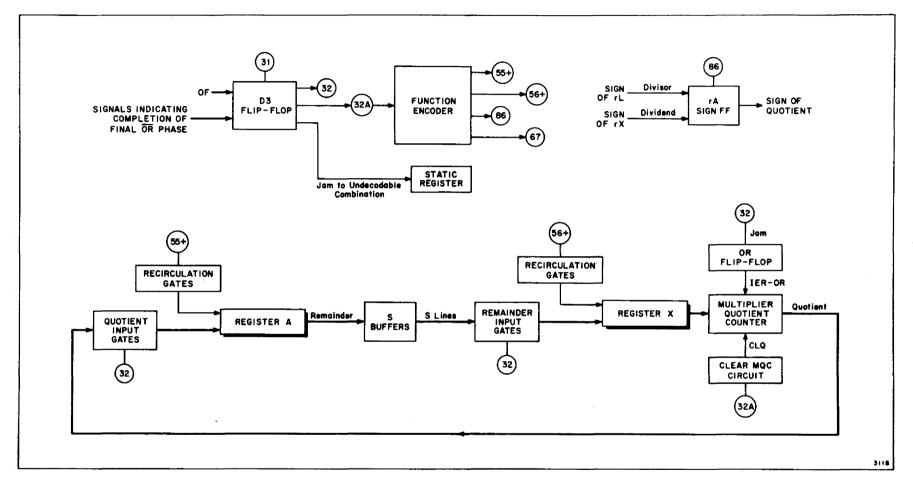

| 4-36 | D3 Step                                          | 4-59 |

| 4-37 | Error Circuits                                   | 4-61 |

| 4-38 | Memory-Check Flip-Flop                           | 4-62 |

| 4-39 | Timing-Error Flip-Flop                           | 4-63 |

| 4-40 | Cycling-Unit Error Flip-Flop                     | 4-64 |

| 4-41 | I/O Abnormal-Condition Flip-Flop                 | 4-64 |

| 4-42 | Manually-Controlled Operations                   | 4-65 |

| 4-43 | One Line Print                                   | 4-66 |

| 4-44 | One Card RPU                                     | 4-67 |

| 4-45 | One Card HSR                                     | 4-67 |

| 4-46 | One Instruction                                  | 4-67 |

| 4-47 | Comparison Stop                                  | 4-67 |

| 4-48 | Keyboard Input                                   | 4-68 |

| 4-49 | Manual Operation                                 | 4-68 |

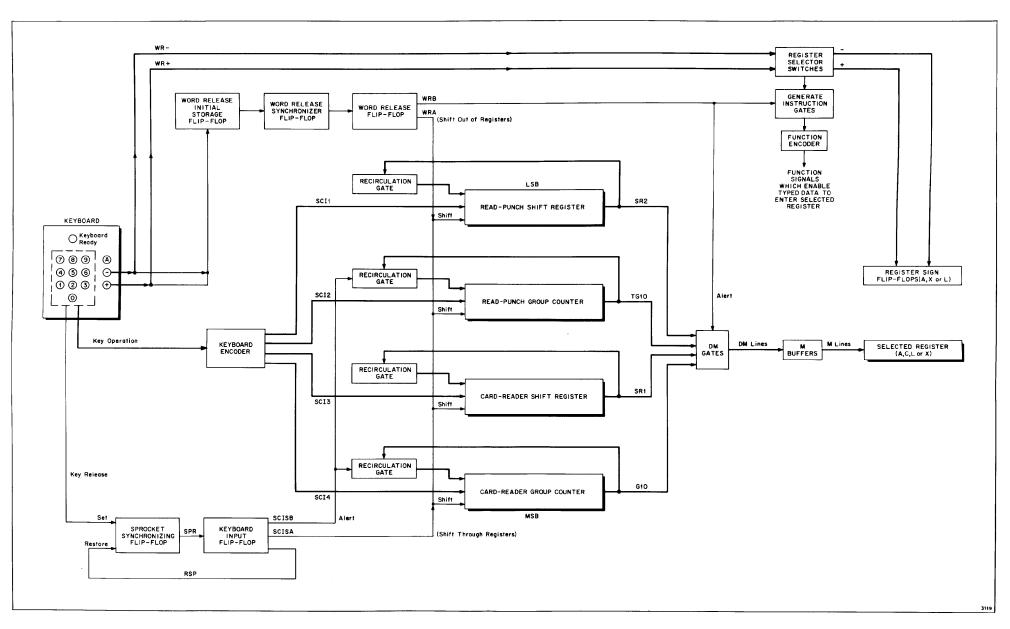

| 4-50 | Depressing a Key                                 | 4-70 |

| 4-51 | Releasing a Key                                  | 4-71 |

| 4-52 | Signing and Releasing the Word                   | 4-72 |

|      |                                                  |      |

| v    | INSTRUCTIONS                                     |      |

| 5-1  | Introduction                                     | 5-1  |

| 5-2  | Input-Output Instructions                        | 5-2  |

| 5-3  | Arithmetic Instructions                          | 5-2  |

| 5-4  | Transfer Instructions                            | 5-3  |

| 5-5  | The $60(H)$ , $56(X)$ , and $50(J)$ Instructions | 5-3  |

| 5-6  | The $25(B)$ , $05(Y)$ , and $30(L)$ Instructions | 5-3  |

| 5-7  | The 25(B) Instruction                            | 5-3  |

| 5-8  | The 77(K) Instruction                            | 5-3  |

| 5-9  | Translate Instructions                           | 5-3  |

| 5-10 | The l2(G) Instruction                            | 5-4  |

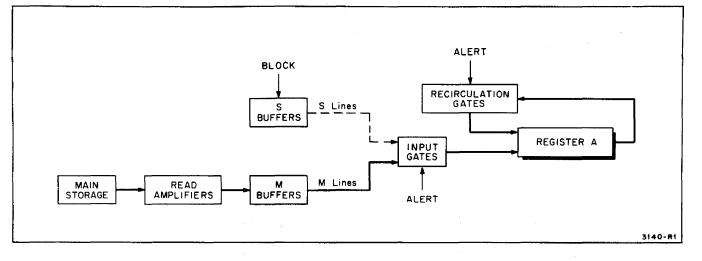

| 5-11 | The 17(R) Instruction                            | 5-4  |

| 5-12 | Miscellaneous Instructions                       | 5-5  |

| 5-13 | The 20(P) Superimpose Instruction                | 5-5  |

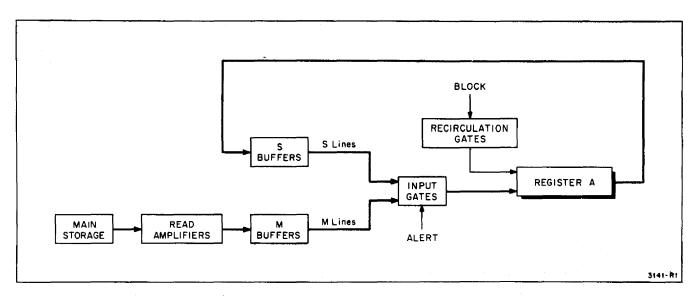

| 5-14 | The 35(E) Extract Instruction                    | 5-5  |

| 5-15 | The 32(N) Shift-Right Instruction                | 5-6  |

| 5-16 | The 37(V) Shift-Left Instruction                 | 5-7  |

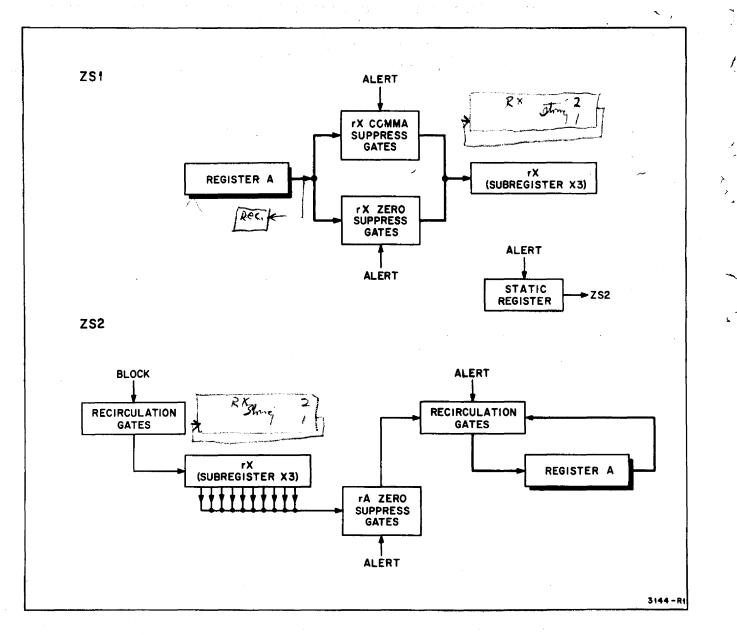

| 5-17 | The 62(ZS) Zero Suppress Instruction             | 5-8  |

| 5-18 | The 67 (STOP) Instruction                        | 5-9  |

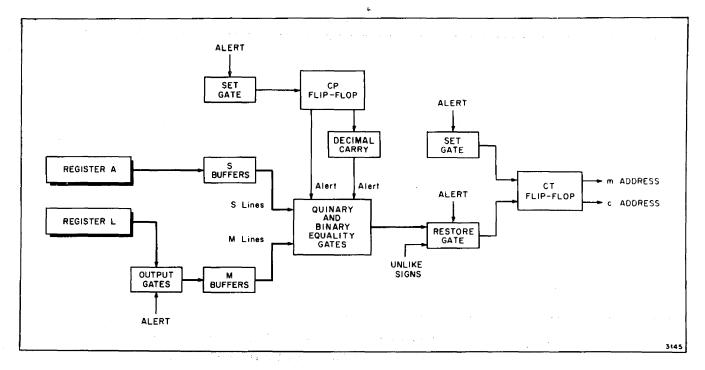

| 5-19 | Comparison Instructions                          | 5-9  |

| 5-20 | The 82(Q) Instruction                            | 5-10 |

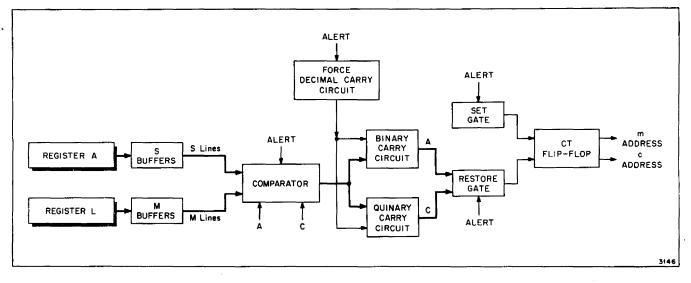

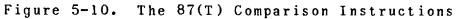

| 5-21 | The 87(T) Instruction                            | 5-11 |

| 5-22 | Test Instructions                                | 5-14 |

| 5-23 | The 22(I 11) Instruction                         | 5-14 |

| 5-24 | The 27(I 21) Instruction                         | 5-15 |

| 5-25 | The 42(I 31) Instruction                         | 5-15 |

|      |                                                  |      |

# Section

# Title

1.3

| VI           | ELECTRONIC CIRCUITRY                                             | - 14         |

|--------------|------------------------------------------------------------------|--------------|

| 6-1          | Introduction                                                     | 6-1          |

| 6-2          | Diodes                                                           | 6-1          |

| 6-3          | Basic Theory                                                     | 6-1          |

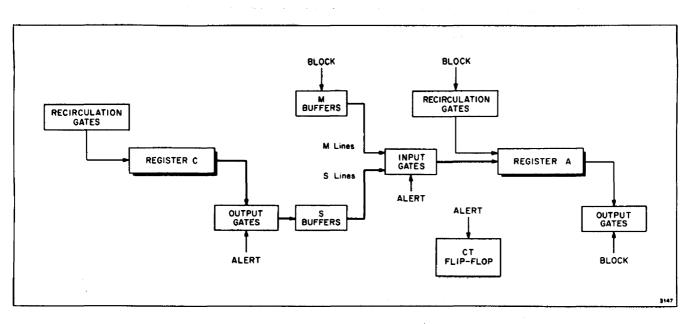

| 6-4          | Germanium Structure                                              | 6-2          |

| 6-5          | Conduction in Semiconductors                                     | 6-2          |

| 6-6          | Doped Germanium                                                  | 6-3          |

| 6-7          | N-Type Germanium                                                 | 6-3          |

| 6-8          | P-Type Germanium                                                 | 6-4          |

| 6-9          | Junction Diodes                                                  | 6-4          |

| 6-10         | Forward Bias                                                     | 6-5          |

| 6-11         | Reverse Bias                                                     | 6-6          |

| 6-12         | Junction Diode as Rectifier                                      | 6-6          |

| 6-13         | Applications                                                     | 6-7          |

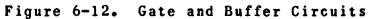

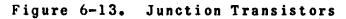

| 6-14         | Transistors                                                      | 6-8          |

| 6-15         | Basic Theory                                                     | 6-8          |

| 6-16         | Common-Base Circuit                                              | 6-9          |

| 6-17         | NPN Transistor                                                   | 6-9          |

| 6-18         | Transistor as Voltage Amplifier                                  | 6-11         |

| 6-19<br>6-20 | PNP Transistor<br>Common Emitton Cincuit                         | 6-12         |

| 6-21         | Common-Emitter Circuit<br>Symbols                                | 6-13<br>6-15 |

| 6-22         | Symbols<br>Summary                                               | 6 - 15       |

| 6-23         | Voltage Breakdown in Junction Transistors                        |              |

| 6-24         | Transistor Identification                                        | 6-17         |

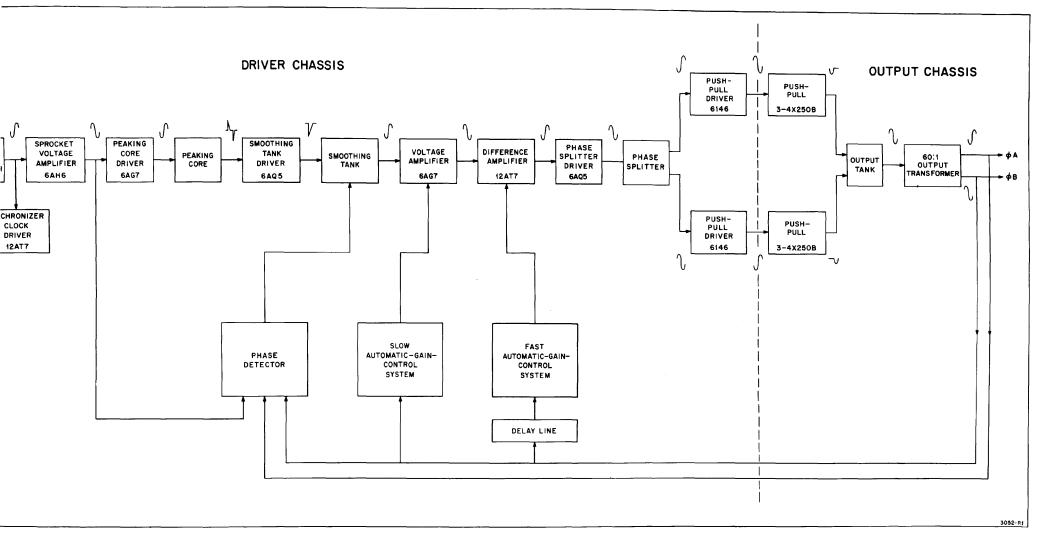

| 6-25         | Clock                                                            | 6-18         |

| 6-26         | General Description                                              | 6-18         |

| 6-27         | Principles of Operation                                          | 6-19         |

| 6-28         | Fast AGC System                                                  | 6-22         |

| 6-29         | General Description                                              | 6-22         |

| 6-30         | Principles of Operation                                          | 6-22         |

| 6-31         | Clock Öutput Voltage Normal                                      | 6-23         |

| 6-32         | Clock Output Voltage Low                                         | 6-23         |

| 6-33         | Clock Output Voltage High                                        | 6-23         |

| 6-34         | Slow AGC System                                                  | 6-24         |

| 6-35         | General Description                                              | 6-24         |

| 6-36         | Principles of Operation                                          | 6-24         |

| 6-37         | Clock Output Voltage Normal                                      | 6-25         |

| 6-38         | Clock Output Voltage Low                                         | 6-25         |

| 6-39         | Clock Output Voltage High                                        | 6-25         |

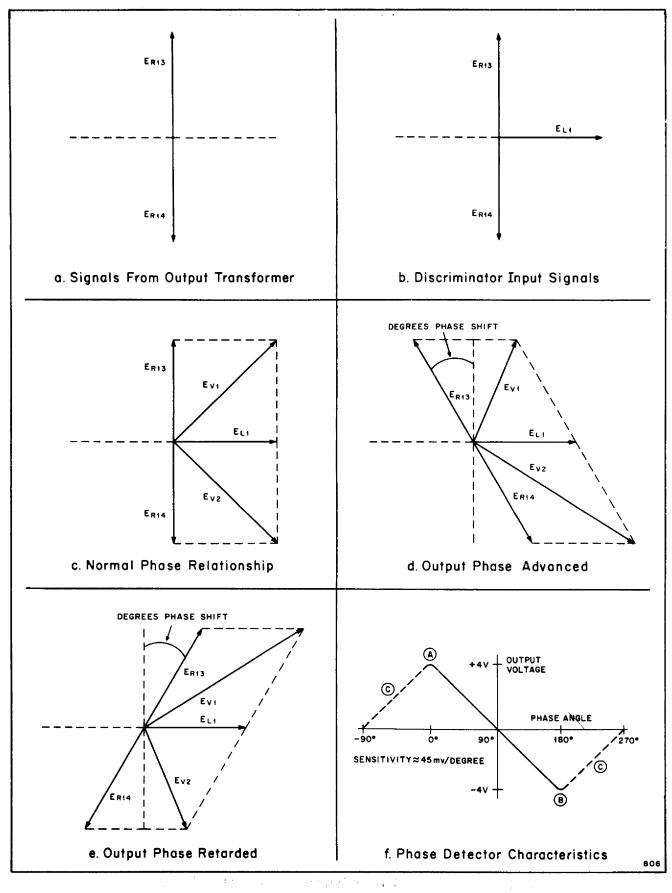

| 6-40         | Phase-Control System                                             | 6-25         |

| 6-41<br>6-42 | General Description<br>Bringinlag of Operation                   | 6-25         |

| 6-42         | Principles of Operation<br>Phase of Cleak Output Advanced        | 6-26<br>6-28 |

| 6-44         | Phase of Clock Output Advanced<br>Phase of Clock Output Retarded | 6-29         |

| 6-45         | Change of Sprocket Frequency                                     | 6-29         |

| 6-46         | Voltage and Current Monitors                                     | 6-31         |

| 6-47         | Magnetic Amplifiers                                              | 6 - 33       |

| 6-48         | General Description                                              | 6-33         |

| 6-49         | Basic Principles of Operation                                    | 6-34         |

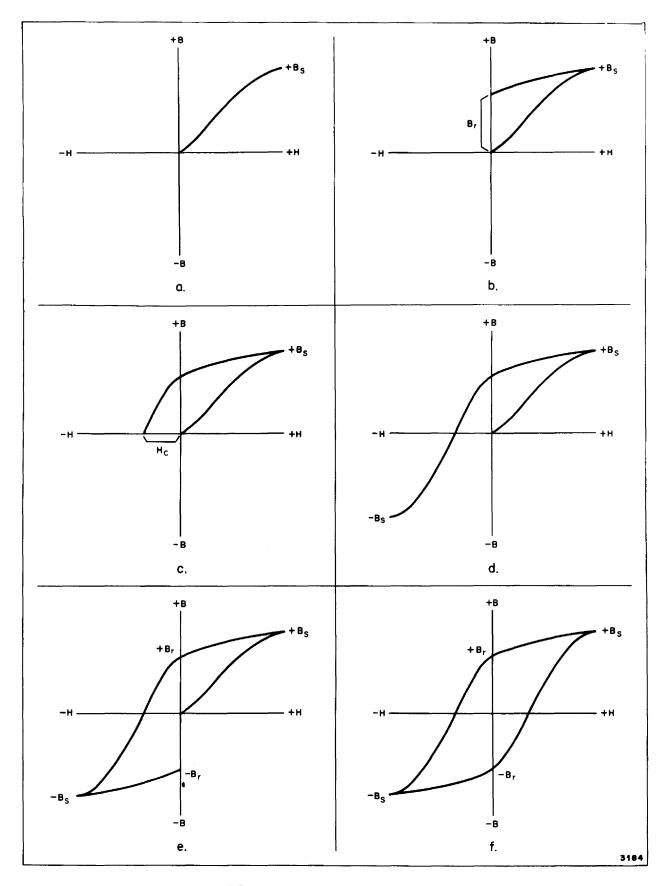

| 6-50         | Magnetization Curves                                             | 6-34         |

| 6-51         | Coil Impedance Variations                                        | 6-35         |

|              | •                                                                |              |

| S | e | c | t. | i | o n |  |

|---|---|---|----|---|-----|--|

|   |   |   |    |   |     |  |

| Page | P | a | g | e |

|------|---|---|---|---|

|------|---|---|---|---|

| 6-52 | Core Materials                        | 6-37 |

|------|---------------------------------------|------|

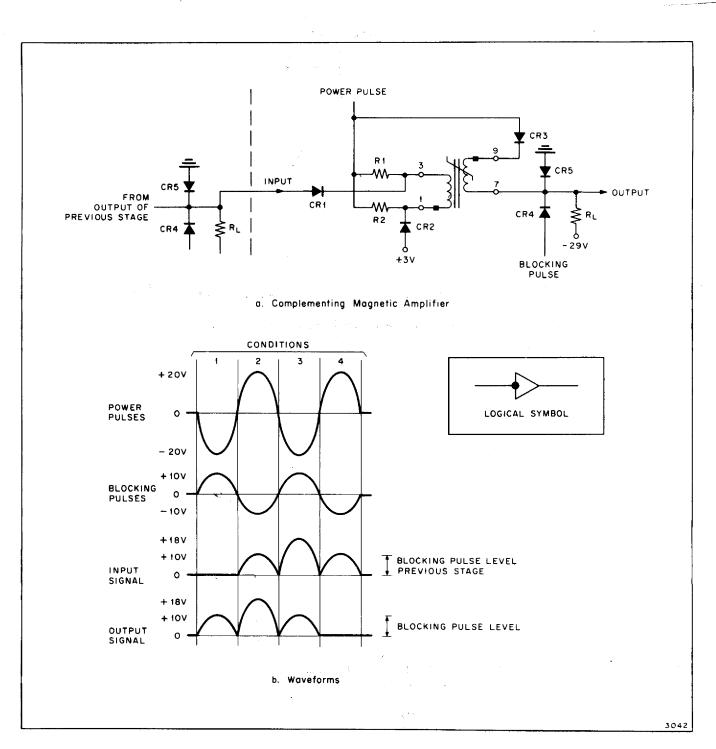

| 6-53 | Complementing Magnetic Amplifier      | 6-38 |

| 6-54 | Condition 1                           | 6-38 |

| 6-55 | Condition 2                           | 6-39 |

| 6-56 | Condition 3                           | 6-39 |

| 6-57 | Condition 4                           | 6-39 |

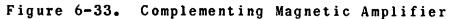

| 6-58 | Noncomplementing Magnetic Amplifier   | 6-40 |

| 6-59 | Condition 1                           | 6-41 |

| 6-60 | Condition 2                           | 6-41 |

| 6-61 | Condition 3                           | 6-42 |

| 6-62 | Condition 4                           | 6-42 |

| 6-63 | Power Requirements                    | 6-43 |

| 6-64 | Mutual Exclusion                      | 6-44 |

| 6-65 | Magnetic Amplifier Circuit Variations | 6-44 |

| 6-66 | Arithmetic Registers                  | 6-44 |

|      |                                       | 6-45 |

| 6-67 | Transistor Amplifier Package (TAP)    | 6-46 |

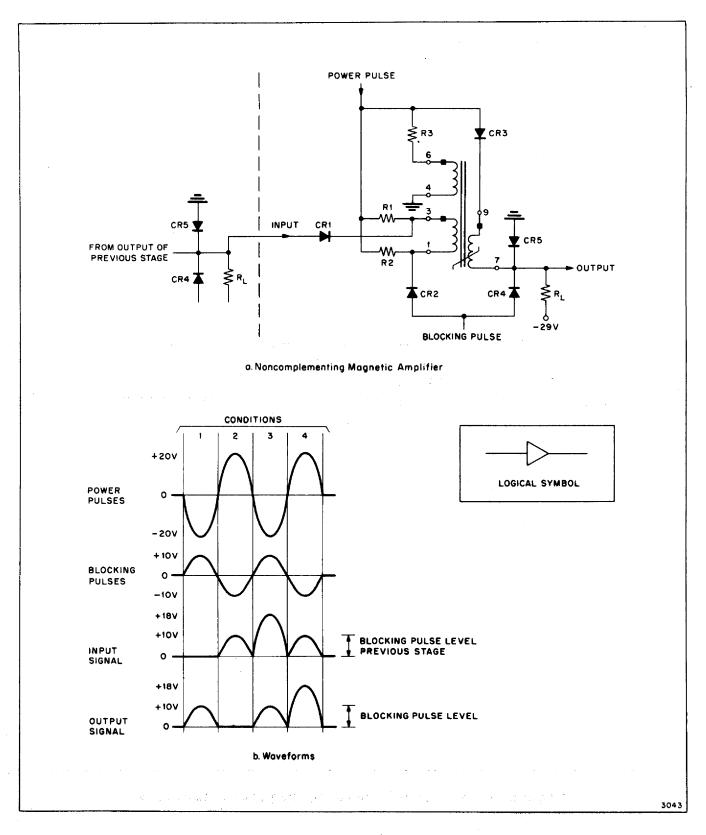

| 6-68 | Storage Unit                          | 6-46 |

| 6-69 | General Description                   |      |

| 6-70 | Write Circuitry                       | 6-47 |

| 6-71 | General Description                   | 6-47 |

| 6-72 | Diode Cluster                         | 6-48 |

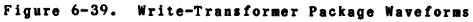

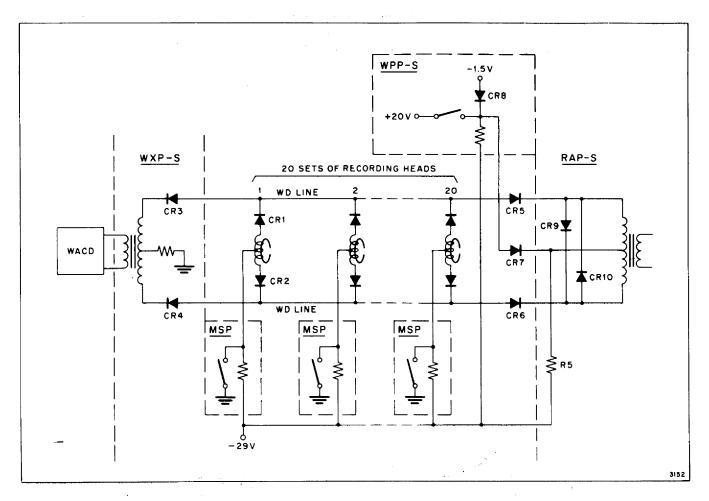

| 6-73 | Write-Transformer Package (WXPS)      | 6-48 |

| 6-74 | Write-Amplifier Complementer-Driver   |      |

|      | Package (WACD)                        | 6-49 |

| 6-75 | Read Circuitry                        | 6-50 |

| 6-76 | General Description                   | 6-50 |

| 6-77 | Write-Pedestal Package (WPPS)         | 6-50 |

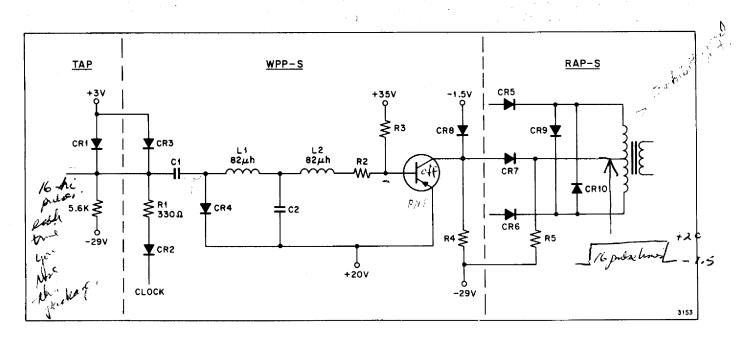

| 6-78 | Read-Amplifier Package (RAPS)         | 6-51 |

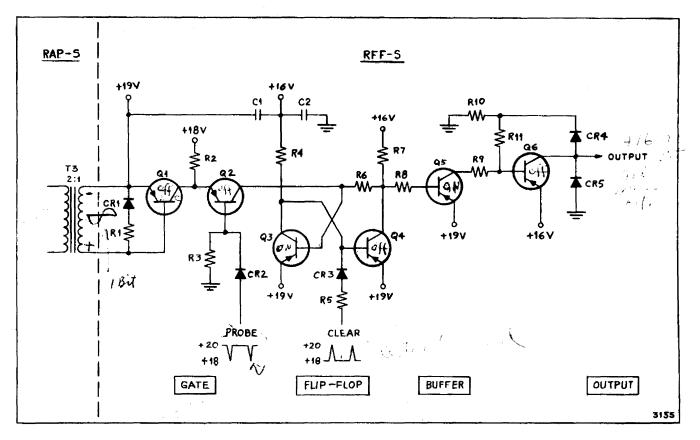

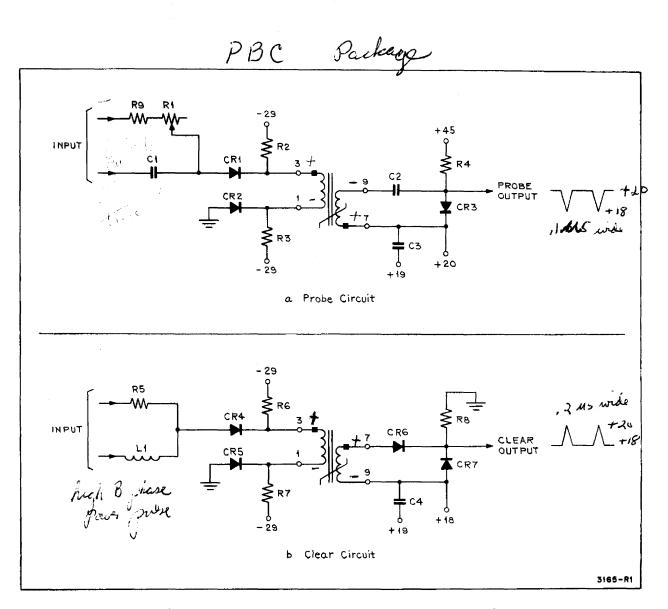

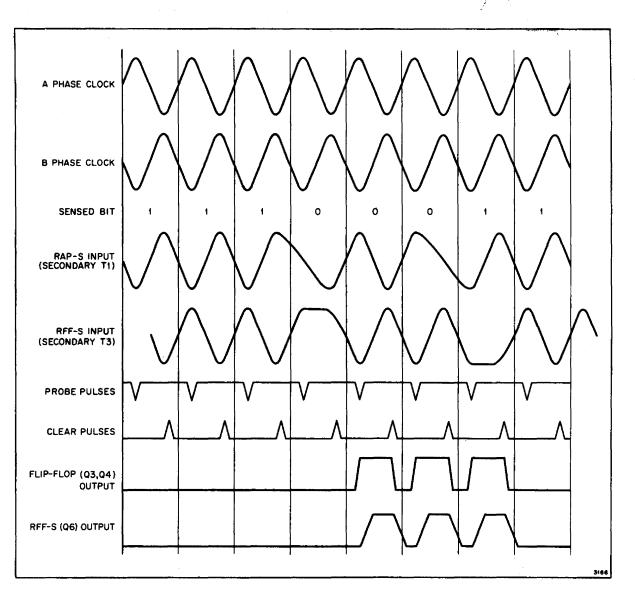

| 6-79 | Read Flip-Flop Package (RFFS)         | 6-54 |

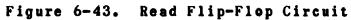

| 6-80 | Probe and Clear Package (PBC)         | 6-55 |

| 6-81 | Head Selection                        | 6-57 |

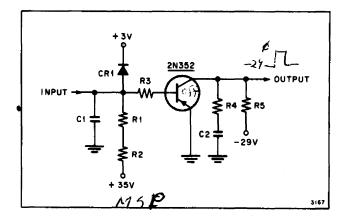

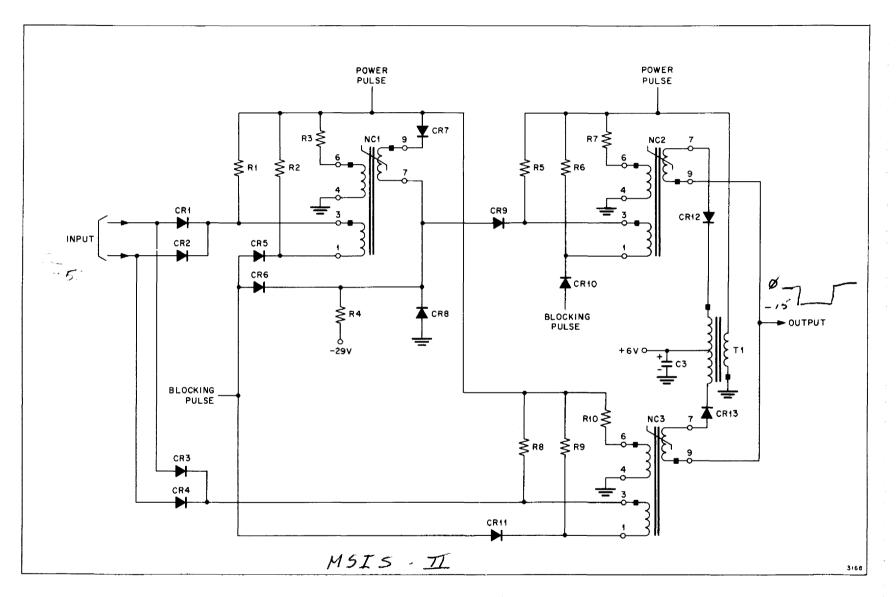

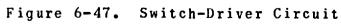

| 6-82 | Matrix-Selector Package (MSP)         | 6-57 |

| 6-83 | Head-Switch Driver Package (MSIS)     | 6-58 |

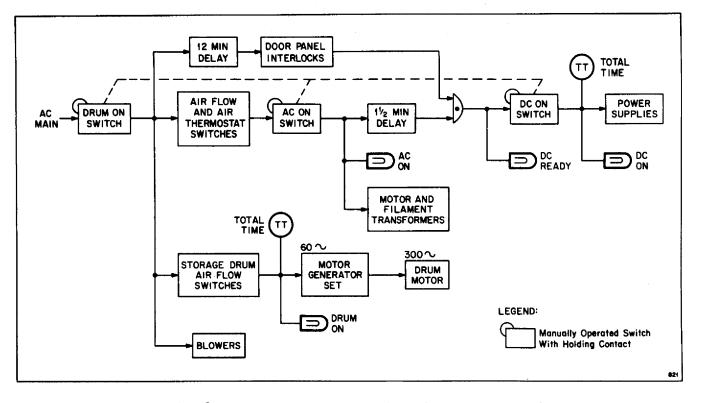

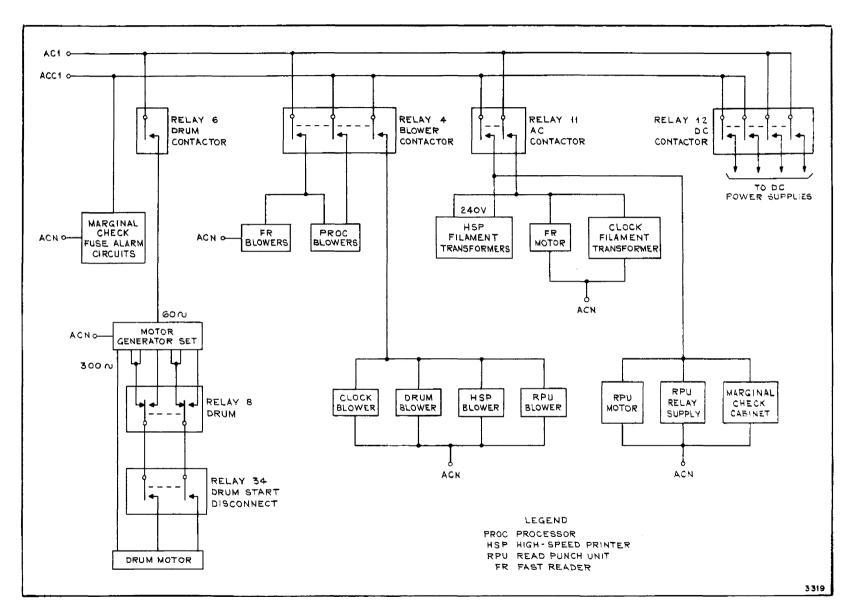

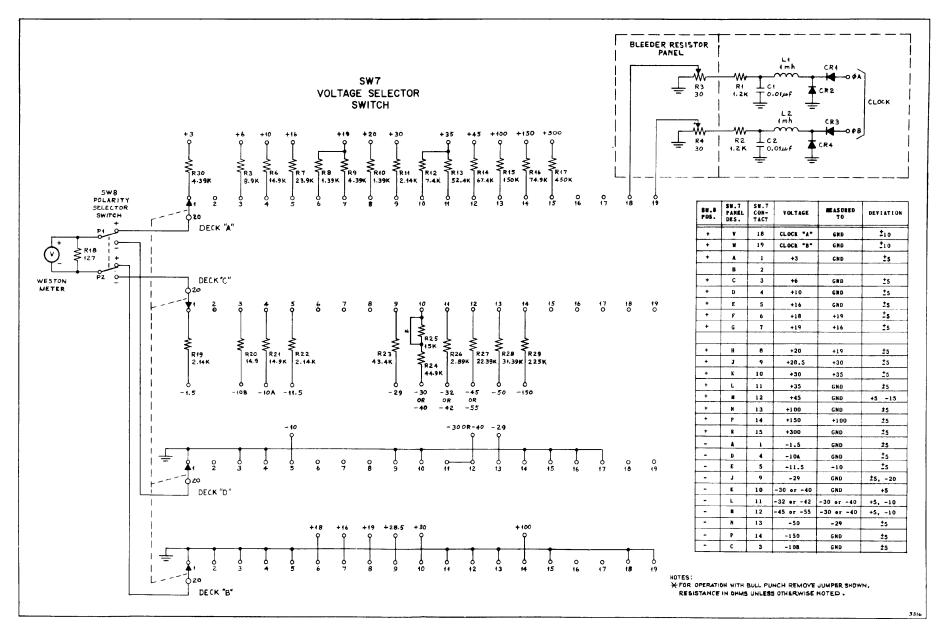

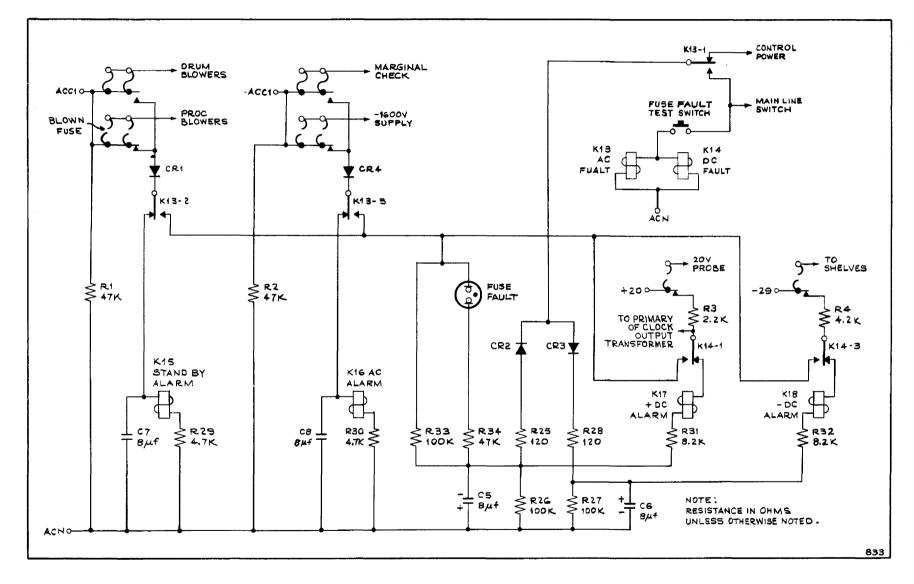

| 6-84 | Power Control and Power Supplies      | 6-59 |

| 6-85 | Power Turn-On Procedure               | 6-59 |

| 6-86 | AC Distribution                       | 6-60 |

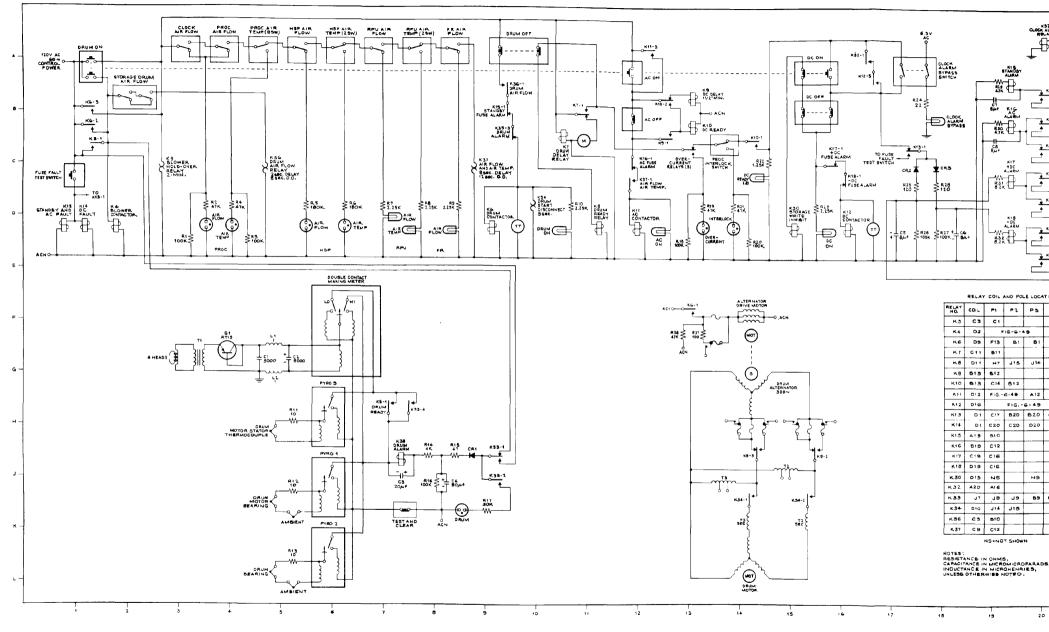

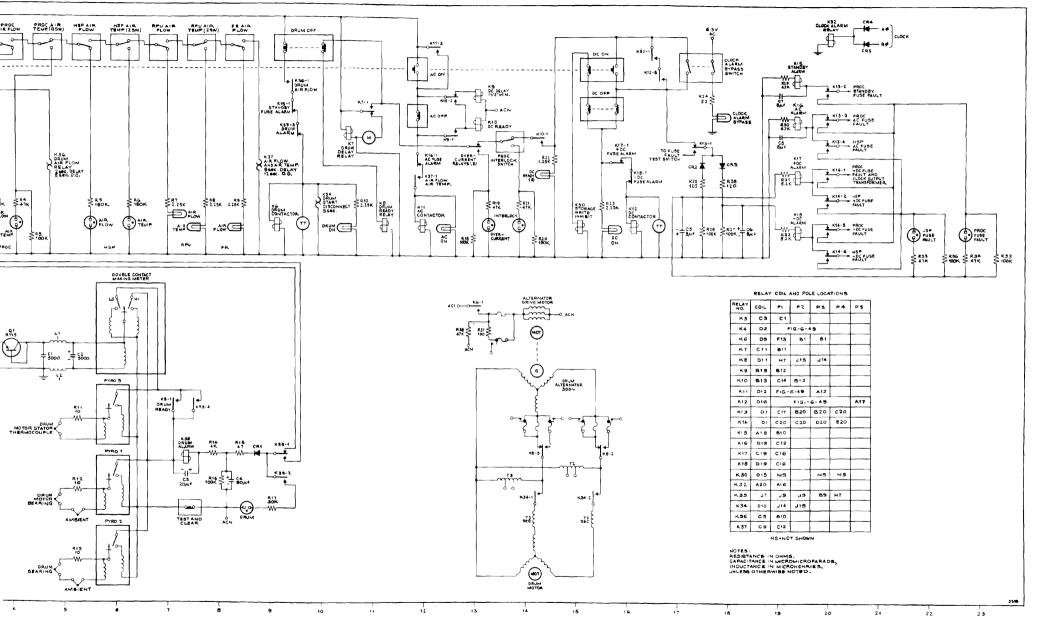

| 6-87 | Power-Control Circuits                | 6-61 |

| 6-88 | Drum Alarm Circuits                   | 6-62 |

| 6-89 | Power Supply                          | 6-62 |

| 6-90 | Head-Spacing Detector                 | 6-63 |

| 6-91 | Stator Temperature Detector           | 6-64 |

| 6-92 | Bearing Temperature Rise Detectors    | 6-64 |

| 6-93 | Power Turn-Off Procedure              | 6-65 |

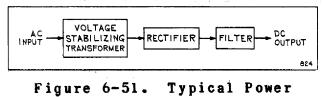

| 6-94 | Power Supplies                        | 6-65 |

| 6-95 | General Description                   | 6-65 |

| 6-96 | Voltage-Stabilizing Transformer       | 6-65 |

| 6-97 |                                       | 6-67 |

|      | Power-Supply Interconnections         | 6-67 |

| 6-98 | Voltage Monitor                       | 0-07 |

,

| Section | Title                           | Page |

|---------|---------------------------------|------|

| 6-99    | Fuses                           | 6-68 |

| 6-100   | Fuse Fault Circuitry            | 6-68 |

| 6-101   | Fuseboard Servicing Precautions | 6-70 |

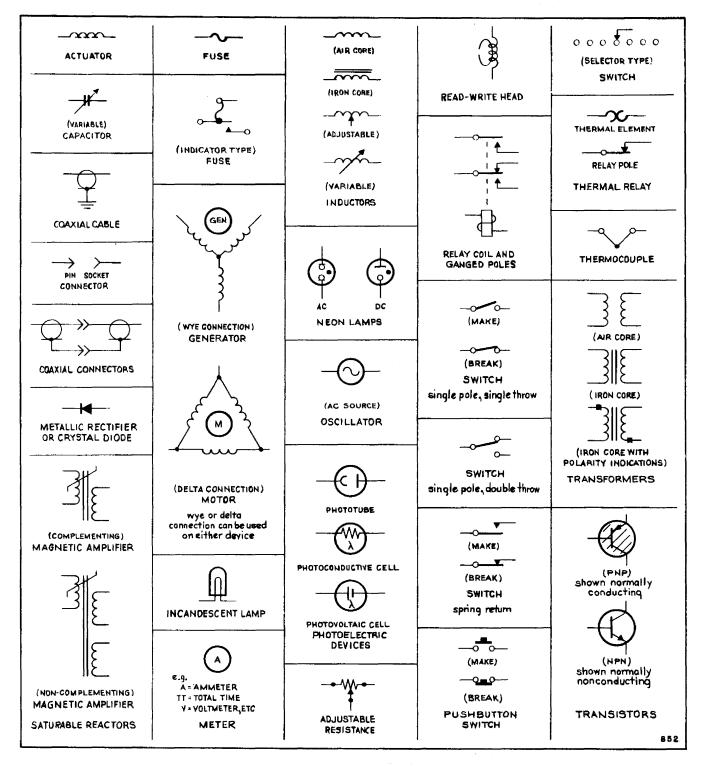

| 6-102   | Standard Symbols                | 6-70 |

APPENDIX B SIGNAL GLOSSARY

# APPENDIX C INSTRUCTION LIST

# A GLOSSARY OF TERMS

1

.

# LIST OF ILLUSTRATIONS

| Figure       | Title                                            | Page         |

|--------------|--------------------------------------------------|--------------|

| 1-1          | Typical Arrangement of New Univac ®<br>System    | 1-14         |

| 1-2          | Central Processor Units                          | 1-14         |

| 1-2          | Remington Rand Tabulating Card                   | 1-16         |

| 1-5          | Kemington Kanu labulating Calu                   | 1-10         |

| 2-1          | Basic Logical Circuit Elements                   | 2-22         |

| 2-2          | Decoding and Encoding Matrixes                   | 2-22         |

| 2-3          | A-Phase and B-Phase Power Pulses                 | 2-23         |

| 2-4          | Twenty-four Time Intervals of a<br>Word Time     | 2-23         |

| 2-5          | Relation Between Timing Signals<br>and Word Time | 2-24         |

| 2-6          | Typical Gating Circuit                           | 2-24         |

| 2-7          | Setting a Typical Flip-Flop                      | 2-25         |

| 2-8          | Restoring a Typical Flip-Flop                    | 2-25         |

| 2-9          | Typical Counter Circuit                          | 2-26         |

| 2-10         | Typical Shift Register                           | 2-26         |

| 2-11         | Digit Positions of a Computer Word               | 2-27         |

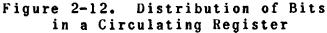

| 2-12         | Distribution of Bits in a Circulating            |              |

|              | Register                                         | 2-27         |

| 2-13         | Special Code Combination in Timing-Band          |              |

|              | Read Circuit                                     | 2-28         |

| 2-14         | Special Amplifiers                               | 2-28         |

| 3-1          | Storage Drug Chewing Computer                    |              |

| 3-1          | Storage Drum Showing Computer<br>Characteristics | 3-58         |

| 3-2          | Word-Storage Pattern                             | 3-50         |

| 3-3          | Timing Band, Expanded View                       | 3-59         |

| 3-4          | Phase Modulation Coder                           | 3-60         |

| 3-5          | Phase Modulated Waveshapes                       | 3-60         |

| 00           | indbo modulatora matobhapob                      |              |

| 4-1          | Search Step of Basic Operation Cycle             | 4-3          |

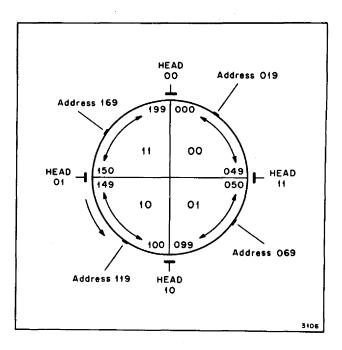

| 4-2          | Drum Quadrants                                   | 4-6          |

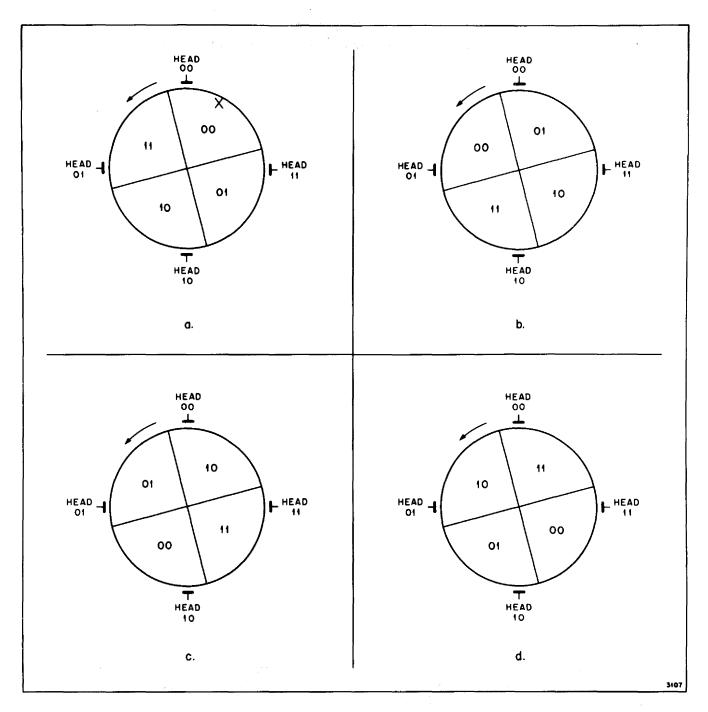

| 4-3          | Drum Quadrants under Fast-Access Héads           | 4-9          |

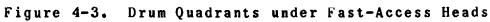

| 4-4          | Quarter Addition of HS2 FF Inputs                | 4-12         |

| 4-5          | Staticize Step                                   | 4-16         |

| 4-6          | Timing of Basic Operation Cycle                  | 4-25         |

| 4-7          | Execution Step of H(60) Instruction              | 4-28         |

| 4-8          | Add Instruction                                  | 4-35         |

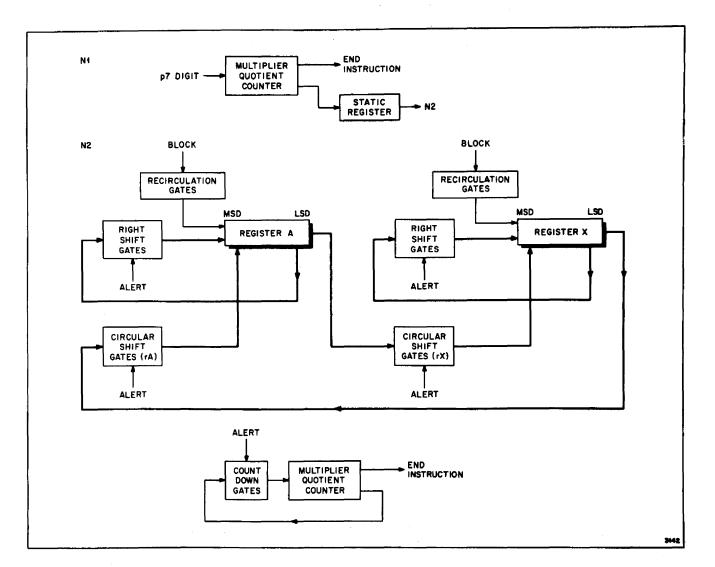

| 4-9<br>4-10  | Multiplication Process                           | 4-42         |

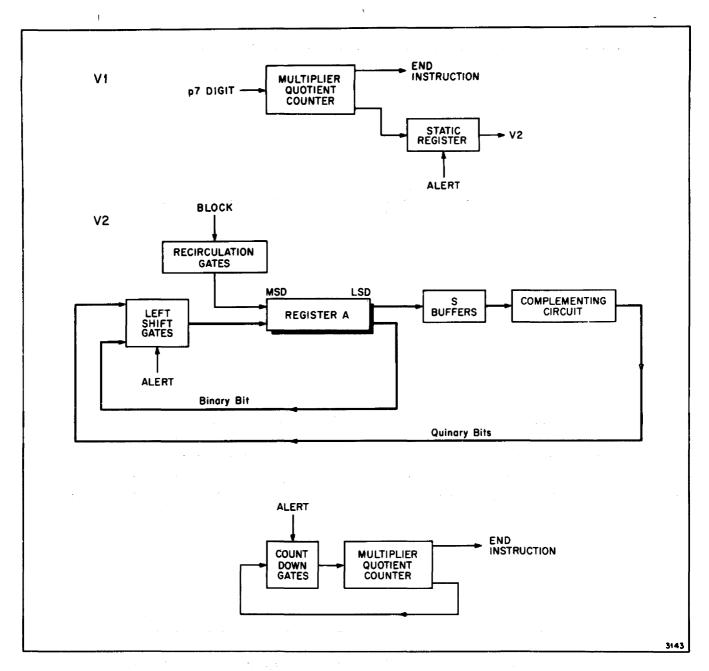

| 4-10<br>4-11 | Multiply Instruction                             | 4-44<br>4-50 |

| 4-11         | Division Process<br>Dl Step of Division          | 4-50         |

| 4-12         | D2 Step, <u>OR</u> Phase                         | 4-56         |

| 4-13         | D2 Step, <u>OR</u> Phase                         | 4-57         |

| 4-15         | D3 Step                                          | 4-60         |

| 4-16         | Keyboard Input Operation                         | 4-73         |

|              |                                                  |              |

| 5-1          | The 25(B) Transfer Instruction                   |              |

|              | ((m) > rA)                                       | 5-16         |

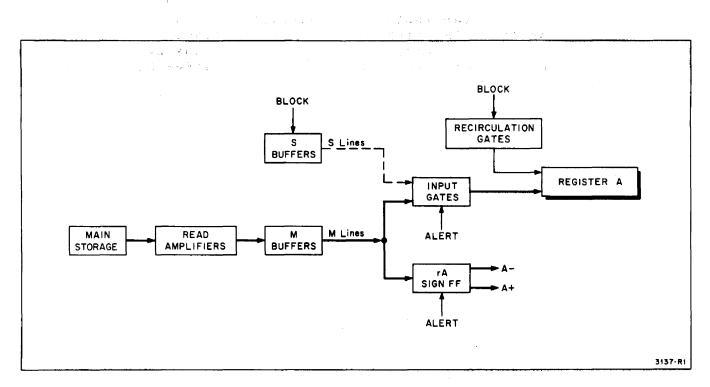

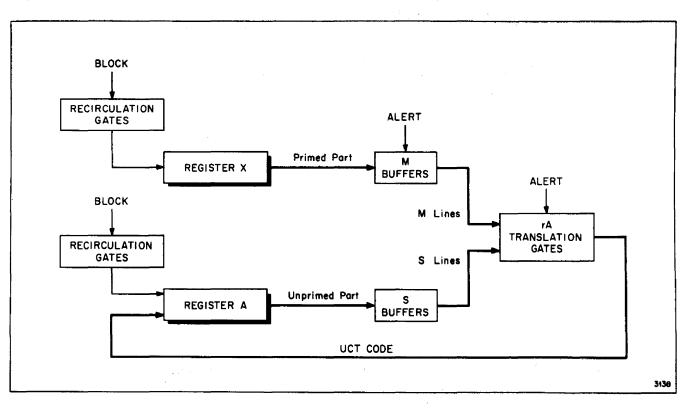

| 5-2          | The 12(G) Translate Instruction                  | 5-16         |

|              | (Card Code to UCT Code)                          | 5-10         |

Figure

| <b>F</b> 0   |                                                      |              |

|--------------|------------------------------------------------------|--------------|

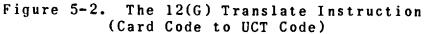

| 5-3          | The 17(R) Translate Instruction (UCT Code            |              |

|              | to Card Code)                                        | 5-17         |

| 5-4          | The 20(P) Superimpose Instruction                    | 5-17         |

| 5-5          | The 35(E) Extract Instruction                        | 5-18         |

| 5-6          | The 32(N) Right-Shift Instruction                    | 5-18         |

| 5-7          | The 37(V) Left-Shift Instruction                     | 5-19         |

| 5-8          | The 62 (ZS 1) Zero-Suppress Instruction              | 5-20         |

| 5-9          | The 82(Q) Equality-Comparison Instruction            | 5-21         |

| 5-10         | The 87(T) Comparison Instructions                    | 5-21         |

| 5-11         | Second Stage of $22(I 11)$ , $27(I 21)$ , and        |              |

|              | 42(I 31) Test Instructions                           | 5-22         |

|              |                                                      | ( 7)         |

| 6-1          | Covalent Bond in a Pure-Germanium Crystal            | 6 - 71       |

| 6-2          | Hole Creation and Movement                           | 6 - 71       |

| 6-3          | N-Type Germanium                                     | 6 - 71       |

| 6-4          | P-Type Germanium                                     | 6-71         |

| 6-5          | Charges in N-Type and P-Type Germanium               | 6-72         |

| 6-6          | Junction Diode with Symbol                           | 6-72         |

| 6-7          | Voltage Gradients as Potential Hills                 | 6-72         |

| 6-8          | Biasing Connections                                  | 6-72         |

| 6-9          | Diode Characteristic and Test Circuit                | 6-73         |

| 6-10         | Junction Diode Used as Rectifier                     | 6-73         |

| 6-11         | High and Low Information Pulses                      | 6-73         |

| 6 - 12       | Gate and Buffer Circuits                             | 6-74         |

| 6 - 13       | Junction Transistors                                 | 6-74         |

| 6 - 14       | Application of Bias Potentials                       | 6-75         |

| 6-15         | Common-Base Transistor Amplifier                     | 6-75         |

| 6-16<br>6-17 | Common-Base Class A Amplifier Stage                  | 6-76         |

| 6 - 17       | Common-Emitter Transistor Amplifier                  | 6-76         |

| 6-19         | Transistor Symbols<br>Typical Transistaniand Cimenia | 6-76         |

| 6-20         | Typical Transistorized Circuit                       | 6-76<br>6-77 |

| 6-21         | Clock, Block Diagram                                 | 6-79         |

| 6-22         | Phase Detector Signals<br>Core Flipping Points       | 6-80         |

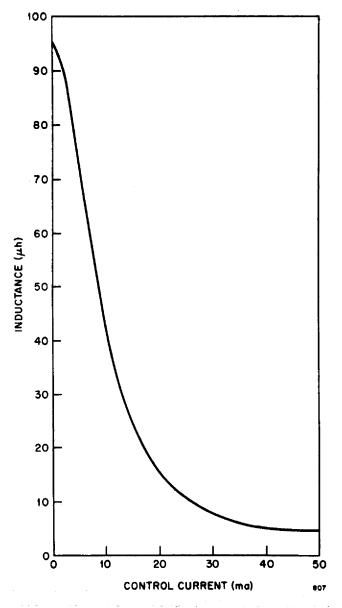

| 6-23         | Increductor Characteristics                          | 6-80         |

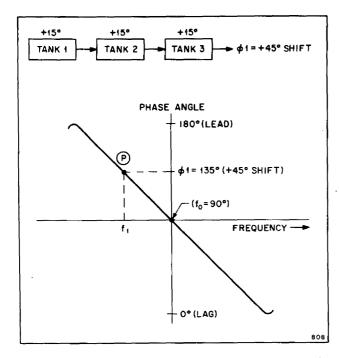

| 6-24         | Phase Response of Three Cascaded Tank                | 0-00         |

| 0-24         | Circuits with No Phase Control                       | 6-81         |

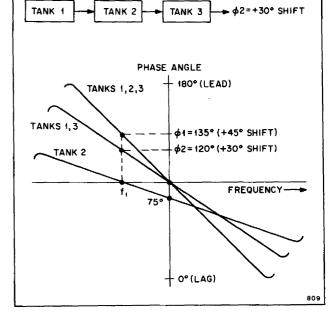

| 6-25         | Partial Phase Correction                             | 6-81         |

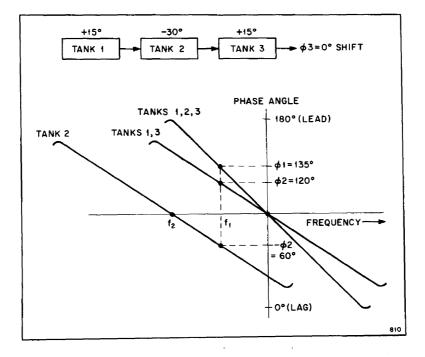

| 6-26         | Full Phase Correction                                | 6-81         |

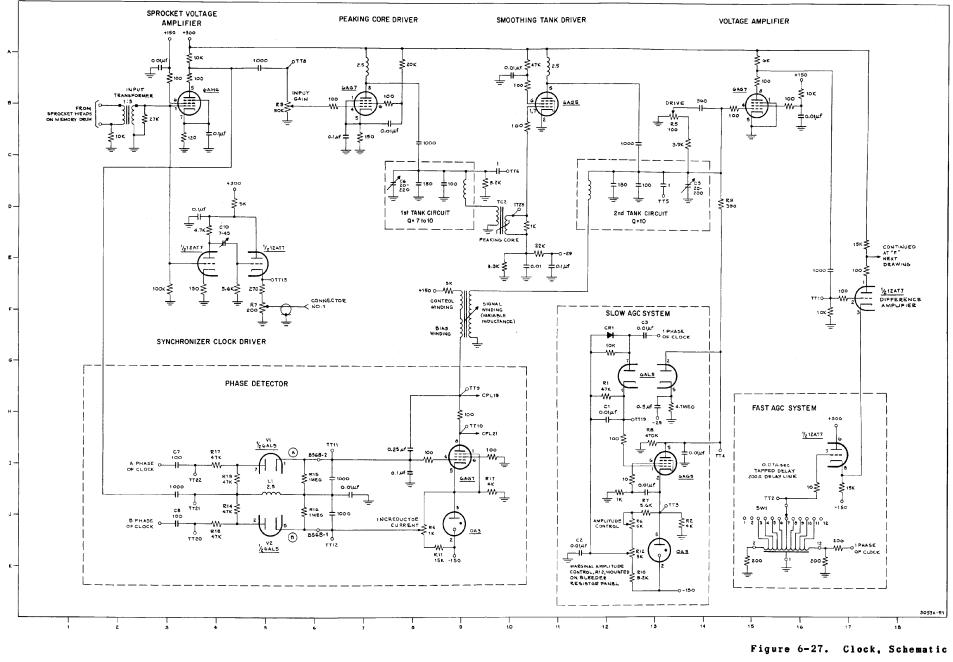

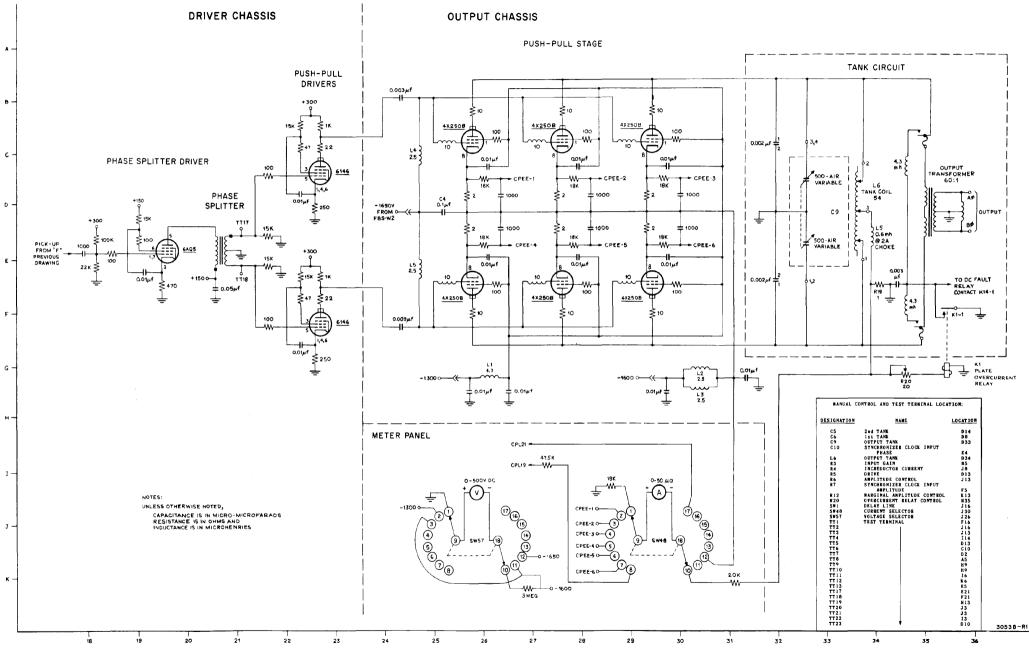

| 6-27         | Clock, Schematic                                     | 6-83         |

| 6-28         | Hysteresis Loop Development                          | 6-87         |

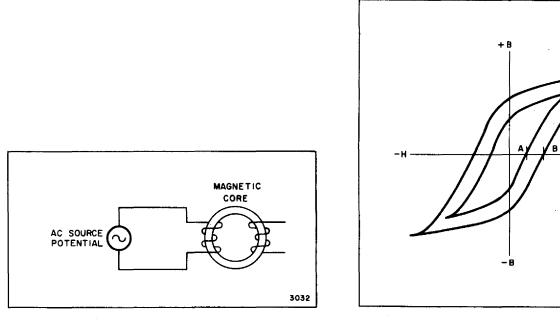

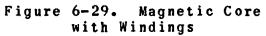

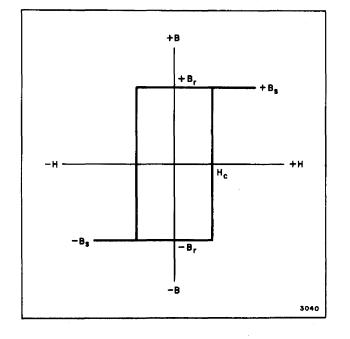

| 6-29         | Magnetic Core with Windings                          | 6-88         |

| 6-30         | Typical Hysteresis Loops                             | 6-88         |

| 6-31         | Idealized Hysteresis Loop                            | 6-88         |

| 6 - 32       | Hysteresis Loop for Nonreactive Coil                 | 6-88         |

| 6-33         | Complementing Magnetic Amplifier                     | 6-89         |

| 6-34         | Noncomplementing Magnetic Amplifier                  | 6-90         |

| 6-35         | Arithmetic Register                                  | 6-91         |

| 6-36         | Storage Unit                                         | 6-91         |

| 6-37         | Recording Method                                     | 6-92         |

| 6-38         | Write-Transformer Circuit                            | 6-92         |

|              | HILV REALERED VERVELD                                |              |

| Figure | Title                                    | Page  |

|--------|------------------------------------------|-------|

| 6-39   | Write-Transformer Package Waveforms      | 6-92  |

| 6-40   | Read-Write Circuit Interconnections      | 6-93  |

| 6-41   | Write-Pedestal Circuit                   | 6-93  |

| 6-42   | Read-Amplifier Circuit                   | 6-94  |

| 6-43   | Read Flip-Flop Circuit                   | 6-94  |

| 6-44   | Probe and Clear Generator Circuits       | 6-95  |

| 6-45   | Read-Circuit Waveforms                   | 6-96  |

| 6-46   | Matrix-Selector Circuit                  | 6-96  |

| 6-47   | Switch-Driver Circuit                    | 6-97  |

| 6-48   | Power Control Circuits, Block Diagram    | 6-98  |

| 6-49   | A-C Distribution Circuits, Block Diagram | 6-99  |

| 6-50   | Power Control Circuits, Schematic        | 6-101 |

| 6-51   | Typical Power Supply, Block Diagram      | 6-103 |

| 6-52   | Holding Up Circuit                       | 6-103 |

| 6-53   | VST Equivalent Circuit                   | 6-103 |

| 6-54   | Circuit Characteristic Curve             | 6-104 |

| 6-55   | Phase Relationships                      | 6-104 |

| 6-56   | Basic Voltage-Stabilizing Transformer    | 6-105 |

| 6-57   | D-C Supply, 100 Volts                    | 6-105 |

| 6-58   | D-C Supplies, Block Diagram              | 6-106 |

| 6-59   | Voltage Monitor Circuit                  | 6-107 |

| 6-60   | Typical Fuse Fault Circuit               | 6-109 |

| 6-61   | Standard Symbols                         | 6-110 |

# LIST OF TABLES

| Table | Title                                            | Page |

|-------|--------------------------------------------------|------|

| 1-1   | Characteristics of the New Univac ${f R}$ System | 1-10 |

| 1-2   | Card Code Combinations                           | 1-13 |

| 3-1   | Translating from Remington Rand to UCT Code      | 3-14 |

| 3-2   | Translating from UCT to Remington Rand Code      | 3-15 |

| 3-3   | Conditional Transfer Flip-Flop Gate Inputs       | 3-27 |

| 3-4   | MQC Countdown Gates                              | 3-39 |

| 3-5   | Input-Output Sentinel Chart                      | 3-49 |

| 3-6   | Band Selection Flip-Flops                        | 3-55 |

| 4-1   | Oddness and Evenness of Biquinary Combinations   | 4-7  |

| 4-2   | Head Selection                                   | 4-7  |

| 4-3   | Instruction Code Combinations                    | 4-22 |

| 4 - 4 | Keyboard Encoder                                 | 4-70 |

| 5-1   | State of Conditional-Transfer Flip-Flop After    |      |

|       | Comparison Operation                             | 5-13 |

3

#### SECTION I

#### INTRODUCTION

The purpose of this manual is to provide the reader with the fundamentals of computer logic and to apply these fundamentals to the theory of operation of the New Univac **R** Type 7900 Central Processor. Similar manuals have been prepared to acquaint the reader with the operating principles of the peripheral equipment of the system: the High-Speed Printer (or HSP); the Card-Sensing Punch Unit, 90 Column, or read-punch unit (RPU); and the Card-Sensing Unit, 90 Column, or card reader.

It is not within the scope of this manual to detail all of the logical operations carried out by the central processor. Section II, however, enables the reader to grasp the basic concepts of logical circuitry. Sections III and IV apply the knowledge of logical circuitry to detailed explanations of computer circuits and some of the more complex functions of the processor. Section V explains the operation of all of the types of instructions, except those few which control the input-output devices. In section VI, the basic theory of the major electronic circuit components, diodes, transistors, and magnetic amplifiers, is explained to enable the reader to analyze the circuits using these components.

## 1-1. FUNCTIONAL DESCRIPTION

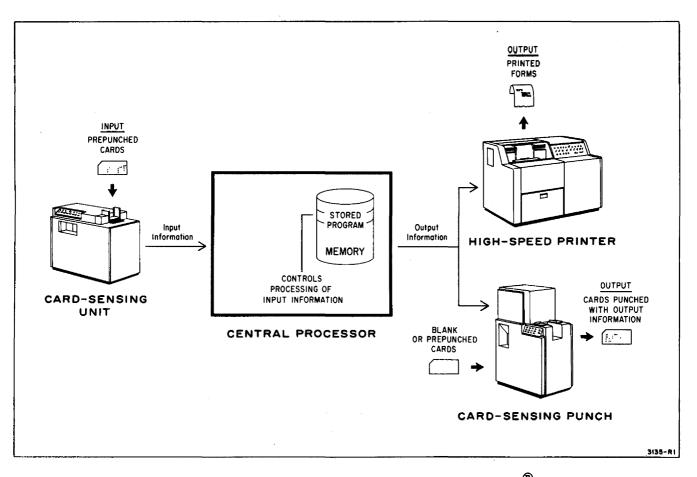

The New Univac  $^{(\mathbf{R})}$  system is composed of the processor, the card reader, the read-punch unit, and the printer.

The first step in processing is to store the program for the problem. Punched tabulating cards, bearing input information to be processed, then are placed in the card reader (figure 1-1). The card reader reads or senses the information represented by punched holes on the cards. The information is transferred from the card reader to the processor where the program stored previously in the magnetic storage drum controls the processing and computation of the input information.

A program, compiled by a programmer, is a sequence of instructions punched on tabulating cards. The instructions on the program cards are read by the card reader and transferred to the computer storage unit. The program automatically specifies and controls the operations required to solve a given problem. The computed results or data processed in the processor are sent, as output, to the printer and to the read-punch unit. The output information may be printed on paper by the printer or punched on other tabulating cards in the read-punch unit or both. The cards placed in the input bin of the read-punch unit can be either prepunched with information or blank. In either case the input card is read at a read station before being punched with computer output at the punch station. The card is read again for checking purposes at a second read station and transferred to one of two output stackers.

Figure 1-1 shows a typical functional arrangement of the system. Variations of this arrangement are possible through program control. The programming and applications manuals on the system cover the many other possible arrangements. Table 1-1 lists the major characteristics of the New Univac ® system. Complete information on the input-output units can be found in the manuals which accompany these equipments.

## 1-2. PROCESSOR

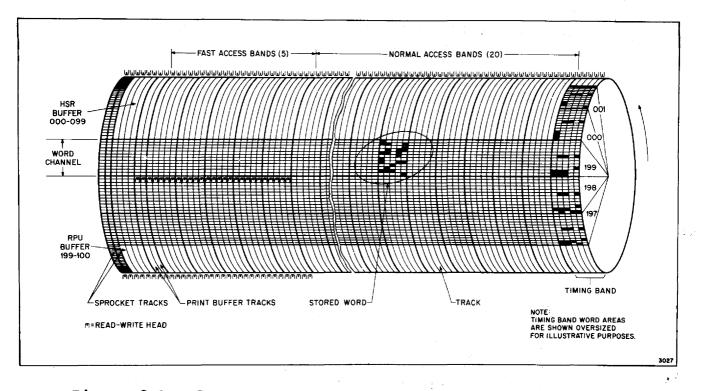

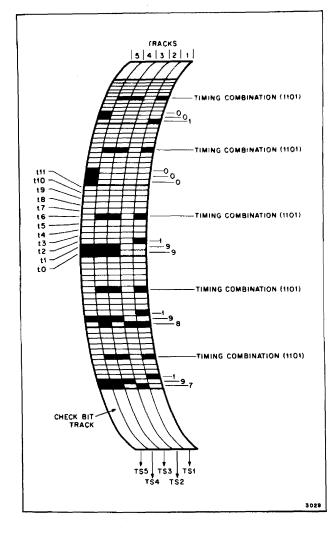

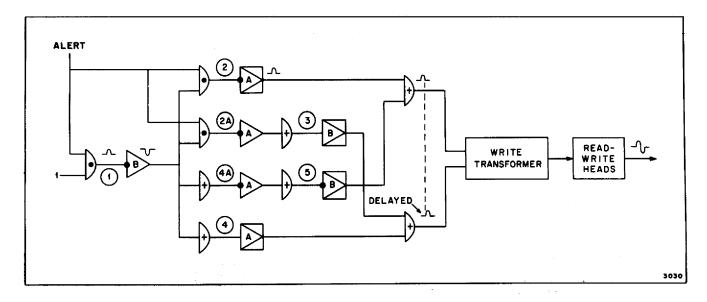

The processor consists of the computing and processing circuitry, the storage drum, the operator's control panel and keyboard, and the system power supplies. The storage device is a cylindrical, magnetically coated drum with a capacity of 5000 computer words. In addition to this 5000-word capacity, which is known as main storage, other areas of the drum are set aside for timing purposes and input-output buffer storage. The buffer storage areas store information coming from or going to the input-output devices. Buffer storage enables the slower input-output devices to keep pace with the faster speeds of the processor and also allows the units of the system to operate in parallel.

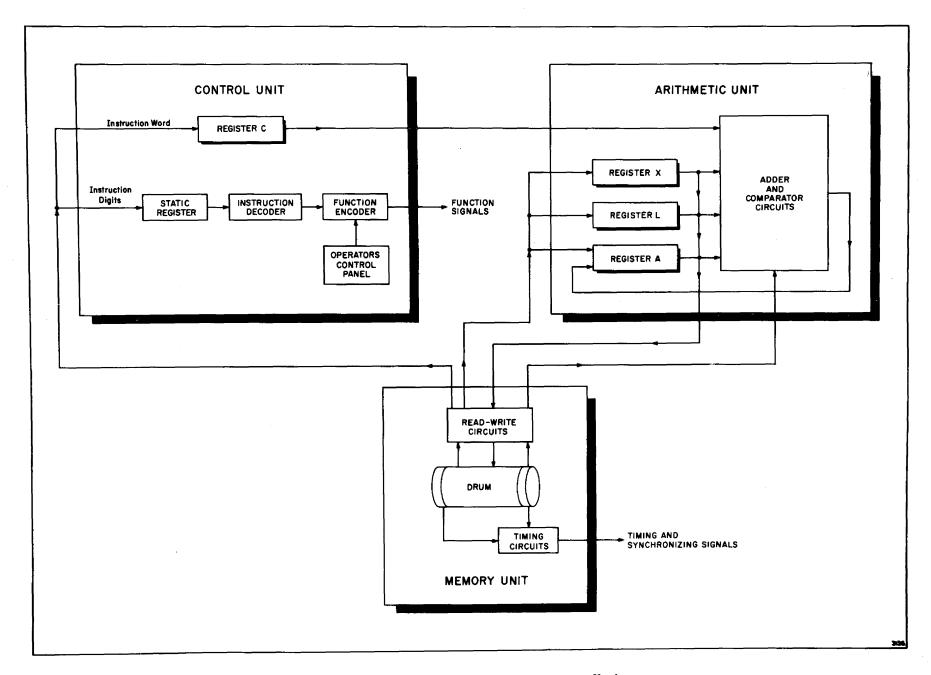

All of the computing and processing circuitry explained in this manual is compactly contained on printed wiring boards, known as packages, within the processor cabinet. Arithmetic, control, and processing operations take place within the magnetic amplifier, transistor, diode, and miscellaneous circuitry on these packages. The clock circuits, which synchronize the operation of the magnetic amplifier components, and most of the system power supplies also are located in the processor cabinet. Three of the four logical units necessary to a dataprocessing system are contained in the processor. These units, shown in figure 1-2, are: the control unit, the storage unit and the arithmetic unit. A general description of each of the three units follows; detailed descriptions of the units can be found in section III.

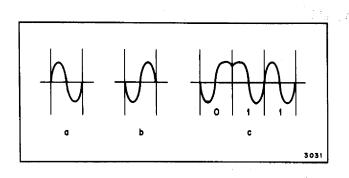

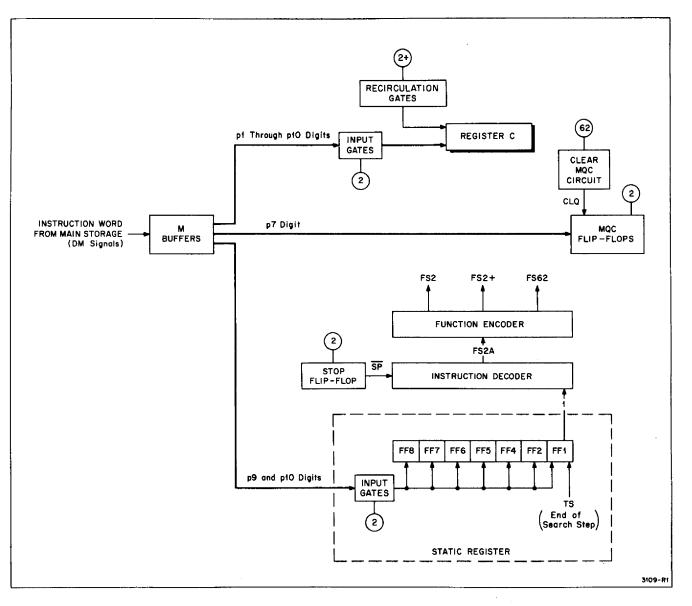

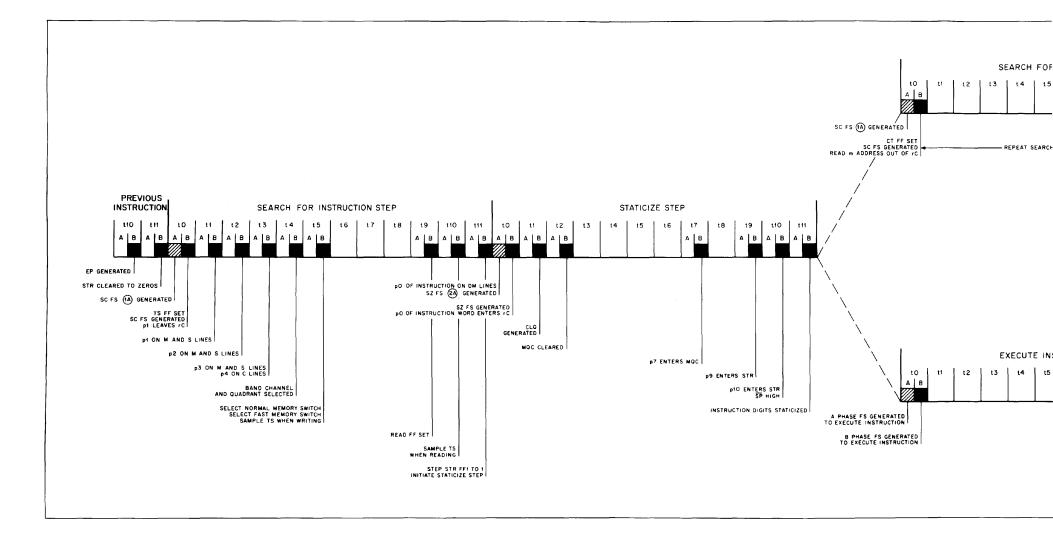

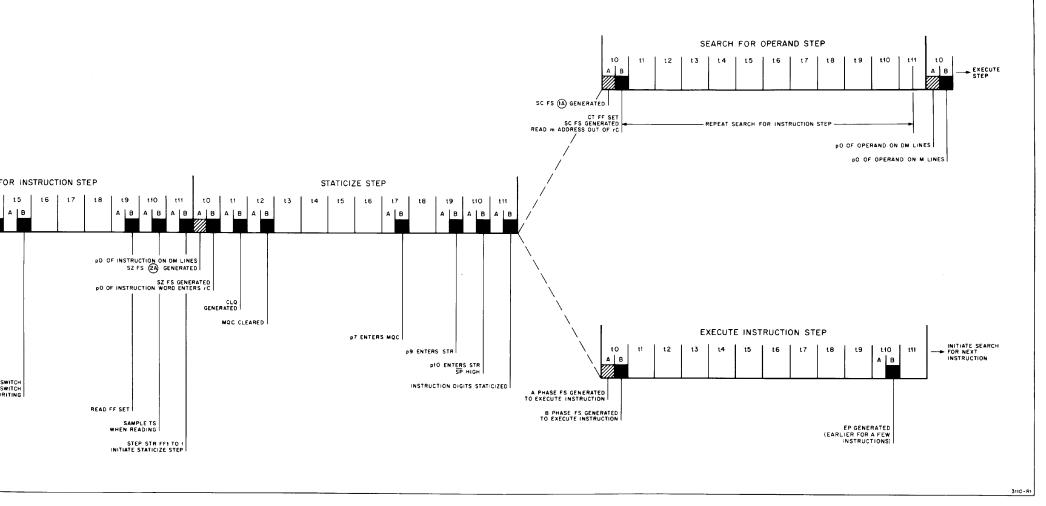

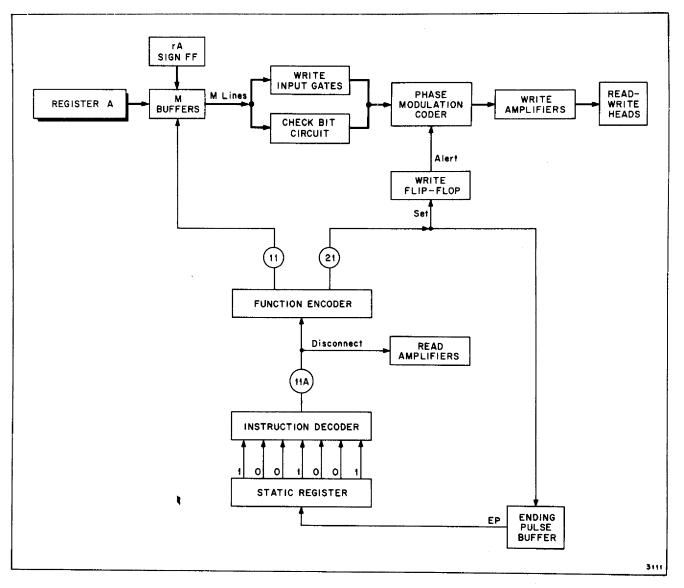

1-3. CONTROL UNIT. The control unit controls all of the operations of the system including the input-output unit. The major components of the control unit are: register C, the static register, the instruction decoder, the function encoder, and the operator's control panel.

Complete instruction words read from storage are stored in register C. Parts of these words are compared with storage addresses in the adder and comparator circuits in order to locate stored information or other instruction words. The two instruction code digits of the instruction word stored in register C are also stored in the static register. These digits are interpreted by the instruction decoder and converted into a function signal. This function signal is converted into a number of other function signals by the function encoder. The function signals control various computer circuits which cause the stored instruction to be executed.

The operator's control panel contains pushbutton switches and indicators which enable the operator to control manually the automatic operation of the system. Abnormal conditions in any of the four units also are indicated at the operator's panel. A keyboard on the panel enables the operator to type information into the processor or to alter the stored program.

1-4. STORAGE UNIT. The main component of the storage unit is the magnetic storage drum. Instructions or data are stored magnetically on the drum. Instructions are read from the drum to control calculations or processing; data is read from the drum to be operated upon by the instruction. The read-write circuits of the drum control reading from or writing onto the drum. Permanently recorded signals on the drum go to the timing circuits which synchronize and time all computer operations.

1-5. ARITHMETIC UNIT. Although the arithmetic unit has many components, the most important components are the three arithmetic registers and the adder and comparator circuits. All arithmetic and comparison operations are performed in the arithmetic unit. Each of the three registers, A, L, and X stores temporarily the ten digits of a word, which is usually the operand in an arithmetic instruction. The operands are operated upon in the adder and comparator circuits, and the results are returned to one of the three registers.

#### **1-6.** CARD READER

The card reader reads information from punched input cards and transfers the information to the processor at a maximum rate of 450 cards per minute. The input cards are placed in the input bin. From the input bin, cards are automatically transported through the read stations to the output stackers. Each card is read by brush sensing at two read stations. The second read station enables the programmer to check the accuracy of the information read at the first read station. After the two readings the cards are transported to one of three output stackers. The program determines which stacker is used.

# 1-7. READ-PUNCH UNIT

The read-punch unit also reads information from input cards, but it is not a normal method of input to the system. The cards inserted into the read-punch input bin are usually blank cards or cards punched with a small amount of information. Under the control of the program the card is read by pin sensing at the first read station and is sent to the punch station where processed or computed information is punched into the card. The card moves to a second read station where the information on the card originally and the information added by punching are checked. The card is then transferred to one of two output stackers as determined by the program. The read-punch unit reads and punches cards at a rate of 150 per minute.

# **1-8.** PRINTER

The information computed by the processor can be printed by the printer on many types of continuous forms at a speed of 600 lines per minute. Each line of print can contain a maximum of 130 characters. The number of spaces between lines is specified by the program. The printer contains 65 print wheels. Each wheel contains all of the characters available for printing. All of the characters to be printed on any one line are printed during the time necessary for one complete revolution of the print wheels. Under control of the program the paper is spaced before the printing of each line.

#### **1-9.** COMPUTER LANGUAGE

The purpose of this section is to familiarize the reader with the basic language of the computer.

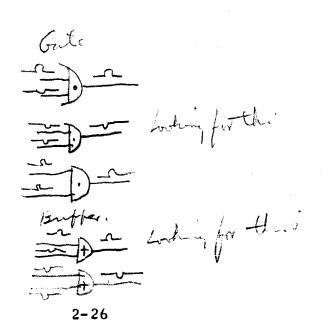

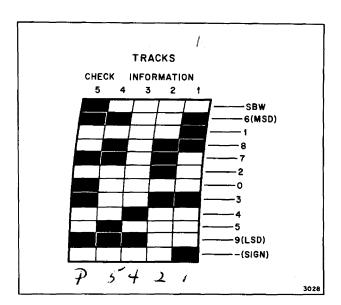

# 1-10. COMPUTER WORDS

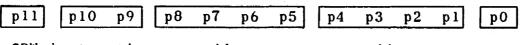

Information is processed by the computer in units known as computer words. A computer word is a group of digits constituting the smallest unit of information which can be processed or stored. Each computer word, which consists of ten digits and a sign, is presented in a space 12 digits long. The twelfth position is used as the spacing between words and is included as part of the word. Each digit of a word consists of four bits (refer to section 1-14). A bit is a binary character (either 0 or 1) which, when combined with other bits in a certain order, can represent a numeric digit. The bits of a digit are transferred in parallel and the digits themselves are transferred in series. To facilitate identification of every digit of a computer word, the following method of naming the digits is used throughout this manual:

#### Computer Word

Position Number Digit

p10 **pll** p9 p8 p7 p6 р5 p4 р3 SBW 9 8 10 7 6 5 4 3

In this method, the 12 digit positions of a computer word are designated pO through pll. The digits of a word are transferred throughout the computer with the least-significant digit (LSD) first, which is the reason for placing digit 1 or pl at the right end of the word and the most-significant digit (MSD), digit 10 or pl0, at the left end of the word.

Computer words are divided into two distinct groups: data words and instruction words. Data words contain information to be processed; instruction words contain instructions and addresses of data words to be used in the instruction. Instruction words, therefore, control processing and computations; data words are part of the information processed or computed. The difference between the data word and instruction word is a programming consideration only. The computer does not differentiate between the two types.

1-11. DATA WORD. A data word consists of a number of information digits which are to be processed or computed. The 12 digit positions of a data word contain ten digits, an algebraic sign, and a space between words (SBW). In the computer word given as an example above, the pO digit position contains the sign of the data word; the pl through plO digit positions contain the numeric digits of the word (even though they may be zero digits); and the pll digit position is the space between words (SBW) and contains a zero digit. The plO digit is usually the most significant of the ten numeric digits; the pl digit is the least significant of the ten digits.

p2

2

**p1**

1

рO

0

1-12. INSTRUCTION WORDS. An instruction word consists of ten numeric digits and a space between words. The pO digit of an instruction word is always a zero. The digits of an instruction word are divided into three groups as shown:

Instruction Word

SBW instruction m address c address code

Digits plO and p9 are the instruction code digits. Every instruction given by the programmer consists of two digits. For example, when the programmer wishes to insert an add instruction into the program he places the digits 7 and O in the plO and p9 digit position of the instruction word.

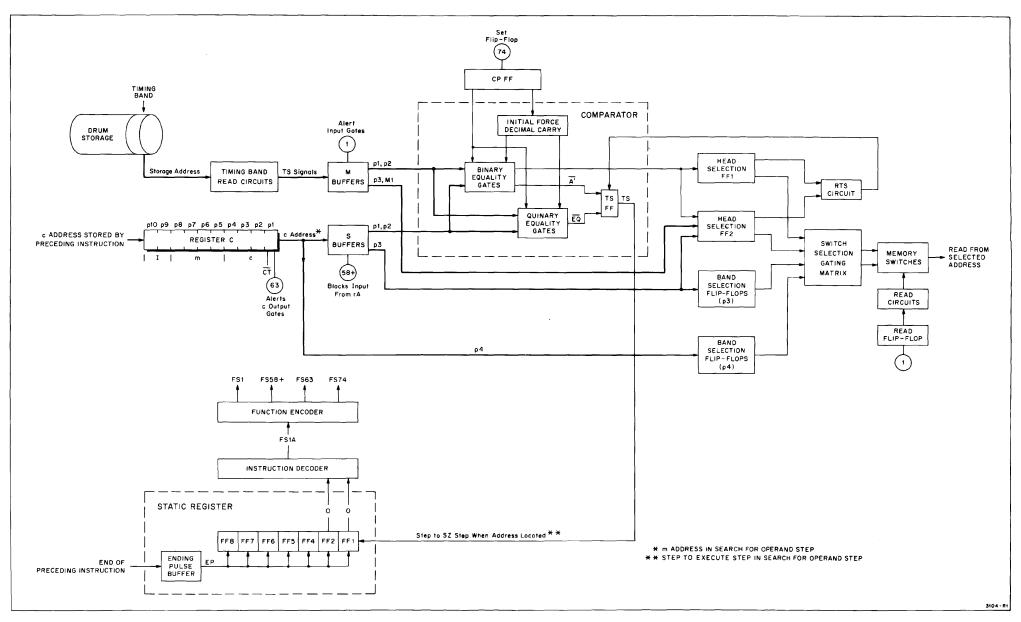

Digits p8 through p5 comprise the m address, which is the storage address of the operand to be used in executing the instruction. For example, when the programmer inserts an addition instruction into the program the operand must be read from the m address in the processor storage before the addition can take place. The programmer inserts the numerical address of the term which is to be read in the m address position of the instruction word. Digits p4 through p1 make up the c (control) address, which is the address of the next instruction. To construct a continuous program, in which the programmer programs one instruction after another in the desired order, each instruction word must contain the address in the processor storage of the next instruction word to be processed. The address of this next instruction word is known as the c address. The unused sign position of the instruction word always contains a zero.

# 1-13. SYSTEM CODES

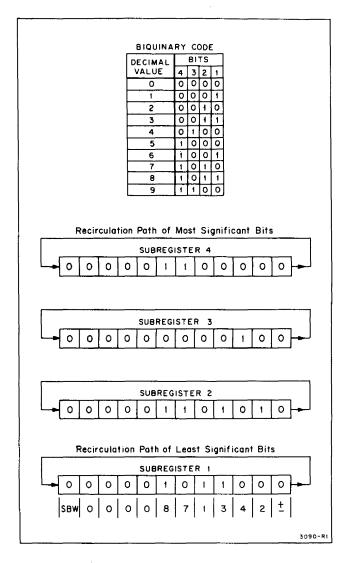

The computer employs two types of coding for numeric (and alphabetic) information processed within the system: computer (UCT) code and Remington Rand (RR) card code. The punched tabulating cards used as the main method of input and output of the system are punched in the card code, in which digits are represented by six bits. The information in card code on the input cards is read from the cards under control of the program and transferred to the translator circuits of the processor. These circuits translate the six-bit card code into four-bit UCT code for internal use in the processor. When processing of the input information is complete, the four-bit UCT code is translated back into six-bit card code which can be punched on the output tabulating cards. 1-14. UCT CODE. The UCT code is a biquinary, four-bit code. Decimal digits O through 9 are represented as shown:

| · · · · · · · · · · · · · · · · · · · | v 1     | 5 C      |          |          |     |

|---------------------------------------|---------|----------|----------|----------|-----|

| Decimal                               | Bit     |          |          |          | 1   |

| Value                                 | 4       | 3        | 2        | 1        |     |

| 0                                     | 0       | 0        | 0        | 0        | a   |

| 1                                     | 0       | 0        | 0        | 1        | b   |

| 2                                     | 0       | 0        | 1        | 0        |     |

| 3                                     | 0       | 0        | 1        | 1        |     |

| 4                                     | 0       | 1        | 0        | 0        |     |

| 5                                     | 1       | 0        | 0        | 0        |     |

| 6                                     | 1       | 0        | 0        | 1        |     |

| 7                                     | 1       | 0        | 1        | 0        |     |

| 8                                     | 1       | 0        | 1        | 1        |     |

| 9                                     | 1       | 1        | 0        | 0        |     |

| Decimal<br>Value                      | 5<br>De | 4<br>cin | 2<br>1a1 | l<br>Wei | ght |

The four bits of this code are assigned weights from left to right of 5, 4, 2, and 1. For example, the decimal digit 4 is 0100, or 0 + 4 + 0 + 0. Examination of the code shows that the last three bits or lowest order bits of the digits 0 through 4 are repeated for the digits 5 through 9. The most significant bit of the combinations determines whether the digit lies in the 0 through 4 range or the 5 through 9 range. In the sign position of the word the 0000 combination denotes a + sign, and the 0001 combination denotes a minus sign.

<sup>a</sup> Represents + when used in the sign position, p0.

<sup>b</sup> Represents - when used in the sign position, pO.

1-7

$q \sim -r$

Six non-numeric code combinations in UCT code are available to the programmer. The non-numeric codes also can be processed through the computer but no value or weights are assigned to the bits of these combinations. These special codes are represented as shown:

| Code |

|------|

| 0101 |

| 0110 |

| 0111 |

| 1101 |

| 1110 |

| 1111 |

The method for manually inserting these non-numeric combinations into the computer is described in section 4-48.

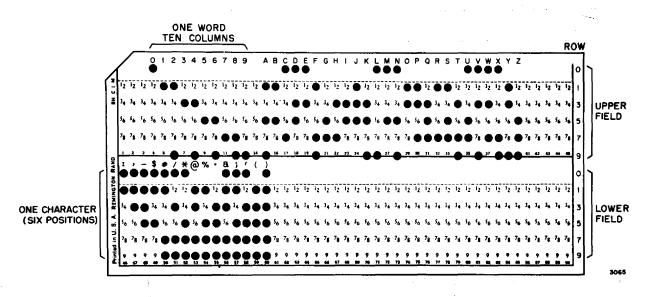

1-15. REMINGTON RAND CARD AND CODE. The Remington Rand card shown in figure 1-3 is divided into two parts: the upper field and the lower field. Each field has six rows of punching positions and is 45 columns wide. Because there are 45 columns in each of the two fields, this card is referred to as a 90-column card. The 90 columns are numbered in the figure from 1 through 45 for the upper field and from 46 through 90 for the lower field. Each card, therefore, has 540 punching positions (90 columns times 6 rows).

The six rows of the upper field and the six rows of the lower field are numbered 0, 1, 3, 5, 7, and 9 as shown at the right of the card. In the figure, the punch in the 0 row of column 4 indicates a decimal value of 0, and a single punch in row 1 of column 2 indicates a decimal value of 1. Examination of table 1-2 shows that 0 and all of the odd decimal numbers are indicated by a single punch in the proper row. The even numbers are indicated by two punches: one punch in one of the 1, 3, 5, or 7 rows and also one punch in the 9 row of the same column. For example, punches in rows 1 and 9 of a column

represent a decimal 2, punches in rows 3 and 9 of a column represent a 4. Because the 1, 3, 5, 7, and 9 rows can indicate an odd or even number, depending upon whether or not there is also a punch in the 9 row of the same column, each of the 540 punch positions is marked with a notation  $(1_2, 3_4, \text{ etc.})$  which indicates the two possibilities.

Table 1-2 lists the decimal values, the rows to be punched in a column to represent each decimal value, and the bit-codes of the various punched-hole patterns. For example, if a hole is punched in row 0 of a column, the LSB of the card code is a 1 bit, or if a hole is punched in row 9, the MSB of the card code combination is a 1 bit. The least significant bit of the card code refers to row 0, the next lowest order bit refers to row 1 and so forth. A punched hole represents a 1 bit; no hole represents a 0 bit.

1

Table 1-1. Characteristics of the New Univac  ${}^{igodold{R}}$  System

.....

۴.

Input-output characteristics are listed in the individual inputoutput manuals.

| STRUCTIONS |                                                                                                                                                                                                                                                                                                                     |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | ilable for the programmer.<br>structions.)                                                                                                                                                                                                                                                                          |

|            | Translate                                                                                                                                                                                                                                                                                                           |

| 8          | Shift                                                                                                                                                                                                                                                                                                               |

| scellaneou | Input Output<br>s                                                                                                                                                                                                                                                                                                   |

| HMETIC SPE | EDS                                                                                                                                                                                                                                                                                                                 |

|            | roseconds<br>ion of two 10-digit numbers)                                                                                                                                                                                                                                                                           |

| (subtr     | roseconds<br>action of two 10-digit<br>s)                                                                                                                                                                                                                                                                           |

| 119 mi     | croseconds (minimum)<br>icroseconds (maximum)                                                                                                                                                                                                                                                                       |

|            | croseconds (minimum)<br>icroseconds (maximum)                                                                                                                                                                                                                                                                       |

| PUTER WORD | \$                                                                                                                                                                                                                                                                                                                  |

| sition     | it positions (ten digit po-<br>s, one sign position and<br>e-between-words position)                                                                                                                                                                                                                                |

| sition     | it positions (ten digit po-<br>s, unused sign position, and<br>e between words)                                                                                                                                                                                                                                     |

| RMATION FL | 0W                                                                                                                                                                                                                                                                                                                  |

| Words      | Serial-parallel                                                                                                                                                                                                                                                                                                     |

| Speed      | 707,000 digits per second                                                                                                                                                                                                                                                                                           |

| CODES      |                                                                                                                                                                                                                                                                                                                     |

| Card       | Six bit Remington<br>Rand code                                                                                                                                                                                                                                                                                      |

|            | ons is ava<br>ypes of in<br>scellaneou<br>HMETIC SPE<br>85 mic<br>(addit<br>85 mic<br>(subtr<br>number<br>119 mi<br>1785 m<br>425 mi<br>1955 m<br>425 mi<br>1955 m<br>PUTER WORD<br>12 dig<br>sition<br>a spac<br>12 dig<br>sition<br>a spac<br>12 dig<br>sition<br>a spac<br>RMATION FL<br>Words<br>Speed<br>CODES |

<u>5</u>4

1990 1996

| •••••••••••••••••••••••••••••••••••••• | SI                                                     | ORAGE                                                                               |

|----------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------|

| Total Ca                               | pacity                                                 | 5000 words (main storage)                                                           |

| Capacity                               | per band                                               | 200 words                                                                           |

| Total nu                               | umber of bands                                         | 25                                                                                  |

| Normal-a                               | ccess bands                                            | 20 (one head per track)                                                             |

|                                        | acity<br>cess time                                     | 4000 words<br>3400 microseconds, maximum<br>(200 word times)                        |

| Fast-acc                               | ess bands                                              | 5 (4 heads per track)                                                               |

|                                        | acity<br>cess time                                     | 1000 words<br>850 microseconds, maximum<br>(50 word times)                          |

| Speed                                  |                                                        | 17,670 rpm 3. 4.1125, Per Rev,                                                      |

| Timing b                               | and                                                    | Provides channel addresses and<br>synchronizes generation of timing<br>pulses       |

| Sprocket                               | tracks (2)                                             | Provide basic half pulse time<br>frequency for clock                                |

| HSP (pri<br>buffer                     | nter)<br>tracks (2)                                    | Store 13 words, which constitute<br>a printed line, from memory                     |

|                                        | d reader)<br>tracks (4)                                | Store 20 words (two complete<br>input card readings)                                |

|                                        | nd-punch unit)<br>tracks (4)                           | Store 30 words (two complete<br>input card readings and one<br>output card reading) |

|                                        | INPUT                                                  | KEYBOARD                                                                            |

| K e y s                                | O through 9                                            | Signs Plus and minus keys                                                           |

| Non-numeric                            | Typed by simultan<br>eous operation of<br>numeric keys |                                                                                     |

Table 1-1. Characteristics of the New Univac () System (cont)

1

| TIMING          |                                                                                     |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------|--|--|--|--|

| Half pulse time | 0.707 microseconds (time for a signal to<br>be transferred through a magnetic core) |  |  |  |  |

| Pulse time      | l.414 microseconds (time for passage of one digit)                                  |  |  |  |  |

| Word time       | 17 microseconds (time for passage of one word)                                      |  |  |  |  |

6112.3

and the second second

Table 1-1. Characteristics of the New Univac  ${

m I\!\!R}$  System (cont)

a and a second second

|         | <u> </u> |             | 1 |   |     |          |    |   |

|---------|----------|-------------|---|---|-----|----------|----|---|

| Decimal | Value    | Row Punches |   | C | ard | Cod      | es |   |

| 0       |          | 0           | 0 | 0 | 0   | 0        | 0  | 1 |

| 1       |          | 1           | 0 | 0 | 0   | 0        | 1  | 0 |

| 2       |          | 1 + 9       | 1 | 0 | 0   | 0        | 1  | 0 |

| 3       |          | 3           | 0 | 0 | 0   | 1        | 0  | 0 |

| 4       |          | 3 + 9       | 1 | 0 | 0   | 1        | 0  | 0 |

| 5       |          | 5           | 0 | 0 | 1   | Û        | 0  | 0 |

| 6       |          | 5 + 9       | 1 | 0 | 1   | <b>0</b> | 0  | 0 |

| 7       |          | 7           | 0 | 1 | 0   | U        | 0  | 0 |

| 8       |          | 7 + 9       | 1 | 1 | 0   | 0        | 0  | 0 |

| 9       |          | 9           | 1 | 0 | 0   | 0        | 0  | 0 |

Table 1-2. Card Code Combinations

Figure 1-1. Typical Arrangement of New Univac<sup>®</sup> System

Figure 1-2. Central Processor Units

# SECTION II

# LOGICAL CIRCUITRY

# 2-1. INTRODUCTION

This section gives the reader the necessary background for understanding processor operations that are described in later sections of the manual. It also enables him to extract from the logical drawings detailed information not specifically supplied in the manual.

Whenever possible, the description is related to the logical drawings by examples of actual circuits. In certain instances, however, simplified versions of typical logical circuits are described as an introduction to the actual circuits shown on the drawings.

# 2-2. GENERAL

The logical drawings represent the actual processor circuitry in symbolic form. Because most of the processor circuitry consists of magnetic amplifiers and diodes, the logical drawings consist principally of diode and magnetic amplifier symbols connected by lines. Signals are indicated on the drawings by abbreviated reference designations or numbers.

This section explains the meaning of the symbols on the logical drawings and describes how the elements that the symbols represent are used to form the basic processor circuits. It also describes the different types of signals and the way they are represented on the drawings. In addition, the method by which timing signals are generated and used to synchronize operations throughout the processor is described.

Only the logical functions of the circuit elements are described here. The electronic theory and operation of magnetic amplifiers and other circuit elements are described in section VI, Electronic Circuitry.

### 2-3. SIGNAL POLARITY

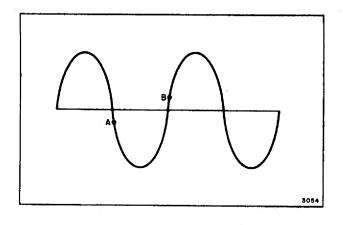

Information is represented in circuitry by high signals or low signals. In this section, high and low signal conditions are distinguished from one another for illustrative purposes as shown in figure 2-la.

A high signal is a definite positive voltage. A low signal is a zero voltage condition. A high signal may be thought of as representing a "pulse condition" and a low signal as representing a "no-pulse condition". Actually, a low signal is not negative, as suggested in figure 2-la. It is illustrated as negative only to avoid the confusion that might result if the zero voltage condition were represented by a straight line.

# 2-4. DIODE CIRCUITS

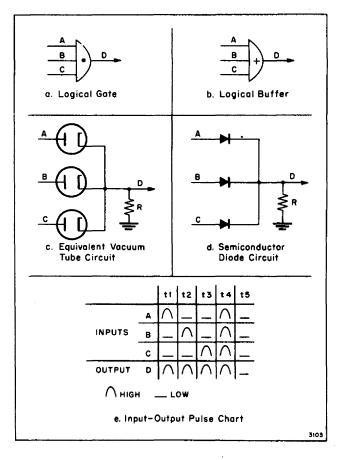

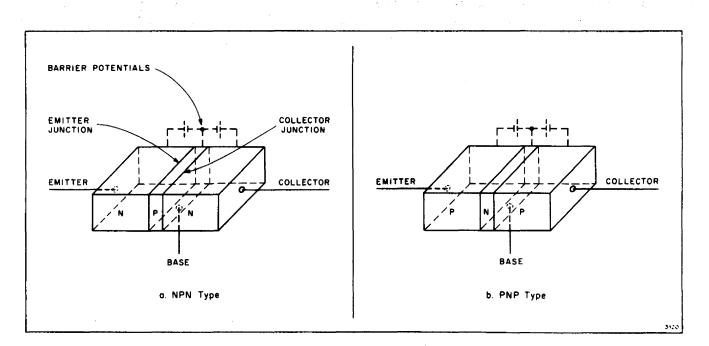

The basic logical element in the circuitry is the diode circuit. A diode circuit is symbolized on a logical drawing as a segment of a circle (figure 2-1b). A diode circuit performs the logical functions of a gate (figure 2-1b, 1), or a buffer (figure 2-1b, 2), or when used as a connecting diode (figure 2-1b, 3), it performs no logical function at all.

Diodes transmit current in one direction but oppose current flow in the opposite direction. They prevent any signal from affecting the source of any other.

# 2-5. GATES

A gate is a circuit designed to produce a prescribed output signal only when every one of its input lines is in a prescribed state. A gate is represented by the diode symbol with a dot in the center. Gating is accomplished when low signals are present on all the input lines (figure 2-lc).

The gate produces a low output signal only when every one of its input lines is low. If one or more of the input signals is high, the output signal is high. High signals cannot be used to perform the gating function since the same high output would be produced whether only one or all of the input signals were high.

#### 2-6. BUFFERS

A buffer is a circuit designed to produce a prescribed output signal when any one of its input lines is in a prescribed state. A buffer is represented by the diode symbol with a plus sign in the center. The buffer output is high when any one of its input lines is high (figure 2-1d).

# 2-7. DIFFERENCES

The difference between a gate and a buffer is a difference of logical definition. The same circuit that serves as a gate for low signals also serves as a buffer for high signals. The important point is that the necessary definitions have been made on the logical drawing. A diode circuit is represented as a gate if its essential function is to perform a gating function; otherwise, it is represented as a buffer or a connecting diode.

# 2-8. CONNECTING DIODE

A connecting diode (figure 2-1b, 3) is represented by a diode symbol with no dot or plus sign in its center. A connecting diode has only one input line and one output line. It has no logical significance other than to prevent the interaction of signals. Connecting diodes are shown on the logical drawings, however, to prevent the magnetic amplifiers that they connect from being confused with another type of magnetic amplifier which does not require a connecting diode (section 2-43).

# 2-9. MAGNETIC AMPLIFIERS

The basic symbol for the magnetic amplifier is a triangle. The point of the triangle indicates the direction of signal flow. Additional notation shows amplifiers as belonging to one of two electronic categories, and one of two logical categories.

#### 2-10. ELECTRONIC DIFFERENCES

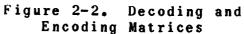

A central sine-wave clock circuit supplies power pulses to all the magnetic amplifiers. The magnetic amplifiers retime and reshape the input signals. Magnetic amplifiers can be divided electronically into two groups: those that receive A-phase power pulses, and those that receive B-phase power pulses.

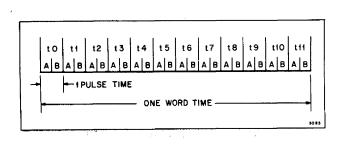

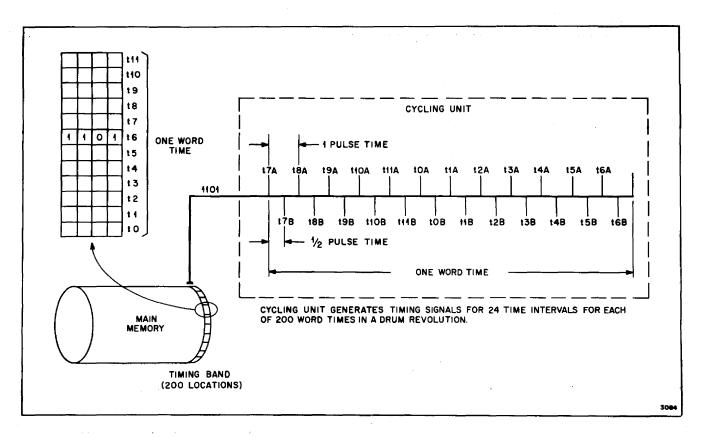

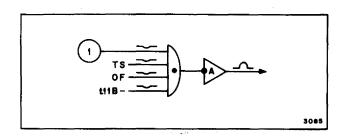

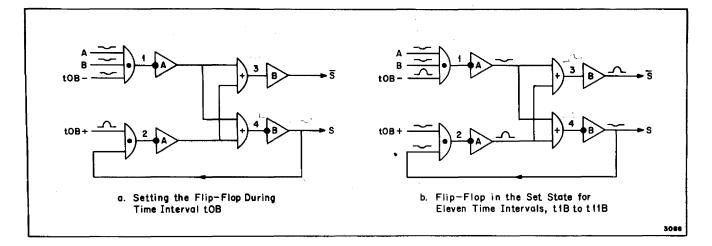

The generation of power pulses is synchronized with the revolving storage drum by sprocket tracks on the drum (figure 2-3). Each sprocket track contains 2400 permanently recorded pulses. These pulses are read continually from the drum at the rate of one every 1.414 microseconds. This is the basic pulse rate of the computer. The sprocket pulses are fed to the sine wave clock which generates an A-phase and a B-phase power pulse for each sprocket pulse it receives. These power pulses differ by half a pulse time and are 180 degrees out of phase. The letter A or B inside the triangle indicates the phase of the power pulse that drives the amplifier.

All the A-phase amplifiers in the computer receive an A-phase power pulse simultaneously. One-half pulse time later, all the B-phase amplifiers receive a B-phase power pulse. Amplifiers connected in series must alternate in phase so that an A-phase amplifier always precedes and follows a B-phase amplifier. Each power pulse has a positive half cycle and a negative half cycle (figure 2-3). During the half-pulse time that the power pulse is negative, the magnetic amplifier receives an input signal. For example, an A-phase amplifier receives an input signal during the half-pulse time that its A-phase power pulse is negative. During the next half-pulse time, the A-phase amplifier delivers an output signal to the B-phase amplifier next in line at the time the B-phase amplifier is receiving the negative half of its B-phase power pulse. This sequence of operation entails a delay of one half-pulse time in the passage of a pulse through an amplifier or one full-pulse time through both an A-phase and B-phase amplifier. The operation of the magnetic amplifier circuits is discussed in detail in section VI.

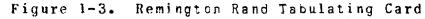

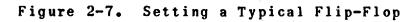

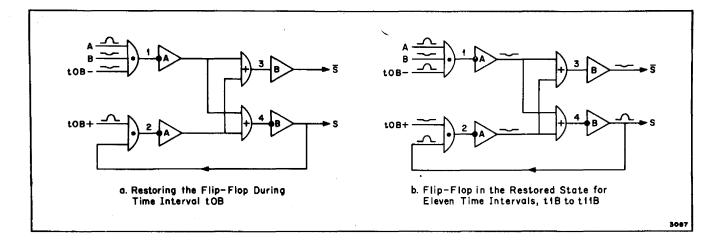

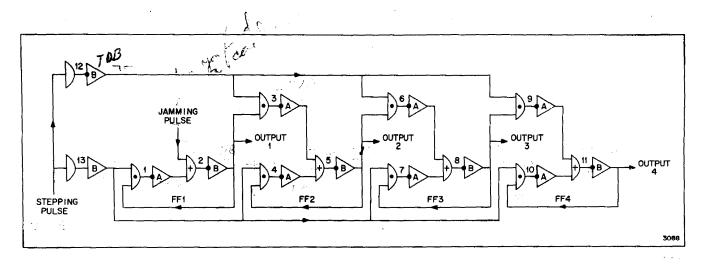

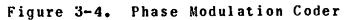

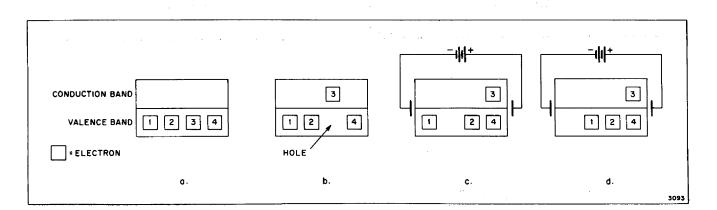

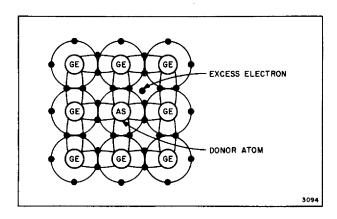

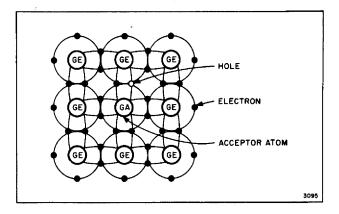

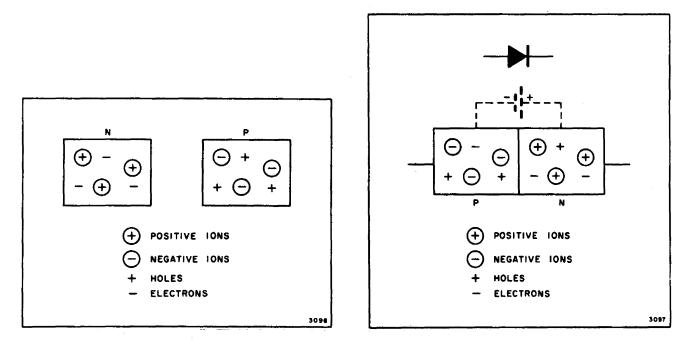

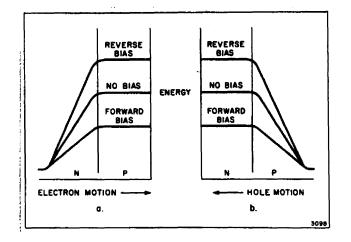

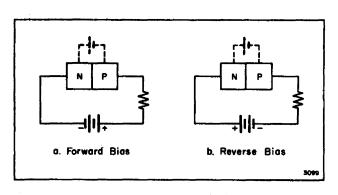

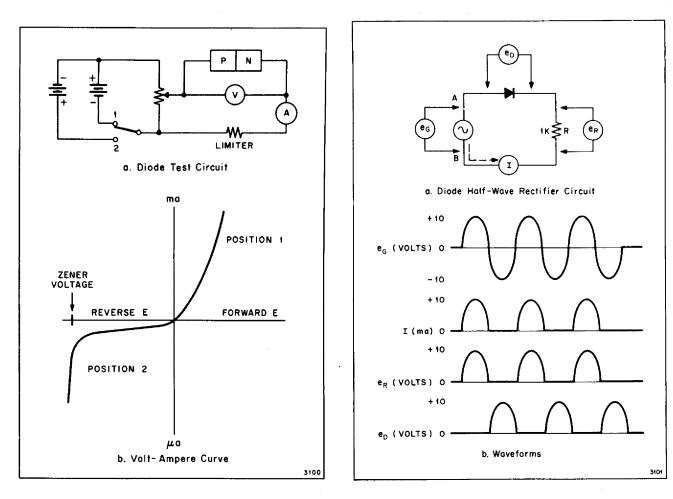

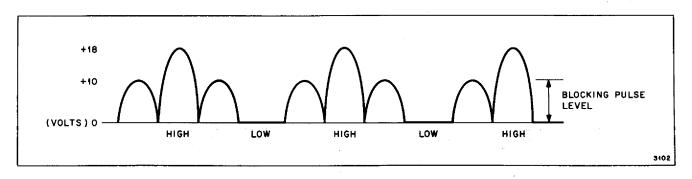

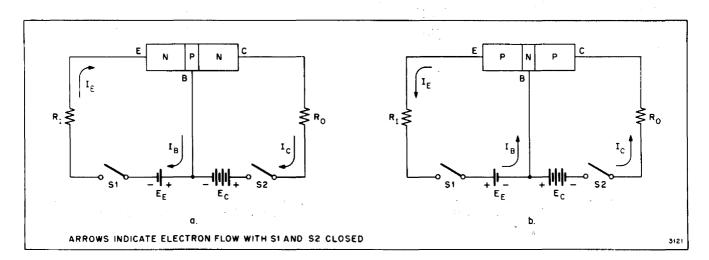

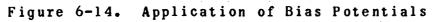

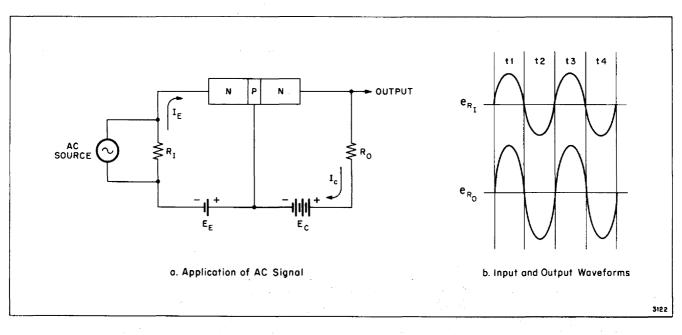

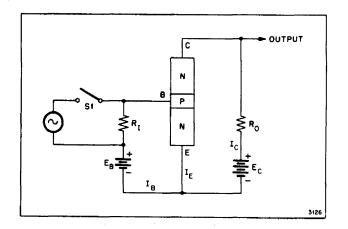

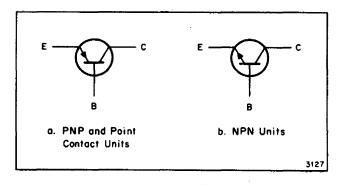

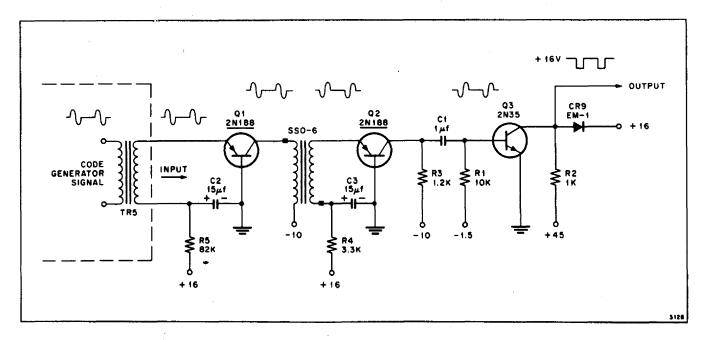

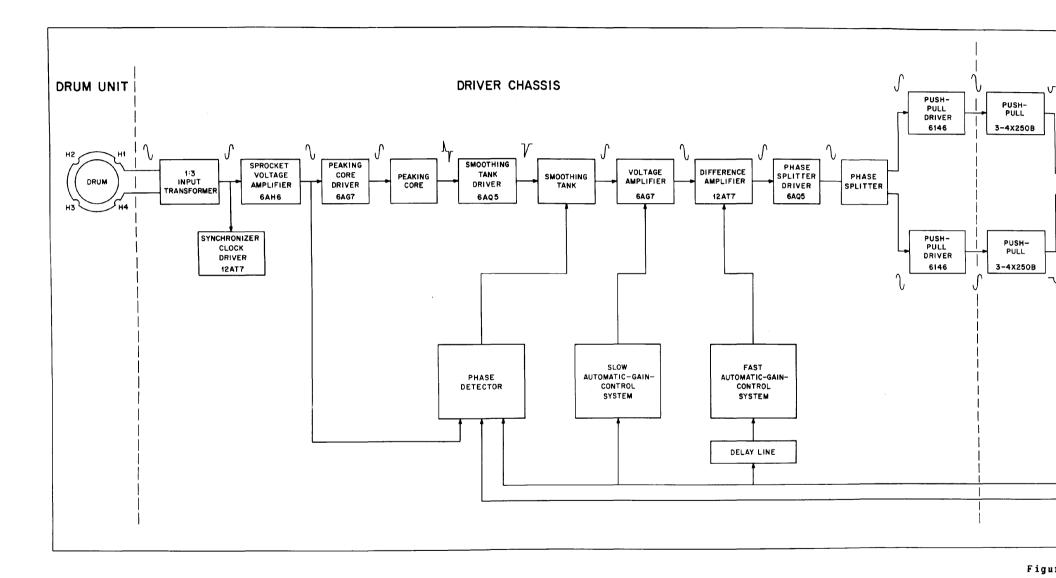

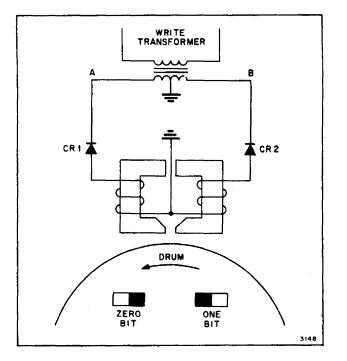

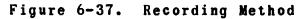

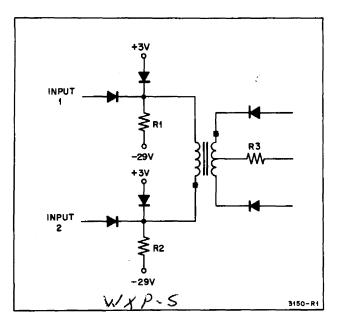

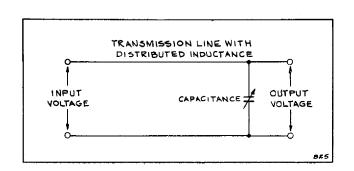

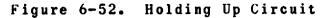

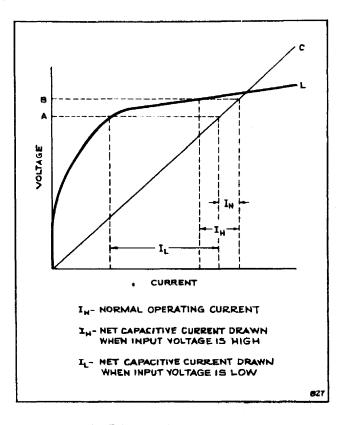

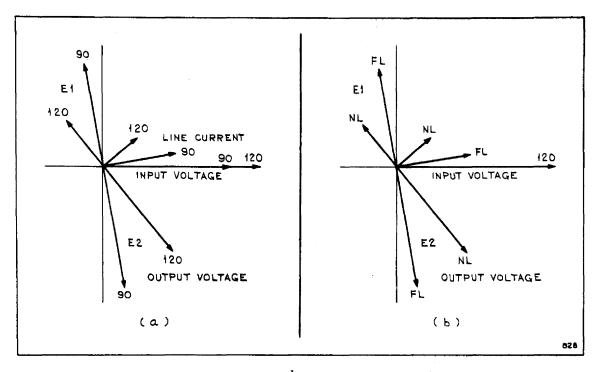

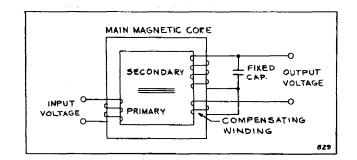

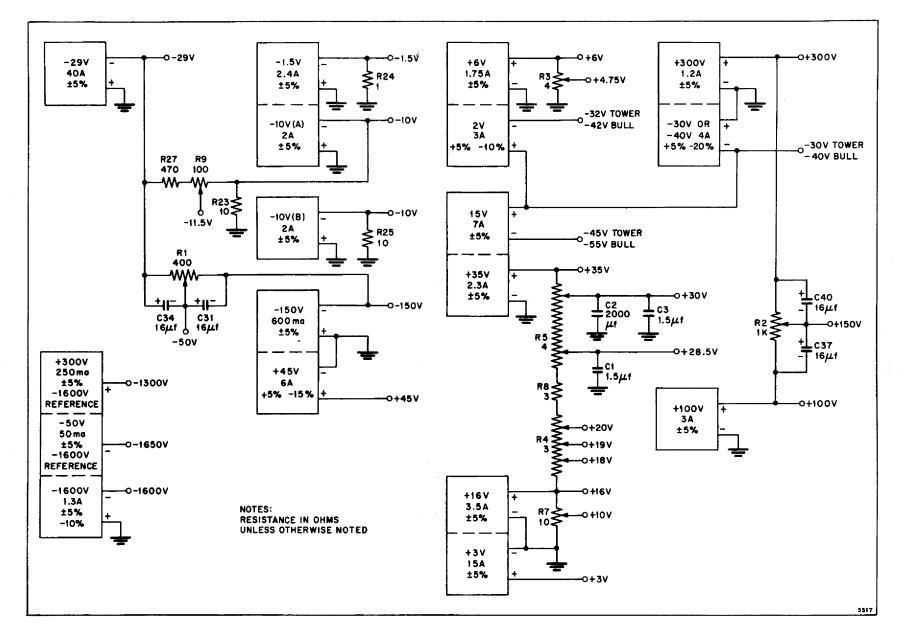

## 2-11. LOGICAL DIFFERENCE