|                                         |                                       | <b>?</b> Y:                                                                                                                   | $\langle \rangle$ | ١U    |          |                           |                           |                            |                 |                                                                   |                                        | •                                     |                       |                 | ••       |                |                      | -        |                   | SH       | EET                  | 1        | ·    |

|-----------------------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------|-------|----------|---------------------------|---------------------------|----------------------------|-----------------|-------------------------------------------------------------------|----------------------------------------|---------------------------------------|-----------------------|-----------------|----------|----------------|----------------------|----------|-------------------|----------|----------------------|----------|------|

|                                         |                                       |                                                                                                                               | <u> </u>          |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       |                       |                 |          |                |                      |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       | 1 .                   |                 |          |                | • • •                |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   | ·                                      |                                       | -<br>                 | •               |          | ••••           |                      |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       | 7                     |                 |          |                |                      |          |                   |          |                      |          |      |

|                                         | · · .                                 |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       |                       |                 |          |                | · · · · · ·          |          |                   | <u> </u> |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           | PRO                       | DUC                        | T FU            | JNC                                                               | TIO                                    | V SI                                  | PEC                   | IFI             | CAT      | ION            |                      |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            | ר <u>ז</u> א רד | م<br>ارم                                                          | ROCI                                   | 2001                                  |                       | CE.             | T        |                |                      |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   | K-20<br>UYK-                           |                                       |                       |                 | 1        | 11 J.          |                      |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 | AN/                                                               | UYK•                                   | -20)                                  | (V)                   | )               |          | •              |                      |          |                   |          |                      |          |      |

| •                                       |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   |                                        | ÷.,                                   | ur<br>Kur<br>Kur      |                 |          |                |                      |          |                   |          | · .                  |          | . 1. |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   | -                                      |                                       |                       |                 |          |                |                      |          |                   |          |                      |          |      |

|                                         |                                       | L                                                                                                                             |                   |       |          |                           |                           |                            |                 |                                                                   | ······································ | · · · · · · · · · · · · · · · · · · · | · · ·                 |                 |          |                |                      |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       |                       |                 |          |                |                      |          |                   |          |                      |          |      |

|                                         |                                       |                                                                                                                               |                   | :     |          |                           |                           |                            | · ·             | . 'r                                                              |                                        |                                       |                       |                 |          |                |                      |          |                   | •        |                      |          |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       |                       | •               |          |                |                      |          |                   |          |                      |          |      |

| SHEET INDEX                             |                                       |                                                                                                                               |                   |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       |                       |                 |          |                |                      |          |                   |          |                      |          |      |

| SHEET                                   | 1                                     | 2                                                                                                                             | 3                 | 4     | 5        | 6                         | 7                         | 8                          | 9               | 10                                                                | 11                                     | 12                                    | 13                    | 14              | 15       | 16             | 17                   | 18       | 19                | 20       | 21                   | 22       | 23   |

| REV                                     | H                                     | Η                                                                                                                             | H                 | F     | G        | ÷                         | F.                        | H                          | F               | F                                                                 | H                                      | Ş                                     | Н                     | G               | (-       | 1.77           | F                    |          | H                 | E.       | H                    |          | H    |

| <i>6</i>                                | · · · · · · · · · · · · · · · · · · · |                                                                                                                               |                   |       | <u>г</u> | r                         | ·                         |                            | 1               |                                                                   |                                        |                                       |                       | 1               | r        | r              | •                    | 1        |                   |          | 1                    | 1        |      |

| SHEET                                   | 24                                    | 25                                                                                                                            | 26                |       | 28       | 29                        |                           | 31                         |                 | 33                                                                |                                        |                                       | 36                    | -               |          | 39             |                      | 41       | 42                | 43       | 44                   | 45       | 46   |

| REV                                     | F                                     | F                                                                                                                             | F.                | F     | F        | H                         | F                         | F                          | F               | F                                                                 | F                                      | F.                                    | 1                     | F               | F        | Į į            | <u> </u>             |          | F                 |          |                      |          | H    |

| SHEET                                   | 47                                    | 48                                                                                                                            | 49                | 50    | 51       | 52                        | 53                        | 54                         | 55              | 56                                                                | 57                                     | 58                                    | 59                    | 60              | 61       | 62             | 63                   | 64       | 65                | 66       | 67                   | 68       | 69   |

| REV                                     | F                                     | F                                                                                                                             | H                 | F     | 1-       | F                         | F                         | F                          | F               | F                                                                 | F                                      | H                                     | G                     | · [             | (        |                | G                    | G        |                   | G        | G                    | G        |      |

|                                         |                                       |                                                                                                                               |                   |       | L        | ł                         | L                         | ·                          | ·····           | L                                                                 | ł                                      |                                       | L                     |                 | <u> </u> |                | ł                    | L        | <b>.</b>          |          |                      | J        |      |

| SHEET                                   | 70                                    | 71                                                                                                                            | 72                | 73    | 74       | 75                        | 76                        | 77                         |                 | 79                                                                |                                        | 81                                    | 82                    | 83              | 84       | 85             | 86                   | 87       | 88                | 89       | 90                   | 91       | 92   |

| REV                                     | 5                                     | F.                                                                                                                            | H                 | H     | H        | 6                         | r'                        | F.T.                       |                 | 6                                                                 | 6                                      |                                       | 1-1                   |                 | +        |                | -                    | 1        | 1                 | 1-       | Anna<br>Anna<br>Anna | •        |      |

|                                         | •                                     |                                                                                                                               | THE<br>SPA<br>APP | CE DE | IORIZE   | D ISSU<br>ORIGI<br>ET. TH | E OF T<br>NAL IS<br>E DAT | HIS SI<br>SSUE )<br>E OF 1 | PECIFIC<br>SHOW | ATION                                                             | CONSI                                  | STS O<br>EET IN                       | F THE<br>IDEX<br>IOWN | SHEET<br>SECTIO | REVIS    | SIONS<br>THE L | (""<br>ATEST<br>RECO | IN RI    | EVISION<br>OF THE | N        |                      |          | 1.4  |

|                                         |                                       |                                                                                                                               |                   | ORIC  | GINA     | L                         |                           |                            |                 |                                                                   | MO                                     | DA                                    | Y                     | YR              |          | n an<br>Ruise  |                      | 38       |                   |          |                      | <u>.</u> |      |

| WRITTEN                                 | BY                                    | D                                                                                                                             | .A.               | Kl    | obe      |                           |                           |                            |                 |                                                                   | 2                                      | 7                                     |                       | 73              | 5        | PE             | KS.                  | Y        |                   | NIV      |                      |          |      |

| ORGANIZA                                |                                       | Tec                                                                                                                           | hni               | .cal  | Sp       | beci                      | fic                       | ati                        | ons             |                                                                   | <b>∠</b>                               |                                       |                       | ' J             |          |                |                      |          |                   |          |                      | BOX 3    |      |

| APPROVAL                                |                                       | R                                                                                                                             | R.                | Re    | ede:     | r                         |                           |                            |                 |                                                                   | 2                                      | 7                                     |                       | 73              | 1        |                |                      |          | U1. F             | -JUL, IV |                      |          |      |

| ORGANIZATION<br>TECHNICAL SPECIFICATION |                                       |                                                                                                                               |                   | TIONS | 3        |                           | ۲.                        |                            |                 |                                                                   |                                        |                                       |                       |                 |          |                | TIO-                 | י -<br>ה |                   |          |                      |          |      |

| M.J. DeBlauw                            |                                       |                                                                                                                               |                   |       | ~        |                           |                           |                            |                 | C                                                                 |                                        | IDI<br>MBI                            |                       |                 |          | N              |                      |          |                   |          |                      |          |      |

| ORGANIZATION Product Development        |                                       |                                                                                                                               |                   |       |          | 2                         | 7                         |                            | 73              | n de la Constantina<br>Antenda Constantina<br>Antenda Constantina |                                        |                                       |                       |                 |          |                |                      |          |                   |          |                      |          |      |

| PROVAL N/A                              |                                       |                                                                                                                               |                   |       |          |                           |                           |                            | SPECIF          | FICATIO                                                           | N NUN                                  | ABER                                  |                       | ······          | s        | PEC. RI        | EV.                  |          |                   |          |                      |          |      |

| ORGANIZA                                |                                       | . ۱۰۰۰<br>۱۹۹۹ - ۱۹۹۹<br>۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹۹۹ - ۱۹ |                   |       |          |                           |                           |                            |                 |                                                                   |                                        |                                       |                       |                 |          | SB-            | -101                 | L60      |                   |          |                      | H        | (*   |

| APPROVAL<br>ORGANIZA                    |                                       |                                                                                                                               | 1                 | N/A   | · .      |                           |                           |                            | -               |                                                                   |                                        |                                       |                       |                 |          |                |                      |          |                   |          |                      | 11       |      |

|                                         |                                       |                                                                                                                               |                   |       |          |                           |                           | 6 C S C                    |                 | 1                                                                 | 1                                      | E -                                   | 1 C                   |                 |          |                |                      |          |                   |          | 1                    |          |      |

LINIVAC

### SPECIFICATION APPROVAL SHEET CONTINUATION

|       |          |                |                   |     |            |     |          |      |                           | зн    |          |                 | REVISION                | Н       |

|-------|----------|----------------|-------------------|-----|------------|-----|----------|------|---------------------------|-------|----------|-----------------|-------------------------|---------|

|       |          |                |                   |     |            |     |          |      |                           |       | SPI      | SB-10           | n symbol<br>)160        |         |

|       |          |                |                   | ·   |            | SI  | HEET INC | DEX  |                           |       |          |                 |                         |         |

| SHEET | .93      | 94             | 95                | 96  | 97         | 98  | 99       | 100  | 101                       | 102   | 103      | 104             | 105                     | 100     |

| REV.  | F        | F              | F                 | ·F  | F          | H   | H        | F    | F                         | Н     | H        | H               | F                       | H       |

| SHEET | 107      | 108            | 109               | 110 | 111        | 112 | 113      | 114  | 115                       | 116   | 117      | 118             | 119                     | 120     |

| REV.  | F        | F              | G                 | G'  | F          | F   | H        | F    | F                         | (     | . (°**   |                 |                         |         |

| SHEET | 121      | 122            | 123               | 124 | 125        | 126 | 127      | 128  | 129                       | 130   | 131      | 132             | 133                     | 134     |

| REV.  | 1        | 1              | ju la<br>Jum<br>L | -   | <u> </u> H | 1   | H        | -    | <b>j</b> <del>v.</del>    | H     | +        |                 | N                       | F       |

| SHEET | 135      | 136            | 137               | 138 | 139        | 140 | 141      | 142  | 143                       | 144   | 145      | 146             | 147                     | 148     |

| REV.  | Н        | F              | F                 | F   | { "        | (   | F        | F    | H                         | H     | H        | \$ <del>.</del> | 20 <b>m</b>             | - feini |

| SHEET | 149      | 150            | 151               | 152 | 153        | 154 | 155      | 156  | 157                       | 158   | 159      | 160             | 161                     | 16      |

| REV.  | F        | F              | F                 | F   | F          | F   | F        | F    | F                         | 1-    | F        | F               | F                       | F       |

| SHEET | 163      | 164            | 165               | 166 | 167        | 168 | 169      | 170  | 171                       | 172   | 173      | 174             | 175                     | 170     |

| REV.  | F        | -              | F                 | F   | (          | F   | G        | +    | , <b>F</b> -1 <sup></sup> | Ge'   | G        | G               | 9 - 200<br>2 - 200<br>2 | G       |

| EET   | 177      | 178            | 179               | 180 | 181        | 182 | 183      | 184  | 185                       | 186   | 187      | 188             | 189                     | 190     |

| REV.  | $G^{*}$  | F.             | H                 | H   | H          | F   | F        | H    | far.                      |       |          | 55              |                         | F       |

| SHEET | 191      | 192            | 193               | 194 | 195        | 196 | 197      | 198  | 199                       | 200   | 201      | 202             | 203                     | 204     |

| REV.  | F        | H              | H                 | F   |            | F   | 1-       | e    | F                         | H     |          | <u></u>         | 1-                      |         |

| SHEET | 205      | 206            | 207               | 208 | 209        | 210 | 211      | 58.1 | 70.1                      |       | 173.]    | 174.1           | 177.1                   | 131     |

| REV.  | F        | <u><u></u></u> | 17                | 1   | G          | F   | H        | G    | G                         |       |          |                 |                         | H       |

| SHEET |          | 200.1          |                   |     |            |     |          |      |                           |       |          | <b> </b>        |                         |         |

| REV.  | H        | H              |                   |     |            |     |          |      |                           |       |          |                 | <u> </u>                |         |

| SHEET |          |                |                   |     |            |     |          |      |                           |       |          |                 |                         |         |

| REV.  | l        | L              |                   |     |            |     |          | L    |                           | L     |          |                 |                         |         |

| SHEET |          |                |                   |     |            |     |          |      |                           |       |          |                 |                         |         |

| REV.  | <u> </u> | <u> </u>       | <u> </u>          |     | L          |     |          |      |                           |       |          | <u> </u>        |                         |         |

| SHEET |          |                |                   |     |            |     |          |      |                           | -<br> |          |                 |                         |         |

| REV.  |          |                |                   |     |            |     |          |      |                           |       |          |                 | <u> </u>                |         |

| EET   |          |                |                   |     |            |     |          |      |                           |       |          |                 |                         |         |

| REV.  |          |                |                   |     | [          |     |          |      |                           |       | <u> </u> |                 |                         |         |

| SHEET |          |                |                   |     |            |     |          |      |                           |       |          |                 |                         |         |

| REV.  |          |                |                   |     |            |     |          |      |                           |       |          | · ·             |                         |         |

| W .                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                   | and the states                                                                                                   |                                                                                              |        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------|

| <br>                                                                                                                                                      | SHE                                                                                                                                                                                                                                                                                                               | ет З                                                                                                             | REVISI                                                                                       | ON H   |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                   | and the second | FICATION<br>10160                                                                            | SYMBOL |

|                                                                                                                                                           | TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                 |                                                                                                                  |                                                                                              |        |

| Paragraph                                                                                                                                                 | Title                                                                                                                                                                                                                                                                                                             | (                                                                                                                | Sheet                                                                                        |        |

| 1.                                                                                                                                                        | SCOPE                                                                                                                                                                                                                                                                                                             |                                                                                                                  | 16                                                                                           |        |

| 1.1                                                                                                                                                       | Scope                                                                                                                                                                                                                                                                                                             |                                                                                                                  | 16                                                                                           |        |

| 2.                                                                                                                                                        | APPLICABLE DOCUMENTS                                                                                                                                                                                                                                                                                              |                                                                                                                  | 16                                                                                           | •      |

| 2.1<br>2.2                                                                                                                                                | Government documents<br>Non-Government documents                                                                                                                                                                                                                                                                  |                                                                                                                  | 16<br>19                                                                                     |        |

| 3.                                                                                                                                                        | REQUIREMENTS                                                                                                                                                                                                                                                                                                      |                                                                                                                  | 20                                                                                           |        |

| 3.1<br>3.1.1<br>3.1.1.1<br>3.1.1.2<br>3.1.1.3<br>3.1.1.4                                                                                                  | Design and construction<br>General design<br>Modular construction<br>Interchangeability<br>Standardization<br>Installed options                                                                                                                                                                                   |                                                                                                                  | 20<br>20<br>20<br>20<br>20<br>20                                                             |        |

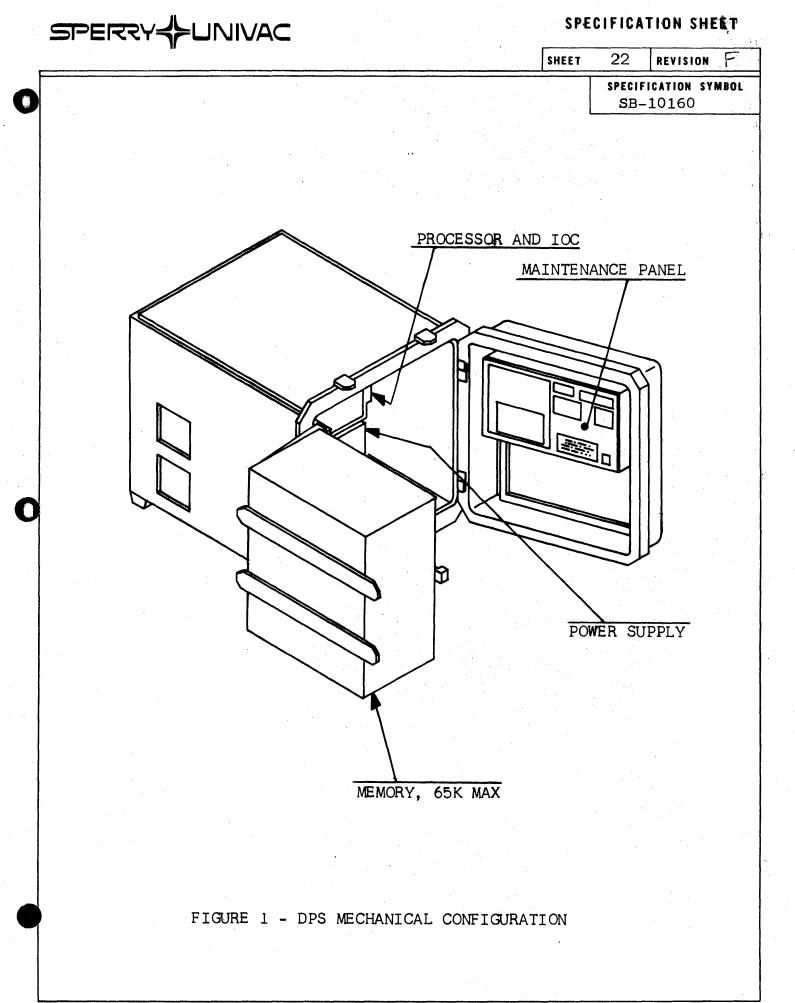

| 3.1.2 $3.1.2.1$ $3.1.2.2$ $3.1.2.3$ $3.1.2.4$ $3.1.2.5$ $3.1.2.6$ $3.1.2.6$ $3.1.2.7$ $3.1.2.8$ $3.1.2.8.1$ $3.1.2.8.2$ $3.1.2.8.3$ $3.1.2.8.4$ $3.1.2.9$ | Mechanical design<br>Physical size and weight<br>Mechanical configuration<br>Rack mounting<br>Interface connectors<br>Cooling<br>Plug-in assembly keying<br>Human engineering<br>Identification and marking<br>Nameplate<br>Field change identification<br>Markings<br>Reference designations<br>Finish and color | n plate                                                                                                          | 21<br>21<br>21<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23<br>23 |        |

| 3.1.3 3.1.3.1 3.1.3.2 3.1.3.3 3.1.3.4 3.1.3.5 3.1.3.6 3.1.3.7                                                                                             | Electrical design<br>Overload protection<br>Time meter<br>Grounding<br>Circuits<br>Test points<br>Safety<br>Overtemperature protection                                                                                                                                                                            |                                                                                                                  | 24<br>24<br>24<br>25<br>25<br>25<br>25                                                       |        |

| 3.2                                                                                                                                                       | Primary power                                                                                                                                                                                                                                                                                                     |                                                                                                                  | 25                                                                                           |        |

|                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                   |                                                                                                                  | 44<br>1                                                                                      |        |

3.4.4.3.3.3.4

3.4.4.3.3.3.5

SPECIFICATION SHEET

SHEET 4 REVISION F

SPECIFICATION SYMBOL

51

51

|                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                      | SB-10160                                                                                     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                              |

|                                                                                                                                                                                                                         | TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                    |                                                                                              |

| Paragraph                                                                                                                                                                                                               | Title                                                                                                                                                                                                                                                                                                                                                                                | Sheet                                                                                        |

| 3.3<br>3.3.1                                                                                                                                                                                                            | General performance<br>DPS arithmetic                                                                                                                                                                                                                                                                                                                                                | 27<br>27                                                                                     |

| 3.4<br>3.4.1                                                                                                                                                                                                            | Detail performance<br>Instruction repertoire                                                                                                                                                                                                                                                                                                                                         | 27<br>27                                                                                     |

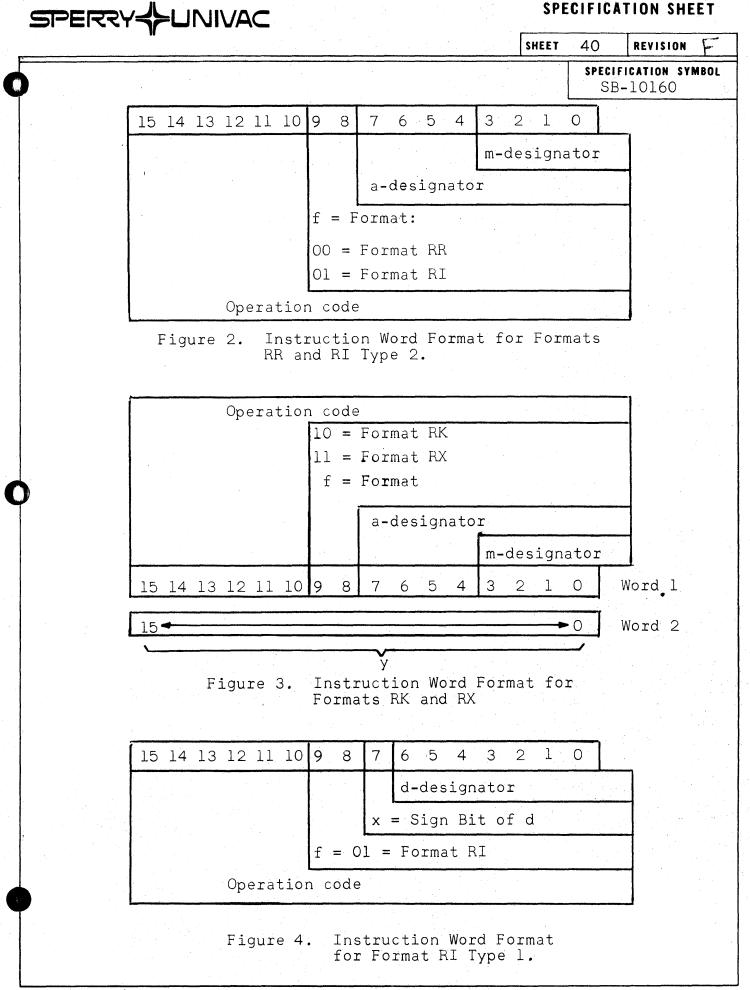

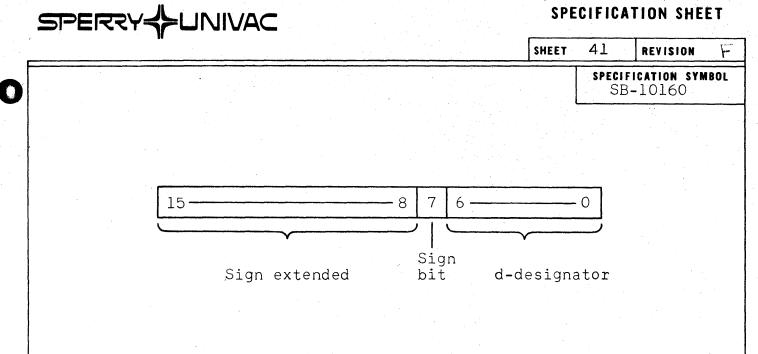

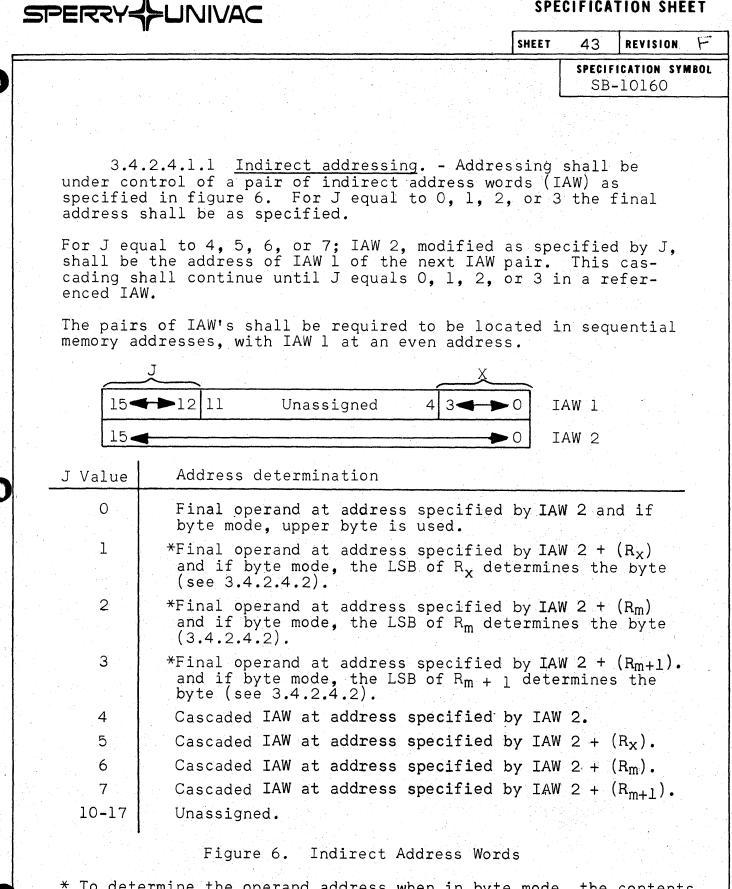

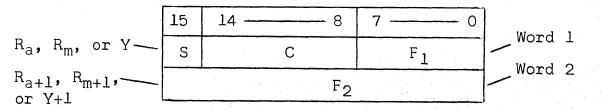

| 3.4.2<br>3.4.2.1<br>3.4.2.2<br>3.4.2.2.1<br>3.4.2.2.2<br>3.4.2.3<br>3.4.2.4<br>3.4.2.4.1<br>3.4.2.4.1<br>3.4.2.4.1<br>3.4.2.4.2<br>3.4.2.5<br>3.4.2.5<br>3.4.2.6<br>3.4.2.7                                             | Instruction words<br>Format RR<br>Format RI<br>Format RI Type 1<br>Format RI Type 2<br>Format RK<br>Format RX<br>Format RX<br>Format RX whole word operations<br>Indirect addressing<br>Format RX byte operations<br>Format RL<br>Double length operations<br>Shift instruction execution                                                                                            | 39<br>39<br>39<br>39<br>39<br>41<br>42<br>42<br>42<br>42<br>43<br>44<br>45<br>45<br>45<br>46 |

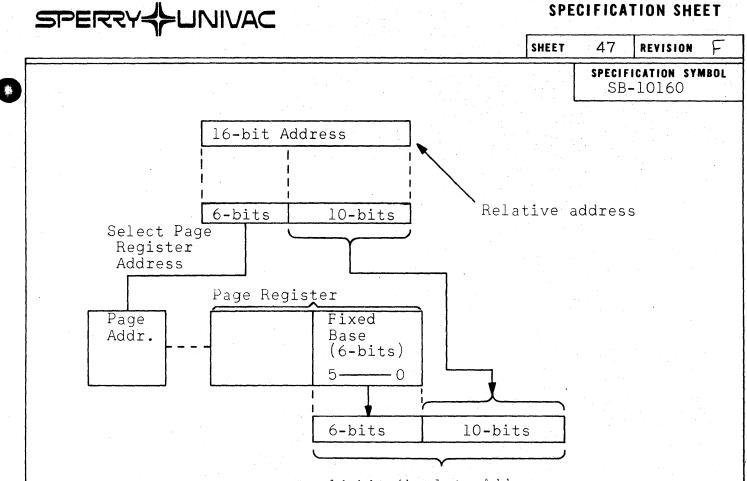

| 3.4.3                                                                                                                                                                                                                   | Relative addressing                                                                                                                                                                                                                                                                                                                                                                  | 46                                                                                           |

| 3.4.4<br>3.4.4.1<br>3.4.4.1.1<br>3.4.4.1.2<br>3.4.4.1.3<br>3.4.4.1.4<br>3.4.4.1.5<br>3.4.4.1.6<br>3.4.4.2<br>3.4.4.3<br>3.4.4.3.1<br>3.4.4.3.2<br>3.4.4.3.3<br>3.4.4.3.3.1<br>3.4.4.3.3.2<br>3.4.4.3.3.2<br>3.4.4.3.3.3 | Memories<br>Main memory<br>Word length<br>Cycle time<br>Capacity<br>Addressing<br>Protection<br>Two-port priority<br>NDRO memory (bootstrap)<br>Microprogrammed read-only memor<br>User-defined microprogram<br>Diagnostic microprogram<br>Diagnostic microprogram<br>Math pack<br>Square root operation<br>Trigonometric and hyperbolic<br>functions<br>Electing point instructions | 49<br>49<br>49<br>50<br>50                                                                   |

| 3.4.4.3.3.3<br>3.4.4.3.3.3.1<br>3.4.4.3.3.3.2<br>3.4.4.3.3.3.3<br>3.4.4.3.3.3.3                                                                                                                                         | Floating point instructions<br>Normalization<br>Floating point zero<br>Floating point round                                                                                                                                                                                                                                                                                          | 50<br>51<br>51<br>51                                                                         |

Floating point residue Characteristic underflow and

overflow

### SPECIFICATION SHEET

|   | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | SHEET                                                | 5                                                                                              | REVISION                                                                   | G    |

|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|------|

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      |                                                                                                | CATION SY<br>10160                                                         | MBOL |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                      | алана.<br>1944 г. – Полонания Полонания (пр. 1914)<br>1944 г. – Полонания Полонания (пр. 1914) |                                                                            |      |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |                                                                                                |                                                                            |      |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                      |                                                                                                |                                                                            |      |