SPERRY LUNIVAC

# RESTRICTIVE NOTICE

This publication describes the general construction, operational characteristics, and capabilities of the SPERRY UNIVAC U1600 computer. It should not be considered an equipment specification. Sperry Univac in no way warrants the accuracy or completeness of this document for the purpose of a procurement specification.

# TECHNICAL Description

SPERRY LINIVAC

# TABLE OF CONTENTS

| INTRODUCTION                              | .1  |

|-------------------------------------------|-----|

| AN EXCELLENT LONG-TERM INVESTMENT         | .1  |

| REAL-TIME APPLICATIONS                    | .1  |

| Shipboard Defense Systems Applications    |     |

| Communications Systems                    |     |

| Signal Processing                         |     |

| Control Systems                           |     |

| Other U1600 Applications                  | .2  |

| SPECIFICATIONS AND FEATURES               | .3  |

| MODULAR ARCHITECTURE                      | .4  |

| CONSTRUCTION                              | .5  |

| MAINTAINABILITY                           | .6  |

| FUNCTIONAL ARCHITECTURE                   | .7  |

| Main Memory                               | 7   |

|                                           |     |

| Memory Interface                          |     |

| DMA Interface Capability                  |     |

| Memory Address Allocation                 |     |

| Memory Addressing.                        |     |

| NDRO Memory Feature                       |     |

| Bank Select Feature                       |     |

| Input/Output Controller                   |     |

| General Registers                         |     |

| Program Address Register                  |     |

| Real-Time Clock and Monitor Clock Feature |     |

| Breakpoint Feature                        |     |

| Power Failure Protection Feature          |     |

| Status Register                           | .13 |

| FUNCTIONAL OPERATION                      | .13 |

| Computer Status Control                   |     |

| Instructions                              |     |

| Math Pac Option                           |     |

| Instruction Addressing                    |     |

| Instruction Word Formats                  |     |

| Single Length Operands                    |     |

| Double Length Operands                    |     |

| Operand Addressing                        |     |

| Interrupts                                |     |

| Interrupt Processing                      | .21 |

# TABLE OF CONTENTS (CONT.)

# FUNCTIONAL OPERATION (CONT.)

| Parallel Input Interface Communication  |      | 7 |

|-----------------------------------------|------|---|

| Parallel Output Interface Communication |      |   |

|                                         |      |   |

| Intercomputer Communication             |      |   |

| Peripheral Input Channel                |      |   |

| Serial Channel Interrupts               | <br> | 2 |

| NTDS Serial Channel Communication       | <br> | 2 |

| Command Instruction                     | <br> | 2 |

| Program Chaining                        | <br> | 2 |

| Externally Specified Addressing (ESA)   |      |   |

| Master Clear                            |      |   |

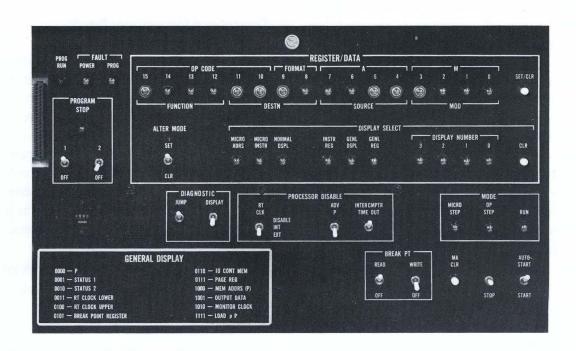

| Control and Maintenance Panels          |      |   |

# LIST OF ILLUSTRATIONS

| Figure No.              | Titles                                                                                                                                                                                                                                                          | Page                                               |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1                       | U1600 Computer                                                                                                                                                                                                                                                  | 2                                                  |

| 2                       | Functional Architecture                                                                                                                                                                                                                                         |                                                    |

| 3                       | U1600 Modular Architecture                                                                                                                                                                                                                                      |                                                    |

| 4                       | Printed Circuit (PC) Card                                                                                                                                                                                                                                       |                                                    |

| 5                       | Power, External RTC and I/O Connectors                                                                                                                                                                                                                          |                                                    |

| 6                       | Computer Opened To Show Construction                                                                                                                                                                                                                            |                                                    |

| 7                       | Memory Address Generation                                                                                                                                                                                                                                       |                                                    |

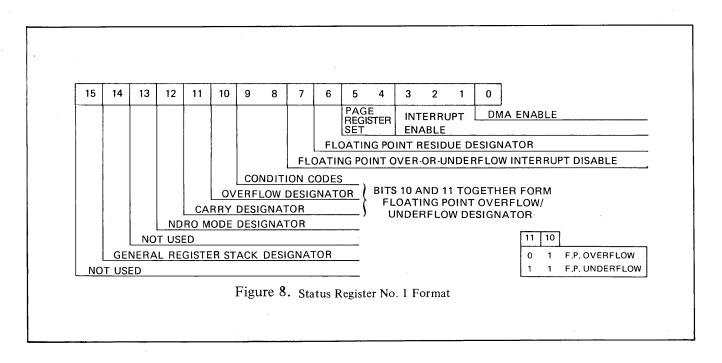

| 8                       | Status Register No. 1 Format                                                                                                                                                                                                                                    |                                                    |

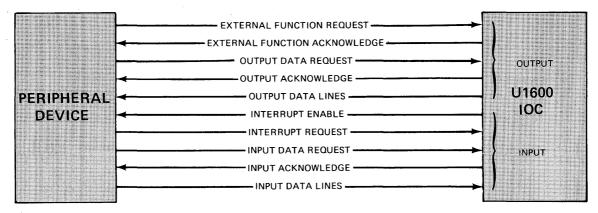

| 9                       | Parallel Interface                                                                                                                                                                                                                                              | 10                                                 |

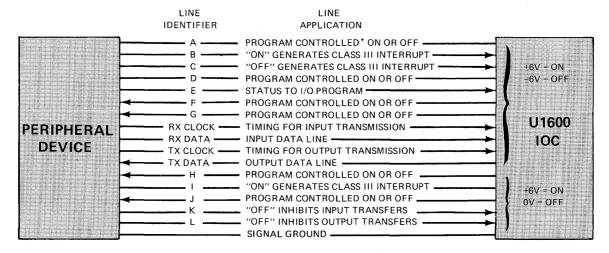

| 10                      | MIL-STD-188C and Vacales Interface                                                                                                                                                                                                                              | 10                                                 |

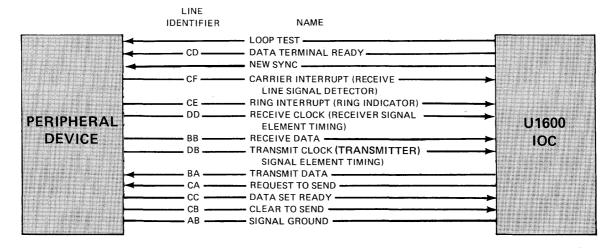

| 11                      | EIA-STD-RS232C Interface                                                                                                                                                                                                                                        | 10                                                 |

| 12                      | NTDS Serial Channel Interface                                                                                                                                                                                                                                   | 11                                                 |

| 13                      | Instruction Word Formats                                                                                                                                                                                                                                        |                                                    |

| 14                      | Status Register No. 2 Formats                                                                                                                                                                                                                                   |                                                    |

| 15                      | Indirect Word Interpretation                                                                                                                                                                                                                                    |                                                    |

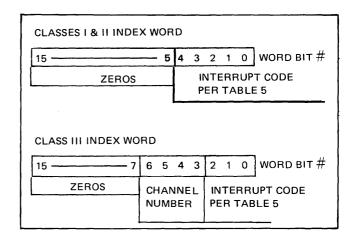

| 16                      | Interrupt Entrance Address Index                                                                                                                                                                                                                                |                                                    |

| 17                      | Serial Channel Interrupt Word Format                                                                                                                                                                                                                            |                                                    |

| 18                      | I/O Channel Control Memory                                                                                                                                                                                                                                      |                                                    |

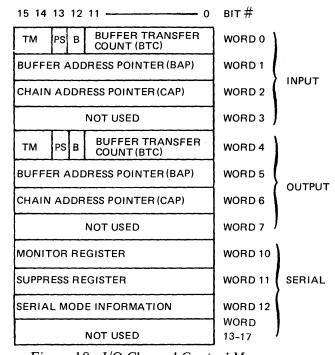

| 19                      | Control Panel                                                                                                                                                                                                                                                   | 24                                                 |

| 20                      | Maintenance Panel                                                                                                                                                                                                                                               |                                                    |

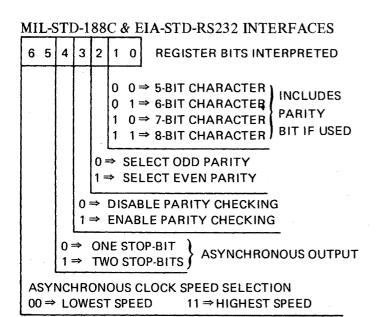

| I                       | Serial Mode Information Interpretation                                                                                                                                                                                                                          | A-30                                               |

|                         | LIST OF TABLES                                                                                                                                                                                                                                                  |                                                    |

| Table No.               | Titles                                                                                                                                                                                                                                                          | Page                                               |

| 1                       | Assigned Memory Addresses                                                                                                                                                                                                                                       |                                                    |

| 2                       | Typical I/O Transfer Rates                                                                                                                                                                                                                                      | 12                                                 |

| 3                       | Page Register Sets                                                                                                                                                                                                                                              | 14                                                 |

| 4                       | Condition Code Indications                                                                                                                                                                                                                                      |                                                    |

| 5                       | Repertoire of Instructions                                                                                                                                                                                                                                      |                                                    |

| 6                       | Interrupt Priority                                                                                                                                                                                                                                              |                                                    |

| 7                       | IOC Instruction List                                                                                                                                                                                                                                            |                                                    |

| 8                       | Control Panel Switches and Indicators                                                                                                                                                                                                                           |                                                    |

| 9                       | Maintenance Panel Switches and Indicators                                                                                                                                                                                                                       |                                                    |

| I                       | Unary-Artihmetic Instruction m-Values                                                                                                                                                                                                                           |                                                    |

| II                      |                                                                                                                                                                                                                                                                 |                                                    |

| III                     | Unary-Control Instruction m-Values                                                                                                                                                                                                                              |                                                    |

| IV                      | Unary-Shift Instruction m-Value                                                                                                                                                                                                                                 | A-6                                                |

| <b>T</b> 7              | Unary-Shift Instruction m-Value                                                                                                                                                                                                                                 | A-6                                                |

| V                       | Unary-Shift Instruction m-Value                                                                                                                                                                                                                                 | A-6<br>A15<br>A-17                                 |

| VI                      | Unary-Shift Instruction m-Value                                                                                                                                                                                                                                 | A-6<br>A15<br>A-17                                 |

| VI<br>VII               | Unary-Shift Instruction m-Value                                                                                                                                                                                                                                 | A-6<br>A-15<br>A-17<br>A-28<br>A-29                |

| VI<br>VII<br>VIII       | Unary-Shift Instruction m-Value.  Trigonometric and Hyperbolic Functions.  Conditions for a-Value in Jump Instructions.  Channel Control Instruction m-Designator  Initiate Transfer Instruction a-Value.  Control Memory Address Selection.                    | A-6<br>A15<br>A-17<br>A-28<br>A-29<br>A-30         |

| VI<br>VII<br>VIII<br>IX | Unary-Shift Instruction m-Value Trigonometric and Hyperbolic Functions Conditions for a-Value in Jump Instructions Channel Control Instruction m-Designator Initiate Transfer Instruction a-Value Control Memory Address Selection a-Designator Jump Conditions | A-6<br>A15<br>A-17<br>A-28<br>A-29<br>A-30<br>A-33 |

| VI<br>VII<br>VIII       | Unary-Shift Instruction m-Value.  Trigonometric and Hyperbolic Functions.  Conditions for a-Value in Jump Instructions.  Channel Control Instruction m-Designator  Initiate Transfer Instruction a-Value.  Control Memory Address Selection.                    | A-6<br>A-17<br>A-28<br>A-29<br>A-30<br>A-33        |

#### U1600 60 Hz EQUIPMENT IDENTIFICATION

#### **Univac Part Number** Description 7311600-01 Data Processing Set 7101970-03, -05 Electrical Equipment Cabinet 7310550-01, -03 Processor Verifier Unit 7101985-03, -06 Control Monitor 7310014-01 Core Memory-Control Unit 7150352-01, -02 Power Supply 3 Phase, 115 Volt Power Supply 3 Phase, 208 Volt 7150354-01, -02 7150353-00, -01 Power Supply 1 Phase, 115 Volt U1600 400 Hz EQUIPMENT IDENTIFICATION 7311600-00 Data Processing Set 7101970-02, -04 Electrical Equipment Cabinet 7310550-00, -02 Processor-Verifier Unit 7101985-02, -04, -05, -07 Control-Monitor 7310014-00 Core Memory-Control Unit 7150350-00, -01 Power Supply 3 Phase, 115 Volt 7150355-00, -01 Power Supply 3 Phase, 208 Volt 7150351-00, -01 Power Supply 1 Phase, 115 Volt U1600 **EQUIPMENT IDENTIFICATION** 7101806-00 -3V NTDS Interface Kit (Fast) 7101805-00 -15V Interface Kit (Slow) 7101807-00 +3.5V ANEW Interface Kit 7128069-00 EIA-STD-RS232 Synchronous Serial Interface Kit 7101803-00 MIL-STD-188C Synchronous Serial Interface Kit 7101802-00 NTDS Fast Serial Interface Kit 7128068-XX MIL-STD-188C Asynchronous Serial Interface Kit 7128070-XX EIA-STD-RS232 Asynchronous Serial Interface Kit 7310548-00 7310548-01 7310548-02 Micro Memory Kit 7310548-03 7310548-04 7128073-00 Electronic Equipment Maintenance Kit 7132198-01 VACALES Serial Interface Kit 7132199-00, -01 -15V (Slow) Peripheral Input Channel Interface Kit 7310022-02 32K Core Memory Array 7128082-00 8K Core Memory Array 7126200-01 Oscillator, RTC Monitor 1KHz 7137180.00 Oscillator, RTC Monitor 32KHz

Adapter Kit, External Mounting

Adapter Kit, External Mounting

Memory Kit, Read

7157900-00

7157900-01

7136820\*

<sup>\*</sup>List of Available NDRO Options

# THE SPERRY UNIVAC U1600 COMPUTER

#### INTRODUCTION

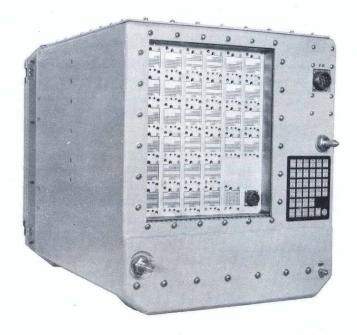

The SPERRY UNIVAC® U1600 is a general-purpose, militarized computer with medium scale computing power in a small, ruggedized package. It is designed to meet the requirements of small and medium sized applications in shipboard, mobile shelter or other severe environments. See Figure 1.

A choice of configurations are offered which encompass a variety of applications. A small configuration can grow with optional functions that increase efficiency and versatility. Most other options can be added in the field by simply incorporating printed circuit cards or memory modules to the basic unit. Hence, current and near-future applications can define an initial configuration. Features to enhance processing and input/output capabilities or to meet requirements of system growth may be added to modular form.

Modularity, versatility and serviceability are design features to make it applicable to the various current and future applications of the armed forces and other Government agencies. Each off-the-shelf unit manufactured by Sperry Univac is wired to accommodate currently offered optional features and also to allow for future enhancements or changes. The computer incorporates a 725 nanosecond core memory, which is expandable to 262,000 words, and an exceedingly flexible microprogrammable control section. These features provide a very fast computing capability as well as affording a basis for tailoring functional operations to specific or unique applications.

# AN EXCELLENT LONG-TERM INVESTMENT

Expansion of functional capability may be accomplished by adding features because any version of the computer contains features that are a subset list of those in a maximum configuration.

A data processing system with a high performance/cost ratio is attainable when the U1600

serves as a foundation. Simplicity and compatibility, combined with functional and physical flexibility, characterize the U1600 in all of its Simplicity, which is available configurations. accomplished by the power and flexibility of the U1600 instructions, provides simple and efficient program generation and implementation. This high quality and maintainable computer, characteristic of Sperry Univac products, will provide the faithful and dependable service expected in a militarized processing system. Reliability and maintainability, two attributes of excellence historically demonstrated in Sperry Univac products, are incorporated in the design and development of the U1600. The input/output capabilities offer a wide interface potential that include byte, whole or dual word parallel transfers, serial transfers, internally controlled buffers, peripheral equipment selection and various interface signal levels and transfer speeds.

# **REAL TIME APPLICATIONS**

Functional characteristics of the U1600 make it as ideally suited to dedicated real-time applications as to the performance of stand-alone and distributed process systems. A hardware initiated, multilevel interrupt processing capability provides efficient and rapid parameter manipulation and preparation prior to the actual interrupt servicing. Overhead functions normally performed by interrupt processing routines are thereby decreased and faster response time is achieved. The processing efficiency obtainable with the use of the general purpose registers and related instructions provides the capability to meet the high data rate environments encountered in time-critical, realtime systems associated with fire control radar, telemetry or on-line process control applications and real-time systems associated with communications, display controlling or data systems.

#### **Shipboard Defense Systems Applications**

Processing all raw data available from a task force and a ship's systems is a huge assignment for a command and control (C&C) system. The U1600 can be utilized very effectively in reducing this burden by absorbing specific data reduction and related overhead tasks in the system.

Functionally a tactical data system coordinates the collection of data from many sources including sonar, radar, IFF and passive detection apparatus communication links. It coordinates all data with ship systems status and navigation information, prepares a clear picture of the tactical situation to aid a decision making process and communicates the decisions to applicable and available action systems and personnel.

The U1600 implemented as a pre-processor has the calculating speed and data handling characteristics to reduce large volumes of raw data to usable values and arranging them in a format acceptable to the C&C computer for direct integration into the total system.

# **Communications Systems**

The U1600 with the I/O controller and its bit and byte manipulation instruction repertoire is ideally suited to communications applications. The serial I/O channels provide great flexibility for handling both synchronous and asynchronous communications lines in a wide range of rates. Network control, store and forward, and line concentration functions are readily implemented through the incorporation of the U1600 in a communications system. Its inherent reliability insures continuous, effective service in these applications.

#### Signal Processing

A major military application is processing radar, sonar and beacon signals. In this application, the systems provide a continual input of data in a real-time environment. High rate processing and fast reaction time is required to determine targets, direction, distance and other information. This critical time data processing task is handled easily by the U1600. Its comprehensive and flexible instruction set executed by the fast central processor section, its programmable real-time clock, and the high-speed, hardware-initiated, interrupt structure provide the capability to perform the complex computations in real-time. Direct access

to memory for real-time data input and/or output is accomplished by the very fast, programmable input/output section or externally controlled direct memory access (DMA) feature.

# **Control Systems**

In addition to weapons control systems, other control systems normally found include air traffic, radar, electronic countermeasures and navigation. Complex control systems, as with signal processing, require high computational capabilities. While the quantity of input data is lower, input is received from more than one source. Here again, the U1600 qualifies for this application. The number of input/output channels can be expanded as required by plug-in units. Complex computations required for commanding the system are accomplished with programs that utilize the fast, general registers and the associated single and double-precision arithmetic.

# Other U1600 Military Applications

- Message Handling receiving, logging and forwarding

- Fire Control

- Navigation

- Management Information

- Telemetry

- Communication Links

- Radar Processing

- Data Reduction

- Sensor Processing

- Range Tracking

- Logistics

Figure 1. U1600 Computer

# THE U1600 COMPUTER

# SPECIFICATIONS AND FEATURES

#### SUMMARY OF STANDARD FEATURES

Militarized Construction; MIL-E-16400

General Purpose, 16-bit digital computer

Physically and functionally modular and expandable

MSI components

Microprogram control

Integral blowers and power supplies

19-inch rack mountable

Front access for maintainability

Plug-in options

#### **Central Processor**

Microprogrammed controller

Two's complement arithmetic

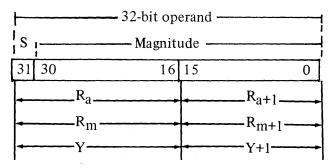

4-bit, 8-bit, 16-bit and 32-bit operands

16 or 32 high speed general purpose registers

4 sets of 64 page registers

Memory write protection and write lock out interrupt

2 program status registers

3-level interrupt processing (hardware serviced)

16-bit and 32-bit instructions

Basic instructions — 5 formats

Sample execution time

Shift 1.0 microsecond

Add .84 microseconds

Multiply 3.6 microseconds

Divide 6.6 microseconds

Direct addressing to 262K words

Relative addressing 1024 word pages

Indexing via general registers

Cascaded indirect addressing

Relative addressing by page

Power Fault/Auto-Restart

Real-time clock and monitor clock

Bootstrap NDRO (read only) memory

Memory Address capability to 524K words

#### Main Storage

Expandable — 32K to 262K words in 32K increments or 8K to 65K in 8K increments (16-bit words)

Read/restore cycle time — 725 nanoseconds

Asynchronous timing

Nonvolital

#### Input-Output Controller

Up to 32 prógram initiated input/output chains I/O instruction repertoire — same format as CP Full Duplex input/output channels Control memory for each channel Up to 16 channels (combination serial and parallel) Parallel channels:

Expandable in 4 channel groups Serial channels:

Expandable in 2 or 4 channel groups

#### **PHYSICAL**

Temperature Range

Operating: 0°C to 50°C Storage: -62°C to +75°C Relative Humidity: to 95%

Size (inches): maximum Height: 20 Width: 19

Depth: 24

Standard cabinet

Weight 230 lbs. maximum (w/o Ext. Mtg. adapters)

Pass through 25 inch hatch without external mounting

adapters or air plenum mounted

# **Primary Power**

115 or 208 volts 1000 watts (maximum configuration)

#### **ENHANCEMENT OPTIONS**

Features of the U1600 computer provide functional adaptatability for many application requirements. Available options increase its capacity, enhance its flexibility, and provide functions required by certain applications. The following options may be selected for the U1600 and may be added without wiring or cabinet changes by plugging the required module into the basic computer unit.

#### **Central Processor**

Additional micromemory  $-\,512$  words (Customer defined). Customer defined Bootstrap NDRO programs.

Math Pac functions

Square root

Trigonometric and hyperbolic vector and rotate

Floating point arithmetic

Double precision multiply and divide Algebraic left and right quadruple shifts

Optional 32KHz rate for real-time clock and monitor clock

#### Main Memory

Memory Size: 32,768 word increments to 262,144 with Direct Memory Access (DMA) interface.

External Memory Bus option provides access to additional 262,144 words of external memory.

#### Input/Output Controller

A maximum of 16 input/output channels are available in groups as follows:

## Parallel Channels in 4 Card Groups (4 Channels/Group)

#### Types:

-3 Volt NTDS interface (fast)

-15 Volt NTDS interface (slow)

+3.5 Volt ANEW interface

#### Modes:

8-bit byte, 16-bit word, or 32-bit dual channel transfers.

Dual channel operations on two 4-channel groups (0 and 1) or (2 and 3) having the same interface types.

Normal transfers available on single or dual channels.

Externally specified addressing (ESA) operation on dual channels.

Intercomputer operation on single or dual channels

Peripheral input simulation on single or dual channels

(NTDS slow interface)

#### Serial Channels in 2 Card Groups (2 Channels/Group)

MIL-STD-188C characteristics/EIA-STD-RS232C characteristics:

2 channels/group

Synchronous - 9600 bits persecond

Asynchronous – 75, 150, 300, 600, 1200, 2400, 4800 or 9600 bits/second (any four may be obtained by the option) program control selection

Character size:

Synchronous or asynchronous -5, 6, 7, or 8 bit (program controlled selection)

NTDS serial interface characteristics:

1 32-Bit Dual Channel/Group Asynchronous — 10 Mbits/second Intercomputer or normal operation

## Serial Channels in 4 Card Groups (4 Channels/Group)

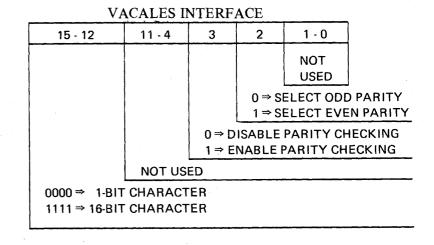

#### **VACALES**

$\label{eq:Synchronous} Synchronous - to 32,000 bits per second \\ Character size - 1-16 bits under program control$

# **Power Supply Input Power**

3 phase Wye 208 volt, 60 Hz or 400 Hz 3 phase Delta 115 volt, 60 Hz or 400 Hz 1 phase 115 volt, 60 Hz or 400 Hz

#### **Optional Cabinet Features**

Langley rack cabinet version External mounting adapters

#### MODULAR ARCHITECTURE

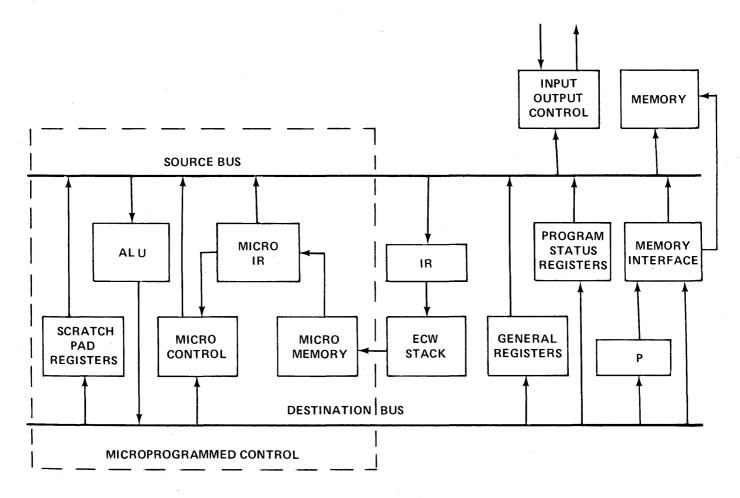

Functionally, the U1600 architecture is organized around a microprogrammed controller and a two-bus data exchange structure. The various functional elements accept bit configurations from the source bus, interpret and manipulate them, and when appropriate, return bit-configured information to the bus for acceptance by another functional element. The second or destination bus provides an additional communication path between the arithmetic and logic unit and the various registers and allows the system to overlap functions. This architectural technique increases processing speed and allows great flexibility in tailoring a system to meet the requirements to special applications. (See Figure 2.)

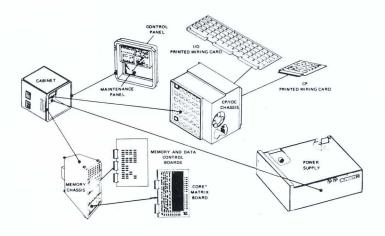

The U1600 is entirely modular. It is in complete compliance with the modularity requirements of MIL-E-16400. The base module of the computer is

the cabinet. As shown in Figure 3, the Central Processor/Input-Output Controller (CP/IOC) chassis, memory, power supply, maintenance panel, and operator panel are basic components of the computer.

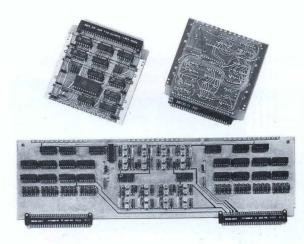

Sperry Univac uses MSI devices for the U1600 logic. The basic replaceable logic unit is a printed circuit card heavily populated with MSI devices. (See Figure 4.) MSI devices combine the flexibility of discrete-component design and the economy, compactness and reliability of large-scale integration. This reduces cost, physical volume and power requirements and also increases circuit speeds. Figure 4 is photo of large and small cards. Plug-in, printed wiring cards are directly inserted into the CP/IOC chassis. Plug-in core matrix boards and printed wiring control boards are directly inserted into the memory module. Careful design of circuits, selection of components and the self contained cooling system assure circuit reliability.

Figure 2. Functional Architecture

Figure 3. U1600 Modular Architecture

Figure 4. Printed Circuit (PC) Card

# CONSTRUCTION

Physically, the functional units are assembled in a cabinet that is constructed from aluminum channel and aluminum sheet and braced to provide structural rigidity. One cooling air inlet is located in the door of the cabinet and the two air exhausts are provided on the left side of the cabinet. Provision has been made in the base for a free-standing mount as well as mounting within a standard 19-inch rack. The front cover incorporates a rugged hinge and latch system that provides a uniform high clamping pressure against the cabinet opening. Gasketing around the periphery of the front cover provides for EMI and moisture sealing. A maintenance panel is located on the inside of the front cover and a control panel on the outside.

The rear of the cabinet contains the I/O connector panel, a power connector and its attendant filter assembly, and DMA optional External Memory bus and external real-time clock jacks (see Figure 5).

The cabinet top is a separate panel which is bolted in place and can be replaced with a water cooled heat exchanger if such a feature were to be required.

Figure 5. U1600 Computer – Rear View

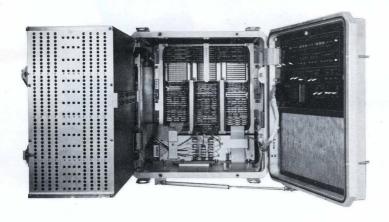

All assemblies have been designed to be repairable in an emergency situation. The only fixed or chassis mounted components are the cooling fans, power line filters and the control/maintenance panel switches and indicators. The assembled computer is shown in Figure 6.

Figure 6. Computer Opened for Maintenance

Optional features offered require only the removal, insertion or substitution of plug-in modules. The U1600 is wired for the maximum configuration which includes:

- 262,144 word memory

- 192 word NDRO memory

- 16 input/output channels consisting of any combination of parallel and serial channels.

- Direct Memory Access

- 32 general registers

- Real-time clock and monitor clock

- 512 words of user defined micromemory

- Connectors mounted in accordance with MIL-F-18870

- MATH PAC

Removal or addition of all options is permitted within the constraints of this maximum configuration.

Design and construction of the U1600 is centered around a selection of high quality components and precise manufacturing processes. Sperry Univac experience in producing equipment for defense systems that are used in military environments provides the techniques for building exceptional quality into the manufactured product. Components selected and assembled under Sperry Univac's quality assurance program produces equipment that operates reliably in adverse environments. This same high quality is a characteristic maintained in all modules of the computer, thereby assuring high reliability for any configuration.

# **MAINTAINABILITY**

Accessibility to replaceable items, easy testing and quick malfunction localization are essential to good and efficient maintenance. Sperry Univac design includes these features. The lowest recommended maintenance level is the printed circuit card. When the cabinet front is opened the maintenance panel is exposed and the memory stacks open out on their hinged supports. Test points are exposed. Printed circuit card modules are accessible for removal or insertion. Any card is removable with a simple tool. Each card has its unique, labeled, keyed position and is guided so that it is aligned properly to the female connector when inserted. Circuits in the memory chassis are accessible from the front of the cabinet. Removing the memory chassis air intake grille exposes the memory chassis circuit boards. After circuit malfunctions have been localized, the memory assembly and logic boards can be pulled out of their slide mountings for replacement. Memory stacks and power supplies can be removed and replaced with simple tools.

Maintenance diagnostic routines for quick malfunction localization are available as built-in and program loaded routines. The built-in microcoded diagnostic routine tests the basic micro instructions, control memory, I/O, lower 16K of memory, I/O instructions and the emulate instruction. The program loaded diagnostic routines are more comprehensive and can be loaded from external memory into computer memory as needed.

#### **FUNCTIONAL ARCHITECTURE**

#### Main Memory

Main memory is an assembly of up to eight 32,768 sixteen-bit word boards of magnetic core storage with a 725-nanosecond read-write cycle time. One such board, with its reading, writing, and addressing circuits, is the basic increment for memory size selection and expansion.

# **Memory Interface**

A single memory interface handles the transfer of information between the processor and main memory and between the memory and the IOC. The input and output functions that are carried out by the IOC are transferred through the interface. Also, access to the NDRO (bootstrap) memory is made through the interface. All 262,144 words of memory may be directly addressed by both the IOC and processor. The processor-verifier (J36) may also interface with an external 262,144-word maximum mass-memory via the external memory bus option.

# **DMA Interface Capability**

The computer design includes a direct memory access (DMA) capability. This allows a customer-provided external controller to read from and write into main memory. This provides a second memory interface in addition to the normal processor-to-memory interface which remains unchanged.

Overall processing throughput can be increased by utilizing the DMA feature which provides an additional access port to each of the two 131K memory banks. This feature adds no additional time to the CP memory references and allows an external device to communicate with one memory bank during the same time period the CP/IOC communicates with the other. Thus, special purpose equipment, that requires a direct access to memory, can be utilized in the U1600 system because it need not share memory time with the running program. The two ports in each memory bank operate on a priority basis. Simultaneous requests for memory access by the CP/IOC and the DMA user are separated to give priority service to the CP/IOC port. If the DMA port initiates a split cycle (Read/Modify/ Write) in one memory bank, and then fails to complete the split cycle with a Write Initiate, that memory bank will wait only approximately 100 usec for the Write Initiate. If there is no Write Initiate during this time, the memory bank will complete the split cycle as a Read/Restore, and then lock out the DMA port for approximately 250 usec. During this 250 usec period, the CPU port will have exclusive use of that memory bank. Any device connected to a DMA port must have its own matching memory interface logic. Memory sharing is possible between two DMA and External Memory bus option equipped U1600's making a total of 524K of common memory available to both computers.

## **Memory Address Allocation**

Main memory is used for storage of programs, constants, and data. Relative addressing to four 64-word page sets in a built-in feature to aid in the development of relocatable software. All locations are accessible to the programs at random and to all sections of the computer. Some locations are given special assignments which programs must respect and provide for their contents. These assigned addresses may be used for general storage when the feature associated with the assignment is not implemented. Table 1 lists the assigned octal addresses.

TABLE 1. ASSIGNED MEMORY ADDRESSES

| Assignment                                                                                     | Addresses (octal)                    |

|------------------------------------------------------------------------------------------------|--------------------------------------|

| NDRO Memory                                                                                    | 00-77 and 300-477                    |

| For Processing Class III Interrupts Class II Interrupts Class I Interrupts Auto Start Entrance | 110-117<br>120-127<br>130-137<br>177 |

| For IOC Operation Command Cells External Interrupt Word Storage (IOC) (Page Set Only)          | 140-141<br>200-217                   |

# **Memory Addressing**

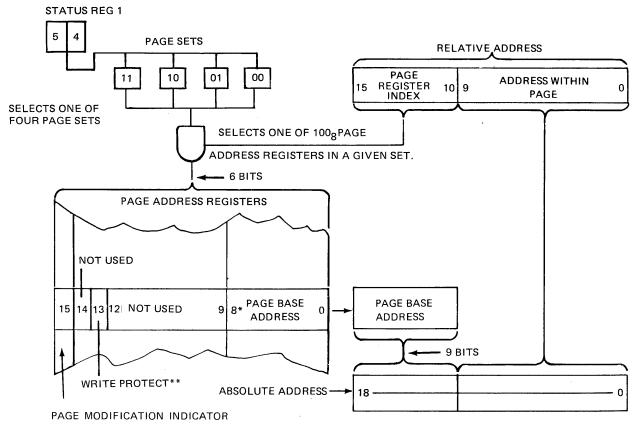

All locations in main memory up to 262,144 words are directly addressable by the central processor and input/output controller. Both the sequential and random access methods are employed. Addresses are specified relative to 2000g word pages. The

lower order ten-bits of the relative address specify the address of a word within a 2000g word page of main memory. The most significant six bits (index) select one register, from a group of 100g page address registers (00-77g), that contains the base address of a specific 2000g word page within main memory. Status register 1 bits 4 and 5 specify which of the four 64-register page sets is to be used. The I/O selection of page register sets 2 or 3 is provided by electing to set bit 13 in the BCW by hard coding. Figure 7 illustrates the final address generated from the two fields of the relative address. Any operation that stores a word in main memory also sets the most significant bit of the page register that was used in generating the memory address.

# **NDRO Memory Feature**

A block of 192 nondestructive readout (NDRO) memory words is provided in the CP. The programs contained in the NDRO memory are fixed at the time of manufacture by the ordering document and cannot be changed by computer read and write operations. The NDRO memory can be changed in the field by a simple and easy card replacement. Addresses assigned to NDRO memory (octal locations 00 through 77 and 300 through 477) parallel similarly numbered relative main memory addresses. A specific bit in status register No. 1 (Figure 8) controls the access to NDRO memory or to corresponding locations in main memory (see Table 1 for address range).

NDRO memory is a convenient storage for programs that will always be available to a computer. These might include an initial load routine which loads a program and checks the validity of the program load and an inspect and change routine.

#### **Bank Select Feature**

The internal memory is normally addressed as two sequential banks of 131,072 words each. Absolute address bit 18 (Figure 7) specifies internal/external memory, address, bit 17 determines which bank of internal memory is to be selected (if bit 18 is a zero), while bits 15 and 16 determine which 32K array within a bank is to be selected. Address bits 15 and 17 may be interchanged on the CPU Mode select card for the CPU port, and these bits may likewise be interchanged at the DMA users interface. The bank addressing would then be interleaved

in 32K blocks of addresses. This feature allows DMA bank selection to be compatible with systems designed around the 65K maximum memory configuration.

# Input/Output Controller

An input/output controller (IOC) relieves the central processor of the computer-peripheral communication burden and permits integrating the U1600 into a system that has an input/output equipment complex established. When an input or output related function is required, the main program initiates an I/O chain that performs the input or output operation according to a stored program defined for the specified channel.

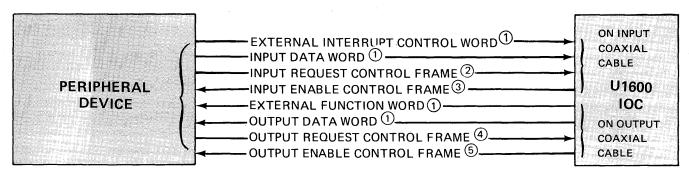

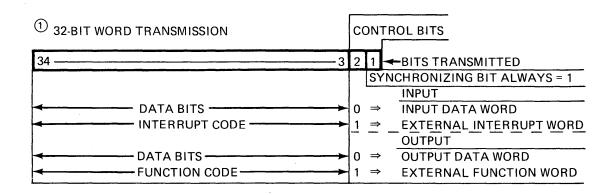

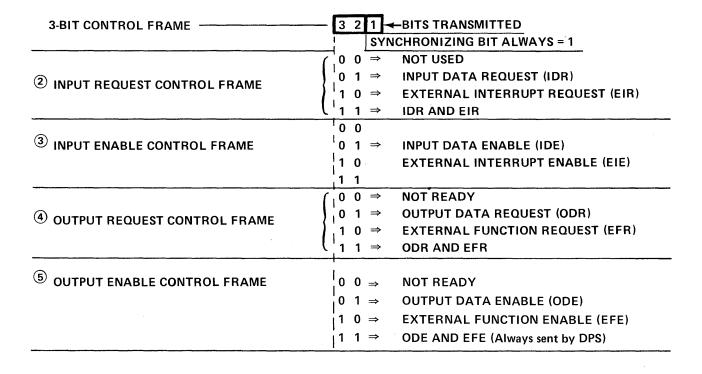

The IOC communicates with external units in the system over the individual IOC-Peripheral equipment interfaces (see Figures 9, 10, 11 and 12) and with memory on the CP/IOC memory bus.

Each IOC-peripheral equipment parallel interface consists of one input channel and one output channel connected to the external device by two respective cables. Output channels are used to transmit data and external functions (or commands) to the peripheral device. Input channels are used to receive data or interrupt codes from the external device.

The complete IOC-peripheral equipment parallel interface has 1, 2, 3, or 4 groups of 4 input and 4 output, 16-bit channels. An 8-bit byte, 16-bit word or a 32-bit double word, parallel interface can be utilized for data transfers. In dual channel modes, the 32-bit parallel transfers use two 16-bit channels (N and N+4) where n = 0.3 or 10-13. All input/ output activity is asynchronous, and the timing is dependent on the speed of the peripheral device compatible with MIL-STD-1397. Serial interfaces for communication circuits are available in asynchronous and synchronous channels. The IOC performs the necessary serial-to-word and word-toserial conversions. Serial channels designed to the EIA-STD-RS232C, MIL-STD-188C or NTDS serial in MIL-STD-1397 are available in 2-channel groups while the VACALES interface is available in 4channel groups.

Interface voltage levels on parallel transfer channels can be supplied in a -15 volt level, a -3 volt level or a +3.5 volt level. See Table 2 for transfer rate.

\*If external memory bus option is incorporated, bit 8 is used for memory select (0 = internal, 1 = external).

Figure 7. Memory Address Generation

<sup>\*\*</sup>The storage of CP registers during an interrupt processing sequence in addresses 110-137 will not be inhibited by an active write protect bit.

# COMPUTER-TO-PERIPHERAL EQUIPMENT INTERFACE (8, 16, OR 32-BIT PARALLEL TRANSFERS)

Figure 9. Parallel Interface

Figure 10. MIL-STD-188C and VACALES Interface

\*PROGRAM CONTROLLED LINES ARE ASSIGNED FUNCTIONS ACCORDING TO THE NEED OF THE PARTICULAR DEVICE CONNECTED TO THE CHANNEL.

Figure 11. EIA-STD-RS232C Interface

(Arrowheads show direction of transmission)

Figure 12. NTDS Serial Channel Interface

TABLE 2. TYPICAL I/O TRANSFER RATES\*

| INTERFACE TYPE                                                                           | OUTPUT                             | INPUT    |

|------------------------------------------------------------------------------------------|------------------------------------|----------|

| Parallel: (words per sec/<br>group)<br>-15V NTDS Slow<br>single channel (8 or<br>16 bit) | 31K                                | 27K      |

| -15V NTDS Slow<br>dual channel (32 bit)                                                  | 30K                                | 26K      |

| -3V NTDS Fast and<br>+3.5V ANEW single<br>channel (8 or 16 bit)                          | 137K                               | 159K     |

| -3V NTDS Fast and<br>+3.5V ANEW dual<br>channel (32 bit)                                 | 123K                               | 135K     |

| Serial:<br>NTDS Serial<br>(32 bit words/sec.)                                            | 111K                               | 108K     |

| EIA-R-232C and<br>MIL-STD-188C                                                           |                                    |          |

| Asynchronous  Synchronous                                                                | 2400,1200<br>150, or 75<br>0 – 960 | Baud     |

| VACALES:<br>Synchronous                                                                  | 0 – 32,0                           | 000 Baud |

\*Note — Under nominal conditions for input or output, actual rates may vary with program and other channel activity.

The memory interface provides the IOC with an access to memory on a time-share basis with the CP. Priority is given to the IOC in case of simultaneous requests.

# **General Registers**

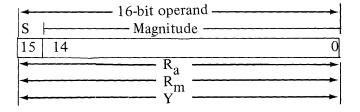

The standard central processor has two sets of 16, high-speed, 16-bit, general purpose registers designated R<sub>0</sub> through R<sub>17</sub> (octal) and an instruction set tailored to their manipulation. The general registers provide for extremely rapid processing of required main memory references. Contents of any number of registers in a set can be changed by one simple instruction which saves program space and 50% of the time to execute the load and store process. With the availability of such registers, programs can be constructed with a greater proportion

of single word (RR format) instructions which decreases both program storage space and program executing time.

A general register can be used as 1) an accumulator for arithmetic, shift, and logical functions; 2) an index register for address and operand modification; and/or 3) a temporary storage location for addresses, operands, etc.

The word format and the operation code of an instruction, that requires a general register reference, define the use of the register; one or both register designator fields (a, m) in that instruction select the register or registers in a set.

A program-controlled 1-bit field in status register 1 selects the set that is used for processor operations. The additional general register set provides greater freedom and increased processing speeds in applications that employ heavy interrupt processing and those that utilize the multi-programming technique. The second general register set is particularly useful in programs requiring rapid task changes. An executive program, for example, that is assigned a set for its own use, need not store the contents of general registers used by worker programs every time it assumes control or when it is requested to process an interrupt.

# **Program Address Register**

The program address register, P, holds the address of the next instruction to be executed in a program sequence. Its contents are advanced by one each time a single-length (16-bit instruction is executed and by two for a double-word instruction. Instructions that cause program transfers (jumps) load the P-register with the entry address of the program that receives control. The variety of ways the P-register contents can be manipulated by instructions provides for efficient program segmentation and for effective use of re-entrant routines.

#### Real-Time Clock and Monitor Clock Feature

The RTC-MON clock feature provides two, program-controlled interrupts via two high-speed registers; one 32-bit register used as RTC count-up storage and the other a 16-bit register as MON clock count-down storage. This feature and associated

controlling instructions are useful for program timing and for synchronous program segments with real-time events. A 1 Khz RTC oscillator, which has an accuracy of  $\pm 2$  counts in 10 seconds, runs continuously and controls the counting speed of both registers. An optional 32 Khz RTC may be ordered in place of the 1 Khz clock. An external clock oscillator with a frequency in the 0 to 50 Khz range may be used instead of the internal oscillator.

# **Breakpoint Feature**

A convenient debugging aid is a breakpoint register than can be loaded and controlled manually by the operator. Breakpoint is a function that stops the computer when it encounters a read or write reference to an address that matches the entry in the breakpoint register. The operator identifies the breakpoint register functions as a read operation or as a write operation, or both, by setting two toggle switches on the operator/maintenance panel.

#### **Power Failure Protection Feature**

The power fault and automatic recovery feature provides a systematic and safe shut-down and recovery capability in the event that any power to modular sections falls below an operable level. Sensors monitor the power supply voltage and when an "out-of-tolerance" voltage is detected, a voltage out signal is generated. When the CP senses the voltage out signal, it generates a power fault interrupt (if enabled by the Load PSW (07RI,RX) instruction), which suspends the normal program sequence, transfers control to the user's software power fault interrupt routine and allows a minimum of 250 microseconds to arrive at an orderly termination. The power fault interrupt routine stores the contents of all working registers and terminates in a jump instruction (operation code 40 RX format, a=6 and m=0) that jumps to itself as long as the voltage "out of tolerance" signal is present. After the signal is removed (power returns to normal), the instruction allows the routine to continue and to restore the working registers and then return control to the program that was interrupted.

If the power continues to drop below operating limits, a CP master clear results in a shut down. When power is reapplied and the AUTO START is

selected, the CP generates an auto start signal that causes execution of the instruction located at address 000 of the NDRO memory. (This address usually contains a jump to the instruction located at the address specified by the contents of memory address 1778.)

The automatic shut-down and recovery routine is a user's software responsibility but should normally perform as described and also be compatible with the Class I interrupt codes assigned.

# Status Register

Status register No. 1 is a 16-bit, high-speed register that provides a dynamic picture of certain processing states. Fields in the status word can be examined or changed by programmed instruction when necessary. During a program interruption (interrupt processing), the computer control logic stores the status word and reloads the register before transferring to the interrupt subroutine. When re-entering the interrupted program, the computer status existing at the time of interruption is reinstated. This allows the program to continue as though it were not interrupted.

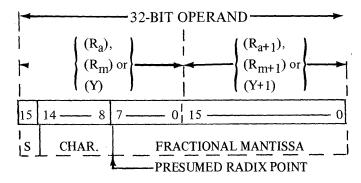

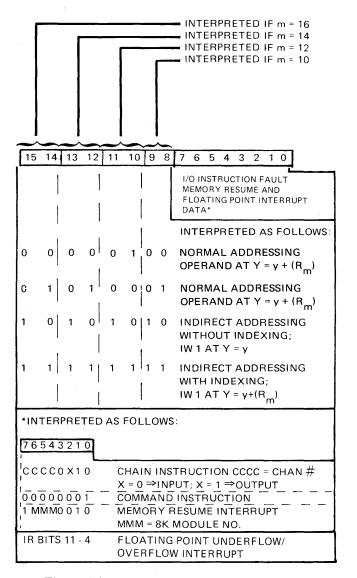

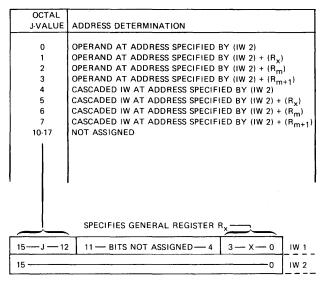

Status register No. 2 (Figure 14) is used to control direct and indirect addressing processes and to hold memory resume interrupt and I/O instruction fault data.

# **FUNCTIONAL OPERATION**

# **Computer Status Control**

The format for status register No. 1 is divided into fields that indicate computer status, interrupt status, and conditions resulting from Arithmetic section operations (see Figure 8).

Details of field designators are as follows:

- a) Bit 0 = 0, disables DMA Bit 0 = 1, enables DMA

- b) Interrupt enable designator:

bit 1 = Class III bit 2 = Class II bit 3 = Class I

When the bit is set, the respective class interrupt

is enabled (can be honored).

c) Page register set, bits 4, 5. Indicates one of four page register sets as shown in Table 3.

TABLE 3. PAGE REGISTER SETS

| Bit 4 | Bit 4 | Page Set |

|-------|-------|----------|

| 0     | 0     | 0        |

| 0     | 1     | 1        |

| 1     | 0     | 2        |

| 1     | 1     | 3        |

- d) Floating point residue designator bit 6=0 specifies that the residue, in a floating point arithmetic operation, will not be saved. Bit 6 = 1 specifies that the residue will be saved.

- e) Floating point over-or-underflow interrupt disable bit 7 = 0 sets the floating point over-flow or underflow interrupt when that result occurs and bits 11 -4 of the instruction register will be stored into bits 7 0 of Status Register 2. If bit 7 = 1, no interrupt is generated on floating point overflow or underflow.

- f) The condition code (bits 9 and 8) indicates the results of arithmetic and compare instructions as shown in Table 4.

- g) The overflow designator (bit 10) is set when an arithmetic or a shift operation produces a result that requires more bits than provided in a register.

- h) The carry designator (bit 11) is set when an arithmetic operation generates a carry beyond the most significant bit in the register.

- i) Floating point underflow/overflow designator (bits 11 and 10) is set when a floating point

operation causes a characteristic underflow or overflow. Bit 11 = 1 and bit 10 = 1, indicate a floating point underflow. Bit 11 = 0 and bit 10 = 1 indicates a floating point overflow. Bits 9 and 8 shall be don't cares in either case.

j) The NDRO Mode (bit 12) directs the CP to select memory as follows for addresses 00 through 77 and 300 through 477:

Bit 12 = 0, Use NDRO memory Bit 12 = 1, Use main memory

k) The general register stack designator (bit 14) specifies the stack of 16 general registers that will be selected by the a- and m-designators in the instruction word.

Status register bit content can be set or cleared by executing the load status register instruction or the load program status word instruction and can be initialized for a class interrupt processing subroutine by loading the "Load Status Register No. 1" memory location assigned to that particular interrupt class.

#### Instructions

Instructions defining operations for the U1600 are designed to maximize circuit effectiveness in attaining high-speed computer functions. The large set of flexible and comprehensive, single and double-word instructions place the computer far beyond the minicomputer capability.

Table 5 lists the instructions and the execution time for each in the applicable formats. Instruction overlap and no memory interleave times were assumed as these are most often encountered. When calculating computer thru-put the I/O data transfer

TABLE 4. CONDITION CODE INDICATIONS

| Condition | on Code | Indicated Re          | esults of                 |

|-----------|---------|-----------------------|---------------------------|

| Bit 9     | Bit 8   | Arithmetic Operation  | Compare Operations        |

| 0         | 0       | Zero                  | $R_a = R_m \text{ or } Y$ |

| 0         | 1       | Not Zero and Positive | $R_a > R_m \text{ or } Y$ |

| 1         | 0       | Not Used              | Not Used                  |

| 1         | 1       | Negative              | $R_a < R_m$ or Y          |

TABLE 5. REPERTOIRE OF INSTRUCTIONS

|          | CODE |          | DESCRIPTION                                                                  | EXECUT           | ION TIME *(M | ICROSEC      | ONDS)        | NOTE<br>REF.  |          | OCTA<br>CODE |     | DESCRIPTION                                                                                       | EXECUTI       | ON TIME *(N           | MICROSE      | conds)                | NOTE<br>REF. |

|----------|------|----------|------------------------------------------------------------------------------|------------------|--------------|--------------|--------------|---------------|----------|--------------|-----|---------------------------------------------------------------------------------------------------|---------------|-----------------------|--------------|-----------------------|--------------|

|          |      | m        |                                                                              | RR               | RI           | RK           | RX           | 11.2.1        |          | a            |     |                                                                                                   |               | RI                    |              |                       |              |

| 00<br>00 |      |          | Diagnostic Return<br>Byte Load                                               | .7               |              | -            | 2.35         |               |          | 1            | }   | Jump on Carry                                                                                     | 1.14<br>1.14  |                       | 1.95<br>1.95 | 2.4<br>2.4            |              |

| 01       | - 1  | j        | Load                                                                         | .84              | 1.56         | 1.66         | 2.35         |               |          | }            |     | Jump Power Out<br>Jump Bootstrap 2                                                                | 1.14          | _                     | 1.95         | 2.4                   |              |

| 02       |      | 0        | Make Positive<br>Make Negative                                               | 1.24<br>1.42     | _            | - )          |              |               |          | 10<br>11     |     | Jump<br>Jump Stop                                                                                 | 1.14          |                       | 1.95         | 2.4                   |              |

|          |      | 2        | Round R <sub>a</sub>                                                         | 1.56             | _            |              | -            |               | 1        | 12           |     | Jump Stop<br>Jump Stop Key 1                                                                      | _             | _                     | _            | - {                   |              |

|          |      | 4        | Two's Complement Single Two's Complement Double                              | .84<br>1.74      | -            | - 1          | -            |               | 140      | 13           |     | Jump Stop Key 2                                                                                   | _             | 1.32                  | -            | -                     |              |

|          |      | 5        | One's Complement Single                                                      | .84              | _            | -            | _            | 1             | 40<br>41 |              | ĺ   | Local Jump<br>Index Jump                                                                          | 1.46          | - 1.32                | 2.15         | 2.50                  |              |

|          |      | 10       | Increase R <sub>a</sub> by 1                                                 | .84<br>.84       | _            | -            | -            |               | 41<br>42 |              |     | Local Jump Indirect                                                                               | 1.28          | 2.20                  | 2.15         | 2.35                  |              |

|          |      | 11       | Decrease R <sub>a</sub> by 1<br>Increase R <sub>a</sub> by 2                 | 1.1              | _            | -            | _            |               | 42       | -            |     | Jump and Link Register Local Jump and Link Memory                                                 | -             | 2.15                  | 2.15         | - 2.35                |              |

| .        | ľ    | 13       | Decrease Ra by 2                                                             | 1.1              | <br>2.4      | -            | <br>3.15     |               | 43       |              |     | Jump and Link Memory                                                                              | 1.48          | -                     | 2.4<br>2.15  | 3.05<br>2.35          |              |

| 02       | }    | 0        | Load Double<br>Executive Return                                              | 10.0             | 2.4          | _            | J. 15<br>-   |               | 44       |              |     | Jump Register Zero Local Jump Equal                                                               | -             | 1.32                  | 2.15         | - 2.35                |              |

|          | }    | 1        | Store Status Register 1                                                      | 1.0              | -            | -            | -            |               | 45<br>45 |              |     | Jump Register Not Zero                                                                            | 1.48          | 1.22                  | 2.15         | 2.35                  |              |

|          | - }  | 2        | Store Status Register 2<br>Store RTC Lower                                   | 1.0<br>1.0       | _            | _            | _            |               | 46       |              |     | Local Jump Not Equal<br>Jump Register Positive                                                    | 1.48          | 1.32                  | 2.15         | 2.35                  |              |

|          |      | 4        | Load P                                                                       | 1.3              | -            | -            | -            | ĺ             | 46       | İ            | 1   | Local Jump Greater Than or Equal                                                                  | - 40          | 1.32                  | -            | - 0.15                |              |

|          | [    | 5        | Load Status Register 1<br>Load Status Register 2                             | 1.6<br>1.0       | _            | -            | _            |               | 47       | 1            |     | Jump Register Negative<br>Local Jump Less Than                                                    | 1.48          | 1.32                  | 2.15         | 2.15                  |              |

|          | Ì    | 7        | Load RTC Lower                                                               | 1.0              | -            | -            | -            | } }           | 50       | 1            | ł   | Floating Point Subtract                                                                           | 7.7-19.0      | 7.7-18.85             | ] -          | 7.7-19.7              | 8,10         |

|          |      | 10       | Enable RTC Disable RTC                                                       | 1.3<br>1.3       | _            | _            | _            |               | 51<br>52 |              |     | Floating Point Add Floating Point Multiply                                                        | 7.7-18.7      | 7.7-18.7<br>15.2-20.3 | -            | 7.7-19.5<br>15.2-21.2 | 8,10<br>8.10 |

|          | - 1  | 12       | Load and Enable MON, Clock                                                   | 1.46             | -            | -            | -            |               | 53       | İ            |     | Floating Point Divide                                                                             | 7.7-25.7      | 7.7-25.7              | -            | 7.7-26.4              | 8,10         |

|          |      | 13<br>14 | Disable MON, Clock<br>Load RTC Double                                        | 1.0<br>1.6       | _            |              |              |               | 54<br>54 |              |     | Load Address Register Load Address Register Multiple                                              | 1.46          | 1.65                  | -            | 3.4                   | 14           |

|          |      | 15       | Store RTC Double                                                             | 1.6              | -            | -            | -            | ĺ             | 55       |              |     | Store Address Register                                                                            | 1.79          | 2.5                   | -            | -                     |              |

|          |      | 16<br>17 | Enable RTC Interrupt<br>Disable RTC Interrupt                                | 1.0<br>1.0       | _            | _            | _            |               | 55<br>56 | }            | 1   | Store Address Register Multiple Double Multiply                                                   | 9.35          | 9.60                  | -            | 3.7<br>10.6           | 10           |

| 03       | - (  | - (      | Load Multiple                                                                | -                | -            | -            | 2.35         | 1             | 57       | ļ            |     | Double Divide                                                                                     | 17.9          | 21.0                  |              | 21.5                  | ļ            |

| 04       | l    | 0        | Square Root<br>Reverse Register                                              | 9.65<br>6.5      | -            | _            | _            | 11            | 60       | ļ            | 1   | Logical Right Single Shift Algebraic Right Single Shift                                           | RL 1<br>RL 2  | 1.1 -<br>1,1          | 1            |                       |              |

|          |      | 2        | Count Ones                                                                   | 7.0              | . –          | - )          |              |               | -        | ,            |     | Logical Right Double Shift                                                                        | RL-3          | 2.15                  | [            |                       |              |

| 04       |      | 3        | Scale Factor Shift<br>Byte Load and Index by 1                               | 3.2              | -            | -            | 2.45         |               | 61       |              |     | Algebraic Right Double Shift<br>Algebraic Left Single Shift                                       | RL-4<br>RL-1  | 2.15<br>3.0           | ĺ            |                       |              |

| 05       |      | ]        | Set Bit                                                                      | 1.21             | -            | - [          | -            |               | 1        | !            |     | Circular Left Single Shift                                                                        | RL-2          | 1.1                   | l            |                       |              |

| 05<br>06 | 1    |          | Load and Index by 1<br>Clear Bit (Zero Bit)                                  | -<br>1.23        | 1.6          | - 1          | 2.45         |               | ľ        | 1            |     | Algebraic Left Double Shift<br>Circular Left Double Shift                                         | RL-3<br>RL-4  | 4,55<br>2,15          | RL           |                       |              |

| 06       | - [  | - 1      | Load Double and Index by 2                                                   | -                | 2.55         | _            | 3.4          |               | 62       | 1            | 1   | Substract                                                                                         | RL-1          | 1.4                   | FORM         | AT <sup>.</sup>       |              |

| 07<br>07 | - 1  | İ        | Test Bit<br>Load PSW                                                         | 1.6              | 3.2          | - 1          | 4.05         |               | - [      |              | 1   | Subtract Double<br>Add                                                                            | RL-2<br>RL-3  | 2.15<br>1,4           | 1            |                       |              |

| 10       |      | 1        | Logical Right Single Shift                                                   | .94              | -            | 1.76         | -            |               |          |              |     | Add Double                                                                                        | RL-4          | 2.15                  | 1            |                       | [            |

| 10       |      |          | Byte Store<br>Algebraic Right Single Shift                                   | -<br>.95         | -            | 1.8          | 2.4          |               | 63       | !            |     | Load Compare                                                                                      | RL-1<br>RL-2  | 1.1<br>1.56           | 1            |                       |              |

| 11       |      |          | Store Store                                                                  |                  | 1.6          | -            | 2.45         |               |          |              |     | Multiply                                                                                          | RL-3          | 4.2                   | 1            |                       | l            |

| 12       |      |          | Logical Right Double Shift                                                   | 2.0              |              | 2.8          | - 2.15       |               | ı        | 1            |     | Dívide                                                                                            | RL-4          | 7.4<br>RI             | RK           | RX                    |              |

| 12       | - 1  |          | Store Double<br>Algebraic Right Double Shift                                 | 2.0              | 2.35         | 2.85         | 3.15         |               | 64       | 1            | 1   | Byte Subtract                                                                                     |               | -                     |              | 2.35                  | †            |

| 13       |      | 1        | Store Multiple                                                               | _                | _            |              | 2.4          | 2             | 65<br>66 |              | 1   | Byte Add                                                                                          | -             |                       | -            | 2.35<br>2.40          |              |

| 14<br>14 |      | 1        | Algebraic Left Single Shift<br>Byte Store and Index by 1                     | 2.3<br>-         |              | 3.15         | 2.25         |               | 67       |              |     | Byte Compare<br>Reserved                                                                          | -             | _                     | _            | 2.40                  |              |

| 15       | 1    |          | Circular Left Single Shift                                                   | .94              | -<br>1.64    | 1.75         | <br>2.35     | ] ]           | 67<br>70 |              |     | Byte Compare and Index by 1                                                                       | -             | 2.6                   | -            | 2.6                   |              |

| 15<br>16 |      |          | Store and Index by 1 Algebraic Left Double Shift                             | 3.9              | 1.04         | 4.7          | 2.35         |               | 1′0      |              | 4   | Master Clear Enable All External Interrupts                                                       | 18.9<br>10.5  | İ                     | i            |                       | 1            |

| 16       |      |          | Store Double and Index by 2                                                  | -                | 2.35         | -            | 3.15         | 1 1           | İ        | İ            | 5   | Disable All External Interrupts                                                                   | 10.5          | 1                     |              |                       |              |

| 17<br>17 | [    |          | Circular Left Double Shift<br>Store Zeros                                    | 2.0              | 1.6          | 2.85         | 2.2          | 1 1           | - 1      | 1            | 6 7 | Enable All External Monitors Disable All External Monitors                                        | 10.5<br>10.5  |                       |              |                       |              |

| 20       |      |          | Subtract                                                                     | .84              | 1.6          | 1.84         | 2.35         | 1             | 1        | ŀ            | 10  | Master Clear Chan a                                                                               | 3.25          |                       | }            |                       |              |

| 21       | ł    | ł        | Subtract Double<br>Add                                                       | 1.74<br>.84      | 2.45<br>1.6  | 1.68         | 3.2<br>2.3   |               | - 1      |              | 14  | Enable Chan a Ext. Int. Disable Chan a Ext. Int.                                                  | 2.75<br>2.75  |                       |              |                       | 7            |