#### SECTION 6 - ARITHMETIC SECTION

6.1. X-D' ADDER

#### 6.1-1. OBJECTIVES

To present the detailed theory of operation involved in the X-D' adder.

#### 6.1-2. INTRODUCTION

The X-D' adder is used in most addition, subtraction, multiplication, and division operations as well as in many other operations where it is used simply as a transmission path.

#### 6.1–3. REFERENCES

- a. UNIVAC 1219 Technical Manual, Volume I, Paragraph 4-4b(3).

- b. UNIVAC 1219 Technical Manual, Volume II, Section 9 (logic diagrams).

#### 6.1-4. INFORMATION

Þ

a. <u>General Description</u>. The X-D' adder is 18 bit positions in length. The outputs of the X and D registers are hard-wired to the adder. The logic is so arranged that the adder actually performs the subtraction of X-D'. The adder's output can be taken to AU, AL, P, S1, and Z1 registers.

The adder is of the end-around borrow type. When a borrow is needed from beyond bit position  $2^{17}$ , it is taken end-around from bit position  $2^{00}$ . In this sheet, a borrow being subtracted from a bit position is described as being applied to that bit position. Borrow and borrow request have the same meaning.

b. Adder Theory.

l. <u>Half-Subtract Method of Subtraction</u>. The X-D' adder employs the half-subtract method of subtraction. Refer to table 6.1-1 for the truth table description of half-subtraction.

The half-subtract is formulated by subtracting each bit position without considering borrows. Each bit position half-subtract is entirely independent of other bit positions.

After the half subtract for each bit position is produced, borrows are considered. If no borrow is applied to a bit position, the adder output is the half-subtract (HS). If a borrow is applied, the adder outputs the complement of the half-subtract (HS'). Refer to figure 6.1-1 for an example of the half-subtract method of subtraction with end-around borrow.

| ADDER INPUTS | HALF SUBTRACT |

|--------------|---------------|

| 00           | 0             |

| 01           | 1             |

| 10           | 1             |

| 11           | 0             |

|              |               |

TABLE 6.1-1. HALF-SUBTRACT TRUTH TABLE

| BIT POSITIONS | 17  | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 09  | 80   | 07 | 06 | 05  | 04 | 03 | 02 | 01 | 00   |

|---------------|-----|-----|----|----|----|----|----|----|-----|------|----|----|-----|----|----|----|----|------|

|               | 0   | l   | 0  | I  | 0  | 1  | 0  | 0  | 1   | 0    | 0  | I  | 1   | 0  | 0  | I  | 1  | 0    |

|               | -0  | 1   | 1  | 1  | 0  | 0  | 0  | 0  | 0   | l    | I  | 0  | 0   | 1  | 0  | 1  | 0  | 0    |

| HALF SUBTRACT | = 0 | 0   | I  | 0  | 0  | 1  | 0  | 0  |     | 1    | I  | I  | 1   |    | 0  | 0  | I  | 0    |

| OUTPUT TERM = | нs' | нs' | НS | НS | нs | нѕ | нs | нs | нs' | н s' | нs | нs | нs' | НS | НS | нs | нs | H S' |

| BINARY OUTPUT | = 1 | l   | 1  | 0  | 0  | 1  | 0  | 0  | 0   | 0    | I  | I  | 0   | l  | 0  | 0  | 0  | l    |

Figure 6.1-1. Example of Half-Subtract Method of Subtraction

The result produced is the same as can be obtained by the normal pencil and paper method. A summation of the borrow conditions in this example is as follows:

a) A borrow is applied to bit position 05 from bit position 04.

b) A borrow is applied to bit positions O8 and O9 from bit position 07.

c) A borrow is applied to bit positions 17 and 16 and end-around to 01 and 00 from bit position 15.

Hereafter, the term stage is used in place of bit position.

2. <u>Generation of a Borrow Request</u>. There is only one bit configuration which will generate a request for a borrow, referred to simply as a borrow. A borrow is generated if, in the same stage, X is  $O_2$  and D' is  $l_2$ . The number of stages affected by this borrow is dependent upon the configurations of the more significant stages.

3. Borrow Enable. There is only one bit configuration which will satisfy or absorb a borrow. If a borrow is applied to it, the bit inputs can supply the required 12 without propagating the borrow request to the next higher stage. A borrow enable condition exists if, in the same stage, X is  $1_2$  and D' is  $0_2$ . In

this condition, a borrow will affect only this stage and will not be transmitted to higher stages.

#### c. Detailed Analysis.

#### 1. Adder Logic Technique.

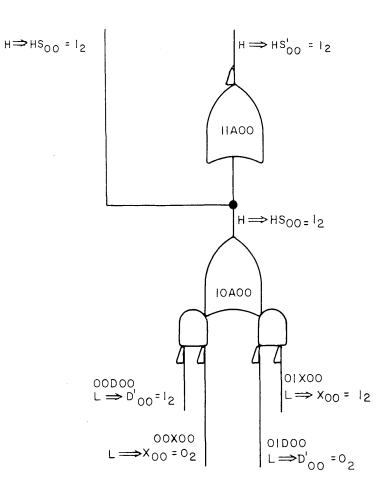

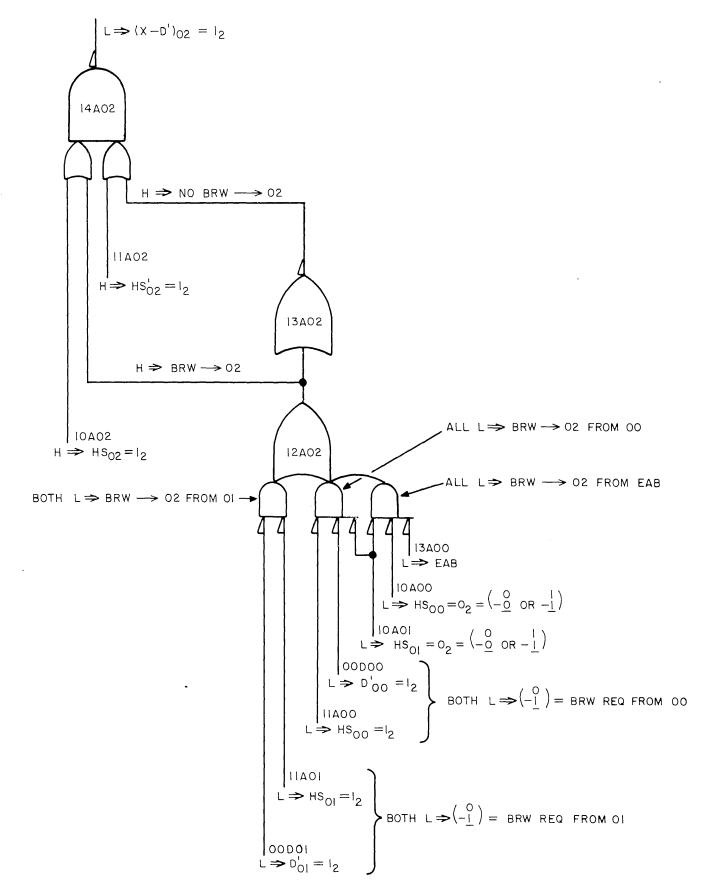

a) <u>Formulation of HS and HS</u>'. Each adder stage has logic circuitry which produces the half subtract and its complement. Refer to figure 6.1-2 for an example using stage 00.

In this example 10A00 can be considered to test  $X_{00}$  and D'00 for the two possible configurations resulting in HS =  $1_2$ . With the use of 11A00, high levels for both HS =  $1_2$  and HS' =  $1_2$  are available.

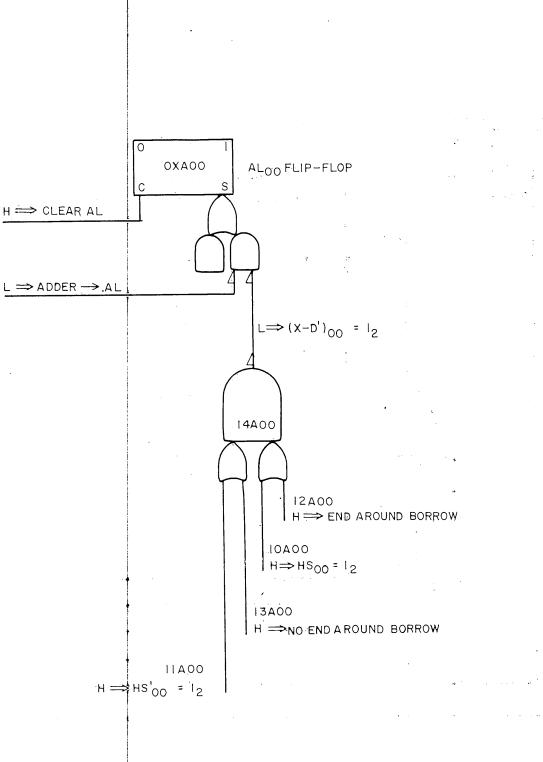

b) <u>Application of Borrow</u>. Either the HS or HS' result is outputted from the adder depending upon the application of borrows to the particular stage. If no borrow is applied, HS is the final result. If a borrow is applied, HS' is the final result. Refer to figure 6.1-3 for an example.

If no borrow is applied to stage 00, 13A00 is a high level input and 12A00 is a low level input. This condition allows the adder output to be determined by input 10A00. 14A00 will output a low level if  $HS_{00} = 1_2$ .

In this example, the output is taken to AL. AL is initially cleared to 0's. Then the Adder  $\rightarrow$  AL signal occurs. AL<sub>00</sub> is set to 1<sub>2</sub> only if 14A00 outputs a low level which represents the adder output of 1<sub>2</sub>.

If a borrow is applied to stage OO, 12AOO is a high level input and 13AOO is a low level input. This condition allows the adder output to be determined by input 11AOO. 14AOO will output a low level if  $HS'_{OO} = 12$ .

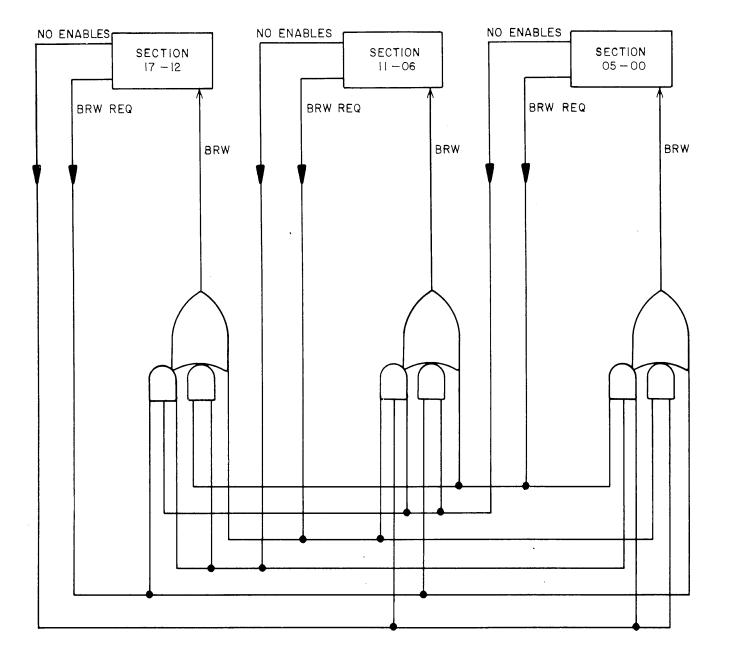

2. <u>Adder Layout</u>. The X-D' adder is divided into three sections comprised of stages 05-00, 11-06, and 17-12. Each section has circuitry to sense borrows applied from other sections. Refer to figure 6.1-4 for a block diagram illustrating the section interconnection. Inter-section borrow requests are discussed later in this sheet.

Each stage of the adder senses borrows generated by the less significant stages in the section and the enable conditions of these bits in order to detect borrows which might affect its own output.

So as to speed the borrow propagation time, each 6-stage section is further separated into two groups.

#### 3. Individual Stage.

a) <u>Stage 00</u>. Refer to figures 6.1-2, 6.1-3, and logic diagrams, figure 9-94. Review the operation of this stage as described previously. A borrow applied to this stage is always an end-around borrow.

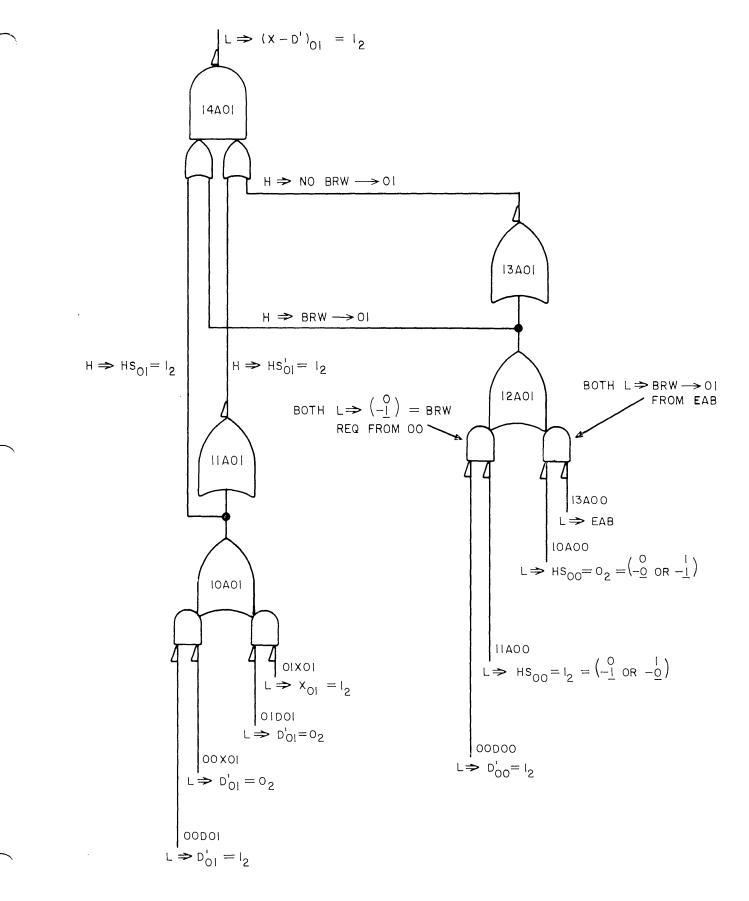

b) <u>Stage O1</u>. Refer to figure 6.1-5 and logic diagrams, figure 9-94. The only difference from stage OO is the borrow sensing logic. 12AO1 outputs a high level if a borrow is applied. There are only two possible conditions which can apply a borrow to this stage. Refer to table 6.1-2 for these conditions.

Figure 6.1-2. X-D' Adder HS and HS' Logic, Stage 00

Figure 6 1-3., X-D' Adder Output Logic, Stage 00

Figure 6.1-4. X-D' Adder Inter-Section Block Diagram

.

Figure 6.1-5. X-D' Adder, Stage 01

TABLE 6.1-2. X-D' ADDER, BORROWS APPLIED TO STAGE O1

| CONDITIONS                           | INPUT LEVELS TO 12A01 |

|--------------------------------------|-----------------------|

| Brw Req from OO                      | 00D00 & 11A00 = L's   |

| No enable & no Brw<br>Req in OO, EAB | 10A00 & 13A00 = L's   |

c) <u>Stage 02</u>. Refer to figure 6.1-6 and logic diagrams, figure 9-94. 12A02 outputs a high level if a borrow is applied. There are only three possible conditions which can apply a borrow to this stage. Refer to table 6.1-3 for these conditions.

TABLE 6.1-3. X-D' ADDER, BORROWS APPLIED TO STAGE 02

| CONDITIONS                                          | INPUT LEVELS TO 12A02       |

|-----------------------------------------------------|-----------------------------|

| Brw Reg from Ol                                     | 00D01 & 11A01 = L's         |

| No Enable & no<br>Brw Req in Ol,<br>Brw Req from OO | 11A00, 00D00, & 10A01 = L's |

| No Enable & no<br>Brw Req in Ol &<br>OO, EAB        | 10A01, 10A00, & 13A00 = L's |

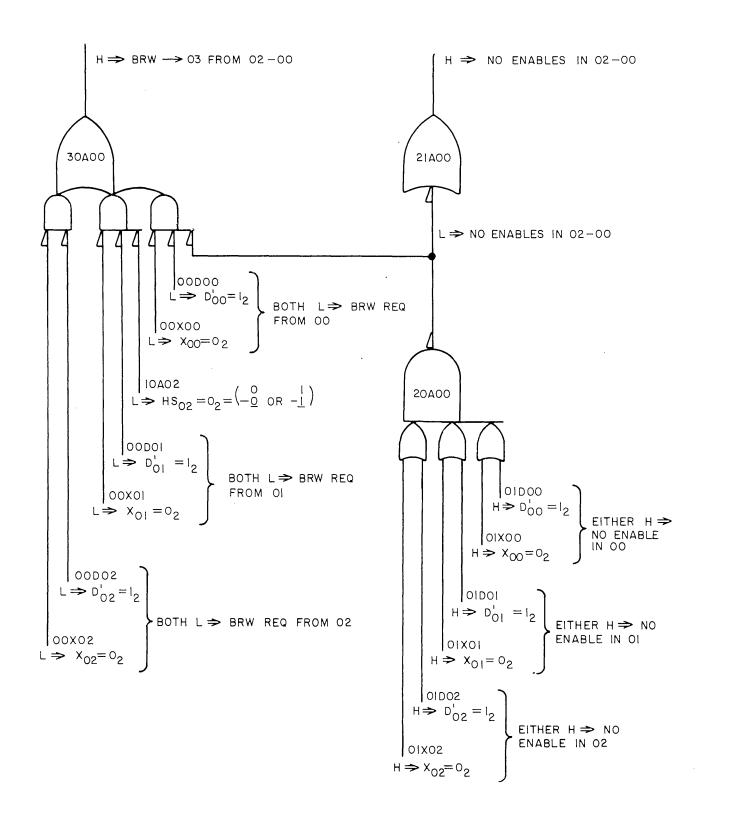

d) <u>Stage 03</u>. Each 6-stage section is separated into two groups, as mentioned previously. The three stages discussed above comprise one group. Stage 03 is the start of the second three-stage group. So as to speed the borrow request propagation, the stage 03 borrow request detection logic is directly fed by the X and D register flip-flops for stages 02 through 00. Refer to figure 6.1-7 and logic diagrams, figure 9-91, for a portion of the stage 03 logic.

This logic simply provides stage 03 with the borrow request and enable status of stages 02 through 00. 20A00 determines if any of these lower three stages has an enable condition which would satisfy and stop a borrow request. An enable condition exists if X is  $l_2$  and D' is  $0_2$  in the same stage. If all input OR gates to 20A00 are satisfied, each of the stages contains no enable. 21A00 passes this information to the remainder of the stage 03 logic.

30A00 is used to detect borrows applied to stage 03 from within stages 02 through 00. Refer to table 6.1-4 for these borrow conditions.

Figure 6.1-6. X-D' Adder, Stage 02

Figure 6.1-7. X-D' Adder, Stage O3 Preliminary Borrow Request Detection Logic

CONDITIONSINPUT LEVELS TO 30A00Brw Req from 0200X02 & 00D02 = L'sNo enable & no<br/>Brw Req in 02,<br/>Brw Req from 0100X01, 00D01, & 10A02 = L'sNo Enables in 02-00,<br/>Brw Req in 0000X00, 00D00, & 20A00 = L's

TABLE 6.1-4. X-D' ADDER, BORROWS APPLIED TO STAGE 03 FROM 02-00

Refer to figure 6.1-8 and logic diagrams, figure 9-94.

12A03 receives the outputs of 12A00 and 30A00 discussed above. If a borrow is applied to stage 03, 12A03 outputs a low level. There are two conditions which can create this borrow. Input 30A00 satisfies 12A03 if a borrow is generated within stages 02 through 00 and is propagated from this group.

Input 12A00 applies a borrow to this stage if there is an end-around borrow which cannot be satisfied within stages 02 through 00. 21A00 inputs a high level to enable the borrow propagation to stage 03.

e) <u>Stages 17-04</u>. The logic for these stages is similar to that described above. Refer to logic diagrams, figures 9-91 through 9-96 for the logic concerning these stages. Inter-section borrows are discussed later in this sheet.

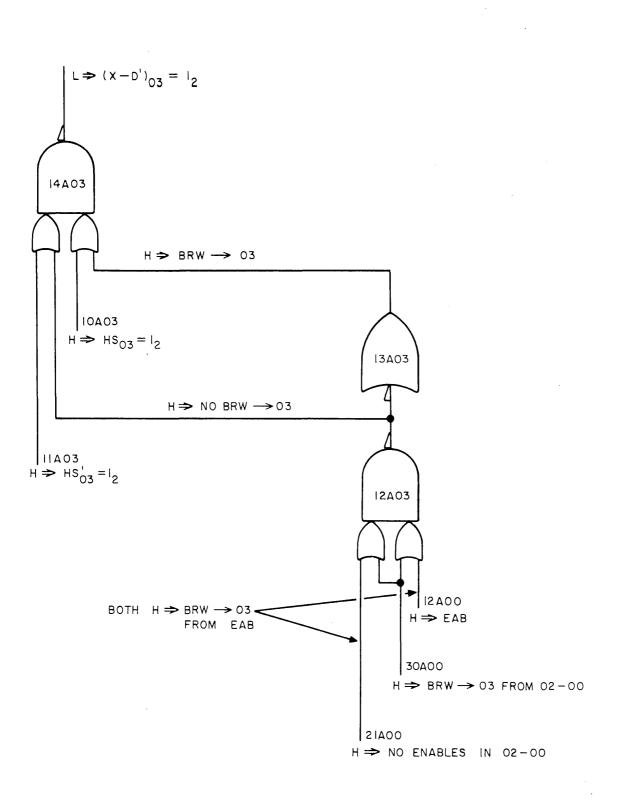

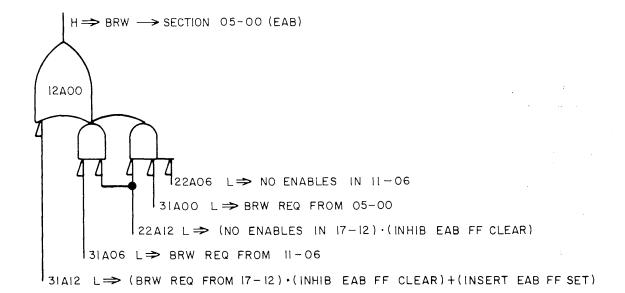

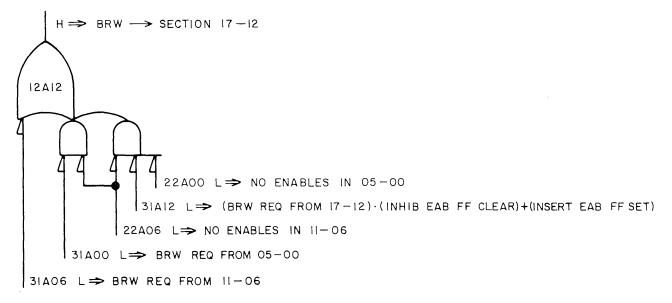

4. <u>Generation of Inter-Section Borrow and Enable Signals</u>. Section 05-00 is used for an example. Refer to figure 6.1-9 and logic diagrams, figure 9-91.

The logical functions of 30A03, 20A03, and 21A03 are the same as for 30A00, 20A00, and 21A00 described previously. Only the stage numbers are different. Therefore, 22A00 outputs a low level if there are no enables in this section (05-00). This signal indicates to other sections that if a borrow should be applied to section 05-00, it would not be satisfied and would be propagated to the next higher section.

31A00 outputs a low level to indicate that a borrow request is generated in section 05-00 and is not satisfied within this section. Therefore, this low level would apply a borrow to the next higher section. Refer to table 6.1-5 for the borrow generating conditions.

TABLE 6.1-5. X-D' ADDER, BORROW REQUESTS FROM SECTION 05-00

| CONDITIONS                                 | INPUT LEVELS TO 31A00 |

|--------------------------------------------|-----------------------|

| Brw Req from 05-03                         | 30A03 = H             |

| No Enables in 05-03,<br>Brw Req from 02-00 | 30A00 & 21A03 = H's   |

Figure 6.1-8. X-D' Adder, Stage 03 Final Portion

$H \implies BRW REQ FROM 05-03$

Figure 6.1-9. X-D' Adder, Inter-Section Borrow Request and Enable Generation

The other two sections generate these same borrow request and enable signals in the same manner. Section 17-12 considers two additional factors in developing these outputs. This section is affected by the status of the Inhibit EAB and Insert EAB flip-flops. If the Insert EAB flip-flop is set, a simulated borrow request is generated by section 17-12. If the Inhibit EAB flip-flop is set, a borrow request (other than the simulated request) from section 17-12 is inhibited. Also, this section is forced to indicate that it contains an enable condition. This simulated enable causes a borrow which is applied to this section from either section 11-06 or section 05-00 to be satisfied. Thus, an end-around borrow is inhibited.

Refer to logic diagrams, figure 9-93 for the effect of the Inhibit EAB and Insert EAB flip-flops.

22A12 outputs a low level if there are no enables in section 17-12 and the Inhibit EAB flip-flop is clear. 31A12 outputs a low level if there is a borrow request from section 17-12 and the Inhibit EAB flip-flop is clear or if the Insert EAB flip-flop is set.

Refer to logic diagrams, figure 9-92 for the borrow request and enable signals generation logic for section 11-06.

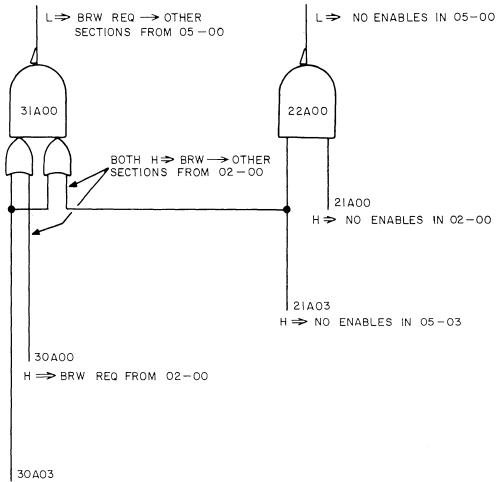

5. Detection of Inter-Section Borrow Requests. Each section evaluates the status of the other sections to determine whether there is a borrow applied to it. A borrow is applied to a section only if there are no enable conditions existing between that section and the section which generated the borrow request. Refer to figure 6.1-4 for a review of the section interconnection.

Refer to figure 6.1-10 and logic diagrams, figures 9-94 through 9-96 for the intersection borrow request detection logic.

Each gate shown in figure 6.1-10 senses three conditions which can apply a borrow to its section. Refer to table 6.1-6, 6.1-7 and 6.1-8 for these conditions.

#### 6.1-5. SUMMARY

The X-D' adder is an 18-bit, end-around borrow adder. It is separated into three sections so as to speed the borrow request signal propagation. The X and D registers are hard-wired inputs to the adder logic. The adder's result is not used until the desired values have been entered into X and D and enough time has expired to allow propagation of any borrows.

Figure 6.1-10. X-D' Adder, Inter-Section Borrow Request Detection

| SECTION 17-12 | SECTION 11-06 | SECTION 05-00 | INPUT LEVELS TO 12A00       |

|---------------|---------------|---------------|-----------------------------|

| Brw Req       |               |               | 31A12 = L                   |

| No Enables    | Brw Req       |               | 31A06 & 22A12 = L's         |

| No Enables    | No Enables    | Brw Req       | 22A12, 31A00, & 20A06 = L's |

# TABLE 6.1-6. X-D' ADDER, INTER-SECTION BORROWS APPLIED TO SECTION 05-00

# TABLE 6.1-7.X-D' ADDER, INTER-SECTION BORROWS APPLIEDTO SECTION 11-06

| SECTION 17-12 | SECTION 11-06 | SECTION 05-00 | INPUT LEVELS TO 12A06       |

|---------------|---------------|---------------|-----------------------------|

|               |               | Brw Req       | 31A00 = L                   |

| Brw Req       |               | No Enables    | 31A12 & 22A00 = L's         |

| No Enables    | Brw Req       | No Enables    | 22A00, 31A06, & 22A12 = L's |

# TABLE 6.1-8.X-D' ADDER, INTER-SECTION BORROWS APPLIEDTO SECTION 17-12

| SECTION 17-12 | SECTION 11-06 | SECTION 05-00 | INPUT LEVELS TO 12A12       |

|---------------|---------------|---------------|-----------------------------|

|               | Brw Req       |               | 31A06 = L                   |

|               | No Enables    | Brw Req       | 31A00 & 22A06 = L's         |

| Brw Req       | No Enables    | No Enables    | 22A06, 31A12, & 22A00 = L's |

NAME:

# 6.1-6. STUDY QUESTIONS

a. Given:  $AL_i = 612160$   $SR = 01010_2$ instruction = 141000 content of address 21000 = 161307

Refer to logic diagrams, figures 9-91 through 9-96. Give the output logic levels for the following gates which exist during the time that the X-D' adder is used in the execution of the above instruction to add AL + Y.

| 31A00 = | 31A12 = |

|---------|---------|

| 22A00 = | 22A12 = |

| 31A06 = | 12A00 = |

| 22A06 = | 12A06 = |

|         | 12A12 = |

# b. Given conditions same as above.

At the completion of the instruction, the final content of AL is  $773463_{\Theta}$ . Refer to logic diagrams, figure 9-94. Assume each of the following malfunctions to occur individually. Determine whether each malfunction would cause the erroneous AL result. Indicate your answers by writing "yes" or "no" beside each malfunction condition.

| Grounded Output | Constant Low Level Output |

|-----------------|---------------------------|

| 12A00           | 12A00                     |

| 10A02           | 10A02                     |

| 11A02           | 11A02                     |

| 12A02           | 12A02                     |

| 13A02           | 13A02                     |

| 14A02           | 14A02                     |

c. Refer to logic diagrams, figures 9-94 and 9-96.

| Given:  |        | out | cput | is a    | higl | level.<br>1 level<br>1evel. |                 |          |                 |

|---------|--------|-----|------|---------|------|-----------------------------|-----------------|----------|-----------------|

| bit pos | itions | 2   | 217  | $2^{1}$ | 6    | $2^{15}$                    | 2 <sup>14</sup> | $2^{13}$ | 2 <sup>12</sup> |

|         | Х      | =   | ?    | 1       |      | 0                           | Ś               | 0        | 1               |

|         | D      | Ξ   | ?    | 0       |      | 0                           | ?               | 1        | 0               |

There are no malfunctions. Use the above information to determine the binary contents of X and D bit positions  $2^{17}$  and  $2^{14}$ . Indicate your results below. Notice that D, rather than D', is referenced.

#### SECTION 6 - ARITHMETIC SECTION

#### 6.2. INSTRUCTION EXECUTION OF SKPODD, SKPEVN AND PARITY EVALUATOR

#### 6.2-1. OBJECTIVES

To present the detailed theory of operation involved in the execution of the parity instructions and the parity evaluator.

#### 6.2–2. INTRODUCTION

Parity refers to the number of  $l_2$ 's, thus, every word has either odd or even parity. The parity evaluation function of the 1219 is useful in determining whether a data word has lost or gained a  $l_2$ .

#### 6.2–3. REFERENCES

UNIVAC 1219 Technical Manual, Volume II, Section 9 (logic diagrams).

#### 6.2-4. INFORMATION

a. SKPODD, SKPEVN Instructions.

1. General Description.

a) Instruction Interpretation.

1) <u>SKPODD</u>, f = 50:54. This instruction formulates the logical product (AND function) of AU  $\cdot$  AL. The parity of their result is evaluated and causes a program skip of the next sequential instruction if the parity is odd. The contents of AU and AL are not disturbed.

2) <u>SKPEVN, f = 50:55</u>. Except for the effect of the parity evaluation, this instruction is the same as f = 50:54. A program skip is performed if the parity is even.

b) Execution Sequence (I). All operations are performed within the I-sequence. Only the one memory reference to obtain the instruction is necessary.

2. Detailed Analysis.

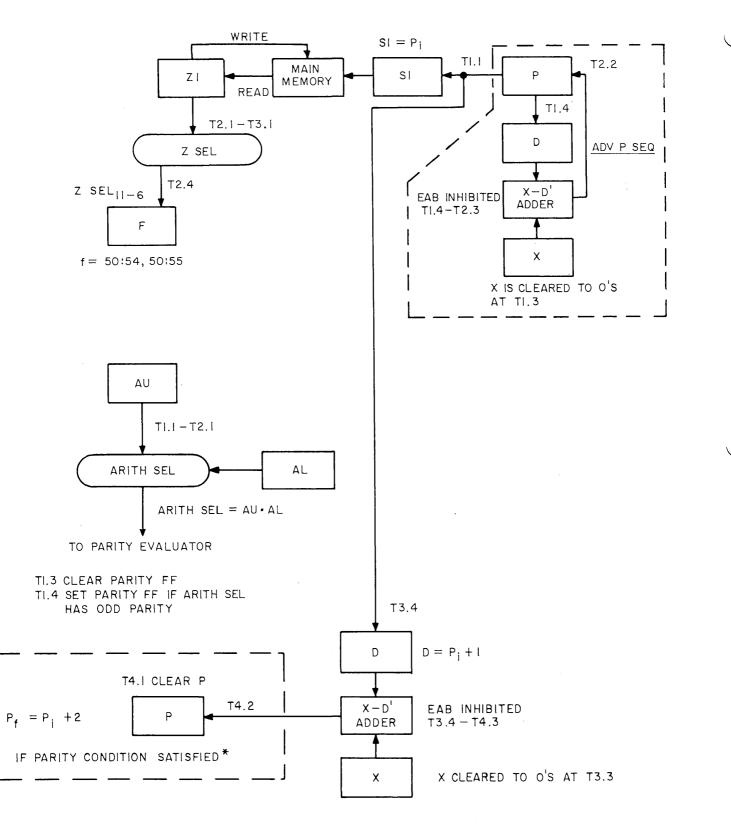

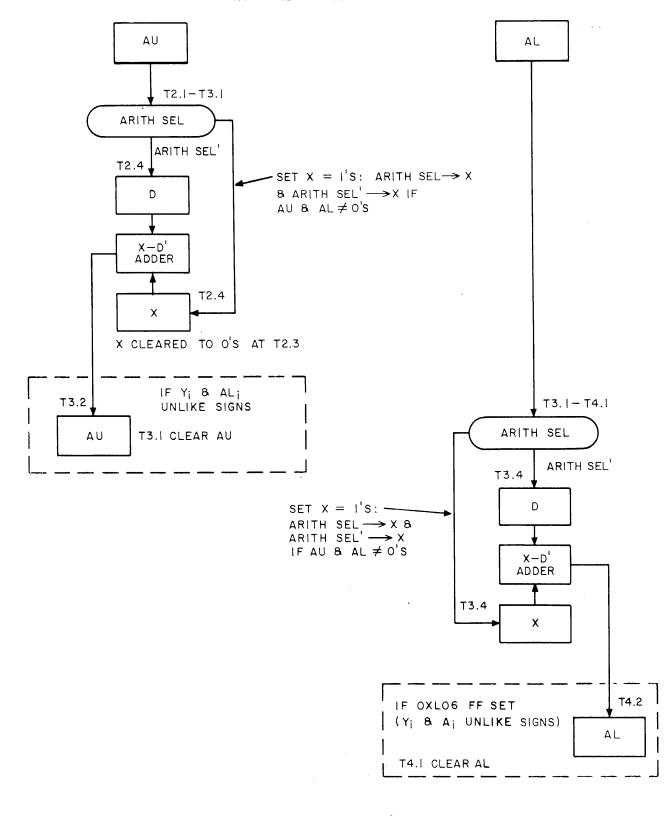

a) <u>Data Flow Block Diagram</u>. Refer to figure 6.2-1 for a block diagram description of the execution of f = 50:54, 50:55.

Most of the I-sequence operations are as previously described. If necessary, refer to study guide sheet number 5.4 for a detailed analysis.

NOTE: \* SKIP IF: (f = 50:54) · (PARITY FF SET) (f = 50:55) · (PARITY FF CLEAR)

Figure 6.2-1. I-Sequence Data Flow for f = 50:54, 50:55

6.2-2

During the set time of the Tl4 flip-flop (Tl.1-T2.1) both AU and AL are applied to arithmetic-select which formulates their logical product. The Parity flip-flop is used to record the parity of this result. This flip-flop affects only the f = 50:54, 50:55 skip evaluation.

The X-D' adder is used to increment P by +1 a second time just as is done by the advance-P subsequence. If P receives the result of this second incrementation, the next sequential instruction will be skipped.

As discussed in a later sheet, the instruction could be obtained from bootstrap or control memory.

b) <u>Essential Commands</u>. Refer to table 6.2-1 for a sequential list of essential I-sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams. The parity evaluator is presented later in this sheet.

b. Parity Evaluator.

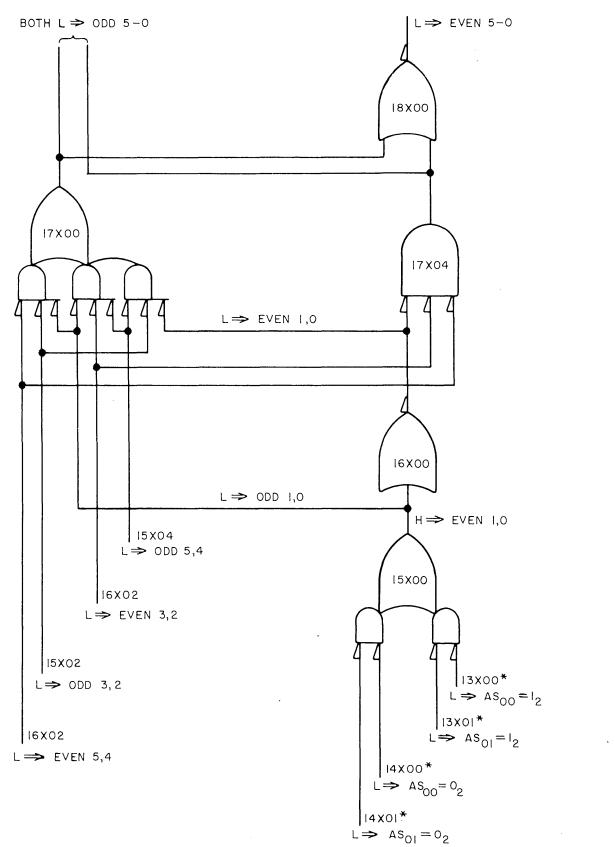

1. <u>General Description</u>. The parity evaluator has hard-wired inputs from arithmetic-select. The parity logic is comprised of several stages. The initial stages separate the arithmetic-select inputs into groups of two bits each. The parity indications from these groups are then combined into sections of three groups each. Total parity is then evaluated from the combination of the three sections. Refer to figure 6.2-2 for an example.

$$\begin{array}{c} \text{ARITH SEL (AU·AL)} = \begin{array}{c} \text{OI} & \text{IO} & \text{OO} & \text{OO} & \text{II} & \text{II} & \text{OI} & \text{II} & \text{II} \\ \text{(BINARY)} \end{array} = \begin{array}{c} \begin{array}{c} \text{OI} & \text{IO} & \text{OO} & \text{OO} & \text{II} & \text{II} & \text{OI} & \text{II} & \text{II} \\ \begin{array}{c} \text{V} & \text{V} & \text{V} & \text{V} & \text{V} & \text{V} & \text{V} \\ \begin{array}{c} \text{O} & \text{O} & \text{E} & \text{E} & \text{E} & \text{O} & \text{E} & \text{E} \\ \end{array} = \begin{array}{c} \text{GROUP PARITY} \end{array} = \begin{array}{c} \text{GROUP PARITY} \end{array} \\ \end{array}$$

NOTES: "E" MEANS EVEN. "O" MEANS ODD.

Figure 6.2-2. Parity Evaluation Example

2. Detailed Analysis.

a) <u>Group Parity</u>. Each group is comprised of two bits. Bits 1 and O are used for an example. Refer to figure 6.2-3 and logic diagrams, figure 9-101. 15X00 tests bits 1 and 0 of arithmetic-select for the two possible even parity conditions. Refer to table 6.2-2 for the four possible configurations of these bits.

6.2-3

TABLE 6.2-1. I SEQUENCE ESSENTIAL COMMANDS FOR f = 50:54, 50:55

| TIME NOTATION | COMMANDS                                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------|

| T4.4          | Clear Sl                                                                                                               |

| T1.1          | P → Sl, Init Memory, *set Incr P ff, AU → Arith Sel,<br>AL → Arith Sel                                                 |

| T1.3          | *Clear D, *clear X, clear Zl, clear F, *set OXL11 ff,<br>clear Parity ff                                               |

| T1.4          | $*P_L \longrightarrow D_L$ , $*P_U \longrightarrow D_U$ , $*set$ Inhib EAB ff, set Parity ff if Arith Sel = odd parity |

| T2.1          | *Clear P, Zl->Z Sel, *clear Incr P ff, drop AU Arith<br>Sel, drop AL->Arith Sel                                        |

| T2.2          | *Adder ->P                                                                                                             |

| T2.3          | *Clear OXL11 ff, *clear Inhib EAB ff                                                                                   |

| T2.4          | Z Sel <sub>ll-6</sub> → F, set 0XF06 ff                                                                                |

| T3.1          | Drop Zl>Z Sel                                                                                                          |

| T3.3          | Clear D, clear X                                                                                                       |

| T3.4          | $P_L \longrightarrow D_L$ , $P_U \longrightarrow D_U$ , set Inhib EAB ff                                               |

| T4.1          | Clear P if skip satisfied**                                                                                            |

| T4.2          | Adder → P if skip satisfied**                                                                                          |

| T4.3          | Clear Inhib EAB ff                                                                                                     |

\* These events are concerned with or are controlled by the advance-P subsequence.

\*\* Skip condition is satisfied if:  $(f = 50:54) \cdot (Parity ff set)$  $(f = 50:55) \cdot (Parity ff clear)$

| 2 <sup>1</sup> | 2 <sup>0</sup> | GROUP<br>PARITY | 15XOO<br>OUTPUT |

|----------------|----------------|-----------------|-----------------|

| 0              | 0              | Even            | Н               |

| 0              | 1              | Odd             | L               |

| 1              | 0              | 0dd             | L               |

| 1              | 1              | Even            | Н               |

TABLE 6.2-2. PARITY EVALUATOR, GROUP 1 & O CONDITIONS

The logic for the other groups is the same except for the bits being sensed.

b) <u>Section Parity</u>. Each section is comprised of three groups (six bits). Section 5-0 is used for an example. Refer to figure 6.2-3 and logic diagrams, figure 9-101.

18X00, 17X00, and 17X04 test the parity conditions of the three groups (5,4; 3,2; and 1,0). Refer to table 6.2-3 for the eight possible parity configurations.

| GROUPS |      |      | SECTION |       | OUTPUT LEVELS |       |  |

|--------|------|------|---------|-------|---------------|-------|--|

| 5,4    | 3,2  | 1,0  | PARITY  | 17X04 | 17X00         | 18X00 |  |

| Odd    | Odd  | Odd  | Odd     | L     | L             | Н     |  |

| Odd    | Odd  | Even | Even    | Ĺ     | Н             | L     |  |

| Odd    | Even | Odd  | Even    | L     | Н             | L     |  |

| Odd    | Even | Even | Odd     | L     | L             | Н     |  |

| Even   | Odd  | Odd  | Even    | L     | Н             | L     |  |

| Even   | Odd  | Even | Odd     | L     | L             | Н     |  |

| Even   | Even | Odd  | Odd     | L     | L             | Н     |  |

| Even   | Even | Even | Even    | Н     | Ĺ             | L     |  |

TABLE 6.2-3. PARITY EVALUATOR, SECTION 5-0 CONDITIONS

The logic for the other sections is the same except for the bits being sensed.

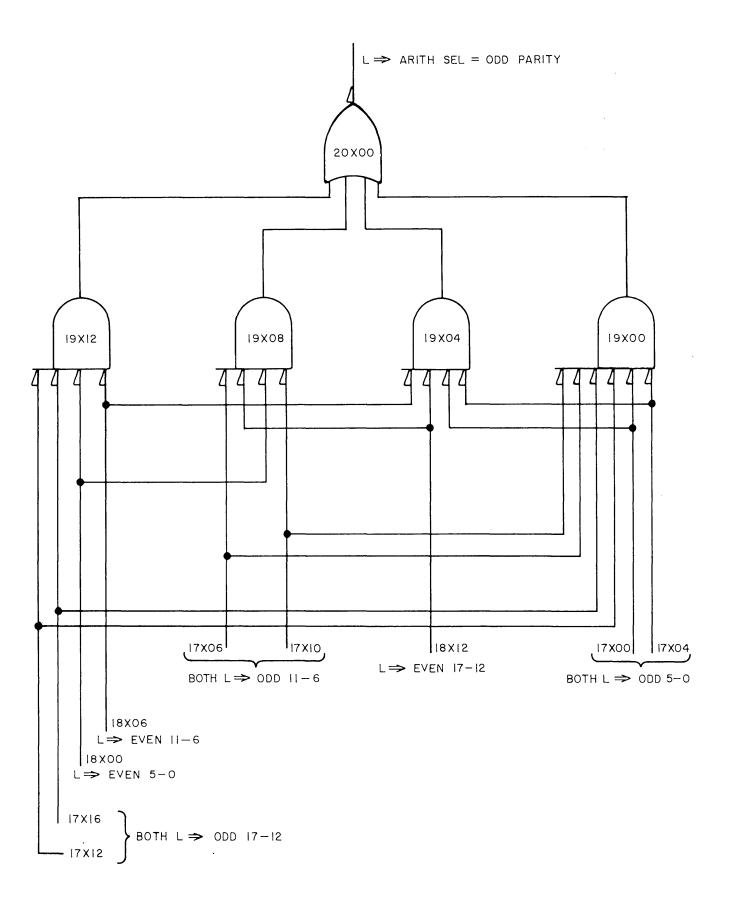

c) <u>Total Parity</u>. Total parity is the combined evaluation of the three sections. Refer to figure 6.2-4 and logic diagrams, figure 9-101.

NOTES: \*INPUTS LABELED "AS" ARE FROM ARITHMETIC SELECT. "EVEN 1,0" MEANS EVEN PARITY IN 2<sup>1</sup> AND 2<sup>0</sup> OF ARITHMETIC SELECT.

Figure 6.2-3. Parity Evaluator, Section 5-0

6.2-6

.

The gates shown in figure 6.2-4 test the parity conditions of the three groups for the four possible odd parity configurations. Refer to table 6.2-4 for the eight possible parity configurations.

|       | SECTIONS | 5     | TOTAL  | OUTPUT LEVELS |       |       |       |       |

|-------|----------|-------|--------|---------------|-------|-------|-------|-------|

| 17-12 | 11-6     | 5-0   | PARITY | 19X00         | 19X04 | 19X08 | 19X12 | 20X00 |

| Odd   | Odd      | Odd ' | Odd    | Н             | L     | L     | L     | L     |

| Odd   | Odd      | Even  | Even   | L             | Ĺ     | L     | L ·   | Н     |

| Odd   | Even     | Odd   | Even   | L             | L     | L     | L     | Н     |

| Odd   | Even     | Even  | Odd    | L             | L     | L     | Н     | L     |

| Even  | Odd      | Odd   | Even   | L             | L     | L     | L     | Н     |

| Even  | Odd .    | Even  | Odd    | L             | L     | Н     | L     | L     |

| Even  | Even     | Odd   | Odd    | L             | Н     | L     | L     | L     |

| Even  | Even     | Even  | Even   | L             | L     | L     | L     | Н     |

### TABLE 6.2-4. PARITY EVALUATOR, TOTAL PARITY CONDITIONS

#### 6.2-5. SUMMARY

The output of 20X00 is the total parity indication of arithmetic-select (AU  $\cdot$  AL). The Parity flip-flop is cleared at TL.3 time of the I-sequence and is set at TL.4 time if total parity is odd. The state of this flip-flop only affects the execution of the f = 50:54, 50:55 instructions to condition the program skip.

Figure 6.2-4. Parity Evaluator, Final Stage

6.2-8

NAME:

6.2-6. STUDY QUESTIONS

Given: AU = 461367a. AL = 763752instruction = 505400

> Refer to logic diagrams, figure 9-101. Give the output logic levels for the following gates which exist at Tl.4 time during the I-sequence of the above instruction.

| 15X00 = | <br>18X06 =   |         |

|---------|---------------|---------|

| 15X02 = | <br>. 17X12 = |         |

| 15X04 = | <br>17X16 =   | · · · · |

| 17X00 = | <br>18X12 =   |         |

| 17X04 = | <br>19X00 =   | ·       |

| 18X00 = | <br>19X04 =   |         |

| 17X06 = | <br>19X08 =   |         |

| 17X10 = | <br>19X12 =   |         |

|         | 20X00 =       |         |

b. Given conditions same as above.

When the instruction is executed, a program skip is performed. Refer to logic diagrams, figure 9-101. Determine whether each malfunction, occurring individually, would cause the erroneous program skip. Indicate your answers by writing "yes" or "no" beside each malfunction condition.

| Grounded Output | <u>Constant Low Level Output</u> |

|-----------------|----------------------------------|

| 15X00           | 15X00                            |

| 16X02           | 16X02                            |

| 16X04           | 16X04                            |

| 16X00           | 16X00                            |

| 17X04           | 17X04                            |

| 17X10           | 17X10                            |

| 18X12           | 18X12                            |

| 19X00           | 19X00                            |

# ⑦ 課題をおりましたの。

A CARL AND A CARL AND A CARL AND A CARL

\*\*\*

|   |                                                                                                                 | 1. P              |                                                                                                                                                                                                                                                                                                                                                       |

|---|-----------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                 | .• <sup>.</sup> . |                                                                                                                                                                                                                                                                                                                                                       |

| • |                                                                                                                 |                   |                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                 |                   |                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                 | • (4)             |                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                 | . (4              | an an ann an Aonaichte an<br>Ann an Aonaichte ann an Aon<br>Ann an Aonaichte ann an Ao |

|   | in the second |                   | 1<br>1                                                                                                                                                                                                                                                                                                                                                |

• •

-

na Angeler and angeler part of the Angeler and angeler part of the

#### SECTION 6 - ARITHMETIC SECTION

#### 6.3. INSTRUCTION EXECUTION OF RSHAU, RSHAL, RSHA, LSHAU, LSHAL, LSHA

6.3-1. OBJECTIVES

To present the detailed theory of operation involved in the execution of instructions with f = 50:41-43, 50:45-47.

#### 6.3-2. INTRODUCTION

These instructions perform either right shifts or left shifts of the content of AU, AL, or AU and AL together.

6.3–3. REFERENCES

- a. <u>UNIVAC 1219 Technical Manual</u>, Volume I, Paragraphs 4-4<u>c</u>(2) and 4-7, table 4-11.

- b. UNIVAC 1219 Technical Manual, Volume II, Section 9 (logic diagrams).

#### 6.3-4. INFORMATION

- a. General Description.

- 1. Instruction Interpretation.

a) <u>RSHAU, f = 50:41</u>. This instruction right shifts with sign extension, the content of AU, the number of places specified by the six least significant bits (k) of the instruction word. The AU bit positions vacated are filled with the sign bit of the original value. Those bits shifted beyond  $AU_{17}$  are lost.

b) <u>RSHAL, f = 50:42</u>. Except for the value shifted, this instruction is the same as f = 50:41. The content of AL is right shifted with sign extension.

c) <u>RSHA, f = 50:43</u>. Except for the value shifted, this instruction is the same as f = 50:41. The combined content of AU and AL is right shifted with sign extension. AU is the more significant value. Those bits shifted beyond AU<sub>17</sub> enter the left end of AL. The AU bits positions vacated are filled with the sign bit of the original AU value. Those bits shifted beyond AL<sub>00</sub> are lost.

d) <u>LSHAU, f = 50:45</u>. This instruction circularly left shifts the content of AU the number of places specified by the six least significant bits (k) of the instruction word. Those bits shifted beyond  $AU_{35}$  enter the right end of AU.

e) <u>LSHAL, f = 50:46</u>. Except for the value shifted, this instruction is the same as f = 50:45. The content of AL is circularly left shifted. These bits shifted beyond AL<sub>17</sub> enter the right end of AL.

f) <u>LSHA, f = 50:47</u>. Except for the value shifted, this instruction is the same as f = 50:45. The combined content of AU and AL is circularly left shifted. Those bits shifted beyond AL<sub>17</sub> enter the right end of AU. Those bits shifted beyond AU<sub>35</sub> enter the right end of AL.

2. Execution Sequences.

a) <u>I-Sequence</u>. During the I-sequence which obtains the instruction from memory, the shift count (k) is placed in KO.

b) <u>Shift Sequence</u>. The shift sequence uses a special timing which runs parallel to main timing and causes the shifting according to the shift count in KO.

# b. Detailed Analysis.

l. <u>I-Sequence</u>. Most of the I-sequence operations are as previously described. If necessary, refer to study guide sheet number 5.4 for a detailed description.

KO receives the six least significant bits of the instruction word from Z-select. This value is the shift count. The function code in F determines the type of shift. The actual shifting is performed by the shift sequence which is initiated during the I-sequence. A detailed analysis of the shift sequence operations is presented later in this sheet.

2. Effect of Hold Flip-Flops. As is developed later in this sheet, the Hold I and Hold 2 flip-flops are set during the shifting operation. These flip-flops keep the machine in the I-sequence and prevent the reading of the next instruction until the shift operation is completed. Refer to logic diagrams, figure 9-28 for the Hold 1 and Hold 2 flip-flops.

These flip-flops both have outputs to the logic on figure 9-14. This logic supplies timing and enables for the I-sequence operations necessary to obtain next instruction. When the Hold flip-flops are set, their high level outputs disable these I-sequence operations. Among the events which are prevented are initiate-memory, advance-P subsequence, clear-F, Z-select F, clear-KO, and Z-select KO. Refer to the proper enable pages in the logic diagrams to develop the disable function of these events.

As long as the Hold flip-flops are set, the shift function code and the remaining shift count are retained in F and KO, respectively.

During the execution of a shift instruction, the F register indicates a shift function code which does not require any main timing sequence other than the I-sequence. Therefore, as the shifts are being performed, the I-sequence flip-flop is set for each main timing cycle. Refer to logic diagrams, figure 9-12 to develop the setting of the I-sequence flip-flop for each main timing cycle as long as F specifies f =50:41-43, 50:45-47.

- 3. Shift Sequence.

- a) Timing.

6.3-2

### b) Shifting Operations.

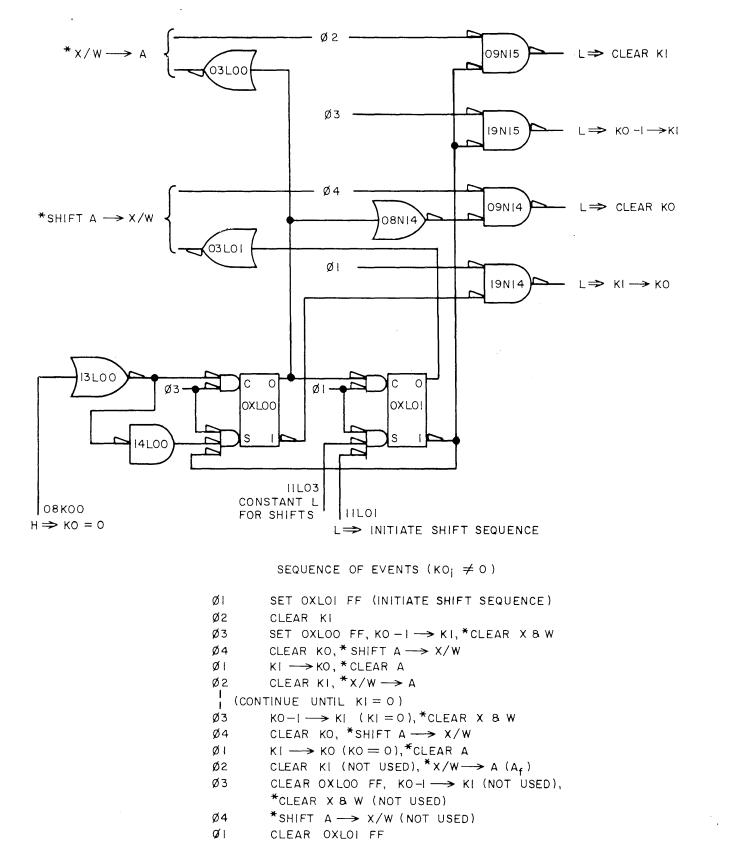

1) <u>Essential Commands</u>. The commands which shift AU and AL by means of X and W, respectively, are enabled by the OXLOO and OXLO1 Shift Sequence flip-flops and are timed by the master clock phases. Refer to table 6.3-4 for a sequential list of essential shift sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams.

| TIME NOTATION | COMMANDS                                                 |

|---------------|----------------------------------------------------------|

|               | I SEQUENCE                                               |

| T1.4          | Clear KO                                                 |

| T2.3          | Clear OXLOO ff                                           |

| T2.4          | $Z \operatorname{Sel}_{5-0} \longrightarrow KO (KO = 0)$ |

| T3.4          | Set Hold l ff, clear Scale Factor ff (1XLOO)             |

| T4.1          | Set OXLO1 ff                                             |

| T4.3          | Set OXLO2 ff, set Hold 2 ff                              |

| T1.1          | Set Clear Hold ff, clear OXLO1 ff                        |

| T1.3          | Clear OXLO2 ff                                           |

| T4.2          | Clear Hold 1 ff, clear Clear Hold ff                     |

|               | I-SEQUENCE FOR NEXT INSTRUCTION                          |

| T1.3          | Clear Hold 2 ff                                          |

TABLE 6.3-1. I AND SHIFT SEQUENCE ESSENTIAL COMMANDS WITH INITIAL SHIFT COUNT = 0

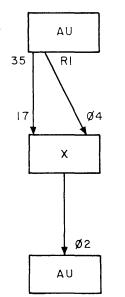

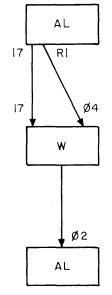

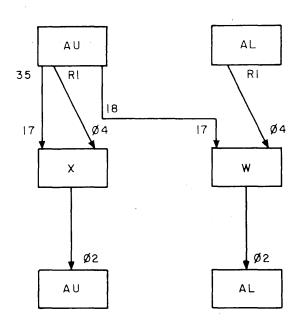

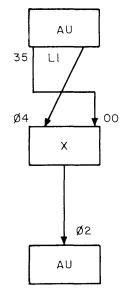

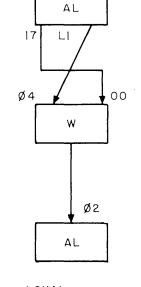

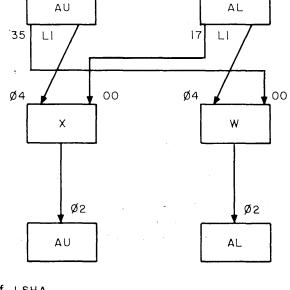

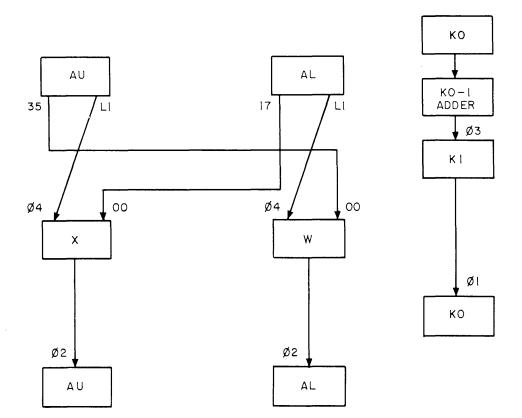

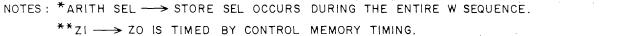

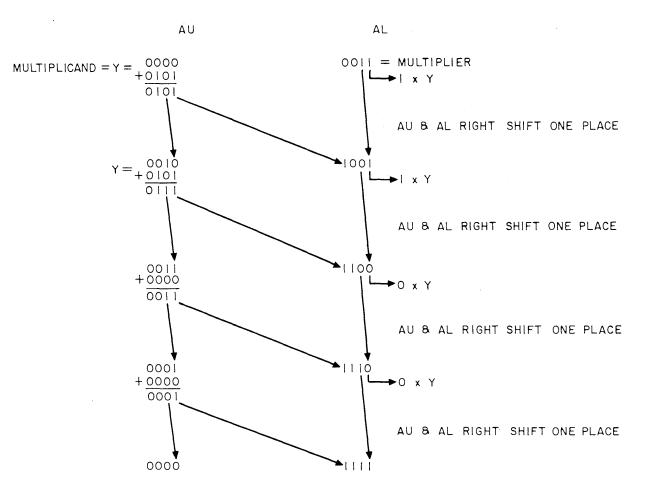

2) <u>Data Flow Block Diagram</u>. Refer to figure 6.3-2 for a block diagram description of the shift sequence operations.

These diagrams illustrate the data flow for a one place shift for each of the shift function codes. One such flow of data can occur per master clock cycle. This data flow is continually repeated until the Shift Sequence flip-flops are cleared at the termination of the shift count.

# TABLE 6.3-2. I AND SHIFT SEQUENCE ESSENTIAL COMMANDS WITH INITIAL SHIFT COUNT $\neq$ 0

| TIME NOTATION | COMMANDS                                                                                                                                                                                                    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | ISEQUENCE                                                                                                                                                                                                   |

| T1.4          | Clear KO                                                                                                                                                                                                    |

| т2.3          | Clear 0XL00 ff                                                                                                                                                                                              |

| т2.4          | $Z \operatorname{Sel}_{5-0} \longrightarrow \mathrm{KO}^{-1}$                                                                                                                                               |

| т3.4          | Set Hold 1 ff, clear Scale Factor ff (1XL00) - HOLSHIFT                                                                                                                                                     |

| T4.1          | Clear KO<br>Clear 0XL00 ff<br>$Z \operatorname{Sel}_{5-0} \rightarrow \operatorname{KO}^{-}$<br>Set Hold 1 ff, clear Scale Factor ff (1XL00) $- \operatorname{HOL}_{SHIFT}^{O}$<br>Set 0XL01 ff<br>Clear K1 |

| T4.2          | Clear K1                                                                                                                                                                                                    |

| T4.3          | Set 0XL00 ff, set Hold 2 ff, K0-1 $\rightarrow$ K1, *clear X, *clear W                                                                                                                                      |

| T4.4          | Clear K0, *shift A→X/W                                                                                                                                                                                      |

| T1.1          | $K1 \rightarrow K0$ , *clear A                                                                                                                                                                              |

| T1.2          | Clear K1, $*X/W \rightarrow A$                                                                                                                                                                              |

| T1.3          | $K0-1 \rightarrow K1$ , *clear X, *clear W                                                                                                                                                                  |

| T1.4          | Clear K0, *shift $A \rightarrow X/W$                                                                                                                                                                        |

| T2.1          | K1→K0, *clear A                                                                                                                                                                                             |

| T2.2          | Clear K1, $*X/W \rightarrow A$                                                                                                                                                                              |

|               | (continue until $K1 = 0$ )                                                                                                                                                                                  |

| TX.3          | $K0-1 \rightarrow K1$ (K1 = 0), *clear X, *clear W                                                                                                                                                          |

| TX.4          | Clear K0, *shift $A \rightarrow X/W$                                                                                                                                                                        |

| TX.1          | $K1 \rightarrow K0$ (K0 = 0), set Clear-Hold ff, *clear A                                                                                                                                                   |

| TX.2          | Clear K1, $X/W \rightarrow A(A_f)$                                                                                                                                                                          |

| <b>TX.</b> 3  | K0-1 $\rightarrow$ K1, clear 0XL00 ff, set 0XL02 ff, *clear X, *clear W                                                                                                                                     |

| TX.4          | *Shift $A \rightarrow X/W$ (not used)                                                                                                                                                                       |

| TX.1          | Clear 0XL01 ff                                                                                                                                                                                              |

| TX.3          | Clear 0XL02 ff                                                                                                                                                                                              |

|               |                                                                                                                                                                                                             |

| next T4.2     | Clear Hold 1 ff, clear Clear-Hold ff                                                                                                                                                                        |

|               | I SEQUENCE FOR NEXT INSTRUCTION                                                                                                                                                                             |

| T1.3          | Clear Hold 2 ff                                                                                                                                                                                             |

\*These events pertain to the actual shifting of AU and AL and are discussed later in this sheet.

f = 50:41

b. RSHAL, f = 50:42

C. RSHA, f = 50:43

d. LSHAU, f = 50:45

| SHIFT COUNT <sub>10</sub> | NUMBER OF MAIN<br>TMG. CYCLES (I SEQ.) | EXECUTION<br>TIME (µs) |

|---------------------------|----------------------------------------|------------------------|

| O through 4               | 2                                      | 4                      |

| 5 through 8               | 3                                      | 6                      |

| 9 through 12              | 4 .                                    | 8                      |

| 13 through 16             | 5                                      | 10                     |

| 17 through 20             | 6                                      | 12                     |

| 21 through 24             | 7                                      | 14                     |

| 25 through 28             | 8                                      | 16                     |

| 29 through 32             | 9                                      | 18                     |

| 33 through 36             | 10                                     | 20                     |

| 37 through 40             | 11                                     | 22                     |

| 41 through 44             | 12                                     | 24                     |

| 45 through 48             | 13                                     | 28                     |

| 49 through 52             | 14                                     | · 30                   |

| 53 through 56             | 15                                     | 32                     |

| 57 through 60             | 16                                     | 34                     |

| 61 through 63             | 17                                     | 36                     |

TABLE 6.3-3. EXECUTION TIME OF f = 50:41-43, 50:45-47

# 6.3-5. SUMMARY

The f = 50:41 - 50:43, 50:45 - 50:47 instructions are format 2 and use the value k. The k value is available in KO after T2.4 time of the I-sequence. The shift sequence is required to complete the executions of these instructions.

| TIME            |                                                                    | f=50: | 41 | 42 | 43 | 45 | 46 | 47 |

|-----------------|--------------------------------------------------------------------|-------|----|----|----|----|----|----|

| 0XL01 ff set•Ø3 | Clear X, clear W                                                   |       | x  | x  | x  | x  | х  | x  |

| 0XL01 ff set·Ø4 | AURl→X                                                             |       | x  | x  | x  |    |    |    |

|                 | *Set $X_{17}=1$ if $AU_{35}=1$<br>( $AU_{35} \rightarrow X_{17}$ ) |       | x  | x  | x  |    |    |    |

|                 | ALR1→W                                                             |       | x  | x  | x  |    |    |    |

|                 | *Set $W_{17}=1$ if $AU_{18}=1$<br>( $AU_{18} \rightarrow W_{17}$ ) |       | x  |    | x  |    |    |    |

|                 | *Set $W_{17}=1$ if $AL_{17}=1$<br>( $AL_{17} \rightarrow W_{17}$ ) |       |    | x  |    |    |    |    |

|                 | AUL1→X                                                             |       |    |    |    | х  | x  | х  |

|                 | *Set $X_{00}=1$ if $AU_{35}=1$<br>( $AU_{35} \rightarrow X_{00}$ ) |       |    |    |    | x  |    |    |

|                 | *Set $X_{00}=1$ if $AL_{17}=1$<br>( $AL_{17} \rightarrow X_{00}$ ) |       |    |    |    |    | x  | x  |

|                 | ALL1→W                                                             |       |    |    |    | Х  | х  | х  |

|                 | *Set $W_{00}=1$ if $AU_{35}=1$<br>( $AU_{35} \rightarrow W_{00}$ ) |       |    |    |    | x  |    | x  |

|                 | *Set $W_{00}=1$ if $AL_{17}=1$<br>( $AL_{17} \rightarrow W_{00}$ ) |       |    |    |    |    | x  |    |

| 0XL00 ff set•Ø1 | Clear AU                                                           |       | x  |    | x  | x  |    | x  |

|                 | Clear AL                                                           |       |    | x  | x  |    | x  | х  |

| 0XL00 ff set•Ø2 | X→AU                                                               |       | x  |    | х  | x  |    | x  |

| -               | **₩ <b>&gt;</b> AL                                                 |       |    | x  | x  |    | х  | x  |

### TABLE 6.3-4. SHIFT SEQUENCE ESSENTIAL COMMANDS

\*These commands are enabled by gates 31W00, 31W17, 31X00, and 31X17 in the logic diagrams, figure 9-33, and are timed by the AUR1 $\rightarrow$ X, ARL1 $\rightarrow$ W, AUL1 $\rightarrow$ X, and ALL1 $\rightarrow$ W commands.

\*\*The transmission of bit 00 for the W→AL command is through gate 83A00 in the logic diagrams, figure 9-33.

####

#

· · · · 1.14 -

-------

n jan en en angeler en  $\sum_{i=1}^{N} (i - 1)$

- 40 · · ·

• 10 L N

•

| STUDY QUESTIONS                |                                                                                                                            |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| a. Given: 31X17 gr<br>instruct | pounded output (logic diagrams, figure 9-33)<br>ion = $504303$<br>AU <sub>1</sub> = $430012$<br>AL <sub>1</sub> = $234756$ |

6.3-6.

1.1.1.1.1

1. For the given conditions, draw below the block diagram of data flow for a 1-place shift like those in figure 6.3-2 of this sheet.

$AU_{f} = \frac{1}{1}$   $AL_{f} = \frac{1}{1}$

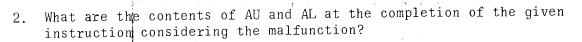

b. Givem: 10F42 grounded output (logic diagrams, figure 9-47) instruction = 504303

$AU_i = 430012$  $AL_i = 534756$

1. For the given conditions, draw below the block diagram of data flow for a 1-place shift like those in figure 6.3-2 of this sheet.

2. What are the contents of AU and AL at the completion of the given instruction considering the malfunction?

$AU_f =$

6.3-12

NAME:

c. Given: llF45 grounded output (logic diagrams, figure 9-47) instruction = 504503AU<sub>1</sub> = 430012

For the given conditions, draw below the block diagram of data flow for a l-place shift like those in figure 6.3-2 of this sheet.

2. What is the content of AU at the completion of the given instruction considering the malfunction?

$$AU_{f} =$$

\_\_\_\_\_

· · · · · ·

.

•

•

I.

### SECTION 6 - ARITHMETIC SECTION

6.4. KO-1 ADDER

#### 6.4-1. OBJECTIVES

To present the detailed theory of operation involved in the KO-1 adder.

#### 6.4-2. INTRODUCTION

The KO-1 adder is used to control the number of repeated operations used in shifting, scaling, multiplication, and division.

# 6.4-3. REFERENCES

- a. <u>UNIVAC 1219 Technical Manual</u>. Volume I, Paragraph 4-2<u>e(3)</u>.

- b. <u>UNIVAC 1219 Technical Manual</u>, Volume II, Section 9 (logic diagrams).

### 6.4-4. INFORMATION

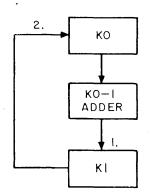

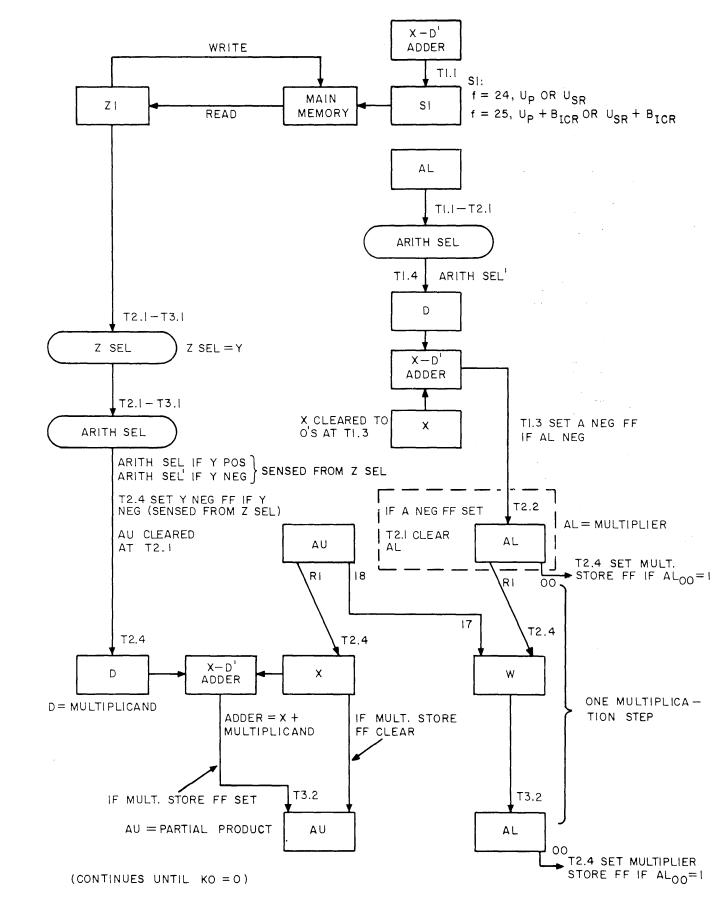

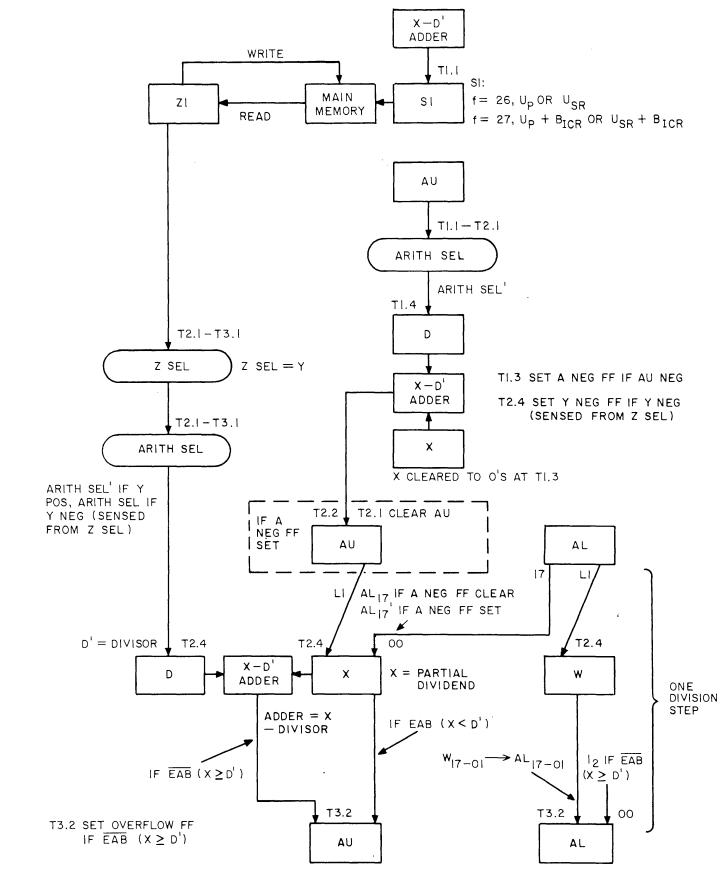

<u>a</u>. <u>General Description</u>. The KO-1 adder is a 6-bit open-ended adder which continually subtracts 1 from the content of the KO register. The output of the adder is taken to the KI register. The decremented value is then taken back to KO. Refer to figure 6.4-1 for a data flow block diagram of the K-counter configuration.

Figure 6.4-1. K Counter Block Diagram

Certain repeating type operations are controlled by the counter. KO is initially set to a specific count. Each time KO receives the new decremented value, one of the repeating operations is performed. When KO holds the value of all O's, the controlled operations are terminated.

# b. Detailed Analysis

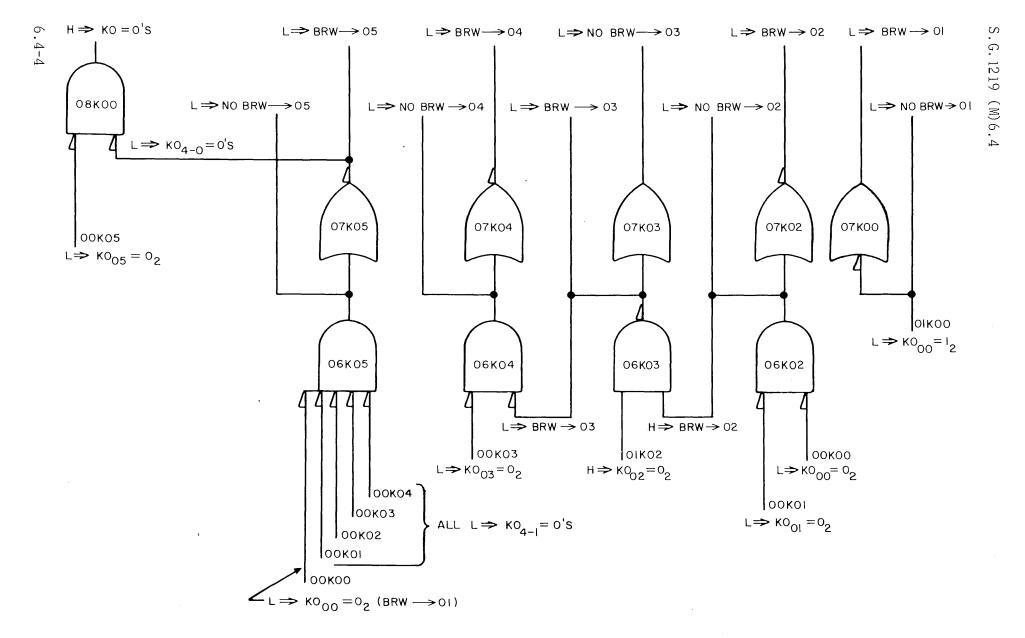

1. Effect of Borrow Request. If a request for a borrow is applied to a bit position of KO, the result of this subtraction produces the complement of the bit. Refer to figure 6.4-2 for examples.

# Figure 6.4-2. KO-1 Adder Borrow Examples

2. <u>Adder Stage 00</u>. Refer to logic diagrams, figure 9-37 for the adder logic.

The subtraction of KO-1 always affects  $KO_{00}$  to produce its complement. This complemented value is outputted by inverter O2KOO and is placed in  $Kl_{00}$  during the "KO-1  $\rightarrow$  K1" command.

3. Generation of Borrow Requests. If a borrow request is applied to a particular bit position, the complement of that bit is the result. If that same KO bit position contains O2, the borrow request is propagated to the next higher bit because the O2 cannot supply the 12 that the borrow requires. All borrow requests originate from the subtraction of  $KO_{OO} - 1$ . A borrow request is applied to a particular bit position if all of the less significant KO bit positions contain O's. Refer to table 6.4-1 for the conditions necessary to apply borrow requests to the KO bits.

|                 | . KO bit positions |    |                |    |                |  |  |

|-----------------|--------------------|----|----------------|----|----------------|--|--|

| Borrows Applied | 04                 | 03 | 02             | 01 | 00             |  |  |

| Brw ->01        |                    |    |                |    | 02             |  |  |

| Brw -> 02       |                    |    |                | 02 | 02             |  |  |

| Brw -> 03       |                    |    | 02             | 02 | 0 <sub>2</sub> |  |  |

| Brw -> 04       |                    | 02 | 02             | 02 | 0 <sub>2</sub> |  |  |

| Brw -> 05       | 02                 | 02 | 0 <sub>2</sub> | 02 | 02             |  |  |

TABLE 6.4-1. KO-1 ADDER BORROW REQUEST CONDITIONS

NOTE: "Brw  $\rightarrow$  XX" means a borrow request is being applied to bit position XX.

6.4-2

Adder bits 05 through 01 have logic which tests all of the less significant KO bits for the binary configurations described above. If a borrow request is applied, the complement of the KO bit is the adder output as was shown for bit 00. Refer to figure 6.4-3 for the adder request logic. This is a portion of that shown in the logic diagrams, figure 9-37.

Gate O8KOO is used to test KO for all O's. This condition terminates the operation being controlled by the K-counter.

### 6.4-5. SUMMARY

The K-counter is comprised of KO and Kl registers and the KO-1 adder. KO is hard-wired to the adder input. The adder is 6 bits in length, and is of the open-ended type. It can only output to Kl.

NOTES: "BRW  $\longrightarrow$  OX" MEANS A BORROW REQUEST IS BEING APPLIED TO BIT POSITION OX. GATE OBKOO IS NOT ACTUALLY PART OF THE REQUEST LOGIC.

Figure 6.4-3. KO-1 Adder Borrow Request Generation Logic

1) Initial Shift Count = 0. If the shift count specified in the six least significant bits of the instruction word equals 0, no shifts are to be performed. The shift sequence is initiated but is terminated before it can effect any shifting.

Refer to table 6.3-1 for a sequential list of essential I and shift sequence control events. Develop these commands by referring to the proper enable pages in the logic diagrams. The commands shown are in addition to the normal I-sequence commands.

As shown, no shifting is performed. Two main timing cycles of the I-sequence are used before the Hold flip-flops are cleared. With the initial shift count equal to 0, the instruction execution time is 4 microseconds.

2) Initial Shift Count  $\neq 0$ . If the shift count specified in the six least significant bits of the instruction word does not equal 0, one or more shifts are performed. The shift sequence is initiated and remains active until the shifting is completed at which time it is terminated.

The shift commands involving AU and AL are generated by the combination of the shift sequence flip-flops (OXLOO and OXLO1) being set and the occurrence of clock phases. OXLOO and OXLO1 are set for the entire shifting operation. The clock phases alone provide the timing for the operation. For each cycle of the master clock, a shift of one place is executed.

KO, K1, and KO-1 adder are used to control the number of shifts by determining the number of clock cycles during which the shift sequence flip-flops will remain set. The shift count which is held in KO and K1 is decremented by 1 during each master clock cycle. When KO reaches the count of O, the Shift Sequence flip-flops are cleared and the AU and AL shift commands are disabled. The KO-1 adder is analyzed in a later sheet.

Refer to figure 6.3-1 for a simplified logic diagram of the shift sequence. Develop the events chart from the logic shown.

Refer to table 6.3-2 for a sequential list of essential I and shift sequence control events. Develop these commands by referring to the proper enable pages in the logic diagrams. The commands shown are in addition to the normal sequence commands.

As shown, shifting is performed until Kl = 0 which causes the clearing of the OXLOO and OXLOI flip-flops after the last shift. Flip-flop OXLO2 is set and cleared at the termination but is not used. The Hold 1 flip-flop is not cleared until T4.2 time of the main timing cycle during which the last shift occurred. The next main timing cycle is also under I-sequence control but is able to read-up the next instruction in the program. The last Hold flip-flop (2) is cleared at T1.3 time of the next instruction's I-sequence.

With the shift sequence active, each master clock cycle performs a one-place shift. Therefore, a maximum of four shifts can be performed during one main timing cycle which has a duration of two microseconds. Including the two microsecond I-sequence which reads-up the shift instruction, a shift instruction with a shift count from 1 through 4 has an execution time of four microseconds. Refer to table 6.3-3 for a complete list of shift count values with the corresponding instruction execution times.

NOTE: \* THESE EVENTS PERTAIN TO THE ACTUAL SHIFTING OF AU AND AL AND ARE DISCUSSED LATER IN THIS SHEET.

Figure 6.3-1. Shift Sequence Simplified Logic

6.3-4

NAME:

# 6.4-6. STUDY QUESTIONS

a. Given: instruction - 504605 06KO3 grounded output (logic diagrams, figure 9-37)

Considering the above malfunction, describe the effect upon the execution of the given instruction. Fully explain your reasoning.

0.4-

# $= \left\{ \left\{ 1, 1, 2, 3, 3 \right\} : \left\{ 1, 2, 3, 3 \right\} \right\} = \left\{ 1, 2, 3, 3 \right\}$

• 5 ....

٢

#### SECTION 6 - ARITHMETIC SECTION

#### 6.5. INSTRUCTION EXECUTION OF SF

#### 6.5-1. OBJECTIVES

To present the detailed theory of operation involved in the execution of the instruction with f = 50:44.

#### 6.5-2. INTRODUCTION

This instruction normalizes the combined contents of AU and AL.

#### 6.5–3. REFERENCES

- a. <u>UNIVAC 1219 Technical Manual</u>, Volume I, Paragraphs 4-4<u>c</u>(4) and 4-7, tables 4-11 and 4-14.

- b. UNIVAC 1219 Technical Manual, Volume II, Section 9 (logic diagrams).

#### 6.5-4. INFORMATION

#### a. General Description

l. Instruction Interpretation. This instruction, SR, circularly left shifts the combined content of AU and AL. AU is the more significant portion. Left shifts are performed until  $AU_{35} \neq AU_{34}$  or until the maximum shift count specified in the six least significant bits of the instruction word has expired. This shift count dictates the maximum number of places that AU and AL can be shifted during the normalize operation. When shifting stops, the difference between the specified maximum shift count and the actual shift count is stored in control memory at the address  $00017_8$ . The original content of this memory address is destroyed.

2. Execution Sequences.

a) <u>I-Sequence</u>. During the I-sequence which obtains the instruction from memory, the maximum shift count is placed in KO.

b) <u>Scale Sequence</u>. The scale sequence uses a special timing chain which runs in parallel to main timing and controls the actual normalize operation.

c) <u>W-Sequence</u>. The W-sequence is active throughout the normalize operation but is only effective at the completion of the operation in storing the difference between the maximum shift count specified and the actual shift count.

b. Detailed Analysis.

1. <u>I-Sequence</u>. The I-sequence operations are as previously described. If necessary, refer to study guide sheet number 5.4 for a detailed description. At the end of the I-sequence, KO contains the six least significant bits of the instruction word which specifies the maximum shift count allowed.

2. <u>Effect of Hold Flip-Flops</u>. The Hold 1 and Hold 2 flip-flops are set during the scale operation to prevent the normal W-sequence operations which store KO in control memory. These flip-flops prevent the setting of the final W-sequence flip-flop (lower bank). When the Hold flip-flops are cleared, the Wsequence is allowed to store KO.

3. W and Scale Sequences.

a) Data Flow Block Diagram.

1) <u>Prior to Scale Termination</u>. Refer to figure 6.5-1 for a block diagram description of one step of the scale operation.

During each master clock cycle with the scale sequence active, AU and AL are circularly left shifted one place as a 36 bit register. The count in KO is decremented by 1. When the scale sequence detects  $AU_{35} \neq AU_{34}$  or KO = 0, the shift operation is terminated.

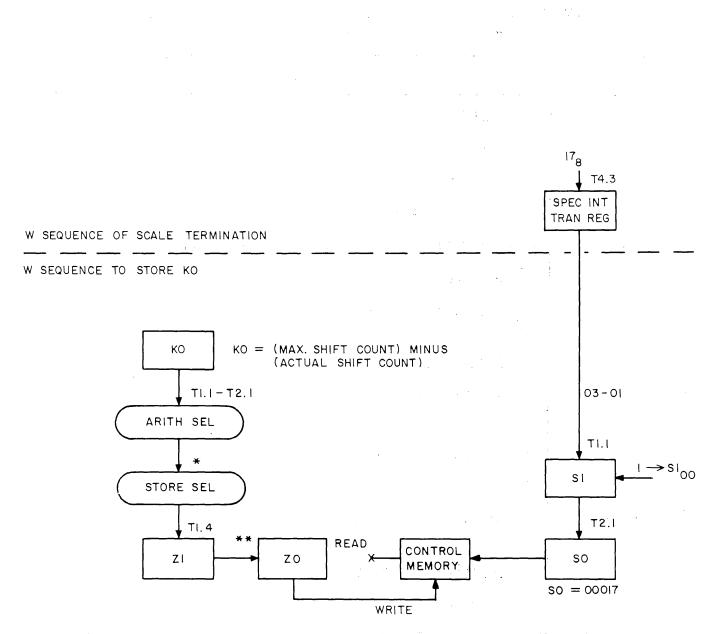

2) <u>Scale Termination (KO Storage)</u>. Refer to figure 6.5-2 for a block diagram description of the KO storage operations.

When the scale sequence is terminated, the W-sequence stores KO in control memory at the address  $00017_8$ . KO still contains its value which existed at the scale termination. This value is the difference between the maximum shift count allowed (KO<sub>i</sub>) and the actual number of shifts executed by the scale sequence.

b) Essential Commands.

1) Aborted Scale Sequence. If the maximum shift count specified by the instruction equals 0 or if the initial value in AU is such that AU35  $\neq$  AU<sub>34</sub>, no shifting of AU and AL is to be performed. The scale sequence is disabled.

Refer to tables 6.5-1 and 6.5-2 for sequential lists of essential I, W, and scale sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams.

2) <u>Normal Scale Sequence Prior to Termination</u>. Refer to table 6.5-3 for a sequential list of essential I, W, and scale sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams.

6.5-2

The scale sequence commands which left shift AU and AL and decrement KO occur continuously until the scale sequence flip-flops OXLOO and OXLO1 are cleared.

3) Scale Sequence Termination. Termination operations are initiated when either  $AU_{34} \neq AU_{33}$  or Kl = 0. Refer to tables 6.5-4 and 6.5-5 for sequential lists of W and scale sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams.

4) <u>W-Sequence Storage of KO</u>. At the termination or abortion of the scale sequence, the Hold 1 and Hold 2 flip-flops are cleared which allows the W-sequence to perform the storage of KO in control memory at the address 000178. Refer to table 6.5-6 for a sequential list of essential W-sequence events. Develop these commands by referring to the proper enable pages in the logic diagrams.

# 6.5-5. SUMMARY

The SF instruction is format 2 and uses the value k. The k value is available in KO after T2.4 time of the I-sequence. The scale and W-sequences are required to complete the execution of this instruction.

Figure 6.5-1. Scale Sequence, One Place Shift

6.5-4

Figure 6.5-2. Final Scale W and Last W Sequence Data Flow

| TABLE 6.5-1. | Ι  | , W,  | AND    | SCALE   | SEQUE | ENCE | ESSENT | IAL | COMMANDS |

|--------------|----|-------|--------|---------|-------|------|--------|-----|----------|

| WI           | TH | MAXIN | AUM∙ S | SHIFT ( | COUNT | ALL( | OWED = | 0*  |          |

| TIME NOTATION | COMMANDS                                     |

|---------------|----------------------------------------------|

|               | I SEQUENCE                                   |

| Tl.4          | Clear KO                                     |

| T2.3          | Clear OXLOO ff                               |

| T2.4          | Z Sel <sub>5-0</sub> → KO (KO = 0)           |

| T3.4          | Set Hold 1 ff, clear Scale Factor ff (1XL00) |

| T4.1          | Set OXLO1 ff                                 |

| T4.3          | Set OXLO2 ff, set Hold 2 ff                  |

|               | <u>W</u> SEQUENCE                            |

| T1.1          | Set Clear Hold ff, clear OXLO1 ff            |

| T1.3          | Clear OXLO2 ff                               |

| T4.1          | **Clear Spec Int Trans Reg.                  |

| T4.2          | Clear Hold 1 ff, clear Clear-Hold ff         |

| T4.3          | **Set Spec Int Trans Reg. = 17 <sub>8</sub>  |

|               | W SEQUENCE TO STORE KO                       |

| T1.3          | Clear Hold 2 ff                              |

$\ast$  The W-sequence events which store KO are not shown.

\*\* These commands pertain to the events which store KO and are discussed later in this sheet.

| TIME NOTATION | COMMANDS                                                                                           |

|---------------|----------------------------------------------------------------------------------------------------|

|               | <u>I SEQUENCE</u>                                                                                  |

| T1.3          | Clear F                                                                                            |

| T1.4          | Clear KO                                                                                           |

| T2.3          | Clear OXLOO ff                                                                                     |

| T2.4          | Z Sel <sub>11-6</sub> $\longrightarrow$ F, set OXF06 ff, Z Sel <sub>5-0</sub> $\longrightarrow$ KO |

| T3.1          | Set Clear Hold ff                                                                                  |

| T3.4          | Set Hold 1 ff, clear Scale Factor ff (1XL00)                                                       |

| T4.1          | **Clear Spec Int Trans Reg                                                                         |

| T4.2          | Clear Hold 1 ff, clear Clear-Hold ff                                                               |

| T4.3          | **Set Spec Int Trans Reg = 17 <sub>8</sub>                                                         |

|               | W SEQUENCE TO STORE KO                                                                             |

| Tl.3          | Clear Hold 2 ff                                                                                    |

|               |                                                                                                    |

TABLE 6.5-2. I. W. AND SCALE SEQUENCE ESSENTIAL COMMANDS WITH  $AU_{35i} \neq AU_{34i}$

-----

1.11

\*The W-sequence events which store KO are not shown.

\*\*These commands pertain to the events which store, KO and are discussed later in this sheet.

· · · · · · · · · · · ·

$(a_{ij})_{ij} = (a_{ij})_{ij} (a_{ij}) (a_{ij})_{ij} (a_{ij}) (a_{ij})_{ij} (a_{ij}) (a_{ij}) (a_{ij})_{ij} (a_{ij}) (a_{ij}) (a_{ij}) (a_{ij})_{ij} (a_{ij}) ($

$e^{i t}$

the second second

and a second second

| I, W, AND SCALE SEQUENCE ESSENTIAL COMMANDS WITH MAXIMUM               |

|------------------------------------------------------------------------|

| SHIFT COUNT ALLOWED $\neq$ 0 AND AU <sub>35i</sub> = AU <sub>34i</sub> |

| FIME NOTATION | COMMANDS                                                                                                                                                                |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | I SEQUENCE                                                                                                                                                              |

| Tl.4          | Clear KO                                                                                                                                                                |

| T2.3          | Clear OXLOO ff                                                                                                                                                          |

| T2.4          | Z Sel <sub>5-0</sub> → KO                                                                                                                                               |

| T3.4          | Set Hold 1 ff, clear Scale Factor ff (1XL00)                                                                                                                            |

| T4.1          | Set OXLO1 ff                                                                                                                                                            |

| T4.2          | Clear Kl                                                                                                                                                                |

| T4.3          | Set OXLOO ff, set Hold 2 ff, KO−1 —> Kl, clear X, clear W                                                                                                               |

| T4.4          | Clear KO, AULI $\longrightarrow$ X, ALLI $\longrightarrow$ W, *AU <sub>35</sub> $\longrightarrow$ W <sub>00</sub> , *AL <sub>17</sub> $\longrightarrow$ X <sub>00</sub> |

|               | FIRST W SEQUENCE                                                                                                                                                        |

| T1.1          | Kl —> KO, clear AU, clear AL                                                                                                                                            |

| T1.2          | Clear Kl, X→ AU, **W→ AL                                                                                                                                                |

| T1.3          | KO-1 → Kl, clear X, clear W                                                                                                                                             |

| T1.4          | Clear KO, AULI $\longrightarrow$ X, ALLI $\longrightarrow$ W, *AU <sub>35</sub> $\rightarrow$ W <sub>00</sub> , *AL <sub>17</sub> $\longrightarrow$ X <sub>00</sub>     |

| T2.1          | Kl → KO, clear AU, clear AL                                                                                                                                             |

| T2.2          | Clear Kl, X → AU, **W → AL                                                                                                                                              |

| (continue     | e until Kl = 0 or $AU_{34} \neq AU_{33}$ )                                                                                                                              |

\*These commands are enabled by gate 31W00 and 31X00 in the logic diagrams, figure 9-33, and are timed by the AUL1  $\longrightarrow$  X and ALL1  $\longrightarrow$  W commands.

\*\*The transmission of bit 00 for the W → AL commands is through gate 83A00 in the logic diagrams, figure 9-33. TABLE 6.5-4. TERMINATION OF SCALE SEQUENCE BY K1 = O(W SEQUENCE)\*

| TIME NOTATION | COMMANDS                                                                                                                                                  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <u>W</u> SEQUENCE                                                                                                                                         |

| TX.3          | KO-1 $\longrightarrow$ Kl (Kl = O), Clear X, Clear W                                                                                                      |

| TX.4          | Clear KO, AUL1 $\rightarrow$ X, ALL1 $\rightarrow$ W, **AU <sub>35</sub> $\rightarrow$ W <sub>00</sub> , **AL <sub>17</sub> $\rightarrow$ X <sub>00</sub> |

| TX.1          | Kl $\longrightarrow$ KO (KO = O), set Clear Hold ff, clear AU, clear AL                                                                                   |

| TX.2          | Clear K1, X $\rightarrow$ AU, ***W $\rightarrow$ AL                                                                                                       |

| TX.3          | KO-1 → Kl, clear OXLOO ff, set OXLO2 ff, clear X, clear W                                                                                                 |

| TX.4          | AUL1 $\rightarrow$ X, ALL1 $\rightarrow$ W, **AU <sub>35</sub> $\rightarrow$ W <sub>00</sub> , **AL <sub>17</sub> $\rightarrow$ X00 (not used)            |

| TX.1          | Clear OXLO1 ff                                                                                                                                            |

| TX.3          | Clear OXLO2 ff                                                                                                                                            |

| next T4.2     | Clear Hold 1 ff, clear Clear-Hold ff                                                                                                                      |

|               | W SEQUENCE TO STORE KO                                                                                                                                    |

| T1.3          | Clear Hold 2 ff                                                                                                                                           |

\*The W-sequence events which store KO are not shown.