- BILL FLANAGAN

6,00

# 1219 COMPUTER MAINTENANCE STUDENT STUDY GUIDE

### 13 JANUARY 1967

### PX 3814-0-1

Prepared by: Defense Systems Training

UNIVAC DEFENSE SYSTEMS DIVISION

© 1967 - SPERRY RAND CORPORATION

### S.G.1219 (M) Effective Pages

LIST OF EFFECTIVE PAGES

| PAGE<br>NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHANGE IN<br>EFFECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PAGE<br>NUMBER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CHANGE IN<br>EFFECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title<br>ii thru viii<br>1.1-1 thru 1.1-2<br>2.1-1 thru 2.1-6<br>3.1-1 thru 3.1-2<br>3.2-1 thru 3.2-2<br>3.3-1 thru 3.3-10<br>4.1-1 thru 4.1-10<br>5.1-1 thru 5.1-8<br>5.2-1 thru 5.2-12<br>5.3-1 thru 5.2-12<br>5.3-1 thru 5.3-6<br>5.4-1 thru 5.4-8<br>5.5-1 thru 5.5-4<br>5.6-1 thru 5.6-6<br>5.7-1 thru 5.7-6<br>5.8-1 thru 5.7-6<br>5.8-1 thru 5.8-6<br>5.9-1 thru 5.10-4<br>5.11-1 thru 5.11-6<br>5.12-1 thru 5.12-8<br>5.13-1 thru 5.13-6<br>5.14-1 thru 5.14-6<br>5.15-1 thru 5.15-10<br>5.16-1 thru 5.16-6<br>5.17-1 thru 5.17-6<br>5.18-1 thru 5.19-8<br>5.20-1 thru 5.20-4<br>5.21-1 thru 5.21-4<br>5.22-1 thru 5.22-4 | Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original | 5.24-1 thru 5.24-6<br>5.25-1 thru 5.25-6<br>5.26-1 thru 5.26-4<br>6.1-1 thru 6.1-18<br>6.2-1 thru 6.2-10<br>6.3-1 thru 6.3-14<br>6.4-1 thru 6.3-14<br>6.4-1 thru 6.4-6<br>6.5-1 thru 6.5-12<br>6.6-1 thru 6.5-12<br>6.6-1 thru 6.5-8<br>6.7-1 thru 7.1-14<br>7.2-1 thru 7.2-14<br>7.3-1 thru 7.2-14<br>7.3-1 thru 7.3-6<br>7.4-1 thru 7.4-12<br>7.5-1 thru 7.5-4<br>7.6-1 thru 7.6-8<br>8.1-1 thru 8.1-14<br>8.2-1 thru 8.2-4<br>8.3-1 thru 8.3-4<br>8.4-1 thru 8.4-20<br>8.5-1 thru 8.5-18<br>8.6-1 thru 8.6-24<br>8.7-1 thru 8.7-6<br>8.8-1 thru 8.10-6<br>8.10-1 thru 8.10-6<br>8.12-1 thru 8.12-12<br>8.13-1 thru 8.13-4<br>8.14-1 thru 8.14-6 | Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original<br>Original |

| 5.23-1 thru 5.23-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Original                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

م مرجع

#### PREFACE

The purpose of this study guide is to provide a text for study of the maintenance of the UNIVAC<sup>®</sup> 1219 computer. The information herein supplements that which is presented in class and that contained in the  $\underline{\text{UNIVAC}^{\$}$  1219 Technical Manual.

Training on the UNIVAC 1219 computer is necessarily complemented by operation descriptions, charts, block diagrams, simplified logic diagrams, and study questions. In this study guide most of these training aids are available for reference in the sequential order of course development. The use of this information is determined by the instructor.

Each section contains a list of references which are portions of the <u>UNIVAC 1219</u> <u>Technical Manual</u>, PX 3316. If no reference is made to this material within the study guide text, the student should read the information at the completion of the study guide section.

#### a Baltalaria

"교육을 한 묘감 여왕 考議된 형왕 (2007) 2010년 - 전 6월 2011년 1월 2011년 - 2011년 - 2011년 - 2011년 2011년 2011년 - 2012년 - 2012년 2011년 - 2012년 - 2012년 - 2012년 8017년 - 2012년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 2011년 2011년 2011년 - 2012년 2011년 - 2012년 2017년 2011년 2011년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 2011년 2011년 - 2012년 2011년 - 2012년 4년 11월 2011년 2011년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 2011년 - 2012년 - 2011년 2011년 - 2012년 - 2011년 4년 11월 2011년 2011년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 - 2011년 2011년 - 2011년 2011년 - 2011년 2011년 - 2011년 -

#### **OUTLINE OF CONTENTS**

SECTION 1 - GENERAL INTRODUCTION 1.1 General Description SECTION 2 - PROGRAMING 2.1Instruction Words SECTION 3 - OPERATION 3.1 Controls and Indicators 3.2 Manual Instruction Execution 3.3 Utility Package I SECTION 4 - LOGIC INTRODUCTION 4.1 Logic Circuits, Symbology, and Component Notation SECTION 5 - CONTROL SECTION 5.1 Master Clock, Mode Control, Phase Step Mode, Phase Repeat Main Timing, Instruction Sequencer, Operation Step Mode. 5.2Sequence Step, and Stop Operations 5.3 Instruction Execution Techniques 5.4 I Sequence 5.5 Function Code Translator Instruction Execution of STOP 5.6 5.7 Instruction Execution of ENTALK, ADDALK 5.8 Instruction Execution of ENTICR, ENTSR 5.9 Instruction Execution of ENTBK, ENTBKB 5.10 Instruction Execution of ENTB, ENTBB 5.11Instruction Execution of ENTAU, ENTAUB, ENTAL, ENTALB, ADDAL, ADDALB, SUBAL, SUBALB 5.12 Instruction Execution of ADDA, ADDAB, SUBA, SUBAB Instruction Execution of CL, CLB, STRB, STRBB, STRAL, STRALB, STRAU, 5.13STRAUB 5.14 Instruction Execution of STRICR, STRADR, STRSR 5.15 Instruction Execution of SLSU, SLSUB, SLSET, SLCL, SLCP 5.16 Instruction Execution of CPAL, CPAU, CPA Instruction Execution of CMAL, CMALB, CMSK, CMSKB 5.17Instruction Execution of RND 5.18Instruction Execution of JP, JPB, JPAUZ, JPALZ, JPAUNZ, JPALNZ, JPAUP, 5.19 JPALP, JPAUNG, JPALNG Instruction Execution of IJPEI, IJP 5.20 5.21Instruction Execution of RJP Instruction Execution of IRJP, IRJPB 5.22 5.23 Instruction Execution of SKP, SKPNBO, SKPOV, SKPNOV 5.24Instruction Execution of BSK 5.25 Instruction Execution of ISK Instruction Execution of BJP 5.26

#### SECTION 6 - ARITHMETIC SECTION

- 6.1 X-D' Adder

- 6.2 Instruction Execution of SKPODD, SKPEVN and Parity Evaluator

- 6.3 Instruction Execution of RSHAU, RSHAL, RSHA, LSHAU, LSHAL, LSHA

- 6.4 KO-1 Adder

- 6.5 Instruction Execution of SF

- 6.6 Instruction Execution of MULAL, MULALB

- 6.7 Instruction Execution of DIVA, DIVAB

#### SECTION 7 - MEMORY SECTION

- 7.1 General Description of Main Memory

- 7.2 Main Memory Internal Operation

- 7.3 General Description of Control Memory

- 7.4 Control Memory Internal Operation

- 7.5 General Description of Bootstrap Memory

- 7.6 Bootstrap Memory Internal Operation

#### SECTION 8 - INPUT/OUTPUT SECTION

- 8.1 General Description

- 8.2 Instruction Execution of SIN, SOUT, SEXF, INSTP, OUTSTP, EXFSTP

- 8.3 Instruction Execution of IN, OUT, EXF

- 8.4 Signal Detection and Selection

- 8.5 Input Data Request Operations

- 8.6 Output Data and External Function Request Operations

- 8.7 Continuous Data Mode Operations

- 8.8 Instruction Execution of OUTOV, EXFOV

- 8.9 Instruction Execution of SKPIIN, SKPOIN, SKPFIN, SKPNR, SRSM

- 8.10 External Interrupt Request Operations

- 8.11 Real Time Clock Request Operations, Generation of RTC Monitor and Overflow Interrupt and Instruction Execution of RTC

- 8.12 Instruction Execution of RIL, EXL, SIL, SXL, WTFI, and Special and Monitor Interrupt Operations

- 8.13 Inter-Computer Operations

- 8.14 B Network Adder

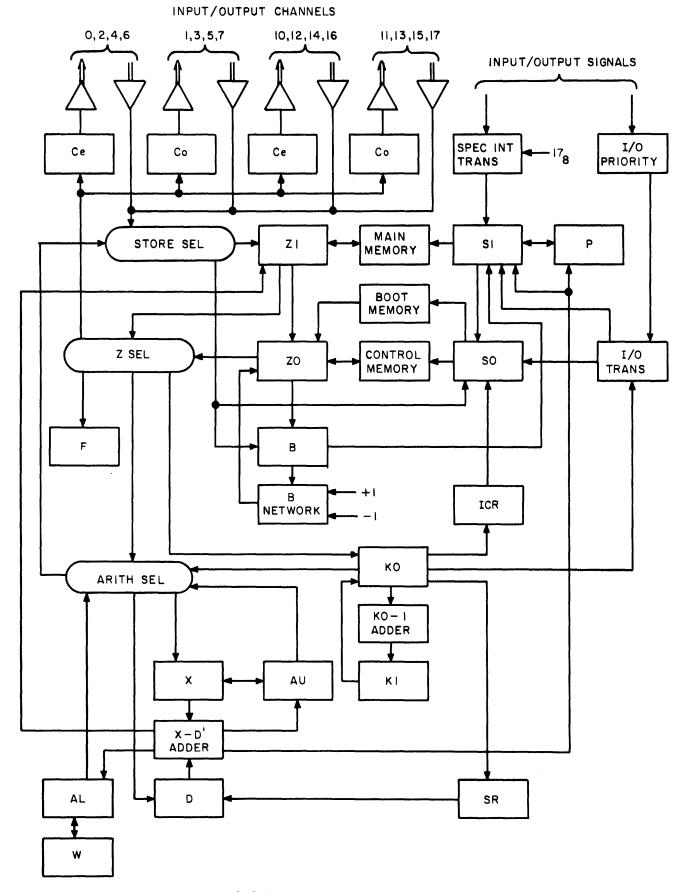

## S.G.1219 (M) Block Diagram

۳

1219 Computer Block Diagram

vii

#### SECTION 1 - GENERAL INTRODUCTION

1.1. GENERAL DESCRIPTION

1.1-1. OBJECTIVES

To present the general characteristics and descriptions of the computer sections and features of those sections.

1.1-2. INTRODUCTION

None.

1.1-3. REFERENCES

UNIVAC 1219 Technical Manual, Volume I, Section 1.

1.1-4. INFORMATION

UNIVAC 1219 Technical Manual, Volume I, Section 1.

1.1-5. SUMMARY

None.

#### SECTION 2 - PROGRAMING

#### 2.1. INSTRUCTION WORDS

#### 2.1-1. OBJECTIVES

To present the instruction word format, interpretation of its designators, definition of terms specified by the instruction, and description of the instruction repertoire.

#### 2.1-2. INTRODUCTION

The instruction word controls the machine operations to perform a predetermined function according to its bit configuration. There are  $102_{10}$  different instructions.

#### 2.1-3. REFERENCES

UNIVAC 1219 Technical Manual, Volume I, Paragraphs 3-6a, b, and c.

#### 2.1-4. INFORMATION

a. <u>General Description</u>. The instruction word is an 18-bit number which controls the computer operations to achieve some predetermined function. This function could be an arithmetic type such as addition or subtraction, a logical type such as logical multiplication (AND function), or a data transfer operation causing a binary word to be brought from memory and placed into a register. The operation to be performed is specified by the bit configuration (coding) of the instruction word.

An over-all computer operation such as navigation, target position prediction, etc., is performed by the sequential execution of selected instructions. This arrangement of instructions is referred to as a program. The instructions are stored in memory along with 18-bit data words. There are no restrictions imposed on the bit configuration of a data word and it may therefore be identical in content to an instruction word. Distinction between these word types is possible, however, because the addresses of the memory locations containing the instructions are kept track of in the P register. When a word is extracted from memory, the computer can distinguish an instruction from data because the time during which the instruction is obtained is different from that involving data word extraction from memory, and because the instruction is placed in a special register.

The memory origin of the instructions executed are controlled such that they are obtained from memory at sequential addresses. The addresses are formulated by incrementing the content of P by +1 after each instruction is obtained. Therefore, as an instruction is being executed, P holds the address of the next instruction.

#### b. Format 1 Instructions.

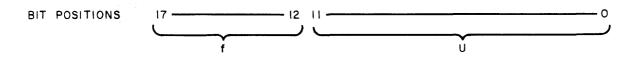

1. <u>Instruction Word Configuration</u>. The format 1 instructions are identified by the 6 most significant binary bits of the word forming an octal code of other than 508. These octal digits comprise the function code (also referred to as the f designator). Refer to figure 2.1-1 for the format 1 configuration.

NOTE: f CAN HAVE ANY VALUE OTHER THAN 508

Figure 2.1-1. Format 1 Instruction Word Configuration

The function code specifies the operation to be performed. The lower 12 bits (U) are used as determined by the function code. If the operation requires a memory reference, U formulates a portion of the memory address. In other cases, U may be the actual number handled by the instruction. Regardless of the origin of this number (memory or U), the number is referred to as the operand.

#### 2. Even-Numbered Function Codes or $f > 50_8$ Instructions.

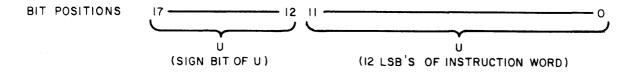

a) Use of U as a Constant. There are only four format 1 instructions which use the U portion as the operand (also referred to as constant). These function codes are f = 36, 37, 70, 718. In order to provide an 18-bit operand value, these instructions extend the sign of U (U<sub>11</sub>) into the upper 6 bits. This value, referred to as XU, is formulated in a register separate from that which holds the function code. Refer to figure 2.1-2 for the XU configuration.

Figure 2.1-2. XU Configuration for f = 36, 37, 70, 71

As an example of the use of XU, consider the instruction word 7040658. The function code of 70 (ENTALK) places the constant XU in the AL register. The initial AL content would be cleared and the XU value of  $774065_8$  would be placed in AL. No memory reference other than that necessary to obtain the instruction word is required.

b) Use of U as an Address. All format 1 instructions other than f = 36, 37, 70, 71 require a memory reference either to obtain an operand or to store a value into memory. U is used as the 12 least significant bits of the address. Sixteen bits are necessary to allow addressing for the complete  $65,536_{10}$ -word memory. The upper 4 bits are supplied from either the P register (P<sub>15-12</sub>) or the special register (SR<sub>4,2-0</sub>). The resulting address is referred to as either Up or U<sub>SR</sub> depending upon which is used. The origin of these 4 bits is determined by the function code and SR<sub>3</sub>. SR<sub>3</sub> is considered to be the SR active bit. If SR is inactive (SR<sub>3</sub> =  $0_2$ ), SR is not used. Refer to table 2.1-1 for the conditions necessary to use Up and U<sub>SR</sub>.

| CONDITIONS .                                           | RESULTING ADDRESS*                                                   |

|--------------------------------------------------------|----------------------------------------------------------------------|

| $(SR_3 = 0_2)$ or $(f = 30, 31, 34, 35, 51-67, 72-76)$ | $U_{p} = \underbrace{15 - 12}_{P_{15-12}} \underbrace{11 - 0}_{U}$   |

| $(SR_3 = 1_2) \& (f = 01-27, 32, 33, 40-47)$           | $U_{SR} = \underbrace{15 - 12}_{SR_{4,2-0}} \underbrace{11 - 0}_{U}$ |

|  | TABLE | 2.1- | 1. | Up | AND | USR | CONDITIONS |

|--|-------|------|----|----|-----|-----|------------|

|--|-------|------|----|----|-----|-----|------------|

\* If interrupt sequence is in effect, upper 4 bits of address are 0's. Address =  $\underbrace{15 - 12}_{0's}$   $\underbrace{11 - 0}_{U}$

All format 1 instructions other than those listed in Table 2.1-1 use XU as a constant. The interrupt sequence is discussed in a later sheet.

There are instructions which can be used to change the contents of SR to any configuration. SR3 is not considered as an address bit; its only use is to specify the activeness of SR.

If  $P_{15-12}$  is used, the address used by the instruction will be in the same area of memory from which the instruction word itself is obtained. Realize that the instruction is obtained from the address held by P. P is advanced to the address of the next instruction while the instruction is being brought from memory. During the instruction execution, P holds the address from which the current instruction was obtained plus one. If the current instruction was extracted from address 017778 which is in bank 1, the upper 4 bits of Up will be 00102 which will reference bank 2. Thus, care must be taken in executing instructions from the last address of a bank.

3. Odd Numbered Function Codes and  $f < 50_8$  Instructions. For instructions with odd-numbered function codes less than 508, the XU, Up, or USR value is modified. These function codes require the addition of one of the control memory B (index) registers to the address or constant formed with U (Up, USR, or XU). The B register to be used is specified by the 3-bit index control register (ICR). There are instructions which can be used to change the contents of ICR. ICR controls all

instruction references to a B register. The modifications of Up + B,  $U_{SR}$  + B, and XU + B are performed in an end-around-carry manner.

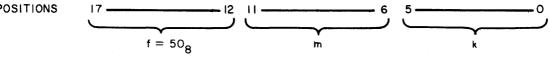

c. Format 2 Instructions. The format 2 instructions are identified by the 6 most significant binary bits of the word forming the octal code of  $50_{\rm B}$ . Refer to figure 2.1-3 for the format 2 configuration.

BIT POSITIONS

Figure 2.1-3. Format 2 Instruction Word Configuration

For these instructions, f only indicates the format 2 configuration. The m designator is the effective function code (sometimes referred to as minor function code). It specifies the operation to be performed and is often referred to as f. The m designator is placed in the same register as is f for format l instructions. The machine is able to determine which designator this register holds by inspecting the format 2 flip-flop. This flip-flop is set if the upper 6 bits of the instruction word indicate format 2  $(50_8)$ .

The remaining 6 bits comprise the k designator. The use of k is determined by m. Most of the format 2 instructions are of the input/output type, and k indicates the I/O channel number to be affected. In other cases, k represents a shift count and a value (constant) to be placed in ICR or SR. None of the format 2 instructions use any of the instruction bits to form a memory address.

d. Fault Function Codes. There are three format 1 function codes which cause an instruction fault condition. These are f = 00, 01, and 77<sub>8</sub>. This fault condition interrupts the program and jumps the program to either address 00000 (control memory) or address  $00500_8$  (bootstrap) depending upon the position of the AUTOMATIC RECOVERY switch. This switch and its effect are discussed in a later sheet. There are other instructions which are illegal; however, they do not cause the fault interrupt condition.

e. <u>Repertoire of Instructions (non-1/0 Type)</u>. There are 3 basic groups of instructions. Some instructions require an operand from memory. Others store the contents of AU, AL, or B into memory. The remaining instructions do not use memory. Refer to table 2.1-2 for a listing of the non-I/O instructions. The important feature of this table shows the use of XU, Up, USR, k and B modification.

Refer to the UNIVAC 1219 Technical Manual, paragraph 3-6c for a more exact description of the instructions. The input/output instructions are discussed in later sheets.

|                                                                                                                                                                                                                                                                              | 1219 COMPUTER REPERTOIRE OF INSTRUCTION                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ENTER (Mem Register)                                                                                                                                                                                                                                                         | SUBTRACT (Reg - Mem Reg)                                                                                                                                                                                   | COMPARE (Reg & Mem)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10 ENTAU Address = U <sub>P</sub> ,<br>11 *ENTAUB U <sub>SR</sub> , U <sub>P</sub> +B, or<br>12 ENTAL U <sub>SR</sub> +B<br>13 *ENTALB<br>32 ENTB<br>33 *ENTBB                                                                                                               | 16       SUBAL       Address = Up,         17       *SUBALB       USR, Up+B,         22       SUBA       or USR+B         23       *SUBAB       SELECTIVE (logical operation                               | 02 CMAL Address =<br>03 *CMALB Up. U <sub>SR</sub> ,<br>06 CMSK Up + B, or<br>07 *CMSKB U <sub>SR</sub> + B<br>SKIP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                              | with Reg & Mem)                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ENTER (non-memory)<br>36 ENTBK $(XU \rightarrow B)$<br>37 *ENTBKB $(XU+B \rightarrow B)$<br>70 ENTALK $(XU \rightarrow AL)$<br>50:72 ENTICR $(k \rightarrow ICR)$<br>50:73 ENTSR $(k \rightarrow SR)$<br>STORE (registr $\rightarrow$ Mem)<br>40 CL 0's $\rightarrow$ Mem at | $\begin{array}{c cccc} 04 & SLSU \\ 05 & *SLSUB \\ \hline \\ 51 & SLSET \\ 52 & SLCL \\ \hline \\ 53 & SLCP \\ \hline \\ $ | 56       BSK       Mem used,         57       ISK       Address =         50:50       SKP       k = con-sole skip         50:51       SKPNBO         50:52       SKPOV         50:53       SKPNCV         50:54       SKPODD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 41 *CLB $\int$ Address Up,                                                                                                                                                                                                                                                   | 50:63 CPA                                                                                                                                                                                                  | 50:55 SKPEVN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 42 STRB $U_{SR}$ , $U_{P}$ + B, or<br>43 *STRBB $U_{SR}$ +B<br>44 STRAL Storage Ad-<br>dress = U_P,                                                                                                                                                                          | ROUND (Reg, no Mem) 50:60 RND k not used                                                                                                                                                                   | 34 JP<br>35 *JPB dress = Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $45 *STRALB \left\{ \begin{array}{l} U_{SR}, U_{P} + B, \\ 46 & STRAU \\ 47 *STRAUB \end{array} \right\} or U_{SR} + B$ $72  STRICR \\ 74  STRADR \\ dress = U_{P}$                                                                                                          | MULTIPLY & DIVIDE (Reg & Mem)<br>24 MULAL<br>25 *MULALB<br>26 DIVA<br>27 *DIVAB<br>MULAL<br>Address = U <sub>P</sub> ,<br>U <sub>SR</sub> , U <sub>P</sub> + B<br>or U <sub>SR</sub> + B                   | $\begin{array}{ccc}  & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & $ |

| 75 STRSR J                                                                                                                                                                                                                                                                   | SHIFT & SCALE FACTOR (no Mem)                                                                                                                                                                              | 65 JPALP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ADD (Reg + Mem $\rightarrow$ register)14ADDALAddress = $U_p$ ,15*ADDALBUSR, $U_p$ + B, or                                                                                                                                                                                    | 50:41 RSHAU<br>50:42 RSHAL<br>50:43 RSHA k = shift count                                                                                                                                                   | 66 JPAUNG<br>67 JPALNG<br>73 BJP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 20 ADDA U <sub>SR</sub> + B<br>21 *ADDAB                                                                                                                                                                                                                                     | 50:44 **SF<br>50:45 LSHAU                                                                                                                                                                                  | INDIRECT JUM P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $\frac{21}{\text{ADD}(\text{AL} + \text{XU} \rightarrow \text{AL})}$ $71  \text{ADDALK}  \text{no memory}$                                                                                                                                                                   | 50:46 LSHAL<br>50:47 LSHA                                                                                                                                                                                  | 54 UPEI jump ad-<br>dress in mem<br>at address<br>Up                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                            | DIRECT RETURN JUMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                            | 76 RJP jump ad-<br>dress = U <sub>P</sub> +1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| NOTES: *Odd function codes less than                                                                                                                                                                                                                                         | <b>u</b>                                                                                                                                                                                                   | INDIRECT RETURN JUMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| **Scale factor instruction (f = 5<br>memory location.                                                                                                                                                                                                                        | 0:44) stores a shift count in a fixed                                                                                                                                                                      | 30 IRJP jump add. =<br>31 *IRJPB NO.+1 at U <sub>P</sub><br>or U <sub>P</sub> + B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                            | STOP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                            | 50:56 STOP k = console<br>stop key                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

TABLE 2.1-2. 1219 COMPUTER REPERTOIRE OF INSTRUCTIONS (NON-1/O)

~

S.G. 1219 (M)2.1

2.1-5. SUMMARY

There are 2 basic instruction types, Format 1 and Format 2. Format 1 instructions  $(f \neq 50_8)$  use the lower 12 bits (U) either as an address (Up or USR) or an operand (constant, XU). Some Format 1 instructions specify modification of the value formed with U by the addition of B<sub>ICR</sub>.

Format 2 instructions ( $f = 50_8$ ) use the m designator as the actual function code. The lower 6 bits (k) is used as a constant.

#### SECTION 3 - OPERATION

#### 3.1. CONTROLS AND INDICATORS

#### 3.1-1. OBJECTIVES

To present the general description of the controls and indicators, their functions, and their uses.

#### **3.1-2.** INTRODUCTION

Although the computer is basically automatic, there are provisions for control of the computer. Indicators provide a means of monitoring the operations. Switches are used to control a part or all of the computer operation, to provide jump and stop conditions, and to govern the speed of operation for maintenance purposes. There are also pushbutton/indicators which monitor and allow the manual setting of flip-flops, and pushbuttons with which an entire register can be cleared.

#### 3.1-3. REFERENCES

UNIVAC 1219 Technical Manual, Volume I, Paragraphs 3-1 and 3-2.

#### 3.1-4. INFORMATION

Refer to the <u>UNIVAC 1219 Technical Manual</u>, Volume I, paragraphs 3-1 and 3-2 for the general description of controls and indicators.

3.1-5. SUMMARY

None.

.