# NAVSEA OP 3514 (PMS/SMS) VOLUME 1

# FIRST REVISION CHANGE 7

# DIGITAL COMPUTER MK 152 SERIES

# DESCRIPTION, OPERATION, AND MAINTENANCE

THIS PUBLICATION SUPERSEDES OP 3514 (PMS/SMS) DATED 1 JANUARY 1972

PUBLISHED BY DIRECTION OF COMMANDER, NAVAL SEA SYSTEMS COMMAND

> 1 JANUARY 1973 CHANGED 1 JULY 1978

1.00

-

# LIST OF EFFECTIVE PAGES

| - 「「「「「「「」」」を行った。 ない かんしょう かんしょう しんしょう |           |                                         |             |

|----------------------------------------|-----------|-----------------------------------------|-------------|

| Page No. *Char                         | nge No.   | Page No.                                | *Change No. |

|                                        |           |                                         | -           |

| Title and A                            | 7         | 2-120                                   | 5           |

| B/(C blank)                            | 7         | 2-121 thru 2-129                        | 0           |

| Flyleaf/Flyleaf-2                      | 0         | 2-130 and 2-131                         | 7           |

| Foreword and Foreword-2                |           | 2-132 thru 2-139                        | 0           |

| Foreword-3/(Foreword-4 blank)          | 7         | 2-140                                   | 5           |

| i thru vii                             | 0         | 2-141 thru 2-150                        | 0           |

| viii and ix                            | 7         | 2–151/(2–152 blank)<br>2–153 thru 2–158 | 7           |

| X                                      | 0         |                                         | 0           |

| xi<br>xii                              | 7         | 2-159                                   | 7           |

|                                        | 0         | 2-160                                   | 0           |

| xiii                                   | 7         | 2-161                                   | 7           |

| xiv thru xvi                           |           | 2-162 thru 2-173                        | 0           |

| xvii thru xix                          | 7         | 2-174                                   | 5           |

| XX                                     | -         | 2-175                                   | 0           |

| xxi                                    | 7         | 2-176                                   | 5           |

| xxii                                   | 0         | 2–177 thru 2–198                        | 0           |

| xxiii thru xxvii                       | 7         | 2-199                                   | 7           |

| xxviii                                 | 0         | 2–200 thru 2–213                        | 0           |

| xxix/(xxx blank)                       | 7         | 2-214                                   | 5           |

| xxxi and xxxii                         | 0         | 2–215 thru 2–267                        | 0           |

| 1-1 thru 1-9                           | 0         | 2-268                                   | 5           |

| 1-10                                   | 5         | 2–269 thru 2–286                        | 0           |

| 1–11 thru 1–13                         | 0         | 2-287                                   | 2           |

| 1-14 and 1-15                          | 5         | 2–288 thru 2–291                        | 0           |

| 1-16 and 1-17/(1-18 blank)             | 7         | 2-292                                   | 7           |

| 2-1                                    | 5         | 2–293 thru 2–295                        | 0           |

| 2-2 thru 2-5                           | 0         | 2-296                                   | 5           |

| 2-6                                    | 7         | 2-297                                   | 0           |

| 2-7 thru 2-12                          | 0         | 2-298                                   | 5           |

| 2-13                                   | 5         | 2-299                                   | 7           |

| 2-14                                   | 7         | 2-300                                   | 5           |

| 2–15 thru 2–17                         | 5         | 2-301 thru 2-305                        | 0           |

| 2-18                                   | 7         | 2-306                                   | 5           |

| 2-19 thru $2-21/(2-22  blank)$         | 0         | 2–307 thru 2–315                        | 0           |

| 2-23                                   | 5         | 2-316                                   | 5           |

| 2–24 thru 2–26                         | 0         | 2-317 and 2-318                         | 0           |

| 2-27                                   | 5         | 2-319                                   | 5           |

| 2–28 thru 2–76                         | 0         | 2–320 thru 2–322                        | 0           |

| 2-77                                   | 5         | 2-323                                   | 5           |

| 2-78 thru 2-101                        | 0         | 2-324 and 2-325                         | 0           |

| 2-102                                  | 5         | 2-326 and 2-327                         | 7           |

| 2-103                                  | 0         | 2-328                                   | 0           |

| 2-104 and $2-105$                      | 5         | 2-329                                   | 5           |

| 2-106                                  | 0         | 2-330                                   | 0           |

| 2-100 and $2-108$                      | 5         | 2-331                                   | 5           |

| 2-109                                  | 7         | 2-332 and 2-333/(2-334 blank)           |             |

| 2-110 and 2-111                        | 5         | 2-335 and 2-336                         | 0           |

| 2–112 thru 2–118                       | 0         | 2-337 and 2-338                         | 5           |

| 2-119                                  | 7         | 2-339 and 2-340                         | 0           |

| *Zero in this column indicates an or   | iginal pa | age.                                    |             |

A Change 7

### LIST OF EFFECTIVE PAGES (Continued)

| Page | No.  |

|------|------|

| Fage | TIO. |

.

\*Change No.

|          | 2-341                          | c |

|----------|--------------------------------|---|

|          |                                | 5 |

|          | 2–342 thru 2–344<br>2–345      | 0 |

|          | 2-345<br>2-346 thru 2-368      | 5 |

|          |                                | 0 |

|          | 2-369/(2-370 blank)            | 5 |

|          | 2-371 thru 2-376               | 0 |

|          | 2-377                          | 5 |

|          | 2-378 thru 2-397               | 0 |

|          | 2-398                          | 5 |

|          | 2-399                          | 0 |

|          | 2-400 thru 2-448               | 0 |

|          | 2-449                          | 7 |

|          | 2-450                          | 0 |

|          | 2-451                          | 5 |

|          | 2-452 and 2-453                | 0 |

|          | 2-454 thru 2-456               | 7 |

| <b>`</b> | 2-457                          | 7 |

|          | 2-458                          | 5 |

|          | 2-459 and 2-460                | 0 |

|          | 2-461                          | 5 |

|          | 2-462                          | 0 |

|          | 2-463 and 2-464                | 5 |

|          | 2-465 thru 2-473               | 0 |

| `        | 2-474 thru 2-476               | 7 |

| -        | 2-477 and 2-478                | 0 |

|          | 2-479 and 2-480                | 5 |

|          | 2-481 thru 2-483               | 0 |

|          | 2-484 and 2-485                | 5 |

|          | 2-486 thru 2-493/(2-494 blank) | 0 |

|          | 3–1 thru 3–26                  | 0 |

|          | 4-1 thru 4-15                  | 0 |

|          | 4-16                           | 7 |

|          | 5-1                            | 6 |

|          | 5-2                            | 7 |

|          | 5-3                            | 0 |

|          | 5-4 and 5-5                    | 6 |

|          | 5-6 thru 5-10                  | 0 |

|          | 5-11                           | 6 |

|          | 5-12                           | 0 |

|          | 5-13 and 5-14                  | 7 |

|          | 5-14A/(5-14B blank)            | 7 |

|          | 5-15 and 5-16                  | 7 |

|          | 5-16A/(5-16B blank)            | 6 |

|          | 5-17                           | 0 |

| ,        | 5-18 and 5-19                  | 0 |

|          | 5-20 and 5-21                  | 7 |

|          | 5-22 and 5-23/(5-24 blank)     | 6 |

|          |                                |   |

\*Zero in this column indicates an original page.

Change 7 B/(C blank)

~>>>

#### CHANGE RECORD

| CHANGE NO.  | DATE | TITLE AND/OR BRIEF DESCRIPTION             | SIGNATURE OF<br>VALIDATING OFFICER |

|-------------|------|--------------------------------------------|------------------------------------|

| , (Hange 46 |      | VOL, I FIRST REV. CH.G                     |                                    |

|             | •    |                                            |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

| <u> </u>    |      |                                            | 1 ·                                |

|             |      |                                            |                                    |

|             |      | -                                          |                                    |

|             |      | <u></u>                                    |                                    |

|             |      | ·<br>· · · · · · · · · · · · · · · · · · · |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

| <u> </u>    |      |                                            |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

|             | +    |                                            |                                    |

|             |      | · · · · · · · · · · · · · · · · · · ·      |                                    |

|             |      | · · · · · · · · · · · · · · · · · · ·      |                                    |

|             |      | · · · · · · · · · · · · · · · · · · ·      |                                    |

|             |      | · · · · · · · · · · · · · · · · · · ·      |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

|             |      |                                            |                                    |

#### FOREWORD

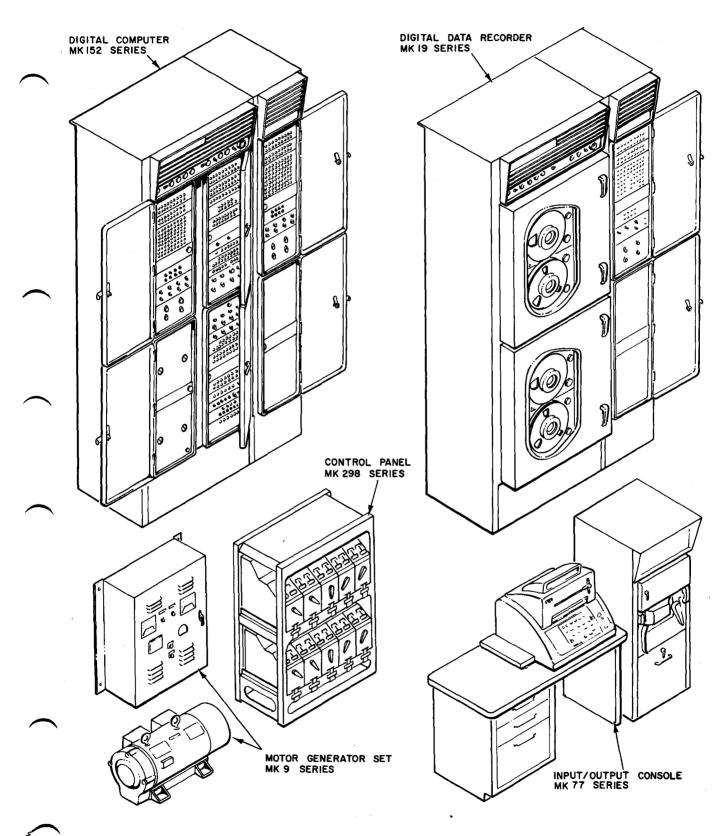

NAVSEA OP 3514 (PMS/SMS) First Revision physically and functionally describes the Digital Computer Mark 152 Series and provides all other information required by ship-board personnel for operation, installation, and maintenance of the equipment.

OP 3514 (PMS/SMS) is one of a family of Ordnance Publications (OP's) which provide comprehensive coverage of all modifications of Digital Computer Mk 152 and associated peripheral equipments. These manuals include the following:

| . [ | Manual                                 | Nomenclature of Equipment                                            |

|-----|----------------------------------------|----------------------------------------------------------------------|

| Ī   | OP 3514 (PMS/SMS) First Revision       | Digital Computer Mk 152 Series                                       |

|     | OP 3515 (PMS/SMS)                      | Input/Output Console Mk 77 Series                                    |

|     | OP 3516 (PMS/SMS)                      | Digital Data Recorder Mk 19 Series                                   |

|     | OP 3517 (PMS/SMS)                      | Control Panel Mk 298 Series                                          |

|     | OP 3518 (PMS/SMS)<br>OP 4245 (PMS/SMS) | Motor Generator Set Mk 9 Series<br>Input/Output Console Mk 95 Series |

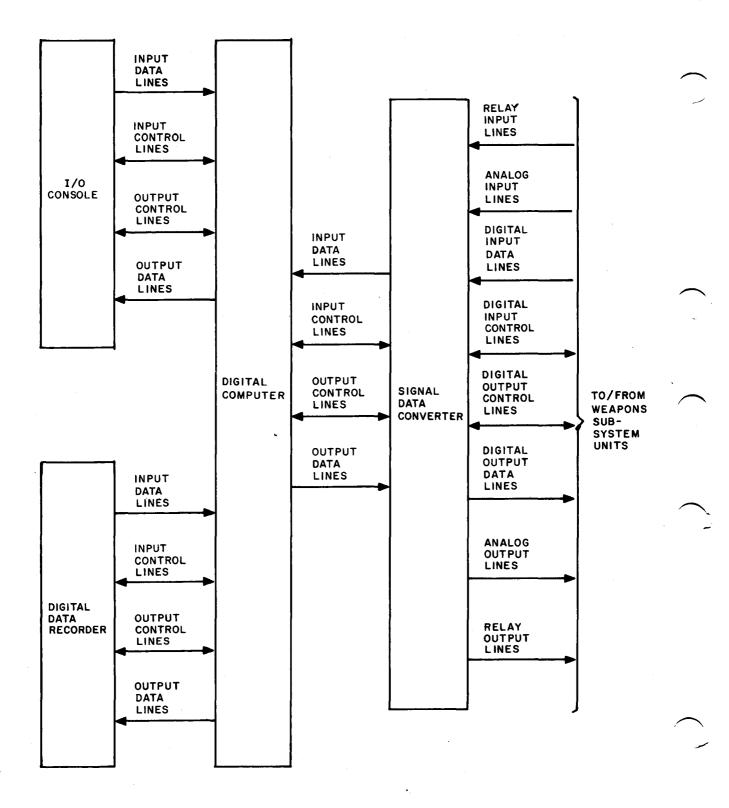

Although not included in the foregoing list, a Signal Data Converter (SDC) is an essential part of any digital Fire Control System (FCS) which employs component parts originally designed for analog operation. The TARTAR, TALOS, and TERRIER weapon systems use SDC's Mk 72, Mk 66, and Mk 75, respectively. Gun Fire Control System (GFCS) Mk 86 uses SDC Mk 69/Mk 70 and Signal Data Translator (SDT) Mk 1 for data conversion.

The digital computer complex equipment configuration found on various gun and guided missile ships depends principally on the shipboard weapons system(s). While other factors can influence the actual configuration on board a particular ship, the following equipments are generally utilized with the missile/gun systems indicated:

| Equipment                                      | TARTAR                   | TERRIER         | TALOS           | GFCS Mk 86      |

|------------------------------------------------|--------------------------|-----------------|-----------------|-----------------|

| Digital Computer<br>I/O Console<br>I/O Console | Mk 152<br>Mk 77<br>Mk 95 | Mk 152<br>Mk 77 | Mk 152<br>Mk 77 | Mk 152<br>Mk 77 |

| Digital Data Recorder                          | Mk 19                    | Mk 19           | Mk 19           |                 |

| Control Panel                                  | Mk 298                   | Mk 298          | Mk 298          |                 |

| Motor Generator Set                            | Mk 9                     | Mk 9            | Mk 9            |                 |

| Signal Data Converter                          | Mk 72                    | Mk 75           | Mk 66           | Mk 69/Mk 70     |

| Signal Data Translator                         |                          |                 |                 | SDT Mk 1        |

CHANGE 7

FOREWORD

| MOD<br>NO. | IL<br>NUMBER | UNIVAC<br>NUMBER | MODULES<br>(DRAWERS) | MEMORY<br>SIZE | I/O<br>CHANNELS   |

|------------|--------------|------------------|----------------------|----------------|-------------------|

| 0          | 2652595      | 7049747-00       | 3(6)                 | 32K            | 16 slow interface |

| 1          | 2525383      | 7049747-05       | 2(4)                 | 32K            | 8 slow interface  |

| 2          | 2536007      | 7049747-08       | 3(6)                 | 32K            | 8 slow interface  |

|            |              |                  |                      |                | 8 fast interface  |

| 3          | 2687278      | 7049747-11       | 3(6)                 | 40K            | 16 slow interface |

| 4          | 2923042      | 7049747-13       | 3(6)                 | 40K            | 8 slow interface  |

|            |              |                  |                      |                | 8 fast interface  |

| 5          | 3140291      | 7049747-14       | 2(4)                 | 48K            | 8 slow interface  |

This manual is applicable to Digital Computers Mk 152 Series configured as follows:

This publication consists of three volumes structured as follows:

VOLUME 1 - Description, Operation, and Maintenance

Chapter 1. Introduction

Chapter 2. Description

Section 2-1. Physical Description

Section 2-2. General Functional Description

Section 2-3. Detailed Functional Description

Chapter 3. Operation

Chapter 4. Installation

Chapter 5. Maintenance

VOLUME 2 Part 1 - Trouble Isolation

Chapter 6. Introduction

Chapter 7. Supporting Maintenance Data

Section 7-1. General Troubleshooting Information

Section 7-2. Manual Troubleshooting

Section 7-3. Troubleshooting Charts

Section 7-4. Schematic Diagrams of Printed Circuit Cards

VOLUME 2 Part 2 and Part 2A-Trouble Isolation

Chapter 8. Diagnostic Program

VOLUME 2 Part 3 - Trouble Isolation

Chapter 9. Functional Schematics

VOLUME 3 - Parts List

Chapter 10. Introduction

Chapter 11. Replaceable Parts List

Ships, training activities, supply points, depots, Naval shipyards and supervisors of shipbuilding are requested to arrange for the maximum practical use and evaluation of NAVSEA technical manuals. All errors, omissions, discrepancies, and suggestions for improvements to NAVSEA technical manuals shall be reported to the Naval Sea Data Support Activity (NSDSA), Naval Ship Weapon Systems Engineering Station (Code 5740), Port Hueneme, CA 93043 on NAVSEA Technical Manual Deficiency/Evaluation Report,

ंद्र

FOREWORD-2 CHANGE 7

NAVSEA Form 5600/2. To facilitate such reporting, three copies of Form NAVSEA 5600/2 are included at the end of each unclassified bound part of this technical manual being changed. All feedback comments will be thoroughly investigated and originators will be advised of action resulting therefrom. Extra copies of Form NAVSEA 5600/2 may be requisitioned from the Naval Publications and Forms Center (NPFC), Philadelphia, PA 19120.

The technical content of the manual covers Digital Computer Mk 152 Series as modified by ORDALTS 7732, 7889, 8008, 8331 Change 1, 30023, 8339, 8286, 8409, 8490, and 30094.

FOREWORD-3/(FOREWORD-4 blank)

-----

### TABLE OF CONTENTS

| Chap | oter    |                                   |                                                                                 | Page                         |

|------|---------|-----------------------------------|---------------------------------------------------------------------------------|------------------------------|

| LIST | OF ILL  | USTRATI                           | ONS                                                                             | xviii                        |

| LIST | OF TAI  | BLES                              | · · · · · · · · · · · · · · · · · · ·                                           | xxiii                        |

| SAF  | ETY SUN | MARY                              | · · · · · · · · · · · · · · · · · · ·                                           | xxxi                         |

| 1.   | INTRO   | DUCTION                           |                                                                                 | 1-1                          |

|      | 1-1.    | Purpose<br>1-3.                   | Functions                                                                       | 1-1<br>1-1                   |

|      | 1-4.    | Capabili<br>1-6.                  | tiesGeneral Characteristics1-10.Operational Characteristics                     | 1-4<br>1-4<br>1-5            |

|      | 1-11.   | System<br>1–12.<br>1–13.<br>1–14. | Description                                                                     | 1-5<br>1-5<br>1-5<br>1-5     |

|      | 1-15.   |                                   | bifferences                                                                     | 1-14                         |

|      | 1-17.   |                                   | ce DataEquipment SuppliedSpecial Tools and Test EquipmentEquipment Nomenclature | 1–14<br>1–14<br>1–14<br>1–14 |

|      | 1-22.   |                                   | ce Publications                                                                 | 1–16                         |

| 2.   | DESCR   | IPTION .                          |                                                                                 | 2-1                          |

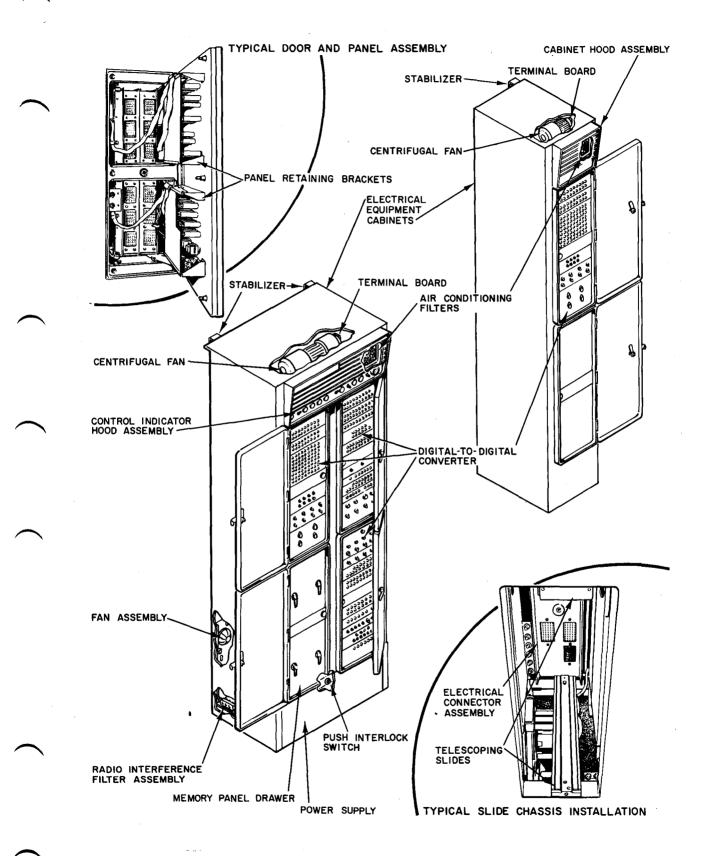

|      |         |                                   | Section 2-1. Physical Description                                               |                              |

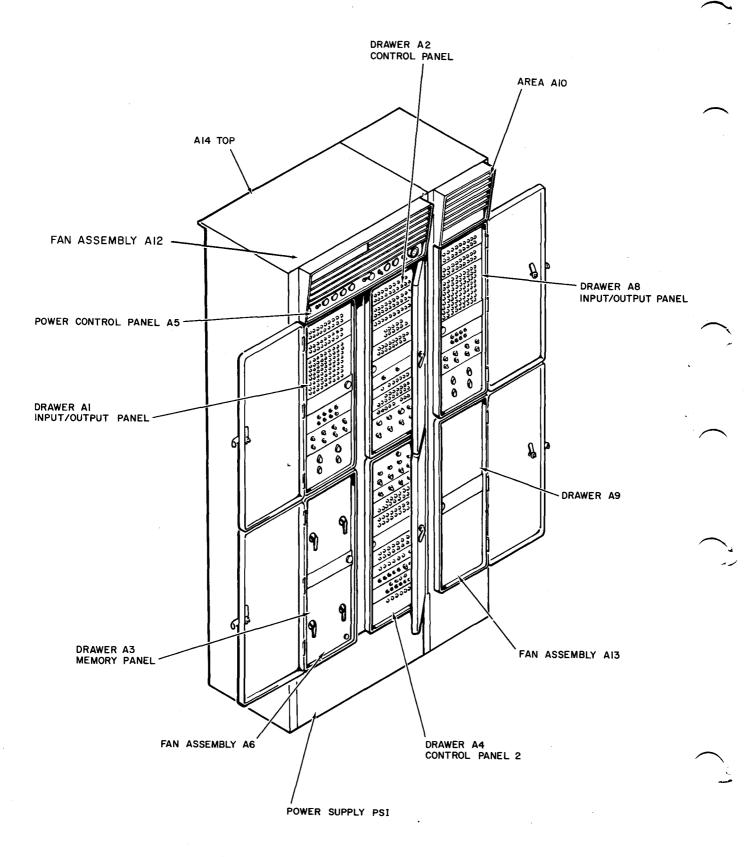

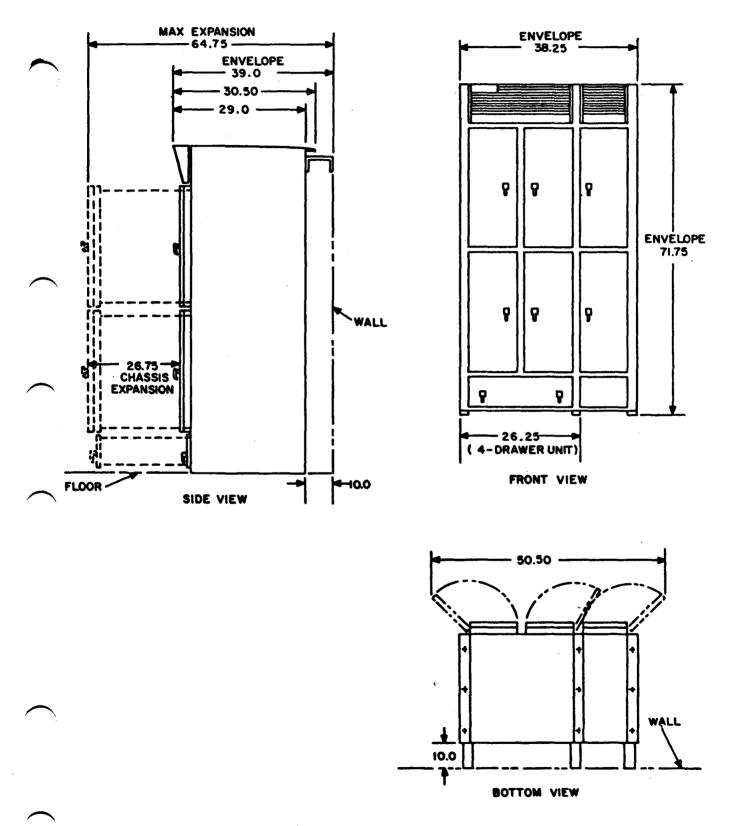

|      | 2-1.    |                                   | tion                                                                            |                              |

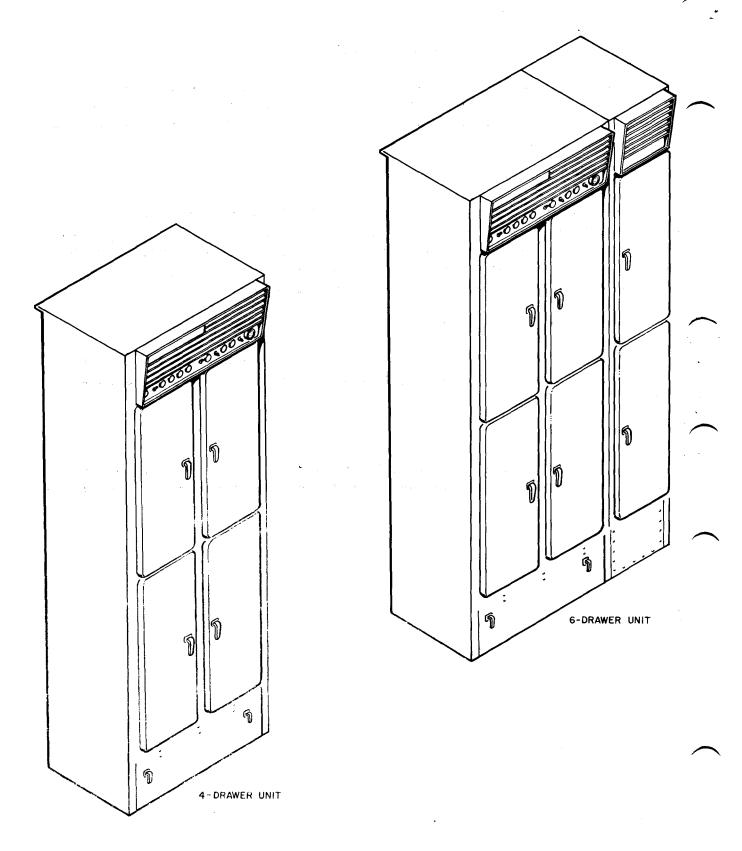

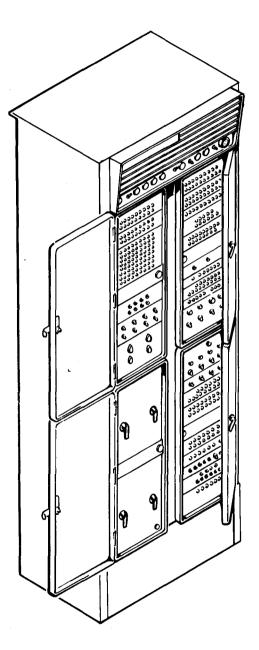

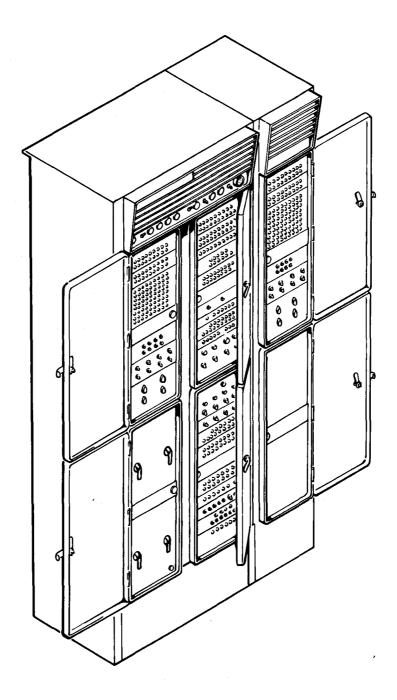

|      | 2-2.    |                                   | er Cabinet                                                                      | 2-1                          |

|      |         | 2-3.                              | Basic Cabinet                                                                   | 2-1                          |

|      |         | 2-4.                              | Expanded Cabinet.                                                               | 2-1                          |

|      |         |                                   | 2-5. Remote Control Console                                                     | 2-1                          |

|      |         |                                   | 2-6. Approximate Size and Weight                                                | 2-1                          |

|      |         |                                   | 2-7.         Cooling                                                            | 2-1                          |

|      |         |                                   | 2-8.Fuse Compliment2-9.Environmental Requirements                               | 2-1<br>2-1                   |

|      |         | 2-10.                             | Cabinet Drawers and Chassis                                                     | 2-1<br>2-3                   |

|      |         | -                                 |                                                                                 |                              |

i

#### TABLE OF CONTENTS (Cont)

#### Chapter

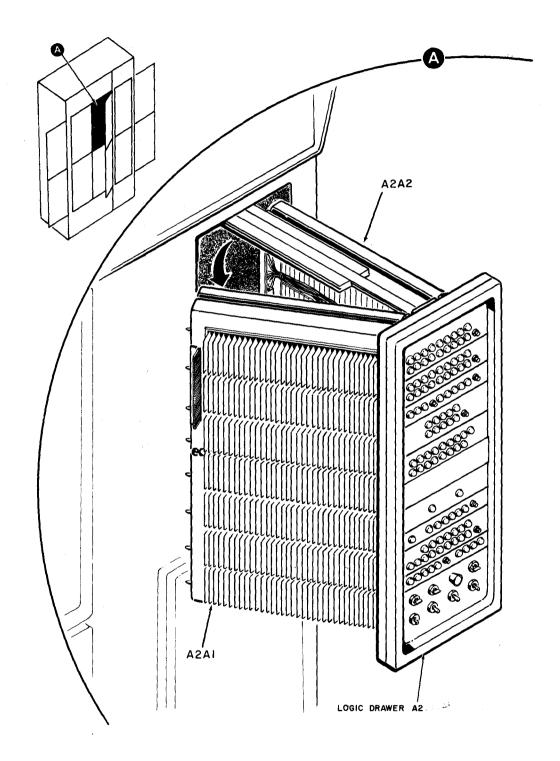

|       |          | 2-11.  | Logic Drawers                         | 2-3  |

|-------|----------|--------|---------------------------------------|------|

|       |          |        | 2-12. Mounting                        |      |

|       |          |        | 2-13. Drawer Locking                  |      |

|       |          |        | 2-14. Logic Chassis                   | 2-3  |

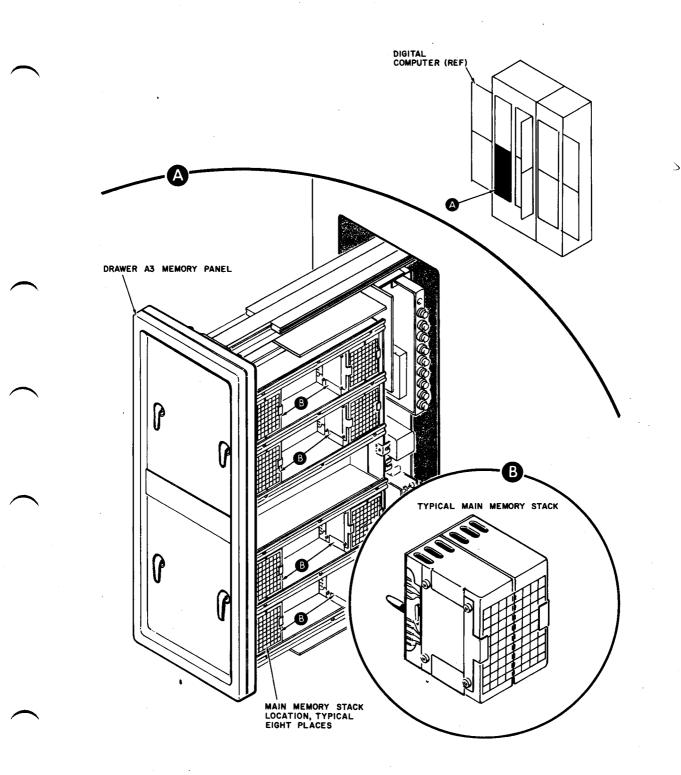

|       |          | 2-15.  | Memory Drawer                         |      |

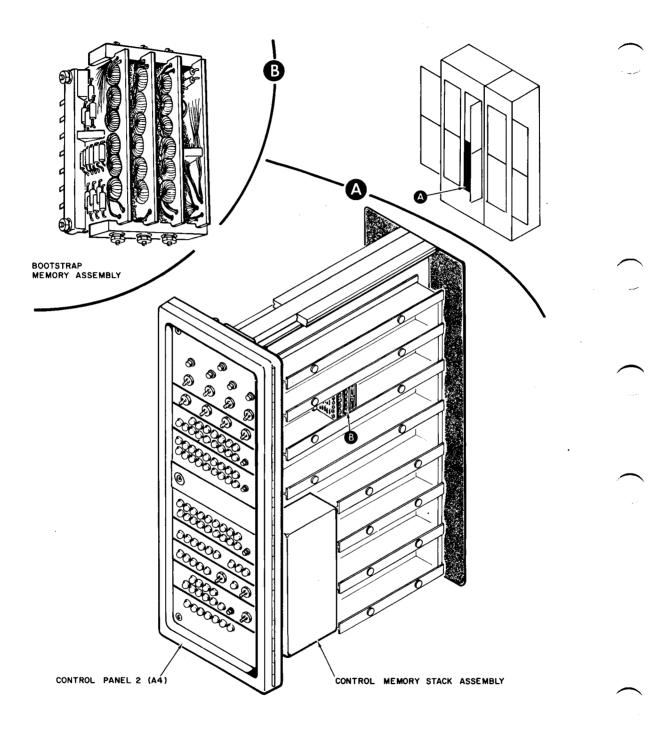

|       |          | 2-16.  | Control and Bootstrap Memories        | 2-3  |

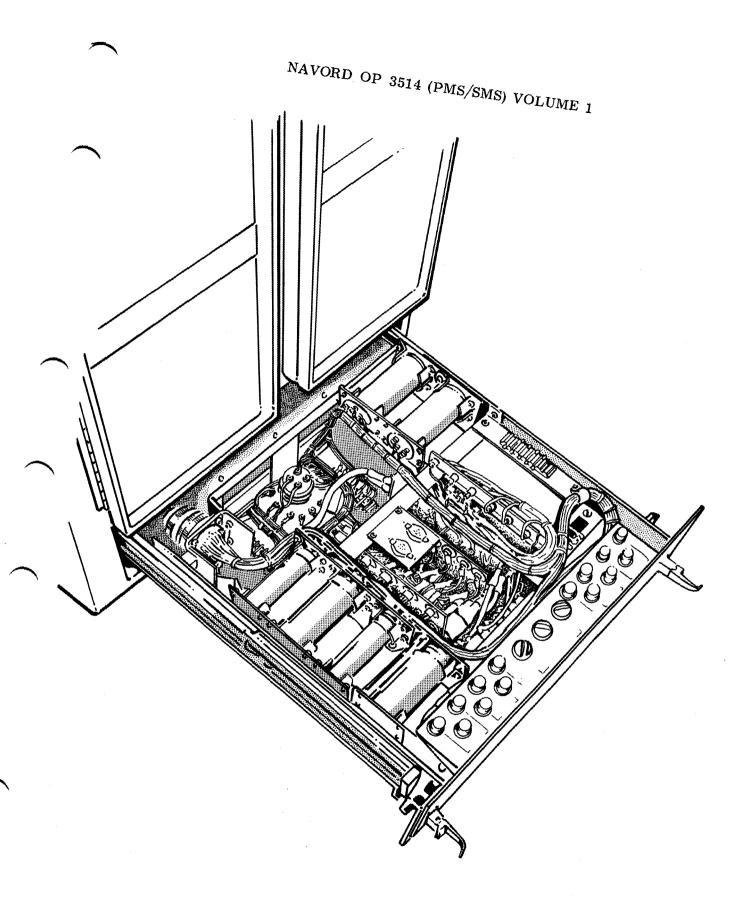

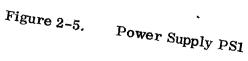

|       |          | 2-17.  | Power Supplies                        | 2-3  |

|       |          |        | 2-18. Main Memory Power Supply        | 2-3  |

|       |          | 2-19.  | Panels                                | 2-10 |

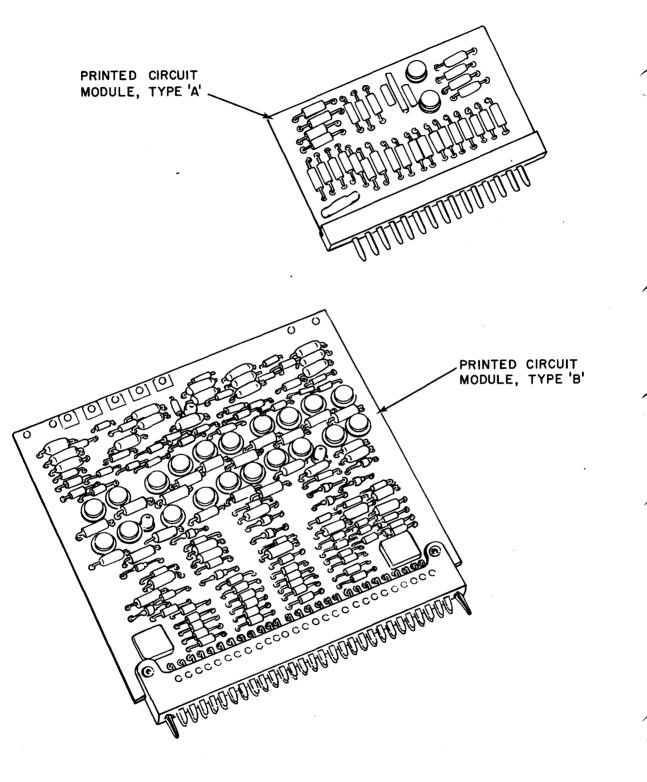

| 2-20. | Computer | Assemb | lies                                  | 2-10 |

|       | 2-22.    | Module | Compliment                            | 2-10 |

|       |          | 2-23.  | Physical Description of Basic Modules | 2-10 |

|       |          |        |                                       |      |

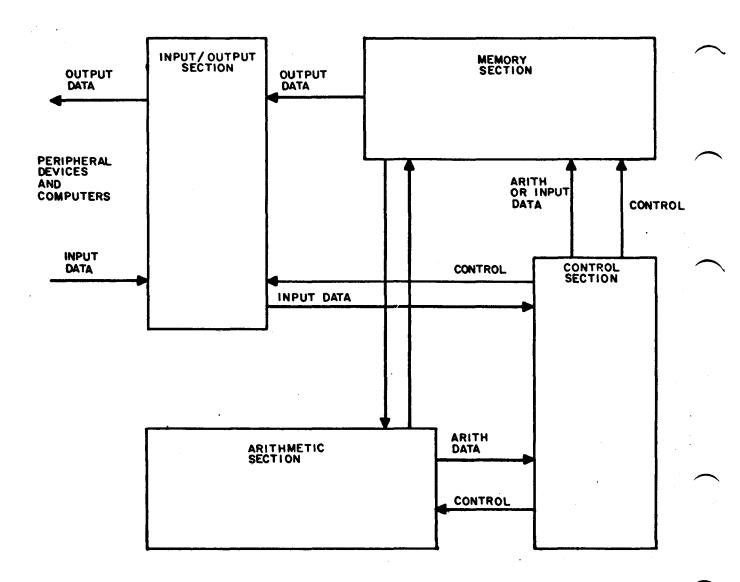

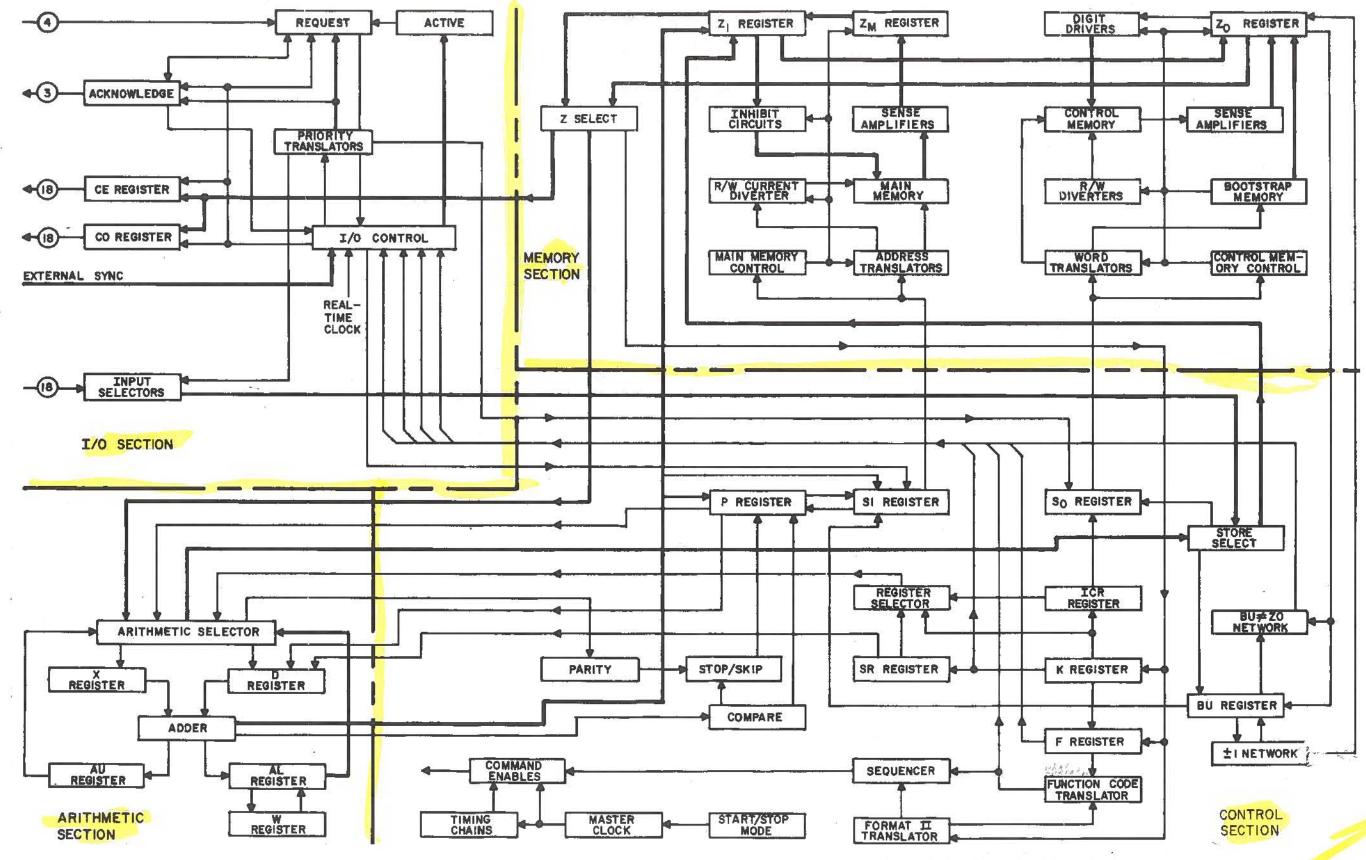

#### Section 2-2. General Functional Description

| 2-27. | General | Descriptio | on                              | 2-19   |

|-------|---------|------------|---------------------------------|--------|

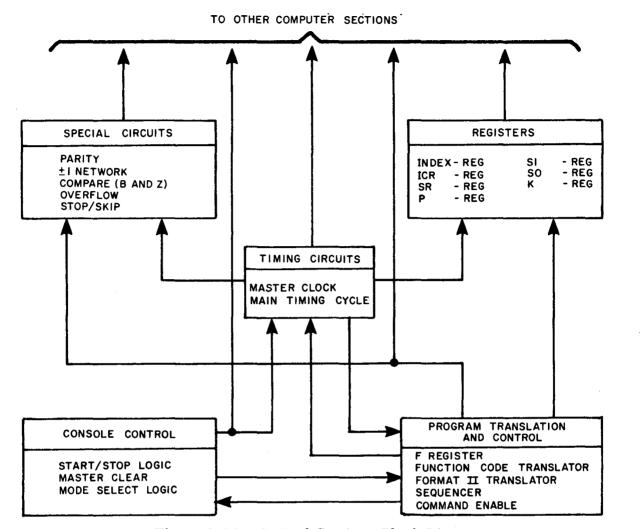

|       | 2-29.   | Control    | Section                         | 2-19   |

|       |         | 2-31.      | Console Control                 | 2-19   |

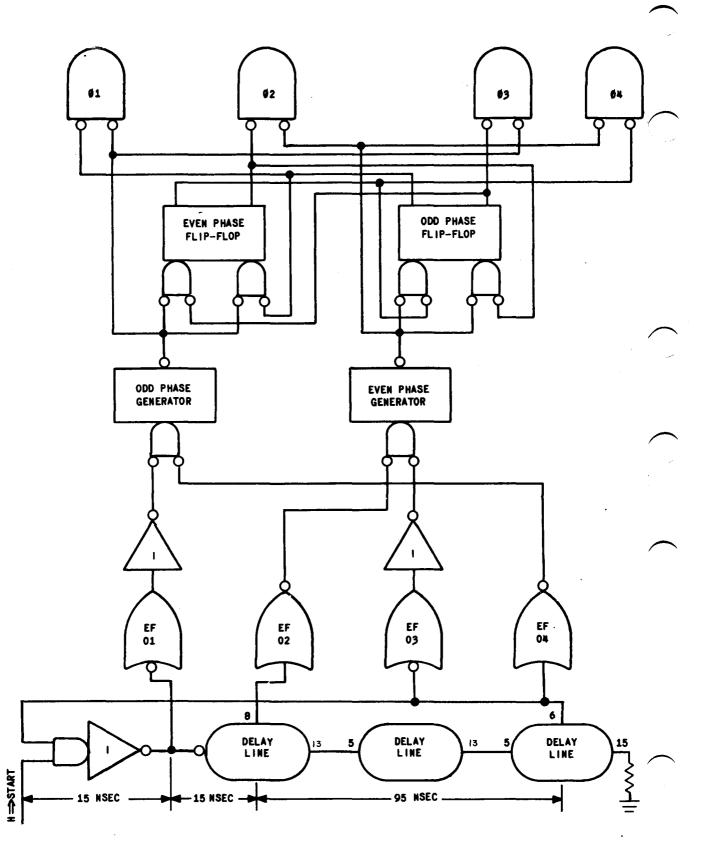

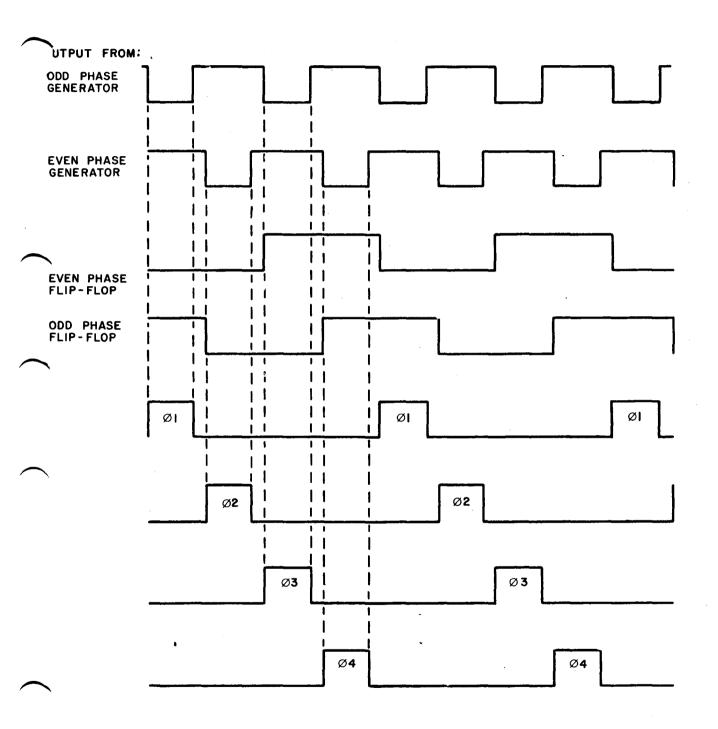

|       |         | 2-32.      | Timing Circuits                 | 2-23   |

|       |         | 2-34.      | Program Translation and Control | 2-23   |

|       |         | 2-35.      | Registers                       | 2-25   |

|       |         | 2-36.      | Special Circuits                | 2-27   |

|       | 2-37.   | Arithme    | tic Section                     | 2-27   |

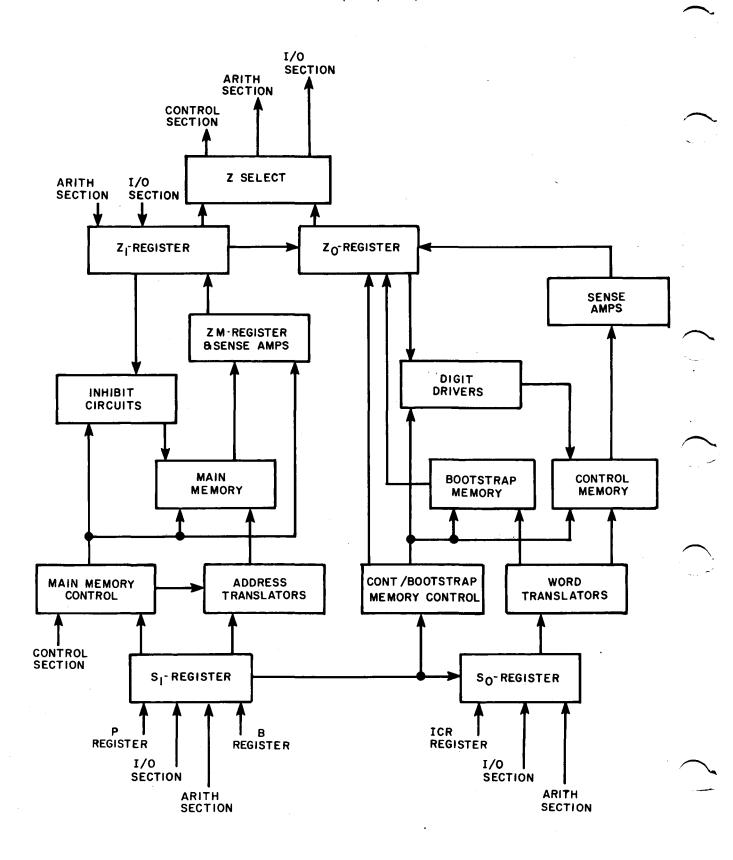

|       | 2-38.   | Memory     | <sup>7</sup> Section            | 2-28   |

|       |         | 2-39.      | Main Memory                     | 2-28   |

|       |         | 2-40.      | Control Memory                  | 2-29   |

|       |         | 2-41.      | Bootstrap Memory                | 2-29   |

|       | 2-42.   | Bootstra   | ap Mode                         | 2-29   |

|       | 2-43.   | I/O Sect   | ion                             | 2-32   |

|       |         | 2-44.      | Major I/O Operations            | 2-35   |

|       |         |            | 2-45. Data Transfers            | 2-35   |

|       |         |            | 2-46. I/O Communication Modes   | 2-35   |

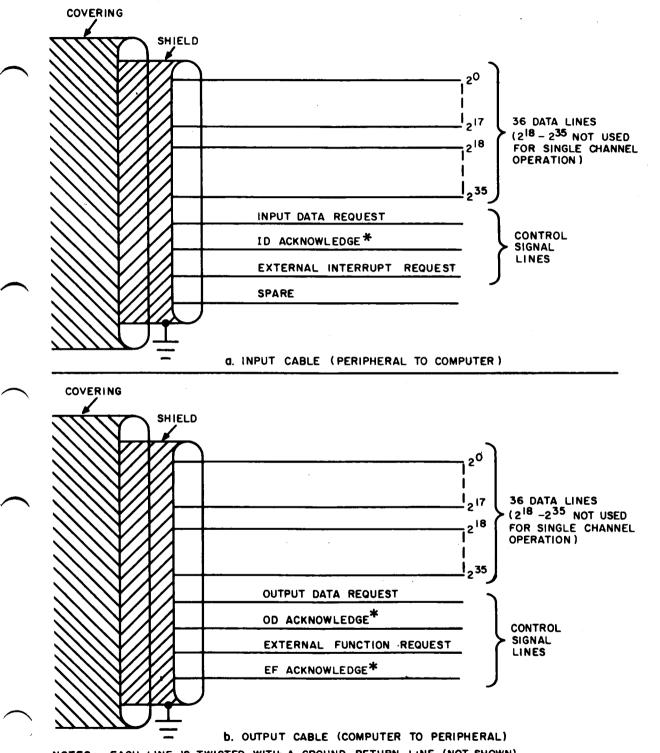

|       |         | 2-47.      | Input/Output Signals            | 2-36   |

|       |         |            | 2-48. Data Request Signals      | 2-36   |

|       |         |            | 2-49. Real Time Clock (RTC)     |        |

|       |         |            | Request Signals                 | 2-36   |

|       |         | 2-50.      | Interrupt Signals               | 2-36   |

|       |         | 2-51.      | Priorities                      | 2 - 37 |

#### TABLE OF CONTENTS (Cont)

| Chapter |            |                                                      | Page |

|---------|------------|------------------------------------------------------|------|

|         |            | 2-52. I/O Circuitry                                  | 2-37 |

| 2-53.   | Instruct   | ions Analysis                                        | 2-38 |

|         | 2-54.      | Instructions Repertoire                              | 2-38 |

|         |            | 2-55. Symbols Used                                   | 2-38 |

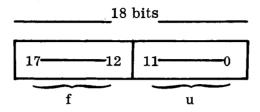

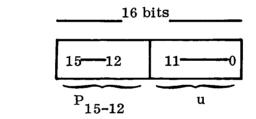

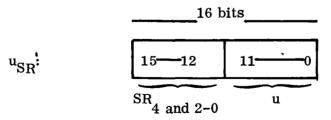

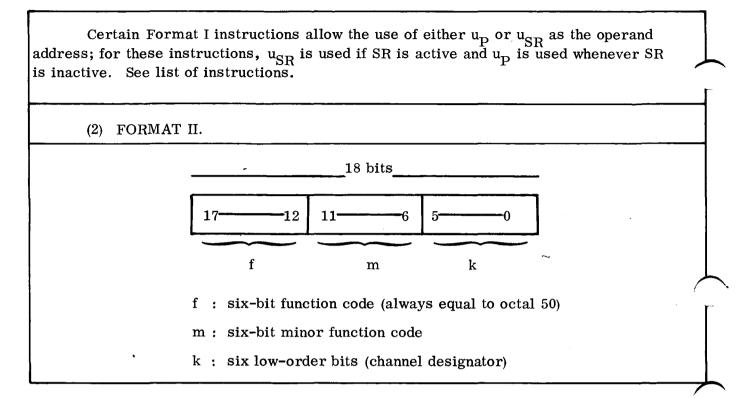

|         |            | 2-56. Instruction Word Formats                       | 2-38 |

|         |            | 2-57. List of Instructions                           | 2-38 |

| 2-58.   | Logic      |                                                      | 2-73 |

|         | 2-59.      | Internal Logic                                       | 2-73 |

|         | 2-60.      | External Logic                                       | 2-73 |

| 2-61.   | Symbolo    | ogy                                                  | 2-73 |

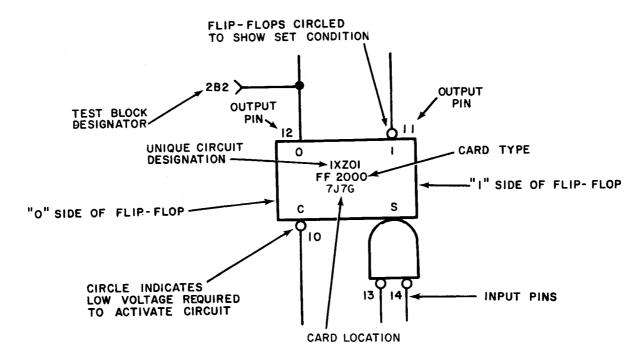

|         | 2-62.      | Circuit Symbology                                    | 2-73 |

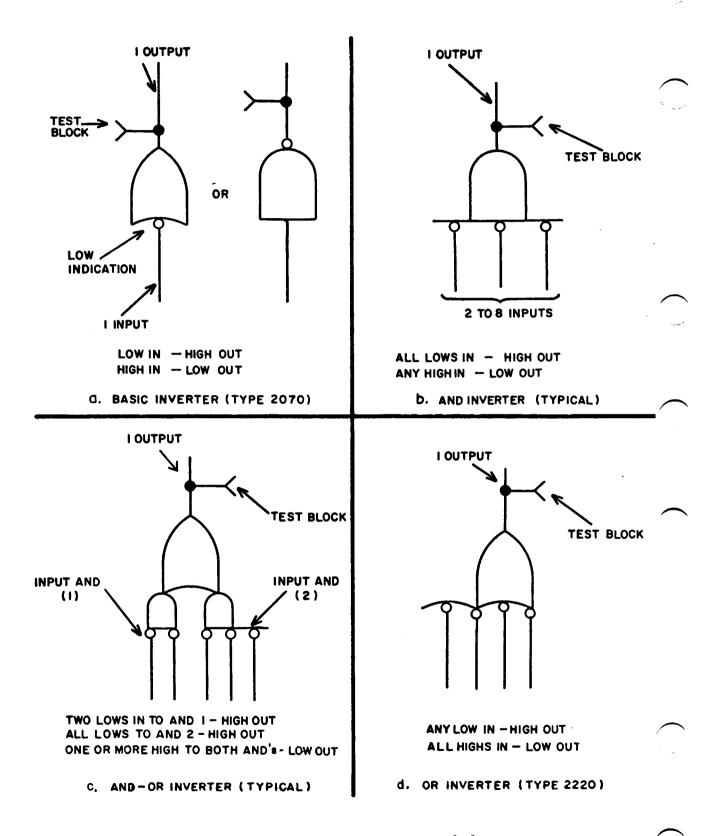

|         |            | 2-63. Inverter                                       | 2-73 |

|         |            | 2-64. AND Inverters                                  | 2-73 |

|         |            | 2-65. AND-OR Inverters                               | 2-73 |

|         |            | 2-66. OR Inverter                                    | 2-73 |

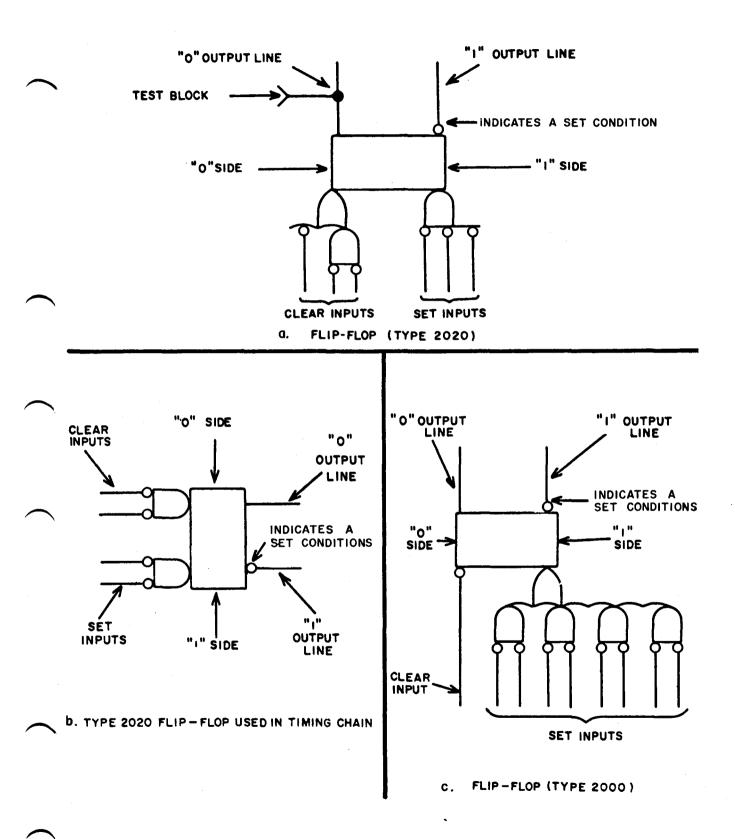

|         |            | 2-67. Flip-Flops                                     | 2-73 |

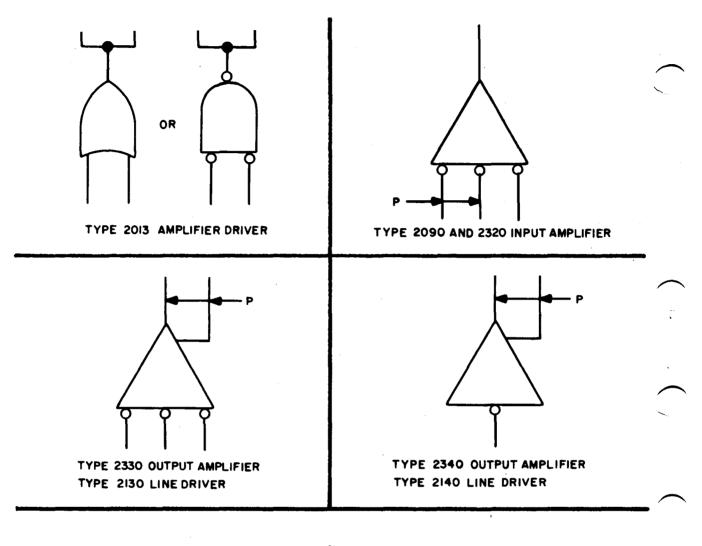

|         |            | 2-68. Amplifier Driver                               | 2-77 |

|         |            | 2-69. Input Amplifiers                               | 2-77 |

|         |            | 2-70. Output Amplifiers and Line Drivers             | 2-77 |

|         |            | 2-71. Indicator Driver                               | 2-77 |

|         | 2-72.      | Reference Designators                                | 2-77 |

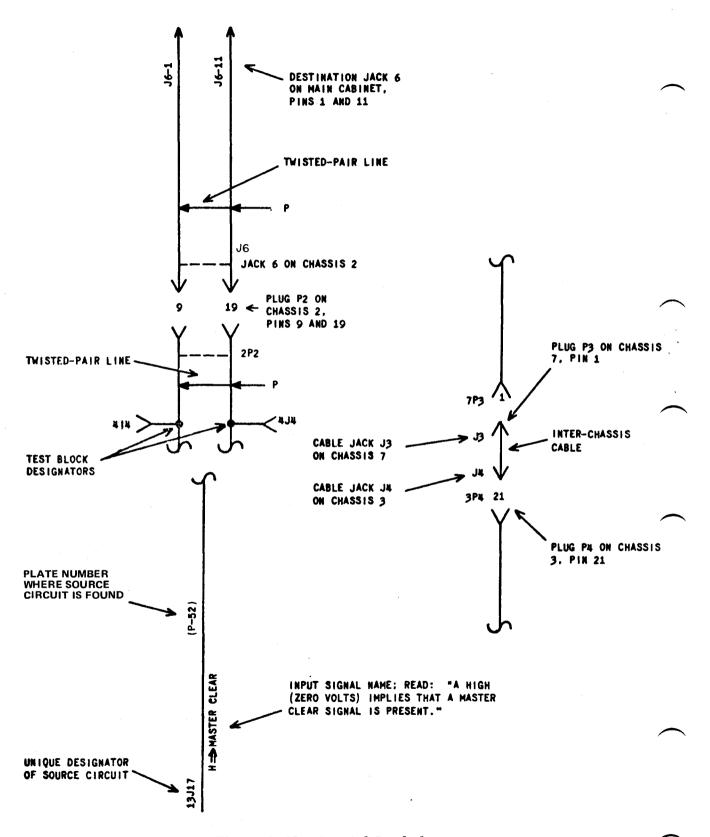

|         |            | 2-73. Unique Designators                             | 2-77 |

| ·       |            | 2-74. Alpha Assignments                              | 2-78 |

|         |            | 2-75. Numeric Assignments                            | 2-79 |

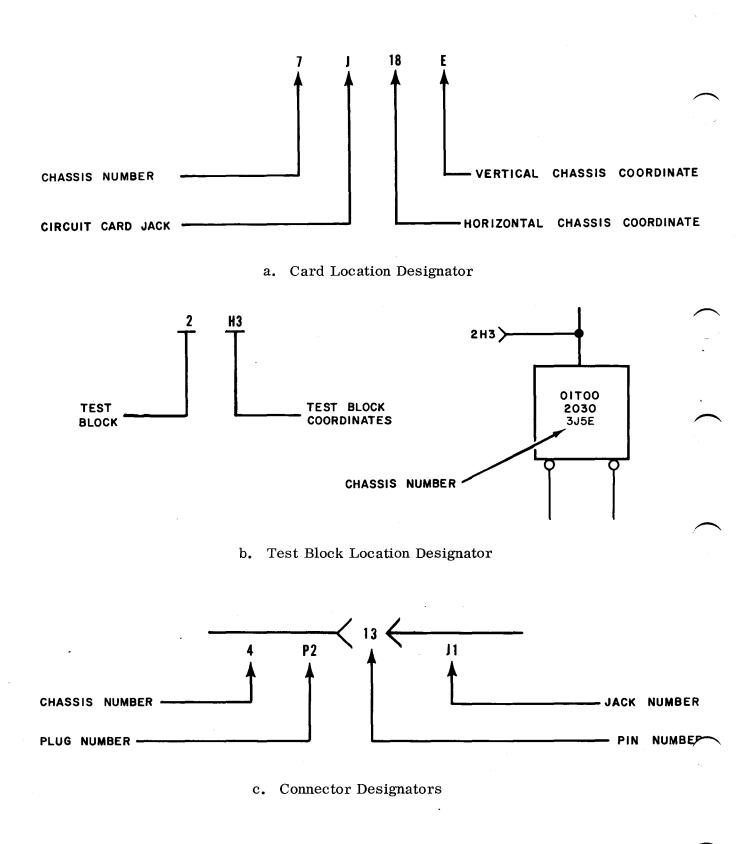

|         |            | 2-76. Card Location Designators                      | 2-79 |

|         |            | 2-77. Test Block Designators                         | 2-79 |

|         |            | 2-78. Connector Designators                          | 2-81 |

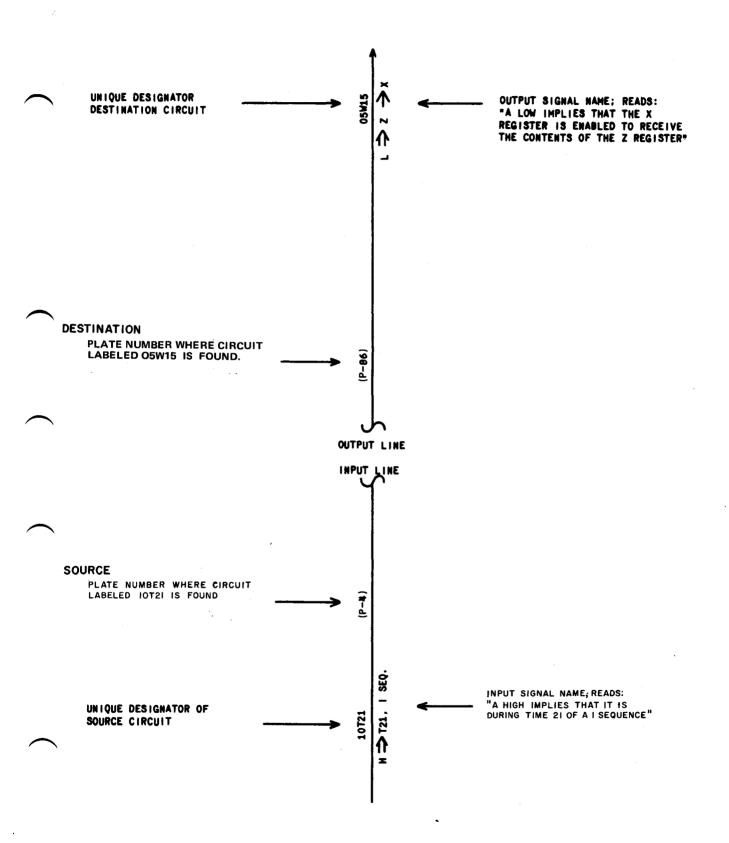

|         |            | 2-79. Special Symbology                              | 2-81 |

|         | 2-80.      | Duplicate Circuits                                   | 2-81 |

|         | 2-81.      | Chassis Maps                                         | 2-81 |

|         | Section 2- | 3. Detailed Functional Description (Control Section) |      |

| 2-82.   | Introduc   | etion                                                | 2-87 |

| 2-83.   | Control    | Section                                              | 2-87 |

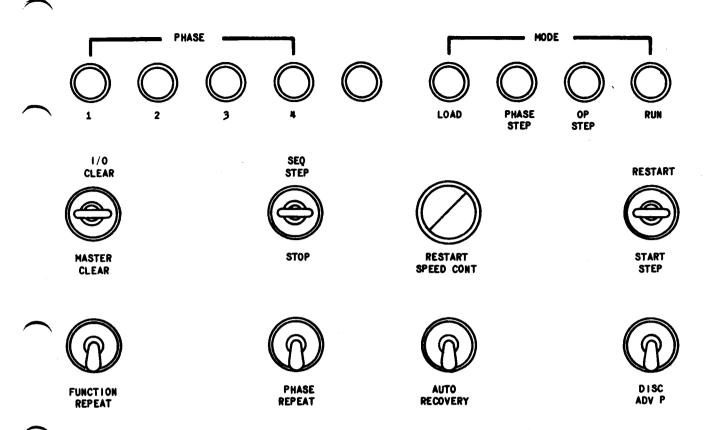

|         | 2-85.      | Console Control                                      | 2-87 |

|         |            | 2-86. Start/Stop Logic                               | 2-87 |

2-87. Start Circuit ..... 2-87

### TABLE OF CONTENTS (Cont)

### Chapter

|                 |         | 2-93. Stop Circuit 2-91                                                                  | L  |

|-----------------|---------|------------------------------------------------------------------------------------------|----|

|                 | 2-94.   | Master Clear 2-91                                                                        | 1  |

|                 |         | 2-99. I/O Clear 2-91                                                                     | 1  |

|                 | 2-100.  | Mode Select Logic 2-92                                                                   | 2  |

|                 | 2-101.  | Run Mode                                                                                 | 2  |

|                 | 2-103.  | Phase Step Mode 2-92                                                                     | 2  |

|                 | 2-108.  | OP Step Mode 2-94                                                                        | 4  |

|                 |         | 2-111. Load Mode 2-94                                                                    | 1  |

| 2 <b>-</b> 113. | Timing  | ; Circuits                                                                               | 1  |

|                 | 2-114.  | Master Clock 2-94                                                                        | 1  |

|                 |         | 2-118. Phase 1 ( $\emptyset$ 1) 2-98                                                     | 5  |

|                 |         | 2-119. Phase 2 ( $\emptyset$ 2) 2-98                                                     | 5  |

|                 |         | 2-120. Phase 3 ( $\emptyset$ 3) 2-95                                                     | 5  |

|                 |         | 2-121. Phase 4 ( $\emptyset$ 4) 2-98                                                     | 5  |

|                 | 2-123.  | Clock Distribution 2-96                                                                  | 3  |

|                 | 2-125.  | Timing Chains 2-96                                                                       | 3  |

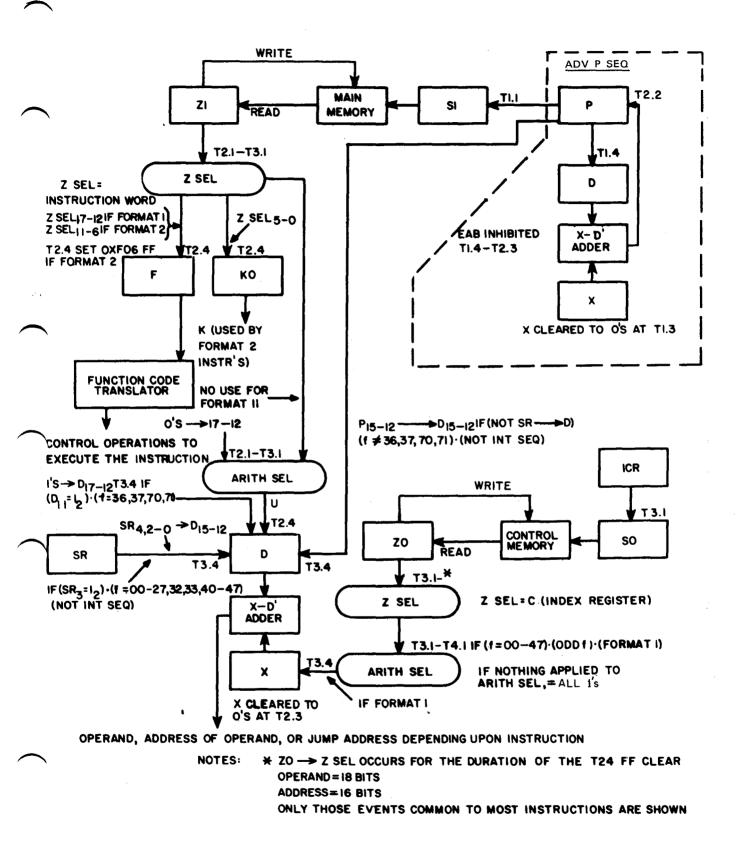

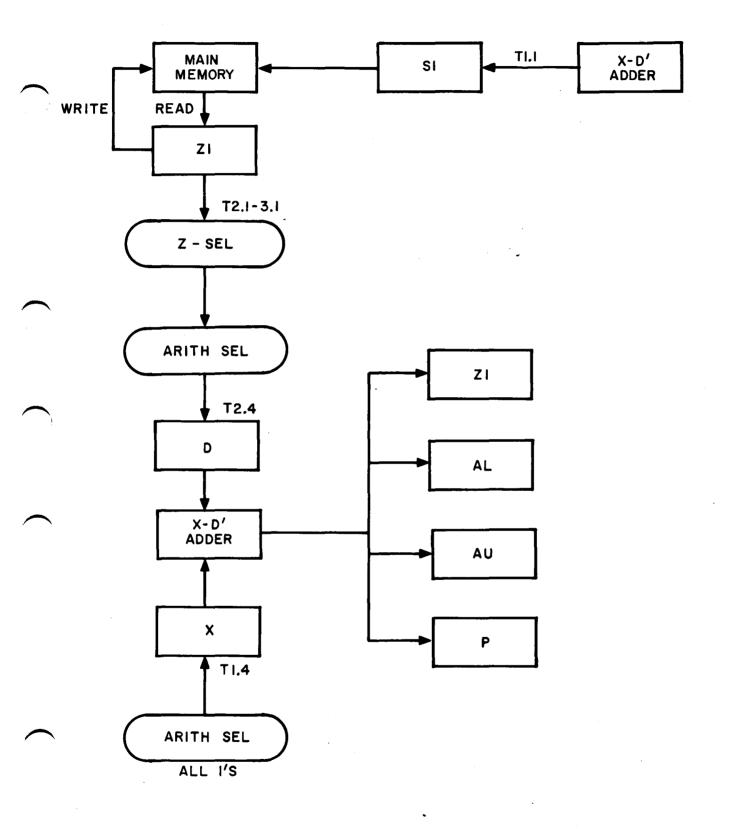

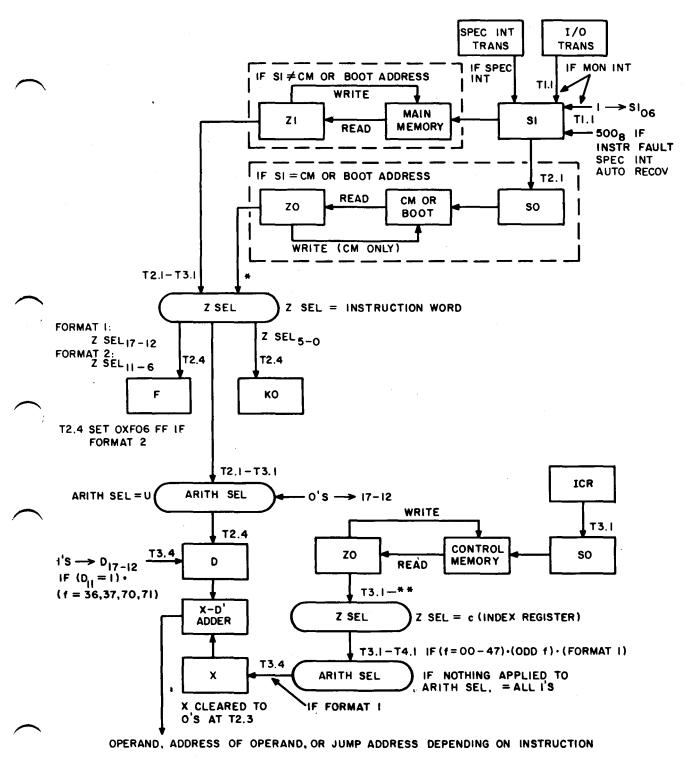

| 2-131.          | Progra  | m Translation and Control                                                                | )0 |

|                 | 2-132.  | F-Register                                                                               | )0 |

|                 | 2-136.  | Function Code Subtranslators                                                             | )2 |

|                 |         | 2-137. Subtranslator 1                                                                   | )2 |

|                 |         | 2-138. Subtranslator 2 2-10                                                              | )2 |

|                 |         | 2-139. Subtranslator 3 2-10                                                              | )2 |

|                 | 2-140.  | Function Translators 2-10                                                                | )3 |

|                 | 2-141.  | Sequencer                                                                                | )3 |

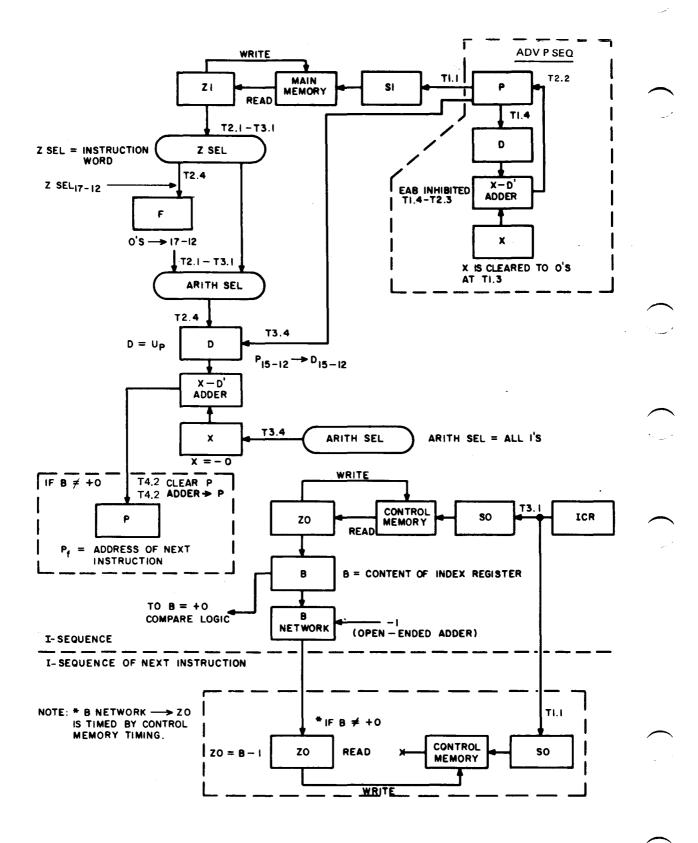

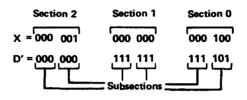

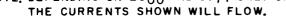

|                 |         | 2-142. I-Sequence 2-10                                                                   | )3 |

|                 |         | 2-143. R-Sequence 2-10                                                                   | )3 |

|                 |         | 2-144. W-Sequence 2-10                                                                   | )3 |

|                 |         | 2-145. B-Sequence 2-10                                                                   | )3 |

|                 |         | 2-146. I/O Sequence                                                                      |    |

|                 |         | 2-147. Interrupt Sequence 2-1                                                            |    |

|                 |         | 2-148, Upper-Rank Sequence Designator 2-10<br>2-153, Lower-Rank Sequence Designator 2-10 |    |

| 2-158.          | Major S | Sequence Analysis                                                                        |    |

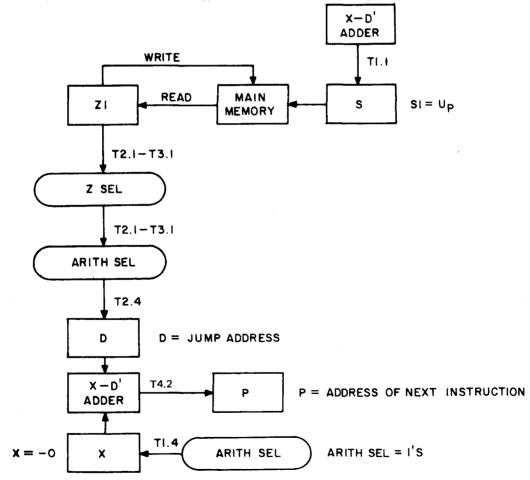

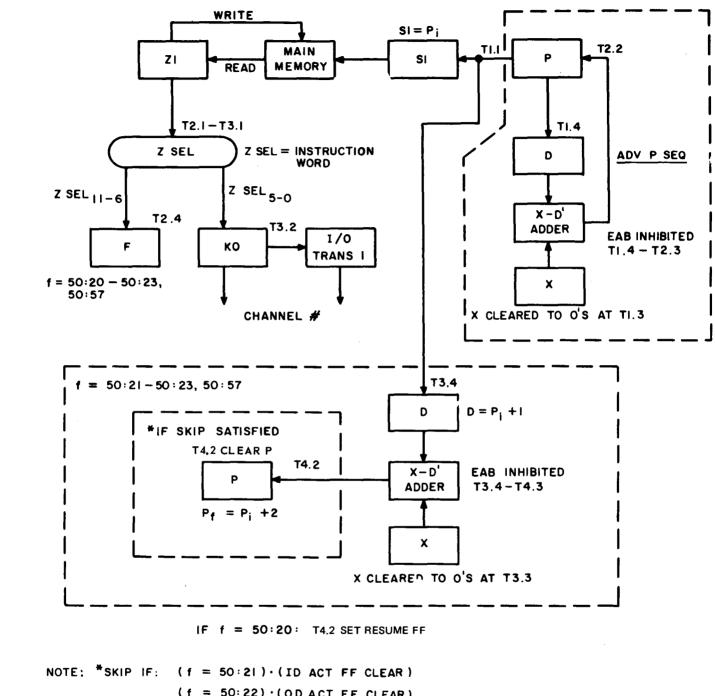

|                 | 2-159.  | I (Initiate) Sequence 2-10                                                               | 05 |

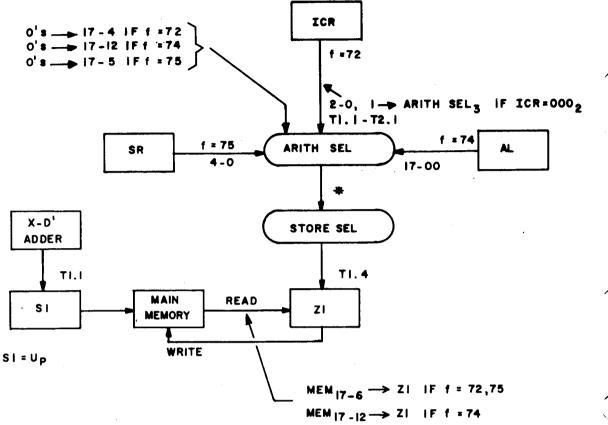

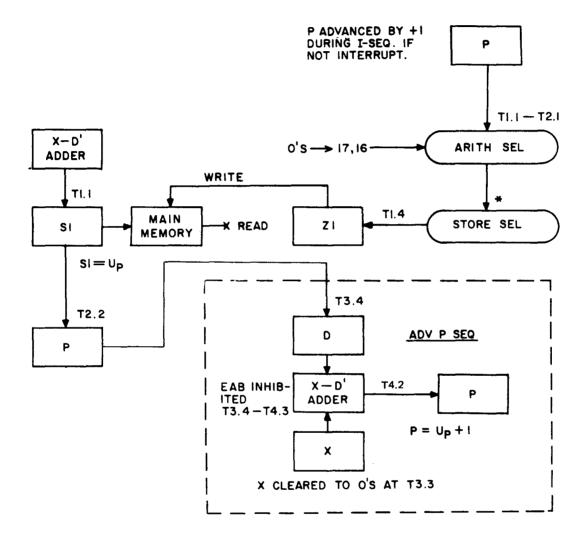

|                 | 2-164.  | Advance-P Subsequence 2-10                                                               | 06 |

|                 | 2-165.  | R (Read) Sequence 2-10                                                                   | )6 |

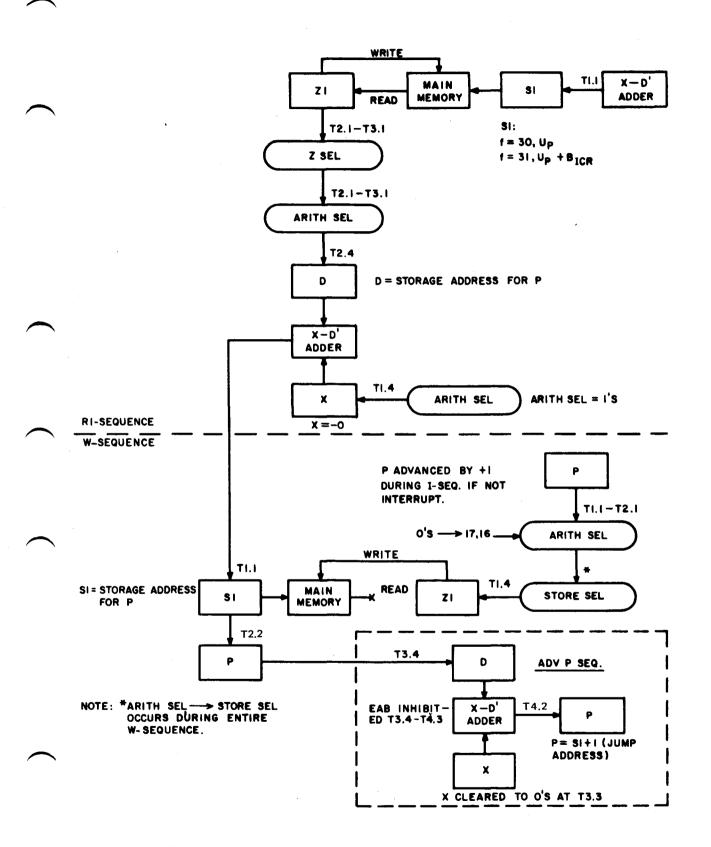

|                 | 2-167.  | W (Write) Sequence 2-12                                                                  | 22 |

| 2-169.          | Comma   | and Instructions 2-12                                                                    | 25 |

|                 | 2-170.  | Execution of Stop Instruction (f= $50:56$ ) 2-12                                         | 25 |

### TABLE OF CONTENTS (Cont)

Chapter

| 2-172. | Execution of ENTALK, ADDALK Instructions                            |         |

|--------|---------------------------------------------------------------------|---------|

|        | (f= 70, 71)                                                         | 2-125   |

| 2-174. | Execution of ENTICR, ENTSR Instruction                              |         |

|        | (f= 50:72, 50:73)                                                   | 2-128   |

|        | 2-175. I-Sequence Data Flow for $f = 50.72$ ,                       |         |

|        | 50:73                                                               | 2-128   |

| 2-176. | Execution of ENTBK, ENTBKB Instructions                             |         |

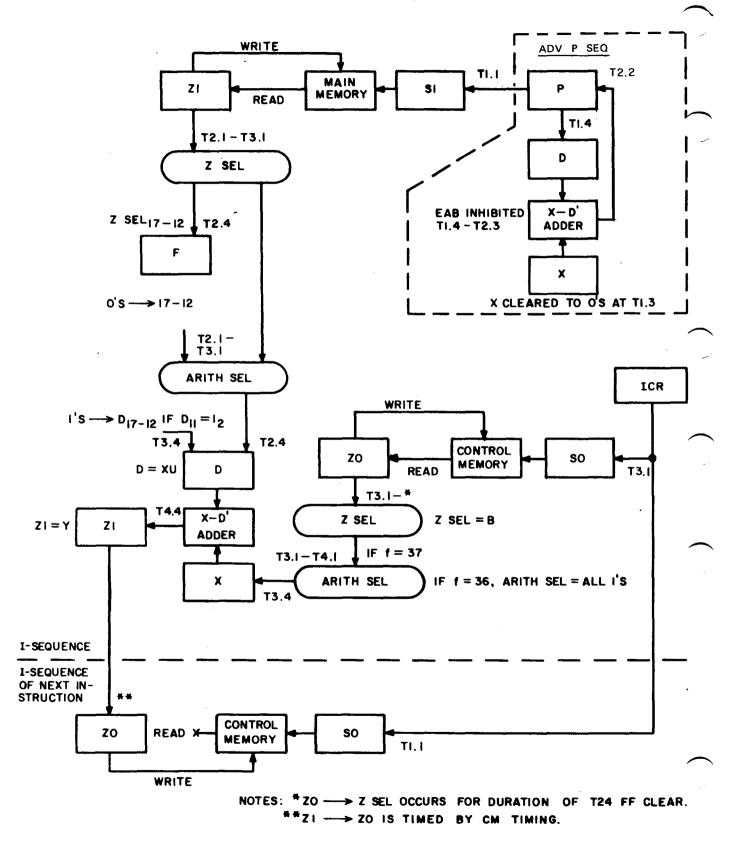

|        | (f=36, 37)                                                          | 2-128   |

|        | 2-177. I and Next I-Sequence Data Flow                              |         |

|        | for $f = 36, 37$                                                    | 2-128   |

| 2-178. | Execution of ENTB, ENTBB Instructions                               |         |

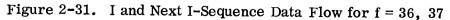

|        | (f= 32, 33)                                                         | 2-137   |

|        | 2-179. R1 and Next I-Sequence Data Flow                             |         |

|        | for $f=32, 33$                                                      | 2-137   |

| 2-180. | Execution of ENTAU, ENTAUB, ENTAL,                                  |         |

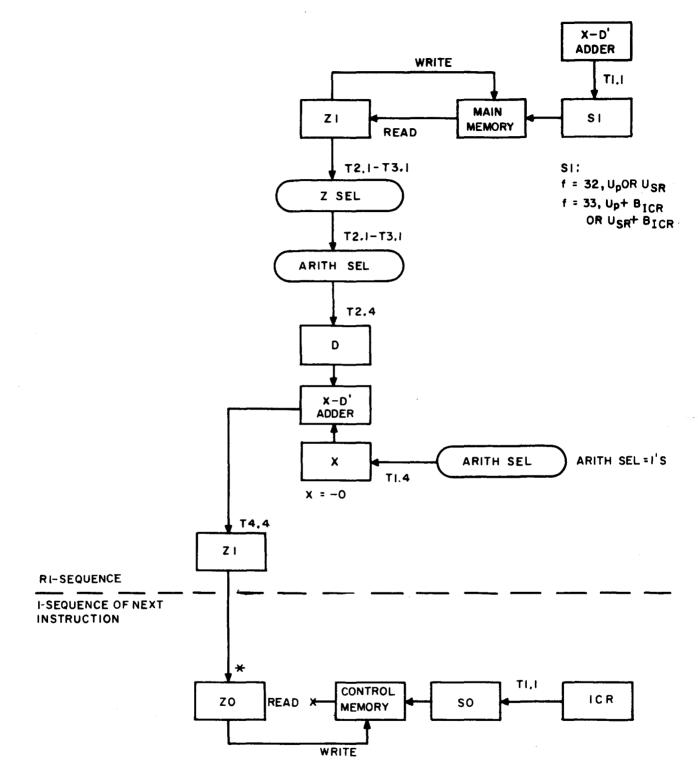

|        | ENTALB Instructions (f= 10, 11, 12, 13)                             | 2-137   |

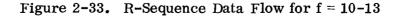

|        | 2-181. ENTAU (f= $10$ )                                             | 2-137   |

|        | 2-182. ENTAUB (f= 11)                                               | 2-137   |

|        | 2-183. ENTAL $(f=12)$                                               | 2-137   |

|        | 2-184. ENTALB (f= 13) $\dots$                                       | 2 - 137 |

|        | 2-185. R1-Sequence Data Flow for                                    |         |

|        | (f= 10-13)                                                          | 2 - 137 |

| 2-186. | Execution of CL, CLB, STRB, STRBB,                                  |         |

|        | STRAL, STRALB, STRAU, STRAUB                                        |         |

|        | Instructions (f= 40, 41, 42, 43, 44, 45,                            |         |

|        | 46, 47)                                                             | 2-138   |

|        | 2-187. CL (f= 40) $\ldots$                                          | 2-138   |

| ·      | 2-188. CLB ( $f=41$ )                                               | 2-138   |

|        | 2-189. STRB (f= 42)                                                 | 2-138   |

|        | 2-190. STRBB (f= 43)                                                | 2-138   |

|        | 2-191. STRAL (f= 44)                                                | 2-138   |

|        | 2-192. STRALB (f= 45)                                               | 2-138   |

|        | 2-193. STRAU (f= 46)                                                | 2-138   |

|        | 2-194. STRAUB ( $f=47$ )                                            | 2-138   |

|        | 2-195. W-Sequence Data Flow for                                     |         |

|        | $f = 40 - 47 \dots \dots \dots \dots \dots \dots \dots \dots \dots$ | 2-138   |

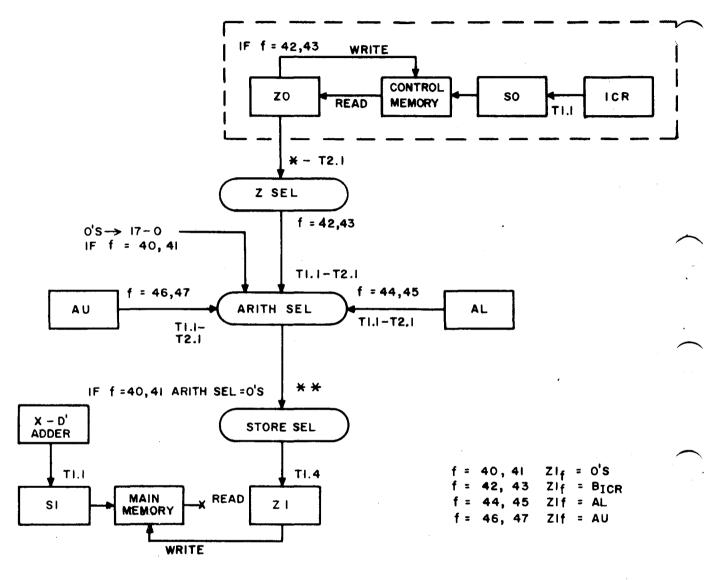

| 2-196. | Execution of STRICR, STRADR, STRSR                                  |         |

|        | Instructions (f= 72, 74, 75) $\ldots$                               | 2-145   |

|        |                                                                     |         |

v

Chapter

|        | 2-197.    | STRICR (f= 72) $\ldots$                         | 2-145   |

|--------|-----------|-------------------------------------------------|---------|

|        | 2-198.    | STRADR (f= 74) $\ldots$                         | 2-145   |

|        | 2-199.    | STRSR (f= 75) $\ldots$                          | 2 - 145 |

|        | 2-200.    | W-Sequence Data Flow for                        |         |

|        |           | f=72, 74, 75                                    | 2-145   |

| 2-201. | Execution | on of Jump (JP, JPB, JPAUZ,                     |         |

|        | JPALZ,    | JPAUNZ, JPALNZ, JPAUP,                          |         |

|        | JPALP,    | JPAUNG, JPALNG, AND BJP)                        |         |

|        | Instruct  | ions (f= 34, 35, 60-67, and 73)                 | 2-145   |

|        | 2-202.    | JP (f= 34)                                      | 2-145   |

|        | 2-203.    | JPB (f= 35)                                     | 2-153   |

|        | 2-204.    | JPAUZ (f= 60)                                   | 2-153   |

|        | 2-205.    | JPALZ (f= 61)                                   | 2-153   |

|        | 2-206.    | JPAUNZ (f= $62$ )                               | 2-153   |

|        | 2-207.    | JPALNZ ( $f= 63$ )                              | 2-153   |

|        | 2-208.    | JPAUP (f= 64)                                   | 2 - 153 |

|        | 2-209.    | JPALP (f= 65)                                   | 2-153   |

|        | 2-210.    | JPAUNG ( $f=66$ )                               | 2-153   |

|        | 2-211.    | JPALNG (f= 67)                                  | 2-153   |

|        | 2-212.    | BJP (f= 73)                                     | 2-153   |

|        | 2-213.    | I-Sequence Data Flow for                        |         |

|        |           | f= 34, 35, and 60 through 67,                   |         |

|        |           | and I and Next I-Sequence Data                  |         |

|        |           | Flow for $f = 73 \dots \dots \dots \dots \dots$ | 2-153   |

| 2-214. | Execution | on of Jump (IJPEI, IJP, RJP, IRJP,              |         |

|        | and IRJ   | PB) Instructions for (f= $54$ , $55$ ,          |         |

|        | 76, 30,   | and 31)                                         | 2 - 161 |

|        | 2-215.    | IJPEI (f= 54)                                   | 2-161   |

|        | 2-216.    | IJP (f= 55)                                     | 2-161   |

|        | 2-217.    | RJP (f= 76)                                     | 2 - 161 |

|        | 2-218.    | IRJP (f= 30)                                    | 2 - 161 |

|        | 2-219.    | IRJPB (f= 31)                                   | 2-161   |

|        | 2-220.    | R1-Sequence Data Flow for f= 54,                |         |

|        |           | 55, W-Sequence Data Flow for                    |         |

|        |           | f=76, and R1 and W-Sequence                     |         |

|        |           | Data Flow for $f=30, 31$                        | 2 - 161 |

| 2-221. | Execution | on of Skip (SKP, SKPNBO,                        |         |

|        | SKPOV,    | and SKPNOV) Instructions ( $f=$                 |         |

|        | 50:50, E  | $50:51, 50:52, and 50:53) \dots$                | 2-161   |

|        |           | · .                                             |         |

Chapter

÷

Page

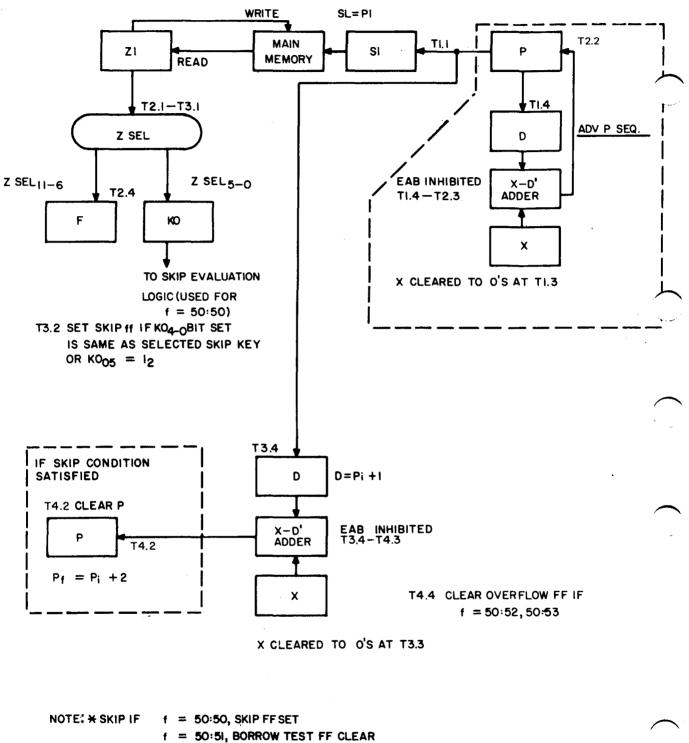

|        | 2-222. SKP (f= 50:50)                       | 2 - 167 |

|--------|---------------------------------------------|---------|

|        | 2-223. SKPNBO (f= 50:51)                    | 2 - 167 |

|        | 2-224. SKPOV ( $f=50:52$ )                  | 2 - 167 |

|        | 2-225. SKPNOV (f= 50:53)                    | 2 - 167 |

|        | 2-226. I-Sequence Data Flow for f= 50:50    |         |

|        | through 50:53                               | 2-167   |

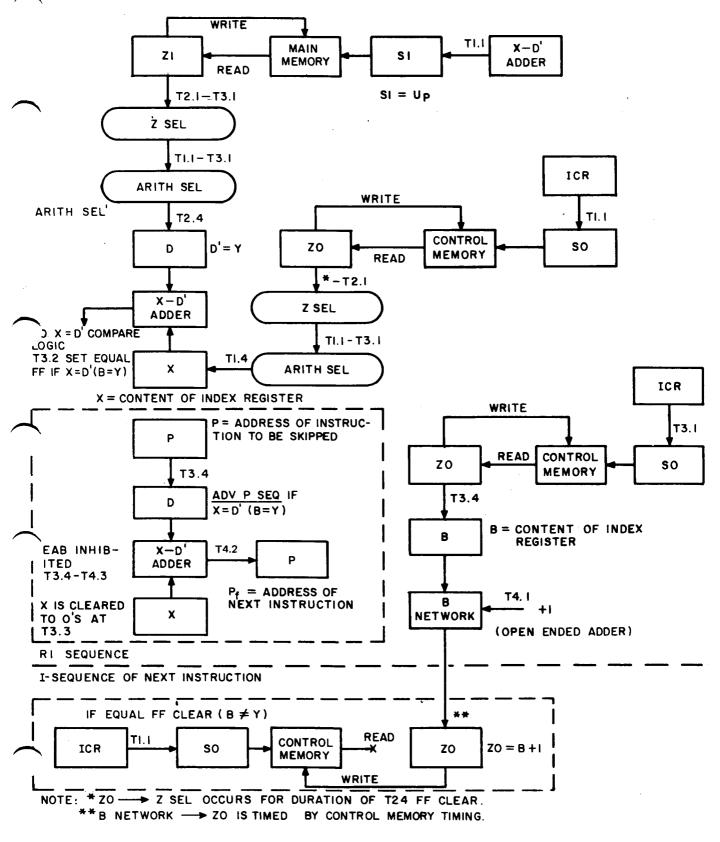

| 2-227. | Execution of Skip (BSK) Instruction (f= 56) | 2-167   |

|        | 2-228. R1 and Next I-Sequence Data          |         |

|        | Flow for $f = 56$                           | 2-167   |

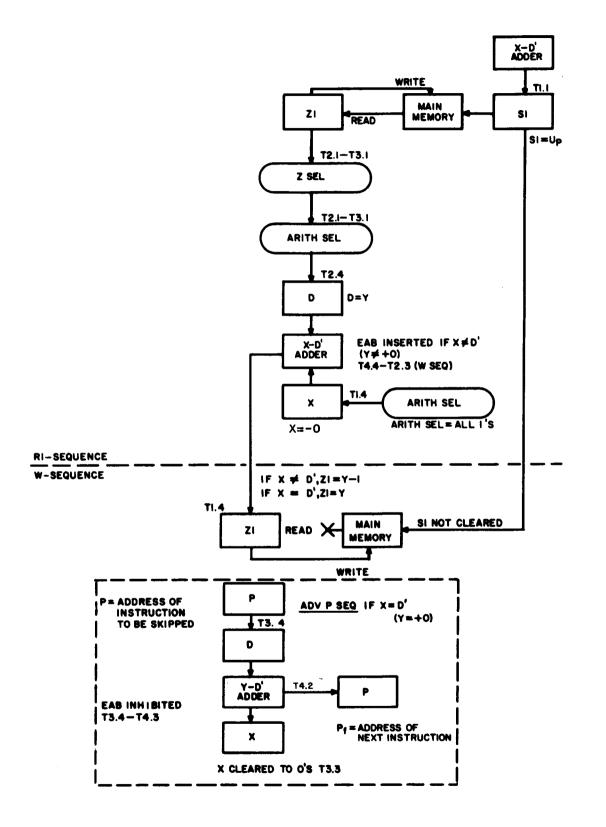

| 2-229. | Execution of SKP (ISK) Instruction (f= 57)  | 2-175   |

|        | 2-230. R1 and W-Sequence Data Flow          |         |

|        | for $f = 57$                                | 2 - 175 |

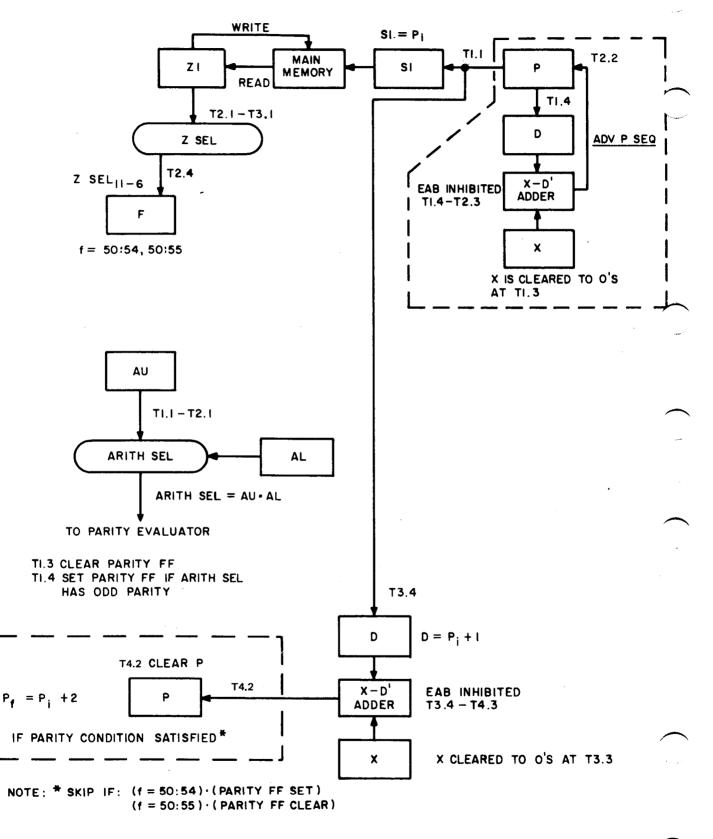

| 2-231. | Execution of Skip (SKPODD, SKPEVN)          |         |

|        | Instructions ( $f = 50:54, 50:55$ )         | 2-175   |

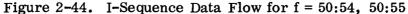

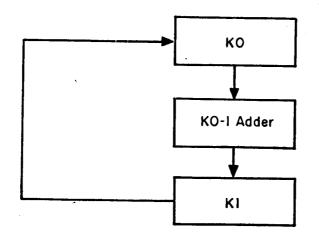

|        | 2-232. I-Sequence Data Flow for             |         |

|        | f = 50:54, 50:55                            | 2-175   |

|        |                                             | •       |

#### Section 2-3. Detailed Functional Description (Arithmetic Section)

| 2-233. | Arithme | tic Sectior | 1                         | 2-183 |

|--------|---------|-------------|---------------------------|-------|

|        | 2-234.  | Adders      |                           | 2-183 |

|        |         | 2-235.      | X-D' Adder                | 2-183 |

|        |         |             | 2-236. Half-Subtractor    | 2-183 |

|        |         |             | 2-237. Borrow Generator   | 2-183 |

|        |         |             | 2-240. Full Adder         | 2-184 |

|        |         | 2-244.      | B Adder                   | 2-185 |

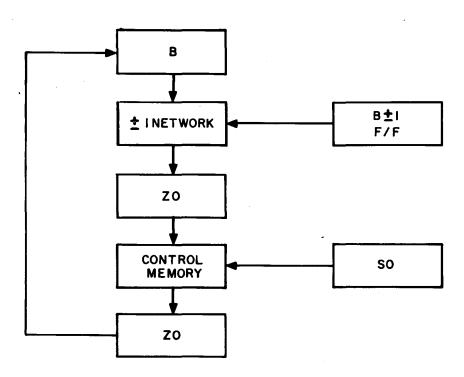

|        |         | 2-248.      | KO-1 Adder                | 2-187 |

|        | 2-251.  | Logic N     | letworks                  | 2-189 |

|        |         | 2-252.      | AU, AL Positive, Negative | 2-189 |

|        |         | 2-253.      | AU, AL Zero               | 2-189 |

|        |         | 2-254.      | Borrow                    | 2-189 |

|        |         | 2-255.      | Overflow                  | 2-189 |

|        |         | 2-257.      | Parity                    | 2-191 |

|        |         |             | 2-258. Group Parity       | 2-191 |

|        |         |             | 2-259. Section Parity     | 2-193 |

|        |         |             | 2-260. Total Parity       | 2-193 |

|        |         | 2-261.      | K-Zero                    | 2-195 |

|        |         | 2-262.      | B-Zero                    | 2-195 |

#### Chapter

#### Page

| 2-263. | Arithme | etic and Logical Instructions                       | 2-196   |

|--------|---------|-----------------------------------------------------|---------|

|        | 2-264.  | Add-Subtract Instructions                           | 2-196   |

|        |         | <b>2–265.</b> ADDAL ( $f= 14$ )                     | 2-196   |

|        |         | 2-266. ADDALB (f= 15)                               | 2-196   |

|        |         | 2-267. SUBAL (f= 16)                                | 2-196   |

|        |         | 2-268. SUBALB (f= 17)                               | 2 - 196 |

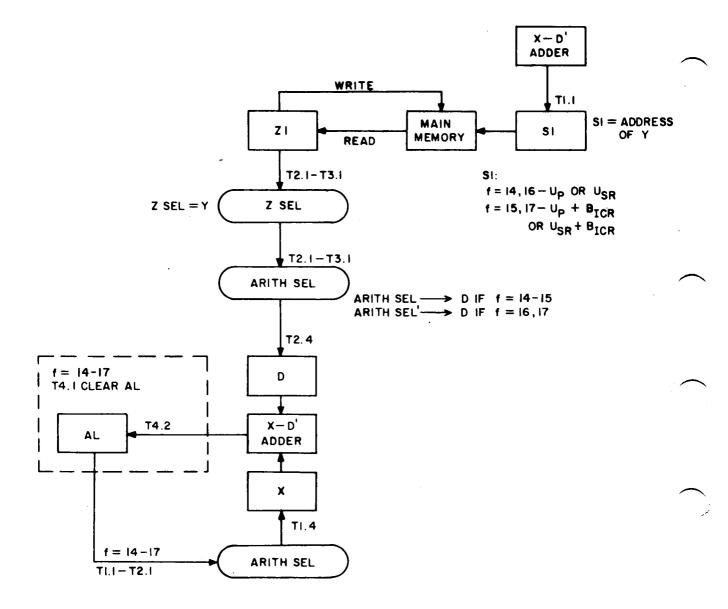

|        | 2-269.  | R1-Sequence Data Flow for $f = 14$ through 17       | 2-196   |

|        | 2-270.  | ADDA (f= 20)                                        | 2-196   |

|        | 2-274.  | ADDAB (f= 21)                                       | 2-200   |

|        | 2-275.  | SUBA (f= 22)                                        | 2-200   |

|        | 2-276.  | SUBAB (f= 23)                                       | 2-200   |

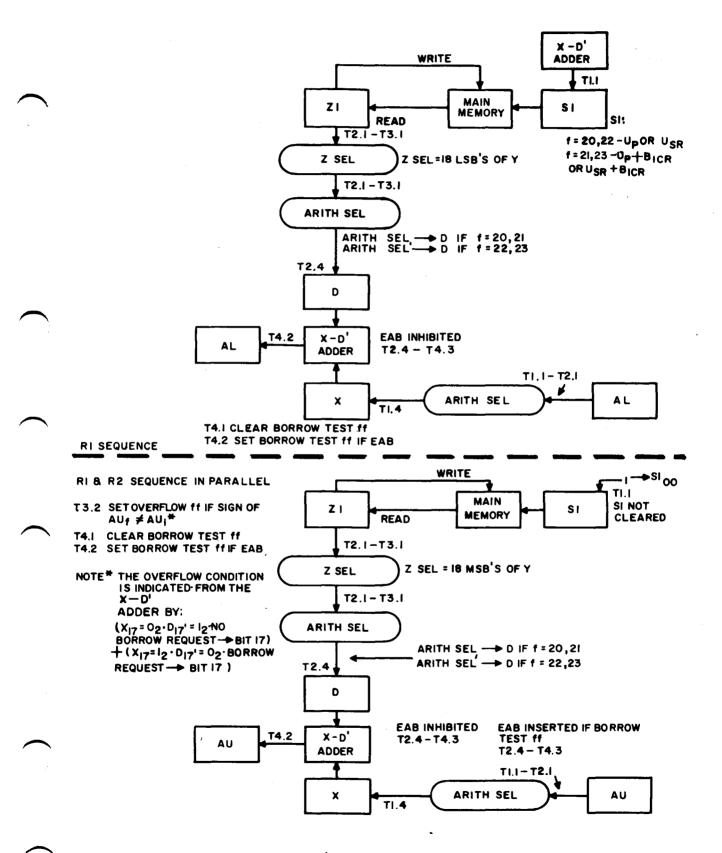

|        | 2-277.  | Rl and Rl/R2 - Sequence Data Flow for               |         |

|        |         | f= 20 through 23                                    | 2-200   |

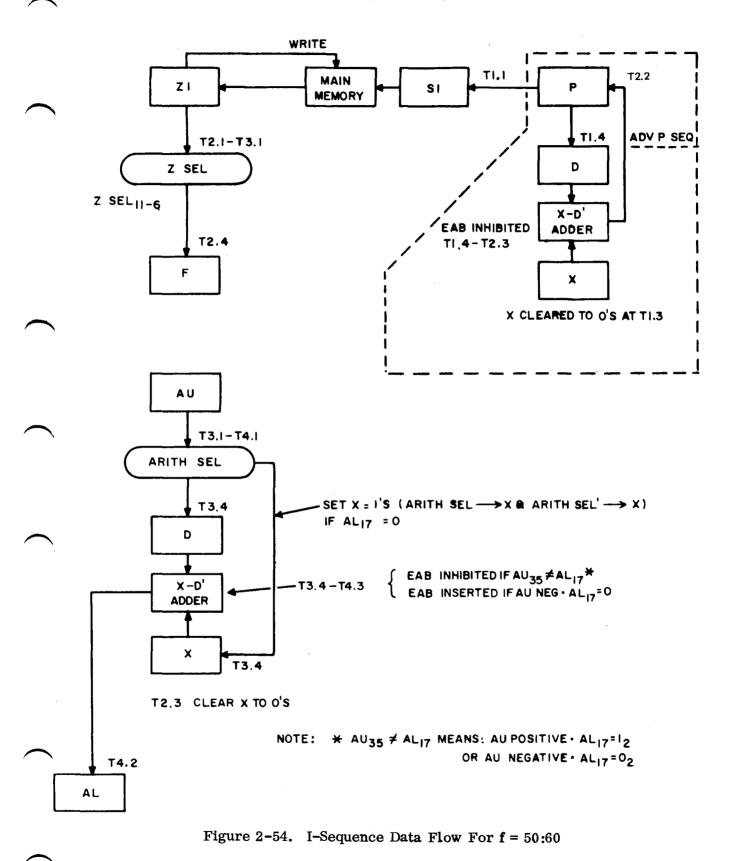

|        | 2-279.  | RND (f= 50:60)                                      | 2-204   |

|        | 2-280.  | I-Sequence Data Flow for f= 50:60                   | 2-204   |

|        | 2-281.  | Logical Instructions                                | 2-209   |

|        | 2-282.  | CMAL (f= 02)                                        | 2-209   |

|        | 2-283.  | CMALB (f= 03)                                       | 2-209   |

|        | 2-284.  | CMSK (f= 06)                                        | 2-209   |

|        | 2-285.  | CMSKB (f= 07)                                       | 2-209   |

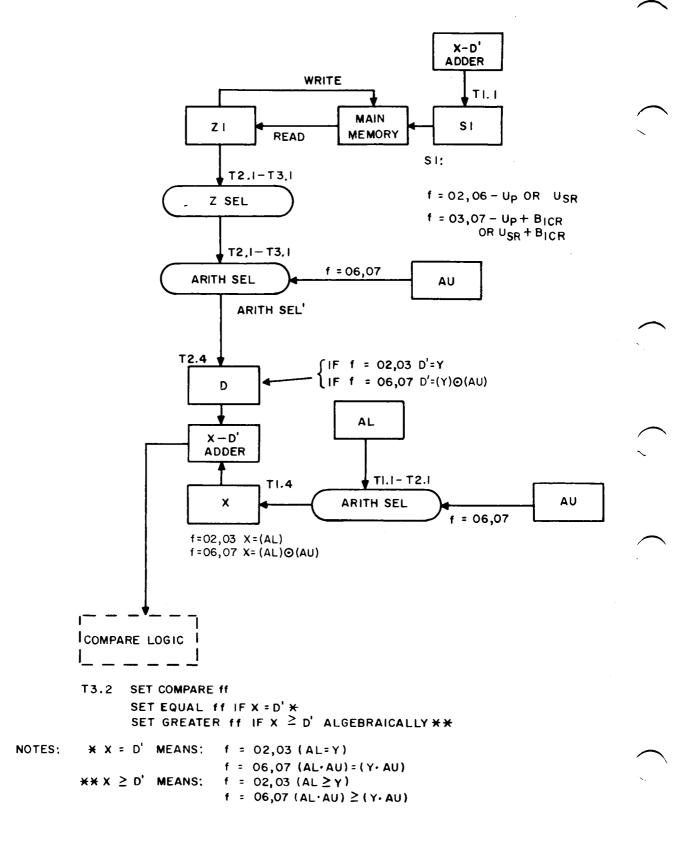

|        | 2-286.  | R1-Sequence Data Flow for $f = 02, 03,$             |         |

|        |         | 06, and 07                                          | 2-209   |

|        | 2-287.  | Clearing of Comparison Flip-Flops                   | 2-209   |

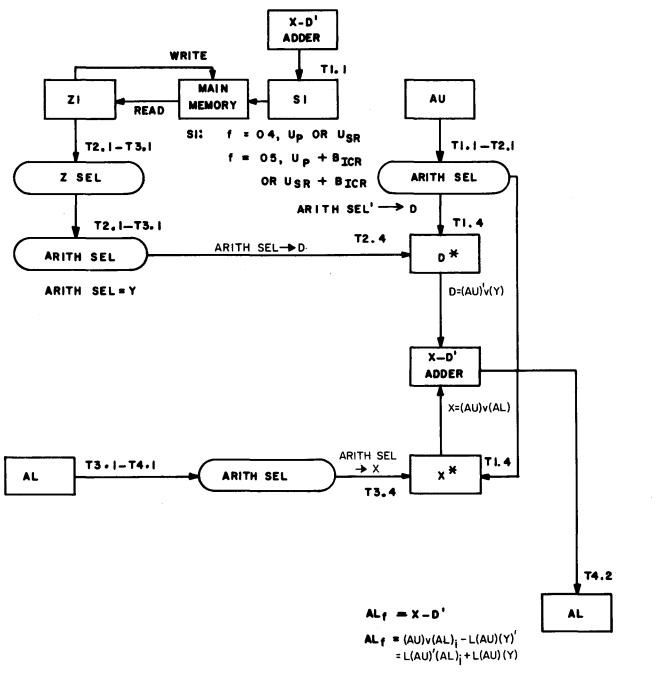

|        | 2-288.  | SLSU (f= 04)                                        | 2 - 213 |

|        | 2-289.  | SLSUB (f= 05)                                       | 2-213   |

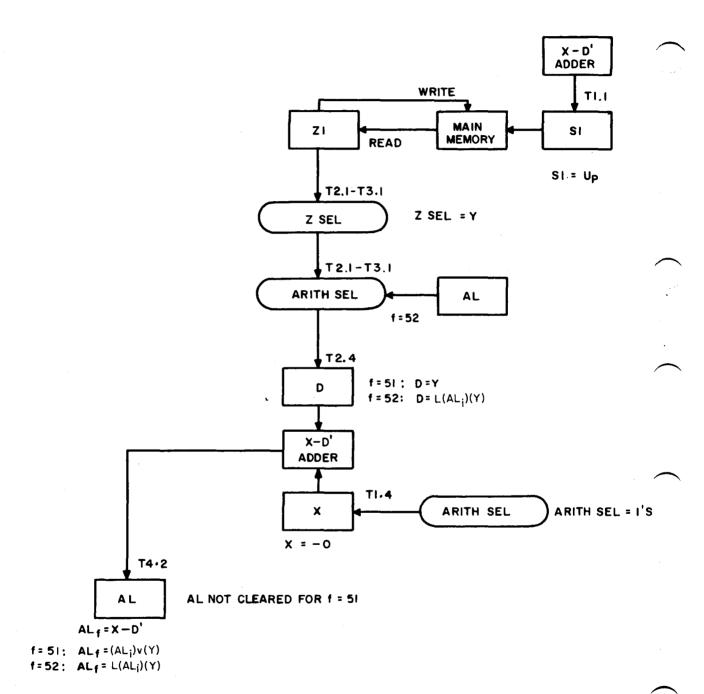

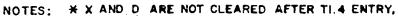

|        | 2-290.  | SLSET (f= 51)                                       | 2 - 213 |

|        | 2-291.  | SLCL (f= 52)                                        | 2-213   |

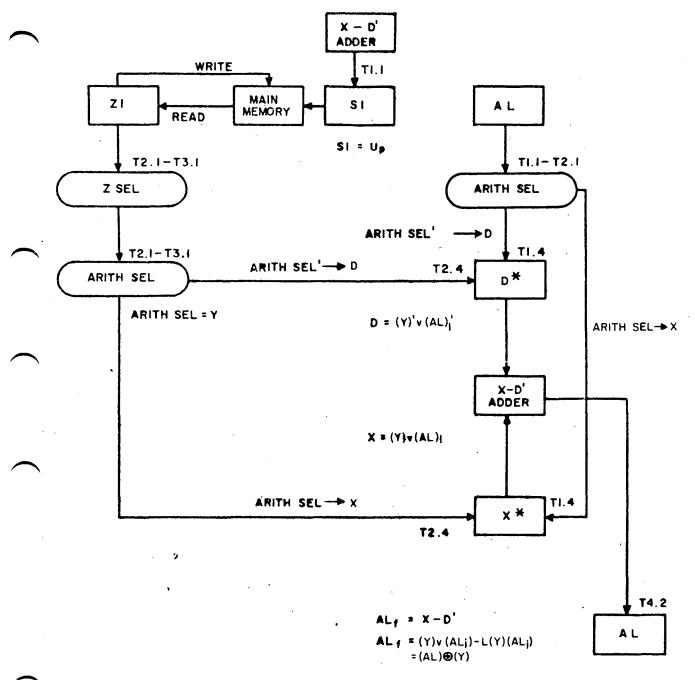

|        | 2-292.  | SLCP (f= 53)                                        | 2-213   |

|        | 2-293.  | R1-Sequence Data Flow for $f = 04$ , and $05 \dots$ | 2-213   |

|        | 2-294.  | R1-Sequence Data Flow for $f = 51$ and $52$         | 2-215   |

|        | 2-295.  | R1-Sequence Data Flow for f= 53                     | 2-215   |

|        | 2-296.  | R1-Sequence Essential Commands                      | 2-218   |

|        | 2-297.  | CPAL (f= 50:61)                                     | 2-218   |

|        | 2-298.  | CPAU (f= 50:62)                                     | 2-218   |

|        | 2-299.  | CPA (f= 50:63)                                      | 2-218   |

|        | 2-300.  | I and Next I-Sequence Data Flow for                 |         |

|        |         | $f=50:61, 50:62, and 50:63 \dots$                   | 2-218   |

|        | 2-301.  | Shift Instructions                                  | 2-222   |

Chapter

| 2-302.   | RSHAU (f= 50:41)                                                                        | 2-222 |

|----------|-----------------------------------------------------------------------------------------|-------|

| 2-303.   | RSHAL (f= 50:42)                                                                        | 2-222 |

| 2-304.   | RSHA (f= $50:43$ )                                                                      | 2-222 |

| 2-305.   | SF (f= $50:44$ )                                                                        | 2-222 |

| 2-306.   | LSHAU (f= $50:45$ )                                                                     | 2-222 |

| 2-307.   | LSHAL ( $f = 50:46$ )                                                                   | 2-225 |

| 2-308.   | LSHA ( $f= 50:47$ )                                                                     | 2-225 |

| 2-309.   | Instruction Sequence                                                                    | 2-225 |

| 2-312.   | Initial Shift Count Equal to Zero or                                                    |       |

|          | $A_{35i} \neq A_{34i}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 2-226 |

| 2-313.   | Initial Shift Count Not Equal to Zero or                                                |       |

|          | $A_{35i} = A_{34i}$ for f= 50:44                                                        | 2-231 |

|          | 2-314. W-Sequence Data Flow for                                                         |       |

|          | SF Instruction ( $f=50:44$ )                                                            | 2-231 |

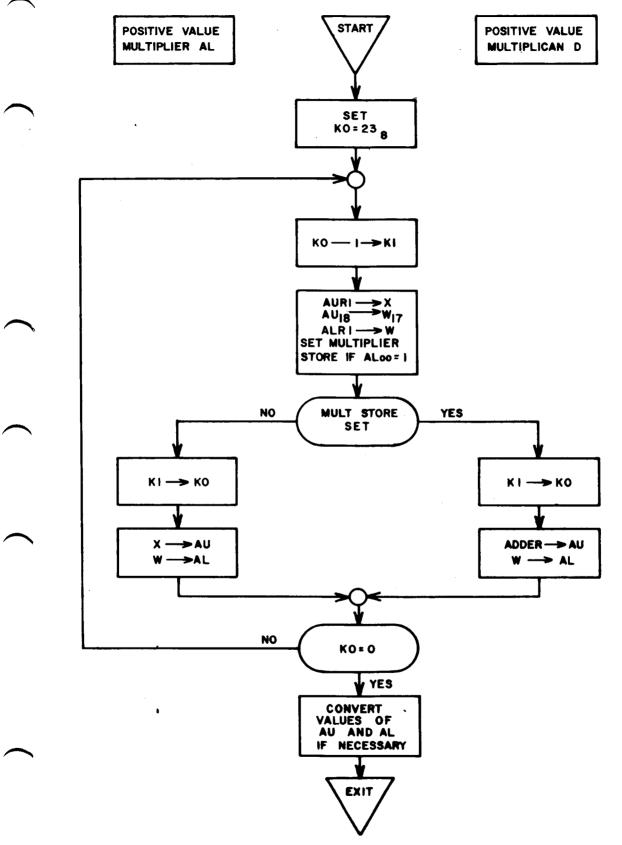

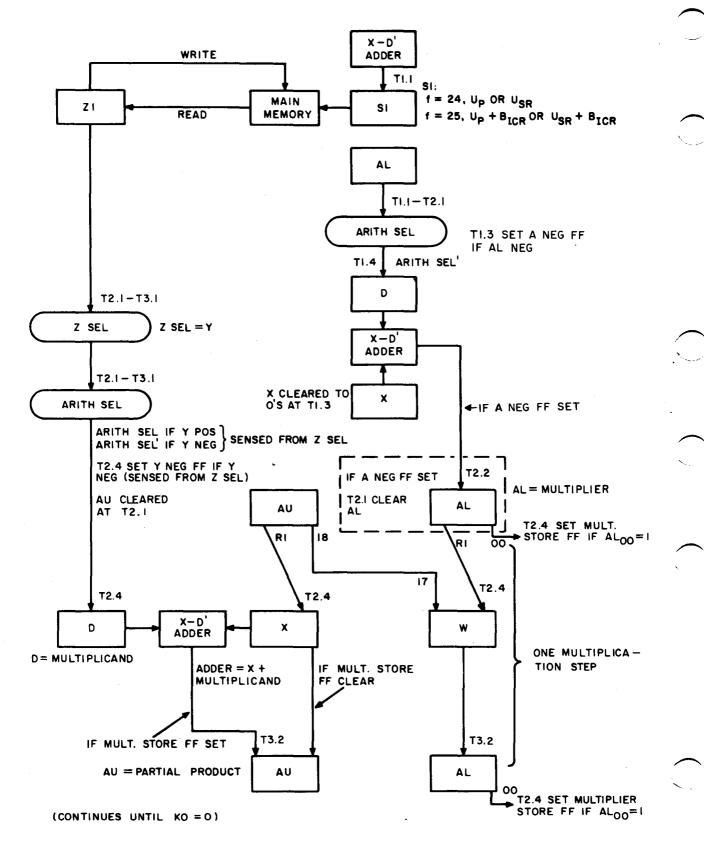

| 2-315.   | Multiply Instructions                                                                   | 2-231 |

| 2-316.   | MULAL (f= 24)                                                                           | 2-232 |

| 2 - 317. | MULALB (f= 25)                                                                          | 2-232 |

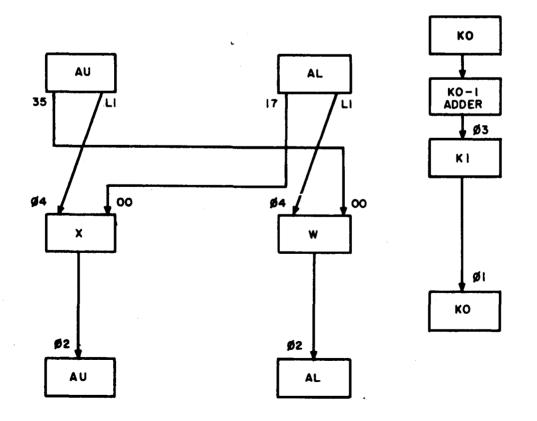

| 2-319.   | R1 and Multiply Sequence Data Flow                                                      | 2-242 |

| 2-321.   | Divide Instructions                                                                     | 2-245 |

|          | 2-322. DIVA (f= 26)                                                                     | 2-245 |

|          | 2-323. DIVAB (f= 27) $\dots$                                                            | 2-245 |

|          | 2-324. R1 and Divide Sequence Data Flow                                                 | 2-245 |

Section 2-3. Detailed Functional Description (Memory Section)

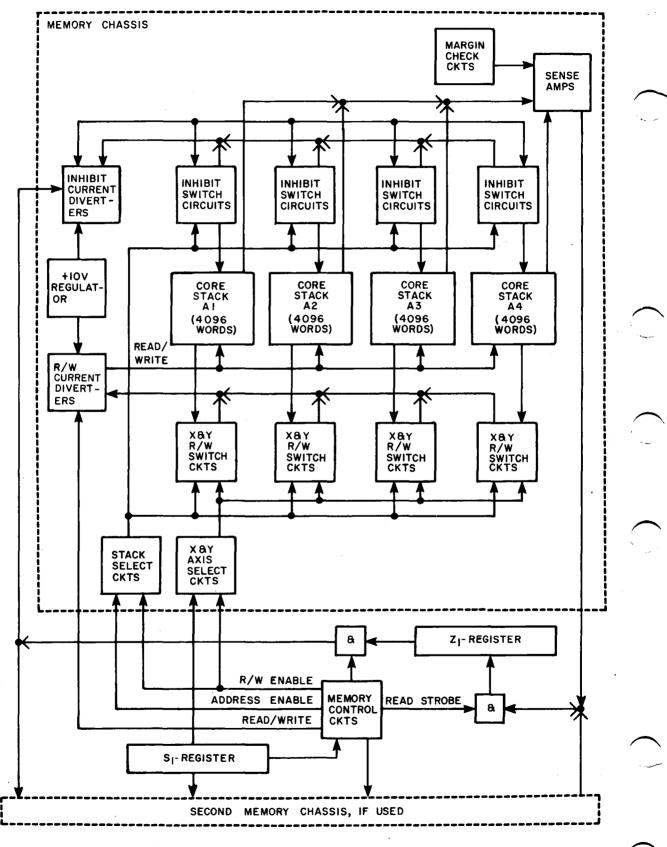

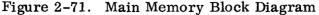

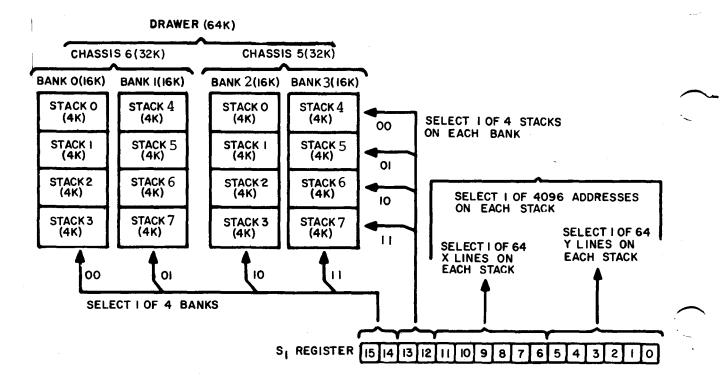

| 2-326. | Memory | Section. |                                | -259 |

|--------|--------|----------|--------------------------------|------|

|        | 2-329. | 16-BIT   | S <sub>1</sub> -Register 2     | -259 |

|        | 2-330. | Address  | s Translators 2                | -259 |

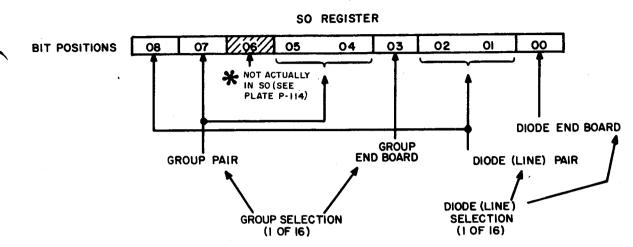

|        | 2-331. | 8-BIT S  | -Register                      | -261 |

|        | 2-332. |          | emory 2                        |      |

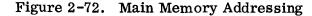

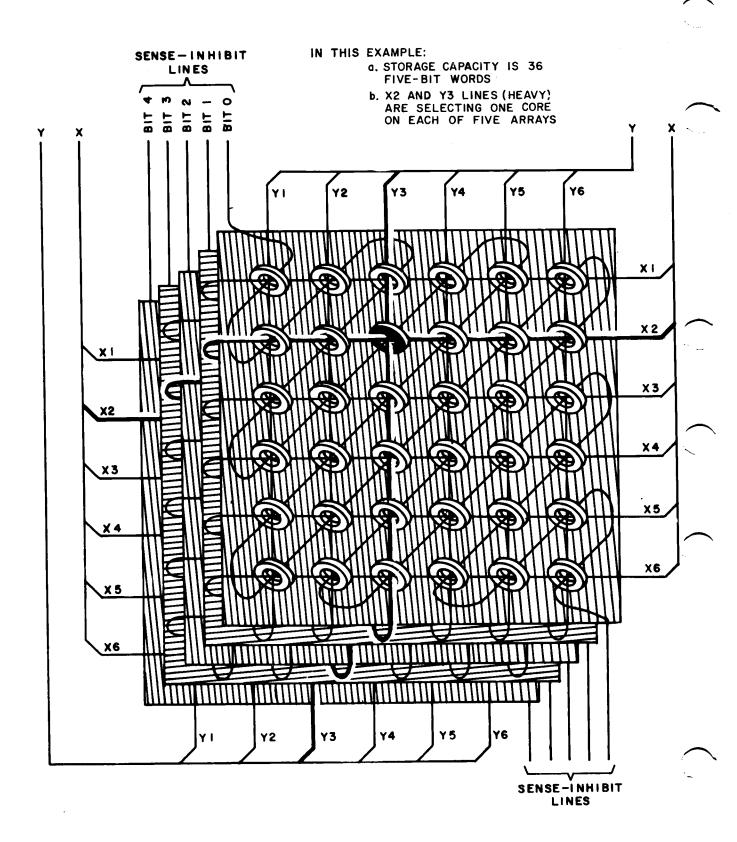

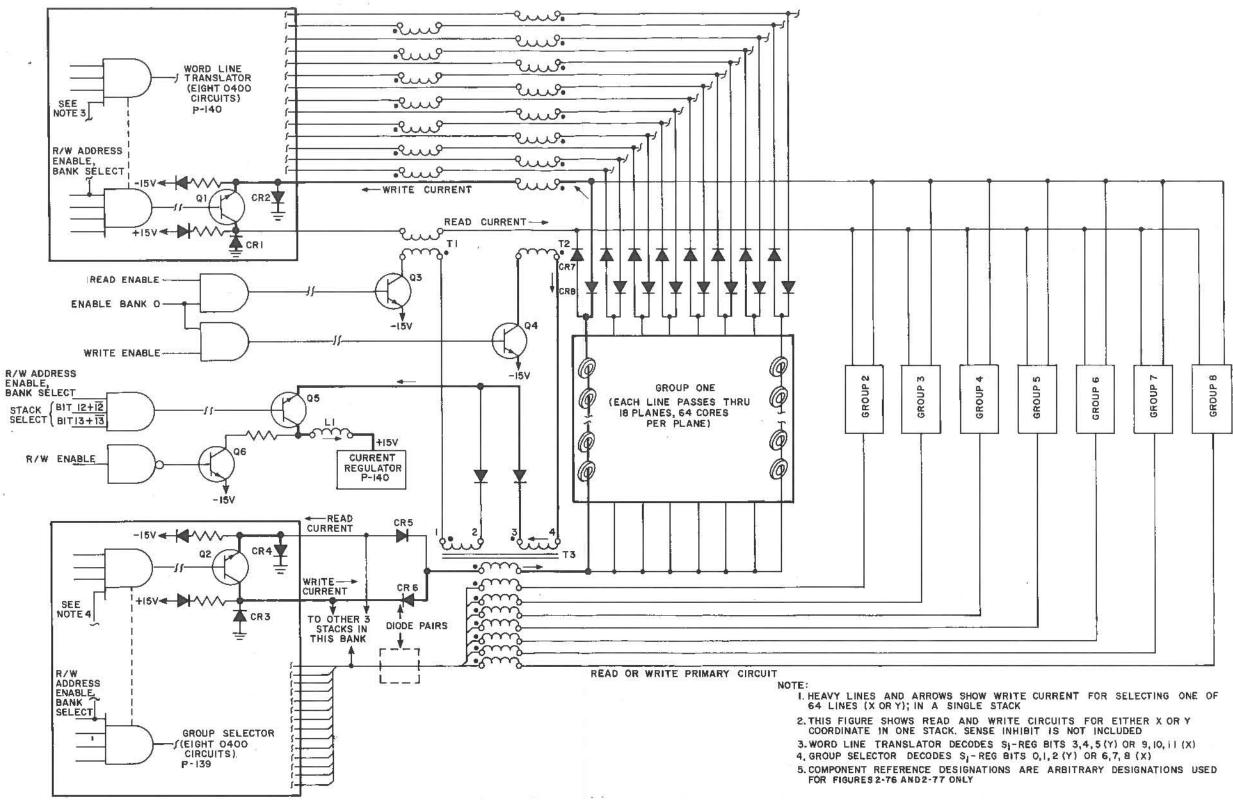

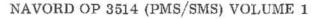

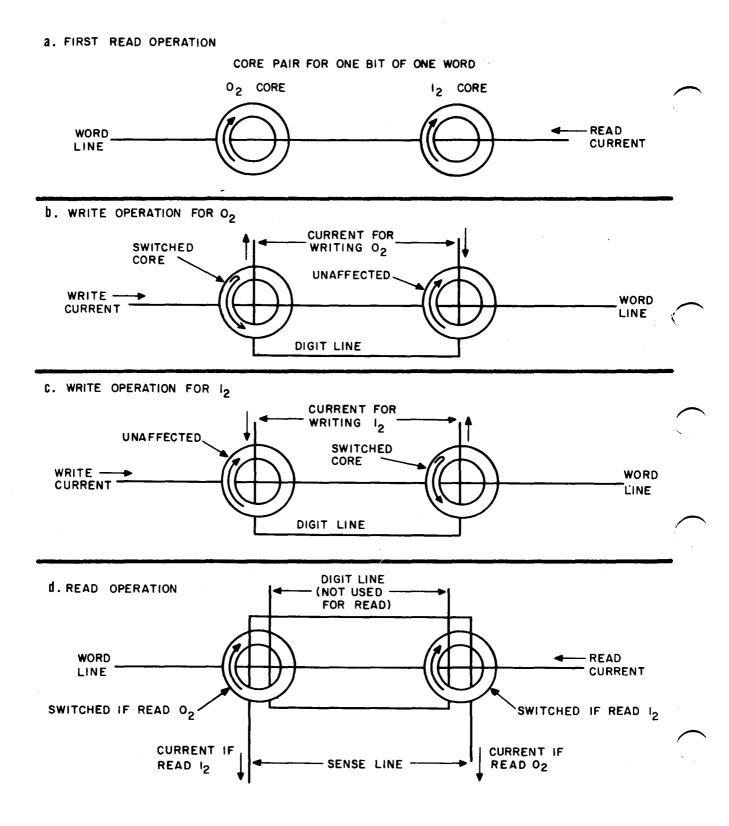

|        |        | 2-335.   | Main Memory Addressing 2       | -261 |

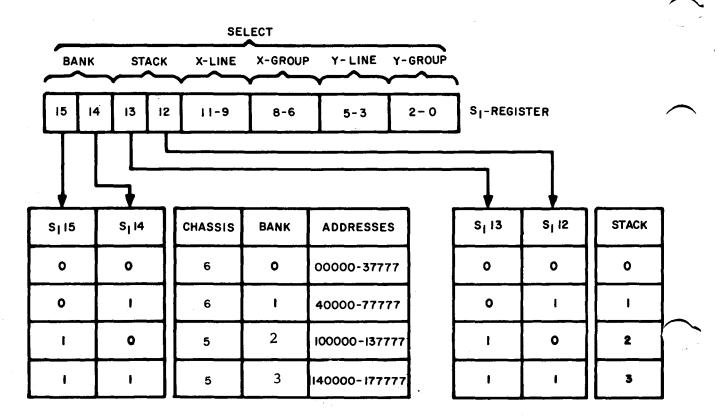

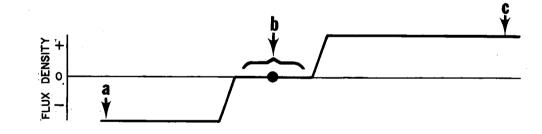

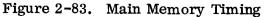

|        |        | 2-338.   | Core Magnetization 2           | -263 |

|        |        | 2-341.   | Memory Stack Operation 2       | -263 |

|        |        | 2-344.   | X and Y-Line Selection 2       | -267 |

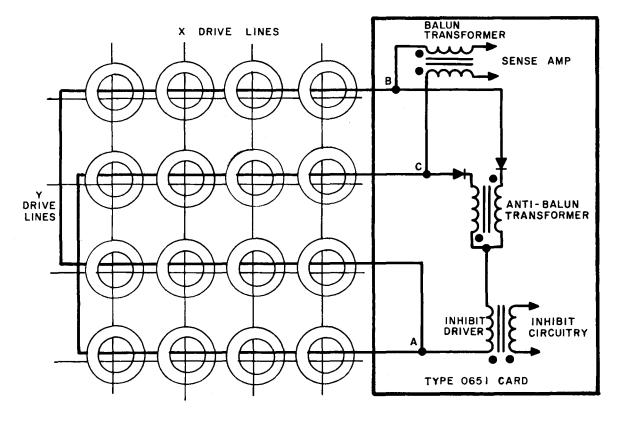

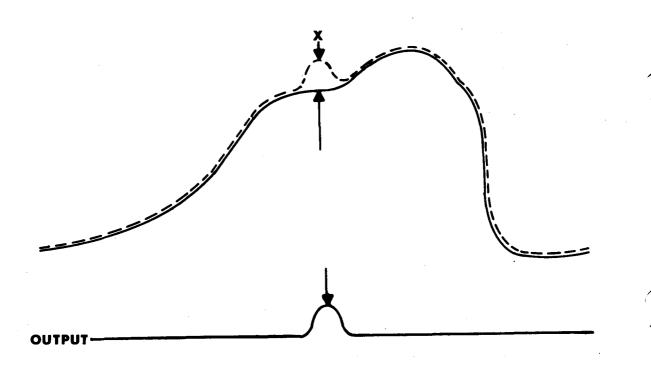

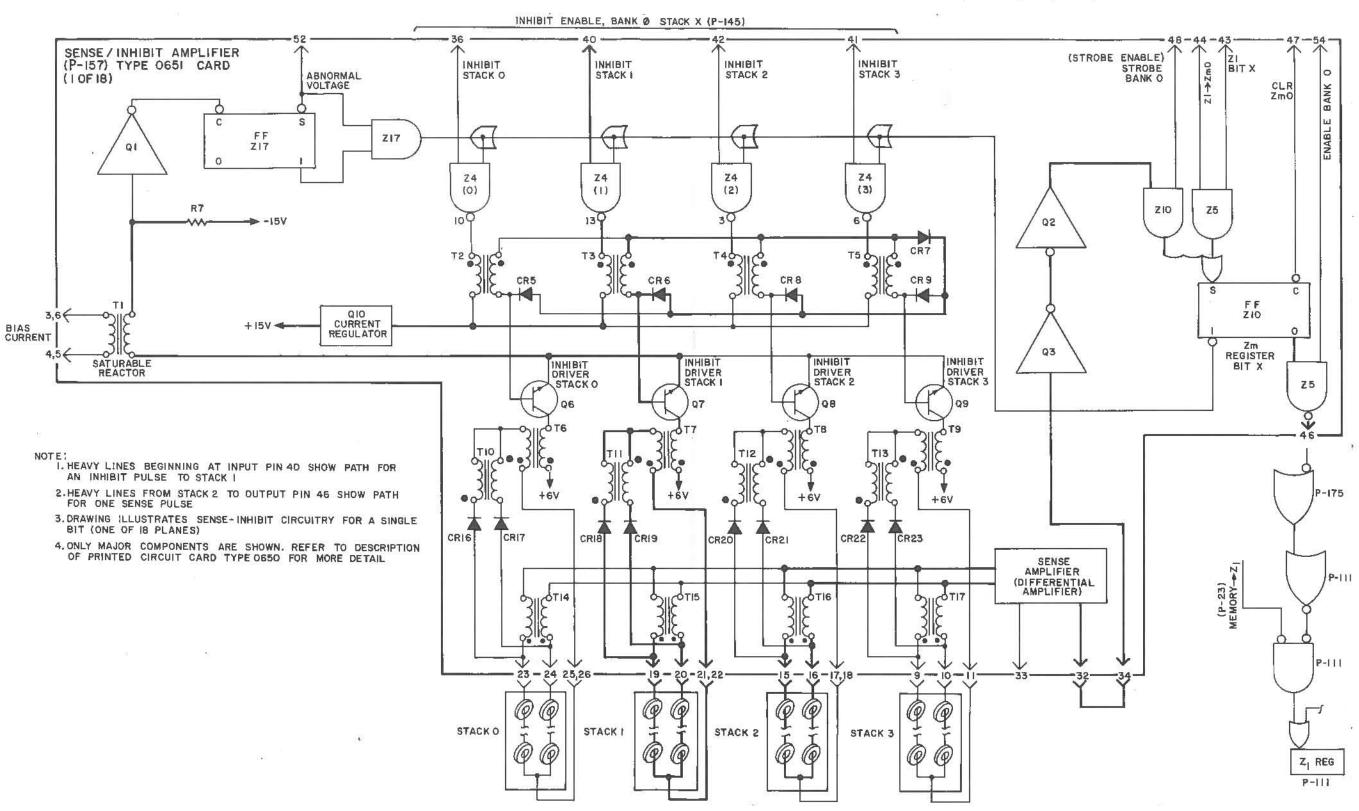

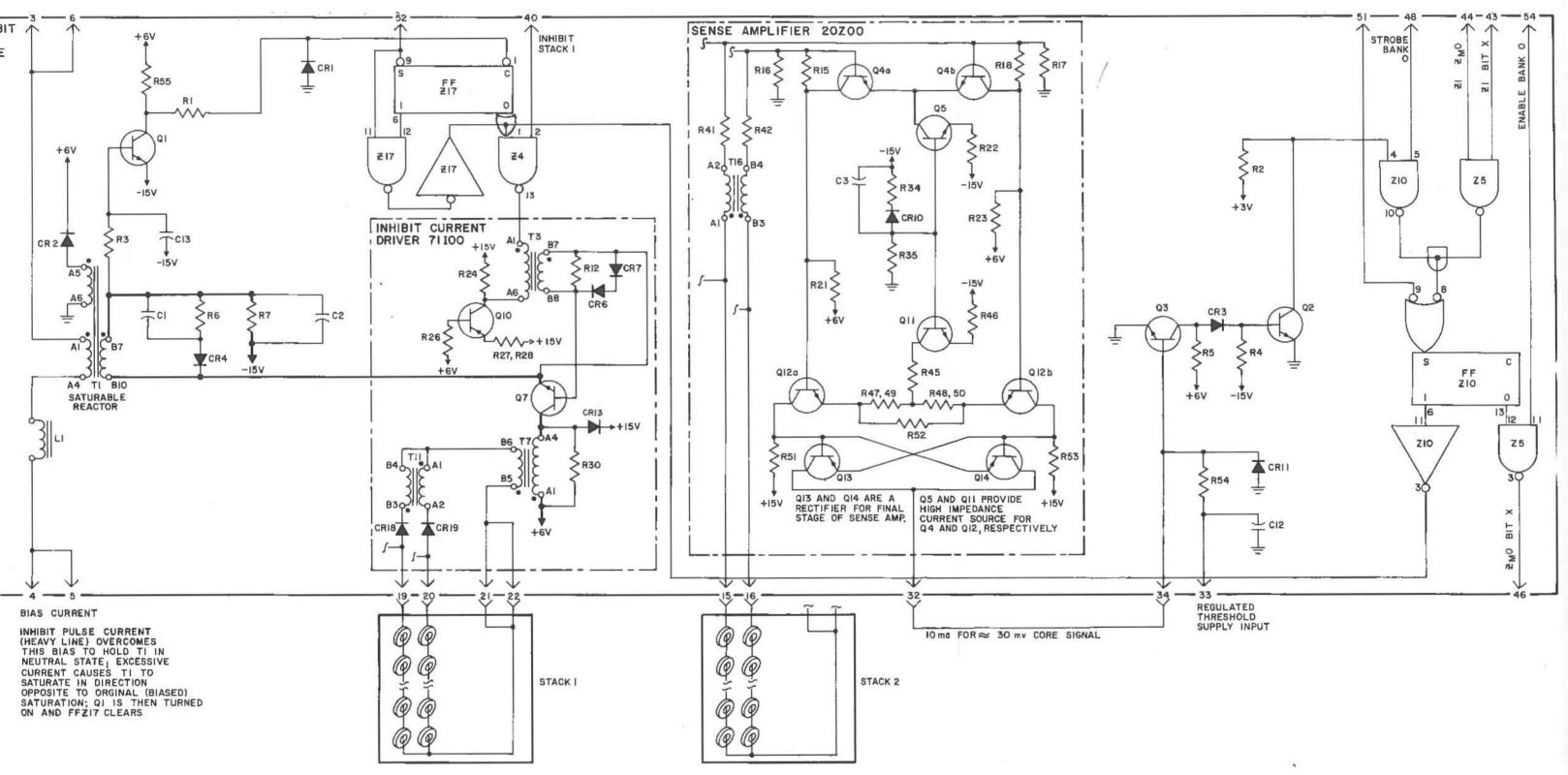

|        |        | 2-355.   | Sense/Inhibit Line Operation 2 | -274 |

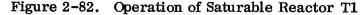

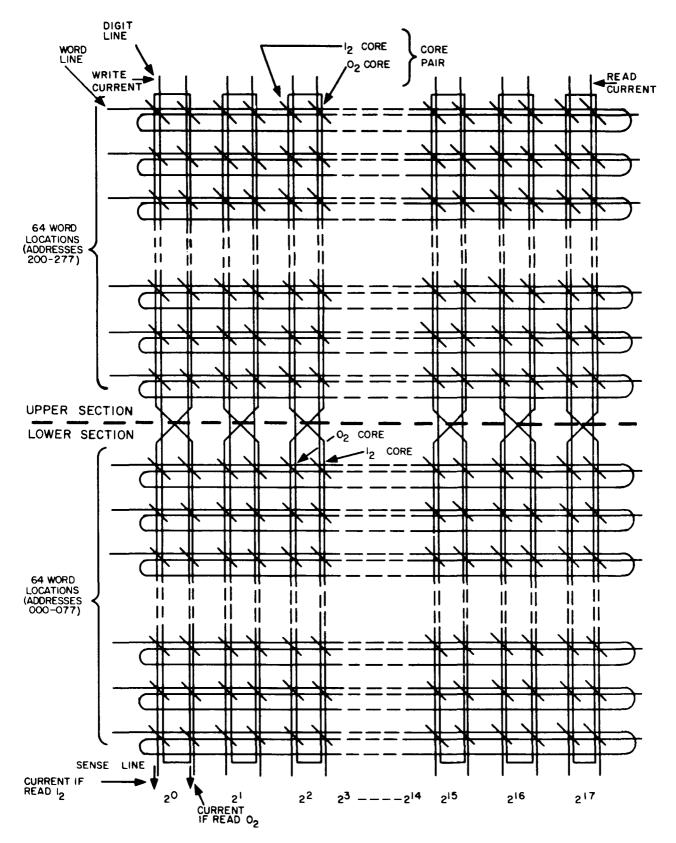

|        |        | 2-369.   | Main Memory Timing 2           | -282 |

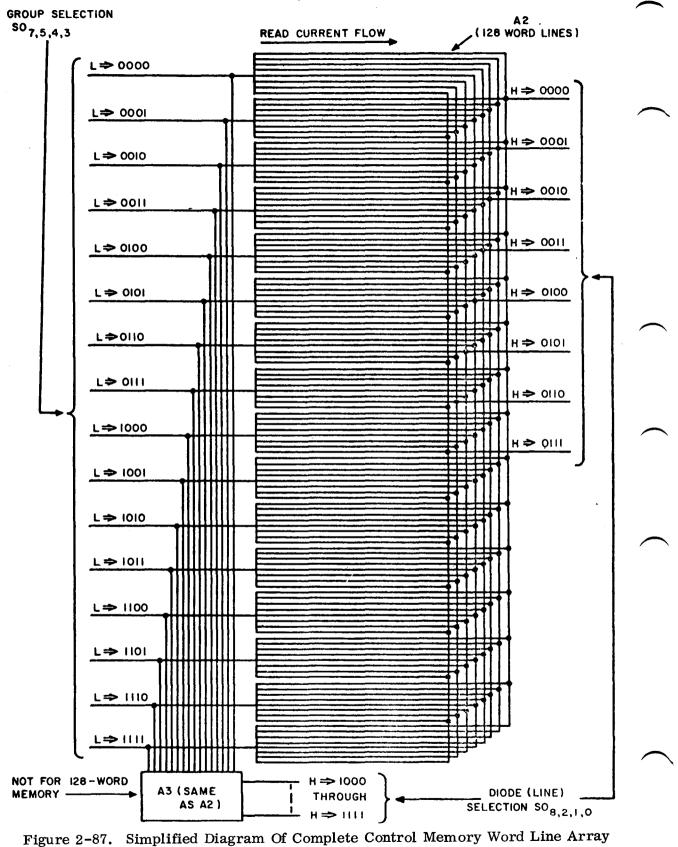

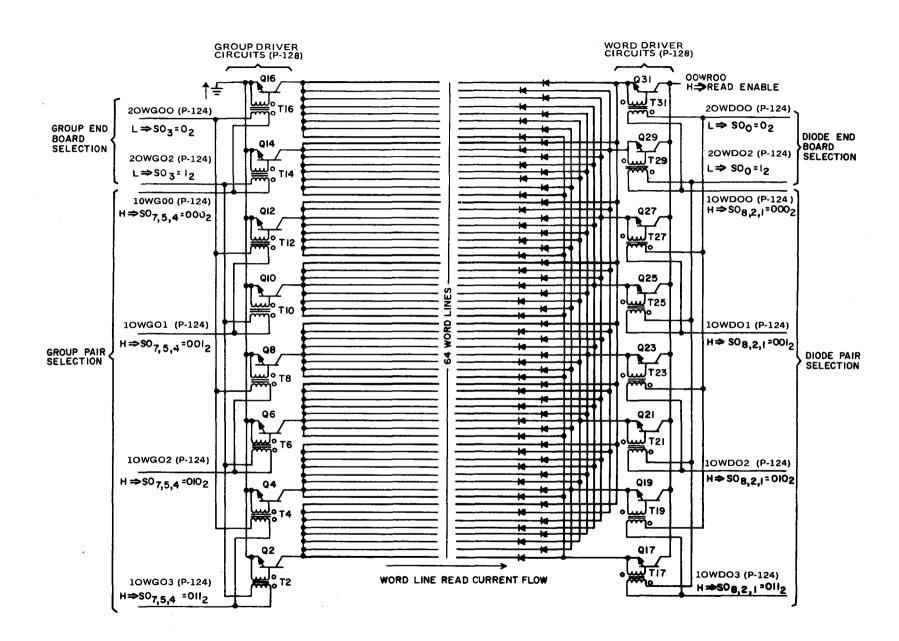

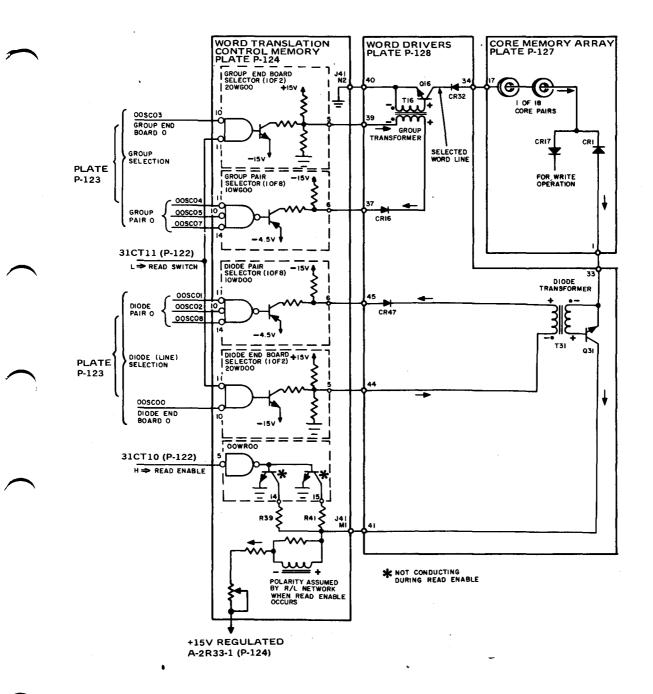

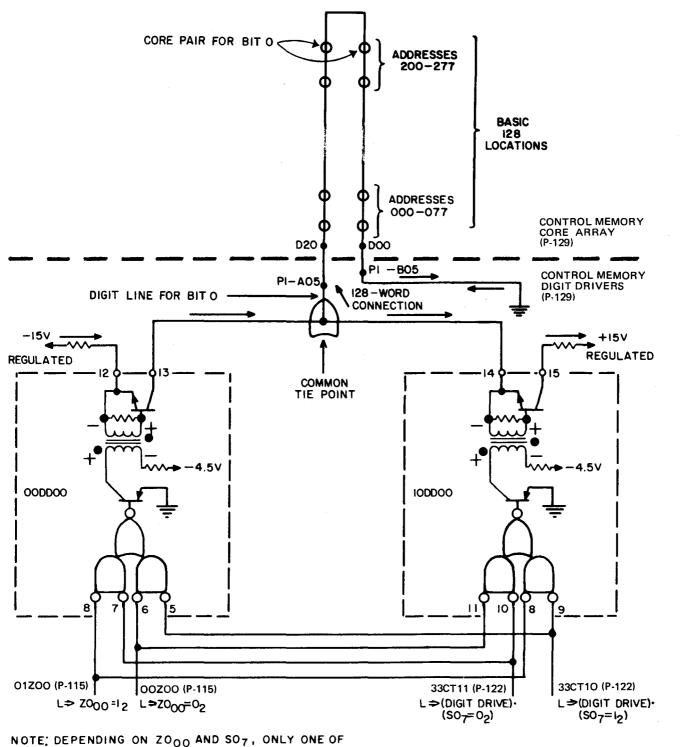

|        | 2-376. | Control  | Memory 2                       | -285 |

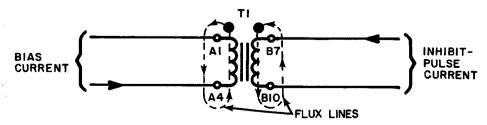

|        |        | 2-377.   | Core Pair Operation 2          | -285 |

|        |        |          |                                |      |

CHANGE 7 ix

### Chapter

|        | 2 - 380. | Physical Arrangement      | 2 - 287 |

|--------|----------|---------------------------|---------|

|        | 2-382.   | Control Memory Addressing | 2-287   |

|        | 2 - 390. | Selected Circuit Analysis | 2-292   |

|        | 2-392.   | Digit-Line Current        | 2-294   |

|        | 2-396.   | Sense Line Output         | 2-295   |

|        | 2-397.   | Control Memory Timing     | 2-295   |

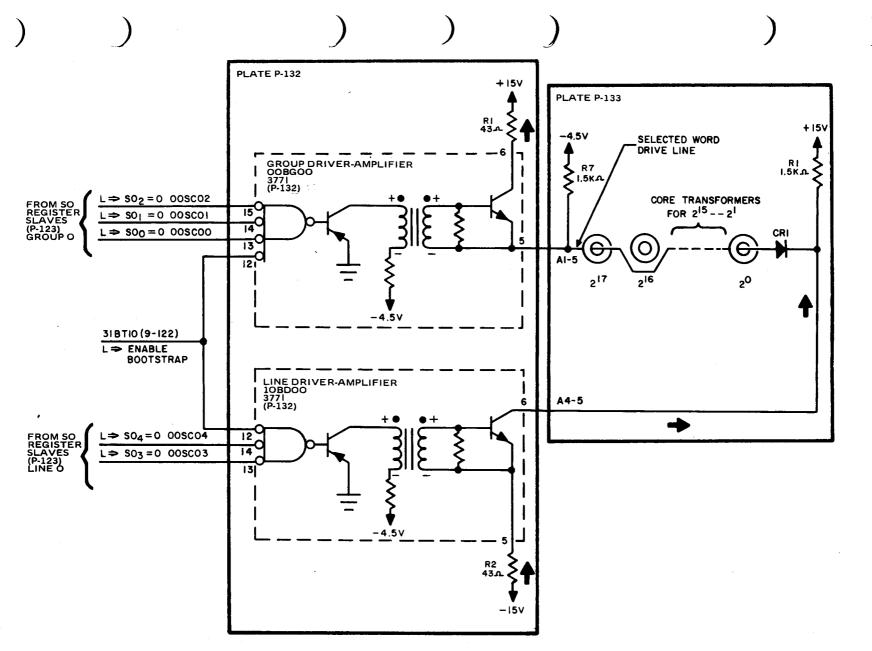

| 2-401. | Bootstra | ap Memory                 | 2-298   |

|        | 2-402.   | Storage Element           | 2-298   |

|        | 2-403.   | Readout Operation         | 2-298   |

|        | 2-404.   | Physical Arrangement      | 2-298   |

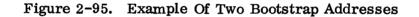

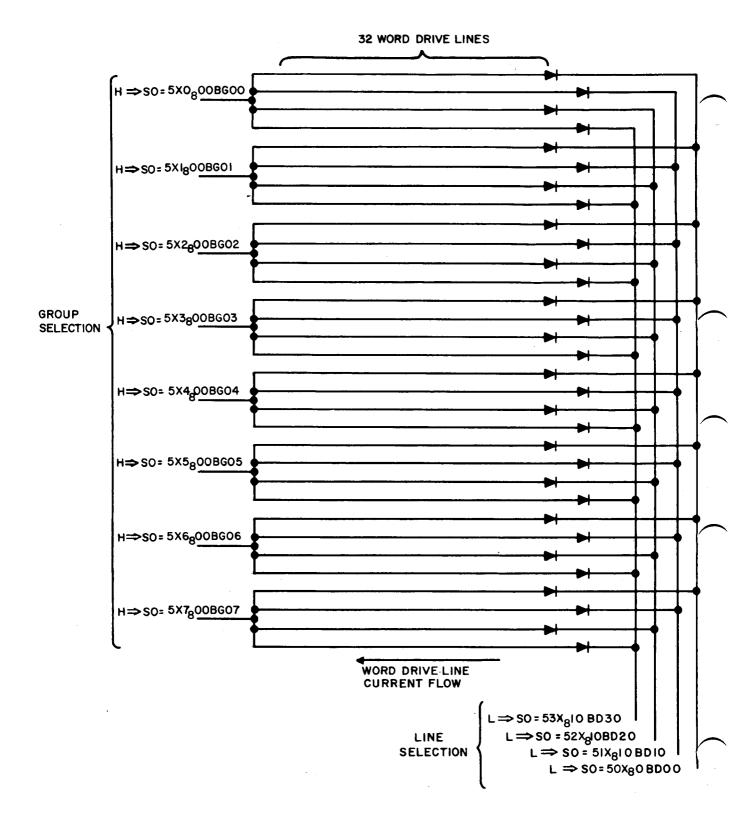

|        | 2-405.   | Group and Line Selection  | 2-300   |

|        | 2-410.   | Sense-Line Analysis       | 2-304   |

|        | 2-411.   | Initiate Bootstrap Memory | 2-304   |

|        |          |                           |         |

#### Section 2-3. Detailed Functional Description (I/O Section)

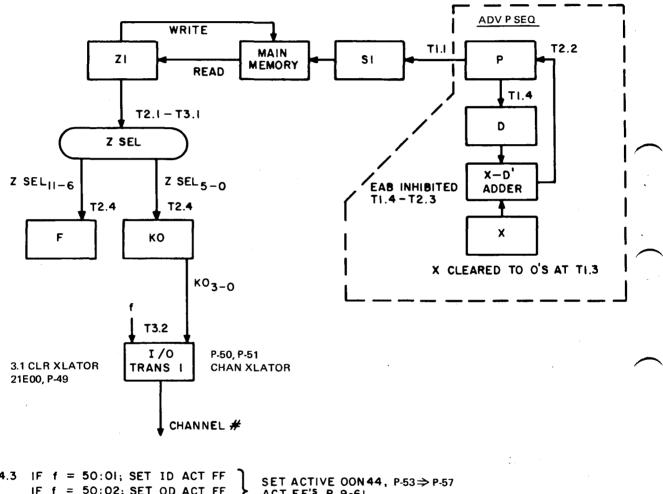

| 2-413. | Input/Ou <sup>-</sup> | tput Section                                    | 307 |

|--------|-----------------------|-------------------------------------------------|-----|

|        | 2-415.                | Interface                                       | 307 |

|        | 2-416.                | Data Exchange Rate 2-3                          | 307 |

|        | 2-417.                | I/O Signals 2-3                                 | 307 |

|        |                       | 2-418. Data Request Signal 2-3                  | 307 |

|        |                       | 2-419. Real-Time-Clock Request (RTC Request)    |     |

|        |                       | Signals 2-3                                     | 309 |

|        |                       | 2-420. Interrupt Signals 2-3                    | 309 |

|        | 2-421.                | Buffers and Address Control Words 2-3           | 309 |

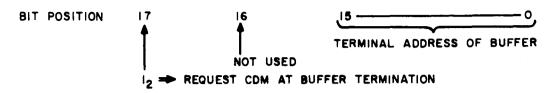

|        |                       | 2-422. Terminal Address Control Word (TACW) 2-3 | 309 |

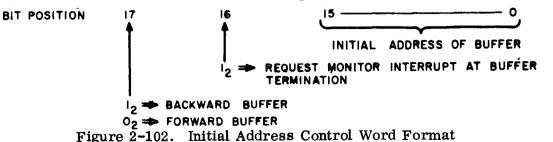

|        |                       | 2-423. Initial Address Control Word (IACW) 2-3  | 309 |

|        | 2 - 425.              | Special I/O Logic 2-3                           | 310 |

|        |                       | 2-426. Active Flip-Flop 2-3                     | 310 |

|        |                       | 2-427. Priority Logic 2-3                       | 310 |

|        |                       | 2-428. I/O Translator 2-3                       | 310 |

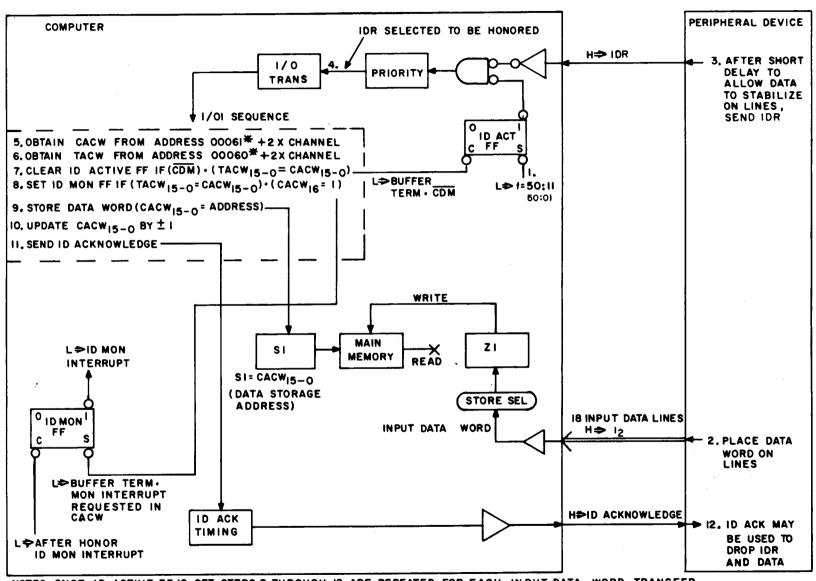

|        | 2-429.                | Data Request Operations 2-3                     | 310 |

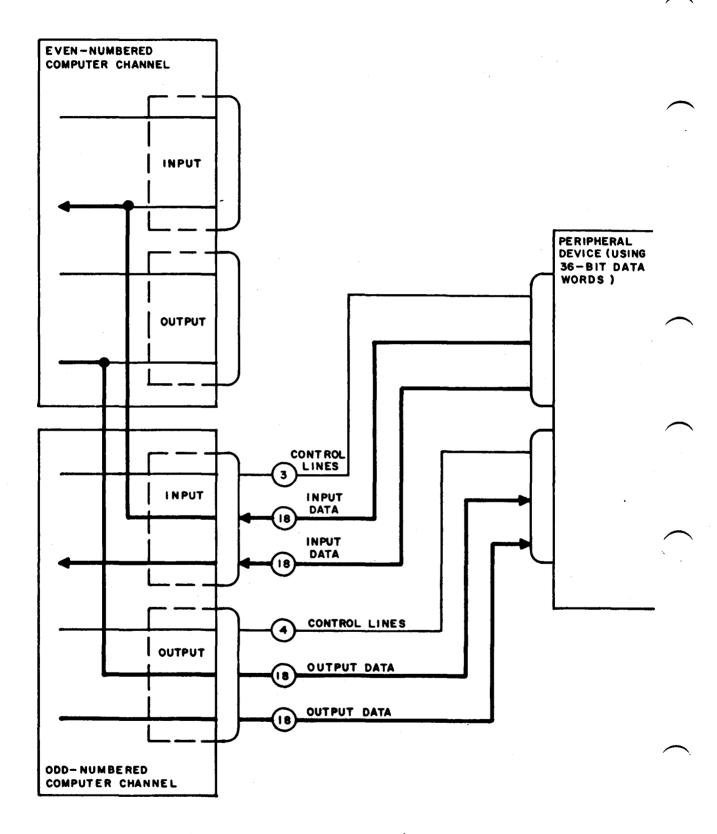

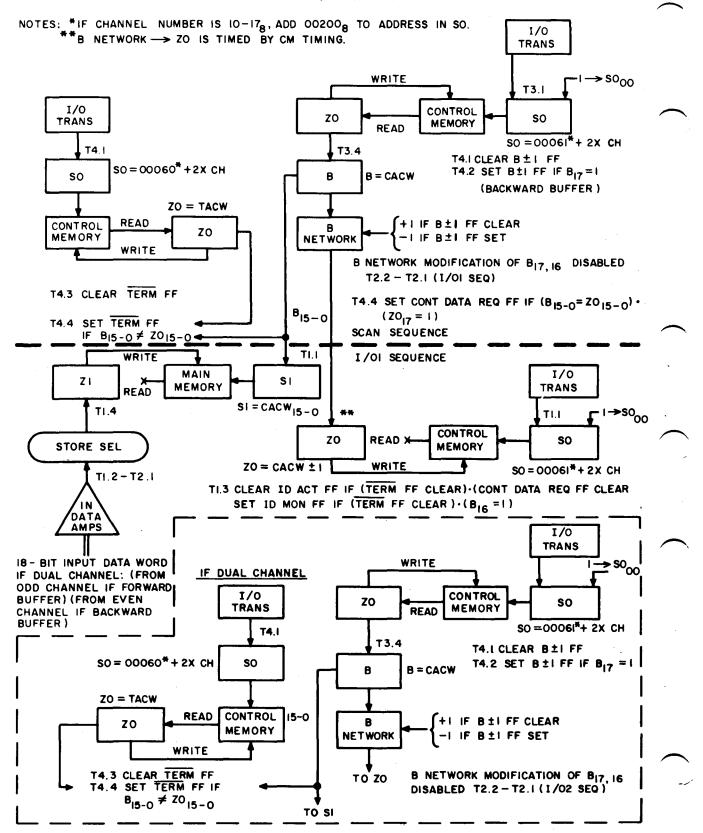

|        | 2-430.                | Dual-Channel Operation 2-3                      | 312 |

|        | 2-431.                | Continuous-Data Mode (CDM) 2-3                  | 312 |

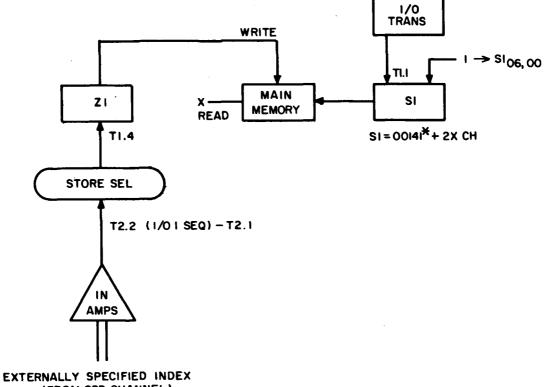

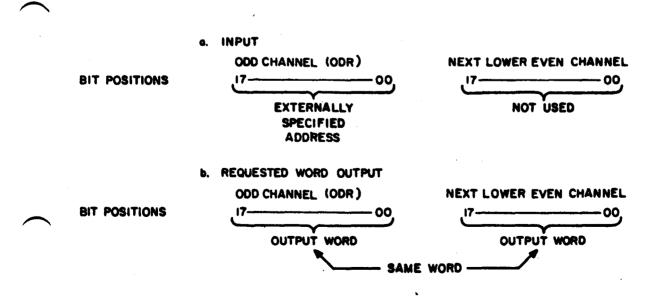

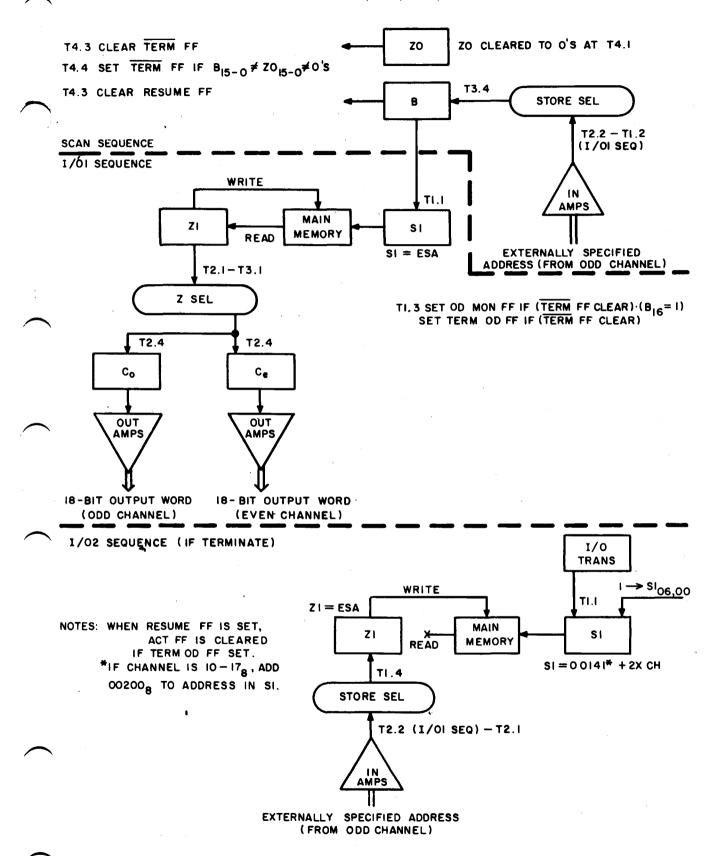

|        | 2 - 432.              | Externally Specified Index (ESI) 2-3            | 312 |

|        | 2-433.                | Externally Specified Address (ESA)              | 313 |

|        | 2-434.                | Execution of SIN, SOUT, SEXF, INSTP, OUTSTP,    |     |

|        |                       | EXFSTP Instructions 2-3                         | 313 |

#### Chapter

.

|          | 2-435.                                                                       | SIN (f= 50:01)                               | 2-313   |

|----------|------------------------------------------------------------------------------|----------------------------------------------|---------|

|          | $2-\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ | SOUT (f= 50:02)                              | 2-313   |

|          | 2-437.                                                                       | SEXF (f= 50:03)                              | 2-313   |

|          | 2-438.                                                                       | INSTP (f= 50:15)                             | 2-313   |

|          | 2-439.                                                                       | OUTSTP (f= 50:16)                            | 2-313   |

|          | 2-440.                                                                       | EXFSTP (f= 50:17)                            | 2 - 313 |

|          | 2-441.                                                                       | I-Sequence Data Flow for f= 50:01 through    |         |

|          |                                                                              | 50:03, and 50:15 through 50:17               | 2 - 313 |

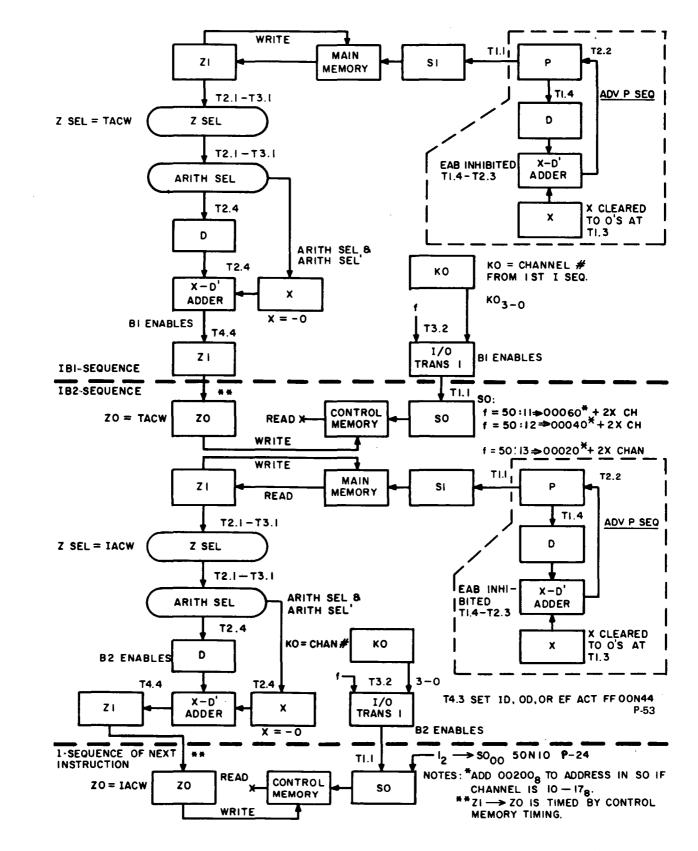

| 2-444.   | Execution                                                                    | on of IN, OUT, and EXF Instructions (f=50:11 |         |

|          |                                                                              | through $50:13$ ).                           | 2-329   |

|          | 2-445.                                                                       | IN ( $f=50:11$ )                             | 2-329   |

|          | 2-446.                                                                       | OUT (f= 50:12)                               | 2-329   |

|          | 2-447.                                                                       | EXF (f= $50:13$ )                            | 2-329   |

|          | 2 - 448.                                                                     | Execution Sequences                          | 2-329   |

|          | 2-449.                                                                       | I-Sequence Data Flow for $f = 50:11$         |         |

|          |                                                                              | through 50:13                                | 2-329   |

|          | 2-450.                                                                       | IB1 Sequence                                 | 2-329   |

|          | 2-451.                                                                       | IB2 Sequence                                 | 2-329   |

|          | 2-452.                                                                       | IB1 and IB2 Sequence Data Flow for f = 50:11 |         |

|          |                                                                              | through 50:13                                | 2-330   |

|          | 2-453.                                                                       | IB1 and IB2 Sequence Essential Commands      |         |

|          |                                                                              | for f= 50:11 through 50:13                   | 2-330   |

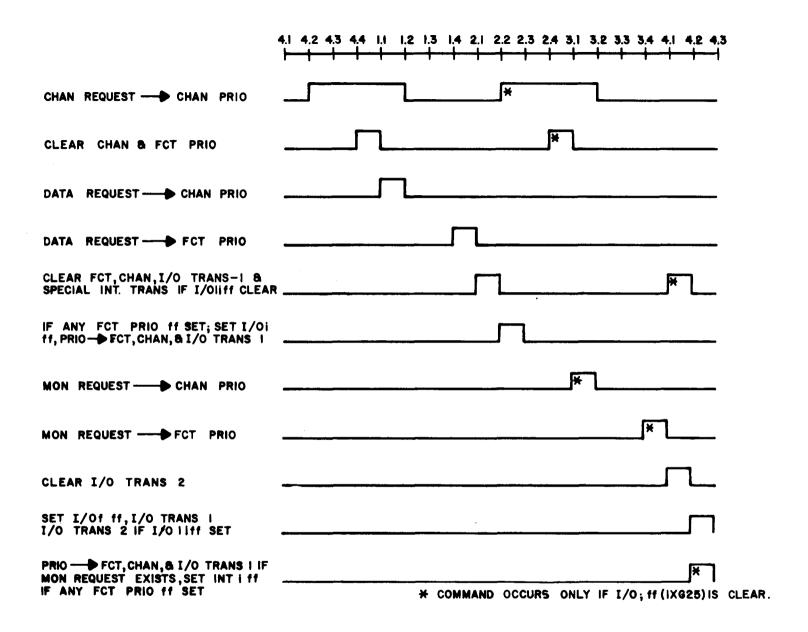

| 2-454.   | Priority                                                                     | y Signal Detection and Selection             | 2-335   |

|          | 2-457.                                                                       | Data Request and Monitor Interrupt           |         |

|          |                                                                              | Priority                                     | 2-336   |

|          | 2-458.                                                                       | Data Request Scan                            | 2-336   |

|          | 2-459.                                                                       | Interrupt Request Scan                       | 2-336   |

|          | 2-460.                                                                       | Request Signal Entrance Logic                | 2-336   |

|          | 2-461.                                                                       | IDR Signal Detection                         | 2-336   |

| 2-463.   | I/O Sign                                                                     | nal Selection                                | 2-337   |

|          | 2-464.                                                                       | Data-Request Scan                            | 2-337   |

|          | 2 - 465.                                                                     | Interrupt Request Scan                       | 2-341   |

|          | 2-466.                                                                       | I/O Signal Selection Essential Commands      | 2-341   |

| 2-467.   | Channel                                                                      | Priority Selection                           | 2-351   |

| 2-470.   | Function                                                                     | n Priority Selection                         | 2-351   |

| 2-473.   | Group F                                                                      | Priority Selection                           | 2-353   |

| 2-474.   | Group 7                                                                      | Translator (I/O Translator 1)                | 2-353   |

| 2 - 475. | Mode T                                                                       | ranslator (I/O Translator 1)                 | 2-355   |

| 2-476.   | Channel                                                                      | Translator                                   | 2-355   |

CHANGE 7 xi

#### Chapter

| 2-477.   | Functio  | n Translator                                 | 2-355   |

|----------|----------|----------------------------------------------|---------|

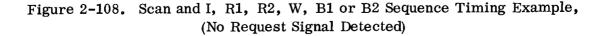

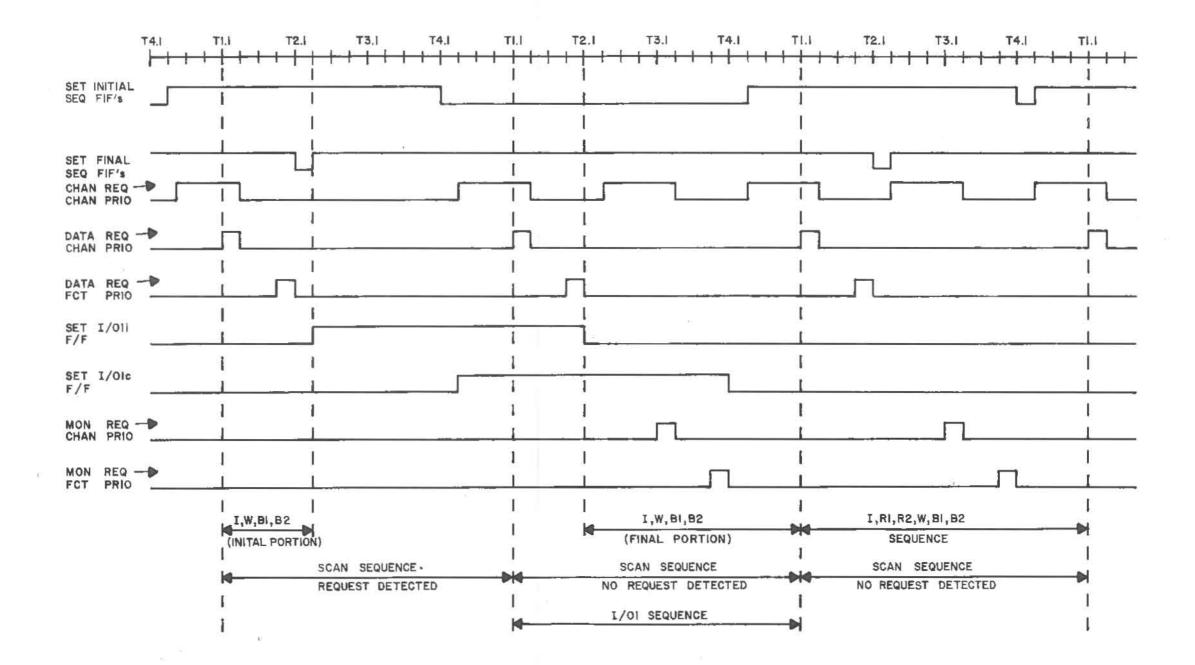

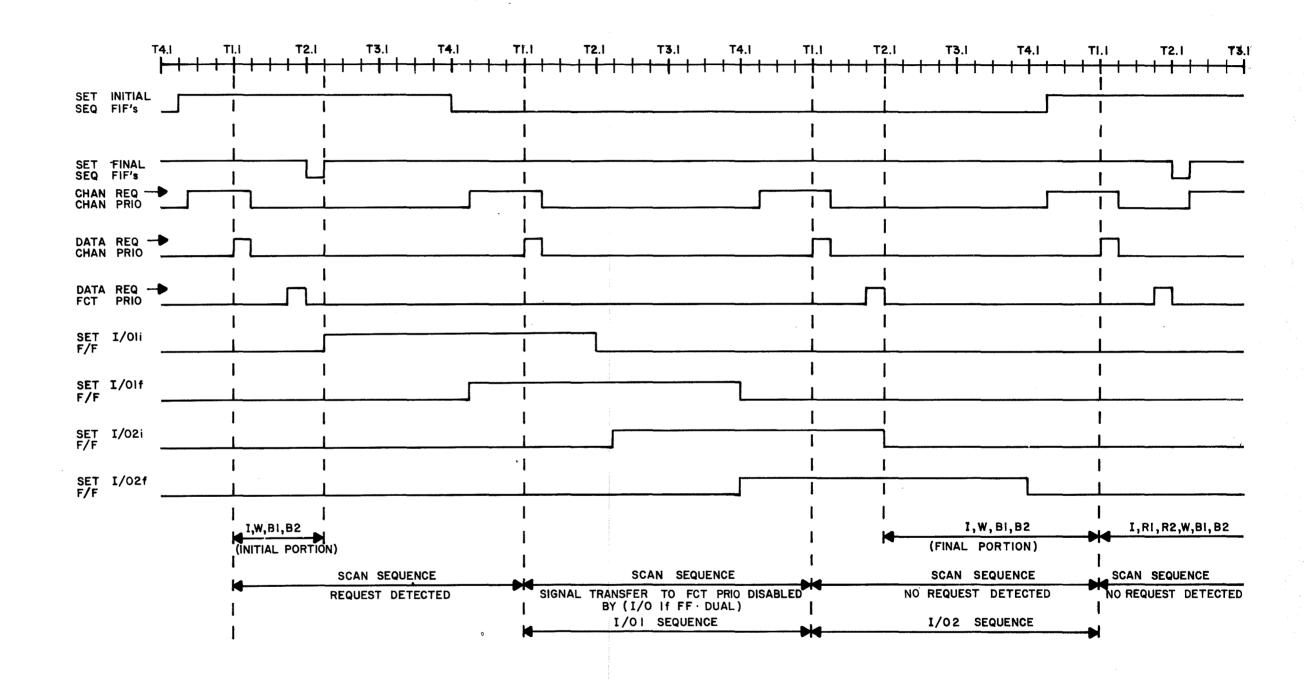

| 2 - 478. | Data-Re  | equest Sequence Timing                       | 2-357   |

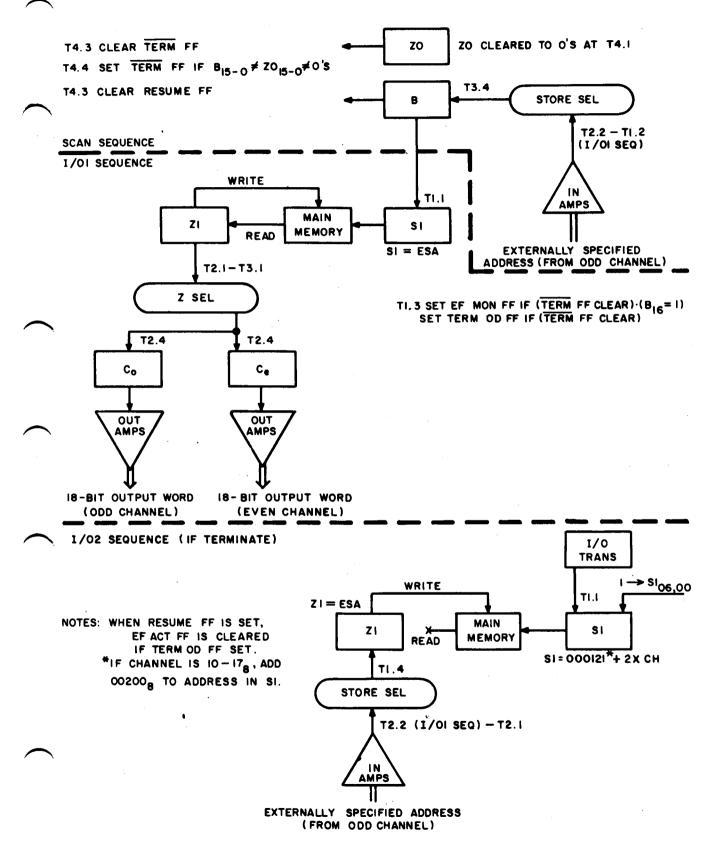

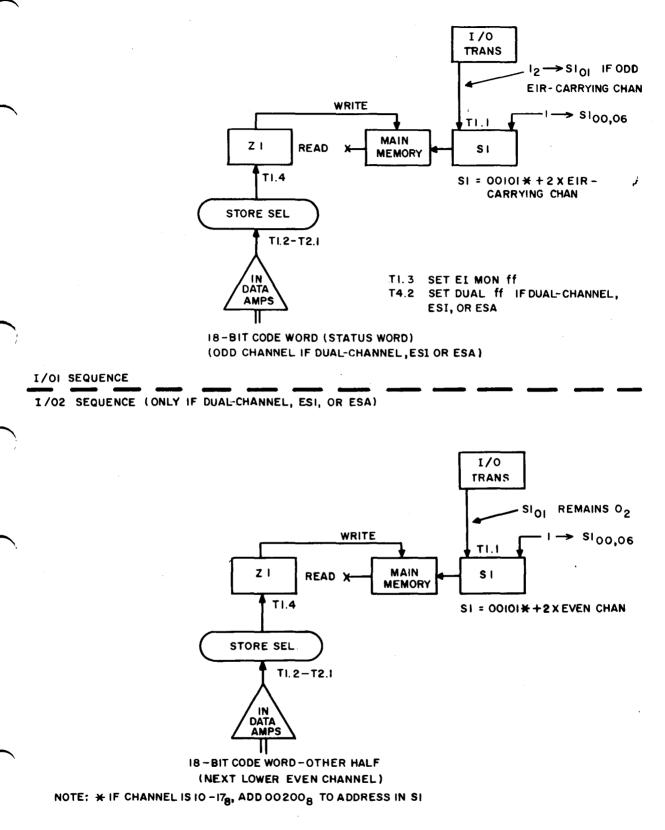

| 2-484.   | Input-D  | ata-Request Operations                       | 2 - 365 |

|          | 2 - 485. | Single-Channel Operation                     | 2 - 365 |

|          | 2-488.   | Dual-Channel Operation                       | 2 - 365 |

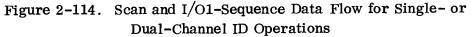

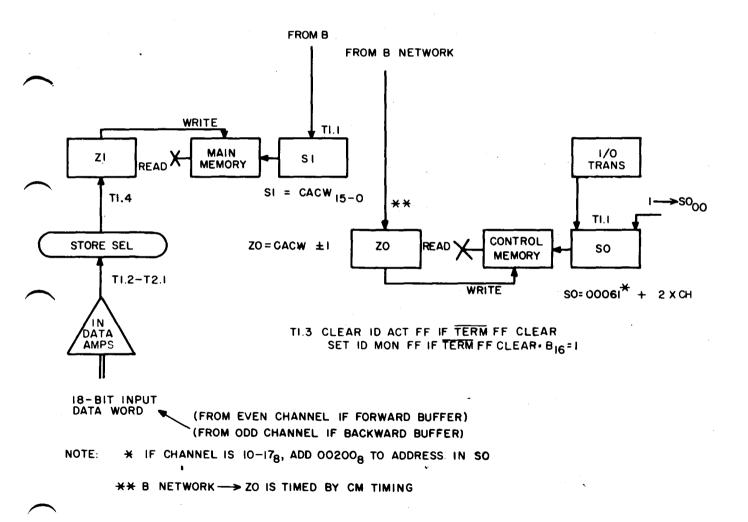

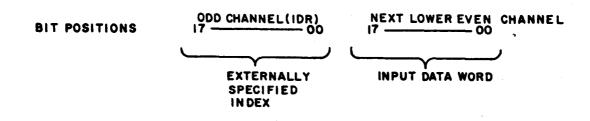

| i.       | 2-490.   | Scan and I/O Sequence Single-Channel         | • .     |

|          |          | ID Operation Data Flow                       | 2 - 371 |

|          | 2-491.   | Scan, I/O1, and I/O2 Sequence Dual-          |         |

|          |          | Channel ID Operation Data Flow               | 2 - 371 |

|          | 2-492.   | Scan and I/O Sequence Essential Commands     |         |

|          |          | for Single-or Dual-Channel ID Operations     | 2 - 371 |

|          | 2-494.   | ID Acknowledge Timing                        | 2-383   |

|          | 2-495.   | Scan, I/O1, and I/O2 Sequence Essential      |         |

|          |          | Commands (Fast Interface)                    | 2-383   |

|          | 2-496.   | Scan, I/O1, and I/O2 Sequence Essential      |         |

|          |          | Commands (Slow Interface)                    | 2-383   |

| 2-497.   | Input Da | ata Operations with ESI                      | 2-383   |

|          | 2-499.   | Scan, $I/O1$ , and $I/O2$ Sequence Essential |         |

|          |          | Commands for ID Operations with ESI          | 2 - 384 |

| 2-500.   | -        | ata Operations with ESA                      | 2-393   |

|          | 2-502.   | Scan, I/O1, and I/O2 Sequence Data           |         |

|          |          | Flow Block Diagram for ID Operations         |         |

|          |          | with ESA                                     | 2-393   |

|          | 2-503.   | Scan, I/O1 and I/O2 Essential Commands       |         |

|          |          | for ID Operations with ESA                   | 2-393   |

| 2-504.   | -        | Data Request Operations without ESI or ESA   | 2-397   |

|          | 2-505.   | Single-Channel Operation                     | 2 - 397 |

|          | 2-508.   | Dual-Channel Operation                       | 2-397   |

|          | 2-510.   | Scan and I/O Sequence Data Flow for          |         |

|          |          | Single-Channel Operation                     | 2-399   |

|          | 2-511.   | Scan and I/O-Sequence Data Flow for          |         |

|          |          | Dual Channel Operation                       | 2-400   |

|          | 2-512.   | Scan, I/O1, I/O, and I/O2 Sequence           |         |

|          |          | Essential Commands for Dual-Channel          |         |

|          |          | OD Operations                                | 2-400   |

|          | 2-513.   | OD Acknowledge Timing                        | 2-409   |

| 2-515.   | Output   | Data Request Operations with ESI             | 2-417   |

| Chapt | ce | $\mathbf{r}$ |

|-------|----|--------------|

|-------|----|--------------|

|        | 2-517.    | Scan and I/O-Sequence Data Flow for        |         |

|--------|-----------|--------------------------------------------|---------|

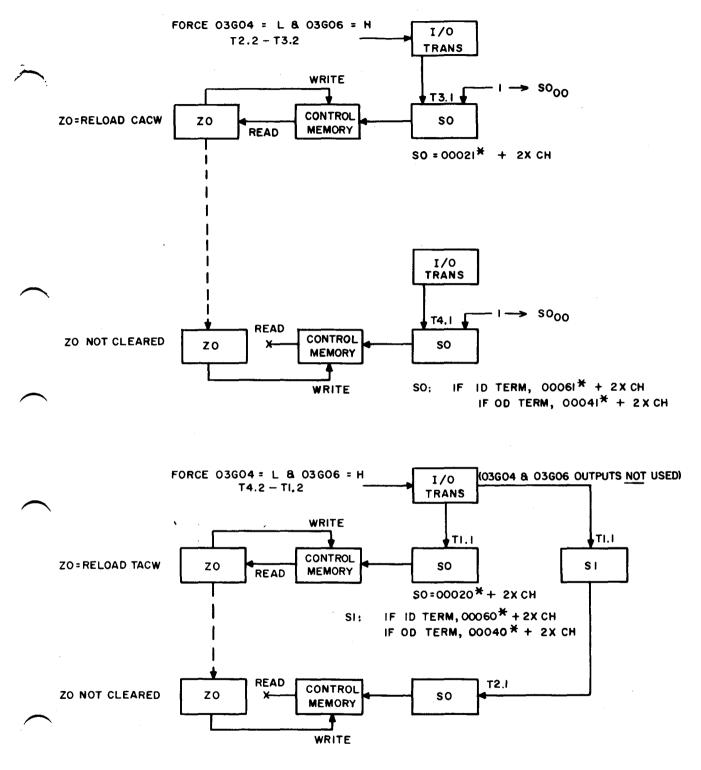

|        |           | OD Operations with ESI (Not Buffer         |         |

|        |           | Termination)                               | 2-417   |

|        | 2-519.    | I/O2 Sequence Data Flow (Buffer            |         |

|        | •         | Termination)                               | 2-418   |

| 2-521. | Output I  | Data Request Operations with ESA           | 2-423   |

|        | 2-522.    | Scan, I/O1, and I/O2 Sequence Data Flow    |         |

|        |           | for OD Operations with ESA                 | 2-423   |

|        | 2-523.    | Scan, $I/O1$ and $I/O2$ Sequence Essential |         |

|        |           | Commands for OD Operations with ESA        | 2-424   |

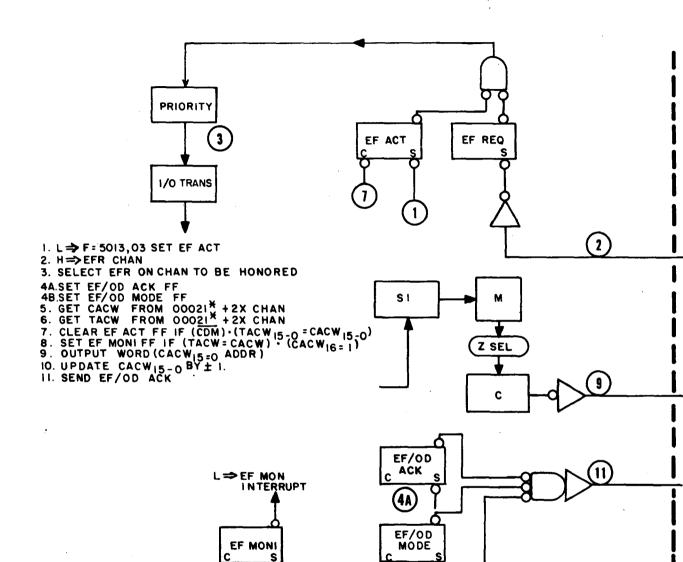

| 2-524. | Externa   | 1 Function Request Operations              | 2-429   |

|        | 2-525.    | Single-Channel EFR Operation without       |         |

|        |           | ESI or ESA                                 | 2-429   |

|        | 2-526.    | Dual-Channel EFR Operation without         |         |

|        |           | ESI or ESA                                 | 2-429   |

|        | 2-527.    | Scan and I/O1 Sequence Data Flow for       |         |

|        |           | Single-Channel Operation.                  | 2-429   |

|        | 2-528.    | Scan, I/01 and I/02 Sequence Data Flow for |         |

|        |           | Dual-Channel Operation.                    | 2-429   |

|        | 2-529.    | Scan, I/O1, and I/O2 Sequence Essential    |         |

|        |           | Commands for Single or Dual-Channel EF     |         |

|        |           | Operations                                 | 2-429   |

|        | 2-530.    | EF Acknowledge Timing                      | 2-437   |

|        | 2-531.    | Normal Mode EF Acknowledge Timing          | 2-437   |

|        | 2-532.    | Intercomputer Mode EF Acknowledge Timing . | 2-437   |

|        | 2-533.    | EF Operations with ESI                     | 2 - 437 |

|        | 2-534.    | I/O2 Sequence Data Flow for Terminate      |         |

|        |           | EF Operations with ESI                     | 2-437   |

|        | 2-535.    | Scan, I/O1 and I/O2 Sequence Data Flow     |         |

|        |           | for EF Operations with ESA                 | 2-437   |

| 2-536. | Continuo  | ous Data Mode Operations                   | 2-445   |

|        | 2-538.    | Continuous Data Mode Sequence Data Flow    | 2-445   |

|        | 2-539.    | CDM Sequence Essential Commands            | 2-446   |

| 2-540. | Executio  | on of OUTOV and EXFOV Instructions         |         |

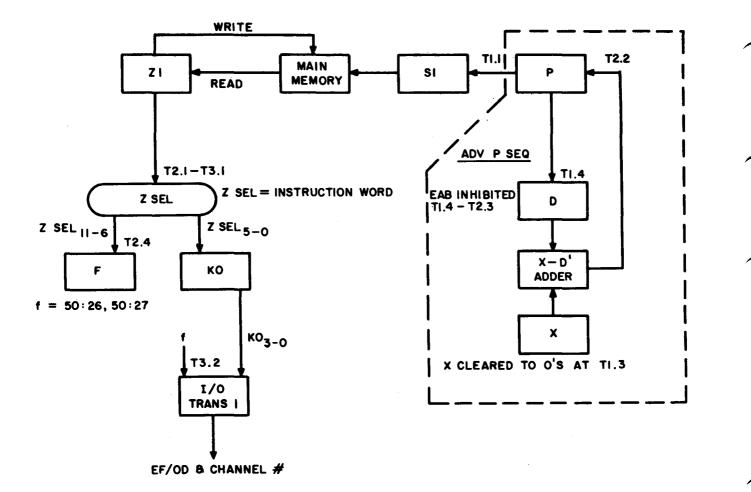

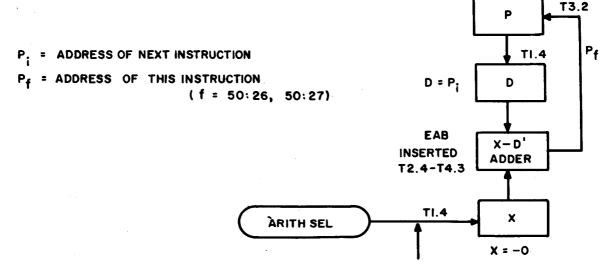

|        | (f= 50:26 | 3, 50:27)                                  | 2-451   |

|        | 2-541.    | I-Sequence Data Flow                       | 2-451   |

|        | 2-542.    | First I-Sequence Essential Commands        | 2-451   |

|        | 2-543.    | Remaining Sequences with Output Available  |         |

|        |           | and No Resume-Fault                        | 2-451   |

CHANGE 7 xiii

#### TABLE OF CONTENTS (Cont)

Chapter

Page

|        | 2-544.  | Sequences After First I-Sequence Essential |         |

|--------|---------|--------------------------------------------|---------|

|        |         | Commands with Output Available and No      |         |

|        |         | Resume-Fault                               | 2 - 451 |

|        | 2-545.  | Remaining Sequences with Output Not        |         |

|        |         | Available and No Resume-Fault              | 2-451   |

|        | 2-546.  | Sequence After First I-Sequence Essential  |         |

|        |         | Commands with Output Not Available and     |         |

|        |         | No Resume-Fault                            | 2-452   |

|        | 2-547.  | Remaining Sequences with Resume-Fault      | 2 - 452 |

|        | 2-548.  | Sequences After First I-Sequence Essential |         |

|        |         | Commands with Resume-Fault                 | 2-452   |

|        | 2-549.  | Decrement P Data Flow                      | 2-459   |

| 2-550. | Executi | on of SKPIIN, SKPOIN, SKPFIN, SKPNR,       |         |

|        | SRSM L  | nstructions                                | 2-459   |

|        | 2-551.  | SKPIIN (f= 50:21)                          | 2 - 459 |

|        | 2-552.  | SKPOIN (f= 50:22)                          | 2-459   |

|        | 2-553.  | SKPFIN (f= 50:23)                          | 2-459   |

|        | 2-554.  | SKPNR (f= $50:57$ )                        | 2-459   |

|        | 2-555.  | SRSM (f= $50:20$ )                         | 2-460   |

|        | 2-556.  | I-Sequence Data Flow for $f = 50:20$       |         |

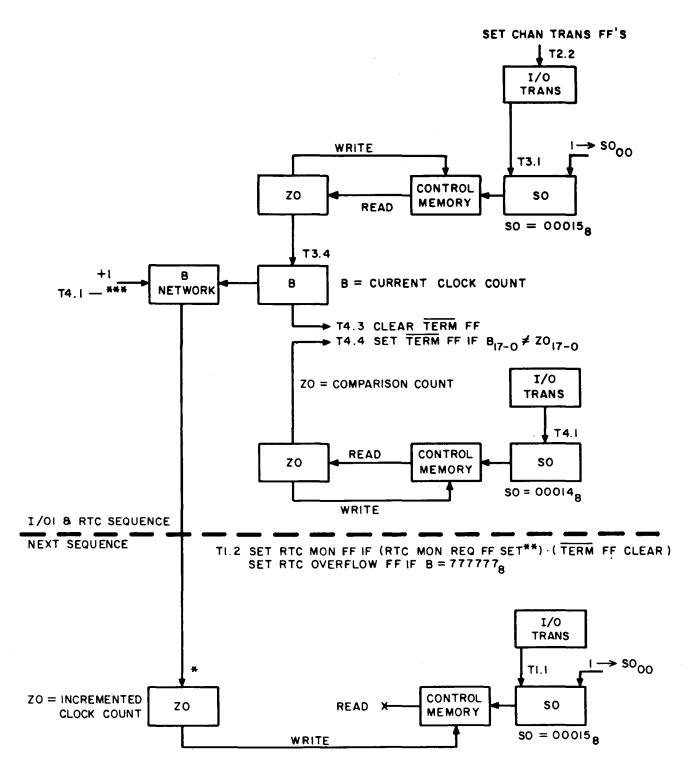

|        |         | through 50:23 and 50:57                    | 2 - 460 |

|        | 2-557.  | I-Sequence Essential Commands for          |         |

|        |         | f= 50:20 through 50:23 and 50:57           | 2-460   |

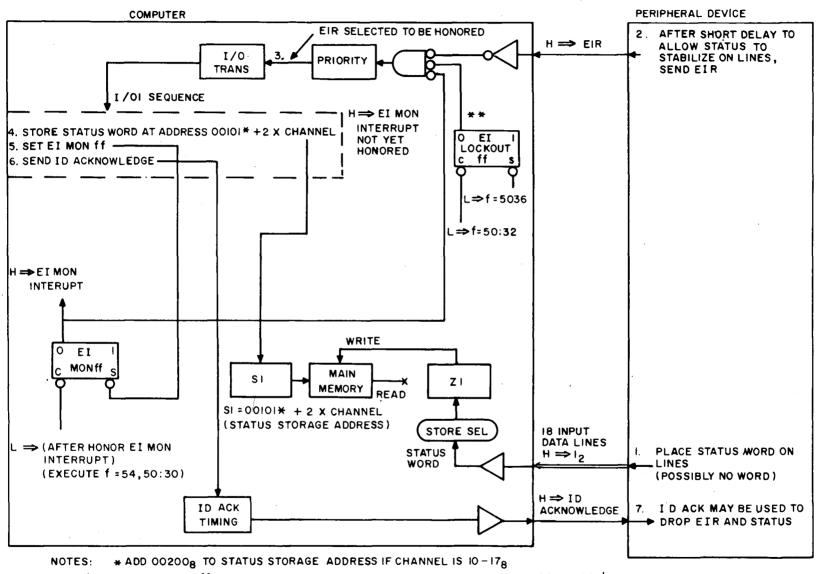

| 2-558. | Externa | al Interrupt Request Operations            | 2 - 465 |

|        | 2-559.  | Single-Channel Operation                   | 2 - 465 |

|        | 2-560.  | Dual-Channel, ESI, or ESA Operation        | 2-465   |

|        | 2-561.  | I/O1 and I/O2 Sequence Data Flow for       |         |

|        |         | EIR Operations                             | 2 - 465 |

|        | 2-562.  | Scan and I/O2 Sequence Essential           |         |

|        |         | Commands for EIR Operations                | 2-465   |

| 2-563. | Real-T  | ime-Clock (RTC) Request Operations,        |         |

|        | Genera  | tion of RTC Monitor Interrupts, and        |         |

|        | Executi | on of RTC Instructions                     | 2-471   |

|        | 2-565.  | RTC Overflow Interrupt                     | 2-471   |

|        | 2-566.  | RTC Request Operations Data Flow           | 2-471   |

|        | 2-567.  | RTC (f= 50:14) Instruction $\ldots$        | 2-472   |

|        | 2-568.  | I/O1, RTC and Next Sequence Essential      |         |

|        |         | Commands for RTC Operations                | 2 - 472 |

#### TABLE OF CONTENTS (Cont)

RIL (f = 50:30)

EXL (f= 50:32)

SIL (f = 50:34)

**RTC** Monitor

SXL (f = 50:36)

Execution of RIL, EXL, SIL, SXL, WTFI, and

Special and Monitor Interrupt Operations Instructions. .

Special and Monitor Interrupt Operations .....

Resume-Fault (Intercomputer Time-

Execution Sequences .....

RIL, EXL, SIL, SXL Operations .....

Instruction Fault .....

Out Fault) ......

#### Chapter

2 - 569.

2 - 570.

2 - 571.

2 - 572.

2 - 573.

2 - 574.

2 - 575.

2 - 576.

2-577.

2-579.

2 - 580.

2 - 581.

2-602.

2 - 578.

|        | 2-582.   | External Sync                           |

|--------|----------|-----------------------------------------|

|        | 2-583.   | RTC Overflow                            |

|        | 2-584.   | External Interrupt Monitor (EI Mon)     |

|        | 2-585.   | External Function Monitor (EF Mon)      |

|        | 2-586.   | Output Data Monitor (OD Mon)            |

|        | 2-587.   | Input Data Monitor (ID Mon)             |

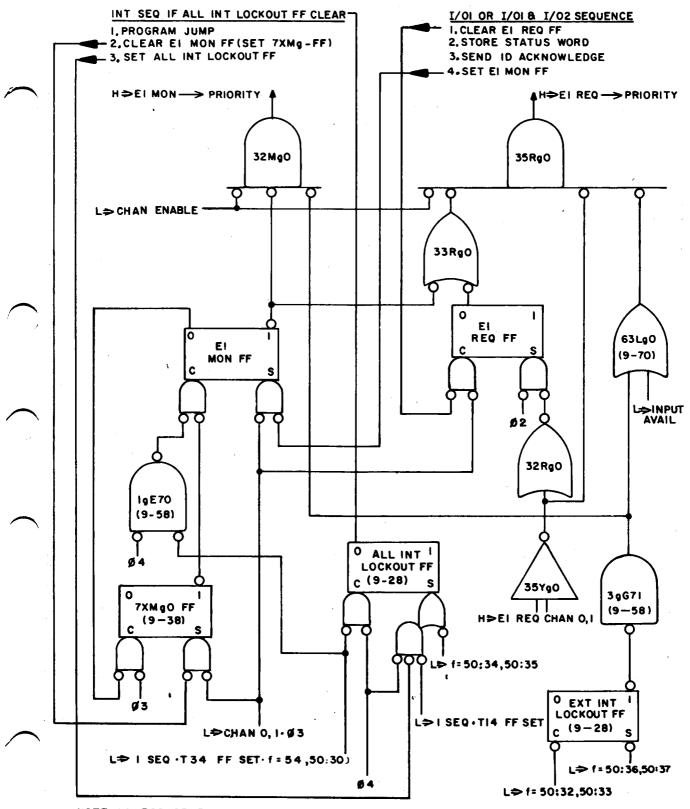

|        | 2-588.   | Honoring Operations                     |

|        | 2-59Ź.   | Special Interrupt Translator            |

|        | 2-593.   | Interrupt/I-Sequence Data Flow          |

|        | 2-594.   | Scan and Interrupt/I-Sequence Essential |

|        |          | Commands                                |

|        | 2-595.   | EI Monitor Operations                   |

|        | 2-596.   | EI Monitor Operation Essential Commands |

| 2-597. | Interco: | mputer Operations                       |

|        | 2-598.   | Intercomputer Channels                  |

|        | 2-599.   | External Function/External Interrupt    |

|        |          | Exchange                                |

|        | 2-600.   | Data Exchange                           |

|        | 2-601.   | ODR Logic                               |

Section 2-3. Detailed Functional Description (Power Distribution)

2 - 603.

Resume Fault Interrupt .....

2 - 477

2 - 477

2 - 477

2 - 477

2 - 477

2 - 477

2 - 477

2 - 477

2 - 478

2 - 478

2 - 478

2 - 478

2 - 478

2 - 478

2 - 478

2 - 478

2 - 4782 - 478

2 - 478

2 - 478

2 - 480

2 - 480

2 - 480

2 - 487

2 - 487

2 - 487

2 - 487

2 - 487

2 - 487

2 - 488

2 - 488

xv

### TABLE OF CONTENTS (Cont)

### Chapter

|    |        | 2-604.<br>2-605.<br>2-606. | GeneralPower Control CircuitMain DC Power Supply and Distribution2-60715 VDC Supply2-608.+15 VDC Supply2-611.±4.5 VDC SupplyMain Memory Power Supply2-613.+6 VDC Power Supply2-614.+3 VDC Supply2-616.±15 VDC Supply | 2-491<br>2-491<br>2-491<br>2-492<br>2-492<br>2-492<br>2-492<br>2-492<br>2-492<br>2-492<br>2-493 |              |

|----|--------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------|

|    |        | 0 010                      | 2-6174.5/-3 VDC Supply                                                                                                                                                                                               | 2-493                                                                                           |              |

|    |        | 2-618.                     | Miscellaneous Circuits                                                                                                                                                                                               | 2-493                                                                                           |              |

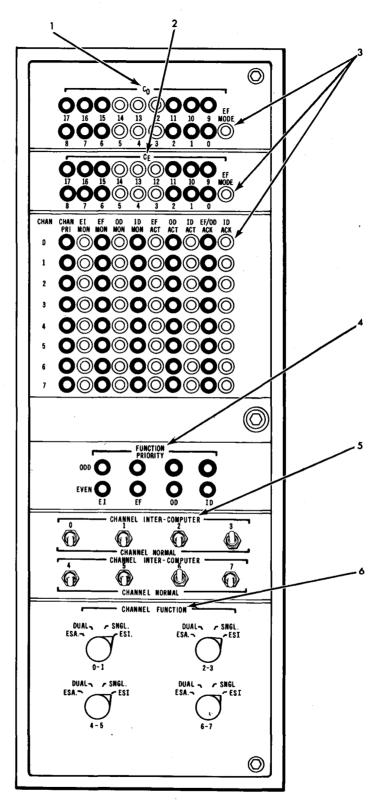

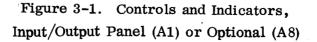

| 3. | OPERA? | rion                       |                                                                                                                                                                                                                      | 3-1                                                                                             |              |

|    | 3-1.   | General L                  | nformation                                                                                                                                                                                                           | 3-1                                                                                             |              |

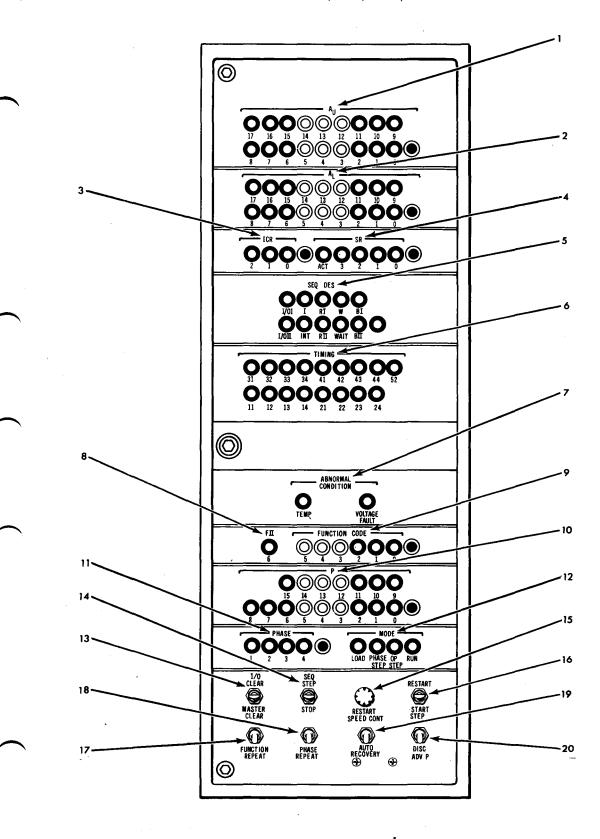

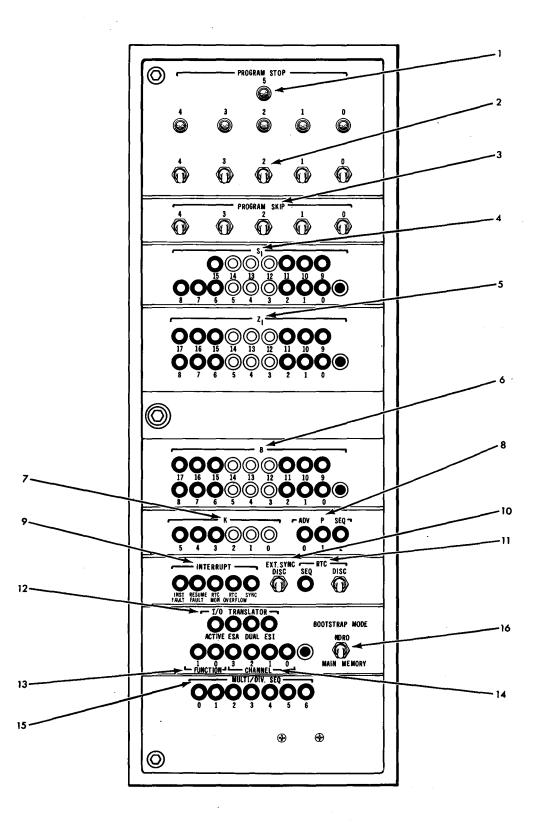

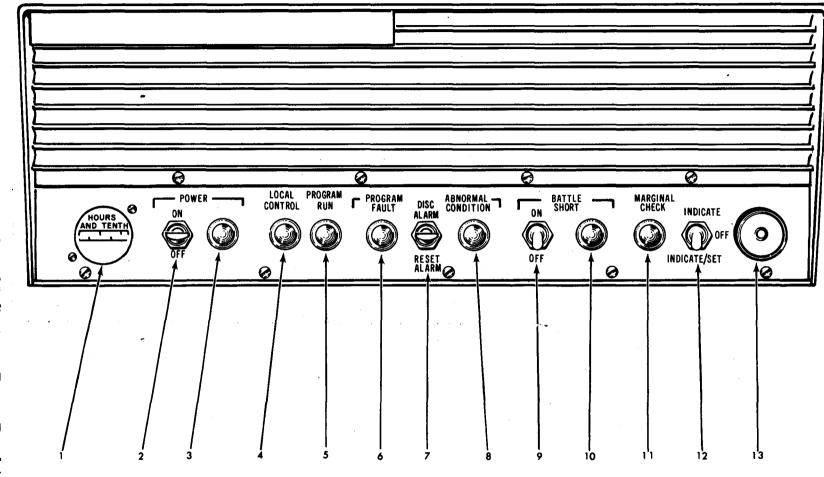

|    | 3-5.   | Controls a                 | and Indicators                                                                                                                                                                                                       | 3-1                                                                                             |              |

|    | 3-9.   | Daily Tur                  | n-On                                                                                                                                                                                                                 | 3-25                                                                                            |              |

| 4. | INSTAL | LATION                     | •••••••••••••••••••••••••••••••••••••••                                                                                                                                                                              | 4-1                                                                                             |              |

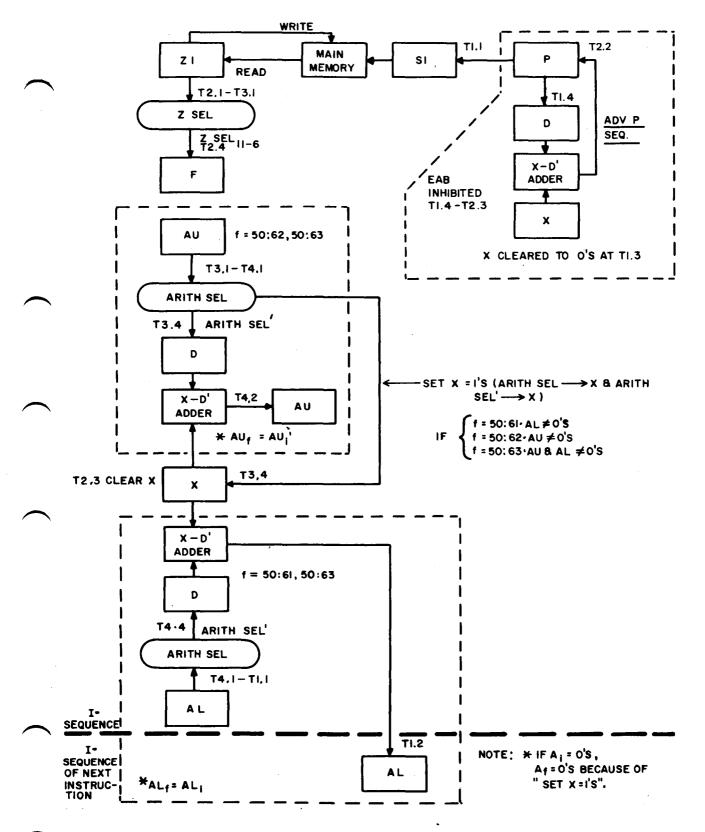

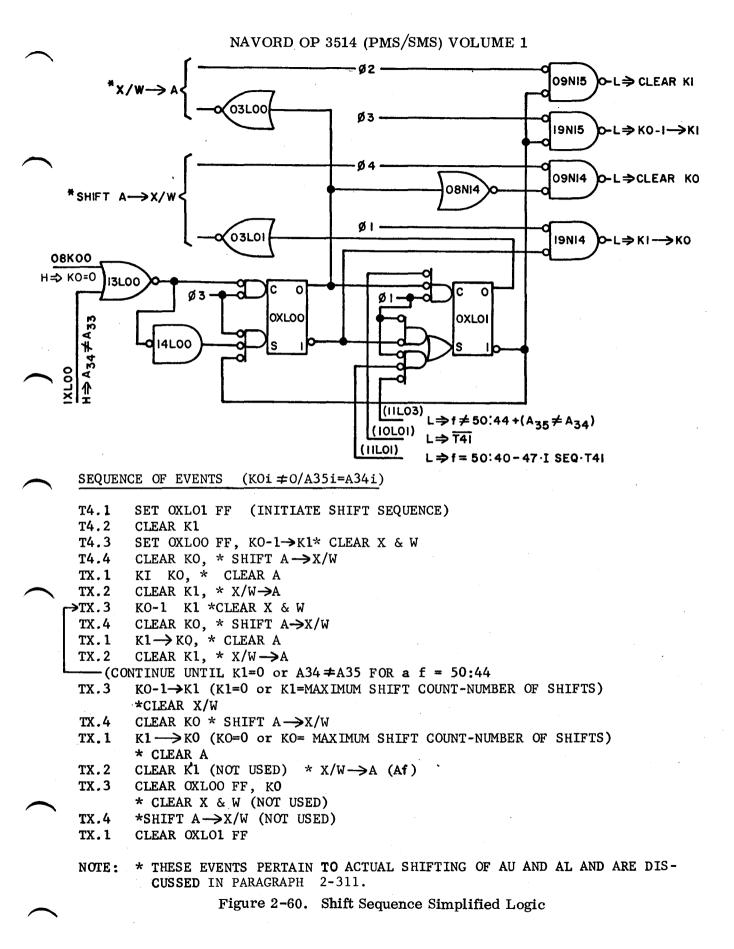

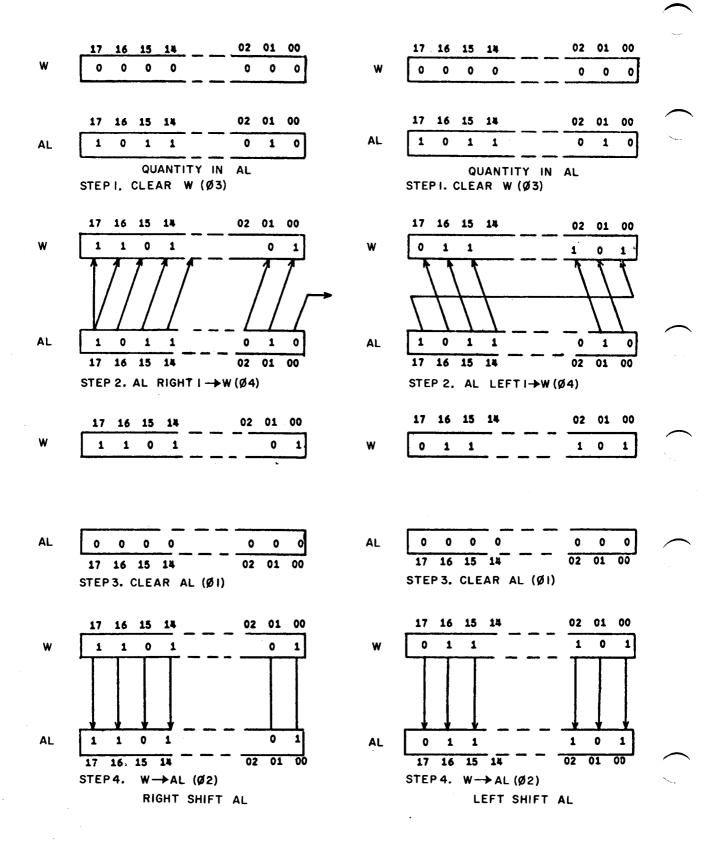

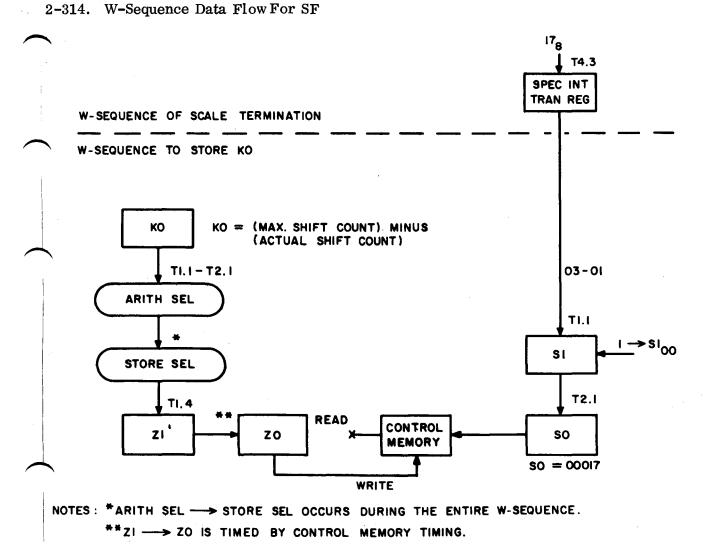

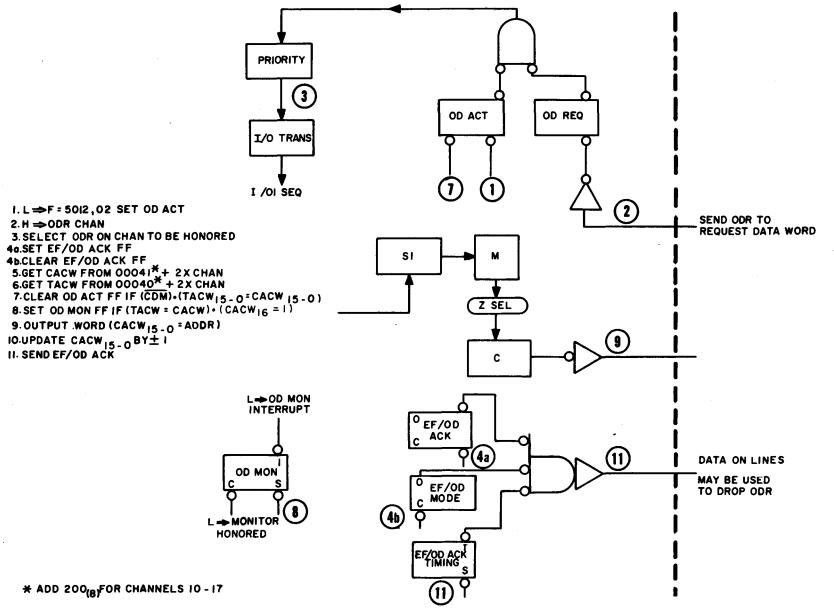

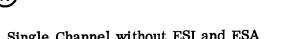

|    | 4-1.   | Unpacking                  | Information                                                                                                                                                                                                          | 4-1                                                                                             |              |