## NAVSHIPS 0967-280-4030

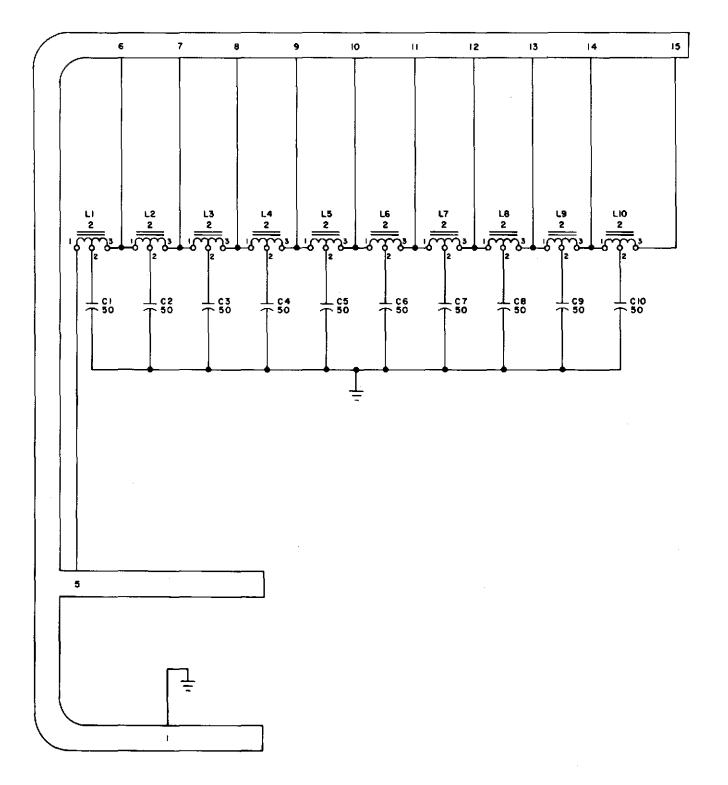

### **VOLUME III**

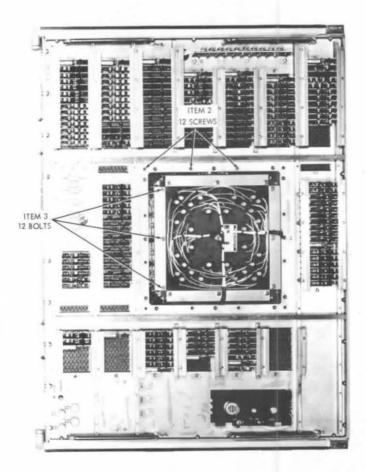

### **TECHNICAL MANUAL**

### for

# DIGITAL DATA COMPUTER CP-642B/USQ-20(V)

### **SECTIONS 5 THROUGH 7**

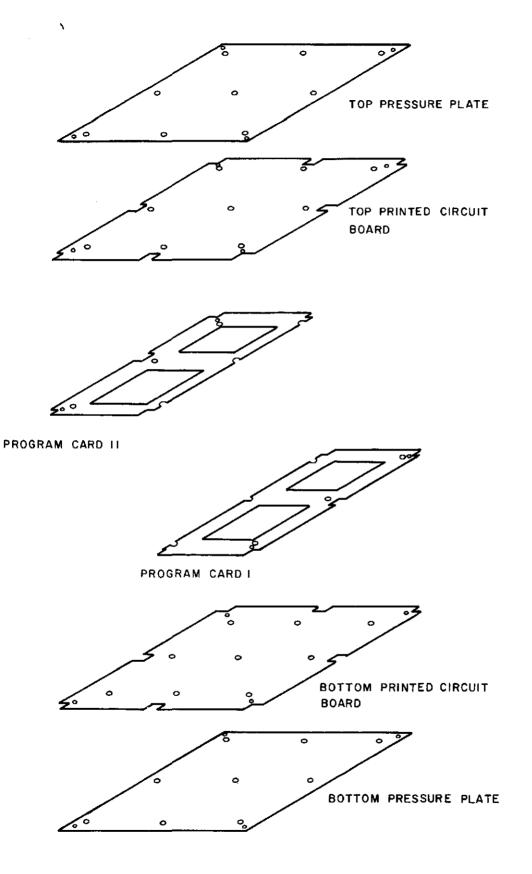

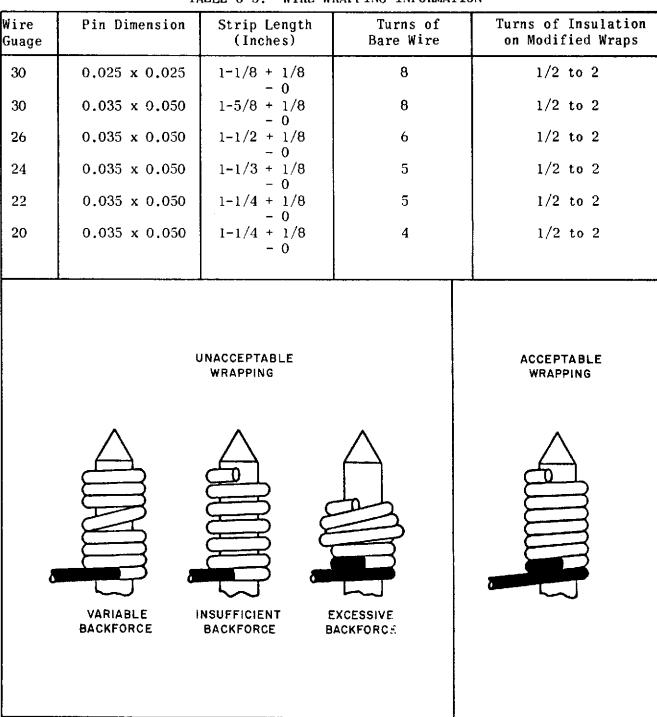

SYLVANIA ELECTRIC PRODUCTS, INC. SYLVANIA ELECTRONIC SYSTEMS NEEDHAM HEIGHTS, MASS.

## DEPARTMENT OF THE NAVY NAVAL SHIP SYSTEMS COMMAND

Contract: NObsr 93272

Approved 22 SEPT 1967

### LIST OF SECTIONS

| SECTI | ON                      | VOLUME |

|-------|-------------------------|--------|

| 1     | GENERAL INFORMATION     | I      |

| 2     | INSTALLATION            | I      |

| 3     | OPERATOR'S SECTION      | I      |

| 4     | PRINCIPLES OF OPERATION | 11     |

| 5     | TROUBLESHOOTING         | III    |

| 6     | REPAIR                  | III    |

| 7     | PARTS LIST              | III    |

| 8     | FUNCTIONAL SCHEMATICS   | IV     |

| 9     | WIRE TABULATIONS        | v      |

### SECTION 5

### TROUBLESHOOTING

### TABLE OF CONTENTS

### <u>Paragraph</u>

<u>Page</u>

| 5-1. | General                        | 5-1                                                                                                      |

|------|--------------------------------|----------------------------------------------------------------------------------------------------------|

| 5-2. |                                | uipment and Special Tools                                                                                |

| 5-3. |                                | roubleshooting                                                                                           |

|      | a. Gen                         | 5-4                                                                                                      |

|      |                                | ory Section Troubleshooting                                                                              |

|      | <u>~</u> . (1)                 | Main Memory Troubleshooting                                                                              |

|      | (2)                            | Control and Bootstrap Memory Troubleshooting                                                             |

|      | • •                            | 5-8                                                                                                      |

|      | <u>.</u> (1)                   | ECCLAT                                                                                                   |

|      | (2)                            | Memory ,                                                                                                 |

|      | (3)                            | Real-Time Clock Test         5-22                                                                        |

|      | (4)                            | Input/Output Test                                                                                        |

|      | (5)                            | Instruction Executive Time Tests                                                                         |

|      | (6)                            | Master Clock Margin Test $\dots$ |

|      | (7)                            | Console Control Nonlogic Tests                                                                           |

|      |                                | t Procedures $\ldots$   |

|      | $\underline{\mathbf{u}}$ . 105 | ECCLAT                                                                                                   |

|      | (2)                            | Memory Tests                                                                                             |

|      | (3)                            | Real-Time Clock Tests                                                                                    |

|      | (4)                            | Input/Output Exercise                                                                                    |

|      | (5)                            | Instruction Execution Time Test                                                                          |

|      | (6)                            | Master Clock Margin Test                                                                                 |

|      | (7)                            | Console Control Nonlogic Tests                                                                           |

| 5-4. | • • •                          | c Troubleshooting $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $5-36$                  |

| 0 11 |                                | er Supplies                                                                                              |

|      | (1)                            | Unregulated Input Power                                                                                  |

|      | (2)                            | Regulated Input Power                                                                                    |

|      | (3)                            | Main Power Supply                                                                                        |

|      | (4)                            | Console Power Supply                                                                                     |

|      | • •                            | sole Controls and Indicators                                                                             |

|      | (1)                            | Blower Power and Computer Power                                                                          |

|      | (2)                            | Overtemp Warning                                                                                         |

|      | $(\overline{3})$               | Local Control Indicators                                                                                 |

|      | (4)                            | Marginal Check Indicators                                                                                |

|      | (5)                            | Fault Indicator                                                                                          |

|      | (6)                            | Run Indicator                                                                                            |

|      | (7)                            | Master Clear                                                                                             |

|      | (8)                            | Run Mode                                                                                                 |

|      | (9)                            | Op Step Mode                                                                                             |

|      | (10)                           | Phase Step Mode                                                                                          |

|      | (11)                           | Load Mode                                                                                                |

|      | (12)                           | Automatic Recovery Switch                                                                                |

|      | (13)                           | Phase Repeat                                                                                             |

|      | (14)                           | Stop Switch                                                                                              |

|      | (15)                           | Start-Step/Restart Switch                                                                                |

|      |                                |                                                                                                          |

$\sim$  .

Contents

NAVSHIPS 0967-280-4030

CP-642B/USQ-20(V) COMPUTER

<u>Page</u>

### TABLE OF CONTENTS (CONT.)

### <u>Paragraph</u>

| (16) | Restart Speed Control     | -45  |

|------|---------------------------|------|

| (17) | Stop                      | 5-45 |

| (18) | Disconnect B7             | 5-45 |

| (19) | Disconnect ADV P          | 5-46 |

| (20) | Disconnect RTC            | 5-46 |

| (21) | Jumps                     | i-46 |

|      | Stops                     |      |

|      | C Register Switches       |      |

|      | Registers and Designators |      |

|      | Mašter Clock              |      |

|      |                           |      |

### LIST OF ILLUSTRATIONS

| <u>Figure</u> |                                                |   |  |   |   |  | <u>Page</u> |

|---------------|------------------------------------------------|---|--|---|---|--|-------------|

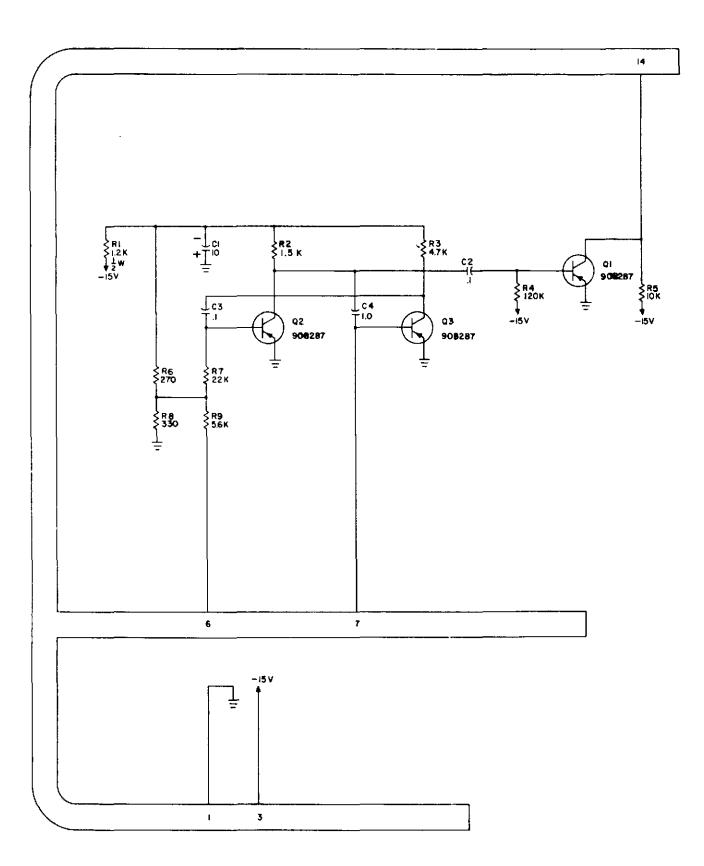

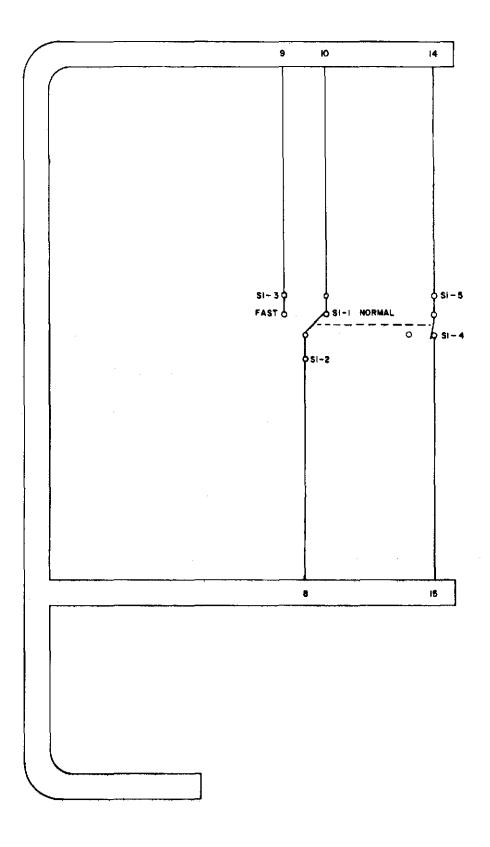

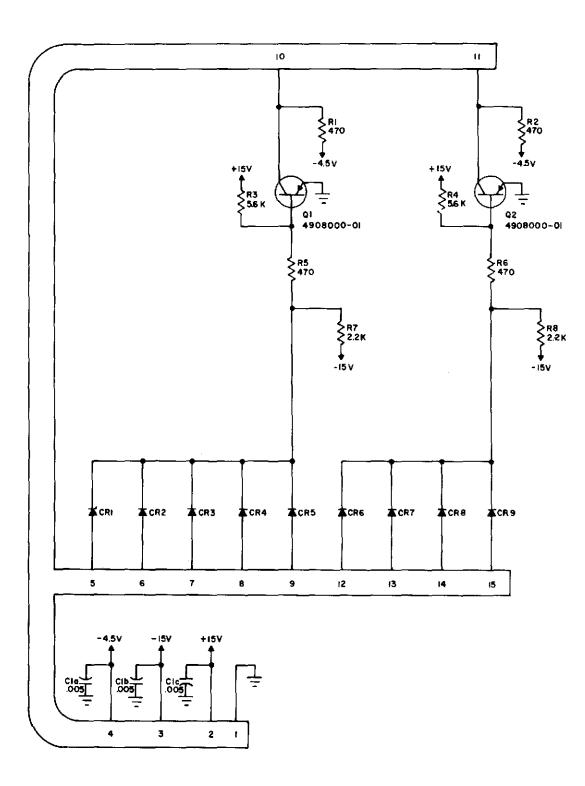

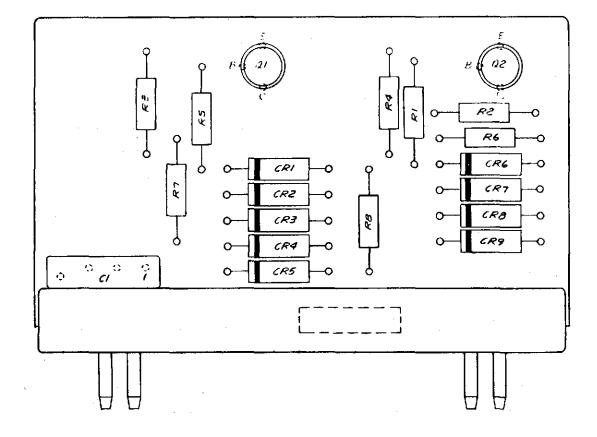

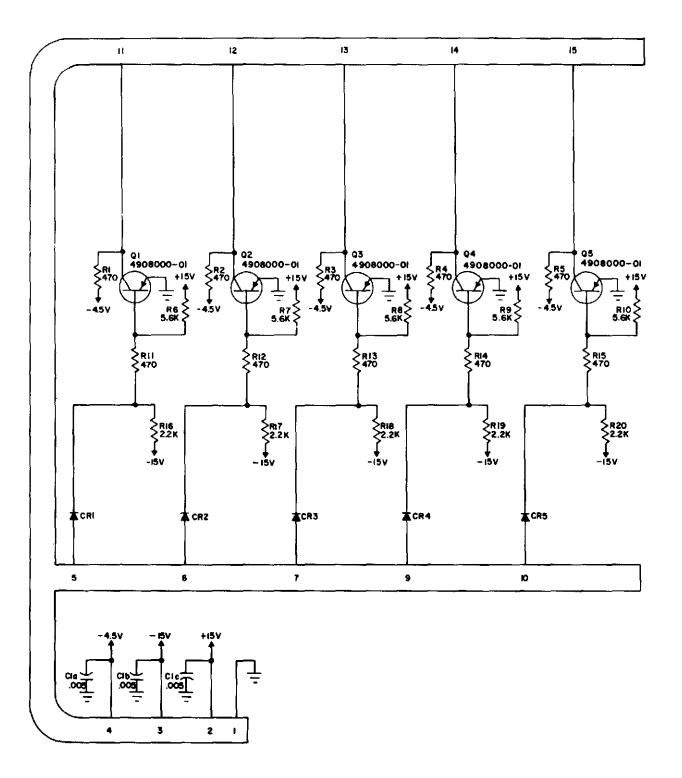

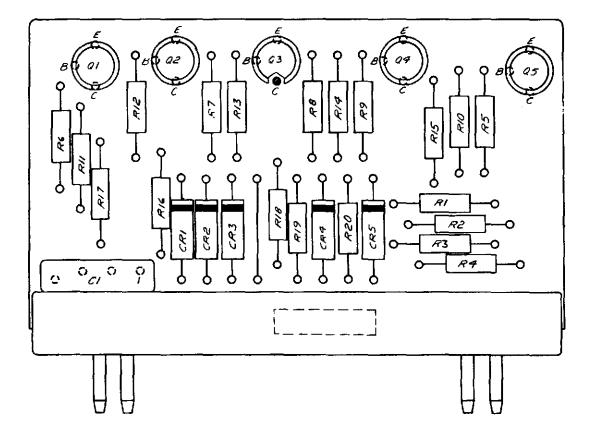

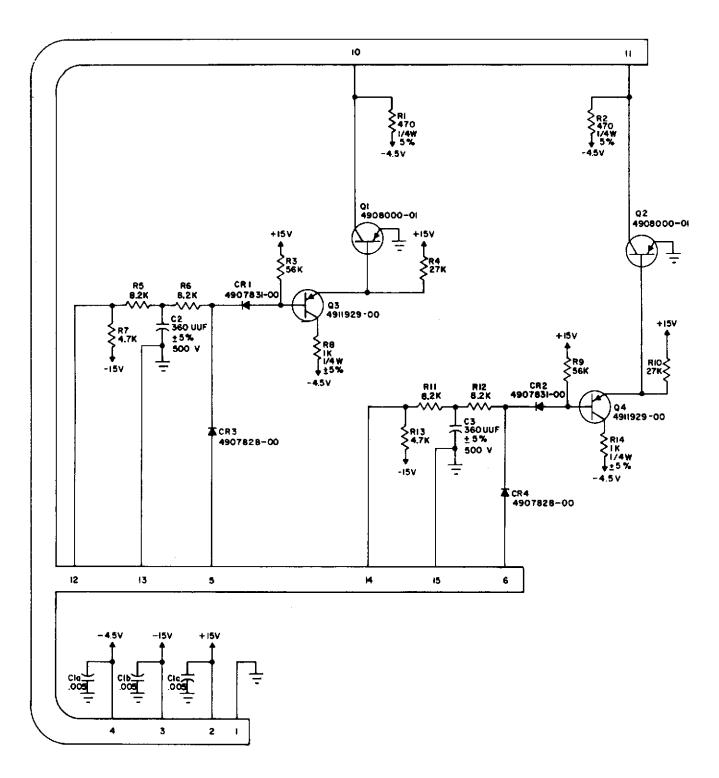

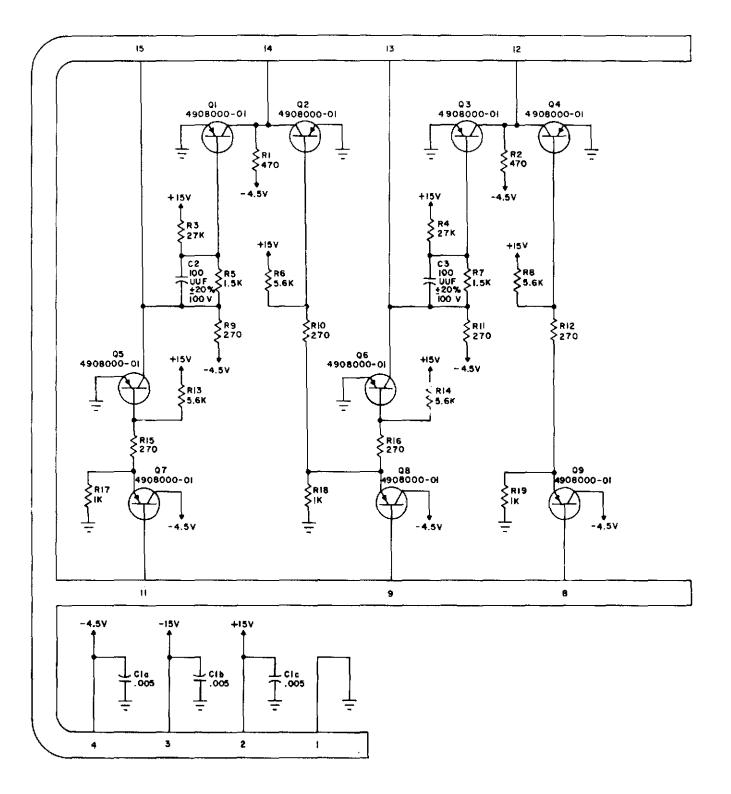

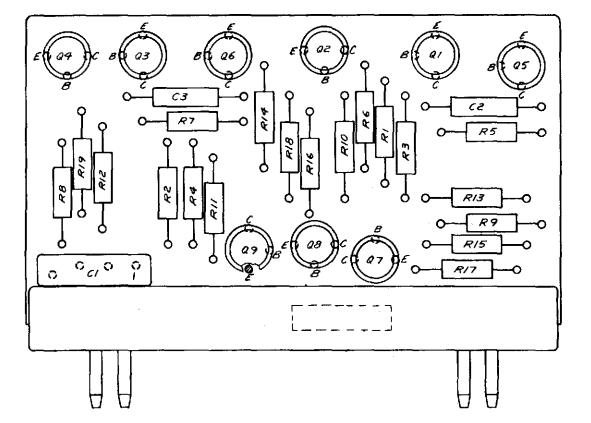

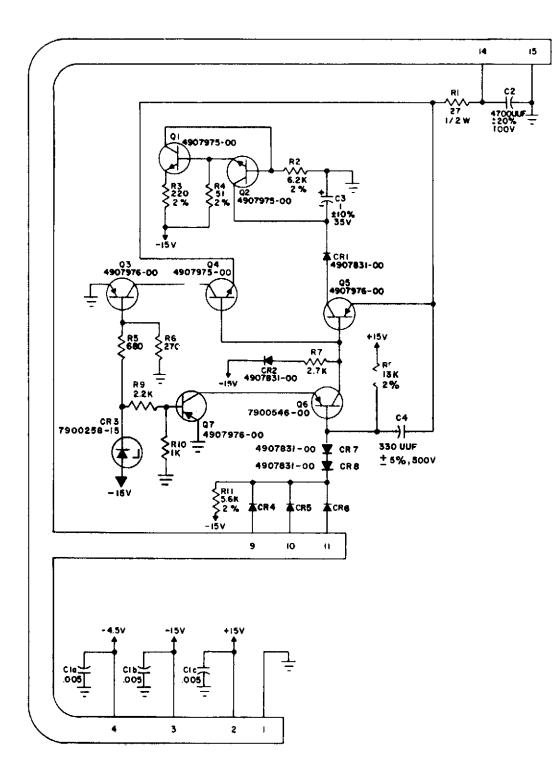

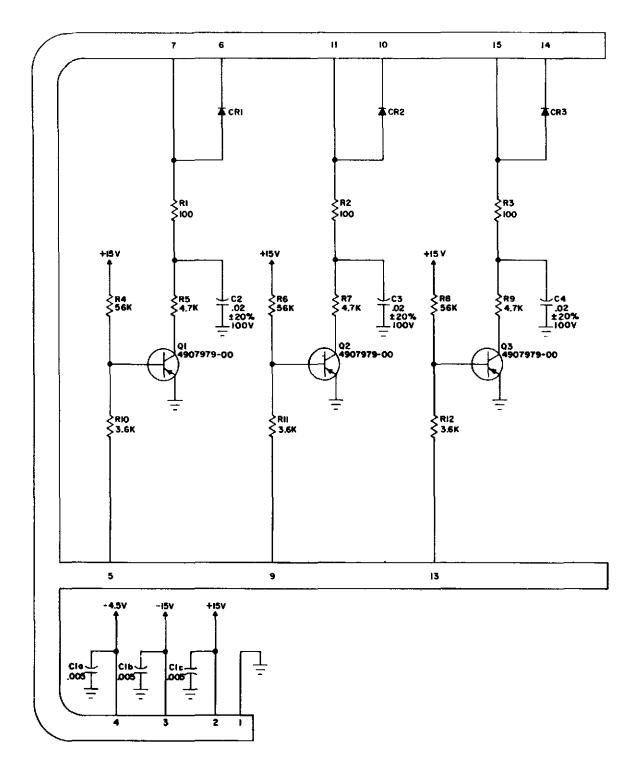

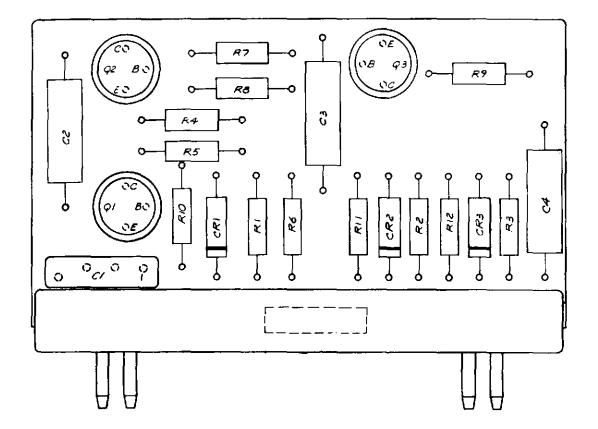

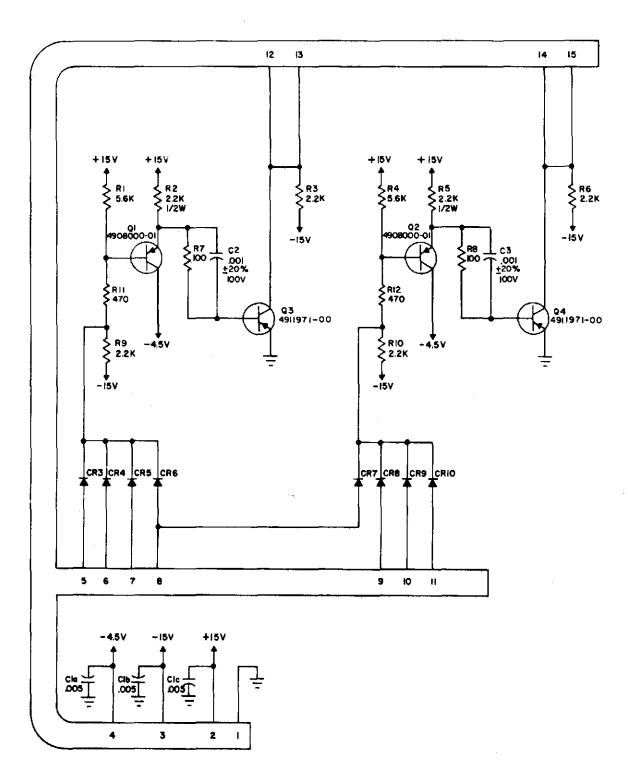

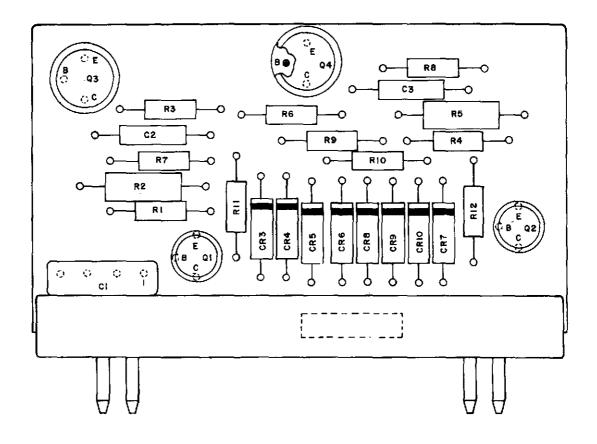

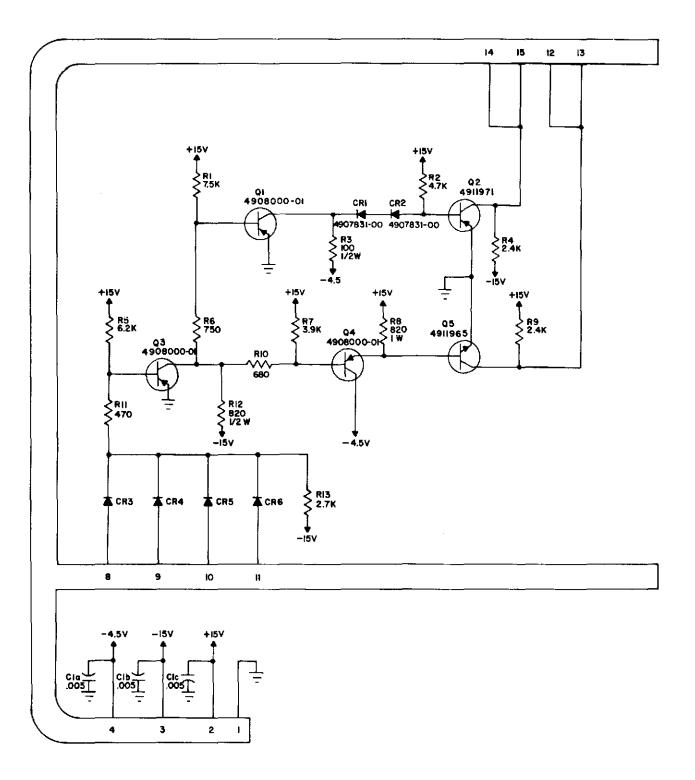

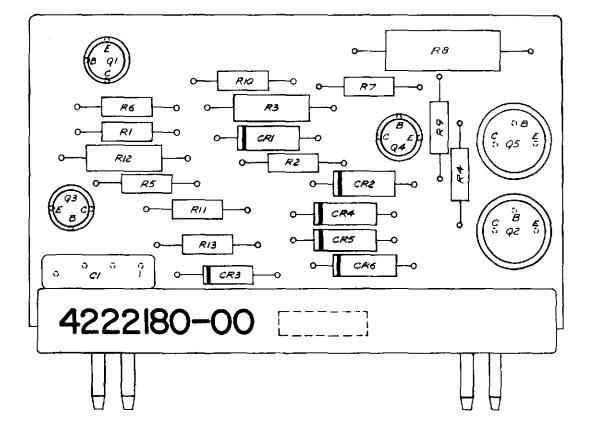

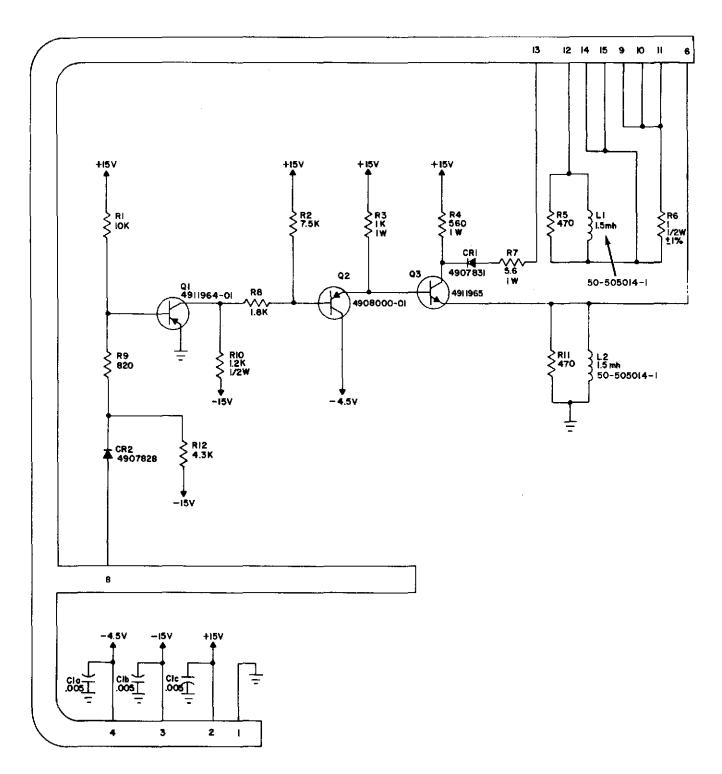

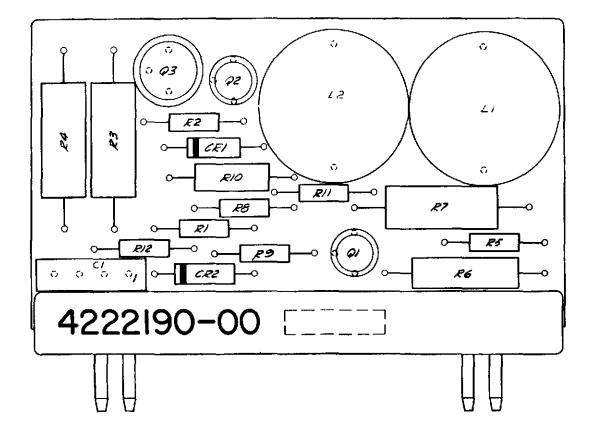

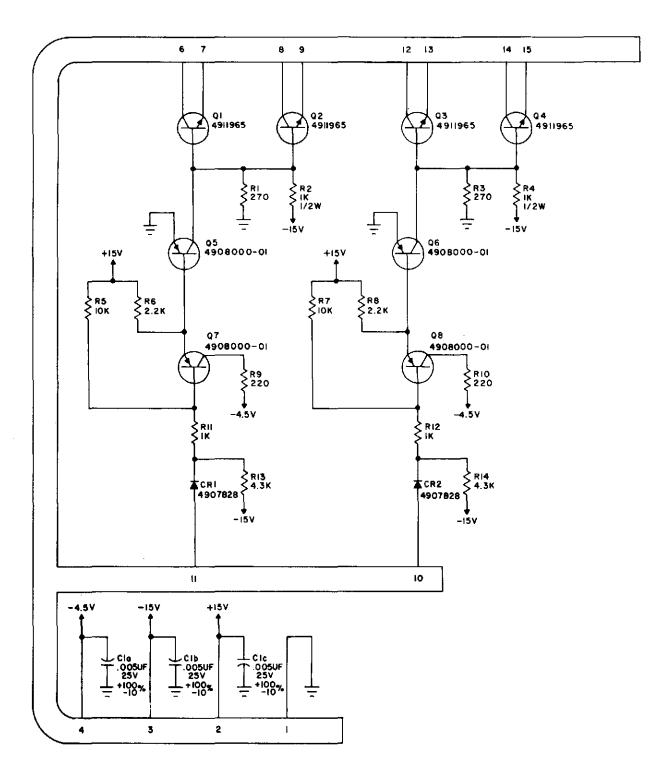

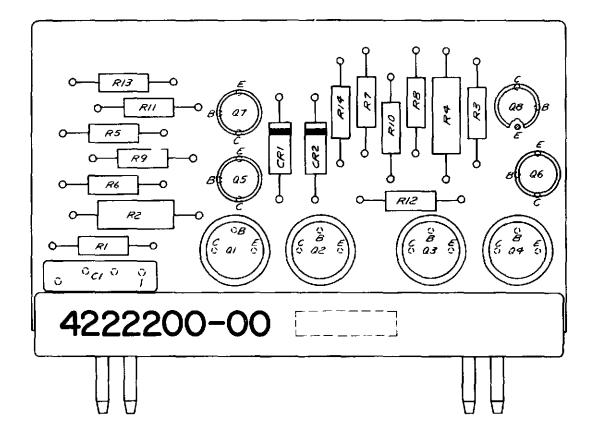

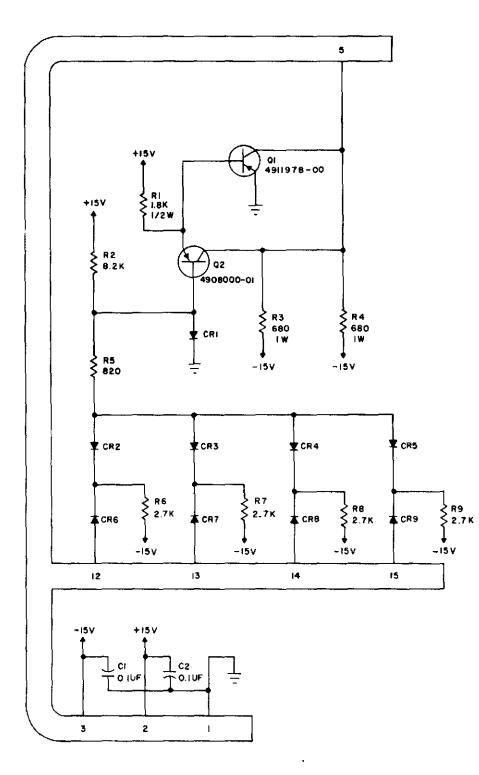

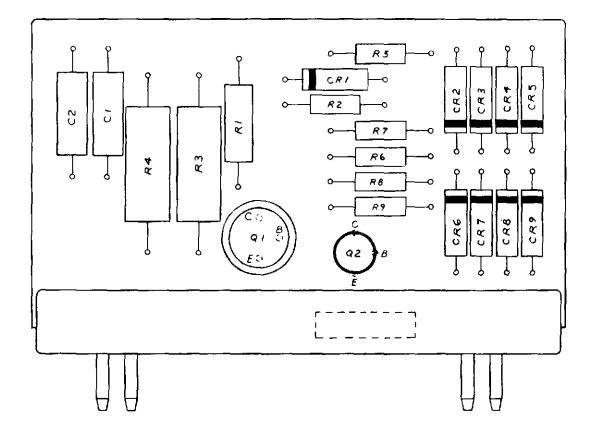

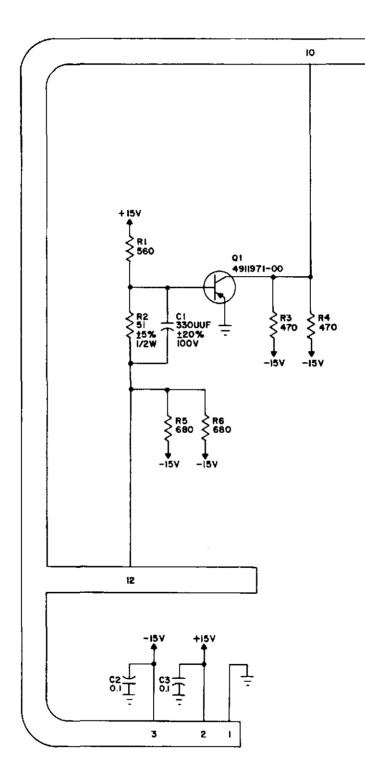

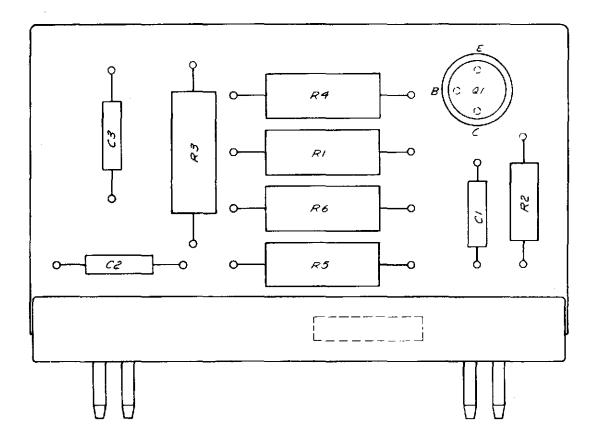

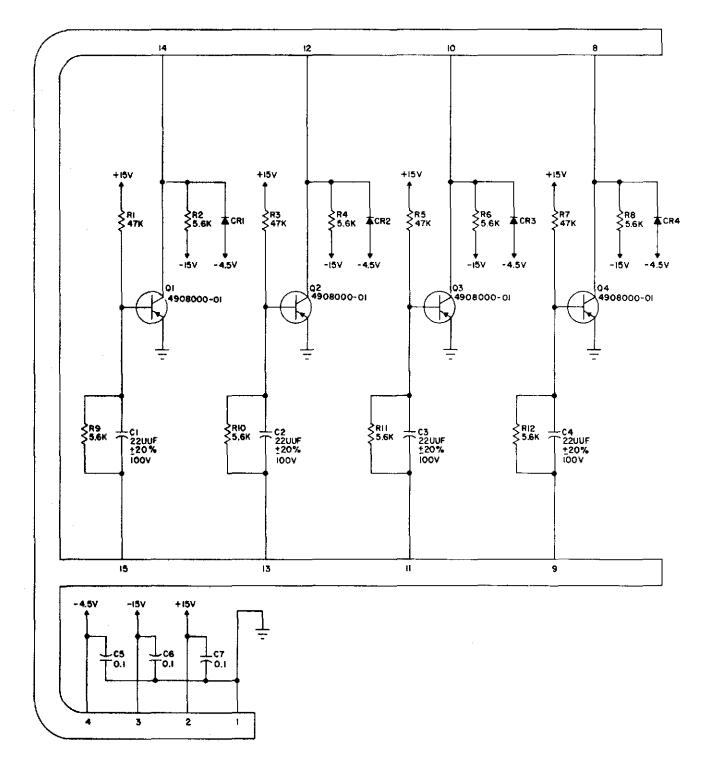

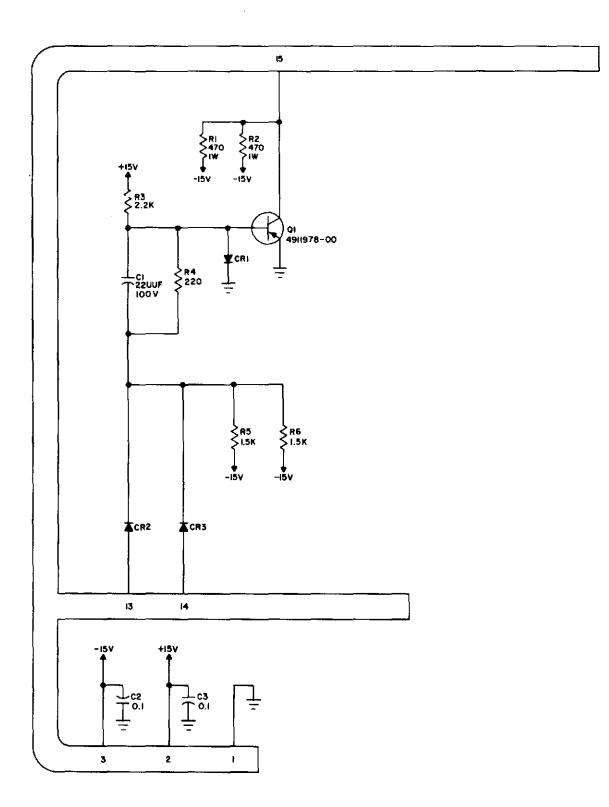

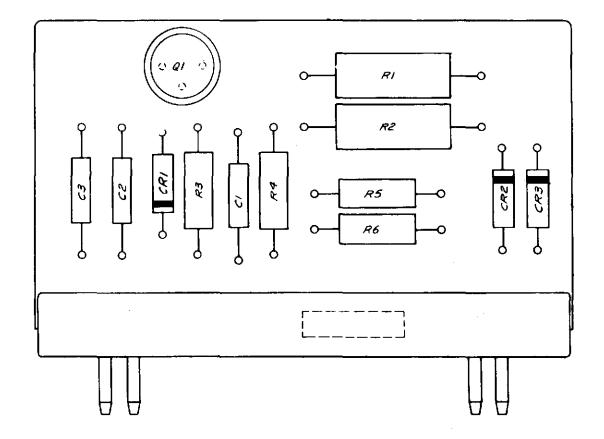

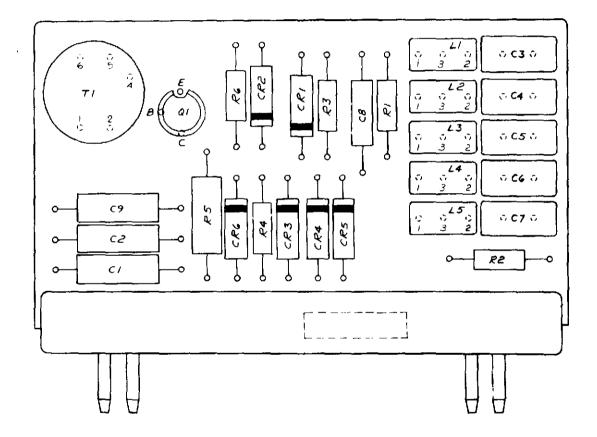

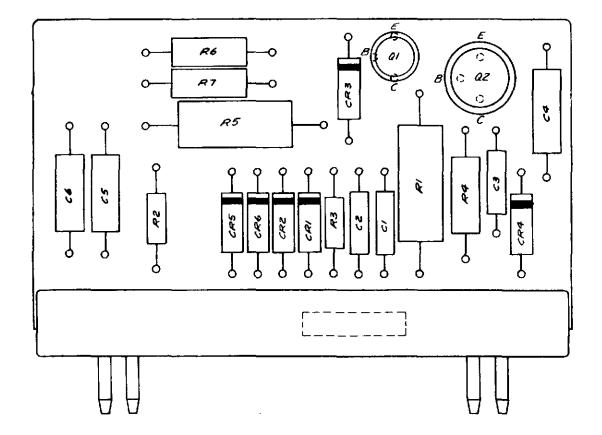

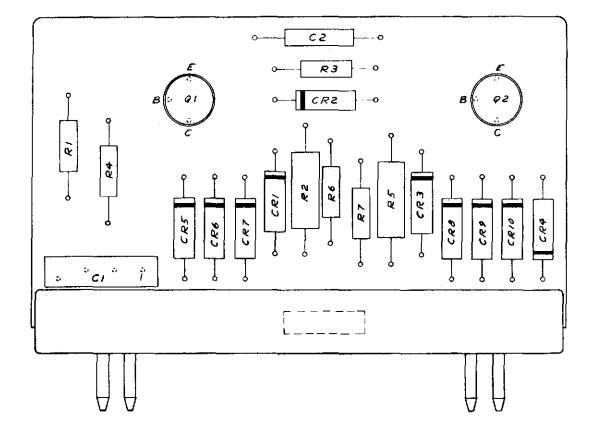

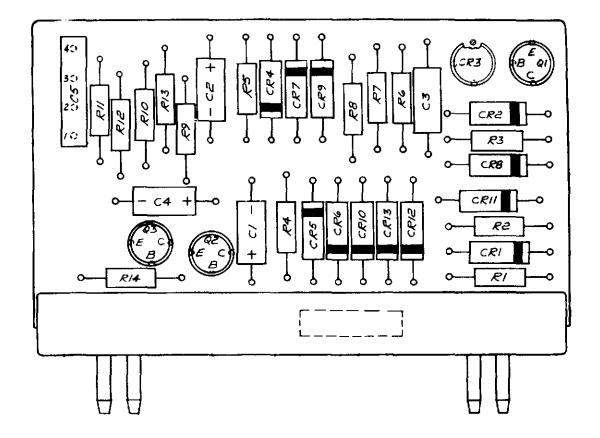

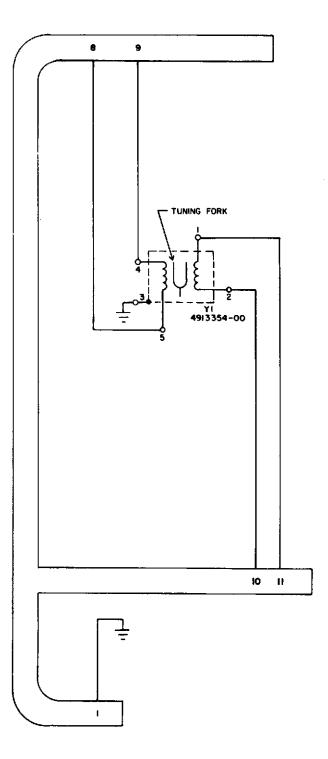

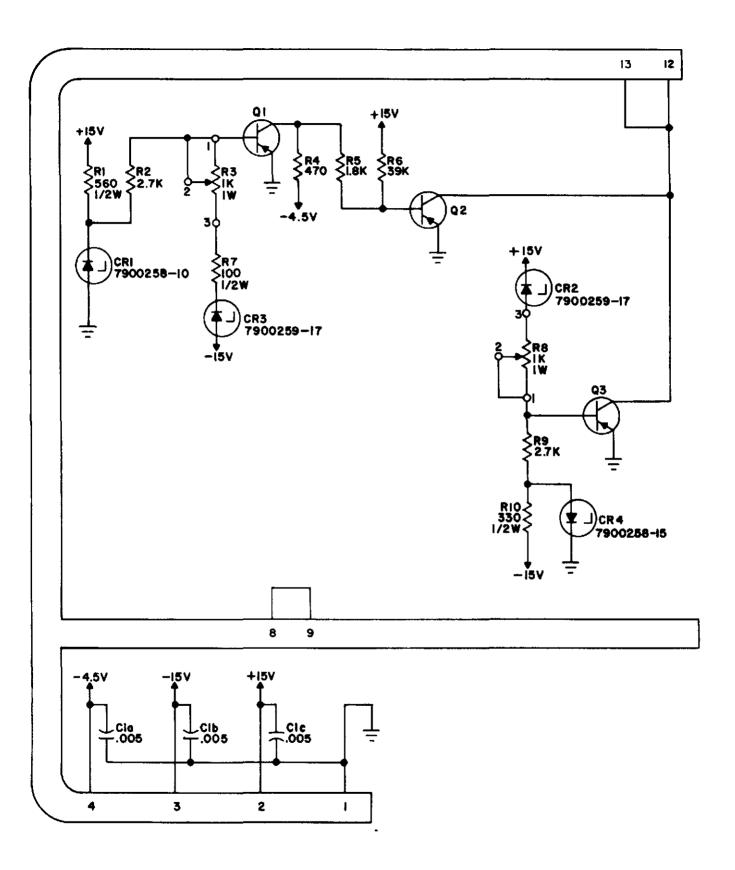

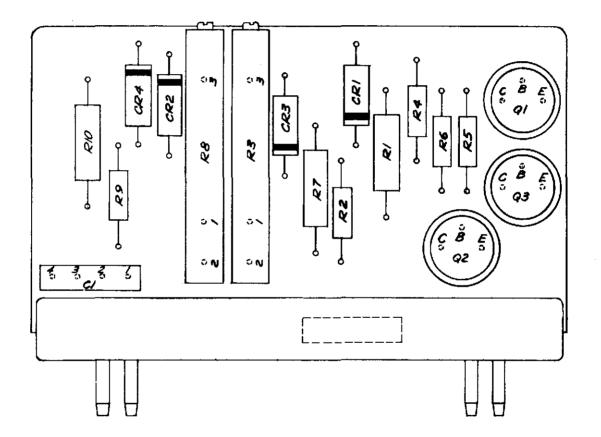

| 5-1.          | Module Extender Schematic                      | • |  | • |   |  | 5-2         |

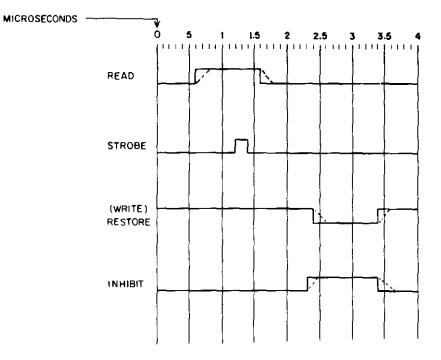

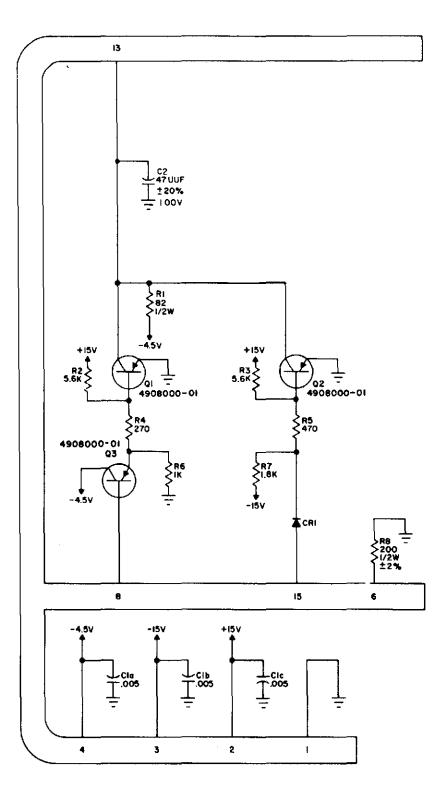

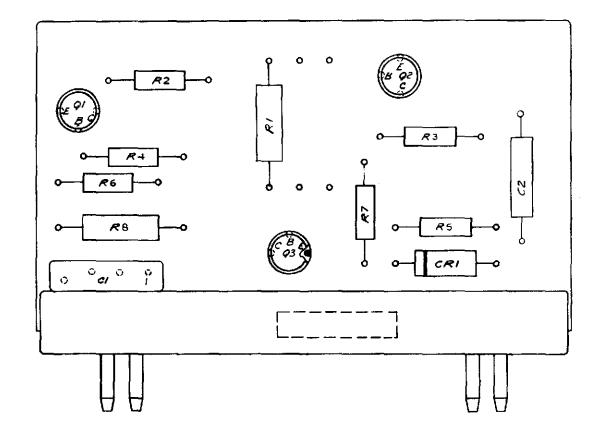

| 5-2,          | Memory Timing Cycle, Idealized Timing Waveform |   |  |   |   |  | 5-7         |

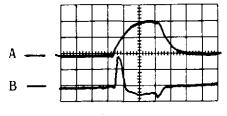

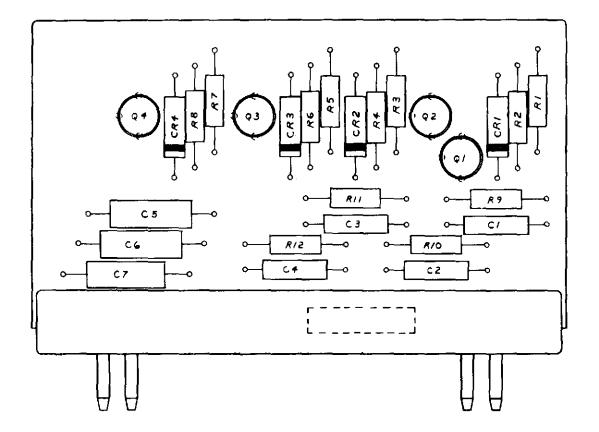

| 5-3.          | Main Memory, Typical Waveforms                 |   |  |   |   |  | 5-17        |

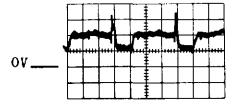

| 5-4.          | Main Memory, Abnormal Waveforms                |   |  |   |   |  | 5-19        |

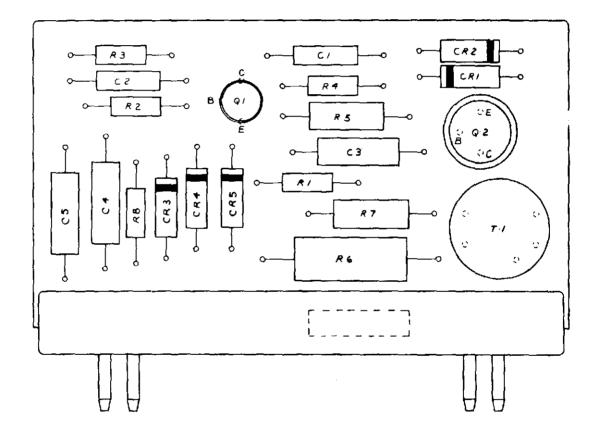

| 5-5.          | Control Memory Words, Diagram of Bit Locations |   |  |   |   |  | 5-20        |

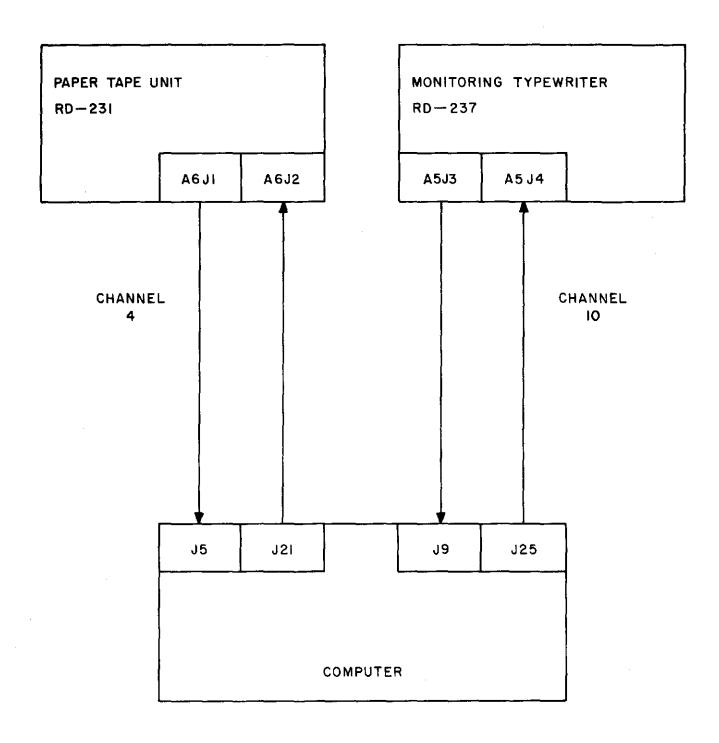

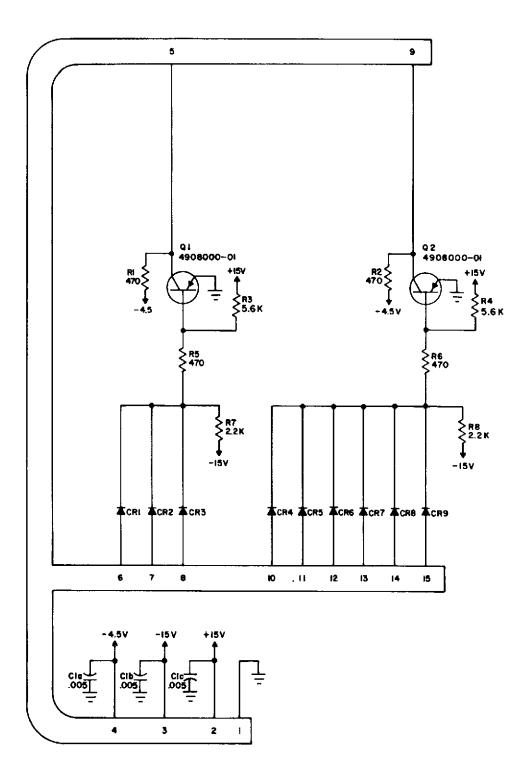

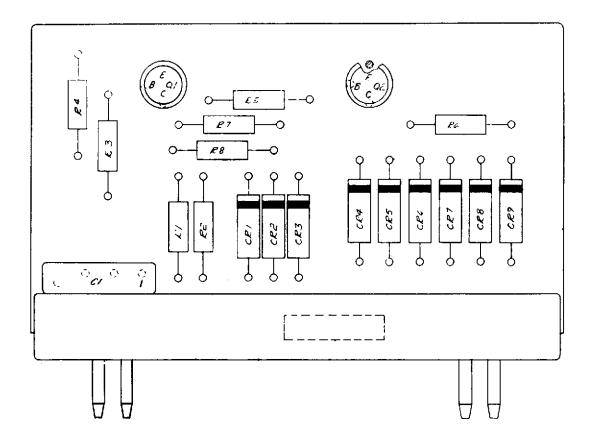

| 5-6.          | MROT Test Setup, Cabling Diagram               |   |  |   | • |  | 5-23        |

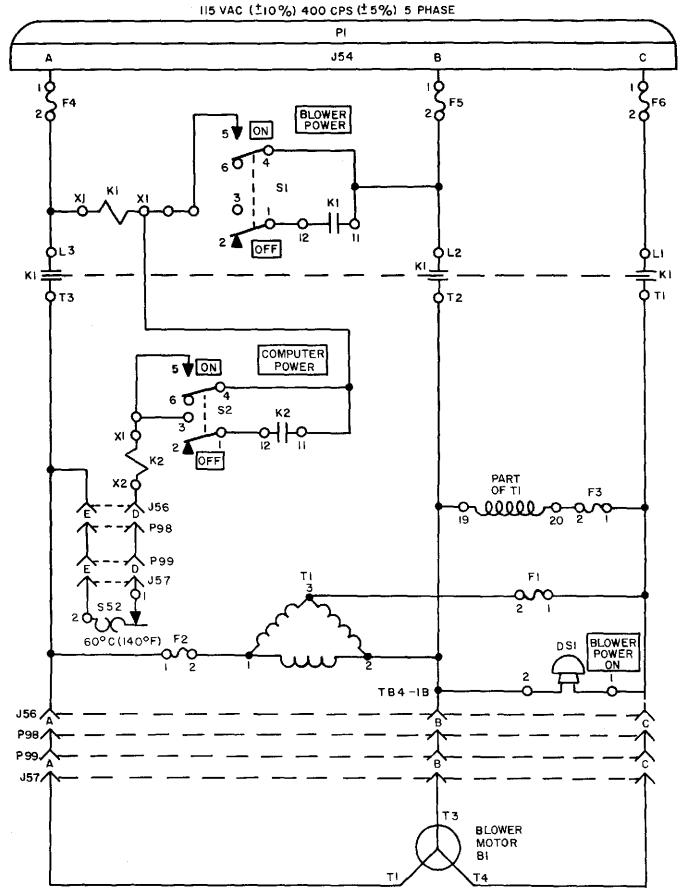

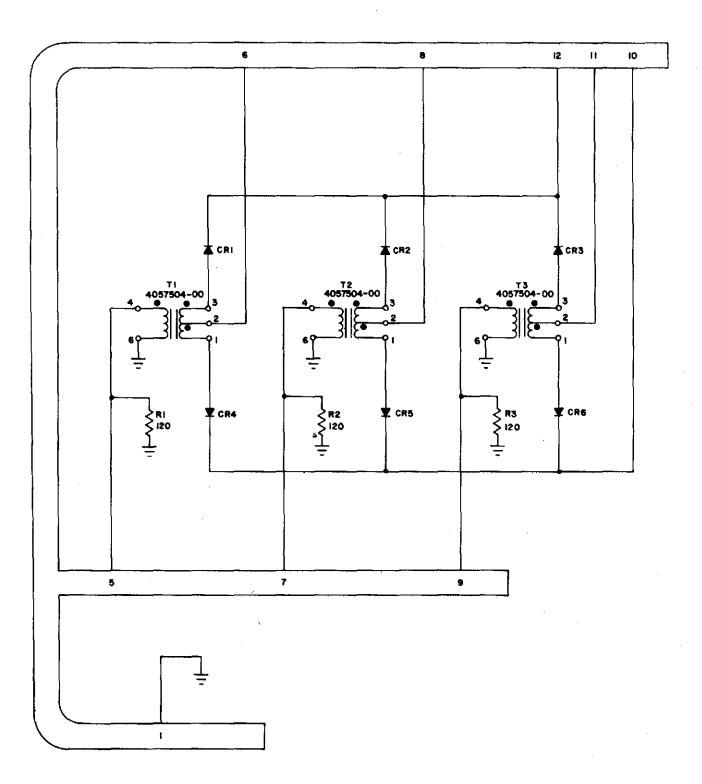

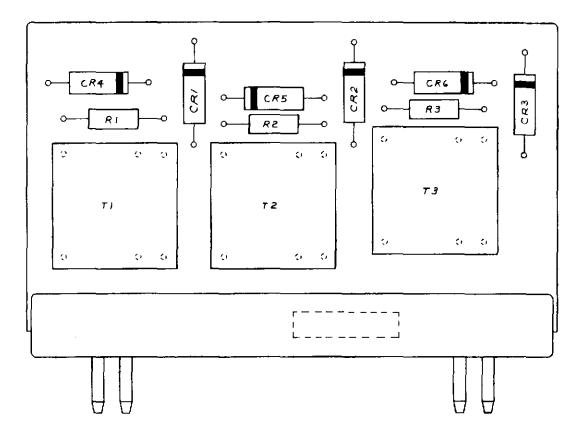

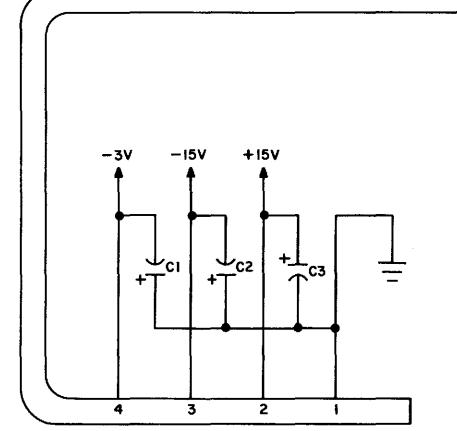

|               | Unregulated Primary Power Distribution Diagram |   |  |   |   |  | 5-39        |

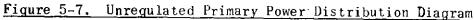

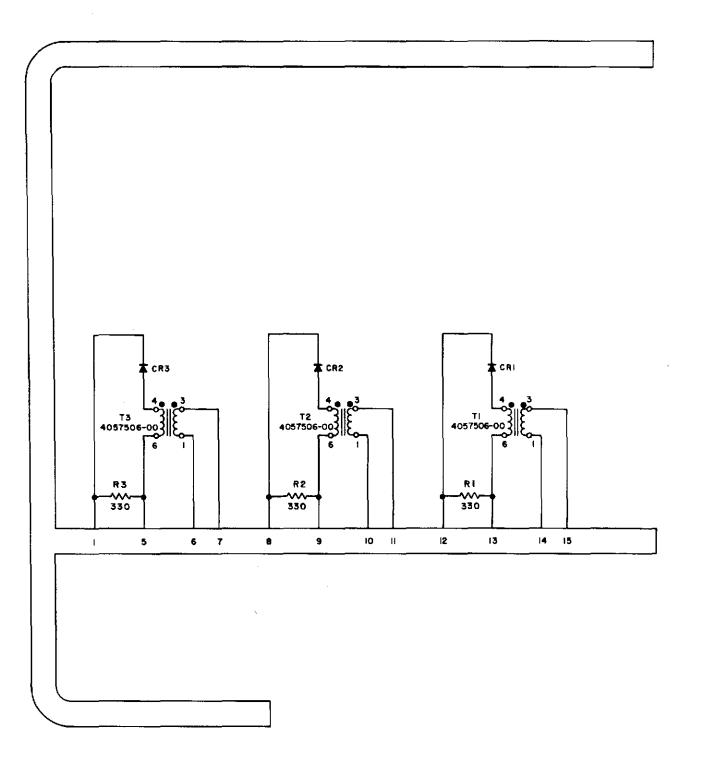

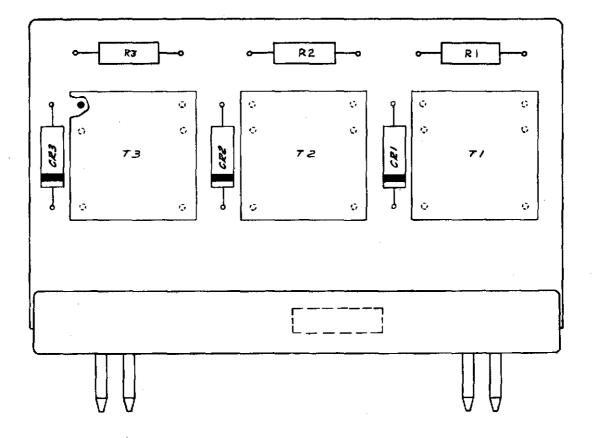

| 5-8,          | Regulated Primary Power Distribution Diagram . |   |  |   |   |  | 5-40        |

### LIST OF TABLES

| <u>Table</u> |                                                 |   |   |   |   |   |   |   |   |   | <u>Page</u> |

|--------------|-------------------------------------------------|---|---|---|---|---|---|---|---|---|-------------|

| 5-1.         | Test Equipment and Special Tools                |   |   |   |   | • |   |   | • | • | 5-3         |

| 5-2.         |                                                 |   |   |   |   |   |   |   |   |   | 5-9         |

| 5-3.         | Master Clock Delay Module FAST/NORMAL Locations |   |   |   |   |   |   |   |   |   | 5-32        |

| 5-4.         | Main Power Supply Characteristics               |   |   |   |   | • | • |   |   | • | 5-37        |

| 5-5.         | Console Power Supply Characteristics            | • | • | ٠ | • | ٠ | • | ٠ | • | • | 5-38        |

5**-**ii

#### SECTION 5

#### TROUBLESHOOTING

5-1. GENERAL.

The logic troubleshooting concepts for the computer are based on the assumption that the troubles will be exposed while running the maintenance routines. The maintenance routines may be run as a result of observing incorrect operational results or they may be run as part of the preventive maintenance procedure. The maintenance routines (referred to as MROT - Maintenance Routines On Tape) are supplied with documentation containing the flow charts, program data sheets, the actual program, and procedures.

The MROT are such that most transmission paths, registers, designators, and modifiers are checked. Several options are available when JUMP or STOP options are selected. A malfunction can cause an error typeout and stop; the program can continue or it may recycle through the routine detecting the error. The error typeout indicates what type of error exists. In many cases, however, maintenance personnel must be relied upon to pinpoint the fault.

The repair concept consists of replacing the faulty printed circuit module with a known good module and verifying the bad module on a module tester. Usually no attempt is made in the field to repair such items as printed circuit modules, memory core stacks, or memory film stacks.

Troubleshooting the nonlogic circuits, such as the main power supply or console, consists of making voltage and/or resistance checks to determine the faulty component.

This section consists of the procedures for loading, running, and interpreting MROT as well as the test procedures for the nonlogic portions of the computer.

5-2. TEST EQUIPMENT AND SPECIAL TOOLS.

Test equipment and special tools required for effective troubleshooting are listed in table 5-1.

If the input/output jumper cables are not available, they may be fabricated as follows: obtain 32 90-pin input/output jacks and 16 90-conductor cables about 48 inches long. Connect the cables and jacks as indicated in paragraph  $2-5\underline{f}$ .

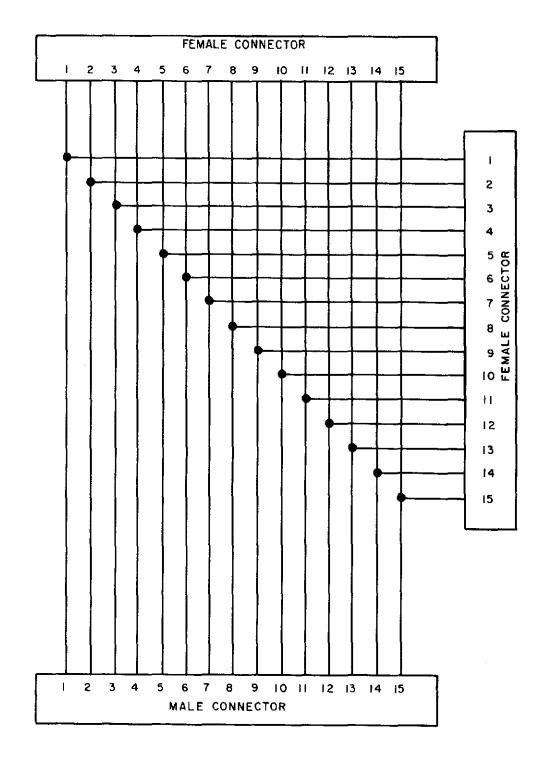

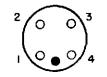

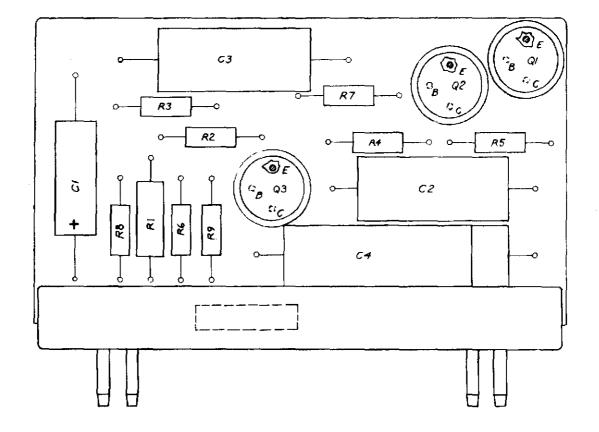

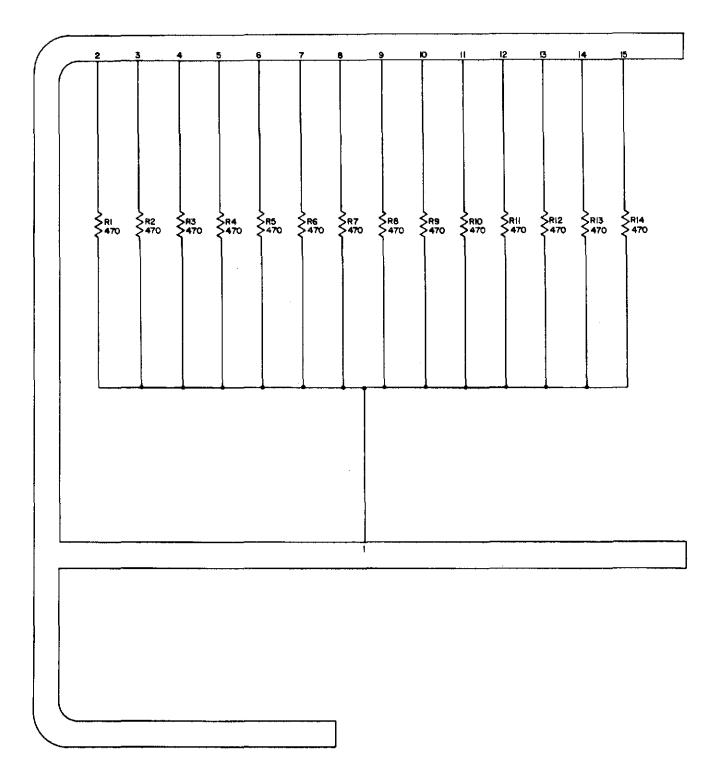

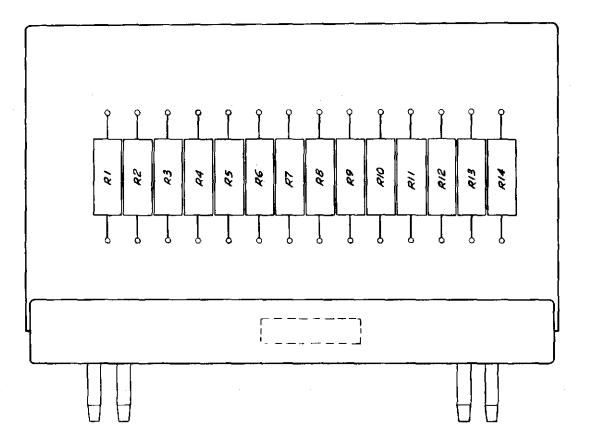

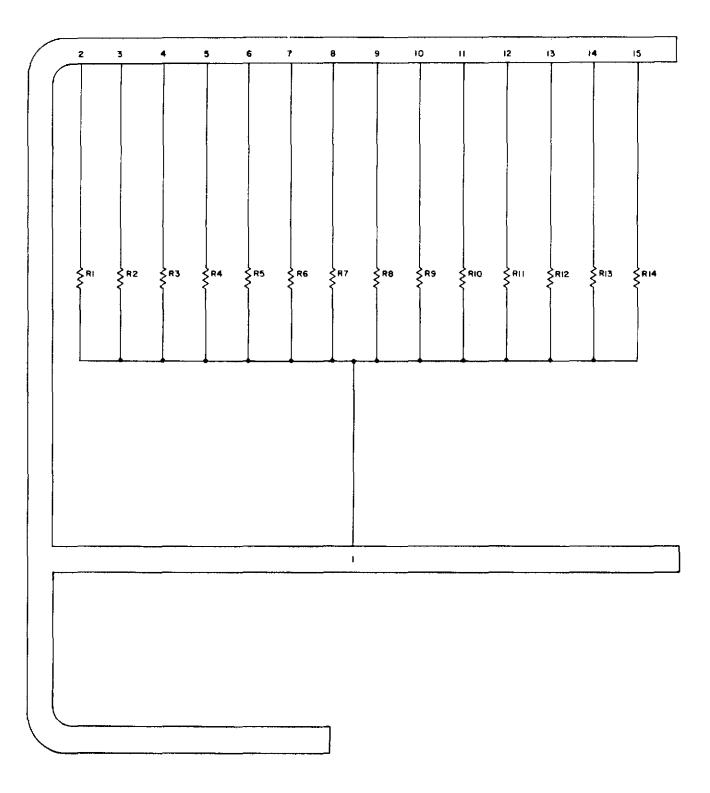

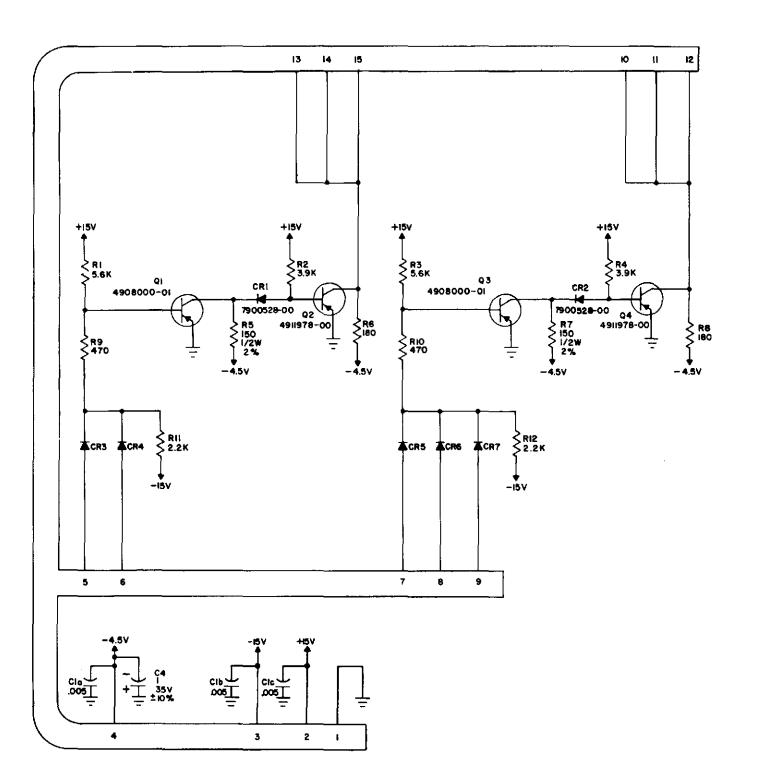

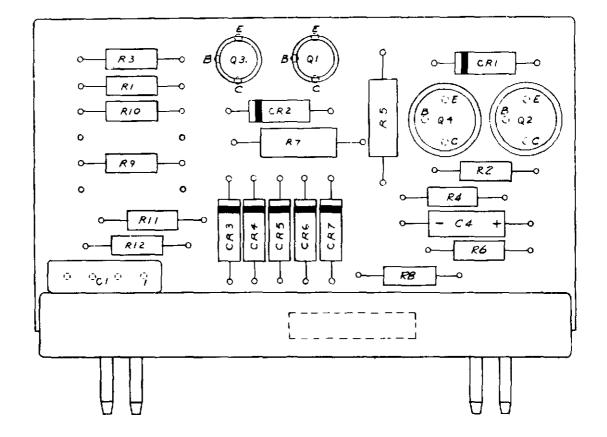

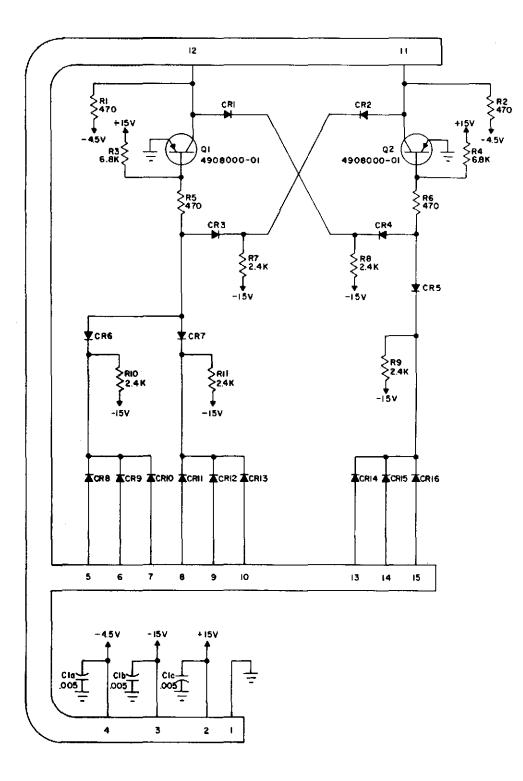

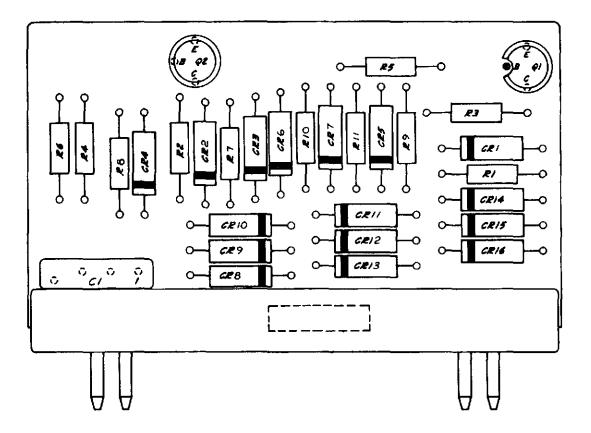

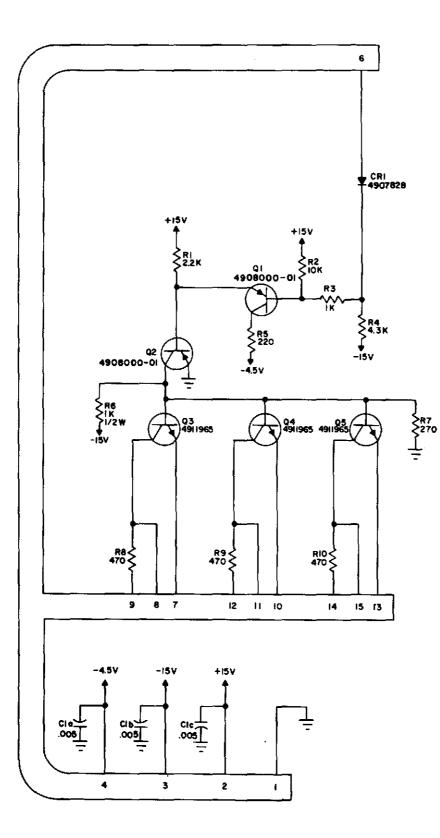

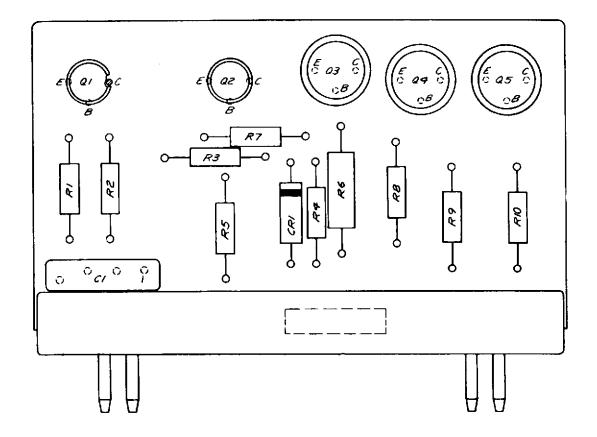

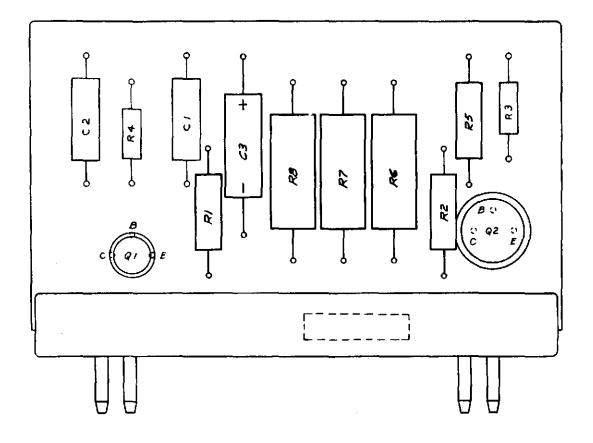

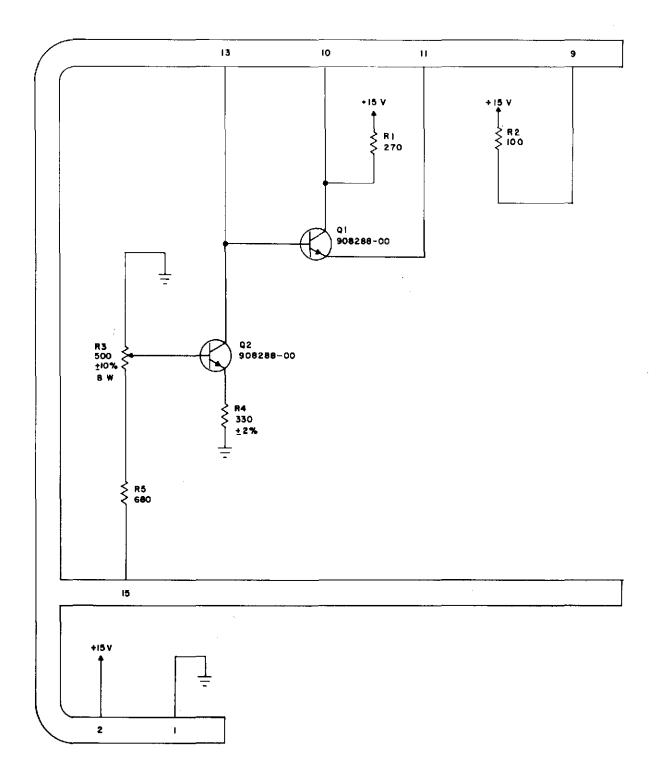

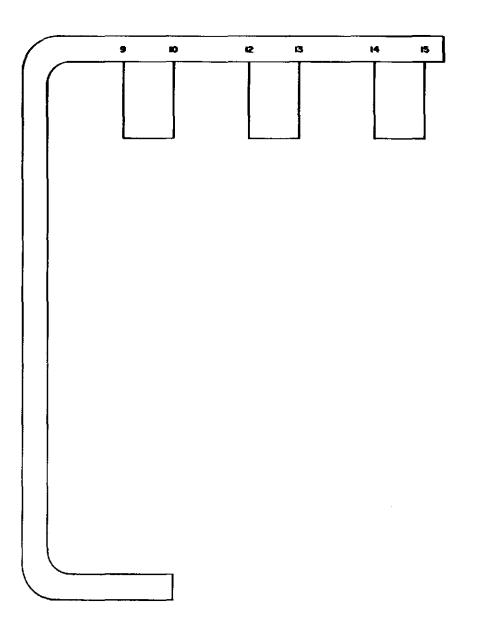

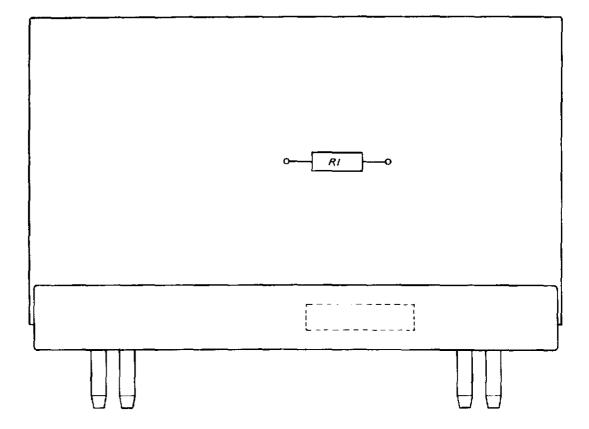

A module extender may be fabricated as follows: obtain a 15-pin male module connector and two 15-contact female connectors. Connect the male connector to the female connector with 36-inch lengths of wire (see figure 5-1). Connect the second female connector to the first with six-inch lengths of wire. The first female connector holds the module, and the second provides test points for all pins.

5-3. LOGIC TROUBLESHOOTING.

Troubleshooting the computer logic circuits is generally done by running the maintenance routines on tape (MROT) and interpreting the error typeouts (if any). The logic troubleshooting can take two forms. It may be desirable to run MROT or it could be more advantageous to run a specific instruction.

ORIGINAL

5-1

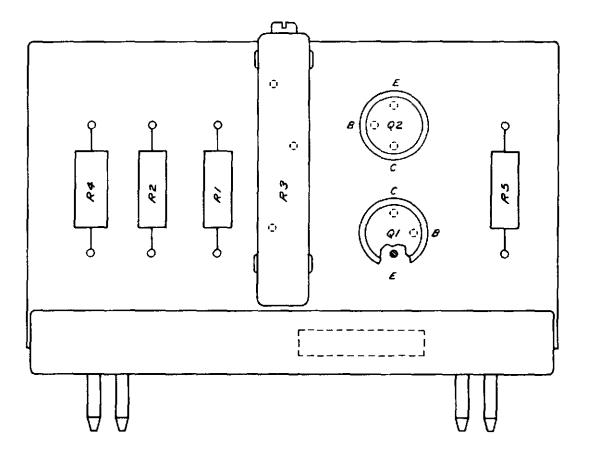

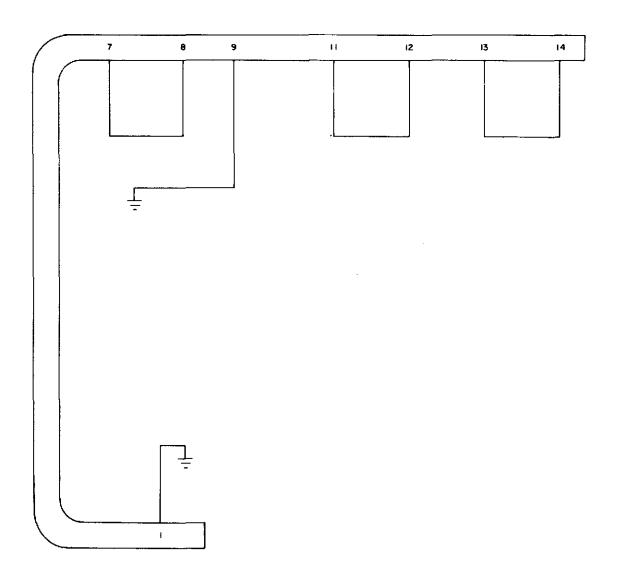

### Figure 5-1. Module Extender Schematic

| NOMENCLA                              | TURE                                                              | FUNCTION                                           |

|---------------------------------------|-------------------------------------------------------------------|----------------------------------------------------|

| NAME                                  | DESIGNATION                                                       | FUNCTION                                           |

| Multimeter                            | AN/PSM-4(C)*                                                      | Measure AC/DC voltages, currents, and resistances. |

| Oscilloscope                          | Tektronix 545*                                                    | View waveforms                                     |

| Dual Channel<br>Pre-Amplifier         | Tektronix Type CA*                                                | Two channel input                                  |

| Current Probe &<br>Termination        | Tektronix Type P6016*                                             | View memory current pulses                         |

| 2 Voltage Probes                      |                                                                   | View voltage pulses                                |

| 1 Probe                               |                                                                   | External sync probe                                |

|                                       |                                                                   |                                                    |

| Tool Set                              | AN/USM-3*                                                         | General purpose                                    |

| Hand stripper                         | Ideal Industries<br>No. 45-171*                                   | Strip insulation from wire                         |

| Hand Crimper                          | Aircraft Marine<br>Products No. 47506*                            | Attach taper pins to wire                          |

| Hand Insertion<br>Tool                | Aircraft Marine Pro-<br>ducts No. 380306*<br>with tip No. 394042* | Insert taper pins into connectors                  |

| Torque Wrench                         |                                                                   | Reassemble memory stacks                           |

| Module Extender**                     |                                                                   |                                                    |

| 15 pin male module<br>connector (1)   | UNIVAC No. 911900                                                 | Part of Module Extender                            |

| 15 pin female module<br>connector (2) | UNIVAC No. 906155                                                 | Part of Module Extender                            |

| 16 I/O Jumper Cables                  |                                                                   |                                                    |

### TABLE 5-1. TEST EQUIPMENT AND SPECIAL TOOLS

\* Or equivalent

\*\* See paragraph 5-2 and figure 5-1.

Table 5-1

### TABLE 5-1. TEST EQUIPMENT AND SPECIAL TOOLS (CONT.)

| NOMENCLA                                                                                                                                  | TURE                                                                                                | FUNCTION                                            |

|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| NAME                                                                                                                                      | DESIGNATION                                                                                         |                                                     |

| Wrapping Tool                                                                                                                             | 14R2 (8130-132)                                                                                     | Make wire-wrap connections                          |

| Power Pack                                                                                                                                | 503885 (8130-151)                                                                                   | Battery for wrapping tool                           |

| Unwrapping Tool<br>Dual for 30 ga.<br>Dual for 20-26 ga.                                                                                  | 505084 (8130-137)<br>A31478 (8130-138)                                                              | Unwraps left or right<br>hand wrapped connections   |

| Bits for<br>30 ga. square pin<br>30 ga. rect. pin<br>24 or 26 ga.<br>Sleeves for<br>30 ga. square pin<br>30 ga. rect. pin<br>24 or 26 ga. | 504221<br>505561 (8130-144)<br>26263 (8130-121)<br>505350<br>17611-2 (8130-129)<br>18840 (8130-128) | Adapts wire wrapping tool<br>to various wire sizes. |

Specific instructions can be manually loaded and initiated. The results of the instruction can be checked, and the execution time can be determined with an oscilloscope. This type of testing can prove computer competence or assist in troubleshooting timing problems that are not tested specifically by MROT. MROT testing consists of loading the routines and selecting the desired options as indicated by the directory typeout portions of MROT. The successful performance of a routine is indicated by a typeout; errors are also indicated by a typeout.

a. GENERAL. - The several MROT available basically consist of ECCLAT, the memory tests, the input/output tests, and others which do not fit into a general category.

These tests are designed to give the highest confidence rating to the computer. They are designed to be followed in any order; some, however, are to follow each other in order. Any individual test can be run to prove the computer competence.

Associated with MROT are error typeouts that occur when an error is detected by the test routine. The error typeout is a terse message indicating what portion of the computer is experiencing trouble. The error typeouts and console indications provide the major clues to isolating a malfunction. The exact trouble may be pinpointed by proper interpretation of typeout and console indications, or it may be necessary to use an oscilloscope and/or voltmeter to pin-point the trouble.

The maintenance routines contain typeout subroutines that type out messages when an error is detected. The messages indicate what particular computer function is failing. For example:

LSHA0

14

This message would be typed out if an error occurred during the test that shifts AQ to the left 14 places. The next step would be to refer to the functional schematics and decide which circuits could cause this error. Further testing in the Op Step and/or Phase Step modes will isolate the trouble to a module that must be replaced. Rerunning the test that detected the error will verify that the trouble has been corrected. For example:

#### XPL TO DL

XXX XXX XXX XXX XXX (X = Binary Number)

XXX XXX XXX XXX XXX

This message indicates an error in the transmission of the complement of X lower (X'L) to D lower. The first 15-bit word is the word that was actually transmitted (error word), and the second 15-bit word is the word that was attempted to be transmitted (test pattern). If corresponding bits are not identical, an error occurred. For example:

> XPL TO DL 111 000 111 000 011 111 000 111 000 111

This message indicates that bit  $2^2$  is being dropped during the transmission. A careful check of the circuits associated with this bit will reveal the fault,

The general procedure for troubleshooting takes the following form:

- 1) Obtain error indication during operation or preventive maintenance.

- 2) Load and run the appropriate MROT.

- 3) Error typeout by MROT.

4) Isolation to section and several possible circuit causes through interpretation of error typeout and console indications.

5) Isolation to a single circuit through interpretation of previous facts and by possible use of test equipment (oscilloscope and/or multimeter).

6) Replacement of faulty component.

7) Rerun the portion of MROT that detected the error (this will prove that the error has been corrected).

8) Resume operation.

If the trouble is isolated to a printed circuit module, it may be desirable to check the module on a module tester.

Use the test equipment and special tools (table 5-1) as indicated by the test procedures given in paragraph 5-3b.

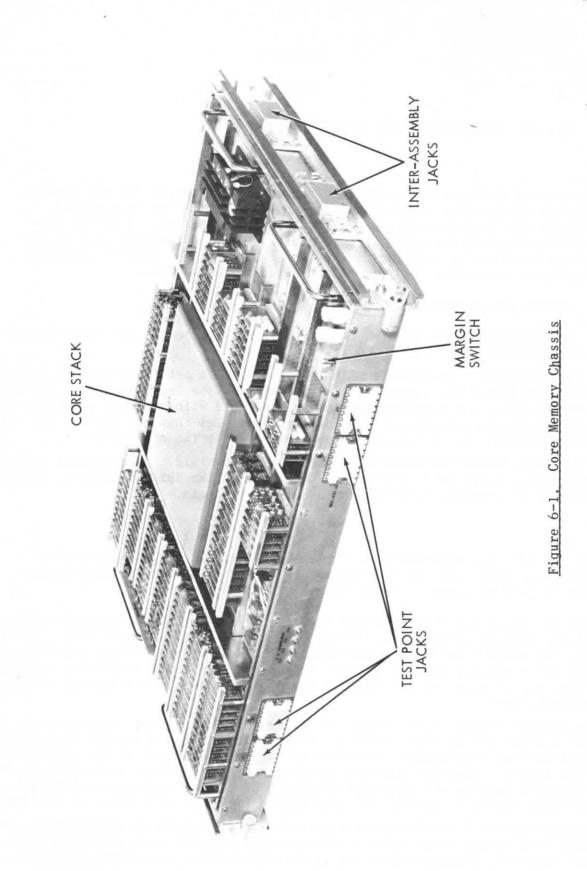

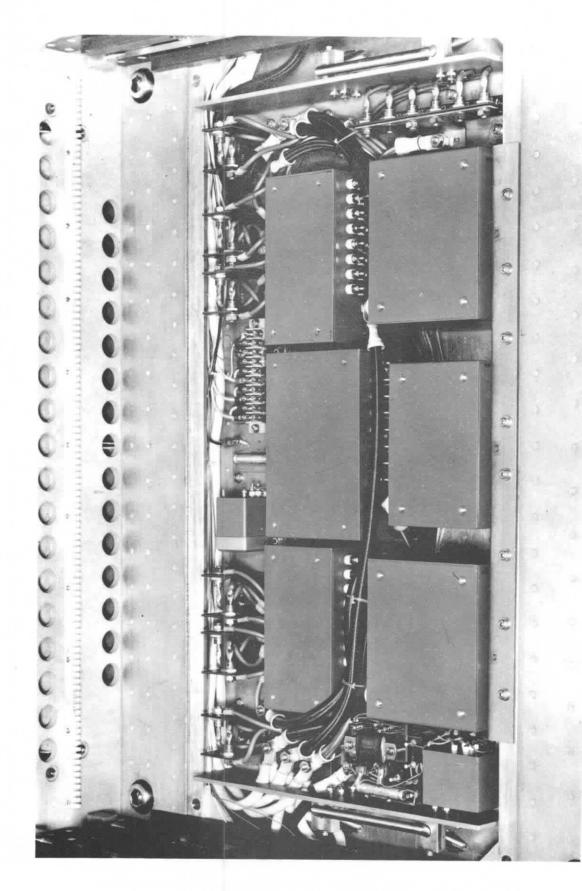

b. MEMORY SECTION TROUBLESHOOTING. - In the memory section, as well as in the other sections of the computer, the troubleshooting procedures are presented primarily to enable personnel to isolate a malfunctioning component. Normal computer troubleshooting techniques are helpful but not necessarily the primary method of solving memory problems. The memories utilize current operated devices. The fol-lowing paragraphs present several troubleshooting techniques and the associated memory waveforms which will aid in the isolation of memory problems.

#### NOTE

Do not attempt to adjust the memories until it has been determined whether or not the cause of a memory malfunction is due to a damaged component.

(1) MAIN MEMORY TROUBLESHOOTING.

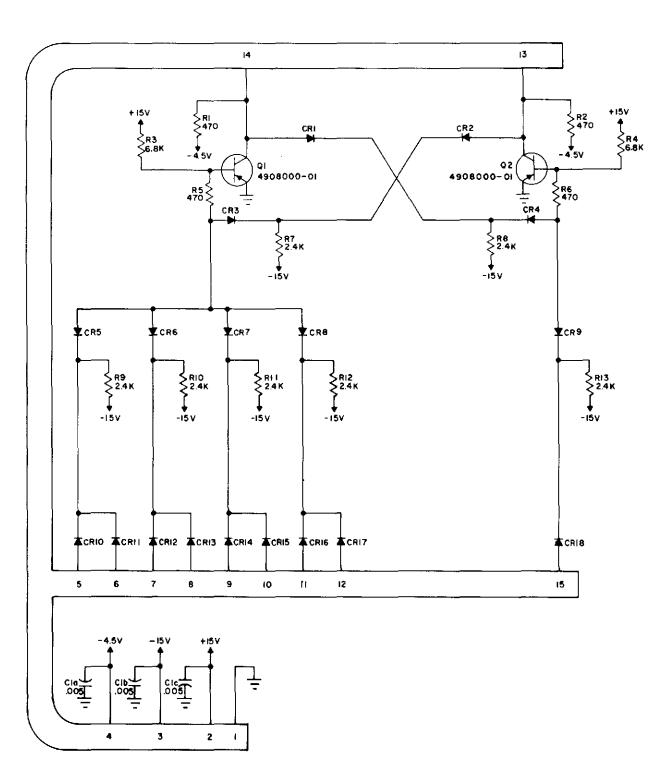

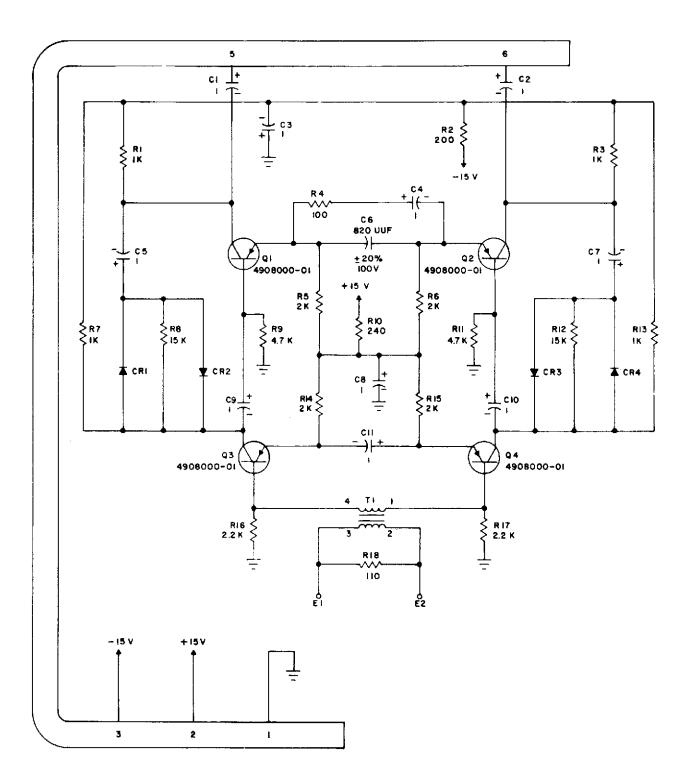

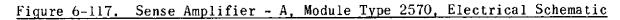

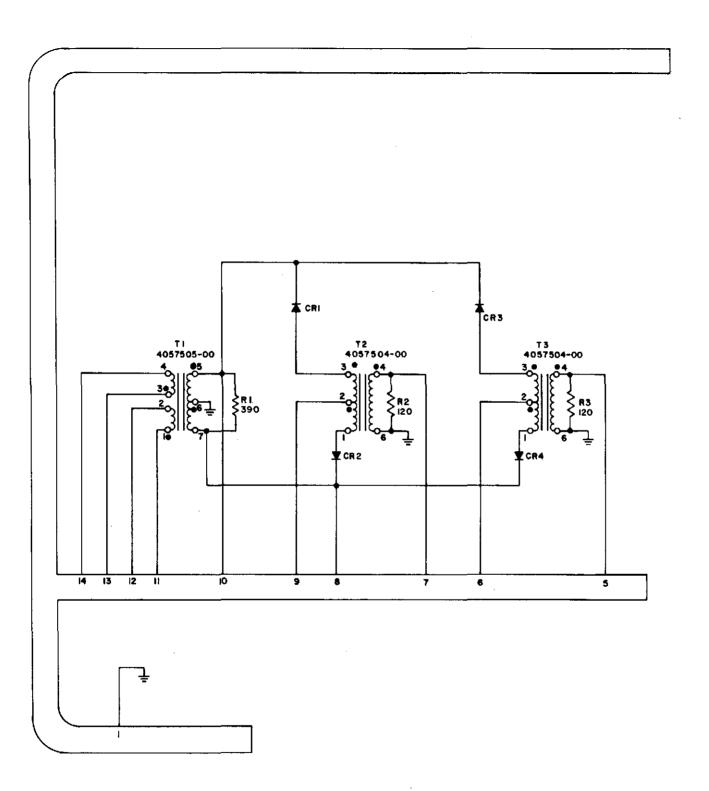

(a) GENERAL. - If a memory chassis is failing, the trouble can usually be isolated to one of three sections (drive line, inhibit, or sense). If the read and write waveforms are correct, the trouble is probably in the sense or inhibit sections. The inhibit section can be checked by observing the inhibit waveforms for each bit while writing zeros. If these waveforms are correct, the one section remaining, the sense section, is probably at fault. Once a trouble is pin-pointed to a certain section, a block-to-block check of waveforms may be made to pin-point the trouble to a module or component. The following paragraphs present a short review of the functions of these sections.

<u>1</u>. DRIVE LINES. - The drive lines control the application of current that creates the magnetic field which switches the cores to one of two stable states. During the read portion of the memory cycle, all cores receiving coincident current are switched to a "O" unconditionally. During the write portion of the memory cycle, all cores receiving coincident current switch back from a "O" to a "1". An inhibit pulse occurring during this write portion prevents a core from switching to a "1". The drive line circuits can be split into two sections: the read/write transformer and the selector circuits. Read/write transformer translation takes place on each memory chassis and determines which of four X or four Y transformers is selected. The proper selector (one of 32X or 32Y) completes the drive line selection, that is, which X and Y lines are receiving the switching currents. Translation for the proper selector also takes place on each memory chassis.

2. INHIBIT LINES. - The inhibit lines prevent selected cores from being switched to a "1" during the write portion of the memory cycle, if a "O" was sensed during the read portion. Translation for the inhibit lines is accomplished on each memory chassis, and current is switched through the selected inhibit line if the Z register has a "O" for a given bit rather than a "1". Inhibit lines run parallel to either an X or a Y drive line, and the current is in the opposite direction to the drive line current. This effectively cancels half of the drive line current. Thus, coincident current is not obtained for the selected cores, and a "1" is not written.

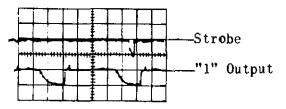

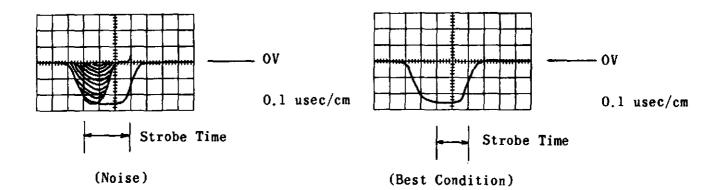

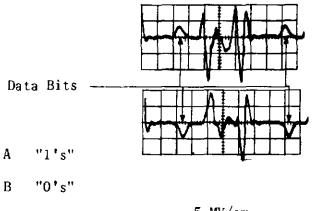

3. SENSE LINES. - The sense lines thread through each core and detect core flux changes as an induced voltage. If this voltage is 10 millivolts or less, the sense amplifier ignores it. If the voltage is about 50 millivolts, the sense amplifier accepts it as a "1". Since a core requires 0.7 microseconds to switch, a "1" from a switched core occurs later in time than a "0", which occurs only when a core fails to switch. Because of this delay, a 0.2 to 0.3 microsecond strobe pulse is initiated approximately 0.5 microseconds after a read pulse is initiated. The data buffer register can accept inputs from the sense amplifiers only during the duration of the strobe pulse. In this way, "0" noise from the cores is isolated from the data buffer register. The data buffer register feeds the Z register which holds the data obtained from the memory reference. Figure 5-2 shows the timing relationships of the various memory pulses.

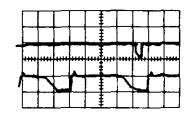

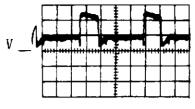

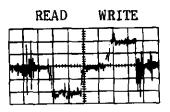

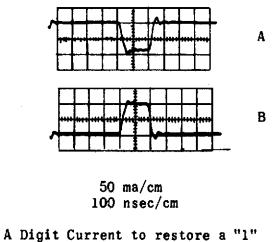

(b) PROCEDURES. - The following steps are presented to assist in the isolation of failing circuits in the memory section. Table 5-2 presents tabulated data concerning the circuitry which affects the bits at various addresses. Figure 5-3 illustrates typical waveforms which may be used as a guide to check actual waveforms. Several of the oscillograms presented are abnormal memory waveforms (see

### Figure 5-2. Memory Timing Cycle, Idealized Timing Waveform

Paragraph 5-3<u>b(1)(b</u>)

figure 5-4). The test points used to obtain some of these will be inaccessible when the chassis is plugged in. If the memory chassis above is to be checked, the one to be checked is to be removed if it is possible to obtain access to these signals during actual operation. In this case, however, six of the memory bits will not be available for accessing due to the removed chassis. The following steps are quite basic but they should be checked thoroughly prior to making any adjustments or replacements.

STEP 1. Determine that the proper bits are being sent to the S register, and, in the case of write functions, check that the Z register contains the correct information to be written. Refer to figures 8-95 through 8-99, 8-103, and 8-104.

STEP 2. Determine that the translation is correct. Refer to paragraph  $4-2\underline{e}(2)(d)$  for an explanation of the translation circuits. Check the read-write drive lines to see if they are properly activated. See the adjustment procedure in paragraph  $6-2\underline{b}(1)$ , if it appears that this is the problem. It is good practice to note the settings prior to any adjustment attempt, in the event that adjusting does not correct the malfunction.

STEP 3. Check the inhibit circuits to determine if this is creating the problem. The inhibit diverters may be either open or shorted; if this happens, a certain bit or block of addresses would contain all ones. Refer to figures 8-105 and 8-106 for inhibit translation and to the waveforms in figure 5-3.

STEP 4. Check the sense output and strobe timing on each chassis. Determine if the output itself is weak or if the timing is off. In either case, adjustments should be made according to paragraph  $6-2\underline{b}(1)$ . Note the settings before attempting any adjustment. If the memory is dropping "1's", the problem may be that the read and write currents are too low. If it is picking up "1's", perhaps the read and write currents are too high, or the inhibit circuits are not functioning. Refer to figure 8-107 for the sense circuit logic. Figure 5-3 shows typical sense output waveforms. In the very remote case that the failure exists within the core plane itself, replace according to paragraph  $6-3\underline{i}$ .

(2) CONTROL AND BOOTSTRAP MEMORY TROUBLESHOOTING.

(a) GENERAL. - Troubleshooting the memories is so closely linked with the adjustments that the procedures for performing both are contained in paragraph  $6-2\underline{b}(2)$ . However, a valuable program for troubleshooting these memories is the control memory test which is described in paragraph  $5-3\underline{c}(2)(\underline{b})\underline{1}$ .

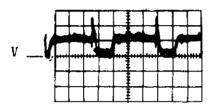

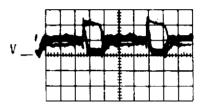

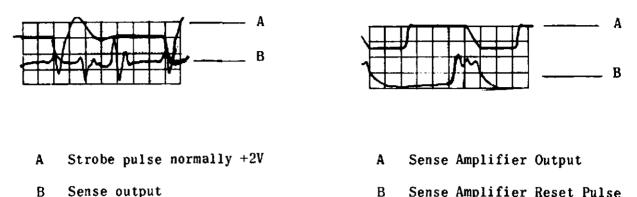

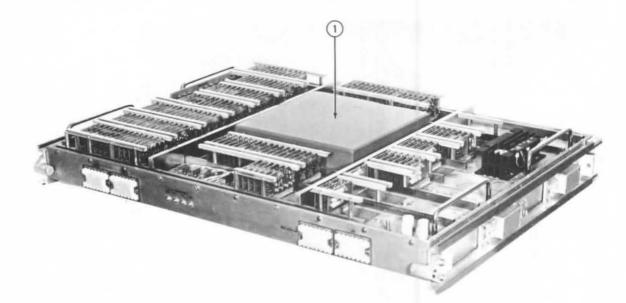

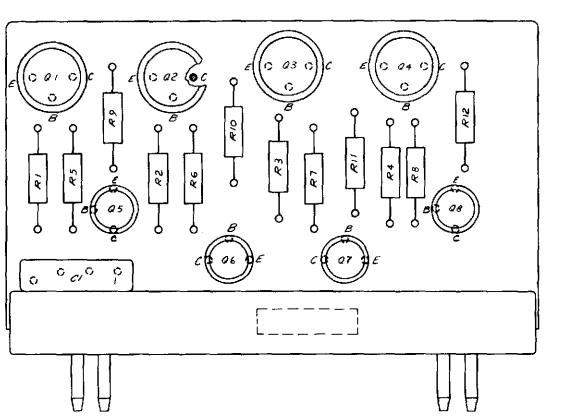

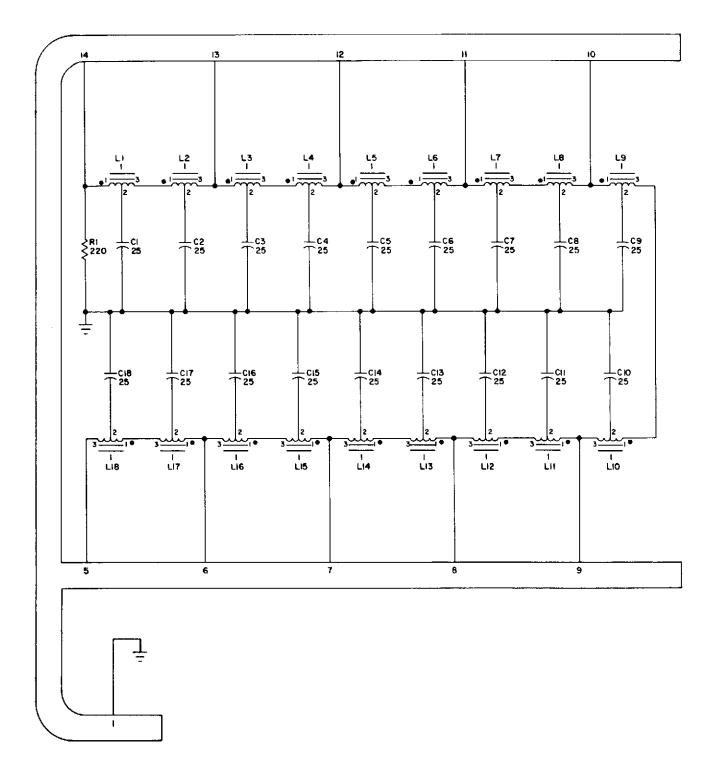

(b) LOCATION OF CONTROL MEMORY WORDS. - The control memory as explained in section 4 can store 64 30-bit words. Words 00 through 37 (octal) are stored on planes A4 and A6 (odd bits on A4, even bits on A6). Words 40 through 77 are stored on planes A3 and A5 (odd bits on A3, even bits on A5). Refer to figure 5-5.

### c. TESTS

(1) ECCLAT. - The Executive Controlled Computer Logic Acceptance Test (ECCLAT) is an executive controlled program designed to check the logic of the computer. ECCLAT, under control of a main executive program, consists of the following test programs.

$(\underline{a})$  J CONTROL TEST. - The function of this program checks the j designator evaluation. Separate test routines have been included for the testing of each j designator.

•

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS

|     |               |              | SENSE     |          |         |          |

|-----|---------------|--------------|-----------|----------|---------|----------|

| BIT | ADDRESS       | CORE PLANE   | AMPLIFIER | LOCATION | INHIBIT | LOCATION |

| 0   | 00000 - 07777 | 9A17         | 93Y00     | 9J13B    | 86 Y 00 | 9J01C    |

| 0   | 10000 - 17777 | 9A17         | 93Y10     | 9J10F    | 86Y10   | 9J02C    |

| 0   | 20000 - 27777 | 9A17         | 93Y30     | 9J25G    | 86Y20   | 9H30C    |

| 0   | 30000 - 37777 | 9A17         | 93¥20     | 9J21C    | 86Y30   | 9J04C    |

| 0   | 40000 - 47777 | 9A23         | 93¥40     | 9J16B    | 86Y40   | 9J05C    |

| 0   | 50000 - 57777 | 9A23         | 93¥50     | 9J13F    | 86¥50   | 9J06C    |

| 0   | 60000 - 67777 | 9A23         | 93¥70     | 9J28G    | 86Y60   | 9J07C    |

| 0   | 70000 - 77777 | 9A23         | 93¥60     | 9J34C    | 86Y70   | 9J08C    |

| 1   | 00000 - 07777 | 9A18         | 93Y01     | 9J13B    | 86Y01   | 9J01C    |

| 1   | 10000 - 17777 | 9A18         | 93Y11     | 9J10F    | 86Y11   | 9J02C    |

| 1   | 20000 - 27777 | 9A18         | 93Y31     | 9J25G    | 86Y21   | 9J03C    |

| 1   | 30000 - 37777 | 9A18         | 93Y21     | 9J31C    | 86Y31   | 9J04C    |

| 1   | 40000 - 47777 | 9A24         | 93Y41     | 9J16B    | 86¥41   | 9J05C    |

| 1   | 50000 - 57777 | 9A24         | 93¥51     | 9J13F    | 86 Y 51 | 9J06C    |

| 1   | 60000 - 67777 | 9A24         | 93Y71     | 9J28G    | 86Y61   | 9J07C    |

| 1   | 70000 - 77777 | 9A24         | 93Y61     | 9J34C    | 86¥71   | 9J08C    |

| 2   | 00000 - 07777 | 9A19         | 93Y02     | 9J14B    | 86Y02   | 9J01C    |

| 2   | 10000 - 17777 | 9A19         | 93Y12     | 9J11F    | 86Y12   | 9J02C    |

| 2   | 20000 - 27777 | 9A19         | 93Y32     | 9J26G    | 86Y22   | 9J03C    |

| 2   | 30000 - 37777 | 9A19         | 93Y22     | 9J32C    | 86Y32   | 9J04C    |

| 2   | 40000 - 47777 | 9A25         | 93Y42     | 9J17B    | 85Y42   | 9J05C    |

| 2   | 50000 - 57777 | 9A25         | 93¥52     | 9J14G    | 86Y52   | 9J06C    |

| 2   | 60000 - 67777 | <b>9</b> A25 | 93¥72     | 9J29G    | 86Y62   | 9J07C    |

| 2   | 70000 - 77777 | <b>9A</b> 25 | 93Y62     | 9J35C    | 86Y72   | 9J08C    |

| 3   | 00000 - 07777 | 9A20         | 93Y03     | 9J14B    | 86Y03   | 9J09C    |

| 3   | 10000 - 17777 | 9A20         | 93Y13     | 9J11F    | 86Y13   | 9J10C    |

| 3   | 20000 - 27777 | 9A20         | 93Y33     | 9J26G    | 86Y23   | 9J11C    |

| 3   | 30000 - 37777 | 9A20         | 93Y23     | 9J32C    | 86Y33   | 9J12C    |

| 3   | 40000 - 47777 | 9A26         | 93Y43     | 9J17B    | 86Y43   | 9J13C    |

| 3   | 50000 - 57777 | 9A26         | 93¥53     | 9J14G    | 86¥53   | 9J10B    |

| 3   | 60000 - 67777 | 9A26         | 93Y73     | 9 J29G   | 86 Y63  | 9J11B    |

| 3   | 70000 - 77777 | 9A27         | 93¥63     | 9J35C    | 86Y73   | 9J12B    |

|     |               |              |           |          |         |          |

|     |               |              |           |          |         |          |

Table 5-2

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS (CONT.)

| BIT | ADDRESS       | CORE PLANE | SENSE<br>AMPLIFIER | LOCATION | INHIBIT | LOCATION       |

|-----|---------------|------------|--------------------|----------|---------|----------------|

| 4   | 00000 - 07777 | 9A21       | 93Y04              | 9J15B    | 86Y04   | 9J09C          |

| 4   | 10000 - 17777 | 9A21       | 93Y14              | 9J12F    | 86Y14   | 9J10C          |

| 4   | 20000 - 27777 | 9A21       | 93Y34              | 9J27G    | 86Y24   | 9J11C          |

| 4   | 30000 - 37777 | 9A21       | 93Y24              | 9J33C    | 86Y34   | 9J12C          |

| 4   | 40000 - 47777 | 9A27       | 93Y44              | 9J18B    | 86Y44   | 9J13C          |

| 4   | 50000 - 57777 | 9A27       | 93¥54              | 9J15G    | 86¥54   | 9J10B          |

| 4   | 60000 - 67777 | 9A27       | 93Y74              | 9J30G    | 86Y64   | 9J11B          |

| 4   | 70000 - 77777 | 9A27       | 93¥64              | 9J36C    | 86Y74   | 9J12B          |

| 5   | 00000 - 07777 | 9A22       | 93Y05              | 9J15B    | 86Y05   | 9J09C          |

| 5   | 10000 - 17777 | 9A22       | 93Y15              | 9J12F    | 86Y15   | 9J10C          |

| 5   | 20000 - 27777 | 9A22       | 93¥35              | 9J27G    | 86Y25   | 9J11C          |

| 5   | 30000 - 37777 | 9A22       | <b>93</b> ¥25      | 9J33C    | 86¥35   | 9J12C          |

| 5   | 40000 - 47777 | 9A28       | 93¥45              | 9J18B    | 86Y45   | 9J13C          |

| 5   | 50000 - 57777 | 9A28       | 93¥55              | 9J15G    | 86¥55   | 9J10B          |

| 5   | 60000 - 67777 | 9A28       | 93¥75              | 9J30G    | 86¥65   | 9J11B          |

| 5   | 70000 - 77777 | 9A28       | 93¥65              | 9J36C    | 86¥75   | 9J12B          |

| 6   | 00000 - 07777 | 10A17      | 93Y00              | 10J13B   | 86 YOO  | 10J01C         |

| 6   | 10000 - 17777 | 10A17      | 93Y10              | 10J10F   | 86Y10   | 10J02C         |

| 6   | 20000 - 27777 | 10A17      | 93¥30              | 10J25G   | 86Y20   | 10J03C         |

| 6   | 30000 - 37777 | 10A17      | 93Y20              | 10J21C   | 86Y30   | 10J04C         |

| 6   | 40000 - 47777 | 10A23      | 93¥40              | 10J16B   | 86Y40   | 10J05C         |

| 6   | 50000 - 57777 | 10A23      | 93Y50              | 10J13F   | 86Y50   | 10J06C         |

| 6   | 60000 - 67777 | 10A23      | 93Y70              | 10J28G   | 86Y60   | 10J07C         |

| 6   | 70000 - 77777 | 10A23      | 93Y60              | 10J34C   | 86Y70   | 10J08C         |

| 7   | 00000 - 07777 | 10A18      | 93Y01              | 10JBB    | 86Y01   | 10J01C         |

| 7   | 10000 - 17777 | 10A18      | 93Y11              | 10J10F   | 86Y11   | 10J02C         |

| 7   | 20000 - 27777 | 10A18      | 93Y31              | 10J25G   | 86Y21   | 10 <b>J03C</b> |

| 7   | 30000 - 37777 | 10A18      | 93¥21              | 10J31C   | 86Y31   | 10J04C         |

| 7   | 40000 - 47777 | 10A24      | 93¥41              | 10J16B   | 86Y41   | 10 <b>J05C</b> |

| 7   | 50000 - 57777 | 10A24      | 93¥51              | 10JBF    | 86Y51   | 10J06C         |

| 7   | 60000 - 67777 | 10A24      | 93Y71              | 10J28G   | 86¥61   | 10J07C         |

| 7   | 70000 - 77777 | 10A24      | 93¥61              | 10J34C   | 86Y71   | 10J08C         |

|     |               |            |                    |          |         |                |

|     |               |            |                    |          |         |                |

Table 5-2

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS (CONT.)

|     |               |            | SENSE         |          |                |                |

|-----|---------------|------------|---------------|----------|----------------|----------------|

| BIT | ADDRESS       | CORE PLANE | AMPLIFIER     | LOCATION | INHIBIT        | LOCATION       |

| 8   | 00000 - 07777 | 10A19      | 93¥02         | 10J14B   | 86Y02          | 10J01C         |

| 8   | 10000 - 17777 | 10A19      | 93Y12         | 10J11F   | 86Y12          | 10J02C         |

| 8   | 20000 - 27777 | 10A19      | 93Y32         | 10J26G   | 86Y22          | 10J03C         |

| 8   | 30000 - 37777 | 10A19      | 93Y22         | 10J32C   | 86Y32          | 10 <b>J04C</b> |

| 8   | 40000 - 47777 | 10A25      | 93Y42         | 10J17B   | 86Y42          | 10J05C         |

| 8   | 50000 - 57777 | 10A25      | 93Y52         | 10J14G   | 86¥52          | 10 <b>J06C</b> |

| 8   | 60000 - 67777 | 10A25      | 93Y72         | 10J29G   | 86Y62          | 10J07C         |

| 8   | 70000 - 77777 | 10A25      | 93Y62         | 10J35C   | 86Y72          | 10J08C         |

| 9   | 00000 - 07777 | 10A20      | 93Y03         | 10J14B   | 86Y03          | 10J09C         |

| 9   | 10000 - 17777 | 10A20      | 93Y13         | 10J11F   | 86Y13          | 10J10C         |

| 9   | 20000 - 27777 | 10A20      | 93Y33         | 10J26G   | 86Y23          | 10J11C         |

| 9   | 30000 - 37777 | 10A20      | 93Y23         | 10J32C   | 86Y33          | 10J12C         |

| 9   | 40000 - 47777 | 10A26      | 93¥43         | 10J17B   | 86Y43          | 10J13C         |

| 9   | 50000 - 57777 | 10A26      | 93¥53         | 10J14G   | 86Y53          | 10J10B         |

| 9   | 60000 - 67777 | 10A26      | 93Y73         | 10J29G   | 86Y63          | 10J11B         |

| 9   | 70000 - 77777 | 10A26      | 93Y63         | 10J35C   | 86Y <b>7</b> 3 | 10J12B         |

| 10  | 00000 - 07777 | 10A21      | 93Y04         | 10J15B   | 86Y04          | 10J09C         |

| 10  | 10000 - 17777 | 10A21      | 93Y14         | 10J12F   | 86Y14          | 10J10C         |

| 10  | 20000 - 27777 | 10A21      | 93Y34         | 10J27G   | 86Y24          | 10J11C         |

| 10  | 30000 - 37777 | 10A21      | 93Y24         | 10J33C   | 86Y34          | 10J12C         |

| 10  | 40000 - 47777 | 10A27      | 93¥44         | 10J18B   | 86Y44          | 10J13C         |

| 10  | 50000 - 57777 | 10A27      | 93¥54         | 10J15G   | 86¥54          | 10J10B         |

| 10  | 60000 - 67777 | 10A27      | 93Y74         | 10J30G   | 86Y64          | 10J11B         |

| 10  | 70000 - 77777 | 10A27      | 93Y64         | 10J36C   | 86Y74          | 10J12B         |

| 11  | 00000 - 07777 | 10A22      | 93Y05         | 10J15B   | 86Y05          | 10J09C         |

| 11  | 10000 ~ 17777 | 10A22      | 93Y15         | 10J12F   | 86Y15          | 10J10C         |

| 11  | 20000 - 27777 | 10A22      | 93¥35         | 10J27G   | 86Y25          | 10J11C         |

| 11  | 30000 - 37777 | 10A22      | <b>93Y2</b> 5 | 10J33C   | 86¥35          | 10J12C         |

| 11  | 40000 - 47777 | 10A28      | <b>93</b> ¥45 | 10J18B   | 86Y45          | 10J13C         |

| 11  | 50000 - 57777 | 10A28      | 93Y55         | 10J15G   | 86¥55          | 10J10B         |

| 11  | 60000 - 67777 | 10A28      | 93¥75         | 10J30G   | 86Y65          | 10J11B         |

| 11  | 70000 - 77777 | 10A28      | 93¥65         | 10J36C   | 86¥75          | 10J12B         |

|     |               |            |               |          |                |                |

|     |               |            |               |          |                |                |

Table 5-2

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS (CONT.)

| BIT | ADDRESS       | CORE PLANE     | SENSE<br>AMPLIFIER | LOCATION        | INHIBIT | LOCATION        |

|-----|---------------|----------------|--------------------|-----------------|---------|-----------------|

| 12  | 00000 - 07777 | 11A17          | 93Y00              | 11J13B          | 86Y00   | 11J01C          |

| 12  | 10000 - 17777 | 11A17          | 93Y10              | 11J10F          | 86Y10   | 11J02C          |

| 12  | 20000 - 27777 | 11A17          | 93¥30              | 11J25G          | 86Y20   | 11J03C          |

| 12  | 30000 - 37777 | 11A17          | 93Y20              | 11J21C          | 86Y30   | 11J04C          |

| 12  | 40000 - 47777 | 11A23          | 93¥40              | 11J16B          | 86Y40   | 11J05C          |

| 12  | 50000 - 57777 | 11A23          | 93¥50              | 11J13F          | 86Y50   | 11 J06C         |

| 12  | 60000 - 67777 | 11A23          | 93¥70              | 11 <b>J</b> 28G | 86Y60   | 11J07C          |

| 12  | 70000 – 77777 | 11A23          | 93¥60              | 11J34C          | 86Y70   | 11J08C          |

| 13  | 00000 - 07777 | 11A18          | 93Y01              | 11J13B          | 86Y01   | 11J01C          |

| 13  | 10000 - 17777 | 11A18          | 93411              | 11J10F          | 86Y11   | 11J02C          |

| 13  | 20000 - 27777 | 11A18          | 93Y31              | 11J25G          | 86Y21   | 11J03C          |

| 13  | 30000 - 37777 | 11A18          | 93Y21              | 11J31C          | 86¥31   | 11J04C          |

| 13  | 40000 - 47777 | 11A24          | 93¥41              | 11J16B          | 86Y41   | 11 <b>J0</b> 5C |

| 13  | 50000 - 57777 | 1.1A24         | 93¥51              | 11J13F          | 86Y51   | 11J06C          |

| 13  | 60000 - 67777 | 11A24          | 93¥71              | 11J28G          | 86Y61   | 11J07C          |

| 13  | 70000 - 77777 | 11A24          | 93¥61              | 11J34C          | 86Y71   | 11J08C          |

| 14  | 00000 - 07777 | 11A19          | 93Y02              | 11J14B          | 86Y02   | 11J01C          |

| 14  | 10000 - 17777 | 11A19          | 93Y12              | 11J11F          | 86Y12   | 11J02C          |

| 14  | 20000 - 27777 | 11 <b>A1</b> 9 | 93Y32              | 11J26G          | 86Y22   | 11J03C          |

| 14  | 30000 - 37777 | 11A19          | 93Y22              | 11J32C          | 86Y32   | 11J04C          |

| 14  | 40000 - 47777 | 11A25          | 93¥42              | 11J17B          | 86Y42   | 11J05C          |

| 14  | 50000 - 57777 | 11A25          | 93Y52              | 11J14G          | 86Y52   | 11J06C          |

| 14  | 60000 - 67777 | 11A25          | 93Y72              | 11J29G          | 86Y62   | 11J07C          |

| 14  | 70000 - 77777 | 11A25          | 93Y62              | 11J35C          | 86Y72   | 11J08C          |

| 15  | 00000 - 07777 | 11A20          | 93Y03              | 11 <b>J</b> 14B | 86Y03   | 11 J09C         |

| 15  | 10000 - 17777 | 11A20          | <b>93</b> Y13      | 11 <b>J1</b> 1F | 86Y13   | 11J10C          |

| 15  | 20000 - 27777 | 11A20          | 93Y33              | 11J26G          | 86Y23   | 11J11C          |

| 15  | 30000 - 37777 | 11A20          | 93Y23              | 11J23C          | 86Y33   | 11J12C          |

| 15  | 40000 - 47777 | 11A26          | 93Y43              | 11J17B          | 86Y43   | 11J13C          |

| 15  | 50000 - 57777 | 11A26          | 93Y53              | 11J14G          | 86¥53   | 11J10B          |

| 15  | 60000 - 67777 | 11A26          | 93Y73              | 11 J29G         | 86¥63   | 11J11B          |

| 15  | 70000 - 77777 | 11A27          | 93Y63              | 11 J35C         | 86Y73   | 11J12B          |

|     |               |                |                    |                 |         |                 |

|     |               |                |                    |                 |         |                 |

ORIGINAL

· .\_.

~~~

5-12

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS (CONT.)

| BIT | ADDRESS                        | CORE PLANE     | SENSE<br>AMPLIFIER | LOCATION         | INHIBIT        | LOCATION         |

|-----|--------------------------------|----------------|--------------------|------------------|----------------|------------------|

| 16  | 00000 - 07777                  | 11A21          | 93Y04              | 11J15B           | 86Y04          | 11J09C           |

| 16  | 10000 - 17777                  | 11A21<br>11A21 | 93Y14              | 11J13B<br>11J12F | 86Y14          | 11J10C           |

| 16  | 20000 - 27777                  | 11A21<br>11A21 | 93Y34              | 11J12F<br>11J27G | 86Y24          | 11J11C           |

| 16  | 30000 - 37777                  | 11A21<br>11A21 | 93Y24              | 11J270<br>11J33C | 86Y34          | 11J12C           |

| 16  | 40000 - 47777                  | 11A27          | 93124<br>93144     | 11J18B           | 86Y44          |                  |

| 16  | 50000 - 57777                  | 11A27<br>11A27 | 93Y54              | 11J10B<br>11J15G | 86Y54          | 11J13C<br>11J10B |

| 16  | 60000 - 67777                  | 11A27<br>11A27 | 93134<br>93Y74     | 11J13G           | 86154<br>86Y64 | 11J11B           |

| 16  | 70000 - 77777                  | 11A27<br>11A27 | 93174<br>93Y64     | 11 <b>J</b> 36C  | 86104<br>86Y74 |                  |

| 17  | 00000 - 07777                  | 11A27<br>11A22 | 93104<br>93Y05     |                  |                | 11J12B           |

| 17  | 10000 = 07777                  | 11A22<br>11A22 |                    | 11J15B           | 86Y05          | 11J09C           |

| 17  | 1                              | 11A22<br>11A22 | 93Y15<br>02Y25     | 11J12F           | 86Y15          | 11J10C           |

| 17  | 20000 - 27777<br>30000 - 37777 |                | 93¥35<br>03¥35     | 11J27G           | 86Y25          | 11J11C           |

|     | 4                              | 11A22          | 93Y25              | 11J33C           | 86Y35          | 11J12C           |

| 17  | 40000 - 47777                  | 11A28          | 93Y45              | 11J18B           | 85Y45          | 11J13C           |

| 17  | 50000 - 57777                  | 11A28          | 93Y55              | 11J15G           | 86Y55          | 11J10B           |

| 17  | 60000 - 67777                  | 11A28          | 93Y75              | 11J30G           | 86Y65          | 11J11B           |

| 17  | 70000 - 77777                  | 11A28          | 93¥65              | 11J36C           | 86Y75          | 11J12B           |

| 18  | 00000 - 07777                  | 12A17          | 93Y00              | 12J13B           | 86Y00          | 12J01C           |

| 18  | 10000 - 17777                  | 12A17          | 93Y10              | 12J10F           | 86Y10          | 12J02C           |

| 18  | 20000 - 27777                  | 12A17          | 93 Y30             | 12J25G           | 86Y20          | 12J03C           |

| 18  | 30000 - 37777                  | 12A17          | 93Y20              | 12J21C           | 86 Y30         | 12J04C           |

| 18  | 40000 - 47777                  | 12A23          | 93Y40              | 12J16B           | 86Y40          | 12J05C           |

| 18  | 50000 - 57777                  | 12A23          | 93Y50              | 12J13F           | 86Y50          | 12 J06C          |

| 18  | 60000 - 67777                  | 12A23          | 93Y70              | 12J28G           | 86Y60          | 12J07C           |

| 18  | 70000 - 77777                  | 12A23          | 93Y60              | 12J34C           | 86Y70          | 12J08C           |

| 19  | 00000 - 07777                  | 12A18          | 93Y01              | 12J13B           | 66Y01          | 12J01C           |

| 19  | 10000 - 17777                  | 12A18          | 93Y11              | 12J10F           | 86Y11          | 12 J02C          |

| 19  | 20000 - 27777                  | 12A18          | 93Y31              | 12J25G           | 86Y21          | 12J03C           |

| 19  | 30000 - 37777                  | 12A18          | 93Y21              | 12J31C           | 86Y31          | 12J04C           |

| 19  | 40000 - 47777                  | 12A24          | 93Y41              | 12J16B           | 86Y41          | 12J05C           |

| 19  | 50000 - 57777                  | 12A24          | 93Y51              | 12J13F           | 85¥51          | 12J06C           |

| 19  | 60000 - 67777                  | 12A24          | 93Y71              | 12J28G           | 86Y61          | 12J07C           |

| 19  | 70000 - 77777                  | 12A24          | 93Y61              | 12 <b>J34C</b>   | 86Y71          | 12J08C           |

|     |                                |                |                    |                  |                |                  |

| L   |                                |                |                    |                  |                |                  |

Table 5-2

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS (CONT.)

| BIT | ADDRESS       | CORE PLANE    | SENSE<br>AMPLIFIER | LOCATION       | INHIBIT        | LOCATION |

|-----|---------------|---------------|--------------------|----------------|----------------|----------|

| 20  | 00000 - 07777 | 12A19         | 93Y02              | 12J14B         | 86Y02          | 12J01C   |

| 20  | 10000 - 17777 | 12A19         | 93¥12              | 12J11F         | 86Y12          | 12J02C   |

| 20  | 20000 - 27777 | 12A19         | 93Y32              | 12J26G         | 86Y22          | 12 J03C  |

| 20  | 30000 - 37777 | 12A19         | 93Y22              | 12J32C         | 86Y32          | 12J04C   |

| 20  | 40000 - 47777 | 12A25         | 93Y42              | 12J17B         | 86Y42          | 12 J05C  |

| 20  | 50000 - 57777 | 12A25         | 93Y52              | 12J14G         | 86Y52          | 12J06C   |

| 20  | 60000 - 67777 | 12A25         | 93¥72              | 12 <b>J29G</b> | 86Y62          | 12J07C   |

| 20  | 70000 - 77777 | 12A25         | 93Y62              | 12 J35C        | 86Y72          | 12J08C   |

| 21  | 00000 - 07777 | 12A20         | 93403              | 12J14B         | 86Y03          | 12 J09C  |

| 21  | 10000 - 17777 | 12A20         | 93¥13              | 12J11F         | 86Y13          | 12J10C   |

| 21  | 20000 - 27777 | 12A20         | 93Y33 .            | 12 J26G        | 86Y23          | 12J11C   |

| 21  | 30000 - 37777 | 12A10         | 93Y23              | 12J32C         | 86Y33          | 12J12C   |

| 21  | 40000 - 47777 | 12A26         | 93¥43              | 12J17B         | 86¥43          | 12J13C   |

| 21  | 50000 - 57777 | 12A26         | 93¥53              | 12J14G         | 86Y53          | 12J10B   |

| 21  | 60000 - 67777 | 12A26         | 93¥73              | 12J29G         | 86¥63          | 12J11B   |

| 21  | 70000 - 77777 | 12A26         | 93¥63              | 12 J35C        | 86473          | 12J12B   |

| 22  | 00000 - 07777 | 12A21         | 93Y04              | 12J15B         | 86Y04          | 12J09C   |

| 22  | 10000 - 17777 | 12A21         | 93Y14              | 12J12F         | 86Y14          | 12J10C   |

| 22  | 20000 - 27777 | 12A21         | 93Y34              | 12J27G         | 86Y24          | 12J11C   |

| 22  | 30000 - 37777 | 12A21         | 93Y24              | 12 <b>J33C</b> | 86Y34          | 12J12C   |

| 22  | 40000 - 47777 | 12A27         | 93Y44              | 12J18B         | 86Y44          | 12J13C   |

| 22  | 50000 - 57777 | 12A27         | 93Y54              | 12J15G         | 86Y54          | 12J10B   |

| 22  | 60000 - 67777 | 12A27         | 93Y74              | 12J30G         | 86Y64          | 12J11B   |

| 22  | 70000 - 77777 | 12A2 <b>7</b> | 93Y64              | 12J36C         | 86Y74          | 12J12B   |

| 23  | 00000 - 07777 | 12A22         | 93Y05              | 12J15B         | 86Y05          | 12J09C   |

| 23  | 10000 - 17777 | 12A22         | 93Y15              | 12J12F         | 86Y15          | 12J10C   |

| 23  | 20000 - 27777 | 12A22         | 93Y35              | 12J27G         | 86Y25          | 12J11C   |

| 23  | 30000 - 37777 | 12A22         | 93Y25              | 12 J33C        | 86Y35          | 12J12C   |

| 23  | 40000 - 47777 | 12A28         | 93¥45              | 12J18B         | 86Y45          | 12J13C   |

| 23  | 50000 - 57777 | 12A28         | 93¥55              | 12J15G         | 86Y55          | 12J10B   |

| 23  | 60000 - 67777 | 12A28         | 93¥ <b>7</b> 5     | 12J30G         | <b>86Y6</b> 5  | 12J11B   |

| 23  | 70000 - 77777 | 12A28         | 93Y65              | 12 J36C        | 86Y <b>7</b> 5 | 12J12B   |

|     |               |               |                    |                |                |          |

|     |               |               |                    |                |                |          |

ORIGINAL

$z_{i} \geq -z^{i}$

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS (CONT.)

| BIT | ADDRESS               | CORE PLANE | SENSE<br>AMPLIFIER | LOCATION             | INHIBIT        | LOCATION        |

|-----|-----------------------|------------|--------------------|----------------------|----------------|-----------------|

| 24  | 00000 - 07777         | 13A17      | 93Y00              | 13J13B               | 86Y00          | 13J01C          |

| 24  | 10000 - 17777         | 13A17      | 93Y10              | 13J10F               | 86Y10          | 13J02C          |

| 24  | 20000 - 27777         | 13A17      | 93Y30              | 13J25G               | 86Y20          | 13J03C          |

| 24  | 30000 - 37777         | 13A17      | 93Y20              | 13J21C               | 86Y30          | 13J04C          |

| 24  | 40000 - 47777         | 13A23      | 93Y40              | 13J16B               | 86Y40          | 13J05C          |

| 24  | 50000 - 57777         | 13A23      | 93Y50              | 13 <sup>:</sup> J13F | 86¥50          | 13J06C          |

| 24  | 60000 - 67777         | 13A23      | 93¥70              | 13J28G               | 86Y60          | 13J07C          |

| 24  | 70000 - 77777         | 13A23      | 93460              | 13J34C               | 86Y70          | 13 <b>J</b> 08C |

| 25  | 00000 - 07777         | 13A18      | 93Y01              | 13J13B               | 86Y01          | 13J01C          |

| 25  | 10000 - 17777         | 13A18      | 93Y11              | 13J10F               | 86Y11          | 13J02C          |

| 25  | 20000 - 27777         | 13A18      | 93Y31              | 13J25G               | 86Y21          | 13 <b>J03C</b>  |

| 25  | 30000 - 37777         | 13A18      | 93Y21              | 13 <b>J</b> 31C      | 86Y31          | 13J04C          |

| 25  | 40000 - 47777         | 13A24      | 93Y <b>4</b> 1     | 13J16B               | 86Y41          | 13J05C          |

| 25  | 50000 - 57777         | 13A24      | 93Y51              | 13J13F               | 86Y51          | 13J06C          |

| 25  | 60000 - 67777         | 13A24      | 93Y71              | 13J28G               | 86Y61          | 13J07C          |

| 25  | 70000 - <b>77</b> 777 | 13A24      | 93Y61              | 13J34C               | 86Y71          | 13J08C          |

| 26  | 00000 - 07777         | 13A19      | 93Y02              | 13J14B               | 86Y02          | 13J01C          |

| 26  | 10000 - 17777         | 13A19      | 93Y12              | 13J11F               | 86J12          | 13J02C          |

| 26  | 20000 - 27777         | 13A19      | 93Y32              | 13J26G               | 86Y22          | 13 J03C         |

| 26  | 30000 - 37777         | 13A19      | 93Y22              | 13J32C               | 86Y32          | 13J04C          |

| 26  | 40000 - 47777         | 13A25      | 93Y42              | 13J17B               | 86Y42          | 13J05C          |

| 26  | 50000 - 57777         | 13A25      | 93Y52              | 13J14G               | 86Y52          | 13J06C          |

| 26  | 60000 - 67777         | 13A25      | 93Y72              | 13J29G               | 86Y62          | 13J07C          |

| 26  | 70000 - 77777         | 13A25      | 93¥62              | 13J35C               | 86Y72          | 13J08C          |

| 27  | 00000 - 07777         | 13A20      | 93403              | 13J14B               | 86Y03          | 13J09C          |

| 27  | 10000 - 17777         | 13A20      | 93¥13              | 13J11F               | 86Y13          | 13J10C          |

| 27  | 20000 - 27777         | 13A2O      | 93¥33              | 13J26G               | 86Y23          | 13J11C          |

| 27  | 30000 - 37777         | 13A20      | 93Y23              | 13J32C               | 86Y33          | 13J12C          |

| 27  | 40000 - 47777         | 13A26      | 93¥43              | 13J1 <b>7</b> B      | 86Y43          | 13J13C          |

| 27  | 50000 - 57777         | 13A26      | 93¥53              | 13J14G               | 86¥53          | 13J10B          |

| 27  | 60000 - 67777         | 13A26      | 93Y73              | 13J29G               | 86Y63          | 13J11B          |

| 27  | 70000 - 77777         | 13A26      | 93Y63              | 13J35C               | 86Y <b>7</b> 3 | 13J12B          |

|     |                       |            |                    |                      |                |                 |

| L   |                       |            |                    |                      |                |                 |

TABLE 5-2. BIT ASSOCIATED CIRCUITS AND CIRCUIT LOCATIONS (CONT.)

| BIT | ADDRESS       | CORE PLANE | SENSE<br>AMPLIFIER | LOCATION        | INHIBIT | LOCATION |

|-----|---------------|------------|--------------------|-----------------|---------|----------|

| 28  | 00000 - 07777 | 13A21      | 93Y04              | 13J15B          | 86Y04   | 13J09C   |

| 28  | 10000 - 17777 | 13A21      | 93Y14              | 13J12F          | 86Y14   | 13J10C   |

| 28  | 20000 - 27777 | 13A21      | 93Y34              | 13J27G          | 86Y24   | 13J11C   |

| 28  | 30000 - 37777 | 13A21      | 93Y24              | 13J33C          | 86Y34   | 13J17C   |

| 28  | 40000 - 47777 | 13A27      | 93Y44              | 1 <b>3</b> J18B | 86Y44   | 13J13C   |

| 28  | 50000 - 57777 | 13A27      | 93Y54              | 13J15G          | 86¥54   | 13J10B   |

| 28  | 60000 - 67777 | 13A27      | 93¥74              | 13J30G          | 86Y64   | 13J11B   |

| 28  | 70000 - 77777 | 13A27      | 93¥64              | 13J36C          | 86Y74   | 13J12B   |

| 29  | 00000 - 07777 | 13A22      | 93Y05              | 13J15B          | 86Y05   | 13J09C   |

| 29  | 10000 - 17777 | 13A22      | 93Y15              | 13J12F          | 86Y15   | 13J10C   |

| 29  | 20000 - 27777 | 13A22      | 93Y35              | 13J27G          | 86Y25   | 13J11C   |

| 29  | 30000 - 37777 | 13A22      | 93Y25              | 13J33C          | 86Y35   | 13J12C   |

| 29  | 40000 - 47777 | 13A28      | 93Y45              | 13J18B          | 86Y45   | 13J13C   |

| 29  | 50000 - 57777 | 13A28      | <b>93</b> ¥55      | 13J15G          | 86Y55   | 13J10B   |

| 29  | 60000 - 67777 | 13A28      | 93175              | 13J30G          | 86Y65   | 13J11B   |

| 29  | 70000 - 77777 | 13A28      | 93Y65              | 13J36C          | 86Y75   | 13J12B   |

|     |               |            |                    |                 |         |          |

NOTE: In address block 00000 - 07777 addresses 100 - 177 and 540 - 577 are not used in core memory.

$(\underline{b})$  K CONTROL TEST. - The function of this program is to test the transmission paths as they are called for by the different k translations. Separate test routines have been included for testing each of the three classes of instructions, the Read, Store and Replace instructions.

(<u>c</u>) COMMAND TEST. - The function of this program is to test the subcommand paths from main control used in the execution of each instruction. In general, the common paths consist of a function code translation, j evaluation, and k designator determination.

(<u>d</u>) CONTROL TEST. - This program checks the transmission lines associated with the R, B, ZØ, UL and B register, UL and control adder, the SØ and U register, the Z and S register, and the 71 instruction; and it evaluates the b designator in the instruction word.

(e) ARITHMETIC TEST. - The objective of this test is to check interregister transmission lines in the arithmetic section, the arithmetic subtractor, and other matrix operations.

### CP-642B/USQ-20(V) COMPUTER

### NAVSHIPS 0967-280-4030

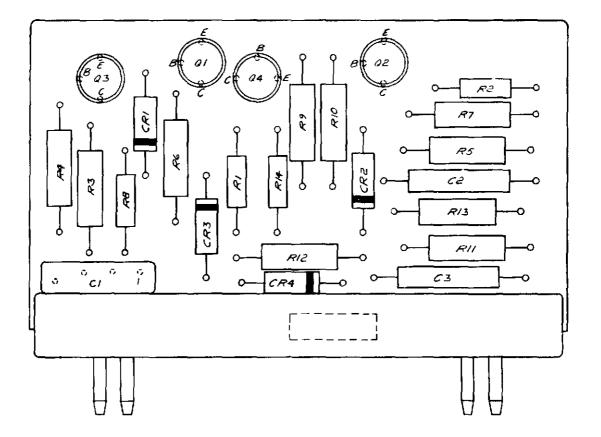

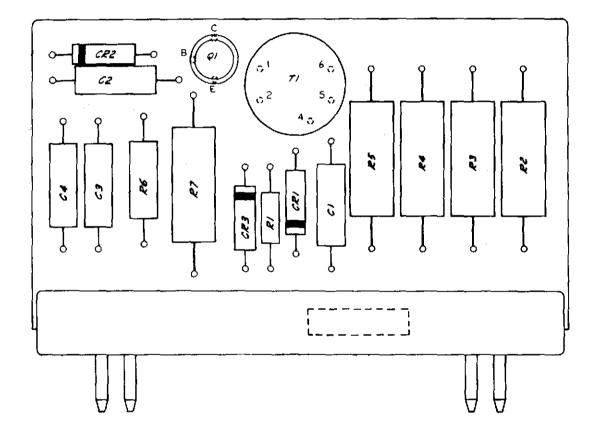

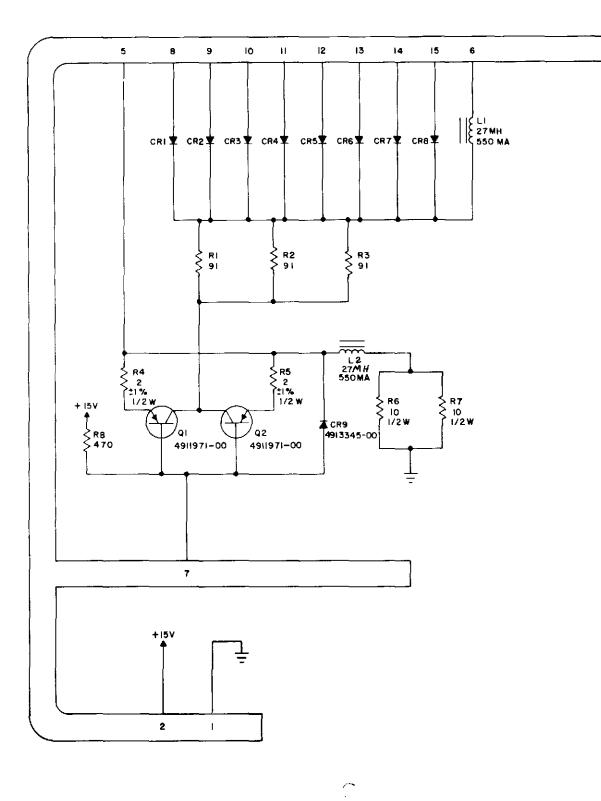

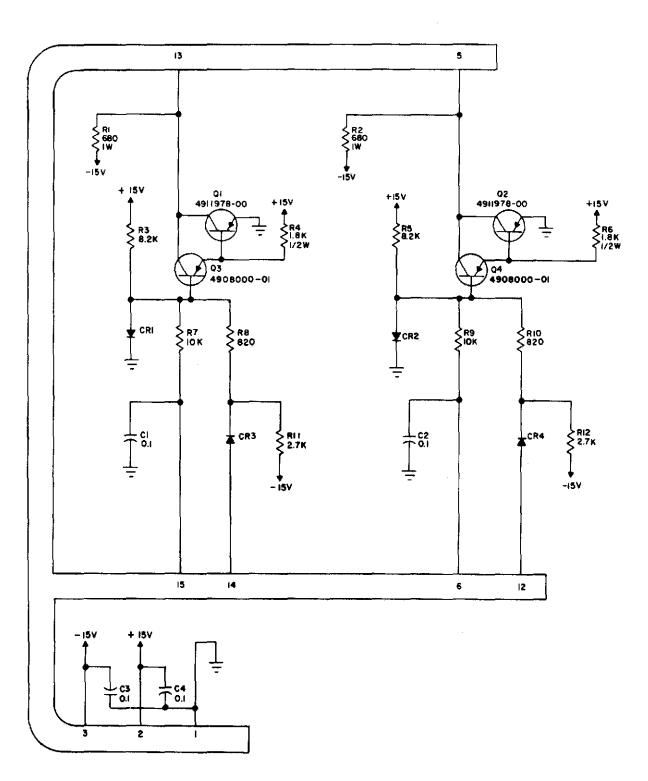

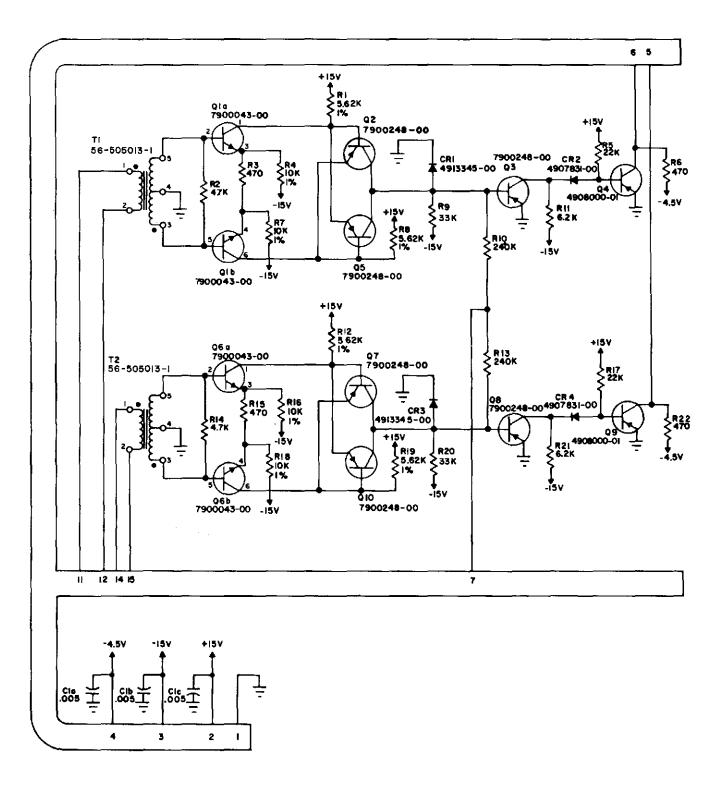

Figure 5-3

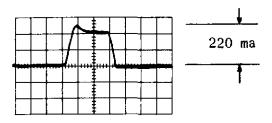

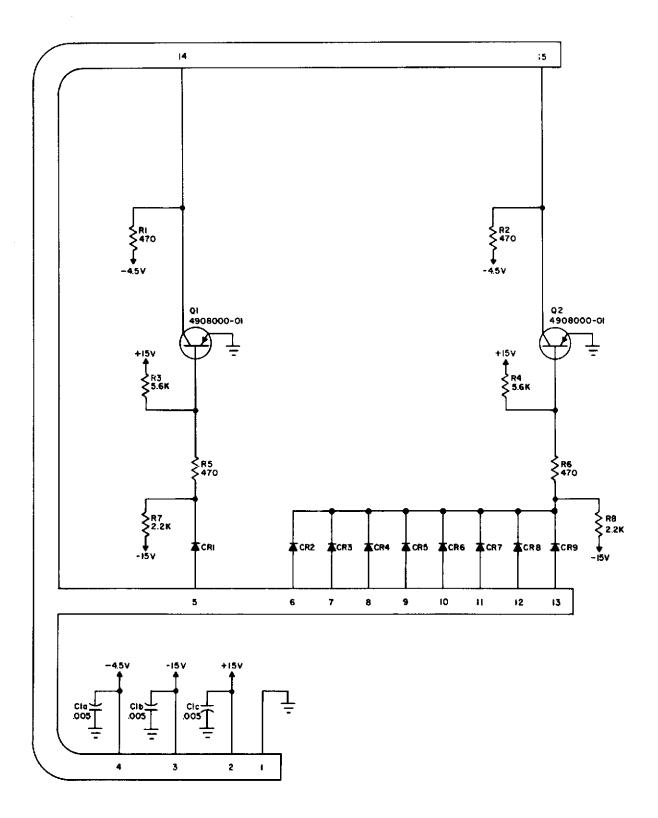

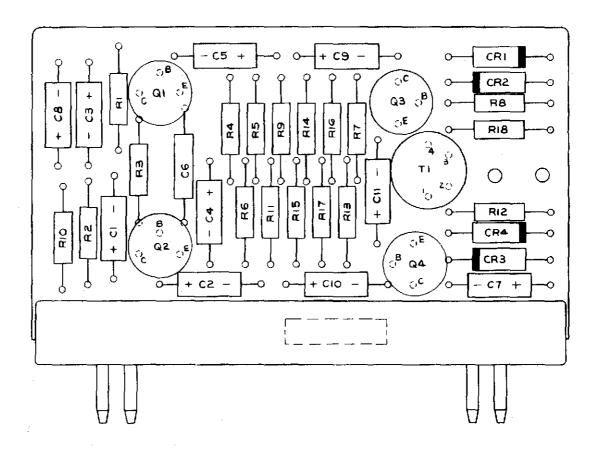

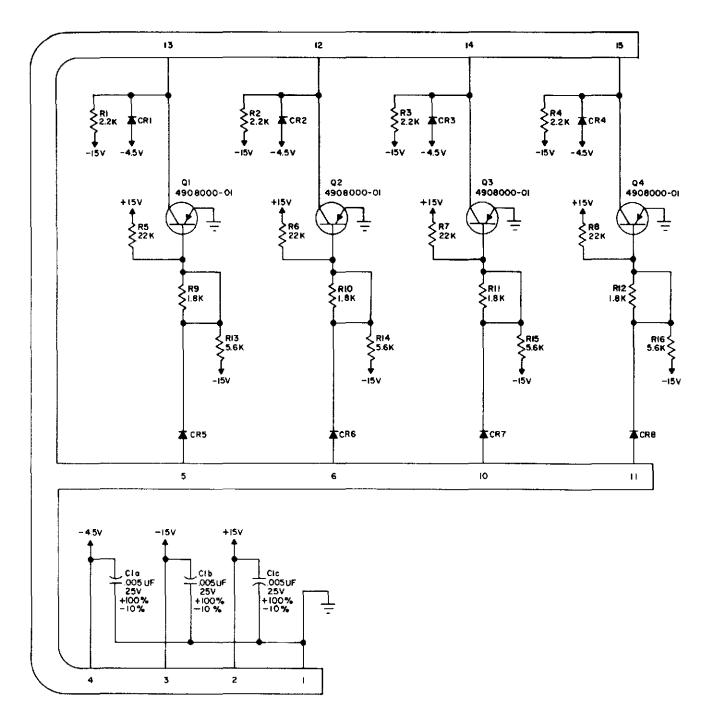

- A. INHIBIT CURRENT

- 1. Oscilloscope settings using type CA Preamplifier. Channel A switch to .1 VOLTS/CM Channel B switch to 15 VOLTS/CM TIME/CM switch to .5 usec MODE switch to ALTERNATE

- Connect a jumper between TB05F1 and F3.

- Connect a P6016 current probe to Channel A input with a P6016 termination and attached to jumper in step 2. Do not ground.

- Connect a voltage probe to channel B input and attach to TB05F1. Connect shield lead to ground.

C. X READ DIVERTER OUTPUT

- 1. Oscilloscope settings using type

CA Preamplifier.

Channel B switch to 5 VOLTS/CM

TIME/CM switch to 1 usec

- 2. Connect voltage probe to channel B input and attach to TB6M3.

- 3. Y diverter outputs are identical.

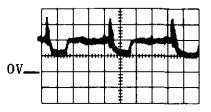

B. INHIBIT CURRENT

- Oscilloscope settings using type CA Preamplifier. Channel A switch to .1 VOLTS/CM TIME/CM switch to 1 usec

- Connect a P6016 current probe to Channel A input with a P6016 termination and attach to inhibit line, such as 86Y00 pin 1 which is inaccessible when the chassis is plugged in.

- D. X WRITE DIVERTER OUTPUT

- Oscilloscope settings using type CA Preamplifier. Channel B switch to 5 VOLTS/CM TIME/CM switch to 1 usec

- 2. Connect voltage probe to channel B input and attach to TB6M8.

- 3. Y diverter outputs are identical.

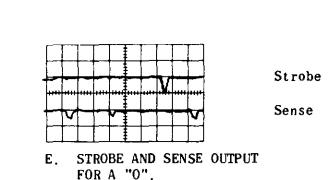

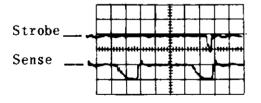

Strobe

Sense

CYCLING A SINGLE ADDRESS

- Oscilloscope settings using type CA Preamplifier. Channel A switch to 5 VOLTS/CM Channel B switch to 5 VOLTS/CM TIME/CM switch to .5 usec/CM MODE switch to ALTERNATE

- 2. Memory margins on NORMAL.

- Connect a voltage probe to channel A input and attach to strobe TB05E7 or E8.

- 4. Connect a voltage probe to channel B input and attach to sense amplifier TBO8M1 through M6.

G. X READ-WRITE WAVEFORM

- Oscilloscope settings using type CA Preamplifier. Channel A switch to .1 VOLTS/CM TIME/CM switch to .5 usec/CM

- 2. Connect P6016 current probe to Channel A input with a P6016 termination. Attach current probe to several X drive lines on end board.

- F. STROBE AND SENSE OUTPUT FOR A "1". CYCLING A SINGLE ADDRESS

- 1. Oscilloscope settings using type CA Preamplifier. Channel A switch to 5 VOLTS/CM Channel B switch to 5 VOLTS/CM TIME/CM switch to .5 usec/CM MODE switch to ALTERNATE

- 2. Memory margins on NORMAL.

- Connect a voltage probe to channel A input and attach to strobe TB05E7 or E8.

- Connect a voltage probe to channel B and attach to a sense amplifier TBO8M1 through M6.

|   | ł |        |   |  |       |   |        |  |

|---|---|--------|---|--|-------|---|--------|--|

|   |   |        |   |  | أسبيا |   |        |  |

| 7 |   | <br>T. |   |  |       | J |        |  |

|   |   |        |   |  |       |   |        |  |

|   |   |        | _ |  |       |   | $\Box$ |  |

H. X READ ONLY WAVEFORM

- Oscilloscope settings using type CA Preamplifier. Channel A switch to .1 VOLTS/CM TIME/CM switch to .5 usec/CM

- Connect P6016 current probe to a single X drive line on the end board.

Figure 5-3. Main Memory, Typical Waveforms (Cont.)

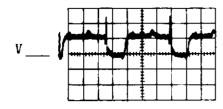

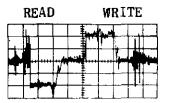

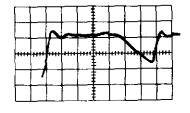

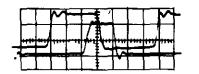

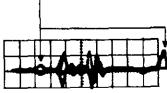

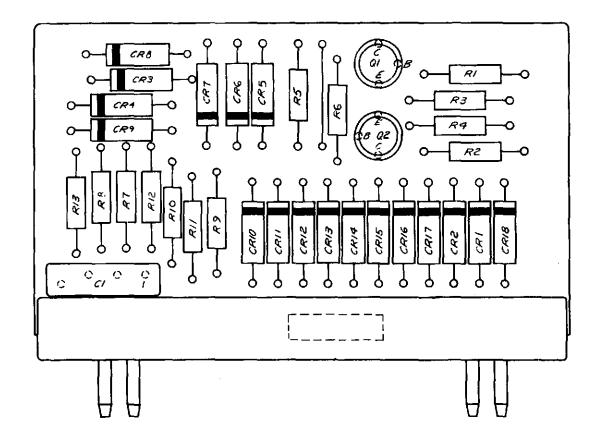

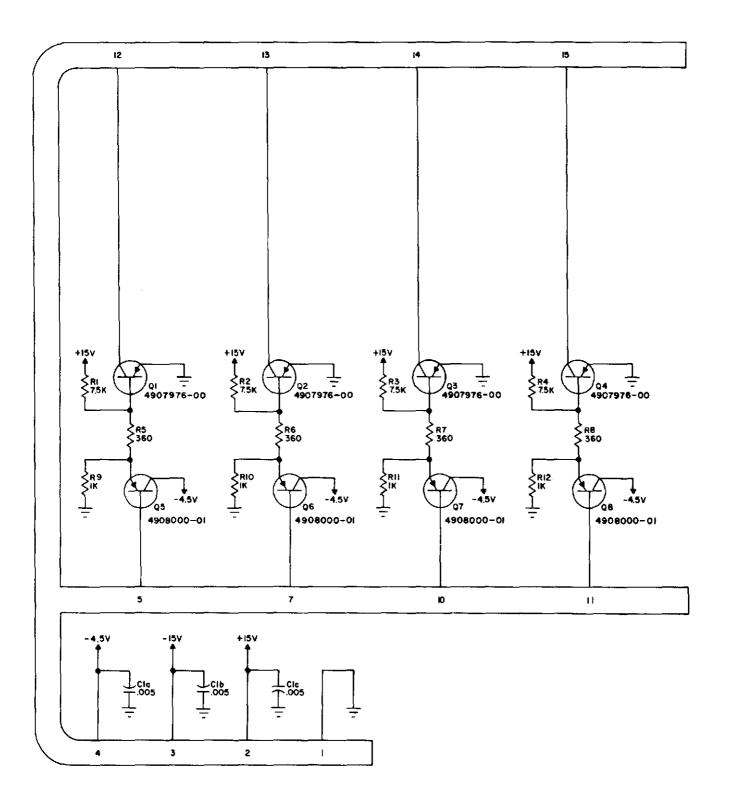

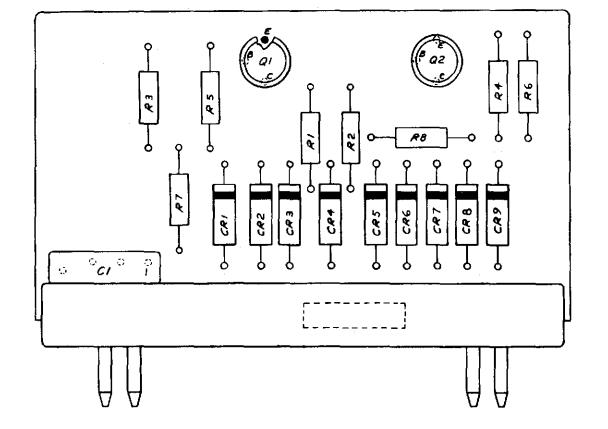

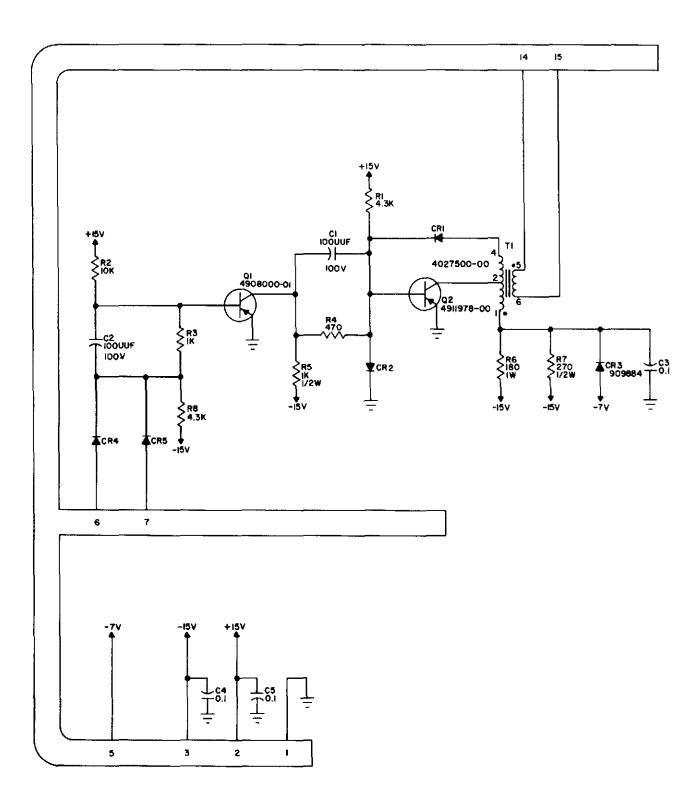

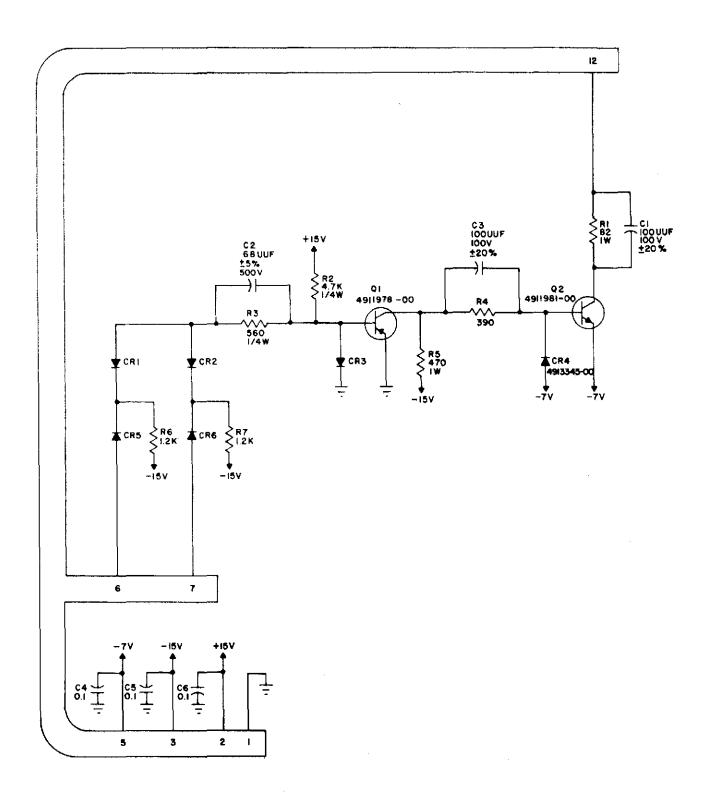

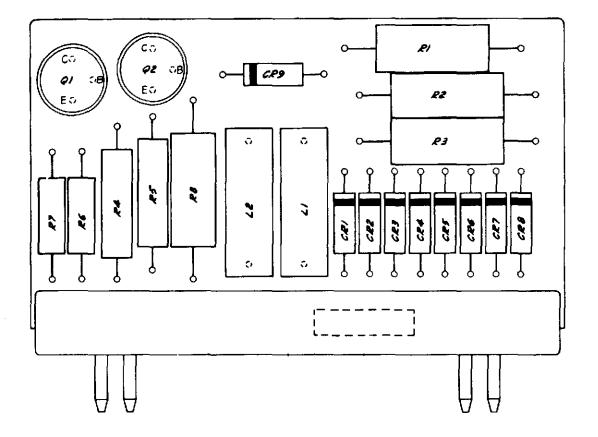

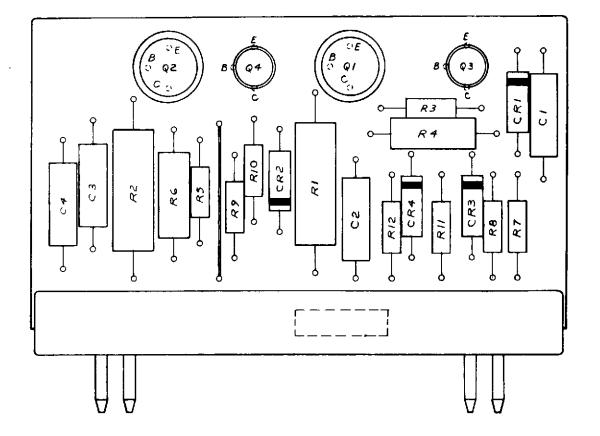

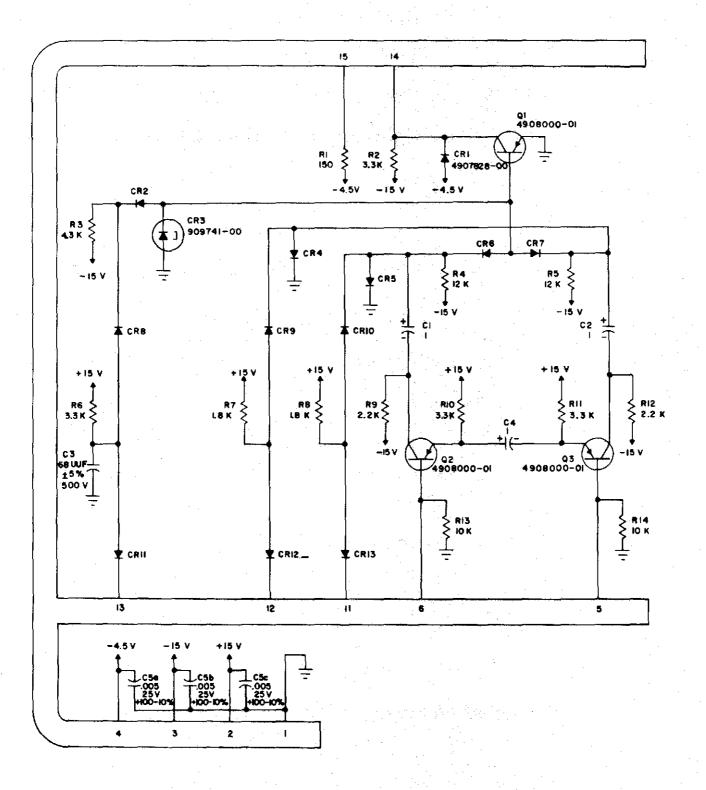

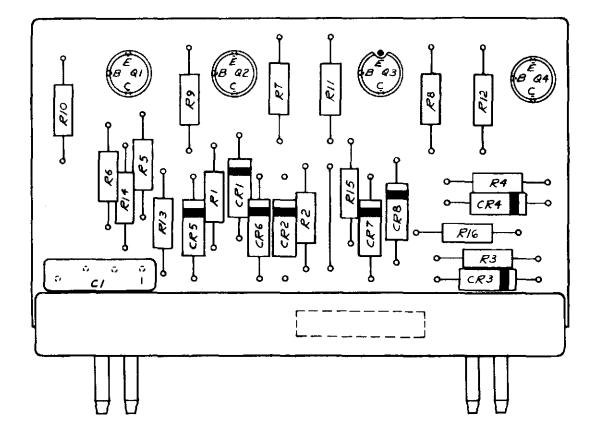

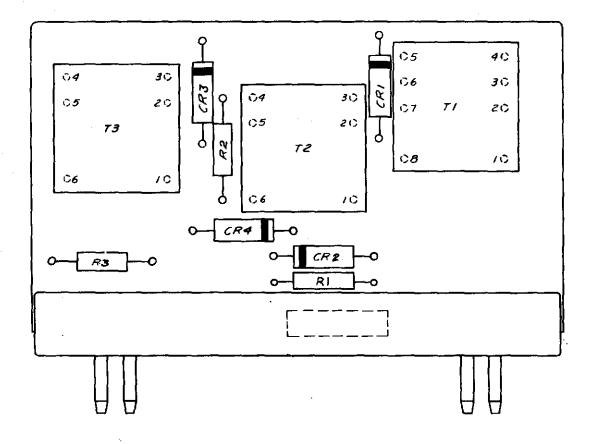

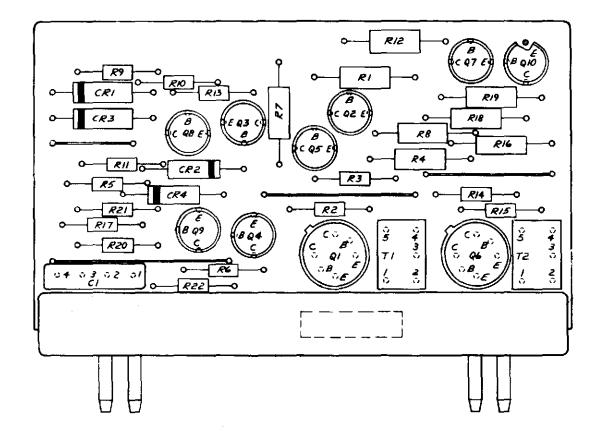

- A. SHORTED X DRIVE LINE CYCLING SINGLE ADDRESS

- Oscilloscope settings using type CA Preamplifier. Channel A switch to 5 VOLTS/CM

TIME/CM switch to 1 usec/CM

- C. SHORTED X DRIVE LINE CYCLING ALL ADDRESSES

- 1. Oscilloscope settings using type CA Preamplifier Channel A switch to 5 VOLTS/CM TIME/CM switch to 1 usec/CM

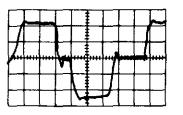

E. BAD "1" OUTPUT

- 1. Oscilloscope settings using type CA Preamplifier. Channel A switch to 5 VOLTS/CM Channel B switch to 5 VOLTS/CM TIME/CM switch to .5 usec/CM

- 2. Memory margins to NORMAL.

- 3. Note the width of the output pulse and the fact that the strobe hits on the return swing which occurs too early.

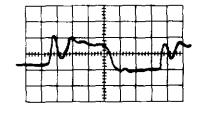

- B. OPEN X DRIVE LINE CYCLING SINGLE ADDRESS

- Oscilloscope settings using type CA Preamplifier.

Channel A switch to 5 VOLTS/CM TIME/CM switch to 1 USEC/CM

- D. OPEN X DRIVE LINE CYCLING ALL ADDRESSES

- 1. Oscilloscope settings using type CA Preamplifier

- Channel A switch to 5 VOLTS/CM TIME/CM switch to 1 usec/CM

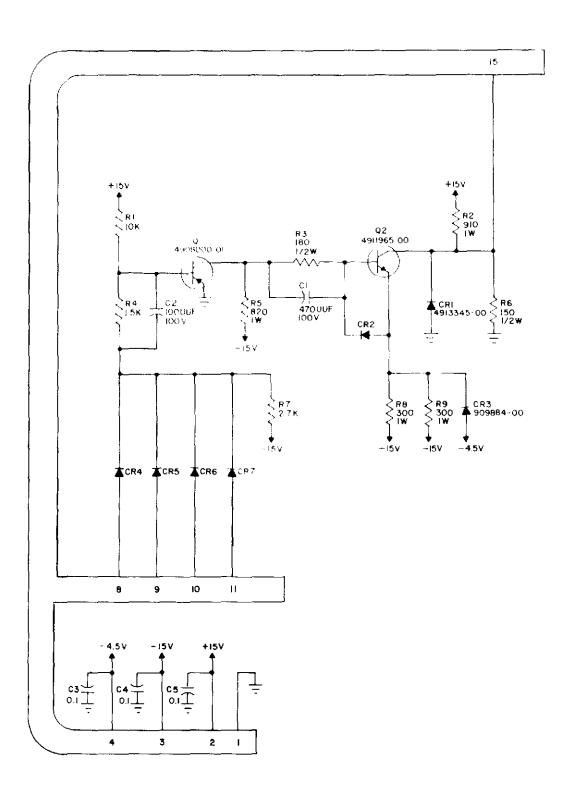

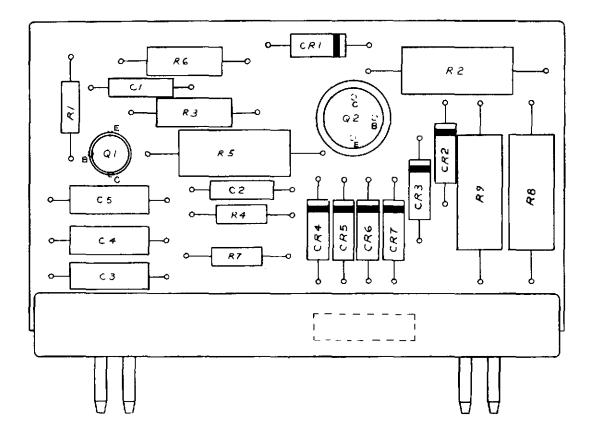

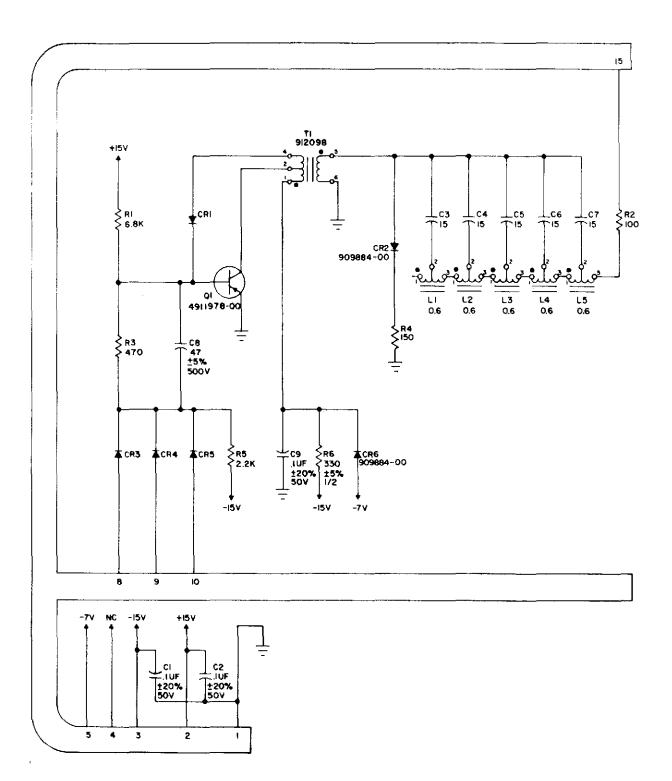

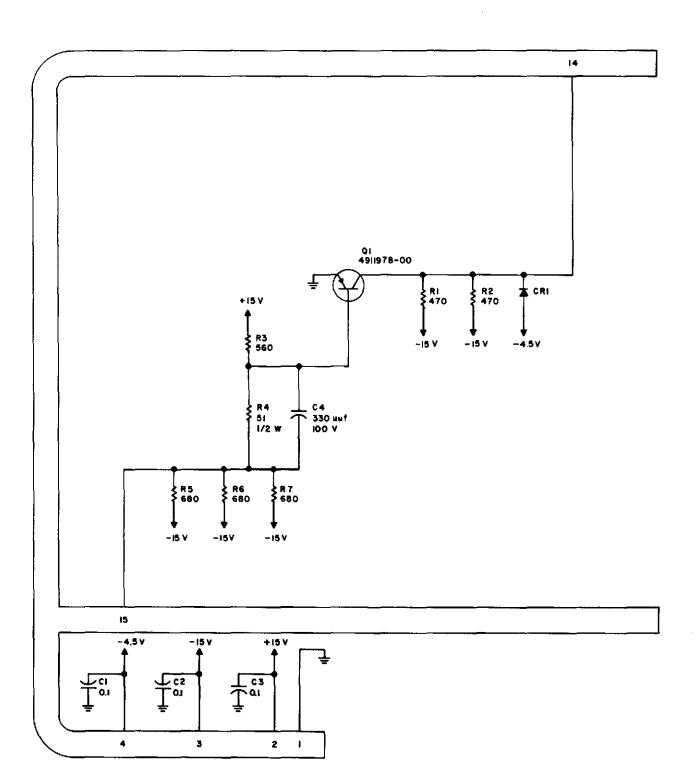

### Figure 5-5. Control Memory Words, Diagram of Bit Locations

(<u>f</u>) INPUT/OUTPUT TEST. - The objective of this program is to exercise and test the input/output section of the computer. Separate routines are included to test the various functions in the input/output section such as data transmissions, buffer operation, buffer termination, and external and internally generated interrupts.

(2) MEMORY. - These tests verify that the individual addresses can be manually altered and that the memory is functioning and insensitive to internally generated noise from the worst patterns in the memory. They also verify the core read marginal checking feature and that the memory circuits are capable of operating under the highest possible repetition rate.

(a) MAGNETIC CORE MEMORY.

1. BRAINWASH. - The brainwash program tests the capability of the main memory section of the computer to accept and retain various bit configurations. Seven patterns are used in the test, the final pattern generating the maximum amount of noise in the magnetic core matrix sense winding. The test is diagnostic in that individually failing bits in the memory array are located exactly and associated with a specific test. When using the program, the memory is considered to be divided into two frames of 16,384 bits each. The frames are further divided into quadrants of 4,096 bits each. The program tests each quadrant as an individual memory unit. The division is justified by the fact that each sense winding encompasses a volume of 4,096 bits and each quadrant contains one inhibit line. Because of subdividing the memory when testing, it is possible to locate the program in any of the eight quadrants. The program starts in the second 4,0008 addresses of each quadrant of memory and is advanced 10,0008 addresses after each test sequence of a quadrant is completed. This permits operating the sense amplifiers in all combinations as well as allowing half pulses to be applied in varying combinations to the memory drive lines.

2. PROGRAM 55. - The 55 program determines the computer's ability to write any pattern of "1's" and "O's" into all core memory locations without using any of the memory addresses. It does not write into control memory. A unique feature of this program is that it can accomplish its duties at any cycle rate.

<u>3.</u> MEMORY CAPACITY TEST. - The memory capacity test checks core memory by causing the quantity stored at each address to be the address itself. Therefore, when read out of memory, the contents would be the same as the address.

$\underline{4}$ . MAGNETIC CORE CYCLING PROGRAM. - The cycle program permits the checking of a particular word or group of words and its associated circuitry. The program continually reads the same address so that the waveforms can be checked to isolate the malfunctioning circuit.

5. CORE READ MARGINAL CHECK. - The core read marginal check utilizes the brainwash program to check the memory under marginal conditions. By means of switches, the signals to the sense amplifiers are increased in width (low margin) or decreased in width (high margin). With an increase in width, less signal is clipped, and a greater possibility of noise being passed through the amplifier exists. With a decrease in width, more signal is being clipped, and less signal is available to the amplifier; therefore, greater sensitivity is required of the amplifier to pass the signal on.

<u>6.</u> REPETITION RATE TEST. - The repetition rate test establishes that the memory is capable of operating properly at a maximum repetition rate.

Paragraph 5-3c(2)(b)

### (b) CONTROL MEMORY.

<u>1</u>. CONTROL MEMORY TEST. - The control memory test program tests the capability of the control memory of the computer to accept and retain various bit configurations. It also checks the address location capabilities. Four patterns are used to test the memory to hold "1's", to hold "O's" and for crosstalk and complement crosstalk. During the address location test, the content of each address is set to its own address. The test is diagnostic in that failing bits are located and associated with a specific address. The failing address is displayed in Q with the failing bits in the A register. During this test all addresses in control memory are treated as 30-bit operands.

<u>2</u>. CYCLE TIME TEST. - The cycle time test checks the control memory cycle time by measuring the leading edge of a signal and the trailing edge of a signal to see that at 50 per cent amplitude the cycle time is less than 700 nanoseconds.

$\underline{3}$ . INSTRUCTION FAULT TEST. - The instruction fault test checks that an instruction cannot be read from the control memory.

(3) REAL-TIME CLOCK TEST. - The real-time clock test provides a recognizable indication of each 10-second period that the real-time clock is operating. For each 10-second period that has elapsed while the real-time clock is operative, the characters 10 SEC will be printed. If the real-time clock is inoperative for a 10-second period, the characters CLK INOP will be printed.

(4) INPUT/OUTPUT TEST. - The major I/O test is included in ECCLAT; however, this test exercises the I/O section further for a greater degree of confidence.

(5) INSTRUCTION EXECUTIVE TIME TESTS. - The instruction execution time test checks the ability of the computer to perform arithmetic functions in the prescribed time.

(6) MASTER CLOCK MARGIN TEST. - The master clock margin test checks the ability of the computer to perform any or all of the tests covered in the logic troubleshooting section, under marginal clock conditions. This is achieved by moving the delay modules of the clock and issuing clock pulses of about 120 nanosecond width (normally 150) and thus reducing the clock cycle time to about 540 nanoseconds (normally 680). Running the computer under clock margin will often reveal intermittent troubles or will indicate areas of weakness that could be future troublespots.

(7) CONSOLE CONTROL NONLOGIC TESTS. - The console control tests are a program controlled method of checking the switches and pushbutton indicators that control the computer. The various indicators associated with computer control are checked.

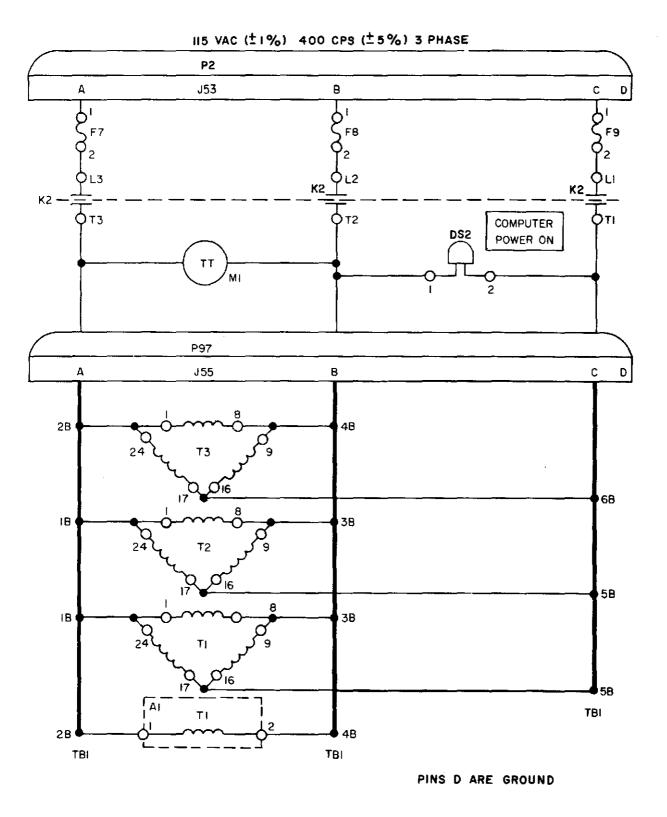

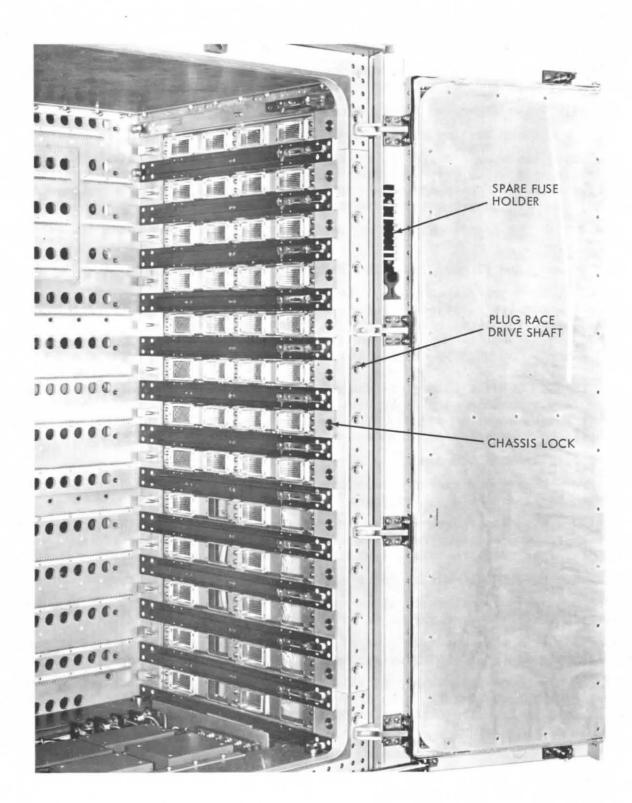

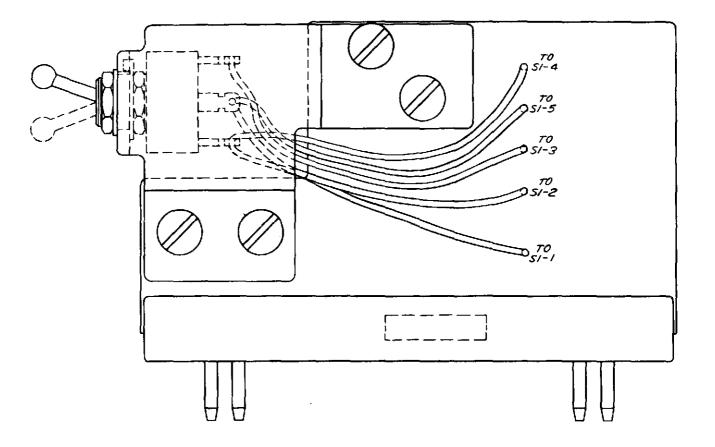

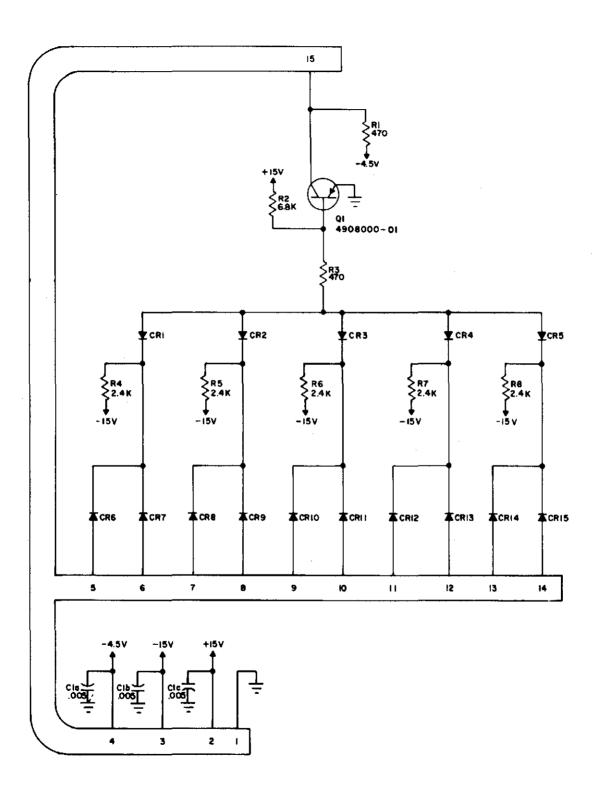

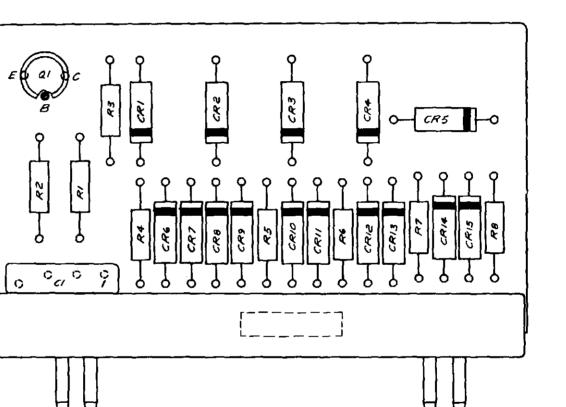

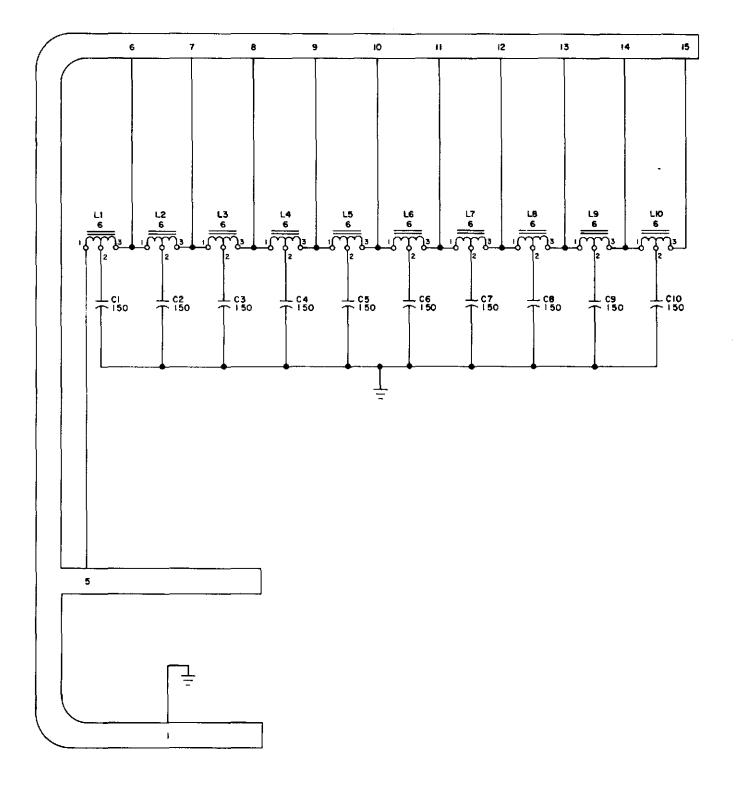

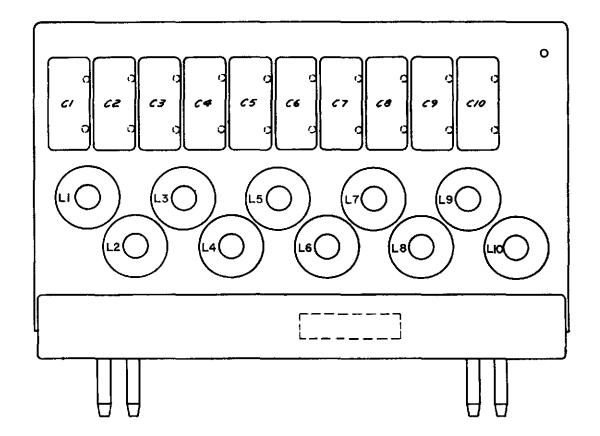

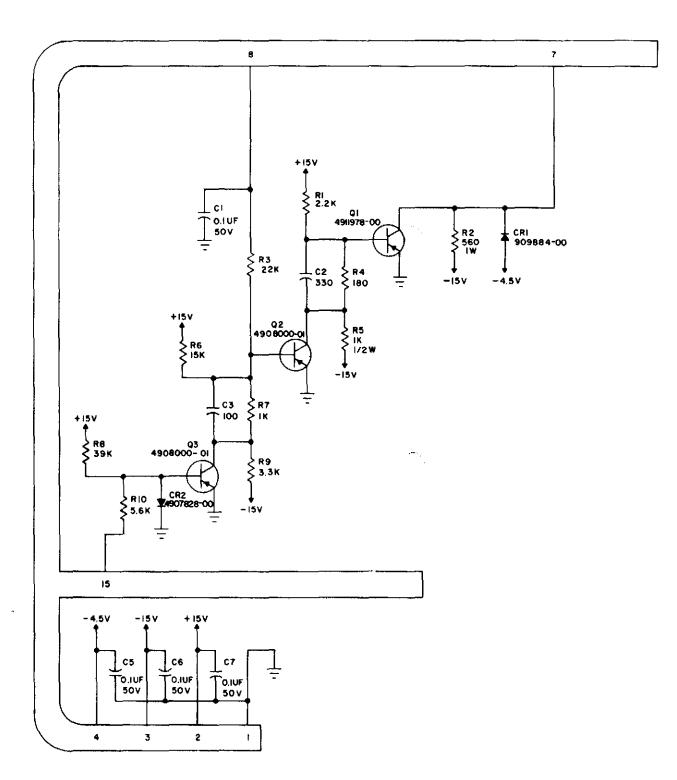

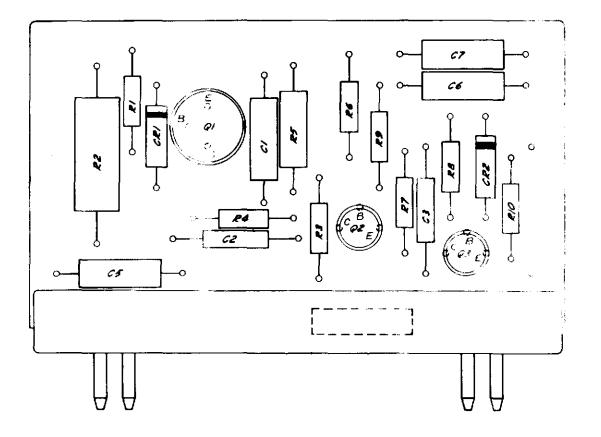

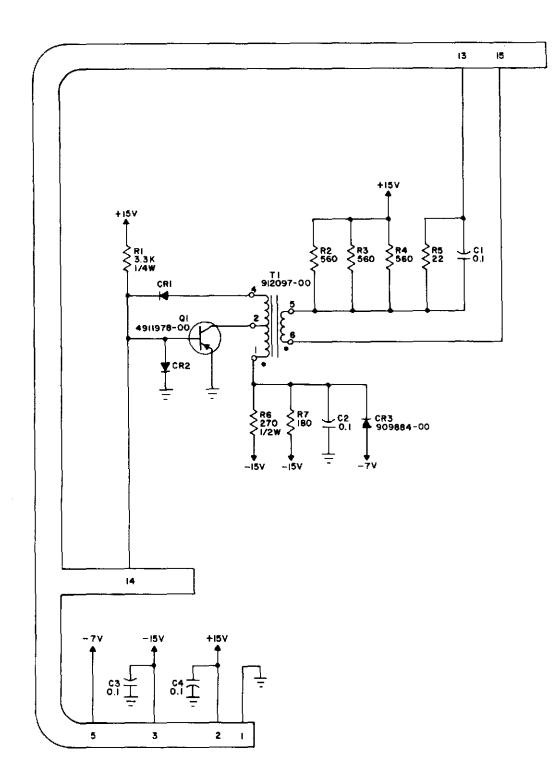

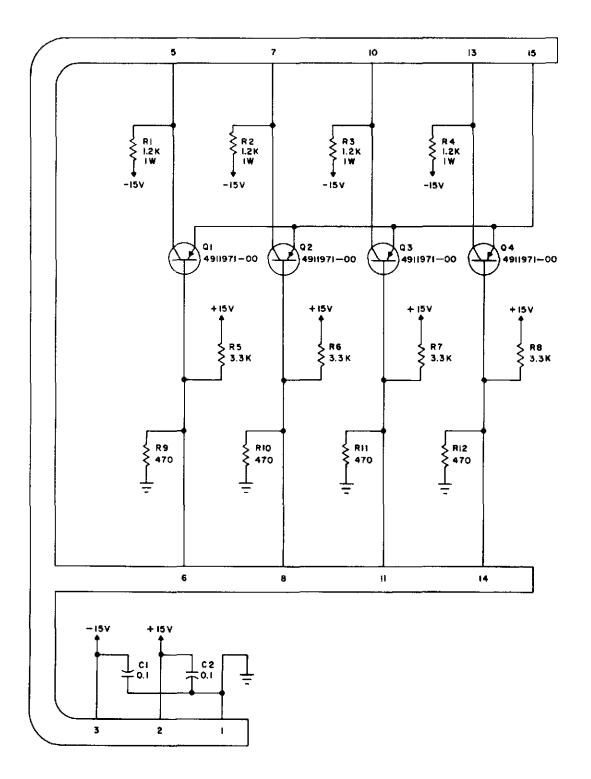

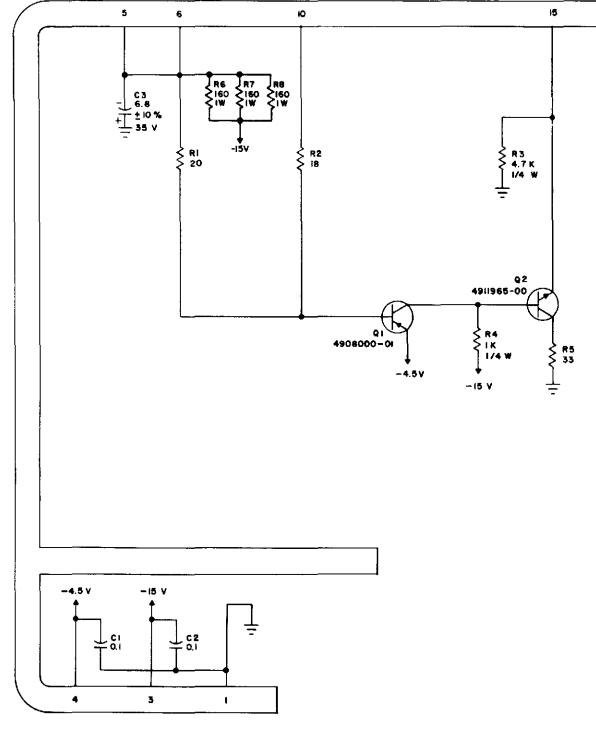

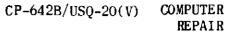

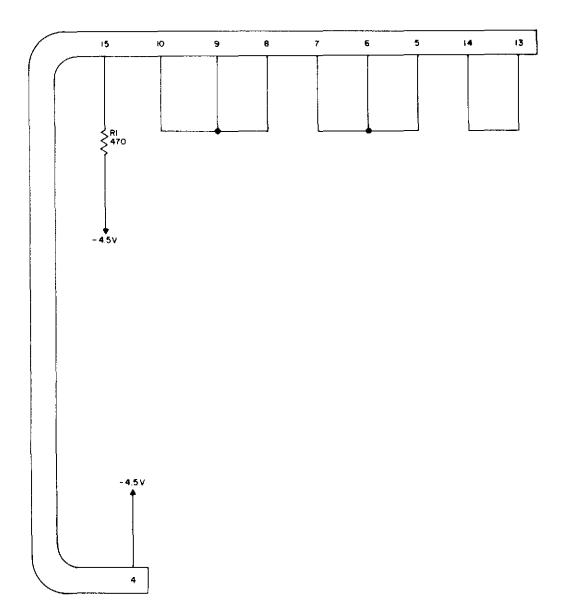

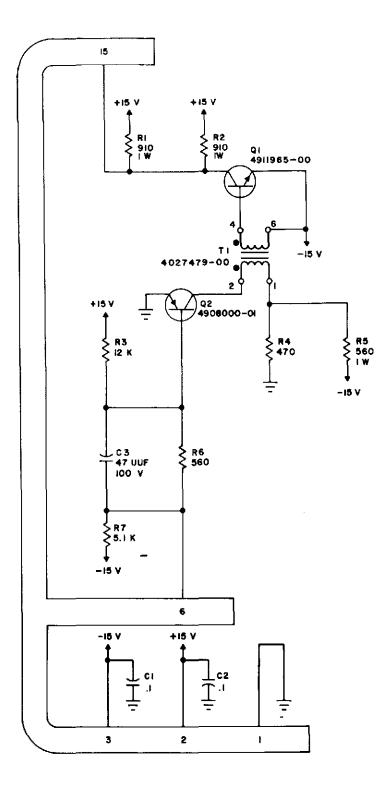

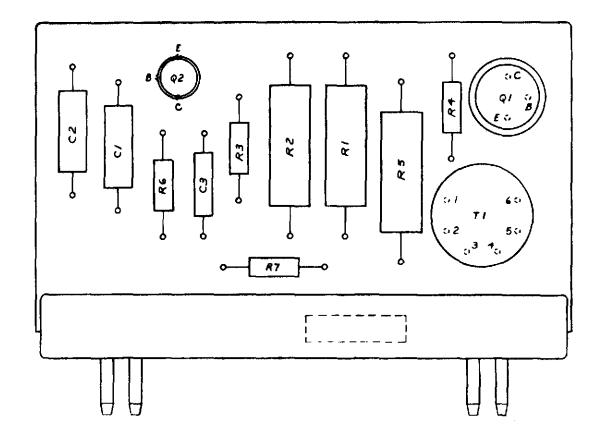

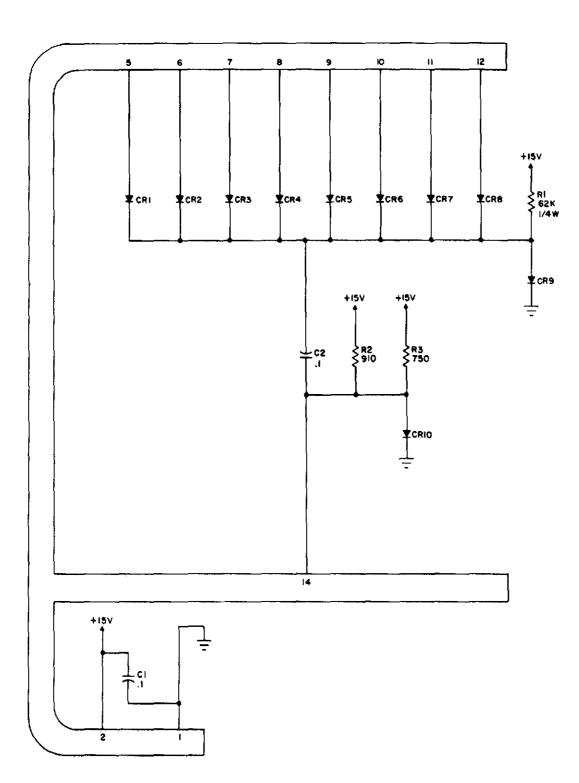

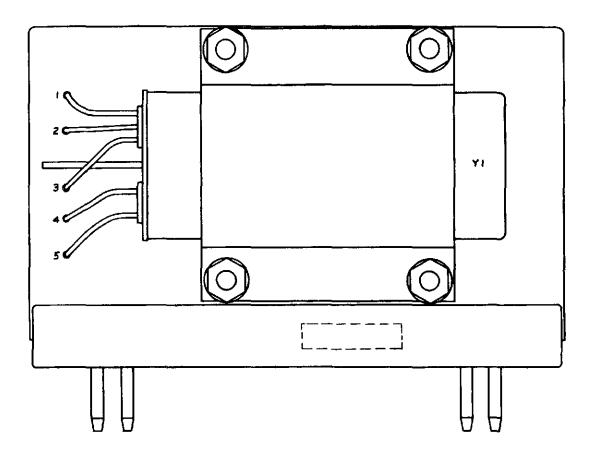

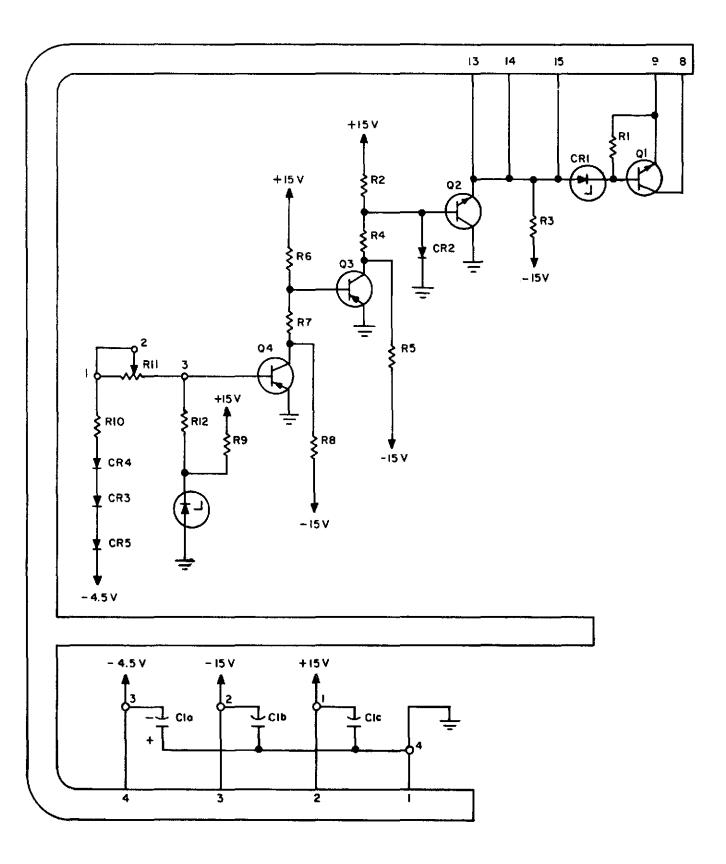

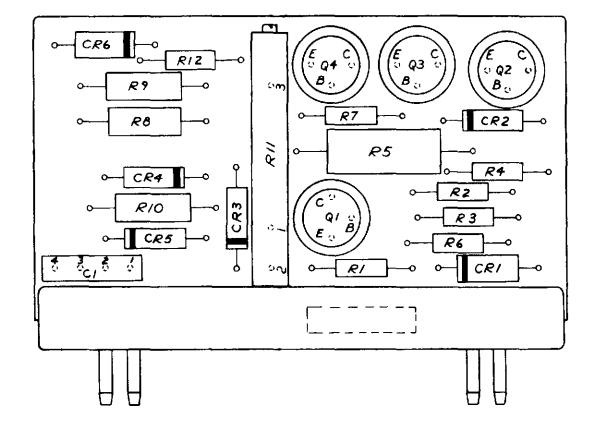

<u>d</u>. TEST PROCEDURES. - The test procedures explained in this paragraph consist of two basic operations. They are: first, the step-by-step setup which must be accomplished before specific programs begin, and, second, the step-by-step procedure to insure a valid run of the test programs. In all cases the MROT test setup must be made according to figure 5-6. Any deviations or additions to the setup are given at the beginning of each individual test. Unless otherwise stated the MROT test setup remains for all tests.

\_\_\_\_

### Figure 5-6. MROT Test Setup, Cabling Diagram

### NOTE

During the step-by-step procedures, reference is made to "Master clear the computer". Whenever this is stated, it is implied that the computer is not running (stopped). For example, the computer cannot be master cleared under control of the phase step mode or when operating at high speed. Certain procedures require that just the MASTER CLEAR pushbutton be pressed. This does not necessarily master clear the computer.

(1) ECCLAT.

STEP 1. Position the CP-642B/USQ-20(V) Utility Package Load Routine on the paper tape reader.

STEP 2. Master clear the computer.

STEP 3. Press the LOAD MODE indicator-switch.

STEP 4. Press the PROGRAM II indicator-switch.

STEP 5. Operate the START-STEP/RESTART switch to the START-STEP position. The utility package load routine enters memory.

STEP 6. Master clear the computer.

STEP 7. Position the ECCLAT program tape on the paper tape reader.

STEP 8. Set the P register to address 00001.

STEP 9. Operate the START-STEP/RESTART switch to the START-STEP position. The ECCLAT program enters the computer starting at address 04000.

STEP 10. Using the input/output jumper cables, jumper all output connectors to all input connectors with the exception of the channel used for the monitoring typewriter. Channels 0 and 1 output must be jumpered to channels 0 and 1 input respectively. All others may be intermixed.

STEP 11. Master clear the computer.

STEP 12. Set the P register to address 04000.

STEP 13. Operate the STOP 5 switch to the up position (refer to step 16).

STEP 14. Operate the START-STEP/RESTART switch to the START-STEP position. The monitoring typewriter types: ECCLAT.

STEP 15. The ECCLAT programs run continuously. To terminate the test, operate the STOP switch to the down position.

STEP 16. If an error occurs, operate the following switches to assist in defining the indications of the program result. Operate the appropriate switch to the up position to acquire the responses as follows:

JUMP 1 - The computer will not repeat the test which failed, but will go on to the next test after the error printout, if possible.

JUMP 2 - The computer repeats an individual test routine.

JUMP 3 - The computer will repeat a main program such as control test.

STOP 5 - The computer stops for visual inspection of registers before the printout in case an error has been detected.

STOP 7 - The computer stops after one execution of the ECCLAT test and is ready to re-execute the complete test.

STOP 4 - The computer will stop after the printout of an error.

STEP 17. Upon successful completion of the test, return the computer to the MROT setup as shown in figure 5-6.

(2) MEMORY TESTS.

(a) MAGNETIC CORE TESTING.

<u>1</u>. BRAINWASH.

STEP 1. Position the utility package load routine on the paper tape reader.

STEP 2. Master clear the computer.

STEP 3. Press the LOAD MODE indicator-switch.

STEP 4. Press the PROGRAM II indicator-switch.

STEP 5. Operate the START-STEP/RESTART switch to the START-STEP position. The load routine enters memory.

STEP 6. Master clear the computer.

STEP 7. Position the brainwash program on the paper tape reader.

STEP 8. Set the P register to address 00001.

STEP 9. Operate the START-STEP/RESTART switch to the START-STEP position. The brainwash program enters the computer starting at 05400.

STEP 10. Master clear the computer.

STEP 11. Set the P register to address 05400.

STEP 12. Operate the STOP 5 switch to the up position (refer to step 15).

STEP 13. Operate the START-STEP/RESTART switch to the START-STEP position. The monitoring typewriter types: BRAINWASH. At the end of a complete program cycle through the computer memory the monitoring typewriter types out: END.

STEP 14. The brainwash program will continuously cycle repeating the typeouts (refer to step 13) until terminated. To terminate, operate the STOP 6 switch to the up position.

STEP 15. If an error occurs, operate the following switches to assist in defining the indications of the program results. Operate the appropriate switch to the up position to acquire the response as follows:

JUMP 1 - Eliminates all printouts.

JUMP 2 - Cycles a major subroutine.

JUMP 3 - Cycles the complete brainwash test in the same quadrant.

STOP 5 - Error stop before printout of errors.

STOP 6 - Stop upon entrance to a major subroutine.

STOP 7 - Stop following the move of program from one quadrant to another.

STOP 4 - Any time an error is found in the generator random number (GRN) tests, the computer stops at the beginning of this test. Operating the START-STEP/RESTART switch to START-STEP re-executes the test if an error was detected while moving the program from one quadrant to the next

2, PROGRAM 55

STEP 1. Disable control memory by grounding 5TB11H4.

#### CAUTION