DATA PROCESSING DIVISION

SYSTEMS

# CARD ASSEMBLER

REFERENCE MANUAL

This manual is published by the Univac Division of Sperry Rand Corporation in loose leaf format as a rapid and complete means of keeping recipients apprised of UNIVAC® Systems developments. The information presented herein may not reflect the current status of the programming effort. For the current status of the programming, contact your local Univac Representative.

The Univac Division will issue updating packages, utilizing primarily a page-for-page or unit replacement technique. Such issuance will provide notification of hardware and/or software changes and refinements. The Univac Division reserves the right to make such additions, corrections, and/or deletions as in the judgment of the Univac Division are required by the development of its respective Systems.

# CONTENTS

| 1. | INTRODUCTION                                                                                                                                                                                                                                                             | 1-1 to 1-4                                                  |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|    | 1.1. THE PURPOSE OF AN ASSEMBLER                                                                                                                                                                                                                                         | 1-1                                                         |

|    | 1.2. CARD ASSEMBLER FOR THE UNIVAC 9200/9300                                                                                                                                                                                                                             | 1-2                                                         |

|    | 1.3. ASSEMBLY LANGUAGE CHARACTERISTICS                                                                                                                                                                                                                                   | 1-4                                                         |

| 2. | THE ASSEMBLER LANGUAGE                                                                                                                                                                                                                                                   | 2-1 to 2-15                                                 |

|    | 2.1. CHARACTER SET                                                                                                                                                                                                                                                       | 2-1                                                         |

|    | 2.2. STATEMENT FORMAT 2.2.1. Label Field 2.2.2. Operation Field 2.2.3. Operand Field 2.2.4. Comments Field                                                                                                                                                               | 2-1<br>2-1<br>2-1<br>2-1<br>2-2                             |

|    | 2.3. EXPRESSIONS 2.3.1. Decimal Representation 2.3.2. Hexadecimal Representation 2.3.3. Character Representation 2.3.4. Location Counter 2.3.5. Relative Addressing 2.3.6. Symbols 2.3.7. Relocatable and Absolute Expressions 2.3.8. Length Attribute                   | 2-2<br>2-2<br>2-3<br>2-3<br>2-3<br>2-4<br>2-4<br>2-5<br>2-6 |

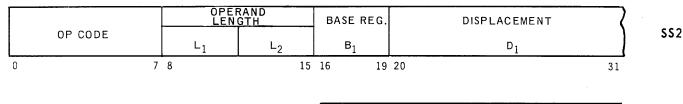

|    | <ul> <li>2.4. MACHINE INSTRUCTIONS</li> <li>2.4.1. RX - Register to Storage Instructions</li> <li>2.4.2. SI - Instruction to Storage Instructions</li> <li>2.4.3. SS1 - Storage to Storage Instructions</li> <li>2.4.4. SS2 - Storage to Storage Instructions</li> </ul> | 2-6<br>2-8<br>2-8<br>2-9<br>2-10                            |

|    | 2.5. DATA AND STORAGE FORMATS 2.5.1. DC — Define Constant 2.5.1.1. Character Representation 2.5.1.2. Hexadecimal Representation 2.5.1.3. Expression Constants 2.5.2. DS — Define Storage                                                                                 | 2-11<br>2-12<br>2-12<br>2-13<br>2-13<br>2-14                |

PAGE:

| 3.1.1 Symbol Definition 3.1.1. Symbol Definition 3.1.2. Assembly Control 3.1.2.1. START - Program Start 3.1.2.2. END - Program End 3.1.2.3. START - Program End 3.1.2.3. START - Program End 3.1.2.3. ORG - Set Location Counter 3.1.3.1. USING - Assign Base Register 3.1.3.1. USING - Assign Base Register 3.1.3.2. DROP - Unassign Base Register 3.1.3.3. Direct Addressing 3.7 3.1.4.1. Program Linking 3.7 3.1.4.2. EXTRN - Externally Defined Symbol Declaration 3.1.4.3. Assembler Program Listing 3.1.5. Assembler Program Listing 3.1.6. Assembler Program Listing 3.1.6. Assembler Control Card 3.1.8. SYSTEM CODES 3.1.4. OUTPUT 4.1. ASSEMBLER CARD OUTPUT 4.1. LEMENT Definition Card 4.1.2. External Definition Card 4.1.3. Program Reference Card 4.1.4. External Reference Card 4.1.5. Text Card 4.1.6. Transfer Card 5. LINKER 5.1. LINKER CONTROL CARD FORMATS 5.2.1. CTL 5.2. LINKER CONTROL CARD FORMATS 5.2.1. CTL 5.3. EQU 5.4. END 5.4. END 5.5. END 5.6. END 5.6. END 5.7. END | 3.  | ASSEMBLER                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3-1 to 3-18                                                                             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

| 4.1 OUTPUT  4.1. ASSEMBLER CARD OUTPUT 4.1.1. Element Definition Card 4.1.2. External Definition Card 4.1.3. Program Reference Card 4.1.4. External Reference Card 4.1.5. Text Card 4.1.6. Transfer Card 4.1.6. Transfer Card 4.1.6. Transfer Card 5.1. LINKER 5.1 LINKER INPUT 5.2 5.2. LINKER CONTROL CARD FORMATS 5.2.1. CTL 5.2.2. PHASE 5.2.3. EQU 5.2.4. END 5.2.4. END 5.2.5. REP 5.3. EXAMPLE  APPENDIX A – PREASSEMBLY MACRO PASS APPENDIX B – INPUT OUTPUT CONTROL SYSTEM (IOCS) APPENDIX C – CARD LOAD ROUTINE  4.1 to 4.1 4.1 4.1 4.1 4.1 4.1 4.2 4.3 4.3 4.3 4.3 4.3 4.3 4.3 4.3 4.3 4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | 3.1.1. Symbol Definition 3.1.2. Assembly Control 3.1.2.1. START — Program Start 3.1.2.2. END — Program End 3.1.2.3. ORG — Set Location Counter 3.1.3. Base Register Assignment 3.1.3.1. USING — Assign Base Register 3.1.3.2. DROP — Unassign Base Register 3.1.3.3. Direct Addressing 3.1.4. Program Linking 3.1.4.1. ENTRY — Externally Defined Symbol Declaration 3.1.4.2. EXTRN — Externally Referenced Symbol Declaration 3.1.5. Assembler Program Listing | 3-1<br>3-2<br>3-2<br>3-3<br>3-3<br>3-4<br>3-4<br>3-5<br>3-7<br>3-7<br>3-8<br>3-8<br>3-8 |

| 4.1. ASSEMBLER CARD OUTPUT 4.1.1. Element Definition Card 4.1.2. External Definition Card 4.1.3. Program Reference Card 4.1.4. External Reference Card 4.1.5. Text Card 4.1.6. Transfer Card 4.1.6. Transfer Card 4.1.6. Transfer Card 5.1. LINKER 5.1. LINKER Special |     | 3.2. SYSTEM CODES                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3-14                                                                                    |

| 4.1.1. Element Definition Card       4-2         4.1.2. External Definition Card       4-3         4.1.3. Program Reference Card       4-3         4.1.4. External Reference Card       4-4         4.1.5. Text Card       4-5         4.1.6. Transfer Card       4-5         5. LINKER       5-1 to 5-12         5.1. LINKER INPUT       5-2         5.2. LINKER CONTROL CARD FORMATS       5-2         5.2.1. CTL       5-3         5.2.2. PHASE       5-3         5.2.3. EQU       5-4         5.2.4. END       5-4         5.2.5. REP       5-5         5.3. EXAMPLE       5-5         APPENDIX A - PREASSEMBLY MACRO PASS       A-1 to A-12         APPENDIX B - INPUT OUTPUT CONTROL SYSTEM (IOCS)       B-1 to B-19         APPENDIX C - CARD LOAD ROUTINE       C-1 to C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 4.  | оитрит                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-1 to 4-5                                                                              |

| 5.1. LINKER INPUT       5-2         5.2. LINKER CONTROL CARD FORMATS       5-2         5.2.1. CTL       5-3         5.2.2. PHASE       5-3         5.2.3. EQU       5-4         5.2.4. END       5-4         5.2.5. REP       5-5         5.3. EXAMPLE       5-5         APPENDIX A - PREASSEMBLY MACRO PASS       A-1 to A-12         APPENDIX B - INPUT OUTPUT CONTROL SYSTEM (IOCS)       B-1 to B-19         APPENDIX C - CARD LOAD ROUTINE       C-1 to C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | 4.1.1. Element Definition Card 4.1.2. External Definition Card 4.1.3. Program Reference Card 4.1.4. External Reference Card 4.1.5. Text Card                                                                                                                                                                                                                                                                                                                    | 4-2<br>4-3<br>4-3<br>4-4<br>4-4                                                         |

| 5.2. LINKER CONTROL CARD FORMATS       5-2         5.2.1. CTL       5-3         5.2.2. PHASE       5-3         5.2.3. EQU       5-4         5.2.4. END       5-4         5.2.5. REP       5-5         5.3. EXAMPLE       5-5         APPENDIX A - PREASSEMBLY MACRO PASS       A-1 to A-12         APPENDIX B - INPUT OUTPUT CONTROL SYSTEM (IOCS)       B-1 to B-19         APPENDIX C - CARD LOAD ROUTINE       C-1 to C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.  | LINKER                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-1 to 5-12                                                                             |

| 5.2.1. CTL 5-3 5.2.2. PHASE 5-3 5.2.3. EQU 5-4 5.2.4. END 5-4 5.2.5. REP 5-5 5.3. EXAMPLE 5-5  APPENDIX A - PREASSEMBLY MACRO PASS A-1 to A-12  APPENDIX B - INPUT OUTPUT CONTROL SYSTEM (IOCS) B-1 to B-19  APPENDIX C - CARD LOAD ROUTINE C-1 to C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     | 5.1. LINKER INPUT                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-2                                                                                     |

| APPENDIX A - PREASSEMBLY MACRO PASS  A-1 to A-12  APPENDIX B - INPUT OUTPUT CONTROL SYSTEM (IOCS)  B-1 to B-19  APPENDIX C - CARD LOAD ROUTINE  C-1 to C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | 5.2.1. CTL<br>5.2.2. PHASE<br>5.2.3. EQU<br>5.2.4. END<br>5.2.5. REP                                                                                                                                                                                                                                                                                                                                                                                            | 5-3<br>5-3<br>5-4<br>5-4<br>5-5                                                         |

| APPENDIX B - INPUT OUTPUT CONTROL SYSTEM (IOCS)  APPENDIX C - CARD LOAD ROUTINE  B-1 to B-19  C-1 to C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ۸.۵ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

| APPENDIX C - CARD LOAD ROUTINE C-1 to C-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                         |

| APPENIIX II = EXECT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     | PPENDIX D - EXEC I                                                                                                                                                                                                                                                                                                                                                                                                                                              | D-1 to D-3                                                                              |

| 1-1. | Source-to-Object Code Translation with Assembler                       | 1-1          |

|------|------------------------------------------------------------------------|--------------|

| 1-2. | 9200/9300 Assembly System                                              | 1-3          |

| 2-1. | Example of Source Code Statements                                      | 2–2          |

| 3-1. | Example of Printer Output of a Program                                 | 3-9 to 3-13  |

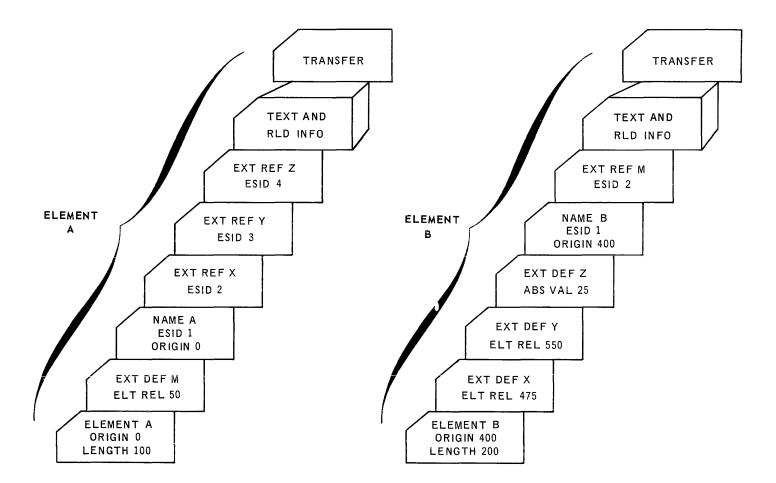

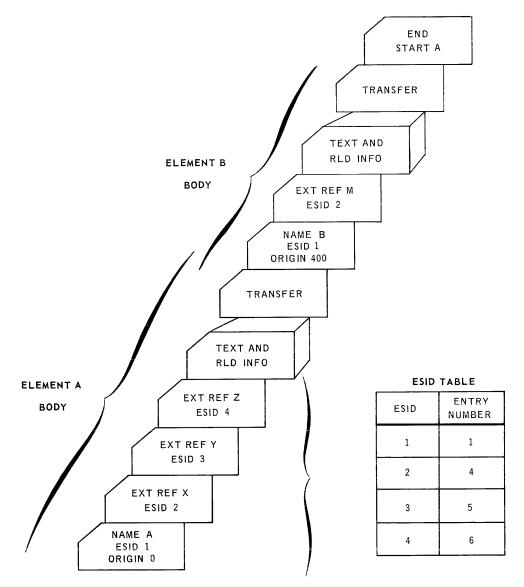

| 5-1. | Elements A and B Deck Structure                                        | 5-7          |

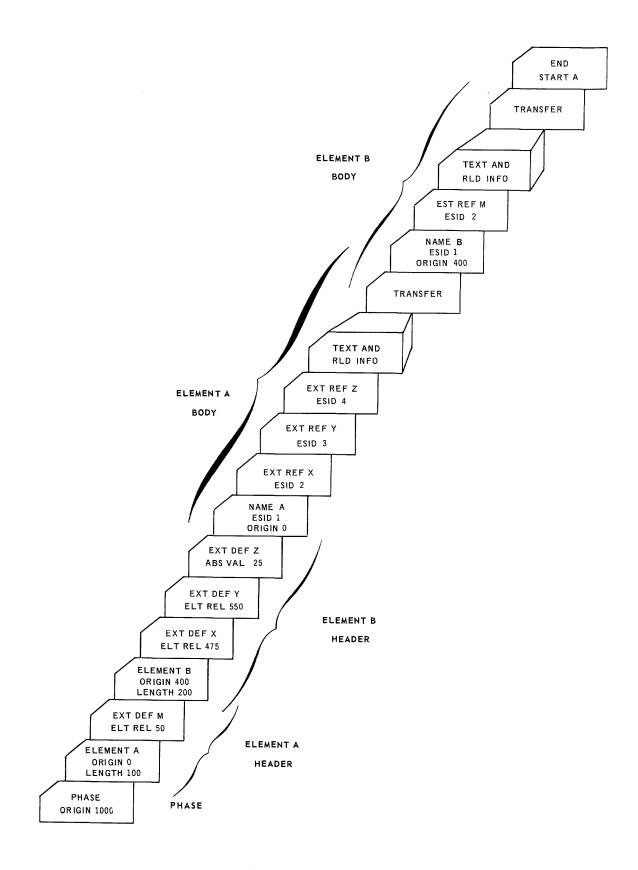

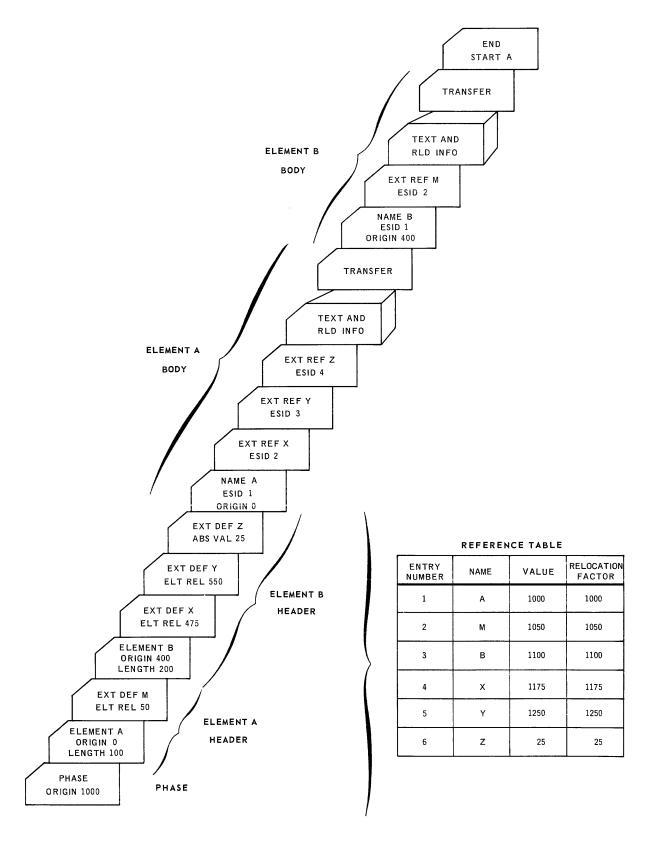

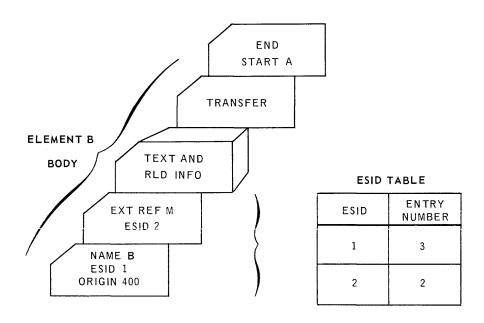

| 5-2. | Linker Input                                                           | 5-8          |

| 5-3. | Header Processing                                                      | 5-10         |

| 5-4. | ESID Processing for Element A                                          | 5-11         |

| 5-5. | ESID Processing for Element B                                          | 5-12         |

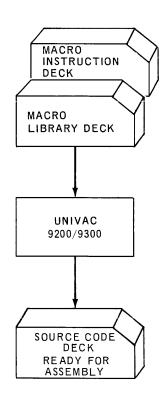

| A-1. | Schematic of Preassembly Macro Pass Operation                          | A - 1        |

|      |                                                                        |              |

|      |                                                                        | TABLES       |

| 2-1. | Instruction Mnemonics                                                  | 2-6          |

| 2-2. | Symbols Used in Describing Operand Formats                             | 2-8          |

| 2-3. | Operand Specifications Using Implied Base Register and Length Notation | 2-11         |

| 2-4. | Characteristics of the Various Constants                               | 2-14         |

| 3-1. | Internal Code                                                          | 3-15 to 3-18 |

PAGE:

Use of this manual presupposes a familiarity with the instruction repertoire and instruction and data formats of the UNIVAC 9200/9300.

#### 1.1. THE PURPOSE OF AN ASSEMBLER

UNIVAC 9200/9300

CARD ASSEMBLER

An Assembler is one result of the many and continuing efforts to improve communications between computers and computer users. The general direction of these efforts has been towards an intermediate language which is close to the language of the user and which relies heavily on the computer for translation into its language.

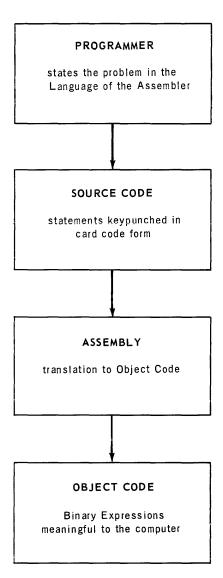

In an Assembler language all coding is represented in the form of statements which are understandable to the programmer. The Assembler then converts these statements into a binary form which is understandable to the computer. The programmer's statements, when keypunched, are called source code. The Assembler converts the source code into object code. Figure 1-1 shows the general flow of source-to-object code conversion with an Assembler.

Figure 1-1. Source-to-Object Code Translation with Assembler

1

PAGE:

# 1.2. CARD ASSEMBLER FOR THE UNIVAC 9200/9300

The Card Assembler for the UNIVAC 9200/9300 System is an efficient, easy-to-use software aid that satisfactorily handles most of the programming problems encountered by the user. Each machine instruction and data form have simple, convenient representations in the assembly language. The rules which govern the use of the language are not complex; they may be learned quickly and applied easily.

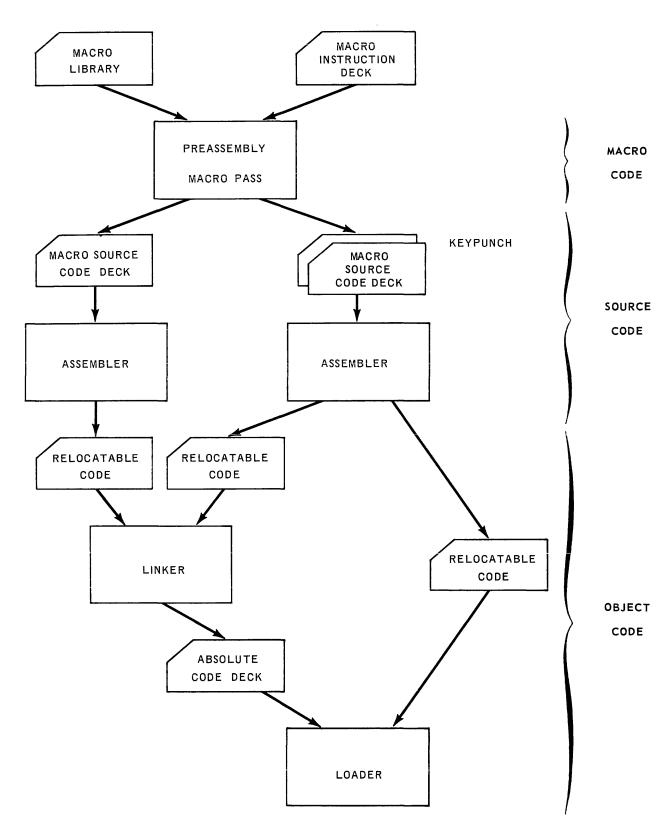

A program in Card Assembler language for the 9200/9300 is written on a standard UNIVAC coding form. The information on the form is keypunched, and the resulting source deck is read twice by the Assembler. Output cards, or an object deck, are produced by the Assembler in relocatable object code or absolute object code. The object deck is ready for loading into the UNIVAC 9200/9300 by means of the Card Program Loader routine. The basic flow of the 9200/9300 Card Assembler and associated software is shown in Figure 1–2. Input to the Assembler is a card deck keypunched from an Assembler coding form or is the output from the Preassembly Macro Pass.

The macro library is in macro code. Parameters are established for the macros by means of macro instructions. The Preassembly Macro Pass (described in Appendix A of this manual) converts the macro code into source code in preparation for assembly.

The assembly operation is a conventional two-pass procedure which produces a card deck in relocatable object code. The outputs of several separate assemblies may be combined by means of a Linker. The Linker output is in absolute object code. When a program is ready to be run, the relocatable or absolute object deck is loaded by a Card Program Loader subroutine.

Figure 1-2. 9200/9300 Assembly System

#### 1.3. ASSEMBLY LANGUAGE CHARACTERISTICS

The succeeding sections of this manual describe in detail the use of the Assembler coding form and the operational characteristics of the Assembler. These characteristics are summarized briefly as follows:

- Mnemonic Operation Codes A fixed name, consisting of two, three, or four letters, is assigned to each machine instruction. The name is chosen to suggest the nature of the instruction, thereby helping the user to learn and remember the instruction.

- Symbolic Addressing and Automatic Storage Assignment Symbolic labels may be assigned to instructions or groups of data. An instruction may then reference the labeled data by label rather than by storage address. In many cases, other data required by the instruction (such as operand length) may be supplied automatically by the Assembler. Another major task of the Assembler is to keep track of all storage locations used and to assign all incoming instructions and data to specific locations. The Assembler also handles all base register and displacement calculations.

- Flexible Data Representation Data may be represented in the Assembler in decimal, hexadecimal, or character notation, thus allowing the programmer to choose the most suitable form for each constant.

- Relocatable Programs and Program Linking Programs are prepared by the Assembler in an absolute or relocatable form. In relocatable form, the actual storage locations to be occupied by a program need not be specified at assembly time, or if specified, they may easily be altered before loading. Provisions are made for linking together, loading, and running as one program the results of separate assemblies, thereby reducing the machine time required to make changes to one part of a program.

- Program Listing One of the outputs of the Assembler is a printed listing of source and object codes. This listing includes flags marking any errors detected by the Assembler. Source code errors do not cause the Assembler to stall. The Assembler continues to process the rest of the source code performing its usual error checks, thus minimizing the number of assemblies required to produce error-free code.

1

# 2. THE ASSEMBLER LANGUAGE

# 2.1. CHARACTER SET

The character set used in writing statements in the Assembler language consists of:

Letters

A, B, C, ..., Z

Digits

0, 1, 2, ..., 9

Special Symbols

\* + - , ( ) ' blank

## 2.2. STATEMENT FORMAT

Statements in the Assembler language are written on a standard coding form. Information for the Assembler and comments are written in columns 1 through 71. Column 72 must be blank. Columns 73 through 80 may contain program identification and sequencing information. The information in columns 1 through 71 consists of the following fields.

## 2.2.1. Label Field

The label field begins in column 1 and is terminated by a blank column. There may be no embedded blanks. It may either be a blank field or contain a symbol whose value is to be defined. More detailed information about symbols is contained under headings 2.3.6. and 3.1.1.

## 2.2.2. Operation Field

The operation field begins with the first nonblank following the label field and is terminated by a blank. It contains either the name of an assembler directive or the mnemonic operation code for a machine instruction.

# 2.2.3. Operand Field

The operand field begins with the first nonblank following the operation field and is terminated by a blank not contained in a character representation. This field contains information which defines the operands of a machine instruction or which supplies the specifications required with an assembler directive.

#### 2.2.4. Comments Field

The comments field begins with the column following the blank terminating the operand field and ends at column 71. It may contain any combination of characters including blanks. It is not processed by the Assembler other than including it on the assembly listing. It may contain remarks to clarify the purpose or operation of the associated coding. A line may consist entirely of comments from columns 2 through 71 if column 1 contains an asterisk.

|    | LABEL<br>1                                   | b OPERATION                                  | N 5<br>14 | OPERAND                                                            | ħ           |

|----|----------------------------------------------|----------------------------------------------|-----------|--------------------------------------------------------------------|-------------|

| 1. | *, T,H,I  S                                  | I S IA                                       | C O MIM   | E,N,T,  L,I,N,E,*   , , , , , , , , , ,                            |             |

| 2. | T <sub>1</sub> A <sub>1</sub> G <sub>1</sub> | B <sub>1</sub> A <sub>1</sub> L <sub>1</sub> | 1,5,,     | T.A.G.2                                                            | <u> </u>    |

| 3. | L,H, ,1,5                                    | , T,A,G3                                     |           | $T_1H_1E_1 = \{O_1P_1E_1R_1A \mid T_1P_1O_1N_1 = \{C_1O_2D_1E_1\}$ | IS LH       |

| 4. |                                              | LH.                                          | 1,5,      | T,A,G,3                                                            |             |

|    |                                              |                                              |           |                                                                    | <del></del> |

Figures 2-1. Example of Source Code Statements

Although the assembler language is free form, it is recommended that source code statements be written with the first character of the operation code in column 8 and the first character of the operand field in column 14. Tabulating the statements in this fashion creates a program listing which is neater in appearance and easier to read. The standard coding form is ruled to conform to this convention. Thus, although the statements on lines 3 and 4 of Figure 2-1 are equivalent to the Assembler, the form of line 4 is preferred to that of line 3.

#### 2.3. EXPRESSIONS

The operand field of a statement in the assembler language ordinarily consists of one or more expressions. Expressions are grouped by parentheses and separated by commas. For example, the basic operand formats for computer instructions are shown in Table 2-3. In this table, each subscripted letter represents an expression. An expression may be a single term or a number of terms connected by operators. The permissible operators are a plus sign (+) representing addition and a minus sign (-) representing subtraction. A leading minus sign is also allowed to produce the negative of the first term. All operations are performed in two's-complement binary notation. A term may be one of the following:

A decimal, hexadecimal, or character representation of an actual value.

A location counter reference.

A symbol.

## 2.3.1. Decimal Representation

A value may be represented directly by a string of up to five digits, 0 through 9, forming a decimal number from 0 through 32767. Such a number is converted to a binary value occupying one or two bytes depending on the type of field for which it is intended. Following are some decimal representations.

| Decimal Representation | Binary Value      |

|------------------------|-------------------|

| 0                      | 0000000           |

| 13                     | 00001101          |

| 257                    | 00000001 00000001 |

| 32767                  | 01111111 11111111 |

# 2.3.2. Hexadecimal Representation

UP-4092

A hexadecimal representation consists of a string of digits preceded by X' and followed by '(apostrophe). Each hexadecimal digit represents a half byte of information. The hexadecimal digits and their values are:

| 0 | _ | 0000 | 8 | _ | 1000 |

|---|---|------|---|---|------|

| 1 | _ | 0001 | 9 | _ | 1001 |

| 2 |   | 0010 | Α | _ | 1010 |

| 3 |   | 0011 | В | _ | 1011 |

| 4 | _ | 0100 | C | _ | 1100 |

| 5 | _ | 0101 | D | _ | 1101 |

| 6 | _ | 0110 | E | _ | 1110 |

| 7 | _ | 0111 | F | _ | 1111 |

Some examples of hexadecimal representations and their values are:

| Hexadecimal Representation | n Binary Value    |

|----------------------------|-------------------|

| X'D'                       | 00001101          |

| X '101'                    | 00000001 00000001 |

| X'7FFF'                    | 01111111 11111111 |

# 2.3.3. Character Representation

A character representation consists of a string of characters preceded by C' and followed by '. The following are valid character representations.

| Character Representation | EBCDIC Value                             |

|--------------------------|------------------------------------------|

| C'D'                     | 11000100                                 |

| C'GROSS'                 | 1100011111011001110101101110001011100010 |

| C'9'                     | 11111001                                 |

# 2.3.4. Location Counter

An indication of the next storage location available for assignment is maintained as a counter called the location counter. After the Assembler processes an instruction or constant, it adds the length of the instruction or constant processed to the location counter.

PAGE:

Each instruction or address constant must have an address which is a multiple of two. Such an address is said to fall on a halfword boundary. If the value of the location counter is not a multiple of two when assembling such a constant or an instruction, a one is added to the location counter before assigning an address to the current line. Storage locations reserved by this process receive binary zeros when the program is loaded.

The current value of the location counter is available for reference in the Assembler language and is represented by the single special character \* (asterisk). If written in a constant representation or in an instruction operand expression, this symbol is replaced by the storage address of the leftmost byte allocated to that instruction or constant. Thus the instruction

BC

represents a one-instruction loop.

# 2.3.5. Relative Addressing

An instruction may address data in its immediate vicinity in storage in terms of its own storage address. This is called relative addressing and is achieved by an expression of the form \*+n or \*-n where n is the difference in storage addresses of the referring instruction and the instruction or constant being accessed. Relative addressing is always in terms of bytes, not words or instructions. For example, in the coding

| LABEL     | b OPERATIO                      | N 5<br>14                        | OPERAND                                   | b        |

|-----------|---------------------------------|----------------------------------|-------------------------------------------|----------|

|           | C <sub>i</sub> H <sub>i</sub> i | 1,5 <sub>1</sub> , L             | MI,T, , , , , , , , , , , , , , , , , , , |          |

| <u> </u>  | B <sub>i</sub> C <sub>i</sub>   | <b>    7</b> ,, <sub> *,+,</sub> | 1, 2, , , , , , , , , , , , , , , , , ,   |          |

|           | AH                              | 1,5,,T,                          | <b>W</b> , <b>Q</b> ,                     | <u> </u> |

|           | B <sub>i</sub> C <sub>1</sub>   | 1,5,,*,-                         | -,1,2, , , , , , , , , , , , , , , , , ,  |          |

| , , , , L | MVG                             | A, B,                            |                                           |          |

the address \*+12 in the second line is the address of the instruction in the last line and the address \*-12 in the fourth line is the address of the instruction in the first line since each of the first four instructions is four bytes long.

# 2.3.6. Symbols

A symbol is a group of up to four alphanumeric characters. The first, or leftmost, must be alphabetic. Special characters or blanks may not be contained within a symbol. The following are examples of valid symbols:

A LOSS A72Z PRFT CAT

PAGE:

The following are not valid symbols for the reasons stated:

**GROSS**

More than four characters

N PA

UP-4092

Embedded blank

SR)N

Special character

A symbol may be assigned any value from 0 through 32767. It is assigned a value, or defined, when it appears in the label field of any source code statement other than a comment. A symbol appearing in the label field of an EQU or ORG directive is assigned the value of the expression in the operand field. In all other cases the value assigned is the current value of the location counter after adjustment to a halfword boundary, if necessary. The value is assigned to the current label before the location counter is incremented for the next instruction, constant, or storage definition. Thus, if a symbol appears in the label field of a statement defining an instruction, constant, or storage area, the symbol is assigned a value equal to the storage area address of that instruction, constant, or storage area.

# 2.3.7. Relocatable and Absolute Expressions

A single term may be either relocatable or absolute. Decimal, character, and hexadecimal representations are all absolute terms. A location counter reference within a section of relocatable code yields a relocatable value. If a symbol is defined by appearing in the label field of a source code statement within a section of relocatable code, its value will be relocatable.

An expression is relocatable in the following cases: if it consists of an absolute expression plus a relocatable term; if it can be reordered to have that form; or if it consists solely of a relocatable term. Some examples of relocatable expressions are:

R

A+R

R+A

R-R+A+R

where R represents a relocatable term and A an absolute term.

An expression is absolute if all of the terms in the expression are absolute or if it consists only of absolute terms plus an even number of relocatable terms of which exactly half are preceded by minus signs. Some examples of absolute expressions are:

Α

A+A-A

A - A + A + A

R+A-R

R-R+A

An expression may be negatively relocatable under certain circumstances (see Data Constants, heading 2.5.1). Such an expression consists of an absolute expression minus a relocatable expression, or an expression which may be reordered to that form. Some examples are as follows:

$$A-R$$

$A-R-R+R$   $R-R+A-R$

# 2.3.8. Length Attribute

The Assembler associates a length attribute with a symbol defined in the label field of a source code line representing an instruction, constant, or storage definition. The length attribute of such a symbol is the number of bytes assigned to the instruction, constant, or storage area involved. The length attribute of an expression is also determined by the Assembler and is a function of the leading term of the expression. If the first term of an expression is an absolute value, a length attribute of one byte is assigned to the expression. If the leading term is a symbol, the number of bytes attributed to the expression is the same as the length attributed to the symbol. Thus, if TAG appears in the label field of an LH instruction (Load Halfword), it would have a length attribute of 4 since LH is a 4-byte instruction. In referencing the same label, the expression TAG + 195 also has a length attribute of 4; but the expression 195 + TAG has a length attribute of 1 because the leading term is a constant.

#### 2.4. MACHINE INSTRUCTIONS

A list of the standard machine instructions giving the numeric and hexadecimal operation codes with the instruction type is shown in Table 2-1.

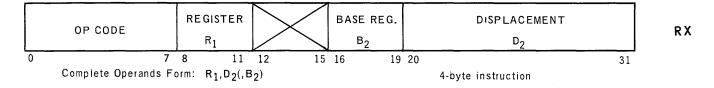

The machine instruction format consists of a label (optional), a mnemonic operation code, and an operand. If a symbol is used in the label field of a machine instruction, it is assigned the address of the leftmost character of the instruction and receives a length attribute equal to the length of that instruction. There are four types of instruction formats. These are shown below together with a brief explanation of the functions performed by the instructions within each format type. Table 2-2 defines the symbols used in the instruction type formats.

| MNEMONIC | FUNCTION                  | HEXADECIMAL<br>OPERATION<br>CODE | FORMAT |

|----------|---------------------------|----------------------------------|--------|

| АН       | ADD HALFWORD              | AA                               | RX     |

| Al       | ADD IMMEDIATE             | A6                               | SI     |

| AP       | ADD (PACKED) DECIMAL      | FA                               | SS2    |

| BAL      | BRANCH AND LINK           | 45                               | RX     |

| вс       | BRANCH ON CONDITION       | 47                               | RX     |

| СН       | COMPARE HALFWORD          | 49                               | RX     |

| CLC      | COMPARE LOGICAL CHARACTER | D5                               | \$\$1  |

| CLI      | COMPARE LOGICAL IMMEDIATE | 95                               | SI     |

Table 2-1. Instruction Mnemonics

| MNEMONIC | FUNCTION                      | HEXADECIMAL<br>OPERATION<br>CODE | FORMAT        |

|----------|-------------------------------|----------------------------------|---------------|

| СР       | COMPARE (PACKED) DECIMAL      | F9                               | S <b>S</b> 2  |

| DP       | DIVIDE (PACKED) DECIMAL       | FD                               | \$\$2         |

| ED       | EDIT                          | DE                               | SS1           |

| HPR      | HALT AND PROCEED              | A9                               | SI            |

| LH       | LOAD HALFWORD                 | 48                               | RX            |

| LPSC     | LOAD PROGRAM STATE CONTROL    | A8                               | SI            |

| MP       | MULTIPLY (PACKED) DECIMAL     | FC                               | SS2           |

| MVC      | MOVE CHARACTERS               | D2                               | \$\$1         |

| M∨I      | MOVE IMMEDIATE DATA           | 92                               | SI            |

| MVN      | MOVE NUMERICS                 | D1                               | SS1           |

| MVO      | MOVE WITH OFFSET              | F1                               | SS2           |

| NC       | AND CHARACTERS                | D4                               | SS1           |

| NI       | AND IMMEDIATE DATA            | 94                               | SI            |

| ос       | OR CHARACTERS                 | D6                               | \$\$1         |

| 01       | OR IMMEDIATE DATA             | 96                               | SI            |

| PACK     | PACK                          | F2                               | <b>\$</b> \$2 |

| SH       | SUBTRACT HALFWORD             | АВ                               | RX            |

| SP       | SUBTRACT (PACKED) DECIMAL     | FB                               | SS2           |

| SPSC     | STORE PROGRAM STATE CONTROL   | <b>A</b> 0                       | SI            |

| SRC      | SUPERVISOR REQUEST            | A1                               | SI            |

| , STH    | STORE HALFWORD                | 40                               | RX            |

| TiO      | TEST I/O                      | A 5                              | SI            |

| тм       | TEST UNDER MASK               | 91                               | SI            |

| TR       | TRANSLATE                     | DC                               | SS1           |

| UNPK     | UNPACK                        | F3                               | SS2           |

| XIOF     | EXECUTE INPUT/OUTPUT FUNCTION | A 4                              | SI            |

| ZAP      | ZERO ADD (PACKED) DECIMAL     | F8                               | \$\$2         |

UNIVAC 9200/9300 CARD ASSEMBLER

Table 2-1. Instruction Mnemonics (cont.)

SI

| SYMBOL MEANING |                                                                              |  |

|----------------|------------------------------------------------------------------------------|--|

| R <sub>1</sub> | The number of the register addressed as operand 1                            |  |

| I <sub>2</sub> | The immediate data or device address used as operand 2 of an SI instruction. |  |

| L              | The length of the operands *                                                 |  |

| Li             | L <sub>i</sub> The length of operand i *                                     |  |

| s <sub>i</sub> | S <sub>i</sub> The storage address of operand i                              |  |

| B <sub>i</sub> | The base register for operand i                                              |  |

| D <sub>i</sub> | The displacement for operand i                                               |  |

<sup>\*</sup> This is the true length of the operand, not the length less one, as required in object code. The Assembler makes the necessary reduction of one in the length when converting source to object code.

Table 2-2. Symbols Used In Describing Operand Formats

# 2.4.1. RX - Register to Storage Instructions

In general, instructions in this format are used to process data between registers and storage, and include such functions as load, store, compare, add, subtract and branch. The mnemonic codes for instructions using this type of format are:

| AH  | Add Halfword        |

|-----|---------------------|

| BAL | Branch and Link     |

| BC  | Branch on Condition |

| СН  | Compare Halfword    |

| LH  | Load Halfword       |

| SH  | Subtract Halfword   |

| STH | Store Halfword      |

# 2.4.2. SI - Instruction to Storage Instructions

| OP CODE | IMMEDIATE OPERAND | BASE REG. | DISPLACEMENT   |

|---------|-------------------|-----------|----------------|

|         | l <sub>2</sub>    | В1        | D <sub>1</sub> |

|         | 7 8 1             | 5 16 19   | 20 31          |

Complete Operands Form:  $D_1(B_1), I_2$

4-byte instruction

PAGE:

In general, instructions with this format are used for processing with control data contained in the instruction. The mnemonic codes for instructions using this type of format are:

| ΑI   | Add Immediate               |

|------|-----------------------------|

| CLI  | Compare Logical Immediate   |

| HPR  | Halt and Proceed            |

| LPSC | Load Program State Control  |

| MVI  | Move Immediate Data         |

| NI   | AND Immediate Data          |

| OI   | OR Immediate Data           |

| SPSC | Store Program State Control |

| SRC  | Supervisor Request          |

| TIO  | Test I/O                    |

| TM   | Test Under Mask             |

| XIOF | Execute I/O Function        |

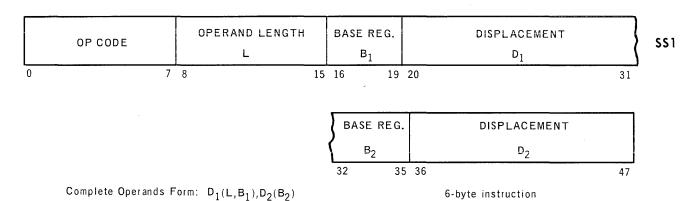

# 2.4.3. SS1 - Storage to Storage Instructions

The instructions with this format are used to process data in storage where the operands are of equal length, and include such functions as comparing, transferring, translating, and logical operations. The mnemonic codes for instructions using this type of format are:

| CLC | Compare Logical Character |

|-----|---------------------------|

| ED  | Edit                      |

| MVC | Move Characters           |

| MVN | Move Numerics             |

| NC  | AND Characters            |

| OC  | OR Characters             |

| TR  | Translate                 |

SECTION:

2

PAGE:

# 2.4.4. SS2 - Storage to Storage Instructions

UP-4092

BASE REG. DISPLACEMENT \* 35 36

Complete Operands Form:  $D_1(L_1,B_1),D_2(L_2,B_2)$

6-byte instruction

The instructions with this format are used to process operands of unequal length and to process packed decimal values. The various functions include decimal operations (add, subtract, compare), shift operations, and pack and unpack operations.

The mnemonic codes for instructions using this type of format are:

AΡ Add Packed Decimal CP Compare Packed Decimal Divide Packed Decimal DP MΡ Multiply Packed Decimal MVOMove With Offset PACK Pack SP Subtract Packed Decimal UNPK Unpack ZAPZero Add Packed Decimal

Where an operand is described in terms of a storage address and a length, the expression used may be simplified from that shown in the instruction format by implying the base register and the length. Information supplied in the USING and DROP directives enable the Assembler to separate a storage address into a base register and a displacement. If a length attribute is associated with the expression but is not specified in the statement, a value equal to the length of the operand is supplied by the Assembler. Table 2-3 lists the complete specification for the operand referencing memory, applicable instruction types, and the operand format as it may be written utilizing an implicit base register and/or length representations.

PAGE:

| A DDI ICA DI E                     | COMPLETE                                         | OPERAND SPECIFICATION USING          |                                   |                                        |

|------------------------------------|--------------------------------------------------|--------------------------------------|-----------------------------------|----------------------------------------|

| APPLICABLE<br>INSTRUCTION<br>TYPES | SPECIFICATION<br>FOR ONE<br>OPERAND              | IMPLIED BASE<br>REGISTER<br>NOTATION | IMPLIED<br>LENGTH                 | IMPLIED BASE<br>REGISTER<br>AND LENGTH |

| RX                                 | D <sub>2</sub> (,B <sub>2</sub> )                | <b>S</b> <sub>2</sub>                | NA                                | NA                                     |

| SI                                 | D <sub>1</sub> (B <sub>1</sub> )                 | S <sub>1</sub>                       | NA                                | NA                                     |

| \$\$1                              | D <sub>1</sub> (L,B <sub>1</sub> )               | S <sub>1</sub> (L)                   | D <sub>1</sub> (,B <sub>1</sub> ) | S <sub>1</sub>                         |

| SS1                                | $D_2(B_2)$                                       | S <sub>2</sub>                       | NA                                | NA                                     |

| \$\$2                              | D <sub>1</sub> (L <sub>1</sub> ,B <sub>1</sub> ) | S,(L,)                               | D <sub>1</sub> (,B <sub>1</sub> ) | S,                                     |

| <b>SS2</b>                         | $D_2(L_2,B_2)$                                   | \$ <sub>2</sub> (L <sub>2</sub> )    | D <sub>2</sub> (,B <sub>2</sub> ) | <b>S</b> <sub>2</sub>                  |

Table 2-3. Operand Specifications Using Implied Base Register And Length Notation

Example: To move 80 characters from the field labeled OPA defined as a 90-character field to the field labeled OPB and defined as an 80-character field, the instruction could be written as

MVC

OPB,OPA

If 90 characters were to be moved the instruction would be written

MVC

OPB(90),OPA

# 2.5. DATA AND STORAGE FORMATS

The formats for data and storage statements are similar to that for a machine instruction. A symbol may be used in the label field. It is assigned the address of the leftmost character of the constant or storage area being specified and is attributed with a length equal to that of the specified constant or storage area. The operation code is either DC (Define Constant) or DS (Define Storage). The operand has various formats which are explained below.

#### 2.5.1. DC - Define Constant

UP-4092

There are three types of constants: C for character representation; X for hexadecimal; and Y for expression. To define a constant, the assembly directive DC is written in the operation field. The statement has the form:

|    | LABEL  | OPERATION CODE | OPERAND |

|----|--------|----------------|---------|

|    | Symbol | DC             | tLn'c'  |

| or |        |                |         |

|    | LABEL  | OPERATION CODE | OPERAND |

|    | Symbol | DC             | Y(e)    |

Of

| LABEL  | OPERATION CODE | OPERAND |

|--------|----------------|---------|

| Symbol | DC             | YL1(e)  |

where: n is a decimal number  $\leq 16$  specifying the number of bytes the constant is to occupy.

t is X or C denoting hexadecimal or character representation, respectively,

c is the actual character or hexadecimal representation for the constant. and

e is any acceptable expression as previously defined.

#### 2.5.1.1. Character Representation

A character representation is a string of as many as 16 characters, including blanks, enclosed by apostrophe marks. The apostrophe mark itself is represented by two successive apostrophes and an ampersand by two successive ampersands. In each of these cases the 2 characters count only as one towards the limit of 16. Thus, to represent a character constant of 16 apostrophies, 32 successive apostrophies would be written, preceded by and ended with an apostrophe. The length specification may be omitted, in which case the length of the constant is determined implicitly from the number of characters between the apostrophe marks. If the number of characters in apostrophes is greater than the length n, the rightmost characters are truncated to fit the field in the area reserved for it. If the number of characters between apostrophes is less than the length, the value is padded with blanks on the right to fill the field.

For example, the following lines each result in a two-byte constant consisting of the letter A followed by blank. The third representation is flagged with an error indication.

PAGE:

| LABEL | ħ | OPERATION 1    | 5<br>14              | OPERAND                 | <b>t</b> |

|-------|---|----------------|----------------------|-------------------------|----------|

| 1     | Γ | DGI            | GL <sub>1</sub> 2,`, | <b>A</b> '.             |          |

|       |   | DG             | C \ A                |                         |          |

|       |   | D <sub>C</sub> | C L 2                | <b>A</b> , <b>B</b> , ' |          |

#### 2.5.1.2. Hexadecimal Representation

A hexadecimal representation is a string of as many as 32 hexadecimal digits enclosed by apostrophe marks. If the digit string is less than twice the length specification, the field is padded with hexadecimal zeros on the left. If more than twice the length specification, the representation is truncated on the left to produce a value equal to the length. The length specification may be omitted, in which case the length of the constant is determined as the smallest number of bytes which will contain the constant specified. If necessary, the field is padded on the left with one hexadecimal zero.

The following illustrates the values of source statements which represent valid hexadecimal constants, three bytes in length:

| CONSTANT REPRESENTATION |           |          | VALUE    |          |

|-------------------------|-----------|----------|----------|----------|

| DC                      | XL3'1'    | 00000000 | 00000000 | 00000001 |

| DC                      | X'123A5'  | 00000001 | 00100011 | 10100101 |

| DC                      | X'1F3456' | 00011111 | 00110100 | 01010110 |

# 2.5.1.3. Expression Constants

Constants of type Y provide a way to write a constant involving a relocatable expression. If the length specification L1 is not present, the expression defining an expression constant may have any value from -32,768 to 32,767 inclusive and may be absolute, relocatable, or negatively relocatable. (A negatively relocatable expression consists of an absolute expression minus a relocatable expression. or an expression that can be reordered to that form.) This type of expression constant (one in which the length specification L1 is not present) provides a convenient notation for representing a complete storage address. It is for this reason that constants of this type are called address constants.

An address constant always occupies two bytes of storage and location counter adjustment to a halfword boundary is performed by the Assembler before storage locations are assigned to the constant. No such adjustment is performed for hexadecimal or character constants.

For example, an address constant designed to generate the address assigned to the label 'TAG' would take the following form.

> DC Y(TAG)

SECTION:

2

An expression constant in which the length specification L1 is present may have any value from 0 through 255 and may be absolute, relocatable, or negatively relocatable. It always occupies one byte of storage, and no location counter adjustment is made before assigning a memory location to the constant. It is useful when an externally defined symbol is assigned to only one byte.

A summary of constant types, lengths, padding and truncation rules appears in Table 2-4.

| CONSTANT<br>TYPE | EXPLICIT<br>LENGTH | IMPLICIT<br>LENGTH | TRUNCATION<br>OR PADDING |

|------------------|--------------------|--------------------|--------------------------|

| С                | variable<br>1-16   | maximum<br>16      | on right side            |

| X                | variable<br>1-16   | maximum<br>16      | on left side             |

| Y                | not stated         | 2                  | on left side             |

| 1                | 1                  | none               | on left side             |

Table 2-4. Characteristics Of The Various Constants

# 2.5.2. Define Storage

UP-4092

The format of the assembler language statement to reserve storage is:

| LABEL             | OPERATION CODE | OPERAND |

|-------------------|----------------|---------|

| Symbol (Optional) | DS             | dCLn    |

ot

| LABEL             | OPERATION CODE | OPERAND |

|-------------------|----------------|---------|

| Symbol (Optional) | DS             | đН      |

where: d is a non-negative integer called the duplication factor, the number of fields to be reserved (d may be a maximum of 256),

n is a decimal number representing the length of the field to be reserved (n may be a maximum of 256),

H represents a field whose length is two bytes and whose storage address must be on a halfword boundary.

The statement DS 0H causes the location counter to be adjusted to a multiple of two without reserving storage. A duplication factor of zero may be used with any storage definition statement to define the address and length of a field without reserving storage for it. The duplication factor may be omitted, in which case a factor of one is assumed.

PAGE:

Thus:

| CARD | DS | 0CL80 |

|------|----|-------|

| FRST | DS | CL40  |

| LAST | DS | CL40  |

would define an 80-byte field named CARD, a 40-byte field named FRST whose address is the same as that of CARD, and a field named LAST whose length is 40 bytes and whose address is 40 greater than that of CARD and FRST.

The location counter is not increased in assembling CARD (because duplication factor is 0) but is with FRST and LAST. Therefore, 40 + 40 = 80 spaces are reserved, with FIRST and CARD assigned the starting location and LAST assigned the mid point. When the duplication factor is specified, it defines the number of fields of length n (for C) or the number of pairs of bytes (for H) to be reserved. For example,

TAG DS 13H

reserves 13 pairs of bytes. The symbol, TAG, refers to the first pair of bytes only and not to the entire 26 bytes. TAG would have a length attribute of two in this instance.

# 3. ASSEMBLER DIRECTIVES AND SYSTEM CODES

# 3.1. DIRECTIVES

In addition to the representation of machine instructions, constants, and storage, the assembler language includes several assembler directives. These are instructions to the Assembler to perform certain functions and provide the user of the assembler language with control of the operation of the Assembler.

The assembler directives, grouped by function, are as follows:

Symbol Definition

EQU

Assembler Control

START

END

ORG

Base Register Assignment

USING

DROP

Program Linking

**ENTRY**

**EXTRN**

Assembler directives, except START, may use a symbol in the operand field, and, with the exception of ENTRY and EXTRN, the symbol must have appeared in the label field of a previous statement.

# 3.1.1. Symbol Definition

EQU - Equate

The value and length attribute of a symbol may be defined explicitly. The statement to accomplish this has the form

| <br>LABEL  | OPERATION | OPERAND                         |

|------------|-----------|---------------------------------|

| <br>Symbol | EQU       | e <sub>1</sub> , e <sub>2</sub> |

where: e, and e, are expressions.

3

PAGF:

The symbol is defined to have a length attribute equal to the value of the second expression in the operand. The second expression in the operand may be omitted, in which case the symbol is defined to have the length attribute of the first expression.

The symbol in the label field is defined to have the value of the first expression in the operand field. If the value of the first expression in the operand field is not between 0 and 32767, the statement will be flagged with an error indication and the symbol will remain undefined.

Thus, if the value of the location counter is 2000 when the following lines are encountered.