# UNIVAC

## 418-111

## **REAL-TIME SYSTEM**

#### SYSTEM DESCRIPTION

This manual describes a UNIVAC system. It is as complete and accurate at the time of publication as is feasible by current documentation techniques. The Univac Division will issue complete revisions of this manual when necessary. The Univac Division reserves the right to make such additions, corrections, and/or deletions as, in the judgment of the Univac Division, are required by the development of its systems. To assure that you have the current version of this manual and for the current status of the system, contact your local Univac Representative.

UNIVAC is a registered trademark of the Sperry Rand Corporation.

Other trademarks appearing in the text of this publication are:

UNISERVO FASTRAND UNISCOPE

©1968 - 1969 - SPERRY RAND CORPORATION

PRINTED IN U.S.A.

## CONTENTS

| c  | ONTENTS                                                                                                                                                                                                                  | i                    |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1. | INTRODUCTION                                                                                                                                                                                                             | 1                    |

|    | 1.1. UNIVAC 418-III REAL TIME SYSTEM                                                                                                                                                                                     | 1                    |

|    | 1.2. MAJOR TYPES OF DATA PROCESSING APPLICATIONS                                                                                                                                                                         | 1                    |

|    | 1.3. SYSTEM AND PERIPHERAL CHARACTERISTICS                                                                                                                                                                               | 2                    |

| 2. | SYSTEM HARDWARE                                                                                                                                                                                                          | 3                    |

|    | <ul> <li>2.1. SYSTEM COMPONENTS</li> <li>2.1.1. Command/Arithmetic Section</li> <li>2.1.2. Input/Output Modules</li> <li>2.1.3. Main Storage</li> <li>2.1.4. Auxiliary Storage Subsystems</li> </ul>                     | 4<br>4<br>4<br>5     |

|    | 2.2. SYSTEM CONFIGURATION                                                                                                                                                                                                | 5                    |

| 3. | MAIN STORAGE                                                                                                                                                                                                             | 7                    |

|    | 3.1. GENERAL                                                                                                                                                                                                             | 7                    |

|    | 3.2. BASIC STORAGE MODULE                                                                                                                                                                                                | 8                    |

|    | 3.3. BANK PARITY ERROR                                                                                                                                                                                                   | 8                    |

|    | 3.4. MULTIPLE BANK ACCESS                                                                                                                                                                                                | 8                    |

|    | 3.5. STORAGE PACKAGING                                                                                                                                                                                                   | 8                    |

|    | 3.6. STORAGE CONFIGURATIONS                                                                                                                                                                                              | 8                    |

|    | 3.7. SIMULTANEITY OF STORAGE ACCESS                                                                                                                                                                                      | 10                   |

|    | 3.8. STORAGE PROTECTION                                                                                                                                                                                                  | 11                   |

| 4. | INPUT/OUTPUT MODULES                                                                                                                                                                                                     | 12                   |

|    | 4.1. GENERAL                                                                                                                                                                                                             | 12                   |

|    | 4.2. NORMAL INPUT/OUTPUT MODE                                                                                                                                                                                            | 13                   |

|    | 4.3. BUFFER CONTROL WORDS                                                                                                                                                                                                | 13                   |

|    | <ul> <li>4.4. EXTERNALLY SPECIFIED INDEX MODE</li> <li>4.4.1. Fullword or Halfword ESI Storage of Characters</li> <li>4.4.2. Hardware ESI Buffer Chaining</li> <li>4.4.3. Automatic Tabling of ESI Interrupts</li> </ul> | 15<br>15<br>15<br>18 |

| 5. | COMMAND/ARITHMETIC SECTION                                                                                                                                                                                                                                            | 20                                     |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|    | 5.1. INTRODUCTION                                                                                                                                                                                                                                                     | 20                                     |

|    | <ul> <li>5.2. THE COMMAND SECTION</li> <li>5.2.1. Reserved Locations</li> <li>5.2.2. Special Register</li> <li>5.2.3. Instruction Address Register</li> <li>5.2.4. Index Register and Index Register Pointer</li> <li>5.2.5. Real Time Clock and Day Clock</li> </ul> | 20<br>21<br>21<br>21<br>21<br>21<br>23 |

|    | <ul> <li>5.3. THE ARITHMETIC SECTION</li> <li>5.3.1. Fixed-Point Arithmetic</li> <li>5.3.2. Floating-Point Arithmetic</li> <li>5.3.3. Binary/Decimal Conversion Instructions</li> </ul>                                                                               | 23<br>24<br>24<br>24<br>24             |

|    | <ul> <li>5.4. INSTRUCTION REPERTOIRE</li> <li>5.4.1. Type I Instructions</li> <li>5.4.2. Type II Instructions</li> <li>5.4.3. Type III Instructions</li> <li>5.4.4. Instruction Groups</li> </ul>                                                                     | 25<br>25<br>25<br>27<br>27             |

| 6. | PERIPHERAL SUBSYSTEMS                                                                                                                                                                                                                                                 | 31                                     |

|    | 6.1. GENERAL                                                                                                                                                                                                                                                          | 31                                     |

|    | <ul> <li>6.2. THE 'FH' SERIES OF MAGNETIC DRUMS</li> <li>6.2.1. FH-432 Magnetic Drum Subsystem</li> <li>6.2.2. FH-1782 Magnetic Drum Subsystem</li> <li>6.2.3. FH-432/FH-1782 Magnetic Drum Subsystem</li> </ul>                                                      | 32<br>34<br>35<br>36                   |

|    | 6.3. FH-880 MAGNETIC DRUM SUBSYSTEM                                                                                                                                                                                                                                   | 37                                     |

|    | 6.4. FASTRAND II MASS STORAGE SUBSYSTEM                                                                                                                                                                                                                               | 39                                     |

|    | 6.5. FASTRAND III MASS STORAGE SUBSYSTEM                                                                                                                                                                                                                              | 42                                     |

|    | 6.6. UNISERVO VI C MAGNETIC TAPE UNIT                                                                                                                                                                                                                                 | 45                                     |

|    | 6.7. UNISERVO VIII C MAGNETIC TAPE UNIT<br>6.7.1. Fully Simultaneous UNISERVO VIII C Subsystem                                                                                                                                                                        | 47<br>49                               |

|    | 6.8. UNISERVO VI C/VIII C SUBSYSTEM                                                                                                                                                                                                                                   | 49                                     |

|    | 6.9. HIGH SPEED PRINTER SUBSYSTEM<br>6.9.1. Line Printer                                                                                                                                                                                                              | 50<br>51                               |

|    | <ul> <li>6.10. THE UNIVAC 9000 SERIES SUBSYSTEMS</li> <li>6.10.1. Inter-Computer Control Unit</li> <li>6.10.2. Modes of Operation</li> <li>6.10.3. The UNIVAC 9200 Subsystem</li> <li>6.10.4. The UNIVAC 9300 Subsystem</li> </ul>                                    | 52<br>52<br>52<br>54<br>55             |

|    | 6.11. HIGH SPEED PUNCHED TAPE SUBSYSTEM                                                                                                                                                                                                                               | 56                                     |

| 7. | COMMUNICATIONS SUBSYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 57                                                                   |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|    | 7.1. INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57                                                                   |

|    | <ul><li>7.2. COMMUNICATION TERMINAL SUBSYSTEMS</li><li>7.2.1. Communications Terminal Module</li><li>7.2.2. Communications Terminal Module Controller</li></ul>                                                                                                                                                                                                                                                                                                                                                                | 57<br>57<br>58                                                       |

|    | 7.3. WORD TERMINAL SYNCHRONOUS<br>7.3.1. Operational Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 58<br>58                                                             |

| 8. | UNIVAC 418-111 REAL TIME OPERATING SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 60                                                                   |

|    | 8.1. GENERAL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60                                                                   |

|    | <ul> <li>8.2. SOFTWARE SYSTEM DESCRIPTION</li> <li>8.2.1. Modularity</li> <li>8.2.2. Real Time Processing</li> <li>8.2.3. Batch and Scientific Processing</li> <li>8.2.4. Multiprogramming</li> <li>8.2.5. Use of Auxiliary Storage</li> <li>8.2.6. Facility Control</li> <li>8.2.7. Utilization of Mass Storage and Drums</li> <li>8.2.8. Control Stream</li> <li>8.2.9. Input/Output</li> <li>8.2.10. Languages</li> <li>8.2.11. Utilities</li> <li>8.2.12. Operator Communications</li> <li>8.2.13. System Setup</li> </ul> | 60<br>61<br>61<br>61<br>62<br>62<br>62<br>62<br>62<br>62<br>63<br>63 |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

| 9. | EXECUTIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 64                                                                   |

| 9. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 64<br>64                                                             |

| 9. | EXECUTIVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| <ul> <li>9.3.2. Cooperative/Symbiont Structure</li> <li>9.3.2.1. Cooperative</li> <li>9.3.2.2. Symbiont Control</li> <li>9.3.2.3. Symbiont Device Handlers</li> <li>9.3.2.4. Remote Symbionts</li> <li>9.3.2.5. Independent or Utility Symbionts</li> <li>9.3.3. The File Control Subsystem</li> <li>9.3.3.1. File Control Module</li> <li>9.3.3.2. File Access Module</li> </ul> | 75<br>75<br>76<br>76<br>76<br>76<br>76<br>77<br>77<br>77 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| <ul> <li>9.4. JOB CONTROL</li> <li>9.4.1. Job Stream</li> <li>9.4.2. Facilities Allocation</li> <li>9.4.3. Element Manipulation</li> <li>9.4.4. Job Execution</li> <li>9.4.4.1. Job Loading</li> <li>9.4.4.2. End of Job</li> <li>9.4.5. Program Control</li> </ul>                                                                                                               | 79<br>79<br>79<br>79<br>80<br>80<br>81<br>81             |

| <ul> <li>9.5. REAL TIME COMMUNICATION CONTROL</li> <li>9.5.1. CTMC Handler</li> <li>9.5.2. WTS Handler</li> <li>9.5.3. Transaction Routing</li> <li>9.5.4. Queue Processor</li> <li>9.5.5. Remote Device Handlers</li> <li>9.5.6. Computer Block Interchange Technique</li> <li>9.5.7. Communication Services</li> </ul>                                                          | 80<br>82<br>83<br>83<br>83<br>83<br>84<br>85             |

| 10. LANGUAGE PROCESSORS                                                                                                                                                                                                                                                                                                                                                           | 86                                                       |

| 10.1. GENERAL                                                                                                                                                                                                                                                                                                                                                                     | 86                                                       |

| 10.2. THE UNIVAC 418–III ASSEMBLER<br>10.2.1. Symbolic Language<br>10.2.2. Assembler Organization and Operation                                                                                                                                                                                                                                                                   | 86<br>86<br>87                                           |

| <ul><li>10.3. FORTRAN</li><li>10.3.1. Language Characteristics</li><li>10.3.2. Compiler Characteristics</li><li>10.3.3. FORTRAN Support Library</li></ul>                                                                                                                                                                                                                         | 87<br>87<br>88<br>89                                     |

| 10.4. COBOL<br>10.4.1. Language Organization<br>10.4.2. COBOL Compiler Characteristics<br>10.4.3. Processor Organization                                                                                                                                                                                                                                                          | 89<br>90<br>90<br>91                                     |

| 10.5. COBOL LIBRARY                                                                                                                                                                                                                                                                                                                                                               | 92                                                       |

| 11. SERVICES AND LIBRARY                                                                                                                                                                                                         | 93                               |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 11.1. GENERAL                                                                                                                                                                                                                    | 93                               |

| <ul> <li>11.2. SORT</li> <li>11.2.1. Parameter Processing</li> <li>11.2.2. Input and Distribution</li> <li>11.2.3. Merge</li> <li>11.2.4. Output</li> <li>11.2.5. Sorting Facilities</li> </ul>                                  | 93<br>93<br>94<br>94<br>94<br>94 |

| 11.3. MERGE                                                                                                                                                                                                                      | 94                               |

| 11.4. PROGRAM MAINTENANCE                                                                                                                                                                                                        | 95                               |

| <ul> <li>11.5. PROGRAM CHECKOUT SERVICES</li> <li>11.5.1. Dump Main Storage</li> <li>11.5.2. Dump Mass Storage</li> <li>11.5.3. Inspect Main Storage</li> <li>11.5.4. Facility Display</li> <li>11.5.5. Date and Time</li> </ul> | 96<br>96<br>96<br>96<br>96<br>96 |

| 11.6. EXECUTIVE INDEPENDENT UTILITIES                                                                                                                                                                                            | 97                               |

| 11.7. SYSTEMS LIBRARY PROCEDURES                                                                                                                                                                                                 | 99                               |

| 11.8. SYSTEMS LIBRARY SUBROUTINES                                                                                                                                                                                                | 99                               |

| APPENDIXES                                                                                                                                                                                                                       |                                  |

| A. INSTRUCTION REPERTOIRE<br>A1. OPERATION CODE SEQUENCE<br>A2. FUNCTIONAL GROUP SEQUENCE                                                                                                                                        | 100<br>100<br>105                |

| B. UNIVAC 418-111 RTOS MINIMUM HARDWARE REQUIREMENTS                                                                                                                                                                             | 111                              |

| FIGURES                                                                                                                                                                                                                          |                                  |

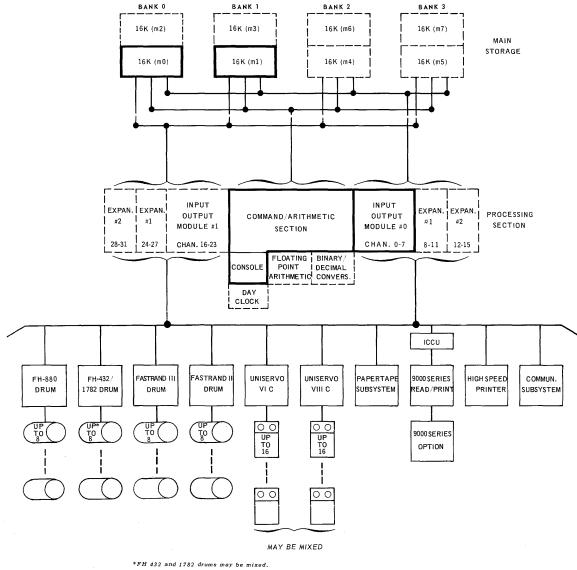

| 2-1. UNIVAC 418-III System Configuration                                                                                                                                                                                         | 6                                |

| 3-1. Storage Unit Assignment in a Maximum Storage Configuration                                                                                                                                                                  | 9                                |

| 3-2. Address Assignment                                                                                                                                                                                                          | 10                               |

| 4-1. Input/Output Module Channel Availability                                                                                                                                                                                    | 12                               |

| 4-2. ISI Buffer Control Words                                                                                                                                                                                                    | 14                               |

| 4-3. ESI Buffer Control Words                                                                                                                                                                                                    | 17                               |

| 4-4. Table Pointer Word                                                                                                                                                                                                          | 19                               |

| 5-1. Format of Reserved Locations                                                                                                                                                                                                | 22                               |

| 5-2. Fixed-Point Accumulator                                                                                                                                                                                                     | 23                               |

| 5-3. Floating-Point Accumulator                                                                                                                                                                                                  | 24                               |

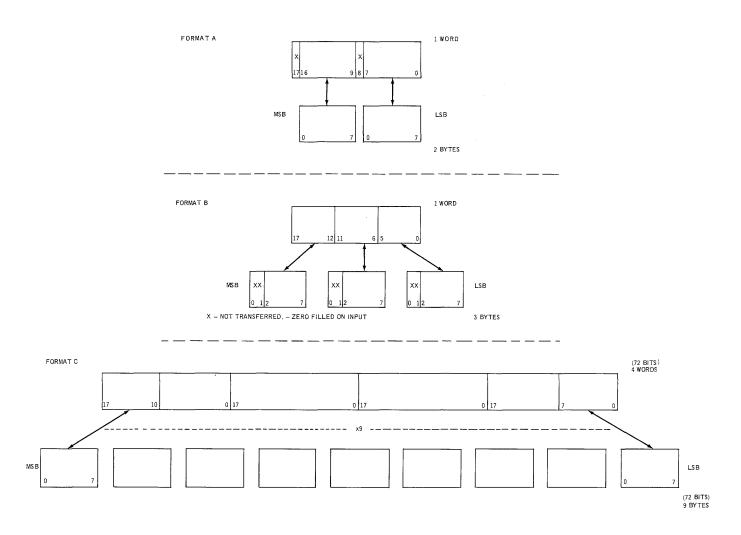

| 6-1. ICCU Data Formats                                                                                                                                                                                                           | 53                               |

## 1. INTRODUCTION

#### 1.1. UNIVAC 418-III REAL-TIME SYSTEM

The UNIVAC 418-III Real-Time System is a medium scale computer system designed to provide complete capability in the three major types of general purpose data processing -- batch, scientific, and real time. Its modular structure implements the latest advances in computer design, system organization, and programming technology. The UNIVAC 418-III Real-Time System offers the medium scale user multiprogramming capability and a real time operating system featuring an executive, a system's support library, and language processors.

#### 1.2. MAJOR TYPES OF DATA PROCESSING APPLICATIONS

The early use of general purpose computers to perform batch, scientific, or real time data processing was accomplished on a computer which, while technically classified as general purpose, was indeed highly specialized. Originally, the only applications were scientific and commercial. Because effective data transmission was unavailable, the early commercial computers were used only for batch processing. With the advent of computer controlled data communication lines, applications were separated into batch, real time, and scientific.

The specialization of the general purpose computer for the requirements of commercial batch data processing include the simultaneous reading and writing of high speed magnetic tapes, a broad data path through the input/output channels, high speed storage, and decimal arithmetic capability.

The specialization of the general purpose computer for the requirements of real time data processing include sophisticated interrupt systems, comprehensive data communication subsystems, discrete buffering of input/output for each communication line, many types of direct access storage devices, and the capability of handling a mixed variety of character coding.

The specialization of the general purpose computer for the requirements of scientific data processing include high speed fixed-point and floating-point arithmetic, and binary word-oriented high speed storage.

Advances in computer technology, particularly in the area of real time capability, have made it possible to produce general purpose computers which meet the requirements of two of the three types of data processing, but seldom all three. Many of the computers available today still have this limitation. *The UNIVAC 418-III System offers its user all three types of data processing capabilities.*

#### **1.3. SYSTEM AND PERIPHERAL CHARACTERISTICS**

The UNIVAC 418-III System provides: up to 131,072 eighteen-bit words of 750 nanosecond cycle core storage; up to 2.66 million word-per-second input/output transfer rate; storage protection; externally specified indexing (discrete communication line buffering); a large instruction repertoire; and automatic tabling of communications interrupts.

The peripheral subsystems of the UNIVAC 418-III System include: magnetic tape with from 34,160 to 96,000 frames-per-second transfer rate with dual synchronizer available for simultaneous reading and writing; FH-432/1782 magnetic drums with 1.44 million character-per-second transfer rate and 4.25 ms and 17 ms average access time respectively; FASTRAND II Mass Storage with up to 1,056,964,608 characters of storage per subsystem; FASTRAND III Mass Storage with up to 1,585,446,912 characters of storage per subsystem; and UNIVAC 9000 Series computer subsystems for online and offline card reading, card punching, and printing as well as a high speed printer subsystem with a printing speed of up to 1600 lines per minute.

The communications subsystem for the UNIVAC 418-III System is the Communications Terminal Module Controller. The Controller and its modules have been enhanced to provide additional communication-oriented functions. These functions are included in order to relieve the Command/Arithmetic Section and the currently running program of the burden of bookkeeping previously associated with computer controlled communications. Among these functions are character and message parity encoding and checking, and End-of-Message recognition. The Communications Terminal Modules offer a full range of line speed, character size, and mode capability. The Communication Terminal Module Controller provides for termination of up to 32 duplex lines. Multiple controllers can be connected to the UNIVAC 418-III System.

While the UNIVAC 418-III System is in the medium price class, it can readily be seen that it provides large scale capabilities. The size and speed of the main storage section and the versatility of the Command/Arithmetic Unit assures complete capability for handling the most demanding requirements. Together with the full range of peripheral subsystems, the system provides a virtually unlimited range of applications capability. The UNIVAC 418-III System is equally capable of handling batch, scientific, or real time processing, and it adjusts dynamically to any one or a mixture of these environments. All system operations are coordinated and controlled by a versatile executive system having full real time and multiprogramming capabilities.

## 2. SYSTEM HARDWARE

#### CHARACTERISTICS

- Up to 131,072 eighteen-bit words

- 750 nanoseconds cycle time

- Up to 2.66 million words/second data transfer rate

- Write storage protection in 256 word increments

- Externally specified indexing (discrete communication line buffering) in full or halfword mode

- 108 standard operation codes

- Floating-point arithmetic option

- Decimal-to-binary and binary-to-decimal conversion options

- Twelve classes of interrupts

- Automatic tabling of communication buffer termination interrupt (ESI)

#### 2.1. SYSTEM COMPONENTS

The UNIVAC 418-III System is constructed of six individual component classifications. The various components (or modules) of the UNIVAC 418-III System are presented in this manual under the following headings:

- Command/Arithmetic Section

- Input/Output Modules

- Main Storage

- Auxiliary Storage Subsystems

- Peripheral Subsystems

- Communications Subsystem

- 2.1.1. Command/Arithmetic Section

The Command/Arithmetic Section of the UNIVAC 418-III System contains all the arithmetic and control circuitry required to perform each instruction in the UNIVAC 418-III repertoire. The Command/Arithmetic Section performs all instruction decoding and execution sequences. Fixed-point addition and subtraction operations are performed on a single-word or double-word basis. Multiplication produces a double-word product. Division produces a single-word quotient. Double-word addition and subtraction operations are standard. The ability to perform floating-point arithmetic operations is available as an optional feature and provides double-word capability. Another optional feature provides decimal-to-binary and binary-to-decimal conversion.

#### 2.1.2. Input/Output Modules

Operation of the Input/Output Modules (IOM) is independent of the Command/Arithmetic Section; these modules control input and output data transfers. One or two IOM's may be used in each system. Each IOM contains a set of high speed Integrated General Registers (IGR) which are used as buffer control words. Each IOM contains from eight to sixteen 18-bit input/output channels. Depending on the peripheral subsystem, these channels can be used singly or in pairs in order to provide a broader data path. Each IOM operates independently of the other giving two-way simultaneity of input/output and storage with an accumulative capacity of 1.33 million 18-bit word transfers per second per module. Main storage provides separate data paths to and from each I/O Module. In previous systems, all the peripheral devices competed with each other for the use of main storage cycles. The simultaneity achieved by the modular design of the UNIVAC 418-III System and the speed of each module makes it possible to handle high speed peripheral devices with no reduction in overall system performance.

#### 2.1.3. Main Storage

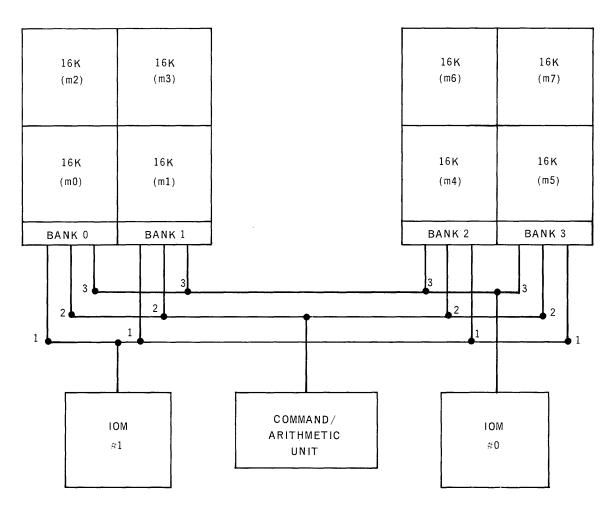

The UNIVAC 418-III System provides a main storage expandable in 16,384 eighteenbit word increments from a minimum of 32,768 words to a maximum of 131,072 words. The main storage read/restore cycle time is 750 nanoseconds. A parity check is made on every storage cycle to ensure accuracy of operation. Up to four 32,768 word banks of storage are provided. Each bank has an access path for IOM #0, IOM #1, and the Command/Arithmetic Unit. Thus, three-way simultaneity can be accomplished to main storage. In previous systems, the input/output section and the Command/Arithmetic Section competed with each other for main storage cycles. Program execution was delayed for every input or output data transfer cycle. The speed of the main storage of the UNIVAC 418-III System and the separate data paths for the IOM's and the Command/Arithmetic Unit makes possible truly simultaneous operation with no delays in program execution.

#### 2.1.4. Auxiliary Storage Subsystems

Up to eight FH-432 and/or FH-1782 magnetic drums may be attached to a single control unit. Each FH-432 drum can store 524,288 eighteen-bit computer words plus parity (1,572,864 alphanumeric characters). Each FH-1782 drum can store 4,194,304 eighteen-bit computer words plus parity (12,582,912 alphanumeric characters). Both types of drum transfer data at up to 1.44 million characters per second. The average access time of the FH-432 is 4.25 milliseconds and that of the FH-1782 is 17 milliseconds.

Up to eight FH-880 magnetic drums may be attached to a control unit. Each FH-880 drum can store 1,572,864 eighteen-bit computer words plus parity (4,718,592 alpha-numeric characters) with a transfer rate of up to 360,000 characters per second. The average access time of the FH-880 is 17 milliseconds.

#### 2.2. SYSTEM CONFIGURATION

Figure 2-1 shows a central site configuration for the UNIVAC 418-III System. The lower portion illustrates the standard peripheral subsystems which can be connected to the system. These peripheral subsystems are described in more detail in Sections 6 and 7 of this manual.

The upper portion of Figure 2-1 illustrates the components which constitute the equivalent of what, in the past, has been called the central processor unit. These components are the main storage section (described in Section 3), the Input/Output Modules (described in Section 4), and the Command/Arithmetic Section (described in Section 5).

The minimum set of these components: the Command/Arithmetic Section with the Console, one IOM with eight input/output channels, and 32,768 words of main storage, is shown inside the heavy lines. The Command/Arithmetic Unit may be expanded to include floating-point arithmetic, binary/decimal conversion instructions, and the Day Clock. The input/output to the UNIVAC 418-III System may be expanded by adding the expansion channels to IOM #0 and/or by the addition of a second IOM, or both. The addition of IOM #1 provides for three main storage referencing units operating on an independent basis.

Main storage may be expanded to 65,536 words horizontally,  $16K \pmod{(m00)}$ , then  $16K \pmod{(m1)}$ , then  $16K \pmod{(m2)}$ , then  $16K \pmod{(m3)}$ . The expansion beyond 65,536 words depends on the manner in which the first 65,536 words were reached. The capability for three-way simultaneous and independent referencing of main storage is provided by the addition of IOM #1, and at least 49K in three banks of storage.

K = 1024 words

Minimum system in heavy lines; optional in broken lines

6

## 3. MAIN STORAGE

#### 3.1. GENERAL

Main storage of the UNIVAC 418-III System is a high performance, immediate access repository for instructions, data, and input/output communications areas. Its design and construction fully supports the concepts of multiprogramming, modularity, and system integrity. Among the characteristics of the UNIVAC 418-III main storage are:

- 750 nanosecond read/restore cycle time

- 32,768 to 131,072 eighteen-bit words

- Parity checking on all storage references

- Three-way simultaneous access by two Input/Output Modules and the Command/ Arithmetic Section

- Modular expansion -- four banks with one or two 16,384 word modules per bank

- Hardware storage protection -- write lockout boundaries establishable in 256 word increments

While these features are all discussed generally as storage features, some of them such as three-way simultaneity and storage protection are functions of the entire system. The main storage, through proper organization, becomes a series of allocatable components of the system in the same manner as the peripheral devices. In realizing this objective, some departures from the traditional close integration of the processor and the storage element have taken place:

- The main storage is comprised of independently accessible banks, yet it presents a continuous addressing structure to the Command/Arithmetic Section.

- In order to service one or two Input/Output Modules and the Command/Arithmetic Section, a method of establishing relative priority between them at each bank is provided in the case that two or three of these referencing units attempt to reference the same bank simultaneously.

To assure that the requesting components will wait for storage access, communication between the bank and the component is done on a request/acknowledge basis.

#### 3.2. BASIC STORAGE MODULE

The basic storage module is composed of 16,384 words of ferrite cores. Each word is 18 bits in length and carries two additional parity bits in nonaddressable levels, one bit for each halfword. One or two storage modules may be assigned to a bank of storage. The physical components of each bank are:

- An 18-bit read/restore register

- Parity checking circuits

- Request/acknowledge circuits

- Maintenance switches allowing each bank to be removed logically for servicing or testing

#### 3.3. BANK PARITY ERROR

Parity is checked when reading or calculated when writing on each storage access. If a parity error is detected, the bank issues a parity error interrupt signal to the Command/Arithmetic Unit. Thus, in addition to the proven reliability of sub-microsecond Univac core memory, the main storage of UNIVAC 418-III System has parity checking for storage reference validation.

#### 3.4. MULTIPLE BANK ACCESS

Each storage bank has three connection paths for storage references. Two or three of the referencing units (one or two Input/Output Modules and the Command/Arithmetic Unit) may attempt simultaneous reference to the same storage bank. The path with the highest priority is serviced first, then the second highest is serviced, and then the third highest is serviced. Should another request occur before the lowest priority path is serviced, that request waits until the lower priority path(s) have been serviced. This sequence prevents any one of the referencing units from monopolizing the use of the storage bank.

#### 3.5. STORAGE PACKAGING

The first 16,384 words of both Bank 0 and Bank 1 and the power supplies for each bank are packaged in a Storage Cabinet. A Storage Expansion Cabinet is required to house the second 16,384 words for Banks 0(m2) and 1(m3). The same packaging arrangement is made for Banks 2 and 3.

#### 3.6. STORAGE CONFIGURATIONS

Figure 3-1 illustrates the maximum storage unit and referencing unit configuration. The minimum configuration is the Command/Arithmetic (C/A) Unit, IOM \*0 and 32K of storage in Bank 0(m0) and Bank 1(m1). This provides two-way simultaniety with 16K in each bank. The capacity of each bank may then be expanded by an additional 16K.

Three-way simultaneity capability is achieved by adding Bank 2 and IOM #1. The addition of Bank 3 provides greater flexibility of storage allocation to ensure as much as possible the achievement of three-way simultaneity.

Figure 3-1. Storage Unit Assignment in a Maximum Storage Configuration

The modular addressability of main storage allows the user to expand his memory requirements either by adding banks to provide more simultaneity or expanding within a bank to provide more storage capacity, or both.

The main storage of the UNIVAC 418-III System is constructed so that the banks of storage have a physical unit/logical unit relationship. This is accomplished by a series of printed circuit cards mounted in each storage cabinet. The printed circuit cards are used to assign the bank number to each of the memory modules. Referring to Figure 3-2, the normal assignment of addresses with a full 131,072 words of storage would be:

| ADDRESSES     | BANK | MODULE     |

|---------------|------|------------|

| 0-16383       | 0    | mO         |

| 16384-32767   | 1    | m1         |

| 32768-49151   | 0    | m <b>2</b> |

| 49152-65535   | 1    | m3         |

| 65536-81919   | 2    | m4         |

| 81920-98303   | 3    | m5         |

| 98304-114687  | 2    | m6         |

| 114688-131072 | 3    | m7         |

Figure 3-2. Address Assignment

Three-way simultaneity is achieved with three banks of storage and three referencing units. This level of performance is normally achieved when the fifth storage module (m4) is acquired. However, if this increase in system performance is desired, the printed circuit cards make it possible for the user to elect to have three-way simultaneity with as little as 49,252 words of storage and three referencing units. The schematic for this configuration would show the first 16K (m0) in Bank 0; the second 16K in Bank 1(m1), and the third 16K in Bank 2(m4). The first and second 16K (m0 and m1) are housed in one storage cabinet, and the third 16K (m4) occupies half of another storage cabinet. The increase to 65,536 words for this configuration would be accomplished by adding a fourth 16K (m5) which would be housed in the other half of the second storage cabinet. Expansion of this configuration beyond 65,536 words requires storage expansion cabinets, with space for two 16K modules each.

#### 3.7. SIMULTANEITY OF STORAGE ACCESS

Computer systems in which the main storage is an integrated component of the central processing unit utilize a storage referencing technique called Main Store Interrupt. Such systems have a single Storage Address Register. The purpose of the Storage Address Register is to precisely define the coordinates for the storage location to be referenced. With only a single Storage Address Register, the storage locations referenced by the input/output section and the Command/Arithmetic Section have to time-share the storage unit. Under Main Store Interrupt, the input/output section is given priority control of the Storage Address Register. When the input/output section requires a storage reference, the access and execution of instructions is delayed for the data transfer. Therefore, if more than one high speed I/O device is in operation at the same time, the program processing may be delayed (interlocked) until the rate of I/O transfer slackens. Most computer systems utilize the Main Store Interrupt technique.

In the UNIVAC 418-III System, each Input/Output Module (IOM) as well as the Command/Arithmetic Unit contains a Storage Address Register. When any one of these devices requires a reference to main storage, it presents a request signal to the appropriate storage bank. Bank selection is determined by the two high order bits of the Storage Address Register. When the request is granted by the storage bank, the low order 15 bits of the Storage Address Register are used to control the access of the specific storage location. Thus, if two (or three) of these devices make simultaneous requests of different storage banks, each storage bank cycles simultaneously with and independently of the others. On this basis, one or two I/O data transfers occur between input/output devices and main storage at the same time that the Command/Arithmetic Unit is accessing an instruction or data. In a multiprogramming environment, the execution time of one program and the input/output time of one or more other programs can now be overlapped to provide simultaneous operation of several programs.

#### 3.8. STORAGE PROTECTION

To prevent inadvertent program changes to out-of-range storage addresses, the UNIVAC 418-III System provides the Guard Limits Register for hardware storage protection. The Guard Limits Register contains the upper boundary limit and a lower boundary limit which is loaded by the Executive to establish allowable operating areas for each program. Before giving control to a particular program, the Executive loads the Guard Limits Register with the boundaries which were assigned to this program at load time and then sets Guard Mode. Storage protection is assigned in increments of 256 words of storage.

Before each change of storage by the Command/Arithmetic Unit, a limits check is performed on the address to ensure that it falls inclusively within the upper and lower limit portions of the Guard Limits Register. Should the address to be referenced *not* fall within those limits and the Guard Mode is set, a Guard Mode Interrupt is generated, preventing the erroneous reference and transferring control to the Executive for appropriate action.

Thus, in a multiprogramming environment, the accidental alteration of one program area by another program, even one being tested, is prevented. This is of particular significance in a real time multiprogramming environment, where the real time program cannot be halted or placed in jeopardy by program testing.

The Executive normally operates in open mode. When the Executive gains control, the Guard Mode is de-activated. This gives the Executive free access to the entire main storage. When finished with its task, the Executive reloads the Guard Limits Register and reactivates the Guard Mode before giving control to a worker program.

## 4. INPUT/OUTPUT MODULES

#### 4.1. GENERAL

The Input/Output Modules (IOM) of the UNIVAC 418-III System provide the data paths and the control circuitry necessary for direct communication between main storage and the input/output devices. The portion of the circuitry and the data paths which are necessary to connect a peripheral subsystem with main storage is called a channel. Each channel allows bidirectional transfers between main storage and the devices on that channel. Each channel contains 36 data lines (18 for input and 18 for output).

The minimum UNIVAC 418-III System includes one Input/Output Module. A second IOM may be added to provide additional channels and an additional main storage referencing unit. As shown in Figure 4-1, each basic IOM contains a minimum of eight channels and can be expanded in increments of four channels to a maximum of sixteen per IOM -- 32 channels for an entire UNIVAC 418-III System.

| MINIMUM           | EXPANSION 1   | EXPANSION 2    |

|-------------------|---------------|----------------|

| (8)               | (4)           | (4)            |

| CHANNELS 0 THRU 7 | CHANNELS 8-11 | CHANNELS 12-15 |

Figure 4-1. Input/Output Module Channel Availability

Most peripheral subsystems utilize both the input and corresponding output lines of the same channel. Data transfers on these subsystems are bidirectional but may not occur at the same instant of time through a single channel. Similarly, data transfers may not occur at the same instant through two different channels on the same IOM. However, if the main storage buffer areas for input/output transfers through two channels of different IOM's are located in different storage banks, these data transfers can occur at the same instant. When two or more subsystems are requesting data transfers at the same time, each IOM performs as a multiplexer with a transfer rate of up to 1.33 million 18-bit words (approximately 4 million characters) per second. The transfer rate capability is 2.66 million 18-bit words if there are two IOM's operating in separate storage banks from each other and from the Command/Arithmetic Section. Each IOM functions as a small processor. Programmed instructions executed by the Command/Arithmetic Unit load index values into the Buffer Control Words located in the IOM and establish desired peripheral subsystem activity. From that point on, the IOM scans the input/output channels automatically, accepting data from and passing data to the subsystem at the normal rate of the subsystem. When a peripheral subsystem requests a data transfer, the contents of the Buffer Control Word for that channel are used as a main storage address, and the transfer occurs. At the same time, the IOM updates the contents of the Buffer Control Word and tests for a terminal condition. This entire operation requires only the time for one memory cycle, 750 nanoseconds.

The Buffer Control Words are located in very high speed Integrated General Registers which are assigned main storage addresses. However, instead of making reference to the main storage addresses, reference is made to the Integrated General Registers.

#### 4.2. NORMAL INPUT/OUTPUT MODE

Each channel operates in one of three states: input, output, or function. The input and output states are employed when transferring data to or from main storage. The channel has the capability of alternating between the input and the output state on consecutive memory cycles. The function state is the means by which the Command/ Arithmetic Unit establishes initial communication with a peripheral subsystem and is basically an output state. During this state, the Command/Arithmetic Unit causes the IOM to transfer one or more function words to a peripheral subsystem. These function words direct the subsystem to perform the desired operation.

#### 4.3. BUFFER CONTROL WORDS

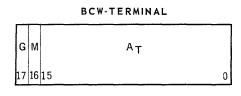

The actual word-by-word transfer (regardless of the transfer state) through a given channel is governed by the Buffer Control Words (BCW) in the IOM. Two Integrated General Registers (IGR) are used to control output and two are used to control input for each channel. The first of these two words is the Buffer Control Word for Terminal Address (BCWT). The second is the Buffer Control Word for Initial Address (BCWI).

The format of the Buffer Control Words is shown in Figure 4-2.

${\rm A}^{}_{\rm I}\,$  : The address of the first word in the buffer area (becomes the current address).

$A_{\rm T}$  : The address of the last word in the buffer area.

G : A<sub>I</sub> Modifier

G = 0  $A_I$  will be incremented by one for each buffer word transfer.

- G = 1  $A_{I}$  will be decremented by one for each buffer word transfer.

- M : Monitor

- M = 0 Channel transfer will terminate when bits 15-0 of the current address  $(A_T)$  equals bits 15-0 of the terminal address  $(A_T)$ .

- M = 1 Channel transfer will terminate when the current address equals the terminal address, and a monitor interrupt will be generated for that channel.

- E : Used by the hardware. This bit must initially be zero.

#### Figure 4-2. ISI Buffer Control Words

The normal input/output mode is referred to as Internally Specified Indexing (ISI) because of the fact that the presence of a data request from a subsystem causes the input/output circuitry of the UNIVAC 418-III System to internally generate the address reference to the specific Buffer Control Words based on the channel through which the data request is received.

#### 4.4. EXTERNALLY SPECIFIED INDEX MODE

The Externally Specified Index (ESI) feature in conjunction with Univac data communication subsystems allows multiple communication lines to transfer characters automatically to and from main storage through a pair of IOM channels. The pair of channels is required because of the manner in which the ESI mode functions.

When operating in ESI mode, each communication line has its data flow governed by its own unique pair of BCW's. Unlike the BCW's for normal mode, the ESI Buffer Control Words are located in main storage to allow accommodation of many multiplexed communication lines. As each line presents a character for transfer to main storage, the address of the unique pair of Buffer Control Words associated with that communication line is also presented to the channel; thus, the BCW address is externally specified. The BCW address is presented on the input lines of one of the paired channels, and the character to be transferred is presented on the input lines of the other of the paired channels. In this manner, the characters received from or transferred to a given communication line are stored in or retrieved from a discrete buffer area controlled by a unique pair of Buffer Control Words for the communication line. The flow of data from a communication line to and from main storage is accomplished under control of the Input/Output Module without the delay or intervention of the Command/Arithmetic Section.

Any adjacent even/odd pair of IOM channels except 0 and 1 can be specified to operate in ESI mode.

#### 4.4.1. Fullword or Halfword ESI Storage of Characters

Paired channels which have been specified to operate in ESI mode must be further designated to operate in fullword or halfword storage mode. In fullword mode, each character is stored in a separate 18-bit word of storage. In halfword mode, two characters are stored in an 18-bit word. The halfword storage method provides twice the capacity in the same number of main storage locations. When storage mode is specified, all communication lines connected through that single pair of channels must operate in the same mode.

Characters stored in fullword mode are placed in the storage location beginning at bit position 0. The unentered bit portion of a storage location (which depends on character size) is set to binary zero. Characters stored in halfword mode are placed in the storage location beginning at bit position 0 or bit position 9. The unentered bit portion of each halfword is set to binary zero.

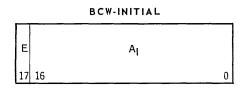

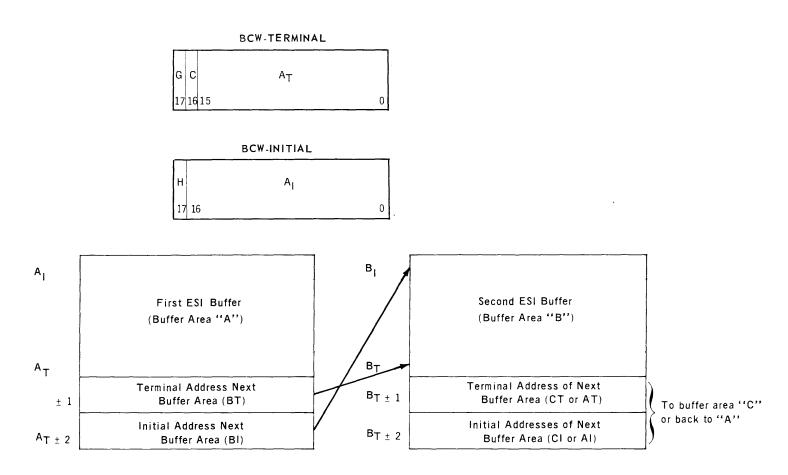

The ESI Buffer Control Words have a format similar to the normal (ISI) Buffer Control Words. The format is shown in Figure 4-3.

#### 4.4.2. Hardware ESI Buffer Chaining

The hardware control of data communication lines in the UNIVAC 418-III System includes ESI buffer chaining. The purpose of ESI buffer chaining is to eliminate the programmed intervention usually required in order to provide additional buffer areas for communication messages. The buffer chaining technique provides the mechanism to include these specifications, as required, during the operation of the system rather than having them a near rigid specification to a supervisory software program. In addition to this flexibility, hardware buffer chaining also eliminates the storage locations usually required for software control of this function plus the time required to execute those instructions each time a buffer termination occurs. ESI buffer chaining is controlled by a specific bit position in the ESI Buffer Control Word for Terminal Address (see Figure 4-3). When the current address in the Initial Address BCW is equal to the Terminal Address, the chaining control bit is examined. If this bit is set to 1, the hardware automatically causes the contents of the two storage locations following the address specified by the Terminal Address BCW to become the new Terminal and Initial Address BCW's and data transfer continues. If the chaining control bit is set to 0, no buffer chaining occurs and data transfer terminates. In either case, when the end of a buffer area is reached, the ESI interrupt status word is stored.

Figure 4-3 contains an example of automatic ESI buffer chaining. Assume the C bit in the Terminal BCW which specified Buffer A is set to 1. When  $A_I$  equals  $A_T$ , the hardware examines the C bit IInon detecting that it is set to 1.  $A_T$  + 1 becomes the new Terminal BCW,  $A_T$  + 2 becomes the new Initial BCW, and data transfer continues. The occurrence of the end of Buffer A is automatically stored in the Interrupt Table (discussed in 4.4.3). The new Buffer Control Words specify Buffer B. When  $B_I$  equals  $B_T$ , the C bit is again examined; if it is set to 1,  $B_T$  + 1 and  $B_T$  + 2 become the new BCW's. These two words can specify a third buffer (buffer C) or a return to Buffer A.

Upon reaching the end of a chain (indicated by C = 0), the contents of the Initial BCW equals the address in the Terminal BCW, and the Terminal BCW is cleared to 0's. The purpose of clearing the Terminal BCW to 0's at the conclusion of a buffer sequence is to prevent any further data transfers to or from the particular communication line. Formerly, upon conclusion of a buffer area, the entire processor channel was terminated. This necessitated Executive intervention to reactivate the channel and allow data transfers to proceed on other communication lines. Using this new technique, the channel is not terminated. If the communication line inadvertently requests additional data transfers after the Terminal BCW has been cleared to 0's, this condition is detected and such requests are logically ignored. This not only prevents the occurrence of a runaway buffer but also eliminates the necessity for the programmed intervention normally required upon termination of a communications buffer in order to prevent the situation.

- $A_T$  : Terminal Address

- A<sub>I</sub> : Initial Address (becomes current)

- $\begin{array}{rcl} G & : = 0 & \text{Increment } A_T \\ & = 1 & \text{Decrement } A_T \end{array}$

- H : = 0 Lower Half

- = 1 Upper Half

- $\begin{array}{rcl} C & : & = 0 & \text{No Chaining} \\ & & = 1 & \text{Chaining} \end{array}$

- Figure 4-3. ESI Buffer Control Words

#### 4.4.3. Automatic Tabling of ESI Interrupts

Automatic tabling of ESI buffer termination and external interrupt status word has been included in the UNIVAC 418-III System. This feature precludes the necessity of a special hardware transfer of control (an internal interrupt) to the Executive each time a communication line buffer area is filled or exhausted as well as making unnecessary the execution of any user provided subroutine.

In the UNIVAC 418-III System, the occurrence of an internal interrupt is handled by a combination of ESI buffer chaining and the automatic tabling of ESI interrupts. The buffer chaining automatically provides an alternate buffer area for the continuity of the data transmission. The automatic tabling of the interrupt associated with the buffer termination provides a record of the occurrence of the event without Executive intervention.

The hardware permits the UNIVAC 418-III Executive to refuse or to accept control when an interrupt attempts to cause a transfer. When the Executive is in the process of providing a series of ESI interrupt status words to the communication control routine, the IOM hardware will continue to table ESI interrupts into main storage without disturbing the C/A unit. Any buffer termination or external interrupt which occurs under these circumstances continues to be stored in an Interrupt Status Table. Upon completion of its task, the Executive examines the tabling mechanism to determine if any interrupts have occurred during the period when interrupts were prevented. If it is determined that an ESI interrupt was tabled during the period when ESI interrupts were prevented, the Executive would again provide the communications control routine with the accumulated interrupt status words. The automatic tabling of interrupts prevents the unnecessary transfer of control and execution of instructions to inform the Executive that there has been an ESI interrupt when the Executive is busily engaged in passing previous ESI interrupts to the communications control program. If no ESI interrupts occur during the period of interrupt prevention, the Executive releases the ESI interrupt lockout.

Each IOM provides an Integrated General Register which is used as the Interrupt Table Pointer for the communications channels on the IOM. The Table Pointer Word provides for specifying the size of the table in increments of 64 words to a maximum size of 512 words. The Interrupt Table Pointer Word also contains an address portion which specifies the location in the table to be used to store the next interrupt status word; each time a status word is stored, this address is incremented by one. When it becomes the last address in the table, the status is stored, and the address is reset to point to the beginning of the table. See Figure 4-4.

#### INTERRUPT POINTER

|    | тs | В  |   | ТР |   |

|----|----|----|---|----|---|

| 17 | 15 | 14 | 9 | 8  | 0 |

#### TS: Interrupt Table Size

This field specifies the size of the interrupt table as follows:

| TS (Octal) | Table size in words (Decimal) |

|------------|-------------------------------|

| 0          | 64                            |

| 1          | 128                           |

| 2          | 192                           |

| 3          | 256                           |

| 4          | 320                           |

| 5          | 384                           |

| 6          | 448                           |

| 7          | 512                           |

B: Address of the interrupt table location.

.

This address must be located in the first 32K of storage. (The address is in 512 word increments.)

TP: A specific address within the table in which the next interrupt will be stored. It must initially be all zeros.

Figure 4-4. Table Pointer Word

The combination of the automatic tabling of ESI interrupts and ESI automatic buffer chaining provides an extremely versatile method for the design and control of communication lines. Formerly, these conditions required critical design of programmed subroutines, the space required to store these subroutines, and the time required to execute the instructions. The new techniques in the UNIVAC 418-III System permit the user to devote his attention to the processing of the data for communications rather than to tedious detail.

## 5. COMMAND/ARITHMETIC SECTION

#### 5.1. INTRODUCTION

The Command/Arithmetic Section (C/A) of the UNIVAC 418-III System is the unit which most nearly corresponds to a central processor unit. As previously described, the input/output and the main storage sections are now separated and perform independently of the Command/Arithmetic Section.

The Command/Arithmetic Section consists of two basic sections: The Command (or Control) Section and the Arithmetic (or Processing) Section.

The Command Section provides the logic for instruction decoding and execution. It includes the Instruction Address Register, which is used for the access of instructions and as a base register for operand access; the Special Register, used as a base register for operand access; and the Index Register Pointer, which is used to control operand address modification. The Command Section is responsible for the initiation of input/output functions but not for the handling of the input/output data transfers associated with these functions. Input/output data transfers occur independently between the Input/Output Modules and main storage under the control of the Input/Output Modules. The Command Section also is responsible for hardware servicing of interrupts.

The Arithmetic Section consists of the accumulators and control circuits necessary for the performance of fixed and (optional) floating-point and binary/decimal conversion arithmetic; shifting; logical operations; tests; and the control of the Block Transfer operation.

#### 5.2. THE COMMAND SECTION

In addition to the previously discussed registers, the Command Section contains the circuitry necessary to reference the Integrated General Registers (IGR) located in the Input/Output Modules and the reserved locations in main storage. The function of the Integrated General Registers is explained in Section 4. The Special Register, the Instruction Address Register, and the Index Register Pointer are located in the Command/Arithmetic Unit but do not have main storage addresses.

#### 5.2.1. Reserved Locations

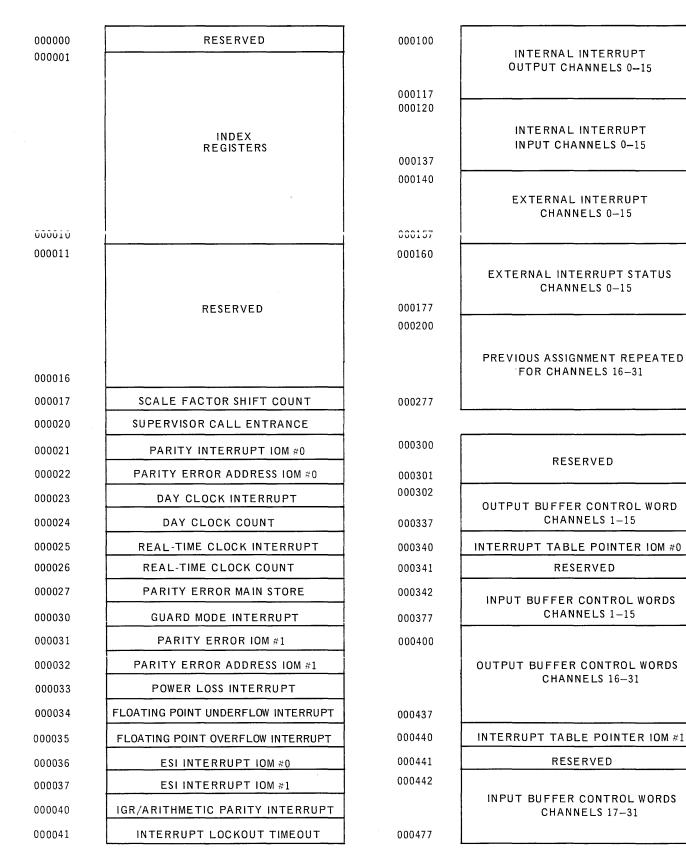

Figure 5-1 shows the location and use of the reserved locations and main storage addresses. Locations  $000302_8$  to  $000377_8$  are Integrated General Registers which are physically located in Input/Output Module #0. Locations  $000400_8$  to  $000477_8$  are Integrated General Registers which are physically located in Input/Output Module #1.

#### 5.2.2. Special Register

The Special Register (SR) is a six-bit register whose contents may be used as a base register for Type I instruction operand access. One of the bits in the Special Register is the SR Active bit. When this bit is set to 1, the other five bits become the high-order five bits of a 17-bit address whose low-order 12 are provided in the Type I instructions. Type I instructions are sensitive to the Special Register. The contents of the SR Active bit and the other five bits of the Special Register can be varied under program control.

#### 5.2.3. Instruction Address Register

The Instruction Address Register (IAR) is a 17-bit register whose contents are used to control the access of instructions from main storage. The IAR has additive properties which normally specify incrementation by one to provide sequential access of instructions. The test commands specify an increment of two in order to perform branching (skipping). The entire contents of the IAR may also be changed by the jump commands in order to provide complete transfer of control.

In addition to its function of providing access to instructions, the high-order five bits of the IAR may also be used as a base register for operand access in certain of the Type I and Type II instructions. If the Type I instruction is not SR sensitive, or if it is SR sensitive and the SR Active bit is not set, then the high-order five bits of the IAR become the high-order five bits of the operand address whose loworder 12 bits are supplied within the instruction. Certain of the Type II instructions cannot be SR sensitive and always use the high-order five bits of the IAR for operand access. The effect of using the high-order five bits of IAR for operand access is to select an operand which is located in the same 4096 word segment as the instruction which calls for the access.

#### 5.2.4. Index Register and Index Register Pointer

Eight main storage locations are reserved for use as Index Registers (IR). The function of the Index Register Pointer (IRP) is to control the storing and loading of one flip-flop type B-register to and from one of these Index Registers. The contents of the B-register are used for address modification in those instructions which call for address modification. The function of Index Register address modification takes place after and in addition to Special Register or Instruction Address Register Base modification.

The Index Register Pointer is a three-bit register whose contents can be set from 0 to 7 by a Load Index Register Pointer instruction. When this instruction is executed, the present contents of the IRP is the designation used to control the automatic storing of the B-register. After storing the contents of the B-register, the IRP is then loaded with the "new" value. This new value then designates the automatic loading of the B-register.

Figure 5–1. Format of Reserved Locations

22

When Index Register modification is called for by an instruction (Type I, Type II, or Type III), the modification takes place at no increase in the execution time of the instruction because the modification value is in the very high speed B-register.

#### 5.2.5. Real Time Clock and Day Clock

The very nature of real time operations makes it necessary for the computer system to be capable of responding to computer-time demands. Two clocking devices are available with the UNIVAC 418-III System, the real time clock, which is standard; and the day clock, which is an optional feature.

The circuitry for control of the real time clock is located in Input/Output Module #0. Every 200 microseconds this circuitry causes the contents of main storage location  $000026_8$  to be decremented by one. When the value of location  $000026_8$  is equal to 0, the circuitry creates a Command/Arithmetic Unit interrupt and causes control to be transferred to main storage location  $000025_8$ . By loading the appropriate value into location  $000026_8$ , the real time clock generates an interrupt after the lapse of a specified time. For example, a value of  $5000_{10}$  would cause an interrupt at the end of one second. The real time clock is under control of the executive which provides the user program with the capability for establishing time-oriented initiation of programmed sequences.

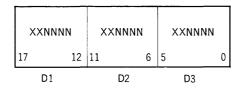

The day clock, which is a 24-hour clock, is an optional feature of the UNIVAC 418-III System. A display on the console shows hours, minutes, tenths, and hundreths of minutes. The clocking mechanism updates a fixed location in main storage every six seconds and causes an interrupt transfer of control to location 0000238 each minute. The time of day appears in the fixed main storage location 0000248 in the following binary coded decimal format:

| HOURS               |    | MINUTES |    |     |   |       |    |      |

|---------------------|----|---------|----|-----|---|-------|----|------|

| T <sub>E</sub><br>N | UN | ITS     | TE | INS | ι | JNITS | ΤE | NTHS |

| 17 16               | 15 | 12      | 11 | 8   | 7 | 4     | 3  | 0    |

The executive uses the day clock to establish the time for its time/date control function. The time is available to the worker program via an executive request.

#### 5.3. THE ARITHMETIC SECTION

The Arithmetic Section consists of two 18-bit accumulators and a number of special purpose registers and circuits which are designed to control and perform the arithmetic, logical, transfer, shift, compare, test, etc., operations in the UNIVAC 418-III instruction repertoire. The two 18-bit registers are combined to form a single 36-bit register for certain of these operations. The 36-bit accumulator is called A. As shown in Figure 5-2, the two 18-bit registers are called A Upper (AU) for the high-order 18 bits of A and A Lower (AL) for the low-order 18 bits of A.

| 35 |         | "A"  |         | 0 |

|----|---------|------|---------|---|

|    | A Upper |      | A Lower |   |

| 17 |         | 0 17 |         | 0 |

Figure 5-2. Fixed-Point Accumulator

#### 5.3.1. Fixed-point Arithmetic

Fixed-point binary arithmetic add and subtract may be performed on an 18-bit (single length) basis in either AU or AL, or on a 36-bit (double length) basis in A. Multiplication of two 18-bit operands produces a 36-bit product in A. Division uses the contents of A as a 36-bit dividend which is replaced by an 18-bit quotient in AL and an 18-bit remainder in AU.

#### 5.3.2. Floating-point Arithmetic

The optional floating-point feature of the UNIVAC 418-III System provides highspeed arithmetic operations for scientific and engineering applications using floating-point binary notation. The floating-point notation used consists of an eight bit characteristic (exponent), a 27-bit mantissa (fixed-point part), and a 1-bit sign position as shown in Figure 5-3.

| s  | CHARACTERISTIC<br>(EXPONENT) | MANTISSA<br>(FIXED-POINT PART) |  |

|----|------------------------------|--------------------------------|--|

| 35 |                              | 26 0                           |  |

Figure 5-3. Floating-Point Accumulator

The eight-bit characteristic (exponent) provides a range of plus or minus  $2^7$  -1, and the mantissa (fixed-point part) provides precision of  $2^{27}$  -1. In addition to the arithmetic functions of add, subtract, multiply, and divide, the floating-point feature provides a Pack and an Unpack instruction.

All floating-point operations are performed on normalized operands and produce normalized results. The speed of execution of floating-point arithmetic instructions in the UNIVAC 418-III System is greater than that of some higher priced systems. For example, the Multiply command requires only 12 microseconds including indexing of the operand and normalizing of the result.

#### 5.3.3. Binary/Decimal Conversion Instructions