# PRELIMINARY UNIVAC 1100 Systems

# Marketing Education

UE- 7022

# PRELIMINARY

# UNIVAC C/SP HARDWARE SYSTEM OVERHEAD MANUAL

This document contains diagrams which can be used for overhead transparencies in presenting the UNIVAC Communications/Symbiont Processor. Each diagram has a facing (odd pages) script describing it. For more detailed information, reference UNIVAC Documentation on the C/SP (indicated in Section VI of this manual). The intent of this manual is modular: presentations may be given using the overheads (even pages) as they are, along with the UNIVAC Documentation on the C/SP as reference, or the overheads may be used as a basis for the type of presentation needed.

Prepared by: Ronald E. Vilmo Marketing Education Worldwide Marketing and Services Roseville, Minn.

# CONTENTS

# SECTION

- I. C/SP HARDWARE

- II. SPECIAL DEVICE CHANNEL

- III. MULTIPLEXER/SELECTOR CHANNEL

- IV. ADAPTER CHANNEL

- V. GENERAL PURPOSE COMMUNICATION CHANNEL

- VI. SOFTWARE OVERVIEW AND MATERIALS

SECTION I

# SECTION I INDEX - C/SP HARDWARE

- 1.–2 HARDWARE BLOCK DIAGRAM

- -4 MEMORY

- -6 FIXED MEMORY

- -8 WORD AND INSTRUCTION FORMATS

- -10 PROGRAM STATUS WORD

- -12 STORAGE PROTECT

- -14 INTERVAL TIMER

- -16 C/SP INTERRUPT SEQUENCE

- -18 INTERRUPT CLASS AND CODE

- -20 INTERRUPT CLASS AND STATUS

- -22 START 1/O INSTRUCTION

- -24 EFFECTIVE ADDRESS (SIO)

- -26 DEV. 00-07 FORMAT (SIO)

- -28 I/O FLOW

- -30 APPENDIX A

### INTRODUCTION TO C/SP

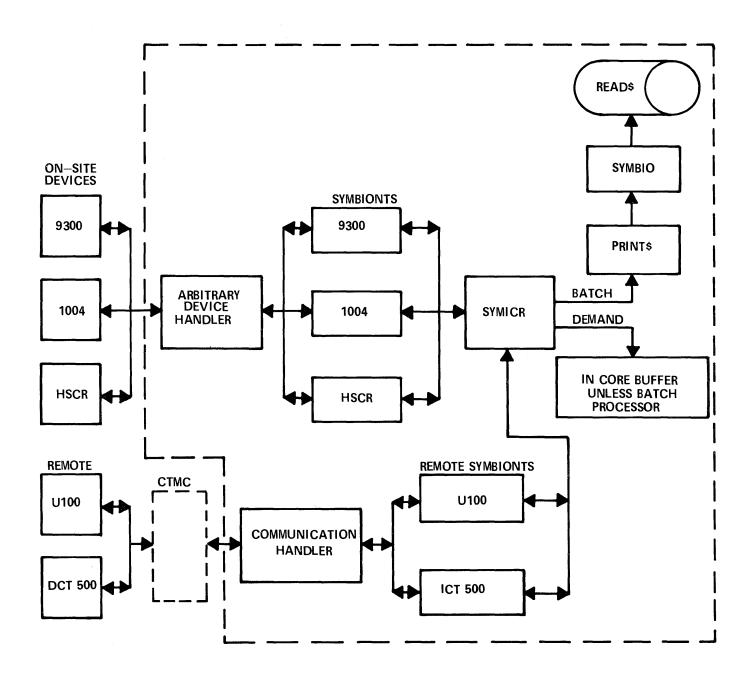

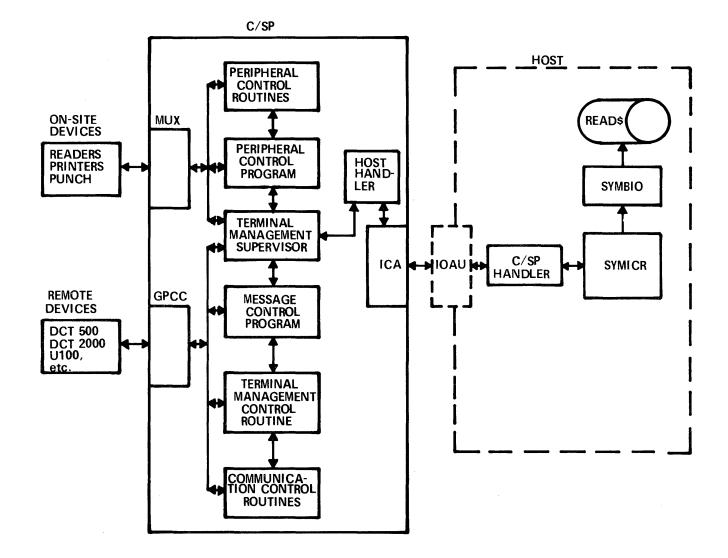

The Communications/Symbiont Processor is a high performance internally programmed communications concentrator-multiplexer intended for use as an on-site communications subsystem. The C/SP can control low and high speed communication lines and provide interfacing to a central computer system.

The primary purpose of the C/SP is to unburden the central computer software of the need for complex communication handlers and sub-routines, thus relieving the load on the central computer. The throughput of the system is thus increased by the reduction of central system overhead. The C/SP is utilized to increase speed and efficiency of on-line message switching, data manipulations, formatting, editing, translation, and verification.

As a remote, the C/SP effects reduced line costs and unburdens the central complex by performing message/data manipulations and exchanging all data with it over high speed lines.

The C/SP consists of three main sections:

Memory Central Processing Unit I/O Section

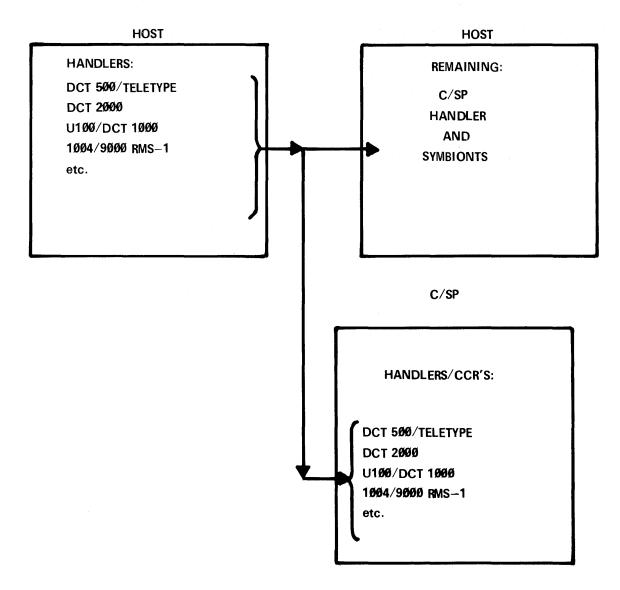

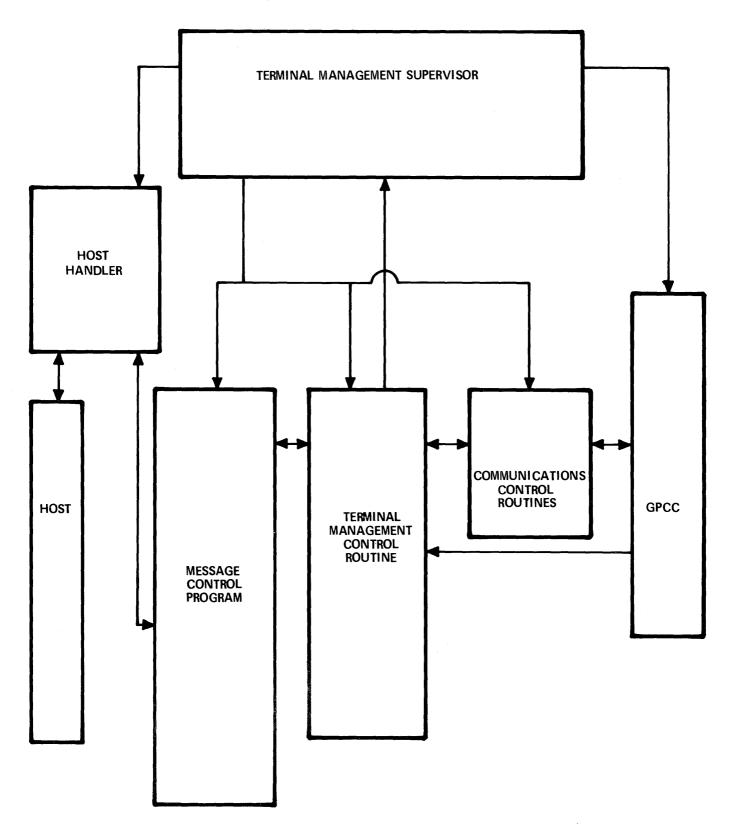

C/SP Software consists of:

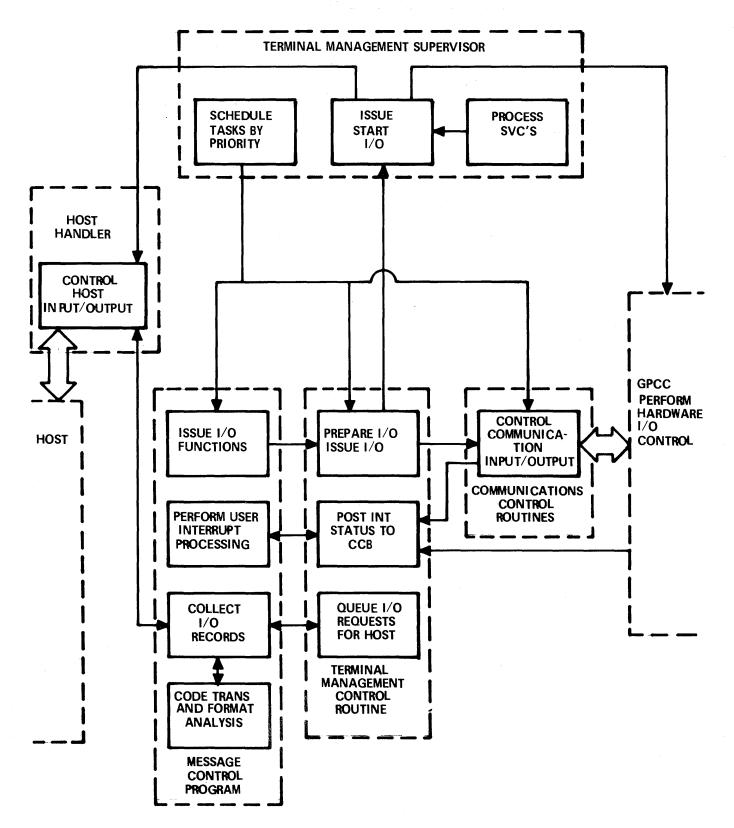

Terminal Management Supervisor (TMS) Message Control Program (MCP) Terminal Management Control Routine (TMCR) Communication Control Routines (CCR) Host Handler

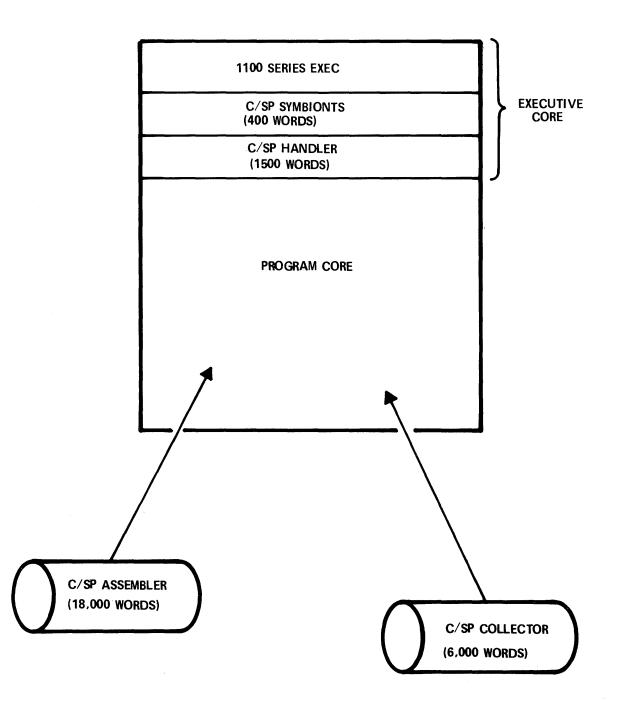

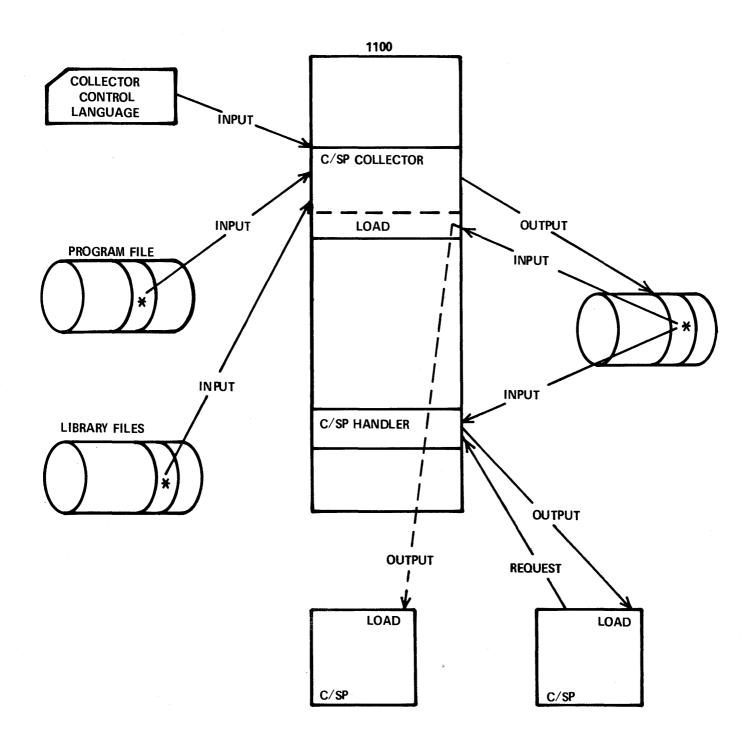

Host Software consists of:

C/SP Symbiont C/SP Handler Initial Load Routine (non-resident) Mass Storage Symbiont (non-resident) Communication Routine (non-resident) Assembler - Support Processor Collector - Support Processor Simulator - Support Processor

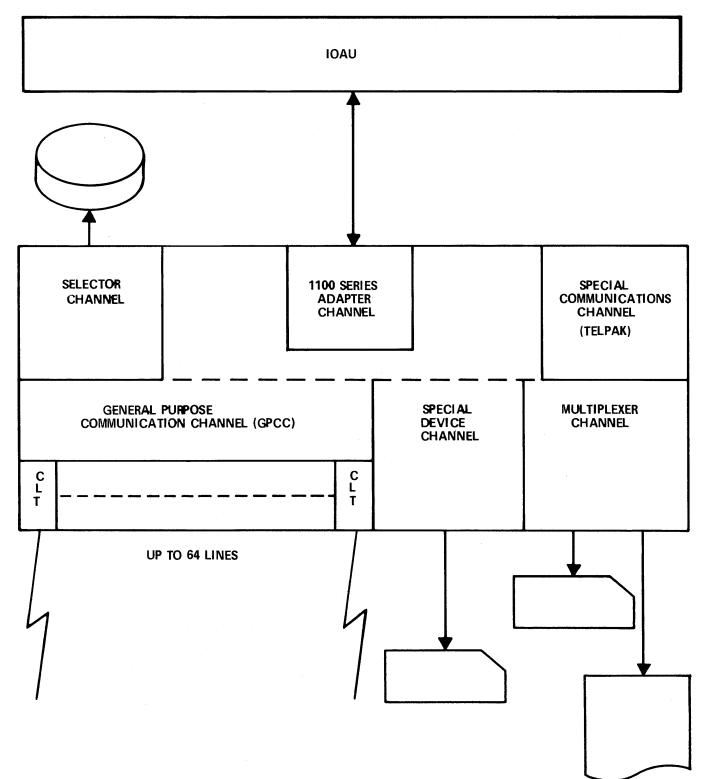

### HARDWARE BLOCK DIAGRAM

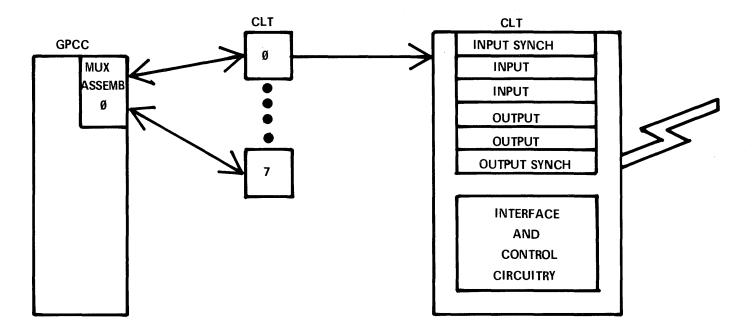

All information transfers to and from the C/SP are handled by a maximum of seven channels designated as zero through six. Channels  $\emptyset$  and 6 are reserved for the General Purpose Communications and Special Device respectfully.

<u>Channel  $\emptyset$  - GPCC</u>: The link between the main storage and the communications line terminals (CLT's). The GPCC control's 8 CLT's (half-duplex) expandable to 64 CLT's (half-duplex) in increments of 8. GPCC expansion at this time may be to 2. In the future 4 GPCC's may be allowed per C/SP.

<u>Channel 6</u> - Special Device Channel (SDC): To provide the means for local program loading and maintenance using an 80 card/minute reader. In the future, a printer and keyboard may be added.

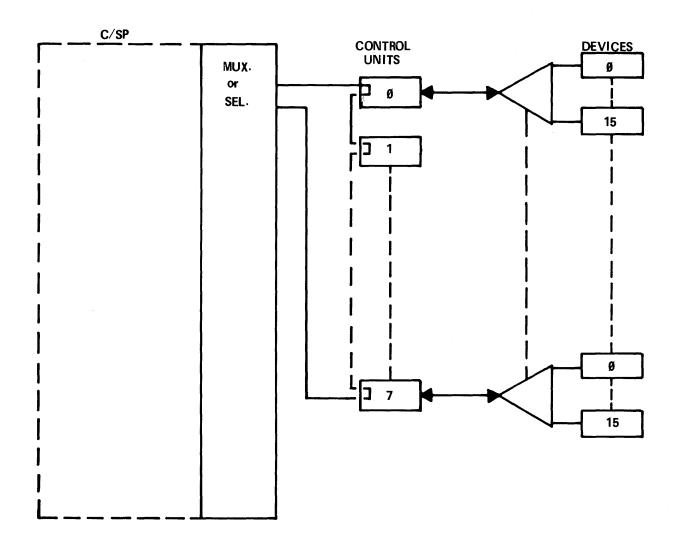

<u>Channels 1 - 5</u> - May be used for the Adapter, Multiplexer, and Selector. The Multiplexer/Selector are alike in that they can drive up to 8 control units and each control unit may control up to 16 devices (9000 peripherals, discs). The MUX/SEL are different in respect that the Selector Channel locks on to a control unit and drives the device, whereas the Multiplexer multiplexes through the control units to any device. The MUX operates in excess of 85K bytes/second. The Selector operates in excess of 625K bytes/second.

The Intercomputer Adapter (ICA) - Provides the means of communication between the C/SP and the Host Computer. The ICA operates at 300K 36-bit words per second on an Internally Specified Index (ISI) basis.

Special Purpose Communications Channel (SPCC) - Operates in 2 modes; either single duplex or full duplex.

Single duplex - Consists of 1 full duplex CLT which operates at 57K bytes per second.

Full duplex - Consists of 8 full duplex CLT's which operate at a combined maximum in excess of 300K bytes/second.

# HARDWARE BLOCK DIAGRAM

### MEMORY

Memory is divided into banks consisting of 2048 bytes per bank.

Each word consists of 4 bytes where a byte is 8 bits of data. Associated with each 8-bit byte is a 9th bit used as the parity bit for that byte. The parity bit is generated in storage when data is written and checked in storage when data is read out. The C/SP used odd parity unless specified as even under message discipline control for those terminals requiring even parity.

# **MEMORY**

| ADDRESS<br>RANGE               | HEXADECIMAL<br>ADDRESS<br>RANGE | LOGICAL<br>MEMORY<br>BANK |

|--------------------------------|---------------------------------|---------------------------|

| <b>600</b> 000 - 02047         | 0000 – 07FF                     | Ø                         |

| Ø2Ø48 — Ø4Ø95                  | 0800 - 0FFF                     | 1                         |

| Ø4Ø96 – Ø6143                  | 1000 – 17FF                     | 2                         |

| Ø6144 - Ø8191                  | 1800 – 1FFF                     | 3                         |

| Ø8192 – 1Ø239                  | 2000 – 27FF                     | 4                         |

| 10240 - 12287                  | <b>280</b> 0 – 2FFF             | 5                         |

| 12288 – 14335                  | 30000 – 37FF                    | 6                         |

| 14336 – 16383                  | <b>3800</b> – 3FFF              | 7                         |

| 16384 – 18431                  | 4000 - 47FF                     | 8                         |

| 18432 – <b>20</b> 479          | <b>4800</b> – 4FFF              | 9                         |

| 201480 - 22527                 | 5000 – 57FF                     | 10                        |

| 22528 — <b>24</b> 575          | 58ØØ – 5FFF                     | 11                        |

| 2 <b>4</b> 576 – <b>26</b> 623 | 6000 – 67FF                     | 12                        |

| 26624 – 28671                  | 6800 – 6FFF                     | 13                        |

| <b>28672</b> – <b>30</b> 719   | <b>7000</b> – 77FF              | 14                        |

| <b>30720</b> - <b>32</b> 767   | 7800 – 7FFF                     | 15                        |

| 32769 – 34815                  | 8000 – 87FF                     | 16                        |

| <b>34816</b> – <b>36863</b>    | 8800 – 8FFF                     | 17                        |

| 36864 – 38911                  | 9000 – 97FF                     | 18                        |

| <b>38912 - 40959</b>           | 9800 – 9FFF                     | 19                        |

| 41960 - 43007                  | AØØØ – A7FF                     | 20                        |

| 43008 - 45055                  | A800 – AFFF                     | 21                        |

| <b>4505</b> 6 – 47103          | <b>6000</b> – 67FF              | 22                        |

| 47104 - 49151                  | <b>B800</b> – BFFF              | 23                        |

| 49152 – 51199                  | C000 - C7FF                     | 24                        |

| 51200 - 53247                  | C800 – CFFF                     | 25                        |

| 53248 – 55295                  | D000 – D7FF                     | 26                        |

| 55296 – 57343                  | D800 – DFFF                     | 27                        |

| 57344 – 59391                  | <b>E000</b> – E7FF              | 28                        |

| 59392 – 61439                  | E800 – EFFF                     | 29                        |

| 61440 - 63487                  | F <b>ØØØ – F7</b> FF            | 30                        |

| 63488 - 65535                  | F <b>800</b> – FFFF             | 31                        |

2K = 1 BANK64 BANKS MAX.

### FIXED MEMORY

The low order memory locations are used by the C/SP in controlling the initiation of I/O commands, interrupt execution, and Internal Timer operation.

The area which is reserved for future C/SP expansion is used for four more CIW Lists when more than one GPCC is utilized in the C/SP System.

Address 68,6 and 69,6 are for the Interrupt Level List indicating a CIW was tabled by the GPCC. The foremost significant bits of address 69,6 are set each time the GPCC tables an interrupt and each bit correspond to the list which was used. If more than one GPCC in the system, the same four bits are used.

Pending Status - Allows the software to pick up status information without requiring the acceptance of an interrupt.

1/0 NEW **PSW** Α 1/0 B NEW **PSW** INTERVAL TIMER NEW **PSW** 1**C** SUPERVISOR CALL NEW **PSW** 2Ø PROGRAM/MACHINE CHECK NEW PSW INTERVAL 28 TIMER 2C CHANNEL ADDRESS WORD 3Ø COMMUNICATION INTERRUPT WORD LIST CONTROL ø INTERRUPT WORD LIST CONTROL 1 COMMUNICATION COMMUNICATION INTERRUPT WORD LIST CONTROL 2 INTERRUPT WORD LIST CONTROL 3 COMMUNICATION 1/0 CODE 4Ø **I/O** A **STATUS** Α INTERRUPT 1/0 RETURN **PSW** Α I/0 **STATUS** В INTERRUPT CODE **I/O** В RETURN 1/0 **PSW** В **INTERVAL** TIMER INTER. CODE **5**Ø **INTERVAL** TIMER **STATUS INTERVAL** TIMER RETURN **PSW** SUPERVISOR CALL **STATUS** SUPERVISOR CALL INTER. CODE **SUPERVISOR** CALL RETURN **PSW** P/M INTERRUPT CODE 6Ø PROGRAM/MACHINE CHECK STATUS CHECK **PROGRAM/MACHINE** CHECK RETURN **PSW**

FIXED MEMORY

Ø

4

8 С

1Ø 14

18

24

6C

RESERVED FOR FUTURE C/SP EXPANSION

INTERRUPT LEVEL LIST PENDING STATUS

UNASSIGNED MAY BE USED AS NORMAL STORAGE

### WORD AND INSTRUCTION FORMATS

The C/SP memory bytes are assembled into 4-byte, 32-bit words. Some instructions and operations utilize the 16-bit half-word.

The C/SP instructions are made up of four formats: RR, RX, RS, SI.

<u>RR (register to register)</u> - The RR format contains an Operation Code and two register designators - R1 and R2. R1 and R2 contain values of 0-15 decimal and point at 16 registers of 32-bit length. (R1 contains Operand 1 and R2 contains Operand 2).

<u>RX (register to indexed storage)</u> - The RX format contains the OP Code, R1, X2, B2 and D2. The X2 designator points at an INDEX value in the registers. B2 points at a register containing a BASE value. D2 contains a twelve-bit DISPLACEMENT value. Operand 2 is referenced via ((X2)+(B2)) + D2 or the contents of the X2-register plus the contents of the B2-register plus the value in D2.

<u>RS (register to storage)</u> - The RS format uses R3 to point at the register containing a third operand (if used).

<u>SI (storage and immediate operand)</u> - The SI format provides an immediate operand (I2 contents) and an operand address - (B1) + D1.

Note: The designator subscript identifies the associated operand. B1 is associated with Operand 1.

# WORD AND INSTRUCTION FORMATS

|   | HALFW  | ORD 1  | ·     | l      | HALFWORD | 2      |    |

|---|--------|--------|-------|--------|----------|--------|----|

|   | BYTE 1 | BYTE 2 |       | BYTE 3 |          | BYTE 4 |    |

| Ø | 7      | 8      | 15 16 |        | 23 24    |        | 31 |

WORD FORMAT

INSTRUCTION FORMAT

RR FORMAT

| OP CODE |     | R1 X | 2 B2  | D2     | 2  |

|---------|-----|------|-------|--------|----|

|         |     |      |       |        |    |

|         |     |      |       |        |    |

| Ø       | 7 8 |      | 15 16 | -19 20 | 31 |

RX FORMAT

| OP | CODE | R1   | R3    | B2       | D2    |

|----|------|------|-------|----------|-------|

|    |      |      |       |          |       |

|    |      |      |       |          |       |

| Ø  | 7    | 8 11 | 12 15 | 16 —— 19 | 20 31 |

RS FORMAT

| OP CODE | 12   | B1 | D1    |

|---------|------|----|-------|

|         |      | 4  |       |

|         |      |    |       |

| Ø 7     | 8 15 | 16 | 20 31 |

SI FORMAT

I-8

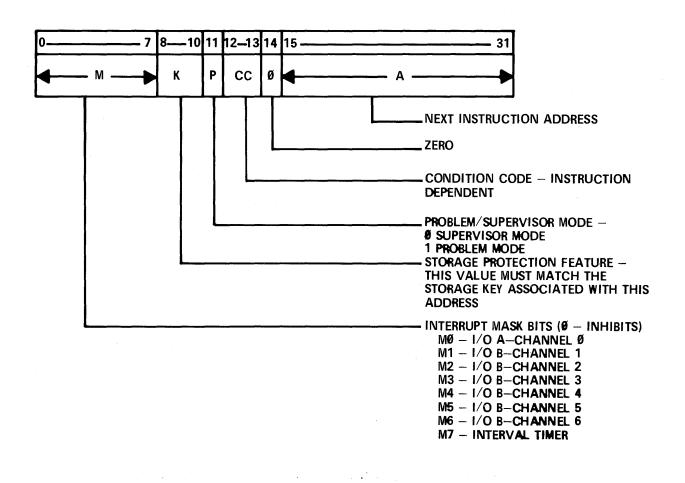

### PROGRAM STATUS WORD

PSW - Contains the information required for execution. The PSW is always zero upon initialization.

3 classes - current (Prog. in control) - becomes <u>return</u> upon interrupt - <u>new</u> is fetched corresponding to interrupt type

Upon interrupt the PSW for the interrupted program is stored by type of interrupt in a certain location in fixed memory and a new PSW is placed in the PSR.

Mask bits (M) - when set to zero's - inhibits all interrupts. If set to 1 - allows the interrupt. I/O A Channel Ø. Channel Ø (GPCC) interrupts are tabled. I/O B Channels 1-6. Interrupts are stacked until allowed, then requested. Last interrupt (7) for the interval timer.

$P - \emptyset$  - supervisor mode (allows execution of the priviledged instructions).

1 - problem mode (or user mode)

CC - condition codes: (vary with the instruction, some use only 2 conditions)

ØØ - Equal

Ø1 - Less than

- $1\emptyset$  Greater than

- 11 Overflow

K - storage protect

- $\emptyset$  Exec can reference anything no matter what the program key.

- 1 Problem program

- 2-7 Values for the user

Address = 18 bits

Upper 6 bits point to one of the hardware registers associated with each 2048 byte bank. If the value in that register is equal to the value of the K-field in PSW, reference to the block of storage is allowed. Otherwise an error occurs.

**I-9**

PSW

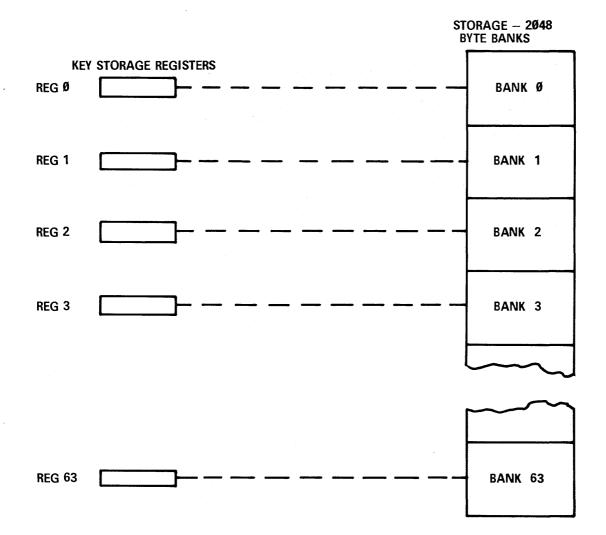

# STORAGE PROTECT

Storage is divided in 2048 byte blocks. Associated with each block is a set of hardware registers called key storage registers. These registers provide the basic protection for storage capacities up to 65K. Each register holds a 3-bit value for a maximum of 8 different storage keys.

When access to storage is initiated by the processor or I/0, the six most significant bits of the storage byte address select a location in the Key Memory which corresponds to the block of storage that is addressed. The Storage Key in the selected Key Memory location is compared for equality with the PSW key or in the case of I/0, with the I/0 Protect Key. If the result is either that the two three-bit keys are equal or that the PSW Key (Protect Key if I/0) is binary zero (000), a match condition exists and access to storage is granted.

Otherwise, the processor signals the storage to abort and not execute the write or read cycle and a storage protection error is set which generates a Program/Machine Check class interrupt request. The Program Machine Check interrupt request is generated <u>only</u> if the storage protection error occurs on a storage access initiated by the processor. The action taken by the C/SP when a storage protection error occurs on an access initiated by an I/O Channel is described in the individual I/O channels that use storage protection.

Note that a PSW Key in the current PSW (or in the case of I/O, an I/O Protect Key) of binary zero (000) grants access to any storage block.

# **STORAGE PROTECT**

I-12

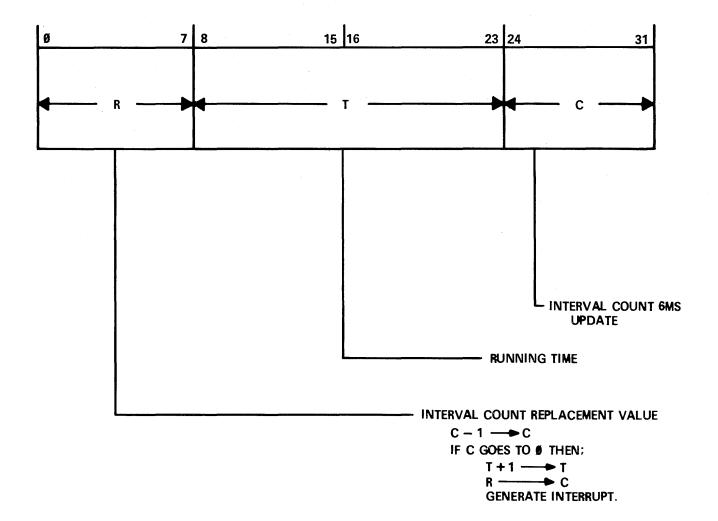

### INTERVAL TIMER

The Interval Timer is a feature in the processor which provides interval timing and time of day information. The Interval Timer can request service only at the end of a processor instruction execution prior to staticizing the next instruction. The processor is locked out during the entire interval timer service sequence. (I/O service sequences may be interlaced with timer in a normal manner as established by the storage priority). The interval timer requests service every 6 milliseconds. When a request for service is granted, the low order halfword of the Interval Timer is read out of storage (if C does not go to zero). If C goes to zero, the upper half is also readout from storage and the T-field is incremented by 1. The R-field transferred into the C-field (for the new interval count), the interval timer class interrupt request is generated, the updated ITW is transferred back to storage and the service sequence ends.

The controlling program sets the C & R-field values, thus having full flexibility of controlling the interval of interrupt request and incrementation of the T-field. If the C-field is zero and the R-field is zero, the timer counting and generation of interrupt request, an IT request which is pending when next service request is generated has no effect on the service sequence with the exception, if the C-field is reduced to zero the pending interrupt is lost, (i.e., the request is still present but the timer holds only one interrupt request).

If the program desires access to the entire ITW, it must fetch the full word in one instruction, so as not to permit the timer to execute a service sequence and possible modify the ITW before the other halfword is fetched.

Bit 7 (M7) of the PSW when set to 1 permits interruption from the IT. If zero the timer cannot interrupt. Service sequences continue normally, but the interrupt request, when generated, remains pending. If the interval timer disable switch on the processor maintenance panel is in the on position, all timer service sequences are inhibited.

Timer service sequences are also inhibited:

- 1. When processor is in the one cycle mode.

- 2. When processor is in the one instruction mode.

- \*3. When processor is in the initial load mode.

- \*4. When processor is stopped because of HPR instruction.

- \*5. When processor is stopped because of detection of a tract stop.

- 6. When non-recoverable error has occurred.

- \*7. When processor is stopped due to a recoverable error detection and the stop on error switch on the maintenance panel is in 'on' position.

- \*8. When processor is stopped and is in the cleared state.

- \*-. These cases the Interval Timer service can resume at the end of the first instruction execution following the depression of the run switch.

The timer is assigned to the Interval Timer class of interrupt. When an interrupt request is accepted by the processor a status half word and an interrupt code half word are stored in fixed memory locations.

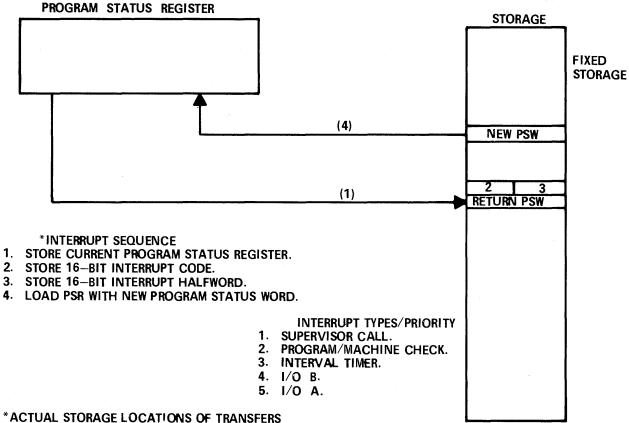

### C/SP INTERRUPT SEQUENCE

### Interrupts

Automatic means to alert the C/SP processor to an exceptional or unexpected condition (end of I/O operation, program errors, machine errors, etc.) thus directing the processor to the appropriate program routine for handling. The system provides for interrupting any task in order to take on a task of higher priority.

Interrupt Sequence: 1. Begins by transferring the current PSW to fixed location in storage ('Return' PSW 2-3. Then the status half word and interrupt code half word is transferred to the assigned location. 4. 'New' PSW is fetched from the fixed location. 'New' becomes 'current' PSW and after processing, the processor can return to the interrupted program (load 'return' PSW) via the LPSW instruction. In certain cases of simultaneously presented interrupts, it is possible to execute more than one interrupt sequence before instruction processing is resumed.

<u>Interrupt Class/Priority</u>: There are 5 classes of interrupts; Supervisor Call, Program-Machine check (PMC), Interval Timer I/O B, I/O A. Within the classes may be several specific sources of interrupt requests.

I/O A, I/O B, and interval timer interrupt requests are controlled by the system mask bits in the 'current' PSW. If bits are set to zero the corresponding channel is not permitted to interrupt. No mask bit control exists over the supervisor call class and all interrupt requests are accepted (in this class). PMC interrupt requests are always accepted unless the processor is executing a PMC interrupt subroutine.

<u>Interrupt Priority</u>: It is possible to execute more than one interrupt sequence between instruction executions. The system mask bits (PSW) become effective immediately and therefore control subsequent interrupt sequences.

The order of executing the contiguous interrupt sequences varies and is a function of the pending instruction requests and mask bits.

The interrupt sequence selected is determined by the following priority:

1. PMC (invalid address strg. protection, or parity, 2. Interval Timing, 3. I/O B, 4. I/O A, 5. PMC (power failure, invalid operation, etc.)

Supervisor Call is not included as the storing and fetching of PSW's is done in the execution phase of the instruction and should not be thought of as an interrupt sequence in the context described.

This does not determine the order, only indicates which interval sequence is selected when simultaneous interrupt requests are made. Example: if I/O A and I/O B interrupt request are presented simultaneously I/O B is processed first.

The final contents of PSW determine which interrrupt subroutine is entered, so the order of executing these subroutines is reversed from the order of executing the interrupt Sequence.

See Appendix A for more information.

# INTERRUPT SEQUENCE

DEPENDENT ON INTERRUPT TYPES.

### INTERRUPT CLASS AND CODE

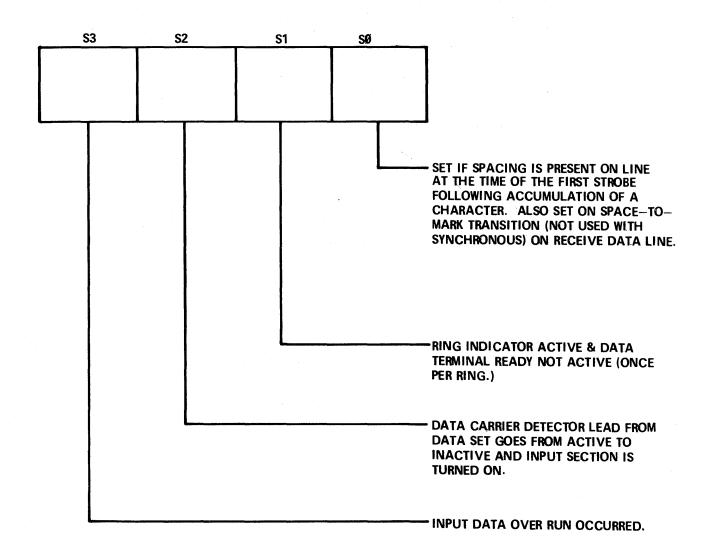

During the interrupt sequence the status halfword and interrupt code halfword are transferred to the assigned locations in fixed memory.

I/O A class interrupt is assigned to channel zero. Channel O is reserved for the GPCC and the bits identifying the channel ID, channel #, device address are all set to O by the hardware as the channel ID and # equal zero and the device address is contained in the CIW.

I/O B class interrupts are assigned to channels 1-6. Bit 16 is set to 0, bits 17-19 are the channel identification code, bit 20 is set to 0, bits 21-23 are the channel number (1-6), and bits 24-31 are the device address.

The Interval Timer interrupt code halfword is always set to 0 by the hardware (timer).

PMC has a value for each type of interrupt within this class.

Supervisor Call- the 'R' bits are the bits from the SVC fields R1 & R2.

# **INTERRUPT CODE HALFWORD**

INTERRUPT CLASS

# INTERRUPT CODE

1/0 A

CHANNEL Ø

BITS 16 \_\_\_\_\_ ----- 31

## CHANNEL:

|                                 | ONAIGUEL.                                                         |   |

|---------------------------------|-------------------------------------------------------------------|---|

| <u>I/O в</u>                    | I. D. NUMBER DEVICE ADDRESS                                       | 5 |

| CHANNEL 0                       | ØCCCØØØØDDDDDDD                                                   | 5 |

| CHANNEL 1                       | ØCCCØØØ1DDDDDD                                                    | ) |

| CHANNEL 2                       | ØCCCØØ1ØDDDDDD                                                    |   |

| CHANNEL 3                       | ØCCCØØ11DDDDDDD                                                   | - |

| CHANNEL 4                       | ØCCCØ1ØØDDDDDDD                                                   | - |

| CHANNEL 5                       |                                                                   |   |

| CHANNEL 6                       | Ø C C C Ø 1 1 Ø D D D D D D D C                                   | ) |

| INTERVAL TIMER                  | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                             | ð |

| PROGRAM/MACHINE CHECK (PMC)     |                                                                   |   |

| POWER FAILURE                   |                                                                   | 1 |

| PARITY                          | 00000000000000000000000000000000000000                            | Ø |

| INVALID OPERATION               |                                                                   | Ø |

| PRIVILEGED OPERATION            | 00000000000000000000000000000000000000                            | • |

| STORAGE PROTECTION              |                                                                   | Ø |

| INVALID ADDRESS                 | <b>0</b> 0 0 0 0 0 0 0 0 0 0 0 0 1 1                              | 1 |

| FORCE PMC SWITCH                |                                                                   | Ø |

| MONITOR SWITCH                  | <b>5 \$</b> \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ \$ | Ø |

| SUPERVISOR CALL                 | 0000000RRRRRRRR                                                   | R |

| C - CHANNEL IDENTIFICATION CODE |                                                                   |   |

- C CHANNEL IDENTIFICATION CODE

- 661 SDC

- Ø10 ICA

- 100 SELECTOR 101 MULTIPLEXER

I-18

# INTERRUPT CLASS AND STATUS

The status halfword is stored during the interrupt sequence. I/O A class interrupt- If bit 15 is set, indicates an error occurred on attempt to store a CIW and no CIW was stored.

I/O B class interrupt- The status is covered during the discussion of the individual channels.

Interval Timer status halfword- If bit 15 is set, indicates a parity error was detected when the Interval Timer read out one of the halfwords of the Interval Timer Word.

Program/Machine check and the Supervisor Call interrupts do not generate any status and these status halfwords are set to 0.

# **STATUS HALFWORD**

| INTERRUPT CLASS           | STATUS HALFWORD                        |

|---------------------------|----------------------------------------|

| BITS                      | Ø 15                                   |

| I/O A                     | 00000000000000000000000000000000000000 |

| I/O B                     | REFER TO INDIVIDUAL I/O CHANNEL        |

| INTERVAL TIMER            | 99999999999999999998                   |

| PROGRAM/MACHINE<br>CHECK  | ଷ୍ୟ ଷ୍ୟ ଷ୍ୟ ଷ୍ୟ ଷ୍ୟ <b>ସଂକ୍ଷାର</b>     |

| SUPERVISOR CALL           | 0000000000000000000                    |

| * E 1 ERROR OCCURRED ON A | TTEMPT TO READ OUT CIW CONTROL LIST    |

E2 -- ERROR OCCURRED ON ATTEMPT TO READ OUT INTERVAL TIMER

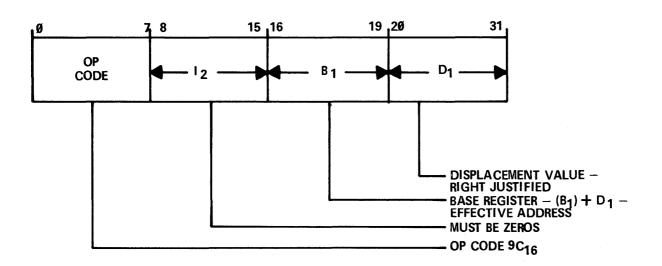

All input/output operations are initiated by this instruction. The effect of the SIO varies and is a function of the channel to which it is directed.

The operation code is 9C hexadecimal. Bits 8-15 are not used and are set to zero.

$B_1$  - The number of the general register which holds the base address for operand 1.

$D_1$  - The displacement value for the base address of Operand 1.

The addition of the contents of  $B_1$  and the value of  $D_1$  fields form the effective address which is the channel number and device address to start the I/O sequence.

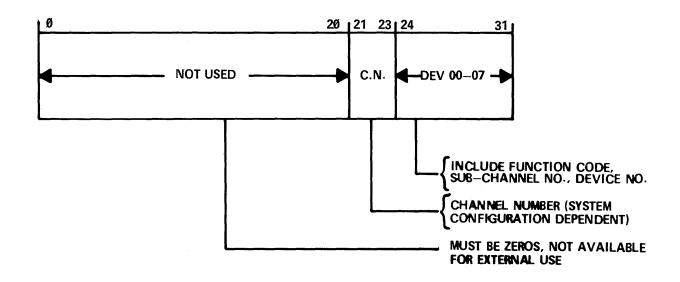

# **START I/O INSTRUCTION**

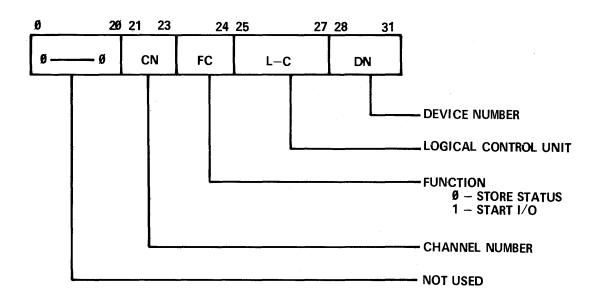

Bits 0-20 are set to zero and are not available for external use.

Bits 21-23 contain the channel number depending on the configuration.

Bits 24-31 contain the function to be performed, the sub-channel or control unit and the device number (8-bits referred to as DEV 00-07).

# DEVICE ADDRESS FORMED BY (B1) + D1

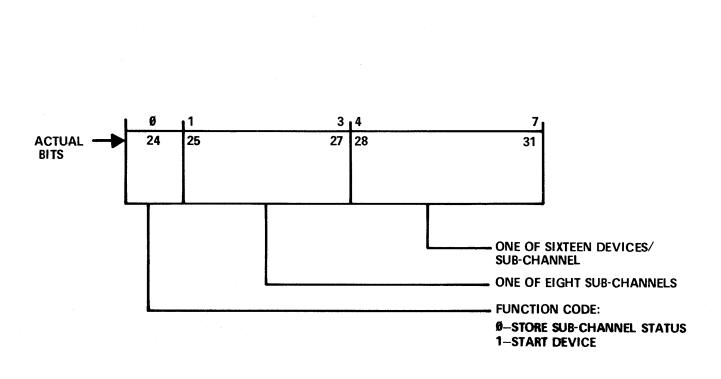

The 8-bits of DEV  $\not 0 \not 0$ - $\not 0 7$  are indicated as:

- bit  $\emptyset$  (24) function code: If set, start the device; If not set, store the sub-channel status.

- bit 1-3 (25-27) Indicates which of the 8 sub-channels to perform the function on.

- bit 4-7 (28-31) Indicates which one of the 16 devices on the subchannel to perform the function on.

**DEV 00-07 FORM**

I-26

I/O FLOW

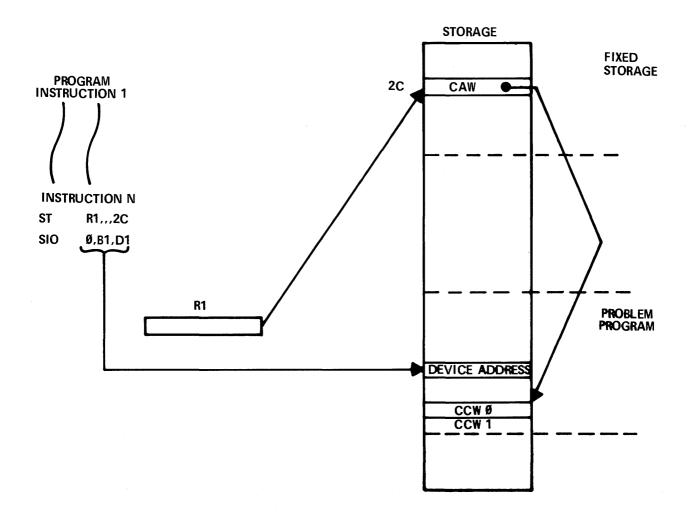

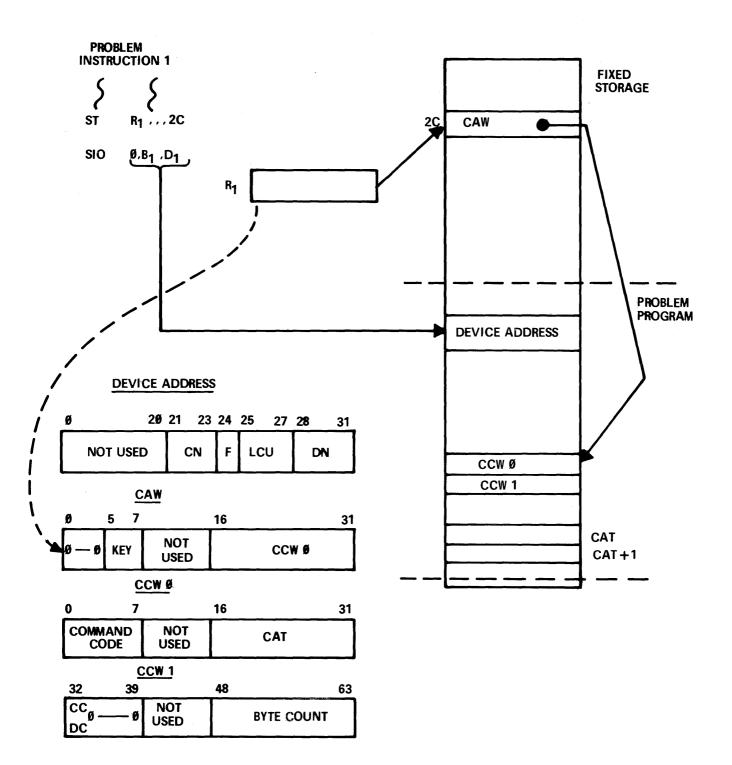

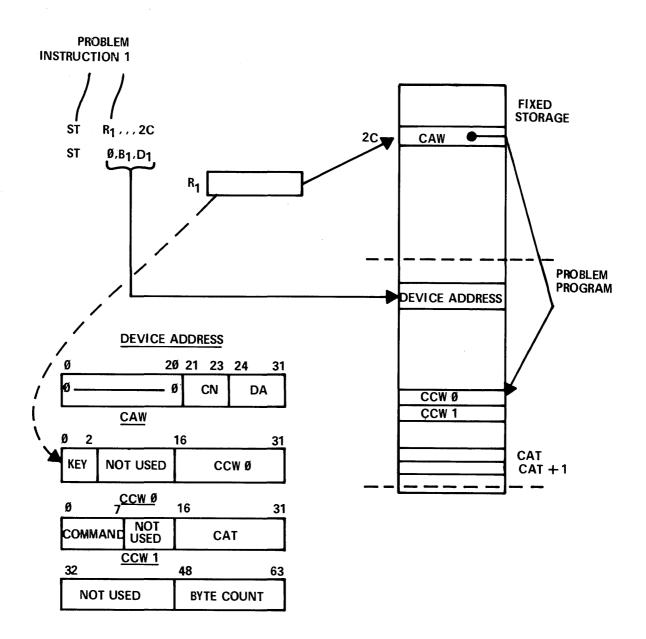

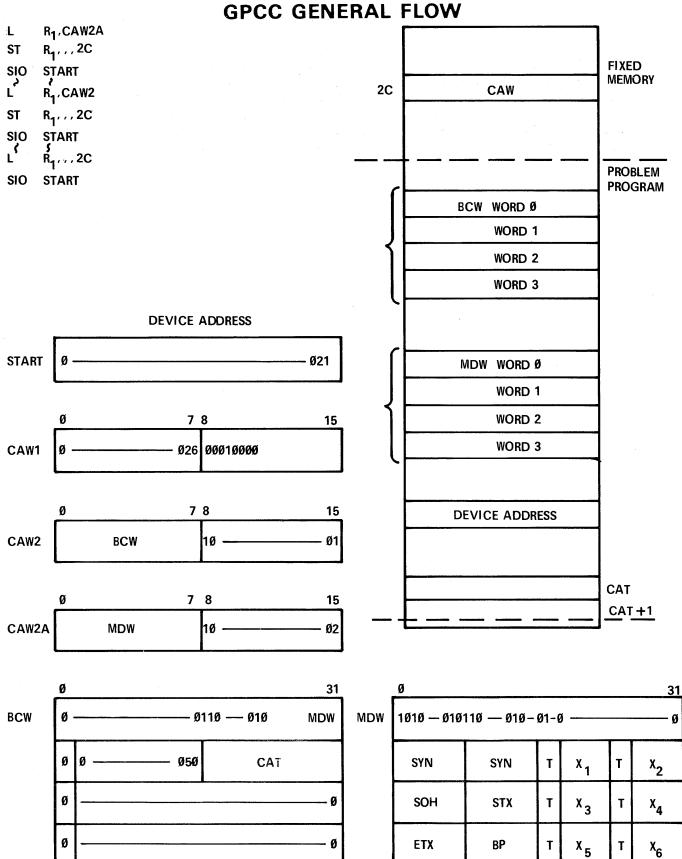

The overall I/O Flow involved in using the SIO instruction is as follows:

The program must first store a Channel Address Word (CAW) in fixed memory. The Channel Address Word, in general, contains a command to an input/output device or an address of such a command. In this case, the CAW indicates an address of a Channel Command Word (CCW-2 words). The CCW indicate the operation to be performed, the address of first byte of data to be transferred and the byte count.

- 1. Store the CAW in fixed memory.

- 2. Issue SIO instruction.

- a. Before the channel responds with the condition code, it fetches the CAW and holds it in its hardware as required by the operation to be performed.

- 3. The channel gets the address of the Channel Command Word (CCW) from the CAW and the process is initiated.

- NOTE: The operand field of the SIO instruction pointing to the device address does not mean the device address is in memory. This was done to show that the contents of B<sub>1</sub> register added to the value D<sub>1</sub> forms the device address.

### Appendix A

A flip-flop is set in an interrupt sequence provided the 'current' PSW is loaded from PMC 'new' PSW. All subsequent PMC requests are not accepted. The flip-flop is reset by executing a LPSW instruction (or system clear switch on processor maintenance panel). A non-recoverable error situation then exists and the processor is stopped if any of the following occur: 1. PMC class interrupt request is generated, 2. Parity error when PSW is read from storage during an interrupt Sequence (including during the execution of a supervisor call instruction - SVC), 3. Parity error when PSW is read from storage during execution of LPSW instruction, 4. Recovery of program time out check Retriggerable Delay Flop (RDF) circuit. \*

Processor Action: 1. Abnormal light on maintenance panel, 2. signal to generate PMC interrupt request, 3. turn off timing pulse clock, 4. generate channel clear signal to all attached channels.

Cause of the non-recoverable error may be determined by examining the indicators on maintenance panel and then reset by depressing system clear switch.

<u>Interrupt Timing</u>: The interrupt sequence takes place only at the end of an instruction execution and before a new instruction is started. The processor either waits until the end of the instruction before executing the interrupt sequence or it ends the instruction early; then it executes the interrupt sequence. If the processor waits until instruction has ended, it is then termed as 'completed'. The PSW then points to next instruction in program. If processor ends the instruction early, the instruction execution is termed 'suppressed' or 'terminated'. Suppressed - effect is as if no operation was specified (Results not stored and CC not changed).

Terminated: All, part, or none of the result will be stored and results are unpredictable. The next instruction address in 'Return' PSW points to the address of the instruction which was suppressed or terminated. An exception to this is the detection of a storage protection or invalid address error when fetching the first half word of an instruction to be executed following a branch instruction. Then the PSW holds the address of the branch instruction.

\* Certain processor component malfunctions may cause the processor to enter a stalled condition or a program loop condition which would not result in a detected error and generation of a PMC interrupt. To assist in detecting an error of this type a SIO is issued to a pseudo I/O channel (7) only for this PMC function. The SIO issued to channel 7 triggers A 1.0-1.5 second retriggerable delay flop. A properly running program contains enough SIO instructions to insure the RDF never recovers.

I-30

NOTES

1

# SECTION II SPECIAL DEVICE CHANNEL

## SECTION IT INDEX - SPECIAL DEVICE CHANNEL

- II. -2 SPECIAL DEVICE CHANNEL (SDC)

- -4 SDC GENERAL I/O FLOW

- -6 CONDITION CODE SETTINGS

- -8 SDC STATUS HALFWORD

- -10 INITIALIZE CARD READER

Special Device Channel (SDC)

The SDC provides the means for local program loading and maintenance using a card reader (Type 0708-27/28) which is 80 column 80 cards per minute reader.

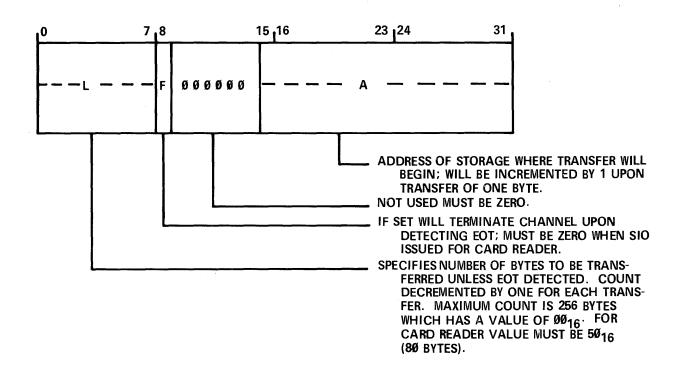

Operation of the card reader is initiated by the C/SP program issuing a Start I/O (SIO) instruction. The SIO specifies a channel number and a device address. The SDC channel number is always 6 and the device address for the card reader is  $02_{16}$ . Before the SIO is issued, a CAW must be scored in fixed memory location  $2C_{16}$ .

CAW - L - number of bytes to be transferred. Maximum if 256 bytes.

For the card reader the number is always 80 bytes.

A SIO is issued for each card to be read.

F if set, indicates termination upon detection of EOT.

Bits 9-14 set to zero by the controlling program.

A address to be used in the storage of data and is incremented as each byte is transferred.

II-2

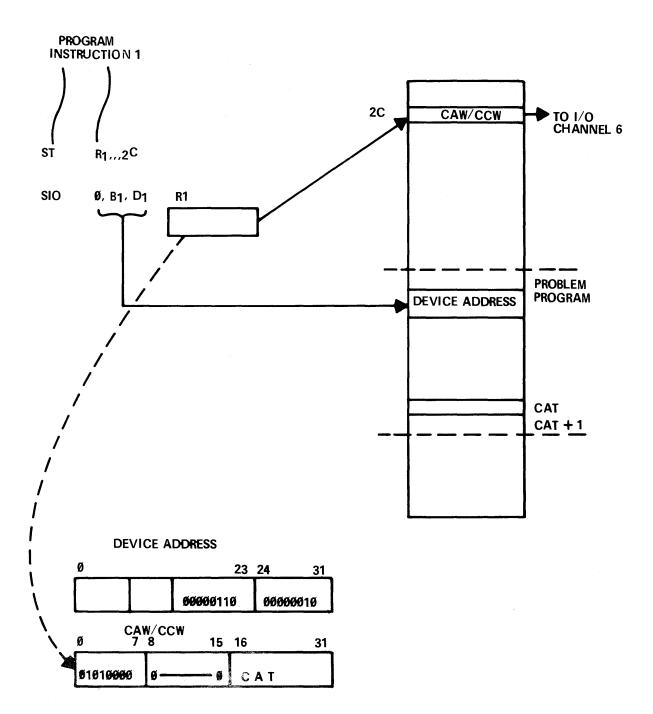

### SDC General I/O Flow

The controlling program stores the CAW in fixed memory location  $2C_{16}$ . Since the card reader performs only one function (read one card) there are no external functions to be decided in the SDC, and there is no need to reference a Channel Command Word (CCW) as the CAW specifies the starting storage address, byte count and control bit for EOT.

- Store the CAW in 20,16

Issue SIO instruction:

- 3. The SDC fetches the CAW and holds the contents as required by the I/Ooperation to be performed (during the SIO time - before the SDC returns a condition code to C/SP).

- 4. The channel then initiates and controls the operation of the I/Odevice and the transfer of data between the device and storage.

Condition Code Settings

SIO with a Device Address of:

00 - Keyboard

01 - Incremental Printer

02 - Card Reader

Device address of  $80_{16}$  indicates keyboard lockout and the SDC does not fetch the CAW.

Device address of 40  $_{16}$  indicates a test I/O function and the channel does not fetch the CAW.

I/O Pending Status - location 6C and 6D of fixed memory allow software to pick up status information without requiring the acceptance of an interrupt. Some channels store status in these location during SIO time when function of SIO is TIO. Some will store status when function is not TIO, such as end of operation or when pending status is the only thing preventing the channel or attached control unit from accepting a new command.

GPCC does not use pending status.

## CONDITION CODE SETTINGS SDC

| SIO | D.A. | ØØ, | Ø1, Ø2, |

|-----|------|-----|---------|

|     |      | -   |         |

| CC = ØØ           | SIO EXECUTED                      |

|-------------------|-----------------------------------|

| $CC = \emptyset1$ | PARITY ERROR ON CAW FETCH         |

| CC = 10           | BUSY EXECUTING PREVIOUS OPERATION |

| CC = 11           | SDC OF LINE                       |

SIO D.A. 80

| CC = 999/11 | KEYBOARD NOT BUSY                                               |

|-------------|-----------------------------------------------------------------|

| CC = Ø1     | NOT USED                                                        |

| CC = 1Ø     | BUSY; WILL BE LOCKED OUT AFTER<br>PREVIOUS OPERATION TERMINATES |

SIO D.A. 40

| CC = 00/11 | NOT BUSY               |

|------------|------------------------|

| CC = Ø1    | HOLDING PENDING STATUS |

| CC = 10    | BUSY                   |

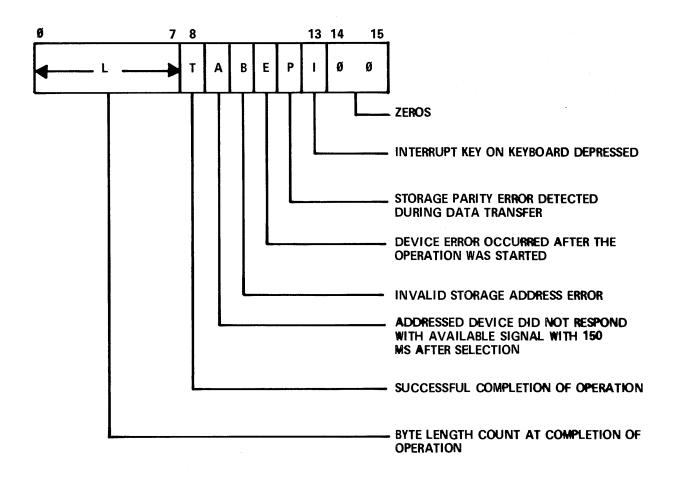

#### SDC Status Halfword

The SDC generates an interrupt request of the I/O B class upon completion of a data transfer error condition, or in response to the interrupt key on keyboard (if keyboard is attached). When the C/SP grants the interrupt request, the SDC stores interrupt code and status in the respective half word location in fixed memory.

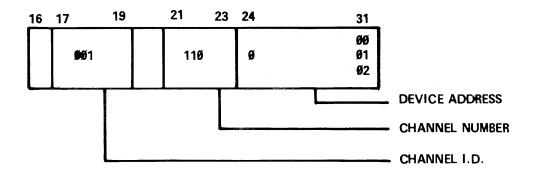

The interrupt code halfword indicates the channel identification in bits 17-19 and is set to 001 by the SDC. Bits 21-23 are the channel number and set to 110 by the SDC. Bits 24-31 is the device address ( $\emptyset$  - keyboard,  $\emptyset$ 1 - printer,  $\emptyset$ 2 - card reader).

## **STATUS HALFWORD**

## **INTERRUPT CODE HALFWORD**

II-8

INITIALIZE CARD READER (SDC)

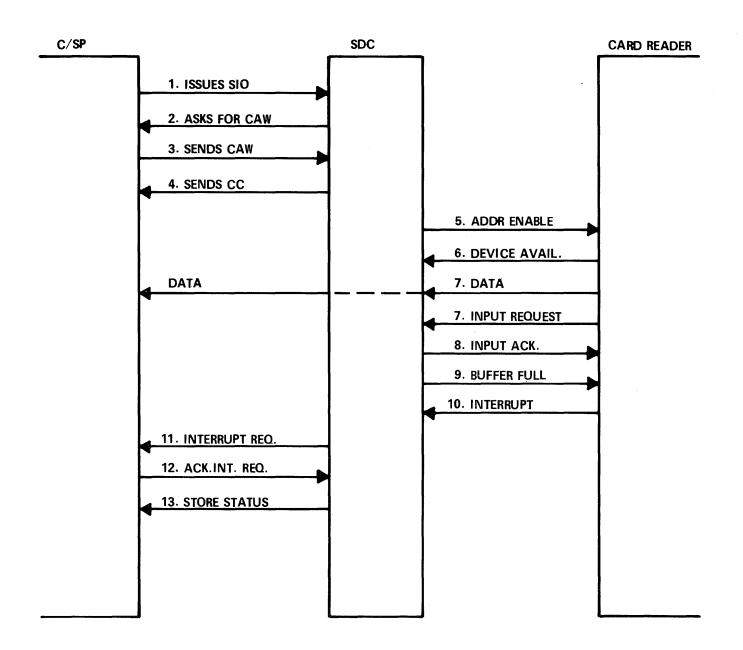

$C/SP \rightarrow SDC$  - The CAW has been stored in fixed memory.

1. C/SP issues the SIO instruction.

- 2-3. During the SIO time the SDC asks for and receives from the C/SP the Channel Address Word (CAW). Assume the channel is not busy.

- 4. The SDC responds with the condition code of  $\emptyset\emptyset$ . SIO was executed.

- SDC -> Card Reader control unit

- 5. SDC generates an Address Enable Request.

- 6. CR control unit responds with Device Available.

- 7. CR control unit puts the data on the data lines and generates an Input Request at the same time.

- 8. SDC responds with an Input Acknowledge when the data has been stored.

- 9. When the byte count goes to zero (or error condition detected) SDC generates a Buffer Full signal.

- 10. CR control unit responds with an Interrupt signal which signals the SDC to generate an interrupt request to the C/SP.

- 11. SDC generates an Interrupt Request to C/SP.

- 12. C/SP generates an Acknowledge of the Interrupt Request indicating the C/SP is able to process the interrupt.

- 13. The SDC stores the status halfword and interrupt code halfword in the fixed memory locations for I/O B class of interrupt.

**INITIALIZE SDC (CARD READER)**

# SECTION III MULTIPLEXER/SELECTOR CHANNEL

# SECTION III INDEX – MULTIPLEXER/SELECTOR CHANNEL

III. -2 MULTIPLEXER/SELECTOR CHANNEL (MUX/SEL)

- -4 CHANNEL ADDRESS WORD (CAW)

- -6 (B<sub>1</sub>) + D<sub>1</sub> OF START I/O INSTRUCTION

- -8 CHANNEL COMMAND WORD (CCW)

-10 CCW (WORD 1)

- -12 CONDITION CODES MUX/SEL

- -14 CHANNEL STATUS WORD (M/S) 0-31

- -16 CHANNEL STATUS WORD (M/S) 32-63

- -18 MUX/SEL GENERAL I/O FLOW

- -20 MULTIPLEXER/SELECTOR CHANNEL

- -22 MUX/SEL CONTROL LINES

- -24 MUX/SEL INITIALIZE DEVICE

#### MULTIPLEXER/SELECTOR CHANNEL (MUX/SEL

The multiplexer and selector channels may be connected up to 8 control units which may be connected up to 16 devices, operating in half duplex mode (one transfer at a time). The channel provides general purpose channel programming, including command chaining, data chaining, transfer in channel and skip commands. The channel interfaces with main storage through the control section of the C/SP.

# C/SP MULTIPLEXER/SELECTOR SELECTOR CHANNEL

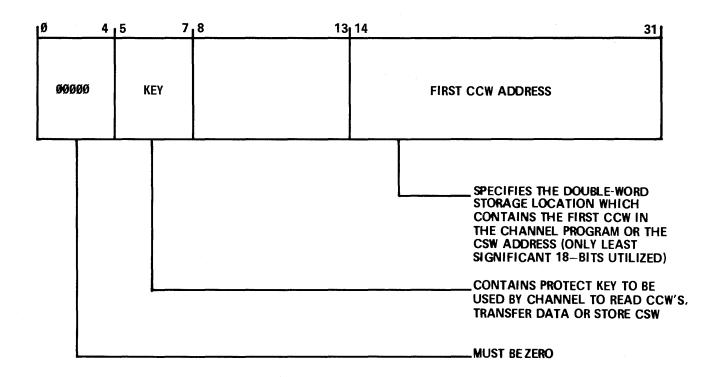

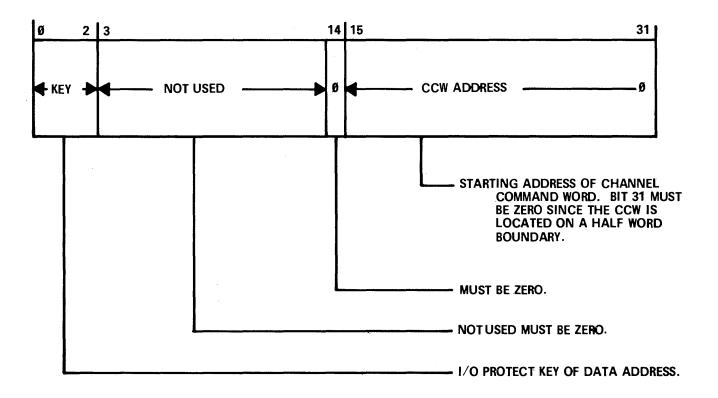

#### CHANNEL ADDRESS WORD (CAW)

The CAW must be set before issuing the SIO instruction (Address  $2C_{16}$  in C/SP fixed memory).

- bits 5-7: contain the storage I/O protection key to be used by the channel to read the Channel Command Words (CCW), transfer data, or store the Channel Status Word (CSW).

- bits 8-31: Specifies the storage location of the first Channel Command Word (CCW) if the function of the SIO instruction is to start the device. If the function is to store sub-channel status, the address of the Channel Status Word (CSW) is contained in these bit positions. Only the least significant 18 bits are utilized.

III-4

1

## CHANNEL ADDRESS WORD M/S

## $(B_1) + D_1$ OF START I/O INSTRUCTION

Initiation of an I/O operation is by the SIO instruction specifying the channel number, and the address of the device associated with the execution of the operation. The SIO instruction generates signals on the 8 bussed address lines. The condition of the channel is indicated by the CC returned to the processor on 2 bussed C/SP I/O interface lines.

The address portion of the SIO instruction:

Channel number - depends on the configuration. Function - either start the I/O operation or store status Logical Control Unit ( $\not 0-7$ ) Device Numbers - one of 16 devices per sub-channel (control unit)  $\not 0/15$ .

## (B<sub>1</sub>) + D<sub>1</sub> OF START I/O INSTRUCTION MUX/SELECTOR

SIO INSTRUCTION

| 9C Ø – – Ø | <sup>B</sup> 1 | D <sub>1</sub> |

|------------|----------------|----------------|

|------------|----------------|----------------|

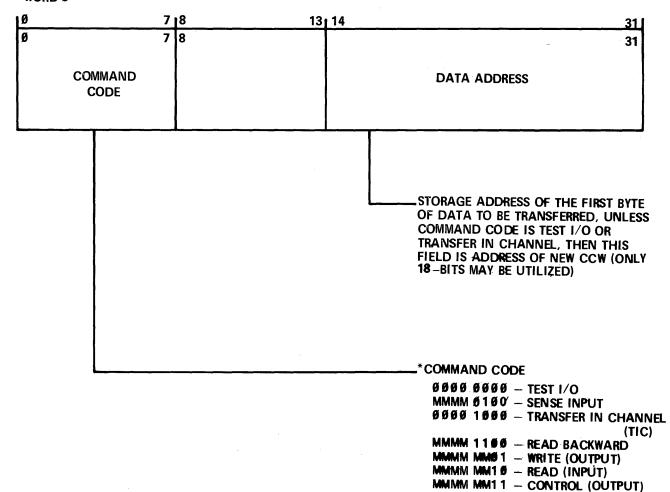

The CCW specifies the operation to be performed by the device or channel. When the specified operation is due to be executed, the CCW format is converted to that of a Hardware Channel Control Work (HCCW) and moved to internal storage location of the channel. The HCCW is modified and updated to control the operation as it progresses. There is a maximum of 8 double words (HCCW) for the multiplexer channel and 1 double word (HCCW) for the selector channel.

Bits  $\emptyset$  - 7: The command byte of the CCW (word  $\emptyset$ ), specifies the operation to be performed by the device or channel. The 'M' bit positions depend on the I/O device.

Bits 14 - 31: Indicate the storage address of the first byte of data to be transferred. If the command byte indicates a Test I/O or Transfer in Channel command, then these bit positions contain a new CCW address.

Transfer In Channel (TIC) - Provides a branching function for the channel; allowing execution of CCW's which are at non-sequential storage locations, for command and buffer loops. The CCW is ignored except for the address field which specifies the address of the next CCW. The object CCW of a TIC may not contain another TIC command.

Sense - A special case of a read, in that sense bytes are read into storage instead of data. A detailed device status is presented as 'intervention required' for a printer. The number of sense bytes varies with the device.

Control - A special case of a write; causing a signal to be sent to the device without any data being written, such as spacing the paper on a printer.

## CHANNEL COMMAND WORD M/S

WORD Ø

\*M - DEVICE DEPENDENT

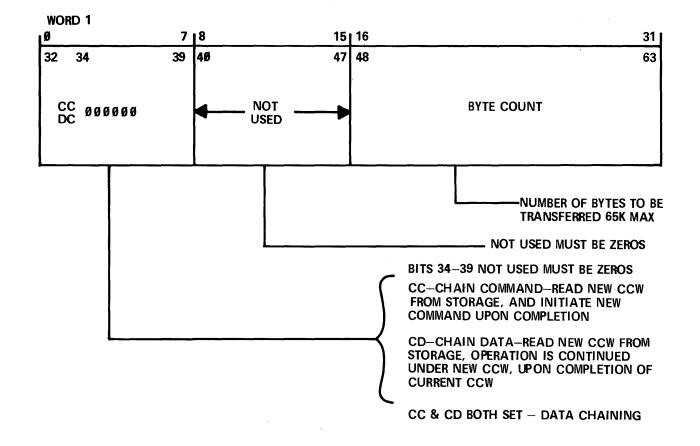

#### CCW (WORD 1)

Bit 32 - CD: Indicates to chain data. Upon transfer completion, controlled by the current CCW, a new CCW is read from storage and the operation continues under control of the new CCW. The command byte is not interpreted except for a Transfer In Channel command.

Bit 33 - CC: Indicates to chain commands. Upon completion of the operation at the device (indicated by status code containing 'device end' set), a new CCW is read from storage and the operation specified by the new command code is initiated.

If both command and data chain bits are set, data chaining occurs.

Bits 34 - 39: Not used, must be zero.

Bits 40 - 47: Not used, must be zero.

Bits 48 - 63: Specifies the number of bytes to be transferred.

Maximum count is 65K.

## CHANNEL COMMAND WORD M/S

## CONDITION CODES MUX/SEL

To initiate the Test I/O command to the multiplexer or selector channels, the SIO instruction must be issued with the start device function (bit 24 of the device address set) and the command byte of the CCW containing the Test I/O command.

## CONDITION CODES MUX/SEL

#### SIO START FUNCTION

$CC = \emptyset \emptyset$  OPERATION INITIATED

$CC = \emptyset 1$  ERROR CONDITIONAL STATUS STORED IN HCCR STATUS

#### FOR CHANNEL DEVICE AVAILABLE

#### CC = 10 BUSY CHANNEL OR SUB-CHANNEL

#### SIO STORE STATUS FUNCTION

- $CC = \emptyset\emptyset$  CHANNEL/DEVICE AVAILABLE

- CC = Ø1 STATUS PENDING INFORMATION IN CSW

- CC = 10 BUSY

- CC = 11 CHANNEL NOT AVAILABLE OR STORAGE PARITY

ERROR WHEN WRITING CSW

#### SIO TEST I/O FUNCTION

$CC = \emptyset\emptyset$  AVAILABLE

- CC = Ø1 STATUS INFORMATION IN HCCW

- CC = 10 BUSY

- CC = 11 CHANNEL OR DEVICE NOT AVAILABLE

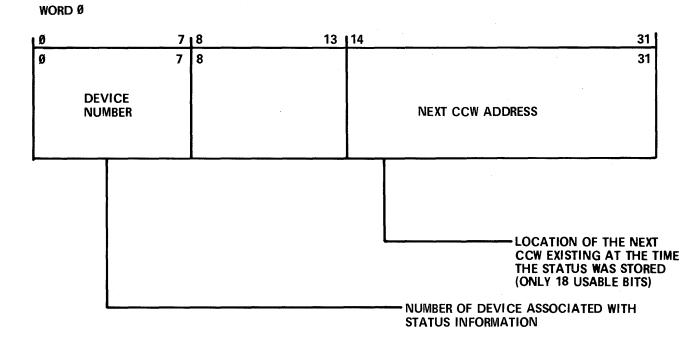

#### CHANNEL STATUS WORD (M/S)

The CSW is a double word written by the channel when the sub-channel (control unit) in the status pending mode is addressed by a store sub-channel status function of the SIO. The status word is written at the double word location specified by the address provided in the CAW.

CSW (word  $\emptyset$ ):

Bits  $\phi$  - 7: The device number associated with the status information.

Bits 14-31: The value of the next CCW address existing at the time the status information was stored.

## CHANNEL STATUS WORD M/S

•

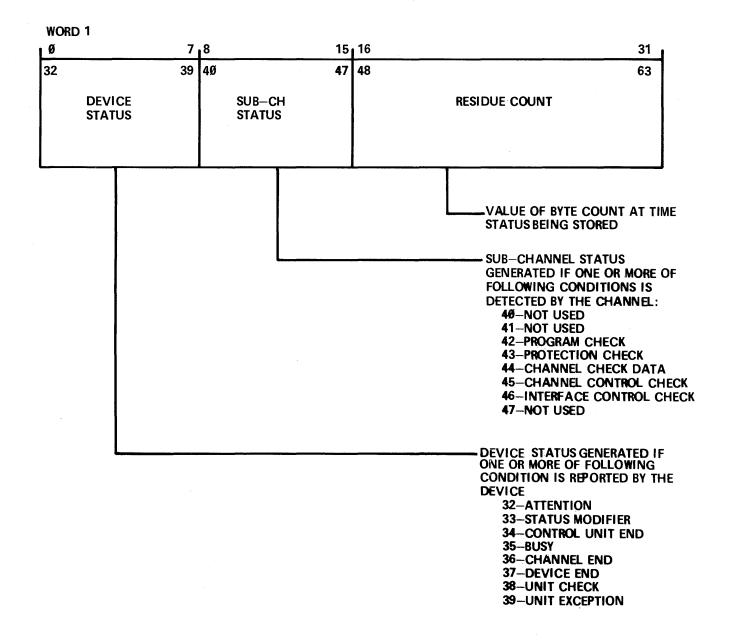

### CHANNEL STATUS WORD (M/S) - (continued)

<u>Bits 32 - 39</u>: Contain the device generated status byte.

- Bit 32 Attention: Present conditions asynchronous to I/O operations. Example: Inactive line becomes active.

- Bit 33 Status Modifier: Presented with device end. May be used to modify the channel sequence in chaining situations.

- Bit 34 Control Unit End: Set when control unit responds to interrogation with busy and status modifier set or abnormal condition detected during busy.

- Bit 35 Busy: Already executing.

- Bit 36 Channel End: End of data transfer.

- Bit 37 Device End: End of operation by an I/O device.

- Bit 38 Unit check: Program intervention is required.

- Bit 39 Unit Exception: Unusual condition, not necessarily an error has been detected.

- Bits 40 47: Contain the sub-channel generated status byte.

- Bit  $4\emptyset 41$ : Not used.

- Bit 42 Program Check: Programming errors detected.

- Bit 43 Protection Check: Attempt to read/write a protected area.

- Bit 44 Channel Check Data: Storage or I/O parity error occured during a data transfer.

- Bit 45 Channel Control Check: Storage parity error during a control word read/write.

- Bit 46 Interface Control Check: Invalid signal sequence on the I/O bus.

- Bit 47 Not used.

- <u>Bits 48 63</u>: The value of the byte count existing at the time the status information was stored.

## CHANNEL STATUS WORD M/S

#### MUX/SEL GENERAL I/O FLOW

The program sets up the CAW and CCW's. The CAW is stored in fixed memory at address  $2C_{16}$ . The contents of  $B_1$  and the value of  $D_1$  form the device address. SIO is issued with the device address and assuming the channel and device is not busy, the CAW is read from fixed memory. The MUX/SEL channel stores the CAW in its' hardware and reads out the CCW's into its' hardware (now HCCW), the address of which is in the CAW. The channel interprets the command code and the execution begins, such as the transfer of data.

## MUX/SEL GENERAL I/O FLOW

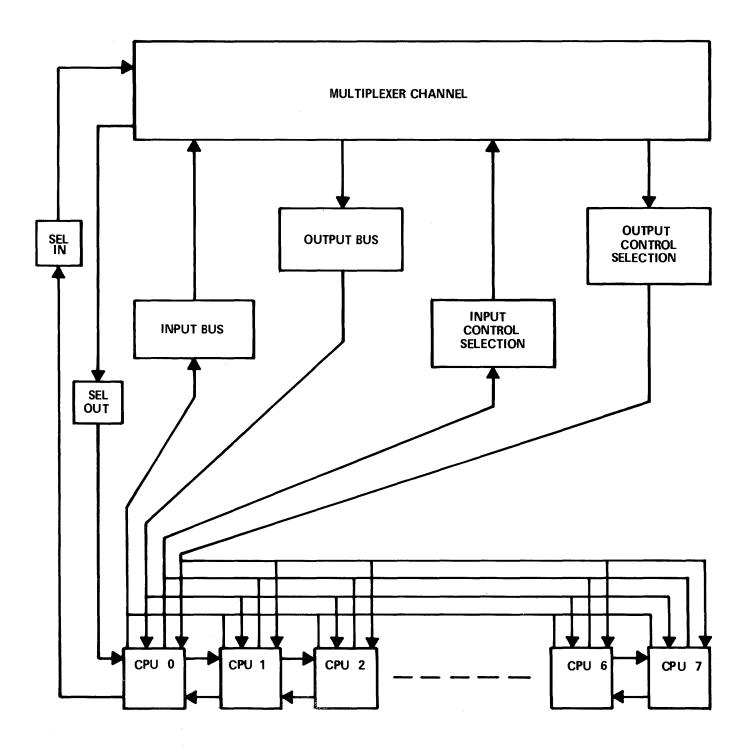

#### MULTIPLEXER/SELECTOR CHANNEL

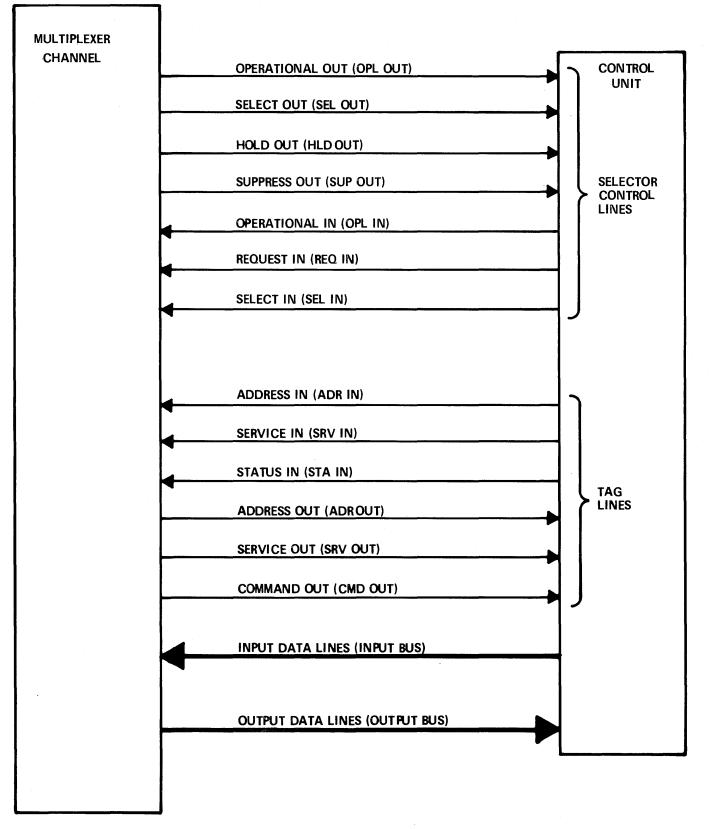

The Input bus and Output bus contain the actual data to be transferred. They each consist of 8 data lines and 1 parity line. The data signals are sent in parallel. The input data, device numbers, and status information are transmitted to the channel via the input bus. The channel transmits output data, I/O commands, and device selection to the control units via the output bus.

The Input and Output control sections contain a combined total of seven selector lines (4 for the output section and 3 for the input section) and six tag lines (3 for the output section and 3 for the input section). The signals are sent in parallel, with the exception of the Select Out and the Select In, which are sent in serial.

## **MULTIPLEXER/SELECTOR CHANNEL**

#### MULTIPLEXER/SELECTOR CONTROL LINES

#### Output Control Section Selection Lines:

- 1. Operational Out (OPL OUT) indicates the channel is active and when the command is dropped a reset condition is indicated. No output control lines are enabled unless OPL OUT is active.

- 2. SELECT OUT (SEL OUT) sent to the first logical control unit and continues on to the next until a control unit connects to the channel. At the last physical control unit the SEL OUT becomes a SELECT IN (SEL IN) and returns to the channel through the control units. SEL OUT and SEL IN perform the same function, therefore, the control unit may use either one for selection control, but not both.

- 3. HOLD OUT (HLD OUT) sent in parallel to the control units at the same time as SEL OUT is sent serially. SEL OUT is valid only with HLD OUT.

- 4. SUPPRESS OUT (SUP OUT) indicates special conditions including command chaining and status suppression.

<u>Output Control Section Tag Lines</u>: carry interlocked responses to the input tag line signals. In most cases, they specify information on the output bus.

- 1. ADDRESS OUT (ADR OUT) used during a channel-initiated selection sequence to indicate a device number is available on the output bus.

- 2. SERVICE OUT (SRV OUT) a positive response to service in (SRV IN) or STATUS IN (STA IN) indicating the channel has accepted the input data or status, or indicates on output that data is available on the output bus.

- 3. COMMAND OUT (CMD OUT) has several applications.

- a. In response to ADR IN indicates a command is available on the output bus and proceed during a control-unit-initiated sequence.

- b. In response to SRV IN causes the control unit to terminate and eventually to initiate an interrupt sequence.

- c. Is a negative response to STA IN indicating the channel cannot accept the status byte at this time.

Input Control Section Selection Lines:

- 1. SELECT IN (SEL IN) provides the return path for the SEL OUT and if seen at the channel indicates no control unit responded to the SEL OUT.

- 2. REQUEST IN (REQ IN) indicates one or more of the control units require service.

- 3. OPERATIONAL IN (OPL IN) indicates to the channel that a control unit is connected.

<u>Input Control Section Tag Lines</u>: Carry interlocked responses in conjunction with the output tag lines. In all cases, they specify information is available on the input bus.

- 1. ADDRESS IN (ADR IN) The control unit activates an ADR IN indicating the device number has been placed on the input bus.

- 2. SERVICE IN (SRV IN) indicates the control unit is ready to receive or transmit a byte of data.

- 3. STATUS IN (STA IN) indicates that status information is available on the input bus.

## **MULTIPLEXER/SELECTOR CONTROL LINES**

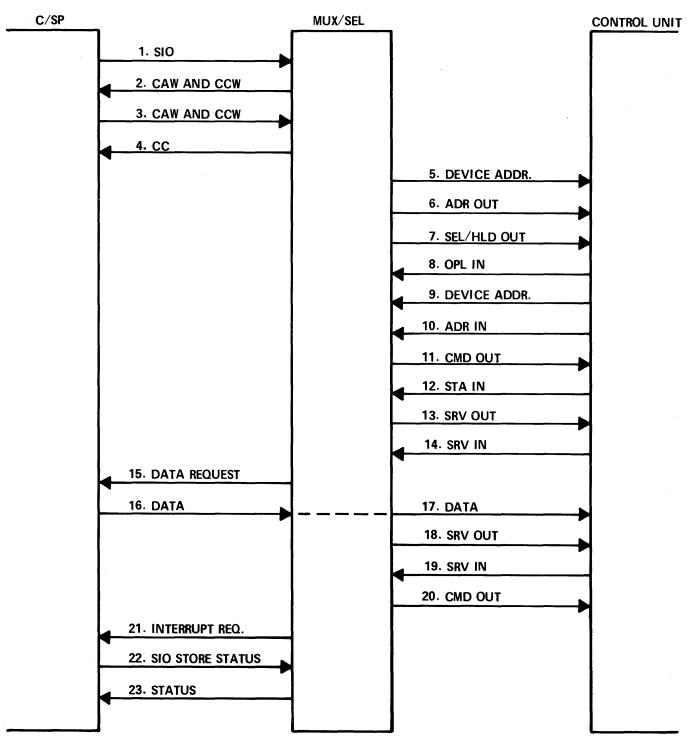

### MULTIPLEXER/SELECTOR INITIALIZE DEVICE

- 1. C/SP issues SIO

- 2-3. MUX/SEL asks for CAW, receives CAW, asks for and receives CCW. 4.\* MUX/SEL sends condition code to C/SP.

#### Initialization of Device

- 5-6. MUX/SEL places the device address on the output bus and raises the Address out signal. All control units compare the address.

- 7. The Select Out and Hold Out signals are raised, by MUX/SEL.

- 8. Operational IN is raised, by control unit. Device now selected.

- 9-10. The device address is placed on the Input bus by the CU, Address In is raised, SEL/HLD OUT, Address Out are dropped.

- 11. The command is put on the Output bus and Command Out signal is raised by channel, Address In is dropped.

- 12. The command is interpreted, Command Out is dropped and status placed on Input bus, STATUS IN is raised by control unit. (STATUS is all zeros)

- 13. Service Out is raised by channel, then Operational In is dropped, Status In, and Service Out is dropped.

- 14. Control Unit raises Service In, indicating ready to receive byte of data.

Data Transfer begins

- 15-16 MUX/SEL requests and receives byte of data from C/SP.

- 17-18 MUX/SEL places data on the output bus and raises Service Out signal. Service In is dropped.

- 19. Control Unit raises SRV IN (ready for another data byte). SRV OUT is dropped.

Termination

- 20. MUX/SEL raises a Command Out indicating the control unit to terminate. SRV IN is dropped.

- 21. Channel generates an Interrupt request to C/SP.

- 22. C/SP accepts, issues SIO to store the sub-channel status.

- 23. C/SP receives status, Terminates.

\*The condition code returned to the C/SP does not necessarily return at this point. It varies as the channel may be busy, then the CC is returned immediately and no CAW is fetched.

This overhead is designed to show the amount of signals transmitted between the C/SP channel, and control units. It should not be interpreted as the absolute procedure.

## **MULTIPLEXER/SELECTOR INITIALIZE DEVICE**

## SECTION IV ADAPTER CHANNEL

## SECTION IV INDEX - INTERCOMPUTER ADAPTER CHANNEL

- IV. -2 (B1) + D1 OF START I/O INSTRUCTION

- -4 CONDITION CODES (ICA)

- -6 CHANNEL ADDRESS WORD (ICA)

- -8 CHANNEL COMMAND WORD (CCW) Ø

- -10 CCW 1

- -12 ADAPTER SENSE BYTES 0, 1, 2

- -14 ADAPTER SENSE BYTES 3, 4, 5

- -16 ADAPTER EF WORD FROM HOST

- -18 ADAPTER HOST EI WORD

- -20 ADAPTER STATUS AND INTERRUPT CODE HALFWORD

- -22 ICA GENERAL FLOW

- -24 C/SP INITIATES DATA TRANSFER

- -26 HOST (IOAU) INITIATES DATA TRANSFER

- -28 HOST C/SP DATA WORD FORMAT

The Intercomputer Adapter (ICA) provides the means of communication between the C/SP and 1100 computer.

Data transfer operations take place only when the adapter channel has accepted matching commands from both C/SP and the Host computer, i.e., the command byte issued by the C/SP via the CCW and the external function (EF) issued by the host both indicate data transfers and in the same direction.

The C/SP indicates a data transfer by issuing a SIO instruction to the adapter channel. When recognized by the adapter channel, the adapter issues data request to the C/SP to get the CAW and then the CCW. The command byte is decoded and appropriate action is taken. If the command is input or output to/from the host, the adapter checks for the matching EF and command byte code. If no match, an External Interrupt (EI) is sent to host, thus any EF issued by the host is considered non-matching (before acknowledgement of the EI). If matching, the data transfer takes place.

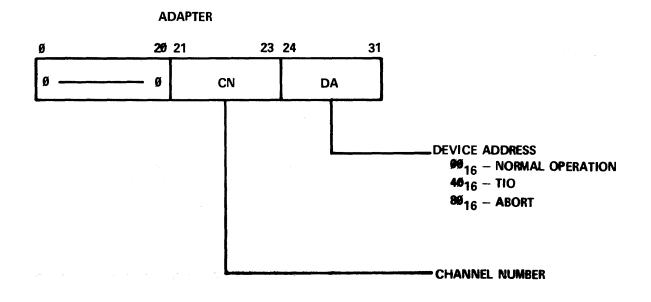

The channel number varies according to system configuration.

The device address contains the function to be performed:  $\emptyset\emptyset16$  - normal data transfer;  $4\emptyset_{16}$  - Test I/O to determine the condition of the ICA;  $8\emptyset_{16}$  - Abort, immediately terminates no matter what operation is in progress. This command causes no interrupt to the Host processor.

## (B<sub>1</sub>) + D<sub>1</sub> OF START I/O INSTRUCTION ADAPTER

#### CONDITION CODES ADAPTER

The adapter returns condition codes to the C/SP, depending on the function indicated by the device address of the SIO instruction.

SIO  $\oint d_{16}$  (START) CC<sup>6</sup> = 1 $\oint$  Busy indicates transfer operation is in progress

SIO 4016 (Test I/O)

The CAW is not fetched for this function.

$CC = \emptyset 1$  Holding pending status - the status byte is stored in the status halfword in fixed memory. The condition code is returned to the C/SP, and the channel clears itself for the next operation.

## SIO $8\phi_{16}$ (ABORT) Aborts immediately no matter what operation is in progress. Abort is accepted or the channel may be off-line.

## CONDITION CODES ADAPTER

## SIO START

| CC = ØØ | INSTRUCTION ACCEPTED             |  |

|---------|----------------------------------|--|

| CC = Ø1 | PARITY ERROR ON CAW OR CCW FETCH |  |

| CC = 10 | BUSY                             |  |

| CC = 11 | CHANNEL OFF-LINE                 |  |

### SIO 40 TEST I/O

| AVAILABLE FOR START I/O |

|-------------------------|

| HOLDING PENDING STATUS  |

| BUSY                    |

| CHANNEL OFF-LINE        |

|                         |

### SIO 80 ABORT

| CC = ØØ | ACCEPTED         |

|---------|------------------|

| CC= Ø1  | CHANNEL OFF-LINE |

### CHANNEL ADDRESS WORD (ICA)

During the SIO time (i.e., the time the channel interprets the function and returns the condition code to the C/SP) the ICA fetches the CAW, assuming the channel is not busy or off-line.

Bits  $\emptyset$  - 2: The I/O protect key of the data address of the CCW. Bits 15 - 31: The address of Channel Command Word (CCW).

## CHANNEL ADDRESS WORD

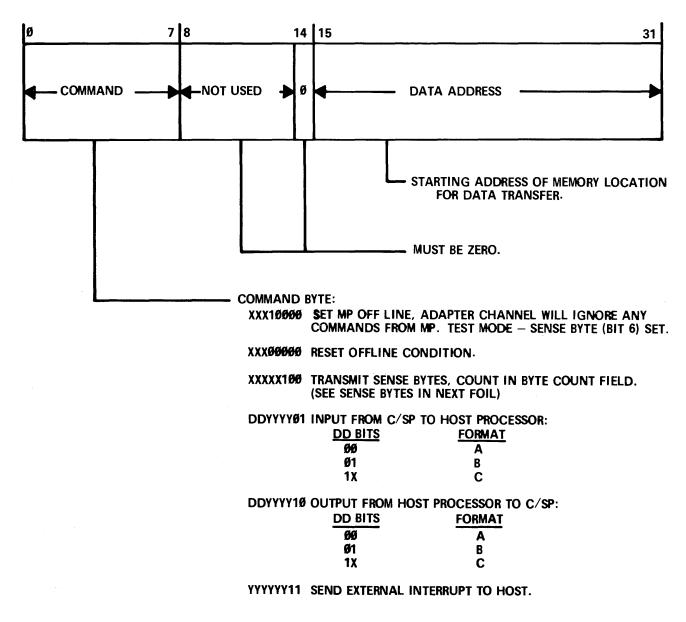

The CCW is a double word or 64 bits which contain the details of the I/O operation to be performed.

Bits  $\emptyset$  - 7 of CCW word zero is the command byte.

Command Byte:

'Set Host off-line' - indicates all data commands from the C/SP are executed in the test mode. 'Reset off-line condition' - indicates to the ICA to put the Host on-line again and also reset bit 6 of sense byte Ø. 'Transmit sense bytes' - All or none of the sense bytes are to be transmitted to C/SP as specified by the byte count in CCW 1. (Sense bytes are used to indicate command information, present data address, condition of ICA to C/SP and Host processor). 'Input - Output formats' - indicate the format of the data to be transferred and the direction of the transfer. 'Send External Interrupt to Host' - used to present status to Host processor. This is a control command, so no data transfer takes place.

Bits 15 - 31: The starting address for the data transfer.

## CHANNEL COMMAND WORD

```

CCW WORD Ø

```

X - NOT INTERPRETED BY ADAPTER CHANNEL.

Y - INTERPRETED IN TEST MODE ONLY.

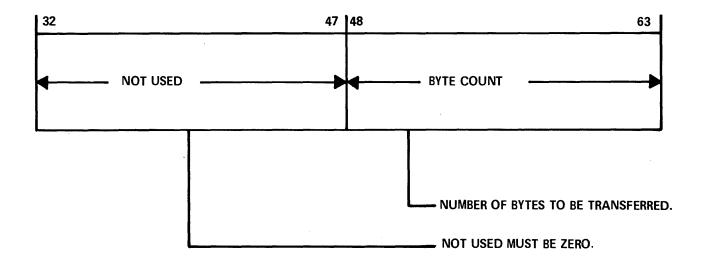

Bits 48 - 63: The number of bytes to be transferred. May be the number of sense bytes to be transmitted in conjunction with the sense command issued in CCW  $\emptyset$ . Bits 32 - 47 are not used.

,

## CHANNEL COMMAND WORD

CCW WORD 1

#### SENSE BYTES

- BYTE Ø INDICATES CONDITION OF ADAPTER CHANNEL TO THE C/SP.

- BYTE 1 & 2 CONTAINS COMMAND INFORMATION FROM HOST PROCESSOR TO C/SP.

- BYTE 3 CONTAINS INFORMATION ON ADAPTER CHANNEL FOR HOST PROCESSOR.

- BYTE 4 & 5 USED IN TRANSFERRING THE HIGH ORDER 16 BITS OF PRESENT DATA ADDRESS.

#### ADAPTER SENSE BYTES 0, 1, 2

The C/SP may request none, 1, 2, 3, 4, 5, or 6 sense bytes as specified by the count in the CCW associated with the Sense Command.

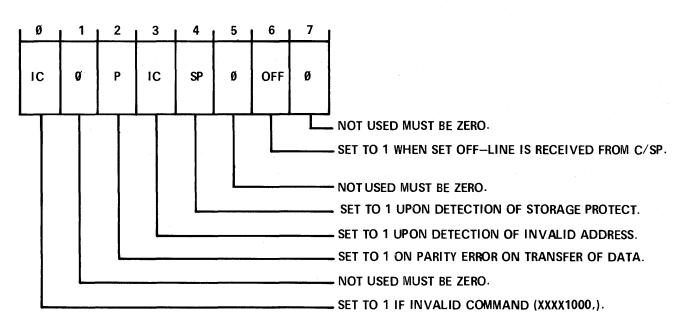

Sense Byte  $\emptyset$  - is used to indicate the condition of the ICA channel to the C/SP.

Bit  $\emptyset$  - Invalid Command: Is set if the command byte from the C/SP cannot be decoded into a meaningful operation.

Bit 1 - not used.

- Bit 2 Parity Error: Set if parity error occurs on a transfer of data from C/SP to ICA.

- Bit 3 Invalid Address: Set if an invalid address is detected during data transfers.

- Bit 4 Storage Protection Error: Set if a storage protection error is determined during a data transfer.

- Bit 5 not used.

- Bit 6 Host Off-Line: Set when a 'Set Host Off-Line' command is received from the C/SP.

Bit 7 - not used.

Sense Bytes 1 and 2 are used to transfer command information from the Host to C/SP.

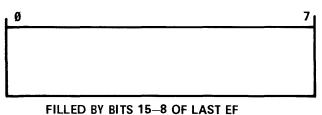

Sense Byte 1 is bits 15 - 8 of the last External Function (EF) received by the ICA from the Host. This would be the word or character count on output from the Host.

Sense Byte 2 is bits  $7 - \emptyset$  of the last External Function (EF) received by the ICA from the Host. This is the C/SP protect Key, format of the data to be transferred and the direction of transfer.

SENSE BYTES 0,1,2 ICA

SENSE BYTE Ø

SENSE BYTE 1

RECEIVED BY ADAPTER CHANNEL.

SENSE BYTE 2

BY ADAPTER CHANNEL

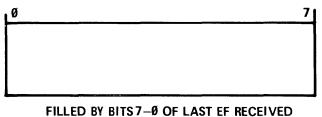

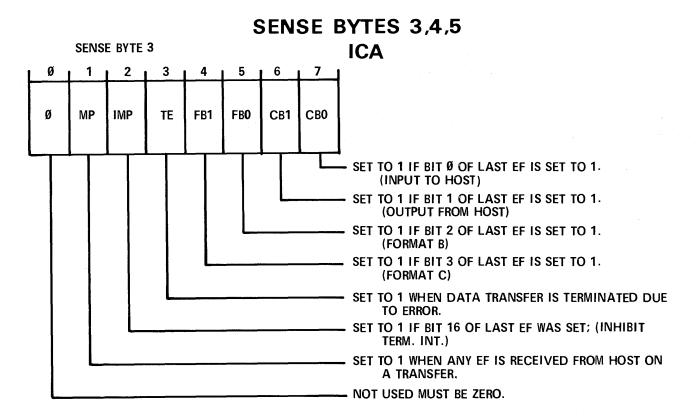

Sense Byte 3 - used to transfer information concerning the operation of the ICA to the Host.

Bit  $\emptyset$  - not used

Bit 1 - Host Termination:

Set when any External Function (EF) is received by the ICA from the Host during a data transfer. The Unit Exception bit (Bit 7) of the Status Byte is simultaneously set. This bit (Bit 1) is reset to zero when Sense Byte 3 is sent to the C/SP.

Bit 2 - Inhibit Host Normal Termination Interrupt:

Set if Bit 16 (Termination Interrupt) of the last EF was set. This inhibits the ICA from sending the normal termination interrupt to Host.

Bit 3 - C/SP Data Transfer Error:

Set when the data transfer is terminated due to a storage protection, invalid address, or parity error in the transfer from the C/SP to ICA. Corresponding bits in Sense Byte  $\emptyset$  are also set.

Bit 4 - Indicates Format C.

Bit 5 - Indicates Format B.

Bit 6 - Indicates Output from Host.

Bit 7 - Indicates Input to Host.

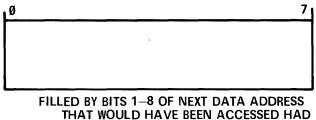

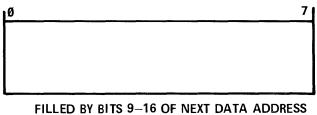

Sense Bytes 4 and 5 - used to transfer the high order 16 Bits of the present data address in the CCW.

Sense Byte 4 is bits 1 - 8 of the next data address that would have been accessed had the transfer not been terminated.

Sense Byte 5 is bits 9 - 16 of the next data address that would have been accessed had the transfer not been terminated.

SENSE BYTE 4

TRANSFER NOT BEEN TERMINATED.

**SENSE BYTE 5**

THAT WOULD HAVE BEEN ACCESSED HAD TRANSFER NOT BEEN TERMINATED.

#### ADAPTER EXTERNAL FUNCTION WORD SENT BY THE HOST

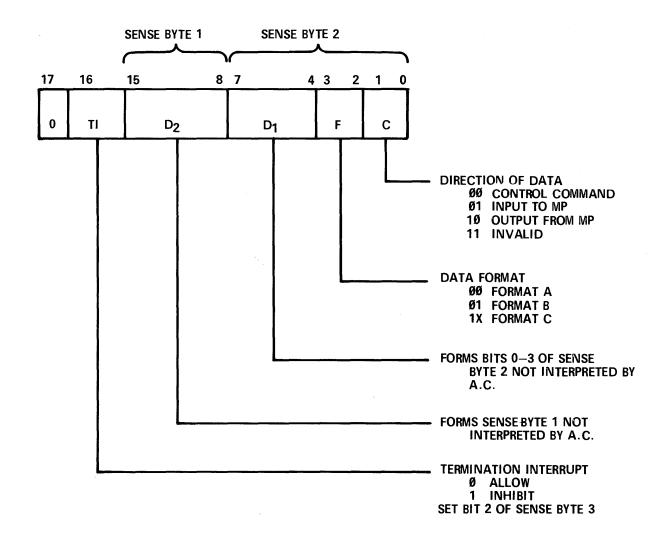

The External Function (EF) is transferred from the Host to the ICA to provide data format and transfer direction information for the ICA and other information for the C/SP via sense bytes 1 and 2.

Bit 17 - not used.

- Bit 16 Termination Interrupt: When set, inhibits the normal termination interrupt to the Host and also sets Bit 2 of sense byte 3.

- Bit 15 18: Forms Sense Byte 1 and are not interpreted by the ICA.

- Bit 7 4: Forms bits  $\emptyset$  3 of Sense Byte 2 and are not interpreted by the ICA.

- Bit 3 and 2: Informs the ICA and C/SP of the data format of the data to be transferred.

- Bit 1 and  $\emptyset$ : Informs the ICA and C/SP of the direction of the data transfer.

## EF SENT BY HOST

#### ADAPTER HOST EXTERNAL INTERRUPT WORD

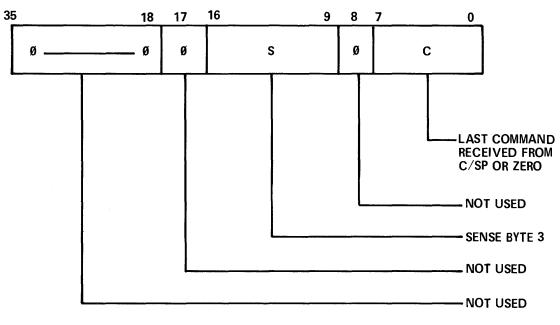

The External Interrupt Word is used to inform the Host of the present condition of the adapter channel and is presented as part of the External Interrupt.

During the ending interrupt sequence to the Host, Field 'C' is set to zero.

## HOST EXTERNAL INTERRUPT WORD

THE S AND C PORTIONS OF THIS WORD WILL BE ZEROED DURING THE ENDING OF THE INTERRUPT SEQUENCE.

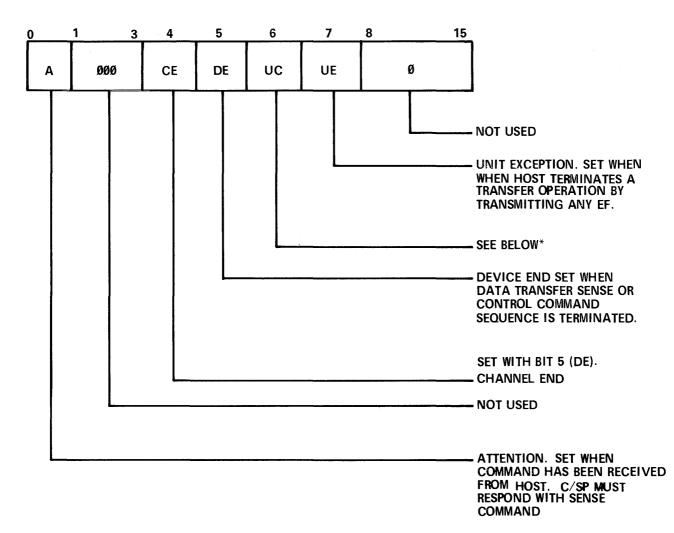

#### Adapter Status Halfword and Interrupt Code Halfword

When an interrupt request is accepted by the C/SP, a status halfword and interrupt code halfword are stored in fixed memory of the C/SP. Only one byte of the status halfword is used and is referred to as the status byte. The interrupt code halfword indicates the ICA channel identification code, channel number, and device address (ICA - device address is zero).

|                          | 16 17 19 | 20.21 23 | 3 24 31        |

|--------------------------|----------|----------|----------------|

| Interrupt code halfword: | I.D.     | No.      | Device Address |

Status halfword (byte) - Used to inform the C/SP of significant conditions during the ICA operation.

- Bit  $\emptyset$  Attention bit: Set when a command has been received from the Host. This bit will remain set until the C/SP responds with a sense command. The ICA will not accept a data transfer command until it receives the sense command.

- Bits 1 3: Are not used and are always zero.

- Bit 4 Channel End: Set when the device and channel are terminated. Bit 5 device end is also set.

- Bit 5 Device End: Set when a data transfer, or control command sequence is terminated.

- Bit 6 Unit Check: Set when any of these errors are sensed during a data transfer; Invalid command, Parity error, Invalid address error, Storage protect error.

- Bit 7 Unit Exception: Set when the Host terminated a data transfer operation by transmitting any External Function.

## STATUS HALF WORD ADAPTER CHANNEL

- \* UNIT CHECK SET WHEN: These errors are sensed during data transfers.

- a. INVALID COMMAND (816)

- b. PARITY ERROR

- c. INVALID ADDRESS ERROR

- d. STORAGE PROTECT ERROR

### ICA GENERAL FLOW

The program sets up the CAW and CCW's. The SIO instruction is issued to the ICA with the contents of  $B_1$  added to the value of  $D_1$  actually forming the device address consisting of the channel number, function (start I/O, Test I/O) and the device address of the device to be activated. (In the case of the ICA, the device is  $\emptyset$ .) The ICA reads the CAW from storage, gets the address for the CCW and reads the CCW out of storage. The command byte is interpreted and if a match exists with the EF (from the Host) the data transfer is initiated.

## ICA GENERAL I/O FLOW

#### INTER-COMPUTER ADAPTER (ICA)

Whenever an interrupt request is sent to and accepted by the C/SP, a status halfword and interrupt code halfword are stored in C/SP fixed memory. If the status halfword has bit  $\emptyset$  set, the C/SP must respond with a sense command (to determine if input or output has been requested by the Host). If Bit  $\emptyset$  is not set, C/SP does not send sense command (checks other bits - as termination).

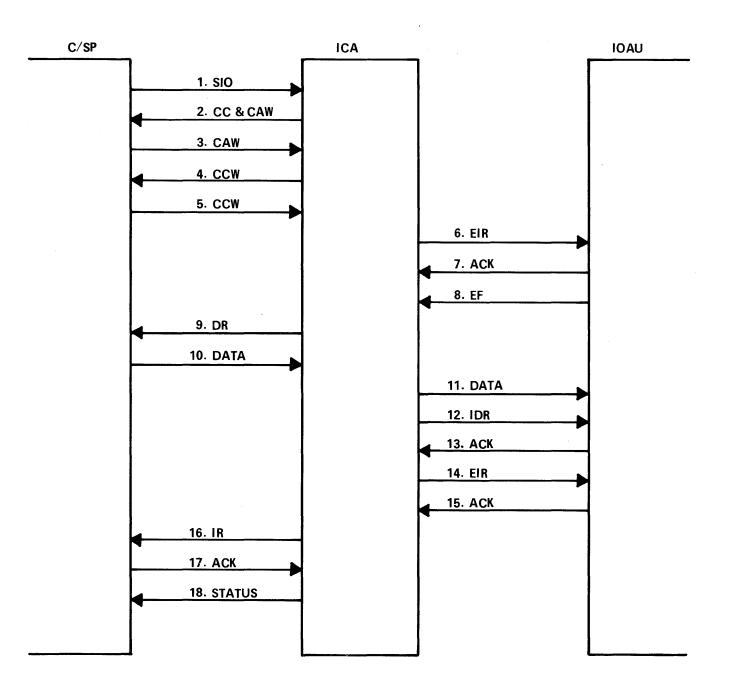

C/SP initiates data transfer.

- 1. C/SP initiates data transfer by issuing SIO instruction.

- 2. ICA accepts the SIO (indicated to C/SP via CC in PSW). The ICA, at the same time it recognizes the SIO, generates a data request to C/SP for the CAW.

- 3-4. ICA gets the CAW and generates a data request to C/SP for the CCW.

- 5. ICA gets the CCW and analyses the command byte of word  $\emptyset$ . The command in this case says input to Host.

- 6. ICA generates an External Interrupt to Host. During that sequence, the status of the adapter is also put on the line to Host. (sense byte 3)

- 7. IOAU sends back an acknowledge, which resets the External Interrupt, clears the input data lines and sense byte 3 (to all zeroes).

- 8. IOAU issues an External Function (EF) word to ICA to accept input. ICA determines if the command codes match (from C/SP and Host C/SP wants to input to Host and Host will accept input).

Data Transfer begins.

- 9. ICA generates a Data Request of C/SP for data byte.

- 10. C/SP sends input byte.

- 11-12. ICA assembles a word, places the data on the input bus, and generates an input data request to IOAU. The data is sent during this time.

- 13. IOAU acknowledges the word has been received. Sequence #9 13 continues until the byte count in CCW goes to  $\emptyset$ .

Termination

- 14. ICA generates an External Interrupt to Host.

- 15. IOAU acknowledges.

- 16. ICA generates an Interrrupt request to C/SP indicating termination.

- 17. C/SP acknowledges it can accept the interrupt.

- 18. ICA sends the status halfword and interrupt code halfword to be stored in C/SP fixed memory location.

## C/SP INITIATES DATA TRANSFER ICA

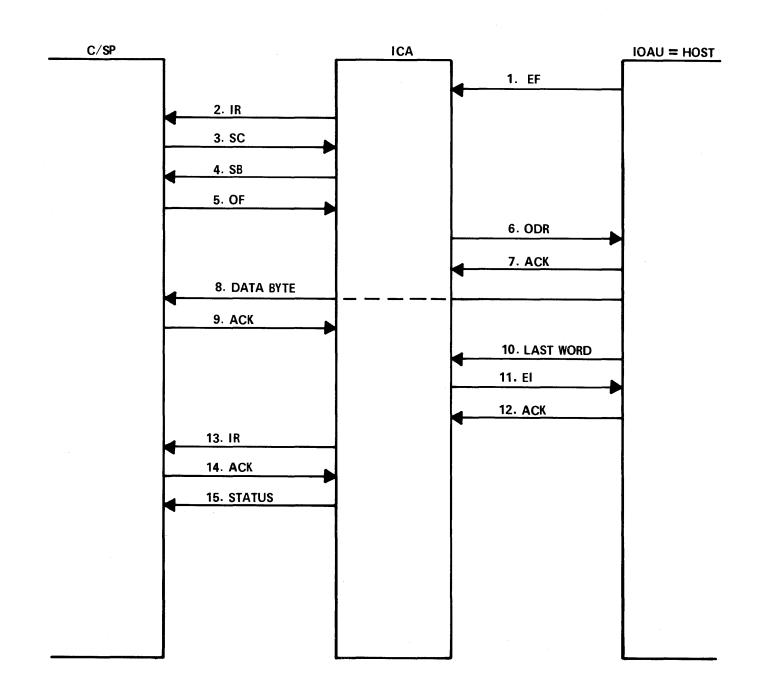

## HOST - (IOAU) INITIATES DATA TRANSFER

- 1. IOAU initiates data transfer by issuing an External function.

- 2. ICA generates an interrupt request to C/SP. When the C/SP acknowledges it can accept the interrupt, status is stored in fixed memory with the attention bit set.

- 3. C/SP must respond with a sense command.

- 4. ICA sends sense bytes. C/SP interprets the sense bytes and finds the Host has output for the C/SP and the amount of data to be transferred.

- 5. C/SP issues the output function.

## Data Transfer Begins:

- 6. ICA generates an output data request to IOAU.

- 7. IOAU acknowledges and sends data word to ICA.

- 8. ICA unpacks the data word and sends the data bytes to C/SP.

- 9. C/SP acknowledges receipt of the bytes.

- 10. ICA, upon completion of the data bytes transferred to C/SP, requests another word from IOAU/Host and sequence #6 10 continues until byte count goes to  $\emptyset$ .

Termination:

- 11. ICA generates an External Interrupt to IOAU indicating termination.

- 12. IOAU acknowledges.

- 13. ICA generates an interrupt request to C/SP to present status.

- 14. C/SP acknowledges indicating it is able to accept the interrupt.

- 15. ICA sends the status halfword and interrupt code halfword to be stored in C/SP fixed memory locations. C/SP checks status, etc. and takes appropriate action - in this case termination.

IV-25

## HOST-(IOAU) INITIATES DATA TRANSFER

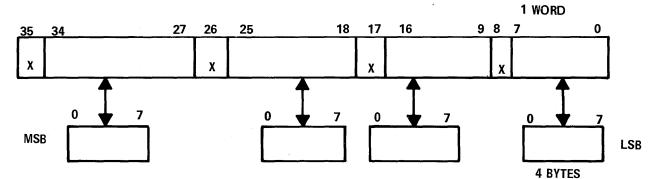

#### FORMAT A

The bits indicated by X are ignored on output to C/SP and zero filled on input to Host. Four bytes per word, indicating quarter word mode.

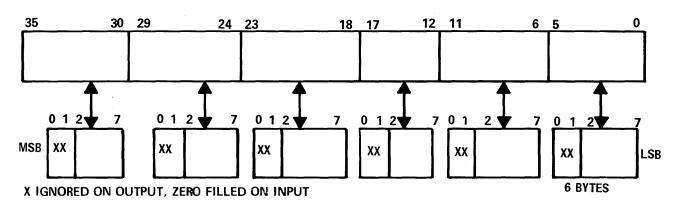

### FORMAT B

Bits indicated by XX are ignored on output to C/SP and zero filled on input to Host. Results in 6 Bit bytes, indicating field data.

#### FORMAT C

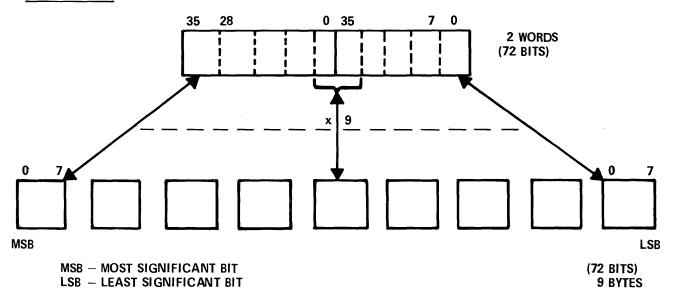

Double Word (72 bits) resulting in 9 bytes, indicating no loss of data.

**ICA FORMATS**

#### 1108 FORMAT B

### 1108 FORMAT C

## SECTION V GENERAL PURPOSE

# COMMUNICATION CHANNEL

## SECTION V INDEX – GENERAL PURPOSE COMMUNICATION CHANNEL

V. -2 GENERAL PURPOSE COMMUNICATION CHANNEL (GPCC)

- -4 CHANNEL ADDRESS WORD (GPCC)

- -6 CONDITION CODE (GPCC)

- -8 CAW FORMAT 1

- -10 CAW FORMAT 2

- -12 CAW FORMAT 3

- -14 CAW FORMAT 4

- -16 CAW FORMAT 5

- -18 BUFFER CONTROL WORD ADDRESS

- -20 BCW FORMAT

- -22 BCW (WORD 1 & 3)

- -24 BCW (WORD 2)

- -26 BUFFER CONTROL WORD (WORD Ø)

- -28 BCW (WORD Ø) CONTINUED

- -30 MDW ADDRESS

- -32 MDW FORMAT

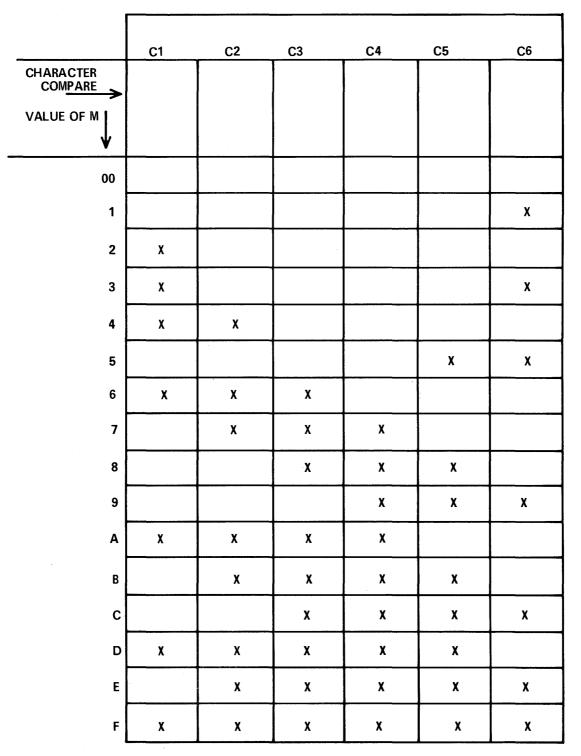

- -34 MDW (WORD 1) COMPARE INFORMATION

- -36 MDW (WORD 2, 3) COMPARE INFORMATION

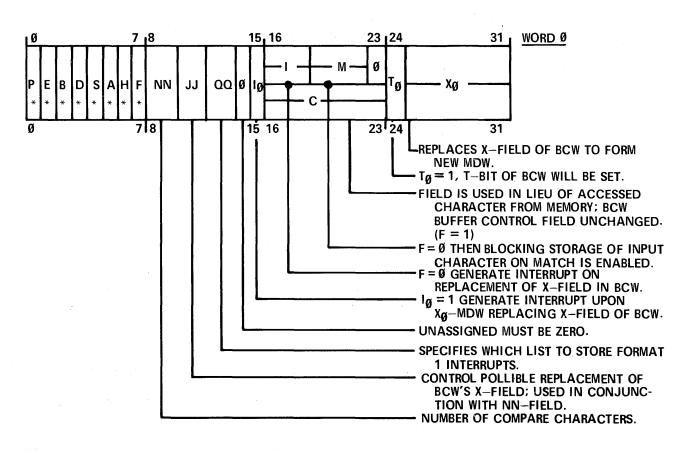

- -38 MDW (WORD Ø) CONTROL INFORMATION

- -40 MDW (WORD Ø) CONTROL INFORMATION CONTINUED

- -42 I-FIELD

- -44 M-FIELD

- -46 NN/JJ-FIELD

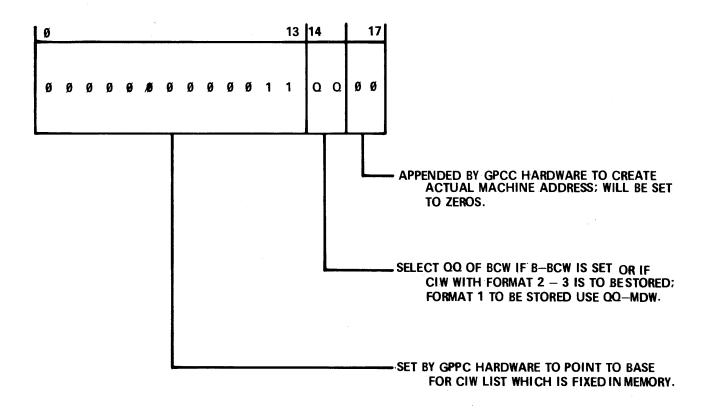

- -48 CIW LIST CONTROL

- -50 CIW ADDRESS

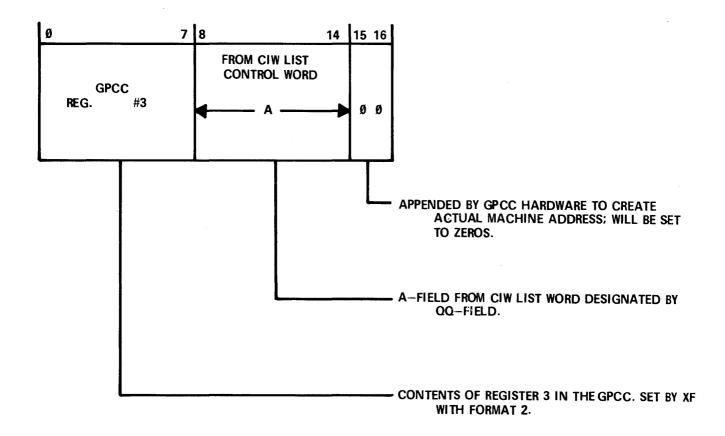

- -52 LIST CONTROL WORD

- -54 GPCC CHANNEL INTERRUPT WORD

- -56 CIW FORMAT 1

- -58 CIW FORMAT 2

- -60 CIW FORMAT3

- -62 COMMUNICATION LINE TERMINAL

- -64 ASYNCHRONOUS CLT EF (XF)

- -66 SYNCHRONOUS CLT XF

- -68 ASYNCHRONOUS/SYNCHRONOUS CLT STATUS

- -70 GPCC GENERAL FLOW

- -72 HOST SYMBIONT/COMMUNICATION BLOCK INPUT

- -74 C/SP SYMBIONT/COMMUNICATION BLOCK INPUT

- -76 APPENDIX B

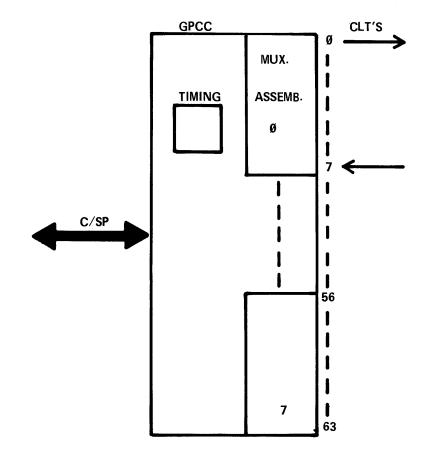

General Purpose Communication Channel (GPCC)

The GPCC performs functions such as multiplexing the various CLT's, so that one CLT may be serviced at a time, recognizing special characters and/or sequences of characters, checking character parity, co-ordinating all data transfers to/from storage and executing other necessary operations.

The CLT's assemble and disassemble data characters for reception and transmission, from/to a communication line. The CLT's cover a wide range of communication with rates up to 50 kilobits/seconds, however, the CLT's must be selected so the combined rate of service requests (one per byte) is no more than 50,000 per second.

GPCC hardware consists of:

- 1. CLT's which provide the actual connection to the communication line or data set (as the case may be).

- 2. Timing assemblies to provide the line frequencies required by the CLT's.

- 3. Multiplexer portion and assemblies provide the connection, on a priority basis, between the CLT's and the GPCC control logic.

- 4. CLT expansion up to 32 CLT's (full duplex)

- 5. GPCC control logic provides the basic logic which interfaces to, and controls the operation of the various CLT's, communicating with them as necessary through the multiplexer and its associated assemblies. In the GPCC control logic are a number of hardware registers, loaded under software control, which assist in these control functions.

- 6. CPU-I/O channel interface provides the interface between the processor/ storage and the GPCC control logic. The interface logic recognizes and passes along SIO instructions intended for the GPCC. The logic requests storage access via the central storage priority network whenever required for data access or control information purposes. It also provides the logic path for interrupt requests from the GPCC to the C/SP (processor).

## **GENERAL PURPOSE COMMUNICATIONS CHANNEL (GPCC)**

#### CHANNEL ADDRESS WORD (GPCC)

The CAW is accessed from storage by the GPCC when a SIO instruction with the GPCC channel # is detected. The CAW is used to initiate, modify, or terminate GPCC action. The GPCC stores the 16 most significant bits of the CAW in 'its' hardware and terms it an external function (XF) so as to distinguish it from any possible new CAW value associated with some succeeding SIO instruction. The actual execution of the stored XF may occur at some time later than the execution of the processor SIO instruction. If an SIO is issued while the GPCC is storing an unexecuted XF, it is rejected. There are 5 CAW formats and are distinguished by their most significant bits of byte 2.

- Format 1 bit =  $\emptyset$ : Directed to an individual CLT, the address of which is specified in the SIO instruction used to turn CLT on, off, etc.

- Format 2 bit = 100: Directed to the GPCC and loads a specified register within GPCC with a specified constant. Seven registers are available and vary in length between 4 and 7 bits. Three are used to establish the high order address bits of various control words in storage. The others used to search for other control codes, in data where Buadot or similar codes are used.

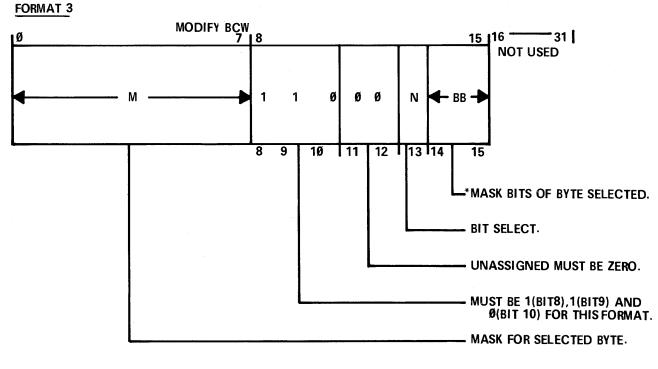

- Format 3 bit =  $11\emptyset$ : Used to modify specified bits within the first word of BCW.

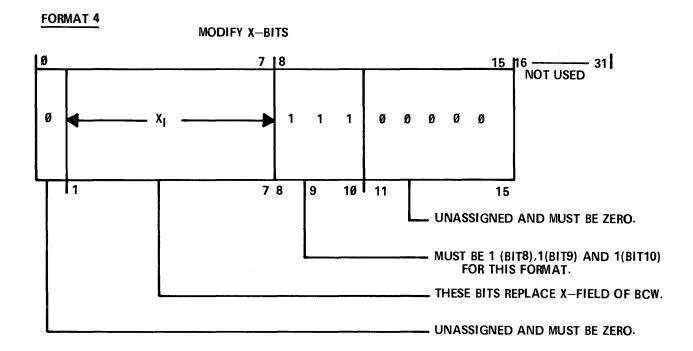

- Format 4 bit = 111: Used to replace the x-bits of BCW. These bits designate the currently active MDW. With the Y-bits of the BCW and GPCC register 2 they form the address of the current MDW.

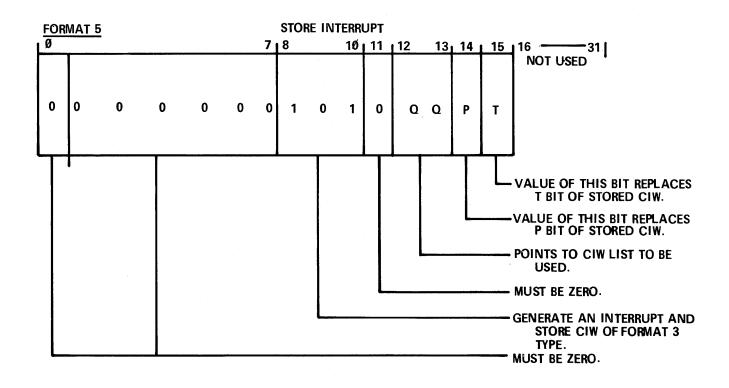

- Format 5 bit = 101: Used to initiate an interrupt with special bits set in the CIW that is stored in the CIW List. Intent is to signal the controlling program through the interrupt handler routine that various time-outs have occurred.

# **GPCC CHANNEL ADDRESS WORD**

#### FORMAT 1 - COMMAND TO A CLT

| <u>Ø 7</u> | 8 15     | <u>16 31</u> |

|------------|----------|--------------|

| S          | ØFFFDDDØ | NOT USED     |

FORMAT 1 - LOAD PROGRAM LOADABLE REGISTER

| Ø 7 | 8 15     | 16       | 31 |

|-----|----------|----------|----|

| I   | 1ØØRRRRR | NOT USED |    |

FORMAT 3 - MODIFY FIRST WORD OF BCW

| <u>Ø 7</u> | 8 15     | 16       | 31 |

|------------|----------|----------|----|

| м          | 11ØØØNBB | NOT USED |    |

FORMAT 4 - REPLACE X-BITS IN BCW

| Ø 7                            | 8 15     | 16 31    |

|--------------------------------|----------|----------|

| Øx <sub>1</sub> x <sub>1</sub> | 111Ø — Ø | NOT USED |

FORMAT 5 - INITIATE INTERRUPT

| Ø 7          | 8 15     | 16       | 31 |

|--------------|----------|----------|----|

| Ø <u> </u> Ø | 1Ø1ØQQPT | NOT USED |    |

### CONDITION CODE (GPCC)

THE GPCC RETURNS CONDITION CODES TO THE C/SP:

- $CC = \emptyset \emptyset$  THE SIO INSTRUCTION WAS ACCEPTED

- $CC = \emptyset 1$  A PARITY ERROR OCCURRED ON A FETCH OF THE CAW

- $CC = 10^{\circ}$  THE GPCC IS BUSY

- CC = 11 INDICATES THE GPCC IS OFF-LINE OR IN A FAULT CONDITION. NO ACTION TAKEN

# CONDITION CODE GPCC

SIO

CHANNEL NO. DEVICE ADDRESS

CC = ØØ ACCEPTED

CC = Ø1 PARITY ERROR ON FETCH OF CAW

CC = 10 BUSY

CC = 11 NO ACTION OFF LINE/FAULT CONDITION

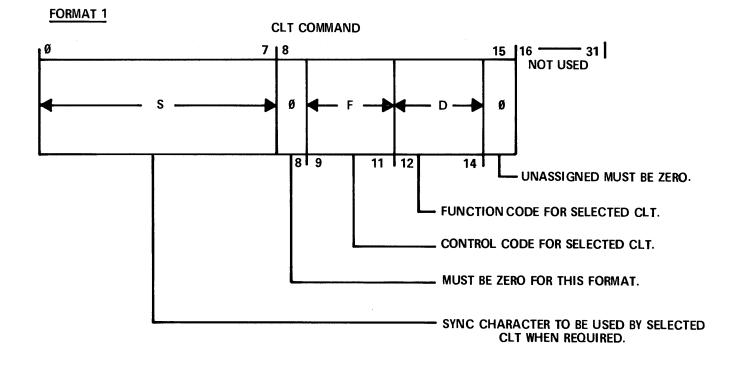

#### CAW FORMAT 1

This format is directed to an individual CLT, the address of which is specified in the SIO instruction.

- S = SYNC character to be loaded into the CLT when required. Left justified with the unused bits equal to zero. A SYNC character of all zeros is not allowed as it is translated as an asynchronous CLT operation.

- Bit 8: Format select must be zero.

- F: Control CLT action Turn on/off input/output, enter test mode, disconnect from the communication line and turn off output, disconnect CLT from system, Mode Set.

- D: Detail bits of XF code for the CLT. Combine with the 3-bit F-field indicating level of code used, number of stop bits to transmit, mode of CLT (half duplex or full).

Further explanation of the F and D fields in covered on the external functions of the CLT's.

# CHANNEL ADDRESS WORD FORMAT GPCC

V-8

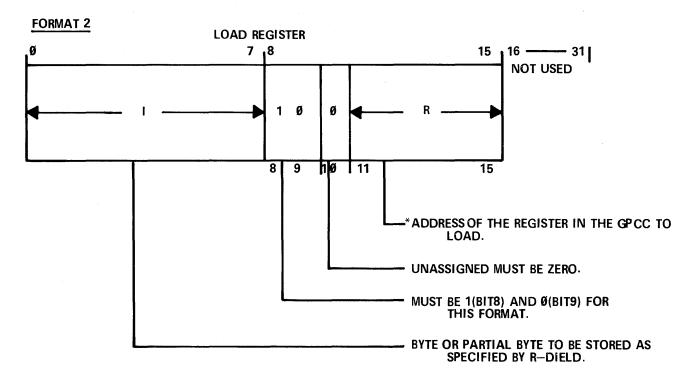

#### CAW FORMAT 2

This format is directed to the GPCC and loads a specified register within the GPCC with a specified constant. There are 7 program loadable registers, which vary in length between 4 and 7 bits. Three of these registers are used to establish the high order address bits of various control words in storage. The others search for FIG/LTRS or other control codes, in data where Baudot or similar codes are used.

I = byte or partial byte to be stored in the GPCC register specified by the R-field and must be right justified.

bits 8 - 10 - Format select: Store data (I) field in a GPCC register.

R = specify the address of the register in the GPCC to be loaded.

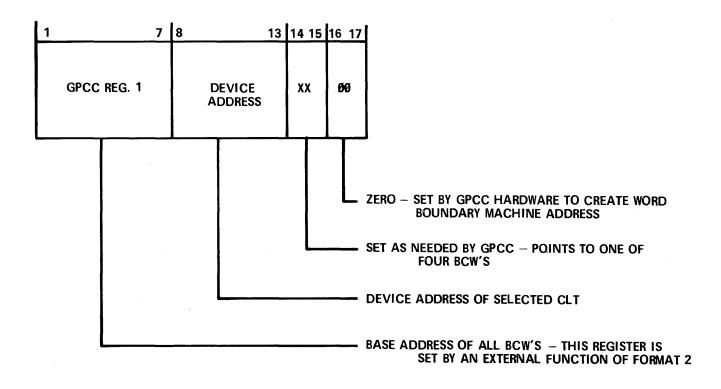

Register 1: 7 bits - MSB of address for BCW's.

Register 2: 4 bits - MSB of address for MDW's.

Register 3: 7 bits - MSB of address for CIW's.

Register 24: 5 bits - special symbol for 5 level code.

Register 26: 5 bits - special symbol for 5 level code.

Register 27: 6 or 7 bits - special symbol for 6 and 7 level code (7 level if parity generation/checking specified).

Register 28: 6 or 7 bits - same as Register 27.

Registers 25 - 28: specify the code level to be used by the addressed CLT.

# CHANNEL ADDRESS WORD FORMAT GPCC

| *REGISTER 1        | M.S.B. ADDRESS BCW – 7 BITS          |

|--------------------|--------------------------------------|

| REGISTER 2         | M.S.B. ADDRESS MDW – 4 BITS          |

| REGISTER 3         | M.S.B. ADDRESS CIW – 7 BITS          |

| REGISTER 25        | SPECIAL SYMBOL LEVEL 5 CODE – 5 BITS |

| REGISTER 26        | SPECIAL SYMBOL LEVEL 5 CODE - 5 BITS |

| REGISTER 27        | SPECIAL SYMBOL LEVEL 6 CODE - 6 BITS |

| <b>REGISTER 28</b> | SPECIAL SYMBOL LEVEL 6 CODE - 6 BITS |

|                    |                                      |

#### CAW FORMAT 3

This format is used to modify specified bits within the first word (control word) of the Buffer Control Word (BCW) in a manner to avoid race conditions. The BCW may be modified by instructions in the processor repertoire. If a BCW is being used by the GPCC at the time an instruction is used to modify the BCW, it is possible that the GPCC will write into the BCW in storage and overlay the area written into by the instruction. Use of this format quarantees the BCW will be set to the condition specified.

- M = mask bits: May be used to select any or all of bits of byte BB of BCW word zero.

- bits 8 10: format select indicating CAW format 3.

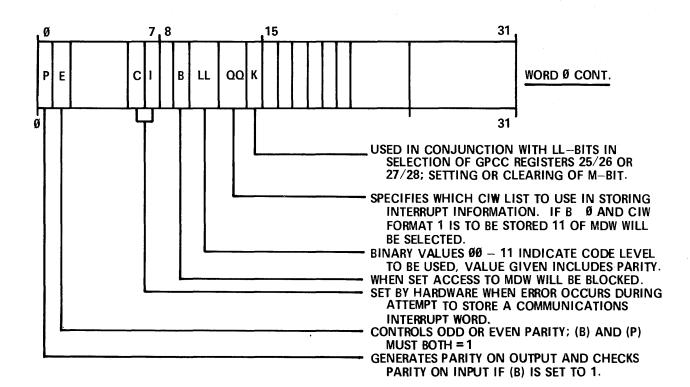

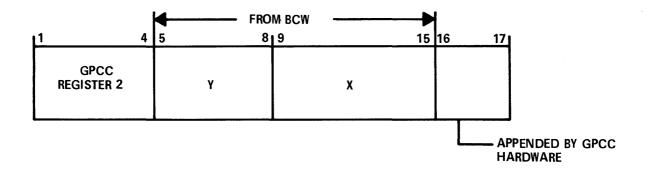

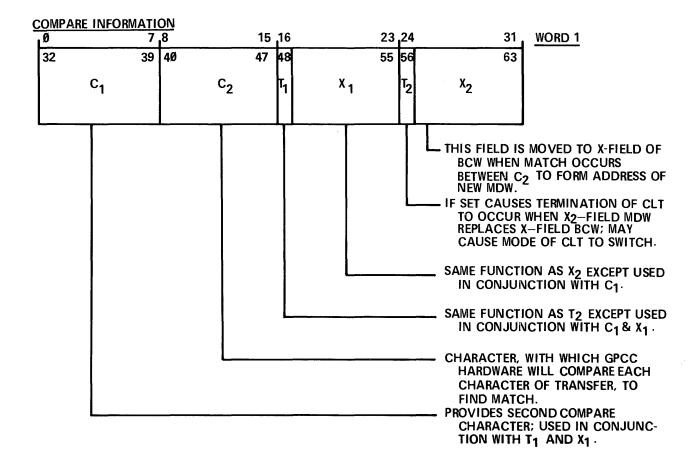

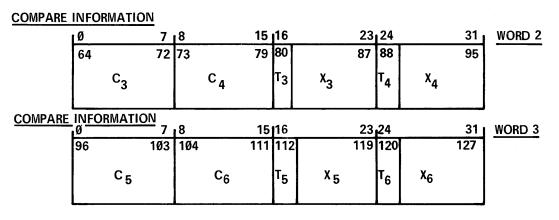

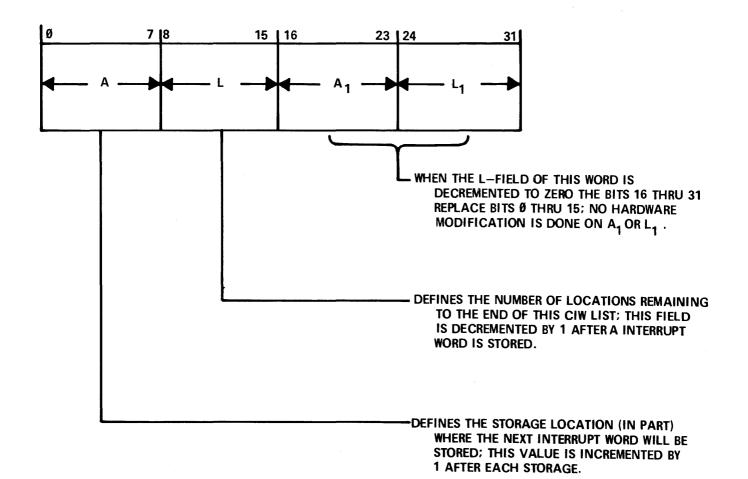

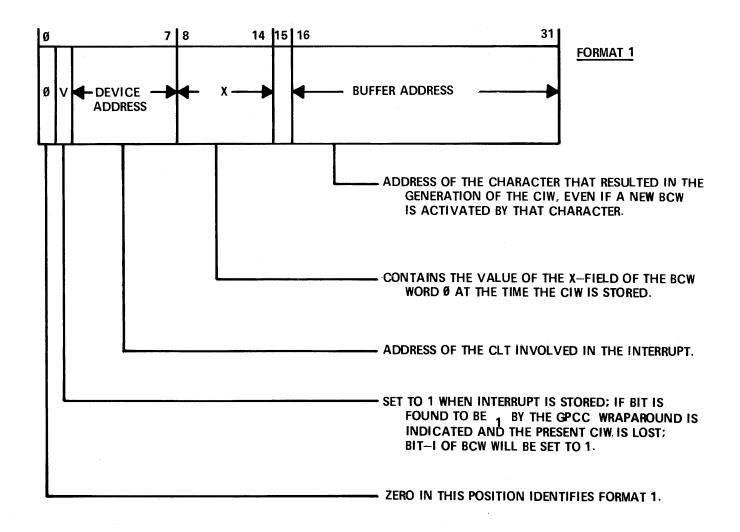

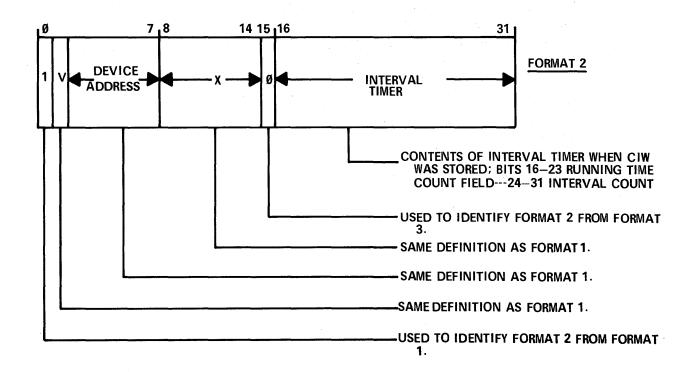

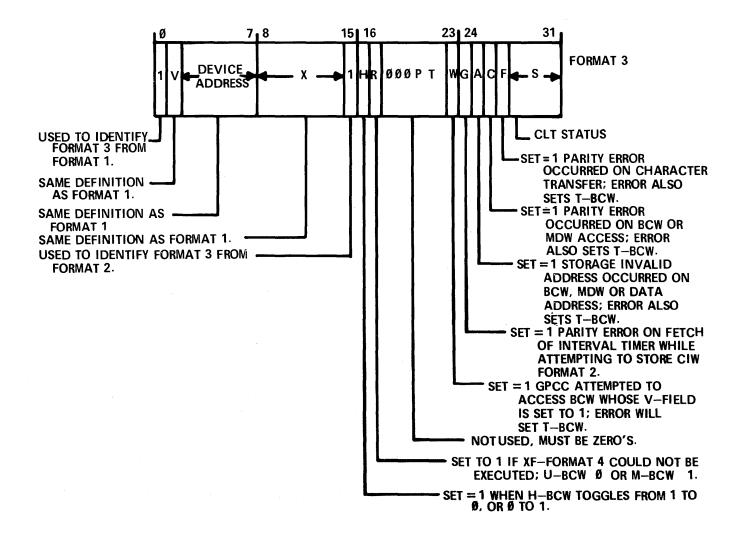

- bits 11, 12: must be zero.