# History and Evolution of 1100/2200 Mainframe Technology

This paper was prepared in recognition of the 35th anniversary of USE inc. and was presented at the Fall 1990 Conference in Seattle, Washington.

> Copyright<sup>®</sup> 1990 Unisys Corporation All rights reserved Printed in U S America

006499-12PETSCH-BJH

# History and Evolution of 1100/2200 Mainframe Technology

November 8, 1990 Richard J. Petschauer

# HISTORY AND EVOLUTION OF 1100/2200 MAINFRAME TECHNOLOGY

# INTRODUCTION

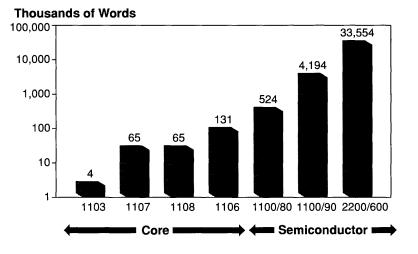

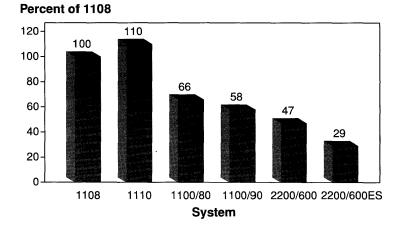

This paper covers the highlights of the history and evolution of the Unisys 1100/2200 Series processor and memory technologies. The period covered spans the last 35 years and includes the recent product announcements in 1990. A number of articles have already covered the earlier years including the computers that were developed then. Others reviewed the formative time of the Eckert Mauchly and Engineering Research Associates (ERA) companies and their joining Remington Rand which later merged into the Sperry Rand organization. Still others have traced the architectural aspects of the 1100 Series. This paper instead concentrates on the internal logic and memory technologies used in the 1100/2200 systems and some of the industry factors present during this time.

These early machines originated during a period when computer designers were searching for better ways to best do the basic functions of computing and memory. This computing, or logic technology as we will call it, had a time lead over that of memory since it had been used in early digital calculators and some control equipment. However these machines were special in nature since their inherent construction and "hook up" determined what function they would perform. The revolutionary concept of the computer was an idea where a general set of basic operations, which could be called out in any sequence, would operate on "data" provided, and return and store the results. The "data" could be numbers or codes representing letters and words.

This programmability of computers, which we all now take for granted, is really what makes them so powerful since it allows them to be used to solve such a wide variety of problems. However, it also required a new class of technology that the earlier calculators did not need-a means to store the sequence of operations, or instructions, to be performed and also a place to hold the input data and the results. This function of "memory" presented a large problem in the early days of computers. The memory used a different technology than the logic for the processor, and the two developed on separate but parallel tracks, which to some extent still continue today. For quite a few years, until the mid 1970s when the semiconductor memory became so capable, memory technology greatly affected the performance, capability, and cost of the computer system.

Early in the memory technology development, a split occurred. One technology family was developed for the program and internal data needed by the computer-which required fast access; and another was developed for less frequently used data which needed to provide larger capacity storage at a lower cost. This "external" storage class, mostly represented today by disk and tape storage, has seen dramatic improvements over the years. However, it is beyond the scope of this paper which will concentrate on the central processor and its internal memory.

#### **THE 1101 COMPUTER**

The 1101 computer is noteworthy since it was the first "1100". It was a commercial offering of a version of the first stored program computer designed by Engineering Research Associates (ERA) under a Navy contract and delivered in 1950. While this was only a 24bit machine with no actual commercial sales, it did provide an engineering learning base for the very successful 1103 which followed it. And the old timers like to recall how the commercial model number was chosen: 1101 is the binary representation for the number 13, the task number the Navy assigned to the original development contract.

# THE 1103 UNIVAC SCIENTIFIC COMPUTER

The 1103 was the first 1100 computer with significant commercial sales. It was introduced in 1953 as the Univac Scientific Computer. It set the standard for the 1100 36-bit word, although its internal organization was changed radically in later machines. Logic was done with vacuum tubes and crystal diodes, mounted on many "suitcase" chassis. A total of about 3900 tubes and 9000 diodes were required. Total power for an installation could be up to about 100 kilowatts including that for the air conditioner, chilled water supply and associated blowers. The recommended floor space was at least 58 by 30 feet for the 38,000 pound computer and its supporting equipment.

# Vacuum Tubes

Most of the 1103 vacuum tubes were triodes. A triode contains a filament which is heated by current passing through it and is placed close to a "cathode" which in turn becomes hot causing electrons to be emitted from a rare earth coating on the cathode surface. The negatively charged electrons are attracted to a surrounding positively charged anode or "plate". When a fine mesh termed a "grid" is placed between the cathode and plate, it acts as a control element. A negative voltage on the grid can greatly reduce the current going to the plate. Usually about 100 to 200 volts is applied to the plate, and about -20 volts on the grid can cut off the tube current. Two triodes were contained in one tube envelope, and this pair could make one flip flop. A flip flop, storing one bit of information could be set to a "one", cleared to a "zero", or toggled, i.e., changed to its opposite state. The later function was quite handy in certain logic and arithmetic operations. Capacitors stored the state of the flip flop for a short time so it would not toggle twice with a single input pulse. Another triode was usually connected to each flip flop output as a "cathode follower" (with

its output taken from the cathode rather than the usual plate). This isolated the output wiring load from the flip flop allowing it to change its state faster. The 1103 used about 12 types of tubes; the most common was the 5963 dual triode, an industrial version of the 12AU7, a common part in home television sets at the time.

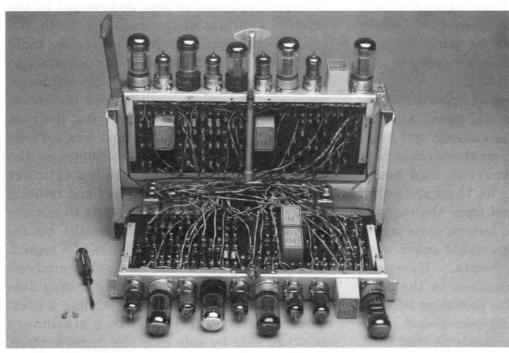

The 1103 "suitcase" chassis opened up easily for test and repair.

Another tube type that was available then was a pentode (so called since it had five rather than the three basic components of the triode). The pentode required less control grid voltage change for a corresponding plate current change and has two special grids. In a modified version, the 7AK7 dual control pentode, one of these grids was made to provide an extra control grid. Therefore, a fast two-input "AND" circuit could be made since plate current would flow only when both grids were positive. This provided the basis of the "gated pulse amplifier", widely used in the 1103 computer. One of the inputs was usually a narrow clock pulse, and the other a wider logic level from another output. Diodes were also used to form "AND" and "OR" circuits, but the pentode tube circuit was preferred for the narrower pulses. A pulse transformer containing one primary and two secondary windings on a linear ferrite core and potted in a special package was also a key feature of the gated pulse amplifier. The two secondary windings provided the option of either a positive or negative pulse for the output. The transformer also allowed the output to be at a different voltage level than the plate, thereby providing the level shifting needed with a vacuum tube circuit. (The plate would swing from about +100 to +200 volts, while the next grid needed values in the negative range).

Vacuum tubes had several known failure modes: the filament could open, surface particles could fall off the cathode and lodge between it and the grid; or, there could be a gradual loss of plate current, and hence reduced output signal, as the rare earth material became depleted from the cathode surface. Because of these factors, some people predicted large computers would never work for more than a few hours. However, conservative design practices in the 1103 proved to be quite effective providing 90 to 98 percent availability in a 24-hour period which was considered quite acceptable at that time. One thing that helped was testing periodically with lowered filament voltages. This reduced the tube currents and simulated end of life conditions on the weaker tubes so they could be replaced before they failed. Thus "marginal checking" was born and is still being used even though most modern parts do not fail often by gradual deterioration.

One additional new problem was seen in some vacuum tubes. If they were held in a cutoff condition for a long time, something happened at the cathode surface so that when the grid became more positive, plate current would not reach its full, normal value. Tubes were originally developed for the radio industry and did not operate in this cutoff mode, so the problem had not been seen there. This "sleeping sickness" problem was eventually solved by the vacuum tube manufacturer changing the cathode coating process.

# Magnetism for Memory

Magnetism played a strong role in early memory technology and still does for external storage such as disks and tapes. It seemed a natural for this since a magnetic surface could be magnetized in small areas with each region representing a one or zero determined by the relative positions of the magnetic north and south poles. Furthermore, these regions could be quite small, and no power was consumed to maintain their state. So the principles of magnetic recording, earlier used for audio, were applied to digital storage. But the time to retrieve the data from a tape was too long for the computer internal memory, so the magnetic drum was invented-a cylinder coated with an iron-oxide surface and rotating at high speed. The maximum time to retrieve any data from the drum would be its revolution time-a few hundredths of a second. Fine copper wires wound in a coil around soft iron cores formed the "heads" for writing data on the drum surface and later reading it back. These heads were placed in a stationary position, side by side near the drum surface. The direction of the current flow in the head

determined whether a one or zero was written. Reading was accomplished by sensing the direction of the voltage across the head winding caused by the small magnetic field around each region moving past the head coil as the drum rotated. ERA had some of the original drum patents. Early tests involved magnetic tape glued on a cylinder with one head used for each bit in the computer word. The track was one-quarter-inch wide, with a bit density of 50 per inch, and could provide "as much as 200,000 bits for a drum with a 34inch diameter and 10 inches long" according to a 1948 patent. Later, an iron oxide material was sprayed directly on the drum surface and bit density increased dramatically.

The 1103 used such a drum memory for program storage and provided 16,384 words with a parallel word access in a maximum time of 17 milliseconds. Many program steps are executed in a certain constant sequence, so the time from one step to the next could be much less than that for a drum revolution if they were stored physically on the drum surface in positions corresponding to their sequential use. However, this made programming difficult, and many times a branch occurred, so that the next program step could not be predicted. Also the sequence and location of the data to be read from memory could usually not be determined very well. A faster memory was needed-one that did not use mechanical rotation. Early 1103 machines used a form of cathode ray tube for this, known as the Williams tube. An electron beam was scanned across a phosphor-coated screen. A large current at a spot would charge it so that in the next scan sequence a small charge would temporarily remain and be sensed. The data had to be continually read and refreshed on a periodic basis. Each tube contained a 32 by 32 matrix and could store 1024 bits. The first five 1103 systems used a 1024-word memory of this type. A total of 36 five-inch diameter tubes were needed which took a considerable amount of space. This type of memory, while faster than the drum, proved to be unreliable and difficult to maintain. What was needed was a low-cost way to store and retrieve data in any random sequence with a short and uniform time delay for access. To answer this problem the ferrite core memory, using a new form of magnetics, was invented in the early 1950s.

The 1100 engineers were quick to seize on the benefits of the ferrite core memory and incorporated a 1024-word unit in the 1103 starting with serial number 6. Delivered in November, 1954, it is believed to be the first commercial unit delivered with a core memory. Beginning with serial number 10, the memory was expanded to 4096 words, and the computer was designated the 1103A. Most of the 1103s used this Random Access Memory, as it was termed, (spawning the acronym "RAM" still commonly used today to refer to this class of memory). This memory also needed vacuum tubes for its operation. The 4096-word unit fit into a separate cabinet and used 470 tubes and 2200 diodes and required about three kilowatts of power. At an engineering meeting in 1956, per bit costs of core memory with electronics were quoted at about \$1.25, with drum at three cents, and tape at 0.1 cent.

The 1103 computer system used clock pulses which came from a timing track on the drum and occurred every two microseconds. It is difficult to control the speed of a drum motor, so instead it provided the computer clock. The 1103A computer had an ADD time of about 30 microseconds and the memory had an access time of six microseconds and cycled at twelve microseconds. The 1103 sold for about one million dollars including the 16,384-word drum memory and a 4096-word core memory. An additional 4096-word core cabinet cost \$200,000. Later an enhanced version of the 1103 was designed and named the 1105. The major changes were a new buffered Input/Output (I/O) and an optional third 4K word core cabinet. (In referring to memory capacity, we will follow the convention where K equals 1024 and M or Meg equals 1024x1024 or 1,048,576). The central computer was unchanged. Combined deliveries of the 1103 and 1105 were about 45 machines.

### THE FERRITE CORE MEMORY

The core memory as first used in the 1103 was an ingenious device that was to last nearly 20 years in the industry and spawn entire organizations using special skills and techniques. The "cores" referred to tiny doughnut shaped rings (toroids) which were made from an iron oxide powder known as ferrite. These were fabricated using ceramic technology which consisted of grinding and powdering the material and mixing it with a binder which held the particles together. The material was then stamped into its final shape with modified pill presses such as those used to make aspirin tablets. Finally, they were fired at high temperature and individually tested for precise uniformity. The cores, used in the 1103A memory, measured 80 thousandths of an inch outside diameter and 50 thousandths of an inch inside diameter. Each core could store one bit of information, corresponding to whether the magnetization flowed in the clockwise or counter clockwise direction. Writing into the core was done by passing a sufficiently large current through a wire passing through the core, and this would create a clockwise or counter clockwise magnetic field in the core (depending on the direction of the current flow) and cause the magnetization, or lines of flux, to take the same direction. When the current was removed, most of the ferrite core, having a high degree of magnetic retention, would maintain its internal direction of magnetic flux.

Reading was accomplished by passing a current through the core forcing it to the zero state. Any change in the flux state of the core would be sensed by another wire passing through the core. A large flux change would mean that the opposite state, i.e., a one had been stored while a small change indicated that the zero state had already been in the core. The act of reading thus cleared the core to the zero state so

that after reading, a stored one had to be rewritten back to its original condition.

The other phase of the core memory opera-tion involved how it was organized into complete а memory and how a relatively small set of drive and sense electronics controlled a large number of individual cores. Each core had a threshold current that if not exceeded would not cause the core to

5

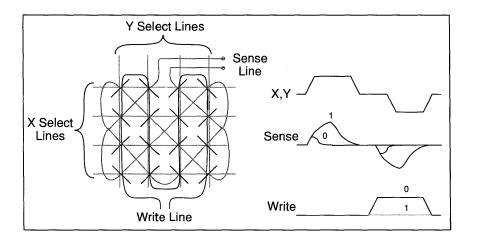

# **Core Memory Operation**

Coincident current core memory, four-wire arrangement and read/write current pulses.

change its magnetic state. But if it were exceeded by a relatively small amount, the core would switch to the opposite state. (The time to switch was inversely proportional to the amount of excess drive current applied). So the core actually provided both the functions of storage as well as a form of a two input "AND" operation.

If one wanted to build a 4096-word, 36-bit per word memory, for example, the person would construct 36 separate planes, each made from an array of 64 by 64 cores. These would be 64 X and 64 Y selection lines on each plane. By placing a "half-current", a value about 10 percent less than the threshold value, down any X and any Y line, only the core at the intersection would receive a magnetic field of sufficient magnitude to switch. A single sense line could link all the 4096 cores in each plane and detect if the selected core had switched. The sense line was wound in a special diagonal way so that each row and column of cores would give an opposite polarity voltage. This was important since the 62 half-selected cores each would generate a small, but reversible, magnetic flux change, and the summation of all of them would be larger than that from a single core switching. With the diagonal sense line, these small voltages would cancel. Actually, a half-selected one would generate a little more voltage than a half-selected zero. Consequently the "worst case pattern", the then familiar arrangement of checkerboard ones and zeros, would sense a net difference between each pair-the so called delta noise-and sense these pairs of differences. This combined delta noise could approach a full amplitude one switching. Fortunately however, this noise would die out before the switching was complete, which took a few microseconds. Therefore the sense amplifier output was strobed shortly after this noise had subsided.

The X and Y lines would be connected in series for all 36 planes. To accomplish this physically the planes were placed on top of one another, forming the "stack". This made a compact arrangement. The stack was difficult to repair, but this was quite an infrequent occurrence.

Each plane then had one sense line for reading. For writing another wire had to be included in each plane, so a total of four wires would thread each core. The write line linked all the cores by first flowing along one row then turning around and going back through the next row until all the cores in one plane were threaded. Writing was accomplished in the second half of the cycle. Either the data was rewritten back into the selected core, which had been cleared to zero when it was read out, or new data could be written in. This writing was accomplished by again applying currents down the same pair of X and Y select lines, but in a reverse direction. This would then switch the core to a one state. If a zero were to be written, a half-select current would be passed through the write line overlapping in time the X and Y currents but in an opposite direction. This would nullify the effect of one of the X-Y select currents, the core would not switch, and it would remain in the zero state. Since the write line acted by preventing switching, it was commonly called the "inhibit" line. Since the inhibit line drove all the cores in the plane, it coupled a great deal of noise into the sense amplifier-about 50 times an output signal-both when it was turned on and off. The sense amplifier had to recover from this large pulse before it could be ready for the next read operation. Drive currents required to switch the cores were several hundreds of milliamperes, and the core output voltage was about 50 millivolts.

In the case cited above, it can be seen that 64 X lines, 64 Y lines, 36 sense lines and 36 write lines-a total of only 200 lines-could control 64x64x36 or 147,456 individual cores. Furthermore, the 64 X and Y lines were usually driven by an eight by eight transformer-diode matrix. (A single transformer-diode was selected by an eight-driver, eight-enable combination. A separate diode and driver had to be used for each of the X and Y current polarities, but the transformer and enable driver could be shared). So one can see that a relatively few circuits could control a rather large number of cores. The larger the core memory was, the more efficient it became. This was particularly important when electronics costs were high as during the days of vacuum tubes and those of the early transistors.

### EARLY TRANSISTOR LOGIC

The transistor was invented in 1947 and by the early '50s was a prime candidate for computers mostly because of its smaller size and greatly reduced power consumption compared to vacuum tubes. These early units were made from germanium, one of the natural elements that exhibit semiconductor properties. They operated in the "bipolar" mode where current is amplified between the input and output. A relatively small current forced into the "base" would cause a much larger current to flow in the "collector". The third terminal, the "emitter", was usually grounded and carried both the base and collector currents. This operation was quite different from a vacuum tube where grid voltage was the control element, and no appreciable grid current was involved. The transistor also had the advantage of operating with a low collector voltage and thus acted as a very good "switch" to turn on and off signals. Furthermore, the output voltage from one transistor stage could usually be directly coupled to a following stage without the large voltage shift as was required by vacuum tubes.

Still, it took a while for the engineers to figure out the best circuit arrangements to use with transistors. At first, some people tried to copy the vacuum tube circuits with their pulses and transformers. (Cartoons were seen on some of the lab walls which showed a small three terminal tubular device under the sole of a large shoe; a caption read: "Stamp Out Transistors"). It later turned out that a simple direct-coupled circuit combined with diodes was a better approach.

One of the problems with transistors at this time was that their frequency response was less than tubes. To overcome this, more current than normally would be needed was forced into the base causing the transistor to turn on faster. However, when the current was later removed, the transistor would remain on for some time such as a large fraction of a microsecond. This delay was defined as the transistor "storage time". A larger "on" current would cause a larger storage time. This effect was minimized by providing a current in the reverse direction to turn the device off harder. The turn-off current sometimes had to be nearly as large as the turn-on value. Improved transistor construction finally reduced this effect, but this took a number of years.

Early transistors were quite expensive and delicate. There was also some concern about their long-term reliability and ruggedness. One competing and attractive technology at the time used low cost magnetic switch cores. These were cores made from a ribbon of permalloy, a magnetic iron-nickel alloy, wrapped on a small bobbin and then wound with several windings. The windings could be connected to inputs, an output, or a clock pulse. The power to operate a logic circuit came from the clock which would force the core to a cleared state. A switching output voltage would indicate that a one state had been stored and would cause a following core to switch. Since read out of a switch core cleared its state, a two-phase clock was needed. Data from cores clocked on the "A" phase would be captured by cores which would be clocked at the "B" phase and vice versa.

In order to evaluate these approaches, two

internal test vehicles were built in the mid '50s: the Magstec, using the magnetic technology, and the Transtec using transistors. Both were built and evaluated; the transistor technology version was used for most applications after this. Some notable non 1100 exceptions in the company were smaller computers developed for early business applications. One was the Solid State 80/90 designed in the Philadelphia location, and the other was the File Computer designed in St. Paul. These combined tubes, magnetic logic, and some transistors.

The first all-transistor computer built by Univac was the Athena, a computer design starting in 1956 for the Air Force which was used for missile guidance. Small diodes were also readily available then. The basic AND-OR logic was done with the diodes; and the transistors provided the amplification, or gain, between stages.

In those days, the companies that manufactured vacuum tubes were the first to market transistors. Philco made one of the faster transistors, using a process termed "surface barrier technology" or SBT. The SB100, as it was called, was the fastest transistor at the time, but it could not handle much current and had a low voltage rating. General Electric made an "alloy junction" processed device, the 2N123, which was slower, but huskier, and could handle more current. The Athena computer used both of these in each logic circuit, the first to provide the voltage gain, and the other to provide current gain and drive the logic loads and wiring capacitance on the output. The Athena computer exceeded all availability goals by a large margin, and proved the reliability of transistor technology. Transistors improved substantially over the next few years in performance, current and voltage handling capability, and cost. In a short time they could even accommodate the higher currents and voltages needed by core memories. Vacuum tubes quickly faded from most computer designer's minds.

# COMPANY SITUATION DURING THE LATE 1950s

Before we cover the technology for the next 1100, it would be helpful to discuss the situation in the St. Paul Development Labs at this time. (The Roseville Plant was not occupied until later in 1961). There were many and various computer and memory projects then. Most of them were funded by one of the government agencies who set the technical objectives for the work. The corporation was now Sperry Rand, and there was a sister organization in Philadelphia also developing computers but with less government work and with designs more geared to business needs than scientific. At about this time the Lawrence Radiation Laboratory at Livermore, California solicited proposals on the next generation of a high performance computer. The St. Paul and Philadelphia groups submitted competing proposals. St. Paul, being conditioned by the Navy which stressed reliable and maintainable equipment, submitted a more conservative design; the Philadelphia design was much more ambitious in both its technology goals and in the logic organization, and promised much more performance. The contract was fixed price, and the customer selected the higher performance machine. This computer, the LARC, proved quite a challenge to complete. It was never delivered to any users besides Livermore because of its high costs. It is believed that the existence of LARC probably delayed the starting of an alternate follow on to the 1103. Besides the Athena computer mentioned earlier, other non 1100 significant developments in this time period included the Naval Tactical Display System (NTDS), which was later commercialized as the 490 Real Time System, and which then spawned the 494 Product.

The Process Control Computer, developed for an industrial customer, formed the foundation for the 418 System which led to its own follow on family. Many of the engineers who designed the later 1100 products had earlier worked on these and other commercial and government computers of various types and gained by this experience.

### **THE 1107 COMPUTER**

The 1107 computer development started in the late 1950s and was announced in December, 1960. It maintained the 36 bit word length from the 1103, but otherwise was quite new in its organization and set the basic architecture for future 1100 machines. A key feature of this is the GRS or General Register Set of 128 words. In the 1107 this was called the Control Memory and was constructed from a new type of magnetic memory fabricated from deposited thin films which will be described in more detail later. A number of companies had been working on film memories including IBM and Burroughs, but this was the first commercial computer to employ them. The company

played up this new technology, and in fact named the system the 1107 Thin Film Memory Computer, with this name appearing on the operator console. In a **Business Week article** dated December 17, 1960, it was stated that the news leaked out about this new computer, and the company stock became the most active on the New York Exchange. Stock Following this, the Exchange asked the

company to announce the product earlier than had been planned, the article said.

# Logic Technology

The basic 1107 logic circuit used transistors, diodes, and resistors. They were mounted on small plug-in printed circuit cards measuring about three by four inches. About 20 variations of these were needed to perform all the computer and I/O logic. An edge connector with 22 contacts was used. These cards plugged into molded connector blocks, each holding eight cards on 0.5 inch centers. A five by five array of these blocks formed a deck holding up to 200 cards. A bay consisted of four decks arranged vertically. Four bays in a "U" shape then made up the computer complex. The film memory used two decks, and the remaining fourteen-with 2800 card locations-were available for the processor and the input/output function for the entire system. Wire-wrap technology, a very reliable technique that had been developed by the phone company, was used to interconnect the cards. It was interesting to note that in this type of design the complete personality of the computer logic was determined by what card

A 1107 logic card plugged into a section of the connector block.

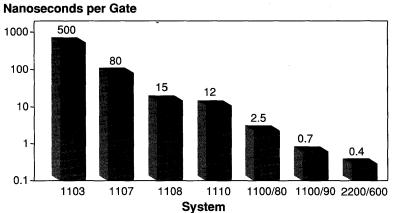

types were plugged into which slots and the wire wrap interconnection on the backplane. Logic design changes could be easily incorporated by changing the backplane wiring and perhaps a card type change in a few slots. The logic delay per stage was about 80 nanoseconds, although it could vary greatly with the length of the wires driven by a given circuit. An innovative feature of the 1107 logic technology was a transformer-diode shift matrix which was important in accomplishing certain arithmetic functions.

# Core memory

Ferrite core memory technology progressed rapidly during the late 1950s, and better transistors and diodes became available for handling the larger currents. The 1107 core memory was large enough to handle both active programs and data so that a drum was not needed for this function. Cycle time was reduced to four microseconds. To further improve performance, it was organized into two separate banks. Every two microseconds, one bank containing the program, or the other containing the data, could be referenced. The entire memory of 65,536–36 bit words fit into a 36-inch wide, 84-inch high cabinet. Since the memory was still fairly expensive, smaller capacities in 16,384 word increments were also available. The core plane contained 4096 cores each measuring 0.050-inch diameter. Pulse transformer and diode arrays were mounted at the end of the core stack to provide the X and Y current selection. Since the memory cores were somewhat temperature sensitive, the drive currents had to be compensated to adjust for the computer room environment.

# Thin film memory

As mentioned above, the 1107 also featured a new, fast type of memory made of small dots of thin magnetic film. It was a small memory of 128 words but cycled at about 0.67 microseconds-six times faster than the core memory. Its function was to store frequently used control words and local registers for the arithmetic and logic sections, so it was important that it operated at a speed close to that of the logic circuits. The access time was half of the cycle time-about 0.33 microseconds. The use of this small high speed memory had a lasting impact on the 1100/2200 architecture and certainly improved its performance.

The 1107 was the first commercial computer to use a thin film memory. (MIT Lincoln Labs built a smaller one earlier). It represented payoff from about seven years of R and D when it was announced. Many companies other were also working on these types of memories. Film was a competitor to the core memory. It was made from a thin film of iron-nickel

A close up view of the 4096 bit 1107 core memory plane using 50 mil cores.

composition deposited in a vacuum through a mask used as a stencil which formed an array of small spots on a thin smooth glass substrate. This was done in the presence of a magnetic field which produced an axis of preferred magnetization in the plane of the film. The magnetization, which represented the two stored states, could be switched to point either parallel or anti-parallel to this direction. All magnetic flux paths must close back on themselves. The path in the thin film had to close through the air and surrounding material which was non-magnetic. Since it is harder to push these flux lines through a nonmagnetic material, a back magnetic force results which has a direction opposite to the original flux lines and attempts to demagnetize the magnetic material. Because of this, the film had to be kept thin which reduced the flux and associated demagnetizing force. (The ferrite core did not have this problem since the flux lines were circular and closed inside the core itself). Because of this limitation, thin film had an output signal about one-tenth that of a typical core.

Writing and reading were accomplished by placing the glass substrate between etched planes of copper conductors which had been laminated onto thin Mylar layers and bonded together. The thin film memory promised lower cost since many storage elements could be made in one deposition, and since the difficult job of threading several wires through a core could be eliminated. It turned out also that film switched from one stored state to the other much faster than core. So it appeared that film could become the next generation of computer memory and the 1107 version was just the beginning. However, the engineers that had to work with these elements knew of the new problems that films introduced that had to be solved before they could fulfill their promise of having all around superior features.

Earlier, the company had designed an experimental model of 1024-word, twomicrosecond memory and reported on this in 1956. It used the same coincident current scheme as cores. However in the construction of the test vehicle it was learned that the uniformity of the magnetic properties of all the individual film elements varied too much for reliable operation. Consequently, the next film memories developed used a linear selection scheme. Instead of the desired word being selected by the coincidence of two pulses, it was directly selected by a full current which could be made large enough to switch all the elements on a given glass substrate. Sensing and writing were accomplished by using conductors flowing at right angles to the word lines. These linear select or "word organized" memories were more costly because of increased driver/selection circuitry, but in a small memory such as that on the 1107 this was not a significant item. The 1107 thin film elements were vacuum deposited onto two-bytwo-inch, thin glass substrates. Each contained a 16 by 18 array of 0.05-inch diameter circular elements. The magnetic elements were only about four millionths of an inch thick. Four arrays were mounted on planes and four planes comprised the entire memory.

The 1107 was scheduled to be delivered in December of 1961, but was delayed until mid 1962. It was technically a successful product and operated well in the field although only about 38 of the units were sold. During a similar time period, about 60 of the 490 systems were delivered.

# TECHNOLOGY DEVELOPMENT IN THE EARLY '60s

Technology development in the early '60s was diverse and rapid. Many new ideas were proposed and some were used in products. Transistors became faster and less expensive. A major innovation was the invention of the integrated circuit which placed many transistors and resistors onto a single piece of silicon, or "chip" as it became known. Originally these devices were quite simple, perhaps one flip flop; their performance then was inferior to that which could be obtained with separate transistors and diodes. But progress was steady, including determining what functions should be performed by the circuits contained on the chips.

Printed circuit board technology was also key for a means to mount and interconnect the components. The company has had a strong printed circuit board development and manufacturing capability since the 1950s. The company also developed special techniques for manufacturing ferrite cores and assembling them. Work continued on improving the magnetic film memory, and a new large continuous production line for film deposition was installed. There were several applications by the company using film memories for military computers during the 1960s. One noteworthy example involved a concept termed "Mated Film". This was a clever idea that produced a very compact and rugged stack with excellent temperature characteristics and operating margins. Both the films and a common write/sense line were deposited on the substrate. There was a pair of film spots for each bit-one on each side of the sense line. This helped close the flux path and improved the operating margins substantially. Holes were etched in the substrate to accommodate a diode lead that was used for word selection. The word lines were merely the diode leads that passed perpendicularly through the planes. This novel arrangement meant that no connections had to be made between planes so they could be placed very close together. Manufacture of this type of memory actually continued through the late 1980s for a number of military computers requiring relatively small, compact memories. However, magnetic film memories never really fulfilled their

promise in the commercial computer area even though many large companies devoted extended efforts to this technology. The principal reason was that core memory stacks costs dropped considerably more than anyone had anticipated, and that film memories needed more costly electronics with their requirement for word organization and the rather small output signal. In addition, even though the films switched faster, the delays in a stack and the electronics diluted this. As cores became faster, there remained less than a 2:1 difference in the speed of the two technologies, not enough to warrant the cost differences. And as customers demanded larger memories, the cost factor became more important.

Many other magnetic memory approaches were proposed during this time by various people and companies in the industry. Some of these were the ferrite sheet, transfluxor, the biax, magnetic rod, twistor, and waffle iron among others. None of these were used to any great extent in general purpose computers. One exception was the plated wire, but we will cover that more a little later. During this time the first semiconductor memories were proposed. The ones made then were quite small and quite expensive, although they were fast and simple to design with.

### **THE 1108**

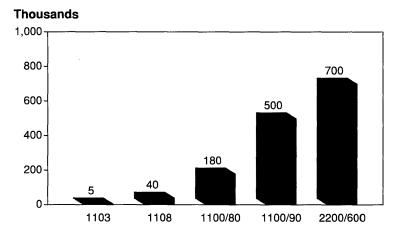

The 1108 system was announced in 1964 and delivered in 1965. It was to be the most successful 1100 system until its time and the first multiprocessor system. Its technology was evolutionary but with considerably faster parameters combined with an efficient logic organization. The 1108 performance exceeded that of the 1107 by about four to five times.

### Logic Technology

At the time that the 1108 technology selection was made, integrated circuit logic still wasn't fast enough, so transistor-diode logic using the latest devices was used. The germanium transistors were replaced with those made from silicon. "Two level logic" was chosen which meant that both an AND and an OR logic function using the diodes could be done before passing through the transistor amplifier which now consisted of two transistors in an arrangement similar to the earlier Athena computer. Logic card size was increased to five by seven inches with 55 I/O pins. Cards were on close 0.3 inch centers, and a total over 900 were used for the processor and the I/O section. The number of card types was increased, but the idea of general purpose cards with the real logic in the wire wrapped backplane-similar to the 1107-remained. A high fan out driver was added to the logic family. It was able to drive many internal loads and long backplane wires, and contributed to simplifying the machine design and aiding its performance. The typical logic stage delay was reduced to 15 nanoseconds, and the clock cycle time came in at 125 nanoseconds.

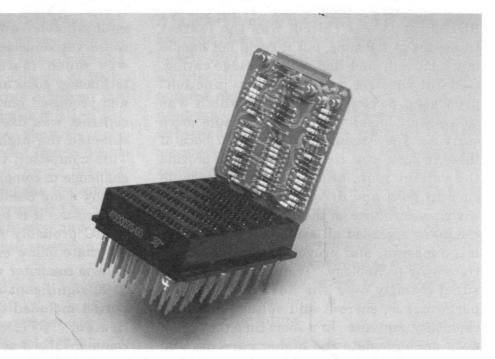

memory in that simultaneous reading and writing from two different addresses was possible. Its cycle time was reduced to 125 nanoseconds. Sixty four chips in circular cans were mounted on a standard logic card together with other supporting components. A total of 127 cards were needed to provide the complete GRS function which became the performance limiting section of the processor complex.

The ferrite core memory cycle time was reduced to 750 nanoseconds-over five times faster than the one in the 1107. This was brought about by the use of a smaller, faster 23 mil core and a new "2-1/2 D" organization. In this new organization the Y select drivers were duplicated for each bit so that if a zero were to be written, the corresponding Y current would merely be left off. This meant that the inhibit line could be eliminated, reducing the large noise generated after writing. It also meant that only three wires

were needed, allowing a smaller, faster core. The cost of doing this was to require 36 sets of Y lines, one per bit, rather than only one set. The reduced cost of transistor drivers minimized the impact of this. Furthermore, each "plane" was made "non square" decreasing the number of Y lines per bit and increasing the X lines but minimizing the total number of drivers. This also reduced the back voltage on both X and

The 1108 logic card; It was in production for 15 years.

An integrated circuit containing one bit of storage was used to perform the GRS function that the film memory had done on the 1107. Its function was enhanced over the thin film Y lines since they drove fewer cores and allowed a planar type stack which reduced interconnections between planes as well as manufacturing costs. One of the concerns at this time was the self heating of a core which would occur if it were switched repeatedly at this fast cycle rate. While repeating one address for many successive cycles would be quite unlikely, the core switching threshold varied with temperature, so if there were heating it might cause a problem. Logic was added to detect this and cause a slight slow down in the rare event such would occur. Another problem with some cores at this time was that they were magnetostrictive. This meant that mechanical stress applied to the core would cause a change in its magnetic properties. It also meant that the switching of a core would physically stress it. Consequently when a core was switched, a shock wave starting from its inner diameter would propagate to its outer diameter edge. Then it would be reflected back in a wave action and proceed to the inner edge where it would be again reflected back out. Normally the effect of this would be quite small. However, if the core were switched at the same frequency corresponding to the round trip delay of this shock wave, a large reinforcement action would occur which might cause a read out error. This problem was usually controlled by picking the right core material and covering the cores with a light spray coating which absorbed most of the shock wave. The coating also prevented the core from rubbing on the wires as a result of vibration caused by cooling fans or other sources.

The 1108 was quite large by today's standards. The processor required a 64-inch wide, 64-inch high cabinet with a separate 36-inch cabinet for power and maintenance. A 65,536 word memory, organized in two banks, took a 48inch unit plus another 36 inches for its power supplies. The original 1108 was delivered in 1965. Enhancements were made soon after allowing multiprocessor capability with up to four memory cabinets for a total of 262,144 words of storage.

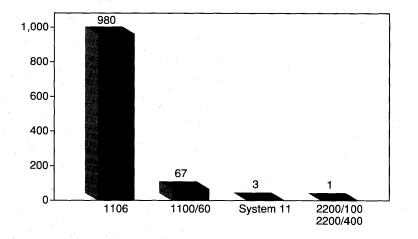

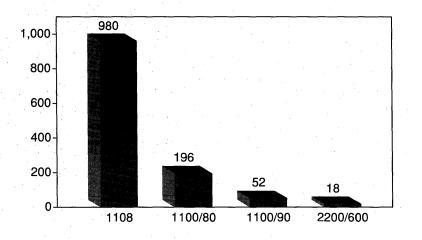

# 1108 Product Enhancements

In about 1969, a slower version of the 1108 with a 1.5 microsecond, 128K word, less costly core memory was introduced. It was named the 1106, and expanded the usage of the 1100s to users who did not need the full power of the 1108. It became a very popular system. Later on in the early 1970s when semiconductor memory technology became cost competitive, the core memories in both were replaced with semiconductor technology and the maximum system memory was doubled to 524,288 words. The GRS chip was also replaced with a more advanced version containing 256 bits. There were no 128 bit versions made, so only half the address locations were used in each chip. The number of printed cards needed for the GRS function dropped from 127 to only 15. The resulting lower cost machines were repriced and renamed the 1100/20 and the 1100/10 with active production continuing until the late 1970s. The 1108 including its enhanced derivatives was one of the most successful computer systems ever developed and greatly expanded the base of loyal 1100 users. Approximately 1000 of these computers were manufactured and delivered to many installations around the entire world.

#### **THE 1110**

### Background

The 1110 system was the next 1100 machine. Its development started in the late 1960s, and it was announced in November, 1971. At its inception both it and the 1106 were planned as extensions to the 1108 family with the objective of extending the performance range to both higher and lower levels. The 1106 as mentioned above came out earlier, since it did not need a new processor but only a new memory. The 1110 objective was to get a machine out in a short schedule with low technology risk yet providing two or more times the performance of the 1108. By this time integrated logic circuits had progressed sufficiently so that they were faster than separate transistors but not by a large amount-only about 25 percent. In addition to this, core memory technology was benefiting from minor cost improvements, but it was difficult to improve their speed very much unless quite small modules were used. But they would be more expensive since the supporting electronics would be prorated over fewer storage bits. Under these conditions how was the 1110 to meet objectives? Part of the answer was to improve the processor performance by increasing the "overlap", or the number of instructions being concurrently executed. While this would increase the amount of logic in the computer by a large factor, the denser and less expensive integrated circuits should accommodate this. In addition, it was felt that more improvement could be obtained at the system level by a more efficient organization.

This was to be accomplished in three principal ways:

(1) The main memory would be broken into two sections. One would be of less capacity but faster, and the other would be larger and operate slower.

Integrated circuit logic speed had improved

significantly and the cost projections became

Logic Technology

significantly and the cost projections became favorable. A type of circuit termed TTL which stood for Transistor-Transistor Logic was becoming standard in the industry. The TTL circuit operated a lot like the diode-transistor circuit everyone was already familiar with. In integrated circuits, transistors are as easy to make as diodes and provided a little better operation. A new standard package adopted by the industry, the dual-inline package, or DIP as it became known, was used. A total of 14 leads at 0.1-inch spacing left two sides of a rectangular package. While the circuit delay only went down to about 12 nanoseconds (from 15 for the 1108), it was felt that the capability of the higher density, lower cost technology would allow the use of additional logic, and thus help performance by producing more concurrent operation in the processor.

The original plan called for a printed circuit card connector having about 100 pins. However since excellent experience was had with the 1108 printed circuit card and its connector, it was decided to continue its use in the 1110. Hindsight indicates this was

(2) A separate Input/Output or "I/O" section would be used to offload this function from the central computer which was now renamed the "Instruction Processor" or IP. (3) The number of processors that could be connected in a multiprocessor system was also increased to four and later to six.

The 1110 was the last system to use separate wires on the backplane.

probably a mistake since the 55 pins were not sufficient to support the 30 integrated circuit logic chips, each with 14 pins, that fit on the card. Many cards were half filled, and about 1050 cards were needed for the entire processor. This integrated circuit also had less noise immunity than the 1108 circuit which forced the addition of considerable twisted pair wiring in order to limit signal crosstalk in the backplane wiring.

Another difficulty in developing the 1110 was the fact that much of the logic personality moved onto the printed circuit wiring where it had been in the easily changed backpanel on the 1108 with its simpler, general purpose cards. This caused the number of unique card types to increase to about 400. It consumed considerable time to layout the interconnect on these cards. Also, many of the design changes arising during computer test required changes to the printed circuit card layouts. All of these factors and the more complicated design with the extra logic caused the development schedule to be delayed from the plan.

# words, while up to four cabinets of primary memory were allowed.

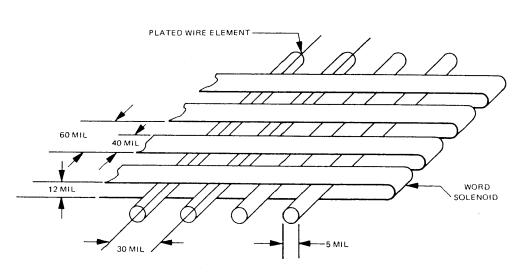

The plated wire memory concept was originally described by Bell Labs at the 1958 Magnetics Conference, and the company became interested in it as having some of the performance benefits of magnetic film, but with lower cost potential and larger output signals. The idea was quite simple: A permalloy, or iron-nickel, alloy of the composition used in magnetic film was plated onto a small copper wire in a continuous fashion as the wire passed through an electroplating bath. Direct current was passed through the wire during plating to force a preferred direction of magnetization to be in the circumferential direction. This has the advantage of a closed flux path allowing the magnetic material to be about 10 times thicker than had been used in the thin film memory in the 1107 and resulted in a larger, easier to use output signal.

# Memory Technology - The Plated Wire Memory

The 1110 used two levels of main memory: A 1.5 microsecond "Extended" memory-the core same 128K word memory that the 1106 used-and a higher speed 64Kword plated wire memory for the "Primary" storage which had a 300 nanosecond read cycle time. A maximum of eight cabinets of extended memory could be used providing one million

To make a memory, one merely wrapped a oneturn word line strap around a group of wires. To write, a large current was passed through the word strap, and a small current was driven through each plated wire. A positive wire current wrote a one while a negative current wrote a zero. For reading, the same word current as writing was used, and it produced a positive or negative signal across the wire depending on whether a one or zero had been stored there. Since the magnetic field produced by the word strap was parallel to the wire and thus perpendicular to the remnant flux (which was circumferential around the wire), read out did not change the state of the stored data. This provided a "Nondestructive Readout" or NDRO operation. As a result, rewrite was not needed-as it was in a core memory-following a read operation. This meant that the read cycle time could be faster than a write cycle since it did not have to recover from write current noise. This was important since normally about 80 percent of memory operations involve reading.

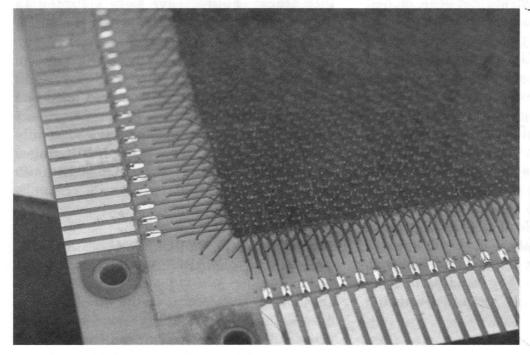

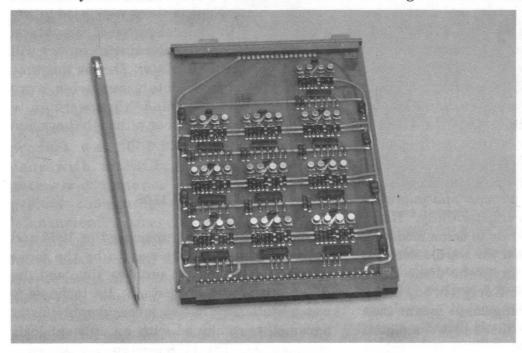

Earlier the company introduced a small byte organized processor, the 9200, which contained an 8K byte plated wire memory module, the first to be used in a commercial product. This created a lot of interest in plated wire memory technology around the country, and many companies began a program to evaluate this technology. While the 1110 memory used the same plated wire, the memory stack was larger at 8K words. The plated wire was only 0.005 inch in diameter, placed 0.03 inches apart. The word straps, running at right angles, were on 0.06 inch centers. Each module of 8K words had its own stack and complete memory electronics. The read cycle time was about 300 nanoseconds while the write cycle was 500. Eight of these were mounted in a 64K word cabinet, and up to four of these could be used in a full system. All modules could be operated concurrently. This small module of 8K words helped performance in a multiprocessor system since it reduced the chance that different processors or I/O units would request data from the same module and have to wait.

A multiple memory adapter (MMA) in each cabinet provided an interface between the requesters and the eight modules. It provided a crossbar switch function and also resolved the priority in the event that two requesters wanted simultaneous access to the same module.

Like many new technologies, plated-wire memory had some problems that the early developers had not envisioned. For one thing it was somewhat strain sensitive. Handling and soldering it to its connections could change its magnetic properties. A more serious problem, also seen in thin film memory, was that repeated writing in one bit location could cause a neighbor to partially lose some of its stored flux and give a smaller signal when later read out. This "disturb" problem was difficult to solve and took considerable experimentation to determine the sequence of reading, writing, etc., so that the wire could be properly tested in the worst case mode before it was assembled into a stack. The plated-wire memory proved more difficult to manufacture than was envisioned and did not reach its cost goals. But even if it had, both wire and core memory were being rapidly overtaken by an offshoot of the integrated logic technology - i.e., semiconductor memory. The 1110 was the last 1100 machine to use magnetic main memory. And in fact, both the wire and core memory on the 1110 system were later replaced with semiconductor memories at lower prices. The renamed system, the 1100/40, also offered twice as much primary memory for a maximum of 512K words.

# 1110 System

The 1110 hardware took more floor space than the 1108. This was principally because separate cabinets were needed for the I/O, and the two types of memory each had their own. A "4 X 4" system (four IPs and four I/Os) required an area of nearly 900 square feet. The first 1110 systems were delivered in 1972, and over 400 processors were manufactured in the next few years.

### SEMICONDUCTOR MEMORY

Using transistors to make memory elements began in the late sixties as the number of components fabricated on the integrated circuit chips increased sufficiently. At first these were limited to quite small memory applications such as register files or like the chip used in the GRS for the 1108 as mentioned earlier. They used similar bipolar transistors as were used for logic and were quite fast. While these were still much too expensive for main memory, they did allow a new memory organization concept to be adopted-the cache memory. The idea behind the cache memory was to have a small, fast memory store the contents of every word read from the larger main memory as well as its adjacent neighboring addresses that shared a

common block of perhaps 8 to 16 words. Studies of address sequences had shown that any address requested was likely to be in the same block as the preceding one requested. So if a number of such blocks were stored in the small high speed memory, a large portion of the time the processor could get the data from that memory and avoid going to a larger, slower unit. This concept was a significant development for computer organization and removed the demand for a large, fast, and low cost memory all in a single technology.

The second significant development was the MOS (Metal-Oxide-Semiconductor) transistor. It was also known as the Field Effect Transistor or FET. This type of device was smaller, denser and less expensive to fabricate than the bipolar transistor. Its lower speed was still sufficient for main memory especially if a cache memory were used. The MOS transistor operates by an electric voltage that is applied to the "gate" which controls current flow between the "source" and the "drain". A thin silicon oxide insulator separates the gate from the rest of the device, and no gate current is needed in operation. Interestingly enough,

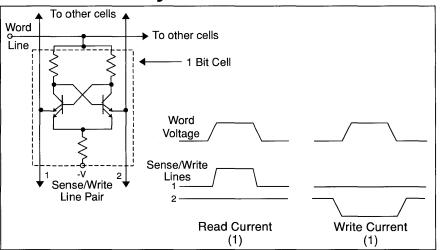

# Bipolar Semiconductor Static Memory Cell

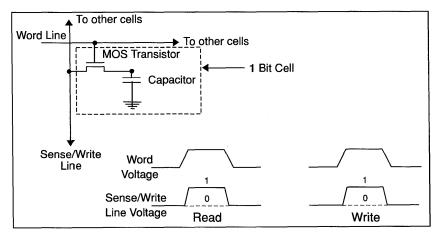

the MOS electrical behavior was similar to a vacuum tube pentode, but with much reduced voltage and power levels. Early MOS memory chips stored 256 bits, but were not used widely for main memory. Industry interest perked up when the 1024-bit device came out early in the 1970s. It had two major innovations. First, address decoding circuits-those that

The bipolar semiconductor memory cell; its fast speed made cache memory feasible.

take the word address and select one each from the 32-word (row) lines and 32-bit (column) lines inside the chip-were duplicated on every chip. While this made the chip about 30 percent larger, it reduced the leads needed for addressing from 64 to only 10 which made the chip package much smaller. The second idea was to use one transistor and a small capacitor for each storage bit rather than the four to six transistors normally needed to make a flip flop. The capacitor stored one bit of data represented by the presence or absence of a voltage charge. The transistor acted as a switch to set or sense this voltage. This produced a very small memory cell. No current in the cell existed except very low leakage currents. Even a very small capacitor could maintain its voltage charge for many milliseconds. Refreshing to restore the charge was required periodically, but since 32 bits could be refreshed in parallel, only a small fraction of the time had to be used to do this. Designers quickly found ways to incorporate the refresh function into the computer timing with minimal impact.

One of the concerns with early semiconductor memory technology involved their reliability, since there were so many components and connections inside of each chip, and since quite a few chips were usually needed to make a complete memory. Since each chip read out only one bit for each read operation, single bit error correction was usually used especially in larger memories. In error correction extra bits are added to each word. For example a 36-bit word requires seven additional bits for error correction. During writing these are set based on the parity of various combinations of the 36-bit data word. Later when this word is read out, if any bit has changed, including the added bits, an error syndrome is formed from again parity checking the combinations. This error syndrome uniquely identifies which bit has changed, and the logic merely changes it to the opposite state. If two bits are in error, they cannot be corrected, but their presence can be detected. This scheme works well with semiconductor memory when each chip is only one bit wide. Then, any number of bits in a chip could fail, but no more the one bit for any address selected would be involved, and the

> error correction circuitry will correct it.

Another early with concern semiconductor memory arose since their data was "volatile". This means that when power is removed, the stored data is lost. Magnetic memory such as core and plated wire could retain their data with no power applied. However, most users did not rely on this feature

# MOS Semiconductor Dynamic Memory Cell

in these random access internal magnetic memories, and most of these memories were not designed to prevent incorrect writing during a nonscheduled power loss anyway. Backup to drum or disk was normally done, so this concern with volatility seemed to be short lived for most commercial applications. In very critical systems an uninterruptible power supply would probably be chosen.

The original 1K MOS memory devices were somewhat difficult to design with and required 20-volt power supplies and special drivers. Also, the core memory costs were still dropping. But when the 4K bit device came out about three years later, these design deficiencies were corrected. Standard five-volt drivers could be used, and the reduced cost per bit-due to the better than expected chip yields-put an end to core memory and other magnetic memory for almost all new commercial products. Second generation 4K devices added another feature-address multiplexing. Normally 12 signals would be needed to select an address for a 4096 by 1-bit chip. With address multiplexing, they were gated onto the chip, six lines at a time, cutting the address signals in half and reducing the package size. While multiplexing slowed the cycle time somewhat, the design community thought the tradeoff was well worth it since it allowed more chips to be packed on a printed circuit board.

The semiconductor memory technology continued to develop very rapidly after this with a new generation coming out about every three years and having four times the capacity of its predecessor. No longer was the main memory such a limiting part of the computer system. Let us return then to what was happening in the area of technology for the computer logic for the next generation of products.

### **THE 1100/80**

Work began on the 1100/80 technology well before the 1110 system was completed. The objective was to get substantial performance improvements over the 1110. The solutions used were well conceived and set the basis for technology direction for the high end of the 1100 Series for sometime in the future. The major items involved an "ECL" type of logic circuit, controlled impedance printed circuit boards and backpanels that used automated design and layout to strict electrical rules, use of a cache memory organization, and a semiconductor main memory.

# **Controlled Impedance Printed Circuit Cards**

Experience on the 1110 had shown that if its circuits had been any faster. the interconnection and wiring between the chips would have become a limitation. The fastest electrical signals can travel is equal to the speed of light, or about one nanosecond per foot in free space. However in most wires and printed circuit boards the insulation material has a dielectric constant higher than free space, slowing the signal down to about two nanoseconds per foot. While most wires between chips were only a few inches, lengths of a couple of feet were not unusual. Faster chips were now switching in a few nanoseconds and getting close to the limits of interconnections. But the added delay at this time was not the most serious problem. A bigger problem was due to reflections and crosstalk which could produce noise and errors in the logic signals if not treated properly. The logic circuit and interconnection wires became part of a complex circuit that had to be treated as a single entity. Formerly the wiring was considered as a load on the logic circuit that looked like an electrical capacitor with a value that was proportional to its length. This was all right for the slower circuits. But as the transition time of the faster circuits approached the transit time of the interconnecting wires, new problems were encountered.

All wires have a characteristic impedance which is determined by their distance to other conductors in the region and the dielectric constant of the intervening space. If one applies a fast voltage pulse to one end of wire, a current will flow in the wire that is independent of what is connected to the other end of the wire-in fact it takes about two nanoseconds for each foot of wire before the far end "knows" that any voltage pulse was applied. The current flowing in the wire is proportional to the size of the voltage pulse, so the ratio between the voltage and the current is constant. This ratio is the "characteristic impedance" measured in ohms (since this is similar to ohms low for dc currents). The voltage pulse and its associated current pulse begin to propagate down the wire as a wave front. Now, if the far end is open with nothing connected to it, the current must be zero there even after the wave front arrives. This creates a discontinuity which then starts another wave that propagates back to the source, where it turns out another discontinuity can occur, and the signal will bounce back and forth many times only being reduced by the small losses in the wire and dielectric material. If the far end had been shorted, the voltage would be zero there, so another type of wave is propagated back to the source, and a similar thing occurs. Now if a resistor having a resistance equal to the characteristic impedance is connected at the end of the line, the current and voltage will maintain their proper relationship when the wave front arrives at the resistor. The wave front is thus completely absorbed, and there are no reflections rattling back and forth. We have a quiet line. (If the resistor is a little different than the characteristic impedance, the reflection is calculated by taking the difference between the two, divided by their sum. So a ten percent difference gives only about a five percent reflection which is usually quite tolerable).

So for fast moving logic signals traveling over

reasonable distances, the wires now had to be thought of as transmission lines. Most logic circuits outputs usually had low resistance so they could drive many loads well. Their inputs had high resistance so they would take less current and be easy to drive. This is the worst combination for a transmission line interconnection. Signals could bounce back and forth several times between two logic circuits before the signal settled to its proper level. So a wire with only a two-nanosecond one-way delay would take 16 nanoseconds for four 2-way trips! The engineers would say, "It isn't the delay that kills you, it is the ringing".

The other problem with the wiring was crosstalk between neighboring wires on a printed circuit board or in the backplane. If

The 1100/80 multilayer card and backpanel technology had many innovations.

one conductor was driven with a signal, it would induce a small voltage on its neighbor through capacitive (voltage) and inductive (current) coupling. This noise from several wires all passing signals at the same time could add up on a nearby single "quiet wire" and cause an error. Twisted pair wire, with one of the wires grounded, helped this quite a bit, but this was quite expensive and not completely effective, especially at the higher speeds.

What was needed was an interconnection wiring scheme that provided a controlled characteristic impedance and also limited the crosstalk to acceptable levels. The answer was a precision multilayer printed circuit board and backpanel technology. The latter would replace the wirewrap backplane that had been used. All interconnections between points had to be made by using a grid of X and Y lines running at a 90 degree angle between each other. (There is almost no crosstalk between perpendicular crossing wires). Each pair of X-Y lines was contained between a pair of ground (or voltage) planes which shielded them from the other pairs. The only crosstalk concern was from the parallel, adjacent conductors, and this could be easily controlled by varying the distance between the adjacent conductors relative to the distance to the ground planes. A smaller distance to the ground plane reduced the crosstalk, but it also reduced the characteristic impedance which would demand more current from the logic circuits and increase system power. The final design used 0.008 inch wide lines, with 0.012inch separation, and a distance to the ground planes that gave a 50 ohm characteristic impedance and only a few percent crosstalk.

# ECL Logic Circuit and Automated Card Layout

The selection of this new controlled impedance interconnect had a lot to do with the choice of the new logic circuit for this technology. TTL devices, such as those used by the 1100 and quite common in the industry, had a 3.5 volt logic swing. If they were to drive the 50 ohm interconnect, which had to be terminated at the end with a 50 ohm resistor, 70milliamperes per output would be needed. The TTL parts couldn't drive this much current, and if they were redesigned to do this, the power consumed would have been quite excessive. Since this power varies with the square of the voltage, a lower logic signal would be quite advantageous. The Emitter Coupled Logic (ECL) circuit was selected for this. It is still used by almost all high speed computers built today. It has only a 0.8 volt logic swing and can readily drive 50 ohms. Both the output signal levels and input switch points are quite closely controlled, providing room for noise margins. The transistors in the circuit operate in the linear mode which keeps enough voltage across the transistor to get its full speed potential and avoid any "voltage saturation" problem. ECL circuits are also considerably faster than TTL circuits built with similar base technologies, so it became the obvious choice for larger machines.

The 1100/80 logic card size was 7 by 10 inches, and it held up to 84 logic chips. The chip used a 16-pin DIP package similar to that of the 1110. A new connector with 240 pins was developed of which 160 could be used for signals, a big increase over previous logic circuits. This helped support the amount of logic on the card. It took four signal layers (2X + 2Y) to interconnect the logic circuits, and with the ground and voltage planes, a total of ten layers were needed. Previously only two or sometimes four layers were sufficient. Sixty cards in two rows could plug into one 50 ohm multilayer printed circuit backpanel measuring about 18 by 21 inches. Four backpanels then fit into one cabinet.

One of the problems encountered was that the thickest backpanel that could be then manufactured could not contain sufficient wires to interconnect all the printed circuit cards. This problem was solved by combining two backpanels. At every 0.10-inch location in both directions a plated through-hole was formed into each backpanel. One backpanel was placed on top of the other. Close tolerance square pins were forced through all the holes in the two backpanels and then were all soldered in one operation, interconnecting the two panels. The pins were made long enough to protrude on both sides. One side was used as the connector contact to mate with the printed circuit card, and the other was used for test probes and provisions for engineering wire changes. This concept was quite effective and has since been used extensively on products which require many complex backplane interconnections.

With so many chips on the printed circuit card, it was apparent that each could have its unique interconnection wiring. Furthermore, there were four layers of wiring, and strict rules had to be followed on how the various connections between one logic output and its various loads would be interconnected in order to avoid any transmission line problems. Since many of these boards had to be done in a

short time period, it was obvious that placement of the chips on a board and the location and arrangement of the wires between them had to be done with the use computer. of а Software to do this was not available at that time, so it was developed internally. The output of the program drove a machine which exposed light on photographic glass plates which became the artwork masters

used to manufacture the board. Computer output also provided the data for board testing. The same program handled the larger backpanel as well. The existence of a design automation capability within the engineering department became a necessity, and its role was destined to become even more important in the future. However, it is beyond the scope of this paper to cover this important area in proper detail.

The printed circuit technology developed for the 1100/80 was named MLP (for Multi Layer Packaging) and was used on a number of other projects. It has also provided a technology basis for handling ECL logic that is still used today.

# Memory Technology

As mentioned earlier, the 1180 was the first 1100 to use a cache memory. It was a shared cache memory in a separate cabinet; any processor in the system was able to access it. The actual term applied to this unit was the "Storage Interface Unit" or SIU. It contained up to 16,384 words, used a 256-bit semiconductor device with an ECL logic

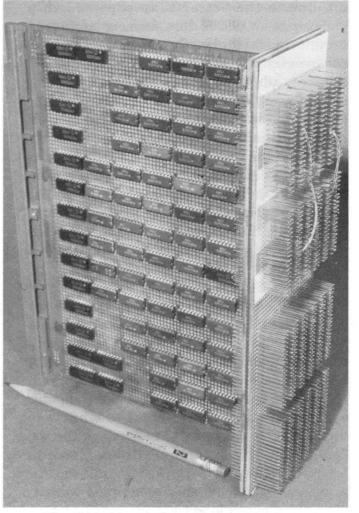

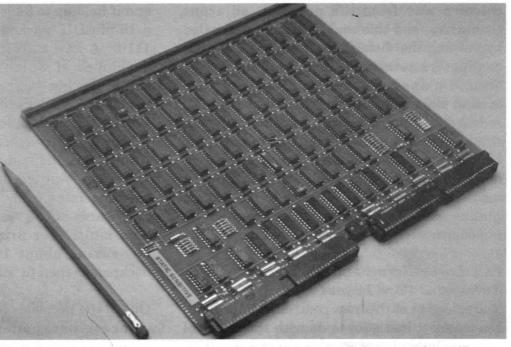

Typical semiconductor memory card of mid 1970s; 16K chip provides 32K words/card for the 1100/80 and 1100/60 systems.

interface and a 45-nanosecond access time. The memory control used the same cards and ECL logic technology as the processor.

The main memory used the 4K bit storage device. Eighty-eight chips were mounted on a 10-by 10-inch printed circuit card. The memory chips had TTL type of signal levels and did not have to operate as fast as the cache memory, so a wirewrap backpanel was still used here. Although the main memory was slower than the cache, it would read out eight words at a time, so that the entire block could be loaded into cache at a faster rate. The eight words were transmitted to the cache memory two words at a time.

# The 1100/80 System

The processor and cache memory each took their own cabinet with four backpanels of circuitry. The processor used 196 cards of 130 unique types with an averaged usage of 52 chips. The I/O section used the same TTL technology as the 1110, but had a new connector with more signal pins. The power system was supplied with 400 cycle power via a motor alternator, since that was felt to improve the immunity from any spikes on the incoming electric power lines. Another first on the 1100/80 was the use of a system support processor, the "SSP", a minicomputer used to monitor all the registers, or flip flops, in the system. This eliminated the need for the large control panels, containing hundreds of indicator lights, that had become common on large computers. The 1100/80 was about twice as fast as the 1110 and was delivered in 1976 as a dual processor system and later was upgraded to four processor capability. At that time the memory device was changed to a 16K chip, and two million words fit into a single cabinet - 16 times what had fit into one 1110 core memory unit and 500 times as much as the old 1103A! The space for a 4 X 4 system was reduced to 512 square feet compared to

864 for the earlier 1110 system. The 1180 was a very successful system. Over 1000 processors were delivered. It also created new technology techniques that set the foundation for many future products starting with the 1100/60-70 systems.

# **THE 1100/60-70**

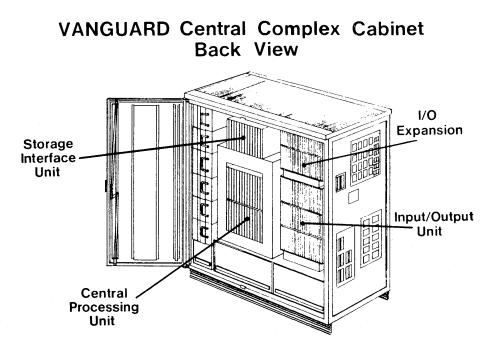

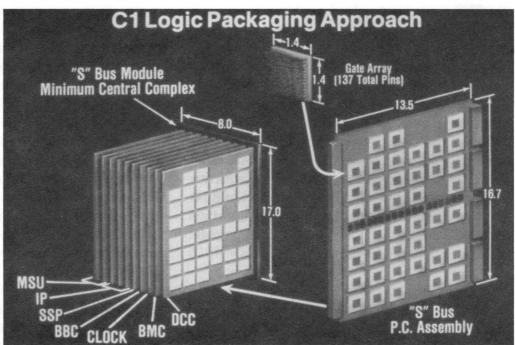

During the 1100/80 development, some computer engineers at the Sperry Research Center observed that microprocessor chips made with MOS technology were becoming quite capable and wondered what would happen if many of these were tied together in a single computer. After they completed a study project, their results showed then that the optimum cost-performance occurred with about four processors, partially because the memory became a bottleneck at much above that. It was also noted that it would be nice if something faster than MOS technology were used. ECL technology density was improving then, and a chip handling four bits of 16 primitive instructions had been developed. Nine of these together with other standard ECL logic chips would fit onto one 1100/80 type card to form a 36 bit ECL microprocessor. This formed the basis for a new product. Up until then the objective for a new processor design had always been to make a machine "bigger and better" than the existing ones. Here was a chance to make a smaller system, yet with reasonable performance, to broaden the usage base for the 1100. (At this time code names began to be used for major design projects with the final name-or model number-selected later at the product announcement date. The code name "Vanguard" was selected for this project; the 1100/60 nomenclature came later).

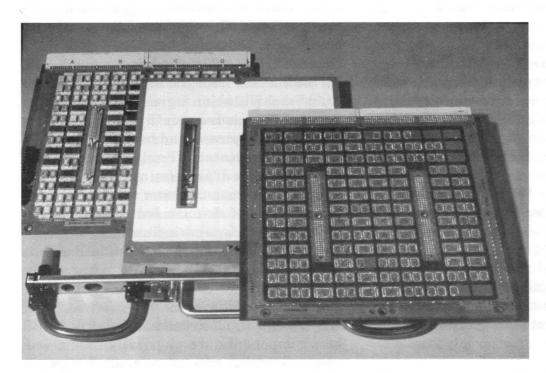

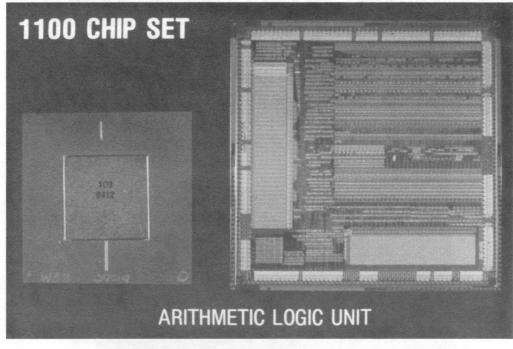

Four of the microprocessor cards were used in one processor together with microprogrammed instructions—a common practice in microprocessor chips—but the first time to be used in an 1100 system. Microprogramming moves random control from logic circuits to memory technology, and with the progress in semiconductor technology a dedicated, small, fast memory for this was quite practical. Otherwise the basic technology and design automation tools already developed for the 1100/80 were a good match for the 1100/60, and this allowed a short development schedule.