# MASS STORAGE SYSTEM

## OPR EXECUTIVE ROUTINE FASTRAND

### HANDLER SUPPLEMENT

UP 3951.4

#### 1.0 CONTENTS

|    | ^ | CONTENTO |

|----|---|----------|

| 1. | 0 | CONTENTS |

2.0 The EXECUTIVE FASTRAND HANDLER 2.1 ASSEMBLY INITIALIZATION 2.2 2.3 ISSUING THE ORDER ٠ ERROR CONDITION INTERRUPTS 2.4 2.4.1 Record Memory Error Drum Longitudinal Parity Error 2.4.2 First Phase Shift Error 2.4.3 2.4.4 Second Phase Shift Error 2.4.5 Missing Sector Error 2.4.6 Memory (Core) Parity Error Non-Ready 2.4.7 Memory Overload Anticipated or Busy Head Count Overflow 2.4.8 2.4.9 2.4.10 Locked Out Write

3.0 SAMPLE CODING

This document is preliminary in nature and is intended as a vehicle for meeting immediate needs with regard to system familiarization and orientation. UNIVAC<sup>®</sup> Division of Sperry Rand Corporation reserves the right to change and/or modify such information contained herein as may be required by subsequent system developments.

Page

1

1

1

1

2 2

2

2

2

2

3 3

3 3

3

4

FASTRAND file control routines will be available at a future date. The following is a description for those users who wish to write their own routine.

#### 2.1 ASSEMBLY

Parameter 6 (see Executive Routine - OPR, UP 3940.14) enables the user to assemble an Executive Routine that contains the FASTRAND Handler. If  $p_q$  is F, the modification will be included and will function according to the following description.

#### 2.2 INITIALIZATION

Before using the FASTRAND Handler to issue any orders, the following lines must be executed:

| LABEL | OPERATION | OPERANDS |

|-------|-----------|----------|

|       | FT        | 1,7      |

|       | JR :      | 0666     |

|       |           |          |

#### 2.3 ISSUING THE ORDER

When the user wishes to issue a FASTRAND order, he must execute a JR 0750 with the FASTRAND order and associated parameters already placed in AR1. The format of the 16 character packet of information that is placed in AR1 is as follows:

| XF Instruction |               |           |            |              |                                    | Count/Memory        | Addres | s Tetrad                                  |   | Drum                            | Addres | s Tetra   | d                  |           |             |

|----------------|---------------|-----------|------------|--------------|------------------------------------|---------------------|--------|-------------------------------------------|---|---------------------------------|--------|-----------|--------------------|-----------|-------------|

| ОР<br>5        | с<br>3        | Unit<br>4 | Function 6 | Detai]<br>12 | 6                                  | 6                   | 6      | ,<br>Sector<br>or Character<br>Count<br>8 | 1 | Core<br>Memory<br>Address<br>15 | 1      | Unit<br>3 | Pos-<br>ition<br>8 | Head<br>6 | Sector<br>6 |

|                |               |           |            |              | Stor<br>Addr<br>fc<br>Requ<br>Rout | ress<br>or<br>lesti | ing    |                                           |   |                                 |        |           |                    |           |             |

|                |               |           |            |              |                                    | 4                   |        | /                                         | 1 |                                 | 4      |           |                    |           |             |

| 4              | 16 Characters |           |            |              |                                    |                     |        |                                           |   |                                 |        |           |                    |           |             |

The FASTRAND instruction (XF) must contain all the necessary bits to execute the desired function. The field marked Count/Memory Address Tetrad will be transferred to Tetrad 56. The field marked Drum Address Tetrad will be transferred to Tetrad 57.

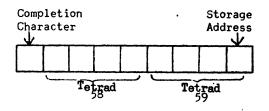

The address that must appear as the "storage address" must be the right-hand address of a 9 character control field in the users program. The handler will store pertinent information, concerning the status of the order, into that field. The character at storage address minus eight (known as the completion status character) should be preset to binary 0. At the completion of the order the handler will move Tetrads 58 and 59 to the storage address as indicated.

1

As long as the completion character remains at O, the user knows his order has not been finished, and must give up control to OPR (see Section 3.0).

The possible values of this character are

- 0 in process

- 1 successful completion

- 2 error see below

- 3 unsuccessful search

- 4 error see below

#### 2.4 ERROR CONDITION INTERRUPTS

In some cases, when programmed recovery of an error condition is impossible, the computer will be brought to a display stop (JC...48). The 16 bits of the display have the following format:

| Bit Positions |                |    |    |      |               |  |  |

|---------------|----------------|----|----|------|---------------|--|--|

| 16            | 15 <b>-1</b> 3 | 12 | 11 | 10-7 | 6-1           |  |  |

| 1             | Channel<br>110 | 0  | 0  | Unit | Error<br>Code |  |  |

The following action is taken for each specific error condition:

2.4.1 Record Memory Error

The order causing the error will be reissued. Before reissuing the order, the bit designating head bar positioning will be inserted into the XF order. The order will be reissued 2 times with the head bar positioning bit. If the order is still unsuccessful after the 2nd issue, a two will be inserted into the completion character. The order will be peeled off the list of XF instructions. Tetrads 58 and 59 are stored in the storage address for the requesting routine and control is returned to the requesting routine.

Modular FASTRAND utilizes a different drum addressing scheme. This makes possible the occurrence of a condition where a Record Memory Error indication being received is in fact the equivalent of a Head Count Overflow in FASTRAND I or II.

Should this occur, a position bit will be inserted and the order reissued two times. It will not be successfully completed and the using program will be informed of a Record Memory Error. A Head Count Overflow indication is also possible on Modular FASTRAND. Further program action upon the above occurrence remains the using program's responsibility.

2.4.2 Drum Longitudinal Parity Error

The order will be reissued 2 times. If the order is still unsuccessful after the 2nd issue, a two will be inserted into the completion character. The order will be peeled off the list of XF instructions. Tetrads 58 and 59 are stored in the storage address for the requesting routine, and control is returned to the requesting routine.

2.4.3 First Phase Shift Error

Same as above

2.4.4 Second Phase Shift Error

Same as above

2.4.5 Missing Sector Error

Same as above if

1. the order was not a search; or

if it was a search and the return memory address was equal to the initial memory address; or 3. if it was a search and the return memory address was  $\geq$  to the initial memory address +64.

If none of the above conditions existed and it was a search, it was an unsuccessful search. In this case a three will be inserted into the completion character. Tetrads 58 and 59 are stored in the storage address for the requesting routine.

2.4.6 Memory (Core) Parity Error

A display stop with an error code of 55 will occur. If the operator depresses the PROGRAM START button, control will be passed to a path that will temporarily bypass the worker program with an error.

2.4.7 Non-Ready

A display stop with an error code of 77 will occur. If the operator depresses the PROGRAM START button, the worker program will be bypassed with an error.

2.4.8 Memory Overload Anticipated or Busy

The instruction will be reissued and control will be returned to the interrupted program.

2.4.9 Head Count Overflow

The order will be peeled off the list of XF orders. A 4 will be inserted into the completion character. Tetrads 58 and 59 will be inserted into the storage address for the requesting routine, and control is returned to the requesting routine.

2.4.10 Locked Out Write

Some FASTRAND Systems will be delivered with the ability to have portions of the drum locked out (inhibit write). If a write is attempted in this area, an error indication will be given. A display stop with an error code of 33 will occur. If the operator depresses the PROGRAM START button, the worker program will be bypassed with an error.

The hardware indication of this occurrence is a Record Memory Error set in conjunction with Head Count Overflow.

#### 3.0 SAMPLE CODING

| the fol | lowing | lines appear | r in the users constant | area and will be used to specify the order: |

|---------|--------|--------------|-------------------------|---------------------------------------------|

| LA      | BEL    | <u>OP</u>    | OPERANDS                |                                             |

|         |        | XF           | 05,0,0,6                | FASTRAND order, position read               |

|         |        | +3           | COMPL                   | Completion storage address                  |

|         |        | +4           | INSEC+00200000          | Input area and sector count                 |

| FR      | DR     | +4           | 0                       | Starting drum address                       |

|         |        | +8           | 0                       |                                             |

| CO      | MPL    | +1           | 0                       | 9 character control field                   |

| The cod | ing to | issue the or | der and test for comple | tion follows:                               |

|         |        | PD           | COMPL-8,1               | Completion status character                 |

|         |        | BA1          | FROR, 16                | Bring order to AR1                          |

|         |        | JR           | 0750                    | Execute FASTRAND issue                      |

| TES     | ST     | JC           | \$+5,26                 | Inhibit Interrupt                           |

|         |        | СС           | COMPL-8,0               | · · ·                                       |

|         |        | JS           | DONE                    | Test for completion                         |

|         |        | LS           | 0526,04                 | Set 4 bit channel status list               |

|         |        | JR           | 0724                    | Go to OPR                                   |

|         |        | J            | TEST                    | Go to test completion                       |

| DON     | IE .   | J            | \$+5,27                 | Allow interrupt                             |

|         |        | cc           | COMPL-8,01              | Successful test                             |

|         |        | UL           | ERROR                   | Error routine                               |

|         |        | J            | MAIN                    |                                             |

|         |        |              |                         |                                             |

4

An example of the necessary instructions to issue an order and to test for completion follows. Assume the following lines appear in the users constant area and will be used to specify the order:

- -