# UNIVAC DATA PROCESSING DIVISION

### ASSEMBLER-80

PROGRAMMERS REFERENCE

This manual is published by the UNIVAC Division of Sperry Rand Corporation in loose leaf format as a rapid and complete means of keeping recipients apprised of UNIVAC <sup>®</sup> Systems developments. The UNIVAC Division will issue updating packages, utilizing primarily a page-for-page or unit replacement technique. Such issuance will provide notification of hardware and/or software changes and refinements. The UNIVAC Division reserves the right to make such additions, corrections, and/or deletions as in the judgment of the UNIVAC Division, are required by the development of its respective Systems.

PRINTED IN U.S.A.

| UP-4084 | UNIVAC 1005<br>ASSEMBLER-80 |   | Contents | 1     |

|---------|-----------------------------|---|----------|-------|

|         | ASSEMBEER-SO                | , | SECTION: | PAGE: |

C

(

ſ

# CONTENTS

| CONTENTS                                                             | 1 to 4     |

|----------------------------------------------------------------------|------------|

| 1. INTRODUCTION TO THE UNIVAC 1005 AND INTERNALLY STORED PROGRAMMING | 1-1 to 1-9 |

| 1.1. ADDRESSING TECHNIQUE                                            | 1-1        |

| 1.2. BASIC LOGIC AND FORMAT                                          | 1-2        |

| 1.3. CONTROL SECTION OPERATION                                       | 1-3        |

| 1.4. OTHER INSTRUCTION FORMATS                                       | 1-4        |

| 1.5. STORAGE ALLOCATION AND USE                                      | 1-4        |

| 1.6. INDIRECT ADDRESSING                                             | 1-5        |

| 1.7. OTHER SPECIAL REGISTERS                                         | 1-8        |

| 1.8. SPECIAL REGISTER LOCATIONS                                      | 1-8        |

| 1.9. ADDRESSING AND USE OF COLUMN 32                                 | 1-9        |

| 2. INTRODUCTION TO ASSEMBLY SYSTEMS                                  | 2-1 to 2-4 |

| 2.1. PURPOSE OF ASSEMBLY SYSTEMS                                     | 2-1        |

| 2.2. MNEMONIC CODING                                                 | 2-1        |

| 2.3. SYMBOLIC CODING                                                 | 2-2        |

| 2.4. RELATIVE CODING                                                 | 2-2        |

| 2.5. MEMORY MAPPING                                                  | 2-2        |

| 2.6. DECLARATIVE INSTRUCTIONS                                        | 2-3        |

| 2.7. ASSEMBLER PROCESSING                                            | 2-4        |

| UP-4084 | UNIVAC 1005<br>ASSEMBLER-80                                   |       | Contents<br>section: | 2<br>Page: |

|---------|---------------------------------------------------------------|-------|----------------------|------------|

|         |                                                               |       |                      |            |

|         | 3. INTRODUCTION TO THE UNIVAC 1005 ASSEMBLY SYSTEM            |       | 3–1 to               | 3-15       |

|         | 3.1. TERMINOLOGY DEFINITIONS                                  | •     | 3-1                  |            |

|         | 3.2. CODING FORM                                              |       | 3-1                  |            |

|         | 3.2.1. LABEL<br>3.2.2. OPERATION                              |       | 3-1<br>3-2           |            |

|         | 3.2.3. OPERAND 1                                              |       | 3-3                  |            |

|         | 3.2.3.1. IA                                                   |       | 3-3                  |            |

|         | 3.2.3.2. FIELD A<br>3.3.3.3. ± INC                            |       | 3-3<br>3-3           |            |

|         | 3.2.4. OPERAND 2                                              |       | 3-4                  |            |

|         | 3.2.4.1. IA, FIELD B, ± INC                                   |       | 3-4                  |            |

|         | 3.2.4.2. FIELD C, ± INC                                       |       | 3-4                  |            |

|         | 3.2.5. COMMENTS                                               |       | 3-5                  |            |

|         | 3.2.6. CARD NUMBER                                            |       | 3-5                  |            |

|         | 3.2.7. REMAINDER                                              |       | 3–5                  |            |

|         | 3.3. OPERAND 1 ADDRESS SPECIFICATION                          |       | 3-6                  |            |

|         | 3.3.1. Symbolic Address (Label) Specification                 |       | 3-6                  |            |

|         | 3.3.2. Increments to Symbolic Addresses                       |       | 3-7<br>3-8           |            |

|         | 3.3.3. Decimal Addressing<br>3.3.4. Row and Column Addressing |       | 3-8                  |            |

|         | 3.3.5. Instruction Location Counter (ILC) Addressing          |       | 3-9                  |            |

|         | 3.4. OPERAND 2 ADDRESS SPECIFICATION                          |       | 3-10                 |            |

|         | 3.4.1. Operand 2, Field C, Blank Addressing                   |       | 3-10                 |            |

|         | 3.4.2. Operand 2 Indirect Addressing                          |       | 3-12                 |            |

|         | 3.5. SUMMARY OF FIELD A, FIELD B, AND FIELD C SPECIFICA       | TIONS | 3–13                 |            |

|         | 3.5.1. FIELD A                                                |       | 3-13                 |            |

|         | 3.5.2. FIELD B                                                |       | 3-13                 |            |

|         | 3.5.3. FIELD C                                                |       | 3-14                 |            |

|         | 3.6. STANDARD SYSTEMS LABELS                                  |       | 3-14                 |            |

|         | 4. UNIVAC 1005 ASSEMBLY SYSTEM INSTRUCTIONS                   |       | 4-1 to               | 0 4-98     |

|         | 4.1. LEGEND                                                   |       | 4-1                  |            |

|         | 4.2. LENGTH OF OPERANDS                                       |       | 4-1                  |            |

|         | 4.3. TRANSFER INSTRUCTIONS                                    |       | 4-4                  |            |

|         | 4.3.1. TRANSFER DESCENDING                                    |       | 4-4                  |            |

|         | 4.3.2. TRANSFER ASCENDING                                     |       | 4-7                  |            |

|         | 4.3.3. TRANSFER CLEAR<br>4.3.4. TRANSFER NUMERIC              |       | 4-9<br>4-10          |            |

|         | 4.3.4. TRANSFER NOMERIC<br>4.3.5. TRANSFER CONSTANT           |       | 4-10<br>4-10         |            |

|         | 4.3.5.1. Symbolic Address Substitution                        |       | 4-14                 |            |

|         | 4.3.5.2. Row/Column and Decimal Addressing                    |       | 4-15                 |            |

|         | 4.3.5.3. Binary Coded Constants                               |       | 4-16                 |            |

|         | 4.3.6. TRANSFER TO REGISTER X                                 |       | 4-18                 |            |

|         | 4.3.7. TRANSLATE                                              |       | 4-19                 |            |

| UP-4084 | UNIVAC 1005<br>ASSEMBLER-80 | Contents<br>section: | PAGE: |

|---------|-----------------------------|----------------------|-------|

|         |                             |                      |       |

C

C

C

| <ul> <li>4.4. ADDITION AND SUBTRACTION</li> <li>4.4.1. ADD ALGEBRAIC</li> <li>4.4.2. SUBTRACT ALGEBRAIC</li> <li>4.4.3. ABSOLUTE ADD (ADD MAGNITUDE)</li> <li>4.4.4. ABSOLUTE SUBTRACT (SUBTRACT MAGNITUDE)</li> <li>4.4.5. ADD CONSTANT</li> </ul>                                                                                                                                                                          | 4-23<br>4-24<br>4-25<br>4-26<br>4-26<br>4-27                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| <ul> <li>4.5. COMPARE INSTRUCTIONS</li> <li>4.5.1. COMPARE NUMERIC SIGNED COMPARISON</li> <li>4.5.2. COMPARE ABSOLUTE (MAGNITUDE) UNSIGNED COMPARISON</li> <li>4.5.3. COMPARE ALPHANUMERIC UNSIGNED COMPARISON</li> <li>4.5.4. COMPARE CONSTANT UNSIGNED COMPARISON</li> </ul>                                                                                                                                               | 4-28<br>4-29<br>4-30<br>4-32<br>4-34                                                        |

| 4.6. CONDITION INDICATORS<br>4.6.1. SET CONDITION<br>4.6.2. STOP (HALT)                                                                                                                                                                                                                                                                                                                                                      | 4-36<br>4-36<br>4-39                                                                        |

| <ul> <li>4.7. SEQUENCE CONTROL INSTRUCTIONS</li> <li>4.7.1. JUMP CONDITION</li> <li>4.7.2. JUMP TEST</li> <li>4.7.3. UNCONDITIONAL JUMP</li> <li>4.7.4. JUMP RETURN</li> <li>4.7.5. JUMP COMPARE</li> <li>4.7.6. JUMP LOOP</li> <li>4.7.7. JUMP INDIRECT</li> </ul>                                                                                                                                                          | $\begin{array}{r} 4-39 \\ 4-39 \\ 4-44 \\ 4-46 \\ 4-46 \\ 4-49 \\ 4-51 \\ 4-54 \end{array}$ |

| 4.8. COUNT                                                                                                                                                                                                                                                                                                                                                                                                                   | 4-55                                                                                        |

| <ul> <li>4.9. EDIT INSTRUCTIONS</li> <li>4.9.1. EDIT LOGICAL</li> <li>4.9.2. EDIT ERASE</li> <li>4.9.3. EDIT SUPERIMPOSE</li> <li>4.9.4. EDIT</li> </ul>                                                                                                                                                                                                                                                                     | 4-57<br>4-58<br>4-60<br>4-60<br>4-61                                                        |

| <ul> <li>4.10 DECLARATIVE INSTRUCTIONS</li> <li>4.10.1. DEFINE INSTRUCTION LOCATION COUNTER</li> <li>4.10.2. DEFINE AREA</li> <li>4.10.2.1. DEFINE SUB-FIELD</li> <li>4.10.2.2. Subfields of Specific Fixed Address Areas</li> <li>4.10.3. DEFINE CONSTANT</li> <li>4.10.3.1. In-line Constants</li> <li>4.10.3.2. In-line Comments</li> <li>4.10.4. DEFINE INDIRECT ADDRESS CONSTANT</li> <li>4.10.5. DEFINE END</li> </ul> | 4-65<br>4-65<br>4-69<br>4-71<br>4-72<br>4-74<br>4-75<br>4-76<br>4-79                        |

| <ul><li>4.11. MULTIPLICATION INSTRUCTIONS</li><li>4.11.1. MULTIPLY</li><li>4.11.2. MULTIPLY (LONG)</li></ul>                                                                                                                                                                                                                                                                                                                 | 4-79<br>4-80<br>4-82                                                                        |

| 4.12. DIVIDE INSTRUCTION<br>4.12.1. DIVIDE                                                                                                                                                                                                                                                                                                                                                                                   | 4-83<br>4-84                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                             |

| UP-4084 | UNIVAC 1005<br>ASSEMBLER-80                        | Contents<br>section: PA | 4<br>ge:                                 |

|---------|----------------------------------------------------|-------------------------|------------------------------------------|

|         |                                                    |                         |                                          |

|         |                                                    |                         |                                          |

|         | 4.13. INPUT/OUTPUT INSTRUCTIONS                    | 4-85                    | $\cap$                                   |

|         | 4.13.1. SHORTENED GENERAL COMMANDS                 | 4-86                    |                                          |

|         | 4.13.2. GENERAL COMMANDS                           | 4-87                    |                                          |

|         | 4.13.3. READ MAGNETIC TAPE                         | 4-92                    |                                          |

|         | 4.13.4. WRITE MAGNETIC TAPE                        | 4-93                    |                                          |

|         | 4.13.5. RECEIVE DATA LINE                          | 4-94                    |                                          |

|         | 4.13.6. SEND DATA LINE                             | 4-95                    |                                          |

|         | 4.13.7. RECEIVE INTERFACE                          | 4-96                    |                                          |

|         | 4.13.8. SEND INTERFACE                             | 4–97                    |                                          |

|         | 5. OPERATING PROCEDURES FOR 1005 ASSEMBLY          | 5–1 to 5–               | -3                                       |

|         | 5.1. LOADING SOURCE PROGRAM                        | 5-1                     | 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1. 1 |

|         | 5.2. LOADING OBJECT PROGRAM                        | 5-2                     |                                          |

|         | 5.3. FINAL LISTING                                 | 5-2                     |                                          |

|         | 5.3.1. Original Source Code                        | 5-2                     |                                          |

|         | 5.3.2. Unfound Indicators                          | 5-2                     |                                          |

|         | 5.3.3. Sequence Number                             | 5-3                     |                                          |

|         | 5.3.4. Object Code Instruction                     | 5-3                     |                                          |

| 1       | 5.3.5. Load Instruction                            | 5-3                     |                                          |

|         | 5.3.6. Diagnostic Message                          | 5-3                     |                                          |

|         | 6. PROGRAM TESTING AIDS                            | 6-1 to 6-               | -3                                       |

|         | APPENDIX A.<br>UNIVAC 1005 ASSEMBLER CODING FORM   | A-1 to A-               | -1                                       |

|         | APPENDIX B.<br>UNIVAC 1005 INSTRUCTION TIMING (80) | B-1 to B-               | -1                                       |

August 23, 1966

### UNIVAC 1005 System ASSEMBLER-80 Programmer's Reference UP-4084

#### UPDATING PACKAGE "A"

UNIVAC 1005 System P.I.E. Bulletin 4, UP-4072.4, releases and announces the availability of Updating Package "A" for the "UNIVAC 1005 SYSTEM ASSEMBLER-80 Programmer's Reference," UP-4084, 59 pages plus 1 Updating Summary Sheet. This material should be utilized in the following manner:

| SECTION | DESTROY FORMER<br>PAGES NUMBERED | FILE NEW PAGE<br>NUMBERED                                  |

|---------|----------------------------------|------------------------------------------------------------|

| 1       | 1 & 2<br>3 & 4                   | 1* & 2 Rev.l<br>3 Rev.l & 4*                               |

| 3       | 9 & 10                           | 9 Rev.1 & 10*                                              |

| 4       | 13 & 14<br>1 & 2<br>5 & 6        | 13* & 14 Rev.1<br>1 Rev.1 & 2*<br>5 Rev.1 & 6*             |

|         | 7 & 8<br>11 & 12<br>15 & 16      | 7 Rev.l & 8 Rev.l<br>11* & 12 Rev.l<br>15 Rev.l & 16 Rev.l |

|         | 19 & 20<br>21 & 22               | 19* & 20 Rev.1<br>21 Rev.1 & 22*                           |

|         | 29 & 30<br>35 & 36               | 29 Rev.1 & 30*<br>35* & 36 Rev.1                           |

|         | 37 & 38<br>39 & 40               | 37 Rev.l & 38*<br>39 Rev.l & 40*                           |

|         | 41 & 42<br>51 & 52               | 41 Rev.1 & 42*<br>51 Rev.1 & 52*                           |

|         | 53 & 54                          | 53* & 54 Rev.l                                             |

|         | 55 & 56<br>61 & 62               | 55 Rev.1 & 56*<br>61 Rev.1 & 62 Rev.1                      |

|         | 63 & 64<br>65 & 66               | 63 Rev.1 & 64 Rev.1<br>65 Rev.1 & 66*                      |

|         | 67 & 68<br>73 & 74               | 67 Rev.l & 68*<br>73 Rev.l & 74 Rev.l                      |

|         | 81 & 82<br>83 & 84               | 81 Rev.1 & 82 Rev.1<br>83 Rev.1 & 84*                      |

| 6       | 85 & 86<br>97 & 98<br>1 & 2      | 85 Rev.l & 86*<br>97 Rev.l & 98*<br>1 Rev.l & 2*           |

|         | 3                                | 3 Rev.l<br>ed pages, remain unchanged.                     |

# 1. INTRODUCTION TO THE UNIVAC 1005 AND INTERNALLY STORED PROGRAMMING

The UNIVAC 1005 is a general purpose, stored program, digital computer. The main store consists of either two or four banks of core memory with 1024 locations per bank. In addition to providing storage for instructions and data, two types of Special Registers are provided in core memory to control the operation of the UNIVAC 1005. The special registers are addressable and in some cases can be used as additional data storage.

#### 1.1. ADDRESSING TECHNIQUE

Each bank of core memory consists of a 32 row by 32 column matrix of six-bit memory locations. Each location is addressed by specifying its Row and Column coordinates. For example; the first memory location has an address of Row 1, Column 1; the last memory location has an address of Row 32, Column 32. These address designations are abbreviated to R1/C1 and R32/C32.

In order to store the address of instructions and data in memory, the six bits of two adjacent memory locations are required. Five of the six bits of the left-hand location are used to specify the Row coordinate, and five of the six bits of the righthand location are used to specify the Column coordinate. A combination of the sixth bits of both locations is used to specify which of the four possible banks of memory is involved.

The UNIVAC 1005 utilizes a special five-bit address concept which operates on a logical rather than a binary arithmetic basis. Special combinations of these five bits are employed for the values 1 to 31 used as row or column coordinates. These five-bit combinations, plus the sixth bit required for bank designation, correspond to the 64 characters of the UNIVAC 1005. Thus, the address of any location in any bank of core memory can be specified by the proper selection of two of these six-bit characters.

The foregoing description indicates the similarity and compatibility of the memory of the UNIVAC 1005 and the UNIVAC 1004.

For the purpose of stored-programming, the main store of the UNIVAC 1005 should be considered as 1922 (or 3844) consecutively numbered, decimally addressed memory locations exclusive of all rows numbered 32 and all Columns numbered 32 of each row. The physical arrangement of main store is then no longer a concern of the programmer. Using this method, the main store of the UNIVAC 1005 takes on the following appearance:

| 1         | 100  | 1923      | 2000 |

|-----------|------|-----------|------|

| 101       | 200  | 2001      | 2100 |

| 201       | 300  | 2100      | 2200 |

|           |      |           |      |

|           |      |           |      |

|           |      |           |      |

|           |      | 3601      | 3700 |

|           |      | 3701      | 3800 |

|           |      | 3801 3844 |      |

| 1701      | 1800 |           |      |

| 1801      | 1900 |           |      |

| 1901 1922 |      |           |      |

BANKS 1 and 2

BANKS 3 and 4

2

Decimal addressing would then produce the following facility for programming:

|                                                    | DECIMAL ADDRESS |

|----------------------------------------------------|-----------------|

| First location of Read Input Storage (Card Col. 1) | 1               |

| Last location of Read Input Storage (Card Col. 80) | 80              |

| First location of Print Storage (Print Pos. 1)     | 161             |

| Last location of Print Storage (Print Pos. 132)    | 292             |

| First location of Punch Storage (Card Col. 1)      | 293             |

| Last location of Punch Storage (Card Col. 80)      | 372             |

Since Print Position 1 is located at address 161, Print Position 23, for example, is located 22 positions away at address 183. This same convenience is extended to the addressing of the programmer's data areas as well as to the other reserved areas of Input Output storage. A complete description of decimal addressing as provided by the UNIVAC 1005 Assembly System appears in Section 3.3.3. of this manual.

#### 1.2. BASIC LOGIC AND FORMAT

The UNIVAC 1005 operates on a basic two address instruction logic. A UNIVAC 1005 instruction may contain the address of one or two units of information called Operands, and an operation code for the process to be performed with these Operands. The Operands are defined by specifying the address of the most significant location (abbreviated MSL), or the address of the least significant location (abbreviated LSL), or both, depending on the operation to be performed. Operations are specified by a one character code.

SECTION:

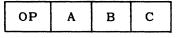

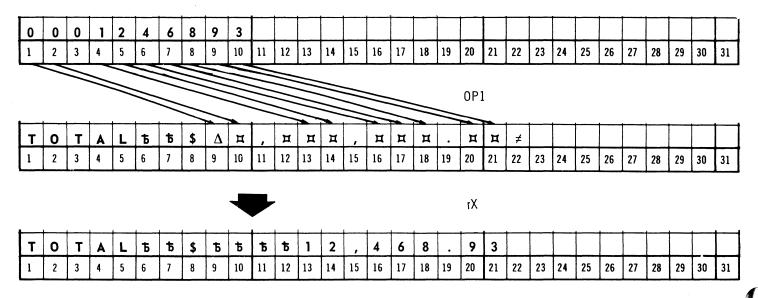

The majority of the UNIVAC 1005 instructions require seven character locations in the following format:

OP is a single character which specifies the operation to be performed.

A is the two character address of the MSL or the LSL of Operand 1.

${\bf B}$  is the two character address of the MSL of Operand 2.

C is the two character address of the LSL of Operand 2.

A, B or C may also represent constant information.

The function called for by an instruction is executed in ascending (LSL to MSL) or descending (MSL to LSL) mode. If the operation is performed in ascending mode, the A portion specifies the LSL of Operand 1. If the operation is performed in descending mode, the A portion specifies the MSL of Operand 1. The use of UNIVAC 1005 character codes to specify operation codes and addresses is called absolute coding or machine coding. A table of these codes and their equivalents is shown in Section 6. As will be explained in succeeding sections of this manual, the UNIVAC 1005 Assembly System provides a convenient method of specifying these codes. The output of the Assembler processing is a deck of punched cards containing instructions in machine code. These cards are read by the UNIVAC 1005 and the instructions stored in core memory under the control of a Load program. The Load program supplied by UNIVAC is a special header card which is placed in the front of the instruction cards.

#### **1.3. CONTROL SECTION OPERATION**

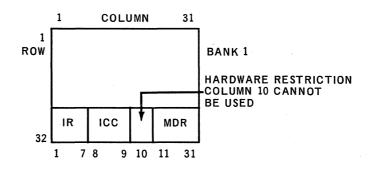

After the program has been loaded, operation of the UNIVAC 1005 proceeds under the control of the Instruction Control Counter (ICC). The ICC is one of the Special Registers located in core memory. The ICC is a two character register which contains the address of the MSL of the instruction to be accessed next by the UNIVAC 1005. As each instruction is accessed for execution, the contents of the ICC are incremented by the number of characters in the instruction -- usually seven. This increment is automatically added to the right-hand character of the ICC, the Column address portion. When the Column count passes 31, an increment of one is added to the Row address portion of the ICC, and the Column portion is returned to 1. The ICC will never create an address of Row 32 or Column 32 because the increment of 1 to "31" produces a result of 1. Memory Bank specification is also advanced as the Row count passes 31. Thus, the access and execution of instructions proceeds in a sequential manner. Instructions are provided to vary this sequential operation when required.

As each instruction is accessed, according to the address in the ICC, it is transferred to the Instruction Register (IR). The IR is a seven character Special Register which is used to examine the instruction. The bit configuration of the single character Operation code is analyzed by the circuitry which establishes and controls the functions necessary to perform the required operation. The address portions of the IR are transferred to the internal storage address controls for OP 1 and OP 2.

PAGE:

4

The normal operation of the UNIVAC 1005 when executing instructions is to access the first character from either the LSL or the MSL of OP 1, and the corresponding character from OP 2 (LSL or MSL) and perform the process. The determination of whether the LSL or the MSL is used is based on the mode--ascending or descending --of the instruction. After operating on the first characters from OP 1 and OP 2, the operation proceeds with successive corresponding characters of OP 1 and OP 2 until the processing of the last character location of OP 2 has been completed. This signals the end of the instruction.

During the execution of each instruction, the contents of the ICC are incremented according to the number of characters in the instruction itself. When the end operation signal is generated, the new address in the ICC is used to control the access of the next instruction (NI). The execution of the program proceeds in this manner to direct the UNIVAC 1005 to accomplish the desired results.

#### **1.4. OTHER INSTRUCTION FORMATS**

The instruction repertoire of the UNIVAC 1005 includes a complete set of commands for control of the operation of the system. In addition to the type of commands previously mentioned--seven characters, with an OP 1 and an OP 2 address--there is a second type of command which provides for flexibility and ease of control of the programming requirements necessary to internally stored program operation.

The second type of instruction is five characters in length and has the following format:

| OP | A | В |

|----|---|---|

|    |   |   |

Where:

OP is a one character operation code.

- A is a two character address or constant whose value is used or whose bit configuration is used to perform special functions.

- B is a two character address of a location in memory.

As is the case with most stored program computers, there are special commands in the UNIVAC 1005 with a format that does not precisely conform to these two basic formats. The Set Condition Instruction is a unique exception to the general rule in that "B" is used for the normal purpose of "A." These special commands will be either five or seven characters in length, and the format variation will be indicated along with a complete description of the operation.

#### 1.5. STORAGE ALLOCATION AND USE

The main store of the UNIVAC 1005 is separated by the hardware into two major areas--input output store, and working store. Input output store consists of selected portions of memory reserved for the information received from and transferred to the input/output devices. When an input or output device is not required by a particular

5

program, the reserved memory area of that device may be used by the programmer for storage of instructions or data. The working store consists of these portions of memory not reserved for input/output information--the remainder of core memory.

The working store is separated by the programmer into two types of areas according to his programming requirements. A portion of working store is established by the programmer to store the information (other than input/output) to be processed. The remainder of working store is used to store the program instructions.

A note should be made at this point that the addressing capability of the instruction address extends to all of main store. This means that the contents of any memory location or locations can be accessed as data to be processed. This includes those locations used by the programmer to store instructions. The use of this capability to operate on instructions as if they were data is an important technique of internally stored programming.

#### 1.6. INDIRECT ADDRESSING

Another facility provided by the UNIVAC 1005 is the ability to perform Indirect Addressing. In the UNIVAC 1005, Indirect Addressing is the ability to specify in the address portion of an instruction the address of the memory location which contains not the data to be processed, but a secondary address which specifies the location of the data to be processed. From a hardware standpoint, this is accomplished by using the primary address-the address in the instruction--to control the transfer of the secondary address to the IR where it is then used as the address of the data to be processed.

From a programming standpoint, Indirect Addressing allows the programmer to establish one series of instructions which perform a programming operation on separately stored but related items of information. This is accomplished by programming the instructions once using primary addresses, and changing the secondary address to refer to the proper item for each use of the series of instructions. For example: a detail card contains four twenty-column transaction items. Each item contains four five-column fields. The program is written using primary addresses which refer to a table of secondary addresses. The table is set up to refer to the address of the fields within an item. A series of addresses in the form of constants is created by the programmer and stored in a portion of working store. There is a series of addresses for each of the transaction items as they will appear in Read Input Storage. Before processing the first transaction item, the program transfers the series of addresses which refer to this item, to the secondary address table locations referred to by the primary addresses in the instructions. The first item is then processed. At the conclusion of the processing of the first item, the program then transfers the series of addresses which refer to the second transaction to the table of secondary addresses. The series of instructions is then executed again, only this time, the table of secondary address references the locations of the fields of the second transaction item causing it to be processed. The program action of changing the contents of the secondary address table is then repeated for the processing of the third and fourth transaction items. An explanation of this example is shown in Figure 1-1.

6 Page:

READ INPUT STORAGE TRANSACTION ONE TRANSACTION TWO TRANSACTION THREE TRANSACTION FOUR FIELD 1 FIELD 2 FIELD 3 FIELD 4 FIELD 2 FIELD 3 FIELD 4 FIELD 1 FIELD 2 FIELD 3 FIELD 1 FIELD 2 FIELD 3 FIELD 4 FIELD 1 FIELD 4 35 36 40 41 45 46 60 61 65 66 70 71 75 76 80 20 21 25 26 30 31 55 56 SECONDARY ADDRESS TABLE ENTRY 1 ENTRY 2 ENTRY 3 ENTRY 4 ADR. OF ADR. OF ADR. OF ADR. OF FIELD 2 FIELD 3 FIELD 4 FIELD 1 MSL LSL MSL LSL MSL LSL MSL LSL 1 2 3 4 4 1 2 1 2 3 4 CONSTANT STORAGE ADR. OF FD. 4, ITEM 1 ADR. OF FD. 1, ITEM 1 ADR. OF FD. 2, ITEM 1 ADR. OF FD. 3, ITEM 1 ENTRY 1 ADR. OF FD. 2, ITEM 2 ADR. OF FD. 3, ITEM 2 ADR. OF FD. 4, ITEM 2 ADR. OF FD. 1, ITEM 2 ENTRY 2 ADR. OF FD. 3, ITEM 3 ADR. OF FD. 4, ITEM 3 ADR. OF FD. 1, ITEM 3 ADR. OF FD. 2, ITEM 3 ENTRY 3 ADR. OF FD. 1, ITEM 4 ADR. OF FD. 2, ITEM 4 ADR. OF FD. 3, ITEM 4 ADR. OF FD. 4, ITEM 4 ENTRY 4

Figure 1–1. Example of Indirect Addressing

UP-4084

SECTION:

1

### 7

#### INSTRUCTIONS REQUIRED

|          | OPERATION                     | FIELD A                                                      | FIELD B                                               | FIELD C                                          | ACTION                                                                                                                                                                                                                                                                                                                                                       |

|----------|-------------------------------|--------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instr. 1 | TRF-D                         | MSL of Entry<br>1 in constant<br>storage                     | MSL of<br>Sec Adr<br>Table                            | LSL of Sec<br>Adr Table                          | The MSL and LSL addresses of<br>the Fields of Transaction One<br>are transferred to the Sec Adr<br>Table                                                                                                                                                                                                                                                     |

| 2        | ADD-ALG                       | *ADR of Loc 3<br>Entry 1, Sec<br>Adr Table<br>(LSL Field)    | *ADR of<br>Loc 1<br>Entry 2,<br>Sec Adr<br>(MSL Fd 2) | ADR of Loc<br>3 Entry 2<br>Sec Adr<br>(LSL Fd 2) | The primary address in the A<br>position of the instruction refers<br>to the lower 2 characters of Entry<br>1 in the Sec Adr Table. These<br>two characters are then used as<br>the A address of this instruction.<br>The primary addresses in the<br>B and C positions similarly refer<br>to the Sec Adr Table Entry 2, and<br>address substitution occurs. |

| 3        | ADD-ALG                       | *ADR of Loc 3<br>Entry 2, Sec<br>Adr (LSL Fd 2)              | *ADR of Loc<br>1 Entry 3<br>Sec Adr<br>(MSL Fd 3)     | ADR of Loc<br>3 Entry 3<br>Sec Adr<br>(LSL Fd 3) | Same as for Instruction 2 except<br>that substitutes are made from<br>Entry 2 and Entry 3.                                                                                                                                                                                                                                                                   |

| 4        | SUB-ALG                       | *ADR of Loc 3<br>Entry 3, Sec<br>Adr (LSL Fd 3)              | *ADR of Loc<br>1 Entry 4,<br>Sec Adr<br>(MSL Fd 4)    | ADR of Loc<br>3 Entry 4<br>Sec Adr<br>(LSL Fd 4) | Same as for Instruction 3 except<br>that substitutions are made from<br>Entry 3 and Entry 4.                                                                                                                                                                                                                                                                 |

| 5        | TRF-D                         | MSL of Entry<br>2, then 3, then<br>4, in constant<br>storage | MSL of Sec<br>Adr Table                               | LSL of Sec<br>Adr Table                          | The addresses of the next item<br>are set up in the Sec Adr Table.                                                                                                                                                                                                                                                                                           |

| 6        | Return to<br>Instruction<br>2 |                                                              |                                                       |                                                  | Transfer control to instruction<br>2 to initiate processing of the<br>next item.                                                                                                                                                                                                                                                                             |

The \* indicates Indirect Addressing

NOTE: Additional programming techniques are necessary to control the number of times these instructions are to be executed for each card read. They are not involved with the use of Indirect Addressing, and were omitted in order to confine the example to the discussion. They will be covered along with the UNIVAC 1005 Operations which are used for the additional techniques. (See the JL and CC instructions if desired.)

Instructions 2, 3 and 4 will not have anything coded in Field C. The MSL and LSL to be used is defined in Field B.

The normal use of Indirect Addressing is with data which contains a multiple item format similar to the punched card format in the preceding example. The multiple item concept is generally used for magnetic tape master and detail files. The use of the Indirect Addressing capability of the UNIVAC 1005 is not restricted to the multiple item concept.

Other UNIVAC 1005 Operations and capabilities designed to implement stored programming techniques are described in this manual along with an example of the application of the technique.

8

#### **1.7. OTHER SPECIAL REGISTERS**

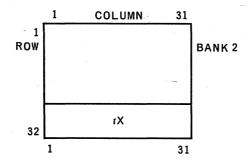

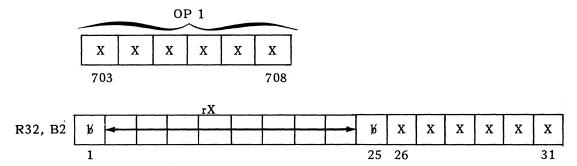

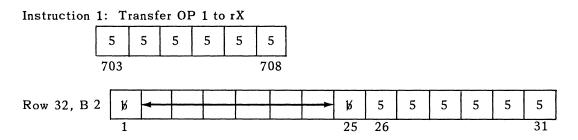

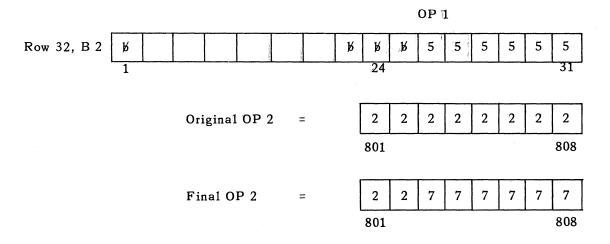

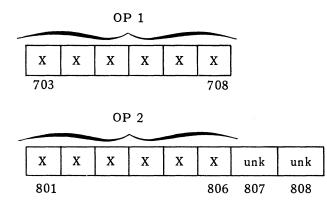

There are two Special Registers in addition to the Instruction Control Counter and the Instruction Register. These are the Multiply/Divide Register (MDR), and a multi-purpose register called Register X (rX).

The MDR is 31 locations in length, and is used in the process of Multiplication and Division. The most significant 10 positions of the MDR are used by the IR and the ICC during part of each Instruction Cycle. When not required for this purpose, the least significant 21 locations may be used for intermediate results of other programming operations.

Register X is 31 locations in length and is used primarily with the Edit Mask Operation, otherwise it may be used when Add or Subtract operations involve Operands of unequal length.

A thorough explanation of the use of rX and the MDR is given in this manual where the Operations which reference them are discussed.

It should be remembered that all Special Registers are located in core memory, are explicitly addressable, and are in addition to the basic two or four banks of main store.

#### 1.8. SPECIAL REGISTER LOCATIONS

The Instruction Register (IR), the Instruction Control Counter (ICC), and the Multiply/Divide Register (MDR) constitute an extra row of core memory--Row 32. This set of special registers is in Row 32 of *BANK 1*

Register X constitutes an extra row of core memory--Row 32 of BANK 2.

When the ICC is incremented for sequential access of instructions, it advances from R31/C31 of Bank 1, Bank 2, Bank 3, and Bank 4, to R1/C1 of Bank 2, Bank 3, Bank 4, and Bank 1 respectively, thus bypassing Row 32 and the special registers. The use of decimal addressing does not include the specification of the addresses of the Special Registers.

#### 1.9. ADDRESSING AND USE OF COLUMN 32

Each of the 32 Rows of memory contains 32 columnar positions. The allocation of memory by the Assembler program is made on the basis of 31 Rows and 31 Columns per Bank. As described in Section 1.8, Row 32 of Bank 1, 2, 3, and Bank 4 are excluded from Assembler allocation and are used for the Special Registers. The explanation of the advance of the Row and Column portions of the Instruction Control Counter indicates that not only is Row 32 of memory bypassed, but also Column 32 of each Row of memory is also excluded from Assembler allocation.

Column 32 of each Row in Bank 2, 3, and 4 becomes a series of one character locations which can be used by the programmer for such things as single character constants, control settings, program switches, etc. Decimal addressing does not include the addressing of any Column 32.

NOTE: Column 32 of each of the Rows in *Bank 1* are reserved for hardware/software control purposes and must not be used by the programmer.

Row 32 of Bank 3 and Bank 4 are also not included in the allocation processing of the Assembler program. Row 32 of Bank 3 and Bank 4 can be used by the programmer for the storage of data and intermediate results of processing.

Control of an internally stored program computer is accomplished by providing the computer with a set of instructions which have been designed to produce the desired results. These instructions are created by the programmer according to the specific requirements and capabilities of the computer. The instructions must be entered in the computer memory in a specific sequence using a precise set of characters. This set of characters constitutes the vocabulary or language of the machine. Machine languages are dictated by the design characteristics of the computer and seldom bear any relationship to human language. Furthermore, machine languages seldom follow any logical pattern that a person could use when writing a program. In addition to the language barrier, there are many clerical-type functions which a programmer must perform when writing a program.

PAGE:

## 2. INTRODUCTION TO ASSEMBLY SYSTEMS

#### 2.1. PURPOSE OF ASSEMBLY SYSTEMS

In order to overcome the language barrier, and to provide the programmer with clerical-type assistance, an assembly system is usually provided as part of the software of an internally stored program computer.

The assembly system allows the programmer to use a machine-oriented language which is also human oriented. The programmer writes the instructions in assembly language according to the rules of the assembly system. These instructions are punched into cards and are read into the computer under the control of a program called the assembler program. The assembler program analyzes the assembly language instructions and translates or converts this language into the precise machine language of the computer. An output deck of punched cards is produced by the assembler processing which contains the machine language instructions. This deck of cards is then read into the computer under the control of a load program which stores the instructions in the required sequence. The computer is then instructed to execute the program.

The deck of cards which contains the instructions written in assembly language is called the source deck. The output deck of cards which contains the instructions in machine language is called the object deck. In some cases, the assembly language is referred to as the source language or source code, and the machine language is referred to as the object language or object code.

#### 2.2. MNEMONIC CODING

The terms mnemonic, symbolic, and relative coding are sometimes erroneously used as synonyms. Each term has a specific meaning, and each one constitutes an important characteristic of an assembler.

An assembly language usually contains a set of mnemonic codes which represent the Operation codes of the computer. These mnemonic codes are established to help the programmer remember the code to be used for the Operation needed.

2

#### 2.3. SYMBOLIC CODING

Symbolic codes are a usual provision of an assembly language to allow the programmer to assign meaningful names to important information within his program. For example, the fields of data in a payroll card are known to the programmer by the type of information they contain, such as Employee Number, Department, Gross Pay, etc. There is normally a limitation on the length of a symbolic name. However, this length is usually enough to permit meaningful abbreviations or contractions. In the example above, the Employee Number field could be named EMPNO; the Department field could be named DEPT.; the Gross Pay field could be named GRPAY. As will be discussed in the section on memory mapping, the actual addresses of these fields in memory are assigned by the assembler program. When the name or label appears anywhere in the source language instructions, the assembler program will use the assigned actual address in the object language instruction.

Symbolic labels are also assigned to instructions in the program which are referenced by other instructions in the program. When a non-sequential transfer of control is required from one series of instructions to another, the programmer must specify the point to which control is to be transferred. Since actual addresses are assigned by the assembly program, the programmer cannot provide the *actual* address. By labelling the instruction to which control is to be transferred, he can use the symbolic address for the same purpose.

#### 2.4. RELATIVE CODING

Relative coding is another assembly system technique which allows the programmer to specify the location of instructions and data, even though the actual addresses are assigned by the assembly program. To use the relative coding technique, the programmer must have a thorough understanding of the memory mapping operation of the assembler program. Once this is understood, relative coding is a simple yet powerful programming technique. In the preceding section on symbolic coding is an explanation of the assembler program assignment of addresses to symbolic labels. This creates a common fixed point of reference between the programmer and the assembler program. By using this common fixed point of reference (the label) as a base, the programmer can specify other locations by their position relative to the base. For example, if the memory location which is to contain the information from card column 1 has been given a label of DETCD, then the memory location which is to contain the information from card column 5 would be 4 locations away. By specifying an operand of DETCD + 4, the programmer causes the assembler program to assign the actual address of the operand by mathematically adding the increment of 4 to the actual address of DETCD. The assembly system usually provides for decrements to symbolic labels as well as increments.

#### 2.5. MEMORY MAPPING

In order to assign the location of instructions and data, the assembler program must keep track of the locations that are used as the assembler processing is performed. To do this, the assembler program contains an Instruction Location Counter (ILC).

3 PAGE:

This is a program created device, not a piece of hardware. The loading of the assembler program itself usually sets the ILC to the actual address of the first memory location. The assembler program then causes the reading of the first source language instruction. This instruction is assigned to an actual address according to the present value of the ILC (in this case, the first memory location).

After the machine language for the instruction has been created by the assembler processing, a card is punched containing the machine language instruction. The number of locations that will be required to store the instruction is added by the assembler program to the value of the ILC creating a new value in the ILC. The assembler program then causes the next source language instruction card to be read. This instruction is assigned to an actual address according to the present value of the ILC. Assume that the actual address assigned to the preceding instruction had been R25/C1 and that the instruction was seven characters in length. (R25/C1 becomes the address of the MSL of the instruction.) The assembler program would then add seven (the number of locations for the first instruction) to the machine code equivalent stored in the ILC, and arrive at the machine code equivalent of R25/C8. This is the actual address assigned to the second instruction assembled.

The use of this procedure by the assembler program insures that the assignment of addresses to instructions follows the sequential access of the instructions by the computer when the object program is executed.

In addition to an ILC, an assembler program may contain a Data Location Counter (DLC). The DLC provides the programmer with the ability to assign locations to his data in an area of memory other than the area to be used for instructions. Instructions are usually assigned to locations starting with the first memory address (low-numbered locations) and proceeding in ascending sequence. Data is usually assigned to locations starting with the last memory address (high-numbered locations) and proceeding sequence.

#### 2.6. DECLARATIVE INSTRUCTIONS

An assembly system with an ILC and a DLC usually provides a set of pseudooperations which allow the programmer to establish and modify the value in the location counters. In addition to the pseudo-operations which manipulate the ILC and the DLC, there are usually other pseudo-operations which are required to instruct the assembler program as to the manner in which the assembly processing is to take place. These pseudo-operations are called declarative instructions. Unlike the previously mentioned pseudo-operations, declarative instructions, which are included in the source language deck, do not produce instructions in the object language deck. The declarative instructions are for the use of the assembler program during the assembly processing, and not for the computer as part of the object program.

An example of a declarative instruction would be one that updates the DLC. Assume the problem called for storing the contents of a header card to print headings on each new page. The programmer would label the source language instruction

4 Page:

line, write the mnemonic pseudo-operation code that decrements the DLC, and indicate the value of the decrement (the number of locations to be reserved for the data). Such a line of source code might appear as

LabelOP Code# of LocationsHDRCDDA80(stands for Define Area)

When this line of source coding is encountered, the DA tells the assembler program to refer to the DLC. The contents of the DLC are decremented by the number of locations to be reserved. The new value of the DLC is assigned as the address of HDRCD. In order to reference the information in the HDRCD area, the programmer can use relative coding.

#### 2.7. ASSEMBLER PROCESSING

An assembler program consists of a set of machine code instructions designed to produce specific results. As is the case with any computer program, the assembler program is designed to receive specific information prepared in a precise format. It is the responsibility of the programmer to prepare the source language program deck according to the rules of the assembly system. Any errors in the source language will produce incorrect results from the assembler processing.

In order to produce a complete object program, the assembler program must read the entire source program before producing any object instruction cards. During the reading of the source cards, the assembler program performs a preliminary analysis and converts or translates from source language to object language wherever possible, eg: the mnemonic operation codes. As each source card is read and the mnemonic operation code is translated, the assembler program determines the length of the instruction. The instruction is assigned to an actual address, and the ILC is updated. If the source language instruction has been assigned a symbolic address by the programmer, the label and the actual address are stored in a table. When these labels appear in the source language instructions as Operand addresses, the assembler program searches the label table using the symbolic address is substituted for the programmer's symbolic operand address.

The assembler program contains many other tables which it references for conversion of the source language to object language. After complete analysis and conversion of the source language, the assembler program causes the object program to be listed and punched.

PAGE

### 3. INTRODUCTION TO THE UNIVAC 1005 ASSEMBLY SYSTEM

Most of the programs for the UNIVAC 1005 will be written in the language of the UNIVAC 1005 Assembly System. The UNIVAC 1005 Assembly System provides the programmer with the necessary functions and convenience described in the preceding section. The use of instruction forms not described in this manual deviates from UNIVAC recommendations and must be the user's responsibility.

#### 3.1. TERMINOLOGY DEFINITIONS

Alphabetic means a letter from the English alphabet (A through Z)

Numeric means an Arabic numeral (0 through 9)

Alphanumeric means the entire 64 character set of the UNIVAC 1005 which includes letters, numbers, and special characters.

#### 3.2. CODING FORM

A coding form to be used to record the programmers instruction for subsequent key punching and processing by the UNIVAC 1005 Assembler program is shown in Appendix A. The coding form is set up in the same format as the punched card, and contains an indication of the card columns to be used for each field.

3.2.1. LABEL

Columns 1 through 5

This field is provided for the symbolic Labels assigned to those lines of coding which are referenced by the object program instructions. A Label may consist of from one to five characters (inclusive) and must begin in column 1 of the field. The first (left-most) character of a Label must be an alphabetic character. The remainder of the characters in a Label can be Alphabetic or Numeric. There is no limit to the number of Labels in a source program. However, if the number of labels exceeds the limit of the Assembler (approximately 40 labels for the 2 Bank Assembler and 310 labels for the 4 Bank Assembler) extra processing is required by the Assembler program. This is fully explained in the section on Operating the Assembler System. Five positions are provided in the Label field to allow meaningful assignment of programmer names. However, only the left-most three positions of a Label are significant to Assembler processing. The first three positions of each Label must be unique within a program. Extreme care should be taken when creating Labels.

2

Labels used in a single program must be unique and may appear only once in the Label field. Labels will be used in the Operand address portion of instruction lines and may appear there as often as necessary. The explanations in this manual of the use of the relative coding technique of increments and decrements to Labels should enable the programmer to address the data in his program without an excess of Labels.

The Label of a line of coding becomes the symbolic address for the left-most (MSL) position of the instruction, and is used whenever the instruction is referenced. Labels are also used for the lines of coding which define data areas, and become the symbolic address for the left-most (MSL) position of the area set aside for data.

Since not all lines of coding require a label, the field may be left blank. Some examples of labels are:

#### 3.2.2. OPERATION

Columns 6 through 10

OPERATION 6

This field is for the mnemonic operation codes provided by the Assembler. Operation codes are usually alphabetic. The majority of Assembler Operation codes are two characters in length, and must begin in column 6.

PAGE:

Some examples of Operation codes are:

| OPERATION                                    |

|----------------------------------------------|

| 6                                            |

| T, A                                         |

|                                              |

| A <sub>I</sub> D <sub>I</sub>                |

| S <sub>I</sub> U <sub>1</sub>                |

| MUU                                          |

| D <sub>1</sub> V <sub>1</sub>                |

| E <sub>1</sub> N <sub>1</sub> D <sub>1</sub> |

| 1                                            |

|               | OPERAND 1 |   |            |  |  |  |  |  |  |  |

|---------------|-----------|---|------------|--|--|--|--|--|--|--|

| l.<br>A.<br>* | FIELD A   | Ŧ | INC.<br>18 |  |  |  |  |  |  |  |

|               |           |   |            |  |  |  |  |  |  |  |

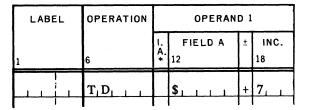

#### 3.2.3. OPERAND 1

This is a heading for those columns which are normally used to specify the address of the MSL or LSL of OP 1 depending on the ascending or descending mode of the instruction. This portion of the coding form is also used for other purposes, since not all Operations involve an Operand 1. The following description of the OPERAND 1 fields is based on the normal use to specify OP 1 addresses. A complete explanation of Operand 1 addressing begins in Section 3.3.

#### 3.2.3.1. IA Column 11

This column is used to indicate Indirect Addressing. When the OP 1 of an instruction is a primary address, an asterisk (\*) is placed in this column. It must be left blank at all other times.

#### 3.2.3.2. FIELD A Columns 12 through 16

This field of the form will normally contain a programmer's symbolic address for the location of instructions and data within his program. Any Labels which appear here must also appear in the LABEL field of some line of coding. Field A is a five position field for OP 1 Labels which always begin in column 12.

#### 3.2.3.3. ± INC Columns 17 through 20

These columns are normally used to indicate an increment to the address assigned to a Label. Increments are shown in decimal numbers. If column 17 contains a plus sign (+) the increment is added. If column 17 contains a minus

4

sign (-) the increment becomes a decrement and is subtracted from the Label address. Increments must be left-justified (begin in column 18). Some examples of OPERAND 1 addresses are:

|               | OPERAND 1       |   |            |  |  |  |  |  |  |  |  |

|---------------|-----------------|---|------------|--|--|--|--|--|--|--|--|

| ۱.<br>А.<br>* | FIELD A<br>12   | Ŧ | INC.<br>18 |  |  |  |  |  |  |  |  |

| t             |                 | - |            |  |  |  |  |  |  |  |  |

| +             | $D_1E_1T_1C_1D$ |   |            |  |  |  |  |  |  |  |  |

| +             |                 | - |            |  |  |  |  |  |  |  |  |

| $\vdash$      | $C_1A_1T_1$     | - | 1          |  |  |  |  |  |  |  |  |

| $\square$     |                 |   |            |  |  |  |  |  |  |  |  |

| *             | $I_1A_11_1$     |   |            |  |  |  |  |  |  |  |  |

|               | OPERAND 2     |   |                       |  |  |   |            |  |  |  |

|---------------|---------------|---|-----------------------|--|--|---|------------|--|--|--|

| I.<br>A.<br>* | FIELD B<br>22 | ± | INC. FIELD C<br>28 32 |  |  | ± | INC.<br>38 |  |  |  |

|               |               |   | 1                     |  |  |   |            |  |  |  |

#### 3.2.4. OPERAND 2

This is a heading for those columns which are normally used to specify the MSL and LSL addresses of Operand 2 in the instruction. This portion of the form is also used for other purposes. The following description of the OPERAND 2 fields is based on the normal use to specify OP 2 addresses. A complete description of OPERAND 2 addressing is found in Section 3.3.

#### 3.2.4.1. IA, FIELD B, $\pm$ INC Columns 21 through 30

These fields are normally used to specify the most significant location (MSL) of OP 2. The description of the contents of these fields is the same as the description of the contents of OPERAND 1.

#### 3.2.4.2. FIELD C, $\pm$ INC Columns 32 through 40

These fields are normally used to specify the least significant location (LSL) of OP 2.

NOTE: The indication for OP 2 Indirect Addressing is in column 21 only. Column 31 is not used as part of the specification for OP 2 LSL.

The description of FIELD C and  $\pm$  INC is the same as the corresponding fields of OPERAND 1.

PAGE

|    | COMMENTS |    |    |    |

|----|----------|----|----|----|

| 41 |          | 56 | 57 | 61 |

|    |          |    |    | 1  |

#### 3.2.5. COMMENTS

#### Columns 41 through 61

This portion of the form is provided to allow the programmer to include pertinent comments as to the purpose of the line or lines of coding. The comments are not considered by the Assembler processing and merely pass through to the printed and punched output. These columns are also used to indicate constant values which are to be included in the object program. This use is described in the section which covers Constants. Comments used for (1) DC operations, (2) Comma (,) operations, (3) In line constant operations (\*), and Comment Card operations may not extend beyond column 61. Comments for all other source code operations may not extend beyond column 56.

| CARD NO. |    |    |  |  |  |  |  |  |  |  |  |

|----------|----|----|--|--|--|--|--|--|--|--|--|

| PG LN NS |    |    |  |  |  |  |  |  |  |  |  |

| 62       | 64 | 66 |  |  |  |  |  |  |  |  |  |

|          |    |    |  |  |  |  |  |  |  |  |  |

|          | 4  |    |  |  |  |  |  |  |  |  |  |

#### 3.2.6. CARD NUMBER

Columns 62 through 66

This portion of the form is subdivided into three fields--PAGE NUMBER, LINE NUMBER, and INSERT NUMBER. These columns are used to indicate the number of the page of coding, and the number of the line from which the key punched card was produced. The Card Number field will assist the key punching effort as well as provide for the re-sequencing of the cards in the event the original sequence is disturbed. For proper assembly processing, it is necessary that the cards be read by the Assembler program in the sequence in which they appear in the source program. The Card Number field is used for external control purposes only. The Assembler program does not check the sequence as it reads the card.

The INSERT NUMBER column is provided as a facility to insert additional lines of coding in a source program, after the initial effort, without disturbing the sequence established by Page and Line Number.

During the assembly processing, the Assembler program assigns a consecutive number to the output cards in the object program deck. The Assembler assigned card number is punched into columns 62 through 65. Column 66 is blank in the output card.

#### 3.2.7. REMAINDER

The remainder of the card columns are not examined by the Assembler program, and are available for whatever use the programmer may determine. Such things as Job Number, Programmer's Initials, and Date may be included on a repetitive punching basis. These items will not appear in the object deck or on the output listing produced by the Assembler. Card Columns 67 through 73 are used for the object language instructions, and columns 74 through 80 are used for instructions to the Load program.

6

#### 3.3. OPERAND 1 ADDRESS SPECIFICATION

There are several methods of specifying operand addresses in the UNIVAC 1005 Assembly System. A description of the most commonly used methods follows below.

#### 3.3.1. Symbolic Address (Label) Specification

A definition of a symbolic address and some examples of Labels have been given in preceding sections. In the UNIVAC 1005 Assembly System, when a Label is used on a line of coding which defines a data area, that line of coding also includes the length of the area to be allocated to the data. The Label is then used to specify the MSL of the data area. By placing a plus sign (+) as a prefix to the Label when it is used as an operand address, the programmer can specify the LSL of the data area.

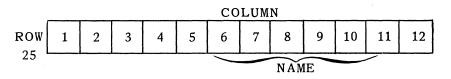

Example: A Declarative has been used to establish a data area of six positions with a Label NAME. Assume the data area has been allocated in memory as:

The following use of the Label NAME as an Operand 1 address of a TRF-D instruction would then cause a substitution of R25/C6, since a Label specifies the MSL of the area.

| LABEL | OPERATION                     |                          | OPERAN            | D 1 |            |

|-------|-------------------------------|--------------------------|-------------------|-----|------------|

| 1     | 6                             | I. FIELD A<br>A.<br>* 12 |                   | Ŧ   | INC.<br>18 |

|       | T <sub>i</sub> D <sub>i</sub> |                          | $N_1 A_1 M_1 E_1$ |     | <u>_</u>   |

The use of the plus sign (+) prefix to the Label NAME as an Operand 1 address in a TRF-A instruction would then cause a substitution of R25/C11, the LSL of the area.

| LABEL | OPERATION |                          | OPERAN              | D 1 |            |

|-------|-----------|--------------------------|---------------------|-----|------------|

| 1     | 6         | I. FIELD A<br>A.<br>* 12 |                     | Ŧ   | INC.<br>18 |

|       |           |                          | $+_1 N_1 A_1 M_1 E$ |     |            |

- 7 page:

- NOTE: The plus sign (+) can be used as a prefix to 5 character Labels by coding the first 4 characters only. The first 3 characters are significant to the Assembler program.

Labels must be coded starting in the left-hand position of Field A (column 12). If the plus sign (+) prefix is used, it must appear in column 12, and the Label starts in column 13.

3.3.2. Increments To Symbolic Addresses

When a Label has been placed on a line of coding, the programmer knows that the Assembler program is going to allocate the number of memory locations required by that line of coding, and will also assign an actual address to the Locations. The programmer does not know the *actual* address which will be assigned, but he knows that the use of the same Label will cause the Assembler program to substitute whatever actual address was assigned. Based on this knowledge, the programmer is then able to specify the address of locations relative to his line of coding. This is accomplished by indicating an increment or decrement to the Label in the ± INC field of the Coding form.

Assume that allocation has been made according to the previous example. The following coding would cause the Assembler program to produce these substitute addresses:

|               | OPERAND 1                                                     |   |            |  |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------|---|------------|--|--|--|--|--|--|--|

| 1.<br>A.<br>* | FIELD A                                                       | Ŧ | INC.<br>18 |  |  |  |  |  |  |  |

|               | N <sub>1</sub> A <sub>1</sub> M <sub>1</sub> E <sub>1</sub>   | + | 1,         |  |  |  |  |  |  |  |

|               |                                                               |   | <u>_</u>   |  |  |  |  |  |  |  |

|               | N <sub>i</sub> A <sub>i</sub> M <sub>i</sub> E <sub>i</sub>   | + | 5          |  |  |  |  |  |  |  |

|               | + <sub>1</sub> N <sub>1</sub> A <sub>1</sub> M <sub>1</sub> E | - | 1          |  |  |  |  |  |  |  |

|               |                                                               |   |            |  |  |  |  |  |  |  |

|               | $+_1N_1A_1M_1E$                                               | - | 5          |  |  |  |  |  |  |  |

|               | N <sub>I</sub> A <sub>I</sub> M <sub>I</sub> E <sub>I</sub>   | • | 3          |  |  |  |  |  |  |  |

|               |                                                               |   |            |  |  |  |  |  |  |  |

|               | + <sub>1</sub> N <sub>1</sub> A <sub>1</sub> M <sub>1</sub> E | + | 1          |  |  |  |  |  |  |  |

| = | address | R25/C7  | (MSL + 1)         |

|---|---------|---------|-------------------|

| = | address | R25/C11 | (MSL + 5 = LSL)   |

| = | address | R25/C10 | (LSL - 1)         |

| = | address | R25/C6  | (LSL - 5 = MSL)   |

| = | address | R25/C3  | (Outside of area) |

= address R25/C12 (Outside of area)

It should be noted that the use of increments is not restricted to addresses within the area allocated by the line of coding.

8 PAGE:

When an increment is used, a plus or minus sign must appear in column 17, and the amount of the increment (in decimal numbers) must start in column 18.

3.3.3. Decimal Addressing

As mentioned in Section 1.1., decimal addressing is provided for by the UNIVAC 1005 Assembly System. This technique allows the programmer to consider the layout of Input Output, instructions, and data in a consecutive sequential manner. This eliminates the problems associated with advancing that takes place in Row and Column addressing.

When a decimal address is specified to the Assembler program, the decimal number is converted to the two-character address required in the object language.

Decimal addresses take the following form:

**¤**N through **¤**NNNN

T = the special character lozenge which indicates to the Assembler

program that what follows is a decimal number.

N through NNNN = a decimal number which must be left-justified.

Indirect Addressing is allowed with decimal addressing.

Examples of decimal addressing

|               | OPERAN                                                                                                                                                                                                                             | DI | L          |                                                                                                                                                                                                                                                     |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I.<br>A.<br>* | FIELD A<br>12                                                                                                                                                                                                                      | Ŧ  | INC.<br>18 |                                                                                                                                                                                                                                                     |

|               | <b>¤</b> <sub>1</sub> 1 <sub>1</sub> 1<br><b>¤</b> <sub>1</sub> 8 <sub>1</sub> 0 <sub>1</sub> 1<br><b>¤</b> <sub>1</sub> 9 <sub>1</sub> 6 <sub>1</sub> 2 1<br><b>¤</b> <sub>1</sub> 1 <sub>1</sub> 9 <sub>1</sub> 2 <sub>1</sub> 2 |    |            | <ul> <li>= First location of Read Input Storage (R1/C1, Bank 1)</li> <li>= Last location of Read Input Storage (R3/C18, Bank 1)</li> <li>= First location in Bank 2 (R1/C1, Bank 2)</li> <li>= Last location in Bank 2 (R31/C31, Bank 2)</li> </ul> |

When decimal addressing is used, the lozenge  $(\pi)$  must appear in column 12. The decimal number must begin in column 13. The decimal number cannot exceed 4 digits, since the maximum address is  $\pi$ 3844 (four bank system).

3.3.4. Row And Column Addressing

Row and Column addressing is used when the programmer knows the actual address of the data. An actual or absolute address in the UNIVAC 1005 is specified by two 6-bit characters which are converted by the computer circuitry into Row, Column and Bank. Row and Column addressing in the UNIVAC 1005 Assembly System allows the programmer to specify Row, Column, and Bank eliminating the need to memorize or reference tables of the two-character codes required in the object program.

AC

PAGE

The following format is used to specify Row and Column address:

#### \$RRCCBn

- \$ is the indication to the Assembler program that what follows is a Row and Column address

- RR = the numeric Row Number (1 32)

- CC = the numeric Column Number (1 32)

- B must be placed in the ± column of the OPERAND field

- n = the numeric Bank Number (1 4)

Example:

|    | OPERANI                                                        | D 1 |            |

|----|----------------------------------------------------------------|-----|------------|

| I. | FIELD A                                                        | ŧ   | INC.<br>18 |

| f  | \$ 0 1 0 1                                                     |     | 1          |

| ┢  | \$ <sub>1</sub> 0 <sub>1</sub> 1 <sub>1</sub> 0 <sub>1</sub> 1 | D   |            |

| t  | \$10131118                                                     | в   | 1, ,       |

|    |                                                                |     |            |

| L  | \$13121311                                                     | в   | 211        |

| 1  | 1                                                              |     |            |

Indirect Addressing can be specified with machine-oriented addresses by placing an asterisk (\*) in the appropriate column (11 or 21) of the form.

The \$ must appear in column 12, 22, or 32, and the letter B must appear in column 17, 27, or 37. Increments to Row and Column address are not allowed.

Row and Column address is also used to specify the address of the Special Registers.

#### 3.3.5. Instruction Location Counter (ILC) Addressing

The ILC is the counter in the Assembler program which keeps track of the allocation of memory locations to instructions. The use of the current value of the ILC for addressing purposes is provided by the UNIVAC 1005 Assembly System. Proper use of this technique is based on the programmer's knowledge of the memory mapping process of the Assembler program. (See Section 2.5).

The \$ character, alone, in the left-hand position of Field A, Field B, or Field C of the coding form, instructs the Assembler program to use the current value of the MSL of the instruction being assembled as the address for the A, B, or C portion of the object instruction. An increment or decrement to the address currently in the ILC can also be specified in the  $\pm$  INC fields for each address. This increment or decrement does not change the value of the ILC itself. The maximum increment or decrement is 961.

Example 1: Assume the value of the ILC is #745 (R25/C1, B1) at the time the following descending transfer instruction is to be assembled.

+ 7 produces an address of 752 (745 + 7) which is the address which will be assigned to the next instruction.

Example 2: The following coding of a descending transfer instruction will cause the instruction itself to be transferred.

| LABEL |  | OPERATION                       |                          | OPERAND 1 |  |            |  |  |

|-------|--|---------------------------------|--------------------------|-----------|--|------------|--|--|

| 1     |  | 6                               | I. FIELD A<br>A.<br>* 12 |           |  | INC.<br>18 |  |  |

|       |  | T <sub>I</sub> D <sub>III</sub> |                          | \$        |  |            |  |  |

#### 3.4. OPERAND 2 ADDRESS SPECIFICATION

The rules for OPERAND 1 address specification (Section 3.3.) apply to OPERAND 2 address specification.

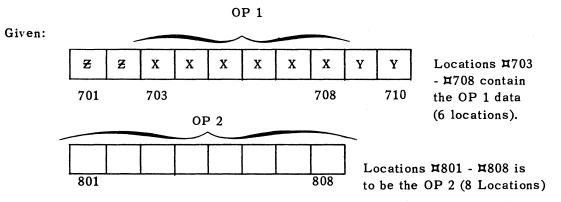

#### 3.4.1. Operand 2, Field C, Blank Addressing