# ILLIAC LIBRARY

PO-I1600-0000-A

# PRINCIPLES OF OPERATION

FOR

### ILLIAC IV PROCESSING ELEMENT MEMORY

BY

THEOFANIS ECONOMIDIS

**APRIL** 1973

INSTITUTE FOR ADVANCED COMPUTATION

AMES RESEARCH CENTER

MOFFETT FIELD, CALIFORNIA

# TABLE OF CONTENTS

| SECTION 1 | INTRODUCTION                          | 1-1   |

|-----------|---------------------------------------|-------|

| SECTION 2 | SUMMARY OF PEM LOGIC CHARACTERISTICS  | 2-1   |

|           | 2.1 CTµL CHARACTERISTICS              | 2-1   |

|           | 2.2 TT <sub>µ</sub> L CHARACTERISTICS | 2-6   |

| SECTION 3 | PEM ORGANIZATION                      | 3-1   |

|           | 3.1 CONTROL BOARD                     | 3-2   |

|           | 3.2 MEMORY BOARD                      | 3-40  |

|           | 3.3 SIGNAL BASE                       | 3-67  |

| SECTION 4 | POWER DISTRIBUTION                    | 4 - 1 |

# LIST OF ILLUSTRATIONS

| FIGURE |                                                            | PAGE  |

|--------|------------------------------------------------------------|-------|

| 1-1    | PEM Functional Interface                                   | 1-2   |

| 1-2    | ILLIAC IV PU Subunits                                      | 1-4   |

| 2-1    | CTµL AND-OR Gate Logic Level                               | 2-1   |

| 2-2    | Configuration of Transistors Employed in the CTuL Gate     | 2-2   |

| 2-3    | Configuration of CTµL AND-OR Gate Offset Level and         |       |

|        | Noise Immunity                                             | 2-3   |

| 2-4    | Basic Diagram of Two-Input CTµL AND-OR Gate (Fairchild)    | 2-5   |

| 2-5    | CTµL Clamping Circuit                                      | 2-5   |

| 2-6    | TTµL Basic Gate Circuit (Fairchild)                        | 2-6   |

| 2-7    | Diagram of a CTµL Output Driving a TTµL Input              | 2-7   |

| 2-8    | TTµL Logic Level Output (a), Input (b)                     | 2-8   |

| 2-9    | Block Diagram of MuL 4100                                  | 2-10  |

| 2-10   | Internal Configuration of MuL 4100                         | 2-11  |

| 2-11   | Basic Cell of MuL 4100 (Fairchild)                         | 2-12  |

| 2-12   | MμL 4100 Pin Configuration                                 | 2-15  |

| 3-1    | Exploded View of ILLIAC IV PEM                             | 3-1   |

| 3-2    | ILLIAC IV Control Board Functional Block Location Diagram  |       |

|        | (Component Side)                                           | 3-3   |

| 3-3    | Address Format in a One-Quadrant Array                     | 3-4   |

| 3-4    | Address Chain from CU to PEM                               | 3-7   |

| 3-5    | Logic Representation of the Address Chain                  | 3-8   |

| 3-6    | X Binary Address Decoder and Combinatorial Address Driver  |       |

|        | (X1 Line)                                                  | 3-18  |

| 3-7    | X1-X10 Address versus Initiate at Control Board            | 3-19  |

| 3-8    | Y Binary Address Decoder and Combinatorial Address Driver  |       |

|        | (Y1 Line)                                                  | 3-22  |

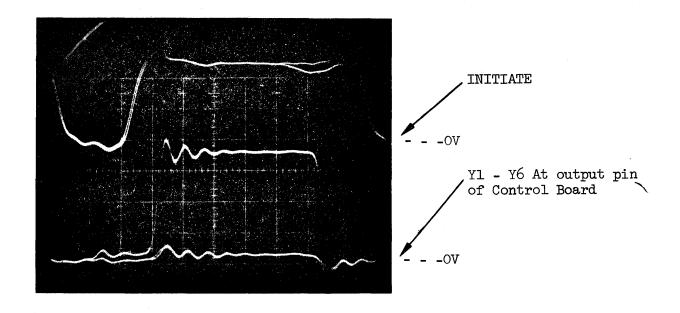

| 3-9    | Y1-Y8 Address versus Initiate at Control Board             | 3-23  |

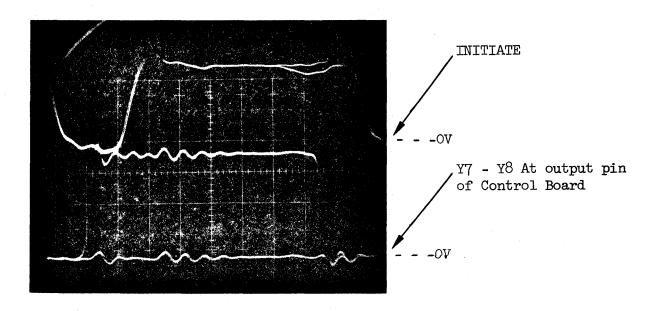

| 3-10   | CL1A and CL1B Logic                                        | 3-28  |

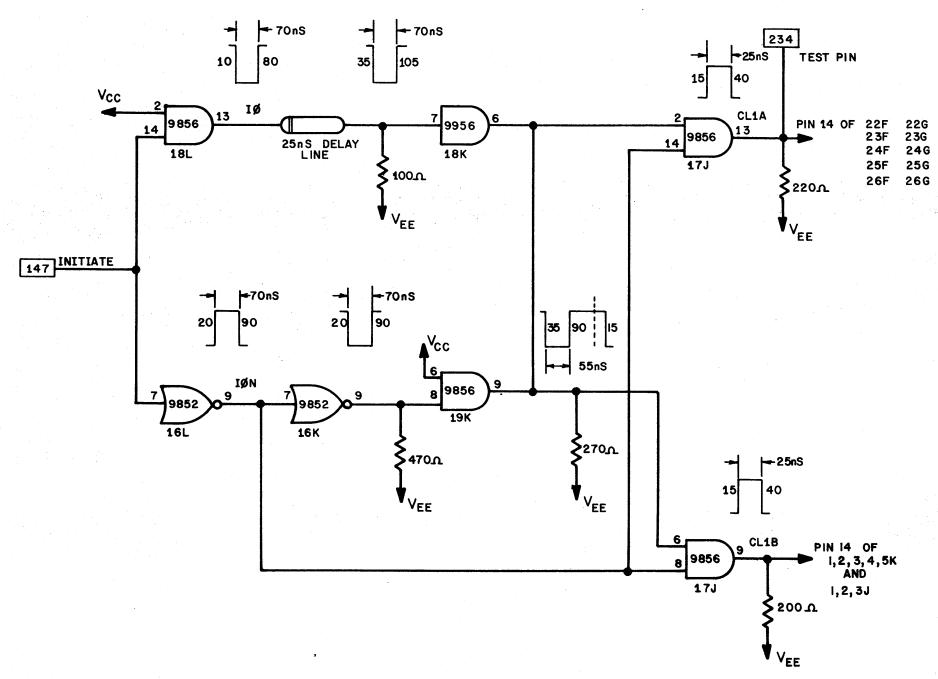

| 3-11   | CL2A and CL2B Logic                                        | 3-29  |

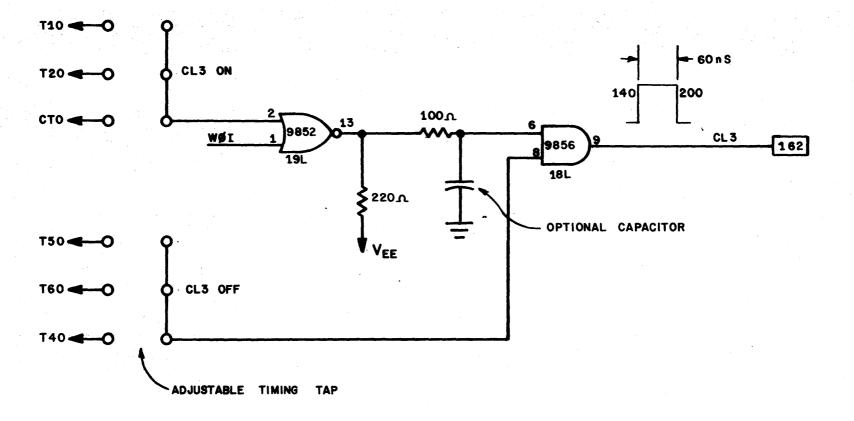

| 3-12   | Data Out Enable Signal (CL3) Logic                         | 3-31  |

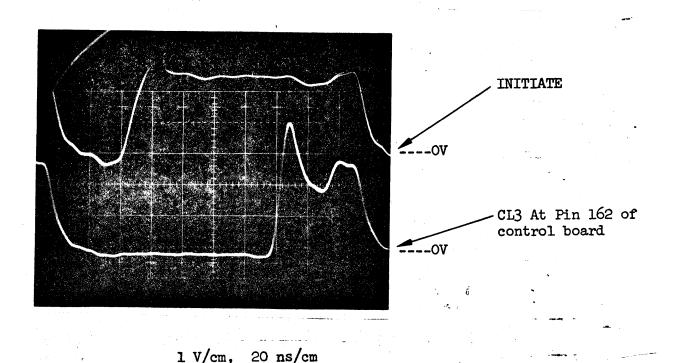

| 3-13   | CL3 versus Initiate                                        | 3-32  |

| 3-14   | Data Out Hold Signal (CL4) Logic                           | 3-34  |

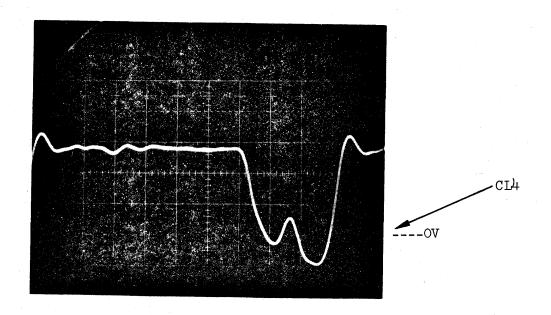

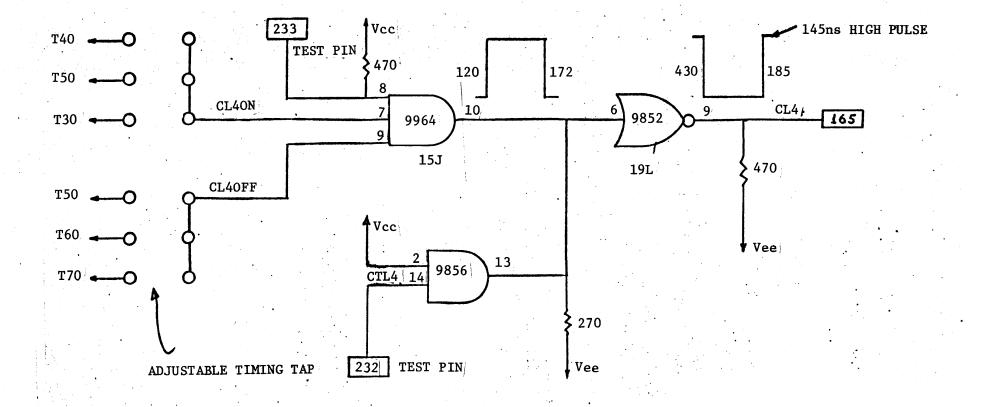

| 3-15   | CL4 at Control Board Pin 165                               | 3-33  |

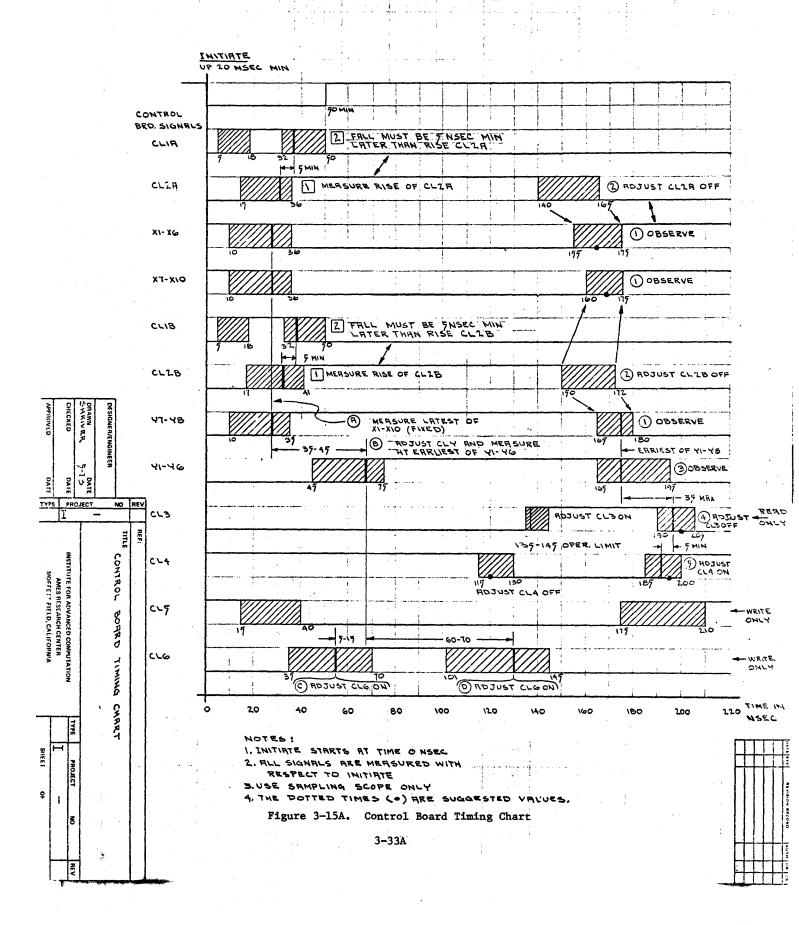

| 3-15A  | Control Board Timing Chart                                 | 3-33A |

|        |                                                            |       |

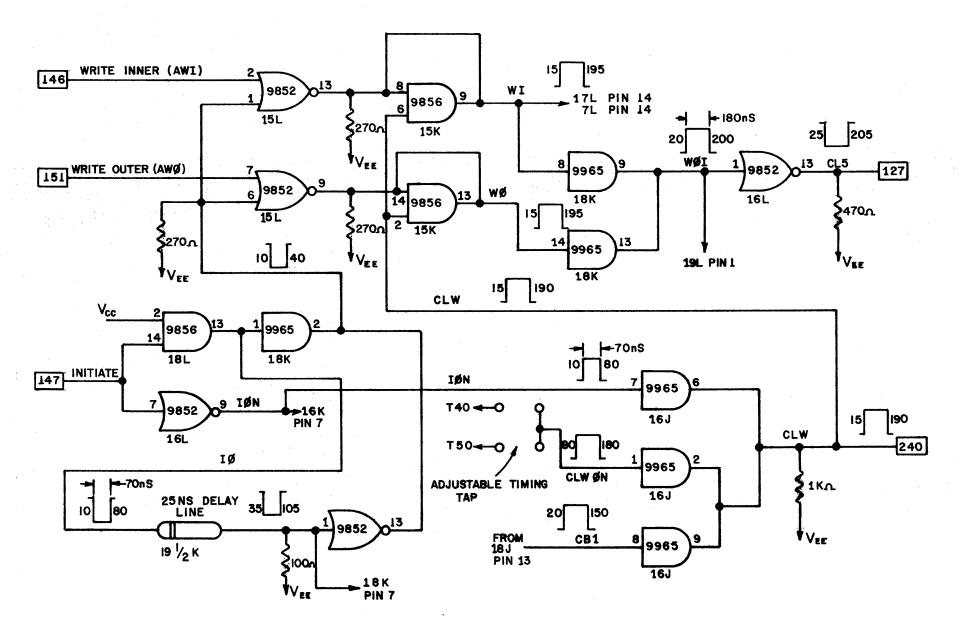

| 3-16   | WRITE Driver Enable Signal (CL5) Logic                     | 3-36  |

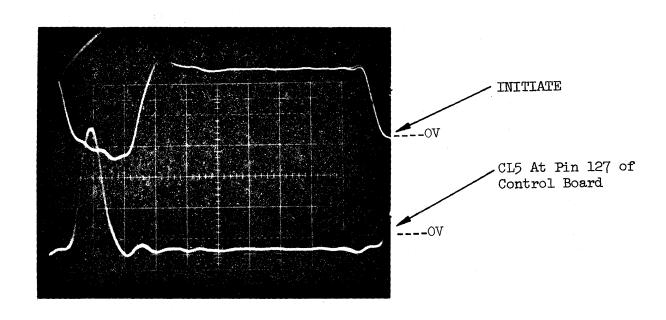

| 3-17   | CL5 versus Initiate                                        | 3-37  |

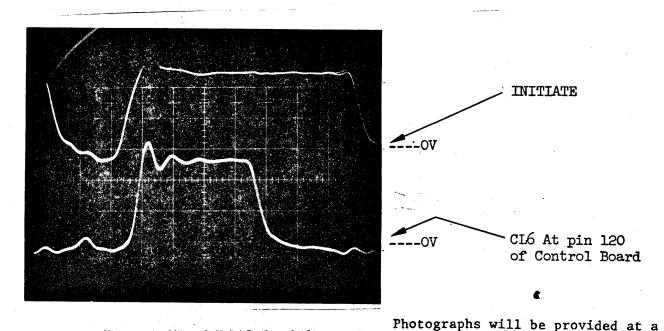

| 3-18   | WRITE Enable Signal (CL6) Logic                            | 3-39  |

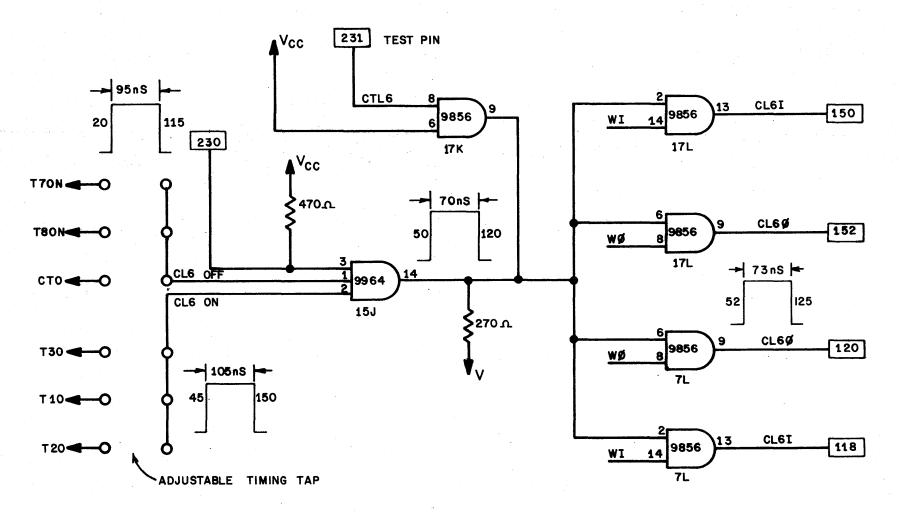

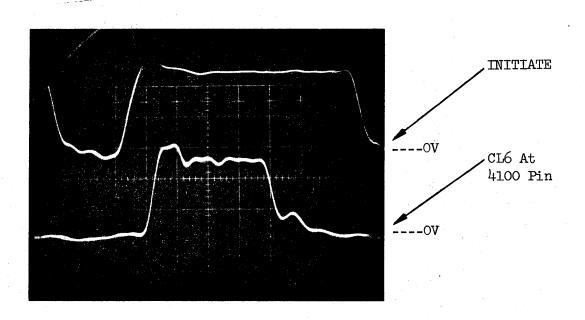

| 3-19   | Photo of CL6 versus Initiate                               | 3-38  |

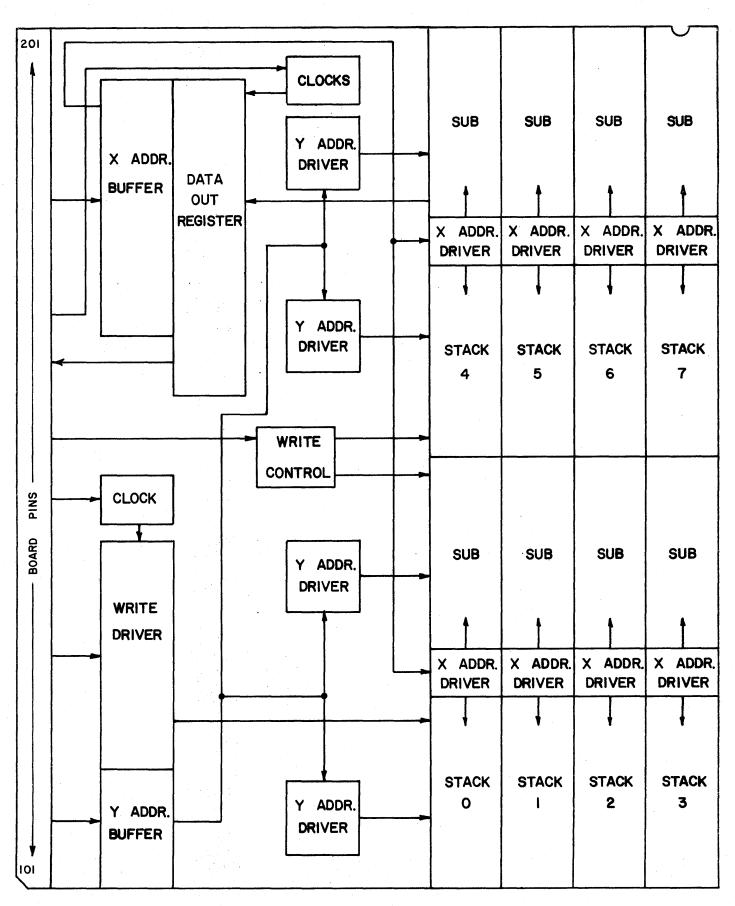

| 3-20   | ILLIAC IV Memory Board Functional Block Diagram            | 2 / 1 |

|        | (Component Side of Board)                                  | 3-41  |

| 3-21   | X Address Buffer and Driver (One Address Line & Control)   | 3-43  |

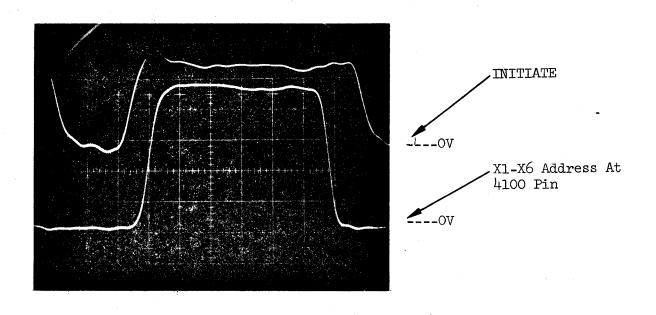

| 3-22   | X1-X6 Address at Memory Board MuL 4100 Pin versus Initiate | 3-44  |

| 3-23   | Y Address Buffer and Drivers (One Address Line & Control)  | 3-45  |

| 3-24   | Y1-Y6 Address at Memory Board versus Initiate              | 3-50  |

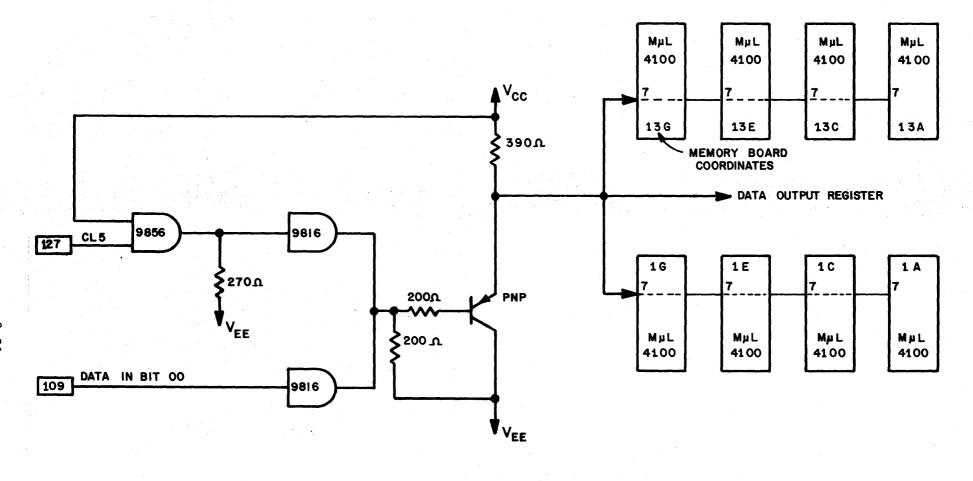

| 3-25   | Memory Board WRITE Control                                 | 3-53  |

| 3-26   | WRITE Control Signal CL6 at Memory Board MµL 4100 Pin      | 2 51  |

|        | versus Initiate                                            | 3-54  |

| 3-27   | Memory Board WRITE Driver (One Bit Line)                   | 3-56  |

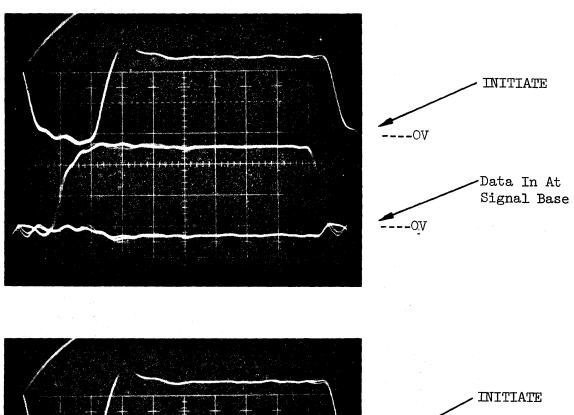

| 3-28   | Data In During WRITE Operation                             | 3-57  |

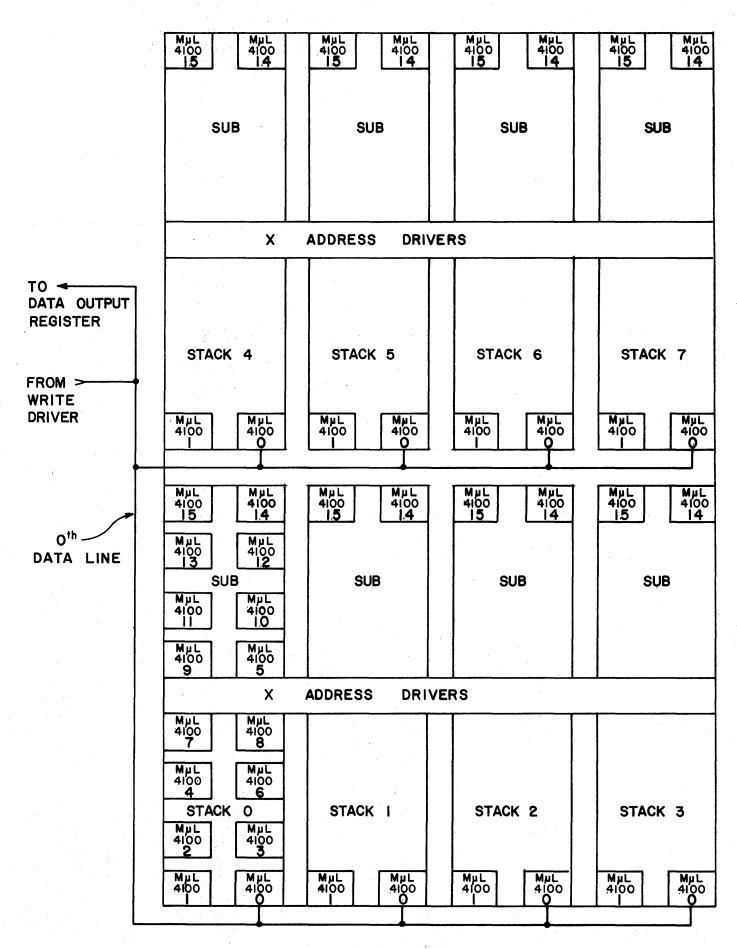

| 3-29   | Memory Board Oth Data Line Layout                          | 3-58  |

| FIGUR | RE:                                                 | PAGE |

|-------|-----------------------------------------------------|------|

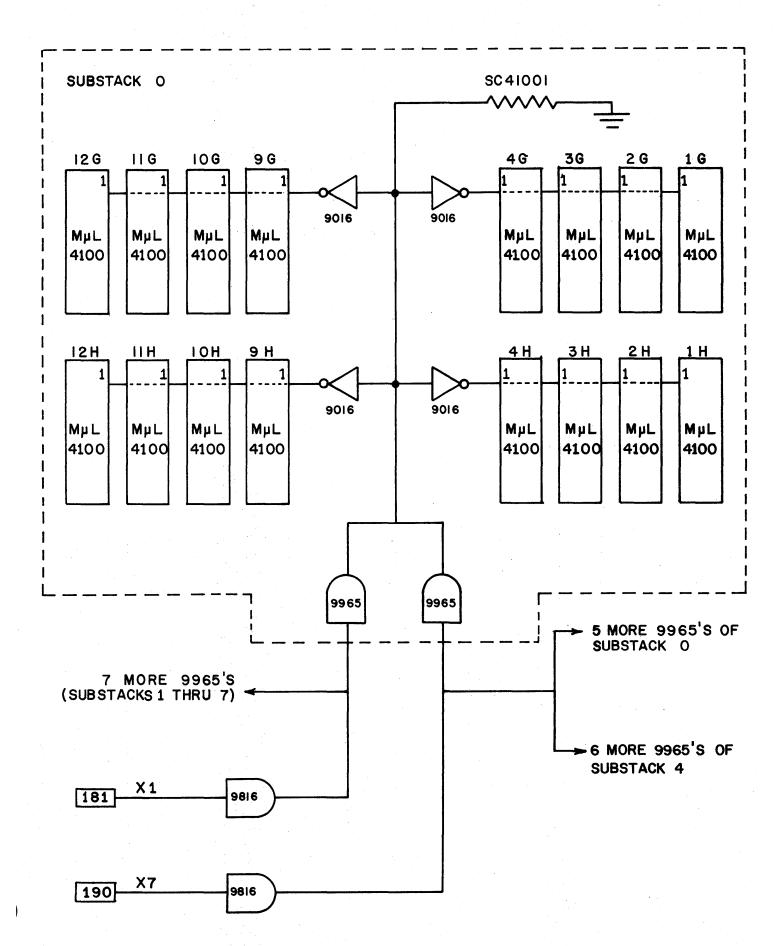

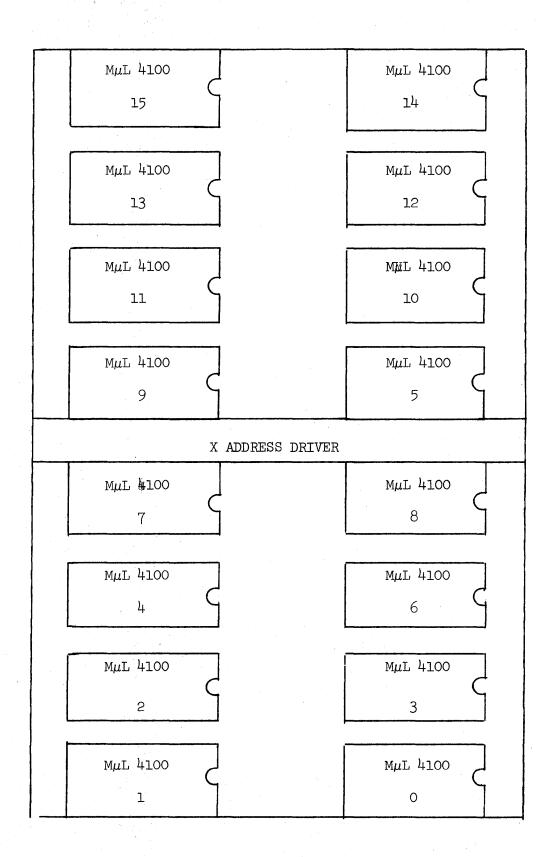

| 3-30  | Memory Board Substack Layout                        | 3-59 |

| 3-31  | Memory Board Data Output Register (One Bit Line)    | 3-63 |

| 3-32  | Data Out During READ Operation                      | 3-66 |

| 3-33  | PEM-MLU Interface, (a) WRITE and (b) READ Operation | 3-69 |

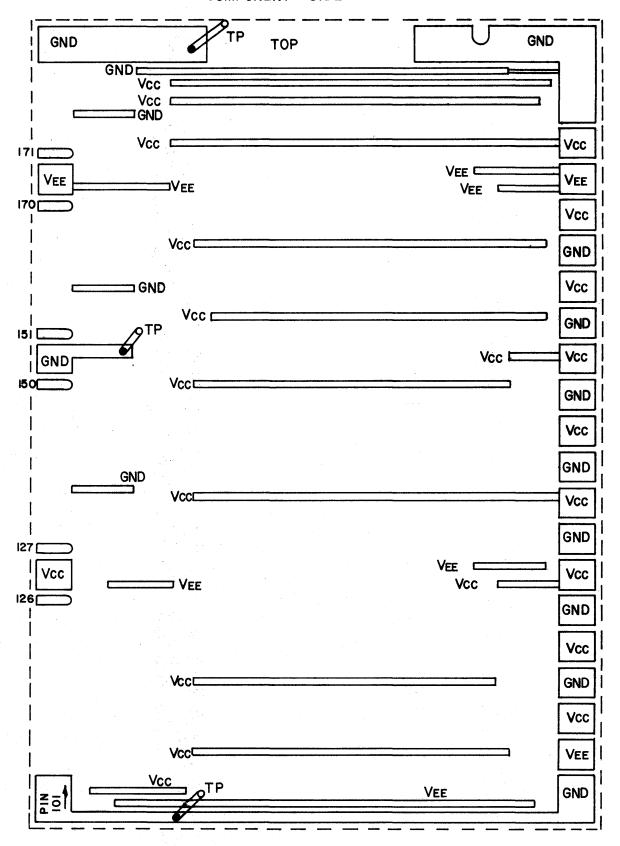

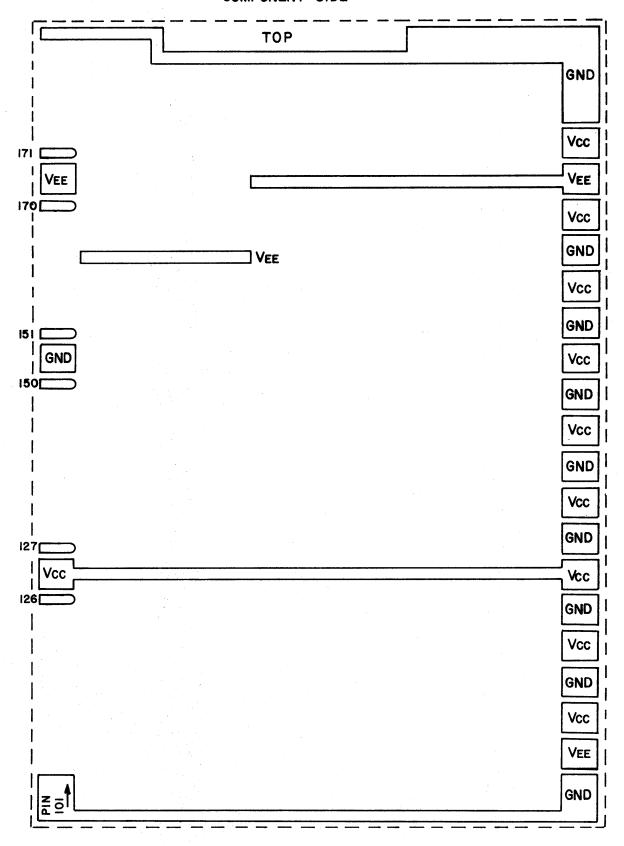

| 4-1   | Memory Board Power Bus Configuration                | 4-3  |

| 4-2   | Control Board Power Bus Configuration               | 4-4  |

| 4-3   | Control Board Adjustable Timing Taps                | 4-5  |

# LIST OF TABLES

| TABLE |                                                                          | PAGE |

|-------|--------------------------------------------------------------------------|------|

| 2-1   | CTµL Wired-OR Truth Table                                                | 2-2  |

| 2-2   | Two-Input CTµL Gate Truth Table                                          | 2-4  |

| 2-3   | Truth Table of Trigger Flip-Flop                                         | 2-9  |

| 3-1   | One-Quadrant Array Configuration                                         | 3-4  |

| 3-2   | Example of One-Quadrant Address Format                                   | 3-5  |

| 3-3   | Signal Name Representation                                               | 3-5  |

| 3-4   | Binary and Combinatorial Address Interface                               | 3-12 |

| 3-5   | Logic Redefinition of Binary Address                                     |      |

| 3-6   | Truth Table of Binary and Combinatorial X Address                        | 3-14 |

| 3-7   | Truth Table of Binary and Combinatorial Y Address                        | 3-15 |

| 3-8   | Truth Table of Binary Address and Substack Select Controls (X Direction) | 3-16 |

| 3-9   | Control Board Timing Generator Input/Output Signals List                 | 3-25 |

| 3-10  | X Address Interface between Control Board and Memory Board               | 3-46 |

| 3-11  | Y Address Interface between Control Board and Memory Board               | 3-49 |

| 3-12  | Numbering Scheme of Memory Board I/O Data Bits                           | 3-60 |

| 3-13  | Address and Control Signals from Up Converter Cards to                   |      |

|       | PEM Control Board                                                        | 3-70 |

| 3-14  | WRITE Data from Up Converter Cards to PEM (OUTER Word)                   | 3-71 |

| 3-15  | WRITE Data from Up Converter Cards to PEM (INNER Word)                   | 3-72 |

| 3-16  | READ Data from PEM to MIR Cards (OUTER Word)                             | 3-73 |

| 3-17  | READ Data from PEM to MIR Cards (INNER Word)                             | 3-74 |

| 3-18  | WRITE Data from PEMX to PEM (OUTER Word)                                 | 3-75 |

| 3-19  | WRITE Data from PEMX to PEM (INNER Word)                                 | 3-76 |

| 3-20  | READ Data from PEM to PEMX (OUTER Word)                                  | 3-77 |

| 3-21  | READ Data from PEM to PEMX (INNER Word)                                  | 3-78 |

#### SECTION 1

#### INTRODUCTION

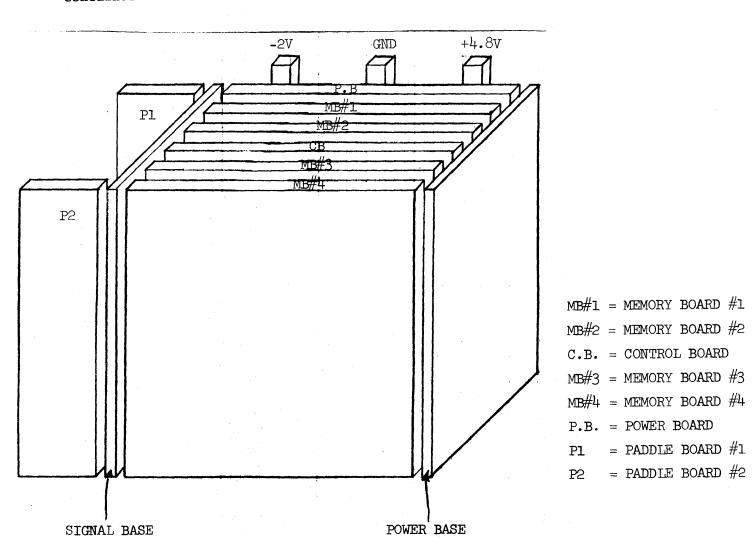

The Processing Element Memory (PEM), which is a subunit of the ILLIAC IV Processing Unit (PU), is used to store 2048 words, each of which is 64 bits long. It consists of four memory boards, one control board, one power board, one power base, and one signal base.

Each memory board is organized into eight substacks, each of which consists of 16 Fairchild MuL 4100 integrated circuit (IC) packages. Each MuL 4100 contains 256 storage cells, which are organized as 256 one-bit words. To access a full memory word (64 bits), one substack on each board is accessed. Write operations affecting only 32 bits of a storage location are also possible; these are carried out by selecting substacks on only two memory boards instead of all four.

The control board provides binary address decoding and all necessary control and timing signals for operation of the PEM. The power board and base are used to provide the necessary power to the PEM; this power originates in external power supplies. The signal base provides all of the signal interconnections between the PEM and the MLU.

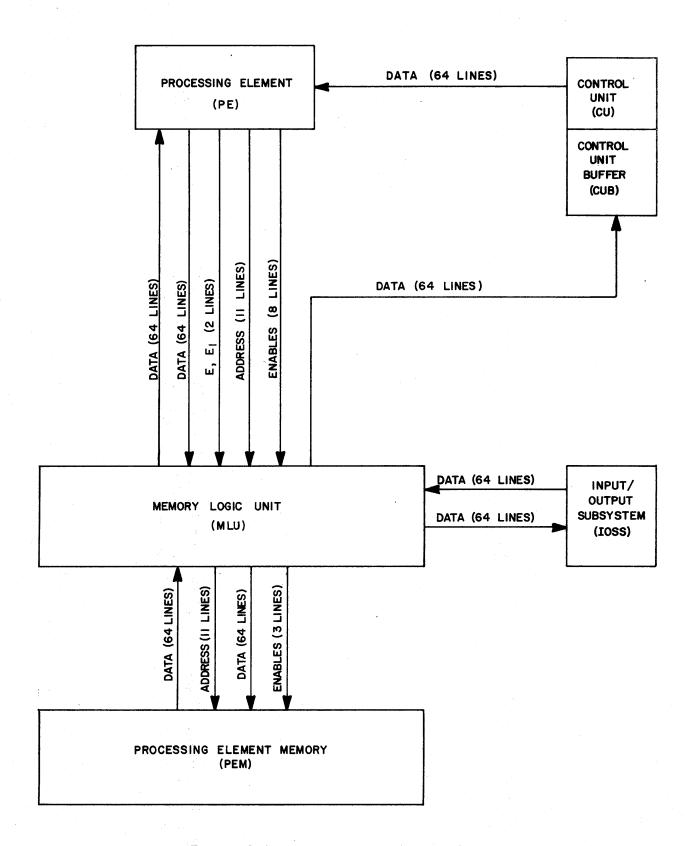

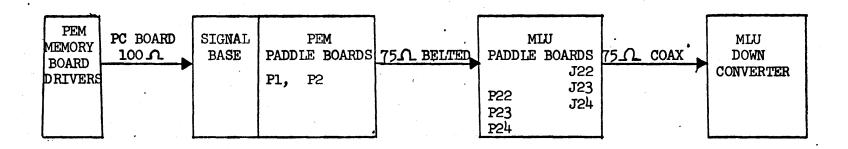

PEM activity is limited to read and write operations. Data that is written into the PEM may originate at the Control Unit (CU), Processing Element (PE), or Input/Output Subsystem (IOSS). CU write operations are carried out through the PE. Data read from the PEM may be sent to the Control Unit Buffer (CUB), PE, or IOSS. All data movement between the PEM and these other units is carried out through the Memory Logic Unit (MLU). The MLU also provides the PEM with the memory initiate, read/write controls, and address information used by the PEM to execute a read or write operation. Figure 1-1 illustrates the functional relationship between the PEM and the MLU, CU, CUB, PE, and IOSS. As shown by this block diagram, the PEM interfaces solely with the MLU.

Figure 1-1. PEM Functional Interface

The PEM-to-MLU interface consists of 64 data lines into the PEM (for write data), 64 data lines out of the PEM (for read data), 11 address lines into the PEM, and one memory initiate line and two write control lines into the PEM (enables).

The 11 address lines are used to access one of the 2048 memory locations in the PEM. These lines are derived, via the PE and MLU, from bits 7 through 17 (PEM subaddress field) of the Memory Service Unit (MSU) configuration control registers (MC1 and MC2), which are part of the CU. Details regarding the origin and routing of this address information are provided in subsection 3.1.1 of this manual as well as in the ILLIAC IV Systems Characteristics and Programming Manual published by Burroughs Corporation.

The memory initiate line (one of three enables) is generated by MLU memory control logic when the MLU receives a memory select signal from the PE. The PEM uses the memory Initiate input to enable its control and timing logic. All PEM timing is referenced to the arrival of the memory Initiate signal. Details regarding the generation of this signal are included in the MLU Principles of Operation Manual.

The two write control inputs are used by the PEM to control its write logic for 32-bit mode or 64-bit mode write operations. One write control input controls the write logic for data bits 00 through 07 and 40 through 63 (designated the outer word) and the other controls the write logic for data bits 08 through 39 (designated the inner word). If both write control inputs are true, the write logic on all four memory boards is enabled, allowing a full 64-bit word to be stored. If only one write control input is true, the write logic on only two of the memory boards is enabled (memory boards 1 and 2 for the inner word or memory boards 3 and 4 for the outer word), allowing only 32 bits to be written. Details regarding the use of the write control signals in the PEM are provided in subsection 3.2.2 of this manual. The generation of these signals by the MLU is discussed in the MLU Principles of Operation Manual.

Address information for read and write memory cycles is provided by the CU through the PE.

Power for the PEM logic circuits is provided by an external power supply via a power supply shunt regulator. There is a separate regulator for each PU.

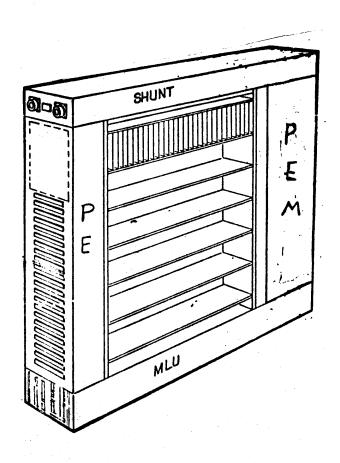

The PEM is housed as an integral part of its PU. Figure 1-2 illustrates the physical relationship of a PEM to the other major components of its PU, namely a PE, MLU, and power supply shunt regulator.

Figure 1-2. ILLIAC IV PU Subunits.

### SECTION 2

# SUMMARY OF PEM LOGIC CHARACTERISTICS

The PEM uses three families of integrated circuits: Complementary Transistor Micrologic (CT $\mu$ L), Transistor Transistor Micrologic (TT $\mu$ L), and Memory Micrologic (M $\mu$ L).

#### 2.1 CTµL CHARACTERISTICS

The  $CT\mu L$  circuits have the following general characteristics:

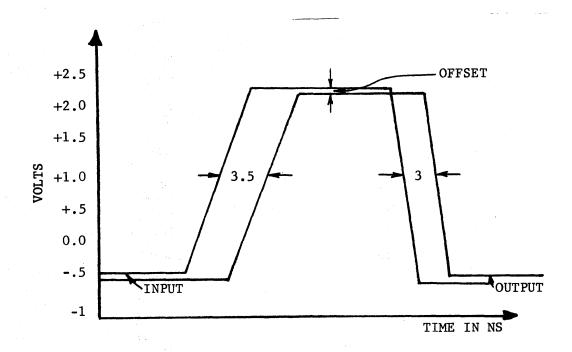

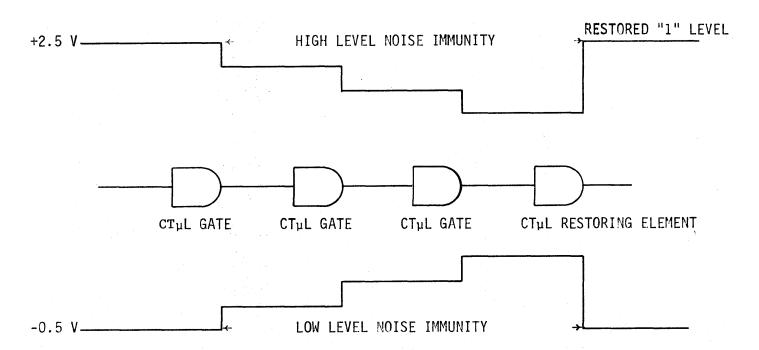

a) <u>High Speed</u>. Each logic decision is represented by a square pulse with a typical propagation delay of 3.0 ns (Figure 2-1) and logic levels from -0.5 V to +2.5 V at 25°C ambient temperature.

Figure 2-1. CTµL AND-OR Gate Logic Level.

b) Wired-OR. Two or more CTµL outputs may be wired together to form an OR function (Table 2-1).

Table 2-1. CTµL Wired-OR Truth Table

| CT <sub>µ</sub> L ( | OUTPUT | OR       |

|---------------------|--------|----------|

| 1                   | 2      | FUNCTION |

| 0                   | 0      | 0        |

| 0                   | 1      | 1        |

| 1                   | 0      | 1        |

| 1                   | 1      | 1        |

|                     |        | 1        |

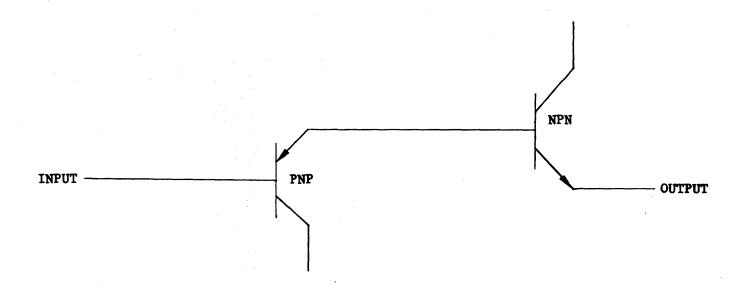

c) <u>Positive Logic</u>. Since the basic gate employs the complementary PNP and NPN transistors (Figure 2-2), it can be said that the CTµL is a form of current mode logic and retains the flexibility of discrete AND-OR functions (1·1 = 1, 1·0 = 0, 0·0 = 0, where 1 represents a logic high and 0 represents a logic low).

Figure 2-2. Configuration of Transistors Employed in the CTµL Gate.

d) Nonsaturating Circuit. The transistors are biased in such a way that they are always ON, thus eliminating the need to overcome a threshold; this makes it possible for the output to follow the input almost immediately (3 ns delay). The CTµL AND-OR gate can be considered as a noninverting amplifier, whose voltage gain is less than one. Since it is impossible to force the base-emitter voltages of the complementary PNP and NPN transistors to follow all the possible conditions, the output levels are offset (Figure 2-1) from the input. The amount of offset is a function of loading, temperature, and input voltage. A signal passing through a succession of CTµL AND-OR gates is most offset in the first gate, the offset decreasing sequentially on succeeding gates because of the reduced input level. However, in order to preserve sufficient system noise immunity, appropriate noise immunity (voltage) levels must be reestablished at intervals by inserting, once every three CTµL AND-OR gates, a restoring element such as inverter, buffer, or flip-flop (Figure 2-3). The current gain of the CTuL family is considerable, making them especially useful for driving loads involving a considerable amount of input capacitance.

Figure 2-3. Configuration of CTµL AND-OR Gate Offset Level and Noise Immunity.

e) Two Power Supplies. The  $CT\mu L$  gates require two power supplies with voltages:

1.

$$V_{cc} = +4.5 \text{ V } \pm 10\%$$

applied at pin 12

2.

$$V_{ee} = -2.0 \text{ V } \pm 10\%$$

applied at pin 11

(Pin 5 is connected to ground.)

CTµL AND-OR gates, functioning on positive logic with a high level of approximately +2.5 V and a low level of about -0.5 V, provide a true (high) output, when all inputs are true (high). If any input is false (low) the output will also be false (low). Table 2-2 shows the logic output of a CTµL AND-OR gate as a function of the inputs. The gate is called AND-OR because its output follows the rules of the logic AND function and it can be tied to any other CTµL element output to perform the wired-OR function (Table 2-1).

Table 2-2. Two-Input CTµL Gate Truth Table

| INI              | PUT              | OUTPUT      |

|------------------|------------------|-------------|

| A                | В                | С           |

| 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>0<br>0 |

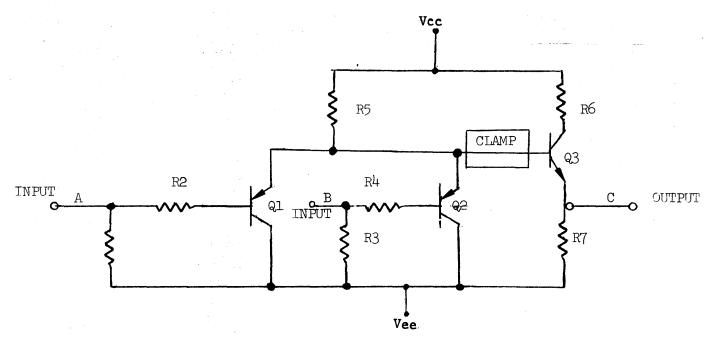

The significant feature of this type of logic circuit is the use of both PNP and NPN transistors to provide a noninverted logic function. In the static state, with no connection to inputs A and B (Figure 2-4), resistors R1 and R2 provide a forward current bias path for the base of Q1 sufficient to hold the transistor ON. Q2 will be held ON in the same manner by the base current through R3 and R4. With both PNP transistors thus conducting, a negative potential of approximately -2 V, less the voltage dropped across Q1 and Q2 (in parallel), is applied to the base of Q3. Q3 is thus forward biased just enough to keep it out of the cut-off state.

Figure 2-4. Basic Diagram of Two-Input CTuL AND-OR Gate (Fairchild).

As long as either input is left open (held negative), that transistor (Q1 or Q2) will remain in the ON state, thus holding the output at a low level. When positive signals are applied to both inputs, the output will be positive, but it always tends to "follow" whichever of the inputs is the least positive.

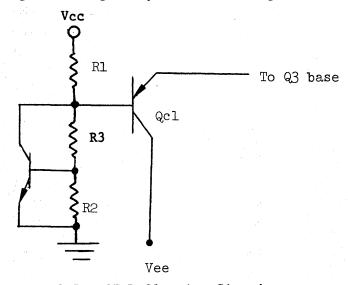

Saturation of Q3 by applying a relatively large positive signal to both inputs is prevented by the clamping circuit shown in Figure 2-5. If the signal, applied to the base of the output transistor Q3 (Figure 2-4), exceeds the positive limit determined by the clamp bias divider, the associated emitter diode of Qc1 (Figure 2-5) will begin to conduct, thus drawing off the excess current to keep the base at a potential of -2 V. The output transistor Q3 is thus held between the limits of cut-off and saturation, minimizing switching delays due to storage time.

Figure 2-5. CTuL Clamping Circuit.

#### 2.2 TT<sub>µ</sub>L CHARACTERISTICS

The TT $\mu$ L family of devices provides greater noise immunity. It is also more effective when driving high-capacitance loads, since in both logic states it provides low output impedance. Only one type of TT $\mu$ L device is used in the PEM: the TT $\mu$ L 9016.

The TTµL 9016 circuit has the following general characteristics:

- a) <u>Inverting Element</u>. The TTµL 9016 package is an inverter. If the input is high the output will be low and vice versa.

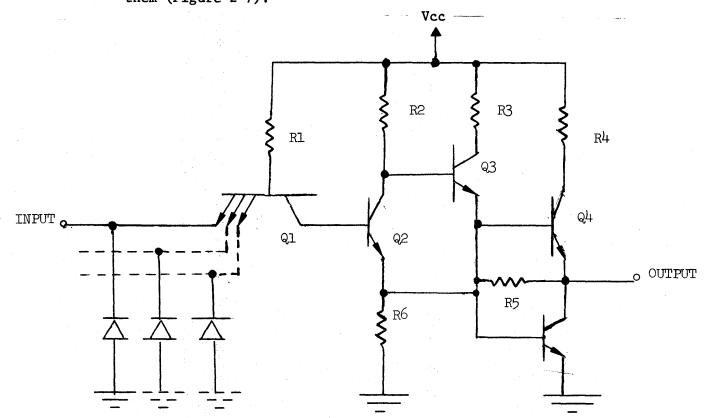

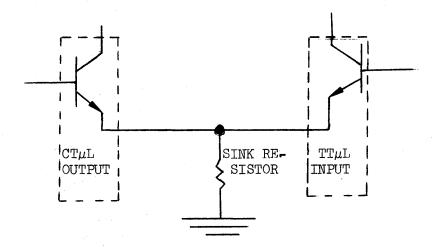

- The input is a current source and the output is a current sink. The input to a TTµL circuit is connected to an emitter of an NPN transistor (Figure 2-6), the base of which is connected to V<sub>cc</sub>. It therefore acts as a current source in that current will tend to flow out of the input toward ground if a path is provided. The output of a TTµL circuit acts as a current sink by providing a very low impedance path to ground through a saturated transistor. In order to drive a TTµL input with a CTµL output (also a current source), a "current sink" resistor is connected to ground between them (Figure 2-7).

Figure 2-6. TTuL Basic Gate Circuit (Fairchild).

Figure 2-7. Diagram of a CTµL Output Driving a TTµL Input.

When the CTµL output transistor is turned ON (is fully conducting), the impedance presented by it is sufficiently low to provide as much current as this resistor can conduct. The TTµL input, having a much higher impedance, is therefore effectively deprived of its current-sink path and the input voltage level is held high.

When the CTµL output transistor is turned OFF (almost cut off), it presents a relatively higher impedance path to the sink resistor, thereby allowing current to flow from the TTµL input circuit through the resistor to ground.

- c) Medium Speed. The TTµL device is relatively slower than the CTµL device for the following reasons:

- 1. It requires additional time for threshold detection.

- 2. It is a saturating element in that the output transistor switches completely from the cut-off state to the saturated state. The storage time of the output transistor in either the cut-off or saturated state introduces an extra delay into the response of the output to any change in the input. The total circuit delay amounts to approximately 7 ns per logic decision.

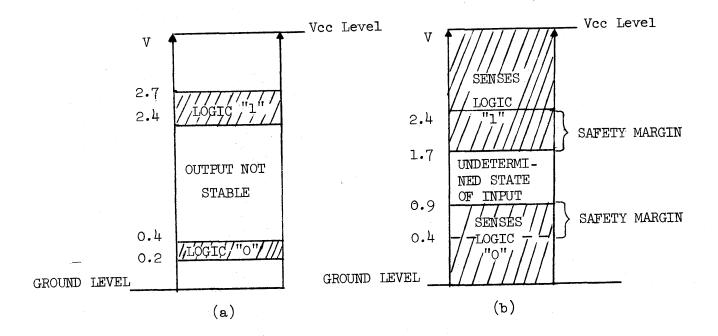

d) Excellent Noise Immunity. The Fairchild TTµL device (9016) provides high noise immunity and has the ability to reshape pulses of marginal amplitude. Figure 2-8 provides information about the characteristics of the output and input of a TTµL device, respectively, and safety margins for noise signals.

Figure 2-8. TTµL Logic Level Output (a), Input (b).

When the signal represented by Figure 2-8(a) becomes an input to a  $TT\mu L$  device, the safety margin due to noise pulse amounts to about 0.7 V for logic ONE and 0.5 V for logic ZERO, as shown in Figure 2-8(b).

#### 2.3 Mul 4100 CHARACTERISTICS

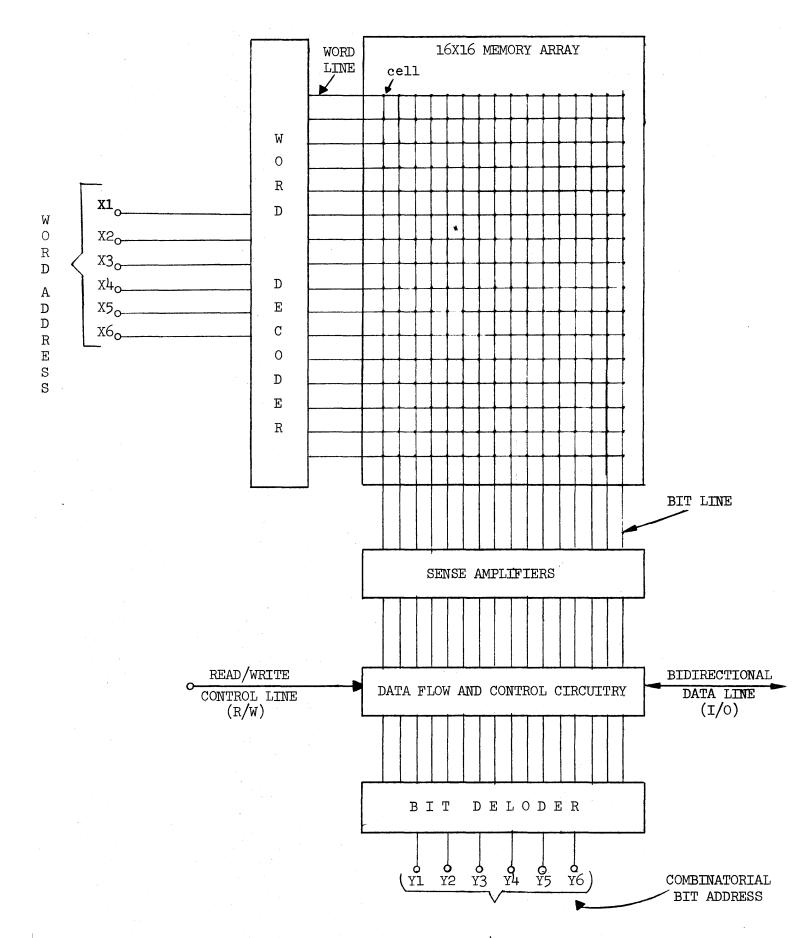

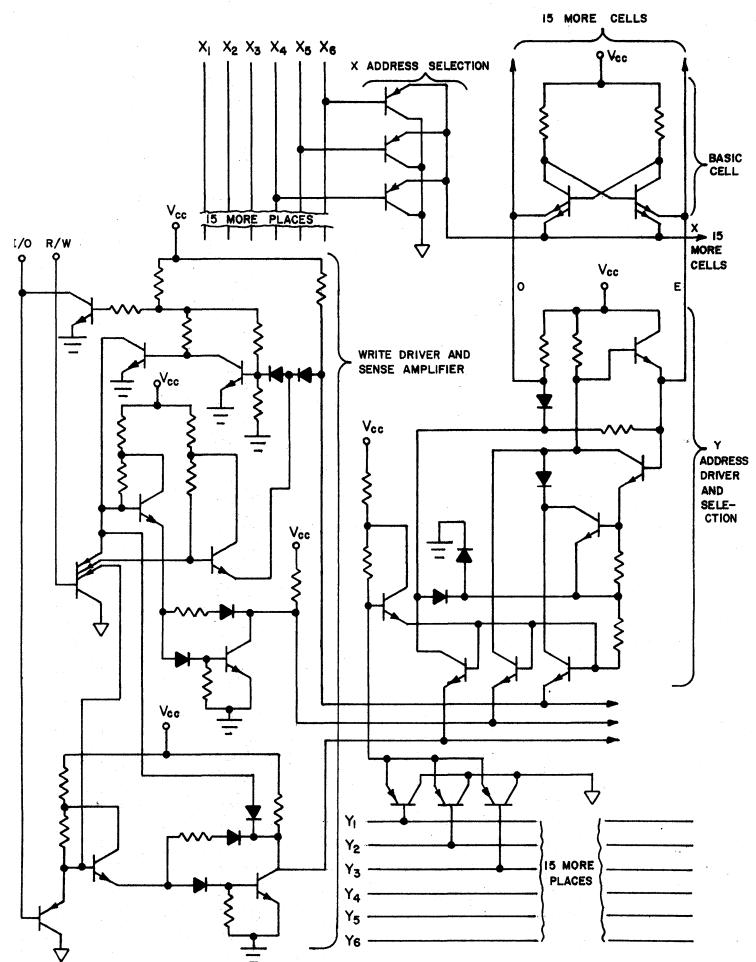

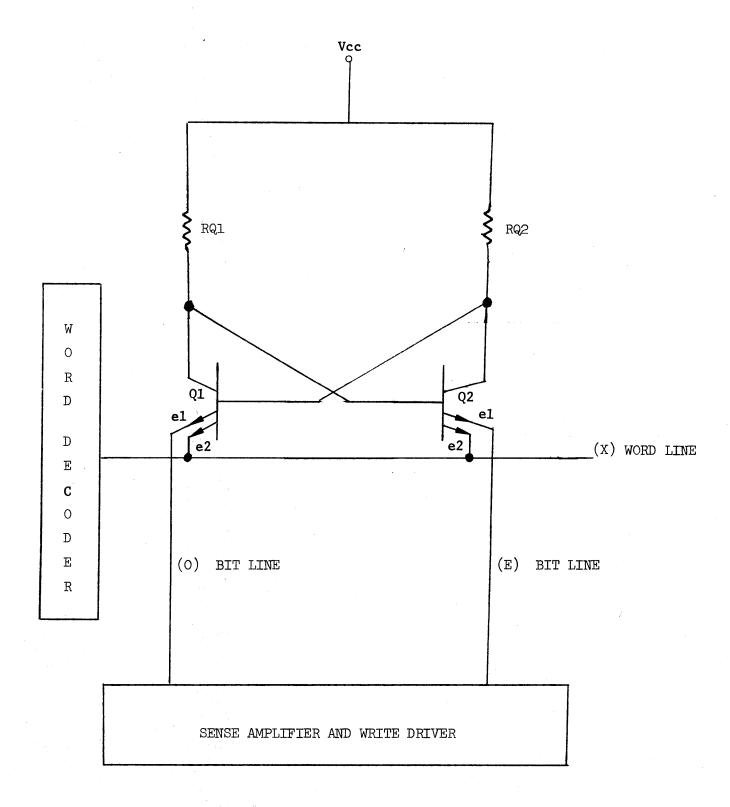

The nucleus of the PEM is the memory package M $\mu$ L 4100 (Figure 2-9) built by Fairchild Camera and Instrument Corporation. The package can provide 256 bits organized as a 16×16 array of flip-flops [1]<sup>1</sup>. This array and associated read/write circuits are shown in Figure 2-10.

The basic cell of the memory chip (Figure 2-11) consists of a flip-flop. One of the transistors in the flip-flop is ON (conducting) while the other one is forced to remain in the OFF state (not conducting). When the "OFF" transistor is forced to conduct by an external signal, the transistor which is already in the ON state returns fo the OFF state. Therefore, the flip-flop can be in either one of two states (ON or OFF); it will remain in one of the states until an external signal causes it to change states.

The flip-flops can be used to store logic ONE's or ZERO's. If T<sup>t</sup> represents the value of the external signal that changes the state of the flip-flop at time t, then the state of the flip-flop at time t+1 is given by the equation:

$$\mathbf{x}^{t+1} = \mathbf{T}^{-t} \cdot \mathbf{x}^{t} + \mathbf{T}^{t} \cdot \mathbf{x}^{-t}$$

which is an exclusive OR, as shown by the truth table of Table 2-3.

Table 2-3. Truth Table of Trigger Flip-Flop

| Тţ | χt | Xt+1 |

|----|----|------|

| 0  | 0  | 0    |

| 0  | 1  | 1    |

| 1  | 0  | 1    |

| 1  | 1  | 0    |

A number in square brackets refers to a reference document listed at the end of this report.

Figure 2-9. Block Diagram of MµL4100

Figure 2-10. Configuration of MµL 4100.

Figure 2-11. Basic Cell of M $\mu$ L4100 (Fairchild)

In order to select one of the 256 memory cells for a read or write operation, the  $X_i$  (i = 1, 2, 3, 4, 5, 6) and  $Y_j$  (j = 1, 2, 3, 4, 5, 6) address lines are enabled simultaneously. These lines operate on the "3-out-of-6 code" (combinatorial address); this code is discussed in subsection 3.1.1.

The  $\mathbf{X}_i$  address lines select one of the 16 word lines inside the memory package, while the  $\mathbf{Y}_i$  address lines select the appropriate write driver on a write cycle or the appropriate sense amplifier on a read cycle. The read/write control line controls the direction of the data flow.

NOTE To avoid any confusion, it must be understood that the term OFF as used in subsequent discussion means that the transistor under discussion is in a very low state of conduction compared to that of the ON transistor.

#### Write Logic ONE

When the memory cell is selected, line X (Figure 2-11) is raised. In this case E is also raised and both emitters of Q2 (Q2el and Q2e2) become positive; consequently, conduction through Q2 decreases. Thus the potential at the base of Q1 rises and Q1 starts conducting more heavily. This reduces the amount of current available to the base of Q2, because the impedance presented by the collector of Q1 is less than that presented by the base of Q2. At this point, line O is more negative than line E and current flows through the emitter Q1el to line O. Transistor Q1 will remain in the ON state, and in this state the cell is regarded as containing a logic ONE.

#### Write Logic ZERO

To write a logic ZERO in the cell discussed above, line X must also go high. This time, however, line O is more positive than line E and Q2 is turned ON. This forces Q1 to be turned OFF.

#### READ

When the cell is to be read, only line X becomes positive and thus any current which is going to flow is now flowing through Qlel and Q2el. A sense amplifier (Figure 2-11) determines which one of the two lines (0,E) draws more current and therefore detects the state of Q1 and Q2. In the first case discussed, where a logic ONE was stored and Q1 is in

the ON state, line O is more positive and the sense amplifier will detect a logic ONE. In the second case, line E is more positive and a logic ZERO is detected.

#### Unselected Cell

When a cell is not selected either for reading from or writing into, lines X and E become negative. Current flows through Qlel, Qle2, Q2el, and Q2e2, but because at the instant that lines X and E became negative one of the transistors was conducting more heavily than the other, and therefore the base of the latter was deprived of sufficient current to make it conduct as heavily as the former, it is held in a less conductive state than that of the former. Conversely, the low current path thus provided through the collector of the latter permits a relatively large base current to flow through the former, thereby holding this transistor in the ON state and the other in the OFF state.

\* \* \*

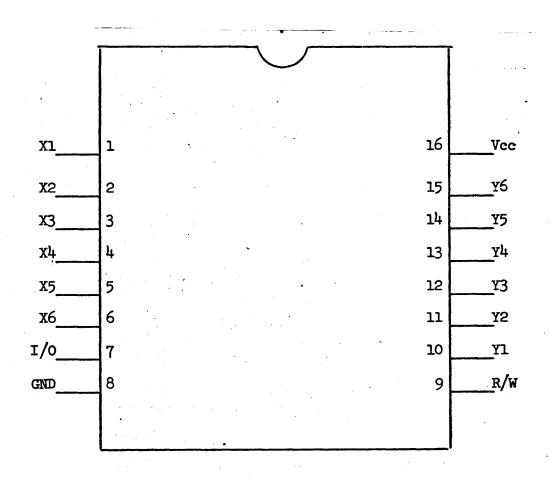

The MµL 4100 is a high speed, LSI, bipolar 256-bit, read/write random access, nondestructive readout memory device, hermetically sealed in a 16-lead, dual in-line package (Figure 2-12). Its basic characteristics are:

- a) <u>TTµL Compatible</u>. The MµL 4100 can be driven directly by a TTµL device.

- b) Maximum Read Access Time. Time from  $X_i$  (i = 1, 2, 3, 4, 5, 6) address at the pins of MµL 4100 until the data is available at I/O pin of MµL 4100 is about 100 ns.

- c) The  $Y_{j}$  (j = 1, 2, 3, 4, 5, 6) address is delayed from the  $X_{i}$  (i = 1, 2, 3, 4, 5, 6) address by approximately 35-45 ns.

- d) The read/write pulse is required to be present only during the write operation, while during the read operation it is just a low level.

- e) The write pulse is required to precede the  $Y_j$  (j = 1, 2, 3, 4, 5, 6) address by at least 10 ns.

- f) The write pulse may be removed about 40 ns prior to removing the  $X_i$  and  $X_i$  addresses from MµL 4100.

- g) Output Wired-OR Capability. Figure 2-10 shows that the I/O line of MµL 4100 is connected to an uncommitted collector. This feature allows the collectors (I/O lines) of several MµL 4100's to be "OR-tied", thereby providing for word expansion.

- h) Partial Decoding on Chip. The binary address is converted into the combinatorial address, which is decoded inside the M $\mu$ L 4100 in order to select the proper word and bit lines.

- i) Power Requirements.  $V_{cc} = +4.8 \text{ V } \pm 10\%$  and ground.

Figure 2-12. MµL 4100 Pin Configuration.

### SECTION 3

# PEM ORGANIZATION

Figure 3-1 shows the physical relationship of the four memory boards, one control board, one power board, one power base, and one signal base in each PEM. The two paddle boards that are connected to the signal base are also shown. The functional responsibilities of the principal logic contained on these boards are discussed in the following subsection.

Figure 3-1. Exploded View of ILLIAC IV PEM.

#### 3.1 CONTROL BOARD

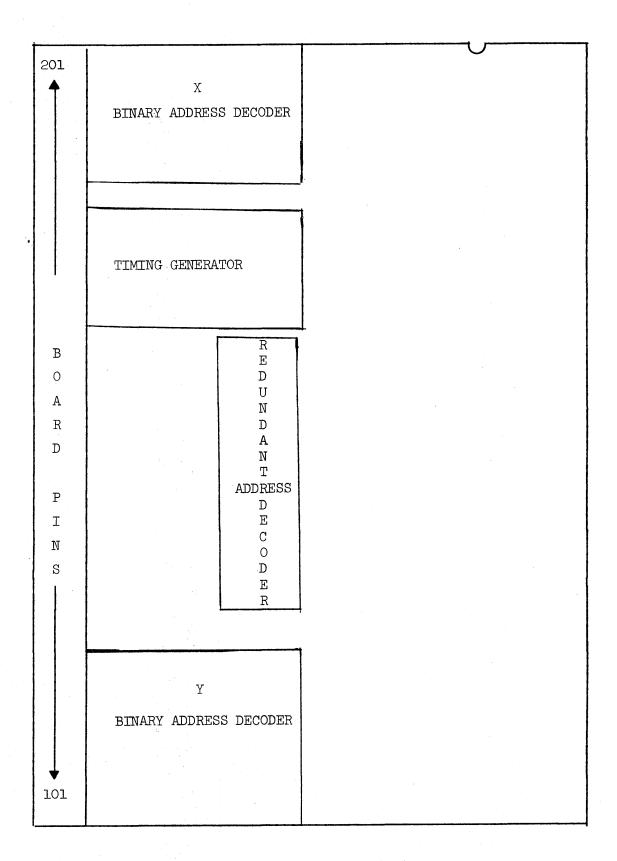

The control board logic provides the control and timing signals needed by other PEM logic to carry out a read or write operation; the logic responsible for this is called the timing generator. Another set of logic on the control board is responsible for translating the 11 bits of binary address received from the MLU into the X and Y components of a combinatorial address. This logic is referred to as the X and Y combinatorial address decoders. Figure 3-2 is a block diagram showing these functional blocks.

#### 3.1.1 Binary Address Decoding

Before examining the control board's address decoding logic, the two address schemes (binary and combinatorial) will be discussed.

#### PEM Binary Address

Addressing in ILLIAC IV is mainly a function of the Memory Service Unit (MSU) whose users are the Input/Output Subsystem (IOSS), the Final Station (FINST), and the Instruction Look-Ahead (ILA). The FINST and ILA are sections of the control unit. The FINST requests and their purposes are as follows:

- a) FINST Own Request: This is for PE read/write operation request.

- b) FINST Request A: This is for the Advanced Station (ADVAST) LOAD(X), BIN(X), or STORE(X) request.

- c) FINST Request B: This is a request for transfer from PE to ACAR (in the MLU that has been described as a transfer operation from PE to CUB).

The address as it is defined by the MSU Configuration Control registers (MCl for instruction addresses and MC2 for data addresses) has the format shown in Figure 3-3 at FINST and ICR. Table 3-1 describes the one-quadrant array configuration.

Figure 2-2. ILLIAC IV Control Board Functional Block Location Diagram (Component Side).

| 26                      | 717 | 1820                              | 2123               | 24                               |

|-------------------------|-----|-----------------------------------|--------------------|----------------------------------|

| FOR FUTURE<br>EXPANSION |     | SELECTS THE PEM WITHIN THE P.U.C. | SELECTS THE P.U.C. | HALF WORD DESIG-<br>NATOR IN ICR |

Figure 3-3. Address Format in a One-Quadrant Array.

Table 3-1. One-Quadrant Array Configuration

|   | -    | ← PROCESSING UNIT CABINET (PUC) |    |    |    |    |    |    |  |

|---|------|---------------------------------|----|----|----|----|----|----|--|

|   | 0    | 1                               | 2  | 3  | 4  | 5  | 6  | 7  |  |

| 1 | 00   | 01                              | 02 | 03 | 04 | 05 | 06 | 07 |  |

|   | 10   | 11                              | 12 | 13 | 14 | 15 | 16 | 17 |  |

| P | 20   | 21                              | 22 | 23 | 24 | 25 | 26 | 27 |  |

| E | 30   | 31                              | 32 | 33 | 34 | 35 | 36 | 37 |  |

| M | 40   | 41                              | 42 | 43 | 44 | 45 | 46 | 47 |  |

|   | 50   | 51                              | 52 | 53 | 54 | 55 | 56 | 57 |  |

|   | - 60 | 61                              | 62 | 63 | 64 | 65 | 66 | 67 |  |

|   | 70   | 71                              | 72 | 73 | 74 | 75 | 76 | 77 |  |

|   |      |                                 |    |    |    |    |    |    |  |

For this discussion, bits 7 through 23 are of primary interest. Bit 24 is used only to designate which half of the word is used (when it is ZERO the left half of the word is used) and bits 2 through 6 are for future memory expansion; if four quadrants were used, two extra bits would be needed to define which one of the four quadrants was to be accessed. Table 3-2, for illustration, shows specified address and components selected according to the format of Figure 3-3.

Table 3-2. Example of One-Quadrant Address Format

| ADDRESS BITS | SELECTED CON | PONENTS IN | THE QUADRANT |

|--------------|--------------|------------|--------------|

| (7-23) 8     | PUC          | PEM        | SUBADDRESS   |

| 000000       | 0            | 0          | 0000         |

| 0 0 0 1 1 1  | 1            | 1          | 0001         |

| 3 7 7 7 7 7  | 7            | 7          | 3 7 7 7      |

As shown by the array configuration of Table 3-1, there are eight PU cabinets in the quadrant, each one containing eight PEM's. Every PU is assigned a two-digit octal number. The first digit (0-7) specifies the PEM in the PU cabinet and the second digit (0-7) specifies the PU cabinet and the quadrant. PE requests will select eight PUC's and all the PEM's in each PUC. Therefore, only 11 bits are sent on to the PEM (bits 7-17). These 11 bits are called the PEM subaddress.

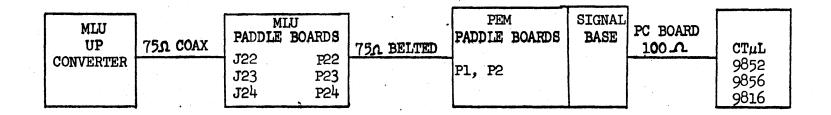

The PEM subaddress leaves the MSU, passes through the FINST and, using the common data bus (CDB), it reaches the PE memory address register (MAR). The address may be indexed by S or X registers of the PE before it gets into the MAR. From the MAR, the address passes through the UP Converter of the MLU for  $CT\mu L$  compatibility and then is applied to the paddle board of the PEM. On PE and MLU signal lists, address bits A5 through A15 are designated as WO5 through W15 (Table 3-3).

Table 3-3. Signal Name Representation

| CONTROL     | LUNIT |       | PROCESSING ELEMENT |       |       | MEMORY LOGIC UNIT |       |       |  |

|-------------|-------|-------|--------------------|-------|-------|-------------------|-------|-------|--|

| SIGNAL NAME | LEVEL | LOGIC | SIGNAL NAME        | LEVEL | LOGIC | SIGNAL NAME       | LEVEL | LOGIC |  |

| TVW-WXX0    | HIGH  | 1     | PYW-WXX0           | HIGH  | 0     | MYW-WXX0          | HIGH  | 1     |  |

| TVW-WXXO    | LOW   | 0     | PYW-WXXO           | LOW   | 1     | MYW-WXXO          | LOW   | 0     |  |

| TVW-WXX1    | HIGH  | 0     | PYW-WXX1           | HIGH  | 1     | MYW-WXX1          | HIGH  | 0     |  |

| TVW-WXX1    | LOW   | 1     | PYW-WXX1           | LOW   | 0     | MYW-WXX1          | LOW   | 1     |  |

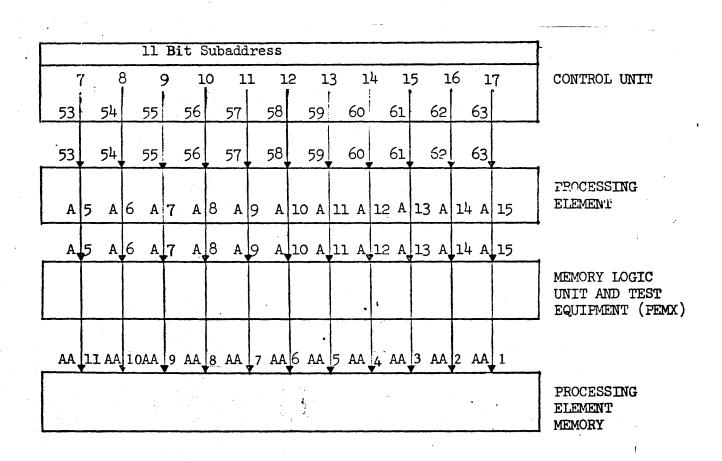

Figure 3-4 shows that each address bit changes name three times until it arrives at the paddle board of the PEM. There is no particular reason for this, other than that the design of the different subunits of ILLIAC IV took place at different times and by different people, all of whom complied with the requirements of the design for 11 bits of address, but assigned names they felt fit best. Apparently the numbering of the subaddress in the CU follows the one-quadrant address format; in PE and MLU it follows the four-quadrant address format, and in the paddle board of the PEM an extra A was added to differentiate the signals inside the PEM from those outside the PEM. This last distinction is called for because, as is shown later, there is a logic redefinition of the address bits inside the PEM. This logic redefinition results from the fact that, while the MLU follows the negative logic convention (Table 3-2), inside the PEM (control board) positive logic is used (Figure 3-5). In order to achieve this redefinition and be consistent with the logic notation of the CU and PE, keeping in mind that all the signals to the PEM pass through the UP Converter of the MLU for CTuL compatibility wherein an inversion takes place, the address bits are buffered and inverted in the control board to provide both the TRUE and COMPLEMENT forms; both forms are needed to decode the binary into the combinatorial address (3-out-of-6 code). It must be mentioned, though, that the CU follows a negative logic notation and, therefore, if its output is a high level signal, it is considered to represent a logic ZERO. signal, however, is brought through the CDB into the PE where it is inverted and then applied to the MAR, the output of which is brought into the MLU. An inversion takes place in the MAR; consequently, its output is the same level as the input to the operand select gates. The PE follows a positive logic notation, but, in order to be consistent with the CU and MLU signal notation, the input and output signals have been assigned the names shown in Table 3-3.

Figure 3-4. Address Chain from CU to PEM.

Figure 3-5. Logic Representation of the Address Chain

#### PEM Combinatorial Address

The PEM storage locations are accessed by using a 3-out-of-6 combinatorial code. This addressing scheme was selected in an attempt to minimize the number of interconnections required between the memory package and the external drivers. In order to reduce the number of external interconnections, decoding logic is provided inside the memory package. This logic decodes the combinatorial address provided by the binary address decoders.

The six least significant bits of the binary address are used for the X direction and the remaining five most significant binary address bits are used for the Y direction. However, in order to access the cell inside the MµL 4100 there are actually only four binary bits available for each direction (X, Y). Thus there are 16 combinations (2<sup>4</sup>) available for each direction; these combinations allow access to all 256 cells of the MµL 4100. If only four inputs for each direction were used, the decoding logic inside the memory package would require 2<sup>4</sup> AND gates of four inputs each as well as extra circuitry to provide the true and complement form of the four binary bits for each direction. By using six inputs instead of four, a combinatorial code may be used [2], allowing a reduction in the number of gates needed.

The advantage to using the binary address would be the need for fewer input pins (pads), but it would also increase the complexity of the decoding circuitry inside the memory package.

Since there are four binary bits of address available for each direction, the decoding scheme will have to take into account 2<sup>4</sup> combinations; these combinations are defined by the Binomial Theorem. According to this theorem:

$$(X+\alpha)^{\nu} = X^{\nu} + {\binom{\nu}{1}} X^{\nu-1}\alpha + {\binom{\nu}{2}} X^{\nu-2}\alpha^2 + ... + {\binom{\nu}{\nu}} a$$

(1)

but

$$\binom{\nu}{\mu} = \frac{\nu!}{(\nu - \mu)! \mu!}$$

where  $\nu > \mu$

gives the number of combinations of  $\nu$  binary bits (variables) taken  $\mu$  at a time and therefore (1) above can be written as

$$(X+\alpha)^{\nu} = \frac{\nu!}{\nu!0!} X^{\nu} + \frac{\nu!}{(\nu-1)!1} X^{\nu-1}\alpha + \frac{\nu!}{(\nu-2)!2!} X^{\nu-2}\alpha^{2} + \frac{\nu!}{(\nu-3)!3!} X^{\nu-3}\alpha^{3} + \ldots + \frac{\nu!}{0!\nu!} a^{\nu}$$

(2)

for  $X = \alpha = 1$  and v = 4. Equation (2) gives:

$$(2)^4 = {4 \choose 0} + {4 \choose 1} + {4 \choose 2} + {4 \choose 3} + {4 \choose 4} = 16 \text{ combinations}$$

(3)

Equation (3) justifies the statement that, if the decoding scheme inside the MµL 4100 uses the straight binary address, it will require  $2^4$  AND gates of four inputs each. If  $\nu$  = 6 and, of course, X =  $\alpha$  = 1, Equation (2) gives:

$$(2^6) = {6 \choose 0} + {6 \choose 1} + {6 \choose 2} + {6 \choose 3} + {6 \choose 4} + {6 \choose 5} + {6 \choose 6} = 64 \text{ combinations}$$

(4)

In order to access the 256 cells of the MµL 4100, only 16 combinations are needed in each direction; therefore, not all the terms of series (4) are needed. By inspection, it is seen that the  $\binom{6}{3}$  term provides 20 combinations,  $\binom{6}{3} = \frac{6!}{3!3!} = 20$ ; this provides 16 combinations to access the cell inside the package with four extra combinations. These extra combinations may be used if the redundancy option is implemented.

NOTE

Use of the combinatorial addressing scheme also makes possible implementation of redundant memory packages. This would allow use of MuL 4100 packages that contain malfunctioning data cells; valid data cells in a redundant package could be substituted for malfunctioning data cells in the primary memory packages. This would require address manipulation outside the memory packages to disable bit lines associated with malfunctioning data cells and automatically access the substitute data cells. This redundancy is not presently used, but the use of a combinatorial address scheme and the redundant address decode logic included on the PEM control board make this a potential feature for the PEM.

By bringing six lines into the MuL 4100, three of which are always high, there is no need for logic inversion circuits to provide the complement form of the address bits as there would be if the straight binary decoding form (four pads) were adopted.

In order to be able to bring six address lines into the memory package for each direction, when only four lines for each direction are received from the MLU, a code conversion is needed to generate these six lines. Eight out of the 11 binary address bits received from the MLU are used to generate the combinatorial address. Four binary address bits are decoded to provide the six-bit combinatorial address for the X direction; the other four are decoded to provide the six-bit combinatorial address for the Y direction. The remaining three binary address bits are used to generate the necessary controls for selecting the proper substack. The equations of the combinatorial address lines and the three substack select address lines will be given in terms of the binary address lines later when the address chain is described. Table 3-4 compares the binary and combinatorial addresses by identifying the various address bit names as they appear at the MLU, PEM paddle board, PEM control board, and PEM memory boards.

Table 3-4. Binary and Combinatorial Address Interface

| BII                | COMBINATORIAL ADDRESS |                           |                             |                                    |                                               |                            |                                        |

|--------------------|-----------------------|---------------------------|-----------------------------|------------------------------------|-----------------------------------------------|----------------------------|----------------------------------------|

| MLU<br>SIGNAL NAME | PEM<br>SIGNAL<br>NAME | PADDLE<br>BOARD<br>NUMBER | CONTROL BOARD INPUT PIN NO. | SIGNAL<br>NAME                     | OUTPUT<br>PIN                                 | SIGNAL<br>NAME             | INPUT<br>PIN                           |

| MYW-W050           | AA11                  | P1                        | 145                         | X1I<br>X1Ø                         | 183<br>182                                    | X1                         | 181                                    |

| MYW-W060           | AA10                  | P2                        | 181                         |                                    |                                               |                            |                                        |

| MYW-W070           | AA9                   | P1                        | 178                         | X2I<br>X2Ø                         | 185<br>186                                    | X2                         | 184                                    |

| MYW-W080           | AA8                   | P2                        | 175                         | X3I<br>X3Ø                         | 189<br>188                                    | Х3                         | 187                                    |

| MYW-W090           | AA7                   | P1                        | 172                         |                                    |                                               |                            |                                        |

| MYW-W100           | AA6                   | P2                        | 184                         | X4I<br>X4Ø                         | 179<br>180                                    | Х4                         | 178                                    |

| MYW-W110           | AA5                   | P1                        | 187                         | X5I<br>X5Ø                         | 177<br>176                                    | Х5                         | 175                                    |

| MYW-W120           | AA4                   | P2                        | 199                         |                                    | ·                                             |                            |                                        |

| MYW-W130           | AA3                   | P1                        | 196                         | X61<br>X6Ø                         | 173<br>174                                    | X6                         | 172                                    |

| MYW-W140           | AA2                   | P2                        | 193                         | X7I<br>X7Ø                         | 191<br>192                                    | Х7                         | 190                                    |

| MYW-W150           | AA1                   | P1                        | 190                         | X8I<br>X8Ø                         | 195<br>194                                    | Х8                         | 193                                    |

|                    |                       |                           |                             | X9I<br>X9Ø<br>X1Ø                  | 197<br>198<br>2Ø1                             | X9<br>X10                  | 196<br>199                             |

|                    |                       |                           |                             | X1ØØ<br>Y1<br>Y2<br>Y3<br>Y4<br>Y5 | 200<br>101<br>102<br>103<br>104<br>105<br>106 | Y1<br>Y2<br>Y3<br>Y4<br>Y5 | 1Ø1<br>1Ø2<br>103<br>104<br>105<br>106 |

#### 3.1.2 X and Y Binary Address Decoder Logic

Before the logic redefinition takes place (Figure 3-4), the address is subdivided into two unequal parts, consisting of the six lower order bits, which are used to generate all the necessary address lines to access the MµL 4100 in the X direction, and the five higher order bits, which are used to generate the address needed to access the MµL 4100 in the Y direction. At this point, the address, in addition to being logically redefined, is assigned the notation shown in Table 3-5. Bits AA1 through AA4 generate the six X combinatorial address lines (Table 3-6), and AA7 through AA10 generate the six Y combinatorial lines (Table 3-7).

The three remaining address bits (AA11, AA6, and AA5) are decoded in such a manner that AA5 and AA6 will generate the controls for the selection of the memory board substacks along the X direction (Table 3-8) and AA11 will generate the controls for the selection of the substacks along the Y direction. Because these three address bits control the selection of a single substack and are not involved in the binary address decoder, they will be explained more thoroughly as part of the discussion of the memory board organization.

Table 3-5. Logic Redefinition of Binary Address

| ADDRESS BITS AT PEM PADDLE BOARD | ADDRESS BITS IN PEM's<br>CONTROL BOARD |                  |  |  |  |  |  |

|----------------------------------|----------------------------------------|------------------|--|--|--|--|--|

| (NEGATIVE LOGIC)                 | Inverter<br>Output                     | Buffer<br>Output |  |  |  |  |  |

| AA1                              | A1                                     | A1               |  |  |  |  |  |

| AA2                              | A2                                     | A2               |  |  |  |  |  |

| AA3                              | A3                                     | A3               |  |  |  |  |  |

| AA4                              | A4                                     | <del>A4</del>    |  |  |  |  |  |

| AA5                              | A5                                     | A5               |  |  |  |  |  |

| AA6                              | A6                                     | A6               |  |  |  |  |  |

| AA7                              | A7                                     | <del>A7</del>    |  |  |  |  |  |

| AA8                              | A8                                     | A8               |  |  |  |  |  |

| AA9                              | A9                                     | A9               |  |  |  |  |  |

| AA10                             | A10                                    | A10              |  |  |  |  |  |

| AA11                             | A11                                    | A11              |  |  |  |  |  |

Table 3-6. Truth Table of Binary and Combinatorial X Address

|               |    | BIN | ARY     | ADDR      | ESS |    |           | COMBINATORIAL ADDRESS |    |    |    |    | 700 | WORD LINE      |  |

|---------------|----|-----|---------|-----------|-----|----|-----------|-----------------------|----|----|----|----|-----|----------------|--|

| A.            | 14 | A.  | AA3 AA2 |           |     | A. | <b>\1</b> | COMBINATORIAL ADDRESS |    |    |    |    |     | (INSIDE<br>THE |  |

| <del>A4</del> | A4 | A3  | А3      | <u>A2</u> | A2  | A1 | A1        | X1                    | X2 | Х3 | Х4 | X5 | Х6  | MμL 4100)      |  |

| 0             | 1  | 0   | 1       | 0         | 1   | 0  | 1         | 0                     | 0  | 1  | 1  | 1  | 0   | 0              |  |

| 0             | 1  | 0   | 1       | 0         | 1   | 1  | 0         | 0                     | 1  | 0  | 1  | 1  | 0   | 1              |  |

| 0             | 1  | 0   | 1       | 1         | 0   | 0  | 1         | 0                     | 1  | 1  | 0  | 1  | 0   | 2              |  |

| 0             | 1  | 0   | 1       | 1         | 0   | 1  | 0         | 0                     | 1  | 1  | 1  | 0  | 0   | 3              |  |

| 0             | 1  | 1   | 0       | 0         | 1   | 0  | 1         | 0                     | 0  | 1  | 0  | 1  | 1   | 4              |  |

| 0             | 1  | 1   | 0       | 0         | 1   | 1  | 0         | 0                     | 0  | 0  | 1  | 1  | 1   | 5              |  |

| 0             | 1  | 1   | 0       | 1         | 0   | 0  | 1         | 0                     | 1  | 1  | 0  | 0  | 1   | 6              |  |

| 0             | 1  | 1   | 0       | 1         | 0   | 1  | 0         | 0                     | 1  | 0  | 1  | 0  | 1   | 7              |  |

| 1             | 0  | 0   | 1       | 0         | 1   | 0  | 1         | 1                     | 0  | -0 | 1  | 1  | 0   | 8              |  |

| 1             | 0  | 0   | 1       | 0         | 1   | 1  | 0         | 1                     | 1  | 0  | 1  | 0  | 0   | 9              |  |

| 1             | 0  | 0   | 1       | 1         | 0   | 0  | 1         | 1                     | 0  | 1  | 0  | 1  | 0   | 10             |  |

| 1             | 0  | 0   | 1       | 1         | 0   | 1  | 0         | 1                     | 1  | 1  | 0  | 0  | 0   | 11             |  |

| 1             | 0  | 1   | 0       | 0         | 1   | 0  | 1         | 1                     | 0  | 0  | 0  | 1  | 1   | 12             |  |

| 1             | 0  | 1   | 0       | 0         | 1   | 1  | 0         | 1                     | 0  | 0  | 1  | 0  | 1   | 13             |  |

| 1             | 0  | 1   | 0       | 1         | 0   | 0  | 1         | 1                     | 0  | 1  | 0  | 0  | 1   | 14             |  |

| 1             | 1  | 1   | 0       | 1         | 0   | 1  | 0         | 1                     | 1  | 0  | 0  | 0  | 1   | 15             |  |

Table 3-7. Truth Table of Binary and Combinatorial Y Address

|     |     | BIN       | ARY      | ADDR          | ESS |               |                           | COMPINATORIAL ADDRESS |    |    |    |    | 700            | BIT LINE  |  |

|-----|-----|-----------|----------|---------------|-----|---------------|---------------------------|-----------------------|----|----|----|----|----------------|-----------|--|

| AA  | .10 | · AA      | A9 AA8 A |               |     |               | AA7 COMBINATORIAL ADDRESS |                       |    |    |    |    | (INSIDE<br>THE |           |  |

| A10 | A10 | <u>A9</u> | А9       | <del>A8</del> | A8  | <del>A7</del> | A7                        | Y1                    | Y2 | Y3 | ¥4 | Y5 | ¥6             | MμL 4100) |  |

| 0   | 1   | 0         | 1        | 0             | 1   | 0             | 1                         | 0                     | 0  | 1  | 1  | 1  | 0              | 0         |  |

| 0   | 1   | 0         | 1        | 1             | 0   | 0             | 1                         | 0                     | 1  | 0  | 1  | 1  | 0              | 1         |  |

| 0   | 1   | 0         | 1        | 1             | 0   | 1             | 0                         | 0                     | 1  | 1  | 0  | 1  | 0              | 2         |  |

| 0   | 1   | 0         | 1        | 0             | 1   | Q             | 1                         | 0                     | 1  | 1  | 1  | 0  | 0              | 3         |  |

| 0   | 1   | 1         | 0        | 0             | 1   | 1             | 0                         | 0                     | 0  | 1  | 0  | 1  | 1              | 4         |  |

| 0   | 1   | 1         | 0        | 1             | 0   | 0             | 1                         | 0                     | 0  | 0  | 1  | 1  | 1              | 5         |  |

| 0   | 1   | 1         | 0        | 1             | 0   | 1             | 0                         | 0                     | 1  | 1  | 0  | 0  | 1              | 6         |  |

| 0   | 1   | 1         | 0        | 0             | 1   | 0             | 1                         | 0                     | 1  | 0  | 1  | 0  | 1              | 7         |  |

| 1   | 0   | 0         | 1        | 0             | 1   | 0             | 1                         | 1                     | 0  | 0  | 1  | 1  | 0              | 8         |  |

| 1   | 0   | 0         | 1        | 0             | 1   | 1             | 0                         | 1                     | 1  | 0  | 1  | 0  | 0              | 9         |  |

| 1   | 0   | 0         | 1        | 1             | 0   | 0             | 1                         | 1                     | 0  | 1  | 0  | 1  | 0              | 10        |  |

| 1   | 0   | 0         | 1        | 1             | 0   | 1             | 0                         | 1                     | 1  | 1  | 0  | 0  | 0              | 11        |  |

| 1   | 0   | 1         | 0        | 0             | 1   | 0             | 1                         | 1                     | 0  | 0  | 0  | 1  | 1              | 12        |  |

| 1   | 0   | 1         | 0        | 0             | 1   | 1             | 0                         | 1                     | 0  | 0  | 1  | 0  | 1              | 13        |  |

| 1   | 0   | 1         | 0        | 1             | 0   | 0             | 1                         | 1                     | 0  | 1  | 0  | 0  | 1              | 14        |  |

| 1   | 0   | 1         | 0        | 1             | 0   | 1             | 0                         | 1                     | 1  | 0  | 0  | 0  | 1              | 15        |  |

Table 3-8. Truth Table of Binary Address and Substack Select Controls (X Direction)

| BIN           | ARY | ADDR | ESS |    | SUBS | TACK<br>ECT | SELECTED<br>SUBSTACKS |               |  |  |

|---------------|-----|------|-----|----|------|-------------|-----------------------|---------------|--|--|

| AA6 AA5       |     |      |     |    | CONT | ROLS        | ON                    |               |  |  |

| <del>A6</del> | A6  | A5   | A5  | Х7 | х8   | х9          | X10                   | MEMORY BOARDS |  |  |

| 0             | 1   | 0    | 1   | 0  | 0    | 0           | 1                     | 3 and 7       |  |  |

| 0             | 1   | 1    | 0   | 0  | 0    | 1           | 0                     | 2 and 6       |  |  |

| 1             | 0   | 0    | 1   | 0  | 1    | 0           | 0                     | 1 and 5       |  |  |

| 1             | 0   | 1    | 0   | 1  | 0    | 0           | 0                     | 0 and 4       |  |  |

The combinatorial X and Y address equations can be derived from Tables 3-6 and 3-7, respectively. Using the positive logic notation, as it appears in Tables 3-6 and 3-7, the following equations are obtained:

$$X1 = \overline{A4}$$

$$X2 = \overline{A1} \cdot \overline{A2} + \overline{A2} \cdot A4 + \overline{A1} \cdot A3$$

$$X3 = \overline{A1} \cdot \overline{A2} + A1 \cdot A4 + \overline{A2} \cdot A3$$

$$X4 = \overline{A1} \cdot A2 + \overline{A1} \cdot A4 + A2 \cdot A3$$

$$X5 = A1 \cdot A2 + A2 \cdot A4 + A1 \cdot A3$$

$$X6 = \overline{A3}$$

$$Y1 = \overline{A10}$$

$$Y2 = \overline{A7} \cdot \overline{A8} + \overline{A8} \cdot A10 + \overline{A7} \cdot A9$$

$$Y3 = A7 \cdot \overline{A8} + A7 \cdot A10 + \overline{A8} \cdot A9$$

$$Y4 = \overline{A7} \cdot A8 + \overline{A7} \cdot A10 + A8 \cdot A9$$

$$Y5 + A7 \cdot A8 + A8 \cdot A10 + A7 \cdot A9$$

$$Y6 = \overline{A9}$$

(5)

From Table 3-8, the X direction substack select controls are derived as follows:

$$X7 = \overline{A5} \cdot \overline{A6}$$

$$X8 = A5 \cdot \overline{A6}$$

$$X9 = \overline{A5} \cdot A6$$

$$X10 = A5 \cdot A6$$

(6)

Since the binary bit AA11 can take on only two values, namely "1" or "0", it is decoded as follows:

$$Y7 = \overline{A11}$$

$$Y8 = A11$$

(7)

When Y7 is true, the right half of the memory stack is selected; when Y7 is false, Y8 is true and therefore the left half of the memory stack is selected.

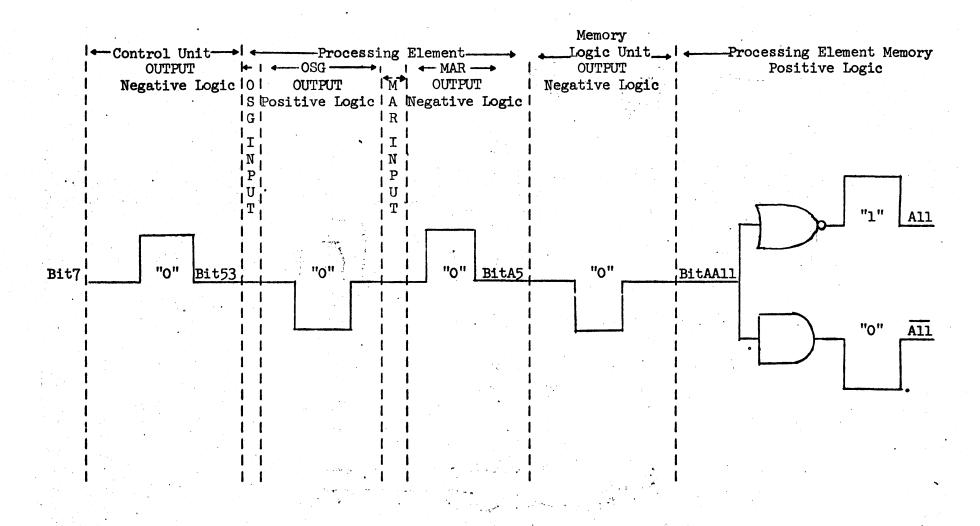

### X Binary Address Decoder and Combinatorial Address Driver

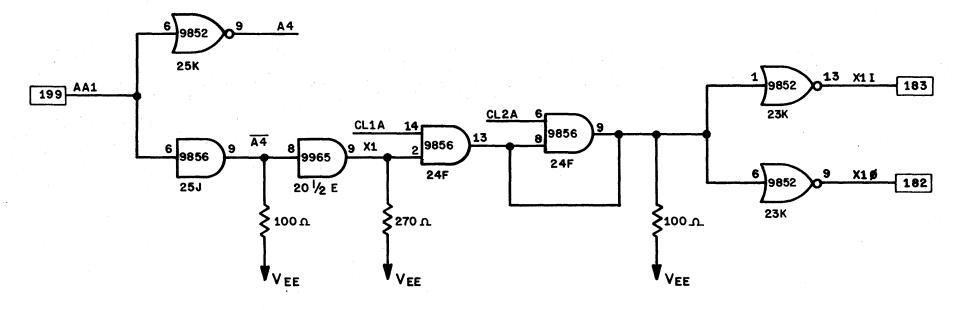

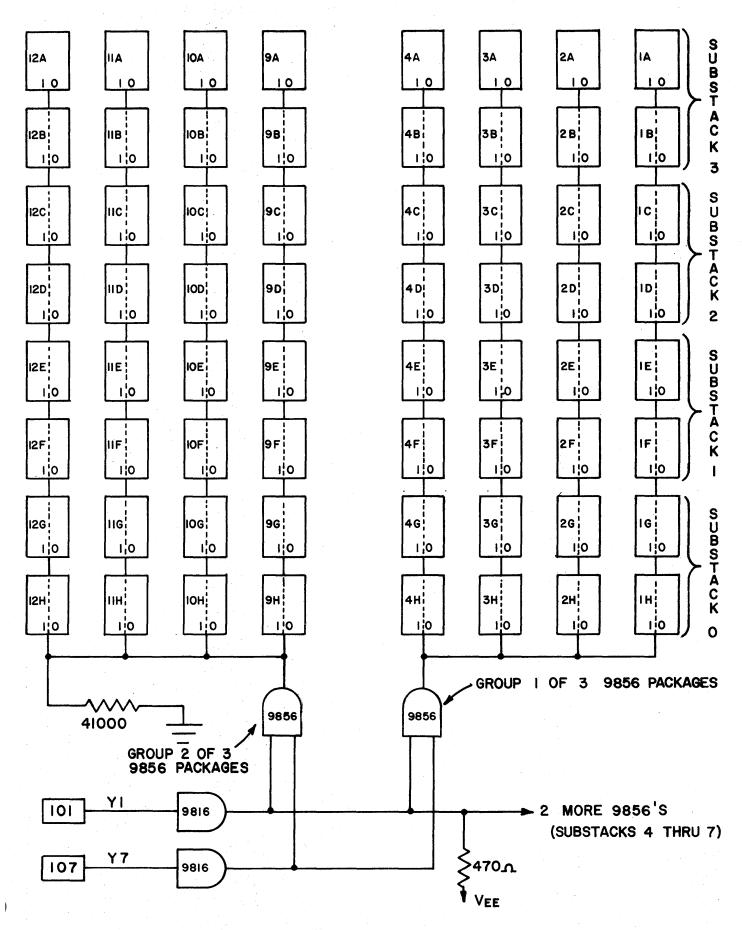

Figure 3-6 shows the logic necessary for decoding the binary address bit AA1 into the combinatorial X1 address and the driver for that line into the memory board. Figure 3-7 illustrates X address timing with respect to Initiate. It is apparent, however, that the only difference in the logic of the X1 through X10 address lines in the control board is the configuration of the decoder, which is derived from the logic equations given above for each one of the address lines. Though the logic required for the combinatorial address differs, the driver is the same for X1 through X10.

After the binary address (X1-X10) has been decoded into the combinatorial form, the line is driven by two  $CT\mu L$  9856 buffers, whose enable signals are CL1A and CL2A. These two buffers comprise a latch, which is needed to reduce the access time by the amount of delay presented by a  $CT\mu L$  9856.

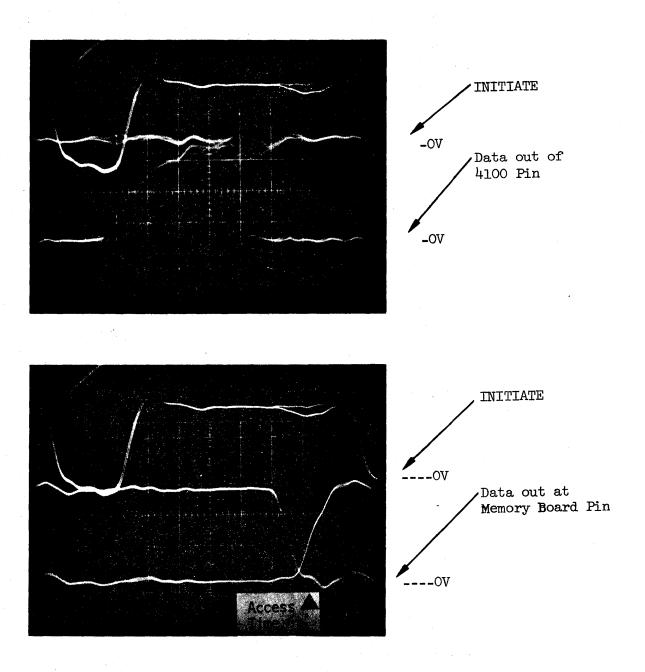

Figure 3-6./ X Binary Address Decoder and Combinatorial Address Driver (X1 Line)

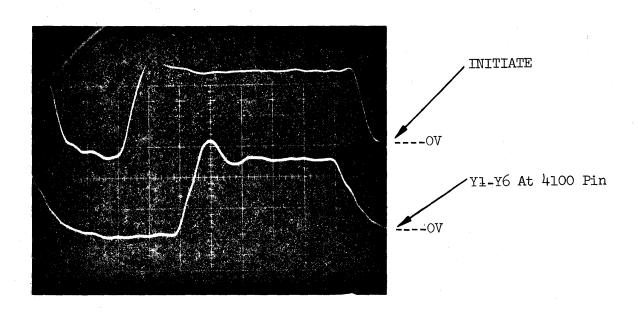

1 **V/cm**, 20ns/cm

Figure 3-7 . X1-X10 Address versus Initiate at Control Board

It is worth noting that access time is defined as the time required by the memory to provide data to the pin of the memory board (data output register) as measured with respect to Initiate.

CLIA enables the address to pass through the first CTµL 9856 buffer of the latch and thus to bypass the second CTµL 9856 buffer. If the address bit is a logic ONE, this signal should remain positive until at least 5 ns after CL2A arrives at the input of the second CTµL 9856 buffer. The reason for requiring CLIA to be present for at least 5 ns after the rise of CL2A is to guarantee that when CLIA is removed, the output of the second CTµL 9856 buffer (pin 9) will continue to be high (assuming a logic ONE for that address bit). If the latch is not allowed to reset before CL2A becomes stable at pin 9, it will remain set for as long as CL2A is asserted. Control logic timing assures that CL2A will hold the address bit in the latch for 165 ns after the arrival of Initiate. It can be said, then, that CLIA is used to enable the address into the register (latch), thereby establishing the leading edge of the address at the memory package, while CL2A is used to hold the address for the specified period, thereby determining the turn-off time of the address at the MµL 4100.

Once the address is available at pin 9 of the second buffer of the latch, the output of that buffer is fanned out and applied to a pair of CTuL 9852 inverters; this inversion is required so that when each address bit passes through the TTuL 9016 hex-inverter of the X address driver on the memory board (see Figure 3-21), it will be at the correct level when it arrives at the memory package. In this way, if a particular address line is required to be low at the MuL 4100, it will leave the pin of the control board in a high state and will arrive at the MuL 4100 after passing through the TTµL 9016 inverter in a low state. These inversions apply only to X1 through X6 address lines. Because X7 through X10 are the substack enables and since only one line among those four is high at a time, the one which is true at the output of the buffer of the latch (pin 9) leaves the control board in a low state, while the other three leave the control board in a high state, forcing the MuL 4100's of the memory substacks they control to receive all the addresses in a low state (see X address driver of memory board, subsection 3.2.1).

The address bit is fanned out to two CTµL 9852 drivers in order to split the address into INNER and OUTER parts for selecting the proper half of the PEM and thus to reduce the load significantly in driving the X address buffers of the memory board.

The use of pull-down resistors is needed to fulfill the requirement of the CTuL family of devices.

### Y Binary Address Decoder and Combinatorial Address Driver

Figure 3-8 shows the logic for decoding the binary bit AA10 into the combinatorial Y1, and the driver of the Y1 address line into the memory board. Figure 3-9 illustrates Y address timing with respect to Initiate. As was mentioned in the discussion of the X binary address decoder, the decoder for the Y address is the result of logic equation (5). There are two differences between the X binary address decoders and the Y binary address decoders. One difference is that the drivers of Y1 through Y6 lines require an extra control signal (CLY) to enable the address into the memory board; the other difference is that the drivers of Y7 and Y8 lines require a pair of CTµL 9856 buffers for splitting the load.

Control pulses CL1B and CL2B perform the same controlling operation as CL1A and CL2A, respectively. CL2B must be present on the second buffer of the latch at least 5 ns before CL1B is removed in order to ensure that the removal of CL1B will not affect the operation of the latch.

The Y direction address will be present as long as CL2B is high. It can be said that CL1B is the enable for Y1 through Y8 address, while CL2B is the signal that maintains the address at the M $\mu$ L 4100 as long as it is needed.

Due to a problem, however, in the early production of MµL 4100's which required the Y address to be delayed at the input of MµL 4100 by approximately 35-45 ns with respect to the X address, an extra clock pulse (CLY) is needed to strobe the Y1-Y6 address precisely at the correct time to meet this requirement. Enabling the Y1-Y6 address could not be achieved simply by using CL1B, because of the skew involved.

It should be noted that the Y direction drivers are noninverting CTµL 9856's, while the drivers for the X direction address lines are inverters. The reason for this can be found in the description of the X and Y address drivers of the memory board, where the X address driver uses an inverter prior to accessing the MµL 4100, and therefore another inversion is required.

Figure 3-8. Y Binary Address Decoder and Combinatorial Address Driver (Yl Line)

1 V/cm, 20ns/cm

Figure 3-9. Yl - Y8 Address versus Initiate at Control Board

### 3.1.3 Redundant Address Decoder

When describing the MµL 4100 device in subsection 3.1.1, it was said that one of the advantages of the combinatorial address is to allow the address to access a spare MµL 4100 if the storage location specified by that address is faulty. This would require proper wiring interchanges between the additional memory package and an external code converter, whose output would be TRUE only when one of the addresses corresponding to a bad bit line is selected.

Although the logic for this feature has been implemented on the control board, its function will not be described here because the ILLIAC IV PEM, as it now stands, does not use memory boards utilizing the redundancy feature.

## 3.1.4 Timing Generator

This portion of the control board generates all the necessary control signals for the internal operation of the PEM. Table 3-9 shows timing generator input and output signals and identifies their respective functions.

#### Definition of Timing Generator Input Signals

a. <u>Initiate (IØ & IØN)</u>. This is the main signal used to initiate the PEM's read or write operation. Because the timing of the control signals in the PEM is very critical, the measurement and adjustment of these signals is performed with respect to the Initiate signal (at the 1 V level); the leading edge (falling edge) is assumed to be present at the control board (pin 147) at time TO. When a read or write operation is requested, the MLU provides the PEM with a low level, 50 ns minimum width pulse at a frequency of about 5 MHz. This signal results from the Initiate memory cycle signal (FIMC-----1) in the memory control card of the MLU. Whenever a read operation is begun, Initiate arrives at the PEM in about 10 ns with respect to FIMC-----1; when a write operation is begun, it occurs at about 75 ns with respect to FIMC-----1.

Table 3-9. Control Board Timing Generator Input/Output Signals List

| INP                     | UT SIGNAL |                                      | OUTPUT SIGNAL  |                                                         |                                       |                                                                                  |  |  |  |  |

|-------------------------|-----------|--------------------------------------|----------------|---------------------------------------------------------|---------------------------------------|----------------------------------------------------------------------------------|--|--|--|--|

| SIGNAL NAME SIGNAL NAME |           | CONTROL<br>BOARD<br>INPUT<br>PIN NO. | SIGNAL<br>NAME | PURPOSE OF SIGNAL                                       | CONTROL<br>BOARD<br>OUTPUT<br>PIN NO. | REMARKS                                                                          |  |  |  |  |

| MINITPL1                | INITIATE  | 147                                  | CL1A           | To turn on X1-X10 address                               | -                                     | It is used internal to the control board.                                        |  |  |  |  |

| MWOUTEN1                | AWØ       | 151                                  | CL2A           | To turn off X1-X10 address                              | <u>-</u>                              | It is used internal to the control board.                                        |  |  |  |  |

| MWINNEN1                | AWI       | 146                                  | CL1B           | To turn on Y1-Y8 address in Y address latch             | -                                     | It is used internal to the control board.                                        |  |  |  |  |

|                         |           |                                      | CL2B           | To turn off Y1-Y8 address in Y address latch            | -                                     | It is used internal to the control board.                                        |  |  |  |  |

|                         |           |                                      | CLY            | To turn on and off Y address                            | -                                     | To achieve 35-45 ns delay of Y address from X address.                           |  |  |  |  |

|                         |           |                                      | CLW            | To stretch WØ & WØI                                     | -                                     |                                                                                  |  |  |  |  |

|                         |           |                                      | WØI            | To hold CL3 low on WRITE cycle; to generate CL5         | -                                     | Both WØ & WØI are used in-<br>ternal to the control board.                       |  |  |  |  |

|                         |           |                                      | CL3            | To enable data out during READ operation                | 162                                   | It is used during READ operation only.                                           |  |  |  |  |

|                         |           |                                      | CL4            | To hold data out until 120 ns from next Initiate        | 165                                   | It is used during READ operation, but is also present during WRITE operation.    |  |  |  |  |

|                         | ·         |                                      | CL5            | To enable data in during WRITE operation                | 127                                   | It is present during WRITE operation only.                                       |  |  |  |  |

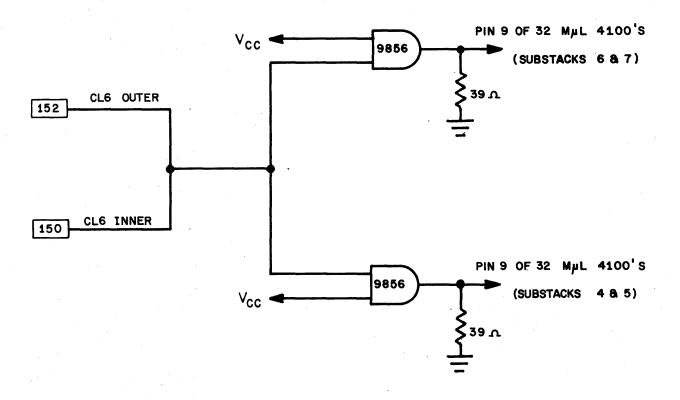

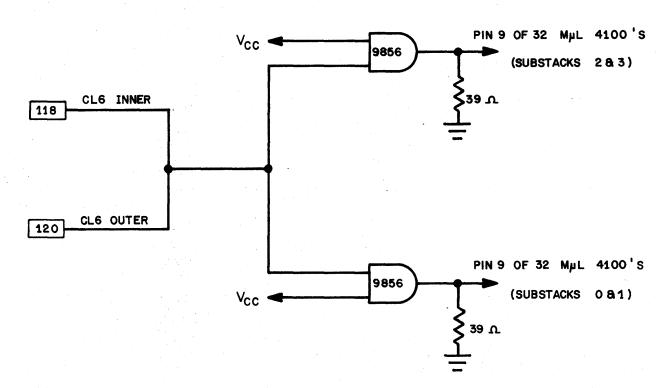

|                         |           |                                      | CL6I<br>CL6I   | WRITE pulse needed to WRITE data in INNER memory boards | 118<br>150                            | To WRITE into memory data bits 8-39.                                             |  |  |  |  |

|                         |           |                                      | CL6Ø           | WRITE pulse needed to WRITE data in OUTER memory boards | 120<br>152                            | To WRITE into memory data<br>bits 0-7 and 40-63. Both<br>CL6I & CL6Ø are present |  |  |  |  |

|                         | 4 - 41    |                                      | WØ<br>WI       | To strobe CL6Ø<br>To strobe CL6I                        |                                       | during WRITE operation only.                                                     |  |  |  |  |

When the signal enters the control board timing generator, it is logically redefined in the same fashion as is the binary address, and, after passing through a 25 ns delay line, it is used as the basis for the precise timing and pulse shaping of the write inner (AWI) and write outer (AWØ) enables and the timing generator output signals (Table 3-9) as well. Because the time varies from signal to signal, a tapped 100 ns delay line is included which provides a relatively simple method for adjusting the falling and trailing edges of any critical signal (the taps normally allow variations in delay in steps of 10 ns). It must be mentioned, however, that the control board should be able to operate in any PEM of the ILLIAC IV system without presenting any significant problems due to tight timing specifications. The variations in the different components used in the PEM require the control signals to be within reasonable limits, but through experience it has been shown that the suggested times in the PEM control board timing chart of Drawing FD41044 have satisfied the requirements of even the worst-case memory boards in the different PEM's. It should be understood, therefore, that the same control signal is not always picked up from the same delay tap on different control boards, but instead some variations should be expected.

- b. Write Outer Enable (AWØ). This is a low level, 50 ns wide pulse appearing at control board pin 151 at the same time as Initiate; it is used to enable CL6Ø control signal during the write operation into PEM memory boards 3 and 4 which accommodate the OUTER word (data bits 0-7 and 40-63).

- c. <u>Write Inner Enable (AWI)</u>. This is a low level, 50 ns wide pulse which may be coincident with Initiate when it appears at control board pin 146. It is used to enable CL6I control signal during the write operation into PEM memory boards 1 and 2, which accommodate the INNER word (data bits 8-39).

#### <u>Definition of Timing Generator Output Signals</u>

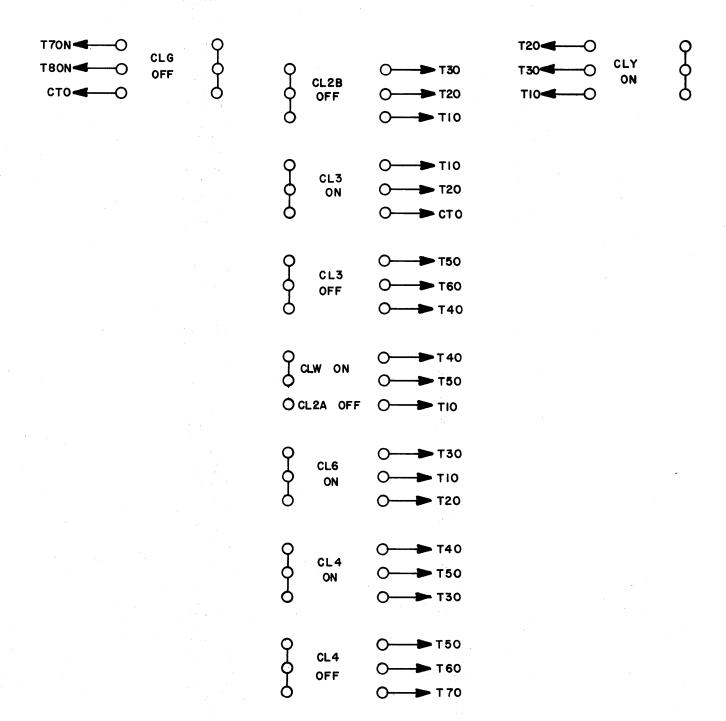

a. Enables of X and Y Combinatorial Address Signals (CL1A, CL1B). These are two high level signals, each about 25 ns wide, which are used to enable the X1-X6 (CL1A) and Y1-Y6 (CL1B) into the combinatorial address register. Because these signals are the result of Initiate, where IØ, delayed by 25 ns through the delay line shown in Figure 3-10, and IØN, driven directly to those gates whose outputs provide CL1A and CL1B, there is no way to adjust these signals through adjustable timing taps. Instead, CL2A and CL2B can be adjusted in such a way that the trailing edge of CL1A and CL1B will remain stable at least 5 ns after the rise (leading edges) of CL2A and CL2B, respectively.

In order to achieve a fast access time, CL1A and CL1B have been timed to be present when X1-X6 and Y1-Y6 address bits arrive at the address register of the control board. The waveforms in Figure 3-10 are readings from one of the 64 PEM's of the ILLIAC IV Quadrant. The numbers at the leading and trailing edges of each waveform specify the time those transitions occur with respect to Initiate, whose trailing edge is measured at 50 percent amplitude and at 0 ns. This point should be kept in mind, since the waveform photos that are provided are only for those control signals that are applied to the memory boards through the control board.

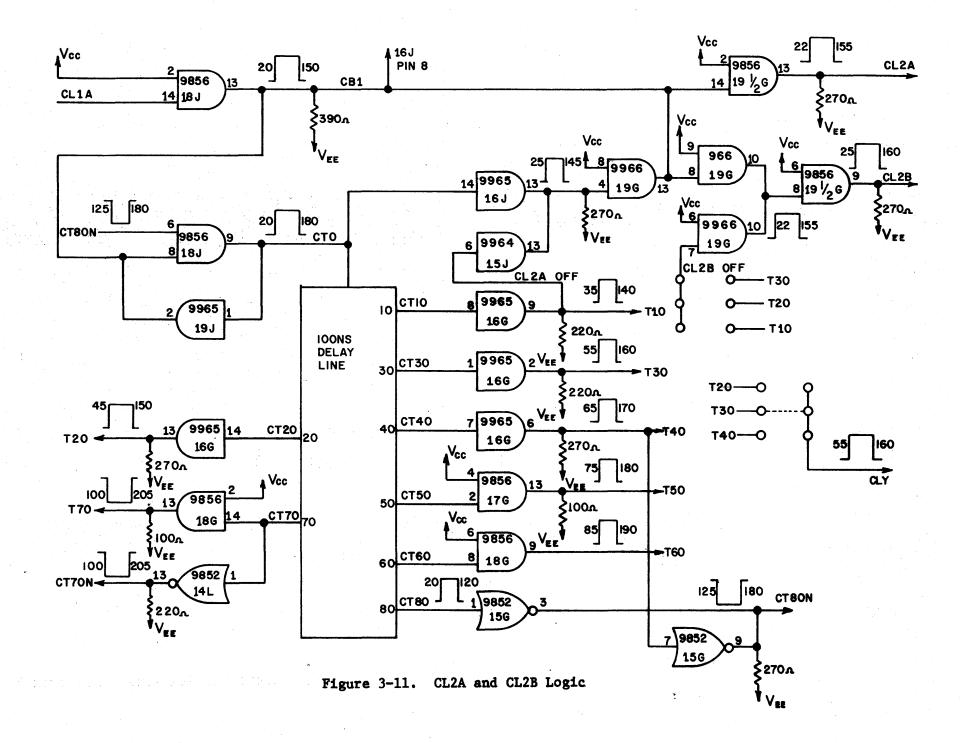

b. X and Y Combinatorial Address Hold Signals (CL2A, CL2B). These are two high level signals, each about 135 ns wide, which are used to hold the combinatorial address stable for about 135 ns. Both signals must be present at least 5 ns before the removal of CL1A and CL1B in order to allow the latch (address register) in the control board to set and provide a stable address until CL2A and CL2B are removed (Figure 3-11). CL2A OFF can be adjusted through tap T10, whose output is a function of CT0, which in turn can be adjusted accordingly through CT8ON. By adjusting CTO, the leading edge of CL2A is affected; this provides a method for adjusting the leading edge of CL2A with respect to the trailing edge of CL1A. Because the leading edge of CL2B is adjusted through circuitry common to CL2A and CL2B, its trailing edge is adjusted through the adjustable timing tap shown in Figure 3-11 (T10, T20, T30). The same figure provides waveforms at different gates to show logic level versus time in nanoseconds as referred to Initiate.

Figure 3-10. CLIA and CLIB Logic.

CLY is used to control the times at which the Y1-Y6 address is turned on and off; this control is made necessary by a special characteristic of M $\mu$ L 4100, which requires that the Y1-Y6 address must follow the X1-X6 address by 35 to 45 ns.

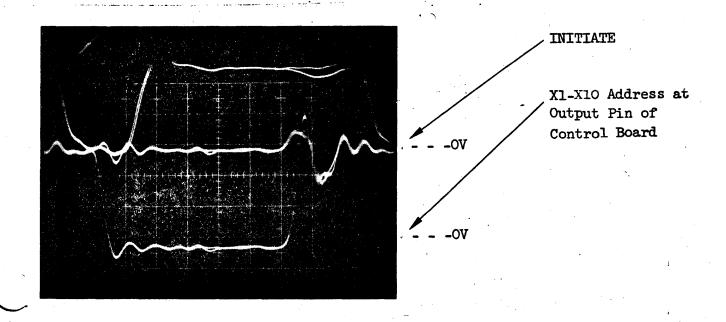

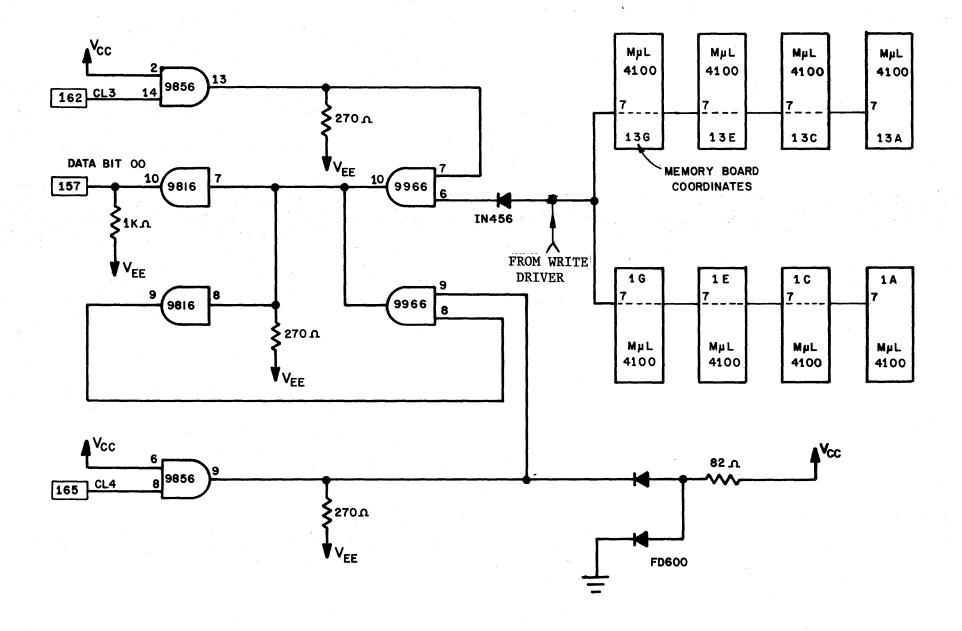

c. <u>Data-out Enable Signal (CL3)</u>. This is a high level signal, about 60 ns wide, which is used to enable the data to be gated out of the memory board's data-out register within the specified access time of 188 ns. It has to remain stable for not more than 35 ns after the removal of Y1-Y10 address; it must also be present for at least 5 ns after the appearance of the leading edge of CL4 at control board pin 165. These measurements may be made at control board pin 162 for CL3 and pins 101-106 for Y1-Y6 address.

This signal has been adjusted to be present during the read operation only; its leading edge (50 percent amplitude) has to occur between 135-145 ns after the Initiate of the current read cycle. The trailing edge of CL3 should occur between 190-205 ns with respect to the current Initiate. However, experience has shown that 200 ns, with respect to Initiate, gives the best results. This means that the leading edge of CL4 must be present no later than 195 ns with respect to the current Initiate. Both the leading and trailing edges of CL3 can be adjusted through the timing taps CL3 ON and CL3 OFF, respectively. Because the leading edge of CL3 did not originally have the 10 ns skew it presently has, an optional capacitor (Figure 3-12) could be used to achieve a finer adjustment in case the adjustable timing tap could not bring the timing within the specified limits. The value of this capacitor would vary from one control board to another; for some control boards, there would be no capacitor at all. It has been observed that a 10 pf capacitor could introduce a delay of about 1 ns in the leading edge of CL3.

Figure 3-12. Data-out Enable Signal (CL3) Logic.

CL3 is forced to be present only during read operations, because the WRITE OUTER or INNER (WØI), which is a high level pulse during write operations, in both the 32- and 64-bit mode of operation, is applied to the NOR gate 19L pin 1. The output of this gate will remain low as long as WØI is present. If a glitch (transient) is present on CL3 during a write operation, CLW ON should be adjusted through its corresponding timing tap in order to reshape WØI (see logic for CL5) to such a degree that it will force NOR gate 19L pin 13 to remain low during the write operation. This adjustment may require a new adjustment of CL5, since this signal is generated directly from WØI. The waveform at the output of the CTµL buffer (AND gate) 18L pin 9 shown in Figure 3-12 indicates the actual reading from one of the 64 PEM's of the ILLIAC IV Quadrant. Figure 3-13 gives the waveform of CL3 at pin 162 of the control board together with Initiate.

Figure 3-13. CL3 versus Initiate.