#### THE MEMORY MANAGEMENT FUNCTION IN A

#### MULTIPROCESSOR COMPUTER SYSTEM

- A Description of the BCC 500

Memory Manager

Wrenwick K. Lee

Technical Report R-2 Issued September 12, 1974

#### THE ALOHA SYSTEM, Task II Department of Electrical Engineering University of Hawaii

Sponsored by Advanced Research Projects Agency ARPA Order No. 1956 Contract No. NAS2-6700

THE ALOHA SYSTEM, Task II, is affiliated with the Department of Electrical Engineering at the University of Hawaii, and is currently conducting studies into the design and fabrication of secure multiprocessor operating systems.

This research was supported by the Advanced Research Projects Agency of the Department of Defense and was monitored by NASA, Ames Research Center under Contract No. NAS2-6700.

The views and conclusions contained in this document are those of the author and should not be interpreted as necessarily representing the official policies, either expressed or implied, of the Advanced Research Projects Agency of the United States Government.

#### ABSTRACT

The BCC 500 System was designed to be a large-scale interactive computing utility supporting up to several hundred on-line users. To achieve this goal, a multi-processor architecture was chosen. Central processors were designed to compile and run user code, while the operating system was designed to be run by several dedicated processors. This paper details the system memory management function which was assigned to one of these processors.

With this architecture, memory management takes on a different dimension. Techniques and capabilities beyond the reach of those attainable by time-sharing memory managment functions on a CPU with other system and user tasks may be employed. The memory manager is continuously active, monitoring the memory system and taking appropriate action more quickly and more often.

ii

#### ACKNOWLEDGEMENTS

The implementation of the BCC 500 memory manager involved the contributions of various members of the BCC 500 staff, among them Jack Freeman, Dr. Butler Lampson, Dr. W. Lichtenberger, Dr. Melvin Pirtle, Rainer Schulz, and Robert Van Tuyl.

---

.

## TABLE OF CONTENTS

| 1. | INTR | ODUCTION                                           |

|----|------|----------------------------------------------------|

|    | 1.1  | Organization                                       |

|    |      | 1.1.1 System Structures (Section 2) 1              |

|    |      | 1.1.2 Hardware (Section 3)                         |

|    |      | 1.1.3 Data Structures (Section 4) 1                |

|    |      | 1.1.4 Microcode (Section 5 and Section 6) 2        |

|    |      | 1.1.5 APU Code (Section 5 and Section 7) 2         |

|    |      | 1.1.6 Communications, Error Handling (Section 8) 2 |

|    |      | 1.1.7 Concluding Remarks (Section 9)               |

| 2. | INTR | ODUCTION - SYSTEM STRUCTURES                       |

|    | 2.1  | Pages                                              |

|    | 2.2  | Page Types                                         |

|    | 2.3  | Unique Names                                       |

|    | 2.4  | Physical Location of Pages 8                       |

|    | 2.5  | Context Blocks 11                                  |

|    |      | 2.5.1 The Process Memory Table 12                  |

|    |      | 2.5.2 The Active Page Table                        |

|    | 2.6  | The Process Table 19                               |

| 3. | INTR | ODUCTION - THE HARDWARE                            |

|    | 3.1  | The Processor         25                           |

|    | 3.2  | Drum & Disk Hardware 26                            |

|    |      | 3.2.1 Data & Address Formats                       |

|    |     | 3.2.2    | Position Counters                           | 39 |

|----|-----|----------|---------------------------------------------|----|

|    |     | 3.2.3    | TSU Control Registers                       | 40 |

|    |     | 3.2.4    | Indicators                                  | 45 |

|    |     | 3.2.5    | TSU Instructions                            | 47 |

|    |     | 3.2.6    | Instruction Timing                          | 50 |

|    |     | 3.2.7    | Status Register                             | 51 |

|    |     | 3.2.8    | Attentions                                  | 54 |

|    |     | 3.2.9    | Select Register in the TSU                  | 54 |

|    |     | 3.2.10   | Disk Seeks & Position Verification          | 57 |

|    |     | 3.2.11   | TSU State                                   | 59 |

| 4. | INT | RODUCTIO | N - DATA STRUCTURES                         |    |

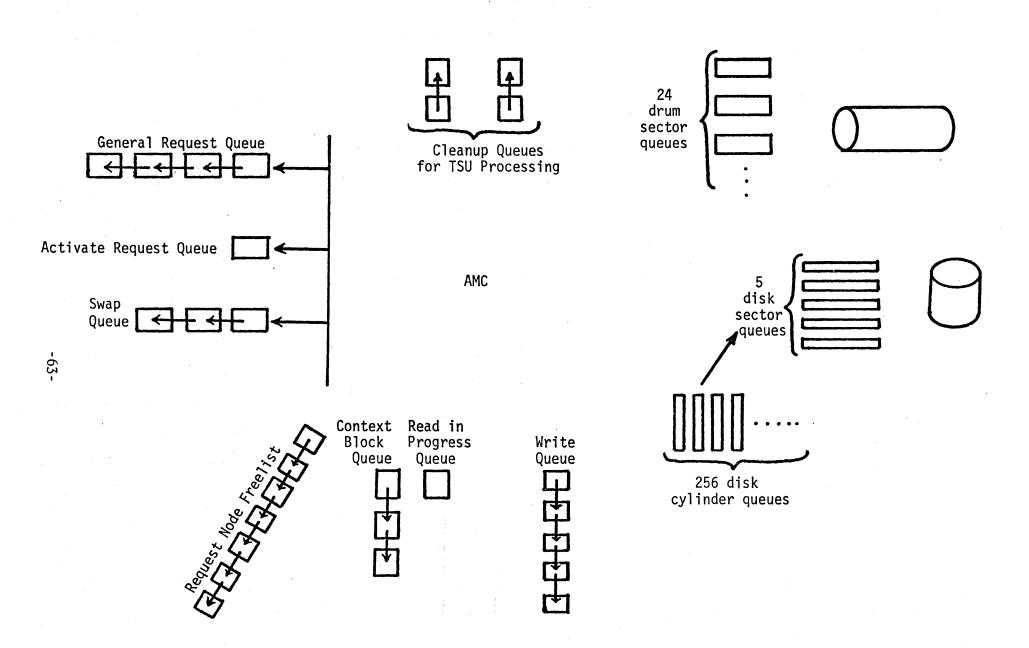

|    | 4.1 | Queues   |                                             | 61 |

|    |     | 4.1.1    | General Request                             | 66 |

|    |     | 4.1.2    | Activate Request                            | 67 |

|    |     | 4.1.3    | Request Entry                               | 68 |

|    | 4.2 | The Co   | re Hash Table                               | 70 |

|    |     | 4.2.1    | CHT Layout                                  | 70 |

|    |     | 4.2.2    | When a Page is 'in CHT'                     | 71 |

|    |     | 4.2.3    | CHT Page Status Information                 | 74 |

|    |     | 4.2.4    | Scheduled Count & Accessibility of Pages    | 75 |

|    |     | 4.2.5    | Removing a Page from CHT, or Clearing DIRTY | 77 |

|    | 4.3 | Drum H   | ash Table                                   | 79 |

|    |     | 4.3.1    | General                                     | 79 |

|    |     | 4.3.2    | DHT Page Status Information                 | 80 |

|    |     |          |                                             |    |

|    |     |          | v                                           |    |

|    |     |          | · · · · · ·                                 | ÷  |

|    | 4.4  | Standar   | d Circular List Structure           | 82   |

|----|------|-----------|-------------------------------------|------|

|    | 4.5  | State o   | of AMC Microprocessor               | 84   |

|    | 4.6  | Importa   | nt Central Memory Locations         | . 84 |

|    | 4.7  | Statist   | cics (Counters)                     | 87   |

|    | 4.8  | Table M   | lanipulations                       | 90   |

| 5. | INTR | ODUCTION  | I - SOFTWARE & FIRMWARE             | 95   |

| 6. | MEMO | ORY MANAG | GER FIRMWARE                        | •    |

|    | 6.1  | The Mer   | mory Manager's Main Loop            | 99   |

|    | 6.2  | Microco   | ode Descriptions                    | 100  |

|    | 6.3  | Detaile   | ed Microcoded Routines Descriptions | 104  |

|    |      | 6.3.1     | Subroutine Linkage                  | 105  |

|    |      | 6.3.2     | Main Loop                           | 105  |

|    |      | 6.3.3     | Process Attention                   | 107  |

|    |      | 6.3.4     | Start Auxiliary Processing Unit     | 109  |

|    |      | 6.3.5     | CHT Hash                            | 109  |

|    |      | 6.3.6     | CHT Search                          | 109  |

|    |      | 6.3.7     | Enter CHT Entry                     | 110  |

|    |      | 6.3.8     | Delete CHT Entry                    | 111  |

|    |      | 6.3.9     | Clear CHT Entry                     | 111  |

|    |      | 6.3.10    | Get Free Core                       | 112  |

|    |      | 6.3.11    | Put Page on Free Core List          | 113  |

|    |      | 6.3.12    | DHT Hash                            | 113  |

|    |      | 6.3.13    | Search DHT                          | 114  |

vi

|    | 6.3.14      | Make DHT Entry                       | 115 |

|----|-------------|--------------------------------------|-----|

|    | 6.3.15      | Delete DHT Entry                     | 115 |

| ۰. | 6.3.16      | Append Entry onto List               | 117 |

|    | 6.3.17      | Stack Entry on List                  | 118 |

|    | 6.3.18      | Remove Entry from List               | 118 |

|    | 6.3.19      | Save State                           | 119 |

|    | 6.3.20      | Dump TSU State                       | 119 |

|    | 6.3.21      | Generate Wakeup                      | 120 |

|    | 6.3.22      | Send TSU Instruction                 | 121 |

|    | 6.3.23      | Stack Entry on Free List             | 121 |

|    | 6.3.24      | Remove Entry from Free List          | 122 |

|    | 6.3.25      | Initialization Sequence for AMC      | 122 |

|    | 6.3.26      | Wait Until Device Idle               | 124 |

|    | 6.3.27      | Compute Next Sector on Selected Unit | 125 |

|    | 6.3.28      | Get Position of Rotating Device      | 126 |

| 7. | MEMORY MANA | GER SOFTWARE                         |     |

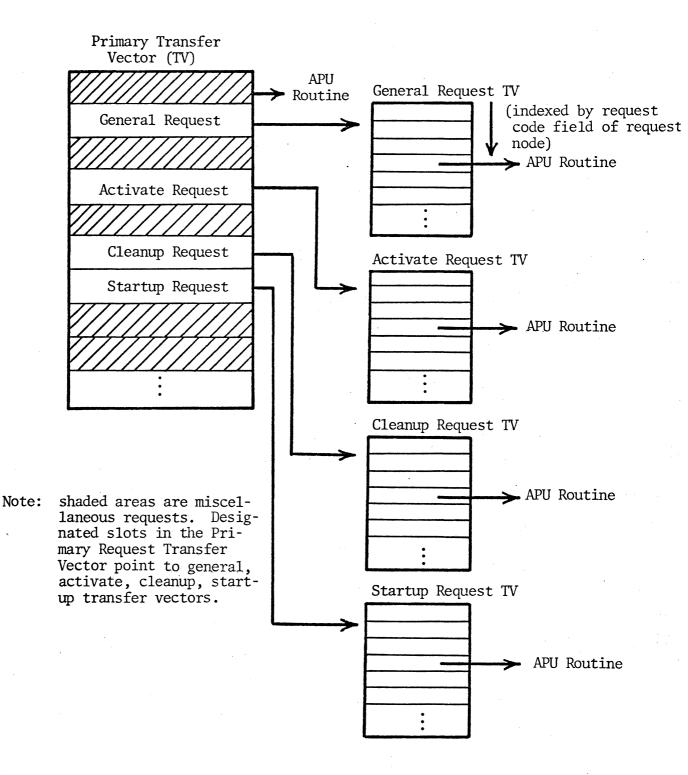

|    | 7.1 APU Co  | de - Overview                        | 127 |

|    | 7.2 Major   | Transfer Vectors                     | 131 |

|    | 7.2.1       | Primary Transfer Vector              | 132 |

|    | 7.2.2       | General Request Transfer Vector      | 132 |

|    | 7.2.3       | Activate Request Transfer Vector     | 133 |

|    | 7.2.4       | Cleanup Request Transfer Vector      | 134 |

|    | 7.2.5       | Startup Request Transfer Vector      | 135 |

|    | 7.3 The Au  | xiliary Processing Unit              | 136 |

vii

## 8. COMMUNICATIONS AND ERROR HANDLING

|      | 8.1   | Communications - The Memory Manager and the Outside World. | 148 |

|------|-------|------------------------------------------------------------|-----|

|      | 8.2   | Error Handling                                             | 150 |

|      |       | 8.2.1 General Error Philosophy                             | 150 |

|      |       | 8.2.2 Types of Errors                                      | 151 |

|      |       | 8.2.3 Errors During Swapping                               | 152 |

|      |       | 8.2.4 Disk Read Errors                                     | 152 |

|      |       | 8.2.5 Disk Write Errors                                    | 152 |

|      |       | 8.2.6 Drum Errors for Non-Swapping Transfers               | 153 |

| 9.   | CONC  | LUDING REMARKS                                             | 154 |

| App  | endix | I Abbreviations for Model I Memory Management System       | 157 |

| Appe | endix | II Microprocessor General Theory of Operation              | 160 |

| App  | endix | III AMC Startup                                            | 180 |

viii

# LIST OF FIGURES

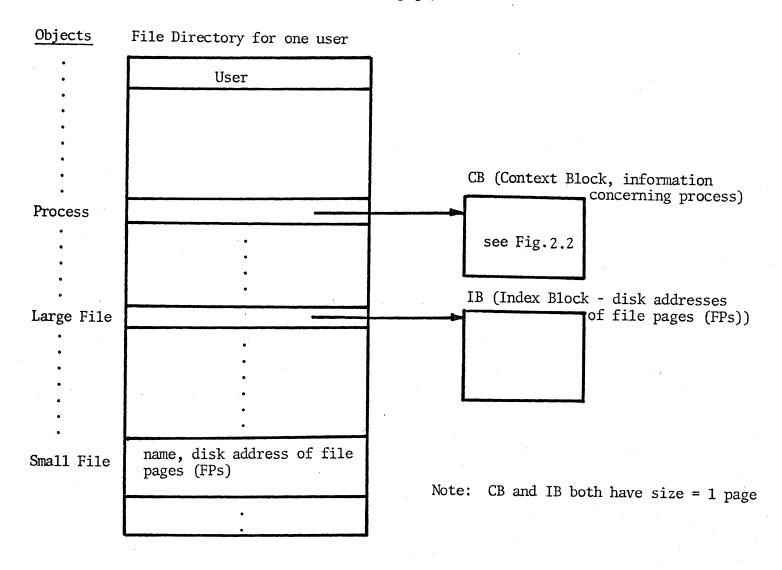

| Fig. | 2.1          | MIB and Associated Page Types CB, IB, FP 5          |

|------|--------------|-----------------------------------------------------|

| Fig. | 2.2          | CB Contents                                         |

| Fig. | 2.3          | CB Storage Allocation                               |

| Fig. | 2.4          | Format of an Entry in a Process Memory Table 20     |

| Fig. | 2.5          | Format of an Entry in an Active Page Table 21       |

| Fig. | 2.6          | Format of the Process Table (PRT) 23                |

| Fig. | 2.7          | Description of PRT Bits 24                          |

| Fig. | 3.1          | Auxiliary Memory System Configuration 27            |

| Fig. | 3.2          | Drum and Disk Page Formats                          |

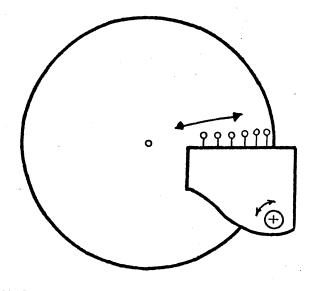

| Fig. | 3.3a         | Drum Characteristics                                |

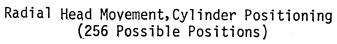

| Fig. | <b>3.</b> 3b | Disk                                                |

| Fig. | 3.3c         | Disk (continuation) 33                              |

| Fig. | 3.4          | Parameters of BCC 500 Rotating Memories 35          |

| Fig. | 3.5a         | TSU Control Registers                               |

| Fig. | 3.5b         | TSU Registers                                       |

| Fig. | 3.6a         | Position Counter (PC) Format                        |

| Fig. | 3.6b         | Drum Record Timing                                  |

| Fig. | 3.7          | TSU Register Loading                                |

| Fig. | 3.8          | TSU Register Loading Interface (Select Register) 55 |

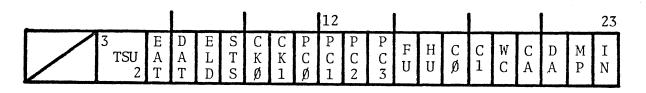

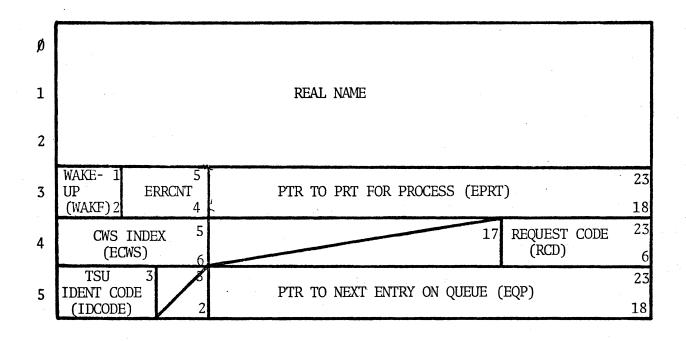

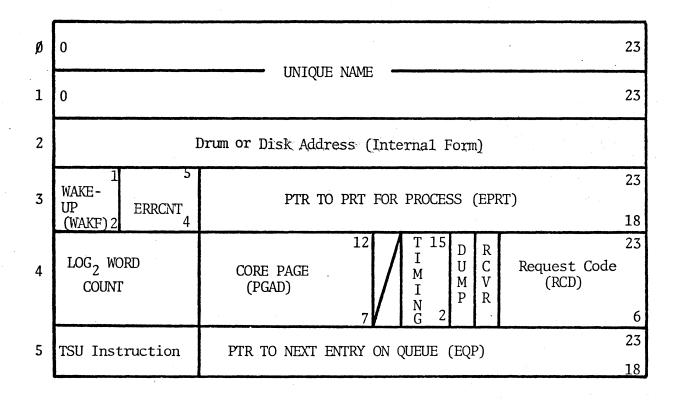

| Fig. | 4.1          | Normal Request Entry                                |

## List of Figures - continued

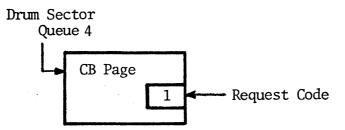

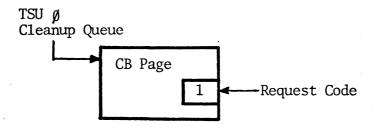

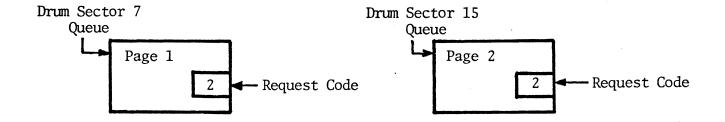

| Fig. | 4.2          | Various AMC Queues                                           |   |

|------|--------------|--------------------------------------------------------------|---|

| Fig. | 4.3          | Direct I/O Request Entry                                     |   |

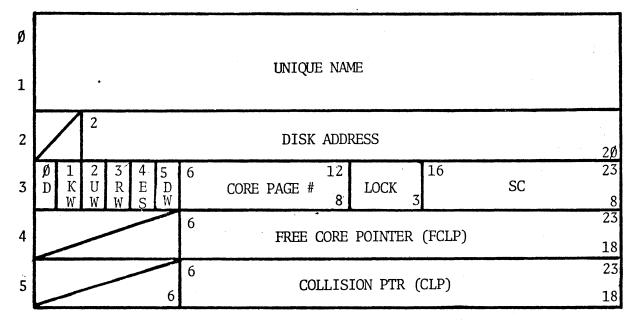

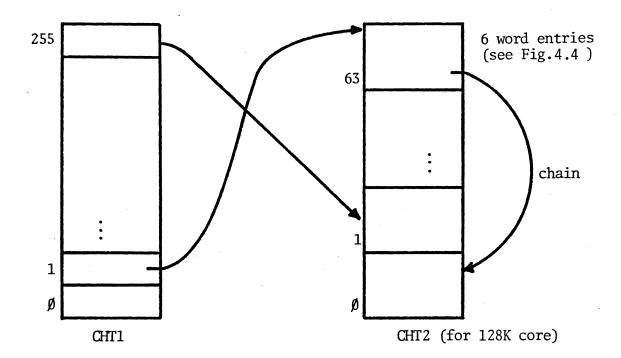

| Fig. | 4.4          | Core Hash Table (CHT2) Entry                                 |   |

| Fig. | 4.5          | CHT Hashing Structure                                        |   |

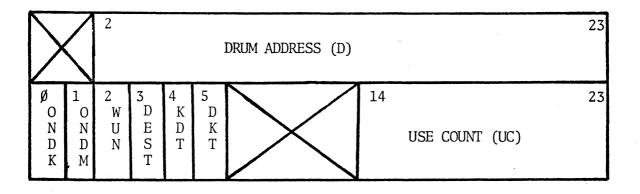

| Fig. | 4.6          | Drum Hash Table Entry 81                                     |   |

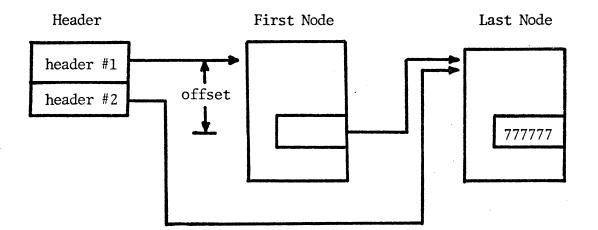

| Fig. | 4.7a         | Circular List Structure 83                                   |   |

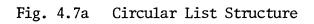

| Fig. | <b>4.</b> 7b | Empty List                                                   |   |

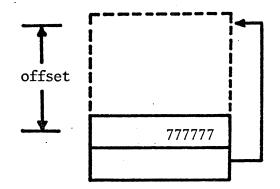

| Fig. | 5.1          | AMC Code Organization                                        |   |

| Fig. | 6.1          | Main Loop                                                    |   |

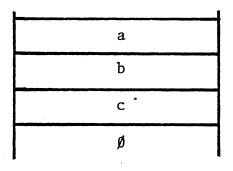

| Fig. | 6.2a         | Three Hash Table Entries                                     |   |

| Fig. | 6.2b         | b is Deleted                                                 | • |

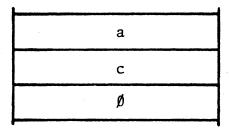

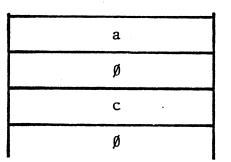

| Fig. | 6.2c         | Corrected Hash Table if a, b, c Hash into same Location. 116 |   |

| Fig. | 6.2d         | Corrected Hash Table if c Hashes into Location it is in. 117 |   |

| Fig. | 7.1          | Dispatching Structure                                        |   |

| Fig. | 8.1          | Memory Manager Communications                                |   |

| APPE | NDIX         |                                                              |   |

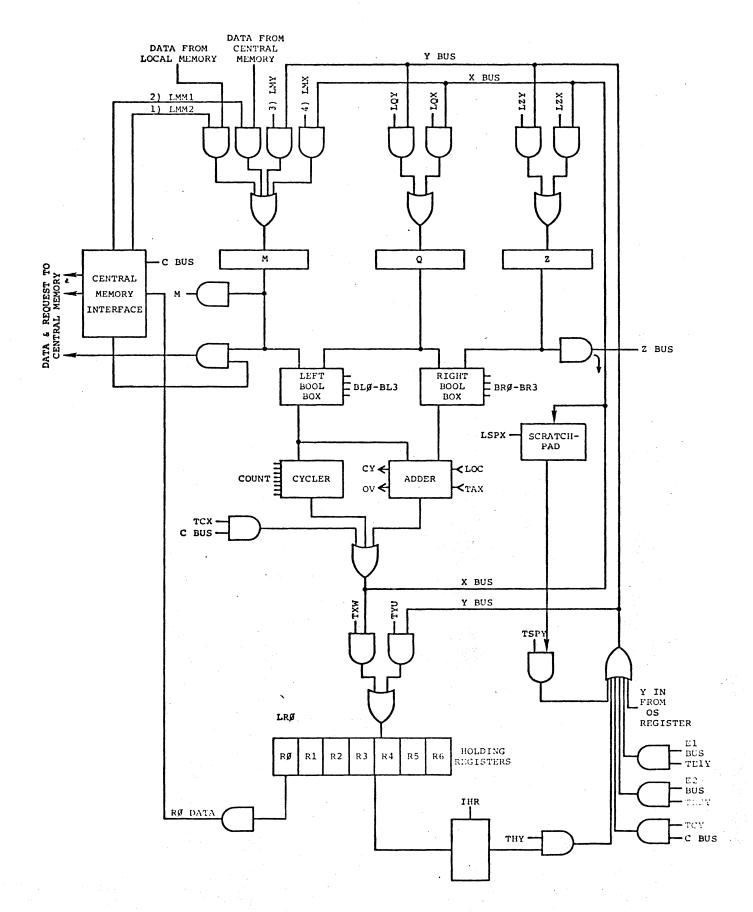

| Fig. | 1 M          | icroprocessor Data Paths: Arithmetic Section 161             |   |

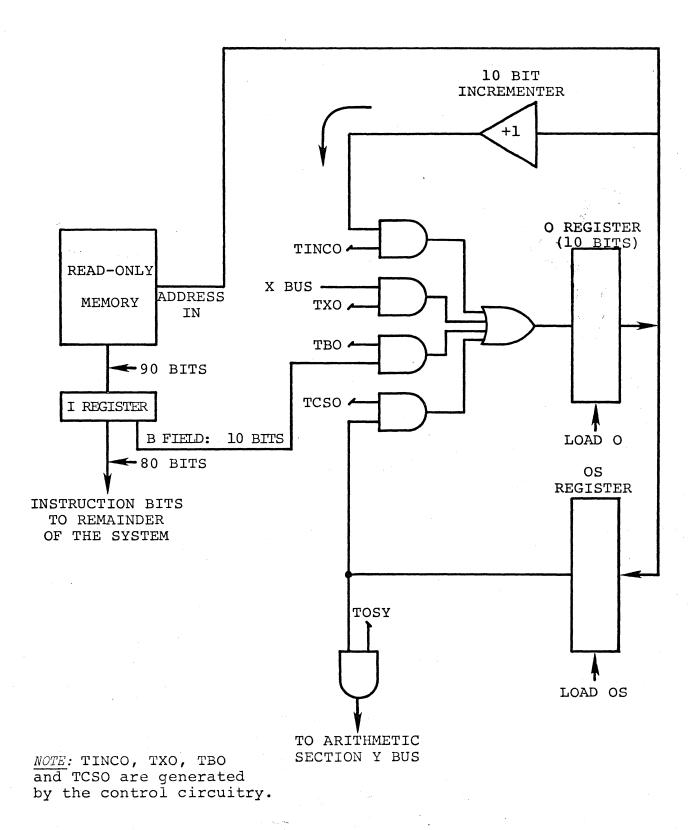

| Fig  | 2 M          | icroprocessor Data Paths: Control Section 162                |   |

х

## LIST OF TABLES

| Table A1. | 90-bit Microinstruction Word                            |

|-----------|---------------------------------------------------------|

| Table A2. | Branch Conditions • • • • • • • • • • • • • • • • • • • |

| Table A3. | Special Functions                                       |

| Table A4. | Bool Box Control                                        |

#### **1** INTRODUCTION

Memory management for the BCC 500 was designed to be controlled by a single dedicated processor. As a result, the central processors do not run memory management tasks. The memory management processor continuously monitors the memory system and quickly responds to events that are important to the memory system.

This report is a technical description of the memory management system. Hardware components, data structures, implementation code, and communications conventions are described in detail.

#### 1.1 Organization

The following parts of the memory management system will be described.

#### 1.1.1 System Structures (Section 2)

This describes the system environment in which the memory manager operates. Concepts such as page, unique name, context block, process table, etc. are discussed.

#### 1.1.2 Hardware (Section 3)

The hardware has been specially adapted to attain the high swap rates desired. The processor, drum, disk and auxilary memory controller are extensively discussed. One can see the differences such as position monitoring, unique name checking, and other features of the hardware.

#### 1.1.3 Data Structures (Section 4)

The fundamental data structures of the memory manager are

detailed. The queue which is used extensively in the memory manager is illustrated. Also the core and drum page tables are explained.

1.1.4 Microcode (Section 5 & Section 6)

The role of microcode is explained. Various examples of microcoded routines are given.

1.1.5 APU Code (Section 5 & Section 7)

The role of APU code is explained. The APU instruction set is given.

1.1.6 Communications, Error Handling (Section 8)

Communications, and error conventions are explained.

1.1.7 Concluding Remarks (Section 9)

Looking in retrospect, comments are given on the relative merits and difficulties of the implementation. Recommendations and questions are also mentioned.

#### 2 INTRODUCTION - SYSTEM STRUCTURES

The following are the important system structures involving the memory manager. An overview of the various structures involved in paging is given and one is introduced to the environment of the memory manager. The number of structures presented is essentially quite small, yet sufficient to give a fair insight into the role of the memory manager.

## 2.1 Pages

The memory system of the BCC 500 consists of 128K words of core, 4 million words of drum, and 125 million words of disk. The BCC 500 System super-imposes a page structure on this storage space. All three levels of storage are sub-divided into 2K-word blocks, called pages. Pages are units of information as well as units of storage space. When we speak of pages of code, pages of data, etc., we mean an amount of code, data, etc., that may be stored in a page of storage. This is just to say that "page" is used in a manner completely analogous to that in which "byte" and "word" are used. When we use "page" to refer to a unit of storage space, we speak of "core pages", "drum pages", and "disk pages" depending on which of the three levels of memory we are referring to. Storage pages have an "origin" as well as an extent (2048 words). Pages of core are 2048 word blocks starting at an address which is congruent to 0 modulo 2048. Similarly, drum and disk pages have fixed "starting addresses" built into the hardware. They are a little different from core pages in that we don't speak of word addresses in connection with these storage devices.

-3-

#### 2.2 Page Types

Pages can be of the following types:

- 1) MIB (Multiple Index Block) the file directory for one user. It also contains the disk addresses of the data pages for small files.

- IB (Index Block) contains the disk addresses of the data pages for a large file.

- 3) CB (Context Block) contains the defining information for a process.

- 4) FP (File Page) contains data and occupies a definite position in a file.

The pages of a file are numbered from 0, up to a maximum value MAXFA. The number for a page is called its file address and specifies its position in the file, which may not be the same as the number of pages preceding it, since some file addresses may have no corresponding pages.

5) PP (Private Page) - contains data and belongs to a process. Private pages are not ordered in any way, but each one can appear in just one PMT\* byte.

The relationships of the various types of pages are shown in Fig. 2.1.

2.3 Unique Names

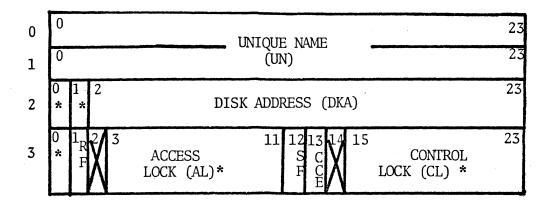

Associated with every page is a 48-bit number called its <u>unique name</u>. This number has the following format:

<sup>\*</sup>PMT is a table of pages belonging to a given process. This is explained further in Section 2.5.1 on the PMT.

MIB and Associated Page Types CB, IB, FP

MIB (Multi-Index Block, size = 1 page)

-5-

| Bits  | Name   | Contents                                     |  |  |  |  |  |

|-------|--------|----------------------------------------------|--|--|--|--|--|

| 0-1   | UNTAG  | 0 = MIB or small file data page              |  |  |  |  |  |

|       |        | 1 = large file IB or data page (FP)          |  |  |  |  |  |

|       |        | 2 = CB  or  PP                               |  |  |  |  |  |

|       |        | 3 = not used                                 |  |  |  |  |  |

| 2-17  | UNUSER | User number of the owner of the page         |  |  |  |  |  |

| 18-36 | UNID   | A number different for each object (file or  |  |  |  |  |  |

|       |        | process) with the same owner. For a MIB this |  |  |  |  |  |

|       |        | field is 0.                                  |  |  |  |  |  |

| 37-47 | UNADR  | Page number + 1 for a private page or a file |  |  |  |  |  |

|       |        | page. For a MIB, IB or CB this field is 0.   |  |  |  |  |  |

Some comments on the implications of this format are appropriate.

1) The number of distinct users is limited to 64K. Each user who exists has exactly one MIB. Every page except a MIB belongs to a MIB, and hence every page belongs to some user. The user to whom a page belongs can be determined from the UNUSER field of the page's unique name.

2) Every <u>object</u> (file or process) has an entry in a MIB. This entry specifies the UNID field of the object. This field is the same in the unique name of every page of the object. It is therefore possible to find the object which a given page is part of, starting from the unique name of the page, by examining the UNUSER field to find the MIB and then comparing the UNID field with each object in the MIB. When a new object is created it is given a new UNID, which is the UNID of the last object created in that MIB, + 1. This ensures that all pages of the new object will be distinguishable from any

-6-

page of any old object, whether or not the old object still exists. When the last UNID value  $(2^{19}-1)$  is assigned to a new object in some MIB, it is not possible to create any more objects in that MIB. This situation can be remedied only by reassigning the UNIDs for all the presently existing objects in that MIB and updating <u>all</u> occurrences of unique names for pages belonging to that MIB anywhere in the system.

3) A file cannot have more than 2047 pages because of the size of the UNADR. It is not possible to move a page to another position in a file without changing its unique name. It is, however, possible to completely reconstruct a file from a complete scan of the disk.

Unique names have the following basic property: <u>no two different pages</u> <u>ever created by the system can have the same unique name</u>. This observation requires some clarification:

1) If the UNID reassignment mentioned above is carried out, it must be thought of as the creation of a new system into which some information from the old system is copied.

2) If a file page is destroyed, and a page with the same file address in the same file is subsequently created, it is considered to be the same page. There is no difference between these two operations performed in sequence and the operation of zeroing the page. It is not claimed that this is the only possible interpretation of the meaning of recreating a file page, but it is a reasonable one, and it is the one adopted by the Memory Management System (MMS).

3) It is not possible to have more than one reference to a private page When the page is destroyed it is removed from all maps in the process

-7-

and therefore ceases to exist in the most complete sense possible. If another private page is created in the same PMT byte, it makes no whether it is regarded as the same page or different (though the latter viewpoint seems preferable):

--if it is the same, the matter is academic since there can be no references to the page at the time it is created and subsequent references to it are under the control of the creator.

--if it is different, the matter is academic since no record of the previous page exists anywhere in the system.

Unique names exist in the system in the following places:

1) Recorded on disk together with a page

2) Recorded on drum together with a page

3) In the core hash table (CHT) entry for a page

- 4) In the entry for an object (and implicitly for each of its pages) in a MIB

- 5) In a PMT entry

- 6) In a PRT\* entry

They also exist in the temporary storage of the MMS.

## 2.4 Physical Location of Pages

A page always exists on disk, and may also exist on drum, in core, both or neither, where by 'exist' we mean that space is allocated for the page. A valid copy of the page may exist in any combination of these three places.

\*PRT is the Process Table -- This is explained further in Section 2.6.

-8-

Since a page p always exists on disk, there is always a disk address K(p) for it. This address is assigned by the monitor, which is responsible for disk allocation, when the page is created. The unique name recorded at K(p) is either UN(p) or 0, the latter if and only if the WUN (Write Unique Name) bit for the page is set in the Drum Hash Table (DHT). The reason for this is that when the page is created it is assigned a free disk page which has UN = 0 and the WUN bit for the page is set. The first time the page is written on the disk, its unique name will be written and the WUN bit will be cleared. When p is destroyed the unique name at K(p) is zeroed.

It is expected that pages will be moved on the disk infrequently, if at all. The combination of unique name and disk address is therefore normally sufficient to identify a page and permit it to be read from the disk; this combination is called the real name (RN) of the page and occupies three words. If a page is moved and an attempt is made to access it using the old disk address, a unique name error will occur, since it is not possible for the same unique name to be written on two different disk pages. The unique name of the page can then be used to find the MIB entry for the object of which it is a part, and from this entry the correct disk address can be obtained. This works because of a second basic property of the system: <u>the correct disk</u> <u>address of a page is always recorded in the MIB entry (for small file page),</u> <u>IB (for large file page) or CB (for private page) for the object of which it</u> is a part. Hereafter we will suppress the IB and CB cases.

It is possible for many occurrences of the real name of a page (other than a private page) to exist in the system. New occurrences are created when a file page is put into a PMT entry, or when the monitor puts a MIB, IB

-9-

or CB into its map, or when a PRT entry is made for a process.

The subset of pages in core or on the drum changes rapidly, as does the physical core or drum location of a page. Core and drum addresses are therefore kept in exactly one place in the system, so that only one change need be made when a page is moved.

1) The core address of a page is kept in the Core Hash Table (CHT), which can be conveniently accessed by unique name. Every page which is in core (the precise meaning of this phrase will be explained later) has a CHT entry, which contains all the information relevant to its sojourn in core.

2) The drum address of a page is kept in the Drum Hash Table (DHT), which in theory can also be conveniently accessed by unique name. Every page which is on the drum or on its way there has a DHT entry, which contains all the information relevant to its sojourn on the drum.

We are now in a position to explain roughly how a page p can be accessed if its RN is known. First use UN(p) to access CHT. If this access is successful the page is in core at the address given by CHT. Otherwise use UN(p) to access DHT. If this access is successful the page is on the drum at the address given by DHT. Otherwise use K(p) to access the disk. If the unique name recorded there agrees with UN(p), the page is there on the disk. Otherwise use UN(p) to find the MIB entry for the page. This may reveal that the page does not exist. Otherwise it is on the disk at the location given by the MIB, and the RN may be updated accordingly.

It is a third basic property of the system that <u>the procedure described</u> above will always yield a valid copy of the page unless there is a failure of

-10-

the MMS. There are some built-in cross-checks to make detection of a failure more likely.

1) When a page is read from drum, the UN which was recorded on the drum may fail to agree with DHT. We give up this cross-check by accessing DHT on disk address rather than unique name. Since it is possible for a disk address to be reassigned (unlike a unique name), an attempt to access a page p on the drum with an old RN r (i.e., K(p) = K(r)) may fail because  $UN(r) \neq UN(p)$ . We can, however determine the facts. If the UN recorded at K(p) agrees with the one on the drum, then we have an old RN and the MMS has not failed. If it disagrees there is indeed a MMS failure. To summarize, using UN(p) to access a DHT keyed on disk address must include reading the page from the drum and checking the recorded UN.

2) When a page is read from disk using a disk address obtained from the MIB, the recorded UN must agree with the one in the MIB.

3) When writing on the disk, the recorded UN must agree with the one obtained from DHT and the drum. This cross-check of the (UN,K) pairing defined by DHT and the drum is gained in return for cross-check (1) which was lost by keying DHT on K.

#### 2.5 Context Blocks (CB)

To define a process for the operating system requires a good deal of information. This information is called the "state" of the process. When a process is dormant, its state is defined by its entry in its owner's file directory (MIB). Such an entry contains the symbolic name of the process, information for controlling access to the process, and the Unique Name of a special

-11-

page of the process called its Context Block. This special page contains the information needed to introduce (or re-introduce) the process into the operating system's job stream, that is, to activate the process.

When a process is active, its state is more complex. Some information about it is kept in tables, such as the Process Table and the character I/O line tables, which are resident in core. Information which is needed only when the process is itself in core (or being swapped in or out) is kept in the Context Block page. This page can be thought of as providing temporary storage for the operating system in certain of its functions with respect to the process.

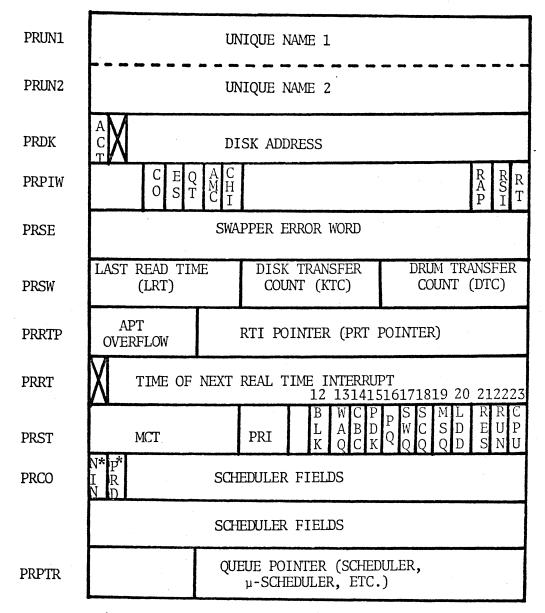

Figures 2.2 and 2.3 detail the layout of the CB. Of particular interest are the MAP, PMT and APT which involve the memory manager.

#### 2.5.1 The Process Memory Table (PMT)

One kind of information the operating system requires about an active process is a list of the Unique Names of all the pages which belong to the process. These names (together with a mapping of the process' address space into them) are needed by the CPU so that it may find the pages to which the process directs references when actually executing instructions. These page names are also required by the Auxiliary Memory Control (AMC) so that it can identify the pages which it needs to swap into core preparatory to the running of the process.

The page names, and some additional information about the pages, are kept in a table called the Process Memory Table (PMT) <u>in the Context Block</u> (CB). These tables begin in a standard place (loc. 300<sub>8</sub>) in each process' Context Block for the convenience of the various parts of the operating

-12-

#### **CB CONTENTS**

0: POP entry indirect address word

1: POP entry indirect address word

2: SP first unused stack address

3: SL last word allocated for stack

4: P for Trap (ring dependent)

5: PAR for Trap (ring dependent)

6: BRU for Trap (ring dependent)

7: BRU for Trap (ring dependent)

10-177: FREE

- 200-277: MAP Map associating virtual addresses with pages (contains indices into PMT)

- 300-1277: PMT Table of pages in use by this process

- 1300-1707: SPT

- 1710-2027: SPCS

- 2030-2115: ICT

- 2116-2235: OFT

- 2236-2650: STACK

- 2659-2751: APT Table of active pages (contains indices into PMT)

- 2752-1763: TRSTATE

- 2764-2775: SWSTATE

- 2776: CTC

2777: IT

## Figure 2.2

-13-

## CB STORAGE ALLOCATION

| SPT (42 words/entry) |                       | 264 |

|----------------------|-----------------------|-----|

| OFT                  | (5 words/entry)       | 80  |

| PMT                  | (4 words/entry) (128) | 512 |

| APT                  | (1 word/entry)        | 65  |

| SPCS (5 words/entry) |                       | 80  |

|                      |                       |     |

1011

| MAP         | 64   |

|-------------|------|

| STATE, ETC. | 25   |

|             | 1090 |

Figure 2.3

system which must reference them. They have room for 128 page names, but can be expanded to allow for up to 255. That is, the limit of 255 is built into the system in a number of places, but the current 128 page limit is imposed by only the software part of the system. We begin by giving explanations of the contents of entries in PMT. Refer to Fig. 2.4 for a picture of a PMT entry.

Unique Name: These two words hold the Unique Name of a page of information. This is the same Unique Name as is written with the page on the disk and drum and kept in the Core Hash Table when the page is in core. It is used by the CPU's map loader when it looks up the page in CHT and by the Swapper when it is swapping the process in or out.

Disk Address: This field holds the address at which the disk copy of the page is stored. It is the address which will actually be sent to the disk TSU (Transfer Sub-Unit) when it is required to read the page into core or to write it on the disk. Such addresses have to be kept because there is no provision at the TSU level for addressing pages by their Unique Names. However, the system does not depend on this disk address being correct. When the transfer of a page to or from the disk begins, the contents of the Class Code field of the addressed page is checked for equality with the Unique Name of the page of information it is desired to transfer. If this check fails the transfer is aborted and a "Class Code Error" is reported to the process for which the transfer was being done. A page's Unique Name and Disk Address are called together its "Real Name."

This is a good place to note an implementation concession for the Drum Hash Table. First we note that the Core Hash Table is a table entered by hashing the Unique Name of a page and containing for each entry the Real Name

-15-

of a page and the absolute address of the core page in which the page is currently stored. Ideally the Drum Hash Table would be completely analogous and each entry would contain a Real Name and a drum page address of the current drum copy of the page. This implementation was not possible, simply because of the amount of core storage which such a table would require. Instead, DHT entries contain only the Disk Address word of the Real Name. Except for the loss in elegance this seldom causes any problems. It just means that in certain cases we have to do an otherwise unnecessary read from the drum to compare a Class Code with a Unique Name.

(The Core Hash Table and Drum Hash Table are explained in greater detail in the section on Data Structures.)

Thus the Disk Address word in PMT entries is used to find the page whose Unique Name appears in the entry both on the disk and on the drum, but in neither case is it considered the final authority in the matter since we always make the comparison between Class Code and Unique Name.

RF (Reference Flag): The system tries to make sure that the pages in the Core and Drum Working Sets of a process are the ones that the process is referencing most frequently. In order to do this, it must somehow be kept informed as to what pages the process is referencing. The CPU's Map Loader provides this information by setting the RF flag in PMT whenever it loads the corresponding page into its map.

SF (Scheduled Flag): When a program causes the Map Loader to load a page into the CPU's map. the Map Loader looks up the page in the Core Hash Table using the Unique Name in the appropriate PMT entry. It is possible that the page is in core for some other process but not supposed to be

-16-

available to the process in which the program is running. Giving the program access to the page under these conditions will in general lead to chaos, since the core storage management system depends on knowing how many processes have access to the pages in core. The SF bit is used to prevent this illegal access. It is set by the core management system if the process is authorized to access the page, and the CPU will trap if it is asked to load a page with SF = 0 into its map.

CCE (Class Code Error): When the pages of a process' Core Working Set are being read into core the Unique Names in PMT are compared with the Class Codes on the pages read. If the comparison fails, the read is aborted and the CCE flag in the PMT entry is set. The SF bit is, of course, reset. If the process tries to reference the page, it will get a trap from the CPU, at which time CCE can be tested to determine the source of the problem.

RDE (Read Error): If a page of the Core Working Set cannot be swapped in because of a "hard" error encountered in trying to read the page from the drum, the RDE bit in the pages PMT entry is set. Like the CCE bit, this error indication is for use in analyzing the page fault which will result if the page is referenced.

#### 2.5.2 The Active Page Table (APT)

When it is time to bring a process into core so that it may execute instructions on a CPU, a request is sent to the Swapper to bring in the pages the process needs in order to run. The Swapper is given a pointer to the process' entry in PRT.\* In the PRT entry the Swapper finds the Real Name

\*Section 2.6 describes the Process Table (PRT).

of the process' Context Block. It brings this page into core. In the Context Block (CB) is a table, called the Active Page Table (APT), which contains pointers into the Process Memory Table (PMT). Entries in APT are marked as to whether the pages they point to are to be swapped in or not. The set of pages which are marked to be swapped in is called the Core Working Set (CWS) of the process. The Swapper scans APT and reads all CWS pages into core. When these reads are completed the process is said to be loaded and is available to be run on a CPU.

Figure 2.5 gives the format of an entry in APT. We now explain the various fields shown in the figure.

Use History; This field is used by the system to keep a history of references the process directs to the page the entry points to. It is updated periodically from the RF flag in PMT and used by the routines which maintain the Core Working Set.

Page Lock: It is possible to lock pages into core, that is, to exempt them from the algorithms which cause DIRTY pages to be written back on the drum and pages not in any Core Working Set to be released from core. The operating system can lock pages directly by turning on bits in the pages' entries in the Core Hash Table. Certain privileged User Programs will also need to insure that pages are kept in core. The Monitor provides a MCALL which can be used to do this. When a process executes this MCALL, the PAGE LOCK field of its CWS entry for the page will be set to a code identifying the lock bit in CHT for which the process is responsible.

-18-

Keep:

Lock: These fields are intended to allow a program to designate elements of its Core Working Set as more important than others. No operations on them are implemented in the current version of the Process Memory System, however.

DWS: In addition to the Core Memory Set there is another subset of APT called the Drum Working Set (DWS). It is the set of pages which are being kept on the drum for the process. It is a superviset of the Core Working Set and is maintained entirely by the software parts of the operating system. The DWS bit in an APT entry is set if the page pointed to is in the process' Drum Working Set.

CWS: This is the bit the Swapper uses to determine whether an APT entry points to a page to be swapped in. It is set if the page is to be swapped in (i.e., is in the process' Core Working Set) and reset if it isn't.

PMT Index: This is an index into the Process Memory Table and points to a Real Name of a page.

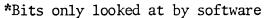

#### 2.6 The Process Table (PRT)

A Process Table entry is kept for each active process in the system. The first three words of this entry give the real name (unique name + disk address) of the context block (CB) for the process. As described in section 2.5, the context block contains various tables: The PMT, a table of pages known to the process and the APT, a set of indices into PMT of currently active pages.

Thus if the swapper is given a process table index, it can (and does) determine which pages to swap.

-19-

Format of an Entry in a Process Memory Table

RDE - Read Error

RF - Reference Flag

SF - Scheduled Flag

CCE - Class Code Error

## Figure 2.4

\* Not used by the Memory Manager

Format of an Entry in an Active Page Table

| 0<br>USE HISTORY (UH) | 7 | 8<br>PAGE<br>LOCK<br>(PGL) | 11<br>) | 12<br>D<br>W<br>S | 13<br>C<br>W<br>S | K<br>E | 15<br>L<br>O<br>C<br>K | 16 | PMT INDEX<br>(PMT) | 23 |  |

|-----------------------|---|----------------------------|---------|-------------------|-------------------|--------|------------------------|----|--------------------|----|--|

|-----------------------|---|----------------------------|---------|-------------------|-------------------|--------|------------------------|----|--------------------|----|--|

An Example of an APT Entry

| 01234567 | 8 9 10 11 | 12 13 14 15 | 1617181920212223 |

|----------|-----------|-------------|------------------|

| 11010011 | 0000      | 1 1 0 0     | 01000101         |

The entry tells us that the page whose Real Name appears in PMT[69] is in the process' Drum and Core Working Sets. The page is not locked in core for this process. Nor is it KEPT or LOCKed in the working sets. The process has made references to the page during

the last interval,

the next to the last interval,

the 3rd from the last interval,

the 6th from the last interval,

the 7th from the last interval,

#### Figure 2.5

Figures 2.6 and 2.7 detail the process table. Of particular interest to memory management are:

1) PRUN1

PRUN2

PRDK

which give the real name of the context block for the process 2) PRSE

which is an error word that the memory manager returns to indicate some problem which prevents it from swapping the process

- 3) In the Process Status Word (PRST),

- SWQ: a request for swapping-in has been put on the memory manager queue. When the memory manager considers it, this bit is reset.

- CBC: creating a request to read in a context block accompanies the setting of this bit (original request is a swapping-in queue request).

- PQ: after the context block has been read in, this bit accompanies the reading in of the individual pages of the process CWS. The CBC bit is turned off.

- LDD: Last leg of swapping in, this bit is set when all the pages have been read into core; PQ bit is turned off.

-22-

## FORMAT OF THE PROCESS TABLE (PRT)

Figure 2.6

-23-

#### DESCRIPTION OF PRT BITS

- CO: Carrier Off Interrupt

- ES: Escape Interrupt

- QT: Quit Interrupt

- CHI: CHIO Interrupt

- AMC: AMC Interrupt

- RAP: Reduce Active Page Set

- RSI: Run Scheduler Initially

- RT: Real Time Interrupt

- MCT: Millisecond Compute Time

- PRI: Micro Scheduler Priority

- BLK: Blocked

- WAQ: Wake-up Queue

- CBC: Context Block Considered

- PDK: Process Delayed for Disk Transfers (No longer used)

- PQ: Process Queued on Sector Read List

- SWQ: On Swapper Request Queue

- SCQ: On Scheduler Queue

- MSQ: On Micro Scheduler Queue

- LDD: Process Loaded

- RUN: Process Running

- CPU: CPU Number

- RES: Resident Process

- NIN: Non-Interactive

- PRD: Process to be Destroyed

- ACT: Active Process in PRT

Figure 2.7

-24-

#### **3** INTRODUCTION - THE HARDWARE

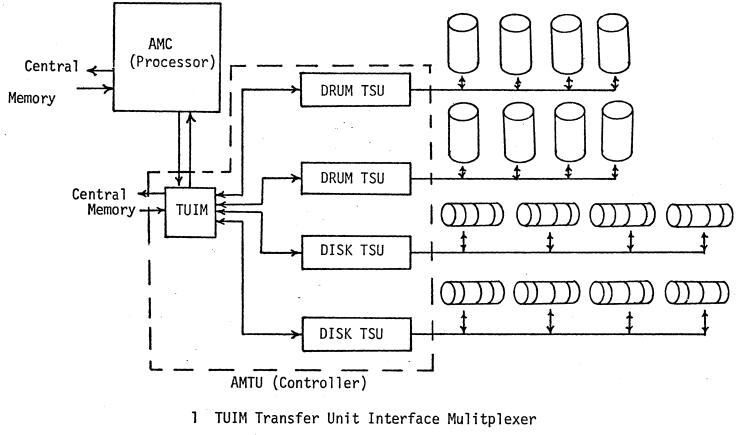

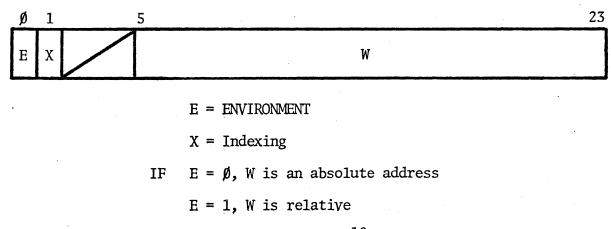

This section describes the characteristics of the hardware used by the memory manager. We shall discuss first the processor, then the drum and disk, and finally the controllers. Figure 3.1 shows the logical relation between the various components.

#### 3.1 The Processor

The processor that runs the memory manager is a microprocessor designed to provide a flexible and wide-ranging ability to perform varied processing and control functions in the system. The BCC 500 uses five of these processors, one of which is fully dedicated to memory management. The memory manager is also known as the Auxiliary Memory Control (AMC), processor.

This processor executes 90-bit microcode instructions, allowing a large number of possible functions to be carried out. Its cycle time is 100 nanoseconds. Basic boolean, shifting, and arithmetic functions are provided by the microprocessor. In addition to ten accumulator-like registers in the processor's arithmetic unit there are 64 scratchpad registers which allow quick access to variables which are referenced frequently.

Most of the memory management functions are implemented directly in the management processor's microcode, resulting in immense processing power for this (dedicated) purpose. Each of the other system microprocessors is similarly dedicated to one or more major system functions (including two that are "dedicated" to general calculation i.e., the CPU's). Except for the microcode and some easily wired special functions and conditions, each microprocessor is identical in construction. (The two CPU's are slightly different.)

-25-

#### 3.2 Drum and Disk Hardware

This section is concerned with the characteristics of the auxiliary memory hardware used by the memory manager. It is intended to describe everything about this hardware which can be observed from the vantage of the AMC.

#### 3.2.1 Data and Address Formats

The AMC is connected to a block transfer unit, or controller called an <u>auxiliary memory transfer unit</u> (AMTU). Figure 3.1 shows the AMC, the AMTU, and their connections with the Central Memory. The AMC uses its own path to Central Memory to access system tables and APU instructions (elaborated on in Sections 5 and 7). The AMTU's path to Central Memory is used only for block transfers of data between Central Memory and the rotating devices. The path between the AMC and the AMTU is used for control: AMTU commands coming from the AMC and status information returning to the AMC.

The AMTU consists of four logically similar block transfer devices called Transfer Sub-Units (TSUs) and a Transfer Unit Interface Multiplexer (TUIM). Each TSU is capable of accepting a single command from the AMC to perform a specified block transfer, to monitor the many types of errors which may occur during a transfer, to report on the status of a transfer after completion, and to report certain other status information--especially rotational position information for the devices--required by the AMC. The TSUs are independent of each other and may perform transfers simultaneously. They share a single Central Memory port; and the TUIM serves

-26-

<4 TSU's Transfer Sub-Units. <2 for drums, <2 for disks.</p>

<u><4</u> Units, drum or disk, per TSU

<4 simultaneous data transfers, 1 per TSU</pre>

<8 simultaneous seeks, 1 per disk</p>

Disk Page Format

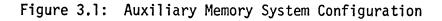

Fig. 3.2 Drum and Disk Page Formats

to multiplex their (independent) requests to the Central Memory, resolving conflicting requests within it. The TUIM also serves as a routing and gathering point for control and status information passed from and to the AMC.

There are two types of rotating memory: drum and disk. The terms drum and disk refer primarily to fixed-head and moveable-head devices respectively, rather than to actual details of construction. (In the present hardware, drums are drums and disks are disks, however.) Drums have a higher transfer rate and no track selection latency (seek time).

The TSUs are consequently of two types: drum and disk. Each can have four devices or <u>units</u> connected to it. Each unit is a logically independent device which rotates and positions its arms independently of the other units (that is, if it has arms). A TSU can perform data transfers for only one of its attached units at a time.

Data is recorded on both drum and disk in units of 2048, 24-bit-word records called <u>pages</u>. Recorded with each page is a 48-bit unique <u>name</u> (UN). Also associated with each disk page is a <u>header</u> which contains the physical address of the page. Figure 3.2 illustrates this. Note that on the disk, header, UN and data are three separate records; while on the drum, UN and data form a single record. Each data record has a checksum. A drum checksum is of length 24 bits and a disk checksum is of length 48 bits. Finally, each word is recorded on disk with an additional parity bit.

The drums were designed specifically to transfer at a high rate. The disk is not required to be quite so fast as the drum, as its main purpose in the system is bulk storage. When processes become active or files are

-29-

accessed their pages primarily reside on the drum; they move into core to be accessed and then back out onto the drum. When they are no longer actively being accessed they return to the disk.

Along with the discussion of the drum and disk, various terms that relate to them will be defined.

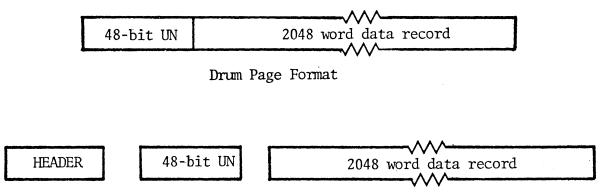

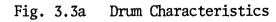

<u>Drum</u>: A page on a drum is defined by its sector and band position. A sector is an angular segment of the drum required to hold one page. As the drum rotates, succeeding sectors come under the heads. There are 24 sectors or pages around the drum. Information is transferred to/from drum in 24 bit-parallel fashion, i.e., 24 heads are used simultaneously. Since the drum is equipped with approximately 1100 heads, it is necessary to specify which grouping of 24 heads to use during a given transfer. This grouping is called a <u>band</u>. There are 42 bands on a drum, allowing for storage of 42 X 24, or 1008 pages (i.e., a total of 1008 X 2048 = 2,064,384 words) per drum.

With a rotation period of 33.3 msec, the drum transfers information at the rate of 750 pages/sec  $(1.5 \cdot 10^6 \text{ words/sec})$ . This is a rather high rate; however one must recall that this is a potential rate and not necessarily an actual one. It is the responsibility of the memory manager to make the most of this potential rate.

<u>Disk</u>: The disk is even more unconventional than the drum. It is a large file with 13 disks each  $4\frac{1}{2}$  feet in diameter. Like the drum, it transfers using a group of heads in parallel to define a logical "band". Since only six heads are used for the 24-bit words being transferred, however, the transfer is partly serial. The heads of a given band are located on a

-30-

- sectors bands 24

- 42 bands 33.3 ms rotation times 1.5 words/usec transfer rate (750 pages/sec)

-31-

DISK

5 SECTORS 24 BANDS 256 CYLINDERS 50 msec rotation .27 words/usec (135 pages/sec)

-32-

-33-

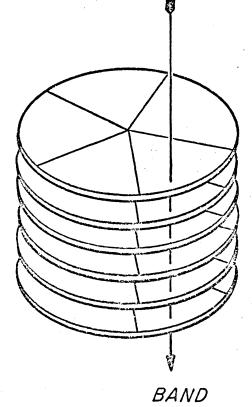

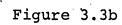

radius of one side of one of the disks. On a disk the head nearest the outer edge moves over a greater circumference than the inside head. (The disk is depicted in figures 3.3b and 3.3c) Thus more bits can be stored under the outside head than the inside head, and the bit rate per head is thus a function of the head's radius. Figure 3.3c shows the relative number of bits transferred during a unit of time. Note that these numbers add up to 50 bits, 2 for parity and 48 for two words. Most disks read words sequentially off tracks, as well as use worst case (low) densities that are the same no matter where the head positions is. The 500 method allows more density and greater transfer rate.

Whereas on the drum the heads are fixed, on the disk they are moveable. On the 500 disk there is an angular positioning arm which moves the heads over the correct logical track, or cylinder.

There are 256 angular positions. For components of the disk address, we use the terms band, sector, and cylinder. A sector is that angular portion of the disk necessary to store one page. There are five sectors per revolution on the disk. Figure 3.3b depicts the organization of the disk. The disk has 13 platters with 26 surfaces. Each surface corresponds to a band. A cylinder is one of the 256 angular positions. (The term cylinder - reminiscent of a drum - derives from the fact that for each track positioning the disk addressing structure otherwise resembles a drum.) In all, there are 30,720 pages (or  $63 \times 10^6$  words) on a disk unit. The disk has a 50 ms rotation time, with an average 4.8 µsec. to transfer a (double) word

All BCC 500 rotating memory parameters are summarized in Figure 3.4.

-34-

| Drum: | 24     | sectors/revolution                         |

|-------|--------|--------------------------------------------|

|       | 42     | bands                                      |

|       | 1,008  | pages/unit or 2,064,384 words/unit         |

|       | 2      | units (Hawaii configuration)               |

|       | 33.3   | ms rotation time                           |

|       | 1.5    | words/µsec transfer rate                   |

|       | ~30    | µs sector gap                              |

| Disk: | 5      | sectors/revolution                         |

|       | 24     | bands                                      |

|       | 120    | pages/cylinder or 240,000 words/cylinder   |

|       | 256    | cylinders/unit                             |

|       | 30,720 | pages/unit or 62,914,560 words/unit        |

|       | 2      | units (Hawaii configuration)               |

|       | 50     | ms rotation time                           |

|       | .21    | words/µsec transfer rate                   |

|       | ~50    | µs sector gap                              |

|       | 65-225 | ms seek time. This subject is discussed in |

|       |        | detail elsewhere                           |

Figure 3.4 Parameters of ECC 500 Rotating Memories

-35-

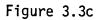

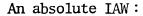

## AMC Disk address internal form:

The disk unit has 5 sectors per band, 24 bands per cylinder, and 256 cylinders. There are two TSUs which may control disks (the Hawaii configuration has only one, however). Each TSU may have up to four disk units attached to it. This information has been packed into one word in order to keep tables small.

| $\square$ | TSU <sup>3</sup> | TRACK NUMBER | 11 | BAND | 17 | SECTOR | 21 | 23<br>UNIT |

|-----------|------------------|--------------|----|------|----|--------|----|------------|

|           | 2                |              | 8  |      | 6  |        | 4  | 2          |

## AMC Drum address internal form:

The two million word drum has 24 sectors per band and 42 bands. Since space in the address word is not as critical in the drum address, the fields have been adjusted to correspond to the device address fields in the TSU.

The address of a page, as accepted by the TSU, is contained in one word with the following format:

2 - 9 cylinder (disk only) 10 - 16 band 17 - 21 sector

The other bits in the word are not used. This format is shown in Fig. 3.5a.

| AMC BUS       | Ø123456789101112131415161718192021222 | .3 |

|---------------|---------------------------------------|----|

| CHECK Ø       | ø 2                                   | 3  |

| CHECK 1       | Ø 2                                   |    |

| STATUS*       | 13 2                                  | 3  |

| un ø          | Ø 2                                   | 3  |

| UN 1          | Ø 2                                   | 3  |

| PAGE ADDR.    | CYLINDERBANDSECTOR2910161721          |    |

| CORE ADDR.    | 5 2                                   | -  |

| INSTR.*       | TAG<br>Ø 3 15 21                      |    |

| WORD COUNT    | 12 2.                                 | 3  |

| UNIT NO.      | 22                                    | 23 |

| *Amplified or | on next page                          |    |

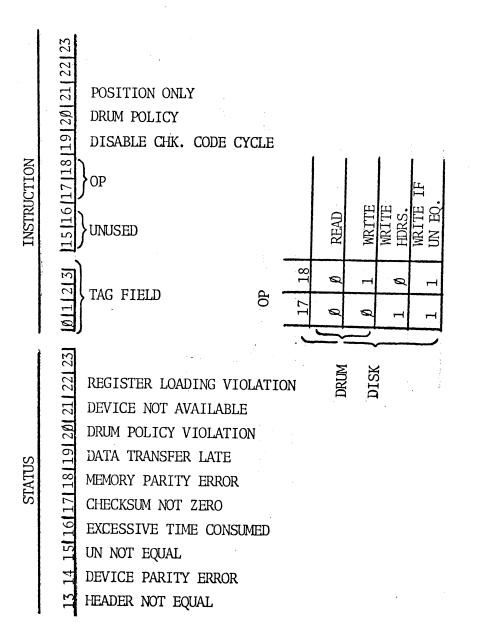

Fig. 3.5a TSU Control Registers

Figure 3.5b: TSU Registers

-38-

## 3.2.2 Position Counters

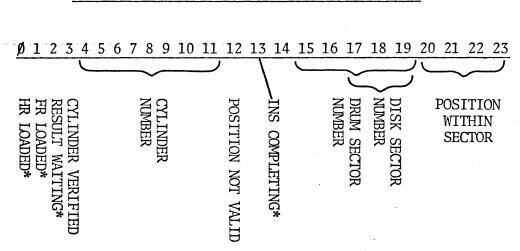

Each TSU has four registers called <u>position counters</u> (PCs), one for each unit. The format of a PC is shown in Fig. 3.6a. The four bits marked \* show the same in all four PCs; they are identical copies of indicators and are discussed in Section 3.2.4. The rest of the PC gives information about the arm position and rotational position of its unit, as follows.

•the sector number tells which sector is currently under the heads

•for the disk, the cylinder number tells which cylinder is currently under the heads or being sought for. For the details of how to interpret this field and the related CYLINDER VERIFIED bit, see Section 3.2.10.

•the position within the sector (PWS) field tells approximately where in the sector the heads currently are.

Figure 3.6b tells how to interpret the PWS field for the drum. The reasons for the strange intervals are historic.

Note especially the definition of the end of sector (EOS) time as the time the PWS field goes from 15 to  $\emptyset$ . This is the reference point from which most activity in the TSU is measured.

If the POSITION NOT VALID bit is on, the information in the PC is meaningless because it is being incremented. If this bit is on, the PC is merely reread until its bit goes off.

The PC for a disk unit is not affected in any way by a seek taking place for that unit.

-39-

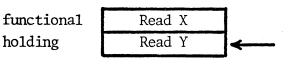

## 3.2.3 TSU Control Registers

A TSU (each TSU operates completely independently of the others) has two sets of control registers. One set, called the <u>functional</u> registers (FR), contains the instruction currently being executed. The other set, called the <u>holding</u> registers (HR), can be read or written by the AMC. Whenever an instruction is completed, and at certain other times, the FR are exchanged or <u>swapped</u> with the HR. Precise details of this process are presented below. Figure 3.5a summarizes the register formats and should be referred to while reading this section.

Timing in the TSU is geared to the transfer of pages between a rotating device and central memory. The time at which most things happen is the EOS time (see Section 3.2.2), the time at which all the data of a sector, and any auxiliary information (checksums, etc.) which the hardware may suffix to the data, has passed by the heads. At this time the inter-sector gap is under the heads; after it has passed by, information related to the next sector begins to come under the heads. We will call this time T, sometimes with a subscript to denote the sector which has just passed by. An EOS time occurs in each unit at regular intervals. The unit addressed by the functional UNIT NO (the <u>selected</u> unit) provides the EOS time for the TSU. A TSU EOS occurs at regular intervals except when a new unit is selected; this case is discussed below.

The TSU works in the following way. The AMC loads the control registers in the order: instruction register, core address, word count, page address, UN, and unit number, into the HR (FR are not generally accessible to the AMC).

# POSITION COUNTER (3-11 UNUSED IN DRUM TSU)

Fig. 3.6a Position Counter (PC) Format

| Ticks     | PWS | Length of<br>Interval | What is<br>Happening                      |

|-----------|-----|-----------------------|-------------------------------------------|

| Ø - 23    | ø   | 24                    | Inter-sector gap                          |

| 24 - 70   | 1   | 47                    | Preamble, data starts                     |

| 71 - 134  | 2   | 64                    |                                           |

| 135 - 157 | 3   | 23                    |                                           |

| 158 - 165 | 4   | 8                     |                                           |

| 166 - 212 | 5   | 47                    |                                           |

| 213 - 276 | 6   | 64                    | Data                                      |

| 277 - 299 | 7   | 23                    |                                           |

| 300 - 307 | 8   | 8                     |                                           |

| 308 - 354 | 9   | 47                    |                                           |

| 355 - 418 | 10  | 64                    |                                           |

| 419 - 441 | 11  | 23                    |                                           |

| 442 - 449 | 12  | 8                     |                                           |

| 450 - 496 | 13  | 47                    |                                           |

| 497 - 560 | 14  | 64                    | Data, checksum, post-<br>amble, dead time |

| 561 - 584 | 15  | 23                    | Dead time                                 |

One tick = 2.4  $\mu$ s.

584 ticks = 1.4 ms = 1 sector time

Transition from PWS=15 to PWS=Ø is End-Of-Sector (EOS)

# Fig. 3.6b Drum Record Timing

We assume sector i is now under the heads. When the EOS time  $T_i$  occurs, the TSU swaps the registers. This takes about 1 µsec. The TSU then starts "executing" the instruction in the FR i.e., it attempts the indicated transfer or arm positioning. Let us say the indicated transfer is for sector j. Then the TSU waits for sector j to come under the heads and does the transfer. At  $T_j$  the registers are swapped again, and the AMC can then look at the HR to find out what happened during the instruction. At the same time, if the HR were loaded again after  $T_i$  but before  $T_j$ , the new instruction is being executed by the TSU. The AMC thus has one sector time to examine the results of the transfer done in the previous sector and set up an instruction for execution in the next sector and can thus accomplish continuous transfer.

Matters are slightly complicated if the unit is changed since the units are not rotationally synchronized. The swap occurs as usual at  $T_i$ . Then the TSU starts to look for an EOS on the newly selected unit. This EOS is called a <u>synchronizing</u> EOS, and until it occurs the TSU is <u>suspended</u>. The synchronizing EOS serves only to activate the suspended TSU. When it occurs, execution of the FR instruction begins, exactly as it would have at  $T_i$  if there had not been a unit change. The second EOS on the new unit is the next effective EOS after  $T_i$ . It follows that the interval between TSU EOS times will be a variable and as long as twice the normal interval following a unit change.

There is a special feature in the hardware to take care of a dualpositioner disk, in which the two units rotate synchronously. When the TSU switches from one unit of the dual positioner to the other it behaves as though

-43-

(Instruction register only)

1) during sector --

functional holding

| 1 | Read X |

|---|--------|

|   | empty  |

2) shortly before sector ends --

loaded by memory manager for next sector

3) end of sector (EOS) --

| functional | Read Y | 12 |

|------------|--------|----|

| holding    | Read X | ]ノ |

swap Registers; use information from functional register (now in holding register) to determine success of last operation; Read Y now ready for next sector

4) before end of succeeding sector --

Instruction Y now being executed Holding register loaded with instruction for the sector to follow

The above pattern is repeated with the functional register instruction being executed while the holding register is loaded in preparation for the next sector. Then between sectors, the registers are again swapped.

# Fig. 3.7 TSU Register Loading

-44-

no unit change had occurred, i.e. it never becomes suspended and no synchronizing EOS is required. If this case were not handled specially, a unit switch on the dual positioner would always cause the TSU to be suspended for a full sectortime.

When the AMC loads the registers, it must load the instruction register first and the unit number last. If the instruction register is not loaded between  $T_i$  and  $T_{i+1}$ , no instruction will be executed during sector i+2. In this case the TSU is said to be <u>idle</u>. A swap occurs as usual at  $T_{i+1}$  to bring the results of the instruction which was loaded at  $T_i$  back to the HR for examination. If the HR are not loaded during sector i+2, however, no swap occurs at  $T_{i+2}$ . In this case the TSU remains idle during sector i+3, and continues to be idle until an instruction is loaded into HR. If this happens during sector j, a swap will occur at  $T_j$  and the TSU will cease to be idle at that point.

If a swap occurs after the instruction register has been loaded but before the unit number has been loaded, a <u>register loading violation</u> occurs. The instruction is taken as a NOP and the status register will indicate the violation after execution of the NOP is complete. See Section 3.2.5 for details of instruction timing, and Section 3.2.9 for how the loads are handled.

## 3.2.4 Indicators

The four indicator bits marked \* in any position counter are each copies of four indicators (see Section 3.2.2 for the significance of the rest of the word) which record the progress of an instruction through the cycle just described. When the holding instruction register is loaded, the HR LOADED

-45-

bit (bit  $\emptyset$  of any position counter) is set. HR LOADED is cleared when the registers are swapped, so it is set exactly when there is an instruction loaded (or partially loaded) in the HR and awaiting execution.

The FR LOADED bit (bit 1 in the PCs) is set from HR LOADED when the registers are swapped. It is therefore set exactly when there is an instruction in the FR being executed or awaiting execution. Note that this bit comes on when an instruction enters the FR even if the sector addressed by the instruction is not under the heads. It therefore provides no information about whether the data transfer is actually underway.

This information is provided by the INS COMPLETING bit (bit 13 in the PCs) which is on if FR LOADED is on and the instruction will complete at the end of the current sector on the selected unit. More precisely FR LOADED may be on and INS COMPLETING off only if

1) the TSU is suspended, or

2) the instruction has DRUM POLICY= $\emptyset$ , and POSITION ONLY= $\emptyset$  and address sector i is not now under the heads (or, in the case of a disk write, CYLINDER VERIFIED is off).

In all other cases FR LOADED implies INS COMPLETING. These cases may be classified as follows:

3) the instruction has DRUM POLICY=1

4) the instruction has POSITION ONLY=1

5) the instruction has DRUM POLICY= $\emptyset$ , POSITION ONLY= $\emptyset$ , addresses sector i and sector i is now under the heads (and, in the case of a disk write, CYLINDER VERIFIED is on).

6) there is a register loading violation

7) the instruction consumes excessive time (see Section 3.2.7).

The definition implies that INS COMPLETING is always on for exactly one sector per completed instruction.

Finally, the RESULT WAITING bit (bit 2 of the PCs) is set from FR LOADED when the registers are swapped. It is cleared when AMC reads the STATUS register. It thus indicates that there is information waiting to be collected about the fate of the last command. The TSU will not swap new values from the FR into the HR if the RESULT WAITING bit is on. This situation occurs if the AMC has not yet read the results of a previous transfer which would be clobbered by the results of the current transfer.

The three bits HR LOADED, FR LOADED and RESULT WAITING may be thought of as resting places for a single bit indicating the presence of an instruction which goes from AMC to HR to FR to HR and back to AMC.

All four indicator bits may change state about 1  $\mu$ sec after a TSU EOS. The INS COMPLETING bit may be set about 1  $\mu$ sec after a synchronizing EOS. These are the only times that the indicators can change state.

## 3.2.5 TSU Instructions

There are two instructions which may be given to a drum TSU. All drum instructions have POSITION ONLY= $\emptyset$ . Normally drum instructions have DRUM POLICY=1 and DISABLE CHECK CYCLE= $\emptyset$  (see below).

$OP=\emptyset$ : Transfer WORD CNT words, from the beginning of drum page PAGE ADDR to central memory locations CORE ADDR through CORE ADDR+WORD CNT-1. At the end

-47-

of the read the UN of the page is left in UNØ and UN1. A checksum for the page (not including the UN) is in CHECKØ; if it is non-zero the data has been read from the drum incorrectly, i.e., there has been a read error. In this case the CHECKSUM NOT ZERO bit in STATUS will be set. PAGE ADDR will be pointing to the next page, CORE ADDR to the first unreferenced core location and WORD CNT will be 77757776B (i.e., -2 in its context); these three registers are normally of little interest after the read. A variety of useful information discussed in detail in Section 3.2.7 is left in STATUS. On a read the checksum is computed for the entire page, regardless of the WORD CNT, as long as it is  $>\emptyset$ .

OP=1: Transfer the UN in UNØ and UN1 and the contents of central memory locations CORE ADDR through CORE ADDR+WORD CNT-1 followed by 2048-WORD CNT zero words to the drum page at PAGE ADDR. CHECKØ and CHECK1 are of no value after this instruction. STATUS reports unusual conditions as for a read, and the addresses and count are left as for a read.

There are five instructions which may be given to a disk TSU. Four are data transfer instructions and have POSITION ONLY= $\emptyset$ . These instructions may have DRUM POLICY on or off (see Section 3.2.6). They normally have DISABLE CHECK CYCLE= $\emptyset$ .

OP=Ø: Read, which works exactly like drum read, except that the disk has two checksum words, CHECKØ and CHECK1. A disk read is not affected by CYLINDER VERIFIED, but it will set CYLINDER VERIFIED if there is no error; see Section 3.2.10.

-48-

OP=1: Write, which works exactly like drum write, except that it is not executed until CYLINDER VERIFIED for the selected unit is set; see Section 3.2.10.

OP=2: Write header, which is an instruction used only by hardware maintenance personnel and is used only at disk maintenance times.

OP=3: Write with UN check. This instruction is like write except that instead of writing UNØ and UN1 it compares them with the values recorded on the disk. If the disk values agree the write proceeds normally. If not the write is aborted and the UN NOT EQUAL bit in STATUS is set. This is the only condition which sets this bit.

The fifth disk TSU instruction has POSITION ONLY=1. The value of OP is ignored in this case. This instruction causes the disk to move the arms to the cylinder specified by PAGE ADDR. The other registers are ignored. No data is transferred. This instruction requires one sector time for execution plus any time during which the TSU is effectively suspended due to lack of cylinder verification. DRUM POLICY must be  $\emptyset$  for this instruction.

The DISABLE CHK CODE CYCLE bit alters the method of computing the checksum words. Normally for the drum (disk) CHECKØ (CHECKØ and CHECK1) is computed by starting with the first word (double word) and then as each word (double-word) arrives doing an Exclusive OR of it with CHECKØ (CHECKØ and CHECK1) and cycling the result left 1. The cycle is suppressed by this bit. The suppression of the check code cycle diminishes the effectiveness of the check code and is intended for hardware check-out purposes only. All other use of drum or disk involving data must specify cycling of the check code.

The TAG FIELD is not used or modified in any way by the TSU. It is

-49-

provided solely for the convenience of the AMC, which by using it may attach a 4-bit tag to an instruction. The tag bits are copied, along with the rest of the instruction, from HR to FR and back to HR. The tag is intended to help identify the loss of instructions due to register loading violations.

## 3.2.6 Instruction Timing

If DRUM POLICY=1 in any instruction and the unit is not changed, the sector position of the page addressed must be the one which will be under the heads immediately after the swap which brings the instruction into the FR, the arm position must be the current arm position (only relevant for disk), and CYLINDER VERIFIED must be set for a disk write. If this is not the case, the instruction is aborted and DRUM POLICY VIOLATION is set in STATUS. If the unit is not changed the instruction requires exactly one sector time to execute.

If DRUM POLICY=1 in any instruction and the unit is changed, the page addressed must be the one which will be under the heads after the synchronizing EOS swap. In this case the instruction requires somewhere between one and two sector times to execute.

If DRUM POLICY= $\emptyset$ , this restriction is not enforced. In this case a transfer instruction may require as much as one full device revolution, plus seek time if the arm position for the page addressed differs from the current arm position and the instruction is a write. The instruction will complete at the first EOS time for the sector addressed after the arms have verified a new position, if required. A POSITION ONLY instruction requires exactly one sector time to

-50-

execute regardless of the PAGE ADDR, unless units are switched, in which case it requires between one and two sector times.

A swap can occur only at a TSU EOS. A swap will occur at each TSU EOS where

HR LOADED or (INS COMPLETING and not RESULT WAITING)

#### 3.2.7 Status Register

The STATUS register contains an assortment of bits which report on errors which may occur during execution of an instruction. They are catalogued here, together with an exhaustive description of the conditions which cause them to be set. The FR STATUS is cleared when a swap occurs. It may then accumulate bits until the next swap, at which time its contents are copied into HR STATUS and it is cleared again. A successful instruction will have a cleared STATUS register.

In the absence of any other comment, an instruction which causes a STATUS bit to be set does nothing and requires exactly one sector time (plus unit change time). Such an instruction leaves WORD CNT = 77757777B and CORE ADDR and PAGE ADDR unchanged. When a data transfer has started it can be aborted by DATA TRANSFER LATE; memory parity errors do not abort the transfer.

REGISTER LOADING VIOLATION is set if the instruction register has been loaded when a swap occurs but the unit number has not. It appears in FR STATUS after the swap which interrupts the loading, and then in HR STATUS after the next swap. See Section 3.2.9 for a discussion of register loading. RLV will also occur if the AMC attempts to

-51-

load the HR when they contain the results of a previous transfer (RESULT WAITING=1). This will happen if, for example, a swap occurs before the AMC can even attempt to load the instruction register. The RLV will appear in the HR at the end of the interval in which this happens, or as soon as the RESULT WAITING bit is cleared (STATUS is read).

- DEVICE NOT AVAILABLE is set if the unit addressed by the UNIT NO register is not connected to the TSU, has power turned off, or is in some bad state.

- 3) DRUM POLICY VIOLATION is set if DRUM POLICY=1 and the page addressed by PAGE ADDR is not under the heads when the instruction arrives in the FR. (See Section 3.2.6.)

- 4) DATA TRANSFER LATE is set if the memory fails to deliver a word soon enough (write) or to absorb one soon enough (read). When it is set the rest of the transfer is aborted; in a write zeros are written. Timing is not changed.

- 5) MEMORY PARITY ERROR is self-explanatory. Timing is not changed and the transfer is not aborted.

- 6) CHECKSUM NOT ZERO is set at the end of a read if CHECKØ (drum) or CHECKØ and CHECK1 (disk) are non-zero, indicating that an error has occurred. Timing is not changed. Note that the UN is <u>not</u> included in the checksum.

-52-

- 7) EXCESSIVE TIME CONSUMED is set if the instruction remains in the FR for more than 1 second. This can happen if the page address is for a non-existent page or if the seek mechanism on the disk fails. The instruction does nothing. INS COMPLETING is set at the next TSU EOS after the 1 second has elapsed, and the instruction completes at the following TSU EOS as usual. ETC can only happen on an instruction with DRUM POLICY=POSITION ONLY=Ø which has a PAGE ADDR whose sector number is too large for the unit (or as a result of hardware failure).

- 8) UN NOT EQUAL (disk write with UN check only) is set if the UN recorded on disk differs from UNØ and UN1. No data is transferred, the disk is not changed, and timing is not changed.

- 9) DEVICE PARITY ERROR (disk read or disk write with UN check only) is set if a word is read from the disk and has the wrong parity. Timing is not changed. One parity bit is recorded with each word on disk, in addition to the two word checksum at the end of the record. This error can occur when reading the UN as well as when reading data. The cases cannot be distinguished.

- 10) HEADER NOT EQUAL (disk transfer only) is set if the page address recorded in the header for the page disagrees with the address in the FR PAGE ADDR register. This can happen only if the header is wrong or was read incorrectly.

The following bits abort transfers before central memory or drum/disk is changed: REGISTER LOADING VIOLATION, DEVICE NOT AVAILABLE, DRUM POLICY VIOLATION, EXCESSIVE TIME CONSUMED, UN NOT EQUAL, HEADER NOT EQUAL.

-53-