## MODEL 990/10A COMPUTER

# **GENERAL DESCRIPTION**

WARNING: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

WARNING: No user serviceable, installable, or replaceable parts are inside the Model 990A13 chassis. The card cage area of the Model 990A13 chassis contains hazardous live electrical components involving risk of energy hazard-high current levels. Installation instructions provided in this manual are to be used by trained personnel familiar with electrical hazards and with a knowledge of basic hand tools and cabling techniques. A detailed knowledge of computer hardware or software is not required.

## LIST OF EFFECTIVE PAGES

Insert latest changed pages and discard superseded pages.

Note: The changes in the text are indicated by a change number at the bottom of the page and a vertical bar in the outer margin of the changed pages, with the following exceptions:

- A change number at the bottom of the page but no change bar indicates either a deletion or a page layout change.

- An entire section with no change bars but with change numbers at the bottom of each page is an entirely new section.

Model 990/10A Computer, General Description (2302633-9701)

| Original Issue | September  | 1982 |

|----------------|------------|------|

| Change 1       | . February | 1984 |

| Change 2       | May        | 1985 |

© 1982, 1984, 1985, Texas Instruments Incorporated. All Rights Reserved.

No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Texas Instruments.

The manual consists of the most recent full revision (indicated as 0) and the following changed pages since the last revision. The total pages and change numbers in this publication are as follows:

| Page  | Change No.                                           | Page                                                                                                                                                                                                                                                          | Change No.                                         | Page                                                                                                                                                                               | Change No.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cover | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c} 1-9 \ - \ 1-23 \\ 1-24 \ - \ 1-2 \\ 1-26 \ \dots \\ 2-1 \ \dots \\ 2-3 \ \dots \\ 2-3 \ \dots \\ 2-4 \ - \ 2-6 \\ 3-1 \ - \ 3-4 \\ 3-5 \ \dots \\ 3-6 \ - \ 3-8 \\ 3-9 \ \dots \\ 3-10 \ \dots \\ 3-11 \ \dots \\ 3-12 \ \dots \end{array}$ | $egin{array}{cccccccccccccccccccccccccccccccccccc$ | 3-15 - 3-18<br>4-1<br>4-2<br>4-3 - 4-14<br>4-15<br>4-16<br>4-16<br>4-17/4-18<br>A-1 - A-10<br>Index-1 - I<br>Customer F<br>Business Re<br>Questionna<br>Business Re<br>Inside Cove | 2         3       0         0       0         1       0         1       0         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1         1       1 |

# Preface

This manual provides information about the Model 990/10A Computer and is directed to both the installation personnel and the end-user.

Information in this manual is divided into the following sections:

#### Section

- 1 General Contains physical and functional descriptions that acquaint the user with the hardware components and capabilities of the Model 990/10A Computer.

- 2 Installation Outlines procedures for unpacking the Model 990/10A Computer from its shipping container and setting the option jumpers and switches.

- 3 Operation Describes the indicators on the front panel and PWB and provides general operating procedures.

- 4 Programming Presents information for use by programmers on the function of the processor and the asynchronous communication controller.

#### Appendix

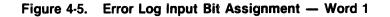

A Using the Multiprocessing Interface — Contains information on system configuration and programming the multiprocessing interface.

The following documents contain additional information related to the Model 990/10A Computer.

| Title                                                                       | Part Number  |

|-----------------------------------------------------------------------------|--------------|

| Model 990/10A Computer Maintenance Manual — Field<br>Theory and Maintenance | 2302634-9701 |

| Model 990/10A Computer Maintenance Manual — Depot<br>Theory and Maintenance | 2302635-9701 |

| Model 990 Computer 990/10 and 990/12 Assembly<br>Language Reference Manual  | 2270509-9701 |

| Model 990 Computer Diagnostics Handbook                                     | 945400-9701  |

| Model 990A13 Chassis Maintenance Manual — General<br>Description            | 2308774-9701 |

| ROM Loader User's Guide                                                     | 2270534-9701 |

# Contents

#### Paragraph

Title

#### Page

## 1 — General Description

•

| 1.1     | General                                        |

|---------|------------------------------------------------|

| 1.2     | Purpose of Equipment                           |

| 1.3     | Equipment Description                          |

| 1.3.1   | Microprocessor                                 |

| 1.3.2   | Memory                                         |

| 1.3.2.1 | Memory Correction and Control1-4               |

| 1.3.2.2 | Memory Mapping                                 |

| 1.3.3   | Input/Output (I/O)                             |

| 1.3.3.1 | TILINE Control                                 |

| 1.3.3.2 | CRU Interface                                  |

| 1.3.3.3 | Asynchronous Communication Controller          |

| 1.4     | Specifications                                 |

| 1.5     | Functional Description of Equipment1-6A        |

| 1.5.1   | Microprocessor                                 |

| 1.5.2   | Memory Mapping                                 |

| 1.5.2.1 | Map Operation                                  |

| 1.5.2.2 | Map Initialization                             |

| 1.5.2.3 | TILINE Peripheral Control Space (TPCS) Mapping |

| 1.5.2.4 | Scratch Pad RAM                                |

| 1.5.2.5 | Loader/Self-Test ROM Mapping1-9                |

| 1.5.3   | Memory Correction and Control                  |

| 1.5.4   | Memory Allocation                              |

| 1.5.5   | Interrupts                                     |

| 1.5.5.1 | Level 0 Interrupt (Power Restored)             |

| 1.5.5.2 | Level 1 Interrupt (Power Failure Imminent)     |

| 1.5.5.3 | Level 2 Interrupt (Error Conditions)           |

| 1.5.5.4 | Level 3 Host Processor Interrupt               |

| 1.5.5.5 | Level 5 or 15 Interrupt (Real-Time Clock)      |

| 1.5.5.6 | Level 8 (EIA Port Interrupt)                   |

| 1.5.5.7 | External Interrupts                            |

| 1.5.5.8 | Nonmaskable Interrupt (NMI)1-13                |

| 1.5.6   | Communication Register Unit (CRU) Controller   |

| 1.5.6.1 | Parallel CRU Operations                        |

| 1.5.6.2 | CRU Addressing                                 |

| 1.5.7   | Backpanel Interface                            |

| 1.5.8   | Front Panel Interface                          |

| 1.5.9   | Asynchronous Communication Port                |

| 1.5.10  | TILINE Interface                               |

ĺ

•

| Paragraph | • Title       | Page         |

|-----------|---------------|--------------|

| 1.5.10.1  | TILINE Master | 1-25         |

| 1.5.10.2  | TILINE Slave  | 1-25         |

| 1.5.10.3  | TILINE Hold   | 1-26         |

| 1.5.10.4  | TILINE Wait   | 1 <b>-26</b> |

### 2 — Installation

| 2.1   | General                                                  |

|-------|----------------------------------------------------------|

| 2.2   | Unpacking/Packing 990/10A Board2-1                       |

| 2.3   | 990/10A Installation Procedures                          |

| 2.3.1 | Setting Option Switches and Jumpers on the 990/10A Board |

## 3 — Operation

| 3.1     | General                                                        |

|---------|----------------------------------------------------------------|

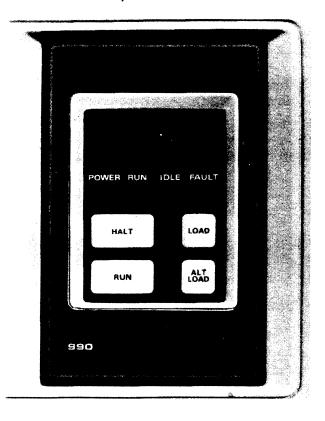

| 3.2     | Control/Display Module Controls and Indicators                 |

| 3.2.1   | Controls                                                       |

| 3.2.1.1 | HALT Switch                                                    |

| 3.2.1.2 | RUN Switch                                                     |

| 3.2.1.3 | LOAD Switch                                                    |

| 3.2.1.4 | ALT LOAD Switch                                                |

| 3.2.2   | Indicators                                                     |

| 3.2.2.1 | Hexadecimal Display                                            |

| 3.2.2.2 | POWER LED                                                      |

| 3.2.2.3 | FAULT LED                                                      |

| 3.2.2.4 | RUN LED                                                        |

| 3.2.2.5 | IDLE LED                                                       |

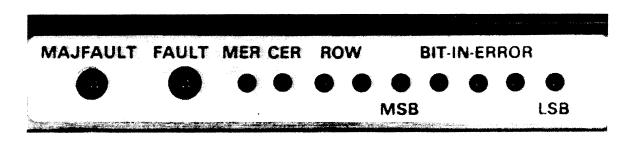

| 3.3     | 990/10A PWB Indicators                                         |

| 3.3.1   | Major Fault LED                                                |

| 3.3.2   | Fault LED                                                      |

| 3.3.3   | Memory Error Indicators                                        |

| 3.3.3.1 | Double-Bit Error                                               |

| 3.3.3.2 | Single-Bit Error                                               |

| 3.3.3.3 | ROW                                                            |

| 3.3.3.4 | BIT-IN-ERROR                                                   |

| 3.4     | 990/10A Self-Test                                              |

| 3.4.1   | Self-Test Description                                          |

| 3.4.1.1 | Major Fault Test                                               |

| 3.4.1.2 | General Fault Test                                             |

| 3.4.2   | Self-Test Execution Time                                       |

| 3.4.3   | Self-Test Error Reporting                                      |

| 3.4.4   | Bypassing a Self-Test Failure                                  |

| 3.4.5   | Other Information Available as a Result of a Self-Test Failure |

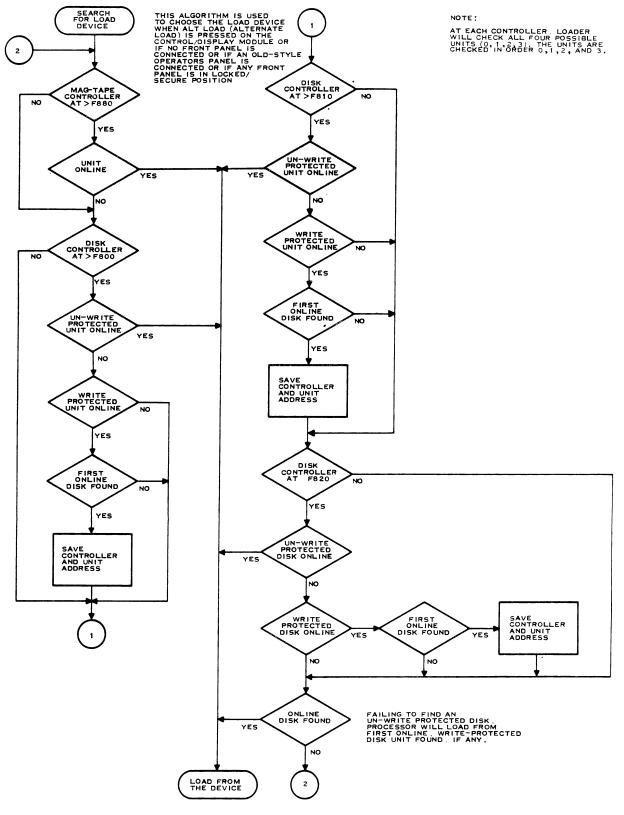

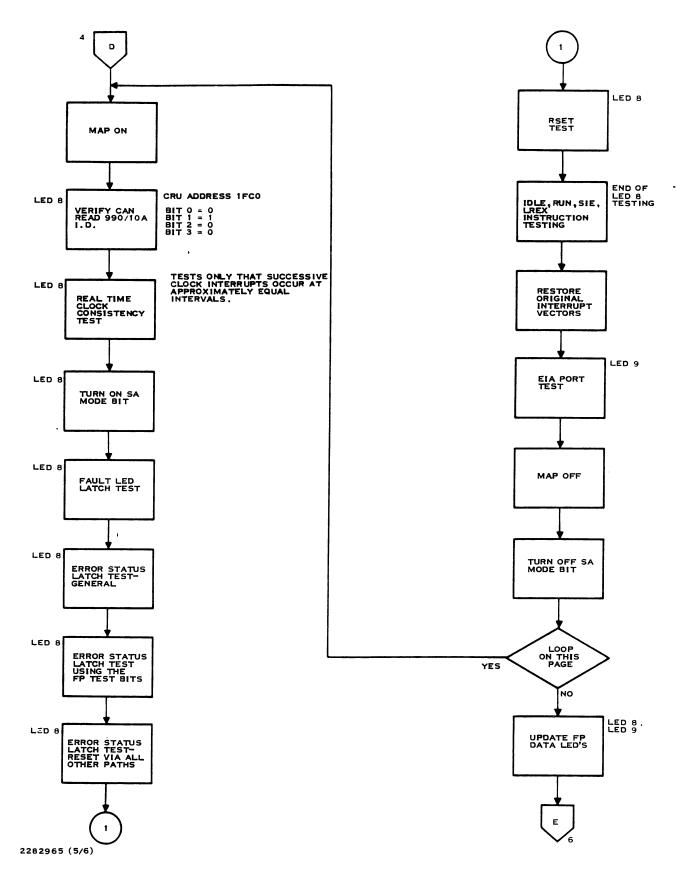

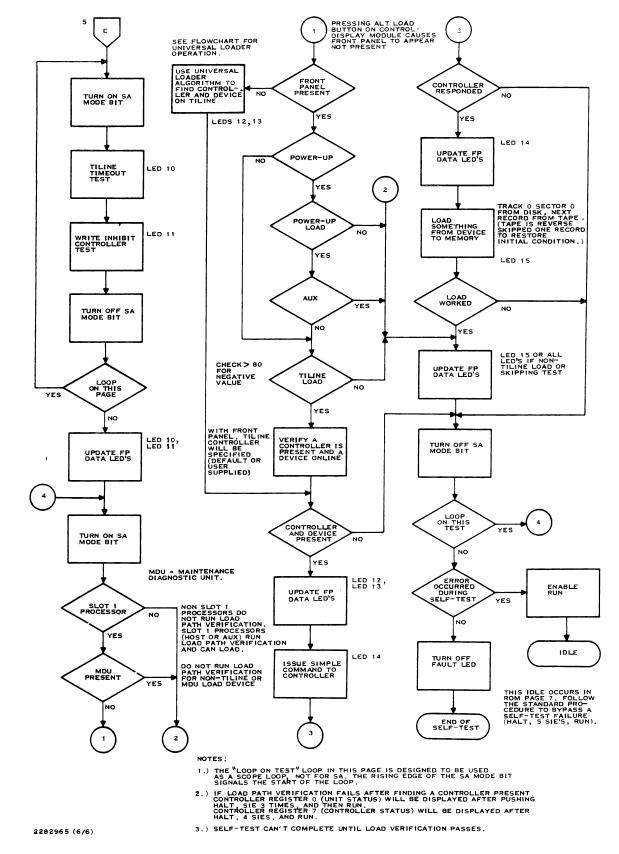

| 3.5     | Load Device Verification                                       |

| 3.5.1   | Special Features of Load Device Verification                   |

| 3.5.2   | Understanding Self-Test Error Codes                            |

| 3.5.3   | Understanding Loader Error Codes                               |

#### Paragraph

#### Title

#### Page

### 4 — Programming

| 4.1   | General                                        |

|-------|------------------------------------------------|

| 4.2   | Instruction Set                                |

| 4.2.1 | Additional Instructions                        |

| 4.2.2 | Mapping Instructions (LMF, LDS, LDD)4-1        |

| 4.3   | Status Register                                |

| 4.4   | Error Status Register                          |

| 4.5   | TMS9902 Asynchronous Communication Controller  |

| 4.5.1 | CRU Implementation External to the TMS 99024-4 |

| 4.5.2 | Interrupt Output                               |

| 4.5.3 | Control and Data Output                        |

| 4.5.4 | Status and Data Input4-11                      |

| 4.6   | Memory Error Log                               |

| 4.6.1 | Error Correction Test                          |

| 4.6.2 | Output Bits                                    |

| 4.6.3 | Input Bits                                     |

## Appendix

| Appendix | Title                            | Page       |

|----------|----------------------------------|------------|

| A        | Using the Multiprocess Interface | <b>A-1</b> |

### Index

## Illustrations

|   | Figure                           | Title                                                                                                                                                                                                                      | Page                |

|---|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 1 | 1-1<br>1-1A<br>1-2<br>1-3<br>1-4 | Model 990/10A Processor BoardModel 990/10A Surface Mount 1-Megabyte Processor BoardTILINE Peripheral Control Space ImplementationFlowchart of Nonmaskable Interrupt and Front Panel CodeSingle-Bit CRU Address Development | 1-2A<br>1-8<br>1-14 |

| Ĩ | 2-1<br>2-2                       | Switch and Jumper Locations                                                                                                                                                                                                |                     |

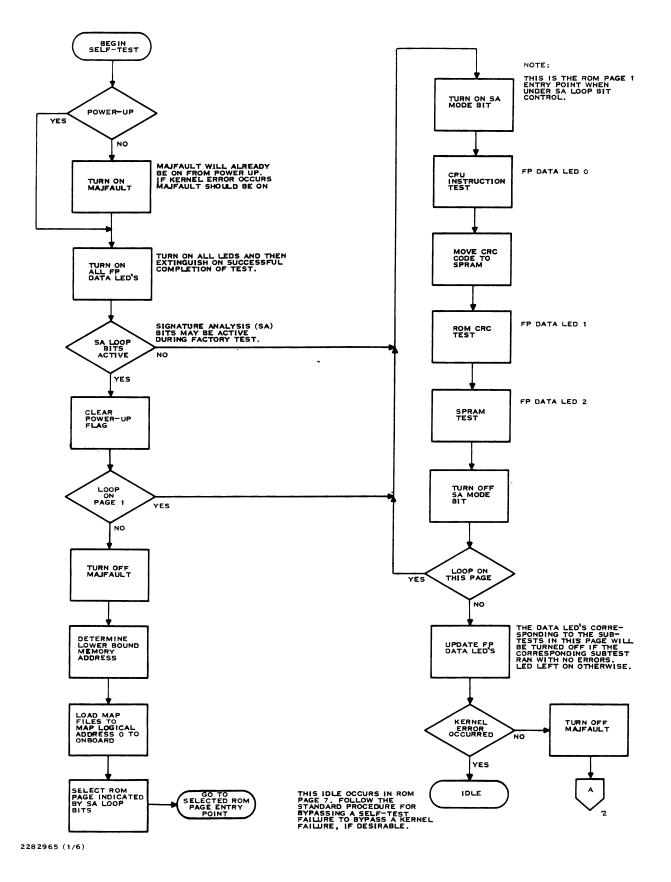

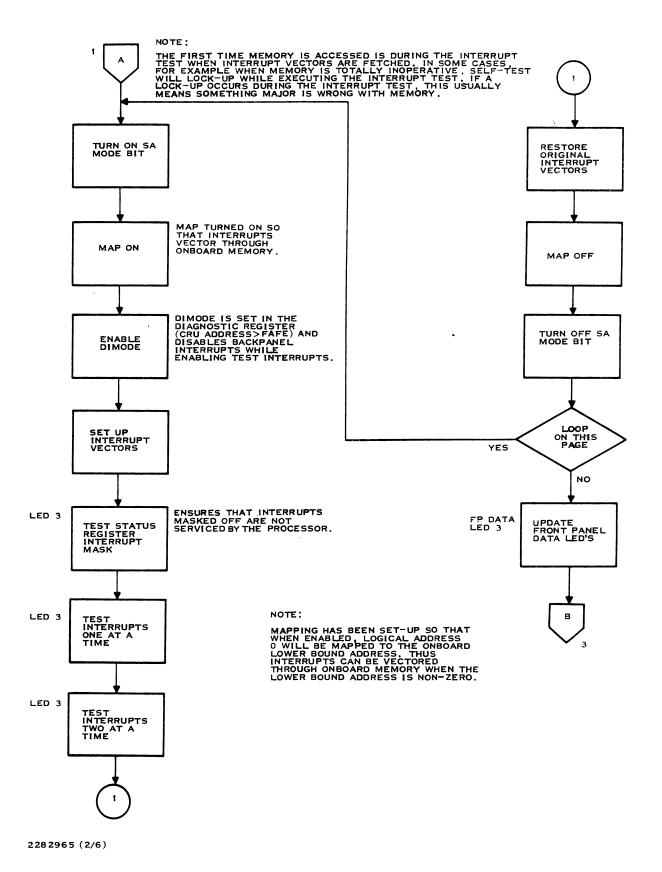

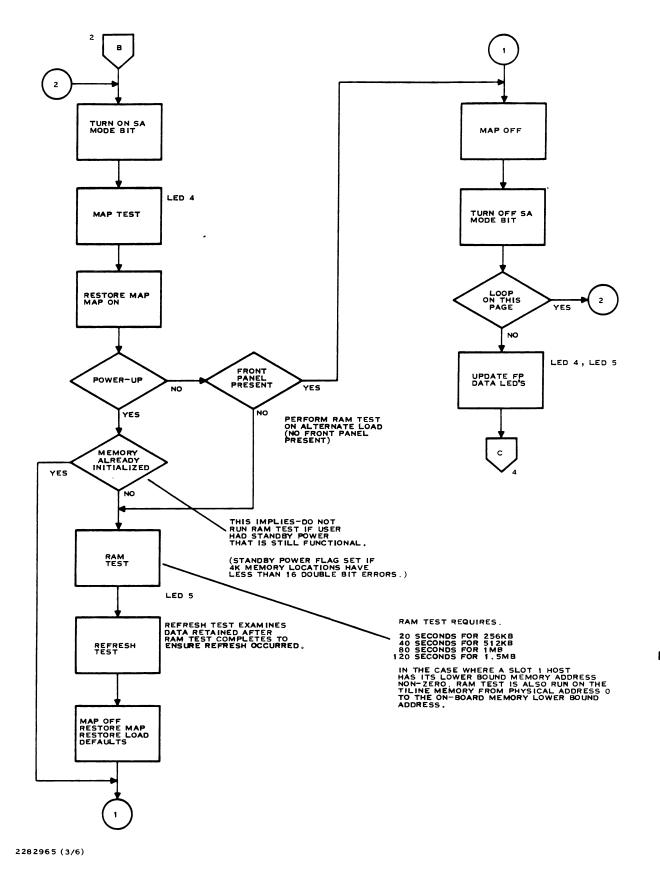

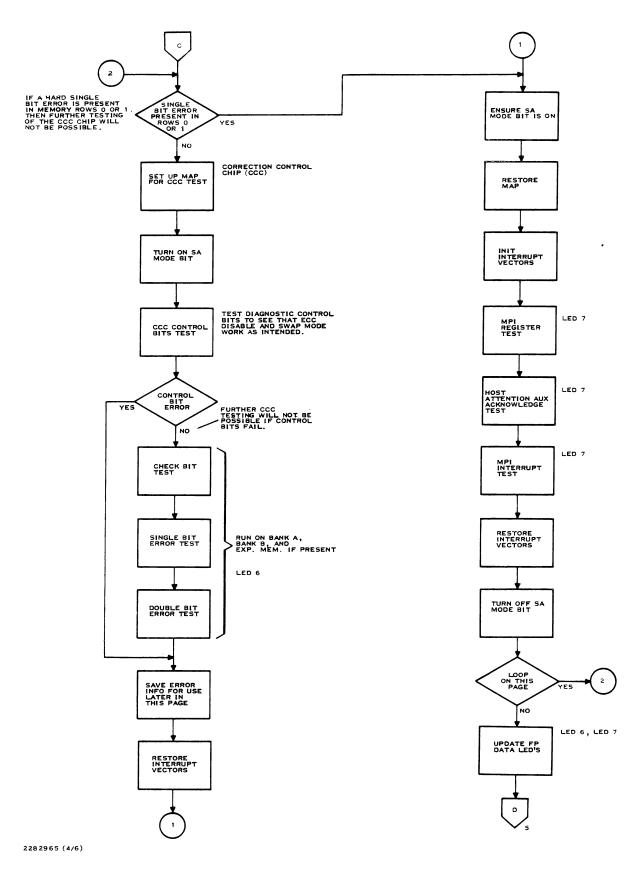

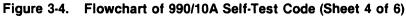

|   | 3-1<br>3-2<br>3-3<br>3-4<br>3-5  | Control/Display Module<br>Universal Loader Search Algorithm<br>990/10A Board Failure Indicators<br>Flowchart of 990/10A Self-test Code<br>Programmer Panel and CDM                                                         |                     |

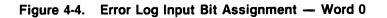

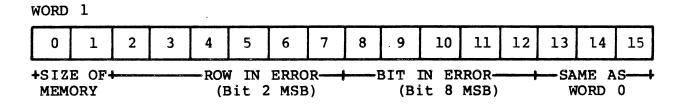

|   | 4-1<br>4-2<br>4-3<br>4-4<br>4-5  | 990/10A Status Register<br>Asynchronous Communication Port Interface<br>Diagnostic Control Output Bit Assignment — Word 0<br>Error Log Input Bit Assignment — Word 0<br>Error Log Input Bit Assignment — Word 1            | 4-3<br>4-14<br>4-15 |

## Tables

| Table | Title                                                  | Page |

|-------|--------------------------------------------------------|------|

| 1-1   | Physical, Electrical, and Environmental Specifications | 1-6  |

| 1-2   | 990/10A Typical Memory Allocation                      | 1-10 |

| 1-3   | Error Status Register CRU Bit Definitions              |      |

| 1-4   | CRU Address Map                                        |      |

| 1-5   | Backpanel Connector P1                                 |      |

| 1-6   | Backpanel Connector P2                                 |      |

| 1-7   | Front Panel Connector P4                               | 1-24 |

| 1-8   | Asynchronous Communication Port Connector P3           | 1-25 |

| 2-1   | Memory Control TPCS Addresses                          | 2-2  |

| 2-2   | 990/10A Controller Starting Address Switch Settings    | 2-5  |

| 2-3   | Option Jumpers                                         | 2-5  |

| 3-1   | Self-Test Error Reporting Bit Assignment               | 3-18 |

| 4-1   | CRU Output Bits to the ACC                             | 4-5  |

| 4-2   | CRU Input Bits from the ACC                            |      |

| 4-3   | Memory Control TPCS Addresses                          |      |

# **General Description**

#### 1.1 GENERAL

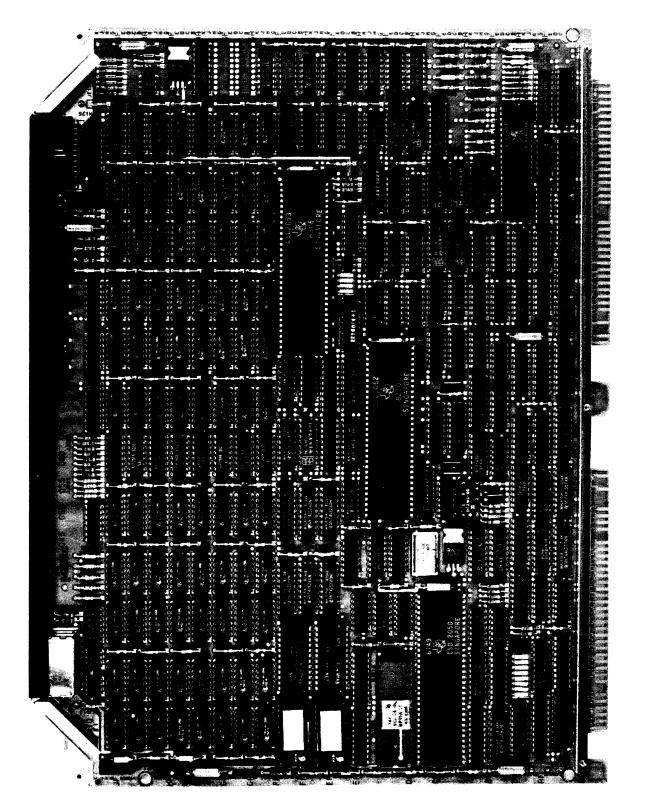

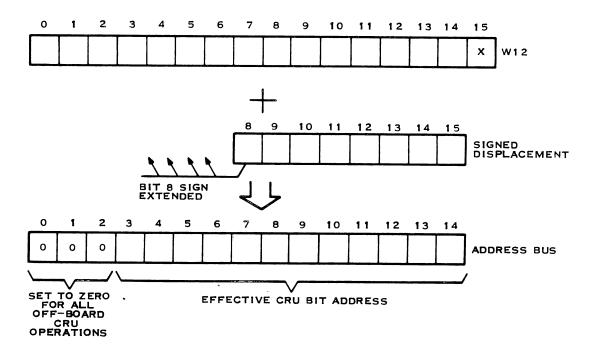

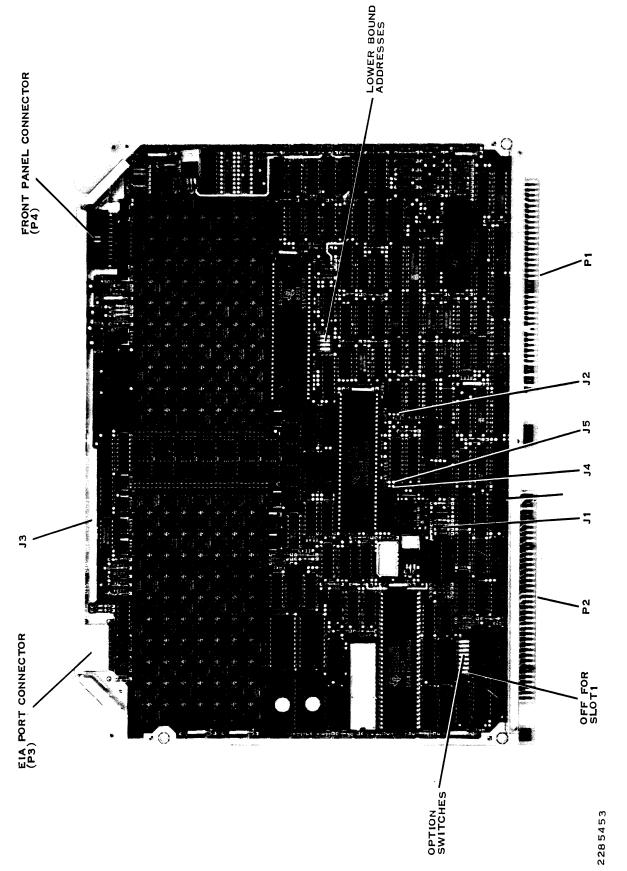

This manual provides unpacking, installation, testing, and operating information for the Texas Instruments Model 990/10A Processor (Figure 1-1 or Figure 1-1A). This section contains functional and physical descriptions to acquaint the user with the hardware components and capabilities of the Model 990/10A Processor, hereafter referred to as the 990/10A.

#### 1.2 PURPOSE OF EQUIPMENT

The 990/10A is a single board replacement for the 990/10 processor. The 990/10A combines a 990/10-compatible processor with a maximum of 1.5 megabytes of error correcting memory, an asynchronous communications port, TILINE<sup>™</sup> interface, communications register unit (CRU) interface, and control logic for operation in a multiprocessor system. When combined in a chassis with appropriate peripherals for input, output, and mass storage, the 990/10A forms part of a standalone minicomputer system.

#### **1.3 EQUIPMENT DESCRIPTION**

The 990/10A is a full-function processor on a single printed wiring board (PWB). Much of the discrete circuitry of the 990/10 is incorporated into custom large scale integration (LSI) devices in the 990/10A, resulting in lower cost and power consumption with increased reliability. The speed increases resulting from the single-board design of the 990/10A give an average 1.5 times increase in throughput over the 990/10, for most applications. The following paragraphs describe the major components of the 990/10A.

TILINE is a trademark of Texas Instruments Incorporated.

2283230

1

2285512

Figure 1-1A. Model 990/10A Surface Mount 1-Megabyte Processor Board

#### 1.3.1 Microprocessor

The TMS 99000 microprocessor used on the 990/10A is an upwardly compatible, high performance member of the TMS 9900 family. This microprocessor implements the 990/10 instruction set and an additional five instructions, providing the capability of a full minicomputer on a single chip.

The following characteristics are offered by the microprocessor.

- Sixteen-bit instruction word

- Memory-to-memory architecture

- 77 instructions including signed multiply and divide

- Multiple register files resident in memory

- 16 prioritized hardware interrupts

- 16 software interrupts

- Programmed input/output (I/O) and direct memory accessing (DMA) capability

- I/O operation addressable in bit, byte, or word increments via the CRU

- Multiprocessor system interlock signal

- Privileged instructions

- User and supervisor modes

#### 1.3.2 Memory

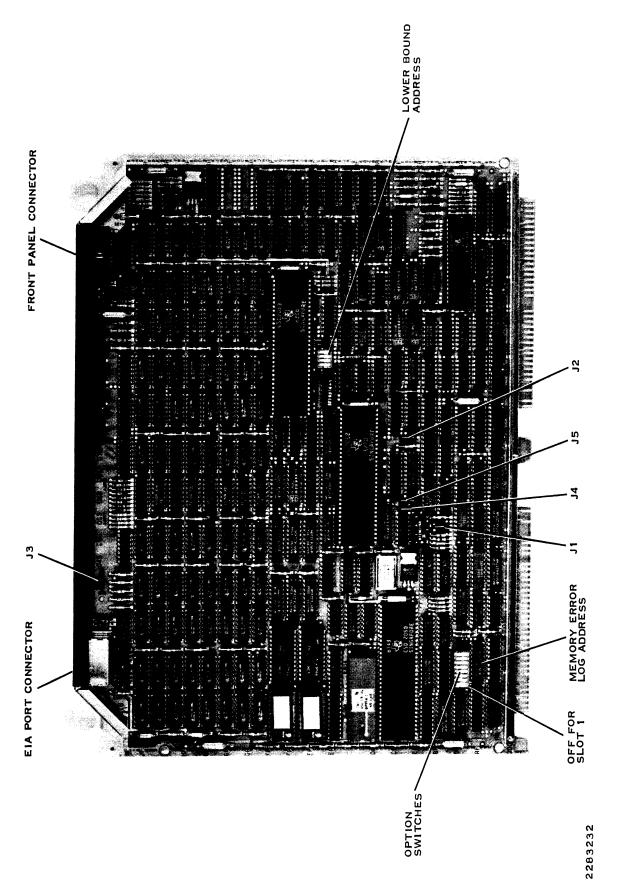

Four pencil switches select the lower bound of on-board memory in 128-kilobyte increments. This memory can be accessed by the microprocessor or by any device on the TILINE bus.

The 990/10A is provided with on-board memory in a variety of configurations:

- Two rows of 64 kilobit dynamic random-access memory (DRAM) integrated circuits (ICs) totalling 256 kilobytes

- Four rows of 64K DRAM ICs totalling 512 kilobytes

- Eight rows of 64K DRAM surface-mount ICs totalling 1024 kilobytes

- One row of 256K DRAM ICs totalling 512 kilobytes

- Two rows of 256K DRAM ICs totalling 1024 kilobytes

- Three rows of 256K DRAM ICs totalling 1536 kilobytes

**1.3.2.1 Memory Correction and Control.** The correction and control chip provides error detection and correction capability for the on-board memory. This chip generates a six-bit checkword with each memory write. On subsequent memory reads, the checkword is used to correct single bit errors and to flag double bit errors.

**1.3.2.2 Memory Mapping.** The memory mapping chip performs a mapping algorithm to convert 16-bit byte level addresses (logical addresses) into 20-bit word addresses (physical addresses) for the internal memory bus. In addition to generating the physical addresses, the memory mapping chip detects an attempt to access memory addresses larger than the value stored in the highest limit register. Logic external to the memory mapping chip generates an error interrupt, preventing out-of-range addressing. This external logic also detects accesses to peripheral controllers and maps these accesses to the TILINE peripheral control space (TPCS).

#### 1.3.3 Input/Output (I/O)

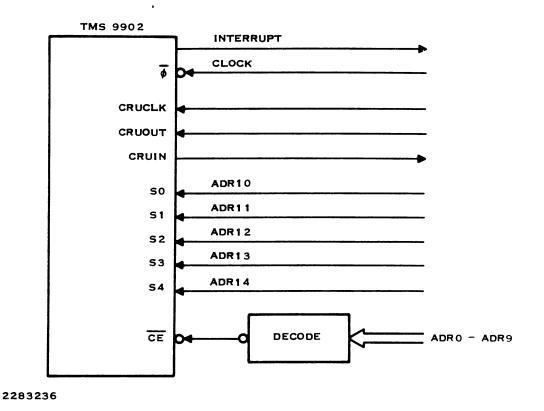

The following paragraphs describe the interface controllers on the 990/10A that provide input/output capability. These controllers are also used for many of the on-board data and control word transfer operations of the processor. Both TILINE and CRU controllers are provided, as well as one on-board asynchronous communication port.

**1.3.3.1 TILINE Control.** The TILINE is a high-speed, asynchronous interface bus that provides transfer rates approaching the rates of DMA interface controllers, but does not require the complex controllers for each device. The 990/10A supports all existing TILINE memory and peripheral devices. TILINE devices can access memory contained on the 990/10A board as well as off-board TILINE memory. The TILINE controller consists of a master controller and a slave controller along with synchronization and interface circuits common to both.

**1.3.3.2 CRU Interface.** The 990/10A provides the CRU interface that is standard on 990 family processors, in a custom integrated circuit. This versatile, command-driven interface can effectively handle a wide range of control and data transfer operations with its extremely flexible format. The CRU can set, reset, or test a field of one to sixteen bits in the CRU array. The CRU operates at a 2.5 megahertz data rate with devices in the main chassis, and at a 1.67 megahertz rate on CRU reads from devices in an expansion chassis. CRU writes to expansion chassis devices occur at 2.5 megahertz. The use of an expansion chassis in the system does not reduce the rate for main chassis communication. In addition to the CRU control function, the CRU controller performs the following functions:

- Bus status decode

- Single instruction execution control

- Run mode logic

- System error latch

- Front panel test logic

- Real-time clock state controller

- Ready generation to the microprocessor

**1.3.3.3** Asynchronous Communication Controller. The asynchronous communication controller provides an interface port for one video terminal, printer, or any other EIA compatible device. The asynchronous communication controller uses the TMS 9902 chip to provide the following:

- Interrupt control

- Timing control between the microprocessor and an I/O device

1

- Asynchronous operation

- Character length of five to eight bits

- Fully programmable data rate

- Interval timer

- Even, odd, or no parity

- 1, 1.5, or 2 stop bits

.

#### 1.4 SPECIFICATIONS

Table 1-1 lists the physical, electrical, and environmental specifications for the 990/10A board.

•

| Characteristic                  |                                        | Specification                                                                                               |

|---------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------|

| Electrical                      |                                        |                                                                                                             |

| Total power required            |                                        | Not more than 30 watts                                                                                      |

| Voltage                         | Current                                | Power Requirements                                                                                          |

| + 5 V main                      | 4.8 A                                  | 24.0 W                                                                                                      |

| + 5 V main (1 megabyte)         | 4.6 A                                  | 23.0 W                                                                                                      |

| + 5 V memory                    |                                        |                                                                                                             |

| with 512K bytes                 | 1.10 A (operating)<br>0.17 A (standby) | 5.5 W<br>0.9 W                                                                                              |

| with 1 megabyte                 | 1.20 A (operating)<br>0.33 A (standby) | 6.0 W<br>1.7 W                                                                                              |

| with 1.5 megabytes              | 1.30 A (operating)<br>0.50 A (standby) | 6.5 W<br>2.5 W                                                                                              |

| + 12 V memory                   | 0.00 A                                 | 0.0 W                                                                                                       |

| + 12 V main                     | 26 mA (EIA drivers)                    | 0.3 W                                                                                                       |

| – 12 V main                     | – 26 mA (EIA drivers                   | s) 0.3 W                                                                                                    |

| – 12 V memory                   | 0.00 A                                 | 0.0 W                                                                                                       |

| – 5 V memory                    | 0.00 A                                 | 0.0 W                                                                                                       |

| Environmental                   |                                        |                                                                                                             |

| Ambient temperature (operating) |                                        | 0 to 65 °C (32 to 149 °F) (Derate 2 °C<br>(3.6 °F) for every 761 m (approximately<br>2500 ft) of elevation) |

| Ambient temperature (storage)   |                                        | – 40 to 70 ° C ( – 40 to 158 ° F)                                                                           |

| Ambient humidity (operating)    |                                        | 5 to 95% (noncondensing)                                                                                    |

| Ambient humidity (storage)      |                                        | 5 to 95% (noncondensing)                                                                                    |

| Shock                           |                                        | 2-inch vertical drop (installed in chassis)                                                                 |

| Vibration                       |                                        | 1 G (5 to 80 Hz) (installed in chassis)<br>0.3 G (80 to 500 Hz) (installed in chassis)                      |

| Physical                        |                                        |                                                                                                             |

| Length $	imes$ Width            |                                        | 362 mm $	imes$ 274 mm (14.25 in. $	imes$ 10.80 in.)                                                         |

| able 1°1. Electrical, Environmental, and i hysical opecnications | able 1.1. | Electrical, Environmental, and P | Physical Specifications |

|------------------------------------------------------------------|-----------|----------------------------------|-------------------------|

|------------------------------------------------------------------|-----------|----------------------------------|-------------------------|

#### 1.5 FUNCTIONAL DESCRIPTION OF EQUIPMENT

The following paragraphs describe the function of the major components of the 990/10A computer.

#### 1.5.1 Microprocessor

The microprocessor is the principal component of the 990/10A computer. The microprocessor implements the 990/10 instruction set and five additional instructions. These additional instructions are compatible with the 990/12 instruction set. It recognizes interrupts, initiates a context switch in response to interrupts, and stores the present context for a return. The microprocessor provides the interrupt mask function, and implements the nonmaskable interrupt (NMI) function for front panel interrupts. The microprocessor controls all CRU operations, both serial and parallel. The microprocessor also features a multiprocessor interlock signal to facilitate multiprocessor operation, and provides privileged instruction capability.

The microprocessor communicates with the rest of the on-board computer functions by means of a synchronous bus. This bus has no external connection off the 990/10A board, but is synchronized with the TILINE bus by means of the TILINE control circuits. Use of the synchronous bus enhances on-board data transfer operations, but sacrifices performance for TILINE communication. For this reason, on-board memory should be used for maximum performance operation.

#### 1.5.2 Memory Mapping

The map logic is contained in a custom LSI circuit. This chip performs the standard 990 family mapping algorithm to convert 16-bit byte level memory addresses from the microprocessor (logical addresses) into 20-bit word addresses (physical addresses) for the memory and memory-mapped I/O devices. It is the physical address that is put on the internal memory bus and on the TILINE bus if the TILINE master logic decodes the address as not being resident on the board.

The logical address generated by the microprocessor is expanded into the physical address space by relocating the logical address into blocks of memory in the two-megabyte address space. The displacement added to the logical address is defined by values stored in the mapping registers.

In addition to generating the physical address, the map chip has error logic that detects an attempt to access memory above the largest limit register. Logic external to the chip generates an interrupt and prevents further accesses when an error is detected. The map chip also detects access to the TPCS and maps these accesses to the high order addresses.

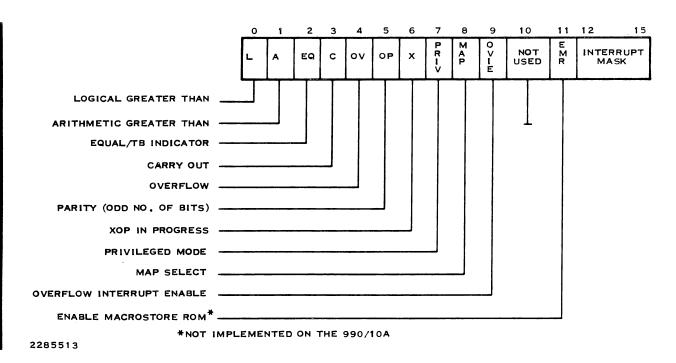

**1.5.2.1 Map Operation.** The map logic consists of three sets of map files. Status register bit 8 selects either map file 0 or map file 1. Map file 2 is selected by the use of a long distance source (LDS) or long distance destination (LDD) instruction. Each map file contains six registers: three 16-bit base registers and three 11-bit limit registers. Mapping is performed by selecting one of the base registers and adding the contents of that register to the high order 11 bits of the logical address. (Note that the low order four bits of the word level logical address are not affected by the map logic.) Within a given map file, the base register to be used is selected by comparing the logical address to the limit registers for that map file. A logical address that is less than or equal to the value of limit register 1 is mapped with base register 1; an address that is greater than the value of limit register 2 is mapped via base register 2; and a logical address that is greater than the value of limit register 3 is mapped via base register 3. If the logical address is greater than all three limit registers, an error condition is flagged. The limit registers accept and hold the ones complement of the desired compare data.

• ••

**1.5.2.2 Map Initialization.** On power-up, bit 8 of the status register is set to zero. Mapping is disabled so that the first 31K words of memory are addressed. This memory may or may not be onboard the 990/10A depending upon the setting of the lower-bound address switches.

#### NOTE

A 990/10A operating in the auxiliary mode will only service certain interrupts as specified in paragraph A.2.2. If these interrupts are to be handled out of local memory, the map chip must be set up to map all interrupts into the on-board address space as determined by the memory bound switches. See Appendix A for additional information on auxiliary mode operation.

#### NOTE

The "greater than" symbol (>) is used to represent hexadecimal numbers.

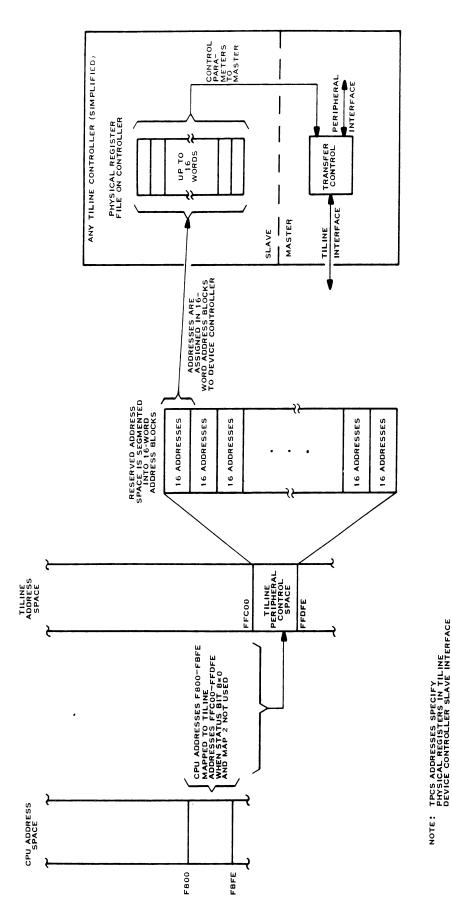

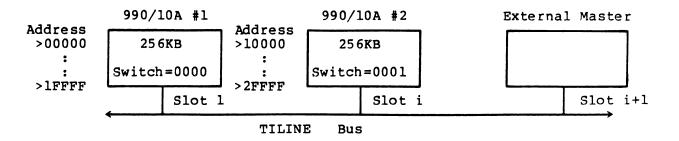

**1.5.2.3 TILINE Peripheral Control Space (TPCS) Mapping.** The TPCS consists of those logical addresses in the range of > F800 through > FBFE, and is reserved for assignment to peripheral device controllers. These addresses are modified before presentation to the TILINE. Five address bits are appended to the left (MSB) side of each address to form a 20-bit TILINE word address. In other words, addresses > F800 through > FBFE are mapped to addresses > FFC00 through > FFDFE. This particular mapping occurs only when map file zero is invoked (Status register bit 8 equals 0) or if mapping is disabled. Figure 1-2 illustrates the TPCS concept.

#### NOTE

Note from Table 1-2 that DRAM addressed in the 128-kilobyte increment from > F0000 to > FFFFF overlaps the TPCS. The 990/10A includes logic to prevent accessing both memory and control registers when its lower-bound memory address switches and amount of memory jumpers permit addressing memory in this range. However, TILINE expansion memory should be limited so that memory does not respond to TPCS addresses. (In other words, lower-bound address switches on TILINE memory controllers should not be set so that > FFC00 through > FFFFF are valid addresses.)

Figure 1-2. TILINE Peripheral Control Space Implementation

2285511

**1.5.2.4** Scratch Pad RAM. During self-test, the 990/10A requires scratch pad memory area for use as workspace registers, temporary storage, etc. Therefore, a 128 x 16 random-access memory (RAM) is implemented which can be accessed during self-test only. To use the scratch pad RAM, a latch must be set by writing a one to bit two of the diagnostic register (CRU address > FAFE). After that, any subsequent access to logical memory address > FA00 through > FAFF is directed to the scratch pad RAM. The scratch pad RAM is disabled by writing a zero to bit two. The scratch pad RAM is not accessible from the TILINE.

**1.5.2.5** Loader/Self-Test ROM Mapping. The loader/self-test read-only memory (ROM) contains a total of eight kilobytes of loader/self-test code. The 990/10A has the capability to directly access one kilobyte of ROM code only. Therefore, the 990/10A uses an addressing scheme that is compatible with the 990/12 to allow the access of an additional seven kilobytes of loader/self-test code. This is accomplished by dividing the loader/self-test ROM into eight pages, with each page containing one kilobyte. From Table 1-2, note that one kilobyte is the total allowed by the address allocation. The page that is being addressed is then determined by three latched bits written into a register at memory address >FAFE, not by the address field. This address normally is within the TPCS and initiates a TILINE cycle. Therefore, the ROM page address field is qualified to be accessible only when the scratch pad RAM is enabled. The ROM page address field then appears as the last word of the scratch pad RAM memory space (>FA00 - >FAFE). On power-up, loader self-test page zero is selected. The page selected is changed by setting the scratch pad RAM enable bit at CRU address >FAFE bit 2 and then writing to bits 13, 14, and 15 of memory address >FAFE. The transition from page to page is based on the principle that the microprocessor prefetches the next instruction before accomplishing the destination write from the present instruction. An example instruction sequence follows:

| LI  | R5,@NPEP  | LOAD NEW PAGE ENTRY POINT            |

|-----|-----------|--------------------------------------|

| INC | R4        | INCREMENT PAGE COUNTER               |

| MOV | R4,> FAFE | PERFORM THE PAGE SWAP AFTER PREFETCH |

| В   | *R5       | BRANCH TO ENTRY POINT                |

#### 1.5.3 Memory Correction and Control

The correction and control chip is a custom LSI integrated circuit that performs the error detection and correction algorithm employed on other 990 memory products. This chip generates a six-bit checkword with each memory write. On subsequent memory reads, the checkword is used to correct single-bit errors and to flag double-bit errors. The error condition of all logic ones or all logic zeros from memory is detected, but other errors of three or more bits may not be detected. An on-chip register that responds to a TPCS address permits control of the error-correcting function for diagnostic purposes. The error correction can be disabled to certain rows of memory chips, or the checkword can be interchanged with the six most significant bits (MSBs) of the data word to verify the cause of a failing condition. Status information about the test results, memory size, memory address, and chip-in-error can be read through two 16-bit registers (the memory error log) in the TPCS whose address is selected by pencil switches on the 990/10A board.

The correction and control chip also includes two addressable registers for controlling interrupts among processors in a multiprocessor system whose addresses are also switch selectable.

#### 1.5.4 Memory Allocation

Table 1-2 illustrates the allocation of the 990/10A memory.

| Description       | Logical Address<br>(Hexadecimal) | Physical Address<br>(Hexadecimal) | Memory Content            |

|-------------------|----------------------------------|-----------------------------------|---------------------------|

|                   | 0000                             | 00000                             | WP level 0 interrupt      |

|                   | 0002                             | ,00001                            | PC level 0 interrupt      |

| Interrupt         | 0004                             | 00002                             | WP level 1 interrupt      |

| vectors           | •                                | :                                 | :                         |

|                   | :                                | :                                 | :                         |

|                   | 003C                             | 0001E                             | WP level 15 interrupt     |

|                   | 003E                             | 0001F                             | PC level 15 interrupt     |

|                   | 0040                             | 00020                             | WP XOP 0                  |

| XOP software      | 0042                             | 00021                             | PC XOP 0                  |

| trap vectors      | •                                | :                                 | :                         |

|                   | :                                | :                                 | :                         |

|                   | 007C                             | 0003E                             | WP XOP 15                 |

|                   | 007E                             | 0003F                             | PC XOP 15                 |

|                   | 0080                             | 00040                             |                           |

|                   | :                                | :                                 | 62K* bytes of general pur |

|                   | :                                | :                                 | pose on-board memory      |

|                   | F7FE                             | 07BFF                             |                           |

|                   | F800                             | 07C00                             | 2K* bytes of on-board RAM |

| General           | :                                | :                                 | not available to processo |

| purpose           | :                                | :                                 | through map file 0        |

| memory            | FFFE                             | 07FFF                             |                           |

|                   |                                  | 08000                             |                           |

|                   |                                  | :                                 | Expansion memory          |

|                   |                                  | FFBFF                             |                           |

|                   | F800                             | FFC00                             | TILINE peripheral contro  |

| TILINE peripheral | :                                | :                                 | registers or scratch pac  |

| control space     | :                                | :                                 | memory (see text)         |

|                   | FBFE                             | FFDFF                             |                           |

|                   | FC00                             | N/A                               |                           |

| Loader and self-  | :                                | :                                 | Loader/self-test ROM      |

| test programs     | •                                | :                                 | (accessible by the proces |

|                   | FFFA                             | N/A                               | sor only)                 |

| Load vector       | FFFC                             | N/A                               | WP load function          |

|                   | FFFE                             | N/A                               | PC load function          |

#### Table 1-2. 990/10A Typical Memory Allocation

Note:

\* K equals 1,024 bytes.

.

#### 1.5.5 Interrupts

The 990/10A uses 16 priority-vectored interrupt levels. The priority ranking system assigns numbers to the levels from 0 (highest priority) to 15 (lowest priority) in order to resolve interrupt conflicts. The interrupts are also maskable via bits 12–15 of the status register. Upon detection of a pending interrupt, the processor compares the interrupt code with the interrupt mask. If the level of the interrupt is less than or equal to the mask level (higher or equal priority), the processor recognizes the interrupt and initiates a context switch after completion of the currently executing instruction. The processor fetches the new context workspace pointer and program counter from the appropriate interrupt vector location and stores the previous workspace pointer, program counter, and status register contents in workspace registers 13 through 15 of the new workspace. The processor then loads the interrupt mask with a value that is one less than the value of the interrupt being processed (except for a level 0 interrupt which loads 0 into the mask). This allows only interrupts of a higher priority to interrupt the service routine. The processor also inhibits additional interrupts until the first instruction. Interrupts are sampled beginning at the first state of the prefetch cycle until one state prior to the end of the destination write cycle.

In addition to the interrupts already discussed, there are two interrupts that are not affected by the interrupt mask. One is referred to as the NMI. This is a level -1 interrupt that vectors through locations > FFFC and > FFFE. This is normally used for front panel control. The other is an illegal operation code interrupt that is normally a level 2 interrupt; but, on the 990/10A, it cannot be masked out via the status register. This allows software emulation of instructions not defined on the 990/10A microprocessor.

**1.5.5.1** Level 0 Interrupt (Power Restored). The highest priority level is reserved for the power restored interrupt. When power is restored, TILINE power reset (TLPRES-) from the power supply remains true long enough for the power supply to stabilize, and then goes false. TLPRES- true (RESET) forces the microprocessor to cease instruction execution. When TLPRES- goes false after being true, the microprocessor initiates a level 0 interrupt trap (power restored). This level 0 interrupt trap never completes on the 990/10A.

When the microprocessor recognizes RESET (TLPRES- true), it sends the RESET bus status code until the level 0 trap is initiated. The single instruction execute controller in the CRU chip recognizes this RESET bus status code and forces an NMI. The result is that the level 0 interrupt context switch completes (first instruction fetched), but this first instruction is not executed because an NMI is present and the NMI interrupt trap is initiated.

The NMI handler in ROM (see paragraph 1.5.5.8) then runs self-test because the NMI occurred due to power restored (or power-up). Following a successful completion of self-test, under the right circumstances, a level 0 interrupt context switch then occurs. See the power-up NMI paragraph in this section for a detailed explanation of what happens on power-up.

**1.5.5.2** Level 1 Interrupt (Power Failure Imminent). When the chassis power supply senses a loss of power, a level 1 interrupt is generated. The hardware has several milliseconds of processing time from the time the interrupt signal is asserted until a master clear (TLPRES-) is issued.

**1.5.5.3** Level 2 Interrupt (Error Conditions). A level 2 interrupt can be caused by error conditions external to the microprocessor as well as by internal microprocessor chip errors. The external error conditions are memory data error, memory map error, and TILINE time-out. The internal microprocessor chip level 2 interrupts include arithmetic overflow interrupt and the privileged op-code interrupt as well as the macroinstruction decode trap.

The macroinstruction decode signal is used to indicate an illegal opcode in the 990/10A. Upon detection of an undefined opcode, the microprocessor chip traps (subroutine call) using the workspace pointer (WP) and program counter (PC) stored in locations > 0008 and > 000A. These locations contain the level 2 interrupt vectors.

The 990/10A implementation differs from the 990/10 with regard to level 2 interrupts. The macroinstruction decode trap is not maskable with the interrupt mask logic and therefore overrides any other interrupt. Also, the trap does not change the interrupt mask.

A flag indicating which condition caused the level 2 interrupt is stored in the error status register.

*Error Status Register.* The error status register stores error conditions and provides a composite output to the level 2 interrupt of the microprocessor. The error status register is read through the CRU at CRU base address > 1FC0. Table 1-3 gives the bit definitions for the error status register.

|                                                                                                                                                                                                                                                  | CRU BASE 1FC0(HEX)                                  |                                 |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|---------------------------------|--|

| ERROR CONDITION                                                                                                                                                                                                                                  | INPUT BIT                                           | OUTPUT BIT                      |  |

| TILINE TIMEOUT<br>PRIVILEGE VIOLATION<br>ILLEGAL OPERATION CODE<br>MEMORY ERROR<br>MAPPING ERROR<br>ARITHMETIC OVERFLOW<br>RESERVED<br>ID (990/10A = 1)<br>ID (990/10-990/12 INDICATOR)<br>BIT1 BIT0<br>0 0 990/10A<br>1 0 990/10A<br>0 1 990/12 | 15<br>14<br>13<br>12<br>11<br>4<br>3<br>2<br>1<br>0 | 15<br>14<br>13<br>12<br>11<br>4 |  |

#### Table 1-3. Error Status Register CRU Bit Definitions

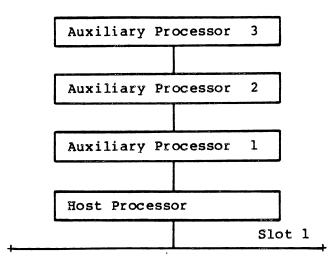

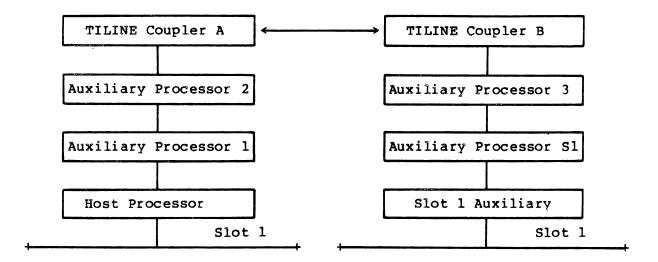

**1.5.5.4** Level 3 Host Processor Interrupt. Logic is included in the 990/10A design to allow multiple processor boards to operate together in a single chassis with the processor in slot 1 acting as a host processor. This requires attention and acknowledge interrupts between the host processor and the auxiliary processors. The host processor can interrupt the auxiliary through a TPCS register. The auxiliary can acknowledge that interrupt by generating an interrupt back to the host. In a similar fashion, the auxiliary can generate an attention interrupt to the host and the host can acknowledge by setting a bit that interrupts the auxiliary. Either of these interrupts can be masked on the remote processor through the TPCS registers.

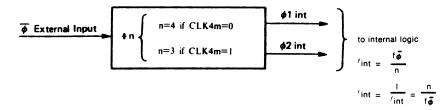

**1.5.5.5** Level 5 or 15 Interrupt (Real-Time Clock). A line frequency synchronized oscillator on the power supply is an input to the 990/10A processor. On every cycle of the oscillator (either 8.33 or 10.0 milliseconds depending on the line frequency) the real-time clock interrupt signal is generated. This signal can be connected by a jumper on the processor board to interrupt level 5 or level 15, or it can be disconnected. The clock on (CKON) and clock off (CKOF) instructions enable or disable the real-time clock interrupt independently of the interrupt mask.

**1.5.5.6** Level 8 (EIA Port Interrupt). The interrupt from the EIA port on the processor board is jumpered to level 8. This interrupt is enabled or disabled by setting a specified CRU output bit and is disconnected by removing a jumper on the processor board (see Section 2 for jumper descriptions).

**1.5.5.7 External Interrupts.** Interrupt requests from other boards can be wired by backpanel jumpers to any of the 13 interrupt request lines (levels 3 through 15). These lines form 13 separate wired-OR interrupt buses. Each interrupt request signal must be an active low signal driven by an open collector TTL gate. The request signal must remain active until it is reset by software communication.

When operated in a slot other than slot 1, only the internally generated interrupts can, in general, be received by the processor. There is one exception that might be exploited for some applications. That exception occurs because the backpanel connector P2 pin 66 is normally an output for TILINE or CRU devices to send interrupts to the interrupt jumper plug. This pin, on a 990/10A is actually an input to interrupt level 14. Therefore it is possible, by modifying the backpanel jumper plug, to direct one external interrupt into the 990/10A at level 14 while operating as an auxiliary processor.

When in slot 1, all interrupts are received by the processor. Those interrupts that are allotted to internal processor board functions share a particular wired-OR interrupt level with the external interrupts unless disconnected by removing the jumper.

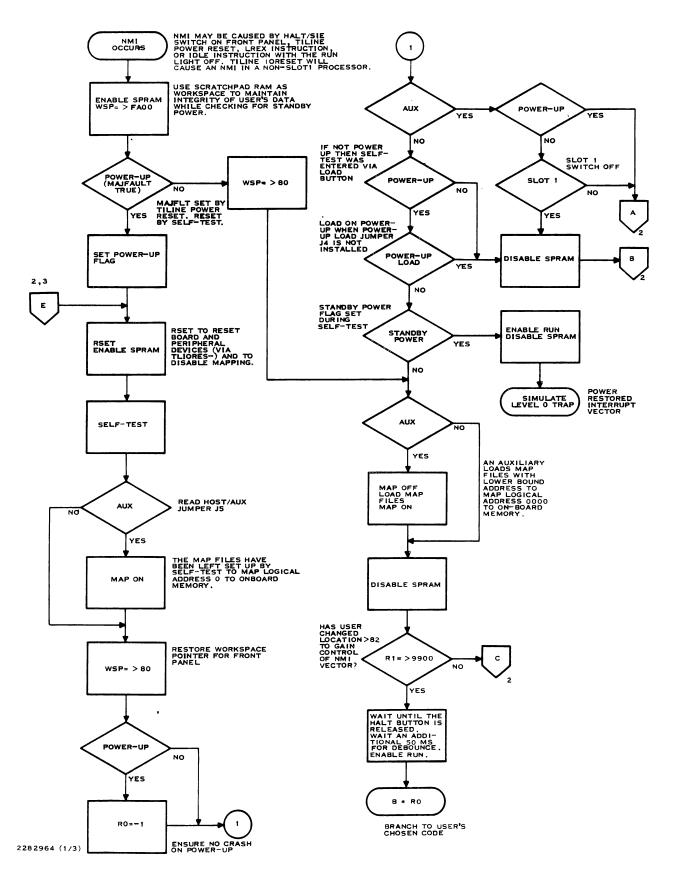

**1.5.5.8** Nonmaskable Interrupt (NMI). The function referred to as the nonmaskable interrupt is equivalent to the load function in other 990 family microprocessors. NMI cannot be disabled by the interrupt mask logic and is therefore always executed as soon as the current instruction is completed. NMI causes execution to begin with the WP at location > FFFC and the PC at location > FFFE. NMI is activated by the restart signal. This signal can result from the execution of an LREX instruction, from the HALT switch on the front panel, or from power-up.

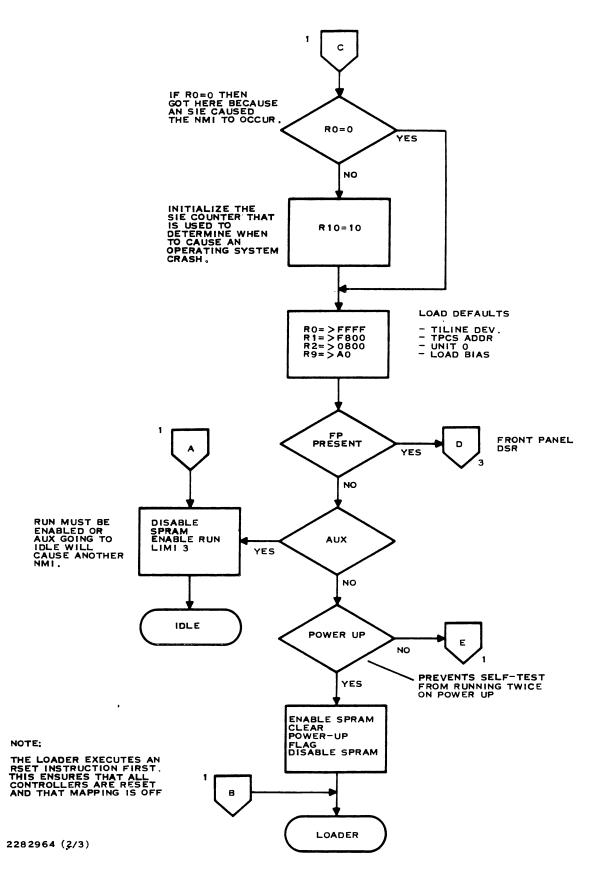

When an NMI occurs, the NMI handler in the loader/self-test ROM determines the sequence that follows the NMI. This sequence depends on whether the central processing unit (CPU) is a host or auxiliary, a front panel is present, and the NMI occurred as a result of power-up. A flowchart of the NMI handler is shown in Figure 1-3.

Figure 1-3. Flowchart of Nonmaskable Interrupt and Front Panel Code (Sheet 1 of 3)

2282964 (3/3,

#### Figure 1-3. Flowchart of Nonmaskable Interrupt and Front Panel Code (Sheet 3 of 3)

**Power-up NMI.** Upon power-up, self-test is always run first. After successful completion of self-test, the power-up load jumper is examined. If the jumper is not installed, the loader is executed. If the jumper is installed, the host/auxiliary jumper is examined. If the CPU is a host and has battery backup, a level 0 interrupt trap (power restored) is taken. If the CPU is a host but has no battery backup, a load is performed unless a front panel is present. If a front panel is present, front panel code is executed.

If the CPU is an auxiliary, map 0 is set up to map logical address 0 to the on-board memory lowerbound address and mapping is enabled. The CPU then idles after executing a LIMI 3 to enable the multiprocessor interrupt.

**Nonpower-up NMI.** An NMI occurring from some condition other than power-up always results in front panel code execution if a front panel is present. If no front panel is present, then a load is performed if the CPU is a host, or a LIMI 3, IDLE if the CPU is an auxiliary. The front panel code operates the same for both hosts and auxiliaries.

#### 1.5.6 Communication Register Unit (CRU) Controller

The 990/10A is compatible with all standard CRU interfaces, but allows 32,768 output bits and 32,768 input bits, instead of the 4096 allowed by previous processors. In addition, multiple bit transfers are made in parallel mode on the 990/10A board. This provides high-speed transfers to the address mapping chip and diagnostic hardware. Parallel transfers off the processor board are not supported. Only the 12 low order CRU bits are available off the 990/10A board, and CRU addresses for off-board functions are compatible with all existing 990 family hardware and software.

#### NOTE

The 990/10A uses the three MSBs of the CRU address field for internal addressing and any attempt to issue a CRU access to an address with any of the three MSBs of register 12 set to a logic one may cause erroneous results.

Both input and output bits can be addressed individually or in fields of from 1 to 16 bits. The processor employs three dedicated I/O pins (CRUBITIN, CRUBITOUT, and STORECLK-) and 12 bits (CRUBIT4 through CRUBIT15) of the address bus at the interface to the CRU system. The processor instructions that drive the CRU interface can set, reset, or test any bit in the CRU array or move data between memory and CRU data fields.

The processor performs three single-bit CRU functions: test bit (TB), set bit to one (SBO), and set bit to zero (SBZ). To identify the bit to be operated on, the processor develops a CRU-bit address and places it on the address bus, CRUBIT4 through CRUBIT15.

For the two output operations, SBO and SBZ, the processor generates a STORECLK- pulse that indicates to the CRU device that the operation is an output operation, and places bit 7 of the instruction word on the CRUBITOUT line to accomplish the specified operation (bit 7 is a one for SBO and a zero for SBZ). The TB instruction is an input operation that transfers the addressed CRU bit from the CRUBITIN input line to bit 2 (equal bit) of the status register.

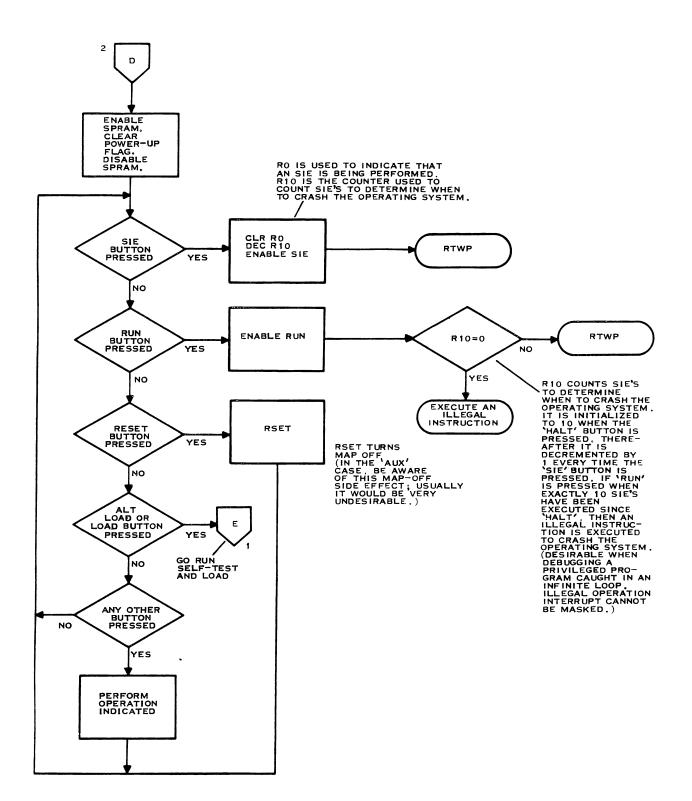

The processor develops a CRU-bit address for the single-bit operations from the CRU base address contained in workspace register 12 (R12) and the signed displacement contained in bits 8 through 15 of the instruction. The displacement allows two's complement addressing from base minus 128 bits through base plus 127 bits. The base address from R12 is added to the signed displacement specified in the instruction, and the result is loaded onto the address bus. Figure 1-4 illustrates the development of a single-bit CRU address.

When the processor is in slot 1, CRU write operations are executed in two clock cycles whereas CRU read cycles are executed in either two or three cycles. If the address to be read is in the expansion chassis or the expanded CRU address space (above > 1FFE), the read operation takes three cycles. If the address lies in the main chassis, it takes two cycles. If the 990/10A is not in slot 1, all CRU cycles are three cycles. The lower rate for expansion chassis operations allows for signal propagation in the interconnecting cable.

2283231

Figure 1-4. Single-Bit CRU Address Development

**1.5.6.1 Parallel CRU Operations.** The 990/10A has the ability to perform multiple bit CRU operations in a parallel mode. When the MSB of the 15-bit CRU address used with a LDCR or STCR instruction is set to one, the CRU transfer takes place in two or three clock cycles with the data transferred in parallel via the on-board data bus. This mechanism is used in the 990/10A to provide high-speed transfers to the map chip and other diagnostic hardware. No provision is made to support parallel CRU transfers off the processor board.

**1.5.6.2 CRU Addressing.** Table 1-4 shows a map of the CRU addresses assigned for the 990/10A. In this table, the addresses are referenced by the R12 value required to address them.

| Bit Serial Address Space<br>(MSB = 0) |                                         |  |  |

|---------------------------------------|-----------------------------------------|--|--|

| CRU Base                              | Contents                                |  |  |

| 0000-02FE                             | Main chassis addresses                  |  |  |

| 0400-06FE                             | Expansion chassis #1                    |  |  |

| 0800-0ÅFE                             | Expansion chassis #2                    |  |  |

| 0C00-0EFE                             | Expansion chassis #3                    |  |  |

| 1000-12FE                             | Expansion chassis #4                    |  |  |

| 1400-16FE                             | Expansion chassis #5                    |  |  |

| 1700-173E                             | Asynchronous EIA port                   |  |  |

| 1740                                  | Output: data terminal ready             |  |  |

| 1742                                  | Input: ring indicator                   |  |  |

|                                       | Output: analog loopback                 |  |  |

| 174C                                  | Interrupt enable EIA port               |  |  |

| 174E                                  | EIA port comm enable                    |  |  |

| 1800-1AFE                             | Expansion chassis #6                    |  |  |

| ——— Write operations to               | addresses above 1C00 are privileged ——— |  |  |

| 1C00-1EFE                             | Expansion chassis #7                    |  |  |

| 1EC4-1ECE*                            | External instructions                   |  |  |

| 1FA6                                  | Map enable                              |  |  |

| 1FBF                                  | CRU chip loopback mode                  |  |  |

| 1FC0-1FDE                             | Error status register                   |  |  |

| <ul> <li>1FE0–1FFE</li> </ul>         | Front panel                             |  |  |

| 7800-781E                             | Diagnostic loopback                     |  |  |

| Bit P                                 | arallel Address Space                   |  |  |

|                                       | (MSB = 1)                               |  |  |

| 9F80-9FFF                             | Map chip registers                      |  |  |

| FAFE                                  | Input: self-test register               |  |  |

|                                       | Output: diagnostic control              |  |  |

| Note:                                 |                                         |  |  |

#### Table 1-4. CRU Address Map

#### 1.5.7 Backpanel Interface

All connections to the computer chassis and peripheral devices (other than the front panel and EIA port) are through the backpanel connector. Table 1-5 and Table 1-6 list the pins and definitions for the backpanel connector.

| Pin<br>Number   | Slot 1<br>Signal | In/Out | Not Slot<br>1 Signal | in/Out | Comments                     |

|-----------------|------------------|--------|----------------------|--------|------------------------------|

| 1, 2            | GND              | _      | ,<br>GND             | _      |                              |

| 3, 4            | + 5 MAIN         | 1      | + 5 MAIN             | I      |                              |

| 5, 6            | NO CONNECT       | _      | NO CONNECT           | _      | (+12V MEMORY)                |

| 7, 8            | + 5 MEMORY       | I      | + 5 MEMORY           | I      | MAIN AFTER SLOT              |

| 9, 10           | NO CONNECT       | 4,3780 | NO CONNECT           | _      | (-5V MEMORY)                 |

| 11              | TLREAD           | I/O    | TLREAD               | 1/O    |                              |

| 12              | GND              |        | GND                  |        |                              |

| 13              | TLPRES-          | I      | TLPRES-              | 1      |                              |

| 14              | TLIORES-         | 0      | TLIORES-             | I      | 470 OHM PULL-UP<br>IN SLOT 1 |

| 15              | GND              |        | GND                  |        |                              |

| 16              | TLPFWP-          | 1 '    | TLPFWP-              | I      |                              |

| 17              | GND              | _      | GND                  |        |                              |

| 18              | CRUBITOUT        | 0      | OPEN(CRUBITOUT)*     | _      |                              |

| 19              | GND              |        | GND                  | -      |                              |

| 20              | TLTM-            | I/O    | TLTM-                | I/O    |                              |

| 21              | GND              |        | GND                  | _      |                              |

| 22              | STORECLK-        | 0      | OPEN(STORECLK-)*     | _      |                              |

| 23              | MODSEL0-         | 0      | OPEN*                | _      |                              |

| 24              | GND              | —      | GND                  | _      |                              |

| 25              | TLGO-            | I/O    | TLGO-                | I/O    |                              |

| 26              | GND              |        | GND                  | —      |                              |

| 27              | TLDAT12-         | 1/O    | TLDAT12-             | I/O    |                              |

| 28              | TLDAT13-         | I/O    | TLDAT13-             | I/O    |                              |

| 29 、            | 120HZ            | 1      | 120HZ                | I      |                              |

| 30              | TLDAT14-         | I/O    | TLDAT14-             | I/O    |                              |

| 31              | TLDAT15-         | I/O    | TLDAT15-             | I/O    |                              |

| 32              | CRUBIT13         | 0      | OPEN(CRUBIT13)*      | _      |                              |

| 33              | NO CONNECT       | -      | NO CONNECT           | —      | IAQ- ON /10                  |

| 34              | CRUBIT15         | 0      | OPEN(CRUBIT15)*      |        |                              |

| 35              | MODSEL1-         | 0      | OPEN*                | _      |                              |

| 36              | CRUBIT12         | 0      | OPEN(CRUBIT12)*      |        |                              |

| 37              | MODSEL2-         | 0      | OPEN*                |        |                              |

| 38              | CRUBIT14         | 0      | OPEN(CRUBIT14)*      |        |                              |

| 39, 40          | NO CONNECT       |        | NO CONNECT           | _      | (+12V MAIN)                  |

| 41, 42          | NO CONNECT       | -      | NO CONNECT           | —      | (-12V MAIN)                  |

| 43              | MODSEL3-         | 0      | OPEN*                | -      |                              |

| 44 <sup>,</sup> | MODSEL4-         | 0      | OPEN*                | -      |                              |

| 45              | MODSEL5-         | 0      | OPEN*                |        |                              |

| 46              | MODSEL6-         | 0      | OPEN*                |        |                              |

Table 1-5. Backpanel Connector P1

| Pin<br>Number     | Slot 1<br>Signal | in/Out   | Not Slot<br>1 Signal | In/Out | Comments                     |

|-------------------|------------------|----------|----------------------|--------|------------------------------|

| 48                | MODSEL8-         | 0        | OPEN(MODSELB-)*      | _      |                              |

| 49                | MODSEL9-         | Ō        | OPEN*                | _      | CBDAT(0)-                    |

| 50                | CRUBIT7          | Ō        | OPEN(CRUBIT7)*       | _      |                              |

| 51                | MODSEL10-        | 0        | OPEN*                |        | CBDAT(1)—                    |

| 52                | CRUBIT6          | 0        | OPEN(CRUBIT6)*       |        |                              |

| 53                | MODSEL11-        | 0        | OPEN <sup>*</sup>    |        | CBDAT(2)—                    |

| 54                | CRUBIT5          | 0        | OPEN(CRUBIT5)*       | _      |                              |

| 55                | TLMER-           | I/O      | TLMER-               | I/O    |                              |

| 56                | CRUBIT4          | 0        | OPEN(CRUBIT4)*       | -      |                              |

| 57                | GND              |          | GND                  |        |                              |

| 58                | TLAV             | I        | TLAV                 | I      |                              |

| 59                | GND              |          | GND                  | —      |                              |

| 60                | CRUBITIN         | I        | CRUBITIN             |        | 470 OHM PULL-UP<br>IN SLOT 1 |

| 61                | MODSEL12-        | 0        | OPEN*                |        | CBDAT(3)-                    |

| 62                | CRUBIT8          | 0        | OPEN(CRUBIT8)*       | _      |                              |

| 63                | TLWAIT-          | 1        | TLWAIT-              | I      |                              |

| 64                | CRUBIT9          | 0        | OPEN(CRUBIT9)*       |        |                              |

| 65                | NO CONNECT       |          | NO CONNECT           | _      |                              |

| 66                | INTP1A-          | 0        | INTP1A-              | 0      | HOST INTERRUPT               |

| 67                | MODSEL13-        | 0        | OPEN*                |        | CBDAT(4)-                    |

| 68                | CRUBIT10         | 0        | OPEN(CRUBIT10)*      | _      |                              |

| 69                | MODSEL14-        | 0        | OPEN*                |        | CBDAT(5)-                    |

| 70                | CRUBIT11         | 0        | OPEN(CRUBIT11)*      |        |                              |

| 71                | TLAK-            | I/O      | TLAK-                | I/O    |                              |

| 72                | GND              |          | GND                  |        |                              |

| 73                | NO CONNECT       | —        | NO CONNECT           | —      | TLCACHEN ON /12              |

| 74                | CBTEST           | <u> </u> | CBTEST               |        | GND IN CHASSIS               |

| 75                | NO CONNECT       |          | NO CONNECT           | -      |                              |

| 76                | MODSEL15-        | 0        | OPEN*                | -      |                              |

| 77, 78<br>、79 ,80 | + 5 MAIN<br>GND  | I        | +5 MAIN<br>GND       | 1      |                              |

# Table 1-5. Backpanel Connector P1 (Continued)

#### Note:

\* Outputs tristate, inputs disabled by slot 1 switch.

| Pin<br>Number | Slot 1<br>Signal | In/Out | Not Slot<br>1 Signal | In/Out | Comments        |

|---------------|------------------|--------|----------------------|--------|-----------------|

| 1, 2          | GND              | _      | GND                  | _      |                 |

| 3, 4          | + 5 MAIN         | 1      | +5 MAIN              |        |                 |

| 5, 4<br>5     | TLAG(OUT)        | ò      | TLAG(OUT)            | Ö      |                 |

| 6             | TLAG(IN)         | ĭ      | TLAG(IN)             | I      |                 |

| 7             | GND              | ·<br>_ | GND                  | _      |                 |

| 8             | TLADR14-         | 1/0    | TLADR14-             | I/O    |                 |

| 9             | TLADR15-         | 1/O    | TLADR15-             | 1/O    |                 |

| 10            | TLADR10-         | 1/O    | TLADR10-             | 1/0    |                 |

| 11            | TLADR12-         | 1/O    | TLADR12-             | 1/O    |                 |

| 12            | TLADR11-         | 1/0    | TLADR11-             | 1/O    |                 |

| 13            | MODSEL23-        | 0      | OPEN(TLPRES-)*       | -      |                 |

| 14            | NO CONNECT       | _      | N.C.(TLIORES-)       |        |                 |

| 15            | TLADR13-         | I/O    | TLADR13-             | I/O    |                 |

| 16            | MODSEL22-        | Ő      | OPEN(TLPFWP-)*       |        |                 |

| 17            | TLADR08-         | 1/0    | TLADR08-             | I/O    |                 |

| 18            | MODSEL21-        | 0      | OPEN(CRUBITOUT)*     |        |                 |

| 19            | TLADR09-         | 1/0    | TLADR09-             | I/O    |                 |

| 20            | TLDAT11-         | I/O    | TLDAT11-             | 1/0    |                 |

| 21            | TLDAT08-         | 1/0    | TLDAT08-             | 1/O    |                 |

| 22            | MODSEL20-        | 0      | OPEN(STORECLK-)*     | _      |                 |

| 23            | TLDAT10-         | 1/0    | TLDAT10-             | I/O    |                 |

| 24            | INT3-            | 1      | OPEN(GND)*           | _      | 470 OHM PULL-UP |

| 25            | TLADR18-         | I/O    | TLADR18-             | I/O    |                 |

| 26            | TLHOLD-          | 1/0    | TLHOLD-              | 1/0    |                 |

| 27            | TLADR17-         | 1/0    | TLADR17-             | 1/0    |                 |

| 28            | RESTART-         | 1      | RESTART-(OPEN)       |        |                 |

| 29            | TLADR16-         | 1/0    | TLADR16-             | I/O    |                 |

| 30            | GND              |        | GND                  | _      |                 |

| 31            | TLADR19-         | 1/0    | TLADR19-             | I/O    |                 |

| 32            | MODSEL19-        | 0      | OPEN(CRUBIT13)*      | —      |                 |

| 33            | TLDAT09-         | I/O    | TLDAT09-             | I/O    |                 |

| 34            | MODSEL18-        | 0      | OPEN(CRUBIT15)*      | _      |                 |

| 35            | TLDAT02-         | I/O    | TLDAT02-             | 1/O    |                 |

| 36            | MODSEL17-        | 0      | OPEN(CRUBIT12)*      | _      |                 |

| 37            | TLDAT03-         | I/O    | TLDAT03-             | I/O    |                 |

| 38            | MODSEL16-        | 0      | OPEN(CRUBIT14)*      | —      |                 |

| 39, 40        | + 12 MAIN        | 1      | + 12 MAIN            | I      |                 |

| 41, 42        | – 12 MAIN        | 1      | – 12 MAIN            | I      |                 |

| 43            | TLDAT06-         | I/O    | TLDAT06-             | I/O    |                 |

| 44            | TLADR01-         | I/O    | TLADR01-             | I/O    |                 |

| 45            | TLDAT07-         | I/O    | TLDAT07-             | I/O    |                 |

| 46            | INT4-            | I/O    | OPEN(MODSELB-)*      |        | 470 OHM PULL-UP |

| 47            | TLADR06-         | I/O    | TLADR06-             | I/O    |                 |

| 48            | INT5-            | Ι_     | OPEN(MODSELA-)*      |        | 470 OHM PULL-UP |

| 49            | TLADR07-         | I/O    | TLADR07-             | I/O    |                 |

| 50            | INT6-            | I      | OPEN*                | —      | 470 OHM PULL-UP |

| 51            | TLADR02-         | I/O    | TLADR02-             | I/O    |                 |

Table 1-6. Backpanel Connector P2

•

| Pin    | Slot 1     |        | Not Slot       |        |                                         |

|--------|------------|--------|----------------|--------|-----------------------------------------|

| Number | Signal     | In/Out | 1 Signal       | In/Out | Comments                                |

|        |            |        |                |        | •                                       |

| 52     | INT7-      | I      | OPEN*          |        | 470 OHM PULL-UP                         |

| 53     | TLADR03-   | 1/O    | TLADR03-       | I/O    |                                         |

| 54     | INT8-      | 1      | INT8-          | I      | 470 OHM PULL-UP                         |

| 55     | TLADR00-   | 1/0    | TLADR00-       | I/O    |                                         |

| 56     | INT9-      | I      | INT9-          | I      | 470 OHM PULL-UP                         |

| 57     | TLADR04-   | I/O    | TLADR04-       | I/O    |                                         |

| 58     | INT10-     | i      | OPEN(GND)*     | _      | 470 OHM PULL-UP                         |

| 59     | TLADR05-   | 1/0    | TLADR05-       | I/O    |                                         |

| 60     | NO CONNECT |        | N.C.(CRUBITIN) | -      |                                         |

| 61     | TLDAT04-   | I/O    | TLDAT04-       | 1/O    |                                         |

| 62     | INT11-     | 1      | INT11-         | 1      | 470 OHM PULL-UP                         |

| 63     | TLDAT05-   | I/O    | TLDAT05-       | I/O    |                                         |

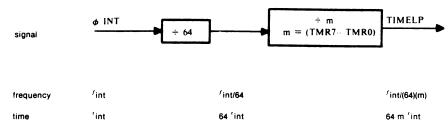

| 64     | INT12-     | I      | INT12-         | 1      | 470 OHM PULL-UP                         |