-0 TS 803 and 803H Technical Reference Manual TeleVideo

### TELEVIDEO SYSTEMS, INC.

### TS 803 AND TS 803H TECHNICAL REFERENCE MANUAL

TeleVideo Part Number 122910-00 Rev. B

### JULY 1984

Copyright (c) 1984 by TeleVideo Systems, Inc. All rights reserved. No part of this publications may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual, or otherwise, without the prior written permission of TeleVideo System, Inc., 1170 Morse Avenue, P.O. Box 3568, Sunnyvale, California 94088.

This document contains reference information to be used in specifying, operating, and maintaining the TS 803 and TS 803H computer systems.

### DISCLAIMER

TeleVideo Systems, Inc. makes no representations or warranties with respect to this manual. Further, TeleVideo Systems, Inc. reserves the right to make changes in the specifications of the product described within this manual at any time without notice and without obligation of TeleVideo Systems, Inc. to notify any person of such revision or changes. All statements, technical information, and recommendations in this document and in any manuals or related documents are believed to be reliable, but the accuracy or completeness therof is not guaranteed.

### WARNING

This equipment generates, uses, and can radiate radio frequency energy, and if not installed and used in accordance with the instruction manual may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant of Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the user at his own expense will be required to correct the interference.

TeleVideo is a registered trademark of TeleVideo Systems, Inc.

TeleVideo Systems, Inc., 1170 Morse Avenue, P.O. Box 3568, Sunnyvale, CA 94088

## COMPUTER SYSTEMS DIVISION LIMITED WARRANTY

TeleVideo Systems, Inc. ("TeleVideo") warrants to its distributors, systems houses, OEMs, and national accounts ("Buyer") that products, except software, manufactured by TeleVideo are free from defects in material and workmanship. TeleVideo's obligations under this warranty are limited to repairing or replacing, at TeleVideo's option, the part or parts of the products which prove defective in material or workmanship within 180 days after shipment by TeleVideo, except that Buyer may pass along to its initial customer ("Customer") a maximum of 90 days coverage within this 180-day warranty period, provided that Buyer gives TeleVideo prompt notice of any defect and satisfactory proof thereof.

Products may be returned by Buyer only after a Return Material Authorization number ("RMA") has been obtained from TeleVideo by telephone or in writing. Buyer must prepay all freight charges to return any products to the repair facility designated by TeleVideo and include the RMA number on the shipping container. TeleVideo will deliver replacements for defective products or parts on an exchange basis to Buyer, freight prepaid to the Buyer or the Customer. Products returned to TeleVideo under this warranty become the property of TeleVideo. With respect to any product or part thereof not manufactured by TeleVideo, only the warranty, if any, given by the manufacturer thereof, applies.

### EXCLUSIONS

This limited warranty does not cover loss or damage that occurs in shipment to or from Buyer or Customer, or is due to, (1) improper installation or maintenance, misuse, neglect or any cause other than ordinary commercial or industrial application, or (2) adjustment, repair or modification by other than TeleVideo-authorized personnel, or (3) improper environment, excessive or inadequate heating or air conditioning and electrical power failures, surges, or other irregularities, or (4) any statement made about TeleVideo's products by salesmen, dealers, distributors or agents, unless confirmed in writing by a TeleVideo officer.

The foregoing TeleVideo limited warranty is in lieu of all other warranties, whether oral, written, express, implied or statutory. Implied warranties of merchantability and fitness for a particular purpose do not apply. TeleVideo's warranty obligations and distributor's remedies hereunder are solely and exclusively as stated herein. TeleVideo makes no warranty whatsoever concerning any software products, which are sold "as is" and "with all faults." TeleVideo's liability, whether based on contract, tort, warranty, strict liability or any other theory, shall not exceed the price of the individual unit whose defect or damage is the basis of the claim. In no event shall TeleVideo be liable for any loss of profits, loss of use of facilities or equipment, or other indirect, incidental, or consequential damages.

TeleVideo Systems, Inc.

TABLE OF CONTENTS

| 1.                         | INTRODUCTION                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------------|

| 2.                         | FUNCTIONAL DESCRIPTION                                                                                    |

|                            | TS 803 System Board                                                                                       |

| 3.                         | CIRCUIT DESCRIPTION                                                                                       |

|                            | Central Processor Unit                                                                                    |

| 4.                         | SYSTEM MAINTENANCE                                                                                        |

|                            | Initialization and Self-Test Diagnostics 4.1<br>Winchester Disk Controller Board Maintenance 4.3          |

| APPE                       | NDICES                                                                                                    |

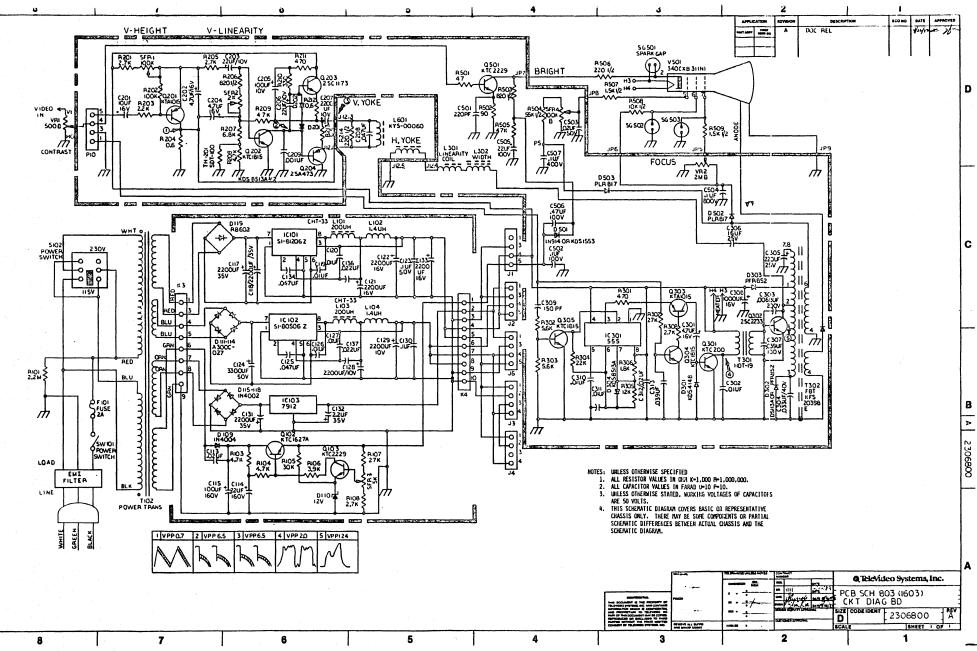

| A.<br>B.<br>C.<br>D.<br>E. | ReferencesA.1Connector Pin AssignmentsB.1DIP Switch SettingsC.1ASCII Character Code ChartD.1SchematicsE.1 |

V

)

# LIST OF FIGURES

| TS 803H Block Diagram                        | . 2.2                                                                                                                                                                                     |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boot Memory Map                              | . 2.3                                                                                                                                                                                     |

| Post-Boot Memory Map                         | . 2.4                                                                                                                                                                                     |

| Video Memory Map                             | . 2.6                                                                                                                                                                                     |

| Block Diagram of the Main Board              | . 3.2                                                                                                                                                                                     |

| CPU Active Lines                             | . 3.3                                                                                                                                                                                     |

| Read-Only Memory Active Lines                | . 3.5                                                                                                                                                                                     |

| Main Memory Active Lines                     | . 3.6                                                                                                                                                                                     |

| Timing for Memory Operations                 | . 3.7                                                                                                                                                                                     |

| Decoder Active Lines                         | . 3.9                                                                                                                                                                                     |

| Serial I/O Active Lines                      | 3.10                                                                                                                                                                                      |

| Floppy Disk Controller Active Lines          | 3.12                                                                                                                                                                                      |

| Winchester Controller Interface Active Lines | 3.14                                                                                                                                                                                      |

| Video Memory Active Lines                    | 3.15                                                                                                                                                                                      |

| CRT Controller Block Diagram                 | 3.17                                                                                                                                                                                      |

|                                              |                                                                                                                                                                                           |

|                                              |                                                                                                                                                                                           |

| Buffor DAM Active Lines                      | 3 22                                                                                                                                                                                      |

| Writing Dick Data                            | 2 25                                                                                                                                                                                      |

|                                              |                                                                                                                                                                                           |

| Reading Disk Data                            | 3.21                                                                                                                                                                                      |

|                                              |                                                                                                                                                                                           |

| ASCII Character Code Chart                   | D.1                                                                                                                                                                                       |

|                                              |                                                                                                                                                                                           |

| OF TABLES                                    |                                                                                                                                                                                           |

| T/O Dout Allucator                           | 2 /                                                                                                                                                                                       |

|                                              |                                                                                                                                                                                           |

| I/O Port Addresses                           | • <u>2</u> • <del>•</del>                                                                                                                                                                 |

| Control Port Decoder Signals                 | . 2.5                                                                                                                                                                                     |

| Control Port Decoder Signals                 | . 2.5                                                                                                                                                                                     |

| Control Port Decoder Signals                 | . 2.5                                                                                                                                                                                     |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8                                                                                                                                                          |

| Control Port Decoder Signals                 | 2.5<br>2.5<br>2.7<br>2.8<br>3.3                                                                                                                                                           |

| Control Port Decoder Signals                 | <ul> <li>2.5</li> <li>2.5</li> <li>2.7</li> <li>2.8</li> <li>3.3</li> <li>3.5</li> </ul>                                                                                                  |

| Control Port Decoder Signals                 | <ul> <li>2.5</li> <li>2.5</li> <li>2.7</li> <li>2.8</li> <li>3.3</li> <li>3.5</li> <li>3.8</li> </ul>                                                                                     |

| Control Port Decoder Signals                 | <ul> <li>2.5</li> <li>2.5</li> <li>2.7</li> <li>2.8</li> <li>3.3</li> <li>3.5</li> <li>3.8</li> </ul>                                                                                     |

| Control Port Decoder Signals                 | <ul> <li>2.5</li> <li>2.5</li> <li>2.7</li> <li>2.8</li> <li>3.3</li> <li>3.5</li> <li>3.8</li> </ul>                                                                                     |

| Control Port Decoder Signals                 | . 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12                                                                                                               |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15                                                                                              |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18                                                                                      |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22                                                                              |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23                                                                      |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24                                                              |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25                                                      |

| Control Port Decoder Signals                 | . 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27                                                       |

| Control Port Decoder Signals                 | . 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24                                                                       |

| Control Port Decoder Signals                 | . 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27                                                       |

| Control Port Decoder Signals                 | . 2.5<br>2.7<br>2.8<br>3.3<br>3.5<br>3.8<br>3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>. B.1                                                          |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>. B.1<br>. B.1<br>. B.2                   |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>. B.1<br>. B.1                            |

| Control Port Decoder Signals                 | . 2.5<br>. 2.5<br>. 2.7<br>. 2.8<br>. 3.3<br>. 3.5<br>. 3.8<br>. 3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>. B.1<br>. B.1<br>. B.2<br>. B.2<br>. B.2 |

| Control Port Decoder Signals                 | 2.5<br>2.7<br>2.8<br>3.3<br>3.5<br>3.8<br>3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>. B.1<br>. B.2<br>. B.2<br>. B.2<br>. B.3                        |

| Control Port Decoder Signals                 | 2.5<br>2.7<br>2.8<br>3.3<br>3.5<br>3.8<br>3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>. B.1<br>. B.1<br>. B.2<br>. B.2<br>. B.3<br>. B.3               |

| Control Port Decoder Signals                 | 2.5<br>2.7<br>2.8<br>3.3<br>3.5<br>3.8<br>3.9<br>3.11<br>3.12<br>3.15<br>3.18<br>3.22<br>3.23<br>3.24<br>3.25<br>3.27<br>B.1<br>B.2<br>B.2<br>B.2<br>B.3<br>B.3<br>B.3                    |

|                                              | Video Memory Active Lines                                                                                                                                                                 |

### INTRODUCTION

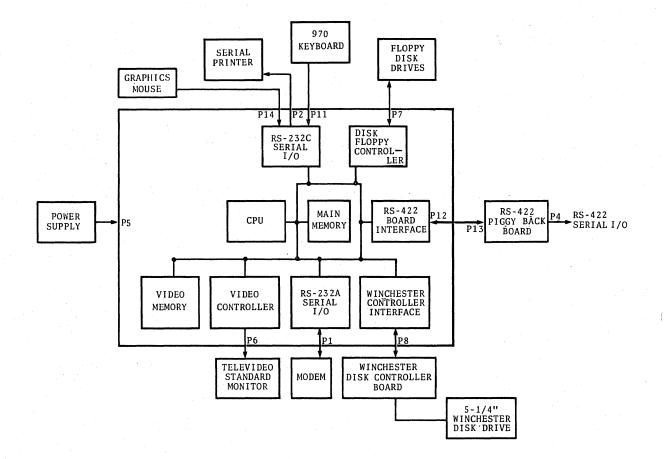

The TeleVideo TS 803 and TS 803H microcomputer systems are based on the Zilog Z80 microprocessor, using the same basic circuit board in different configurations.

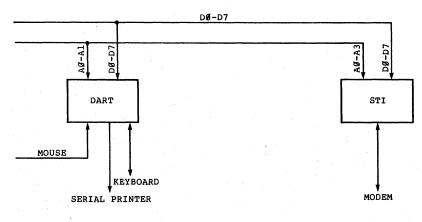

The TS 803 contains two vertically-mounted slim-line floppy disk drives. This system features two RS-232C serial I/O ports: one configured to transmit data to a serial printer and receive data from a graphics mouse, and the other configured for a modem or similar device.

The TS 803H contains one vertically-mounted slim-line floppy disk drive and one 5 1/4-inch slim-line Winchester hard disk drive. The I/O port configuration is identical to the TS 803.

A TS 803 option board adds a single RS-422 serial I/O port to the system board. This option is field-installable.

Main memory for both systems is 64 kilobytes of dynamic RAM. A separate memory, dedicated to graphics and video display, is composed of 32 kilobytes of dynamic RAM. Graphics display capability is 640 pixels horizontal by 240 pixels vertical, with 24 lines by 80 characters for alphanumeric display. Read-only memory is 8 kilobytes, used for system boot and power-up diagnostics.

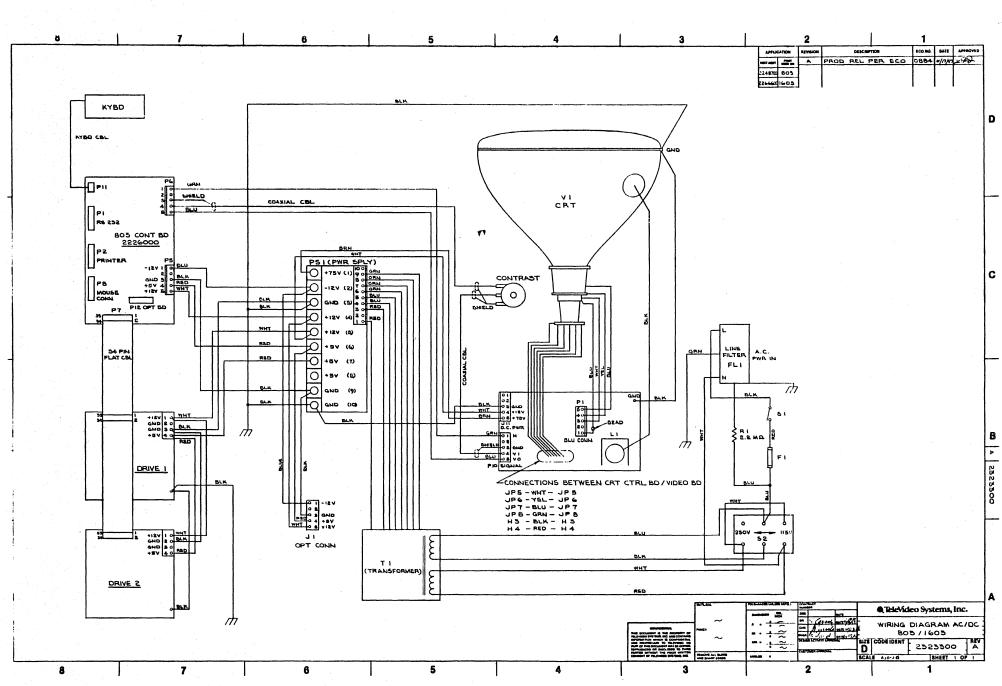

Both systems use the same switching-type power supply, TeleVideo 970-type keyboard, and video driver circuits.

## 2. FUNCTIONAL DESCRIPTION

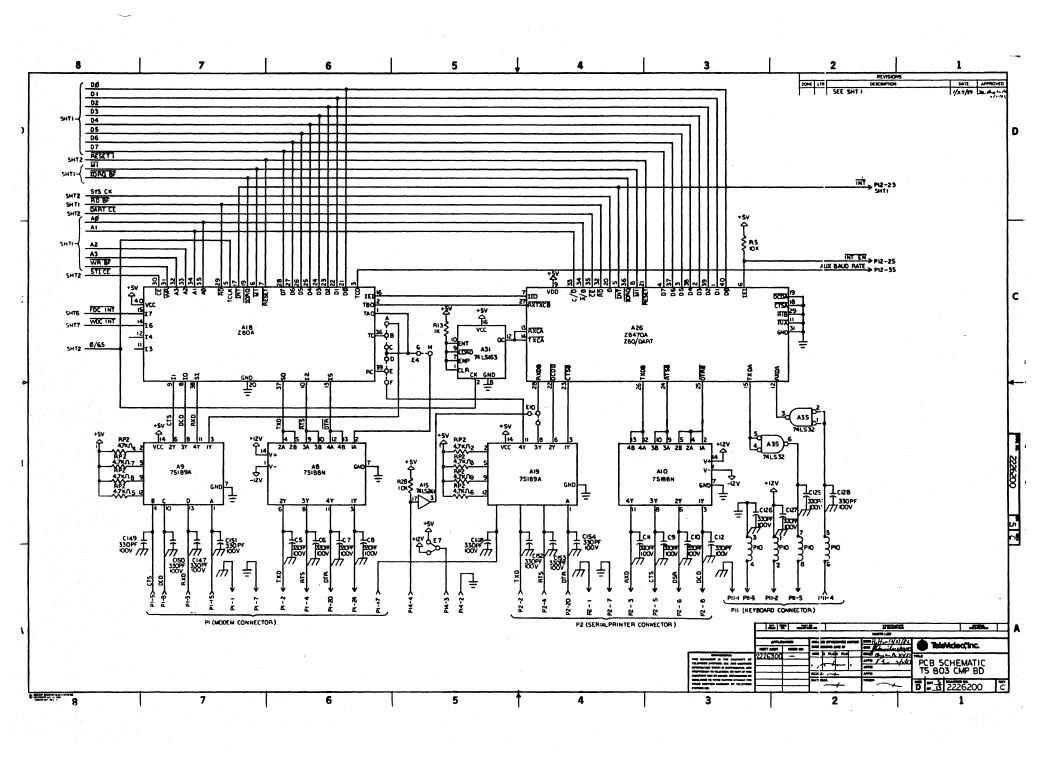

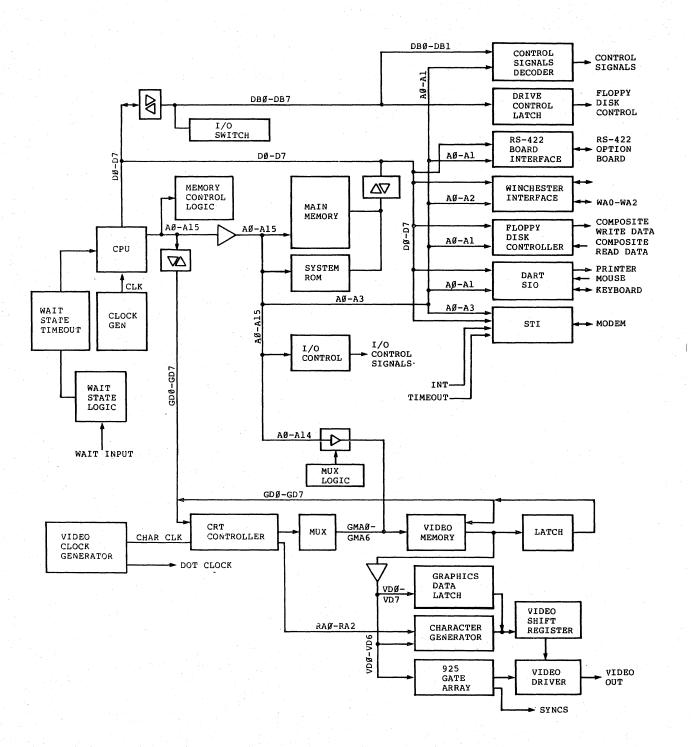

The TS 803 system is contained on a single circuit board. The RS-422 option board and the Winchester disk controller board are mounted piggyback fashion on the system board. A block diagram of the TS 803H, showing all system features, is in Figure 2-1.

Figure 2-1 TS 803H Block Diagram

### TS 803 SYSTEM BOARD

The central processing unit functions are carried out by a Zilog Z80 CPU microprocessor device. The CPU carries out logical and computational functions of the running software, handles graphics processing, and updates video memory.

The CPU communicates with the system on a 16-bit address bus, an 8-bit data bus, and control lines. Interrupts from the system are passed to the CPU on an interrupt line. The system has six interrupting devices, including a software time-of-day clock. The order of interrup priorities as as follows:

| (highest) | 0. | RS-422 option board              |

|-----------|----|----------------------------------|

|           | 1  | Z80A DART (RS-232C serial I/O)   |

|           | 2  | Z80 STI (RS 232C modem port)     |

|           | 3  | FD 1793 floppy disk controller   |

|           | 4  | Winchester disk controller board |

| (lowest)  | 5  | Time-of-day clock                |

Interrupts 0 through 2 are prioritized in a daisy-chain arrangement. Interrupts 3 through 5 are wired to the Z80 STI interrupt input pins.

Main memory is configured in 64K x l dynamic RAM devices. Standard main memory is 64 kilobytes. Read-only memory is configured in a single 16K x 8 EPROM device.

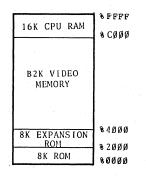

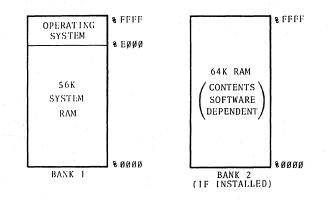

Two mappings of main memory are used in the system. At boot, the system selects the map of Figure 2-2. The lower eight kilobytes of the CPU memory address space are occupied by the system ROM. The next eight kilobytes are reserved for expansion of the ROM. The area from %4000 through %BFFF is occupied by the video memory, physically separate from main memory. The upper 16 kilobytes of the CPU address space are located in main memory, and are loaded with the operating system, such as CP/M.

Figure 2-2 Boot Memory Map

After boot, the system switches to the memory map shown in Figure 2-3. Main memory is now fully addressed, with 56 kilobytes of user space. The upper eight kilobytes of main memory are now dedicated to the operating system. The lower end of memory contains vectors to operating system BIOS routines in CP/M that in turn call video memory.

## Figure 2-3 Post-Boot Memory Map

An I/O port decoder is contained in a decoder device on the system board. The decoder is addressed on address bus lines A4 through A7 as shown in Table 2-1. The decoder produces enables, which, along with the system control lines, configure the system I/O ports and pass data to peripheral devices.

### Table 2-1 I/O Port Addresses

| Device                           | Address |

|----------------------------------|---------|

| System Status Switch 1           | £00     |

| Diagnostic Indicators 1 and 2    | 810     |

| Diagnostic Indicators 3 and 4    | 811     |

| RS-422 Control and Auto Wait     | 812     |

| Memory Bank Select               | 813     |

| STI Device                       | 820-82F |

| DART Device                      | 830-833 |

| RS-422 SIO Device                | 840-843 |

| Floppy Disk Controller           | 880-883 |

| Floppy Disk Drive Decoder        | 890     |

| Winchester Disk Controller Reset | 8A0     |

| Winchester Disk Controller       | 8B0-8BF |

| Graphics Controller              | %C0-%CF |

I/O port enables at addresses %00 through %13 are applied to a system control port decoder to produce the functions listed in Table 2-2. This decoder is addressed as an I/O port on the addresses shown, and data is written on lines D0 and D1 to perform the listed function.

## Table 2-2 Control Port Decoder Signals

| Address                                       | Dl                              | D <b>0</b>                      | Function                                                                                                                                                   |

|-----------------------------------------------|---------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| %10<br>%10<br>%10<br>%11<br>%11<br>%11<br>%12 | 1<br>0<br>1<br>1<br>0<br>1<br>0 | 0<br>1<br>1<br>0<br>1<br>1<br>0 | Indicator 1 on<br>Indicator 2 on<br>Indicators 1 and 2 off<br>Indicator 3 on<br>Indicator 4 on<br>Indicators 3 and 4 off<br>RS-422 on; auto wait on        |

| 812<br>812<br>812<br>812<br>813<br>813<br>813 | 0<br>1<br>1<br>0<br>0<br>1      | 1<br>0<br>1<br>0<br>1<br>0      | RS-422 off; auto wait on<br>RS-422 off; auto wait off<br>RS-422 off; auto wait off<br>Select memory bank 0<br>Select memory bank 1<br>Select memory bank 2 |

The RS-232C serial I/O channels are configured in separate devices. The Z80 STI contains a single RS-232C channel configured for interface to a modem. Two other communications channels are contained in a Z80A DART device. One channel is configured to transmit data to a serial printer at standard baud rates and to receive data from a graphics mouse. The other channel handles keyboard I/O at 9600 baud.

Timeout for the RS-232C baud rate, interrupts, and a time-of-day clock are handled through the Z80 STI. Timer settings for standard baud rates are shown in Table 2-3. To change the baud rate, load the hexidecimal value given in the table into the appropriate STI time data register.

## Table 2-3

Interval Timer Settings for Baud Rates

| Baud Rate | Hex | Decimal |  |

|-----------|-----|---------|--|

| 75        | 80  | 128     |  |

| 110       | 60  | 96      |  |

| 150       | 40  | 64      |  |

| 300       | 20  | 32      |  |

| 600       | 10  | 16      |  |

| 1200      | 08  | 08      |  |

| 2400      | 04  | 04      |  |

| 4800      | 02  | 02      |  |

| 9600      | 01  | 01      |  |

|           |     |         |  |

TeleVideo Systems, Inc.

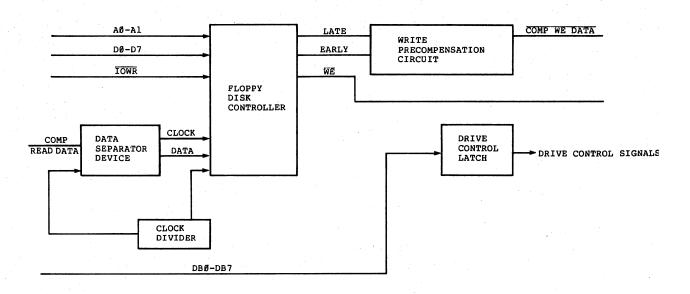

The floppy disk controller on the system board supports two drives in double-sided, double-density format. This circuit is composed of a Western Digital FD1793 floppy disk controller, an SMC 9216 data separator, and a drive control latch at I/O port address %90.

The Winchester disk control board interface is installed in both the TS 803 and TS 803H. The control board is installed in the TS 803H only.

Space is allocated on the system board for a parallel interface. This area is uninstalled in any of the standard systems, and is not supported by TeleVideo.

Screen updates are provided through a Synertek SY6545 CRT controller device. This device is programmed during power-up through the system ROM for display characteristics and operating modes.

Video memory is composed of two banks of 16K x 1 dynamic RAM devices. The memory is accessible by either the CPU or the CRT controller during alternate clock cycles. All writes of data to video memory are done by the CPU. The CRT controller retrieves the data from video memory and controls the screen updates. Dynamic RAM refresh is handled by the CRT controller and is transparent to normal operation.

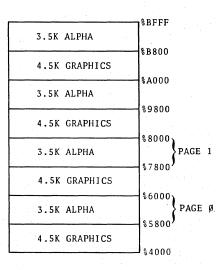

Video memory is mapped as shown in Figure 2-4. The memory is divided into 4.5 kilobyte portions of graphics storage, with 3.5 kilobyte portions of alpha storage. Each alpha area holds the full two kilobytes of data for a single page. Only pages 0 and 1 of the alpha area can be accessed.

### Figure 2-4 Video Memory Map

TeleVideo Systems, Inc.

Page 2.6

A TeleVideo 925-type gate array character generator creates the dot patterns for the alphanumeric characters as they are called up from video memory. The character generator output is sent to a shift register, which generates a serial alpha bitstream. Graphics video goes directly from video memory to the shift register, bypassing the alpha circuits. The shift register output is passed through a video driver board and sent to the system monitor.

Diagnostic indications for the system are given by four LED indicators on the system board. The diagnostic code for these indicators is given in Chapter 4.

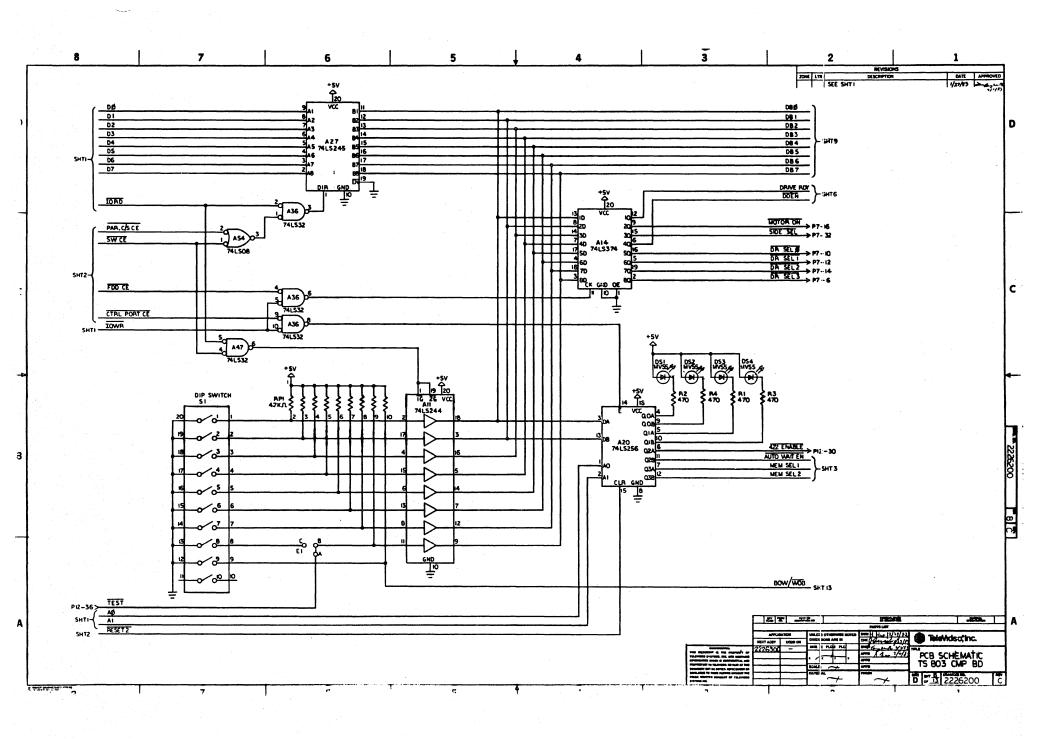

Also included on the system board is a bank of ten DIP switches, of which nine are designated to be read by software. These switches function for default baud rate selection, system mode, and general system configuration.

### RS-422 OPTION BOARD

The optional RS-422 board adds a single RS-422 channel to the system. This board receives parallel data lines and control lines from the system and generates the RS-422 signal used to communicate with a TeleVideo network processor. The RS-422 channel operates according to the TeleVideo Systems Service Processor Protocol. Data is transferred between the system and service processor at a nominal 800 kilobaud rate.

## WINCHESTER DISK CONTROLLER BOARD

The Winchester disk controller board receives commands and data from the system using address lines A0 through A2 to address internal registers, and data lines D0 through D7 to pass data.

The board uses a WD1010-00 controller processor. Individual registers in the controller processor are accessed through a task file register. This register is addressed on A0 through A2, and data is written or read as in Table 2-4.

### Table 2-4 Task File Register

| Address      | Read                  | Write                 |

|--------------|-----------------------|-----------------------|

| <b>%B0</b>   | WE 1010-00 tri-stated | WD 1010-00 tri-stated |

| %B1          | Error flags           | Write precomp cyl.    |

| 8B <b>2</b>  | Sector count          | Sector Count          |

| %B <b>3</b>  | Sector number         | Sector Number         |

| %B4          | Cylinder low          | Cylinder low          |

| %B5          | Cylinder high         | Cylinder high         |

| <b>%B6</b>   | Sector/Drive/Head     | Sector/Drive/Head     |

| 8B7          | Status Register       | Command register      |

| %B8 thru %BF | Not used              | Not used              |

TeleVideo Systems, Inc.

A summary of the task file register functions is give in Table 2-5.

## Table 2-5

Task File Register Functions

Function Register Contains error flags for bad block detect, Error Register CRC data field, ID not found, aborted command, TK0000 error, and data address mark (DAM) error. Defines the starting cylinder number at which Write Precomp Cylinder the RWC (reduced write current) line is This value is internally asserted. multiplied by four to obtain the actual cylinder. Contains the number of sectors that are to be Sector Count transferred to buffer RAM. Sector Number Contains the starting sector of a command. Least significant eight bits of the starting Cylinder Number cylinder number. Low Cylinder Number Carries the most significant bits of the starting cylinder number. The other bits of High this register are unused. Sector/Drive/Head Contains the sector size, drive number, and head number parameters for the operation. Status Register Contains status bits for device busy, device ready, write fault (same as WF line), seek complete (same as SC line), data request (same as BDRQ line), command in progress, and error register flags set. Command Register This register contains the current command: **RESTORE** - restore heads a. SEEK - for seek operations between b. multiple drives C. READ SECTOR - transfers one or more sectors to disk WRITE SECTOR - writes one or more d. sectors to disk SCAN ID - updates the head, sector size, e. sector number, and cylinder registers f. WRITE FORMAT - used to format a single

track

For a typical operation, the task file registers are written to or read for status, and a command is given to the command register. The WD1010-00 then tri-states the address bus and executes the command. At the end of the operation, the task file is again opened to the system.

A detailed description of the WD 1010-00 device is given in the referenced Western Digital documentation.

## 3. CIRCUIT DESCRIPTION

This section contains circuit descriptions of the major functional blocks on the system board.

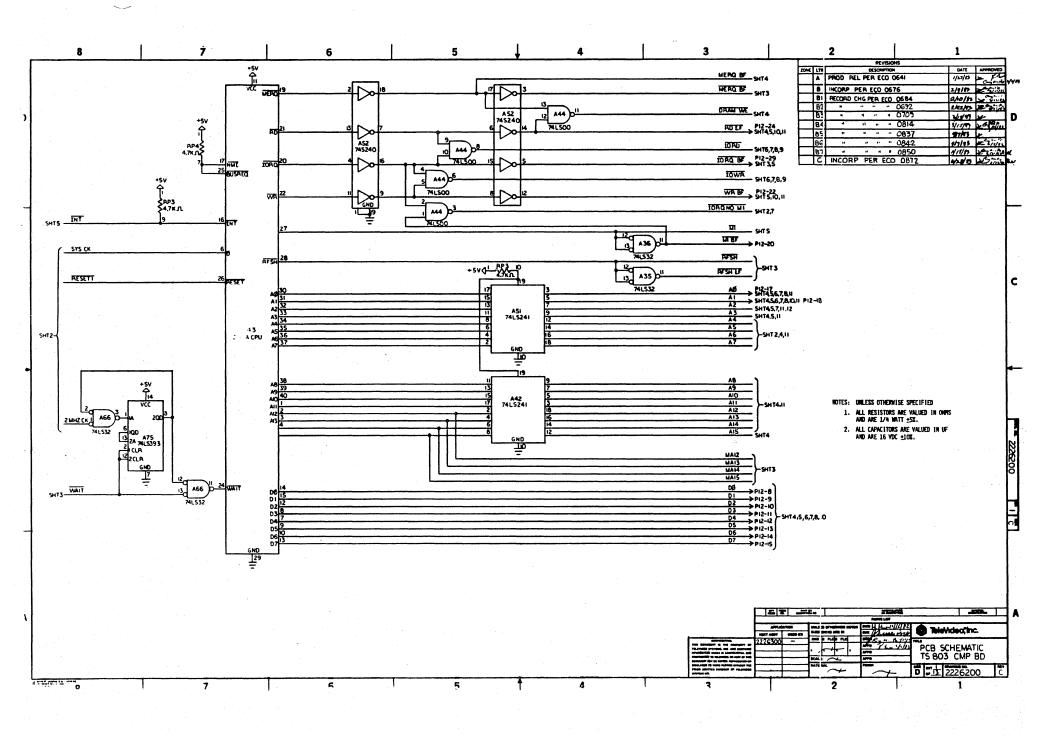

The system board contains the CPU, main memory, I/O ports, controllers, and video display circuits for the system. A block diagram of the system board is shown in Figure 3-1.

## Figure 3-1 Block Diagram of the Main Board

### **CENTRAL PROCESSOR UNIT**

The major components of the central processing unit are:

| A43      | Zilog Z80A CPU System Microprocessor |

|----------|--------------------------------------|

| A51, A42 | Address Drivers                      |

| A52      | Control Buffers                      |

| A18      | Z80 STI                              |

| A57      | 2764-2 System ROM                    |

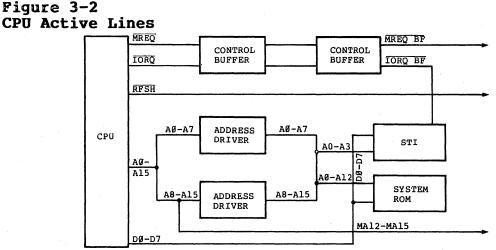

The active lines for the CPU are diagrammed in Figure 3-2 and are listed with a description in Table 3-1.

write operation.

Table 3-1 CPU Devices

### Device/Active Line Source/Description

Z80A CPU

Handles central processing functions, graphics display-related processing, and all writes to video memory. CPU timing conforms to the standards shown in the Zilog Data Book.

CPU Memory Request. Indicates that address bus holds valid address for memory read or

CPU Input/Output Request. Indicates that lower half of address bus holds a valid address for an I/O read or write operation.

CPU Memory Refresh. -RFSH together with -MREQ indicates that lower seven bits of

-MREQ

-IORQ

-RFSH

A0-A15

CPU address lines to system, driven through address drivers.

address bus contain a refresh address to RAM.

Circuits

| MA12-MA15 | CPU | memory access lines, driven directly from |

|-----------|-----|-------------------------------------------|

|           | CPU | to drive memory decoder ROM.              |

D0-D7 CPU/System data bus lines.

Address Drivers Drives address lines A0 through Al5.

Control Buffers One set of buffers control lines from CPU and passes them through combinational logic to derive associated control signals.

Z80 STI Serial Timer Interrupt Controller. Sets lower order interrupt priorities.

Interrupt priorities are set using the interrupt controller facilities of the Z80 STI for the lower order interrupts, and daisy chaining the interrupts for the RS-232C and RS-422 ports in standard Z80A fashion. Interrupt priorities are listed in Chapter 2.

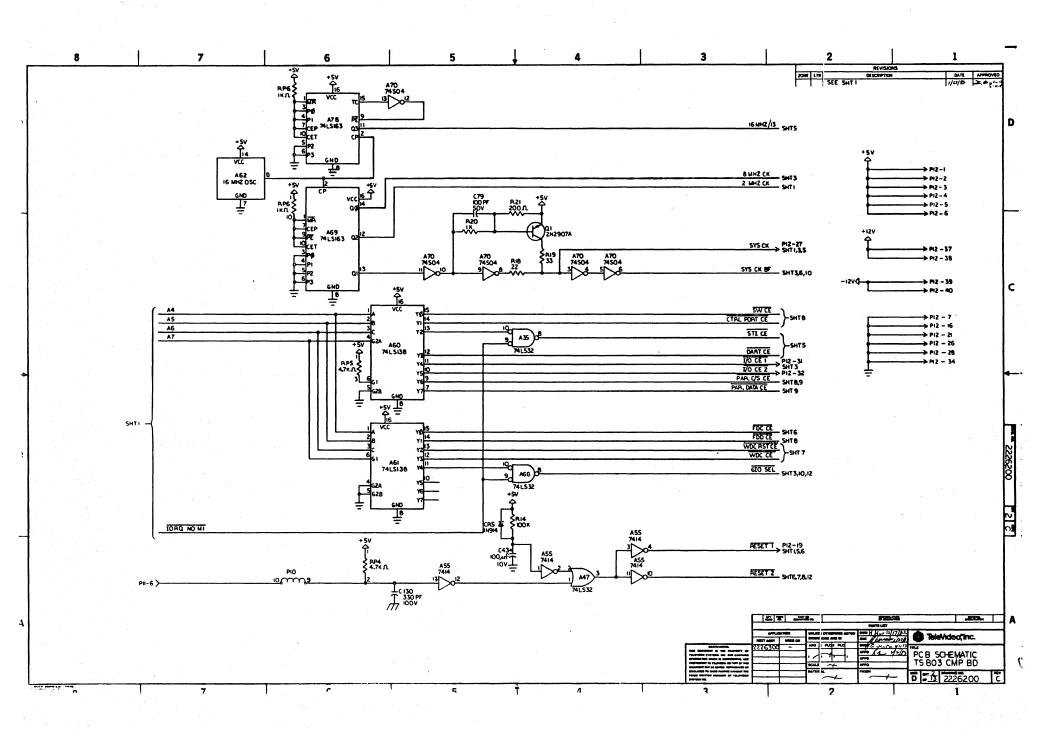

System clock is generated from a 16 MHz clock module output. The signal is passed to two four-bit counters. One counter produces the 4 MHz system clock signal, an 8 MHz clock for the TTL logic in the memory control circuit, and a 2 MHz clock for the wait state timeout circuit. The system clock signal is passed through a driver transistor before being applied to the system devices. The other counter produces a divide-by-thirteen clock signal of 1.23 MHz, used to derive all the RS-232C baud rates through the 280 STI.

Resets from the keyboard are de-glitched before application to the system.

## **READ-ONLY MEMORY**

The major components of the read-only memory are:

| A57 | 2764-2 System ROM |

|-----|-------------------|

| A59 | Memory Decoder    |

| A58 | Data Buffer       |

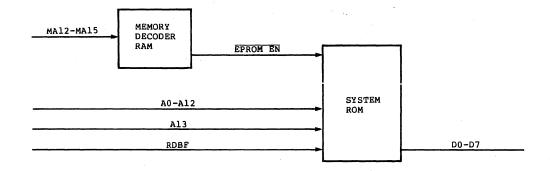

The active lines for the read-only memory are diagrammed in Figure 3-3 and are listed with a description in Table 3-2.

Page 3.4

## Figure 3-3 Read-Only Memory Active Lines

## Table 3-2 Main Memory Components

| Device/Active Line | Source/Description                                                                                                                |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| System ROM         | Read-only memory.                                                                                                                 |  |  |  |

| A0-A12             | CPU. Address lines to ROM.                                                                                                        |  |  |  |

| A13                | CPU. Allows higher-capacity compatible devices to be installed.                                                                   |  |  |  |

| -EPROM EN          | CPU. Memory decoder line to enable ROM.                                                                                           |  |  |  |

| -RD BF             | CPU. Control line that enables a read of<br>ROM. Also controls data buffer that puts ROM<br>data on data bus lines D0 through D7. |  |  |  |

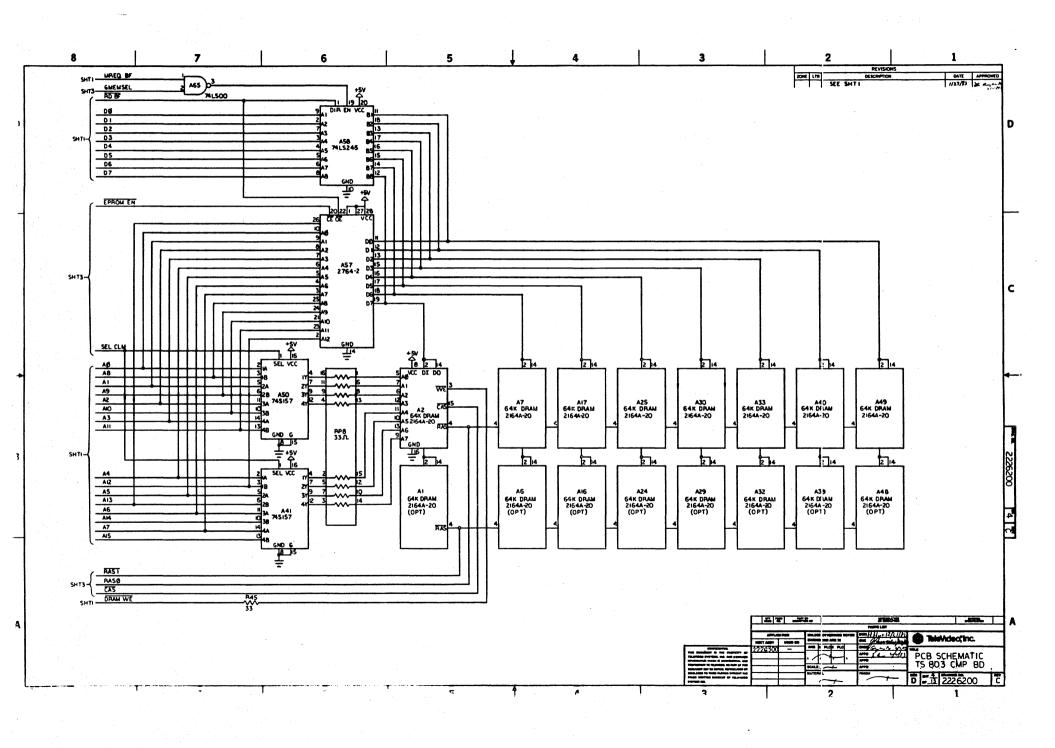

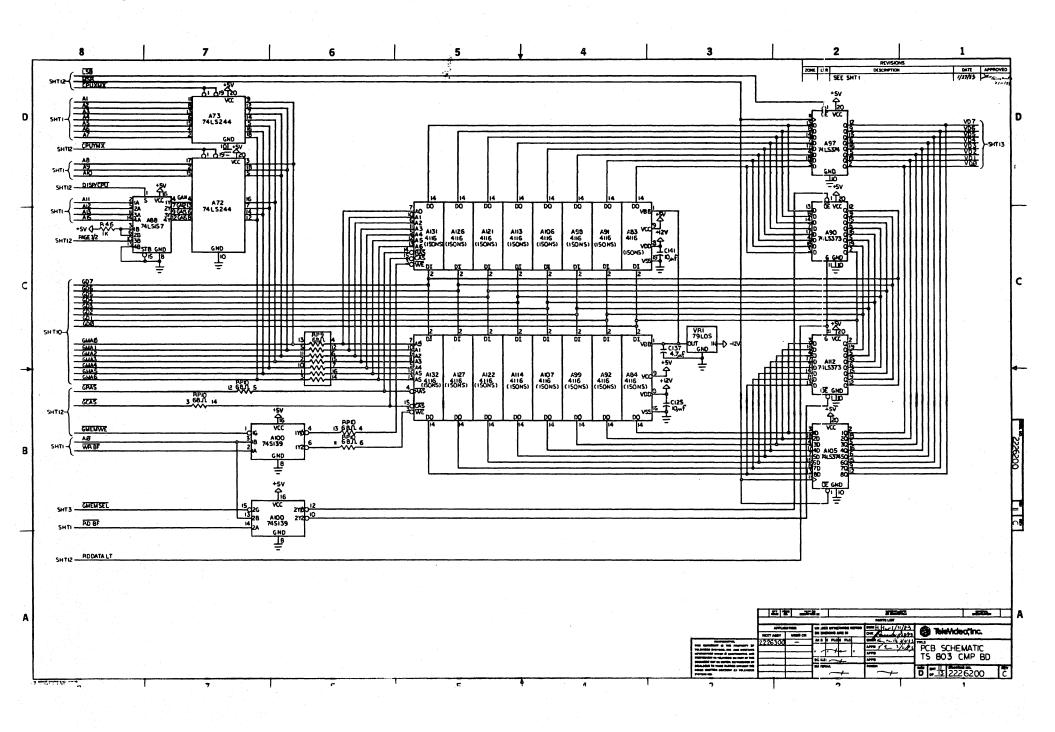

### MAIN MEMORY

The major components of main memory are:

| Al,A2,       | 64K x 1 | Dynamic   | RAM   |         |

|--------------|---------|-----------|-------|---------|

| A6,A7,A16,   |         |           |       |         |

| A17,A24,A25, |         |           |       |         |

| A29,A30,A32, |         |           |       |         |

| A33,A39,A40, |         |           |       |         |

| A48,A49      |         |           |       |         |

| A41,A50      | Address | Multiple  | exers |         |

| A71,A79      |         | Signals   |       | Machine |

| A59          |         | Decoder I |       |         |

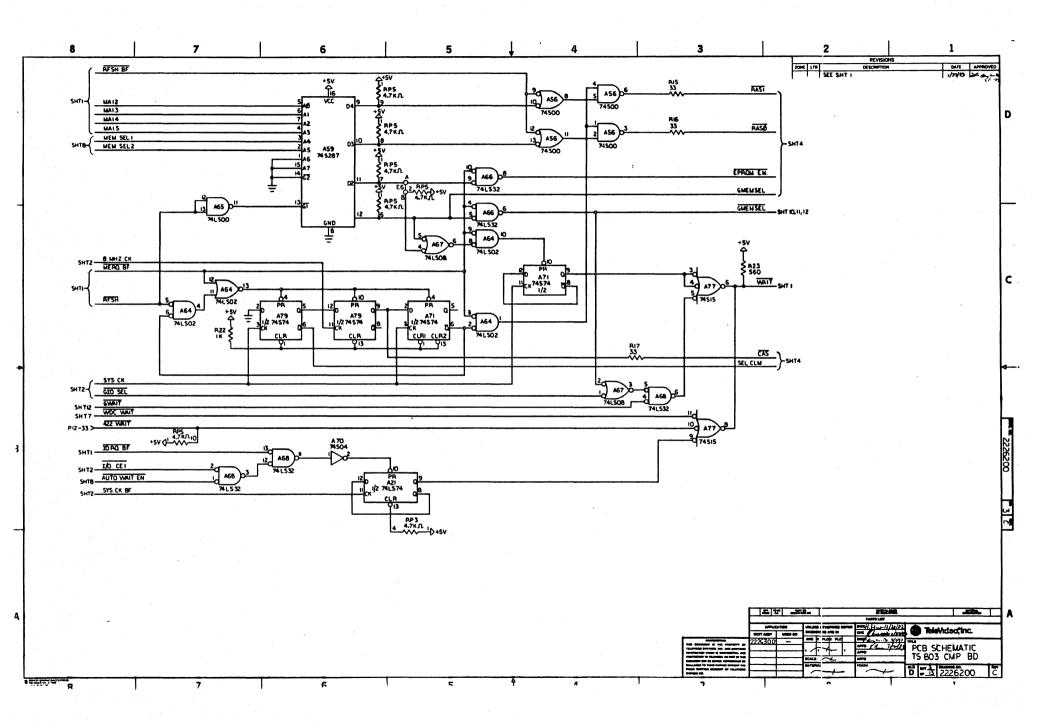

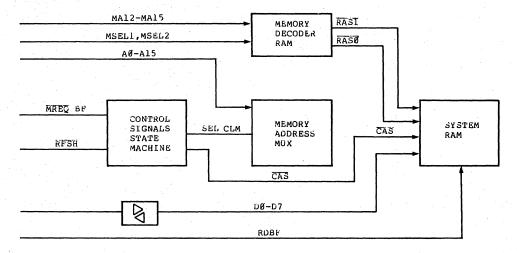

The active lines for the main memory are diagrammed in Figure 3-4 and are listed with a description in Table 3-3.

# Figure 3-4

Main Memory Active Lines

A timing diagram for memory operations is shown in Figure 3-5. Other signals not shown in Figure 3-4 are as shown in the Zilog Data Book.

## Figure 3-5 Timing For Memory Operations

## Memory Control Logic

The sequence of operations in Table 3-3 takes place during a memory access.

Table 3-3 Memory Access Sequence of Operations

Device/Active Line Source/Description

-MREQ BF,-RFSH CPU. Inactive high to hold state machine in a preset state.

MA12-MA15 CPU. Along with MEM SEL1 and MEM SEL2, from I/O port decoder, form command address to memory decoder ROM.

-MREQ BF CPU. Activated to begin memory access.

-RAS State Machine. Active when -MREQBF goes goes active as an AND function of -MREQ BF and the third F/F of the state machine. -RAS is ANDed with memory decoder ROM signals to produce bank select signals -RAS0 or -RAS1.

SEL CLM State Machine. Produced on next clock after -RAS to change memory address multiplexers from a row to a column address.

-CAS State Machine. Produced on next clock after SEL CLM to complete the memory address.

For a memory refresh, the preset -RAS signal from the state machine is ANDed with the -RFSH signal from the CPU to hold the state machine in the preset state. The memory request signal, -MREQ BF gates the -RAS signal to the RAS gates, where it is ANDed with the buffered refresh signal -RFSH BF to produce simultaneous refresh of both memory banks. Memory refresh is carried out every instruction fetch cycle.

### DECODERS

The major components of the decoders are:

| A60,A61     | I/O Signals Decoder            |

|-------------|--------------------------------|

| A20         | System Control Signals Decoder |

| A11         | ID Switch Buffer               |

| A68,A21,A77 | Wait State Logic               |

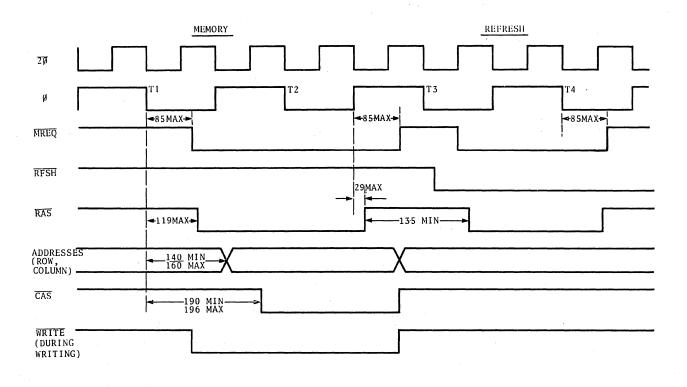

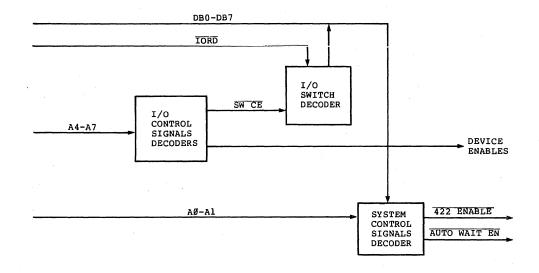

The active lines for the decoders are diagrammed in Figure 3-6 and are listed with a description in Table 3-4.

### Figure 3-6 Decoder Active Lines

## Table 3-4 Decoder Devices

### Device/Active Line Source/Description

I/O Control Signals Decoder

Contained in two demultiplexer devices, addressed by lines A4 through A7. Line A7 changes decoder from low order address selection to high order address selection. A listing of port addresses is given in section 2.

System Control Signals Decoder

ID Switch Buffer Latch is addressed with lines A0 and Al. Data is supplied to latch on lines DB0 and DB1. Settings of 10-section DIP switch are enabled to data bus lines DB0 through DB7 with decoded signal -SW CE and CPU signal -IORD

Contained in dual 4-bit addressable latch.

decoded signal -SW CE and CPU signal -IORD. Nine sections of the DIP switch are used, with each switch position being software defined as listed in the system User's Manual.

### Wait State Logic

Wait states are inserted by peripheral devices to allow response time to a CPU request. Waits for the graphics section, Winchester disk controller, and RS-422 interface are passed through combinational logic to produce the signal -WAIT. When video memory is accessed, a single automatic wait state is produced by a flip-flop before being combined into the -WAIT signal. Wait signals from the RS-422 board are given a single wait state in a similar flip-flop. The signal -WAIT is passed through a timeout counter, clocked by the 2 MHz clock, to limit the maximum wait time to 32 microseconds. The timeout is applied to the -WAIT input of the CPU.

### SERIAL I/O

Both systems contain RS-232C ports for modem, printer, keyboard, and graphics mouse. The major serial I/O components are:

| A18 | Z80 8 | STI  |

|-----|-------|------|

| A26 | Z80A  | DART |

The active lines for the serial I/O are diagrammed in Figure 3-7 and are listed with a description in Table 3-5.

## Figure 3-7 Serial I/O Active Lines

Default baud rates for the RS-232C serial I/O channels are set by a DIP switch on the system board as defined in the system User's Manual.

The system board also contains an interface to the RS-422 option board. This board is optional in the TS 803 and TS 803H.

Table 3-5 Serial I/O Devices

### Device/Active Line Source/Description

Z80A DART

Handles keyboard I/O, printer output, and mouse input. Baud rate for keyboard channel is derived by dividing 153.8 KHz clock signal at the DART down to 9600 baud. Asynchronous baud rate for the printer output is generated by a timeout signal from Z80 STI on channel TB0. Jumper option on board connects incoming clock for synchronous operation.

280 STI 280 STI serial I/O channel is configured as modem interface or for general purpose. Baud rate is derived from STI timer channel TAO. STI outputs are buffered before application to connector Pl.

The system uses a standard TeleVideo 970-type keyboard with certain keycaps changed. The keyboard contains an Intel 8048 microprocessor to scan the keyboard matrix for a closure. When a closure is detected, the keyboard sends a code for the key position to the system through the DART. The system must perform a hardware reset when a CTRL/RESET is sent from the keyboard.

Keyboard codes are listed in the system User's Manual.

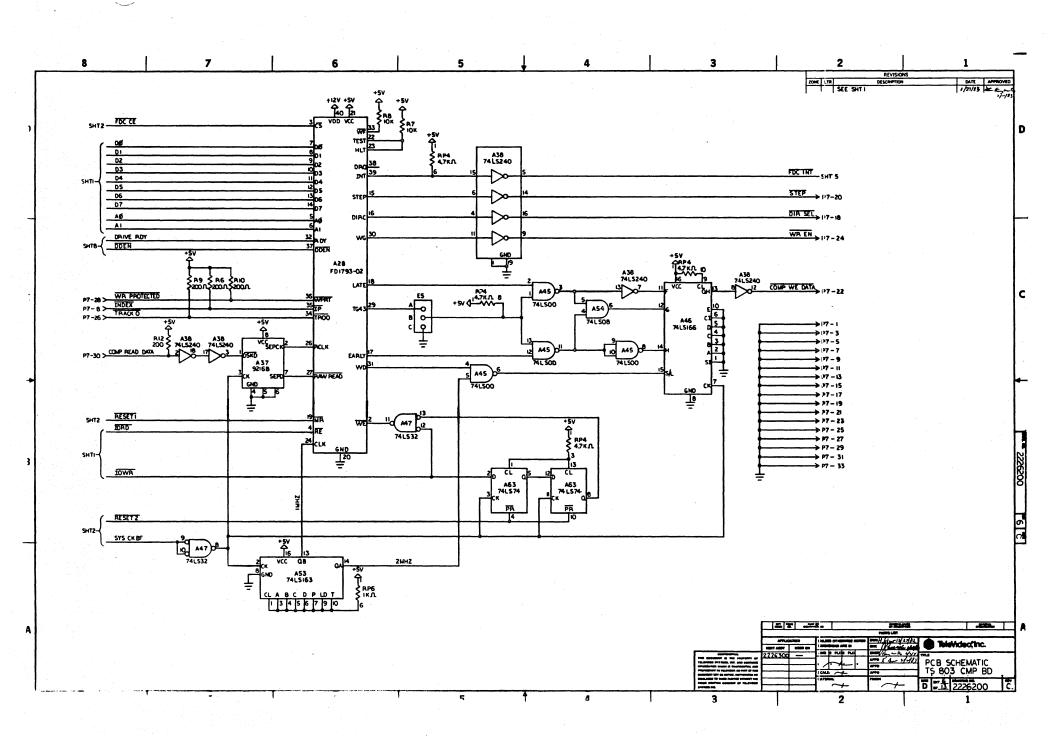

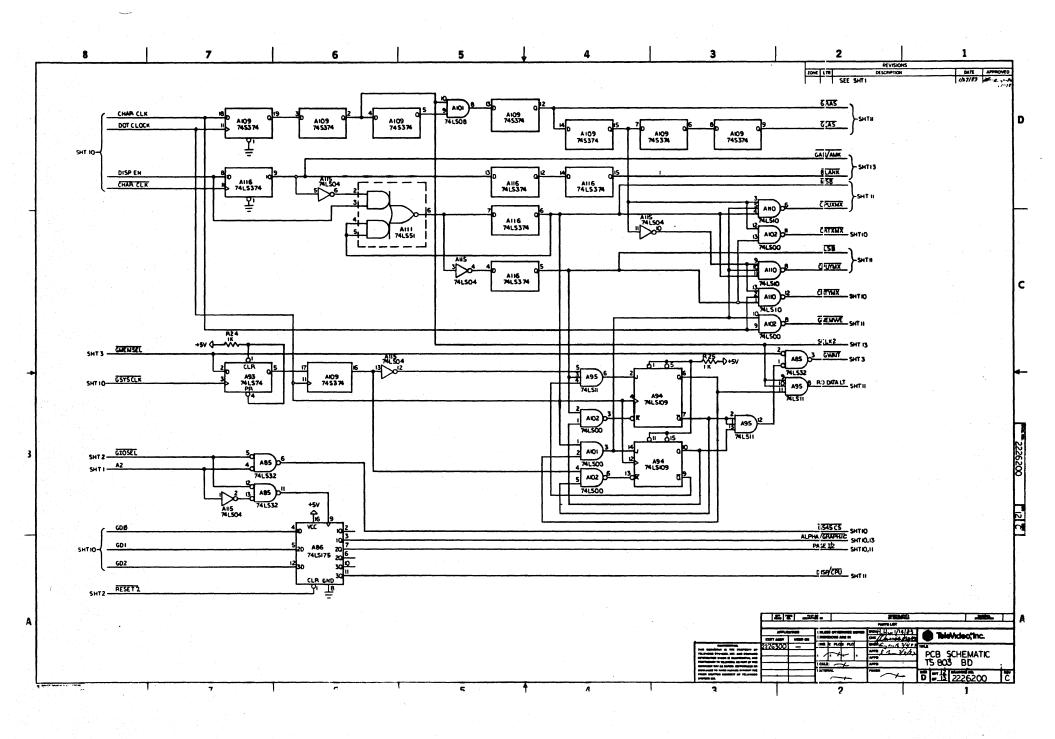

### FLOPPY DISK CONTROLLER

The major components of the floppy disk controller are:

| A28         | FD1793 Floppy Disk Controller Device |

|-------------|--------------------------------------|

| A37         | 9216B Data Separator Device          |

| A45,A46,A54 | Write Precompensation Circuit        |

| A53         | Clock Divider                        |

| A14         | Drive Control Latch                  |

The active lines for the floppy disk controller are diagrammed in Figure 3-8 and are listed with a description in Table 3-6.

## Figure 3-8 Floppy Disk Controller Active Lines

## Table 3-6 Floppy Disk Controller Devices

| Device/Active Line        | Source/Description                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Floppy Disk<br>Controller | Provides serial/parallel conversion of data<br>passing between floppy disk and system, as<br>well as all drive control functions, such as<br>head step, head direction, write protect,<br>track 0 detection, and write precompensation.<br>Controller can be programmed to handle seek<br>track, read sector, write sector, read<br>address, read track, write track, and force<br>interrupt operations. |

| D0-D7                     | Carries data and programming signals between the FDC and CPU.                                                                                                                                                                                                                                                                                                                                            |

| EARLY,LATE                | FDC. Signals to precompensation logic.<br>These signals are outputs of the FDC.                                                                                                                                                                                                                                                                                                                          |

| Precompensation<br>Logic  | This circuit is based on a shift register.<br>The LATE signal is applied to the F pin, the<br>EARLY signal is applied to the H pin and the<br>normal signal is applied to the G pin. When<br>the WD signal of the FDC goes high, the<br>appropriate bit position is shifted out of<br>the register, along with zeros in all the<br>other bit positions.                                                  |

Write precompensation appears in the form of the position of the bit in the data stream output of the shift register. Precompensation is applied in 250-nanosecond increments. A normal bit occupies the second position in the shifted data stream and occurs 500 nanoseconds after the stream starts. An early bit appears 250 nanoseconds sooner, and a late bit 250 nanoseconds later.

The duration of the entire string of pulses from the precompensation logic, including the data bit and all the zeros in the other bit positions, is much less than the minimum duration between two adjacent bits in the disk data stream.

A counter that clocks the precompensation logic at 4 MHz. A 1 MHz signal from the divider is applied to the WD input of the FDC to gate the data bits into a definite early, late, or normal category.

-IOWR

Clock Divider

tor.

Latch

Latch

Data Separator

Drive Control

Data Separator

Drive Control

tor.

Separates the raw read data and clock signals for the FDC.

CPU. Two flip-flops are used to make the -WE signal shorter to satisfy the data hold time

Selected as an I/O port on address %90, Latch receives control signals on DB0 through DB7.

Separates the raw read data and clock signals for the FDC.

Selected as an I/O port on address %90, Latch receives control signals on DB0 through DB7. Other drive control signals are generated by the FDC according to programmed instructions from the system.

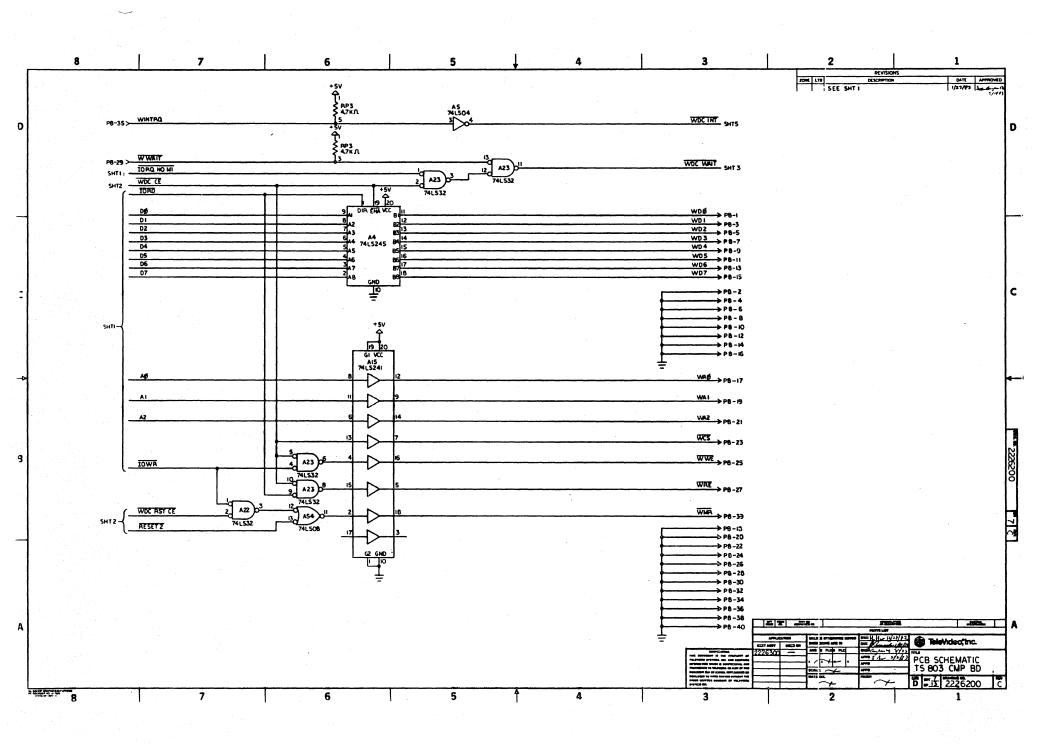

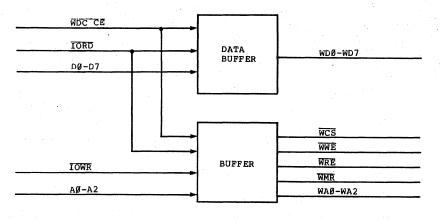

### WINCHESTER CONTROLLER INTERFACE

The major components of the Winchester controller interface are:

| A4  | Data Bu | lffer |

|-----|---------|-------|

| A15 | Buffer  |       |

The active lines for the Winchester controller interface are diagrammed in Figure 3-9.

## Figure 3-9 Winchester Controller Interface Active Lines

The components of the Winchester controller interface act to pass data between the Winchester disk controller board and the system. The interface is written to as an I/O port by the system.

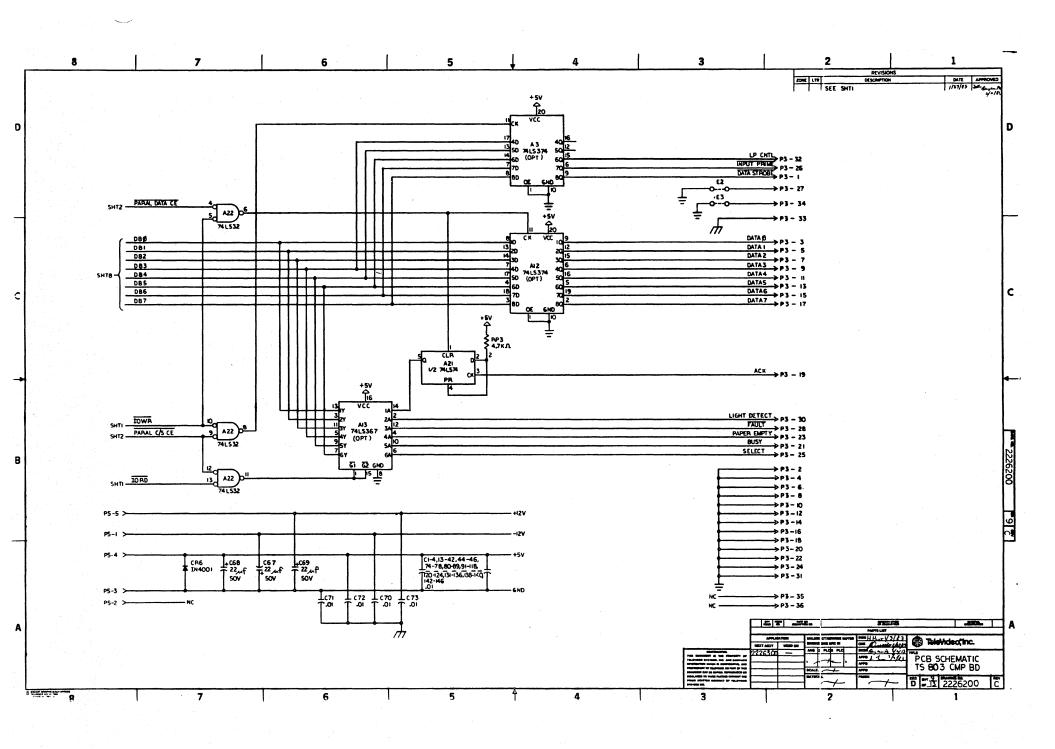

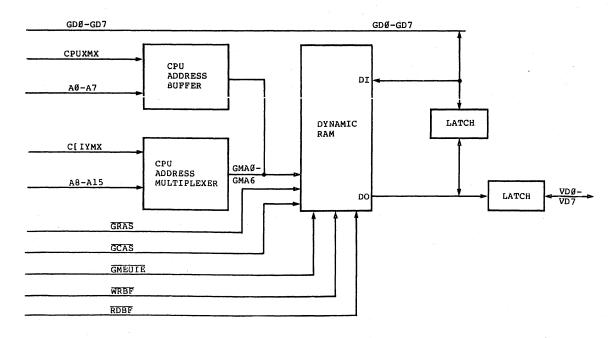

## VIDEO MEMORY

The CPU performs all writes to video memory, and reads data from video memory to perform graphics formatting. All graphics control is contained in firmware in system ROM and is acted on by the CPU. On alternate clock cycles, the CRT controller reads data from video memory to perform screen updates. The major components of video memory are:

| A83,A84,<br>A91,A92,A98,            | Type 4116 Dynamic RAM devices                 |

|-------------------------------------|-----------------------------------------------|

| A99, A106,A107,                     |                                               |

| All3,All4,Al21,<br>Al22, Al26,Al27, |                                               |

| A131,A132                           |                                               |

| A73<br>A72,A88                      | CPU Address Buffer<br>CPU Address Multiplexer |

| A97,A105                            | Data Out Latch                                |

| A90,A112                            | Data In Latch                                 |

The active lines for video memory are diagrammed in Figure 3-10 and are listed with a description in Table 3-7.

## Figure 3-10 Video Memory Active Lines

## Table 3-7 Video Memory Devices

### Device/Active Line Source/Description

-GRAS,-GCAS

Video memory control logic. These signals are continuously generated every eight dot clock times. Used by both the CPU and CRT controller accesses to video memory.

Al-Al5 CPUXMX,CPUYMX CPUXMX,CPUYMX CPUXMX,CPUYMX COntrol lines for the CPU address to video memory.

-GWAIT

Video memory control logic. Holds off CPU access to video memory until the display cycle is completed. With -GWAIT, the CPU can request video memory at any time, but can only access it at CPU access times (alternate to display cycles).

GD0-GD7

CPU. Buffered data lines D0-D7, carries write data to video memory. Buffer is controlled by memory decoder line -GMEMSEL.

-GMEMWE

Video memory control logic. Write enable for video memory.

-RDBF

CPU. With -GMEMSEL, enables buffers for CPU read of video memory on GD0-GD7.

GMA0-GMA6 CRT controller. Address to video memory for display cycle read. Both banks of memory are addressed at the same time.

VD0-VD7

Video memory. Carries read data from video memory. Data is multiplexed using -MSB and -LSB. In this way, two words of video data are read in each display cycle access. The first word is placed on the screen immediately after access, the second word is displayed during CPU access times.

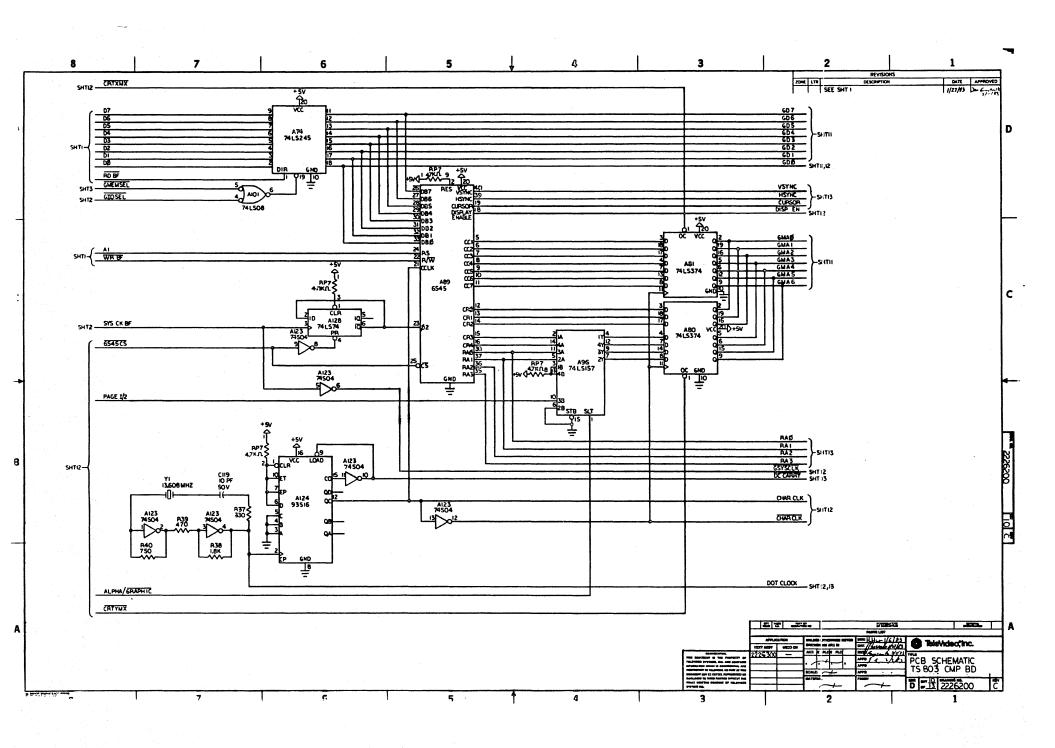

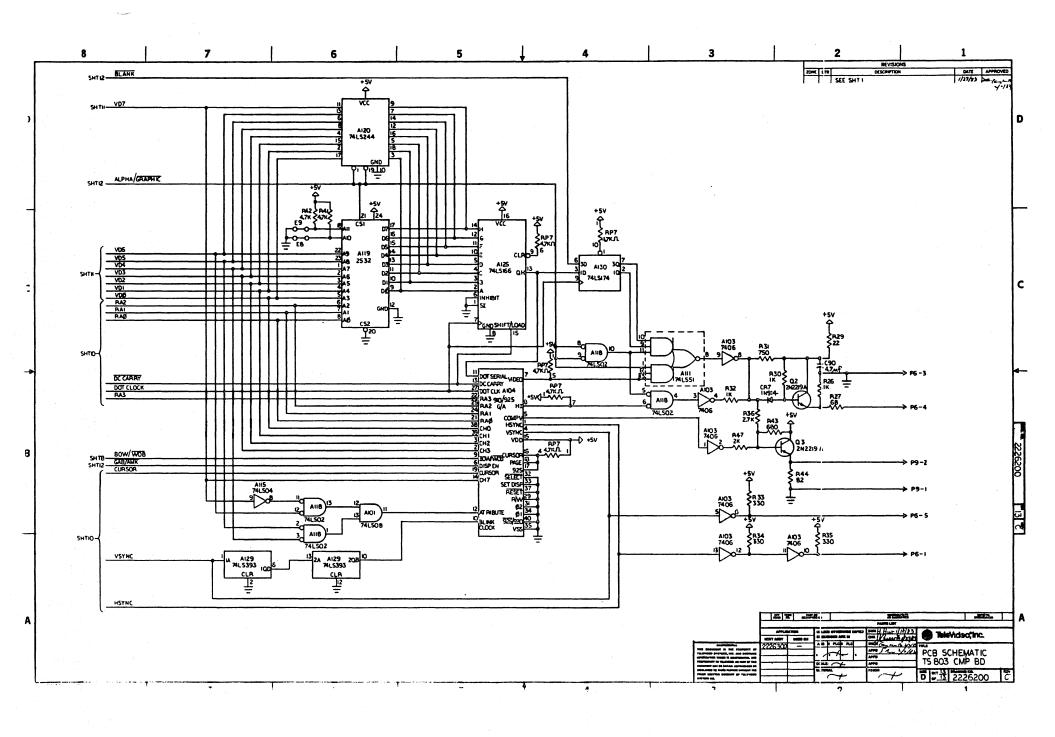

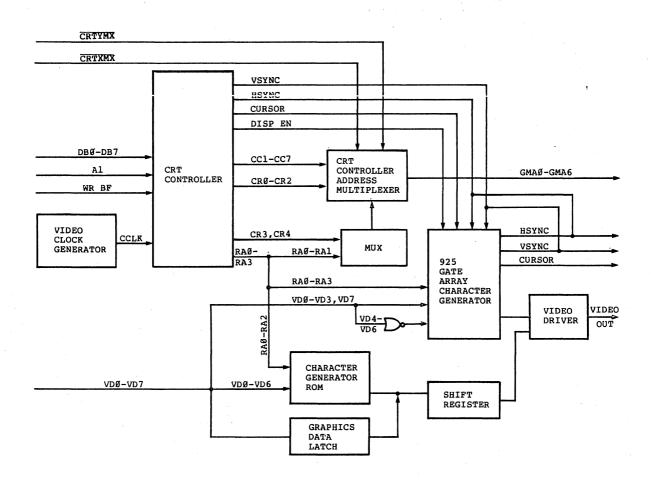

## CRT CONTROLLER AND CHARACTER GENERATOR

The CRT controller retrieves data from video memory for screen updates, and performs refresh of the dynamic RAM in video memory. Alphanumeric data from the video memory is passed through a character generator and shifted into a serial bit stream for the video display circuits. Graphics data is sent directly to the shift register. The major components of the CRT controller and character generator are:

| Synertek SY6545 CRT Controller               |

|----------------------------------------------|

| CRT Controller Address Multiplexer           |

| Multiplexer                                  |

| Video Clock Generator                        |

| Type 2532 Character Generator ROM            |

| TeleVideo 925 Gate Array Attribute Generator |

| Graphics Data Latch                          |

| Shift Register                               |

| Video Drivers                                |

|                                              |

A block diagram of the CRT controller is shown in Figure 3-11.

## Figure 3-11 CRT Controller Block Diagram

Table 3-8 lists the CRT controller and character generator components and their description.

### Table 3-8

**CRT Controller and Character Generator Components**

### Device/Active Line Source/Description

CRT Controller Performs screen updates and generates control signals for video display. The controller is operated in the shared memory mode and the input address mode.

VSYNC,HSYNC CRT controller. Vertical and horizontal synchronization signals for video monitor.

CURSOR

DISP EN

CRT controller. Active for cursor position.

CRT controller. Active when CRT controller is generating display information.

GD0-GD7 CPU. Carries programming data to CRT controller.

Al

-WR BF

CPU. Selects CRT controller internal register for programming or status read.

CPU. Selects the direction of data transfer, write or status read, with the CRT controller.

Timing for the operations between the CPU and the CRT controller is derived from the system clock through a dual flip-flop divider. The clock,  $\emptyset 2$ , is produced when the controller is selected for the operation through the -6545CS line.

Using a 13.6 MHz crystal and divider, produces the character clock and dot clock. The character clock is used as a time base for internal CRT controller functions. The dot clock is used by the fast logic of the display circuits, and to shift out the video bit stream.

CRT Controller Address Mux

Video Clock

Generator

Gates the row and column address lines from the CRT controller to video memory address lines GMA0 though GMA7.

CR0-CR4,RA0,RA1

CRT controller. Row address lines. A multiplexer selects lines CR3, CR4, RA0, and RA1 for alpha mode, and de-selects these lines for graphics mode.

CC1-CC7

CRT controller. Column address lines to video memory.

-CRTXMX,-CRTYMX Video memory control logic. Controls the gating of row and column addresses to video memory address lines GMA0 through GMA7.

Character A read-only memory containing the fonts for Generator display characters. Four character sets are included in the ROM. These sets are selected at jumper options E8 and E9 as described in the system User's Manual.

VD0-VD6, Video memory/CRT controller. These lines RA0-RA2 form the address to the character generator.

Graphics Data Latch In graphics mode, as controlled by the ALPHA/-GRAPHICS line from the CRT controller, bypasses the VD bus lines around the character generator. The ALPHA/-GRAPHICS line is switched as an I/O port from the CPU, and the mode is programmed on line GD0 through CPU data line D0.

Shift Register Takes in alpha or graphics data and creates a serial bit stream for the video drivers.

Attribute Gate Lines VD0 through VD6, RA0 through RA3 are Array applied to the attribute gate array to generate screen attributes and other signals for the video monitor.

Video Drivers Boost the video signal for application to the TeleVideo monitor video board.

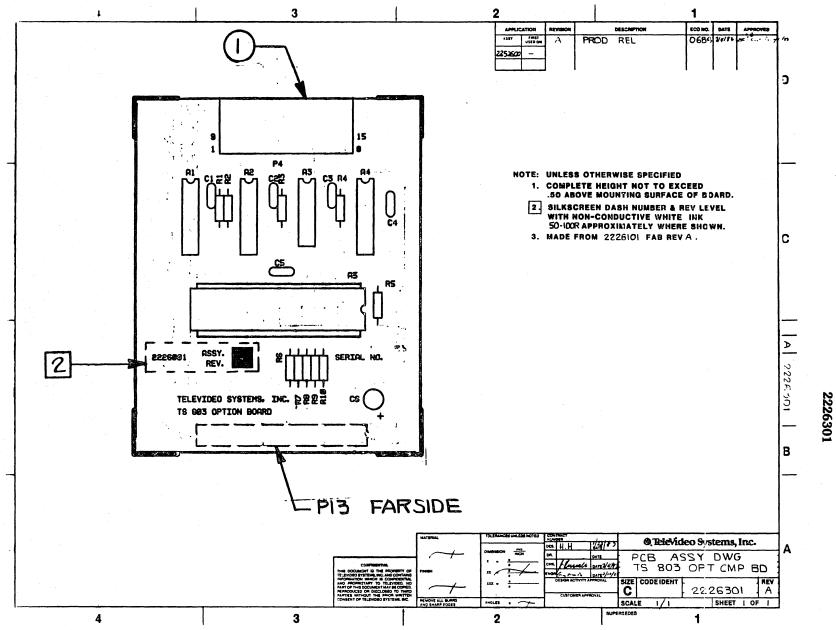

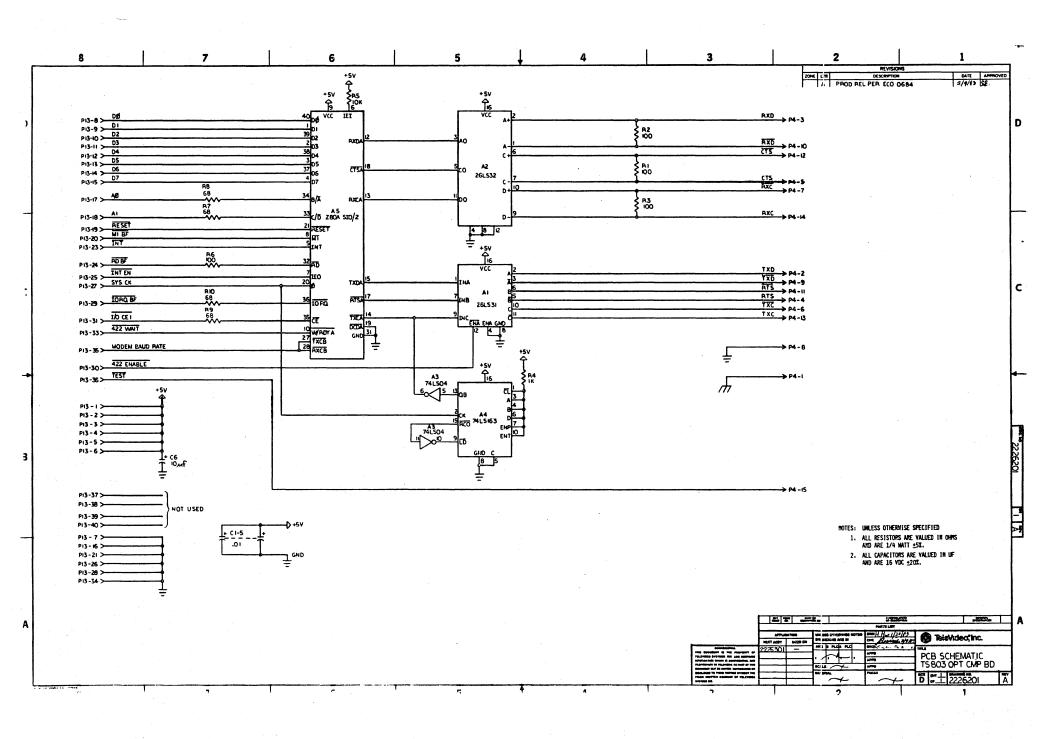

### TS 803 OPTION BOARD

The TS 803 option board plugs into Pl2 of the sytem board and supplies an RS-422 interface to the system. The board contains the following major components:

| A5 | Z80A SIO                   |

|----|----------------------------|

| A2 | Differential Line Receiver |

| Al | Differential Line Driver   |

| A4 | Clock Divider              |

Baud rate for the SIO device is derived from the system clock. The MODEM BAUD RATE line to the SIO device is non-functional. When the board is installed in the system, it occupies the highest priority in the CPU interrupt structure by having its IEI pin tied to +5 Vdc.

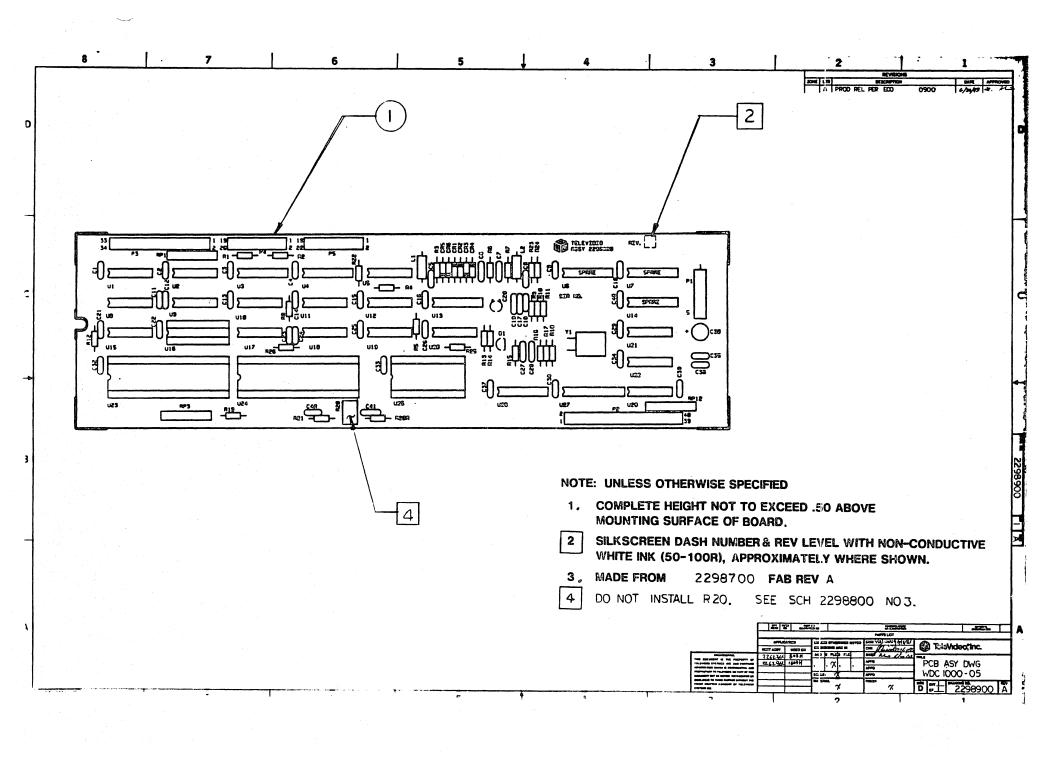

## WINCHESTER DISK CONTROLLER BOARD

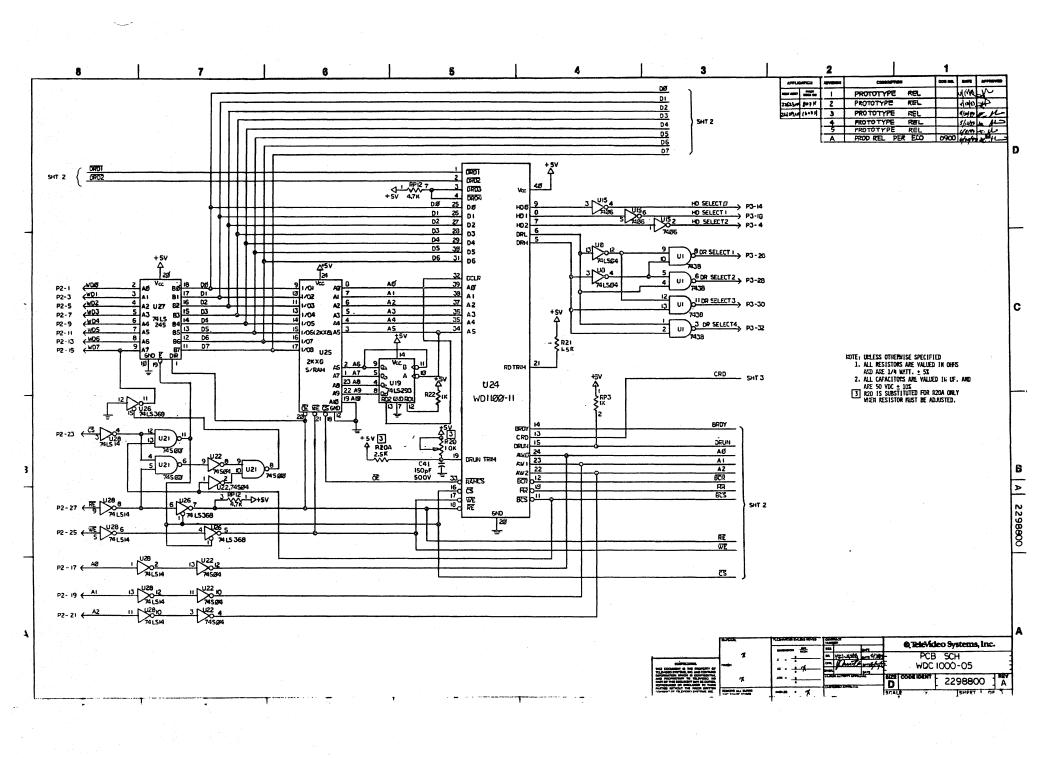

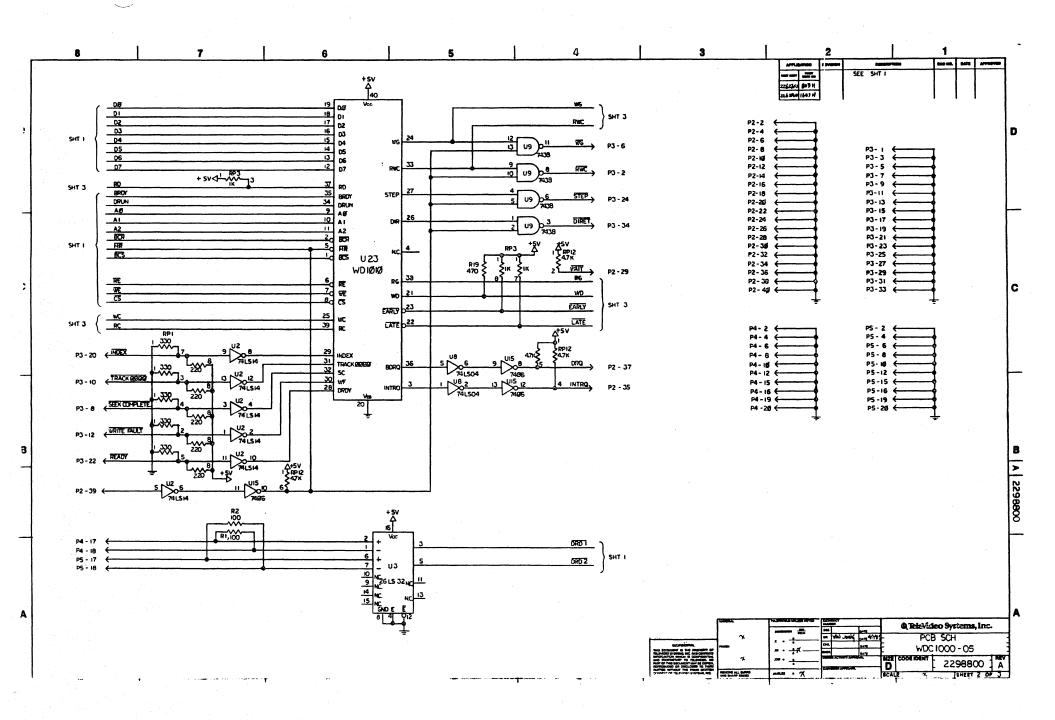

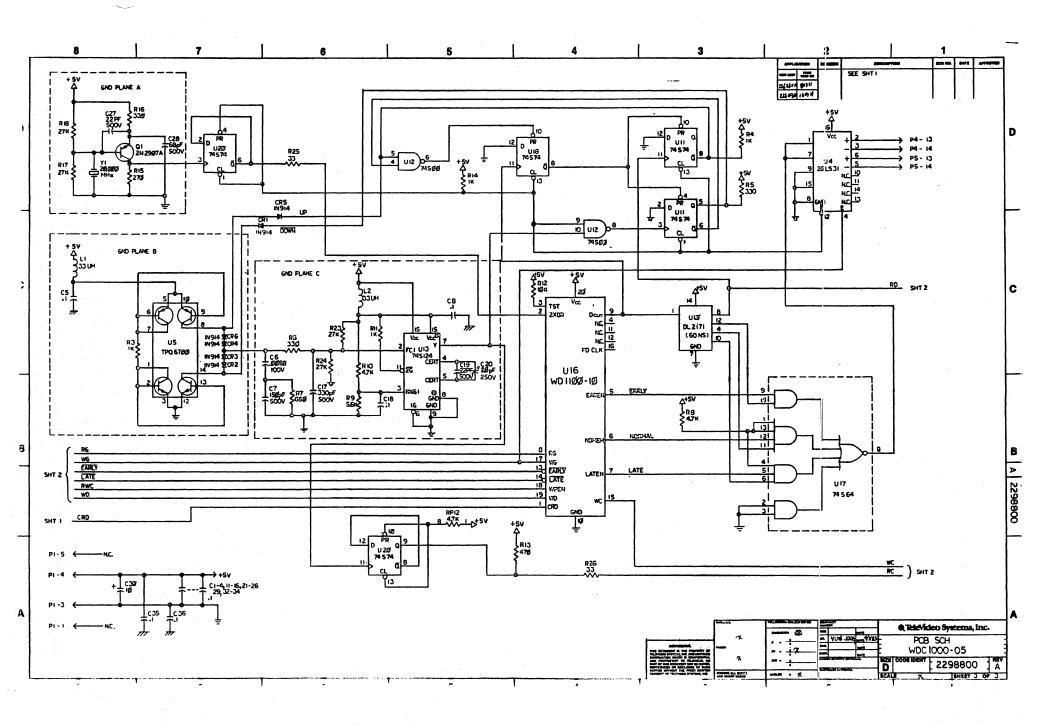

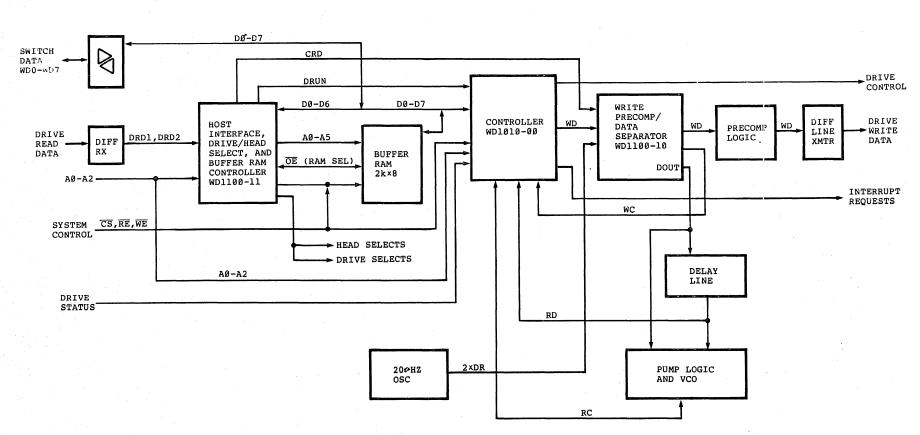

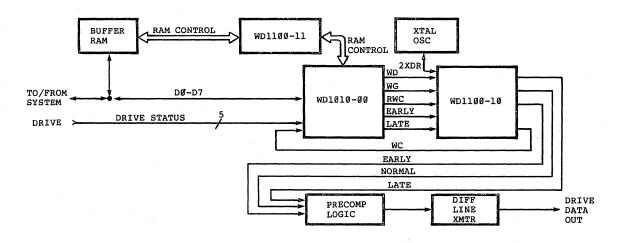

The WD1000-05 Winchester Disk Controller board provides all control and data handling functions needed to interface the system with a 5 1/4-inch Winchester disk drive. Figure 3-12 shows a block diagram of the WD1000-05.

The major components of the WD1000-05 disk controller board are:

| U24         | WD1100-11 Host Interface, Head and Drive Select,   |

|-------------|----------------------------------------------------|

|             | and Buffer Ram Controller                          |

| U23         | WD1010-00 Winchester Disk Controller               |

| U16         | WD1100-10 Write Precompensation and Data Separator |

| U25         | Type 6116 Buffer RAM                               |

| U <b>26</b> | Board Busy Tristate Buffer                         |

| U5          | Error Amplifier                                    |

| U11,U18     | Pump Logic                                         |

| U13         | Voltage Controlled Oscillator (VCO)                |

| U27         | Host Interface Bus Transceiver                     |

| <b>U3</b>   | Differential Line Receiver                         |

| U17         | Precompensation Logic                              |

| U4          | Differential Line Transmitter                      |

|             |                                                    |

TeleVideo Systems, Inc.

Figure 3-12 Winchester Disk Controller Board Block Diagram

TS 803/TS 803H Technical Reference

Circuits

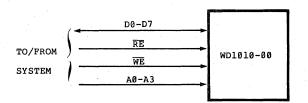

#### System/Controller Interface

The system programs the Winchester controller board by accessing the WD1010-00 controller device Task File registers.

The active lines for the system/controller interface are diagrammed in Figure 3-13 and are listed with a description in Table 3-9.

## Figure 3-13 System/Controller Interface Active Lines

Table 3-9 System/Controller Interface Components

| Active Line Source/Description |                                                                   |           |

|--------------------------------|-------------------------------------------------------------------|-----------|

| A0-A3                          | System. Task file register addres                                 | S.        |

| -WE or -RE                     | SystemWE to activate task file<br>-RE to activate task file read. | write, or |

| D0-D7                          | System. Data or command.                                          |           |

Register addresses and contents are summarized in Chapter 2.

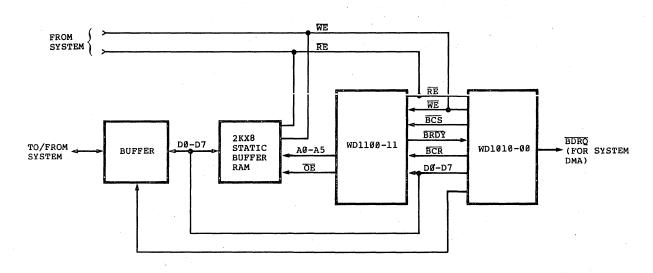

#### **Operations with Buffer RAM**

The Winchester controller board uses a 2 kilobyte-by-8-bit buffer RAM to interact with the system during disk read or write operations. When writing to disk, the system writes the data to the buffer RAM on a sector basis. After a sector of data is loaded into buffer RAM, the WD1010-00 reads the data from the buffer RAM to the disk.

The active lines for the buffer RAM are diagrammed in Figure 3-14 and are listed with a description in Table 3-10.

# Figure 3-14 Buffer RAM Active Lines

```

Table 3-10

Buffer RAM Components

```

| Active Line | Source/Description                                                                                                                                                               |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7       | System. Sets up Write Sector command in<br>WD1010-00 task file and writes data to buffer<br>RAM.                                                                                 |

| -BCR        | WD1010-00. Strobed to zero counter in WD1100-11.                                                                                                                                 |

| BDRQ        | WD1010-00. Active to indicate that the controller has set the drive up to receive data.                                                                                          |

| -BCS        | WD1010-00. Set high to enable host control<br>of buffer RAM. Transceiver direction is<br>ready for write.                                                                        |

| -WE         | System. Loads buffer and increments counter with -CS.                                                                                                                            |

| -BRDY       | WD1100-11. Active to indicate buffer full.                                                                                                                                       |

| INTRQ       | WD1010-00. Signals end of command to system.                                                                                                                                     |

| -BCS        | WD1010-00. Active to disconnect host control<br>of buffer RAM. Board busy tristate buffer on<br>line WD7 is activated by -BCS to prevent<br>system access during next operation. |

| -RE         | WD1010-00. Reads buffer RAM to transfer data to disk (described below).                                                                                                          |

TeleVideo Systems, Inc.

Page 3.23

-BCS

WD1010-00. Set high to allow next operation by system. Board busy tristate buffer inactive.

Reads of buffer RAM occur after a sector of data has been loaded to the RAM from the disk. For a read from buffer RAM, see Table 3-11.

#### Table 3-11 Read from Buffer RAM

| Active Line  | Source/Description                                                                                                                                                                                                                      |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0-D7        | System. Sets up data and Read Sector command in WD1010-00 task file.                                                                                                                                                                    |

| -BCS<br>-BCR | WD1010-00. Active to disconnect host control<br>of buffer RAM. Board busy tristate buffer on<br>line WD7 is activated by -BCS to prevent<br>system access during next operation.<br>WD1010-00. Strobed to zero counter in<br>WD1100-11. |

| -WE          | WD1010-00. Loads buffer from disk (described below), and increments counter with -CS.                                                                                                                                                   |

| BRDY         | WD1100-11. Active to indicate buffer full.                                                                                                                                                                                              |

| -BCR         | WD1010-00. Strobed to zero counter in WD1100-11.                                                                                                                                                                                        |

| -BCS         | WD1010-00. Set high to enable system control<br>of buffer RAM. Board busy tristate buffer<br>inactive.                                                                                                                                  |

| -BDRQ        | WD1010-00. Active to initiate transfer to system.                                                                                                                                                                                       |

| -RE          | System. Reads buffer RAM and increments counter with -CS.                                                                                                                                                                               |

| -BRDY        | WD1100-11. Active to indicate buffer empty.                                                                                                                                                                                             |

| -INTRQ       | WD1010-00. Set high to stop operation.                                                                                                                                                                                                  |

|              |                                                                                                                                                                                                                                         |

Multiple sector writes and reads are handled through a sector count register and multiple sector flag. When this flag is set, the controller re-loads the buffer RAM after each transfer and decrements the register. When the sector count register is zeroed, the controller ends the loop as for a single sector transfer.

#### Writing Disk Data

The write sector command requires that the Winchester controller locate the place on the disk that is to receive the data, control the write operation to buffer RAM by the system, then read the data from buffer RAM, condition the data into MFM format, and write the data to disk.

Under MFM, clock bits are recorded only when two successive data bits are missing in the serial data stream. Using MFM reduces the total number of bits required to record a given amount of information on the disk. Because this effectively doubles the amount of disk capacity, it is termed "double density".

Encoding MFM follows three rules: (a) if the current data cell contains a data bit, then no clock is generated; (b) if the previous data cell contained a data bit, then no clock is generated; (c) if the previous data cell and the present data cell are vacant, then a clock is generated in the current clock cell. Data and clock cells are defined by the state of the write clock line, WC. If WC is low, it is a data cell; if WC is high, it is a clock cell. Both clock and data cells are 100 nanoseconds long in ST506-compatible drives.

The active lines for writing disk data are diagrammed in Figure 3-15 and are listed with a description in Table 3-12.

#### Figure 3-15 Writing Disk Data

Table 3-12 Writing Disk Data

Active Line

## Source/Description

D0-D7

System. Write sector command. The WD1010-00 checks its cylinder registers against the current cylinder position.

Circuits

-BCR

WD1010-00. Strobed to begin write to buffer RAM by system.

BRDY

WD1100-11. Buffer RAM full.

to disk.

-BCS

WD1010-00. Active to disconnect host control of buffer RAM. Board busy tristate buffer on line WD7 is activated by -BCS to prevent system access during next operation.

-STEP,-DIRET WD1010-00. Moves head to locate cylinder.

-SEEK COMPLETE

Drive. Informs WD1010-00 that the head settling time for the current step is expired. If current step is not the required cylinder position, the head is moved again. After seek to desired cylinder, controller checks for desired sector address by reading data from drive.

WD1010-00. Write gate signal to WD1100-10.

WG

-WC

WD1100-10. Carries 5 MHz write clock, derived from 2XDR clock signal, to WD1100-00.

-RWC

-WD

WD1010-00. Write data as read from buffer RAM and serialized by WD1010-00.

WD1010-00. Reduced write current signal;

turns on precompensation circuits for write

-EARLY,-LATE

WD1010-00. Precompensation signals to WD1100-10.

Precompensation is used to counteract the effects of dynamic bit shift when writing the inside recorded tracks of the disk. Dynamic bit shift results when a bit on the disk influences the position of an adjacent bit. The leading edges of the bits are moved closer together, or further apart, depending upon the polarity of each bit. Because the positions of the bits shift as they are written to the disk, the data is harder to recover without error. Write precompensation is applied to counteract the effects of dynamic bit shift.

Precompensation predicts the direction a bit will be shifted, then writes the bit out of position in the opposite direction to the shift. The prediction is done in the WD1010-00 by checking the next two data bits, the last bit written, and the present bit.

| EARLY,NORMAL,<br>LATE | WD1100-10. Precompensation signals to<br>precompensation logic. Data is shifted +/-12<br>nanoseconds from normal position. |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------|

| Data                  | Differential Line Driver. Carries MFM<br>formatted, precompensated, RS-422 write data<br>to drive head.                    |

| -BCS                  | Set high to allow next operation by system.<br>Board busy tristate buffer inactive.                                        |

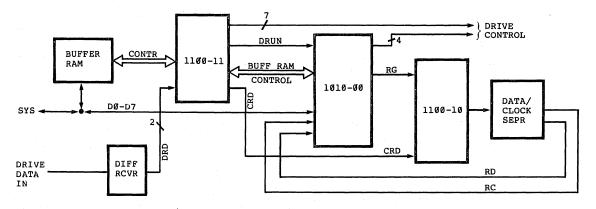

## Reading Disk Data

For disk reads, the Winchester disk controller board locates the sector to be read, identifies the start of the data field, reads the data in from the disk, separates the data and clock signals, writes the data to buffer RAM, and controls the system read of the data out of buffer RAM.

The active lines for reading disk data are diagrammed in Figure 3-16 and are listed with a description in Table 3-11.

## Figure 3-16 Reading Disk Data

Table 3-13 Disk Data

Active Line

#### Source/Description

D0-D7

System. Read sector command. The WD1010-00 checks its cylinder registers against the current cylinder position.

-BCS

WD1010-00. Active to disconnect host control of buffer RAM. Board busy tristate buffer on line WD7 is activated by -BCS to prevent system access during next operation.

Circuits

-STEP, -DIRET

WD1010-00. Moves head to locate cylinder.

-SEEK COMPLETE

Drive. Informs WD1010-00 that head settling time for the current step has expired. If current step is not the required cylinder position, the head is moved again. After seek to desired cylinder, controller checks for desired sector address by reading data from drive.

-DRD1,-DRD2

Differential Data Receiver. Carries differential data from drive.

CRD

DRUN

WD1100-10. Composite read data.

WD1100-11. Output of internal one-shot that retriggers on data field. When DRUN is counted high for 2 consecutive bytes, the ID field must be found within the next 8 disk revolutions, or an error is signalled. When the ID field is found, an address mark (AM) must be found within 15 bytes of the end of the data field. If the AM is not found in eight retries, an error is signalled.

-RG

WD1010-00. Set low to begin read of data from disk. This line may also be lowered for two byte times during the search for the AM to allow WD1010-00 to re-lock to the reference clock.

An address mark (AM) identifies the start of a field of information within each sector of data. The WD1010-00 looks for the AM pattern, consisting of the data pattern %AI, with a missing clock pattern %OA. According to the rules of MFM encoding, the data byte %Al requires a missing clock pattern of %OE, so the address mark can only be on disk by design.

Dout

RD

WD1100-10. Carries data to phase detector and VCO to separate read data and clock signals.

WD1100-10. Read data signal.

VCO. Read clock signal.

RC

-BCR

-BCS

WD1010-00. Strobed to begin write of data to buffer RAM by WD1010-00.

Set high to allow next operation by system. Board busy tristate buffer inactive. INTRQ

WD1010-00. Set high to indicate that buffer RAM is full and system may initiate read.

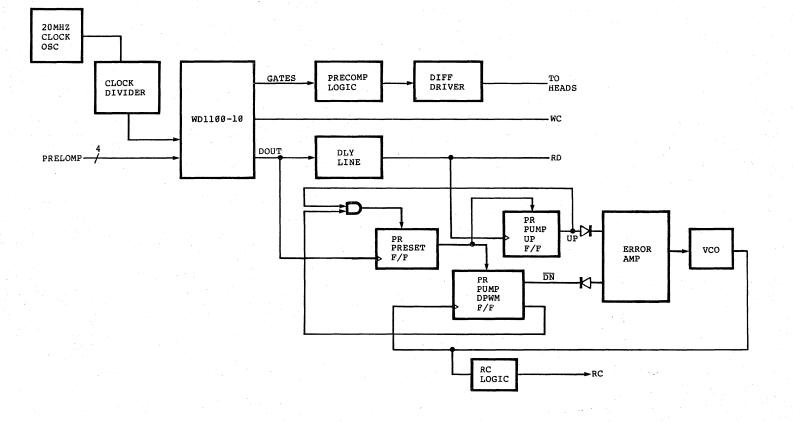

#### Pump Logic and VCO

Using MFM, the board circuits must remain in synchronization with the data without clock bits on every data bit. The pump logic and VCO circuits synthesize clock bit timing when the clocks are present, and synchronize to clock bits when they are present. The synthesized clock, RC, is used as the read clock for the WD1010-00.

The VCO is held locked to the Dout signal of the WD1100-10 through the pump logic. This circuit is essentially a threestate machine that operates in a continuous loop around pump-up, reset, and pump-down. A block diagram of the pump logic and VCO is shown in Figure 3-17.

Assuming an initial state of preset, all -Q outputs of the circuit are set low. This produces a low state at the UP line, and a high state at the -DOWN line. When a data bit at the Dout pin of the WD1100-10 clocks the preset flip-flop, it sets the pump flip-flop preset signals high. If a delayed data bit clocks the pump-up flip-flop first, the UP line gets toggled low, causing a pump up error voltage. If a VCO bit clocks the pumpdown flip-flop first, the -DOWN line gets toggled low, causing a pump down error voltage. If both signals arrive simultaneously, both flip-flips are toggled and the net error voltage is zero. Coincident signals give a toggle to the preset flip-flop to place the circuit into its initial state.

During write data operations, and when the board is idle, the data rate of the WD1100-10 is the write data rate, derived from the crystal-controlled oscillator 2XDR signal. Because this presents a stable signal at the Dout pin of the WD1100-10, the circuit tends to idle in a loop around the three states. The net average frequency of the VCO at this time is slightly below the write data rate.

During read data operations, the data rate at the Dout pin varies according to disk speed, media inconsistencies, and other variables. Now the VCO signal makes wider variations in the same loop as it tracks the data rate.

The pump signals are presented to an error amplifier, which generates voltage variations of between 1.7 and 3.3V for extreme pump-down and pump-up conditions. This produces a net VCO frequency of 10.0000 MHz +/-.0005 MHz. The VCO output signal is divided to produce a read clock for the WD1010-00.

Figure 3-17 Pump Logic and VCO Block Diagram

TeleVideo Systems, Inc.

Page 3.30

### 4. SYSTEM MAINTENANCE

The TS 803 and TS 803H contain self test diagnostics that are automatically run during system initialization at power-up. These diagnostics light LED indicators on the system board and send messages to the video monitor. When the tests are completed successfully, the system reads the status switches to determine the bootstrapping device. Successful conclusion of the tests and bootstrapping procedure is indicated when the system prompt is shown on the video monitor. The diagnostic LED indicators are not visible with the system case closed.

A special set of diagnostics for the system is available from TeleVideo. These diagnostics provide a more detailed check of the system, with error messages that closely isolate a malfunction.

#### INITIALIZATION AND SELF-TEST DIAGNOSTICS

At power-on, the system executes a hardware reset of all major components, including the CPU, CRT controller, STI, DART, RS-422 option board, floppy disk controller, and Winchester controller board. The CPU jumps to location %0000 to obtain a vector to the initialization and self-test diagnostic routine.

The first test is a memory test. The upper 1 kilobyte of main memory is tested by writing in an incrementing pattern and then reading the pattern back. If the pattern is read back correctly, a memory test is loaded into this area from system ROM. The memory test checks the rest of main memory with the same test: writing in an incrementing pattern, then reading the pattern back. During this test diagnostic LED 1 is lit. Failure of the memory test is indicated by the message:

Hardware Error: (Memory); Contact Distributor

The CPU stops executing the diagnostics and diagnostic LED 1 remains lit. Successful completion is signalled when LED 1 goes out and the system moves to the next routine.

The system shifts back to ROM for the remainder of the procedure. The CRT controller is now initialized into alpha mode, the rear panel switch is read for line frequency, and the controller is set for an 80 x 24-line display.

#### Maintenance

Next, the STI device is tested by writing a pattern into some of its data registers, and reading the pattern back. During this test diagnostic LED 2 is lit. Failure of the STI test is indicated with the message:

Hardware Error: (STI); Contact Distributor

The CPU stops executing the diagnostics and LED 2 remains lit. Successful completion is signalled when LED 2 goes out and the system moves to the next procedure.

The STI is then initialized. The UART is set for asynchronous mode, the rear panel baud rate switches are read and the timer set accordingly, and interrupts are disabled. The interrupts are disabled to allow the tests to run fully. They must be reenabled by system software at the conclusion of the procedure.

Next, the DART is initialized. Channel B is set asynchronous, with its baud rate coming from the STI timer, and channel A is set asynchronous with its baud rate derived from system clock.