## Please Check for CHANGE INFORMATION at the Rear of this Manual

INTERACTIVE DIGITAL PLOTTER

4663

SERVICE MANUAL

Tektronix, Inc. P.O. Box 500 Beaverton, Oregon 97077

MANUAL PART NO. 070-2669-00 PRODUCT GROUP 12 First Printing AUG 1980 Revised JUN 1983 Ł

# WARNING

THE FOLLOWING SERVICING INSTRUCTIONS ARE FOR USE BY QUALIFIED PERSONNEL ONLY. TO AVOID PERSONAL INJURY, DO NOT PERFORM ANY SERVICING OTHER THAN THAT CONTAINED IN OPERATING INSTRUCTIONS UNLESS YOU ARE QUALIFIED TO DO SO.

> Copyright © 1980 by Tektronix, Inc., Beaverton, Oregon. Printed in the United States of America. All rights reserved. Contents of this publication may not be reproduced in any form without permission of Tektronix, Inc.

> This instrument, in whole or in part, may be protected by one or more U.S. or foreign patents or patent applications. Information provided on request by Tektronix, Inc., P.O. Box 500, Beaverton, Oregon 97077

TEKTRONIX is a registered trademark of Tektronix, Inc.

## MANUAL REVISION STATUS

## PRODUCT: 4663 and 4663S Interactive Digital Plotters

This manual supports the following versions of this product: Serial Numbers B010100 and up.

|   | REV DATE | DESCRIPTION                                                                                                                                                   |  |  |

|---|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   | AUG 1980 | Original Issue                                                                                                                                                |  |  |

|   | MAR 1981 | Revised: page 2-1.                                                                                                                                            |  |  |

|   | JUL 1981 | Revised: pages ii, iii, vi, vii, 3-27 and 3-35.                                                                                                               |  |  |

|   | SEP 1981 | Revised: pages 3-30 and 3-36                                                                                                                                  |  |  |

|   | NOV 1981 | Revised: pages 3-14 and 3-15.                                                                                                                                 |  |  |

|   | MAY 1982 | Revised: page 2-8.                                                                                                                                            |  |  |

|   | JUL 1982 | Revised: page 1-1.                                                                                                                                            |  |  |

|   | JUN 1983 | Revised: pages ii, iii, iv, v, vi, vii, viii, 1-3, 2-2, 2-6, 2-8, 2-9, 3-2, 3-25 through 3-63,<br>4-1 through 4-5, A-3, A-6, A-7, A-9 through A-12, and A-16. |  |  |

|   | JUN 1983 | Deleted: pages 3-64 through 3-67, 4-6, and 4-7.                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

|   |          |                                                                                                                                                               |  |  |

| L |          |                                                                                                                                                               |  |  |

# CONTENTS

| Section 1 |                                        | Page |

|-----------|----------------------------------------|------|

|           |                                        |      |

|           | About This Manual                      |      |

|           | General Description                    |      |

|           | Specifications                         | 1-2  |

| Section 2 | PREVENTIVE MAINTENANCE AND CALIBRATION |      |

|           | Preventive Maintenance                 | 2-1  |

|           | General                                | 2-1  |

|           | Cleaning the Platen and the Case       | 2-1  |

|           | Lubrication Information                |      |

|           | Pen Drive Cable Checks                 |      |

|           | Adjustment and Calibration Procedures  |      |

|           | Introduction                           |      |

|           | Equipment Required                     |      |

|           | Preliminary Steps                      |      |

|           | X-Axis Cable Adjustments               |      |

|           | Y-Axis Cable Adjustment                |      |

|           | Power Supply Adjustment                |      |

|           | X-Axis Limit Switch Adjustment         |      |

|           | Y-Axis Limit Switch Adjustment         |      |

|           | Carriage Height Adjustment             |      |

|           | Measuring Platen Electrostatic Voltage |      |

|           | Processor Timing Checks                |      |

|           | Pen-to-Pen Registration Check          |      |

|           | Orthogonality Check                    |      |

|           | Lamp Test                              |      |

|           | Line Quality and Accuracy Check        | 2-12 |

|           | Joystick Operational Check             | 2-12 |

|           | Media Advance Clutch Tension Check     | 2-12 |

|           | Media Advance Adjustments              | 2-12 |

| Section 3 | THEORY OF OPERATION                    |      |

| Section 5 | System Description                     | 3-1  |

|           | Backplane (Central Bus)                |      |

|           | Inter-Functional Block Communications  |      |

|           | Protocol                               |      |

|           | Read Cycle Description                 |      |

|           | Write Cycle Description                |      |

|           | Interrupt Operation                    |      |

|           | Bus DMA Operation                      |      |

|           | I/O Addressing                         |      |

|           | The Processing of Commands             |      |

|           | Pen Movement Commands                  |      |

|           | Interface Commands                     |      |

|           | Transform-Modifying Commands           |      |

|           | Response-Invoking Commands             |      |

|           | Front Panel Switch Commands            |      |

|           |                                        |      |

-0

### Section 3 (cont)

2

| Circuit Descriptions                |  |

|-------------------------------------|--|

| Introduction                        |  |

| Processor and Memory 3-12           |  |

| Processor Functional Block          |  |

| 6800 Processor                      |  |

| Bus Buffers and Transceivers        |  |

| Timing and Processor/Bus Handshake  |  |

| Timing and Processor/Bus Handshake  |  |

| (Early Version)                     |  |

| IRQ Vectoring                       |  |

| DMA Bus Control                     |  |

| Bus Transaction Timer               |  |

| Miscellaneous Interface/Parameter   |  |

| Entry I/O                           |  |

| Memory Functional Block             |  |

| Bus Interface                       |  |

| RAM                                 |  |

| CMOS RAM                            |  |

| ROM                                 |  |

| Memory Handshake                    |  |

| PROM                                |  |

| ROM Memory Size Decode              |  |

| PROM Memory Size Decode             |  |

| Parameter Entry Functional Block    |  |

| ROM Patch "B" Functional Block      |  |

| Communications Interface            |  |

| RS-232-C Interface                  |  |

| Bus Data and Address Transceivers   |  |

| Decode                              |  |

| GPIB/RS-232 ROM                     |  |

| Bus Handshake                       |  |

| GPIB/RS-232 Interrupt               |  |

| RS-232 Interface                    |  |

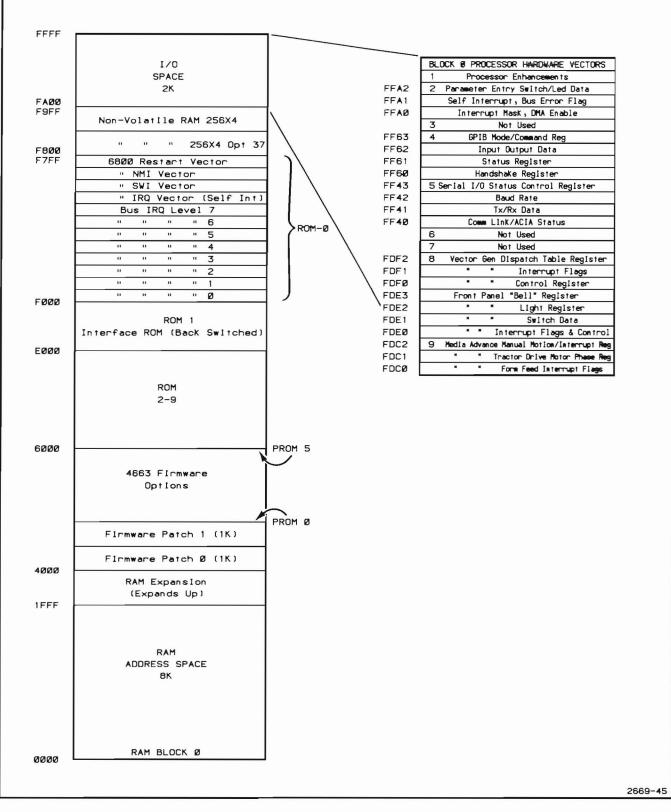

| Terminal-ACIA-Modem Connection      |  |

| Baud Rate Generator                 |  |

| GPIB                                |  |

| General Information                 |  |

| Data Bus (and Read/Write Registers) |  |

| Management Bus                      |  |

| Transfer Bus                        |  |

| Handshake Sequence                  |  |

| RS-232-C Adapter                    |  |

### Section 3 (cont)

| Vector Generator                          |        |

|-------------------------------------------|--------|

| Front Panel Switches and Lights Interface |        |

| Address Decode                            |        |

| Bus Handshake                             |        |

| Bus Transceiver                           |        |

| Switch Change Logic.                      | 3-38   |

| Front Panel Interrupt                     | 3-40   |

| Light Enable Latch                        | 3-40   |

| Parallel-In/Serial-Out Shift Register     | 3-40   |

| Light Data Clock                          | 3-40   |

| Bell Latch                                | 3-40   |

| Motion Generation Interface               |        |

| General Operating Scheme                  |        |

| 8X300 Microprocessor                      |        |

| Right Bank Hardware RAM Copy/Right        |        |

| Decoder                                   | 3-43   |

| Left Memory Bank                          |        |

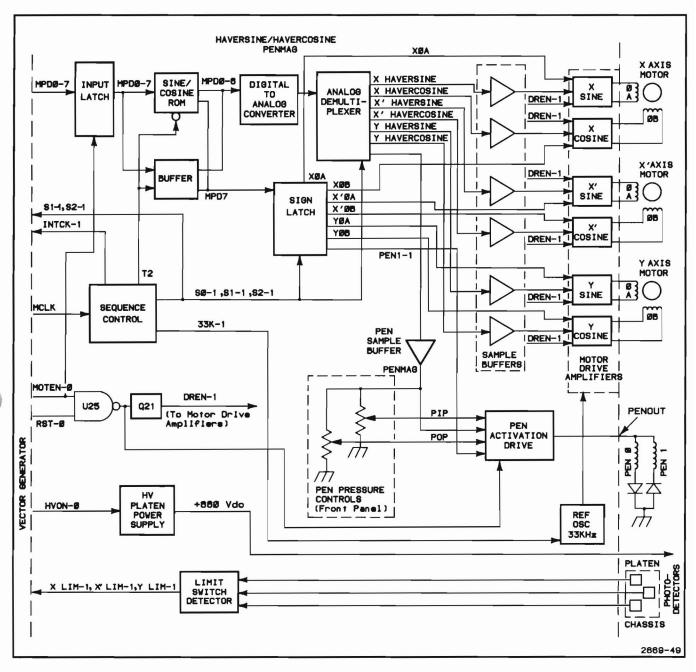

| Motor Pen Drive                           |        |

| Motor Pen Drive Operation Sequence        |        |

| Input Latch                               |        |

| Sine/Cosine ROM                           |        |

| Buffer                                    |        |

| Digital-to-Analog Converter               | 3.49   |

| Analog Demultiplexer                      |        |

| Sequence Control                          |        |

| Sign Latch                                |        |

| Sample Buffers                            |        |

| Motor Pen Drive Amplifiers                |        |

| •                                         |        |

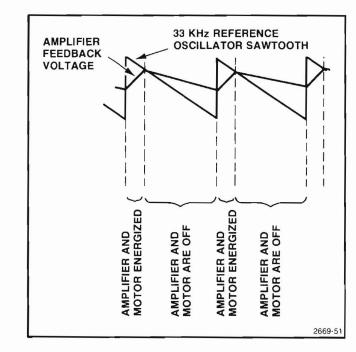

| Reference Oscillator                      |        |

| Pen Activation Drive                      |        |

| Limit Switch Detector                     |        |

| High Voltage Platen Power Source          |        |

| Front Panel Switches and Lights           |        |

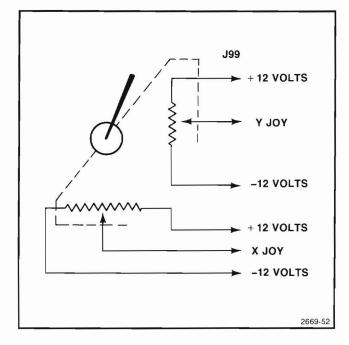

| Joystick Rate Generator                   |        |

| Power Supply                              |        |

| General Power Supply Operation            |        |

| Line In                                   |        |

| Ac to Dc                                  |        |

| Control Power Supply                      | 3-58   |

| Inverter Control Logic/On-Off             |        |

| Switching Transistors and Transformer     |        |

| +5 V Inverter Output                      |        |

| Rectifiers/Filters/Internal Supply        |        |

| +12, -5, and -12 V Linear Regulators      |        |

| Fault Circuit                             |        |

| 60 Watt Auxiliary Board                   |        |

| Fan Regulator Circuit Board               |        |

| ROM Overlay Circuit Board                 | . 3-63 |

Page

| Section 4  | CIRCUIT DESCRIPTIONS OF OPTIONS Page           |

|------------|------------------------------------------------|

|            | About This Section4-1                          |

|            | Option 1 — Standard Plotter (Including RS-232) |

|            | Plus GPIB                                      |

|            | Option 4 — GPIB Only4-3                        |

|            | Option 30 — 4081 Interface                     |

|            | Option 31 — Circular Interpolation and         |

|            | Macros                                         |

|            | Option 32 — Downloadable Characters            |

|            | and Math                                       |

|            | Option 36 — Media Advance4-4                   |

|            | Address Decode4-4                              |

|            | Joystick Interface4-4                          |

|            | IRQ4-4                                         |

|            | Motor Drive4-5                                 |

|            | Out-of-Paper Detector                          |

|            | Option 37 — Additional Parameter Entry         |

|            | Set-Up Memory                                  |

|            | Option 48 — 220 V @ 50 Hz Operation 4-7        |

| Appendix A | SIGNAL DESCRIPTIONS                            |

| Appendix B | COMMAND SUMMARY                                |

Appendix C ERROR CODES

# TABLES

| Table | Description Page                                  |

|-------|---------------------------------------------------|

| 1-1   | 4663 Option Summary1-3                            |

| 1-2   | Accessories1-3                                    |

| 1-3   | Physical Characteristics 1-4                      |

| 1-4   | Power Requirements1-4                             |

| 1-5   | Environmental Specifications1-4                   |

| 1-6   | Performance Specifications1-5                     |

| 1-7   | Page Sizes (Full Page Aspect Ratio)               |

| 3-1   | I/O Block Assignments (F7FF to FFFF)              |

| 3-2   | ROM 0 Interrupt Service Routine Locations         |

| 3-3   | ROM Content                                       |

| 3-4   | EPROM/ROM Comparison                              |

| 3-5   | Communications Interface Board EPROM/ROM          |

|       | Placement                                         |

| 3-6   | RS-232 Registers 3-27                             |

| 3-7   | Bit Assignments for RS-232 Registers              |

| 3-8   | RSCTRL Register (ACIA)                            |

| 3-9   | D5 and D6 Bits of RSCTRL Register (ACIA)          |

| 3-10  | D2, D3, and D4 Bits of RSCTRL Register (ACIA)3-31 |

| 3-11  | D0 and D1 Bits of RSCTRL Register (ACIA)          |

| 3-12  | RSSTUS Register (ACIA)                            |

| 3-13  | BAUDWR (Write-Only)                               |

| 3-14  | U951 Hex Codes for Baud Rate Generation           |

| 3-15  | GPIB Interface Read/Write Registers               |

| 3-16  | Bit Assignments for GPIB Registers                |

| 3-17  | Management Bus Signal Lines                       |

| 3-18  | Transfer Bus Signal Lines                         |

| 3-19  | 8X300 Memory Map                                  |

| 3-20  | Front Panel Switch Addresses                      |

| 4-1   | Motor Drive Register Update                       |

|       | Information                                       |

| 4-2   | Media Advance Registers                           |

| A-1   | Signal DefinitionsA-1                             |

01

46

# **ILLUSTRATIONS**

| Figure     | Description                                     | Page |

|------------|-------------------------------------------------|------|

| 1-1        | 4663 Interactive Digital Plotter                | . ix |

| 1-2        | Horizontal and Vertical Page Orientations       |      |

|            | for English Page Sizes (Drafting)               | 1-7  |

| 1-3        | Horizontal and Vertical Page Orientations       |      |

| 8 - 54     | for Metric Page Sizes (Drafting)                | 1-8  |

| 1-4        | Horizontal and Vertical Page Orientations       |      |

|            | for English Page Sizes (Graphing)               | 1-9  |

| 1-5        | Horizontal and Vertical Page Orientations       |      |

| 2-1        | for Metric Page Sizes (Graphing)                |      |

| 2-1        | Side Panel Quarter-Turn Latches                 |      |

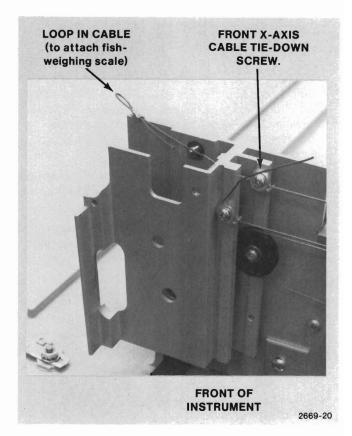

| 2-2        | Front X-Axis Cable Tie-Down Screw and           | .2-3 |

| 2-0        | Loop Detail                                     | 2-3  |

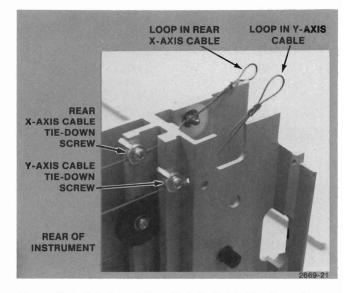

| 2-4        | Y-Axis and Rear X-Axis Cable Tie-Down Screw and |      |

|            | Loop Detail                                     |      |

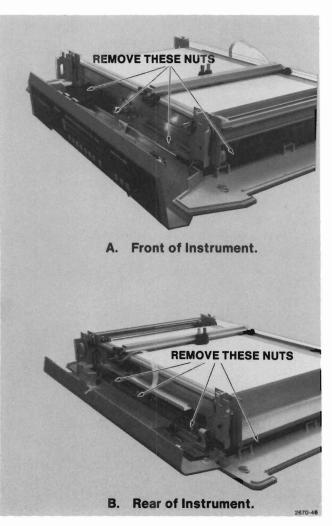

| 2-5        | Nuts Holding the Pen Drive Mechanism            |      |

|            | Assembly                                        |      |

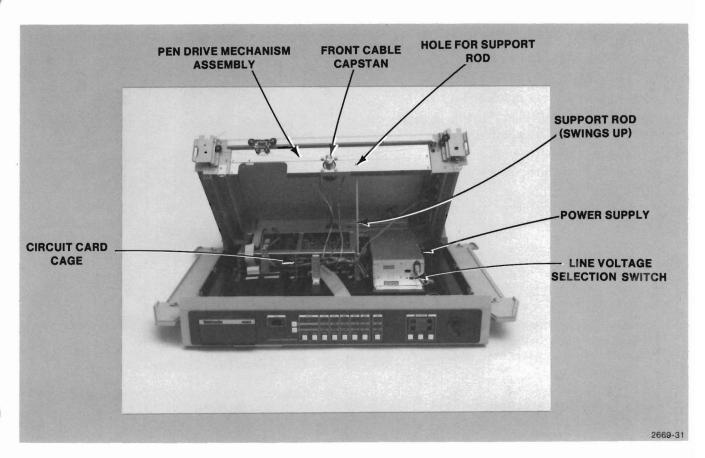

| 2-6        | Access to the Plotter's Electrical Circuitry    |      |

| 2-7        | Joystick Adjustment                             | .2-6 |

| 2-8        | X-Axis Limit Switch Calibration Fixture         |      |

|            | Placement                                       |      |

| 2-9        | X-Axis Limit Switch Detail                      | .2-8 |

| 2-10       | Y-Axis Limit Switch Calibration Fixture         |      |

| 0.11       | Placement                                       |      |

| 2-11       | Platen Electrostatic Voltage Test Points        |      |

| 2-12       | Test Pattern Produced by Self-Test Feature      |      |

| 3-1<br>3-2 | Functional Block Diagram of the 4663 Plotter    |      |

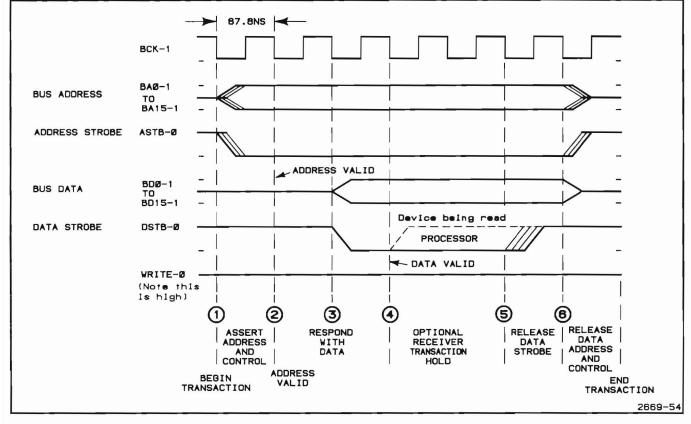

| 3-3        | Bus Read Transaction Timing                     | 3-4  |

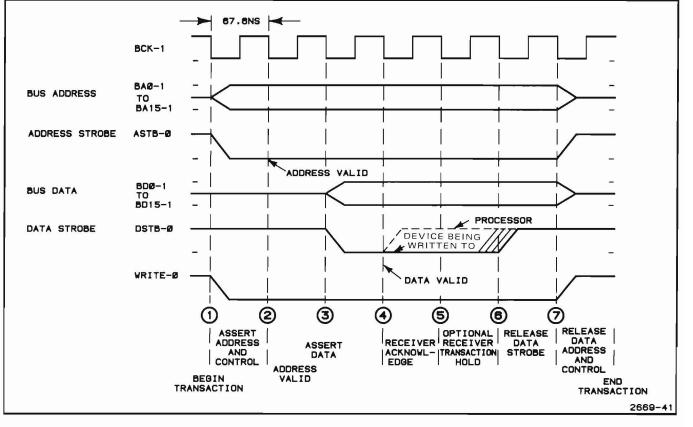

| 3-4        | Bus Write Transaction Timing                    |      |

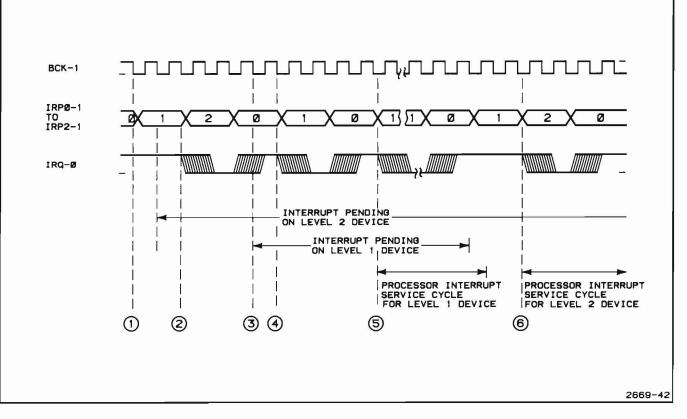

| 3-5        | Bus Interrupt Timing Diagram                    |      |

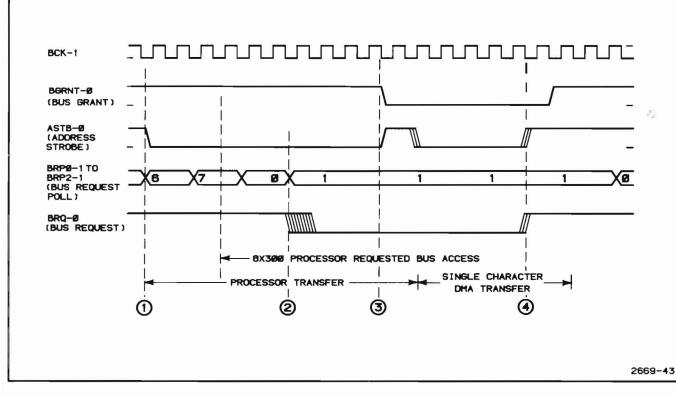

| 3-6        | Bus Character DMA Timing Diagram                |      |

| 3-7        | Processor/Memory Functional Block Diagram       |      |

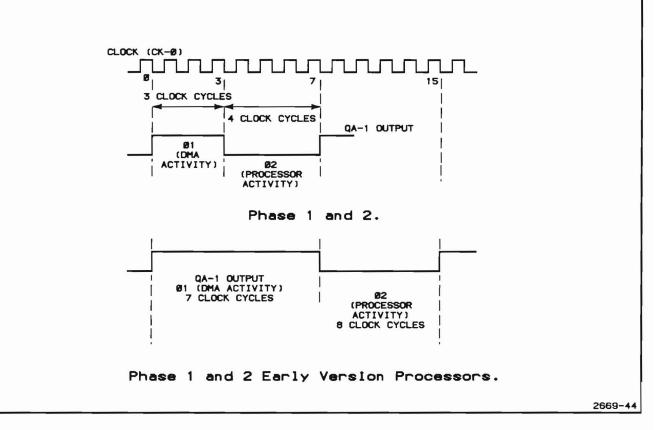

| 3-8        | Phase 1 and Phase 2 Clock                       |      |

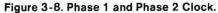

| 3-9        | Memory Map for the 4663 Plotter                 |      |

| 3-10       | Terminal-Plotter-Modem RS-232 Connection        |      |

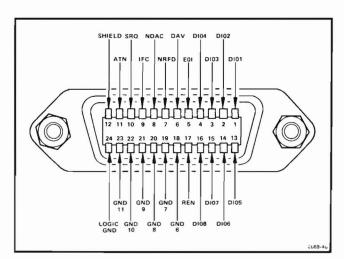

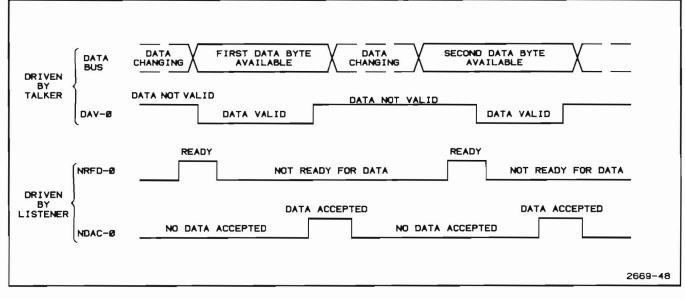

| 3-11       | GPIB Connector                                  |      |

| 3-12       | GPIB Handshake Sequence                         | 3-36 |

R

| Figure | Description                                 | Page   |

|--------|---------------------------------------------|--------|

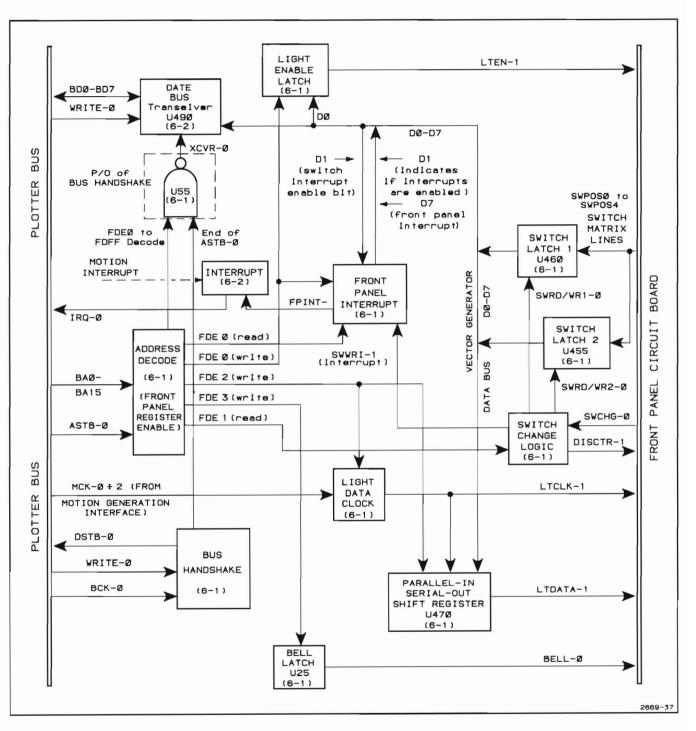

| 3-13   | Front Panel Interface Portion of the Vector |        |

|        | Generator                                   | .3-29  |

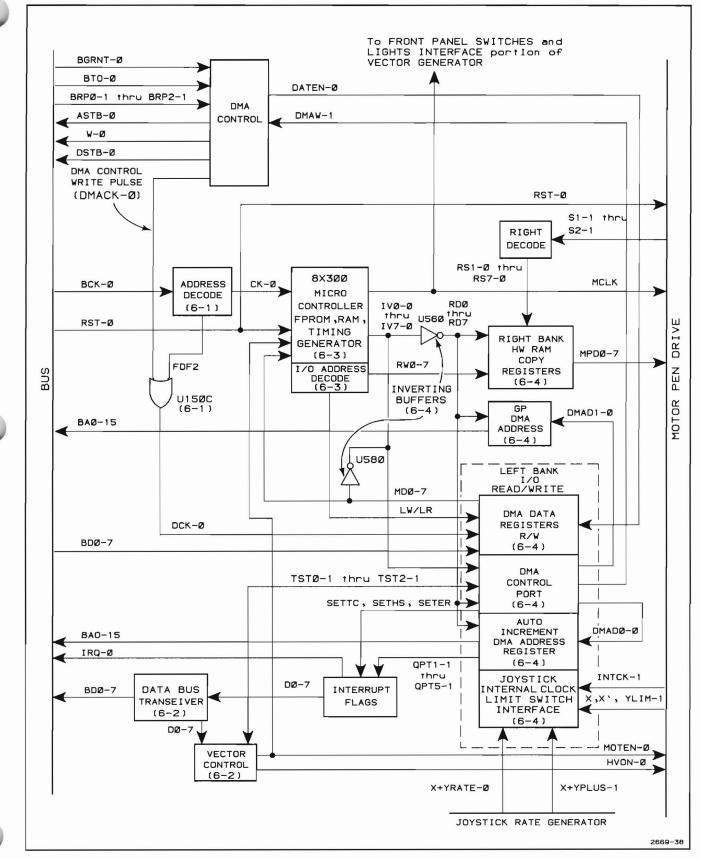

| 3-14   | Motion Generation Interface Portion of the  |        |

|        | Vector Generator                            | .3-41  |

| 3-15   | Motor Pen Drive Block Diagram               | . 3-47 |

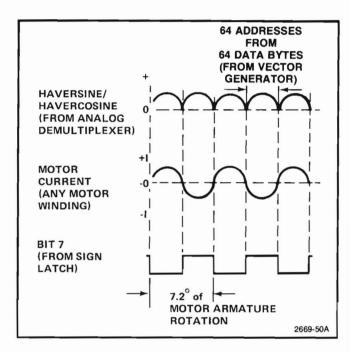

| 3-16   | Motor Drive Amplifier Signals               | .3-49  |

| 3-17   | Motor Drive Amplifier Comparator Inputs     | .3-50  |

| 3-18   | Joystick Connection                         |        |

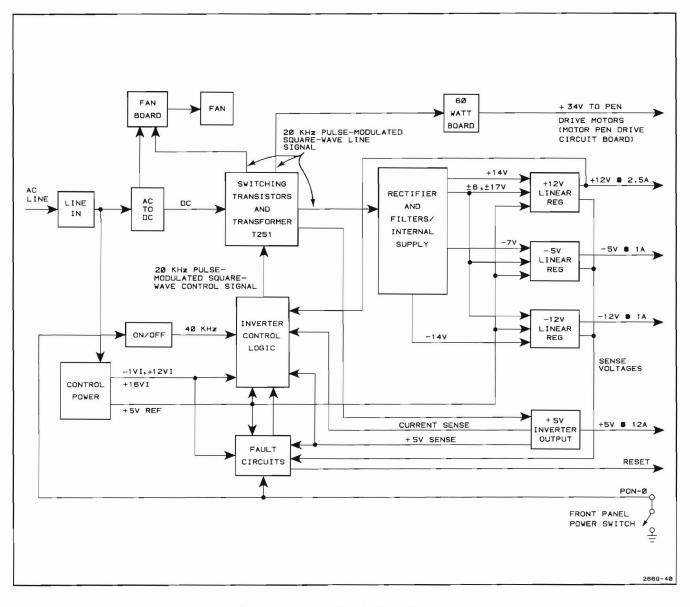

| 3-19   | Power Supply Block Diagram                  | .3-56  |

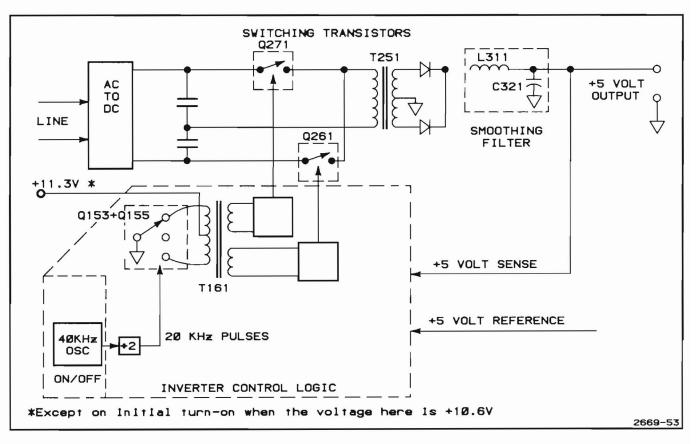

| 3-20   | +5 V Power Supply Regulation                |        |

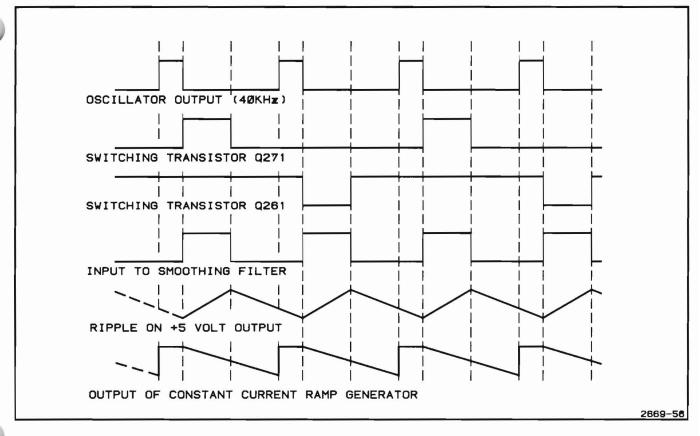

| 3-21   | Power Supply Waveform Summary               |        |

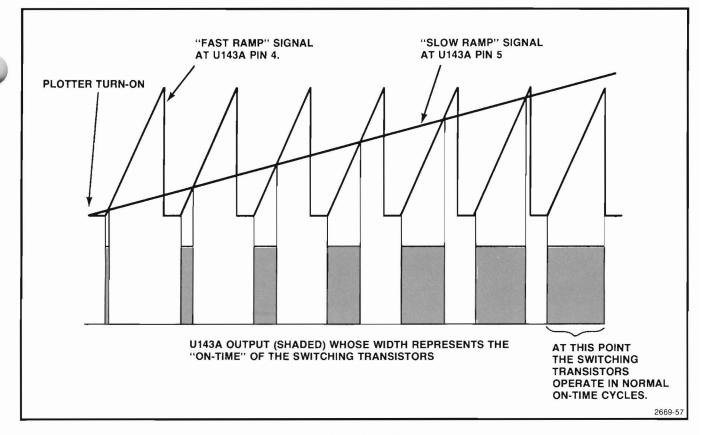

| 3-22   | Soft Start Waveforms                        | .3-61  |

-

-

0

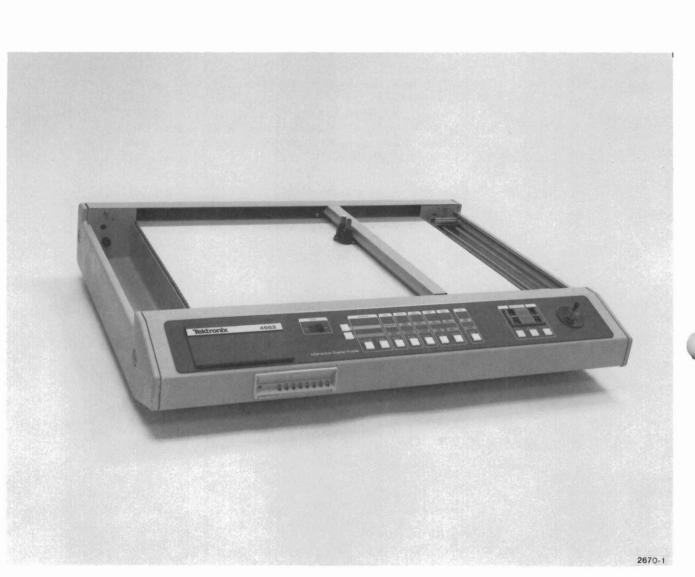

Figure 1-1. 4663 Interactive Digital Plotter.

# Section 1

# SPECIFICATIONS

## INTRODUCTION

The TEKTRONIX 4663 (and 4663S—see 4663 Operator's Manual) Interactive Digital Plotter, (Figure 1-1) is capable of dual-pen graphic recording from digital source devices. The standard 4663 Plotter is equipped with a RS-232-C Communications Interface, enabling it to be used with Tektronix terminal-based systems. In addition, an optional interface is available to connect the Plotter to devices having a GPIB (IEC)<sup>1</sup> interface (such as the TEKTRONIX 4050 Series Graphic System).

The X- and Y-axes of the Plotter are controlled by splitphase synchronous ac motors (two motors in the Xaxis and one motor in the Y-axis). These motors control the movement of a pen carriage containing two pens through a system of cables and pulleys. The internal circuitry converts external commands into appropriate vector movements. The two-pen carriage permits multicolor graphics or graphics with multiple pen types. (Note that only one pen can draw at any instant.) The pen carriage also contains a crosshair cursor, which can be used to optically check or align plotted points and for digitizing.

The 4663 will draw on a variety of media in sheets up to 17 x 22 in (431.8 x 558.8 mm). In addition, a media advance option is available (Option 36) to automatically advance a roll of paper. This option uses a 200 ft roll of paper up to 18 in wide with 1/2 in tear-off strips (containing sprocket holes) on each side. Sheet paper is held in position by electrostatic attraction generated by the platen and roll paper is held in position mechanically by the paper advance mechanism.

<sup>1</sup> The GPIB Interface is defined in IEEE Standard 488-1975: IEEE Standard Digital Interface for Programmable Instrumentation.

The 4663 offers high quality resolution and plotting capabilities using a variety of pen types, media, and page/viewport sizes. The most basic Plotter operation is graphics — the moving of the pen carriage across the plotting surface, the lifting and lowering of either pen to produce written vectors. The Plotter can also print alphanumeric characters in any resident fonts. In addition, the Plotter can act as a digitizer, transmitting the coordinate position of the active pen along with pen status (up or down). Several user-definable variations of each recording operation can be used to increase the versatility of the Plotter. The variations include the following:

- modification of the size of the plotting area,

- scaling the plots,

- manual pen positioning using the joystick,

- rotation of the plot,

- alteration of the axes and character dimensions,

- point digitizing,

- choice of plotting speeds and pen pressures,

- use of programmable macros and,

- the initiation of a self-test.

Actual implementation of these variations differs according to the interface being used. Several userdefined variations can be conveniently introduced via a front panel Parameter Entry card. Parameters selected in this manner remain stored in the Plotter for up to 90 days, even when the Plotter is turned off.

#### SPECIFICATIONS

## **ABOUT THIS MANUAL**

The service documentation for the 4663 Interactive Digital Plotter consists of two volumes. Volume 1 (this volume) contains the Plotter's specifications, preventive maintenance procedures (including detailed calibration instructions), circuit descriptions, signal descriptions, error codes, and a Plotter interface command summary. Volume 2 contains a short form calibration procedure, assembly/dissembly procedures for replacing parts, interconnecting cable diagrams, electrical and mechanical parts lists, schematics, strapping tables, instrument and option installation procedures, and diagrams of circuit board component locations.

For detailed troubleshooting procedures, consult the 4663 Diagnostic Test Fixture Instruction Manual (see Section 8 of Volume 2).

## **GENERAL DESCRIPTION**

The 4663's internal circuitry includes a 6800 and an 8X300 microprocessor. The 6800 microprocessor oversees all general aspects of the Plotter's operation. These include storing commands, communicating with the host computer, accepting front panel commands (including Parameter Entry), etc. The 8X300 microprocessor, on the other hand, controls the generation of motor pen drive signals (including the pen lifters) using information supplied by the 6800 microprocessor.

## SPECIFICATIONS

The remainder of this section contains a series of tables summarizing the physical properties, the electronic specifications, and the performance characteristics of the 4663 Interactive Digital Plotter. The following tables are included:

- Table 1-1 4663 Option Summary

- Table 1-2 Accessories

- Table 1-3 Physical Characteristics

- Table 1-4 Power Requirements

- Table 1-5 Environmental Specifications

- Table 1-6

Performance Specifications

- Table 1-7 Page Sizes (Full Page Aspect Ratio)

#### **Option Summary**

The standard instrument contains an RS-232-C interface with Full Duplex capability. Table 1-1 lists the options which can be added to the instrument. Notice that the Plotter can be equipped with only one serial interface at a time.

#### SPECIFICATIONS

#### Table 1 -1 4663 OPTION SUMMARY

| Option | Name                                                       | Description                                                                                                                              |  |

|--------|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1      | GPIB<br>Interface                                          | Provides communications with<br>GPIB instruments, such as the<br>TEKTRONIX 4050 Series Con-<br>troller.                                  |  |

| 4      | GPIB<br>Interface<br>Only                                  | Same as Option 1, except that the standard RS-232 interface is removed.                                                                  |  |

| 30     | RS-232<br>Interface<br>to Tektronix<br>4081                | Permits the Plotter to be con-<br>nected to the TEKTRONIX<br>4081 Graphic System.                                                        |  |

| 31     | Circular<br>Interpolation<br>and<br>Programmable<br>Macros | Permits the Plotter to draw<br>arcs and circles and to use<br>programmed moves and draws<br>(macros).                                    |  |

| 32     | Downloadable<br>Characters<br>and Math<br>Character Set    | Permits the host computer to<br>program the Plotter to draw<br>user-defined, math, and Greek<br>characters.                              |  |

| 36     | Media Advance                                              | Permits the Plotter to be<br>equipped with roll paper (in-<br>stead of sheets), which can be<br>advanced under host computer<br>control. |  |

| 37     | Additional<br>Parameter<br>Entry Setup<br>Memory           | Allows more than one operat-<br>ing configuration to be stored<br>in the Plotter.                                                        |  |

| 48     | 220 V, 50 Hz                                               | Permits the Plotter to be<br>operated with a 220 V line<br>source.                                                                       |  |

| 48     | 220 V, 50 Hz                                               | operated with a 220 V line                                                                                                               |  |

#### Table 1-2

#### ACCESSORIES

#### **Standard Accessories**

Power Cord Pens, Fiber Tip (for paper) Red (3 each) Black (3 each) Blue (3 each) Green (3 each) RS-232-C Interface Cable Sheet Paper (17 x 22 in, 100 sheets/box) 4663 Interactive Digital Plotter Operator's Manual 4663 Interactive Digital Plotter Reference Guide

#### **Optional Accessories**

Wet Ink Pen Assembly With PL3 point (dia=.01 in, 0.3 mm) PL5 point (dia= .02 in, 0.5 mm) PL8 point (dia= .03 in, 0.8 mm) Pen Replacement Parts Kit 1 cap 1 body section 1 barrel 1 locking nut 6 ink reservoirs Ink Reservoir (6 per pkg) Ink For Film (3/4 oz Squeeze bottle) Black (each) Red (each) Green (each) Blue (each) Brown (each) For Paper (3/4 oz Squeeze bottle) Black (each) **Ball Point Pens** Black (3 each) Red (3 each) Green (3 each) Blue (3 each) Fiber Tip Pens (water soluble for acetate) Black (3 each) Brown (3 each) Red (3 each) Orange (3 each) Yellow (3 each) Green (3 each) Blue (3 each) Magneta (3 each) Purple (3 each) Dust Cover (soft vinyl) **GPIB** Cable Roll Paper (18 in x 200 ft for Option 36) Sheet Paper (17 in x 22 in 100 sheets per box) Mylar (17 in x 22 in 100 sheets per box) 4663 Service Manual (two volumes) 4663 Diagnostic Test Fixture Manual

| Table 1-3                |

|--------------------------|

| PHYSICAL CHARACTERISTICS |

| Weight              | Outside Dimensions  |                     |                    |

|---------------------|---------------------|---------------------|--------------------|

| th origin           | Length              | Width               | Height             |

| 80 lbs<br>(36.4 kg) | 38.0 in<br>(965 mm) | 30.1 in<br>(765 mm) | 6.8 in<br>(173 mm) |

# Table 1-4 POWER REQUIREMENTS

| Line Voltage,<br>Switch Selection | Voltage Range  | Line Fuse Size |

|-----------------------------------|----------------|----------------|

| 110 V                             | 90 — 130 V     | 5 A Fast-Blo   |

| 220 V                             | 180 — 250 V    | 2.5 A Fast-Blo |

| Line Frequency                    | . 48 — 440 Hz  |                |

| Input Power 115 Vac.              | 3.5 A maximum; | 2.4 A typica!  |

## Table 1-5

ENVIRONMENTAL SPECIFICATIONS

| Characteristic | Non-operating                                                                                                                                      | Operating                    |  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|--|

| Temperature    | —67 to 167° F<br>(—55 to + 75° C)                                                                                                                  | 32 to 104° F<br>(0 to 40° C) |  |

| Altitude       | To 50,000 ft<br>(15240 m)                                                                                                                          | To 15,000 ft<br>(4572 m)     |  |

| Vibration      | Up to 40 Hz<br>@.01 in (.03 cm)<br>total displacement                                                                                              |                              |  |

| Shock          | To 30 Gs, ½ sine,<br>11 ms duration                                                                                                                |                              |  |

| Transportation | Meets National Safe Transit Committee<br>type of test when packaged as shipped by<br>factory. Test procedure 1A, Category II with<br>a 12 in drop. |                              |  |

| Humidity       | Mil-T-28800B per test conditions 810B at<br>50.71 procedure IV (5 day operating and<br>non-operating, 90 to 95% Relative<br>Humidity).             |                              |  |

(a)

| Characteristic                        |          | Specifications                                                   |  |

|---------------------------------------|----------|------------------------------------------------------------------|--|

| Default Paper Size                    |          | A Size — 8 ½ x 11 in<br>(216 x 279 mm)                           |  |

|                                       |          | B Size — 11 x 17 in<br>(279 x 432 mm)                            |  |

|                                       |          | C Size — 17 x 22 in<br>(432 x 559 mm)                            |  |

|                                       |          | A4 Size — 8.3 x 11.7 in<br>(210 x 297 mm)                        |  |

|                                       |          | A3 Size — 11.7 x 16.5 in<br>(297 x 420 mm)                       |  |

|                                       |          | A2 Size — 16.5 x 23.4 in<br>(420 x 594 mm)                       |  |

| Paper Control                         | (Sheets) | Electrostatic Hold-Down                                          |  |

|                                       | (Roll)   | Mechanical Hold-Down with Option 36                              |  |

| Paper Drive Speed<br>(Option 36)      |          | ≥4.5 in/s (114 mm/s)                                             |  |

| Paper Drive Resolution<br>(Option 36) |          | 0.016 in (0.4 mm)                                                |  |

| Plotting Area                         |          | Y-Axis≤17.25 in (438 mm)<br>X-Axis≤23.5 in (597 mm)              |  |

| Plotting Speed                        |          | 16.47 in/s along either axis, 23.3 in/s at a 45° angle           |  |

| Acceleration                          |          | 600 in/s <sup>2</sup> (15240 mm/s <sup>2</sup> ) in<br>PREVIEW   |  |

|                                       |          | 400 in/s² (10160 mm/s²) in<br>NORMAL                             |  |

|                                       |          | 300 in/s² (7620 mm/s²) in<br>ENHANCED 1                          |  |

|                                       |          | 240 in/s <sup>2</sup> (6096 mm/s <sup>2</sup> ) in<br>ENHANCED 2 |  |

| Table 1-6                  |  |  |

|----------------------------|--|--|

| PERFORMANCE SPECIFICATIONS |  |  |

| Characteristic      | Specifications                                                                                  |  |  |

|---------------------|-------------------------------------------------------------------------------------------------|--|--|

| Point Plotting Rate | 30 Points/s (max)                                                                               |  |  |

| Plotting Accuracy   | 0.15% of Vector Length $\pm~0.0025$ in (0.0635 mm)                                              |  |  |

| Repeatability       | Returns any previously plotted point to within $\pm$ 0.0025 in (0.0635 mm)                      |  |  |

|                     | Resolution (Addressable)<br>0.001 in (0.0254 mm)                                                |  |  |

|                     | Pen Pressure<br>Coarse Pressure, $\pm$ 25%                                                      |  |  |

|                     | Pen Height (Up)<br>0.058 in ± 0.013<br>(1.47 ± 0.33 mm)                                         |  |  |

| Linearity           |                                                                                                 |  |  |

| Geometry            | Mean vector shall not deviate more than $\pm$ 0.015 in from a straight line between two points. |  |  |

| Line Aberrations    | Short term non-linearity shall not deviate more than $\pm$ 0.003 in from mean vector.           |  |  |

| Orthogonality       | $\pm$ 0.015 in (0.38 mm) across the plotting surface.                                           |  |  |

### SPECIFICATIONS

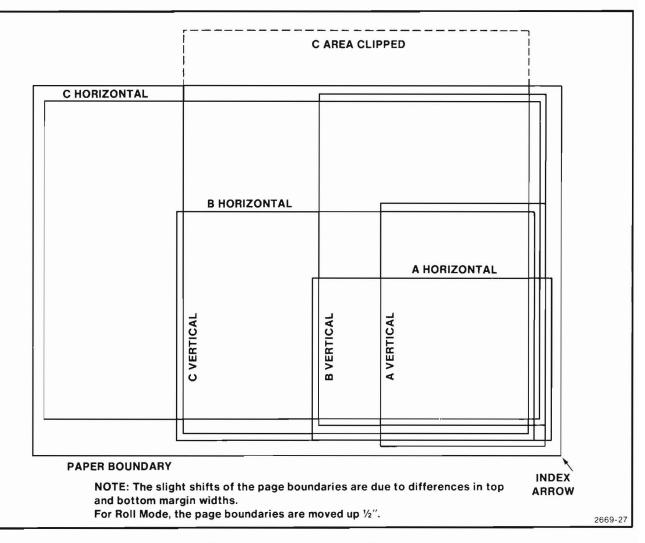

| Page<br>Format Orientation | Page Size &      | Measuremen      | ts (width x height)  | Figure <sup>b</sup><br>No. |     |

|----------------------------|------------------|-----------------|----------------------|----------------------------|-----|

|                            | Media Dimensions | English-inch    | Metric-mm            |                            |     |

|                            |                  |                 |                      |                            |     |

| Drafting                   | Horizontal       | C 22 x 17 in    | 21.00 x 15.5         | 533.4 x 393.7              | 1-2 |

| Drafting                   | Horizontal       | B 17 x 11 in    | 15.76 x 10.24        | 400.3 x 260.1              | 1-2 |

| Drafting                   | Horizontal       | A 11 x 8.5 in   | 10.50 x 7.74         | 266.7 x 196.6              | 1-2 |

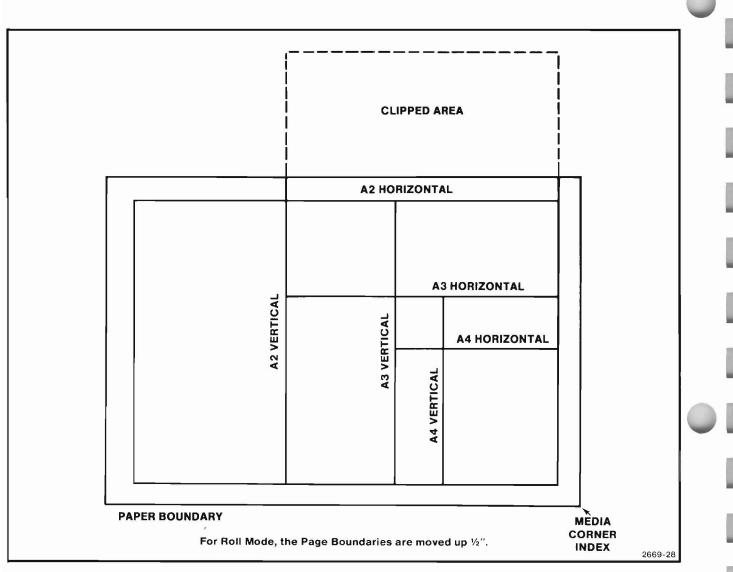

| Drafting                   | Horizontal       | A2 594 x 420 mm | 22.72 x 15.75        | 574.0 x 400.0              | 1-3 |

| Drafting                   | Horizontal       | A3 420 x 297 mm | 15.75 x 10.91        | 400.0 x 277.0              | 1-3 |

| Drafting                   | Horizontal       | A4 297 x 210 mm | 10.91 x 7.48         | 277.0 x 190.0              | 1-3 |

| Drafting                   | Vertical         | C 17 x 22 in    | 15.50 x <sup>a</sup> | 393.7 x <sup>a</sup>       | 1-2 |

| Drafting                   | Vertical         | B 11 x 17 in    | 10.24 x 15.76        | 260.1 x 400.3              | 1-2 |

| Drafting                   | Vertical         | A 8.5 x 11 in   | 7.74 x 10.50         | 196.6 x 266.7              | 1-2 |

| Drafting                   | Vertical         | A2 420 x 594 mm | 15.75 x <sup>a</sup> | 400.0 x <sup>a</sup>       | 1-3 |

| Drafting                   | Vertical         | A3 297 x 420 mm | 10.91 x 15.75        | 277.0 x 400.0              | 1-3 |

| Drafting                   | Vertical         | A4 210 x 297 mm | 7.48 x 10.91         | 190.0 x 277.0              | 1-3 |

| Graphing                   | Horizontal       | C 22 x 17 in    | 20.50 x 16.00        | 520.7 x 406.4              | 1-4 |

| Graphing                   | Horizontal       | B 16.5 x 11 in  | 15.00 x 10.00        | 381.0 x 254.0              | 1-4 |

| Graphing                   | Horizontal       | A 11 x 8.5 in   | 10.00 x 7.00         | 254.0 x 177.8              | 1-4 |

| Graphing                   | Horizontal       | A2 594 x 420 mm | 22.20 x 15.75        | 564.0 x 400.0              | 1-5 |

| Graphing                   | Horizontal       | A3 420 x 297 mm | 15.35 x 10.91        | 390.0 x 277.0              | 1-5 |

| Graphing                   | Horizontal       | A4 297 x 210 mm | 10.91 x 7.28         | 277.0 x 185.0              | 1-5 |

| Graphing                   | Vertical         | C 17 x 22 in    | 16.00 x <sup>a</sup> | 406.4 x <sup>a</sup>       | 1-4 |

| Graphing                   | Vertical         | B 11 x 16.5 in  | 10.00 x 15.00        | 254.0 x 381.0              | 1-4 |

| Graphing                   | Vertical         | A 8.5 x 11 in   | 7.00 x 10.00         | 177.8 x 254.0              | 1-4 |

| Graphing                   | Vertical         | A2 420 x 594 mm | 15.75 x <sup>a</sup> | 400.0 x <sup>a</sup>       | 1-5 |

| Graphing                   | Vertical         | A3 297 x 420 mm | 10.91 x 15.35        | 277.0 x 390.0              | 1-5 |

| Graphing                   | Vertical         | A4 210 x 297 mm | 7.28 x 10.91         | 185.0 x 277.0              | 1-5 |

@

Table 1-7 PAGE SIZES (FULL PAGE ASPECT RATIO) 3

$^{\rm a}{\rm The}$  page dimension is clipped since it would extend beyond the platen boundary.

$^{\rm b}\mbox{All}$  figures are shown with FULL PAGE initial aspect ratio.

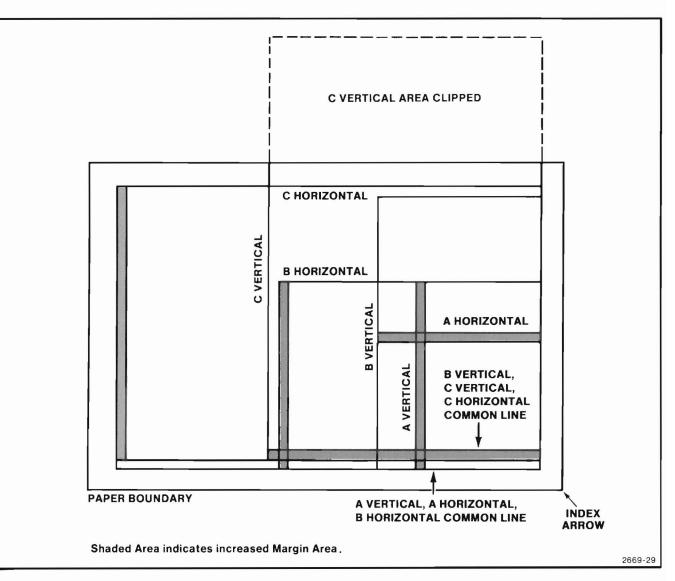

Figure 1-2. Horizontal and Vertical Page Orientations for English Page Sizes (Drafting).

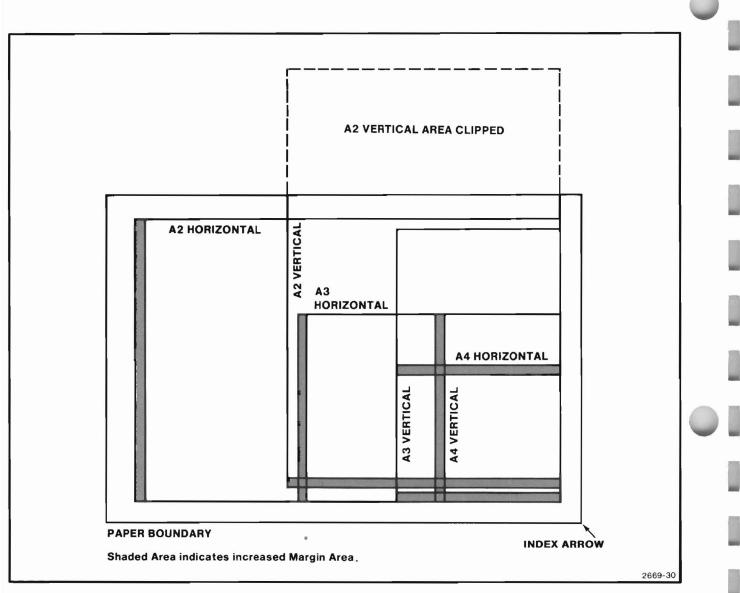

Figure 1-3. Horizontal and Vertical Page Orientations for Metric Page Sizes (Drafting).

Figure 1-4. Horizontal and Vertical Page Orientations for English Page Sizes (Graphing).

Î

Figure 1-5. Horizontal and Vertical Page Orientations for Metric Page Sizes (Graphing).

# Section 2

# **PREVENTIVE MAINTENANCE AND CALIBRATION**

## **PREVENTIVE MAINTENANCE**

#### General

Preventive maintenance consists of cleaning, visual inspection, adjustment, etc. Performed on a regular basis, preventive maintenance may improve the reliability of this instrument. The frequency and severity of the instrument's use will determine the required maintenance interval. It is, however, recommended that the Plotter's three pen drive cables be checked and adjusted at least every 500 hours of Plotter operation. Perhaps this might become the basis for performing preventive maintenance checks and calibration on the instrument. A convenient time to perform preventive maintenance is preceding calibration.

#### **Cleaning the Platen and the Case**

Occasional cleaning helps retain the electrostatic paper hold-down ability of the platen and preserves the appearance of the 4663. The frequency of cleaning varies with the instrument's environment. use the following procedure to clean the plotter:

- 1. Pull the Parameter Entry card out to the Media Form line and press the switch over SHEET.

- Press the front panel MEDIA CHANGE switch. (If the Plotter was not in SHEET mode previously, it will be necessary to press MEDIA CHANGE twice more to move the pen carriage to the upper right corner.) Then, turn the POWER switch off and disconnect the power cord. Remove any paper present on the platen.

# CAUTION

Do not use abrasive and strong chemical cleaners on the platen, as these can scratch or remove layers of the thin insulating film on the platen's electrostatic surface. Conductive cleaners must also be avoided. These include products containing ammonia, oils, liniments, or scents which leave an electrically conductive film if not entirely removed. This film causes the electrostatic paper hold-down to fail due to the conductivity of the film residue.

- 3. The most acceptable way to clean a platen is to use water, because it will not leave a residue on the platen's surface.

- 4. If more extensive cleaning is necessary, use a plain detergent or alcohol pad (Tektronix P/N 006-2398-00). A plain detergent is one that contains no bleach, scents, fabric softeners, or colored crystals. Either detergent or alcohol pad method will leave a residue which must be removed.

#### NOTE

Part number 006-2398-000 is for one pad only. A box of 50 can be ordered by using a quantity of 50.

- 5. If alcohol was used, remove the thin alcohol residue on the platen surface by wiping the platen with a soft, moist (with water) cloth. Turn the cloth frequently to avoid smearing the residue.

- 6. To remove any detergent residue, use step five, and repeat at least three times to remove all the residue.

- 7. Dry the platen with a clean, dry cloth.

- 8. Clean the Plotter case with a cloth lightly dam-

- 9 pened with a mild detergent solution.

- Connect the power cord to the power source, and if necessary, change the Parameter Entry card's Media Form line back to ROLL mode. The Plotter may again be operated.

#### **Viscous Oil Dampers**

On the end of each pen drive motor capstan, there is a viscous oil damper. It is normal for this damper to contain an air bubble in the oil resevoir and to have a thin residue of oil on its outer surface. The damper is not defective when these items appear. The air bubble helps compensate for tolerances and heat expansion. The thin oil residue is inherently present on the surfaces of the damper, though it serves no purpose. Isopropyl alcohol is a partial solvent for silicone oil such as that used in these dampers. It is the only cleaning agent used to clean up oil residues. Most other solvents effective for removing silicone oil will also attack the polycarbonates used in 4663 parts such as the damper covers.

Silicone oils have insulating properties. Do not touch circuit boards or plug connectors without first washing your hands if the dampers have been handled. Oil may prevent electrical contact or result in excess capacitance on circuit boards and plugs.

### **Lubrication Information**

The Plotter requires no periodic lubrication since all cable pulley bearings, motor bearings, fan bearings, and the bearings for the Y-axis arm rollers are all permanently lubricated. In addition, the rubber treads for all Y-axis arm rollers have lubrication impregnated in them.

### Pen Drive Cable Checks

The Plotter uses a system of three cables, each driven by a separate motor, to move the pen carriage. Although the cables are coated with plastic and made of multiple strands of steel wire, they may eventually become worn and break, especially when used after extensive periods of time without adjustment. Periodically (at least every 500 hours), the entire length of the three cables should be checked for broken wire strands, kinks, worn spots, or other failures. If any of these conditions are found in a cable or its coating, replace the cable. Check and adjust the cable tension, if necessary. This procedure is covered in the instrument calibration procedures later in this section.

## ADJUSTMENT AND CALIBRATION PROCEDURES

#### Introduction

A thorough cleaning and inspection for loose, damaged, or worn parts should precede any adjustments. It is especially important to check the three pen drive cables for broken strands, worn spots, etc., at this time. After a 30-minute warm-up period, perform the adjustment procedures in a + 68 to + 86° F (+ 20 to + 30° C) environment.

### **Equipment Required**

Large screwdriver.

7/16 in nutdriver (or screwdriver listed above).

Fish-weighing scales (0-6 lbs capacity).

Pozidrive screwdriver.

PBUS Extender Circuit Card 067-0813-00 (670-5235-00).

Voltmeter (DVM). Range, 0 to + 20 Vdc minimum; accurate within  $\pm\,$  0.05%. Also a range to + 1000 Vdc.

Short screwdriver with a narrow flat blade.

5/64 in Allen wrench bent at a 90° angle.

Pen Carriage Height Gauge 003-0957-00.

Two X-Axis Limit Switch Calibration Fixtures (003-0840-00).

Pozidrive screwdriver, very short.

Y-Axis Limit Switch Calibration Fixture (003-0849-00).

Oscilloscope. (A Tektronix 465 or equivalent.) Single trace with a vertical deflection factor of at least 5 mV per division and a sweep rate of at least 10 ns per division. Bandwidth should be from dc to at least 100 MHz.

C size plotting paper.

Square.

### **Preliminary Steps**

- 1. Turn off the power to the Plotter and disconnect the power cord.

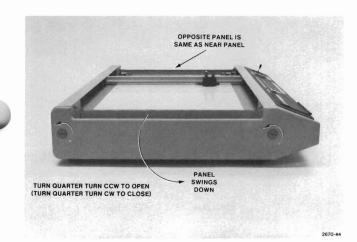

- Lower the two end panels by turning the large quarter-turn end panel latches ¼ turn CCW. There are two latches on each end panel (see Figure 2-1).

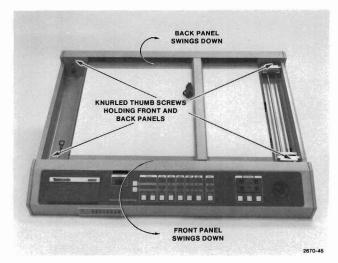

- 3. When both end panels have been lowered, lower the front and back panels. To do this, unscrew each of four knurled thumbscrews that hold the front and back panels in place (see Figure 2-2).

#### **PREVENTIVE MAINTENANCE and CALIBRATION**

#### X-Axis Cable Adjustments

For replacement of these cables, refer to Volume 2.

- Attach a scale (like a fish-weighing scale) to a loop (you may have to tie one, preferably a Bowline) on the end of the front X-axis cable (see Figure 2-3). While loosening the cable tie-down screw next to the loop, maintain six pounds (2.7 kg) of tension in the cable.

- Continue to maintain six pounds of cable tension while moving the Y-axis arm back and forth across the platen several times.

- 3. Tighten the cable tie-down screw (loosened in Step 1) while the scale continues to indicate six pounds of cable tension.

- 4. Repeat steps 1-3 for the rear X-axis cable (refer to Figure 2-4).

Figure 2-1. Side Panel Quarter-Turn Latches.

Figure 2-3. Front X-Axis Cable Tie-Down Screw and Loop Detail.

Figure 2-4. Y-Axis and Rear X-Axis Cable Tie-Down Screw and Loop Detail.

## Y-Axis Cable Adjustment

For replacement of this cable, refer to Volume 2.

- Attach the scale, used in the previous steps, to a loop on the end of the Y-axis cable (see Figure 2-4). (Again, you may have to tie a loop, preferably a Bowline.) While loosening the Y-axis cable tiedown screw, maintain three pounds (1.4 kg) of tension in the cable.

- 2. Continue to maintain three pounds of cable tension while moving the pen carriage back and forth along the Y-axis arm several times.

- 3. Tighten the cable tie-down screw (loosened in Step 1) while the scale continues to indicate three pounds of cable tension.

## **Power Supply Adjustment**

1. Unscrew the eight nuts (on studs) which hold the pen drive mechanism assembly to the Plotter base (Figure 2-5).

Before tilting up the pen drive mechanism assembly in the next step, make sure the rear panel has been opened and swung down out of the way. Also, exercise care to avoid damaging or stretching the pen drive cables.

- Grasp the front of the pen drive mechanism assembly under the corner brackets and lift the front of the assembly only, back to about a 45° angle. A support rod is stored along the right side of the circuit card cage to hold this assembly up. Insert the free end of the support rod into the hole located about three inches (75 mm) to the right of the front cable capstan (see Figure 2-6).

- 3. Remove the circuit card holding bracket (retainer). Then, insert the PBUS Extender circuit card into any of the unoccupied circuit card cage connectors on the right side of the circuit card cage.

Figure 2-5. Nuts Holding the Pen Drive Mechanism Assembly.

Figure 2-6. Access to the Plotter's Electrical Circuitry.

- 4. Plug the Plotter's power cable in and turn the POWER switch to ON. After about a five-second wait, the pen carriage moves to the upper-right corner of the platen. If the INIT light is still on, move the Parameter Entry card slightly (fully in) until the light goes out.

- 5. Connect the positive lead of the digital voltmeter to Pin 71 (+ 12 Vdc) of the Extender card. The other lead should be connected to GND (Pin 1, 2, 79, or 80). Adjust R1 on the back of the power supply (use a short screwdriver with a narrow, flat blade) to obtain a + 12 V  $\pm$  60 mVdc reading.

- 6. Observe that the cooling fan is working. It is located between the circuit card cage and the power supply.

#### **Joystick Sensitivity Adjustments**

#### Y-Axis Adjustment

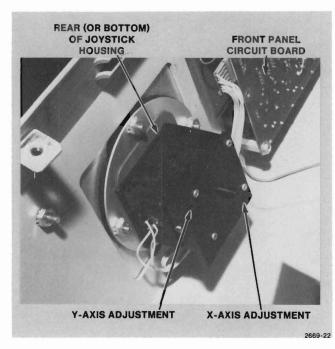

- 1. Insert the 5/64 in Allen wrench into the Y-axis adjustment hole shown in Figure 2-7.

- 2. Turn the wrench slowly until the Y-axis motor starts to turn. Note this wrench position.

- 3. Turn the wrench back the other direction until the motor begins to turn the other direction. Note this wrench position also.

- 4. Set the final adjustment near the center of these two extreme wrench positions.

#### X-Axis Adjustment

- 1. Repeat the Y-Axis Adjustment procedure for the Xaxis adjustment.

- 2. See Figure 2-7 for the X-axis adjustment location. This will affect both of the X-axis motors together in the same manner as for the Y-axis motor.

## X-Axis Limit Switch Adjustment

When you power up the Plotter, the pen carriage and the Y-axis arm move into the light beam of three carefully positioned photo-detectors (referred to as limit switches). These limit switches establish the initial pen position, and all subsequent plotting is done with reference to this position. Therefore, if any problems are noticed in the positioning of plots, calibrate these limit switches as follows:

- 1. Unplug J7, J8, and J9 from the Motor Pen Drive circuit card.

- 2. Connect the positive lead of the DVM to Pin 6 of the extender card (X LIM-1) and the negative lead to ground (Pin 1, 2, 79, or 80).

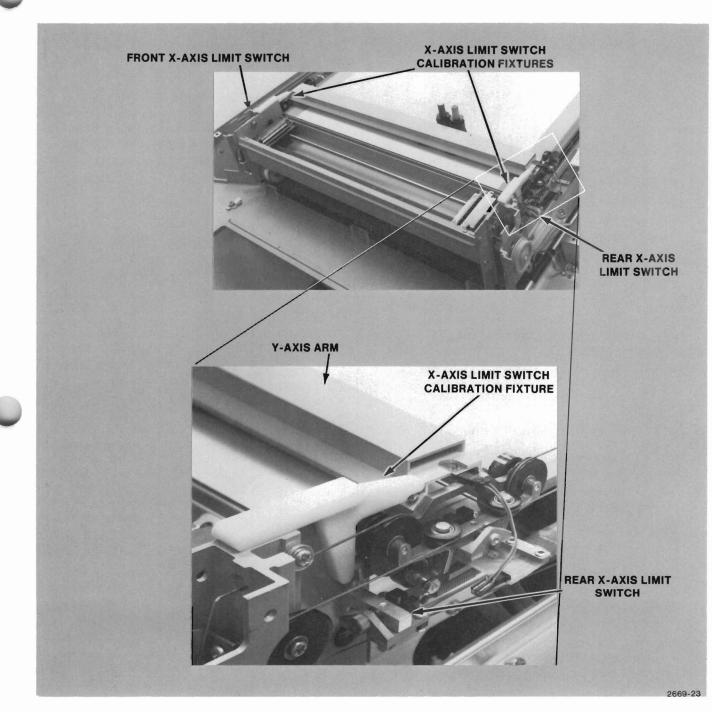

- 3. Attach the two X-axis limit switch calibration fixtures in place (see Figure 2-8). Both fixtures go on the right end (front and rear) of the instrument.

- 4. Move the Y-axis arm up against these two fixtures as shown in Figure 2-8.

#### Figure 2-7. Joystick Adjustment.

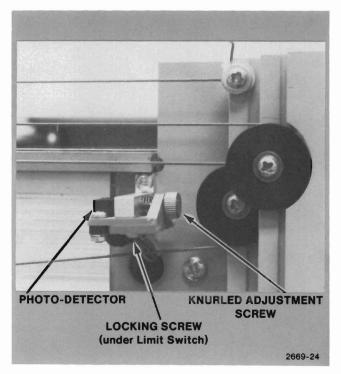

- Loosen (but do not remove) the locking screw on the underside of the front limit switch (see Figure 2-9).

- Adjust the knurled thumbscrew to change the voltage observed on Pin 6 back and forth from a TTL high to a TTL low.

- 7. Tighten the locking screw on the underside of the front limit switch.

- 8. Repeat Steps 5-7 for the rear limit switch. This time, observe the voltage on Pin 8 of the Extender card. It may be necessary to use a short Phillips screwdriver to reach the locking screw on this limit switch.

- 9. Remove the X-axis limit switch calibration fixtures.

Figure 2-8. X-Axis Limit Switch Calibration Fixture Placement.

Figure 2-9. X-Axis Limit Switch Detail.

## Y-Axis Limit Switch Adjustment

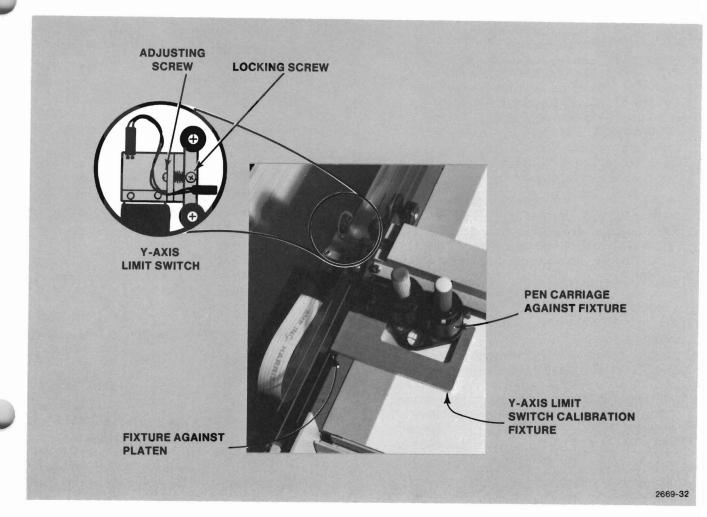

- 1. Attach the positive lead of the DVM to Pin 10 of the PBUS Extender circuit card.

- 2. Attach the Y-axis limit switch calibration fixture to the back edge of the platen (see Figure 2-10).

- .3. Move the pen carriage so that it presses firmly against the fixture as shown in Figure 2-10. Also ensure that the fixture is seated tightly against the back edge of the platen.

- 4. Loosen the locking screw under the Y-axis limit switch (see the insert in Figure 2-10). It may be necessary to use a short Phillips screwdriver.

- 5 Turn the adjusting screw (see Figure 2-10) until the observed voltage on Pin 10 of the Extender card changes back and forth from a TTL high to a TTL low.

- 6. Tighten the locking screw under the limit switch (loosened in Step 4).

- 7. Remove the Y-axis limit switch calibration fixture.

- 8. Reconnect J7, J8, and J9 to the Motor Pen Drive circuit card. (These were removed in Step 1 of the X-Axis Limit Switch Adjustments.)

### Carriage Height Adjustment (Plotters with serial numbers B062075 and up)

Check the pen carriage height by using the Pen Carriage Height Gauge. Lay the gauge flat on the platen surface. Attempt to slide either end of the gauge under the pen carriage as shown in Figure 2-9A. The shaved end of the gauge should slide under the carriage easily. The thick end should not.

Figure 2-9A. Pen Carriage Height Adjustment.

#### **PREVENTIVE MAINTENANCE and CALIBRATION**

Figure 2-10. Y-Axis Limit Switch Calibration Fixture Placement.

Raise or lower the carriage height as follows:

- 1. Loosen the two setscrews at each end of the carriage (Figure 2-9A).

- 2. Adjust the adjustment screws in the rail adjusters until the pen carriage height is between 0.085 and 0.105 inches from the platen surface as measured with the Pen Carriage Height Gauge. The height should be checked at several locations on the platen surface.

- 3. When the pen carriage is set at the proper height, tighten the two setscrews in each rail adjuster to secure the adjustment screws at the proper setting.

### **Measuring Platen Electrostatic Voltage**

Dangerous voltages are measured in this procedure. While making these measurements, make sure that you are not touching the voltmeter probe tip and that the probe tip does not touch other components or the Plotter chassis. In addition, use only one hand to hold the voltmeter probe and make sure that no part of your body is touching the Plotter chassis.

- Place the Plotter in SHEET mode (if not already in this mode). To do this, pull the Parameter Entry card out to the Media Form line and press the switch over SHEET. Then press the MEDIA CHANGE front panel switch twice.

- 2. Set the voltmeter to read the + 1000 Vdc scale.

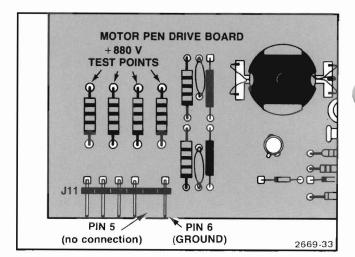

- Attach the negative voltmeter lead to Pin 6 of J11 on the Motor Pen Drive circuit card (see Figure 2-11).

- 4. Carefully attach or touch the positive voltmeter lead (probe) to each of the four load resistors directly behind J11 as shown in Figure 2-11. A reading of + 880 Vdc ± 10% should be measured at each resistor. The input impedance of the voltmeter will affect this reading. The technician should interpret this reading with the input impedance of the voltmeter in mind.

#### NOTE

If an attempt is made to measure this voltage on Pins 1-4 of J11, the input impedance of even a 10  $M\Omega$  voltmeter will place a sizable load on the High Voltage Platen Power Supply. This will lower the voltmeter reading and provide an inaccurate check.

#### **Processor Timing Checks**

- Attach an oscilloscope lead to Pin 77 (MASTER CLOCK) of the Extender card. Set the oscilloscope to 10 ns/DIV and 2 V/DIV. Check that the MASTER CLOCK has a period of 67.8 ns (or 6.8 DIV on the scope).

- 2. Attach the oscilloscope lead to Pin 27 (INTER-RUPT TIMER) of the Extender card. Set the oscilloscope to 1 ms/DIV and 2 V/DIV. Check that the period of the INTERRUPT TIMER is 8 ms (or 8 DIV on the scope). Tolerance is  $\pm 10\%$  or  $\pm 0.8$  ms.

- 3. Turn the Plotter's power OFF.

- 4. Remove the Extender circuit card.

- 5. Replace the circuit card retainer.

- To return the Plotter back to its normal mechanical configuration, perform Steps 1-5 of Appendix C (Volume 2) in reverse order.

Figure 2-11. Platen Electrostatic Voltage Test Points.

### **Pen-To-Pen Registration Check**

- 1. Turn the Plotter's power back ON.

- 2. With a pen in each pen holder (preferably each pen should have a different color) and a sheet of C size paper on the platen, press PEN SELECT 1, unless that light is already on.

- Move the pen carriage near the middle of the platen.

- 4. Press the UP/DOWN switch, turning that light on. The pen carriage should move toward the rear of the instrument slightly and to the left (nearly a 45° angle). Then the pen should lower to the paper.

- Press the UP/DOWN switch again, turning that light off. The pen should move back to its original position, leaving a dot on the paper.

- 6. Press PEN SELECT 2, turning that light on and the PEN SELECT 1 light off.

- Press the UP/DOWN switch again, turning that light on. The pen carriage should move toward the front of the instrument slightly and to the left (nearly a 45° angle) before lowering to the paper.

- 8. Press the UP/DOWN switch again, turning that light off. The pen should move back to its original position, leaving a dot on the paper.

- 9. Verify that these two dots are on top of each other.

#### **Orthogonality Check**

1. Pull the Parameter Entry card out and make the following entries:

INITIAL PAGE SIZE: C PAGE ORIENTATION: HORIZONTAL INITIAL ASPECT RATIO: FULL PAGE AXIS ORIENTATION: Column 1

Press OUTLINE VIEWPORT. Remember to press the lower of the two left SHIFT switches prior to pressing the PLOT CONTROL switch. The Plotter should draw a rectangular box which has the dimensions shown in Table 1-7. Measure these to verify size accuracy and use a square to verify orthogonality.

### Lamp Test

- Pull the Parameter Entry card out to the EXECUTE SELF TEST line and press the switch over column 2. All of the front panel lights (except the Parameter Entry light) should come on.

- 2. Replace any lights that are not on (see Volume 2).

- 3. Press the switch again to extinguish the lights.

## Line Quality and Accuracy Check

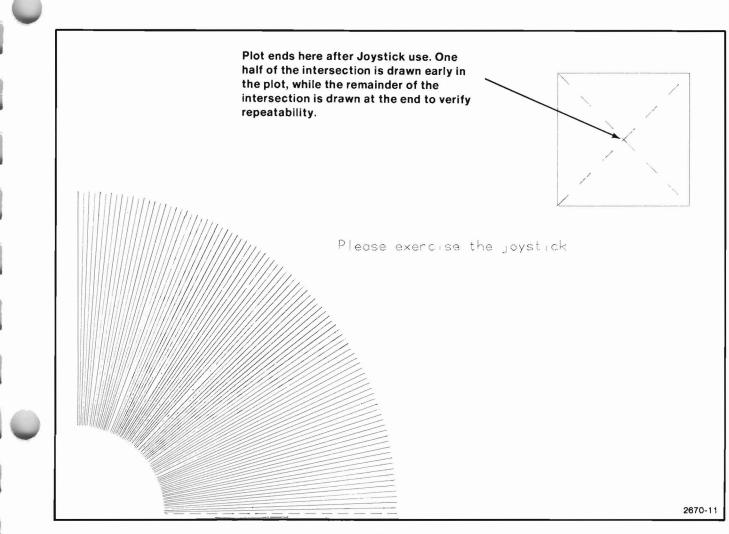

- 1. Press the switch over column 1 (on the EXECUTE SELF TEST line). The Plotter should draw a plot similar to that shown in Figure 2-12.

- 2. Examine this plot for line quality and accuracy. Early in the plot, the Plotter draws the right side of the center "X" in the box; finally, after permitting the technician to briefly exercise the joystick, the Plotter completes this center "X." Verify that the Plotter has not lost any positional accuracy by examining the center of the "X."

- 3. If the line quality checks indicate non-straight lines, the three dampers might be suspect. There is one damper on the end of each pen drive motor capstan, except on early model Plotters which do not use dampers. The damper is an oil-filled, inertia-absorbing device. Check to see if oil has leaked out. Notice that the damper is not entirely filled with clear-colored oil; there should be a bubble of about 1/4 to 1/3 of the damper's volume.

## **Joystick Operational Check**

- 1. Move the joystick control.

- 2. Verify that the pen carriage moves in the direction that the joystick handle is pressed and that its speed is dependent upon the deflection angle of the joystick handle.

### Media Advance Clutch Tension Check

- If the Plotter is equipped with Option 36, check the paper roll clutch assembly tension. To do this, first disengage the paper from the paper drive tractors. Then, pull the paper from the roll at least six inches (150 mm) and release. The paper roll should rewind at least ½ to ¾ revolution. If it does not, refer to Appendix A of Volume 2 for the clutch adjustment (under Option 36 Installation).

- 2. Thread the paper back into the paper drive tractors.

### Media Advance Adjustments

- 1. Refer to Section 2 of the Operator's Manual for adjustments of the paper drive mechanism. There are two adjustments: one to accommodate different paper widths, and the other to adjust the paper laterally. Adjust both as necessary.

- 2. Turn the Plotter's power off.

@

This completes the adjustment and calibration procedures for the 4663 Plotter.

#### **PREVENTIVE MAINTENANCE and CALIBRATION**

Figure 2-12. Test Pattern Produced by Self-Test Feature.

# Section 3

# THEORY OF OPERATION

## SYSTEM DESCRIPTION

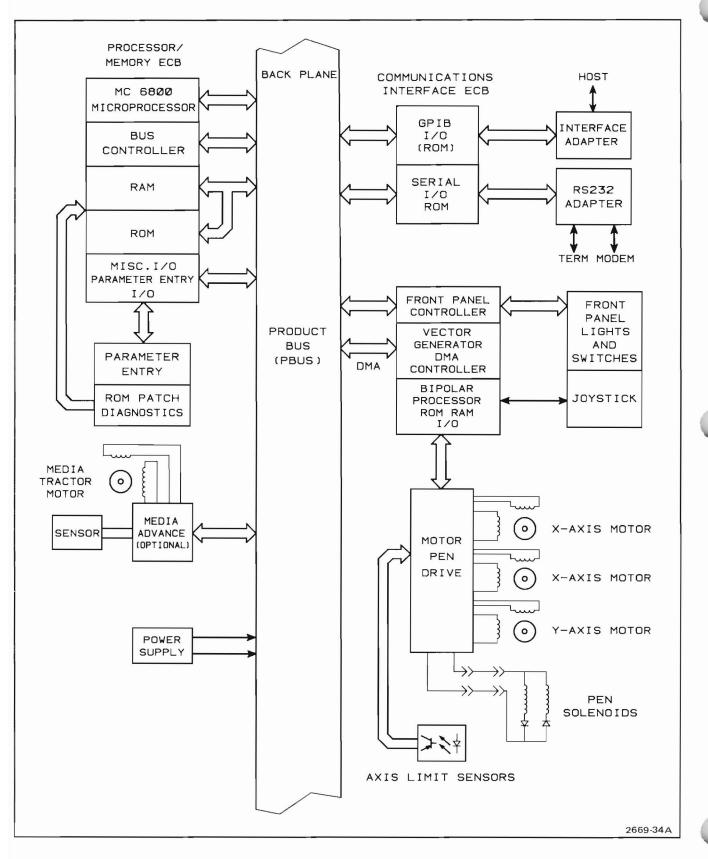

The basic electronics structure of the 4663 Plotter is composed of functional blocks residing on a central bus. A diagram of this structure is shown in Figure 3-1. The central bus is an 80-pin backplane circuit card cage and most functional blocks, representing circuit cards, connect directly into this backplane. There are a few exceptions, however, where a functional block does not connect directly to the bus. First, the Parameter Entry, Front Panel Switches and Lights, and the ROM Patch blocks "piggy-back" onto other modules, which in turn, are connected to the central bus. Second, the Motor Pen Drive block is functionally piggy-backed, or indirectly connected, to the Vector Generator module, simply because this block communicates primarily with the Vector Generator. Physically, however, the Motor Pen Drive circuit card connects into the backplane to obtain its power. Figure 3-1 shows the functional piggy-back relationships.

The 4663 Plotter contains two microprocessors. The 6800 residing on the Processor circuit card controls the overall operation of the Plotter. The second microprocessor (an 8X300) resides on and controls the operation of the Vector Generator functional block. The Plotter is electrically organized such that the 6800 microprocessor views all other functional blocks as peripheral devices, including the Vector Generator and its microprocessor.

## THEORY OF OPERATION

Figure 3-1. Functional Block Diagram of the 4663 Plotter.

# **BACKPLANE (CENTRAL BUS)**

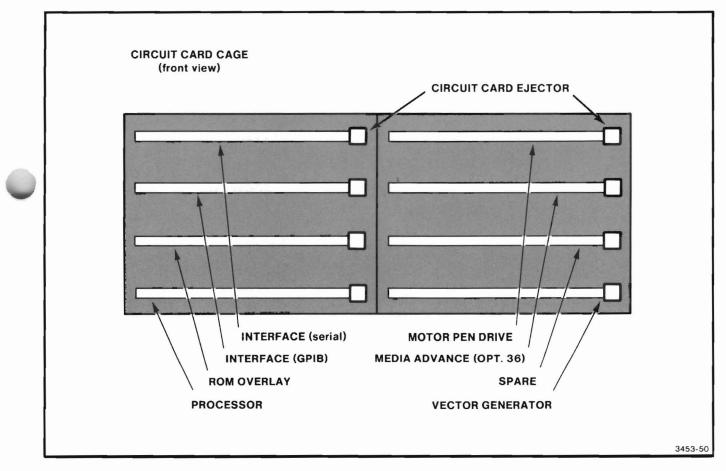

The 4663 Backplane is a circuit board with eight 80pin connectors, each of which is designed to connect to a circuit card. This arrangement forms a bus structure between the other functional blocks. (In most cases, each functional block represents one circuit card.) A diagram of the 4663 Backplane and the functional blocks that connect directly to the Backplane are shown in Figure 3-2.

## NOTE

The right and left sides of the Backplane are **NOT** symmetrical. Therefore, it is not possible to interchange circuit cards from the left side to the right side and vice-versa. However, it is possible to interchange any of the cards within a side.

A detailed description of the electrical signals on the Backplane is located in Appendix A of this volume. A pin/signal list is included in Volume 2.

Figure 3-2. 4663 Backplane.

# INTER-FUNCTIONAL BLOCK COMMUNICATIONS PROTOCOL

Following is a description of the communications protocol between the functional blocks in the 4663. The basic transactions are the following:

Read Write Interrupts DMA (Direct Memory Access) I/O Addressing (In/Out)

The rest of this section gives detailed circuit descriptions.

#### NOTE

For the purposes of this manual, "Processor" refers to the main Plotter microprocessor (i.e., the 6800).

## **Read Cycle Description**

The Read transaction begins when the Processor places the BUS ADDRESS on lines BAO-1 to BA15-1. (This is labeled as 1 in Figure 3-3.) The address is simultaneously qualified as valid by ADDRESS STROBE (ASTB-0), also sent from the Processor. One bus clock cycle later, at **2**, the address value has settled and can be considered valid. Notice that the WRITE-0 control line is not asserted with the address in this example; this indicates a Read transaction is occurring. Several bus clock cycles (at a frequency of 14.7456 MHz) later, at **3**, the device being read (a RAM, ROM, or I/O register) places BUS DATA on the lines BD0-1 to BD15-1. BUS DATA is simultaneously qualified as valid by DATA STROBE (DSTB-0), which is also sent from the device being read. One bus cycle later, at **4**, the data value has settled and can be considered valid.

The delay between address assertion by the Processor and data response by the device being read is the device access time; it may range from one bus clock cycle (67.8 ns) up to when the total read transaction is completed (within 3.8  $\mu$ s, which is the bus timeout period). The assertion of ASTB-0 must precede DSTB-0 by at least one bus clock cycle. If DSTB-0 is not asserted before the bus timeout period, the Processor assumes the device being read is non-existent and automatically terminates the transaction by releasing

Figure 3-3. Bus Read Transaction Timing.

both BUS ADDRESS and ASTB-0. The Bus Control causes the BUS TIMEOUT INTERRUPT to be generated to the Processor whenever the bus timeout period has been exceeded.

One clock cycle after the device being read has asserted DSTB-0 (at **3**), the device releases it (at **4**, when data is defined as valid). If the Processor requires a longer hold time for the data, it must now assert DSTB-0. This ensures that the Processor has control of the transaction and can delay the termination if necessary. At **5**, the Processor releases DSTB-0, indicating that it has read the BUS DATA. Finally, one bus clock cycle later, at **6**, the Processor releases BUS ADDRESS and ASTB-0, which also causes the device being read to release BUS DATA. This completes the entire Read transaction. On the next falling edge of the bus clock, a new transaction can begin with the assertion of a new BUS ADDRESS by the Processor.

## Write Cycle Description

The Write transaction begins when the Processor places the BUS ADDRESS on the lines BAO-1 to BA15-1. (This is labeled **1** in Figure 3-4.) The address is simultaneously qualified as valid by ADDRESS STROBE (ASTB-0), which is also sent from the Processor. One bus clock cycle later, at **2**, the address value has settled and can be considered valid. Notice that the WRITE-0 control line is also asserted with the address in this example. This indicates that a Write transaction is occurring. Several bus clock cycles later, at **3**, the Processor places BUS DATA on the lines BD0-1 to BD15-1. The BUS DATA can be considered valid one bus clock cycle later, at **4**, when the data value has settled. The delay between address assertion by the Processor and data assertion may range from one bus clock cycle up to when the total write transaction is completed (within 3.8  $\mu$ s, which is the bus timeout period). The assertion of ASTB-0 must precede DSTB-0 by at least one bus clock cycle.

All information is now valid, and at **4** the Processor releases DSTB-0, since it was held for one bus clock cycle. The device being written to must now assert DSTB-0 for a minimum of one bus clock cycle until at least **5**. If the device being written to requires a longer hold time for the data, it must continue to hold DSTB-0. This ensures that the device has control of the transaction and can delay the termination, if necessary (in case the device has a slower memory, for example). If the device does not hold DSTB-0, the Processor assumes that the device being written to is non-

Figure 3-4. Bus Write Transaction Timing.

existent and automatically terminates the transaction by releasing both BUS ADDRESS and ASTB-0. The Bus Control causes the BUS TIMEOUT INTERRUPT to be generated to the Processor if the bus timeout period has been exceeded. This might occur, for example, if a memory location has failed.

When the device being written to has stored the BUS DATA, it releases DSTB-0, at **6**. This signals the Processor to end the write cycle. On the next bus clock cycle, at **7**, the Processor releases BUS ADDRESS, ASTB-0, WRITE-0, and BUS DATA. Then, on the next falling edge of the bus clock, a new transaction can begin when the Processor asserts a new BUS AD-DRESS.

## **Interrupt Operation**

The Plotter is an interrupt-driven device. This means that each module has a predetermined interrupt level visible to the 6800 Processor. Before a functional block receives or generates some activity, it must first interrupt the Processor. The Processor completes its present activity and then services the interrupt, unless a higher priority interrupt comes along. The interrupt is serviced according to a set of instructions stored in ROM (the system firmware). This means that if a functional block generates (or transmits) a request for action to another block(s), it must first convert the request (or data) into an 8-bit data byte(s) before interrupting the Processor. Some typical requests that generate interrupts include pressing a front panel switch, host-generated commands, joystick commands, generating output responses to the communications interface, turning the front panel lights on or off, etc.

The Plotter uses eight levels of priority-vectored interrupts to identify the functional block requesting the interrupt. The Processor can then access the system firmware for instructions on servicing that interrupt, since each interrupt level has its own interupt vector in the system firmware (ROM). The eight levels of priority interrupt are used with a serial poll scheme, which is controlled with a three-bit counter (Interrupt Poll Counter, located on the Processor circuit card). This counter runs continuously on the bus at one-half the bus clock frequency (or 7.3728 MHz). The three counter lines are INTERRUPT POLL 0-1 to INTERRUPT POLL 2-1 (IRP0-1 to IRP2-1). When a functional block with a pending interrupt sees its preassigned (strapped) interrupt level appear, it asserts INTERRUPT REQUEST (IRQ-0). This signals the Processor to begin its interrupt sequence. If, however, the Processor is busy at that time and can not immediately service the interrupt, the Interrupt Poll Counter continues to count. However, the limits of the count are modified to eliminate counts of a lower priority. This means that the counter counts only between 0 (the highest priority) and the level of the pending interrupt, but no lower. Each time the counter counts to a lower priority level, the functional block with a pending interrupt drops the IRQ-0 signal. The poll count therefore continues, scanning only for higher priority interrupt levels. When the Processor finishes its present activity and reaches the vectoring stage of the interrupt cycle, the current pending interrupt having the highest count is used to locate the next interrupt vector.

A higher level (priority) interrupt, if one occurs before the Processor's vectoring in the interrupt sequence has started, may subsequently update a lower priority limit. This means that a functional block with a higher interrupt level can come along and also assert IRQ-0 when it sees its strapped interrupt poll count. Then, all subsequent poll counts will be between the highest priority and the new interrupting device's level. Therefore, the device with the first interrupt will not be included in the poll count. After the Processor has serviced the highest priority interrupt, the poll will expand again to include the lower priority levels (or down to the next highest priority level with a pending interrupt). This expansion occurs when the interrupt service firmware handler writes a new interrupt control byte to the interrupt poll hardware.

(a)

A table of the plotter's assigned interrupt levels is shown in Appendix E of Volume 2.

A timing diagram of the interrupting process is shown in Figure 3-5; the following discussion explains the key points in this diagram.

The INTERRUPT REQUEST POLL (IRP0-1 to IRP2-1) occurs synchronously with bus clock (but at one-half the frequency) but asynchronously with any bus transactions, (shown by 1). A level 2 module with a pending interrupt sees the level 2 poll count at 2 and asserts INTERRUPT REQUEST (IRQ-0). This action now establishes the lower priority limit at 2, resets the poll counter, and initiates the Processor's interrupt service cycle.

The interrupt request poll continues over the range 0-2. Notice that whenever the poll count is anything but 2, the level 2 interrupting device releases IRQ-0. Then, before the Processor can clear the level 2 interrupt, a level 1 module with a pending interrupt appears, at **3**. This level 1 interrupting device sees the level 1 poll count appear and asserts an INTERRUPT REQUEST (IRQ-0), which establishes 1 as the new lower priority level at **4**. With two interrupts now pending, the Processor finishes the current transaction while the poll continues to count within the new limits 0-1. After the Processor has completed the prior transaction and the poll counter has counted to the level number of the interrupting module (in this case 1), the Processor locates the interrupting vector and transfers to the appropriate service routine in system firmware to clear the interrupt at **5**. Since the poll counter is now limited to level 0 and 1 interrupts, the pending level 2 interrupt must wait until the Processor is finished with higher priority transactions. After the level 1 interrupt is cleared, the poll counter is allowed to count again until it reaches the next highest priority interrupt level (which is now level 2) at **6**.

The level 2 interrupt establishes the upper scan register at 2 and initiates another interrupt cycle by asserting IRQ-0, and the process is repeated until this interrupt is also cleared. Then, with no other interrupts pending, the interrupt poll counter proceeds to count between 0 and 7, waiting for another interrupt from one of the 4663 functional blocks.

#### Figure 3-5. Bus Interrupt Timing Diagram.

## **Bus DMA Operation**