# TABBLE DOUBLE DENSIT FLOPPY DISK INTERFACE

owner's manual

950 DOVLEN PLACE • SUITE B • CARSON, CALIF. 90746 (213) 538-4251 • (213) 538-2254 Tarbell Double Density Floppy Disk Interface

# COPYRIGHT (C) 1979,1980 TARBELL ELECTRONICS ALL RIGHTS RESERVED.

NO PART OF THIS PUBLICATION MAY BE REPRODUCED, TRANSMITTED, TRANSCRIBED, STORED IN A RETRIEVAL SYSTEM, OR TRANSLATED INTO ANY LANGUAGE OR COMPUTER LANGUAGE, IN ANY FORM OR BY ANY MEANS, ELECTRONIC, MECHANICAL, MAGNETIC, OPTICAL, CHEMICAL, MANUAL OR OTHERWISE, WITHOUT THE PRIOR WRITTEN PERMISSION OF TARBELL ELECTRONICS, 950 DOVLEN PLACE, SUITE B, CARSON, CALIFORNIA, 90746

.

The following addendum to the Tarbell Double Density manual provides jumper options involving the Qume DT8 for use with the Double Density interface board.

| Drive<br>Desiginator             | Drive<br>Option                                                                                                                                            |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C<br>D<br>DC<br>2S               | closed<br>open<br>open<br>open                                                                                                                             |

| DS1<br>DS2<br>DS3<br>DS4         | <pre>drive select for A drive select for B } we treat the drive as drive select for C } one big drive for double drive select for D sided operation.</pre> |

| T40<br>HA<br>Y<br>DL<br>DS       | open open closed open closed                                                                                                                               |

| SHUNT                            |                                                                                                                                                            |

| A<br>B<br>X<br>R<br>I<br>Z<br>HL | closed closed open closed closed open open open                                                                                                            |

All other drive jumpers are left as is from the factory.

1

.

# TABLE OF CONTENTS

Section

Nov 25,1980

| 1   | Introduction                        |

|-----|-------------------------------------|

| 2   | Software Integration                |

| 3   |                                     |

| 4   | Detail Theory of Operation          |

| 4   | Reset Circuit                       |

|     | Bootstrap Circuit and listing       |

|     | Address Selection Circuit           |

|     | Disk Control Circuit                |

|     |                                     |

|     | Direct Memory Access operation      |

|     | Write Precompensation circuit       |

|     | Data Recovery circuit               |

| 5   | Assembly Instructions               |

| 6   | Jumper Options                      |

|     | Normal Board Setup                  |

|     | Address Selection                   |

|     | XRDY or PRDY selection              |

|     | Write Precompensation Selection     |

|     | Bootstrap jumper                    |

|     | Persci drives                       |

|     | Interrupt option                    |

|     | Mwrite option                       |

|     | 8257 Clock option                   |

| ,   | 1793 Read Delay option              |

|     | Extra buffer chip                   |

| 7   | Parts List                          |

| 8   | Warranty                            |

| 9   | <u> </u>                            |

| 10  | IEEE S-100 BUS Specification        |

|     |                                     |

|     |                                     |

| 12  | Port and bit definitions            |

| 1.2 |                                     |

| 13  |                                     |

| 14  |                                     |

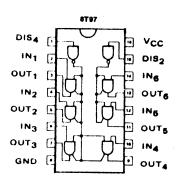

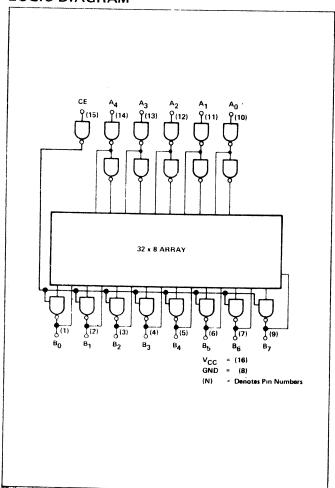

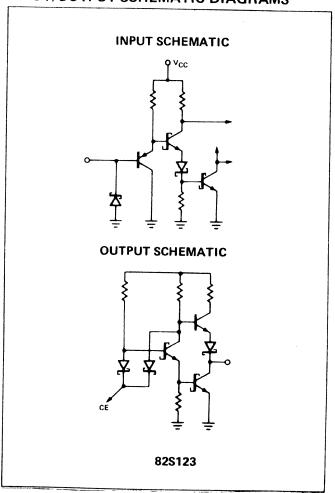

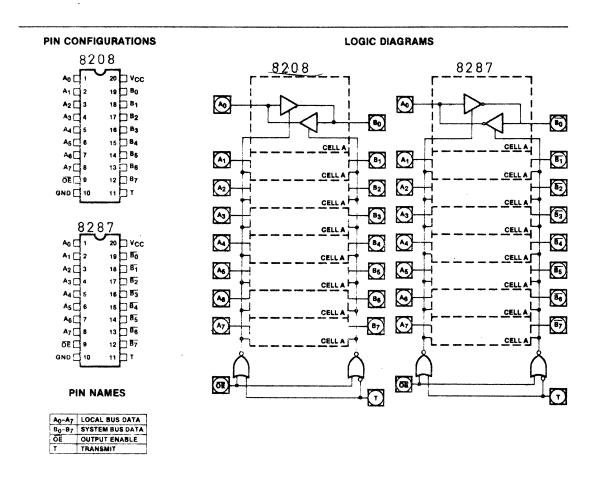

| Α   | IC Data Silects/ who I carron notes |

Description

# INTRODUCTION TO THE TARBELL DOUBLE DENSITY FLOPPY DISK INTERFACE

The Tarbell Double Density Interface is an IBM soft sector floppy disk interface using the Western Digital 1791/1793 Floppy Disk controller chip and built to the IEEE S-100 Standard.

This interface is very similar to the now popular Tarbell Single Density Interface in function, but with many added new features.

These features include operation as either single or double density, or both, direct memory access (DMA), and extended memory addressing capability, with processor speeds of either 2 or 4 Mhz. The on-board BOOTSTRAP feature allows full system memory of 64K by using the PHANTHOM line on the bus.

Software available to run the double density controller is the widely used CP/M(R) disk operating system, and the new MP/M multi-tasking operating system. Both operating systems use an enhanced I/O system utilizing the new direct memory access capability, and automatic density select features that this product offers.

The capacity of the Disk Operating System running under CP/M ver 1.4 in Double Density will be 476 Kbytes per disk, and 243 Kbytes Single Density per disk. These values will double when using Double Sided Drives.

Under CPM ver 2.2, the storage capacity of the disk can increase by the use of the deblocking function in the BIOS. Below is a table showing the disk storage that is possible.

Single Density

Double Density

Deblocked 512 x 16

243 Kbytes / side

476 Kbytes / side

600 Kbytes / side

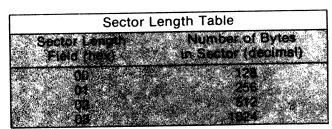

It should be noted that the capacities listed above are realized as a result of using the CP/M operating system. If this operating system were not used, then the disk could hold more data, because the disk may be formatted with sectors of 256,512,1024 bytes in length. For further information about this, consult the 1791/1793 data sheet for sector lengths that may be used.

Note: CP/M and MP/M are trademark and tradenames of Digital Reaserch Post Office Box 579, Pacific Grove, California 93950.

# SECTION 2: GETTING CP/M RUNNING WITH THE INTERFACE

One of the major problems confronting the implementers of new micro-computer systems, has been the lack of input/output (I/O) standards. The emergence of Digital Research's CP/M(r) disk operating system as a standard I/O environment has contributed greatly to alleviating this problem. Now the problem is reduced to implementing CP/M on the target hardware system, which consists of tailoring the BIOS part of CP/M to the situation. Unfortunately, since we can't assume any particular console interface at the factory, there is no way to make the system generation completely automatic.

Because of all the different possible system configurations, and because we try to update our hardware and software as quickly as possible, it has been difficult to create and maintain a set of documentation that is useful and correct for getting our double-density floppy disk interface working under CP/M. These instructions represent a major rewrite effort in this direction. We hope that most of the faults in the earlier instructions have been corrected in this set.

These instructions explain how to get the Tarbell Double Density Floppy Disk Interface going with Digital Research's CP/M 1.4 or 2.x disk operating system. It is important not to try and make more than one change in your system at a time. For example, if you wish to go from our single density interface operating under CP/M 1.4, to our double density interface operating DMA under CP/M 2.2 with a different memory size, DON'T try to do it all at once. First the single-density to double density, then to DMA, then to 2.2, then to different memory size.

Be sure that the title of the instructions you are going to use, matches the situation you have. If it doesn't, and you can't seem to find one that does match, call or write to us, and we'll try to help. If you don't think you are capable of carrying out the required instructions yourself, we can generate a customized system for you. Just have us send you an I/O tailoring questionaire. The cost is usually about \$50.

#### INSTALLATION NOTES

- 1. The MWRITE option available on our board is only for those computers where the MWRITE is not generated directly from the bus signals PWR and SOUT. It is not intended as a substitute for the normal MWRITE line, which must be implemented somewhere on the bus (usually on the CPU or front panel).

- 2. Install the double density board as close to the CPU as possible, between the CPU and memory board(s).

INSTRUCTIONS FOR GETTING THE TARBELL DOUBLE DENSITY INTERFACE OPERATING WITH CP/M 1.4 WHEN YOU HAVE CP/M 1.4 ALREADY GOING ON A TARBELL SINGLE-DENSITY INTERFACE

- First make sure that your situation matches the title above. If it doesn't, find another sheet that does match.

- 2. Check the option jumpers on your double-density board against the manual to make sure the board is addressed for EO through F8 (hex), and that all other options are correct.

Use your current single-density interface, operating under CP/M 1.4 to do the following steps:

- Use the FORMAT91 program on the public domain (provided with the interface) to format at least two disks. DON'T use any of your old format programs to do this. When it says "READY TO FORMAT?" be SURE to get the public domain disk out of there before typing Y. Test the disks using the DISKTEST program.

- 4. Put one of the newly formatted disks in drive B. Put a disk with your normal CP/M 1.4 system and system programs in drive A. perform the following steps:

- logged into drive A, type SYSGEN. Answer source as a) drive A, destination as drive B. Reboot.

- type PIP with no arguments, then the following steps. b) \*B:=A:DDT.COM

- \*B:=A:ASM.COM

- \*B:=A:SYSGEN.COM

- \*B:=A:ED.COM

- while still in PIP program, remove your system diskette from drive A, and insert into drive A the Public Domain #2 diskette that came with the double-density interface. continue as shown below: \*B:=A:ABIOS24.ASM

- \*B:=A:DBOOT24.ASM

- 5. Now take out the public domain disk #2 and put it aside. Take the newly formatted disk out of drive B and put it into drive A. Boot up on it. It should come up normally, since a copy of your system was just put onto it.

- 6. Using ED.COM, edit the ABIOS24.ASM to change the EQU's for your memory size, console, printer, drives, etc. Leave the DMACNTL and DUBSID EQU's set to FALSE. Set the MSIZE EQU to the same size as the CP/M 1.4 system you are now running on this disk. Be sure to set the console port numbers correctly. Exit from the editor. Rename the file to ABIOSxx.ASM, where xx is your MSIZE.

- 8. Assemble ABIOSxx with ASM.COM. Print the .PRN file if desired, then erase it.

- 9. Using ED.COM, edit DBOOT24.ASM. Set the MSIZE EQU to

size used above. Leave the DOUBSID, DOUBDEN, and DMACNTL EQU's set to FALSE. Exit from the editor. Rename the file to DBOOTxx.ASM.

- 10. Assemble DBOOTxx.ASM with ASM.COM. Print the .PRN file if desired, then erase it.

- 11. Use SYSGEN to put a copy of your current CP/M 1.4 system onto the disk as a file. When it asks for source, answer A. When it asks for destination, press carriage-return to reboot. Then do a SAVE 32 CPMxx.COM, where xx is your system size.

- 12. Use DDT to bring in the CPMxx.COM file and to overlay the BIOS and BOOT hex files onto it. Type DDT CPMxx.COM. Then type IABIOSxx.HEX. Then type Rbias where bias is in the table below:

| 20 D480 24 C480 28 B480 32 | bias                 |

|----------------------------|----------------------|

| 36 9480 40 8480 44 7480 48 | A480<br>6480<br>2480 |

Now type IDBOOTxx.HEX . Then type R900 . Then do Ctl-C.

- 13. Next enter SYSGEN. When it asks for source, press return to skip. When it asks for destination, type A. At this point you may write this system onto more than one disk. After you are finished writing onto the disk(s), DON'T press return to reboot.

- 14. You can now shut off your computer, remove the single density interface, and put the double-density interface in. Then turn your computer back on.

- 15. The system you have just written onto one or more disks should now boot up correctly on the double-density interface. If it doesn't, check over the BIOS and BOOT .PRN files to make sure all EQU's were set correctly. Check your board to verify again that all the jumper options are right. If you still can't get it going, read section 2-3 of these instructions.

- 16. If the system does come up correctly, congratulations! You are now running the double-density interface in non-DMA mode. If you want to operate double-density next, see section 2-2 of these instructions. If you want to try operating in DMA mode, go to step 6 in this section, changing the DMACNTL EQU to TRUE in both the BIOS and the BOOT .ASM files. The rest of the instructions are the same.

- 17. Finally, if you notice any errors in this documentation, PLEASE call or write about it.

HOW TO MAKE THE TARBELL DOUBLE DENSITY INTERFACE OPERATE IN THE DOUBLE DENSITY MODE ASSUMING YOU HAVE THE DOUBLE DENSITY INTERFACE OPERATING IN THE SINGLE DENSITY MODE.

- l. Check your situation against the title above. If it doesn't match, look for other instructions that do. In order to operate in double density mode, you will either need to be operating at 4 or above 4 Mhz (Z80 or 8085), or you need to be operating in DMA mode. To set DMA mode, see step 16 of the instructions in section 2-1.

- 2. Format some disks double density with DFORMAT, and test them using  $\mathtt{DTEST}_{\:\raisebox{3.5pt}{\text{\circle*{1.5}}}}$

- 3. If you boot up on a single density system which was created using the auto-select I/O section (ABIOS or 2ABIOS), all you have to do is put the formatted double-density diskette in drive B. Files may be transferred to the new double density disk using PIP. Don't try to use the COPY utility to copy from single density to double density or vise-versa.

- 4. If you want to put a system from the first two tracks on the single density disk onto a double density disk, SYSGEN alone will not work. This is because the first sector of the first track contains a byte which has to be DD (hex) for double density, and your single-density disk doesn't have that byte. To perform this operation correctly, follow these steps:

- a) On your single density disk, edit the file called DBOOTxx.ASM to change the DOUBDEN EQU from FALSE to TRUE. It is important that the MSIZE match your current CP/M system size (xx).

b) Assemble the new file: ASM DBOOTxx

- c) Do a SYSGEN, answering source on A, skip the destination and reboot. Enter SAVE 34 CPMxx.COM where xx is system size.

- d) Then overlay the CPMxx.COM system image with the new DBOOT:

DDT CPMxx.COM

IDBOOTxx.HEX

R900

- e) Then press control-C to return to CP/M.

f) Type B:, <cr> to log in drive B. Type A:, <cr>>

- g) Then do another SYSGEN, this time skipping the source, and answering B to the destination. (This assumes you still have your double-density disk in B.)

- 5. Now you can take the double density disk out of drive B and put it into drive A and boot up on it.

# WHAT TO DO IF YOUR TARBELL DOUBLE DENSITY FLOPPY INTERFACE IS NOT WORKING

- 1. Recheck the jumper options on the interface board against your manual in section 6. Note that manuals of boards rev B and earlier have an error in the board addressing section. People with these manuals can get a new manual free by sending us the cover of their old manual.

- 2. Recheck the EQU's in the BIOS and BOOT .ASM files to make sure that all are set correctly.

- 3. If you have a friend with a working Tarbell Double Interface, try using your interface in his computer. If his works and yours doesn't, there is probably something actually wrong with your interface. If so, you might want to consider sending it back to Tarbell for repair. If your interface does work in your friend's computer, the problem might be in your software, or in some other component of your system. Just because the other components of your system work under other circumstances, doesn't mean that there is nothing wrong with them.

- 4. Another thing to check is the diskette that you're using. Is it formatted correctly? How do you know it is?

- 5. Do you have dynamic memory in your computer. If so, how is it refreshed? It is possible that the way it is refreshed interferes with our interface, or that the way our interface works interferes with the memory's refresh circuitry.

- 6. Does your CPU board fully implement the new IEEE S-100 standard? In particular, does it use pin 67 (the phantom line) for anything besides phantom? Does it implement the control-disable, data-disable, and status-disable lines? Does it implement the PSYNC, PHOLD, and PHLDA lines? Neither the SDS SBC-100 or SBC-200 CPU boards meet this requirement.

- 7. Does the memory which occupies address 0000 in your system have a phantom line on pin 67?

- 8. Do you have other boards in your system that use the XRDY and PRDY lines (pins 3 and 72) besides the Tarbell interface and the CPU? If so, it might be best to disconnect those lines completely.

- 9. Since the Tarbell Double Density Floppy Disk Interface uses lines on your motherboard that aren't normally used, some of these lines could be shorted or open, or the connector pins could be dirty.

- 10. Check your system power supply, with a scope if possible, to make sure that all your voltages are steady, clean, and the right level, both on the drives and the motherboard. It is very important that on the drive power supply, the 24 volt, 5 volt, and -5 volt returns be connected together at the power supply end.

- ll. If you are having problems with the bootstrap, it's possible that C17 is not quite the right value to reduce the effects of ringing on the bus. You might try 100, 220, 390, 470, or 680 pf capacitors, in that order. The symptom is that the bootstrap flip-flop gets reset before it has a chance to read a complete sector if the value of C17 is to too small, or, the bootstrap will not release soon enough if the value of C17 is to big. The value of C17 is not as critical as it may seem, but it's value in some cases will be controlled to some extent by the noise and impedance effects of your computer bus. If you have a good fast scope, you can observe the bootstrap operation by looking at pin 19 on the 8257. This is the DRQ line, and it should be a series of short pulses that happen over a period of about 2 ms. If they don't last that long, you may have to adjust C17.

- 12. If the DRQ line mentioned above never goes high at all, that means the interface is never receiving a valid data byte. This could be caused by a variety of factors, including a bad data separator component, bad 1793, bad drive, etc.

- $13.\ \mbox{If the interface}$  is picking up excessive errors after warming up, it could be the 1793. We are now testing these IC's more carefully.

\*\*\* NOTE \*\*\*

If you decide to send the interface back for repair, be sure to include a copy of your receipt, showing the date you bought it.

INSTRUCTIONS FOR GETTING THE TARBELL DOUBLE DENSITY INTERFACE OPERATING WITH CP/M 2.x WHEN YOU HAVE CP/M 2.x ALREADY GOING ON A TARBELL SINGLE-DENSITY INTERFACE

- 1. First make sure that your situation matches the title above. If it doesn't, find another sheet that does match.

- 2. Check the option jumpers on your double-density interface board against the manual to make sure the board is addressed for E0 through F8 (hex), and that all other options are correct.

Use your current single density interface, operating under CP/M 2.x to do the following steps:

- 3. Use the FORMAT91 program on the public domain #2 disk (provided with the interface) to format at least two disks. DON'T use any of your old format programs to do this. When it says "READY TO FORMAT?" be SURE to get the public domain disk out of there before typing Y. Test the disks using the DISKTEST program.

- 4. Put one of the newly formatted disks in drive B. Put a disk with your normal CP/M 2.x system and system programs in drive A. Now perform the following steps:

- a) logged into drive A, type SYSGEN. Answer source as drive A, destination as drive B. Reboot.

- b) type PIP with no arguments, then the following steps.

\*B:=A:CPM.COM

\*B:=A:DDT.COM

\*B:=A:ASM.COM

\*B:=A:SYSGEN.COM

\*B:=A:ED.COM

c) while still in the PIP program, remove your system diskette from drive A, then insert into drive A the Public Domain #2 diskette that came with the double-density interface. Then continue as shown below:

\*B:=A:2ABIOS24.ASM

\*B:=A:2DBOOT24.ASM

- 5. Now take out the public domain disk #2 and put it aside. Take the newly formatted disk out of drive B and put it into drive A. Boot up on it. It should come up normally, since a copy of your system was just put onto it.

- 6. Using ED.COM, edit the 2ABIOS24.ASM to change the EQU's for your memory size, console, printer, drives, etc. Leave the DMACNTL and DUBSID EQU's set to FALSE. Set the MSIZE EQU to the same size as the CP/M 2.x system you are now running on this disk. Be sure to set the console port numbers correctly. If you have Shugart 800 drives, don't set the step rate any faster than 10 ms. Exit from the editor. Rename the file to 2ABIOSxx.ASM, where xx is your MSIZE.

- 8. Assemble 2ABIOSxx with ASM.COM. Print the .PRN file if desired, then erase it.

- 9. Using ED.COM, edit 2DBOOT24.ASM. Set the MSIZE EQU to the size used above. Leave the DOUBSID and DMACNTL EQU's set to FALSE. Exit from the editor. Rename the file to 2DBOOTxx.ASM.

- 10. Assemble 2DBOOTxx.ASM with ASM.COM. Print the .PRN file if desired, then erase it.

- 11. Use SYSGEN to put a copy of your current CP/M 2.x system onto the disk as a file. When it asks for source, answer A. When it asks for destination, press carriage-return to reboot. Then do a SAVE 34 CPMxx.COM, where xx is your system size.

- 12. Use DDT to bring in the CPMxx.COM file and to overlay the BIOS and BOOT hex files onto it. Type DDT CPMxx.COM. Then type I2ABIOSxx.HEX. Then type Rbias where xx is MSIZE and bias is in the table below:

| ХХ | bias                 | хх | bias                 | xx | bias                 | xx | bias                 |

|----|----------------------|----|----------------------|----|----------------------|----|----------------------|

| 36 | D580<br>9580<br>5580 | 40 | C580<br>8580<br>4580 | 44 | B580<br>7580<br>3580 | 48 | A580<br>6580<br>2580 |

Now type I2DBOOTxx.HEX . Then type R900 . Then do Ctl-C.

- 13. Next enter SYSGEN. When it asks for source, press return to skip. When it asks for destination, type A. At this point you may write this system onto more than one disk. After you are finished writing onto the disk(s), DON'T press return to reboot.

- 14. You can now shut off your computer, remove the single-density interface, and put the double-density interface in. Then turn your computer back on.

- 15. The system you have just written onto one or more disks should now boot up correctly on the double-density interface. If it doesn't, check over the BIOS and BOOT .PRN files to make sure all EQU's were set correctly. Check your board to verify again that all the jumper options are right. If you still can't get it going, read section 2-3 of these instructions.

- 16. If the system does come up correctly, congratulations! You are now running the double-density interface in non-DMA mode. If you want to operate double-density next, see section 2-2 of these instructions. If you want to try operating in DMA mode, go to step 6 in this section, changing the DMACNTL EQU to TRUE in both the BIOS and the BOOT .ASM files. The rest of the instructions are the same.

- 17. Finally, if you notice any errors in this documentation, PLEASE call or write about it.

GETTING THE TARBELL VERSION OF CP/M 1.4 OR 2.X RUNNING ON YOUR TARBELL DOUBLE-DENSITY FLOPPY DISK INTERFACE WITHOUT A CURRENTLY RUNNING CP/M SYSTEM OF ANY KIND

- 1. First make sure that your situation matches the title above. If not, you may find that another set of instructions will get your system going sooner.

- 2. You need to have the following hardware installed:

- a) An assembled and tested Tarbell Double Density Interface

- b) At least 24k bytes of random access memory, of which at least the first 32 bytes can be disabled by phantom line pin 67 going low.

- c) A Z-80, 8085, or 8080 CPU board which conforms to the IEEE S-100 standard.

- d) A console interface of some type, preferably not memory—mapped video, which supports an alphanumeric keyboard and a CRT display or teleprinter. If possible, this interface should be addressed for status on port 0, data on port 1, with bit 0 of the status low meaning keyboard ready, and with bit 7 of the status low meaning CRT display ready. If these port and status requirements are met, the Tarbell CP/M 1.4 or 2.x disks for the DD controller should boot up with no further work. Just put the disk in, push reset, and run. Skip to step 8 if so. If not, you will need to fulfill the requirements of substep (e) below and continue.

- e) Either a front panel or a ROM monitor (any ROM should be outside the 24k RAM), which allows depositing bytes into specified RAM addresses and executing at an address.

- 3. If possible, have a friend make a copy of your original CP/M disk, and don't use it except to make further copies. Then use the copy for the following steps.

- 4. Turn the computer on, then the CRT-keyboard, then the drive power.

- 5. Put the CP/M disk into the disk drive (on most drives, the label on the disk should face the door of the drive). Close the door. Push reset (and run if you have one) buttons on the computer.

- 6. The head should load against the disk and move in one track. If it doesn't do this, something is wrong with the hardware setup, and you should try a few times more. If it still doesn't do it, FIRST remove the diskette, then shut down the system. Something is either wrong with the hardware or the diskette. If so, have someone look at it or call Tarbell. If it does load and step ok, go onto the next step.

- 7. Either stop the computer from running, if you have a front panel, or jump into your ROM monitor, if you have one.

- 8. Look at the BIOS (Basic Input Output System) listing that

came with our CP/M. Find the label BOOT. After the LXI SP instruction, you will see a series of NOP's. This area is reserved for initializing console interfaces that require it. Using either front panel or ROM, deposit the initialization routine required, if any, at the address indicated by the listing. There should be a copy of any required initialization routine in the manual on your console interface. Assembly language code for the initialization of some common console interfaces can be seen in the following lines on the page.

- 9. Still looking at the BIOS listing, find the label CONST. Examine the code there for our "standard" interface. Put the code here to do a status check on your console interface. Notice that if your status bits are true when high, instead of low like ours, you will need to change the RNZ to an RZ. Other changes which might be required are the port number after the IN, and the mask after the ANI. Check your console interface manual for examples and instructions.

- 10. The next routine is labeled CONIN. Deposit the code to read a byte from your console keyboard into register A. Notice that you might need to make similar changes, such as JNZ to JZ, mask, and port numbers.

- ll. The last routine to change is labeled CONOT. Deposit the code to write the byte in register C to your console. Again, you might need to replace our JNZ with a JZ and make port number and mask changes. Be sure to end each of these routines with an RET instruction.

- 12. This should be all the patches you need to make to the CP/M system residing in memory, to get going temporarily. Now examine the content of address 5A00 (hex), which should be a C3 (hex for JMP) and execute (run) at that location.

- 13. Our BIOS should give you an opening message. If so, you're on the air, so go to step 14. If not, the system may not have loaded properly, and something may be wrong with the diskette or hardware setup. In that case, refer to section 2-3.

- 14. If you haven't already done so, copy the system and files onto another disk. In order to do this, keep your system disk in drive A and put a blank disk into drive B. Then type: COPY ALL. This will copy your original disk onto the blank disk. Note that the system you are running is only in memory, and the system on the disk hasn't yet been modified. Leave the new disk in drive B until you press return to reboot. Then take the original disk out of drive A and never use it again except to copy it. Now remove the copy you made from drive B and label it exactly the same as the original. You will find that it is important to keep the disk labels current, as it is easy to get confused and make a mistake. Put the new copy into drive A for further work. Then press Ctl-C.

- 15. The next thing to do is edit the BIOS and BOOT .ASM files and overlay them onto your system. Use the method described in the

Tarbell CP/M 1.4 or 2.x User's Guide, as this will properly document all your changes and allow you to make use of memory larger than 24k.

16. The latest ABIOS (Auto-density select Basic Input Output System) is always available from Tarbell for \$15. Just ask for Public Domain Disk # 2.

This is a disk which is regularly updated with our latest ABIOS 2ABIOS for the Tarbell Double Density Floppy Disk Interface. Other utilities are also maintained on this disk, such as format test routines. We also had room to include the source for the FORTH language from the Forth Interest Group. Their name and address included on the .ASM file. Following is a short description of each For further information, see the comments in the file itself, or the Tarbell CP/M User's Guide. The latest version of this disk is always available within 1 week from Tarbell for \$15. having problems, it's always wise to see if there is a newer version of this disk available than the one you have. 1. DBOOT24.ASM

This is the secondary coldstart loader for CPM 1.4 only.

### 2. DDUMP.ASM & DDUMP.COM

THIS IS A MODIFIED DUMP.COM FROM SAM SINGER AND FROM THE CP/M USERS GROUP. THIS PROGRAM WILL ALLOW YOU TO VIEW ONLY TRACKS 2 - 76 OF DOUBLE DENSITY DISK. THE ONLY LIMITATION IN THE PROGRAM IS THAT IT WILL NOT DUMP BY GROUP NUMBERS. ALL OTHER FEATURES ARE USEABLE.

# 3. DFORMAT.ASM & DFORMAT.COM

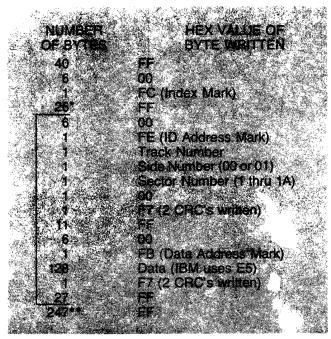

This is the double density format program. It will also format a double sided disk if asked to. This format program formats track 26, 128 byte sectors, tracks 1 - 76 in 51, 128 bytes sectors.

#### 4. DTEST.ASM & DTEST.COM

THIS PROGRAM IS USED TO TEST A DOUBLE DENSITY DISK FOR ERRORS. PROGRAM FIRST COMES UP IT WILL ASK YOU FOR A "TITLE:". YOU WHEN MAY TYPE IN ANYTHING YOU WANT SUCH AS <FORMATTED WITH 62.5 NSEC,187.5 NSEC> AND THEN A CNTL-P, CARRIAGE RET, OR IF YOU DON'T WANT JUST TYPE A CARRIAGE RET. THE TITLE ALLOWS YOU TO KEEP A ANYTHING, RUNNING TAB ON THE ERRORS AND USING CNTL-P WILL TURN ON LIST DEVICE FOR MAKING A HARDCOPY LISTING. THE NEXT QUESTION WILL BE STARTING TRACK. YOU MUST ANSWER THIS WITH A TRACK NUMBER THE REST OF THE PROGRAM SHOULD BE CLEAR. THIS PROGRAM READS TRACK AT A TIME AND KEEPS A RUNNING TAB OF ERRORS FOUND. DURING THE READING OF THE TRACK, IF A SECTOR IS BAD IT WILL DISPLAY NUMBER AND THE NUMBER OF RETRYS IT TOOK TO READ IT. IT SHOULD BE NOTED IT WILL DO 11 RETRYS MAX, AND THEN GO ON TO THE NEXT SECTOR. IT TAKES MORE THAN 10 RETRYS, THEN YOU SHOULD REFORMAT THE AGAIN, AS OUR DBIOS ONLY DOES 10 RETRYS BEFORE INDICATING A FAILURE. RETRYS ON THE ORDER OF 1 TO 5 IS TYPICAL, IF THEY OCCUR AT ALL, WITH THIS INTERFACE. THIS PROGRAM DOES NOT WRITE ON THE DISK, IT IS READ ONLY.

### 5. FORMAT.ASM & FORMAT.COM

IF YOU ARE USING OUR OLD SINGLE DENSITY FORMAT PROGRAM, YOU WILL NOT BE ABLE TO READ THEM ON THE NEW INTERFACE IN SINGLE DENSITY. IS BECAUSE THERE IS A BYTE IN THE INNER RECORD GAPS THAT THE 1771 WILL READ BUT THE 1791/1793 WON'T. THIS FORMAT PROGRAM FIXES THAT PROBLEM FOR BOTH THE 1791/1793 AND WILL STILL ALLOW YOU TO USE IT WITH YOUR PRESENT 1771 CONTROLLER ALSO. YOU SHOULD DESTROY AND OLD COPIES OF THE OLD FORMAT PROGRAM YOU HAVE, AND USE THIS ONE FROM HERE ON OUT. THIS PROGRAM ALSO FORMATS A DOUBLE SIDED DISK.

#### \*\*\* NOTE \*\*\*

THIS FORMATS SINGLE DENSITY ONLY, 26 SECTORS OF 128 BYTES AND ONLY RUNS ON THE NEW CONTROLLER BOARD.

# 6. FORMAT91.ASM & FORMAT91.COM

This program will only run on the single-density interface. It will format disks in standard IBM single-density format, to read correctly on the double density interface.

#### 7. DFRAND.ASM

This is another format program, which only runs on the double-density interface, and which formats disks double-density in a random format. This is very useful to use in conjunction with the DTEST program, while setting up precomp. It gives a more realistic representation of the way that data may be present on the disk. Do NOT use this program to format disks that are to be used next with CP/M, as the directory needs to be filled with E5's.

# 8. MACRO.LIB & SKEW.LIB

THIS LIBRARY IS NECESSARY IF YOU HAVE DIGITALS MACRO ASSEMBLER AND WISH TO CHANGE AND ASSEMBLE DDUMP.ASM AND DTEST.ASM. THESE PROGRAMS USE MACROS.

# 9. STAT.COM (FOR CPM V1.4 ONLY)

THIS IS AN UPDATED VERSION OF THE STAT PROGRAM FOR THE ORIGINAL DISTURBUTION. IT FUNCTIONS THE SAME AS THE OLD ONE. THE ONLY IMPROVEMENT WAS TO MAKE IT DISPLAY THE CORRECT CAPACITY OF A DOUBLE DENSITY DISK. IT WILL STILL WORK SINGLE DENSITY.

#### 10. ABIOS24.ASM

THIS IS THE AUTO-DENSITY SELECT VERSION OF THE BIOS THIS BIOS WILL AUTOMATICALLY SELECT THE DENSITY OF THE DISK YOU ARE USING IN EITHER DRIVE, AND WILL ALLOW YOU TO CHANGE THE DENSITY AT IF YOU ARE GOING TO CHANGE THE DENSITY OF THE "A" DRIVE, YOU MUST HAVE A DISK WITH THE SAME SYSTEM SIZE AS THE ONE YOU REMOVED. FILE TRANSFERS FROM SINGLE TO DOUBLE OR DOUBLE TO SINGLE IS COMPLETELY = TRUE BEFORE YOU USE  $\mathtt{SET}$ DOUBDEN YOU MUST AUTOMATIC. ABIOS24.ASM, AS THIS IS THE ONLY WAY THE AUTO-DENSITY CAPABILITY OF PROGRAM KNOWS IT IS LOOKING FOR A DOUBLE DENSITY DISK IN ANY DRIVE. 11. 2ABIOS24.ASM

THIS IS THE AUTO-DENSITY SELECT VERSION FOR CPM V2.x AND THE NEW INTERFACE. THIS BIOS MUST BE USED WITH 2DBOOT24.ASM TO BRING UP PLEASE NOTE THAT 2ABIOS24 AND 2DBOOT24 ARE ONLY FOR CPM V2.x AND WILL NOT RUN ON CPM V1.4 OR CONVERSELY.

# \*\*\* NOTE \*\*\*

YOU MUST SET DMACNTL = TRUE IF YOU WILL BE RUNNING DOUBLE DENSITY at 2 MHz. 12. 2DBOOT24.ASM

THIS IS THE SECONDARY COLD START LOADER FOR CPM V2.x FOR USE WITH 2ABIOS24.ASM. SEVERAL EQU'S APPEAR IN THIS LOADER. DMACNTL -SETTING THIS TRUE WILL ALLOW THE PROGRAM TO BOOT IN THE SYSTEM CONTROL. IF FALSE, SYSTEM UNDER PROGRAM DATA TRANSFER. BOOTS DOUBDEN - SETTING THIS TRUE PUTS THE SPECIAL ID BYTE INTO GENERATION OF A DOUBLE DENSITY SYSTEM DISK THAT WILL BE BOOTED IN FROM DRIVE 'A'. SETTING THIS FALSE ALLOWS BUILDING A SYSTEM SINGLE DENSITY DISK. THIS BYTE IS HOW THE SYSTEM KNOWS WHETHER OR NOT A SINGLE OR DOUBLE DENSITY IS ON LINE.

# \*\*\*\* NOTE \*\*\*\*

IF YOU HAVE TROUBLE READING A SINGLE DENSITY DISK CONTROLLER, YOU MAY HAVE A DISK WITH THE WRONG SECTOR FORMATTING. TO THIS FIND OUT, TAKE ANOTHER DISK AND USE THE NEW FORMAT.COM FILE ON THIS DISK TO REFORMAT IT. THEN USING YOUR OLD CONTROLLER, TRANSFER ALL THE PROGRAMS YOU WISH TO SAVE FROM THE DISK THAT WOULD NOT RUN ON THE NEW CONTROLLER BOARD TO THE NEWLY FORMATTED DISK. WE REALIZE THAT THIS IS ALSO A REAL HASSEL TOO, BUT IT IS A NECESSARY EVIL. BESIDES, THE NEW FROMATTED DISK WILL STILL WORK WITH THE OLD CONTROLLER BOARD.

## \*\*\* NOTE \*\*\*

IF ALL ELSE FAILS, EVEN AFTER READING THE DIRECTIONS, FEEL FREE HERE AT TARBELL ELECTRONICS. AND IF YOU WOULD LIKE TO CALL ME DISCUSS ANYTHING ABOUT THE BOARD OR SOFTWARE, CALL ME.

THANKS FOR INPUTS AND OUTPUTS ON THIS PRODUCT AND HOPE YOU FIND THIS PRODUCT BOTH INFORMATIVE AND FUN TO WORK WITH.

> GERALD.W.MULCHIN ENGINEERING DEPT. TARBELL ELECTRONICS 213 538 4251

#### GENERAL THEORY of OPERATION

The internal operation of a floppy disk operating system is probably the most complicated part of a micro-computer system. The hardware and software interact very closely, and therefore a very strong knowledge of 8080 assembly language and common logic operations is desirable to understand this section. Knowledge of the IEEE S-100 standard is also desirable, as there are some changes that have been made to the S-100 bus with this new specification. The IEEE S-100 Standard has been enclosed with this manual in the appendix, along with the data sheets for the rest of the integrated circuits used on the interface.

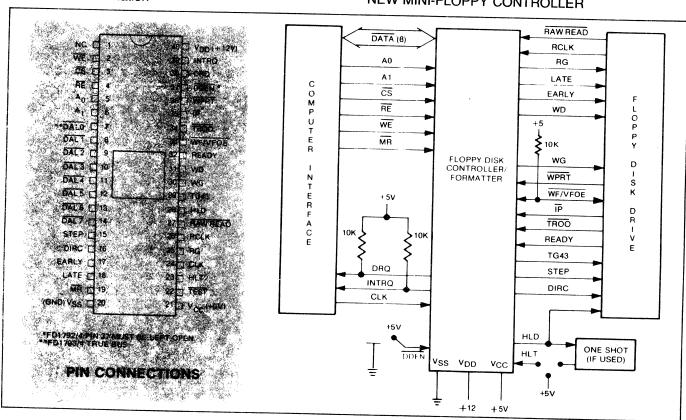

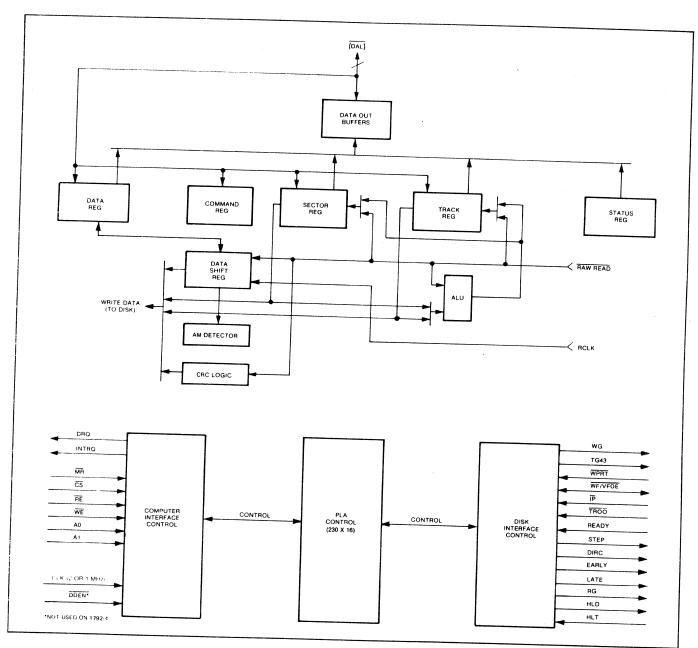

The heart of the Double Density interface is the 1791/1793 Floppy Disk Controller Chip. This chip is very similar to the 1771 in operation, but now includes all the functions necessary to run Double Density. For your convenience, the 1791/1793 data sheet is included in the appendix.

The interface may be broken down into subsections as follows:

- 1. 1791/1793 disk controller chip.

- 2. 8257 Direct Memory Access Controller chip.

- Phase Locked Loop circuit.

- 4. Write Precompensation circuit.

- 5. General Drive and Computer interface.

The 1791/1793 controls the actual reading or writing to the floppy disk, and in which density this will happen. The floppy controller chip contains 4 internal registers which are programmed by the computer through it's data and address lines. the four registers are as follows:

- 1. status register

- 2. track register

- 3. sector register

- 4. data register

Review of the data sheet will help in understanding each function of these 4 registers.

DDEN is used to control in which density the floppy disk controller chip will be operating. Low equals Double Density, High equals Single Density.

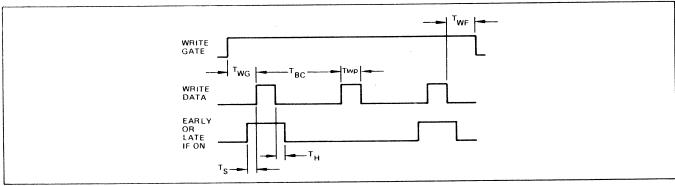

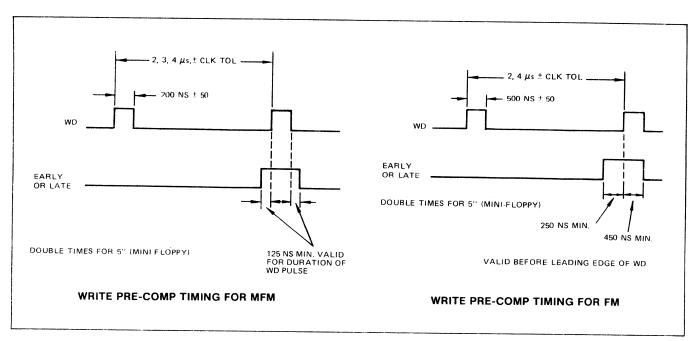

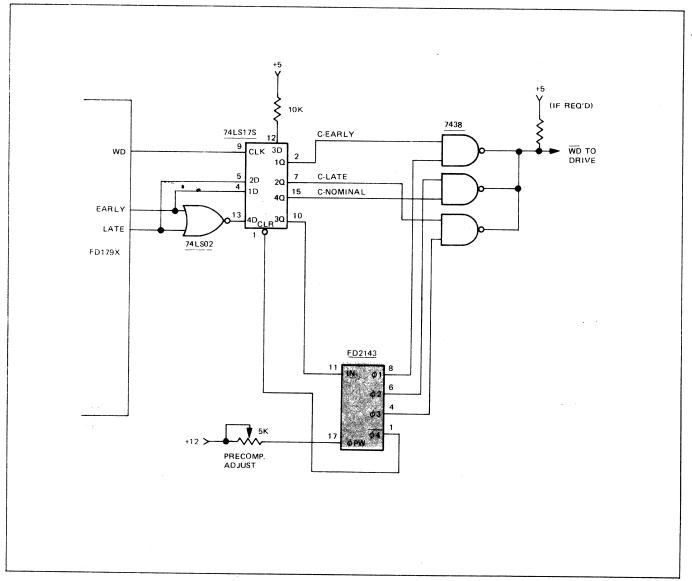

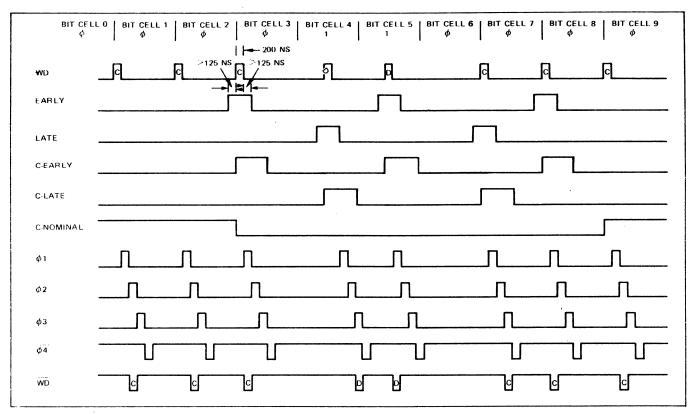

EARLY and LATE control the Write Precompensation of the data being written to the disk. These two signals along with the TRK > 43 line control the amount of shift in time the bit that is being written to the disk is subjected. Precompensation during writing is a must because of the bit packing on the medium of the disk.

This interface also has provisions for precompensation on tracks < 43, and it is recommended that a small amount be used. The amount of precompensation is a switch selection, and will be explained in the jumper options.

READ GATE is an output used for synchronization of the data seperator circuit during read operations. A high on this pin indicates

that a field of 'ones' (or zeros) has been found in the inner record gaps of the disk.

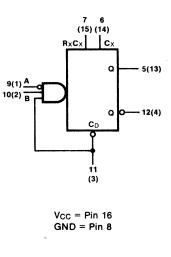

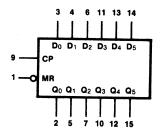

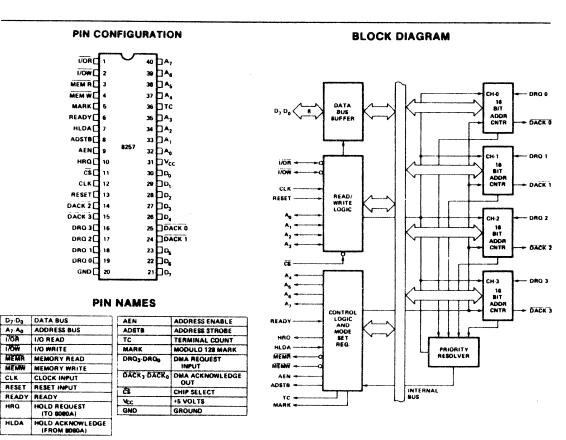

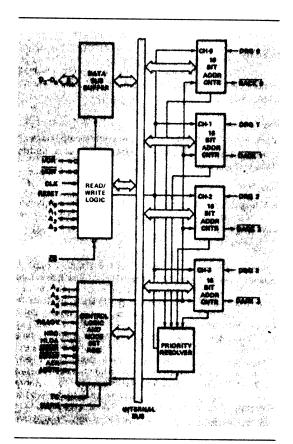

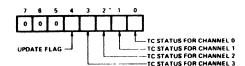

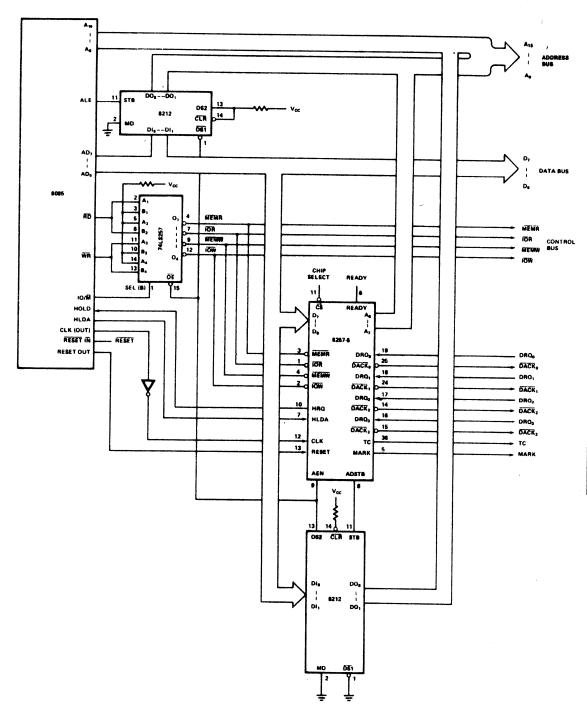

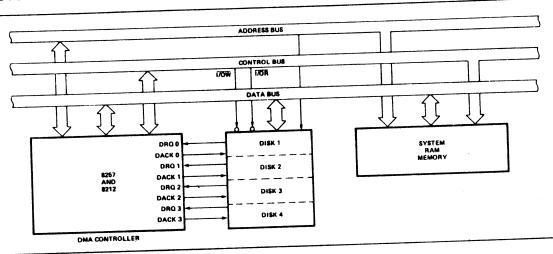

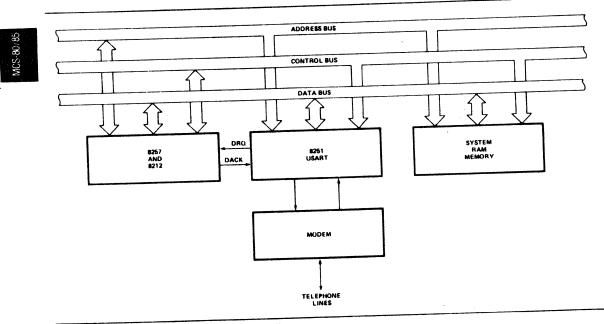

The 8257 Direct Memory Access Controller chip controls the of computer data between the disk and computer. This device can be thought of as a high speed semi-intelligent cpu It contains 16 registers of which only 3 are used by this operation. floppy disk interface board. One is a command register, and the other two are byte pair data registers. During read and write operations, the 8257 must be initialized with the byte transfer count, the address of where the data is to go, and the type of transfer that is to occur, such as read or write. The 8257 can transfer up to 16384 bytes and put it into any memory locations within a normal 8080's addressing range. The important aspect about the 8257 is that it will transfer data to or from memory without the need of intervention other than being initally programmed by the cpu. After it been programmed, it alone transfers the data, and in fact removes cpu from the S-100 bus during these transfers. information about the 8257 is available in the INTEL data catalog and in the appendix of this manual.

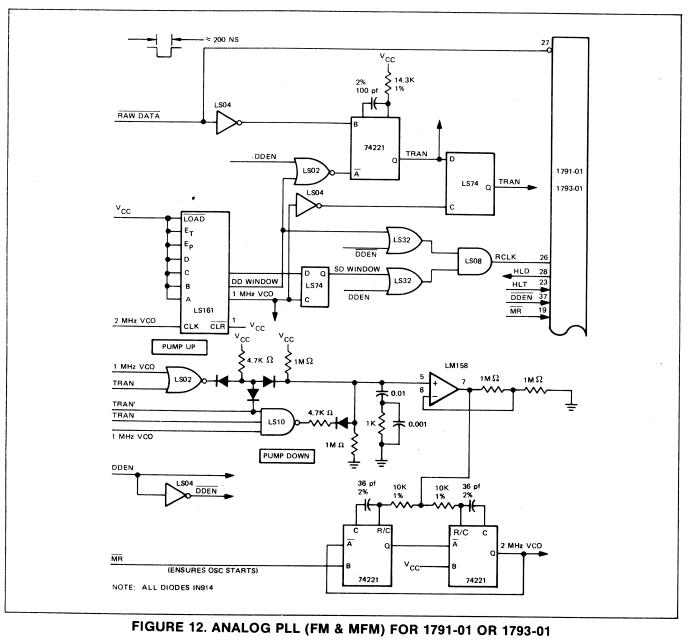

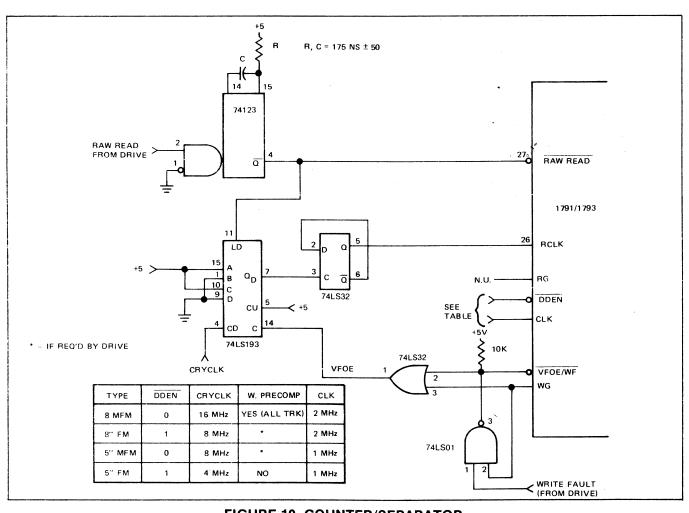

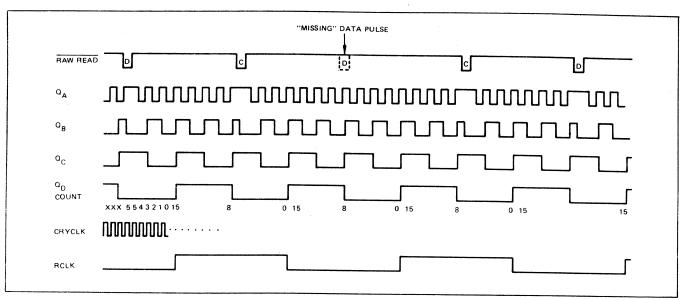

The Phase Locked Loop circuitry on this interface is necessary for reliable data recovery, especially while running under double density. It's function is to remove effects of data fluctuations during READ operations which may be the result of drive speed or power line changes, and general system noise. The Phase Locked Loop is used during Single and Double Density operation. This is accomplished by logic on the interface and is controlled by the DDEN line and an internal hardware latch. Tri-state switching is used to select the master oscillator timing clock. When in Single Density, the master clock is equal to 8 Mhz. Double Density selection causes the master clock to change to 16 Mhz. A close examination of the schematic will show these logic changes during density selects.

The write precompensation is in general terms really a count down circuit, controlled by the EARLY, LATE, and TRK > 43 lines during writing operations. This applies only when operating in double density, as the EARLY and LATE signals are not active during single density. The count down circuit is clocked by the 16 Mhz oscillator circuit. The amount of precompensation is determined by the preset value jammed into the 74LS161 from the EARLY or LATE of the floppy chip. After this value is loaded, the 74LS161 counts until it reaches zero, at which time it writes the data to the disk. effect of this is to delay the time the bit would have been written to the disk, until it is actually written. The smallest amount of precompensation that may be realized from this circuit is: 1 / 16 Mhz = 62.5 nsec.

Jumpers provided on the interface have been selected for optimum drive performance. Selection is based on manufacturer's recommendations for the drive in use, and our testing here at Tarbell Electronics.

The computer interface for this board is based on the IEEE  $\,$ 5-100 bus interface specification. It is not radically different from the old S-100 bus design, and should run with most S-100 products on the

market. If you have any questions about your interface cards, check the section on S-100 compatible products in our manual.

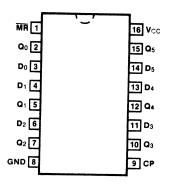

The Disk Interface occupies an address range from E0-EF hex for the DMA controller portion and F8-FD hex for the disk controller portion. A jumper is provided to allow the address range to be moved to 60-6F hex and 78-7D hex respectively, to avoid address conflicts with exsiting computer boards you may have in your system. This is explained in the jumper options section. The address ports are used as follows:

```

E0 hex 8257 address register (must be two bytes to this port)

E1 hex 8257 word count register (must be two bytes to this port)

```

E8 hex 8257 command register (1 byte)

F8 hex disk command port (input)

F8 hex disk status port (output)

F9 hex disk track port (input/output)

FA hex disk sector port (input/output)

FB hex disk data port (input/output)

FC hex wait control port (input)

FC hex drive select port (output)

FD hex DMA end of operation port (input)

FD hex extended address port (output)

The extended address port (FD hex), allows the DMA controller to transfer data to and from memory beyond the normal 64k range of the 8080 cpu. This function is avalible for both read and write operations using the disk interface. The extended address lines are provided on the S-100 bus as described in the IEEE S-100 bus interface specification. The extended lines are A16-A23.

To use the extended address function, user written software must supply an 8 bit value corresponding to the bank of memory you want to access, out to port FD hex before any read or write operations occur with the disk interface. During DMA operation, this 8 bit latch is enabled, placing its contents onto the extended address lines. The output of this latch is normally tri-state until the DMA controller becomes active. Also, this latch may be programmed at any time with any value you wish, except during an actual transfer by the DMA controller. You could even change this latch value between byte transfers if you wish. With optional decoding on memory boards, possible memory capacities can be theoretically 8 banks of 64k (512kbytes), to 256 banks of 64k (16 Megabytes).

The interface is set up for Shugart 8" compatible drives, which means drives with a Shugart interface such as Shugart 800/801 and Siemens FDD 100-8,120-8, and 220-8 will interface directly to the controller board. There are many drives which fall into this catagory and we will be supplying updates as we go along for your convenience. At this time we at Tarbell Electronics have run the Shugart 800/801 and all 8" drives made by Siemens. This includes both single and double density. Persci drives model 270/277's are now supported with this interface. See the section on jumpers for an explanation and changes which must be made to support Persci drives.

# DETAIL THEORY of OPERATION

This section of the manual will deal in depth with the theory of operation of the double density board. The explanation will be broken down into sections within the board design.

The following logic notation will be used: XX' = The logic name XX not, or the inversion of XX.

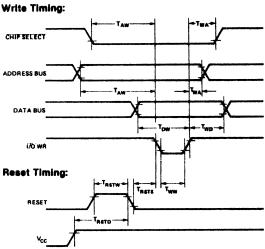

#### 1. RESET circuit

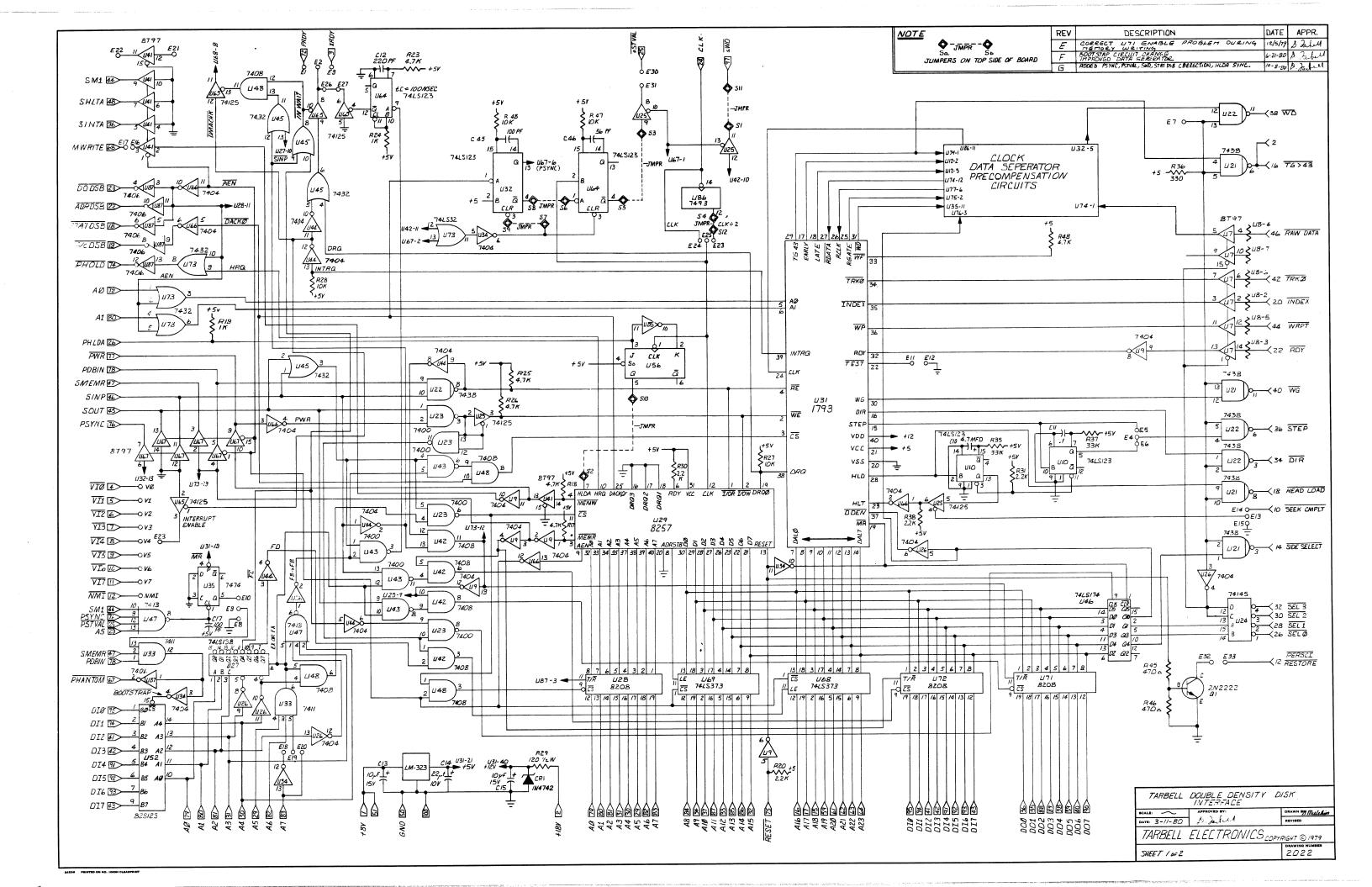

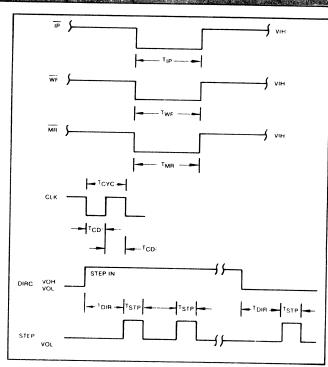

The floppy disk interface receives it's reset from line 75 (PRESET) on the S-100 bus whenever a power on sequence is initiated or whenever a RESET on the front panel of the computer is pushed. This line is active low (0) whenever a reset is pushed. The result of pushing a reset is to cause the floppy disk controller chip to do a restore of drive 0 to the home position, reset the DMA controller chip to the idle state, and the latch (U46), which is used for drive select, density select, and side select, to be cleared to the following condition, (a.) select drive 0, (b.) select single density, and (c.) select side 0.

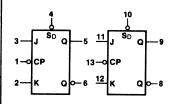

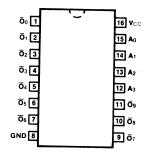

The reset line from the bus is first inverted by U9 (7404) to provide an active high (1) signal for the DMA controller chip U29 (8257). This signal is inverted again to provide an active low (0) reset for floppy controller chip, U31 (1791/1793), and for U46 (74LS174) an 6 bit latch. This active low reset signal also turns on the bootstrap circuit by pulling the preset line of U35 low.

#### 2. BOOTSTRAP Circuit

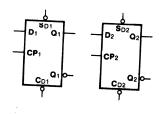

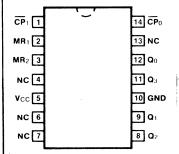

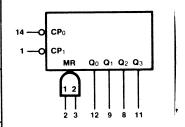

The bootstrap circuit is enabled during a power up sequence or the front panel reset switch. The reset causes a preset of flip-flop U35, a 7474 D-toggle flip flop, causing it's output, pin 5, to go high (1). This output is tied to one of three (3) inputs of U33, a 7411 3-input AND gate. The two other inputs come from the S-100 bus interface pins 47 (SMEMR), and 78 (PDBIN). The output of U33 is tied to the input of a 7406 (U87), which drives the PHANTOM line (67) U33 also also drives a hex inverter U34, which drives the chip select line on the Bootstrap Prom low, enabling the data outputs of the prom on to the data bus. When run is enabled on the computer, the contents of the prom are read onto the data bus and into the cpu Because this prom is only 32 bytes long, the method of instructions. disabling it when it has completed all its instructions, is to look at address line 5 of the S-100 bus. This address line is fed to one inputs of U47, a 7421 4-input AND gate. The other three (3) lines in to U47 are PHASE 1 (25), PSYNC (76), and SMI (44). computer has read all 32 bytes of the prom, and an attempt to read the 33rd byte is tried, address line 5 will go high (1), which causes one input of U47 to go high. The three other inputs of U47 will high, causing its output to go high. This output line then causes the output of U26, a 7404 inverter, to go LOW (0), resetting U35. When this flip flop is reset, its output, pin 5, will go low, disabling both the PHANTOM line and the Bootstrap Prom chip select. This action releases the the bus data lines back the their normal operating condition. During power up of your system, if you wish to disable the bootstrap circuitry, and have a front panel, you may raise address-data switch 5 and hit examine. This will turn off the bootstrap circuit, allowing you to access all computer memory. The bootstrap may be defeated entirely by using jumpers E8 to E9 on the disk interface. Using jumpers E9 to E10 enables the bootstrap during each reset. Below is a listing of the bootstrap prom for both the standard Tarbell disk ports, and for our non-standard disk ports. Our Model 101 is for people who wish to run the disk interface at addresses 60 to 7D hex.

# STANDARD PROM BOOTSTRAP LISTING

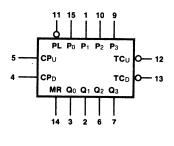

| 0000<br>00F8 =<br>00F8 =<br>00F8 =<br>00FA =<br>00FB =<br>00FC =<br>007D =                                                                                                        | ;<br>DISK<br>DCOM<br>DSTAT<br>SECT<br>DDATA<br>WAIT<br>SBOOT | EQU<br>EQU<br>EQU<br>EQU<br>EQU | DISK+2<br>DISK+3<br>DISK+4                 | COMMAND PORT.  DISK STATUS PORT.  SECTOR PORT.                                                                                                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000 DBFC 0002 AF 0003 6F 0004 67 0005 3C 0006 D3FA 0008 3E8C 000A D3F8 000C DBFC 000E B7 000F F21900 0012 DBFB 0014 77 0015 23 0016 C30C00 0019 DBF8 001B B7 001C CA7D00 001F 76 | BOOT: RLOOP: RDONE:                                          | ORA JP IN MOV INX JMP           | A SECT A,8CH DCOM WAIT A RDONE DDATA M,A H | ;WAIT FOR HOME.(caused by reset) ;CLEAR ACCUM. ;CLEAR REG L. ;CLEAR REG H. ;SET A = 1. ;START AT SECTOR 1. ;READ THE SECTOR. ;ISSUE THE COMMAND. ;WAIT FOR DRQ OR INTRQ. ;SET FLAGS. |

| NON-STANDARD                                                                                                                        | BOOTSTRAP                              | PROM                                                    | LISTING                                                                     |                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000                                                                                                                                |                                        | ORG                                                     | 0                                                                           | ; PROM RUNS AT LOC ZERO.                                                                                                                                                                                                                                                                                                 |

| 0078 = 0078 = 007A = 007B = 007C = 007D =                                                                                           | DCOM<br>DSTAT<br>SECT<br>DDATA<br>WAIT | EQU<br>EQU<br>EQU<br>EQU                                | DISK<br>DISK+2<br>DISK+3<br>DISK+4                                          | ;BASE ADDRESS OF DISK PORTS. ;COMMAND PORT. ;DISK STATUS PORT. ;SECTOR PORT. ;DATA PORT. ;WAIT PORT. ;START OF SBOOT.                                                                                                                                                                                                    |

| 0000 DB7C<br>0002 AF<br>0003 6F<br>0004 67<br>0005 3C<br>0006 D37A<br>0008 3E8C<br>000A D378<br>000C DB7C<br>000E B7<br>000F F21900 | BOOT: RLOOP:                           | IN XRA MOV MOV INR OUT MVI OUT IN ORA JP IN MOV INX JMP | WAIT A L, A H, A A SECT A, 8CH DCOM WAIT A RDONE DDATA M, A H RLOOP DSTAT A | ;WAIT FOR HOME.(caused by reset) ;CLEAR ACCUM. ;CLEAR REG L. ;CLEAR REG H. ;SET A = 1. ;START AT SECTOR 1. ;READ THE SECTOR. ;ISSUE THE COMMAND. ;WAIT FOR DRQ OR INTRQ. ;SET FLAGS. ;DONE IF INTRQ. ;ELSE,GET A BYTE FROM DISK. ;PUT IT INTO MEMORY. ;BUMP POINTER. ;LOOP TILL DONE. ;READ DISK STATUS. ;SET THE FLAGS. |

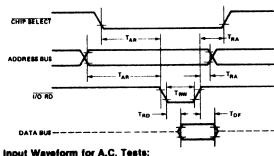

#### 3. ADDRESS SELECTION

The double density controller board is selected based on the low order 8 address line values presented to the interface during an input or output instruction. The normal address range for this board is from EO hex to FD hex. There are provisions for changing the address range from 60 hex to 7D hex by means of jumpers E4,E5,and E6.

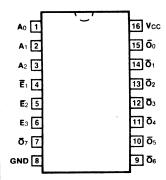

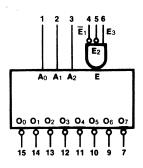

The base address for the DMA controller (8257) is EO hex, with all possible 16 address from EO to EF hex available for use by the DMA controller chip. U33, a three input AND gate, is used to determine the base address of EO hex by tying address lines A7,A6,and A5 to its three inputs. You will notice that an inverter, U34, is in between one input of U33, and address line A7. By selecting the proper jumper at E4,E5, and E6, you may select a base address of either EO hex or 60 hex. By using the inverter, U34, you will select the base address of 60 hex. By not using the U34, but using the jumper which bypasses U34, you will select a base address of EO hex. The output of U34 is next

AND'ed with the inversion of A4 through U26. This gate (U48) is used to allow selections from E0 hex to EF hex for I/O operations with the DMA controller. The output of U48 drives one of the inputs to U43 for selecting the DMA controller chip select line. The other input for U43 (7400), comes from U45 (7432). U45 determines whether the current I/O operation is an Input or an Output with the interface board. The signals SINP and SOUT are two status lines from the CPU card used to determine the I/O operation. Because these two signals will not occur together, they may be OR'ed together through U43 to provide just one general signal for I/O operation decoding.

Disk I/O ports for the 1791/1793 floppy controller chip are decoded by U47, a 4 input AND gate. One input to U47 comes from U33's output, which is the address decode for the base address of Ex hex or 6x hex. Address lines 4 and 3 are tied to two of the other inputs of U47. Address line 2 is inverted through U26 (7404) and is the fourth input to U47. The Output of U47 goes high whenever any of the following address appear on the address bus, F8, F9, FA, and FB hex.

Ports FC and FD hex are decoded by U27 (74LS138). The output of gate U33 is used for the enable input of U27. The other two enables of U27 are an enable when low function and are derived from the inversion of address lines 3 and 4 through two inverters U26. The output of inverter U26 pin 10 also goes to one input of gate U48. If address line 4 is high (eg. Port FC), The output of U26 pin 10 will be low (0), causing the output of gate U48 to be low, disabling the selection of any port with the base address of Ex hex. The 3 low address lines, A0, A1, and A2 determine which port is selected on the output of U27. Also, even though the low 3 lines of the address bus are used by U27, only two of the possible 8 ports are used by the disk interface board. Port decodes from U27 for F8, F9, FA, and FB are not used. Only Ports FC and FD hex are used.

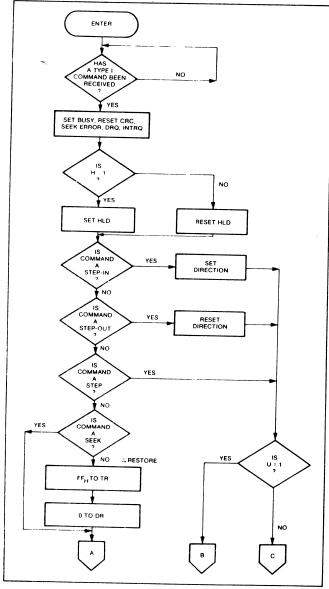

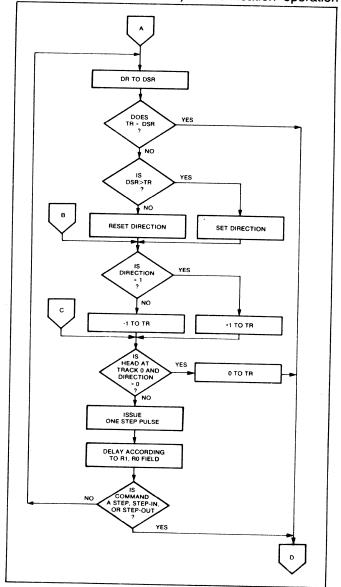

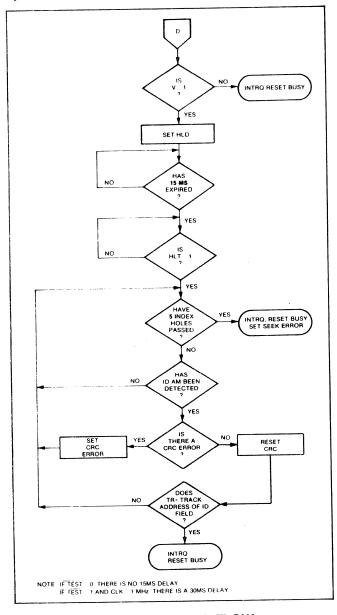

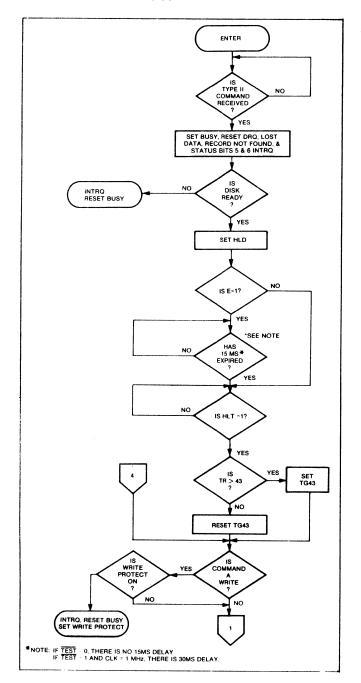

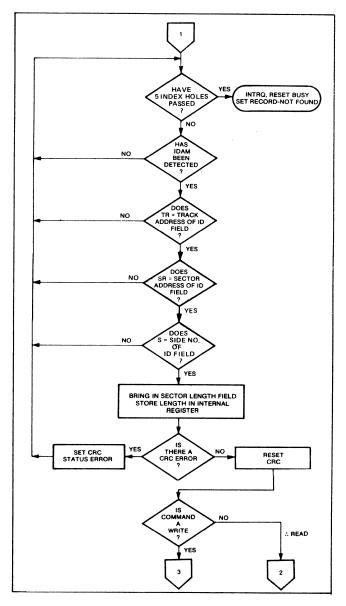

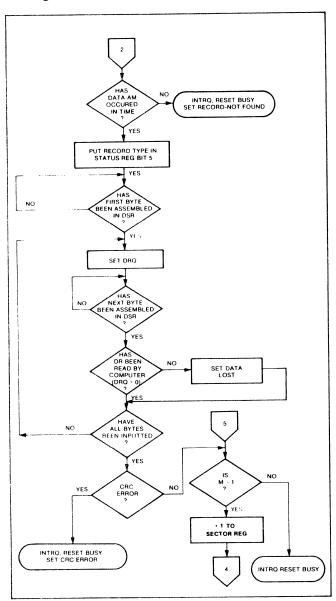

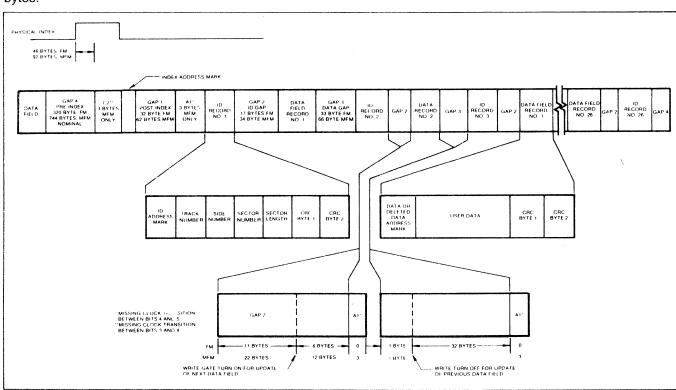

#### 4. DISK CONTROL circuit

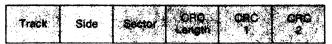

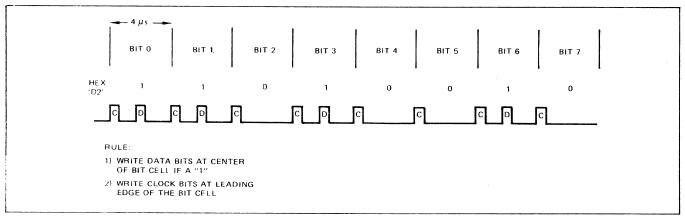

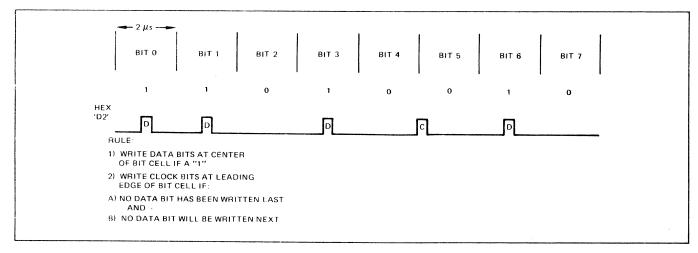

The 1791/1793 Floppy disk formatter/controller chip performs all the functions necessary to read or write data to a floppy disk drive. Both single and double density storage capabilities are supported. The chip is compatible with the IBM 3740 (FM) data format, IBM System 34 (MFM), or may be operated non-standard by using the controllers variable length sector capability.

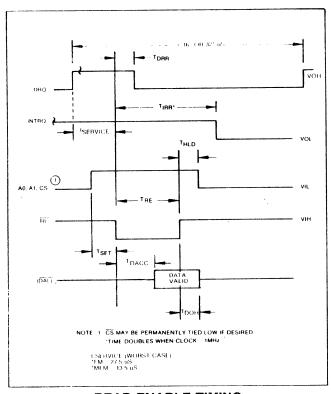

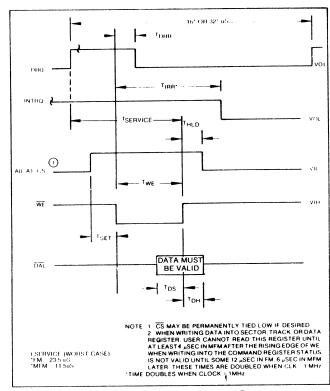

The floppy controller chip contains five (5) internal registers that can be read or be written to. These registers are used to write commands, read status, and read and write data to and from the floppy disk drive. These five registers are selected by providing the proper binary code on the AO and Al lines of the floppy chip in conjunction with either a read or write operation. The registers and their addresses are as follows:

#### DETAIL THEORY of OPERATION

| 0 0 0 Status Reg Command Reg 0 0 1 Track Reg Track Reg 0 1 0 Sector Reg Sector Reg 0 1 1 Data Reg Data Reg | CS'                   | Al                    | <b>A</b> 0 | $RE^{1} = 0$            | WE ' = 0                |  |

|------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------|------------|-------------------------|-------------------------|--|

| 1 x x Deserected Deserected                                                                                | 0<br>0<br>0<br>0<br>0 | 0<br>0<br>1<br>1<br>x |            | Track Reg<br>Sector Reg | Track Reg<br>Sector Reg |  |

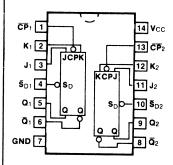

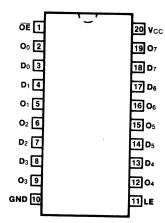

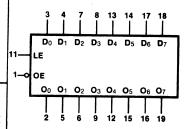

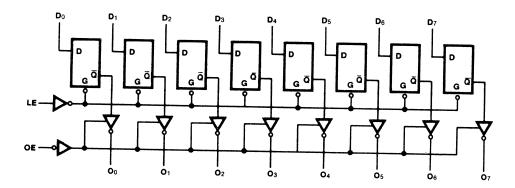

The five internal registers of the floppy controller chip are through the internal interface data bus. The internal data bus is buffered by U71 (8208) and U72 (8208). U71 and U72 are 8 bit bi-directional transcievers which are used as bi-directional data buffers between the computer S-100 bus and the floppy disk interface internal data bus. These transceivers allow data travel in either direction depending upon whether the TRANS/REC' pin (11) is high or low. To program the floppy controller chip, AO,Al are selected for the desired operation. Write enable of U31 is made active low processor signal SOUT and PWR' gated together by U23 (7400). The data that the CPU wishes to program the floppy controller with, is now placed on the DOO - DO7 lines of the CPU card. This data is then presented to U71. Because we are not in the DMA mode of operation, the TRANS/REC' pin is already pulled low, causing the transceiver to be in receive mode. The data is then passed through U71 onto the internal data bus and into the floppy chip DALO - DAL7 lines. select, pin 3, of U31 is made active low by U48 (7408) output. One input of U48 comes from the DMA controller and the other input is from U43 which is the gating of the address port and the I/O mode desired. In this case, since we are programming the floppy controller, any port address in the range of F8 - FB hex gated together with SOUT will cause the data to be written to the controller chip.

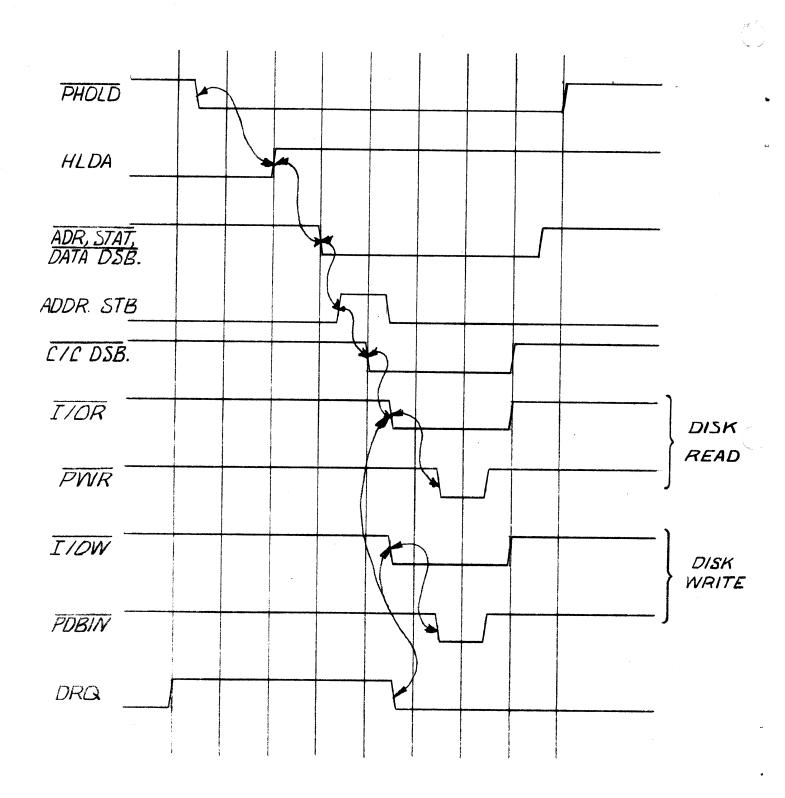

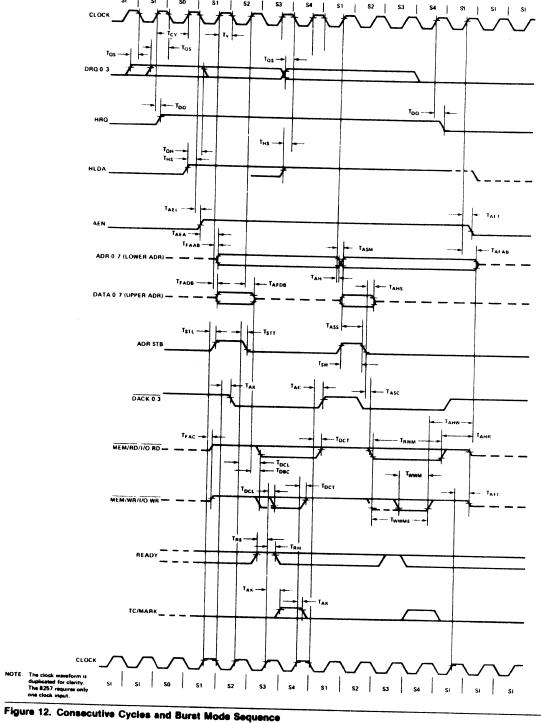

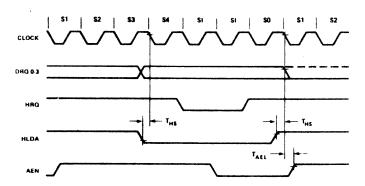

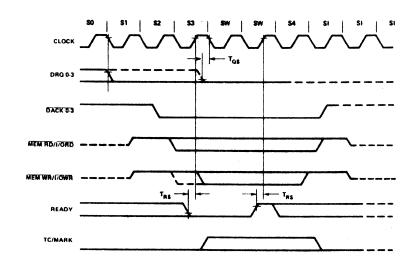

## 5. Direct Memory Access

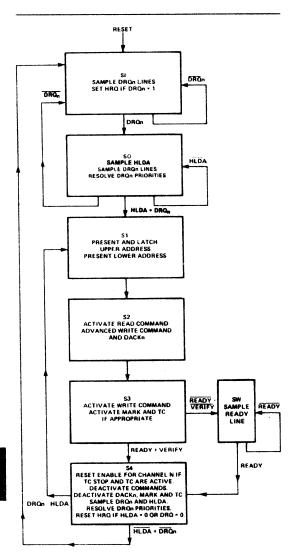

The sequence of operations for a DMA access is as follows:

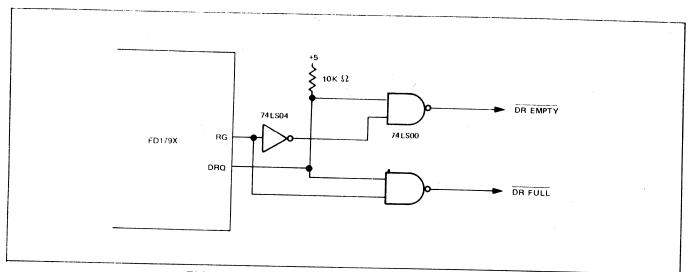

- A. The Basic Input Output System (BIOS part of CP/M) program sends a series of initialization bytes to the 8257. These include the starting address in memory for the data, the number of bytes to transfer, and the type of command (read, write, verify) which is being requested. The port numbers for these and other transfers are listed on page 3-3 in this manual.

- B. The BIOS then sends track number, sector number, and type of command (read or write) to the 1793.

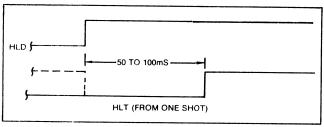

- C. The 1793 then causes the head to load against the media (we are assuming we're already on the correct track). When the 1793 finds a sector header that matches the track and sector number in it's registers, and is ready to write or read the first byte, it activates its DRQ line, which is fed to the 8257. This signifies that it is ready to transfer a byte.

- D. Soon after receiving the input on its DRQO line, the 8257 makes its HRQ line go high. This is fed through an OR gate

- to S-100 bus line PHOLD'. This notifies the CPU that there is a DMA request pending.

- E. When the CPU finishes the cycle it is currently in, it sends back a PHLDA signal over the S-100 bus to the HLDA input on the 8257. This tells the 8257 that its DMA request has been granted, and that the CPU is in a HOLD state.

- F. The 8257 then activates its AEN line, which indicates that it has a valid address on AO to A7 and DO to D7. This signal is ORed with the HRQ to keep PHOLD' active, and disables the CPU address and data lines using S-100 bus lines DO DSB' and ADR DSB'. AEN also is fed to (U41) and (U67), which gates the DD board's own status and control lines onto the S-100 bus (PWR', PDBIN, SMEMR, SINP, SOUT, PSYNC, MWRITE, SINTA, SHLTA, SM1).

- G. A short time later, the 8257 activates its DACKO' line, which disables the CPU's status and control lines, using S-100 bus lines STAT DSB' and C/C DSB'. The time between step F and G provides the overlap time, during which both our DD board and the CPU board have control of these status and control lines.

- H. At the same time as the DACKO' line is activated, the 8257 activates either its MEMR' line, or its I/OR' line, depending upon whether it's going to do a write or read respectively, to disk. Step I will explain what happens for a write operation, Step J for a read (from disk) operation.

- I. For a write operation: The MEMR' line coming from the 8257 is used for several things. It is fed through U67 to S-100 lines PDBIN and SMEMR to the system memory to gate the memory onto the S-100 bus. It is also used to activate U72 so that the S-100 DI bus is fed into the DD board's internal data bus and therefore providing a path from the memory output to the 1793. A short time after the MEMR' signal, the I/OW' signal is fed from the 8257 to the WE' input on the 1793, which strobes the data into the 1793. The 1793 then writes the data onto the disk.

- J. For a read operation: The I/OR' signal from the 8257 is fed to the 1793, gating the data in its register onto the data bus. This signal is also used to activate U71 in the outward direction, so that the data is fed onto the S-100 DO bus out to the system memory. (mod for rev-e) A short time after the I/OR' signal, the MEMW' signal is generated by the 8257. This is used to generate the S-100 bus line PWR', which strobes the data into memory.

- K. After either step I or J above, the reverse sequence occurs, turning over control of the bus back to the CPU.

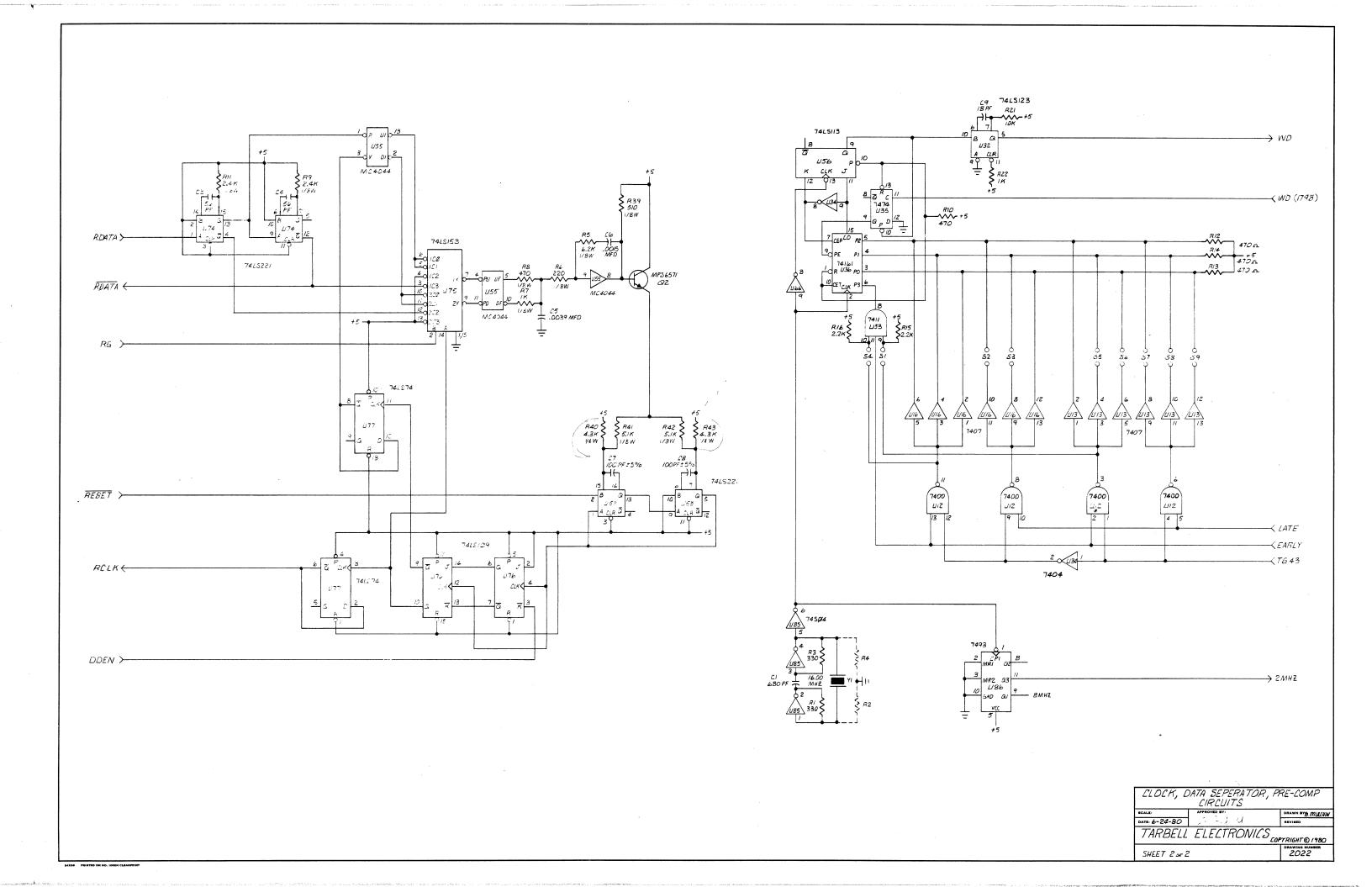

#### 6. Write Precompensation

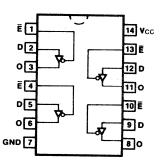

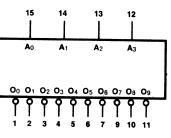

The Write Precompensation circuit consists of a programmable counter, (U36), for delaying or advancing write data pulses during disk writes, a dip switch (SW-1) for adjusting the precompensation value, and the necessary decoding logic for early, late, and TRK > 43 (U12).

#### DETAIL THEORY of OPERATION

The 1793 produces along with it's write data pulses, two signals called 'early' and 'late'. These two signals, along with TRK > 43, are decoded by a 1 of 4 decoder circuit (U12) to select the switch setting from SW-1 for loading into the counter (U36).

Loading the counter starts the counter down counting. If there is no early or late signal generated (no precomp needed), the programmable counter is loaded with a positive (0111) 7, which is the zero precompensation center reference value.

Values from (0110) 6 through (0000) 0 are increasing late times, and values (1000) 8 through (1110) -2 are increasing early times. The programmable counter is clocked with 16 MHz during double density. Therefore, the minimum resolution is 62.5 nsec.

After the counter has been loaded with the desired value of precompensation, the counter down counts until a carry is produced. The carry, delayed one (1) clock cycle by a D-toggle flip-flop(U35), is used to trigger a 250 nsec. one-shot. The output of the one-shot, after buffering, is the precompensated data which is written to the drive. The counter then remains stopped until a new data pulse is sent from the 1793, starting the whole process again.

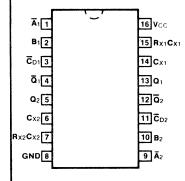

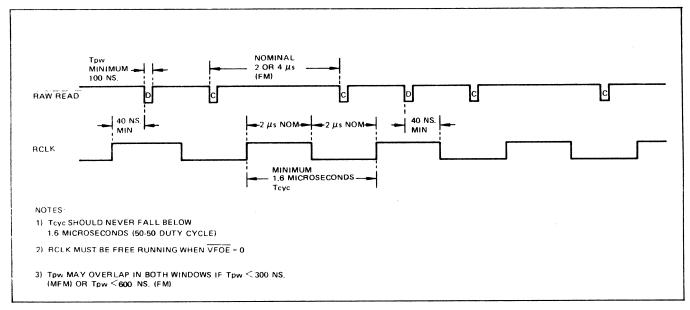

## 7. Data Recovery

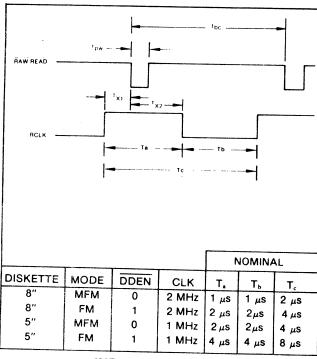

Data recovery is provided by an on board Phase Locked Loop circuit. This circuit allows for maximum data recovery reliability, while rejecting drive speed variations and bit crowding. One shot (U74) conditions the data being read from the disk and provides RDATA\* to the 1793. It also provides data to the phase comparator (U55) which is part of the phase locked loop. The active filter network which consist of U55,R5,R6,R7,R8, C5,C6 and Q2 removes noise and jitter from the incoming data and provides a correction voltage to the voltage controlled oscillator (U53). This oscillator provides the master clock frequency necessary for a stable read clock signal (RCLK) for the 1793. This output is either divided by 2 or divided by 4, controlled by the DDEN line, to provide the necessary 500 KHz or 250 KHz RLCK signal for double density or single density operation.

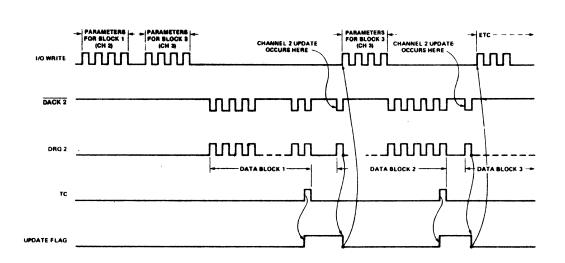

# DMA READ/WRITE CYCLE

500 NSES / DIV

### ASSEMBLY INSTRUCTIONS

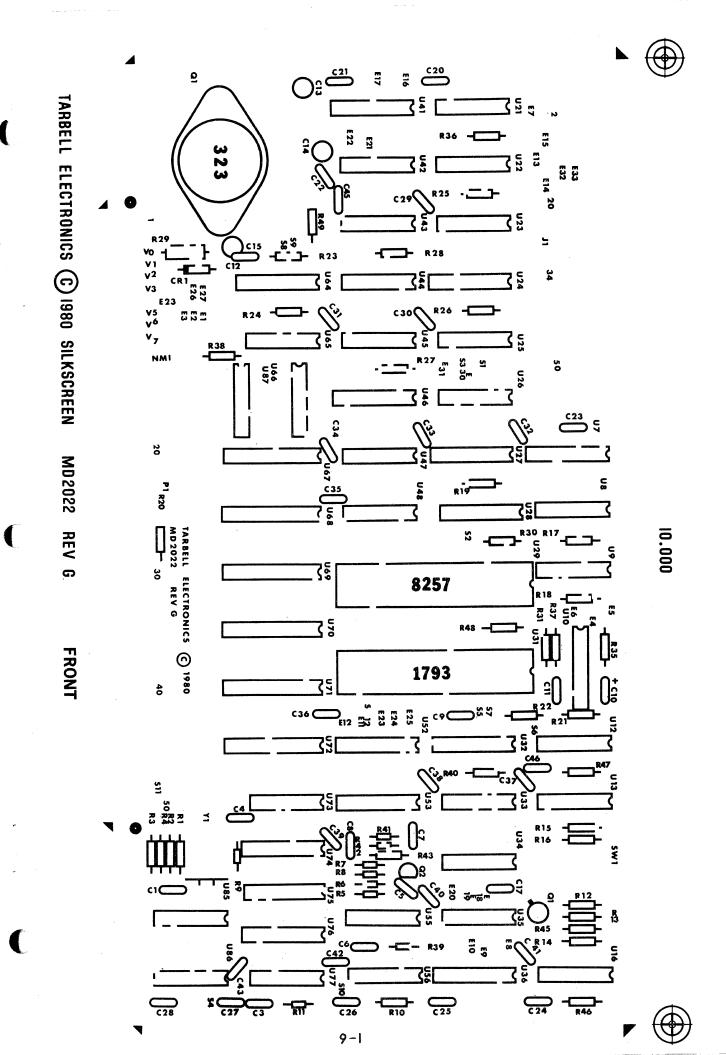

Before attempting any assembly operations, it is recommended that you read this section and the parts list section first. This will help put your mind into a comfortable state about what you are going to be doing with the board.

- 1. () Locate and confirm that your kit contains all the parts listed in the parts list in this manual. Any errors found should be reported to Tarbell Electronics for corrective measures. Also, you should make any necessary changes which you receive from Tarbell Electronics, on your board at this time.

- 2. ( ) If you are using sockets, install them at this time.

- 3. ( ) Locate the 50 pin header connector and install it at the top of using the 2 2-56 x 3/8 mounting screws and hardware.

- 4. ( ) Locate Q1, an LM-323 votage regulator, and the heatsink. Mount the regulator and heatsink on the board using the  $4-40 \times 3/8$  screws and hardware.

- 5. () Locate Q2, an MPS6571 transistor, and mount it as indicated by outline on the board.

- 6. () Locate the crystal, Yl, and mount it on the board. Mount the crystal down close to the board. Then take a small piece of wire and push it through the hole that is to the left of crystal, and solder it. Then, take the other end of this wire and bend it over the top of the crystal and cut off all but 1/8" of it. Then solder the wire to the crystal can. Do not over heat the crystal can, or you may open the hermetic seal.

- 7. () Using the parts list and using the board layout drawing, start mounting all the capacitors on the board. Be sure to observe the polarity of the tantalum capacitors Cl3,Cl4,Cl5. The little square block on the board is the end that the plus (+) lead of the capacitor goes into.

- 8. ( ) Using the parts list and board layout drawing, mount all the resistors on the board.

- 9. () Locate the dip switch and mount it. Note, if the dip switch you have has only 8 positions, you will have to mount the switch on the board starting at position 2 at the location on the board. There should be one open location at the top of the switch that is not used after you mount the switch.

- 10. ( ) Do not mount the IC's at this time, as you will need to check the voltage regulators for proper output voltages.

- 11.() After all the components are mounted, plug the board into your computer and check the voltage regulators for proper operation. CAUTION\*\* Be sure your computer is turned off before you plug in the board. The output of Ql should be approx. 5 volts +/- .5 volts. The output of CRl should be approx. 12 volts +/- .75 volts.

### ASSEMBLY INSTRUCTIONS

- 12.() Using the parts list and board layout drawing, mount the IC's into their respective locations. Use ''GREAT'' caution with the two 40 pin IC's when mounting them as it is possible to bend or break some of the leads on the part.

- 12.() This completes the assembly of the unit. On the following pages are the jumper options for setting up the board for your system.

This board has very little jumpering required to get it running. The only jumpers that need setup are for address selection, XRDY or PRDY line, Write Precompensation value, and drive type selection.

### 1. Normal Board Setup

The normal configuration is as follows:

- a. Board address set for base address of EO hex.

- b. PRDY line used for processor wait.

- c. SW-1 set for 62.5 nsec on trk < 43 and 187.5 nsec for trk > 43.

For normal operation with Shugart compatible drives, install jumpers as follows:

- ( ) El3 to El5

- ( ) E4 to E6 <-- normally etched on the board

### NOTE \*\*

The write precompensation may be the only adjustment you will have to make for your drives.

### 2. Address Selection

This board may be addressed in one (1) of two (2) address areas in your computer. Either an address range of 60 - 7D hex or E0 - FD hex may be selected. You should beware of existing computer boards in your system which use these address ports for I/O operations, as a conflict may exist. Our I/O section for CP/M uses an address range of E0 - FD hex, as does our Standard bootstrap prom.

|    | ] | POR' | Γ   | J |     |    |     |  |  |

|----|---|------|-----|---|-----|----|-----|--|--|

|    | - |      | -   |   |     |    |     |  |  |

| E0 |   | FD   | Hex |   | E19 | to | E20 |  |  |

| 60 | _ | 7D   | Hex |   | E19 | to | E18 |  |  |

### 3. XRDY or PRDY selection

Three possible configurations exist in the selection of the right line to use. These are, no front panel, front panel, and if you have a front panel, who made it.

No Front Panel Jumper E1-E2 or E3-E2

Imsai Front Panel Jumper E1-E2

Altair Front Panel Jumper E3-E2

### NOTE \*\*

Be sure that other boards in your system do not use either the XRDY or PRDY lines improperly, as this would cause improper operation of this interface board. Things to beware of are memory boards which

activate a tri-state driver in anticipation of memory wait states, or dynamic memory boards which require the use of this line for refresh operations, or memory boards which use slow memorys such as old, old 2102's.

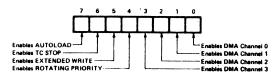

# 4. Write Precompensation Selection

The selection of the write precompensation is based on the type of drive you are using and the amount of errors you are getting from the disk when you run our special disk test program. To properly set the precompensation, first set the dip switch Sl for a value of 62.5nsec for < 43 and 187.5 nsec for > 43 as shown in the Precomp Table in Fig.1 Next, format a good certified double density disk with our DFRAND.COM program. Then read the disk for errors using our DTEST.COM program. If you find any errors, then change the precompensation switch settings to another value in the table and run the sequence again. The initial values of 62.5nsec for < 43 and 187.5nsec for > 43 were found to be midrange values here at Tarbell Electronics. These values are with the switch positions 5 and 8 on (if there is a 9 position switch), or positions 4 and 7 on (if there is an 8 position switch).

After you have found the proper settings for the precompensation switches, reformat the disk using the DFORMAT.COM program so that the disk will have the proper data in each sector required for CP/M operation. (E5 data fill)

SW - 1 settings

|        |       | Trk <  |    |    |       |   |       | <u>-</u> | Frk > 43                                 | 3<br> |       |   |

|--------|-------|--------|----|----|-------|---|-------|----------|------------------------------------------|-------|-------|---|

| -      | -Earl | y      | La | te |       | E | arly- |          |                                          |       | Late- |   |

| Pos    | 1     |        | 2  | 3  |       | 4 | 5     | 6        | * The Care Care (See Care Care Care Care | 7     | 8     | 9 |

| ns<br> |       | ns<br> |    |    | ns    |   |       |          | ns                                       |       |       |   |

| 62.5   | 1     | 62.5   | 0  | 0  | 62.5  | 0 | 1     | 1        | 62.5                                     | 0     | 0     | 0 |

| Х      | X     | х      | X  | Х  | 187.5 | 0 | 1     | 0        | 187.5                                    | 0     | 1     | 0 |

| X      | Х     | 250.0  | 0  | 1  | 250.0 | 0 | 0     | 1        | 250.0                                    | 0     | ī     | ĭ |

| X      | Х     | х      | x  | x  | 312.5 | 0 | Ō     | 0        | 312.5                                    | ĭ     | Ō     | ń |

| Х      | Х     | 375.0  | 1  | 0  | х     | x | x     | x        | 375.0                                    | ī     | 0     | i |

| Х      | х     | X      | х  | х  | x     | x | x     | x        | 437.5                                    | î     | 1     |   |

| х      | х     | 500.0  |    | 1  | x     | x | x     | X        | 500.0                                    | i     | i     | 1 |

FIG 1

Note: x = not adjustable, 1 = on, 0 = off

# 5. Bootstrap

The on-board bootstrap may be enabled or disabled by jumpers

E8, E9, and E10 as follows.

Bootstrap enabled - Jumper E9 to E10 Bootstrap disabled - Jumper E9 to E8

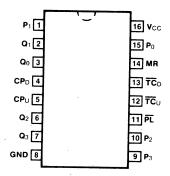

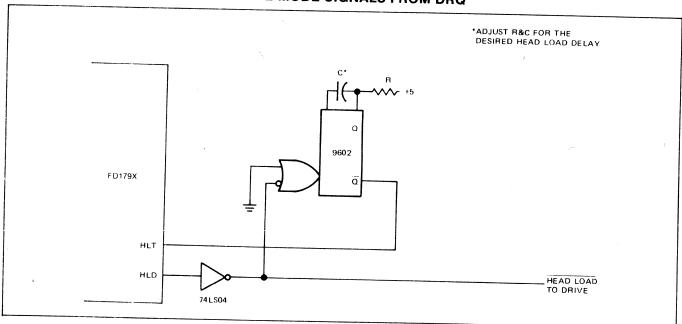

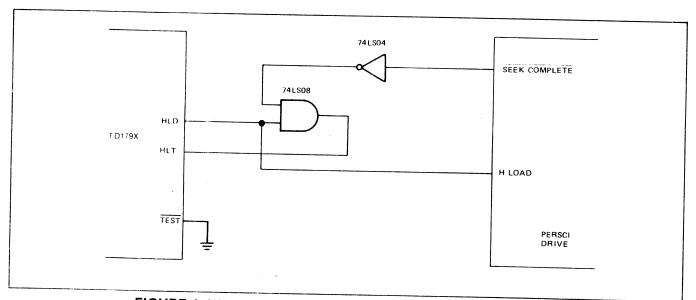

### 6. Persci drives

If you have a Double Density board Rev. D or Rev. E, and want to run a Persci model 277/270 with it, then do the following changes to the board.

- 1. On the double density interface:

- a. on back side, cut the trace connecting E4 to E6 and jumper E4 to E5. (bypasses step one-shot)

- b. Jumper Ell to El2. ( 1793 test pin)

- c. Jumper El3 to El4. (seek complete line)

Now you must make the Persci 277/270 look like a Shugart compatible drive. Thanks to John Mock of Bits & Bytes of Fullerton, we now have the all the changes. These are changes which you must make to the drive and in some cases will involve making trace cuts on the Persci drive.

# Cuts to make:

1. Trace to P1-16 (back side)

- 2. Trace between BL-BC (front side)

- 3. Trace between Ull-12 and Ull-13 (back side)

- 4. Trace between Ull-10 and Ull-11 (back side)

- 5. Trace from Pl-2 to Ul-8 (front side)

- 6. Trace to P1-30 (back side)

- 7. Trace to P1-32 (back side)

### Jumpers to add:

- 1. Ull-12 to P1-32 (back side)

- 2. Ull-10 to P1-30 (back side)

- 3. H to M (for head load)

- 4. H to BL (for head load)

Persci jumpers: (board assy.200263-007 rev N/S)

1() A - B 2() J - Z 3() K - L 4() N - P 5() T - S 6() U - V 7() BK-BM 8() BA-BB 9() AK-AH 10() X - W 11() AD-AE 12() AP-AR 13() AS-AT 14() AM-AN 15() BE-BD

Jumpers E-D and G-F and AC-AB should be open.

### Drive select:

| Drive 1 (A & B)            | Drive 2 (C & D)                         |

|----------------------------|-----------------------------------------|

| Ull 13 to 2<br>Ull 11 to 4 | Ull 12 to 2<br>Ull 10 to 4<br>Remove Ul |

Our bios packages for CP/M use with the double density board must have some of the equates changed for proper operation with the Persci 277/270, and 299.

In the bios change HLAB EQU 0 to HLAB EQU 8 for head load at beginning of seeks.

Set DUAL to TRUE as there are two heads moving together.

These changes were tried on our Persci model 277/270 here at Tarbell Electronics which has a revision number of N/S. We are not sure about other revisions which Persci makes or about there operation in Double Density. You should probably consult the factory about any revisions you have which do not agree with our own. Operation with the Persci has been quite good in Single Density operation on the new controller. But Double Density has been poor. This is probably due to the fact that our Persci 277/270 is not rated for Double Density operation. This is probably due to head design. Adjusting the precompensation may help some what.

# Persci 299 Jumpers

The Double density interface has provisions on the 50 pin drive connector at the top to allow the connector to modified for small differences between drive manufactures. In particular, Persci drives. You will notice that each connection has a double feed through hole with a short etch line connecting each end. By cutting this line with a sharp ex-acto blade, the line may may be be broken open. To allow the persci 299 to work with our interface, some of these lines must be cut, and jumpers put on for the differences between Shugart and Persci. Below is a list of cuts and jumpers to make to this connector.

CUTS

(revision C to revision F only)

Back side of board, cut trace connecting pin 2 and pin 16 of 50 pin connector. Front side of board, cut the following lines between feed-through holes:

| C hole | X cut | C hole |

Cut 2,4,6,8,12,14,16,18,24,30,32 as shown above.

Jumpers are referenced as being placed in a FROM - TO fashion as shown below.

|   | [      | Coni | necto | or]  |

|---|--------|------|-------|------|

| 2 | 4      | 6    |       | etc. |

| 0 | 0      | 0 -  |       | TO   |

| X | l<br>X | X    |       | cut  |

| 0 | <br>   | 0 -  |       | FROM |

| 1 | 1      | i    |       |      |

Jumpers to install:

| FROM | TO |

|------|----|

|      |    |

| 14   | 2  |

| 32   | 4  |

| 18   | 16 |

| 30   | 18 |

## 7. Interrupt option

Interrupts from the Floppy controller may be used to generate a interrupt to the CPU if desired. The large hole (E23) just above pin 8 of the S-100 connector is the output for the interrupt line. This is an active low signal and is normally tri-state. This line may be connected to any of the S-100 vector interrupt lines on the bus. You will need a vector interrupt card if you plan on using interrupts other than RST 7. The vector interrupt lines are defined in the S-100

standard on pages 10-1 to 10-5 of this manual.

### 8. MWRITE option

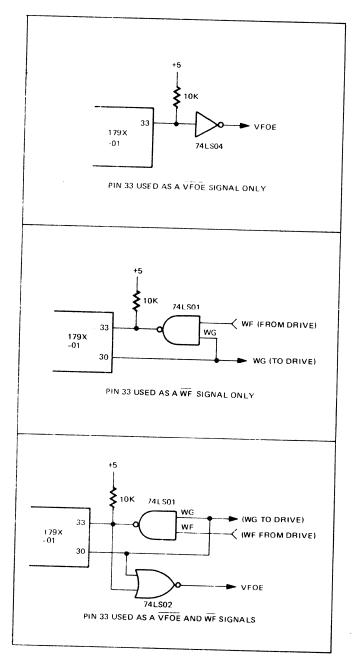

If your memory boards require the MWRITE signal to write data into memory, and this signal is not generated on the cpu or front panel, then you will have to jumper El6 and El7 together. If your memory boards use PWR' for writing data into memory, then leave El6 to El7 open.