# TANDBERG 5 <sup>1</sup>/<sub>4</sub> " Streaming <sup>1</sup>/<sub>4</sub>" Tape Cartridge Drive Maintenance and Parts Manual

## TDC 3319 Maintenance Manual

## TDC 3319 Maintenance Manual

Since this manual was produced while the TDC 3319 was still in its early stages, there are discrepancies between some of the descriptions in it and the actual product.

Most of them are known to us and will be corrected when the manual is updated. Nevertheless we would very much appreciate your corrections and comments. Please write or phone our Documentation Department at the address on the left below.

TANDBERG DATA A/S P.O. Box 9 Korsvoll N-0808 OSLO 8 NORWAY

Phone (47-2) 23 20 80 Telex 72633 tdata n

C 1984 Tandberg Data A/S

TANDBERG DATA INC. 571 N. Poplar, Suite H Orange, CA 92668 USA Phone 714-978-6771

Part no. 40306 Publ. no. 545 July 198 Revision no. Related publications available from our Sales Department:

| Publ. no. | Part no.         | Title                                                |

|-----------|------------------|------------------------------------------------------|

| 5446      | 402451<br>402508 | TDC 3319 Reference Manual<br>TDC 3319 Reference Card |

| 5447      | 402732           | TDC 3200 The GIC-24 and QIC-02 Standard, Revision D  |

1

This publication may describe designs for which patents are granted or pending. By publishing this information, Tandberg Data A/S conveys no license under any patent or any other rights.

Every effort has been made to avoid errors in text and diagrams. However, Tandberg Data A/S assumes no responsibility for any errors which may appear in this publication.

It is the policy of Tandberg Data A/S to improve products as new techniques and components become available. Tandberg Data A/S therefore reserves the right to change specifications at any time.

We appreciate any comments on this publication.

| 1.                              | READ THIS FIRST                            |

|---------------------------------|--------------------------------------------|

| 2.                              | A SHORT DESCRIPTION OF THE DRIVE           |

| 2.1<br>2.2                      | Illustrated Description                    |

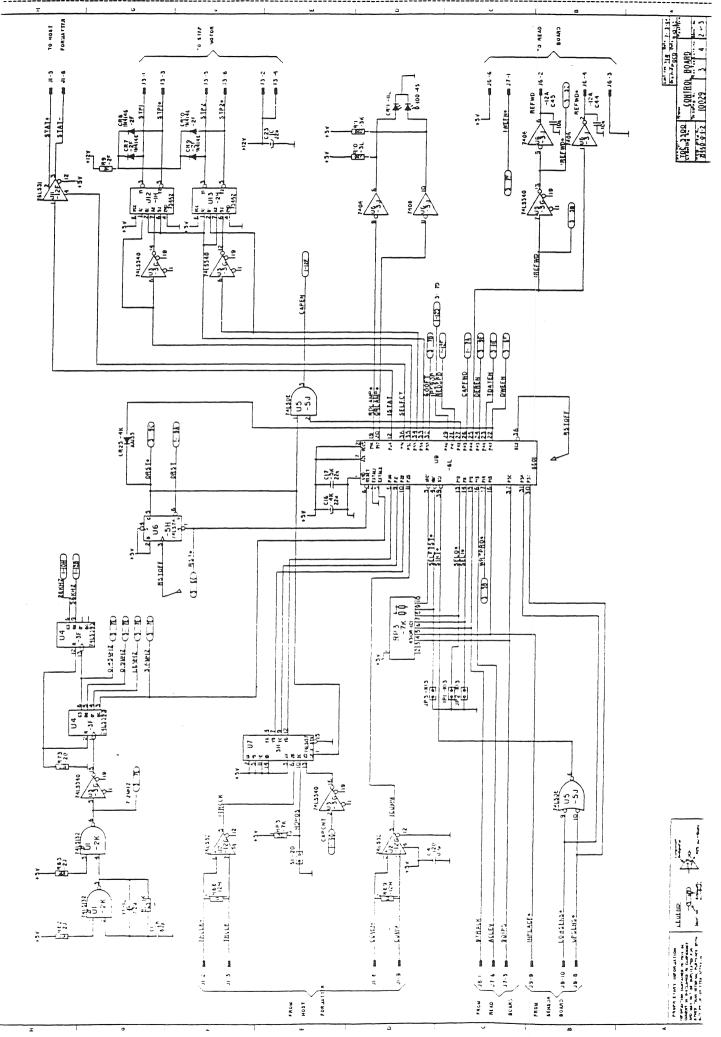

| 3.                              | BLOCK DIAGRAMS 8                           |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.5 | Overall Block Diagram                      |

| 4.                              | CONTROL BOARD                              |

| 4.1<br>4.2<br>4.3<br>4.4        | Description/Adjustments/Schematic Diagrams |

| 5.                              | READ BOARD                                 |

| 5.1<br>5.2<br>5.3<br>5.4        | Description/Adjustments/Schematic Diagrams |

| 6.                              | SENSOR BOARD                               |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5 | Description/Adjustments                    |

| 7.                              | FORMATTER BOARD                            |

| 7.1<br>7.2<br>7.3<br>7.4        | Description/Adjustments/Schematic Diagrams |

1

Continued overleaf

| 8.                                                          | MAINTENANCE                                                                                                                                                                                                                                                                                       | 58                               |

|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8<br>8.9 | Service Philosophy<br>Selftests<br>Power-up Selftests<br>Manually Activated Selftests<br>Host Activated Selftest<br>Head Cleaning<br>Necessary Hand Tools<br>Diagnostic Tools<br>Adjustments                                                                                                      | 58<br>59<br>61<br>62<br>62       |

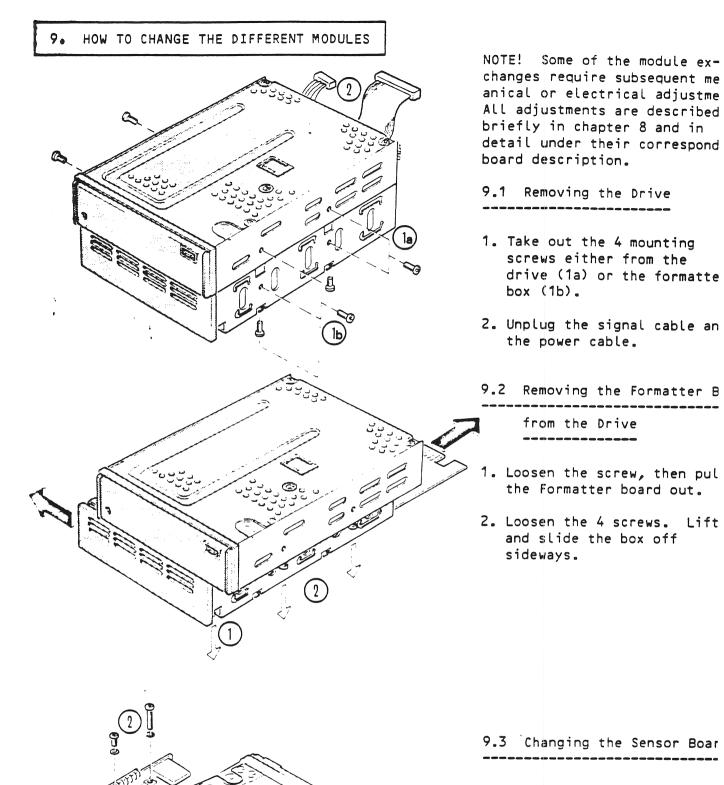

| 9.                                                          | HOW TO CHANGE THE DIFFERENT MODULES                                                                                                                                                                                                                                                               | 63                               |

| 9.1<br>9.2<br>9.3<br>9.4<br>9.5<br>9.6<br>9.7<br>9.8<br>9.9 | Removing the Drive<br>Removing the Formatter Box from the Drive<br>Changing the Sensor Board<br>Changing the Read Board<br>Changing the Control Board<br>Changing the Stepper Motor (and Door Assembly)<br>Changing the Capstan Wheel<br>Changing the Capstan Motor<br>Changing the Head Assembly | 63<br>64<br>64<br>65<br>66<br>66 |

| 10.                                                         | SPARE MODULE LIST                                                                                                                                                                                                                                                                                 | 68                               |

|                                                             | APPENDIX 1: The Basic Drive Command Set Summary (QIC-44) .                                                                                                                                                                                                                                        | 69                               |

|                                                             | APPENDIX 2: The Basic Drive Status Byte Summary                                                                                                                                                                                                                                                   | 70                               |

#### 1. READ THIS FIRST

This manual is intended for service technicians who have attended a Tandberg Data service course on TDC 3300 drives.

To avoid a lot of double work and to save space, we have left out of this manual such descriptions of the drive that are already given in the "TDC 3319 Reference Manual" (part number 402451, publication number 5446). We therefore strongly recommend that the reference manual be considered a part of the maintenance manual, and that you use it as a source of details that this manual does not supply.

This manual can be regarded as divided into three main parts. The first part (chapters 1, 2, and 3) gives a general description of the drive. It comprises an illustrated description, an interconnection diagram and block diagrams.

The second part (chapters 4, 5, 6, and 7) contains schematics, parts lists, mnemonics lists, and component location drawings of each printed circuit board. Adjustments, where relevant, are dealt with in the description of each schematic diagram.

The third part (chapters 8, 9, 10, and appendix) explains the drive's resident selftests and how to replace all mechanical assemblies. Furthermore you'll find an illustrated spare module list and summaries of commands and status bytes for the basic drive.

Contact our local representative or our Sales Department if you have any questions regarding service courses or additional documentation.

#### Updating/backdating

The updating routine for this manual is based on the distribution of ECNs (Engineering Change Notices). The ECNs describe changes in hardware and firmware from the time of the first release of the product.

If you want updating/backdating for your maintenance manual, please fill in the updating card which is inserted in the front of this manual and mail it to us. This is definitely the easiest way to get your name on our ECN mailing list!!

> Since this manual was produced while the TDC 3319 was still in its early stages, there are discrepancies between some of the descriptions in it and the actual product.

Most of them are known to us and will be corrected when the manual is updated. Nevertheless we would very much appreciate your corrections and comments.

### 2. A SHORT DESCRIPTION OF THE DRIVE

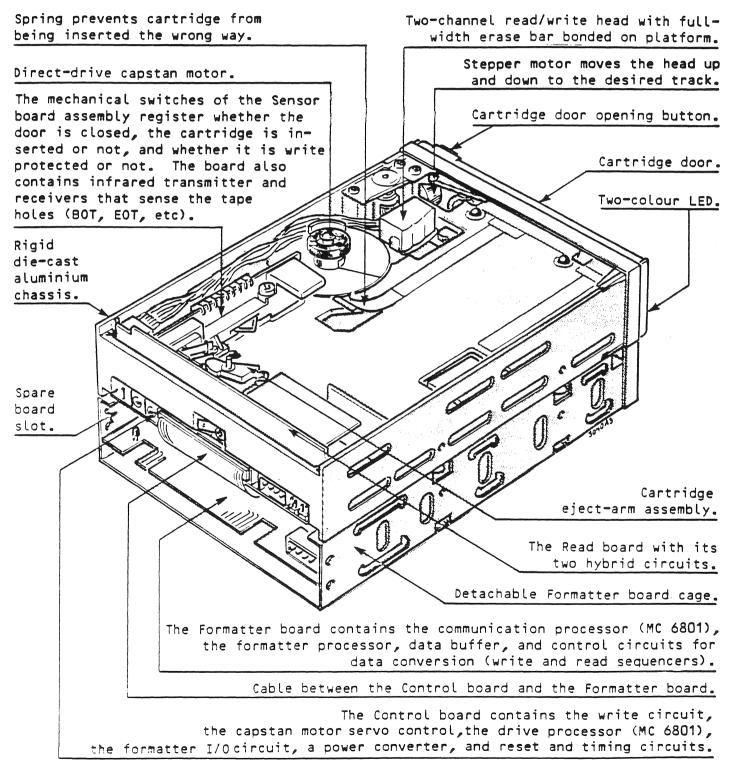

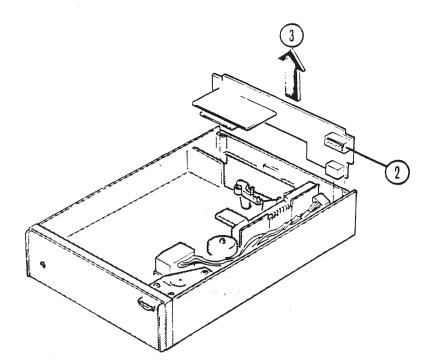

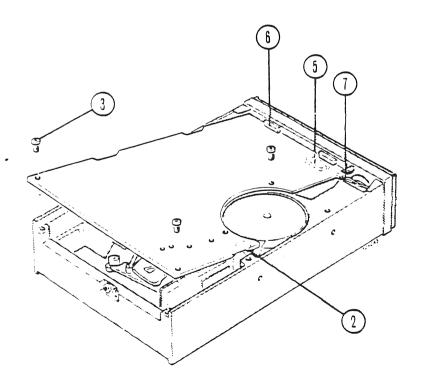

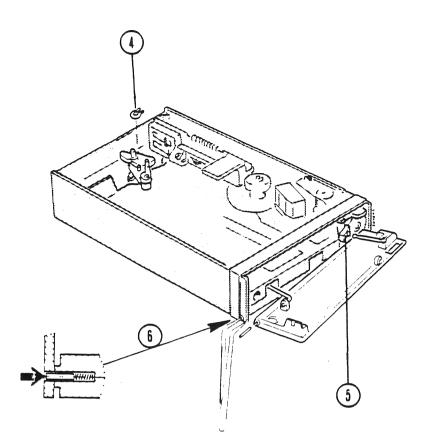

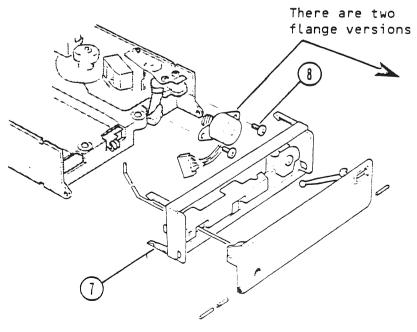

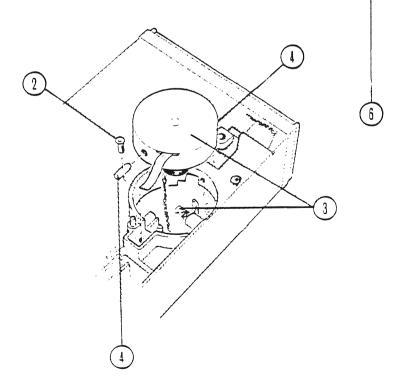

### 2.1 Illustrated Description

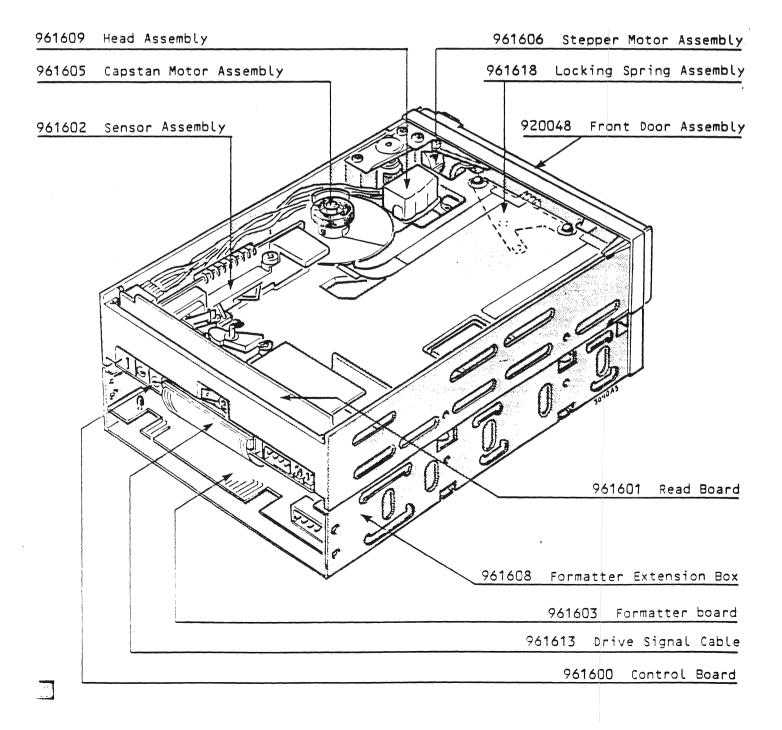

The Tandberg Data TDC 3319 is a streaming 1/4" tape cartridge drive comprising the TDC 3309 (basic drive) and the TDC 3350 (intelligent formatter). It records and reads serially on nine tracks, and can store from 45 Mbytes to 60 Mbytes depending on tape length. The mode of operation is streaming, i.e. the drive is designed to run the whole length of the tape without (normally) interruption.

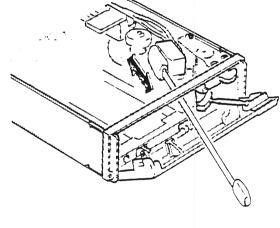

NOTE: Drive shown without top cover!

· ·

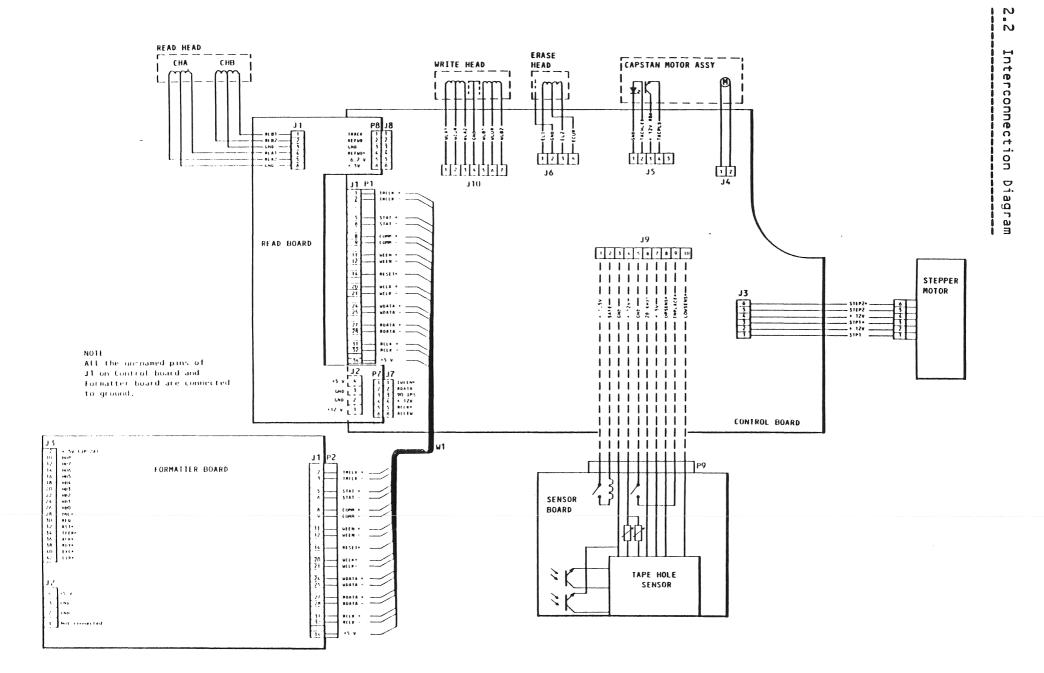

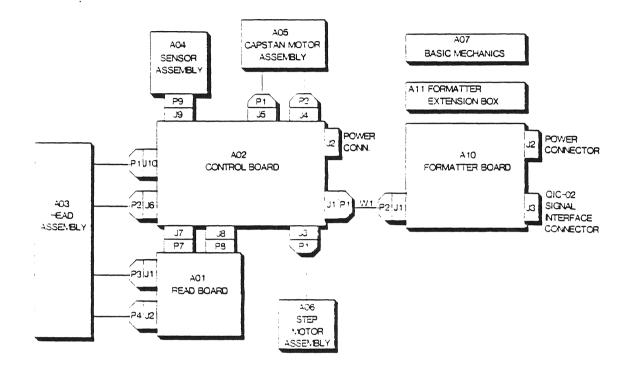

### 3. BLOCK DIAGRAMS

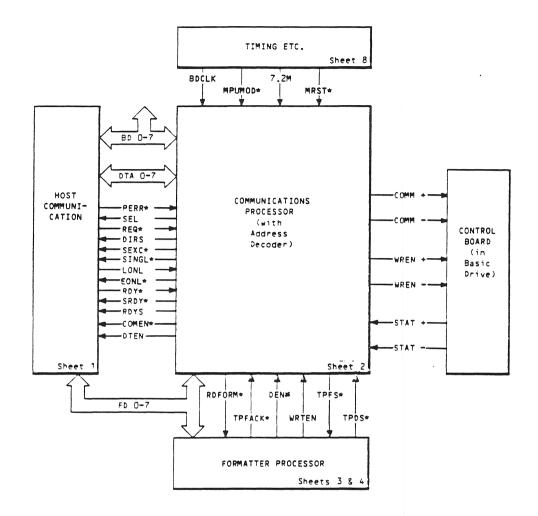

### 3.1 Overall Block Diagram

Overall block diagram.

### CAPSTAN MOTOR ASSEMBLY

The capstan Motor with its built-in tacho sensor is part of the Capstan Servo which provides the tape motion required for the various operating modes: 45/90 ips, read/write, wind/rewind. The motor is DC operated. See separate block diagram of Capstan Servo.

### STEPPER MOTOR ASSEMBLY

Part of the head motion system which ensures that reading or writing takes place on the exact track requested by the host. The highresolution stepper mechanism has 122 steps between each track (5 micrometres per step). The head motion is controlled by the basic drive microprocessor which allows high accuracy dynamic head positioning. A detailed description of the principles for the track position alorithm is given in the TDC 3319 Reference Manual, section 2.3.

### HEAD ASSEMBLY

The read/write and erase functions are combined in one common head. The erase section is active over the full width of the tape and thus erases all tracks in one operation.

### TANDBERG DATA

The read/write sections are active only for one track at a time. Since a read check is always carried out after the writing of each block of data, the head has one section for forward tape motion and one section for reverse tape motion. Track location on the tape is illustrated in the TDC 3319 Reference Manual, subsection 3.5.2.

#### SENSOR ASSEMBLY

The following sensors are located on the Sensor board (see interconnection diagram, section 2.2):

- SAFE: A microswitch operated by the write protect switch on the tape cartridge. Prevents writing when the cartridge is write protected.

- IN PLACE/DOOR CLOSED: A microswitch operated by the tape cartridge. Prevents operation when the door is not closed or when no cartridge is inserted.

- LP/BOT/EOT/EW: Opto-electronic sensors that detect holes in the upper and lower half of the tape. The sequence of pulses from the two sensors allow the control logic to determine whether a BOT, an EOT, an LP or an EW has been detected.

CONTROL BOARD

See separate block diagram and description, section 3.2.

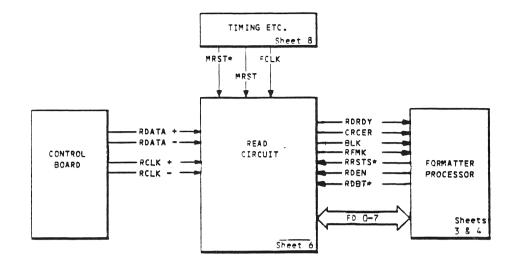

READ BOARD

See separate block diagram and description, section 3.4.

FORMATTER BOARD

See separate block diagram and description, section 3.5.

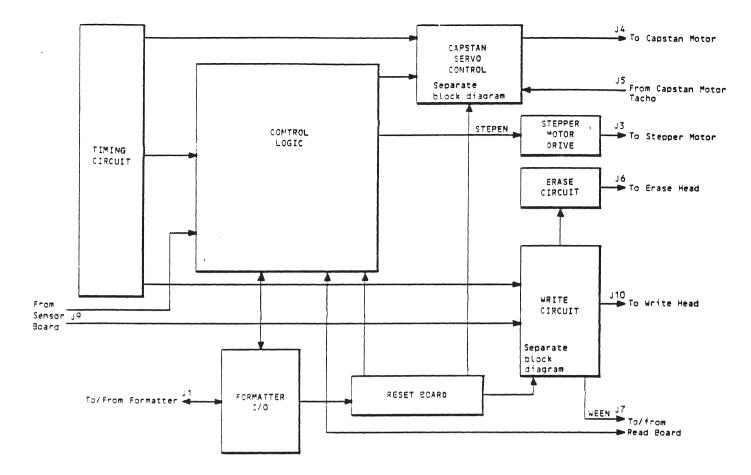

3.2 Control Board Block Diagram

#### CONTROL LOGIC

The central component of this block is a microprocessor that reads the status of all sensors, executes commands from the Formatter and accordingly controls the read/write and erase circuits, head motion circuits and supervises the Capstan Servo. The processor is automatically programmed during reset/power-up to operate in single-chip mode as an input/output processor.

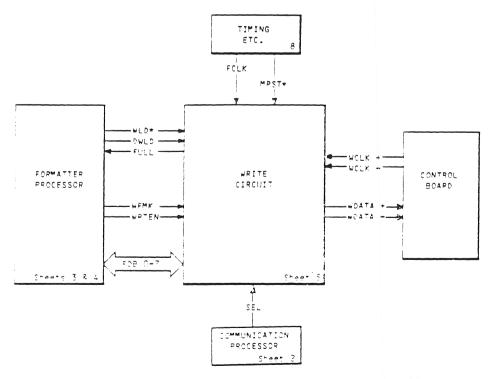

### WRITE CIRCUIT

The read/write head and the Write Amplifier have two channels: channel A for forward direction and channel B for reverse direction. Write current is supplied to the head when a not-write-protected cartridge is inserted and the drive is set in Write mode. The circuit also adjusts the write current according to the tape type in use. Refer to detailed diagram in chapter 4 (Control board sheet 3).

Block diagram of the Control board.

.

## ERASE CIRCUIT

Supplies erase current to the erase head.

## TIMING CIRCUITS

stable 7.2 MHz signal from a crystal controlled oscillator is scaled own to provide the various timing signals used in the Control Logic, the Write Circuit and the Capstan Servo Control.

## FORMATTER I/O

10

Input and output buffers for signals from and to the Formatter.

CAPSTAN SERVO CONTROL

See separate block diagram, section 3.3.

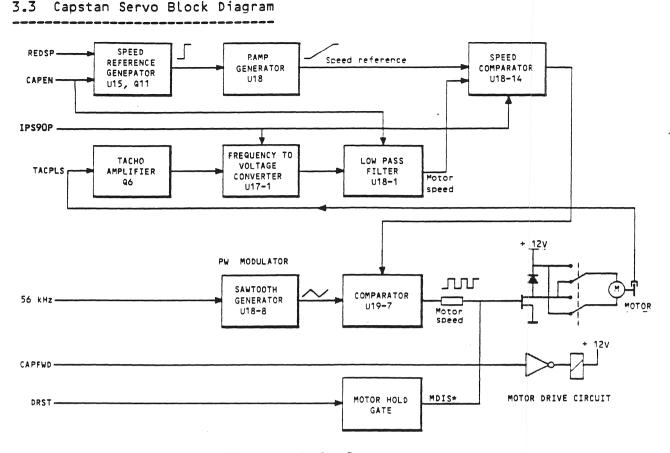

Block diagram of the Capstan servo

The Capstan servo controls the capstan motor. The servo loop is closed by the feedback from the opto-electronic tacho generator in the motor. The 64-slot disc on the motor shaft interrupts the light to the optosensor and provides an output signal with a frequency proportional to the motor speed. This signal passes through the Tacho Amplifier and is applied to an accurate frequency-to-voltage converter that provides a voltage proportional to the motor speed.

The motor speed signal is compared with a signal originating in the Speed Reference Generator. Any difference between the two signals is amplified and results in a corrective input to the Pulse Width Modulator (PWM) which drives the motor.

The PWM comprises a sawtooth generator operating at 56 kHz and a comparator that generates a pulse signal with the duty cycle required to maintain constant speed.

The speed can be set at 45 or 90 ips by the IPS90P signal which determines the conversion ratio of the Frequency-to-voltage Converter.

Start/stop is controlled by the CAPEN signal which applies the reference voltage within the Speed Reference Generator. REDSPD reduces the capstan speed by 10 % for test purposes. During stop the motor current is cut off.

Linear acceleration is ensured by applying the speed reference voltage via the Ramp Generator which converts the voltage step into a ramp voltage. During power-up or reset the MDIS\* signal will inhibit the motor drive power FET.

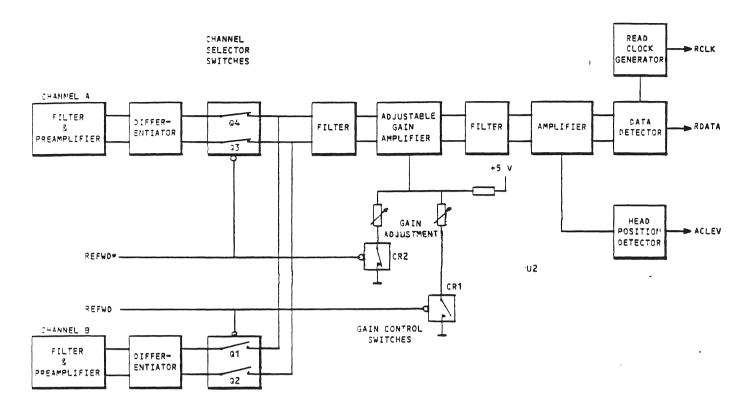

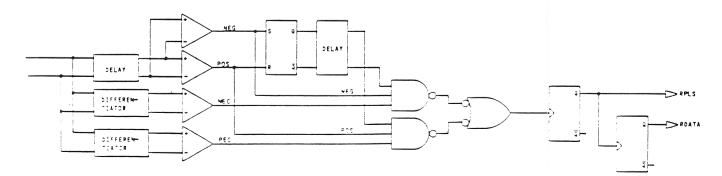

### 3.4 Read Board Block Diagram

Block diagram of the Read board.

The signal from the read head in operation is applied to the channel selector switches via a filter, a preamplifier and a differentiator. The channel selector is operated by the REFWD signal. The state of this signal depends on whether the tape motion is forward or reverse.

The differentiation shapes the signal into a waveform in which the peaks of the read head voltage have been transformed into distinct zero cross-ings.

After further filtering, the signal is applied to the Data Detector in which an RPLS pulse is generated for each binary "one" in the signal. RPLS is then applied to the Read Clock generator which phase-locks to the signal. The output of the Read Clock Generator, RCLK\*, follows the long term variations in the bit-rate of the signal reproduced from tape.

Further, the RPLS pulses are elongated to establish the restored data signal, RDATA, in which the "ones" are represented by high and the "zeroes" by low signal levels during the whole clock period.

The ACLEV signal obtained by peak detection of the signal from the amplifier is utilized by the Control Logic to detect the edge of the tape or the position of the reference track and thus establish the basis for the head positioning system.

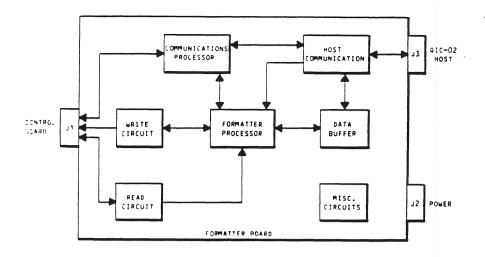

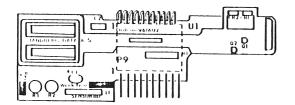

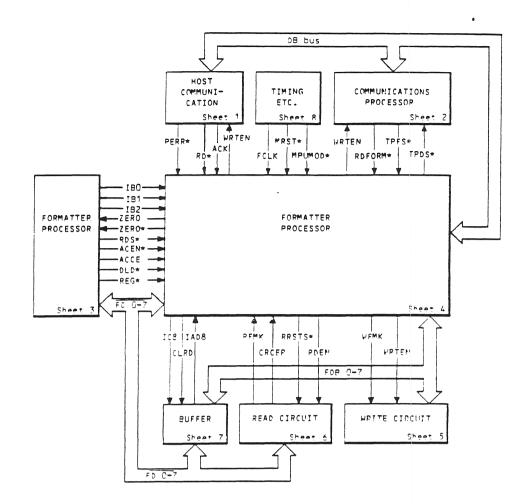

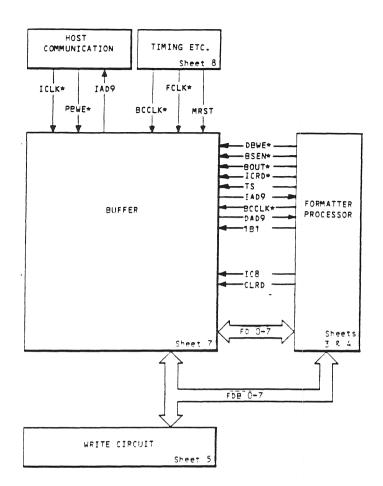

### 3.5 Formatter Block Diagram

Overall block diagram of the Formatter board

The formatter is the interface between the host and the tape unit. In one direction it converts parallel digital data from the host to serial data in GCR code for writing on the tape. In the opposite direction the formatter transforms serial GCR coded data from the tape into parallel digital data to the host.

### HOST COMMUNICATION

Host Communication is the interface between the Formatter and the host. It contains the ports and the handshake logic required for the communication between the HD-bus and various formatter buses.

#### COMMUNICATIONS PROCESSOR

The Communications Processor decodes QIC-02 commands from the host, and issues commands to the control board processor in the basic drive and to the Formatter Processor. The Communications Processor also reads status signals from the processor on the control board in the basic drive and from the Formatter Processor.

### FORMATTER PROCESSOR

The Formatter Processor has the primary control of the data flow on the FD and FDB buses, and it controls the Write Circuits in order to create the required data block format (described in section 2.3 of the TDC 3319 Reference Manual). The formatting involves generation of preamble and postamble, generation of the marker byte, controlling that the data field always contains 512 bytes, and assigning and generating the block address.

During a read operation the formatter processor starts the decoding of data when the read circuits have detected the block marker. At the end of the data block follows decoding of the block address, and the validation of the CRC check which determines whether the block shall be transferred to the host or whether it must be read once more. (Further explained in the TDC 3319 Reference Manual, subsection 8.8.6.)

T

### DATA BUFFER

The Data Buffer provides sufficient storage capacity to allow data written on the tape to be stored long enough for re-writing if the readafter-write check indicates data error. Writing will not start until at least one data block (512 bytes) has been loaded into the buffer. While one block is being recorded, more data can be loaded within the total buffer capacity which is 4K minimum (optionally 8 or 16K). Except for the last 512 bytes already written on the tape and the 512 bytes being written, the total buffer area is always available for loading from the host because new data will be written over data already in the buffer, provided that this data has been successfully verified.

During read operations, each block of data is loaded into the buffer and remains there in queue for transferal to the host via the FD-to-DB port.

### READ CIRCUITS

####

The Read Circuits process the RDATA signal from the Control Board in the Basic Drive unit. This involves detection of the file marker which follows immediately after the preamble, and conversion of of the GCR coded serial data into binary data on parallel form.

### WRITE CIRCUITS

The Write Circuits convert parallel binary data from the host into GCRcoded serial data; and generates the CRC character included with each data block to be written on the tape.

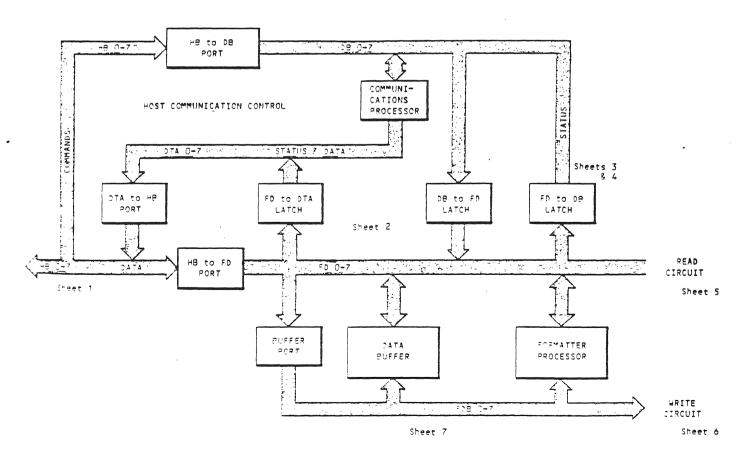

Block diagram of Formatter bus connections.

#### TANDBERG DATA

THE FOLLOWING DESCRIPTION CONCERNS BUS MANAGEMENT AND REFERS TO THE BLOCK DIAGRAM ON THE PREVIOUS PAGE.

Communication on the buses is time-shared between the various circuits connected to each bus. The ports are controlled in such a manner that no collisions occur in the communication path.

### HB-TO-DB PORT

Carries commands from the host to the Formatter. Controlled by the Communications Processor.

### HB-TO-FD PORT

Carries data from the host to the Data Buffer. Controlled by the I/O Control. Enabled while the Formatter Processor executes a jumpinstruction (FD-bus is free) whenever the host has data to be transferred to the formatter.

### DTA-TO-HB PORT

Carries data from the Data Buffer via the FD-to-DTA port; or status signals from the Communication Processor to the host. Controlled by the Communication Processor.

### FD-TO-DTA LATCH

Carries data from the Data Buffer to the host via the DTA-to-HB port. Controlled by the Communications Processor.

## DB-TO-FD LATCH

Carries commands from the Communications Processor to the Formatter Processor. Loaded under control of the Communications Processor. Unloaded under control of the Formatter Processor (mailbox function).

### FD-TO-DB LATCH

Carries status signals from the Formatter Processor to the Communication Processor. Loaded under control of the Formatter Processor. Unloaded under control of the Communications Processor (mailbox function).

,

### BUFFER PORT

Carries data from the FD-bus to the FDB-bus. Permanently enabled.

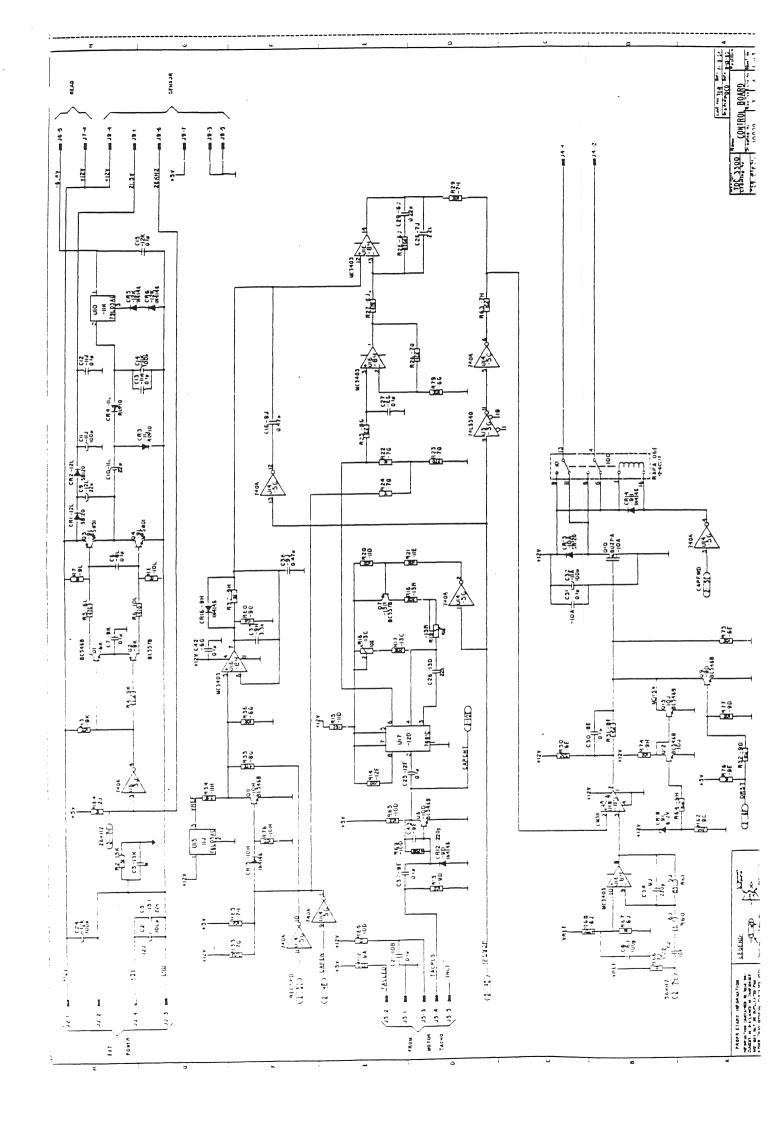

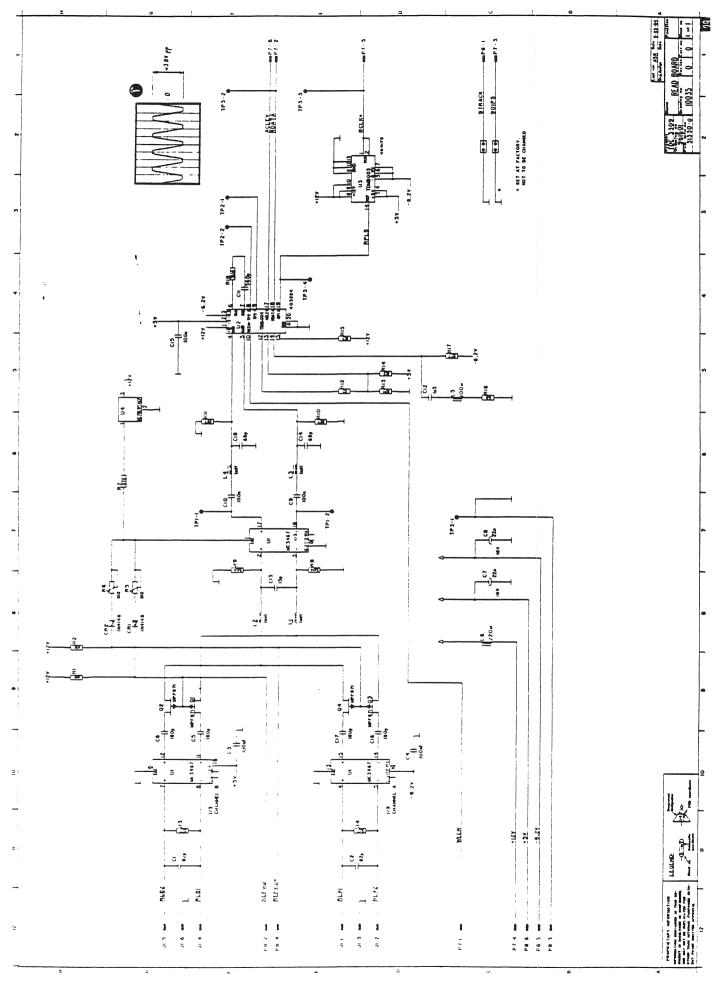

#### 4. CONTROL BOARD

### 4.1 Description/Adjustments/Schematic Diagrams

#### Sheet 1

### SPEED REFERENCE GENERATOR

The voltage regulator U15 provides the reference voltage VREF. The reference voltage will only be applied to the Ramp Generator if Q11 is held cut off by CAPEN from the control logic.

REDSPD reduces the reference voltage to the Ramp Generator and hence reduces the speed by 10%.

### RAMP GENERATOR

The voltage step applied to the Ramp Generator when the speed reference generator is enabled, gives a linearly rising voltage at the output (across C36). To maintain equal acceleration at 45 ips and 90 ips, the IPS90P signal connects C18 in parallel with C36 and thus reduces the ramp slope with a factor of 2.

#### TACHO AMPLIFIER

Amplifies the tacho pulses (TACPLS) to an amplitude suitable for the frequency-to-voltage converter. The time gaps between consequtive pulses, renamed CAPCNT, are monitored by the processor and the control logic to detect tape motion.

### FREQUENCY-TO-VOLTAGE CONVERTER

The output signal at pin.6 of U17, a frequency-to-voltage converter, is a pulse train in which the duty cycle varies linearly with the tacho pulse rate at the input. The time constant and hence the conversion ratio can be varied by adjusting R16. When the 90-ips (IPS90P) is true, Q7 connects R19/R20 into the time constant circuit and thus alters the conversion ratio.

### LOW PASS FILTER AND AMPLIFIER

Provides smoothing of the pulse signal from the frequency-to-voltage converter as well as the required phase stabilisation. The effect of the CAPEN signal is to offset the DC error voltage sufficiently to insure that there is absolutely no tape motion when the Speed Reference Generator is disenabled.

### SPEED COMPARATOR

Compares the speed signal from the low pass filter with the speed reference signal. The resulting signal is applied to the PWM.

## PULSE WIDTH MODULATOR (PWM)

Comparator U19-7 compares the speed error signal with the saw-tooth signal from generator U18-8 and produces a pulse modulated signal with a pulse width directly proportional to the required motor torque.

### MOTOR HOLD GATE

Transistor Q9 connects the input of the Motor Drive Circuit to ground while DRST is present during power-up or reset, and will then prevent tape motion. Q13 has the same effect if +12 V fails.

### MOTOR DRIVE CIRCUIT

The signal from the PWM is applied to the gate of the power FET Q10, which closes the motor circuit from +12 V during the on-periods of the PWM signal provided the motor hold gate is not activated. The CAPFWD signal activates the relay K1 which changes the motor current and hence determines the direction of rotation.

### DC/DC CONVERTER

Transistors Q3 and Q4 open and close in anti-phase. The circuit consists of two "current pumps": Q4 pumps a +12 V into C9 through CR1, then Q3 switches the negative side of C9 to the +12 V supply. This approximately doubles the voltage at the top of this capacitor referred to ground. C11 is now charged to approximately this voltage through CR2. C10/CR3 and C14/CR4 operate in a way similar to C9/CR1 and C11/CR2, except that the positive side of C10 is switched to ground. This means that a negative charge is supplied to C14/C13 through CR4.

Regulator U10, offset by two diode voltage drops, provides a fairly stable -6.2 V supply.

### TANDBERG DATA

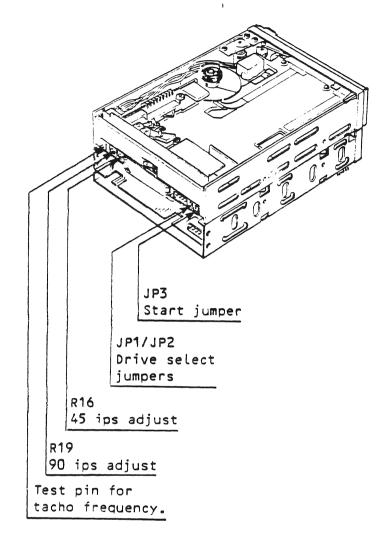

## TAPE SPEED ADJUSTMENT

Insert a cartridge and connect a frequency counter to the test pin. IMPORTANT! 45-ips adjustment first!

45-ips adjustment

Conditions: Jumper JP1: OPEN Jumper JP2: CLOSED

Momentarily short-circuit JP3, and adjust R16 to 1475 Hz on the frequency counter.

Alternatively, if no frequency counter is available, adjust for the brightest red light in the indicator LED at the front of the unit.

90 ips adjustment

| Condit | ions: | 45 ips tape speed must | be |

|--------|-------|------------------------|----|

|        |       | correctly adjusted.    |    |

| Jumper | JP1:  | CLOSED                 |    |

| Jumper | JP2:  | CLOSED                 |    |

Momentarily short-circuit JP3 and adjust R19 to 2951 Hz.

Alternatively, if no frequency counter is avaliable, adjust for the brightest possible red light in the indicator LED at the front.

Sheet 2

-----

### TIMING CIRCUIT

The x-tal oscillator U1-3 operating at 7.2 MHz drives the ripple counter U4, from which the various clock signals are available.

#### CONTROL LOGIC

The microprocessor U9 is programmed during the power-up phase to operate as an input/output processor with no external data or address bus.

The mode programming of U9 is carried out automatically during power-up via the data selector U7 which applies +5 V to pins 8, 9, and 10 of U9 while the DRST\* pulse is applied to U7. This sets U9 in single chip mode. After power-up the same lines are used for input signals connected via U7.

The processing of the input signals to produce the required outputs is controlled by a program stored in the internal program memory in U9.

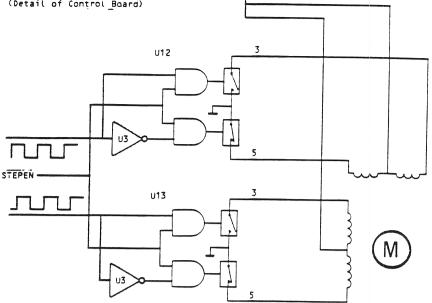

The STEPEN signal from the processor enables the stepper motor dual drivers, U12 and U13 (see detail schematic), and allows the drive signal from the processor to connect the outputs Y1 and Y2 of each driver to ground alternately at the drive pulse rate. The result is that the two halves of each motor winding draws current from the +12 V supply during alternate half cycles of the drive signal.

The drive signals for the two motor windings are in quadrature.

### FORMATTER I/O CIRCUITS (Part of)

Convert V.11 input and output signals to and from TTL-levels.

INNUDERO UNIA

STEPPER MOTOR DRIVE (Detail of Control\_Board)

+12 V

Detail of stepper motor drive.

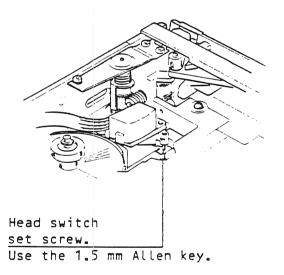

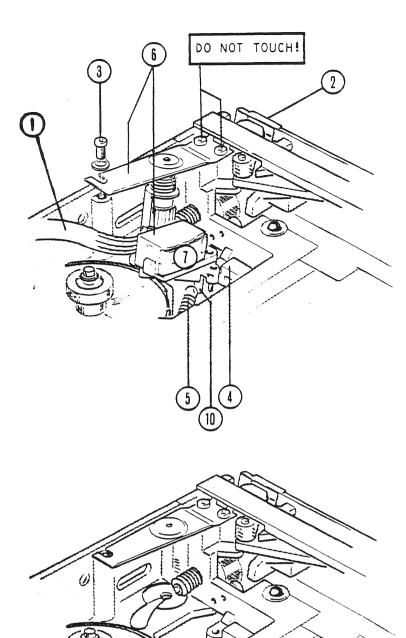

HEAD SWITCH ADJUSTMENT Conditions:

- \* Not-write-protected tape cartridge inserted

- \* Jumper JP1 closed

- \* Jumper JP2 open

Turn the head switch screw counterclockwise until it no longer protrudes above the head platform. Momentarily short-circuit JP3 to start the drive in search for the tape edge. Wait for the front panel light to switch off. Then turn the head switch screw clockwise until the red front panel light just switches on again (be careful not to adjust further clockwise beyond this point).

NOTE: After completing the adustments, cpen the door slowly to allow the head to move up to Track 1 position.

Sheet 3

### FORMATTER I/O CIRCUITS (Part of)

Convert V.11 input and output signals to and from TTL-levels.

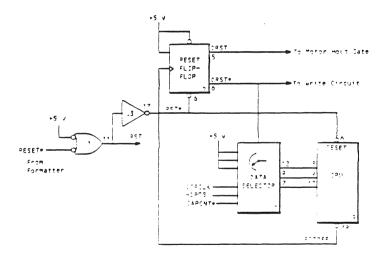

#### RESET CIRCUIT

The reset sequence is initiated by a reset signal, RESET from the host via the Formatter, or by a power-up condition.

In either case the processor U9 and the U6 flip-flop is reset, and its output DRST\* will in turn set the data selector U7 so as to apply +5 V to the programming inputs of U9. DRST also goes to the motor hold gate of the Capstan Servo where it prevents tape motion until the power-up or reset condition is over.

When the processor finds the conditions mature for normal operation, it ends the reset sequence by applying RSTOFF to the reset flip-flop, U6.

Simplified detail of Reset Circuit.

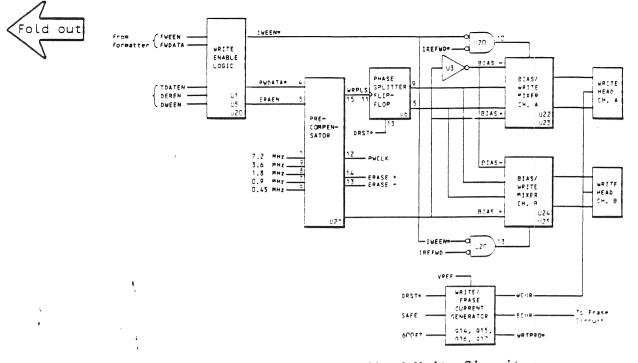

#### WRITE CIRCUIT

The write/bias current fed to the center tap of the write head is supplied from a gated voltage generator. The write and bias signals are synchronized in the bias/write gates.

The write current is inhibited in reset mode by DRST\*, and SAFE from the sensor board inhibits writing if the tape cartridge is set for write protection. The 600-feet signal from the control logic sets the write current in accordance with the tape type present in the recorder.

The effect of the precompensator is to adjust the spacing between the write pulses in order to compensate for pulse crowding. The phase splitter flip-flop, U6, toggles at the write pulse frequency and provides a symmetrical drive signal for the bias/write gates.

The write enable logic controls the passage of write data from the formatter as well as activation of the erase circuit.

INNUULNO UNIN

Simplified detail of Write Circuit.

### ERASE CIRCUIT

Driven by ERASE+ and ERASE- respectively, transistors Q18 and Q19 switche the erase current which is supplied from Q15. The potentiometer R87 adjusts the symmetry of the circuit.

WRITE CURRENT ADJUSTMENT Conditions:

- \* Tape speed correctly adjusted

- \* Not-write-protected tape cartridge inserted

- \* Jumper JP1 closed

- \* Jumper JP2 closed

- \* DC voltmeter connected to the WCUR line. (Accessible from bottom of control board or on the head connector.)

Momentarily short-circuit JP3 to start the tape, and adjust R72 for 14 V on the WCUR line.

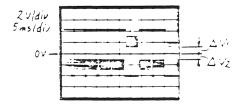

ERASE BALANCE ADJUSTMENT

Conditions:

\* Not-write-protected tape cartridge inserted \* Oscilloscope connected to TP2-2 and ground.

Set up a write command (60 hex pattern) on track 0 and adjust with R87 until balance is obtained  $(\Delta v_1 = \Delta v_2)$ .

·

·

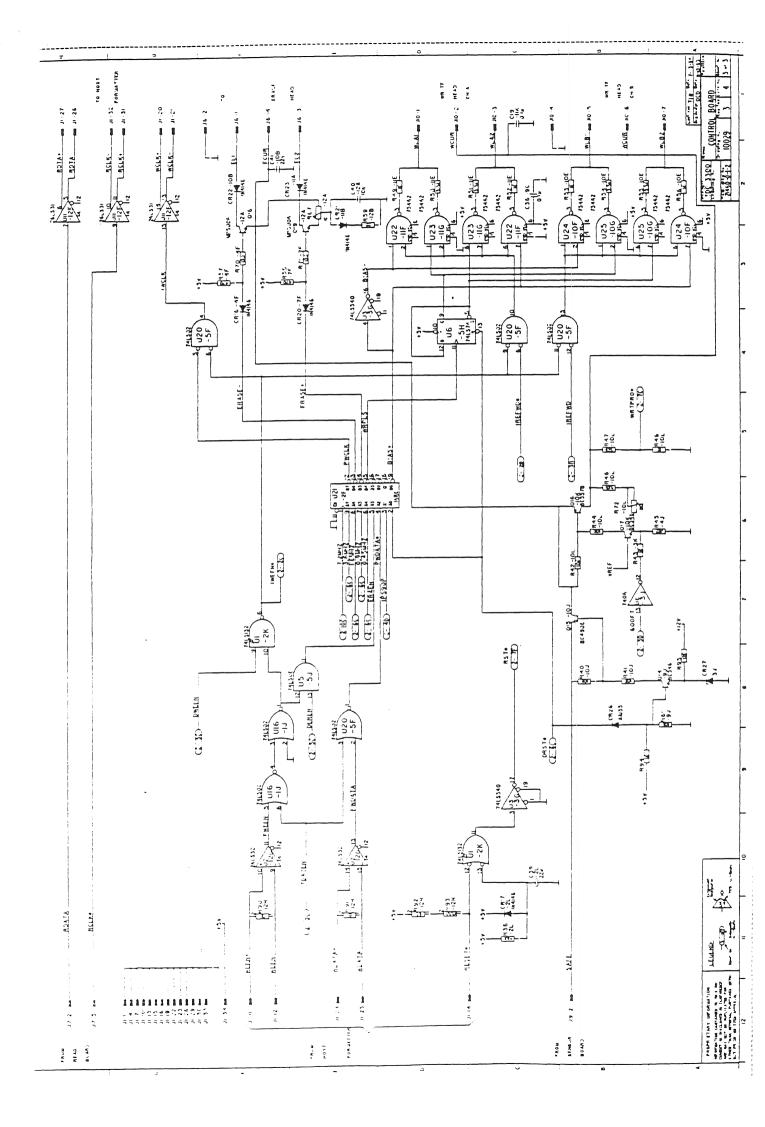

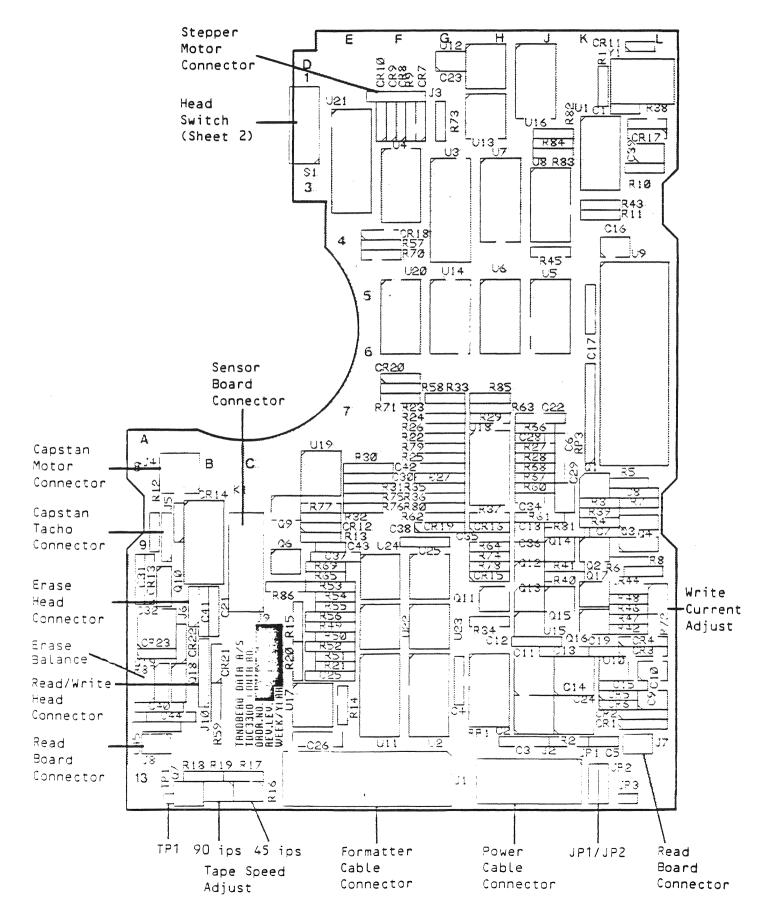

4.2 Control Board Component Location

The Control board has revision level 0, and is seen from the component side.

TANDBERG DATA

4.3 Control Board Mnemonics List

The mnemonics refer to the scematic diagrams for the Control board.  $\gamma$  A "\*" following a signal denotes the inverted signal.

| MNEMONIC | FUNCTION                                                |

|----------|---------------------------------------------------------|

| 0.45 MHz | 0.45 MHz timing signal                                  |

| 0.9 MHz  | 0.9 MHz timing signal                                   |

| 1.8 MHz  | 1.8 MHz timing signal                                   |

| 28 kHz   | 28 kHz timing signal                                    |

| 3.6 MHz  | 3.6 MHz timing signal                                   |

| 56 Hz    | 56 Hz timing signal                                     |

| 56 kHz   | 56 kHz timing signal                                    |

| 7.2 MHz  | 7.2 MHz timing signal                                   |

| 600Ft    | 600 feet tape, sets write current for 600 ft. tape      |

| 90IPS    | Control line, drive operates at 90 ips when active      |

| 9TRACK   | Control line, tells processor that 9-tr. head is connec |

| ACLEV    | Acceptable level on read channel                        |

| BIAS+    | Bias positive signal                                    |

| CAPCNT   | Capstan tacho pulse, counts tacho pulses                |

| CAPEN    | Capstan enable                                          |

| CAPFWD   | Capstan forward, sets capstan motor direction           |

| COMM+    | Command positive line                                   |

| COMM-    | Command negative line                                   |

| DEREN    | Drive erase enable                                      |

| DRST     | Drive restart                                           |

| DRST*    | Drive restart                                           |

| DWEEN    | Drive write enable                                      |

| ECUR     | Erase current                                           |

| EL1      | Erase leg 1, connection for erase head                  |

| EL2      | Erase leg 2, connection for erase head                  |

| ERASE+   | Erase positive                                          |

| ERASE-   | Erase negative                                          |

| FWDATA   | Formatter write data                                    |

| FWEEN    | Formatter write/erase-enable                            |

| GRLMP*   | Green Lamp                                              |

| ICOMM    | Internal command line                                   |

| INPLACE* | Cartridge in place                                      |

| IPS90P   | 90 ips controlled from processor                        |

| IREFWD   | Internal read forwards, enables heads                   |

| IREFWD*  | Internal read forwards, enables heads                   |

| ISTAT    | Internal status line                                    |

| ITRCLK   | Internal transmitter clock                              |

| IWCLK    | Internal write clock                                    |

| IWEEN*   | Internal write/erase-enable                             |

| LOWSNS*  | Lower sensor                                            |

| MDIS*    | Capstan motor disable                                   |

| PWCLK    | PAL write clock                                         |

| PWDATA*  | PAL write data                                          |

.

| MNEMONIC | FUNCTION                                       |  |

|----------|------------------------------------------------|--|

| RCLK*    | Read clock from read board                     |  |

| RCLK+    | Read clock, positive to formatter              |  |

| RCLK-    | Read clock, negative to formatter              |  |

| RDATA    | Read data from read board                      |  |

| RDATA+   | Read data pos. to formatter                    |  |

| RDATA-   | Read data neg. to formatter                    |  |

| RDLAMP*  | Red Lamp                                       |  |

| REDSPD   | Reduces speed by 10 %                          |  |

| REFWD    | Read forwards                                  |  |

| REFWD*   | Read forwards                                  |  |

| RESET*   | Reset                                          |  |

| RPLS     | Read pulse                                     |  |

| RST*     | Restart                                        |  |

| RSTOFF   | Restart off                                    |  |

| SAFE     | Cartridge write protected                      |  |

| SELECT   | Drive selected                                 |  |

| SELFTST* | Triggers drive selftests                       |  |

| SEL1*    | Drive select 1                                 |  |

| SELO*    | Drive select O                                 |  |

| SINT*    | Sensor interrupt                               |  |

| STAT+    | Status positive to formatter                   |  |

| STAT-    | Status negative to formatter                   |  |

| STP1     | Stepper motor 1                                |  |

| STP1*    | Stepper motor 1                                |  |

| STP2     | Stepper motor 2                                |  |

| STP2*    | Stepper motor 2                                |  |

| TACKLED  | Tachometer led current                         |  |

| TACPLS   | Tachometer pulse from capstan motor            |  |

| TDATEN   | Test data enable                               |  |

| TRCLK+   | Transfer clock positive, from formatter        |  |

| TRCLK-   | Transfer clock negative, from formatter        |  |

| UPSENS*  | Upper sensor                                   |  |

| VREF     | +5 V ref. voltage                              |  |

| WCLK+    | Write clock positive to formatter              |  |

| WCLK-    | Write clock negative to formatter              |  |

| WCUR     | Write current                                  |  |

| WDATA+   | Write data positive to formatter               |  |

| WDATA-   | Write data negative to formatter               |  |

| WEEN+    | Write/erase enable, positive                   |  |

| WEEN-    | Write/erase enable, negative                   |  |

| WLA1     | Write leg A 1, connection for lower write head |  |

| WLA2     | Write leg A 2, connection for lower write head |  |

| WLB1     | Write Leg B 1, connection for upper write head |  |

| WLB2     | Write leg B 2, connection for upper write head |  |

| WRPLS    | Write pulse                                    |  |

| WRTPRO*  | Write protected cartridge                      |  |

| WRTPRO   | Write protected cartridge                      |  |

### 4.4 Control Board Parts List

| Comp. Designator                                                                                           | Part no.                                                           | Description                                                                                                                                                                                        | Qty.                            |

|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| Capacitors<br><br>C1<br>C2, C11, C14,                                                                      | 386386                                                             | 82 pF cer.1                                                                                                                                                                                        | 1                               |

| C24, C32<br>C3, C17<br>C4, C8, C12,<br>C13, C15, C19,<br>C21, C25, C27,                                    | 398634<br>359232                                                   | 100 uf ELKO +/-20 % RE (F) 35 V<br>0.022 uf ma 105 e 223 maa                                                                                                                                       | 5<br>2                          |

| C30, C31, C37,<br>C38, C42<br>C5, C35<br>C6<br>C7<br>C9, C10, C16                                          | 393311<br>382456<br>383864<br>394784                               | 0.1 uF SA 205 E 104 MAA<br>1000 pF cer.2 10 % min. 50 V<br>100 pF cer.2 10 % min. 400 V<br>0.1 pF p.est.M 10 % 50 V                                                                                | 14<br>2<br>1<br>1               |

| c23, c39<br>c18, c36<br>c22, c40,                                                                          | 381637<br>392047                                                   | 22 uF tantalum 16 V<br>0.47 uF p.est.M. 10 % 50 V                                                                                                                                                  | 5<br>2                          |

| C44, C45<br>C26<br>C28<br>C29<br>C33<br>C34<br>C41                                                         | 384999<br>402618<br>382183<br>390467<br>383354<br>381192<br>392385 | 0.01 uF<br>0.022 uF P.car 5 % 25 V MKC 1862<br>2200 pF cer.2 10 % min. 50 V<br>0.22 uF p.est.M. 10 63 V MKS2<br>0.22 uF CAC4Z5U224M/SA305E224MAA<br>220 pF cer.2 10 % min. 50 V<br>3.3 uF tantalum | 4<br>1<br>1<br>1<br>1<br>1<br>1 |

| Diodes<br><br>CR1<br>CR2, CR13<br>CR3, CR4, CR5<br>CR6, CR7, CR8,<br>CR9, CR10, CR12,<br>CR14, CR15, CR16, | 400752<br>404756<br>385107                                         | 1.3 kohm met. film 1 %, 1/8 W<br>120 SB 120<br>10 RGP 10J                                                                                                                                          | 1<br>2<br>2                     |

| CR17, CR18, CR20,<br>CR21, CR22, CR23<br>CR11<br>CR19<br>CR24                                              | 384841<br>399467<br>286560<br>350833                               | 1N 4148<br>100 D100-4S LED (LD100-5/S)<br>ZENER 8.2 V<br>AA 135                                                                                                                                    | 16<br>1<br>, 1<br>1             |

•

| Comp. Designator                                                                                                                                         | Part no.                                                                                                                                                               | Description                                                                                                                                                                                                                                                                                                                                                                      | Qty.                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Circuits<br>U1<br>U2<br>U3<br>U4<br>U5<br>U6<br>U7<br>U8<br>U10<br>U11<br>U12, U13, U22,<br>U23, U24, U25<br>U14, U21<br>U15<br>U17<br>U18<br>U19<br>U20 | 340640<br>389518<br>393068<br>387700<br>381939<br>380229<br>382880<br>384604<br>400956<br>389166<br>393233<br>961630<br>394755<br>393068<br>401066<br>389892<br>384324 | 74LS132<br>26LS32<br>74LS540<br>74LS393<br>74LS08N<br>74LS08N<br>74LS157<br>7406N<br>79L05AC<br>26LS31<br>75462<br>TDC 3300 WR ASE Dec. firmw.<br>78L05ACP<br>76810P<br>Mc3403<br>LM311<br>74KS02N                                                                                                                                                                               | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1 |

| Transistors<br>Q1, Q6, Q9,<br>Q11, Q12, Q13,<br>Q14, Q17<br>Q2, Q7, Q8,<br>Q16<br>Q3<br>Q4<br>Q10<br>Q15<br>Q18, Q19                                     | 386436<br>389540<br>400899<br>402296<br>401290<br>379066<br>392852                                                                                                     | 548 BC 548B RL<br>557 BC 557B RL<br>51 MPSW51<br>1 MPSW01<br>71 BUZ71A<br>490 BC490B p RL 80V1A 625MW DATA<br>6 MPSU06                                                                                                                                                                                                                                                           | 8<br>4<br>1<br>1<br>1<br>2                                                                  |

| Assorted<br>0300<br>J1<br>J2<br>J3<br>J4<br>J5<br>J6<br>J7, J8<br>J9<br>J10<br>J11<br>XRP1<br>JP1, JP2<br>Y1<br>TP1<br>S1                                | 403338<br>402145<br>402666<br>402043<br>402972<br>404214<br>402235<br>391717<br>402324<br>403265<br>961607<br>400512<br>402744<br>399338<br>358894<br>403338           | Spring 62353-3<br>Angled 2x17 pin connector<br>172294-1 4-pins M/172296-1 AMP<br>5268-6<br>5268-2 2-pin<br>5267-05 5-pin<br>5267-04 4-pin<br>826632-3 2 straight rows 2x3 pin<br>163880-8 10-pin connector<br>5267-07 7-pin<br>Socket under S1<br>Socket 4E 39500 14-pin<br>Jumper C42315-A1347-A102, 2 pol<br>7.2 MHz NC-18/C series-res.<br>4 mm metal plint<br>Depress switch | 1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1<br>1                          |

| Comp. Designator .               | Part no.         | Description                                      | Qty.                       |

|----------------------------------|------------------|--------------------------------------------------|----------------------------|

|                                  |                  |                                                  |                            |

| Resistors                        |                  | 1                                                |                            |

| R1                               | 400752           | 1.3 kohm met. film 1 % 1/8 W                     | 1                          |

| R5, R6, R57,                     | 400752           | 1.5 KOHM MEC. FICH 1 % 178 W                     |                            |

| R58                              | 404198           | 470 ohm met. 1 %                                 | 4                          |

| R2, R67                          | 390252           | 1 Mohm met.film 1 %                              | 2                          |

| R3, R4, R13,                     |                  |                                                  |                            |

| R20, R21, R25,                   |                  |                                                  |                            |

| R26, R29, R31,<br>R32, R36, R39, |                  |                                                  |                            |

| R40, R41, R42,                   |                  |                                                  |                            |

| R44, R63, R64,                   |                  |                                                  |                            |

| R65, R74, R75,                   |                  |                                                  |                            |

| R77, R78, R79,<br>R80, R81, R82, |                  |                                                  |                            |

| R83, R85                         | 403188           | 10 kohm met. film 1 %                            | 29                         |

| R87                              | 402153           | 10 ohm potmeter                                  | 1                          |

| R7, R8, R22,                     |                  |                                                  |                            |

| R24, R43, R48,                   |                  |                                                  |                            |

| R66, R76, R84,                   | 107107           |                                                  | 10                         |

| R86<br>R9                        | 403127<br>401457 | 1 kohm met. film 1 %<br>2 kohm met. film 1 %     | 10                         |

| R10, R11, R14,                   | 401491           |                                                  |                            |

| R62                              | 403579           | 220 ohm met. film 1 %                            | 4                          |

| R12, R30                         | 403864           | 330 ohm met. film 1 %                            | 2                          |

| R15                              | 400447           | 180 ohm met. film 1 %                            | 2<br>1<br>2<br>2<br>2<br>2 |

| R16, R19<br>R17, R18             | 402165<br>400516 | Pot. meter 10 kohm T7YB<br>20 kohm met. film 1 % |                            |

| R23, R73                         | 400565           | 100 ohm met. film 1 %                            | 2                          |

| R27, R35                         | 401848           | 47 kohm met. film 1 %                            |                            |

| R28                              | 403416           | 270 kohm met. film 1 %                           | 1                          |

| R33, R50, R51                    | 107401           | 7 7 hobe not file 1 4                            | 5                          |

| R54, R55<br>R34                  | 403196<br>401738 | 3.3 kohm met. film 1 %<br>9.1 kohm met. film 1 % | 5                          |

| R37, R68, R69                    | 383821           | 470 kohm met. film 1 %                           | 3                          |

| R38                              | 403249           | 56 kohm met. film 1 %                            | 1                          |

| R45                              | 400732           | 2.2 kohm met. film 1 %                           | 1                          |

| R46                              | 400117           | 4.7 kohm met. film 1 %                           | 1                          |

| R47<br>D/9 D52 D53               | 404361           | 3.9 kohm met. film 1 %                           | 1                          |

| R49, R52, R53,<br>R56            | 312229           | 1 kohm met. film 1 %                             | 4                          |

| R59                              | 404752           | 22 ohm met. film 1 %                             | 1                          |

| R60                              | 402687           | 33 kohm met. film 1 %                            | 1                          |

| R61                              | 385265           | 330 kohm met. film 1 %                           | 1                          |

| R70, R71                         | 403974           | 150 ohm met. film 1 %<br>Pot. meter 2.2 kohm TX  | 2<br>1                     |

| R72<br>RP1                       | 400434<br>401998 | 100 ohm package DIL 20 %                         |                            |

| RP2, RP3                         | 388311           | 10 kohm package 4310R-101-103                    | 1 1                        |

| -,                               |                  |                                                  |                            |

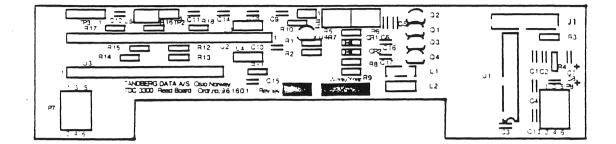

### 5. READ BOARD

### 5.1 Circuit Description

The following describes revision level 0 of the Read board. There are major changes between revison level 0 and revision level 1, most of them in the data detector circuitry. This will be described when the manual is updated.

### FILTER AND PREAMPLIFIER

The read head is part of the input filter that precedes the amplifier U1. The filter has a low pass characteristics.

### ADJUSTABLE-GAIN AMPLIFIER

The amplifier is common for the two channels, however the gain is individually adjustable for channel A and B to compensate for different characteristics of the two sections of the head.

### GAIN CONTROL SWITCHES

The gain control potentiometers R5 and R6 for channel B and channel A respectively are connected into the circuit via the diodes CR1 and CR2 which are switched by the signals REFWD and REFWD\*.

### DIFFERENTIATOR

####

The capacitors C16 and C17 in conjunction with the filter succeeding the Channel selector differentiates the signal and thus transforms the peaks of the signal into zero crossings.

#### CHANNEL SELECTORS

Channel A is selected when REFWD\* switches Q3 and Q4 on. Similarily, channel B is selected by REFWD.

Circuit diagram of Data Detector U2.

old out

# DATA DETECTOR (U2)

This circuit is custom made for Tandberg Data. Two comparators at the front end of the circuit detect the zero-crossings of the differentiated read signal. Control signals verify the validity of the resulting pulses which trigger a precision one-shot that generates 550 ns pulses (RPLS). Another one-shot, in series, generates the read data signal (RDATA).

U2 also generates the ACLEV signal that indicates that the level on the read channel is acceptable.

## READ CLOCK GENERATOR (U3)

This circuit is custom made for Tandberg Data. It is a phase-locked loop that generates the RCLK\* signal that follows the long term variations of the bit rate.

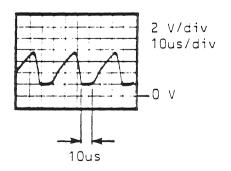

# GAIN CONTROL ADJUSTMENT

The adjustment potentiometers for gain in channels A and B (forward and reverse), are accessible when the top cover has been removed.

## Conditions:

- \* Tape speed correctly adjusted

- \* Write current correctly adjusted

- \* Jumper JP1 closed

- \* Jumper JP2 closed

- \* Oscilloscope connected to TP2-1 or TP2-2

- \* Not-write-protected tape cartridge inserted.

Momentarily short-circuit JP3 to start the adjustment. Adjust R6 for slight clipping of the signal while the tape moves forward (see scope picture 1). Wait for the tape to reverse and adjust R5 similarly.

# 5.2 Read Board Component Location

# 5.3 Read Board Mnemonics List

The mnemonics refer to the schematic diagram for the Read board. A "\*" following a signal denotes the inverted signal.

| MNEMONIC                                                                                                              | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 90IPS<br>9TRACK<br>ACLEV<br>IWEEN*<br>RCLK*<br>RDATA<br>REFWD<br>RLA1<br>RLA2<br>RLB1<br>RLB2<br>RLB1<br>RLB2<br>RPLS | 90 ips control line, drive operates at 90 ips when active<br>Control line, tells processor that 9-tr. head is connected<br>Acceptable level on read channel<br>Internal write/erase-enable<br>Read clock<br>Raw read data from read board<br>Read forwards, enables lower heads<br>Read leg A 1 connection for lower head<br>Read leg A 2 connection for lower head<br>Read leg B 1 connection for upper head<br>Read leg B 2 connection for upper head<br>Read leg B 2 connection for upper head |

.

•

.

## 5.4 Read Board Parts List

| Comp. Designator                                                                                     | Part no.                                                                                         | Description                                                                                                                                                                                                                  | Qty.                                      |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| Capacitors                                                                                           |                                                                                                  |                                                                                                                                                                                                                              |                                           |

| C1, C2<br>C3, C4, C9, C10<br>C5, C6, C16,                                                            | 386386<br>393311                                                                                 | 82 pF cer.1 2 %<br>0.1 uF SA 205 E 104 MAA                                                                                                                                                                                   | 2<br>4                                    |

| C17<br>C7, C8<br>C11<br>C12<br>C13<br>C14<br>C15                                                     | 288608<br>381637<br>382298<br>380064<br>401461<br>388160<br>394784                               | 180 pF cer.1 2 %<br>22 uF tantalum 16 V<br>560 pF cer.1 2 %<br>1500 pF cer.2 10 % min. 50 V<br>15 pF cer.1 2 %<br>68 pF cer.1 2 % 10 V<br>0.1 uF p.est. M.10 % 50 V                                                          | 4<br>2<br>1<br>1<br>1<br>1                |

| Diodes<br><br>CR1, CR2                                                                               | 384841                                                                                           | 1N 4148                                                                                                                                                                                                                      | 2                                         |

| Resistors                                                                                            |                                                                                                  |                                                                                                                                                                                                                              |                                           |

| R1, R2<br>R3, R4<br>R5, R6<br>R11, R12, R23<br>R14<br>R15, R16, R22<br>R17<br>R18<br>R19, R20<br>R21 | 403188<br>403196<br>400434<br>402630<br>404198<br>403025<br>404752<br>400565<br>401294<br>401123 | 10 kohm met. film 1 %<br>3.3 kohm 1 % 1/8 W<br>Pot.meter 2.2 kohm TX<br>3.16 kohm met.film 1 %<br>470 ohm met. film 1 %<br>2.7 kohm met. film 1 %<br>22 ohm met. film 1 %<br>100 ohm met. film 1 %<br>1.5 kohm met. film 1 % | 2<br>2<br>3<br>1<br>3<br>1<br>1<br>2<br>1 |

| Transistors<br><br>Q1, Q2, Q3, Q4                                                                    | 392874                                                                                           | 971 MPF 971                                                                                                                                                                                                                  | 4                                         |

| Circuits                                                                                             |                                                                                                  |                                                                                                                                                                                                                              |                                           |

| U1<br>U2<br>U3<br>U4                                                                                 | 400540<br>403224<br>920047<br>394755                                                             | MC3467P<br>TDMBOO4 custom made for TD<br>TDMBOO3 custom made for TD<br>78LO5ACP                                                                                                                                              | 1<br>1<br>1                               |

| Assorted                                                                                             |                                                                                                  |                                                                                                                                                                                                                              |                                           |

| J1<br>L1, L2, L3, L4<br>L5<br>L6<br>P7, P8<br>TP1, TP3<br>TP2                                        | 402235<br>397082<br>392960<br>393778<br>403408<br>385503<br>390574                               | 5267-04 4-pin<br>1000 uH 10 %<br>100 uH 10 %<br>220 uH 10 % Plessey<br>Connectors, 67118-003 2x3-pin<br>Test points, 826629-2, 1 row 1x2-pin<br>Test point, 826629-3, 1 row 1x3-pin                                          | 1<br>4<br>1<br>2<br>2<br>1                |

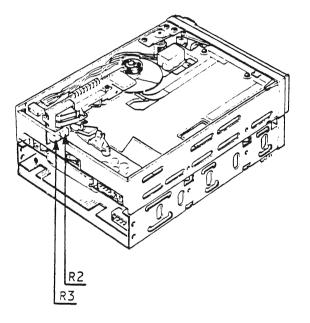

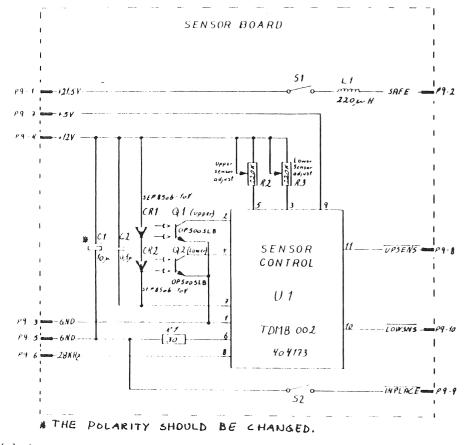

#### 6. SENSOR BOARD

## 6.1 Description and Adjustments

SAFE is true when the tape cartridge in the basic drive is set for write protection (S1 open). Switch S2 confirms the presence of a cartridge in the drive by generating the INPLACE\* signal (S2 closed).

Light from the two light emitting diodes CR1 and CR2 activates the corresponding photo transistors Q1 and Q2 when a hole in the tape opens the light path. Q1 will detect a hole in the upper part of the tape and results in UPSENS\* being generated. Similary, LOWSNS\* is generated when Q2 detects a hole in the lower half of the tape. These signals are analyzed by the processor on the Control board to determine the position of the tape.

Adjusting Sensor Sensitivity

Conditions:

- \* Cartridge inserted

- \* Oscilloscope connected to U1 pin 3

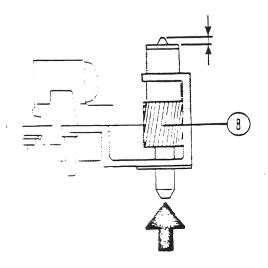

Rewind the tape to BOT. Turn the capstan wheel slowly to align one of the upper holes in the tape with the upper sensor. This corresponds to max signal on the scope. Then adjust R2 to obtain clipping over 10 us of the signal period (see picture).

Move the scope probe to U1 pin 5 and align one of the lower tape holes with the lower sensor (max signal). Use R3 to adjust to 10 us clipping as described above.

#### **6.**2 Schematics

•----

6.3 Component Location

6.4 Mnemonics List

The mnemonics refer to the schematic diagram for the Sensor board.

| MNEMONIC | FUNCTION                  |

|----------|---------------------------|

| 28KHz    | 28 kHz timing signal      |

| GND      | Ground                    |

| INPLACE  | Cartridge in place        |

| LOWSNS   | Lower sensor              |

| SAFE     | Cartridge write protected |

| UPSENS   | Upper sensor              |

#### 6.5 Parts List

-----

| Comp. Designator | Part no.         | Description                                           | Qty. |

|------------------|------------------|-------------------------------------------------------|------|

| Capacitors       |                  |                                                       |      |

| c1<br>c2         | 384489<br>394784 | 10 uF tantalum 25 V<br>0.1 uF p.est. MKT 1817/MKS 2   | 1    |

| Diode            |                  |                                                       |      |

| CR1, CR2         | 394080           | sep 8506-104 JR-LED. side row                         | 1    |

| Resistors        |                  |                                                       |      |

| R1<br>R2, R3     | 317249<br>402491 | 31.6 ohm met. film 1 %<br>Pot.meter 220 kohm TX 220 K | 1    |

| Circuit          |                  |                                                       |      |

| U1               | 404173           | TDMB002 Custom made for TD                            | 1    |

| Assorted         |                  |                                                       |      |

| L1               | 393778           | Coil 220 uH 10 % 11x5mm Q>45                          | 1    |

| P9<br>A1, A2     | 401147<br>404841 | 163740-8 10-pin<br>Transistor 500 or 500 SLB          | 1    |

| s1, s2           | 403505           | Switches SS-5 GLD                                     | 2    |

| 0400             | 402964           | PA 6 black plastic bracket                            | 1    |

| 0450             | 402406           | Spring, write protect                                 | 1    |

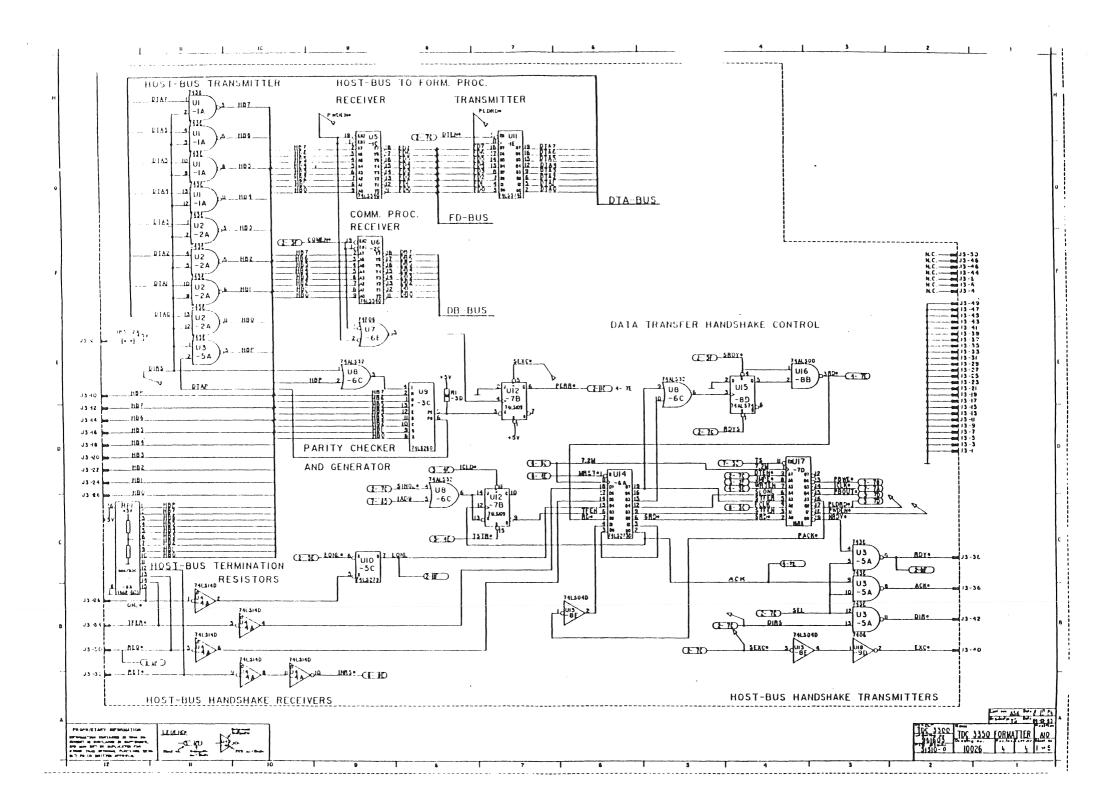

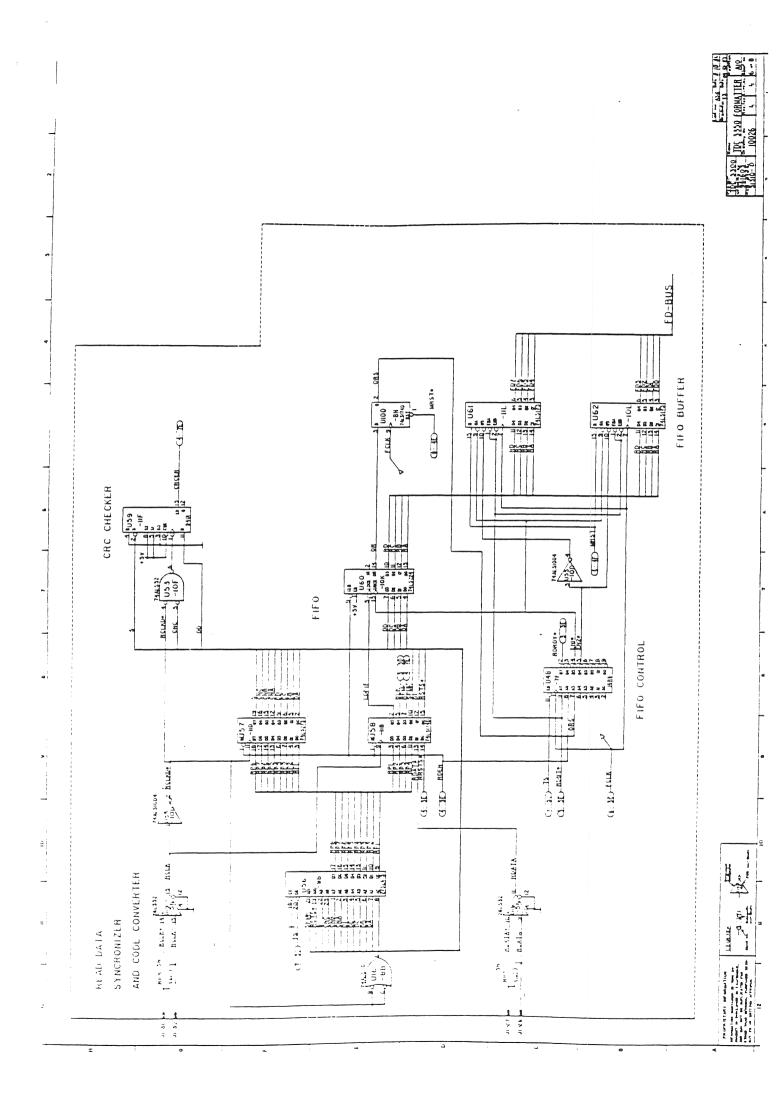

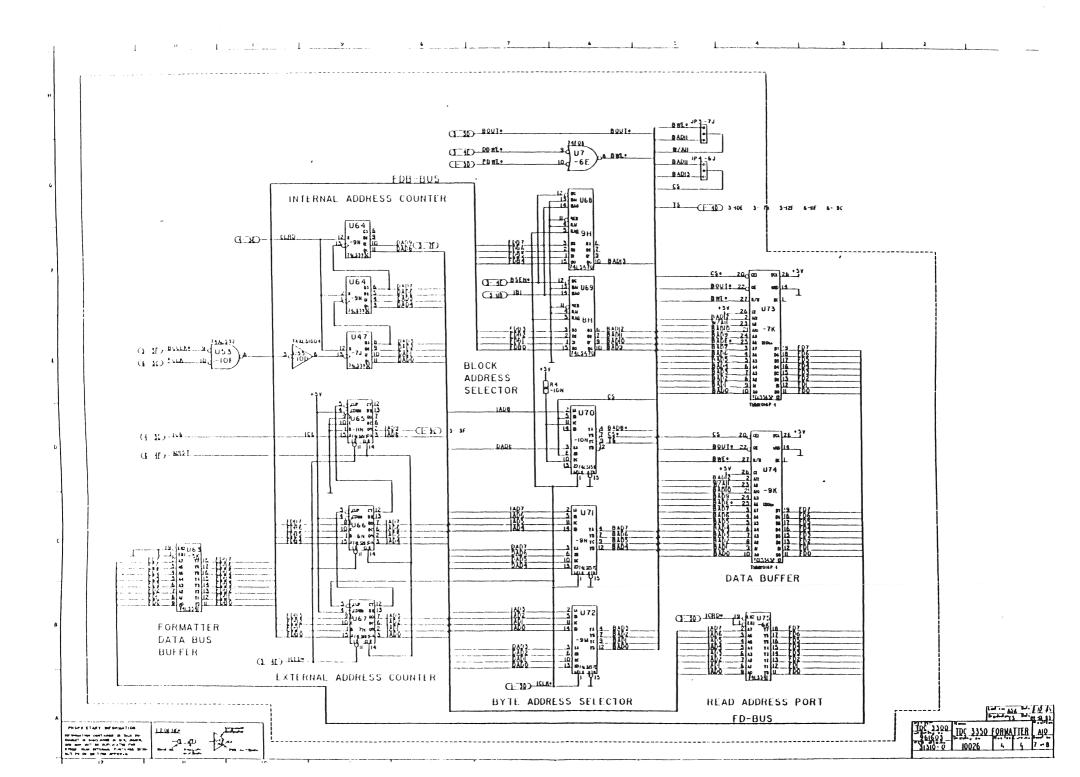

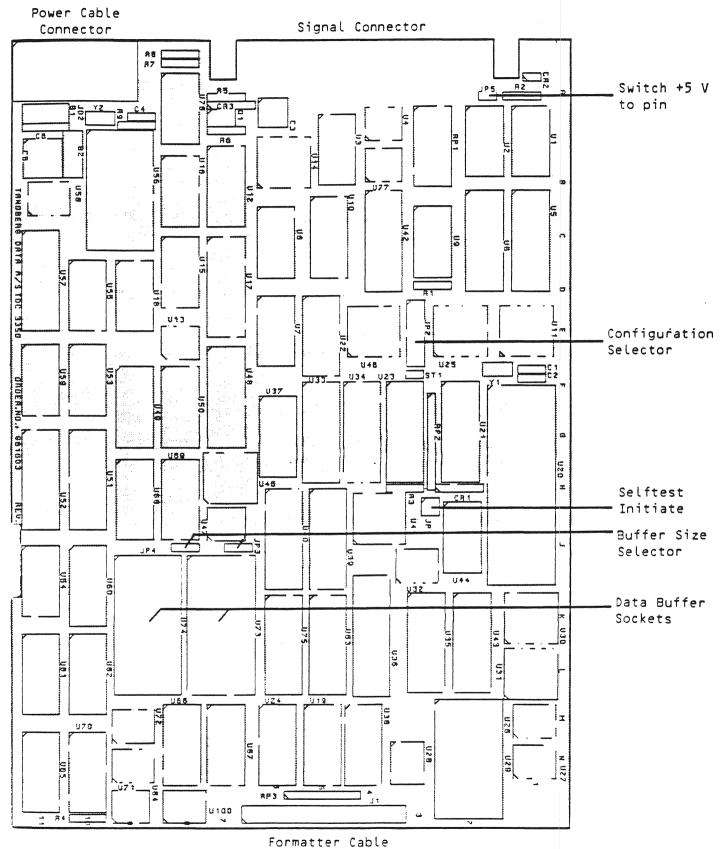

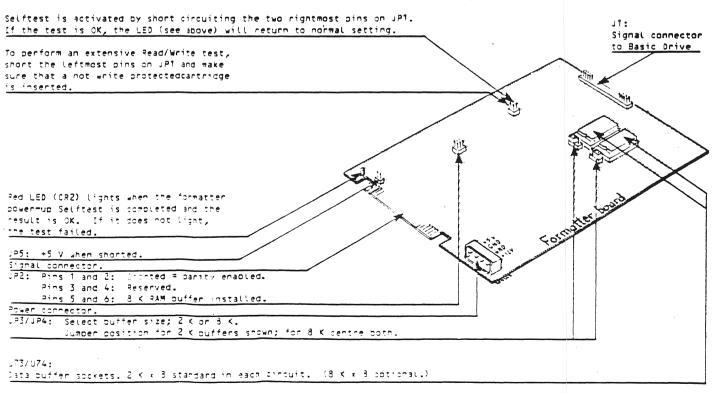

7. FORMATTER BOARD

## 7.1 Description/Adjustments/Schematic Diagrams

Sheet 1

#### PARITY CHECKER AND GENERATOR

------

Checks data and commands from the host for odd parity and generates PERR\* when parity error is detected. Sets correct level of parity bit in data and status words to the host.

#### DIA-TO-HB PORT

-----

Carries data to the host when enabled by DIRS from the Communications Processor.

#### HB-TO-FD PORT

Carries data from the host to the Data Buffer when enabled by PWDENA from the 1/0-controller in the handshake control during the short time interval when the formatter Processor makes a jump.

#### FD-TO-DTA LAICH

----

Loaded with data from the Data Buffer on the PLDRD\* pulse from the I/Ocontrol. The contents of the latch is applied to the DTA-bus while DTEN\* from the System Control Latch is present.

#### HB-TO-DB PORT

-----

Carries commands from the host to the formatter when enabled by  ${\sf COMEN*}$  from the Communications Processor.

#### DATA TRANSFER HANDSHAKE CONTROL

Exchanges status signals and commands between the host and the formatter. The signals affect operation of the data buffer, the formatter processor and the Host Communications control.

Signal connections between this circuit diagram sheet and other sheets of the Formatter circuit diagram.

Connections to other boards are also shown.

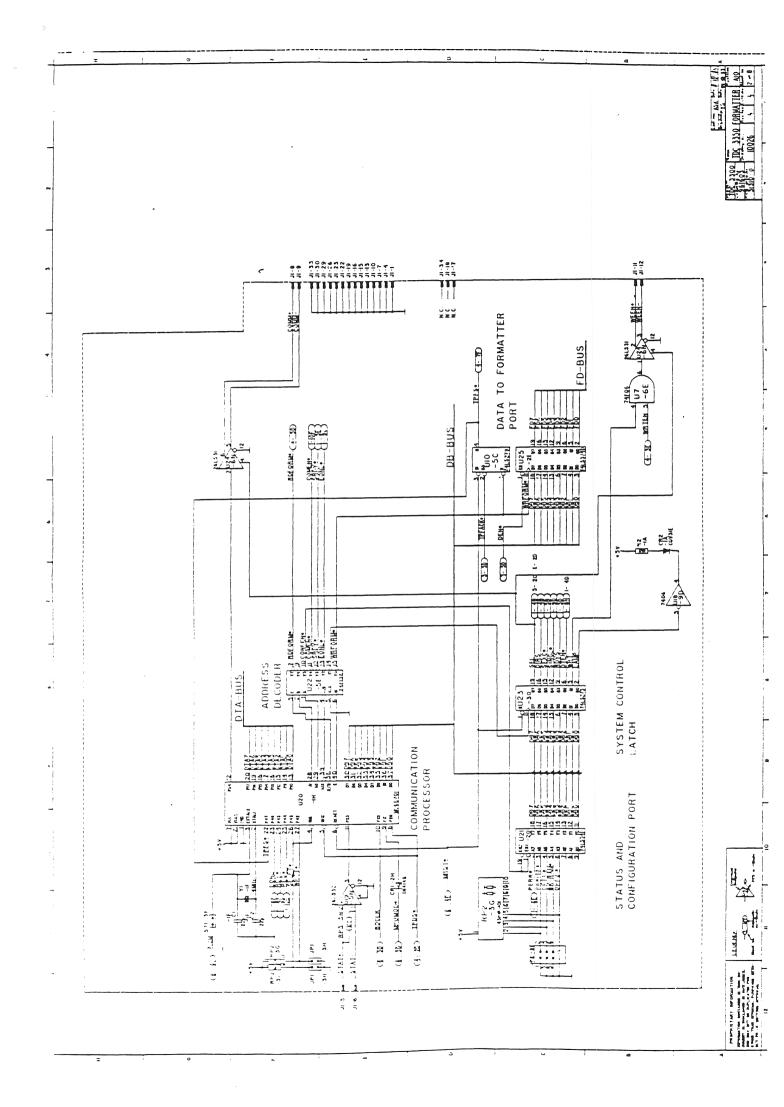

## COMMUNICATIONS PROCESSOR

The microprocessor with its internal program memory has an overriding control over all functions of the basic drive and the formatter. This includes:

- \* Reading and decoding commands from the host via HB-to-DB port.

- \* Starting or stopping the tape.

- \* Moving the head to the next track when reversing at BOT.

- \* Searching for tape edge or reference track at the beginning of a tape.

- \* Reversing tape motion, and carrying out a re-try operation when a reading error has occurred.

- \* Keeping track of the the number of blocks and filemarks on the tape and how many times repeated reading and writing has been carried out.

The processor also has communications tasks, such as:

- \* Loading commands to the Formatter Processor into the DB-to-FD latch.

- \* Reading the contents of the FD-to-DB latch to obtain status information from the Formatter Processor.

- \* Unloading the contents of the FD-to-DTA latch into the DTA-bus.

## ADDRESS DECODER

Decodes data from the processor to provide the various clock pulses and enabling pulses.

# STATUS AND CONFIGURATION LATCH

Via this port the Communications Processor can read:

- \* The size of the installed buffer circuits (necessary for generation of the correct segment addresses).

- \* Parity error.

The Port is enabled by CONFEN\*

## SYSTEM CONTROL LATCH

Stores a system control word issued by the Communications Processor. Each bit in the control word represents one particular system parameter.

## DB-TO-FD LATCH

----------

Stores commands from The Communications Processor to the Formatter Processor. The latch is loaded on the WRFORM-pulse from the Address Decoder, and output data is available on the FD-bus during the DEN\* pulse from the Formatter Processor.

Signal connections between this circuit diagram sheet and other sheets of the Formatter circuit diagram.

Connections to other boards are also shown.

-

1 \*

í

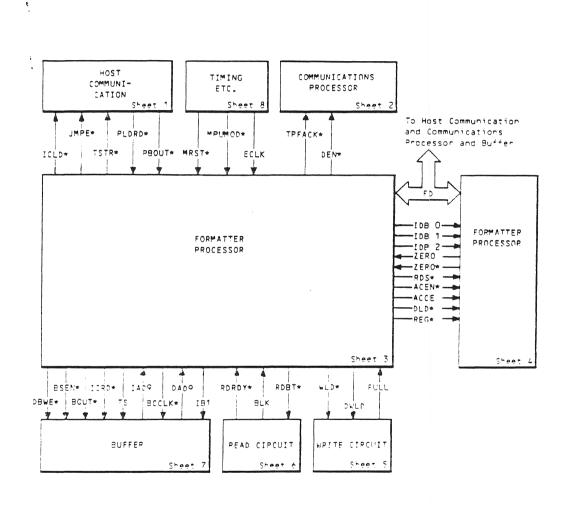

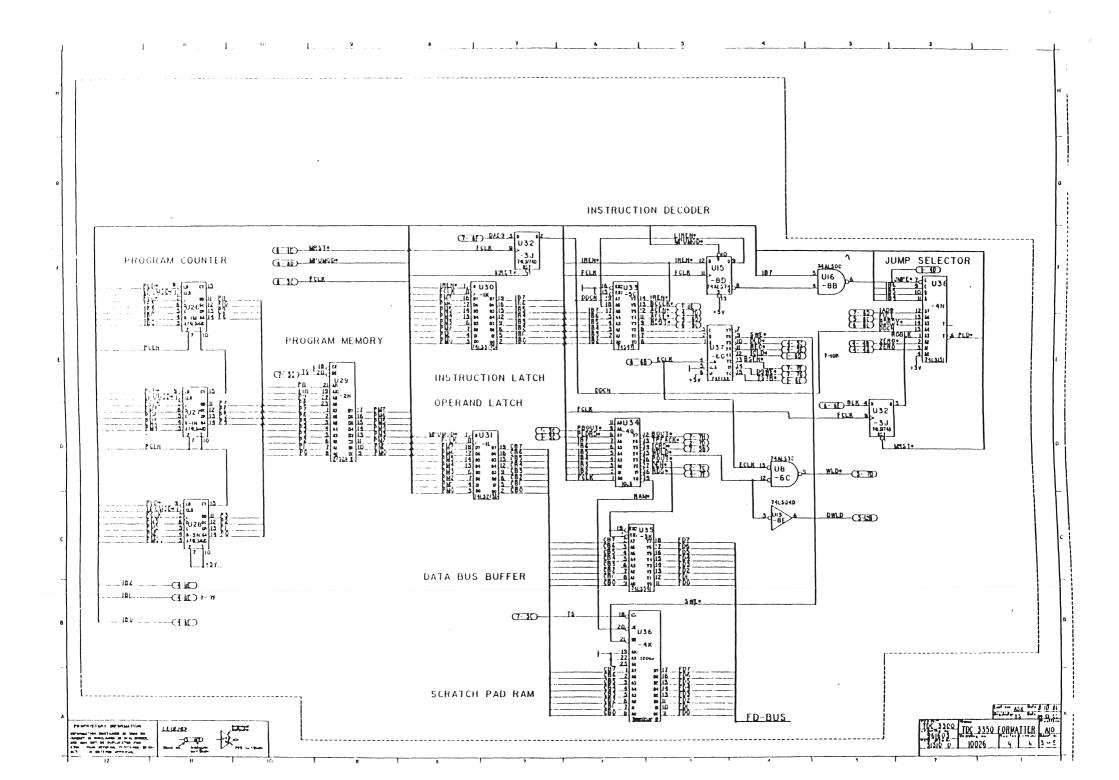

FORMATTER PROCESSOR

## PROGRAM COUNTER

Loaded from Program Memory and Instruction Latch when a jump instruction is to be executed (PLD\* present). Counts up on FCLK pulses between the jump instructions. MPUMOD\* initializes the program counter at power-up and reset.

#### PROGRAM MEMORY

PROM containing the entire program for the Formatter Processor. The address being applied from the program counter selects the instruction to become available at the output.

## INSTRUCTION LATCH

Loaded from the Program Memory when IREN\* from the Instruction Decoder is present. The latch then holds the instruction for one FCLK period in 1-byte instructions; or until the operand has been transferred in 2-byte instructions.

#### OPERAND LATCH

##

Loaded from the program memory. In a 1-byte instruction the operand latch is loaded with the instruction. In a 2-byte instruction it is also loaded during the first FCLK pulse with the instruction (which is not used), but ends up with the operand after the second FCLK pulse.

## INSTRUCTION DECODERS

### Each instruction word stored in the instruction latch will activate one or more of the output lines from the decoders depending on the operation to be carried out.

# DATA BUS BUFFER

Connects the output of the Operand Latch to the FD-bus when required.

## SCRATCH-PAD RAM

Temporary storage for variables and system parameters used by the formatter processor.

Fold out ſ

JUMP SELECTOR

Generates PLD\* which initiates loading of the Program counter when a jump instruction is to be executed. The jump condition is determined by the instruction bits IB4-IB6. JMPE\* enables the selector. While the jump instruction is carried out the FD-bus is not occupied by the formatter processor and can therefore be used for data transmissions between data buffer and host.

Signal connections between this circuit diagram sheet and other sheets of the Formatter circuit diagram.

Connections to other boards are also shown.

(1) (1)

٢ . •

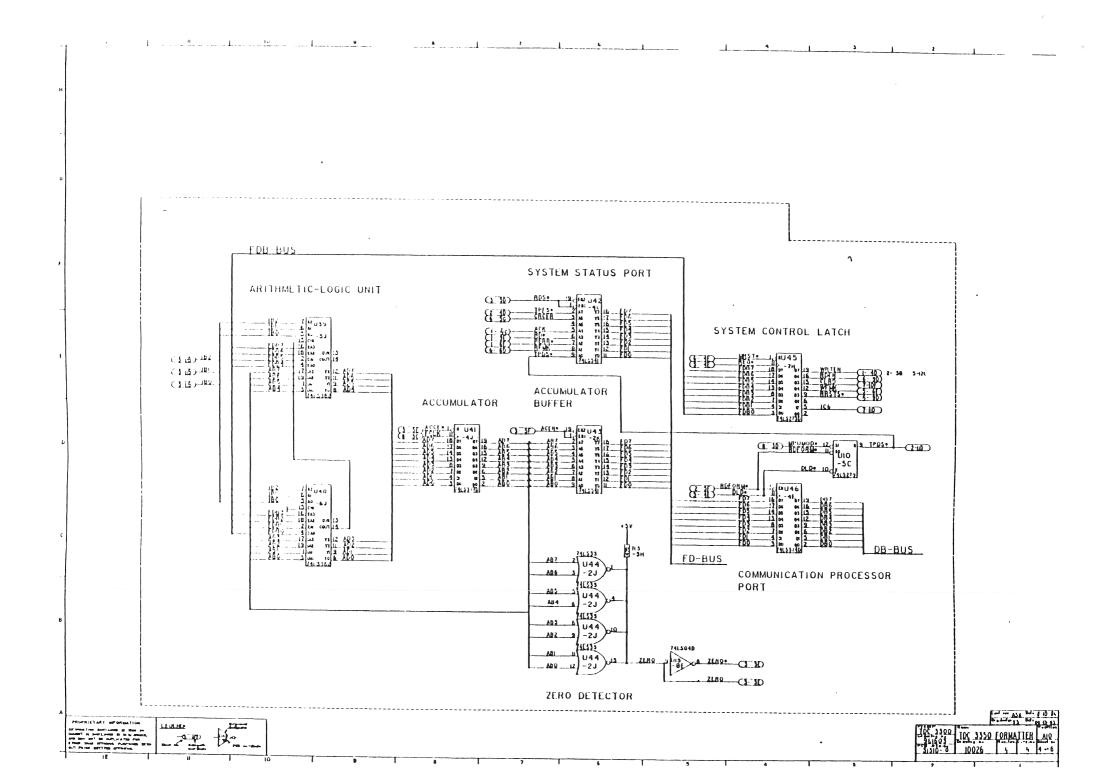

## ARITHMETIC/LOGIC UNIT

Performs arithmetic and logic operations on data from the FDB bus and from the accumulator output. The result is presented to the accumulator input. The operation to be carried out is determined by IBO-IB2 from the Instruction latch.

#### ACCUMULATOR

##

Stores the result from the arithmetic/logic unit.

## ACCUMULATOR BUFFER

The tristate outputs of these line drivers are enabled by ACEN\* from the instruction decoder (sheet 3). Data in the Accumulator Buffer can be distributed to the following circuits:

- Data Buffer (Sheet 7)

Block Address Selector (Sheet 7)

External Address Counter (Sheet 7)

Scratch Pad RAM (Sheet 3)

FD-to-DB Latch (Sheet 4)

- System Control Latch (Sheet 2)

- Write FIFO (Sheet 5)

#### SYSTEM STATUS PORT

Applies system status parameters to the FD bus when the tristate outputs are enabled by RDS\* from the Instruction Decoder (sheet3).

# SYSTEM CONTROL LATCH

Generates system control signals based on data picked up from the FD-bus when REG\* is present.

## FD-TO-DB LATCH

Status signals for the Communication Processor is loaded into the latch from the FD-bus while DLD\* is present. The tristate outputs apply the stored information to the DB-bus during RDFORM\*.

## ZERO DETECTOR

Provides two of the input signals (ZERO and ZERO\*) to the Jump Selector when the accumulator output is zero.

ţ.

Signal connections between this circuit diagram sheet and other sheets of the Formatter circuit diagram.

.

Connections to other boards are also shown.

X.

WRITE CIRCUIT

The write operation includes the following phases as determined by WMO and WM1 from the Write Data Sequencer:

- \* Generation of the preamble. Takes place in the write data controller until the write FIFO is full (while WMO=O and WM1=O).

- \* Generation of the marker (1 byte). Takes place in the write data controller when WMD=1 and WM1=0.

- \* Conversion of the 512 data bytes and the block address into 5-bit serial GRC code. Takes place in the Write Data Controller when WMO=1 and WM1=1.

- \* Generation of the CRC character, which takes place in the CRC generator throughout the whole data field, and block address and subsequently converting it into 5-bit serial GRC code (takes place in the write data controller when WMO=0 and WM1=1).

- \* Generation of the postamble. Takes place in the write data controller when WM=O and WM1=O (high density mode).

The durations of preamble, data field and postamble are controlled by the FormatterProcessor.

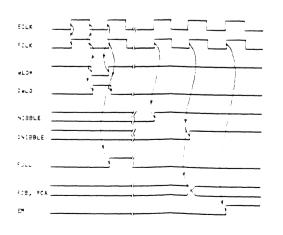

WRITE FIFO CONTROLLER

Generates:

- \* Read and write addresses for the Write FIFO.

- \* FIFO FULL signal which makes the Write Data Sequencer leave the high density mode.

- \* FIFO empty (EM) which makes the sequencer enter CRC mode. The FIFO controller is enabled by WRTEN from the Formatter Processor, whereas DWLD clocks the write address counter.

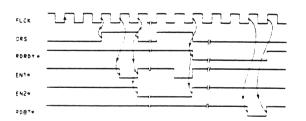

Write FIFO Controller timing.

# Fold out

Data from the FD bus can be written into either one of the four FIFO locations as determined by the write address while the WLD\* pulse is present.

Reading out from the FIFO is controlled by the read address bits RCA and RCB, and takes place in two consecutive 4-bit nibbles. The MSN \* or the LSN\* enabling pulse from the Write Data sequencer selects the most significant or the least significant nibble.

## WRITE DATA SEQUENCER

Interacts very closely with the Write Data Controller in the various phases of the write operation described above. WCLKS determines the bit rate of the serialized data signal from the Write Data Controller whereas WCLKS controls the nibble operation. Status signals from the FIFO Controller(EM and FULL) change the mode of operation.

### WRITE DATA CONTROLLER

Performs the conversion of 4-bit nibbles into serial 5-bit GRC code in interaction with the Write Data Sequencer.

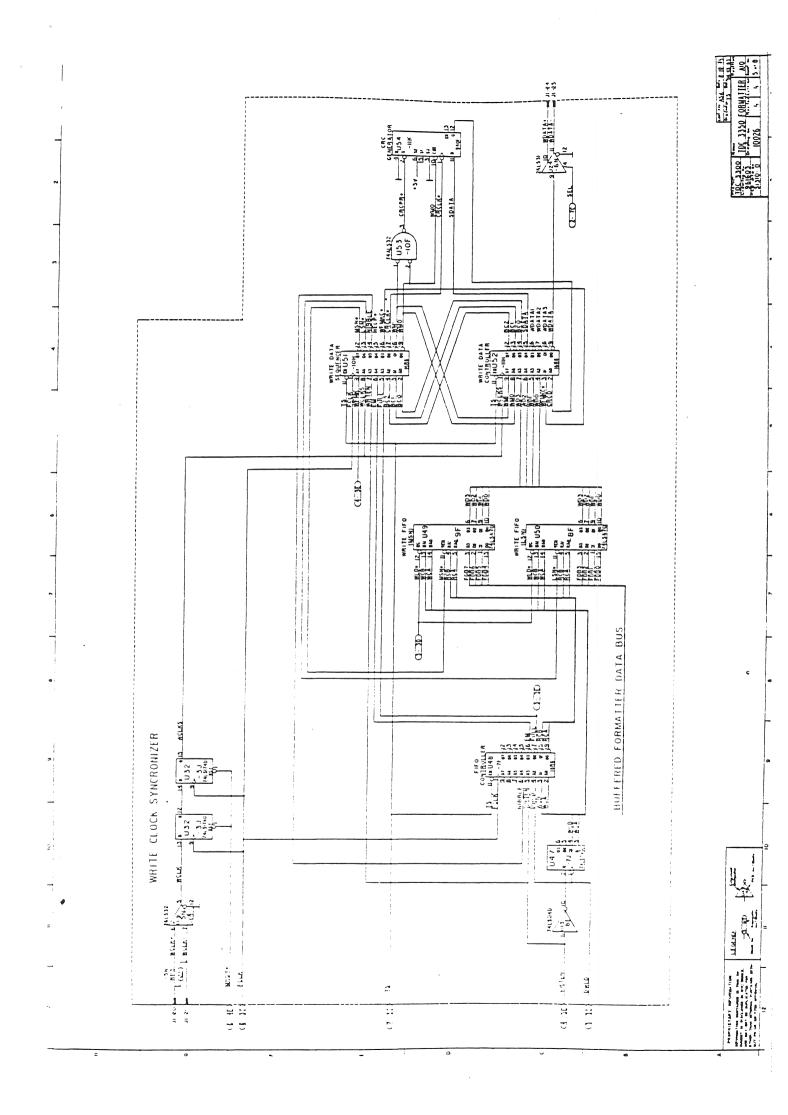

## WRITE CLOCK SYNCHRONIZER

4 • 1

Locks the WCLK signal from the Control Board to the FCLK to generate the

WCLKS pulses.

Signal connections between this circuit diagram sheet and other sheets of the Formatter circuit diagram.

Connections to other boards are also shown.

. .

## READ CIRCUITS

The read operation includes the following phases:

- \* Examination of the serial bit stream (RDATA) from the Read Board in the Basic Drive in search for the preamble and the block marker.

- \* After detection of the block marker, reduction of the 5-bit GRC coded data into 4-bit nibbles.

- \* Conversion of the nibbles into 8-bit words which are forwarded to the Formatter Processor on parallel form.

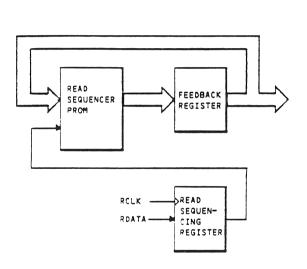

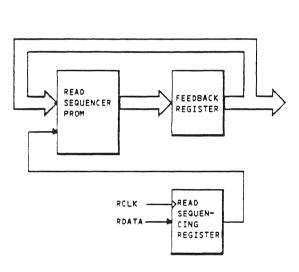

## READ DATA SYNCHRONIZER AND CODE CONVERTER

Simplified diagram of Read Data Synchronizer and Code Converter. GCR-coded RDATA is clocked into the Read Sequencing Register by RCLK, and appears at the DI output which represents one of the address bits for the Read Sequencer PROM. Each received data bit will thus represent one of two possible memory locations depending on whether the bit is a "one or a zero". The content of the accessed location is fed back via the Feedback Register and forms a new address along with the next bit on the DI-line.

Accordingly, a specific route through the memory will correspond to one particular DI bit pattern. It may help comprehension to think of the Read Sequencer PROM as a maze where you will reach a given destination only by taking the appropriate path at every diversion.

The operation of this circuit in search for specific bit patterns (preamble,block marker,etc), and for code conversion is explained in the following:

## READ CIRCUITS

The read operation includes the following phases:

- \* Examination of the serial bit stream (RDATA) from the Read Board in the Basic Drive in search for the preamble and the block marker.

- \* After detection of the block marker, reduction of the 5-bit GRC coded data into 4-bit nibbles.

- \* Conversion of the nibbles into 8-bit words which are forwarded to the Formatter Processor on parallel form.

READ DATA SYNCHRONIZER AND CODE CONVERTER

ŧ

:

Simplified diagram of Read Data Synchronizer and Code Converter. GCR-coded RDATA is clocked into the Read Sequencing Register by RCLK, and appears at the DI output which represents one of the address bits for the Read Sequencer PROM. Each received data bit will thus represent one of two possible memory locations depending on whether the bit is a "one or a zero". The content of the accessed location is fed back via the Feedback Register and forms a new address along with the next bit on the DI-line.

Accordingly, a specific route through the memory will correspond to one particular DI bit pattern. It may help comprehension to think of the Read Sequencer PROM as a maze where you will reach a given destinatic only by taking the appropriate path at every diversion.

The operation of this circuit in search for specific bit patterns (preamble,block marker,etc), and for code conversion is explained in the following:

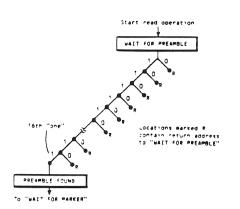

Path through the Read Sequencer PROM when searching for preamble in the DI bit stream.

# Search for Preamble

Before the preamble arrives, DI from the Sequencing Register and the Feedback Regist outputs are all zeroes.

As the first bit appears on the DI-line, a new memory location will be accessed in which the next address is stored. This address is fed back via the Feedback Register to the Read Sequencer PROM along with the bit on the DI line. The 16th DI pulse in a continuous string of "ones" will access the location which confirms that the preamble has been detected. Any departure from the string of 16 consecutive"ones" will return the sequencer to the starting point, and will require a subsequent string of 16 "ones".

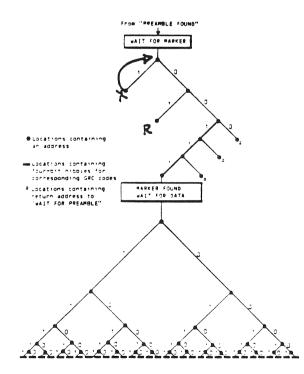

Path through the Read Sequencer PRCM when searching for block marker and when converting GCR codes to binary ribbles.

## Search for Marker, and Conversion

## of GRC Codes

From the location representing preamble detection a search will now start for the block marker being represented by another location accessible only through an error-f reception of the marker bit pattern.