## PROM User's Manual Addenda and Errata

Sun Microsystems, Inc. • 2550 Garcia Avenue • Mountain View, CA 94043 • 415-960-1300

The Sun logo, Sun Microsystems, and Sun Workstation are registered trademarks of Sun Microsystems, Inc.

Sun, Sun-2, Sun-3, Sun-4, Sun386*i*, SunInstall, SunOS, SunView, NFS, NeWS, and SPARC are trademarks of Sun Microsystems, Inc.

UNIX is a registered trademark of AT&T.

All other products or services mentioned in this document are identified by the trademarks or service marks of their respective companies or organizations.

SunIPC is a trademark of Sun Microsystems, Inc.

ALM and ALM2 are trademarks of Sun Microsystems, Inc.

DVMA is a trademark of Sun Microsystems, Inc.

Tapemaster is a trademark of Ciprico, Inc.

Copyright © 1988 - 1989 Sun Microsystems, Inc. - Printed in U.S.A.

All rights reserved. No part of this work covered by copyright hereon may be reproduced in any form or by any means – graphic, electronic, or mechanical – including photocopying, recording, taping, or storage in an information retrieval system, without the prior written permission of the copyright owner.

Restricted rights legend: use, duplication, or disclosure by the U.S. government is subject to restrictions set forth in subparagraph (c)(1)(ii) of the Rights in Technical Data and Computer Software clause at DFARS 52.227-7013 and in similar clauses in the FAR and NASA FAR Supplement.

The Sun Graphical User Interface was developed by Sun Microsystems Inc. for its users and licensees. Sun acknowledges the pioneering efforts of Xerox in researching and developing the concept of visual or graphical user interfaces for the computer industry. Sun holds a non-exclusive license from Xerox to the Xerox Graphical User Interface, which license also covers Sun's licensees.

## Contents

| New Monitor Command Feature                         | 1    |

|-----------------------------------------------------|------|

| EEPROM Security Feature                             | 1    |

| The Password                                        | 2    |

| Changing Security Modes                             | 3    |

| EEPROM Layout for PROM Security                     | 4    |

| 3-D Logo EEPROM Parameter                           | 4    |

| Sun-3 Extended Tests                                | 5    |

| New Boot Path Extended Tests                        | 5    |

| Sun-3/400 Series and Sun-3/80 PROM                  | 5    |

| The Power-Up Test Sequence                          | 6    |

| Diagnostic LEDs                                     | 7    |

| Sun-3/80 LED                                        | 8    |

| The Boot Sequence                                   | 8    |

| Diagnostic Power-Up                                 | 9    |

| More Interactive Self-Test Commands                 | 11   |

| A Successful Sun-3/80 Self-Test                     | 11   |

| Test Loop Menu — Sun-3/400 Series and Sun-3/80      | 12   |

| Successful Diagnostic Boot Display                  | 12   |

| Remote Testing                                      | 13   |

| Diagnostic Self-test Sequence                       | _ 14 |

| Sun-3/80 LED                                        | 20   |

| Self-Test Descriptions                              | 22   |

| LED Register Test                                   | 22   |

| UART SCC (Z8530) Port A,B Write/Read Test           | 22   |

| Keyboard/Mouse SCC (Z8530) Port A,B Write/Read Test | 23   |

| Central Cache Write Miss, Writeback Test                        |

|-----------------------------------------------------------------|

| Central Cache Line Cross Invalid Read Miss Test                 |

| Central Cache Line Cross Write Miss Writeback Test              |

| Central Cache Writeback Timeout Test                            |

| Block Copy (Source=Cache Miss,Dest=Cache Miss) Test             |

| Block Copy (Source=Cache Miss,Dest=Cache Hit) Test 47           |

| Block Copy (Source=Cache Hit,Dest=Cache Miss) Test              |

| Block Copy (Source=Cache Hit,Dest=Cache Hit) Test 49            |

| Memory Write/Write/Read Read Test (Central Cache on)            |

| IOC Tag RAM Write/Write/Read Test                               |

| IOC Tag RAM Address Test                                        |

| IOC Tag RAM 3-Pattern Test                                      |

| IOC Data RAM Write/Write/Read Test                              |

| IOC Data RAM Address Test                                       |

| IOC Data RAM 3-Pattern Test                                     |

| IOC Data RAM Read Byte Alignment Test                           |

| IOC Data RAM Write Byte Alignment Test                          |

| VME Loopback Test                                               |

| VME Loopback and DVMA Test                                      |

| IOC Read Hit Test                                               |

| IOC Invalid Read Miss Test                                      |

| IOC Write Hit Test                                              |

| IOC Write Miss, No Writeback Test                               |

| IOC Write Miss, Writeback Test 59                               |

| IOC Read Miss, Writeback Test                                   |

| IOC Valid Write Hit (Central Cache Match, Unmod) Test           |

| IOC Invalid Read Miss (Central Cache Match, Unmod) Test 63      |

| IOC Invalid Read Miss (Central Cache Match, Modified)<br>Test65 |

| IOC Valid Read Miss (Central Cache Match), Writeback Test66     |

| IOC Flush (Valid, Modified) Test 68                             |

| IOC Flush (Valid, Not Modified) Test                            |

|   | IOC Flush (Not Valid, Not Modified) Test            |

|---|-----------------------------------------------------|

|   | I/O Mapper Invalid Page (IO.DT) Test                |

|   | IOC Write Miss, Writeback (Write Protect) Test      |

|   | IOC Invalid Read Miss (IO Mapper IO.EN = 0) Test    |

|   | IOC Write Miss (IO Mapper IO.EN = 0) Test           |

|   | IOC Random Data Block Write Test                    |

|   | IOC Random Data Block Read (Central Cache off) Test |

|   | IOC Random Data Block Read (Central Cache on) Test  |

|   | P4 Overlay Frame Buffer Write/Write/Read Test       |

|   | P4 Overlay Frame Buffer Address Test                |

|   | P4 Overlay Frame Buffer 3-Pattern Test              |

|   | P4 Overlay Frame Buffer March Test                  |

|   | P4 Overlay Frame Buffer Read Byte Alignment Test    |

|   | P4 Overlay Frame Buffer Write Byte Alignment Test   |

|   | P4 Enable Plane Write/Write/Read Test               |

|   | P4 Color Plane Write/Write/Read Test                |

|   | Printer Controller Check — Sun-3/80                 |

|   | Clock/Calendar Device — 3/80 Only                   |

|   | LANCE Ethernet Controller Check — 3/80 only         |

| , | ESP SCSI Check — 3/80 Only)                         |

| H | ost System Initialization                           |

| Т | he Sun-3 PROM Monitor                               |

| B | ringing up the PROM Monitor                         |

| С | onventions                                          |

| M | Ionitor Command Overview                            |

|   | Executing a Command                                 |

|   | Default Values                                      |

|   | Word Sizes                                          |

| T | he Monitor Commands                                 |

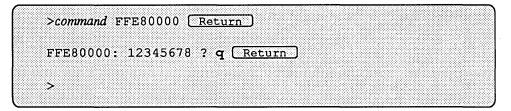

|   | Displaying and Modifying Memory                     |

| S | pecial Monitor Commands                             |

|   | Address Increment/Decrement Command                 |

|   | The ^r Command — Sun-3/400 series only              |

| The <sup>t</sup> Command                            | 39             |

|-----------------------------------------------------|----------------|

| The ^i Command                                      | 90             |

| The <sup>c</sup> Command                            | 90             |

| The ! Command                                       | 90             |

| Regular Monitor Commands                            | 90             |

| Monitor a Command                                   | <del>)</del> 0 |

| Monitor A Command—Sun-3/400 Series                  | 91             |

| Monitor b Command                                   | 91             |

| Monitor c Command                                   | <del>)</del> 3 |

| Monitor d Command                                   | <del>)</del> 3 |

| Monitor e Command                                   | <del>)</del> 3 |

| Monitor <b>f</b> Command                            | <del>9</del> 3 |

| Monitor F Command—Sun-3/400 Series                  | 94             |

| Monitor g Command                                   | 94             |

| Monitor h Command                                   | 94             |

| Monitor i Command — Sun-3/200 or Sun-3/400 series   | 94             |

| Monitor j Command — Sun-3/200 or Sun-3/400 Series   | 95             |

| Monitor k Command                                   | 95             |

| Monitor 1 Command                                   | 95             |

| Monitor m Command                                   | <del>9</del> 5 |

| Monitor n Command — Sun-3/200 and 3/400 series only | 96             |

| Monitor o Command                                   | 96             |

| Monitor p Command                                   | 96             |

| Monitor q Command                                   | 96             |

| Monitor <b>r</b> Command                            | 97             |

| Monitor R Command—(Sun-3/400 Series only)           | 98             |

| Monitor s Command                                   | 98             |

| Monitor T Command—Sun-3/400 Series                  | 98             |

| Monitor u Command                                   | 99             |

| Monitor v Command                                   | 01             |

| Monitor w Command                                   | 01             |

| Monitor × Command                                   | 01             |

| Monitor y Command — Sun-3/200 or -3/400 Series 10   | 01             |

,

| 1.1. SPARCsystem 330 Self-Tests and Monitor Commands | 103 |

|------------------------------------------------------|-----|

| Self-Test Interaction                                | 103 |

| Successful Self-Test Display                         | 107 |

| To Read the CPU Board LED Table                      | 107 |

| The SPARCsystem 330 PROM Monitor                     | 109 |

| Monitor <b>r</b> Command                             | 110 |

| Monitor <b>s</b> Command                             | 110 |

| Monitor t Command                                    | 110 |

| Monitor v Command                                    | 110 |

| Monitor <b>^a</b> Command                            | 111 |

| Monitor <b>^c</b> Command                            | 111 |

| Monitor ! Command                                    | 111 |

| Identifying A Faulty Memory Module                   | 111 |

| SPARCsystem 330 Extended Tests                       | 111 |

| SPARCsystem 330 Initialization                       | 113 |

|                                                      |     |

## Tables

| Table 1-1         Self-Test Execution Time Comparisons | 7   |

|--------------------------------------------------------|-----|

| Table 1-2 Miscellaneous Registers for the 68020        | 97  |

| Table 1-3 Miscellaneous Registers for the 68030        | 97  |

| Table 1-4 Function Code Values                         | 98  |

| Table 1-5 Port Arguments                               | 100 |

| Table 1-6 Option Arguments                             | 100 |

| Table 1-7 SPARCsystem CPU Board LED Interpretation     | 108 |

|                                                        |     |

## Figures

| Figure 1-1  | Sun-3/75, 3/140, 3/150, 3/160, and 3/110 Diagnostic Boot |     |

|-------------|----------------------------------------------------------|-----|

| Tiguie 1-1  | Sequence                                                 | 14  |

| Figure 1-2  | Sun-3/50 and Sun-3/60 Diagnostic Boot Sequence           | 15  |

| Figure 1-3  | Sun-3/260 and Sun-3/280 Diagnostic Boot Sequence         | 16  |

| Figure 1-4  | Sun-3/400 Series Diagnostic Boot Sequence                | 17  |

| Figure 1-5  | Sun-3/80 Diagnostic Boot Sequence                        | 19  |

| Figure 1-6  | Sun-3 Monitor Help Menu                                  | 85  |

| Figure 1-7  | SPARCsystem 330 Diagnostic Boot-Up Display               | 104 |

| Figure 1-8  | Diagnostic Boot-Up Display - Continued                   | 105 |

| Figure 1-9  | Diagnostic Boot-Up Display - Continued                   | 106 |

| Figure 1-10 | D Ethernet Loopback Connector                            | 112 |

|             |                                                          |     |

· · ·

### PROM User's Manual Addenda and Errata

The PROM User's Manual describes PROM monitor commands, self-tests and extended tests for Sun-2 through Sun-386i systems. This text adds to or modifies the information found there, for Sun-3 systems with the new, 2.8 version of the Boot PROM, and all Sun-3/400 series, the Sun-3/80 and SPARCsystem 330s.

In the past, all numerical PROM monitor commands were entered in hexadecimal. If you have PROM version 2.8, or a Sun-3/400 series system, a Sun-3/80 or SPARCsystem 330, you may now enter decimal or ASCII values after the PROM monitor prompt ( > ). This feature is particularly useful when using the monitor q command to program the EEPROM, which sometimes requires that you convert letters and decimal numbers to hexadecimal values before you enter them.

To enter a decimal value after a PROM monitor command, simply precede the value with the "%" character:

>q 050 %20

To enter an ASCII character, simply precede it with the "@" character:

If the value you enter is not preceded by a % or @ character, the monitor program treats that the value as hexadecimal.

Chapter 10 of the PROM User's Manual describes the Sun-3 and Sun-4 EEPROM. There is now a Security Mode Select Feature, located at EEPROM address 0x492. This feature provides a non-secure mode that permits the use of all PROM monitor commands.

It also provides a *command secure* mode that permits the use of PROM monitor commands (other than c, for continue, or b, for boot, without parameters) only when a password is entered. In the command secure mode, you may operate your workstation normally, including powering down, booting, terminating with the L1-A command, and re-booting. You may not, however, perform any unusual operations, such as booting a non-standard kernel, running diagnostics,

Feature

**New Monitor Command**

**EEPROM Security Feature**

1

or changing EEPROM or CPU board memory contents, without entering a password.

Finally, this feature provides a *fully secure* mode that does not permit use of the PROM monitor (other than the c command with no parameters) without entering a password. To power-up, re-boot, or perform any other PROM monitor operation, you must supply a password. This mode allows you to control access to the workstation by turning it off. The workstation does not automatically boot on power-up.

# CAUTION In fully secure mode, even a default boot cannot be completed unless the password is entered. Once the SunOS is halted, you cannot restore it until you enter the correct password after the prompt. If the password is unknown, the system CPU board must be serviced as a failed board.

The Password

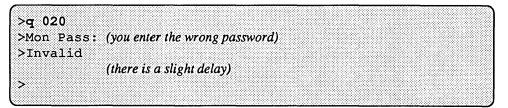

If you should attempt to enter a PROM monitor command such as q, for example, on a system that is set for one of the secure modes, your interaction might look like this:

|           |              | at EEPROM offset  |  |

|-----------|--------------|-------------------|--|

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

| >q 020    |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

| >Mon Pass | (you enter t |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

| >EEPROM ( |              | on 020 are shown) |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

|           |              |                   |  |

Or, if you enter an incorrect password, your interaction might look like this:

You may now try again or enter an unprotected command.

To install or change a password, the system must be in non-secure mode, or you must know the existing password for a secure system. You then use the PROM monitor  $\mathbf{q}$  command to enter the password in EEPROM offset location 490 for Sun-3 and Sun-4 (SPARC) systems, or 160 for the Sun386i.

NOTE

When you attempt to change the values stored in the EEPROM monitor password locations, you will be prompted with this message:

Modifiying security location(s). Are you sure?(y/N)

If you enter y for yes, the change you entered is written to the location shown. If you enter n for no, nothing is written to EEPROM, and the contents of the next location are displayed.

To enter a monitor password, use the @ character, described at the beginning of this document, in order to enter the letters that make up the password. If you do not use the @ character, you must enter the hexadecimal equivalent of the letters. Following is an example of the way you would enter a password called *mypasswd* on a Sun-3 or Sun-4 system. You enter one letter per location, followed with : <u>Return</u>. To exit the command, you may enter any non-

hexadecimal character, such as period, as shown.

| >q 493                         |                |                    |

|--------------------------------|----------------|--------------------|

| > EEPROM 493: 00? @m           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) <b>Yes</b> |

| > EEPROM 494: 00? @y           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) <b>Yes</b> |

| > EEPROM 495: 00? @p           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) <b>Yes</b> |

| > EEPROM 496: 00? @a           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) <b>Yes</b> |

| > EEPROM 497: 00? @s           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) <b>Yes</b> |

| > EEPROM 498: 00? @s           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) <b>Yes</b> |

| > EEPROM 499: 00? @w           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) Yes        |

| > EEPROM 49a: 00? @d           |                |                    |

| Modifiying security location(s | ). Are you sur | e?(y/N) Yes        |

| > EEPROM 49b: 00? .            |                |                    |

| >                              |                |                    |

*TE* If a password was already stored in locations 493-49a, hexadecimal values would appear in place of the zeroes in the example above.

The password you enter must either fill the eight bytes (locations 493-49a) with a character or a zero.

Note that changes to the security mode and password do not take effect until the PROM monitor mode is re-entered.

It is recommended that the password is changed before the security mode is changed. For more information on using the EEPROM **q** command, refer to the *PROM User's Manual*, Sun PN 800-1736, or the Monitor (8S) section of the *SunOS Reference Manual*.

**Changing Security Modes**

The EEPROM offset location 492 (or 162 for a Sun386i) contains a value that determines the security mode. The table below shows the interpretation of values found in that location. The "0x" denotes a hexadecimal value.

| 0x1              | command secure |

|------------------|----------------|

| 0x5e             | fully secure   |

| all other values | non-secure     |

Because the PROM monitor password is stored as text, it is recommended that the chmod and /etc/chown commands be used so that the /dev/eeprom device file may be accessed by the super-user. To accomplish this, enter:

| 8 <b>su</b> |        |         |         |        |          |

|-------------|--------|---------|---------|--------|----------|

| Passwo      | ord: e | nter yo | ur supe | r-user | password |

| # cd /      | 'dev   |         |         |        |          |

| # /etc      |        | n roc   | ot ee   | prom   |          |

| # chmc      |        |         |         |        |          |

|             |        |         |         |        |          |

#### EEPROM Layout for PROM Security

Here is a table that shows the EEPROM offset locations for the Sun-3, Sun-4 and Sun386i systems.

| Sun386i<br>Offset | Sun-3,-4<br>Offset | Field     | Function                                                                                                                                                               |

|-------------------|--------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x160-1           | 0x490-1            | bad_login | The bad login<br>counter stores<br>the number of<br>invalid pass-<br>word attempts.<br>The maximum<br>value is 65535<br>and the counter<br>does not roll<br>over to 0. |

| 0x162             | 0x492              | secure    | The values 1<br>and 0x5e<br>correspond to<br>command<br>secure and fully<br>secure, respec-<br>tively. Any<br>other value is<br>non-secure.                            |

| 0x163-a           | 0x493-a            | password  | If the password<br>is shorter than 8<br>bytes, the pass-<br>word string is<br>fenced with a<br>null character.                                                         |

#### **3-D Logo EEPROM** Parameter

If your system has a CG6 board, you may set EEPROM location 0x020 to 0x06 so that, upon power-up, the Sun logo appears to be three-dimensional. Refer to the *PROM User's Manual* monitor **q** command description for information on changing EEPROM values.

#### **Sun-3 Extended Tests**

Chapter 9 of the *PROM User's Manual* describes Sun-3 extended tests. For workstations with the boot PROM version 2.8, many of these tests are unavailable, and the user interface has changed. The new PROM version tests only the devices needed to boot the operating system. Therefore, when you invoke the extended tests from the monitor prompt,

>x

the menu of extended tests look something like this:

Extended Test Menu: (Enter 'q' to exit) Cmd - Test Intel Ethernet Test ie mk \_ Mouse/Keyboard Ports Test Serial Ports Test rs

NOTE

For CPU boards with the AMD AM7990 (Lance) Ethernet chip, the first choice will be

ae - AMD Ethernet Test

New Boot Path Extended Tests In order to invoke the disk and tape bootpath tests when a version 2.8 PROM is installed on a Sun-3 CPU board, you must enter an asterisk after the boot command, from the monitor prompt:

>b\*device ()

The extended test appropriate for the named *device* will then be executed, and any error messages displayed on the screen. *device* could be one of the following:

- sd for SCSI disk

- st for SCSI tape

xd for Xylogics 7053 Disk Controller

xt for Xylogics tape

xy for Xylogics 450/451 Disk Controller

Sun-3/400 Series and Sun-3/80 PROM For Sun-3/400 series and Sun-3/80 users, the text that follows is intended to replace Chapters 7 and 8 in the *PROM User's Manual*, Sun PN 800-1736-10. These chapters cover changes to PROM monitor commands and self-tests associated with the Sun-3/400 product. In addition, the information in Chapter 13 of the PROM manual, "Sun-4 Extended Test System", applies to the Sun-3/400 series workstation. If you have a Sun-3/400 series system, Chapter 9, "Sun-3 Extended Test System" does not apply.

#### The Power-Up Test Sequence

In order to perform the power-up tests, two assumptions must be met. The CPU (the non-PMMU portion of the MC68030 for the Sun-3/400 series system) must be functional and the ability to fetch instructions from the Boot PROM must be intact.

Powering up a Sun-3 workstation resets the CPU to *boot* state, which means that all instruction fetches are forced to the Boot PROMs. Execution of the minimum-confidence power-up tests begin immediately. These tests do not employ any memory until memory has been successfully checked.

The objective of the power-up test sequence is to determine whether or not the CPU board logic and main memory are functional. Following the successful completion of the power-up tests and subsequent workstation initialization, an attempt is made to boot the SunOS operating system, an EEPROM-specified program, or an operator-specified stand-alone program.

If hardware problems are detected during the verification process, the PROM monitor prompt should appear.

For Sun-3/400 series systems, if the Diagnostic Switch at the rear of the system is in NORM position, you will not be able to interact with the self-tests. You may read the LEDs on the CPU board edge (described later in this chapter) to determine whether or not a test is failing, and you will see a rotating diagonal symbol after the

Testing megabytes of memory...

message on the console during the memory tests. The quantity of memory checked during a power-up with the diagnostic switch on NORM is dependent on EEPROM programming. The EEPROM chapter in the *PROM User's Manual* and the eeprom command description in the *SunOS Reference Manual* explain how to set the parameter that controls the quantity of memory tested.

For the Sun-3/80, which has no diagnostic switch, an EEPROM parameter must be set in order to execute a diagnostic boot-up and view the self-test display on a terminal. Refer to the "Diagnostic Power-Up" section for more information on this setting.

If the workstation contains a large amount of main memory, self-tests may last as long as eight minutes. The table below compares the self-test duration of various Sun-3 systems.

| System Type      | Clock Rate<br>in MHz | Memory Size<br>in Megabytes | Self-test Duration<br>in Minutes |

|------------------|----------------------|-----------------------------|----------------------------------|

| Sun-3/160        | 16 MHz               | 4 Meg                       | .5 Min                           |

| Sun-3/75         | 16 MHz               | 8 Meg                       | .75 Min                          |

| Sun-3/60         | 20 MHz               | 24 Meg                      | 1.75 Min                         |

| Sun-3/80         | 16 MHz               |                             | 11 Sec (est.)                    |

| Sun-3/260        | 25MHz                | 64 Meg                      | 2.5 Min                          |

| Sun-3/400 series | 33MHz                | 128 Meg                     | 2.75 Min (est.)                  |

| SPARC system     |                      | 128 Meg                     | 8.0 Min (est.)                   |

Table 1

Self-Test Execution Time Comparisons

If the Diagnostic Switch is in the NORM position, (or the Sun-3/80 EEPROM parameter set), the power-up tests execute successfully and, if you do *not* terminate the default boot sequence, an attempt is made to down-load the SunOS operating system.

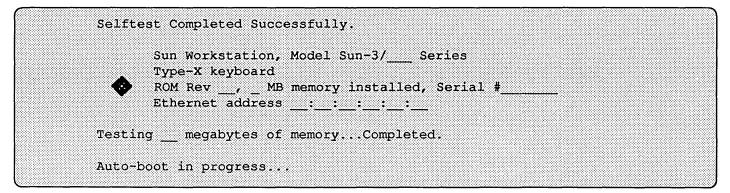

A display something like this appears on the *workstation's* screen to indicate that power-up tests are successful:

#### **Diagnostic LEDs**

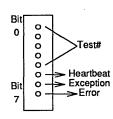

One requirement of Sun-3 firmware is to assign a unique test number to most of the power-up tests and display that number in bits *zero* through *four* of the diagnostic LEDs as the test is running. Given that there are fewer test numbers than there are power-up tests, power-up tests that check the same part of hardware share a test number.

If one of these power-up tests should fail, bit *seven* of the diagnostic LEDs also lights up. Bit seven serves as an indicator that there is a hardware problem. The LED display permits the service person not only to conclude whether or not there is a problem, but to determine which type of power-up test is failing.

Sun-3/80 LED

For the sake of completeness, LED *five* is the *heart beat* LED. After the powerup tests have been completed, but prior to invocation of the SunOS operating system or an EEPROM-specified program, LED 5 will blink on and off to indicate that the IU is actually executing instructions. LED *six* indicates whether or not the failure is an exception (i.e. unexpected trap or unexpected interrupt). The diagram to the left shows LED designations for Sun-3/400 series systems.

Sun-3/80 systems have one green LED that blinks while a test is in progress, and turns OFF when there is an error condition. When the light stays ON, everything is functioning satisfactorily:

| LED status | Visual | Condition |

|------------|--------|-----------|

| Blinking   | Θ      | Testing   |

| OFF        | 0      | Error     |

| ON (Green) |        | Ok        |

#### The Boot Sequence

Following the initialization of the workstation, the default boot sequence is executed. There are two issues that must be considered here. One has to do with *what is to be down-loaded* while the other has to do with *where it is to be loaded from.*

Assuming *no* operator intervention, the position of the Diagnostic Switch (on all Sun-3's except the Sun-3/80) will determine *what* is to be booted. If the Diagnostic Switch is in the NORM position, the SunOS operating system is booted. Otherwise, if the Diagnostic Switch is in the DIAG position, the EEPROM-specified program is booted. Be aware that the PROM monitor program is invoked if no EEPROM-specified program is available.

If you are in the PROM monitor mode, you may specify *what* is to be booted and *where* it is to be booted from. See command **b** (boot) in the chapter titled *Sun-3 PROM Monitor Commands* for a description of how to boot user-specified programs from user-specified devices.

If you are interacting with a Sun-3 workstation through the console to reach the monitor program, you may enter L1-a (or Break) on a terminal) IMMEDI-ATELY after the

Testing \_\_\_ megabytes of memory...Completed.

message.

### CAUTION

Do not use L1-A procedure once the automatic boot has started; the file systems may be damaged if disks are powered-on and the operating system has started to run.

If the operating system is already booted, use the procedures described in Chapter 3 of the *PROM User's Manual* to start the monitor.

Once you are in the monitor mode (symbolized by the > prompt), you should do the following:

Press L1-a or Break again when the message above finishes.

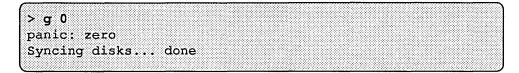

Next you may see this message:

The firmware also determines from what boot device the program will be loaded. If the Diagnostic Switch is in the NORM position and the content of EEPROM location 0x18 is equal to 0x12 (an arbitrarily chosen value), Sun-3 firmware will attempt to boot the SunOS operating system from the boot path specified in the EEPROM, beginning at location 0x19. If the boot path is missing or contains an error, the monitor program is invoked.

If the Diagnostic Switch is in the NORM position and the content of EEPROM location 0x18 is *not* equal to 0x12, Sun-3 firmware attempts to boot the SunOS operating system using the following boot device polling sequence:

- 1. Xylogics Disk (450-451).

- 2. SCSI Disk.

- 3. Ethernet.

If the Diagnostic Switch is in the DIAG position, the firmware assumes that both the path name of the file containing the to-be-loaded program and the boot device are specified in the EEPROM, beginning at EEPROM location 0x22. If either the file name or the boot device is not present or is in error, the monitor is invoked. If the Diagnostic Switch is in the DIAG position, you may connect a terminal to Serial A or B and interact with the self-tests and the Extended Test System, if required.

#### **Diagnostic Power-Up**

NOTE There is no diagnostic switch on a Sun-3/80; an EEPROM setting is required to allow a diagnostic boot-up that displays test names and errors through Serial Port A. Enter the PROM monitor mode and use the **q** command to write **12** to location 0x70b. Any other value causes tests to run without error reporting to the terminal. Refer to "Displaying and Modifying Memory" for information on use of the **q** command.

> If the Diagnostic Switch exists and is on DIAG, the self-test is executed as it is when the switch is 'off' or on NORM, except that all of memory is tested. In addition, self-test status information is directed only to serial ports A and B, using the MMU (Memory Management Unit) bypass until all hardware required for the Video Monitor has been successfully tested.

Any hardware failures during the selftests will invoke scope loops to permit troubleshooting the failure. An RS-232 terminal with its characteristics set to 9600 Baud, 8 data bits, 1 stop bit and no parity should be connected to Serial Port A of the CPU board if you wish to view self-test status and interact with the system. If you use Serial Port B you must set the terminal baud rate to 1200.

Limited interaction with the self-test program is possible in this mode and the following characters will invoke the following actions when entered from the terminal connected to serial port A during self test. Each of these commands is documented below.

#### ESCAPE Key — Sun-3/400 Series and Sun-3/80

Pressing this key any time during the self-test sequence prior to the display of the Selftest Passed message causes the self-test sequence to abort and a warning message is displayed. The necessary memory sizing and other setup is done, and then, for the Sun-3/400 series, the program displays the PROM Monitor menu. For the Sun-3/80, this message is displayed:

<Warning: selftests aborted by user>

<Initializing Main Memory 0x0000000C Megabytes Initialized>

Type a Character within 10 seconds to enter the Menu Tests...(e for e

mode)

EEPROM: Using RS232 A port.

Selftest Completed.

Note that this abort can be done if the test is running normally (without any errors) or if the test is presently looping on any error encountered.

#### Control-q Key — Sun-3/400 Series Only

Holding down the <u>Control</u> key while pressing the q key any time during the execution of a particular Sun-3/400 Series self-test causes that one selftest to stop and execution of the next self-test to begin. For example, if the <u>Control-q</u> sequence was entered during the MEMORY

WRITE/WRITE/READ TEST, that test would terminate and the next test ( MEMORY ADDRESS TEST) would begin. Note that this action can be performed if the test is running normally (without any errors) or if the test is presently looping on any error encountered.

#### Control-l Key — Sun-3/400 Series and Sun-3/80

Holding down the <u>Control</u> key while pressing the 1 key any time during a self-test causes that particular self-test to terminate and control to be transferred to the TEST LOOP MENU. From within this menu any particular self-test can be executed and looped directly, without executing the self-tests that normally come before it. Once a test is invoked from the TEST LOOP MENU, a test control flag is set so that once that test has finished it will go back to the beginning of that one particular test and start it all over again. In order to proceed to the next self-test after a particular self-test has been invoked from this menu, enter the <u>Control-q</u> sequence or the <u>Esc</u> key to go to next test or to the Monitor (as described above). See the section on the Test Loop Menu for more details.

More Interactive Self-Test Commands

**b** Press the **b** (a mnemonic for *burn-in*) key, prior to the display of the ...Completed or Selftest Finished message, to execute the power-up test sequence indefinitely. This option is useful during the manufacturing burn-in stage.

For the Sun-3/80, when the last selftest is finished the message testsAutomaticallycontinuing will be displayed and the self-test will be restarted again, using the System Enable Register read test as the first test. The SCC and terminal I/O tests are bypassed in burn-in mode since operator interaction is required. This looping sequence will continue until an ESCAPE is entered, a reset is done, or the "b" key pressed again to turn burn-in mode off. The burn-in mode can be toggled by successive pressing of the "b" key. Note that this burn-in mode key can be processed during a test that is running normally (no errors), if the test is presently looping on an error encountered, or at the end of selftest when the "Selftest Finished" is displayed and an operator input is requested.

**s** Press the **s** key prior to the display of the ...Completed message to *re-start* the power-up test sequence.

#### Space Bar

If one of the power-up tests fails, it will continue to re-execute forever unless interrupted. Press the <u>space bar</u> to terminate the failed test and execute the next power-up test.

#### Control-m

Holding down the <u>Control</u> key while pressing **m** causes this test to end and sets a flag that allows execution of only the quick memory tests.

#### Control-b

Holding down the <u>Control</u> key while entering **b** causes this test to end and sets a test control flag so that all the tests that require the Bus Error circuitry to work will be skipped. This test is also the equivalent of a "Control-m". It assumes that 8MB of ECC memory are present on the board, because the test is executed before memory has been sized. This test displays no error messages. The Bus Error dependent tests skipped are:

> Bus Error Register Test The Level 1 to Level 3 Interrupt tests P4 Video RAM Board Tests.

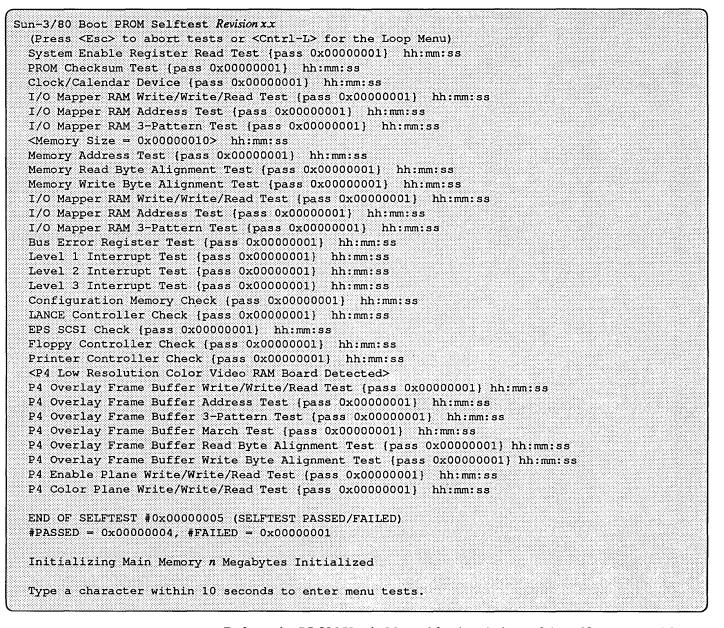

A Successful Sun-3/80 Self-Test

For a Sun-3/80, After the selftest have completed the final status of the selftest sequence will be displayed, as shown by the following example:

END OF SELFTEST # 0x0000005 (SELFTEST FAILED) #PASSED = 0x00000004, #FAILED = 0x00000001 <Initializing Main Memory 0x0000000C Megabytes Initialized> Type a Character within 10 seconds to enter the Menu Tests...(e for echo mode)

Test Loop Menu — Sun-3/400 Series and Sun-3/80 The Test Loop Menu is a menu appears when you press <u>Control-1</u> (loop) key either during Sun-3/400 series or Sun-3/80 self-test execution. Test. The menu allows the operator to transfer self-test control directly to a specified self-test and loop that test continually. This option is intended to support debugging a specific failing test or section of hardware without running all of the previous self-tests.

Once in the Test Loop Menu the following display will be shown on the terminal:

| <                                                                                                   |

|-----------------------------------------------------------------------------------------------------|

| (a) System Enable Register Test                                                                     |

| (b) I/O Mapper RAM Write/Write/Read Test                                                            |

| (b) I/O Mapper RAM Address Test                                                                     |

| (c)I/O Mapper RAM 3-Pattern Test                                                                    |

| (t)ECC Memory Forced CE Test                                                                        |

| (u) ECC Memory Forced UE Test                                                                       |

| <                                                                                                   |

| or, for the Sun-3/80                                                                                |

| <                                                                                                   |

| (a) System Enable Register Test                                                                     |

| (b) I/O Mapper RAM Write/Write/Read Test                                                            |

| (b)I/O Mapper RAM Address Test                                                                      |

| (c)I/O Mapper RAM 3-Pattern Test                                                                    |

| (w)P4 Enable plane Write/Write Read Test                                                            |

| (x)P4 Color Plane Write/Write/Read Test                                                             |

| <pre>&lt;&lt;&lt; Press ,Space for more, <esc> to quit or select an option &gt;&gt;&gt;</esc></pre> |

|                                                                                                     |

At this point you may either press the space bar to see more self-tests, or enter the key code for the test you want to execute in loop mode. Once a test is selected, that test is invoked and executed continually, regardless of whether the test passed or failed. From this point you can use any of the special control keys to continue the selftest if desired: <u>control-q</u> to continue the self-test in non-loop mode or <u>Esc</u> to abort all self-tests and go to the PROM Monitor.

Successful Diagnostic Boot Display For a Sun-3/400 series or Sun-3/80 system, upon self-test completion a status message that looks something like this is displayed:

END OF SELFTEST #0x00000005 (SELFTEST FAILED)

#PASSED=0x00000004, #FAILED=0X0000001

NOTE There is no diagnostic switch on a Sun-3/80; an EEPROM setting is required to allow a diagnostic boot-up. Enter the PROM monitor mode and use the q command to write 12 to location 0x70b. Refer to "Displaying and Modifying Memory" for information on use of the q command.

During a diagnostic boot, after self-test has completed successfully, you will be prompted to enter the extended tests, as shown below.

| If you press a terminal key during this time the Extended Test Menu is displayed<br>on the terminal screen. See the "Sun-3 Extended Test Sequence" chapter in this<br>document for details. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Type a character within 10 seconds to enter Menu Tests(e for echo mode)                                                                                                                     |

| Optional Menu Tests                                                                                                                                                                         |

| Selftest passed.                                                                                                                                                                            |

If you do not assert control of the system by pressing a terminal key within the 10 seconds delay time the Boot PROM program will next display the Sun logo and message on the console.

**Remote Testing**

If you press **e** on a *dumb terminal* keyboard, during the ten second period, all subsequent output will appear on *both* the console video monitor *and* a terminal attached to Serial Port A or B.

The purpose of this feature is to enable an individual at a remote site, using a terminal attached to a non-local machine by way of a telephone line with modems at each end, and the individual on-site to observe the system's behavior simultaneously. Once a system is in this mode, the local and non-local parties can communicate by employing the # command. Specifically, if the person at the remote site would like to send a message to the person on-site, he or she would simply type the # before typing the actual message. In order to terminate the message, the person at the remote site would enter a second #. At this point, the on-site person would be able to respond by prefixing and terminating their response with the #.

The # option will be very useful in the situation where an on-site customer has contacted a remote repair depot regarding a potential hardware problem. The repair person at the remote repair depot could initiate diagnostics on the nonlocal machine and allow both parties to observe the output. Beyond that, the repair person and the customer could communicate by way of the # command.

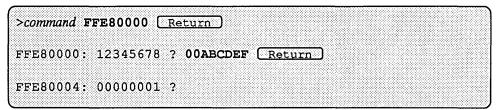

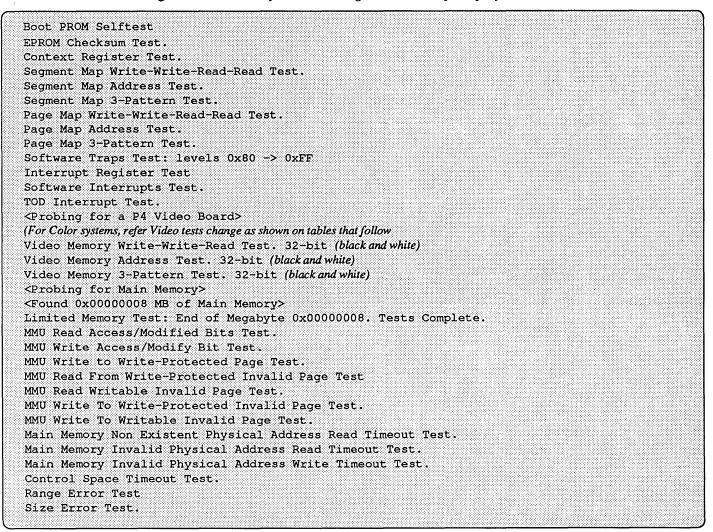

Diagnostic Self-test Sequence

The following text lists diagnostic mode self-tests for each Sun-3 system. If the diagnostic switch is enabled, the name of each test appears on the terminal until all self-tests are complete. The tests differ slightly according to the system architecture. The examples that follow represent each Sun-3 workstation.

Figure 1 Sun-3/75, 3/140, 3/150, 3/160, and 3/110 Diagnostic Boot Sequence

| Boot PROM Selftest                                                     |

|------------------------------------------------------------------------|

| PROM Checksum Test                                                     |

| DVMA Reg Test                                                          |

| Context Reg Test                                                       |

| Segment Map Wr/Rd Test                                                 |

| Segment Map Address Test                                               |

| Page Map Test                                                          |

| Memory Path Data Test                                                  |

| NXM Bus Error Test                                                     |

| Interrupt Test                                                         |

| TOD Clock Interrupt Test                                               |

| MMU Access Bit Test                                                    |

| MMU Access/Modify Bit Test                                             |

| MMU Invalid Page Test                                                  |

| MMU Protected Page Test                                                |

| Parity Test                                                            |

| Memory Size = 0x00000xxx Megabytes                                     |

| Memory Test (testing xxxxxxx MBytes)                                   |

| Selftest passed                                                        |

| Optional Menu Tests                                                    |

| Type character within 10 seconds to enter menu tests (e for echo mode) |

| Boot PROM Selftest                                                      |

|-------------------------------------------------------------------------|

| PROM Checksum Test                                                      |

| Context Reg Test                                                        |

| Segment Map Wr/Rd Test                                                  |

| Segment Map Address Test                                                |

| Page Map Test                                                           |

| Memory Path Data Test                                                   |

| NXM Bus Error Test                                                      |

| Interrupt Test                                                          |

| TOD Clock Interrupt Test                                                |

| MMU Access Bit Test                                                     |

| MMU Access/Modify Bit Test                                              |

| MMU Invalid Page Test                                                   |

| MMU Protected Page Test                                                 |

| Parity Tests                                                            |

| Memory Size = 0x00000xxx Megabytes                                      |

| Memory Test (testing xxxxxxx MBytes)                                    |

| Selftest passed                                                         |

| Optional Menu Tests                                                     |

| Type a character within 10 seconds to enter Menu Tests (e for echo mode |

Figure 2 Sun-3/50 and Sun-3/60 Diagnostic Boot Sequence

Figure 3 Sun-3/260 and Sun-3/280 Diagnostic Boot Sequence

Boot PROM Selftest PROM Checksum Test DVMA Reg Test Context Reg Test Segment Map Wr/Rd Test Segment Map Address Test Page Map Test Memory Path Data Test NXM Bus Error Test Interrupt Test TOD Clock Interrupt Test MMU Access Bit Test MMU Access/Modify Bit Test MMU Invalid Page Test MMU Protected Page Test ECC Error Tests Cache Data 3 Pat Test Cache Tags 3 Pat Test Memory Size = 0x00000xxx Megabytes Memory Test (testing xxxxxxx MBytes) Selftest passed Optional Menu Tests Type character in next 10 seconds to enter menu tests... (e for echo mode)

| System name Boot Prom Self-Test                                                                             |  |

|-------------------------------------------------------------------------------------------------------------|--|

| (Hit key for character echo, space bar for next test, control-m, control-b)                                 |  |

| System Enable Register Read Test {pass 0x00000001}                                                          |  |

| PROM Checksum Test                                                                                          |  |

| I/O Mapper RAM Write/Write/Read Test (pass 0x00000001)                                                      |  |

| I/O Mapper RAM Address Test {pass 0x00000001}                                                               |  |

| I/O Mapper RAM 3-Pattern Test (pass 0x00000001)                                                             |  |

| Bus Error Register Test (pass 0x00000001)                                                                   |  |

| Level 1 Interrupt Test (pass 0x00000001)                                                                    |  |

| Level 2 Interrupt Test (pass 0x00000001)                                                                    |  |

|                                                                                                             |  |

| Level 3 Interrupt Test (pass 0x0000001)                                                                     |  |

| TOD Clock Interrupt Test {pass 0x0000001}                                                                   |  |

| <sizing main="" memory=""></sizing>                                                                         |  |

| <memory size="0x00000010"></memory>                                                                         |  |

| Memory Write/Write/Read Test {pass 0x00000001}                                                              |  |

| Memory Address Test {pass 0x0000001}                                                                        |  |

| Memory 3-Pattern Test {pass 0x00000001}                                                                     |  |

| Memory Read Byte Alignment Test {pass 0x00000001}                                                           |  |

| Memory Write Byte Alignment Test (pass 0x00000001)                                                          |  |

| Parity Memory No Error Test {pass 0x00000001}                                                               |  |

| Parity Memory Forced Error Test {pass 0x00000001}                                                           |  |

| ECC Memory No Error Test {pass 0x0000001}                                                                   |  |

| ECC Memory Forced CE Test {pass 0x00000001}                                                                 |  |

| ECC Memory Forced UE Test {pass 0x00000001}                                                                 |  |

| Central Cache Tag RAM Write/Write/Read Test {pass 0x00000001}                                               |  |

| Central Cache Tag RAM Address Test {pass 0x00000001}                                                        |  |

| Central Cache Tag RAM 3-Pattern Test {pass 0x0000001}                                                       |  |

| Central Cache Data RAM Write/Write/Read Test {pass 0x00000001}                                              |  |

| Central Cache Data RAM Address Test (pass 0x00000001)                                                       |  |

| Central Cache Data RAM 3-Pattern Test (pass 0x00000001)                                                     |  |

| Central Cache Data RAM Read Byte Alignment Test {pass 0x00000001}                                           |  |

| Central Cache Data RAM Write Byte Alignment Test {pass 0x00000001}                                          |  |

| Central Cache Read Hit Test {pass 0x00000001}                                                               |  |

| Central Cache Invalid Read Miss Test {pass 0x0000001}                                                       |  |

| Central Cache Valid Read Miss Test (pass 0x00000001)                                                        |  |

| Central Cache Write Hit Test (pass 0x00000001)                                                              |  |

| Central Cache Write Miss, No Writeback Test (pass 0x00000001)                                               |  |

| Cache Write Miss, Wo Writeback Test (pass 0x00000001)<br>Cache Write Miss, Writeback Test (pass 0x00000001) |  |

|                                                                                                             |  |

| Central Cache Line Cross Invalid Read Miss Test {pass 0x00000001}                                           |  |

| Central Cache Line Cross Write Miss Writeback Test (pass 0x00000001)                                        |  |

| Central Cache Writeback Timeout Test (pass 0x00000001)                                                      |  |

| Block Copy (Source=Cache Miss, Dest=Cache Miss) Test (pass 0x00000001)                                      |  |

| Block Copy (Source=Cache Miss,Dest=Cache Hit) Test (pass 0x00000001)                                        |  |

| Block Copy (Source=Cache Hit,Dest=Cache Miss) Test {pass 0x00000001}                                        |  |

| Block Copy (Source=Cache Hit,Dest=Cache Hit) Test {pass 0x00000001}                                         |  |

|                                                                                                             |  |

Figure 4 Sun-3/400 Series Diagnostic Boot Sequence

18

Memory Write/Write/Read Test (Central Cache on) {pass 0x00000001} IOC Tag RAM Write/Write/Read Test {pass 0x00000001} IOC Tag RAM Address Test (pass 0x00000001) IOC Tag RAM 3-Pattern Test (pass 0x00000001) IOC Data RAM Write/Write/Read Test (pass 0x00000001) IOC Data RAM Address Test {pass 0x0000001} IOC Data RAM 3-Pattern Test (pass 0x00000001) IOC Data RAM Read Byte Alignment Test (pass 0x00000001) IOC Data RAM Write Byte Alignment Test (pass 0x00000001) VME Loopback Test (pass 0x00000001) VME Loopback and DVMA Test (pass 0x00000001) (not for Sun-3/460) IOC Read Hit Test (pass 0x00000001) IOC Invalid Read Miss Test (pass 0x00000001) IOC Write Hit Test {pass 0x00000001} IOC Write Miss, No Writeback Test (pass 0x00000001) IOC Write Miss, Writeback Test (pass 0x00000001) IOC Read Miss, Writeback Test {pass 0x00000001} IOC Valid Write Hit (Central Cache Match, Unmod) Test (pass 0x00000001) IOC Invalid Write Miss (Central Cache Match, Unmod) Test (pass 0x00000001) IOC Invalid Read Miss (Central Cache Match, Unmod) Test (pass 0x00000001) IOC Invalid Read Miss (Central Cache Match, Modified) Test {pass 0x00000001} IOC Valid Read Miss (Central Cache Match), Writeback Test {pass 0x00000001} IOC Flush (Valid, Modified) Test {pass 0x00000001} IOC Flush (Valid, Not Modified) Test (pass 0x00000001) IOC Flush (Not Valid, Not Modified) Test {pass 0x00000001} IO Mapper Invalid Page (IO.DT) Test (pass 0x00000001) IOC Write Miss, Writeback (Write Protect) Test (pass 0x00000001) IOC Invalid Read Miss (IO Mapper IO.EN = 0) Test {pass 0x00000001} IOC Write Miss (IO Mapper IO.EN = 0) Test {pass 0x00000001} IOC Random Data Block Write Test {pass 0x00000001} IOC Random Data Block Read (Central Cache off) Test {pass 0x00000001} IOC Random Data Block Read (Central Cache on) Test {pass 0x00000001} <P4 Low Resolution Color Video RAM Board Detected> P4 Overlay Frame Buffer Write/Write/Read Test (pass 0x00000001) P4 Overlay Frame Buffer Address Test {pass 0x0000001} P4 Overlay Frame Buffer 3-Pattern Test (pass 0x00000001) P4 Overlay Frame Buffer March Test (pass 0x00000001) P4 Overlay Frame Buffer Read Byte Alignment Test {pass 0x00000001} P4 Overlay Frame Buffer Write Byte Alignment Test (pass 0x00000001) P4 Enable Plane Write/Write/Read Test (pass 0x00000001) P4 Color Plane Write/Write/Read Test {pass 0x00000001} Selftest passed Type character within 10 seconds to enter Extended Tests System (e for echo mode)

| Figure 5  | Sun-3/80 Diagnostic Boot Sequence |  |

|-----------|-----------------------------------|--|

| I Iguit J | Dun 5700 Diagnobile Door Dequence |  |

Refer to the *PROM User's Manual* for descriptions of the self-tests named for workstations other than the Sun-3/400 series and the Sun-3/80.

Here is a summary of the LED displays for the Sun-3/400 series and Sun-3/80 during the power-up self-tests. Many of the tests are the same for both systems; the test description will indicate which tests is system-specific, In case of error in a Sun-3/400 series test, the LED in bit position 7 also lights. The text that follows this chart shows both the normal test and error displays. As indicated, many tests share the same LED display.

#### Sun-3/80 LED

| LED status | Visual | Condition |

|------------|--------|-----------|

| Blinking   | Θ      | Testing   |

| OFF        | 0      | Error     |

| ON (Green) |        | Ok        |

The Sun-3/80 has one green LED only, which lights steadily during normal function, blinks during a test, and turns off when there is an error. The messages that appear on a terminal attached to Serial Port A describe the specific test in progress and the nature of any errors found.

| LED L  | LED Display |                                                |  |  |  |

|--------|-------------|------------------------------------------------|--|--|--|

| •= ON, | o=OFF       | SelfTest being Performed.                      |  |  |  |

| 7654   | 3210        |                                                |  |  |  |

|        |             | A reset will set LEDs to this state.           |  |  |  |

| 0000   | 000•        | Keyboard/Mouse SCC Write/Read Test             |  |  |  |

| 0000   | 00          | System Enable Register Read Test               |  |  |  |

| 0000   | 0 • 0 0     | PROM Checksum Test                             |  |  |  |

| 0000   | 0 • 0 •     | I/O Mapper RAM Test(s)                         |  |  |  |

| 0000   | 0 • • 0     | Bus Error Register Test                        |  |  |  |

| 0000   | 0 • • •     | Interrupt Test(s)                              |  |  |  |

| 0000   | • • • •     | ECC Memory Sizing and Test(s)                  |  |  |  |

| 0000   | • • • •     | Parity Memory Sizing and Test(s)               |  |  |  |

| 0000   | • • • •     | ECC Memory Forced Error Test(s)                |  |  |  |

| 0000   | • • • •     | Central Cache Tag RAM Test(s)                  |  |  |  |

| 0000   | ••00        | Central Cache Data RAM Test(s)                 |  |  |  |

| 0000   |             | Central Cache Hit/Miss Test(s)                 |  |  |  |

| 0000   | • • • 0     | Block Copy Test(s)                             |  |  |  |

| 0000   |             | Memory Write/Write/Read Test(Central Cache on) |  |  |  |

| 000.   | 0000        | IOC Tag RAM Test(s)                            |  |  |  |

| 000.   | 000•        | IOC Data RAM Test(s)                           |  |  |  |

| 000.   | 0000        | VME Loopback Test                              |  |  |  |

| 000.   | 00          | VME Loopback and DVMA (not for 3/460)          |  |  |  |

| 000.   | 0 0 0 0     | IOC Read/Write/Flush Test(s)                   |  |  |  |

| 000•   | 0 • 0 •     | P4 Overlay Frame Buffer Test(s)                |  |  |  |

The following table explains the Sun-3/400 series LED code.

#### Self-Test Descriptions

LED Register Test

The following paragraphs describe each individual test, and the messages and indications generated if it fails. Some tests do not apply to both the Sun-3/400 series and Sun-3/80; refer to the Diagnostic Boot Sequence display examples on previous pages for lists of applicable self-tests.

The first Sun-3/400 series test is indicated by a slow loop through the Diagnostic LEDs, from LED 7 through LED 0. It is intended to determine if the CPU is able to fetch instructions correctly from the Diagnostic PROM and transfer data across the data bus to the LED status register.

NOTE If all the LED s on a Sun-3/400 series remain lighted, you could have a low voltage or board seating problem, or the system could contain the wrong Boot PROM.

NOTE The diagrams that follow depict the LED states for each self-test. Note that the LEDs are shown here for convenience in reading as binary numbers; the least significant bit is on the right. In most systems, the LEDs are read with bit 0 on the left for desktop installations and with bit 0 on top for deskside installations.

The tests are described here in the order that they are executed.

#### UART SCC (Z8530) Port A,B Write/Read Test

This test checks the ability of the Sun-3/400 series workstation CPU to communicate with port A and B of the Zilog Z8530 Serial Communications Chip (SCC). It performs a write/read test of port A and B SCC chip internal registers WR12/RR12. The purpose of this test is to test the path between the CPU and the SCC so that all subsequent tests may display the test name and error status to a terminal attached to Serial Port A.

The test enters a scope loop on a data compare error, but no error messages are displayed on the terminal during this test.

The diagram below summarizes the LED states for a Sun-3/400 series CPU board.

| Hexadecimal Value Of LEDs | Visual Representation | Condition |

|---------------------------|-----------------------|-----------|

| 0x00                      | bit 7 0000000 bit 0   | okay      |

| 0x80                      | •0000000              | error     |

Keyboard/Mouse SCC (Z8530) Port A,B Write/Read Test This test checks the ability of the CPU to communicate with port A and B of the Zilog Z8530 Serial Communications Chip (SCC). It performs a write/read test of port A and B SCC chip internal registers WR12/RR12. Note that this test is for the SCC used for the keyboard and mouse.

The test enters a scope loop on a data compare error, but no error messages are displayed on the terminal during this test because this is a test of the path to the SCC chip.

The diagram below summarizes the LED states for a Sun-3/400 series workstation.

| Test Number | Hexadecimal Value Of LEDs | Visual Representation | Condition |

|-------------|---------------------------|-----------------------|-----------|

| 1           | 0x01                      | bit 7 0000000 • bit 0 | okay      |

| 1           | 0x81                      | •000000               | error     |

System Enable Register Read Test This test reads the System Enable Register and verifies that all bits read are zero, ignoring the Diagnostics Switch bit.

The test enters a scope loop on data compare errors, with the following terminal message:

exp xxxxxxx, obs xxxxxxx, xor xxxxxxx

The diagram below summarizes the LED states.

| Test Number | Hexadecimal Value Of LEDs | Visual Representation  | Condition |

|-------------|---------------------------|------------------------|-----------|

| 3           | 0x03                      | bit 7 000000 • • bit 0 | okay      |

| 3           | 0x83                      | •00000••               | error     |

#### PROM Checksum Test

24

The checksum of all locations in both PROMs with the exception of the last word is calculated and compared to an expected value that is stored in the last word of the second PROM. If this test fails, the PROMs should be replaced.

The test enters a scope loop on data compare errors, with the following terminal message:

Checksum error: Exp xxxxxxx, Obs xxxxxxx

The diagram below summarizes the LED states.

| Test Number | Hexadecimal Value Of LEDs | Visual Representation | Condition |

|-------------|---------------------------|-----------------------|-----------|

| 4           | 0x04                      | bit 7 00000 ●00 bit 0 | okay      |

| 4           | 0x84                      | ●00000●00             | error     |

I/O Mapper Write/Write/Read Test This test verifies the address and data paths to the IO Mapper RAM, as well as address bit and data bit uniqueness.

For each test address of IO Mapper RAM: (base+0x0,base+0x01,base+0x02,base+0x04,base+0x08,...,base+iomapper\_size)

For each data pattern at each test address: (0x0,0x1,0x2,0x4,0x10,0x20,...0x80000000)The test does the following:

- Writes test data to the test address.

- $\square$  Writes inverted test data to test address + 0x04.

- Reads back data from the test address and compares.

Upon error, the test loops through the steps shown above with constant test data and a constant test address.

This test enters a scope loop on data compare errors, with the following terminal message:

addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The diagram below summarizes the LED states.

| Test Number | Hexadecimal Value Of LEDs | Visual Representation | Condition |

|-------------|---------------------------|-----------------------|-----------|

| 5           | 0x05                      | bit 7 0000000 bit 0   | okay      |

| 5           | 0x85                      | •00000•0•             | error     |

## I/O Mapper RAM Address Test

This test writes the complete I/O Mapper RAM address space with the longword address as the data, then reads back the entire address space and verifies that no addresses are overwritten. This is a test for addressing uniqueness of the I/O Mapper RAM.

This test enters a scope loop on data compare errors, with the following terminal message:

addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The LED display shown for the I/O Mapper Write/Write/Read Test applies to this test also.

This test writes the complete I/O Mapper RAM address space with a repeated three-long-word pattern sequence, then reads back the entire address space and verifies the data.

This test enters a scope loop on data compare errors, with the following terminal message:

addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The LED display shown for the I/O Mapper Write/Write/Read Test applies to this test also.

Bus Error Register Test

I/O Mapper RAM 3-Pattern

Test

This test does the following:

- 1. Verifies that attempting to read an invalid memory address causes a bus error, with appropriate data written to the BUSERR register.

- 2. Verifies that attempting to read an FPA device address while the ENABLE-FPA bit in the System Enable Register is off causes a bus error, with appropriate data written to the BUSERR register.

This test enters a scope loop upon error, with one or more of the following terminal error messages:

error1: No Bus Error Reading Invalid Memory Address, read addr = 0xyyyyyyyy, error2: Bus error reg TIMEOUT bit not set. error3: No Bus Error Reading Disabled FPA, read addr = 0xyyyyyyyy. error4: Bus error reg FPAENERR bit not set.

| Test Number | Hexadecimal Value Of LEDs | Visual Representation | Condition |

|-------------|---------------------------|-----------------------|-----------|

| 6           | 0x06                      | bit 7 0000000 bit 0   | okay      |

| 6           | 0x86                      | 0000000               | error     |

Level 1 Interrupt Test

This test forces a Level 1 soft interrupt to verify that an autovector Level 1 interrupt will occur.

This test enters a scope loop upon error, with the following error message:

error: No level 1 interrupt occurred.

The diagram below summarizes the LED states.

| Test Number | Hexadecimal Value Of LEDs | Visual Representation   | Condition |

|-------------|---------------------------|-------------------------|-----------|

| 7           | 0x07                      | bit 7 00000 • • • bit 0 | okay      |

| 7           | 0x87                      | •0000•••                | error     |

Level 2 Interrupt Test

This test forces a level 2 soft interrupt to verify that an autovector Level 1 interrupt will occur.

The test enters a scope loop upon error, with the following terminal error message:

error: No level 2 interrupt occurred.

The LED display for this test is the same as that for the Level 1 Interrupt test.

Level 3 Interrupt Test

This test forces a level 3 soft interrupt to verify that an autovector Level 3 interrupt will occur.

The test enters a scope loop upon error, with the following error message:

error: No level 3 interrupt occurred.

The LED display for this test is the same as that for the Level 1 Interrupt test.

TOD Clock Interrupt Test

This test enables the TOD CLock to interrupt and then verifies that the interrupt occurs.

This test enters a scope loop upon error, with the following error message:

error: No TOD interrupt occurred.

The LED display for this test is the same as that for the Level 1 Interrupt test.

Memory Write/Write/Read Test

This test verifies the address and data paths to Main Memory, as well as address bit and data bit uniqueness.

For each test address of main memory: (0x0,0x1,0x2,0x4,0x8,0x10,0x20,...size\_of\_mem\_installed)

For each data pattern at each test address: (0x0,0x1,0x2,0x4,0x10,0x20,...0x80000000)The test does the following:

- □ Writes test data to test address.

- $\Box$  Writes inverted test data to test address + 0x04.

- Reads back data from test address and compares.

Upon error, the test loops through the steps shown above with constant test data and a constant test address.

This test enters a scope loop on data compare errors, with the following message:

addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The diagram below summarizes the LED states.

| Test Number | Hexadecimal Value Of LEDs | Visual Representation  | Condition |

|-------------|---------------------------|------------------------|-----------|

| 8           | 0x08                      | bit 7 0000 • 000 bit 0 | okay      |

| 8           | 0x88                      | ●000●000               | error     |

Memory Address Test

This test writes the complete Main Memory address space with the longword address as the data, then reads back the entire address space and verifies that no addresses are overwritten. This is a test for addressing uniqueness of the Main Memory RAM.

This test enters a scope loop on data compare errors, with the following terminal message:

addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The LED display is that same as that shown for the Memory Write/Write/Read Test.

### Memory 3-Pattern Test

This test writes the complete Main Memory address space with a repeated three long word pattern sequence, then reads back the entire address space and verifies the data.

This test enters a scope loop on data compare errors, with the following terminal message:

addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The LED display is that same as that shown for the Memory Write/Write/Read Test.

Memory Read Byte Alignment Test This test verifies that byte, word, and long word read operations produce the appropriate byte-aligned data.

The test enters a scope loop on data compare errors, with the following message:

byte misalignment: addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The LED display is that same as that shown for the Memory Write/Write/Read Test.

Memory Write Byte Alignment Test This test verifies that byte, word, and long word read operations produce the appropriate byte-aligned data for various byte-aligned write operations.

This test enters a scope loop on data compare errors, with the following terminal message:

byte misalignment: addr xxxxxxx, exp xxxxxxx, obs xxxxxxx

The LED display is that same as that shown for the Memory Write/Write/Read Test.

Parity Memory No Error Test

This test will execute only if a Parity Memory board was detected when main memory was sized.

The test does the following:

- 1. Determines if Parity memory is installed. If not, it bypasses the test.

- 2. Initializes all Parity memory with zero to initialize the check bits.

- For each test address 0x0000000,0x00000001,0x00000002,...,0x00040000, 0x00800000,0x00800001,0x00800002,...0x00840000, or up to total Parity memory installed (16MB max):

For each data pattern 0x0000001,0x0000003,0x0000007,...0xffffffff at one specific test address:

The test:

- (a) Writes 0x0 to Memory Error Address register to clear previous interru

- (b) Enables Parity checking on Parity board.

- (c) Enables Level 7 interrupts in Memory Error Control Register.

- (d) Enables system interrupts in System Interrupt Register.

- (e) Verifies that Memory Error Control register was properly set.

- (f) Writes longword test data to test address.

- (g) Reads longword from test address.

- (h) Verifies that no Level 7 interrupt occurred.

- (i) Verifies that Memory Error Control register was not modified.

Upon error, the test loops through steps a - i with a constant test address and constant test data.

Possible error messages for this test are:

error1: Memory Error Control Reg not written: exp=0x00000000, obs=0x00000000, testaddr=0x00000000, testdata=0x00000000 error2: Unexpected parity error (level 7) interrupt: testaddr=0x00000000, testdata=0x00000000 Memory Error Control Reg: obs=0x00000000 Parity Memory Error Reg: obs=0x00000000 Memory Error Address Reg: obs=0x00000000 error3: Bad Memory Error Control Reg after memory write: exp=0x00000000, obs=0x00000000, testaddr=0x00000000, testdata=0x00000000

| Test Number | Hexadecimal Value Of LEDs | Visual Representation   | Condition |