#### AR3-00

## Sun-4D Architecture

Michel Cekleov, Jean-Marc Frailong, Pradeep Sindhu

Written: January 30, 1990 **Revised**:

June 22, 1992

Version: 1.4

Copyright 1989-1992, Sun/Xerox. All rights reserved.

Abstract:

This description of the Sun-4D architecture is intended for kernel and diagnostic programmers. It discusses the memory model and its implications, the address spaces organization, the processor unit architecture, the main memory organization, the I/O subsystem architecture, interrupt handling, reset, and interactions with JTAG.

An important goal of this document is correctness. Please report any error, omissions or oversights immediately so they can be corrected in future revisions.

**Keywords:**

Architecture, Programming Model, Memory Model, Viking, Cache, Main Memory, I/O, Boot, Sunness, JTAG, Interrupts

Maintained by:

Michel Cekleov

## **Revision History**

| Revision 0.1 | 12/22/89<br>Limited distribution for review purposes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision 1.0 | 1/30/90<br>First general release<br>Viking chapter removed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Revision 1.1 | <ul> <li>4/25/90</li> <li>Changed CC Error register format, error bits made write-one-to-clear<br/>Added internal errors of BW</li> <li>Clarified BW time-outs</li> <li>Added bit to BW control register</li> <li>JTAG control register &amp; command encoding changed</li> <li>Added LEDs status bits in BootBus Status_2 register, modified register encoding</li> <li>Specified MQH SIMM ID register format</li> <li>Added Refresh Enable to MQH Control &amp; Status register</li> <li>Documented change in ECC structure for Memory subsystem</li> <li>Changed polarity of ECC enable bit in MQH Diagnostic register</li> <li>Explained memory initialization &amp; scrubbing</li> <li>Clarified stream write DVMA model</li> <li>Added RSB bit to Stream Buffer Control registers in SBI</li> <li>Specified Loopback mode for SBI</li> <li>Board slot number of control board changed form 0xA to 0xF</li> <li>Additional status bits in BARB shadow ring 0</li> <li>Changed order of bits in CARB shadow ring 0</li> <li>Added JTAG specification for CC</li> <li>Added INIT bit to MQH DynaBus Control and Status register</li> </ul> |

| Revision 1.2 | 6/12/90<br>Modified semantics of Local Software Reset (SI bit of CC reset register)<br>Modified INTSID for MQH & SBI errors<br>Added TLD mode bit to DynaBus CSR in BW & IOC<br>Changed encoding of IOC cache flags<br>Added RDTOL to IOC DynaBus CSR<br>Added IOC internal errors<br>Clarified MQH ECC error interrupts, added SWAP to ECC error registers<br>CC reference counters modified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

#### Revision 1.3 3/29/91

\$

Various sections: explanations related to dual-processor system board CC: Warning that CC LVL15 is level-sensitive

CC: Warning that Local reset disables Viking parity, but not CC parity BW: Added chip test bits in DCSR

Sun/Xerox Private Data

BootBus: Reorganization of the control & status registers, introduction of dual-processor board BootBus

MQH: Clarification of address generation

MQH: Added section on column and row address generation

- MQH: Specified RequestDelay and MCRAM information for Mitsubishi & TI SIMMs

- MQH: Updated Client Device Errors table

IOC: Cache reduced to 4 lines instead of 8

IOC: Added chip test bits in DCSR

SBI: IMS bit removed, Interrupt Diagnostic register now write-only

SBI: BA64 and BA32 are now supported

SBI: LBE bit is cleared on reset

SBI: Writing a 0 into FWB & IRB bits has no effects, streaming buffers need to be initialized even if not used

Error: Clarified early vs. late store errors

Error: Documented DeMap time-out error case

JTAG: Scan chain changes to BW, IOC, SBI due to register changes

JTAG: Corrected Viking and CC JTAG Component ID

JTAG: Added scannable registers to system board & control board chains

#### Revision 1.4 6/22/92

Removed single-processor BootBus description

Renamed document to Sun-4D architecture

Incorporated Scorpion features in all chapters

Introduction chapter includes a physical description of Scorpion.

Address Spaces chapter has been completely rewritten for clarity

Address tables have been moved to the beginning of each functional units

chapters (processor, memory and I/O).

Processor Unit includes BWP description.

Power Supply Failure interrupt has been replaced by the Ethernet Link Test feature on the Scorpion BootBus.

Memory Unit chapter includes MQHP description

More detailed description of refresh variables (RFEN, RCNT).

NV\_SIMMs documented as part of the Memory Unit chapter

Programming notes on NV\_SIMMs.

Programming notes removed from Reset chapter. Obsolete due to POST FCS Specification.

•

## **Table of Contents**

| Chapter 1      |                                               |           |

|----------------|-----------------------------------------------|-----------|

|                | n                                             |           |

|                | pe                                            |           |

|                | dware Architecture Overview                   |           |

|                | SunDragon                                     |           |

|                | Scorpion                                      |           |

|                | Processor Unit                                |           |

|                | I/O Unit                                      |           |

|                | Main Memory Unit                              |           |

| -              | lementation Overview                          |           |

|                | SunDragon Implementation                      |           |

| 1.3.2          | Scorpion Implementation                       | 10        |

| Chapter 2      |                                               |           |

| •              | odel                                          |           |

|                | rview                                         |           |

|                | ic Definitions                                |           |

|                | al Store Ordering (TSO)                       |           |

| 2.4 Part       | ial Store Ordering (PSO)                      | 16        |

|                | JSH instruction                               |           |

| 2.6 TSC        | D/PSO Mode Control                            | 19        |

| 2:.7 Spe       | cial Considerations for I/O                   | 20        |

| 2.7.1          | Processor Initiated References to I/O Devices | 20        |

| 2.7.2          | I/O Device Initiated References to Memory     | 21        |

|                | I/O Interrupts                                |           |

|                | InterProcessor Interrupts                     |           |

| Chapter 3      |                                               |           |

|                | ices                                          |           |

|                | ual Addresses                                 |           |

|                | SPARC Virtual Address Spaces                  |           |

|                | SBus DVMA Virtual Address Spaces              |           |

|                | sical Address Space                           |           |

|                | Memory Space, I/O Space and Cacheability      |           |

|                | I/O Space Allocation                          |           |

| 323            | Device Identifiers                            | 26        |

|                | Unit Numbers                                  |           |

|                | CSR Space                                     |           |

| 27K            | ECSR Space                                    | 29        |

| J.2.0<br>2 7 7 | SBus Space                                    |           |

| J.4.1<br>2 7 0 | Jose Space                                    | ,20<br>20 |

| 3.2.8          | Local Space                                   | גד<br>זר  |

| 5.5 Syst       | em Board Physical Space                       |           |

| Chapter 4                                   |    |

|---------------------------------------------|----|

| Processor Unit                              |    |

| 4.1 Address Map                             | 31 |

| 4.2 Viking processor                        | 35 |

| 4.2.1 Control register                      |    |

| 4.2.2 PTE Referenced and Modified Bits      |    |

| 4.2.3 MMU Demapping                         |    |

| 4.3 The External Cache                      |    |

| 4.3.1 Organization                          |    |

| 4.3.2 Cacheability                          |    |

| 4.4 Cache Controller                        |    |

| 4.4.1 External Cache Processor Tags         |    |

| 4.4.2 External Cache Data                   |    |

| 4.4.3 Block Copy and Block Zero             |    |

| 4.4.3.1 Principles of Operation             |    |

| 4.4.3.2 Stream Data Register                |    |

| 4.4.3.3 Stream Source Address Register      |    |

| 4.4.3.4 Stream Destination Address Register |    |

| 4.4.3.5 Programming Notes                   |    |

| 4.4.4 Reference/Miss Count Register         |    |

| 4.4.5 Interrupt Registers                   |    |

| 4.4.5.1 Interrupt Pending Register          |    |

| 4.4.5.2 Interrupt Mask Register             |    |

| 4.4.5.3 Interrupt Pending Clear             |    |

| 4.4.5.4 Interrupt Generation Register       |    |

| 4.4.6 BIST Register                         |    |

| 4.4.7 Control Register                      |    |

| 4.4.8 Status Register                       |    |

| 4.4.9 Reset Register                        |    |

| 4.4.10 Error Register                       |    |

| 4.4.11 Component Identification Register    |    |

| 4.4.12 Reset state of the Cache Controller  |    |

| 4.5 Bus Watcher                             |    |

| 4.5.1 External Cache Bus Tags               |    |

| 4.5.1.1 Address Format                      |    |

| 4.5.1.2 Tag Format                          |    |

| 4.5.2 ComponentID Register.                 |    |

| 4.5.3 Dynabus Control and Status Register   |    |

| 4.5.4 DynaData Register                     |    |

| 4.5.4.1 Event counting                      |    |

| 4.5.4.2 Error logging                       |    |

| 4.5.5 Control Register                      |    |

| 4.5.6 Interrupt Table                       |    |

| 4.5.0 Interrupt Table Clear                 |    |

| 4.5.8 Counter-Timers                        |    |

| 4.5.8.1 Counter-Timers Structure            |    |

|                                             |    |

|   | 4.5.8.2 Prescaler Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

|---|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|   | 4.5.9 Reset state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 71       |

| Į | 4.5.10 Programming Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

|   | 4.6 Boot Bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 71       |

|   | 4.6.1 EPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|   | 4.6.2 SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 73       |

|   | 4.6.3 Serial Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|   | 4.6.4 KeyBoard/Mouse Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 74       |

|   | 4.6.5 LED Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75       |

|   | 4.6.6 TOD Clock and NVRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 75       |

|   | 4.6.7 JTAG Master Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          |

|   | 4.6.7.1 JTAG Command Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76       |

|   | 4.6.7.2 JTAG Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 76       |

|   | 4.6.8 Status and Control Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|   | 4.6.8.1 Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

|   | 4.6.8.2 Status_1 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78       |

|   | 4.6.8.3 Status_2 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 78       |

|   | 4.6.8.4 Status_3 Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|   | 4.6.8.5 System Software Reset Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 80       |

|   | 4.6.8.6 Board Version Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|   | 4.6.9 Semaphore Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|   | 4.6.9.1 Semaphore 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|   | 4.6.9.2 Semaphore 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |

|   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 1 | Chanter 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

|   | Chapter 5<br>Main Memory Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83       |

|   | Main Memory Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |          |

|   | Main Memory Unit           5.1         Main Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 83       |

|   | Main Memory Unit         5.1       Main Memory Architecture         5.1.1       SunDragon Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 83<br>83 |

|   | Main Memory Unit         5.1       Main Memory Architecture         5.1.1       SunDragon Memory Architecture         5.1.2       Scorpion Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

|   | Main Memory Unit         5.1       Main Memory Architecture         5.1.1       SunDragon Memory Architecture         5.1.2       Scorpion Memory Architecture         5.1.3       SIMM Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|   | Main Memory Unit         5.1       Main Memory Architecture         5.1.1       SunDragon Memory Architecture         5.1.2       Scorpion Memory Architecture         5.1.3       SIMM Organization         5.1.3.1       DRAM SIMM                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|   | Main Memory Unit         5.1       Main Memory Architecture         5.1.1       SunDragon Memory Architecture         5.1.2       Scorpion Memory Architecture         5.1.3       SIMM Organization         5.1.3.1       DRAM SIMM         5.1.3.2       NV_SIMM                                                                                                                                                                                                                                                                                                                                                                                                                |          |

|   | Main Memory Unit         5.1       Main Memory Architecture         5.1.1       SunDragon Memory Architecture         5.1.2       Scorpion Memory Architecture         5.1.3       SIMM Organization         5.1.3.1       DRAM SIMM         5.1.3.2       NV_SIMM         5.2       Memory Queue Handler Access                                                                                                                                                                                                                                                                                                                                                                  |          |

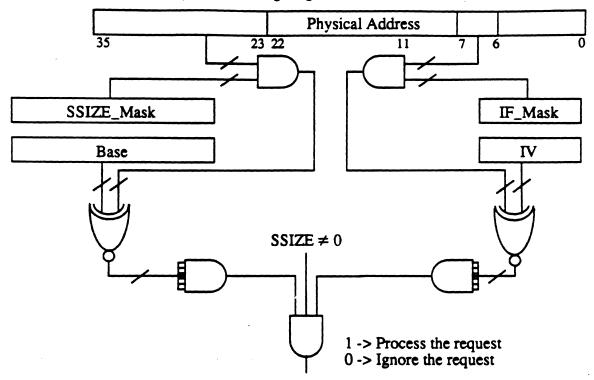

|   | Main Memory Unit         5.1       Main Memory Architecture         5.1.1       SunDragon Memory Architecture         5.1.2       Scorpion Memory Architecture         5.1.3       SIMM Organization         5.1.3.1       DRAM SIMM         5.1.3.2       NV_SIMM         5.2       Memory Queue Handler Access         5.3       Address Decoding                                                                                                                                                                                                                                                                                                                               |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers                                                                                                                                                                                                                                                                                                                                      |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Filtering                                                                                                                                                                                                                                                                                                                                               |          |

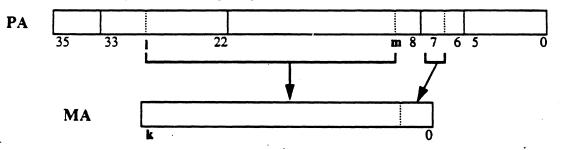

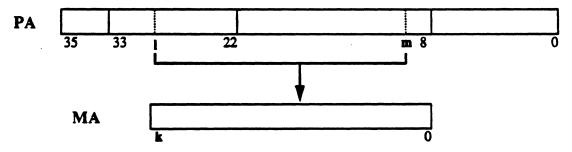

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Filtering         5.3.3 Memory Group Address Generation                                                                                                                                                                                                                                                                                                 |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.3.1 No Interleaving or Two-way interleaving                                                                                                                                                                                                |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.3.1 No Interleaving or Two-way interleaving         5.3.3.2 Four-way interleaving                                                                                                                          |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.3.1 No Interleaving or Two-way interleaving         5.3.3.2 Four-way interleaving         5.3.4 Row and Column Address                                                                                     |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.3.1 No Interleaving or Two-way interleaving         5.3.4 Row and Column Address         5.3.5 Group Type Registers                                                                                        |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.3.1 No Interleaving or Two-way interleaving         5.3.3.2 Four-way interleaving         5.3.4 Row and Column Address         5.3.5 Group Type Registers         5.3.6 Memory Control and Status Register |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.3.1 No Interleaving or Two-way interleaving         5.3.4 Row and Column Address         5.3.5 Group Type Registers         5.3.6 Memory Control and Status Register         5.4 Dynabus Registers         |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3 I DRAM SIMM         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.4 Row and Column Address         5.3.5 Group Type Registers         5.3.6 Memory Control and Status Register         5.4 Dynabus Registers                                                                       |          |

|   | Main Memory Unit         5.1 Main Memory Architecture         5.1.1 SunDragon Memory Architecture         5.1.2 Scorpion Memory Architecture         5.1.3 SIMM Organization         5.1.3 SIMM Organization         5.1.3.1 DRAM SIMM         5.1.3.2 NV_SIMM         5.2 Memory Queue Handler Access         5.3 Address Decoding         5.3.1 Address Decoding Registers         5.3.2 Address Filtering         5.3.3 Memory Group Address Generation         5.3.3.1 No Interleaving or Two-way interleaving         5.3.4 Row and Column Address         5.3.5 Group Type Registers         5.3.6 Memory Control and Status Register         5.4 Dynabus Registers         |          |

|     | 5.5 ECC Mem   | ory Architecture                     |        |

|-----|---------------|--------------------------------------|--------|

|     | 5.5.1 ECC     | Memory Operations                    |        |

|     | 5.5.2 Synd    | romes                                |        |

|     | 5.5.3 ECC     | Registers                            |        |

|     |               | Correctable Error Address Register   |        |

|     |               | Correctable Error Data Register      |        |

|     |               | Uncorrectable Error Address Register |        |

|     |               | Uncorrectable Error Data Register    |        |

|     | 5.5.3.5       | ECC Diagnostic and Control Register  | 107    |

|     | 5.6 Memory T  | iming Registers                      | 108    |

|     | 5.7 Reset     |                                      | 109    |

|     | 5.8 Programm  | ing notes                            | 109    |

|     | 5.8.1 MQH     | I Initialization                     | 109    |

|     | 5.8.2 Main    | memory test                          | 110    |

|     | 5.8.3 ECC     | Errors Clearing                      | 110    |

|     | 5.8.4 ECC     | Testing                              | 110    |

|     | 5.8.5 Scrut   | bbing                                | 111    |

|     | 5.8.6 On-li   | ne spare memory blocks               |        |

|     | 5.8.7 Non     | Volatile Memory                      | 111    |

|     | 5.8.7.1       | Introduction                         |        |

|     | 5.8.7.2       | NVRAM Access                         |        |

|     | 5.8.7.3       | Address Mapping                      |        |

|     | 5.8.7.4       | Battery Status Checking              |        |

|     | 5.8.7.5       | Multiple Bus Configuration           |        |

|     | Chapter 6     | •                                    | •<br>• |

| ÷ · | I/O Unit      |                                      | -115   |

|     | 6.1 I/O Model |                                      | 116    |

|     |               | ammed I/O                            |        |

|     |               | IA I/O                               |        |

|     |               | Consistent Mode DVMA                 |        |

|     |               | Stream Mode DVMA                     |        |

|     |               | Stream Read Buffers                  |        |

|     |               | Stream Write Buffers                 |        |

| -   |               |                                      |        |

|     |               | Chip                                 |        |

|     |               | e Organization                       |        |

|     |               | ss to the cache                      |        |

|     |               | Dynabus Tags                         |        |

|     |               | SBus Tags                            |        |

|     |               | Cache State Bits                     |        |

|     |               | Cache Data                           |        |

|     |               | Siers                                |        |

|     |               | ComponentID Register                 |        |

|     |               | Dynabus Control and Status Register  |        |

|     |               | DynaData Register                    |        |

|     | 0.3.3.3       |                                      |        |

| 6.3.3.4 Control Register                                                                                                        |          |

|---------------------------------------------------------------------------------------------------------------------------------|----------|

| 6.3.4 Reset                                                                                                                     |          |

| 6.4 SBus Interface Chip                                                                                                         |          |

| 6.4.1 I/O MMU                                                                                                                   |          |

| 6.4.2 Registers                                                                                                                 |          |

| 6.4.2.1 ComponentID Register                                                                                                    |          |

| 6.4.2.2 Control Register                                                                                                        |          |

| 6.4.2.3 Status Register                                                                                                         |          |

| 6.4.2.4 Slot Configuration Registers                                                                                            |          |

| 6.4.2.5 Slot Stream Buffer Control Regi                                                                                         | sters138 |

| 6.4.2.6 Interrupt State Register                                                                                                |          |

| 6.4.2.7 Interrupt TargetID Register                                                                                             |          |

| 6.4.2.8 Interrupt Diagnostic Register                                                                                           |          |

| 6.4.3 Loopback mode                                                                                                             |          |

| 6.4.4 Reset                                                                                                                     |          |

| Chapter 7                                                                                                                       |          |

| Error Management                                                                                                                | 143      |

| 7.1 Error reporting mechanisms                                                                                                  |          |

| 7.1.1 Bus errors                                                                                                                |          |

| 7.1.1.1 Types of bus errors                                                                                                     |          |

| 7.1.1.2 Bus errors on prefetch operation                                                                                        |          |

| 7.1.1.3 Bus errors on instruction fetches                                                                                       |          |

| 7 1 1 4 Pue emers on data loade                                                                                                 |          |

|                                                                                                                                 |          |

| 7.1.1.5 Bus errors on synchronous data<br>7.1.1.6 Bus errors on asynchronous data<br>7.1.1.7 Bus errors on block conv operation | stores   |

| 7.1.1.7 Bus errors on block copy operation                                                                                      | ions145  |

| 7.1.1.8 Bus errors on MMU TLB operat                                                                                            |          |

| 7.1.1.9 Bus errors on SBus DVMA read                                                                                            |          |

| 7.1.1.10 Bus errors on SBus DVMA wr                                                                                             |          |

| 7.1.2 Interrupts                                                                                                                | •        |

| 7.1.2.1 Local level-15 interrupt                                                                                                |          |

| 7.1.2.2 Broadcast level-15 interrupt                                                                                            |          |

| 7.1.3 Resets                                                                                                                    |          |

| 7.1.3.1 CPU watchdog reset                                                                                                      |          |

| 7.1.3.2 System watchdog reset                                                                                                   |          |

| 7.2 Types of errors                                                                                                             |          |

| 7.2.1 Software errors                                                                                                           |          |

| 7.2.2 Hardware-corrected errors                                                                                                 |          |

| 7.2.2.1 Memory correctable ECC error.                                                                                           |          |

| 7.2.3 Recoverable errors                                                                                                        |          |

| 7.2.3.1 Dynabus time-out                                                                                                        |          |

| 7.2.3.2 Dynabus rejection                                                                                                       |          |

| 7.2.3.3 Memory uncorrectable ECC erro                                                                                           | or149    |

| 7.2.3.4 External cache parity error                                                                                             |          |

| 7.2.3.5 Viking write parity error                                                                                               |          |

| 7.2.3.6        | DeMap time-out                          | 150  |

|----------------|-----------------------------------------|------|

| 7.2.3.7        | SBus time-outs                          | 150  |

|                | SBus PTE Errors                         |      |

| 7.2.3.9        | SBus rejection                          | 150  |

|                | SBus parity errors                      |      |

| 7.2.3.11       |                                         |      |

| 7.2.4 Fatal    | CITORS                                  |      |

| 7.2.4.1        | Dynabus parity error                    | 152  |

| 7.2.4.2        | Dynabus arbitration parity error        | 152  |

| 7.2.4.3        | Dynabus arbitration time-out            | 152  |

| 7.2.4.4        | XBus parity error                       | 152  |

| 7.2.4.5        | Cache consistency errors                | 153  |

| 7.2.4.6        | WriteSingle time-out                    | 153  |

| 7.2.4.7        | Multiple DeMaps                         | 153  |

| 7.2.4.8        | Device-specific errors                  | 154  |

| 7.2.5 Critic   | cal errors                              | 154  |

| 7.2.5.1        | AC Failure                              | 154  |

|                | Temperature Warning                     |      |

| 7.2.5.3        | Fan Failure                             | 154  |

| Chapter 8      |                                         |      |

| -              | ·····                                   | 155  |

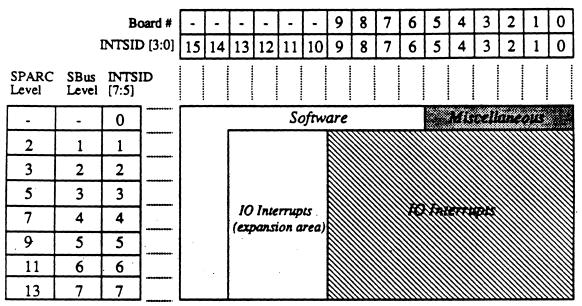

|                | of Interrupt Model                      |      |

|                | ieneration                              |      |

|                | nt <b>errupts</b>                       |      |

|                | essor Interrupts                        |      |

|                | ella <b>neo</b> us Interrupts           |      |

|                | Counter-Timers                          |      |

| 8.2.3.2        | Memory Queue Handler Chips              |      |

|                | SBus Interface Chips                    |      |

|                | Interrupts                              |      |

|                | Cache Controller                        |      |

|                | Serial Ports                            |      |

|                | Environment Interrupts                  |      |

|                | ran <b>spor</b> t                       |      |

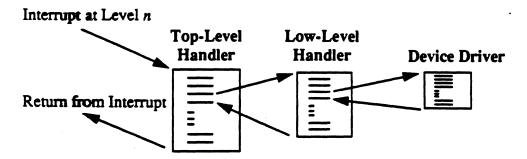

|                | landling                                |      |

|                | Level Handler                           |      |

|                | Level Handler                           |      |

|                |                                         |      |

|                | errupt Usage                            |      |

| ora with or mu | an ahr a safe                           | 10/  |

| Chapter 9      |                                         |      |

|                | • • • • • • • • • • • • • • • • • • • • |      |

|                | 25. <u></u>                             |      |

| 9.1.1 Syste    | m Reset                                 | .169 |

|                | Power-On Reset                          |      |

| 9.1.1.2        | Service Processor Reset                 | .169 |

| 9.1.1.3 System Software Reset          |

|----------------------------------------|

| 9.1.1.4 System Watchdog Reset          |

| 9.1.2 Local Reset                      |

| 9.1.2.1 Local Software Reset           |

| 9.1.2.2 Watchdog Reset                 |

| 9.2 Reset Source Identification        |

| 9.3 Loopback Mode                      |

| 9.4 System Bootstrap                   |

|                                        |

| Chapter 10                             |

| JTAG                                   |

| 10.1 Scan Rings                        |

| 10.1.1 System Board                    |

| 10.1.2 System Control Board            |

| 10.2 Software Interface to JTAG        |

| 10.2.1 Active JTAG Controller          |

| 10.2.2 Programming the JTAG Controller |

| 10.2.2.1 Reset                         |

| 10.2.2.2 SelRing                       |

| 10.2.2.3 SelDataReg                    |

| 10.2.2.4 SelInstReg                    |

| 10.2.2.5 Shift                         |

| 10.2.2.6 RunIdle                       |

| 10.2.2.7 IRtoDR                        |

| 10.2.2.8 DRtoIR                        |

| 10.2.3 Service Processor Interface     |

| 10.3 On-chip JTAG Instructions         |

| 10.3.1 Common Instruction Set          |

| 10.3.1.1 Instruction Register          |

| 10.3.1.2 ID Register                   |

| 10.3.2 Viking                          |

| 10.3.3 CC                              |

| 10.3.4 BW                              |

| 10.3.5 MQH                             |

| 10.3.6 IOC                             |

| 10.3.7 SBI                             |

| 10.3.8 CARB                            |

| 10.3.9 BARB                            |

| 10.3.10 BIC                            |

| 10.3.11 JTAG EEPROM                    |

| 10.3.12 74BCT8244                      |

| References                             |

Í

ŧ

• •

# Chapter 1 Introduction

### 1.1 Scope

This document describes the Sun-4D system architecture. The Sun-4D Architecture defines the programmer's model of systems build around Dynabus. It is intended to be the *reference* for software and firmware. The first two Sun hardware platforms based on this architecture are SunDragon and Scorpion. The Sun-4D Architecture provides a great deal of flexibility. Systems based on this architecture may include one, two or four Dynabusses, from 1 to 20 processors and up to 40 SBus boards for I/O. Only built-in I/O devices are described in this document. The usual I/O interfaces found in other Sun systems like SCSI, Ethernet and VME are not described here as they are all attached to an SBus through a combination of I/O Cache and SBus Interface chips. They are described in companion documents.

Although, this document is intended to encompass all system implementations using the same Dynabus chip set, it focuses specifically on SunDragon and Scorpion.

This document also describes the diagnostic features that are accessible from processors. However, diagnostic interfaces that must be accessed from a remote service processor are not described here.

#### 1.2

I

14

## Hardware Architecture Overview

Sun-4D defines a shared memory multiprocessor architecture. Sun-4D systems are composed of three types of units: the Processor unit, the Main Memory unit and the I/O unit. All these units are interconnected through one, two or four Dynabus(ses). Dynabus is a high-speed, consistent, packet-switched bus [4]. In a given implementation, the total number of units and the number of units of a given type is dictated mainly by the following considerations: bandwidth of the Dynabus(ses), overall computing throughput and I/O connectivity.

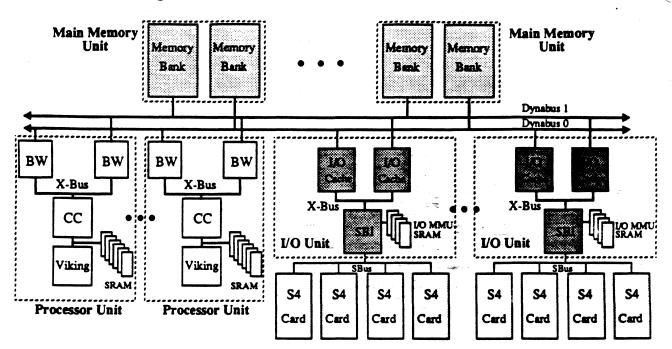

#### 1.2.1 SunDragon

SunDragon is built around two Dynabusses, and all units have two Dynabus ports. Physical addresses are interleaved on a 256-byte boundary across the two busses. For practical purposes, the two Dynabusses appear to programmers as a single bus with twice the bandwidth.

SunDragon can have between 1 and 20 Processor units, namely a SunDragon system can support between 1 to 20 Viking processors. SunDragon can include between 1 and 10 Main Memory units. The minimum main memory capacity is 64 Mbytes (using 4 M-bit DRAM chips) and the maximum 5 G-bytes (using 16 M-bit DRAM chips). SunDragon uses SBus as I/O bus. A SunDragon system can have between 1 and 10 SBus (i.e. 1 to 10 I/O units), each supporting four slots.

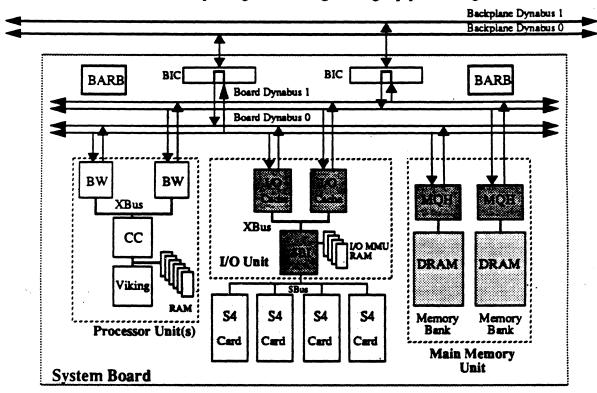

The Figure below illustrates how the various units are interconnected.

#### SunDragon Logical Organization

#### 1.2.2 Scorpion

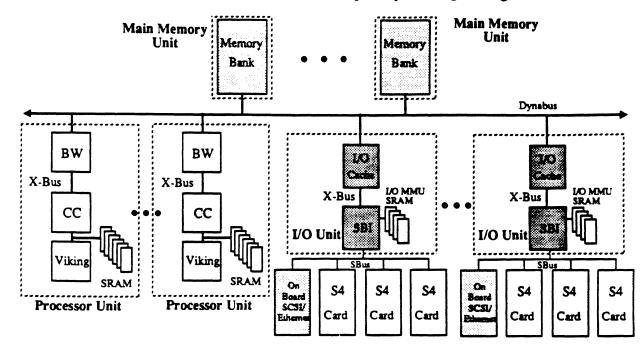

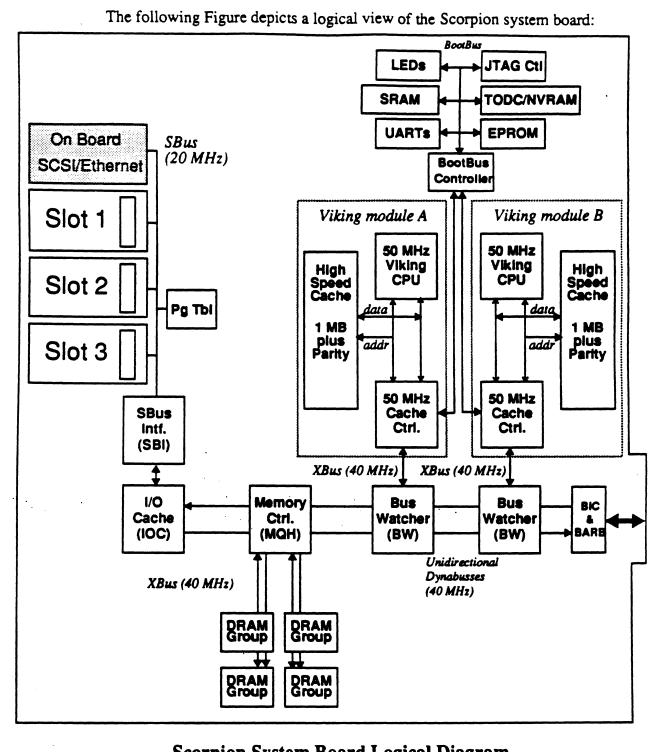

Scorpion is based on the same chip set as SunDragon, but the system is more restricted in term of flexibility and expendability. Scorpion is built around a single Dynabus. Because of this single Dynabus architecture, all Processor, Memory and I/O units in Scorpion have a single Dynabus interface.

A Scorpion system can include 1 to 8 processor units, 1 to 4 I/O units and 1 to 4 main memory units. Therefore, Scorpion can support between 1 to 8 Viking processors, from 1 to 4 SBus and a main memory capacity between 32 M-bytes and 2 G-bytes. Each I/O unit interfaces an SBus with three slots. The fourth slot is used by an on-board SCSI and Ethernet interface.

#### The Figure below describes the Scorpion system logical organization:

#### Scorpion Logical Organization

#### 1.2.3

#### **Processor Unit**

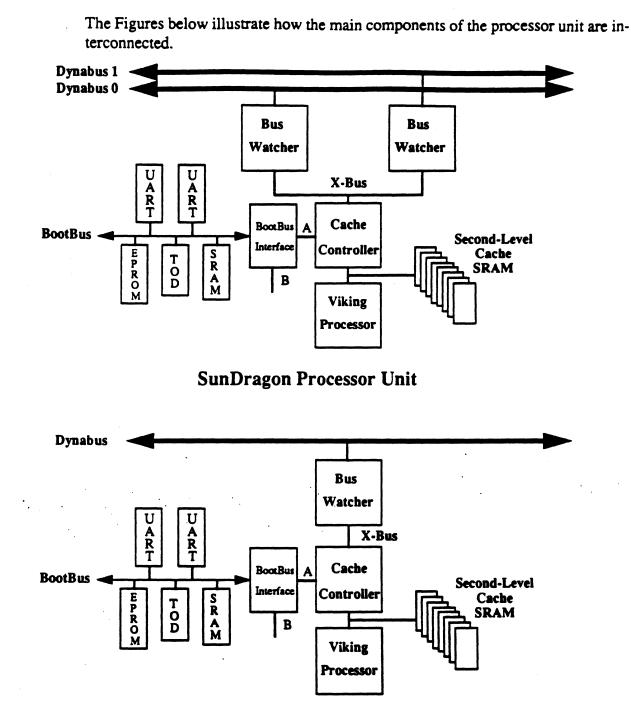

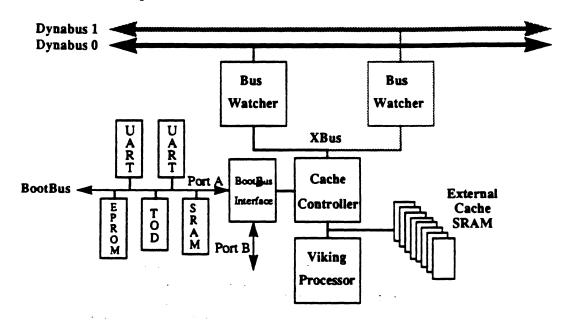

Each processor unit consists of a Viking processor, a second-level cache and the Dynabus interface(s). The Viking processor chip includes: an Integer Unit (IU), a Floating Point Unit (FPU), a SPARC Reference Memory Management Unit (SRMMU), a 16 K-byte Data Cache and a 20 K-byte Instruction Cache. Viking is fully compatible with the SPARC architecture [1].

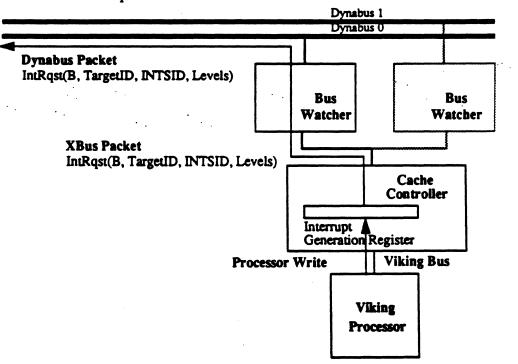

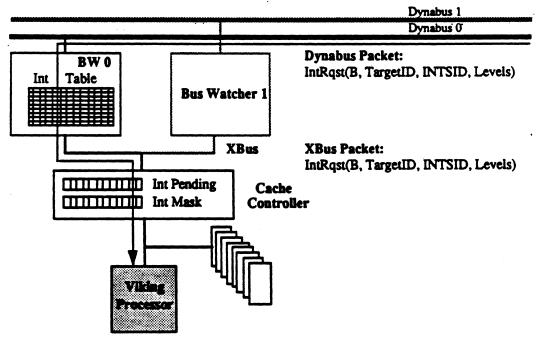

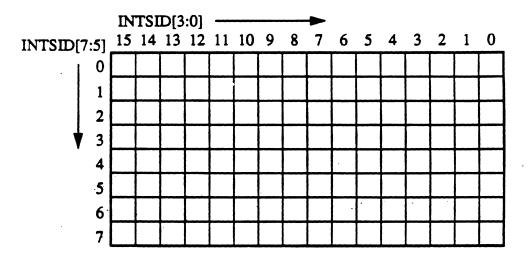

The second-level cache is a one M-byte, direct-map, physical address cache. It consists of a Cache Controller chip (CC), eight 128 Kx9 SRAM chips and either one or two Bus Watcher chips (BW). Each Bus Watcher links the Cache Controller to a Dynabus. In SunDragon, the processor unit comprises two Bus Watchers in order to interface the Cache Controller to the two system Dynabusses. In Scorpion, the processor unit includes only a single Bus Watcher. The Bus Watcher(s) and the Cache Controller cooperate to support the cache consistency protocol. All processor caches in Sun 4-D systems are kept consistent by the hardware.

An 8-bit local bus, called the BootBus, is supported by the Cache Controller. It is used to attach I/O devices that comprise the "Sunness" part of a processor unit, including the EPROM used for bootstrap and Power-On Self Tests. A single BootBus may be shared among multiple processor units. For packaging reasons, two processor units share the same BootBus both in SunDragon and Scorpion.

**Scorpion Processor Unit**

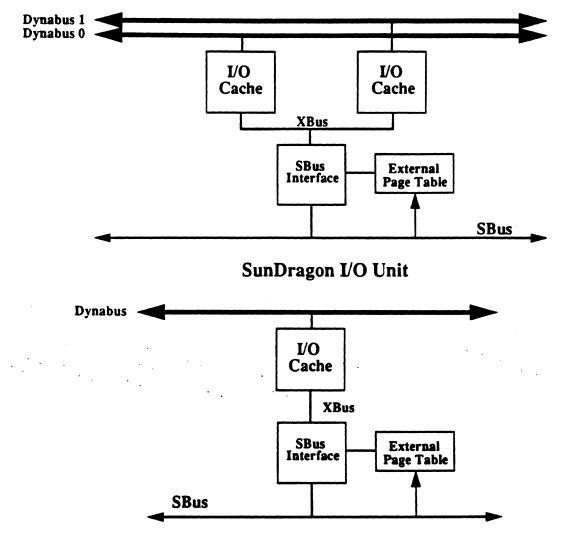

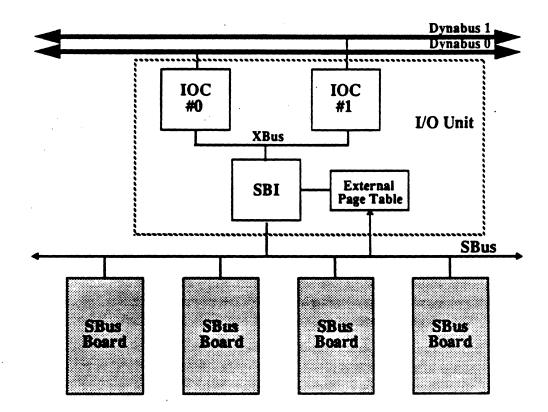

#### 1.2.4 I/O Unit

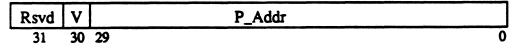

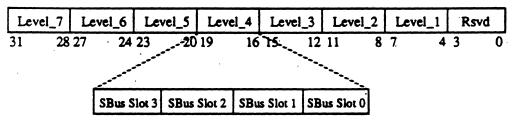

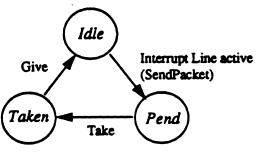

All "regular" I/O devices are attached via SBus. In SunDragon, an SBus is interfaced to both Dynabusses through an SBus Interface chip (SBI) and two I/O Cache chips (IOC). In Scorpion, the I/O units comprises an SBus Interface chip and a single I/O Cache chip. IOC chips contain a small I/O cache that is kept consistent with the processor caches. SBus addresses are translated into memory and I/O addresses

9/10/92 - Rev 1.4

with an I/O MMU dedicated to this SBus. The I/O MMU is implemented with an external SRAM array, called the External Page Table (XPT), which is controlled by the SBI. Each SBus provides 4 SBus slots.

The Figures below describes how the components of the I/O unit are interconnected.

Scorpion I/O Unit

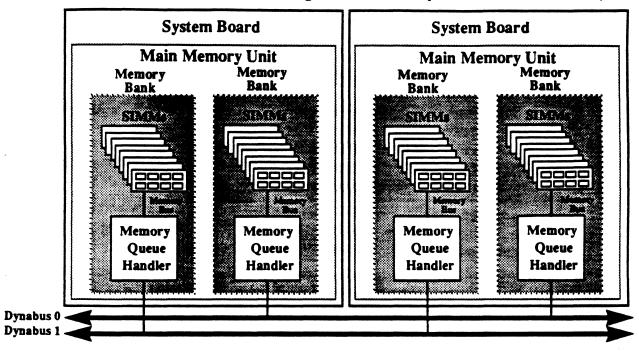

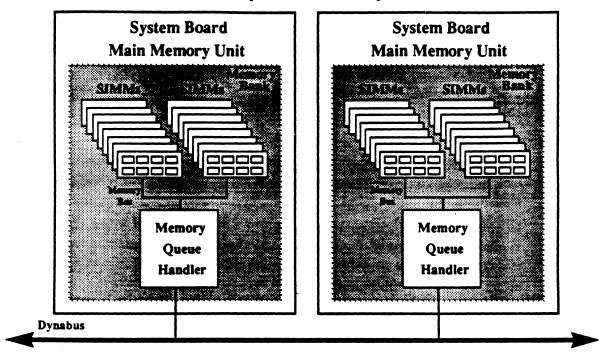

#### 1.2.5 Main Memory Unit

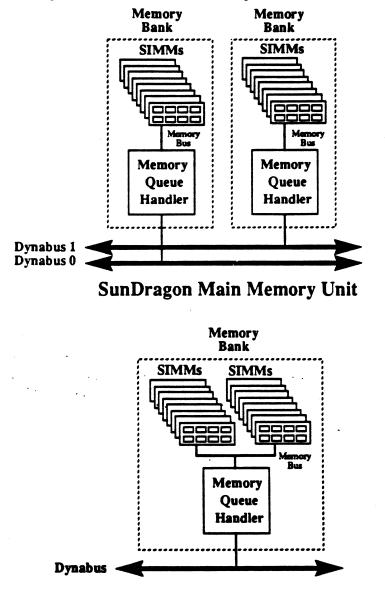

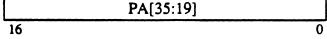

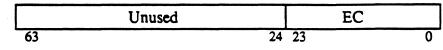

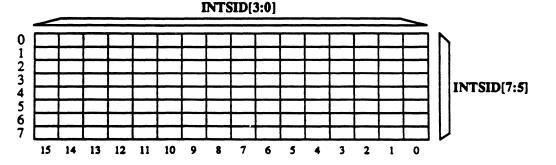

The main memory in SunDragon is interleaved across both Dynabusses on a 256byte boundary. A SunDragon main memory unit consists of two memory banks, one per Dynabus. A memory bank is a DRAM memory array controlled by a Memory Queue Handler chip (MQH). A SunDragon main memory unit can have a memory capacity between 32 M-bytes (with 4 M-bit chips) and 512 M-bytes (with 16 M-bit chips.

A Scorpion main memory unit consists of a single memory bank. As in SunDragon, a memory bank consists of a DRAM array controlled by a Memory Queue Handler

chip. In Scorpion, a memory array associated with an MQH is twice the size of the memory array of a SunDragon memory bank. Therefore, a Scorpion memory unit has the same capacity as a SunDragon main memory unit (between 32 and 512 M-bytes).

The Figures below describe the components of the Main Memory unit:

Scorpion Main Memory Unit

## **1.3** Implementation Overview

#### 1.3.1 SunDragon Implementation

The mix of different types of units on the same board is only the result of packaging considerations. All units of the same type are identically accessible (with the same

Page 6

access time) whatever the board on which they are located. The main memory access latency is the same for all processors whatever the physical location of the accessed memory bank. The access latency to an I/O device is also the same for all processors regardless of the particular SBus to which the device is attached.

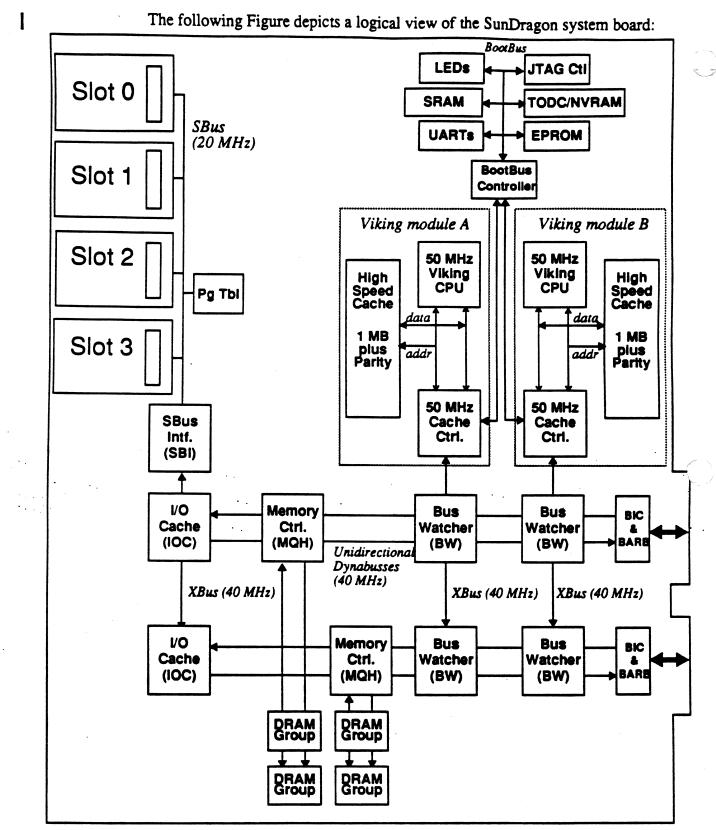

There is only one type of System Board. The SunDragon system board contains two processor units, one main memory unit and one I/O unit. The SunDragon rack can accommodate up to 10 system board.

Processor units on a system board are pluggable components (Viking module). As a result, a system board may contain 0, 1 or 2 processors.

Introduction

Sun-4D Architecture

SunDragon System Board Logical Diagram

9/10/92 - Rev 1.4

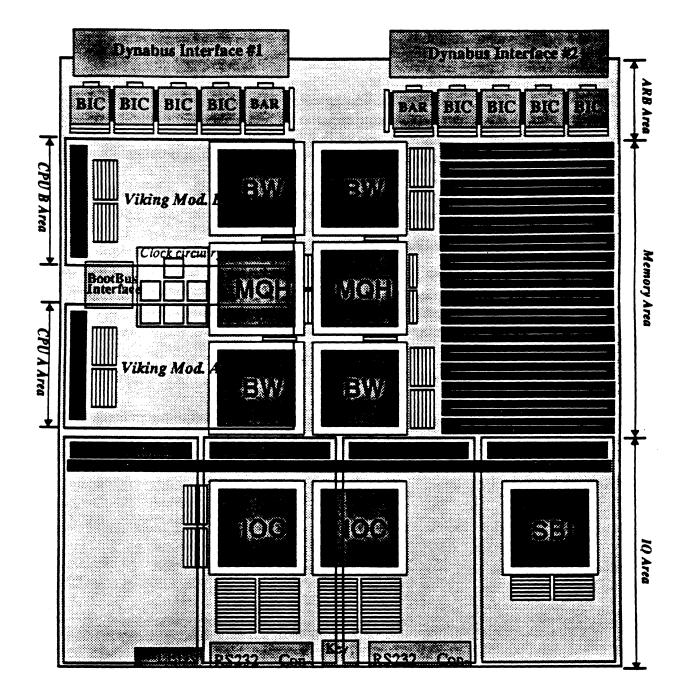

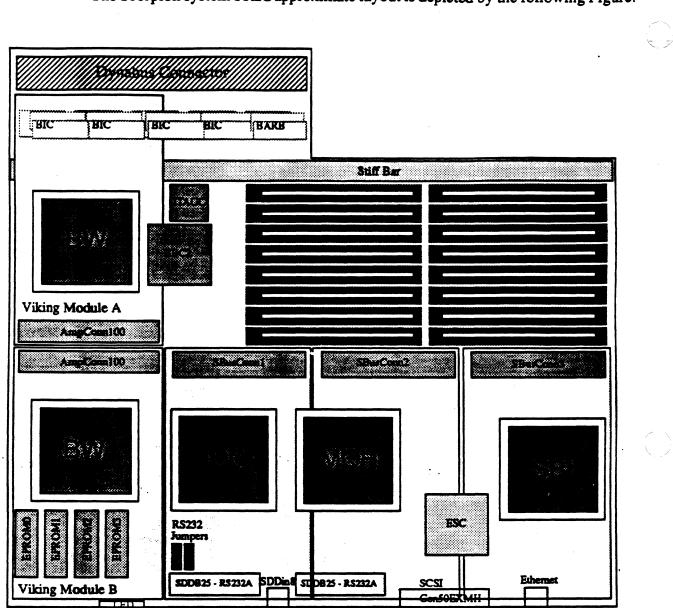

The SunDragon system board approximate layout is depicted by the following Figure.

SunDragon System Board Layout

The SunDragon backplane contains the two Dynabusses. The interface between the on-board Dynabusses and the backplane Dynabusses is done with Bus Interface chips (BIC). BICs are16 bit-sliced pipeline registers (4 per Dynabus).

The Dynabus arbitration is done at two levels with Board Arbiter chips (BARB) and Central Arbiter chips (CARB). A BARB can serve four Dynabus devices. There is one BARB per bus on the System Board. The CARB can serve 10 BARBs.

Two CARBs, one per Dynabus, and the clock generation circuitry are mounted on a specific board called the System Control board. This board is attached to the rear of the backplane.

All ASICs support JTAG for testing and configuration purposes. JTAG provides a serial data path to shift information inside the chips. At the system level, SunDragon implements an extended version of JTAG, called JTAG+, that allows to select a particular board and a chip on that board. There are no jumpers on the System Board as all initialization parameters can be loaded in the chips with JTAG. The JTAG scan bus is accessible by the processors and, for manufacturing purposes, by an external controller attached via the system backplane.

#### **1.3.2** Scorpion Implementation

Scorpion, like SunDragon, uses only one type of system board. The mix of different units on the system board was dictated by packaging consideration. The Scorpion system board comprises two processor units, a main memory unit and an I/O unit. Scorpion backplane supports a single Dynabus. A control board is connected to the back of the backplane.

The processor modules and the main memory SIMMs are identical for SunDragon and Scorpion.

There are only three SBus slots (i.e. three SBus connectors) due to the physical size of the board. However, the I/O unit can support four SBus slots and the "fourth SBus slot" is used by an on-board SCSI and buffered Ethernet interface.

#### Scorpion System Board Logical Diagram

The Scorpion system board approximate layout is depicted by the following Figure.

# Chapter 2 Memory Model

Sun-4D's memory model conforms to the reference memory model defined in Version 8 of the SPARC Architecture Manual. This chapter describes the memory model and provides additional details relevant to Sun-4D programmers. It begins with an overview, and then goes on to describe the **Total Store Ordering (TSO)**, and **Partial Store Ordering (TSO)** models supported by Sun-4D systems. Although the memory model treats I/O and processors as much alike as possible, there are still special considerations that apply to I/O; these are taken up last.

## 2.1 Overview

The memory model defines the semantics of memory operations such as load and store and specifies how the order in which these operations are issued by a processor is related to the order in which they are executed by memory. Except where indicated otherwise, the term processor refers to any entity that generates memory references, and the term memory includes device I/O registers. The model applies to all configurations of SunDragon and Scorpion whether they contain multiple processors or not. The standard SPARC memory Total Store Ordering (TSO) is supported, as is the higher performance version called Partial Store Ordering (PSO). The PSO model is enabled via the PSO mode bit in the Viking's MMU control register.

The TSO and PSO models allow SunDragon and Scorpion to achieve higher performance than a machine that is restricted to using the well known "Strong Consistency" model. In this model, the loads, stores, and atomic load-stores of all processors are executed by memory serially in an order that conforms to the order in which instructions were issued by individual processors.

Programs written on Sun-4D systems using single-writer-multiple-readers locks will be portable across PSO, TSO, and Strong Consistency. Programs that use write-locks but read without locking will be portable across PSO, TSO, and Strong Consistency only if writes to shared data are separated by STBAR<sup>1</sup> instructions. If these STBAR's are omitted, then the code will be portable only across TSO and Strong Consistency. The guidelines for other programs are as follows: Programs written for PSO will work automatically on Sun-4D systems running in TSO mode or on a machine that implements Strong Consistency; programs written for TSO will work automatically on a machine that implements Strong Consistency; programs written for Strong Consistency may not work on Sun-4D systems regardless of the mode in which it is running; it is more likely that such a program will break

I

I

<sup>1.</sup> STBAR is defined in the SPARC Architecture Manual, Version 8. The encoding is identical to RDASR %r15,%g0.

with PSO than with TSO. Finally, programs written for Sun-4D systems assuming TSO may not work when the machine is in PSO.

2.2 Basic Definitions

Memory is the collection of locations accessed by the SPARC load/store instructions; see the SPARC Architecture Manual for a list. These locations include real memory, I/O device registers, and registers accessible via alternate space. For the purpose of ordering, the memory model makes no distinction between the normal and alternate space versions of instructions. However, see the note in section 2.7 on page 20 for loads and stores to I/O devices.

Memory is byte addressed, with half-word accesses being aligned on a 2-byte boundary, word accesses being aligned on a 4-byte boundary, and double-word accesses being aligned on an 8-byte boundary. The largest datum that is atomically read or written by memory hardware is a double-word. Also, memory references to different bytes in a given double-word are treated for ordering purposes as references to the same location. Thus the unit of ordering for memory is a double-word.

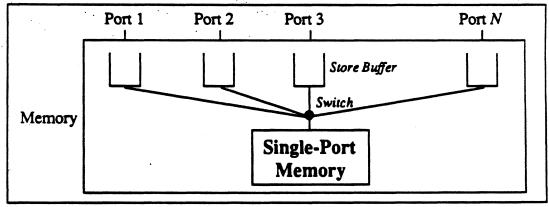

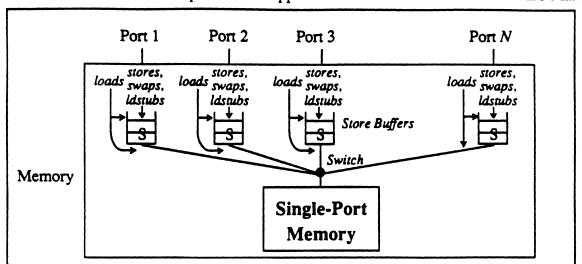

Memory is modeled as an N port device where N is the number of processors. A processor initiates memory operations via its port in what is called the **issuing order**, or the **program order**. Each port contains a Store Buffer used to hold stores and atomic-load stores. A switch connects a single-port memory to one of the ports at a time for the duration of each memory operation. The order in which this switch is thrown from one port to another defines the memory order of operations. The Figure below shows this model.

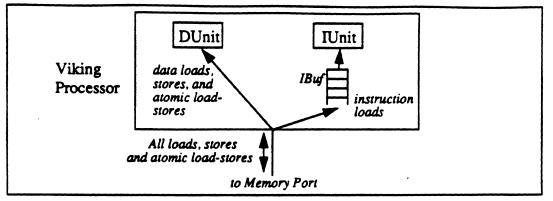

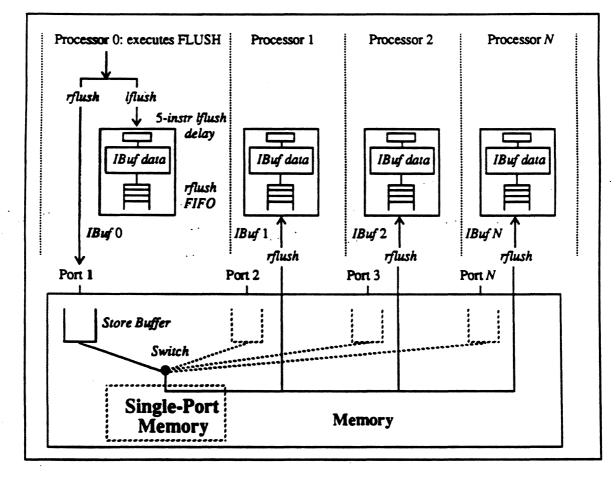

For purposes of the memory model, a Viking processor consists of three parts: a DUnit, an IUnit, and an IBuf.

The DUnit issues loads, stores and atomic load-stores to data; the IUnit issues loads to instructions; and the IBuf is a buffer where the value returned by such a load is placed when it arrives from memory (IBuf models Viking's internal instruction buffer). Notice that because of IBuf, a load to an instruction at address A may appear at the memory port *before* a data load or store issued by an earlier instruction to address A. The ordering of instruction loads relative to data loads and stores is enforced via the FLUSH instruction. When a Viking executes FLUSH A, the read data corresponding to location A is removed from IBuf if it is present.

## **Total Store Ordering (TSO)**

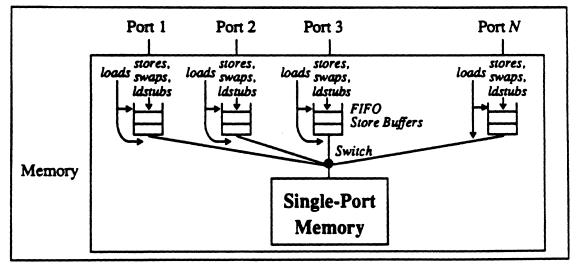

The Total Store Ordering model guarantees that the store and atomic load-store instructions of all processors appear to be executed by memory serially in a single order called the memory order. Furthermore, the sequence of store and atomic load-store instructions in the memory order for a given processor is identical to the sequence in which they were issued by the processor. The Figure below shows the ordering constraints for this model graphically. A formal specification appears in V8 of the SPARC Architecture Manual.

Stores and atomic load-stores issued by a processor are placed in its dedicated Store Buffer, which is FIFO. Thus the order in which memory executes these operations for a given processor is the same as the order in which the processor issued them. The memory order of these operations corresponds to the order in which the switch is thrown from one port to another.

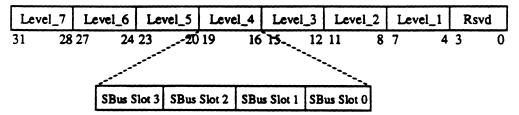

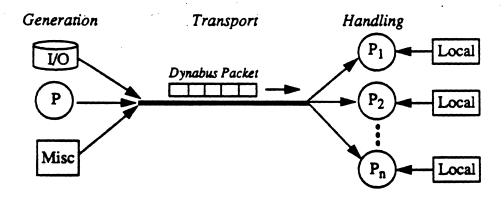

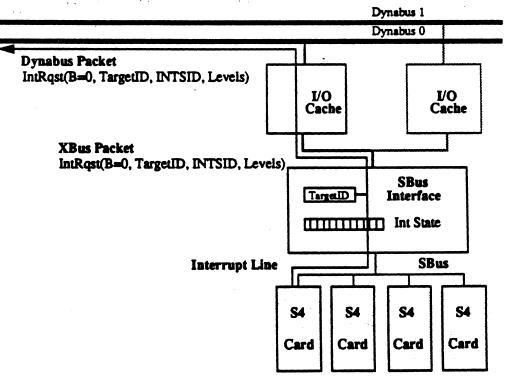

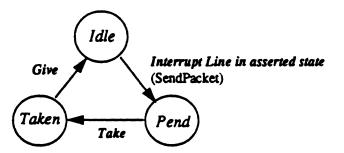

A load by a processor first checks its Store Buffer to see if it contains a store to the same location (atomic load-stores do not need to be checked for because they are blocking). If it does, then the load returns the value of the most recent such store, otherwise the load goes directly to memory. Since not all loads go to memory, loads in general *do not* appear in the memory order. A processor is blocked from issuing further memory operations until the load returns a value.