## SPARC classic Engine OEM Technical Manual

PART TWO: Appendices K & L microSPARC Reference Material

."

来山

Sun Microsystems, Inc. 2550 Garcia Avenue Mountain View, CA 94043 U.S.A.

Part No:. 801-3137-10 Revision A, April, 1993

## SPARC classic Engine OEM Technical Manual

PART TWO: Appendices K & L microSPARC Reference Material

Sun Microsystems, Inc. 2550 Garcia Avenue Mountain View, CA 94043 U.S.A.

Part No:. 801-3137-10 Revision A, April, 1993

## microSPARC Reference Manual

Use the Texas Instruments microSPARC Reference Manual to define the operating parameters for the microprocessor, and for any firmware/software development that you require.

The TI documentation included here is accurate as of the date of release of the SPARCengine EC OEM Technical Manual. Please call Texas Instruments to ensure that you have the most current documentation. Please use caution in developing plans on this information until you confirm it is the latest information available.

X

SPARCclassic Engine OEM Technical Manual

K-2

# *micro*SPĄRC<sup>™</sup>

# **Reference Guide**

Highly Integrated SPARC for Low-Cost Desktop Solutions

### Table of Contents

| Overview    | ,                                       | . 3 |

|-------------|-----------------------------------------|-----|

| Integer U   | Jnit                                    | . 5 |

| U           | Overview                                |     |

|             | Instruction Pipeline                    | 7   |

|             | Memory Operations                       |     |

|             | ALU/Shift Operations                    |     |

|             | Integer Multiply                        |     |

|             | Integer Divide                          |     |

|             | CTI's                                   |     |

|             | Instruction Cache Interface             |     |

|             | Data Cache Interface                    |     |

|             | Interlocks                              |     |

|             | Traps and Interrupts                    |     |

|             | Floating Point Interface                |     |

|             | Special Features                        |     |

|             | Divergence from SPARC Version 8         |     |

|             |                                         |     |

| Floating    | Point Unit                              |     |

|             | Overview                                |     |

|             | Deltas from SPARC Version 8             | 21  |

|             | Implementation Specific Features        | 22  |

|             | Software Considerations                 | 23  |

|             | FPU Instruction Timings                 | 25  |

| Memory      | Management Unit                         | 27  |

| 1.1011101 J | Overview                                |     |

|             | Translation Lookaside Buffer            |     |

|             | CPU TLB Lookup                          |     |

|             | CPU TLB Flush and Probe Operations      |     |

|             | Processor MMU Registers.                |     |

|             | IO MMU Registers                        |     |

|             | IO MMU Bypass Mode                      |     |

|             | Physical Address Register               |     |

|             | TLB Table Walk                          |     |

|             | Instruction Translation Buffer Register |     |

|             | Arbitration                             |     |

|             | Translation Modes                       |     |

|             | Page Mode Detection                     |     |

|             | Errors and Exceptions                   |     |

|             |                                         |     |

|             | Diagnostic Features                     | οU  |

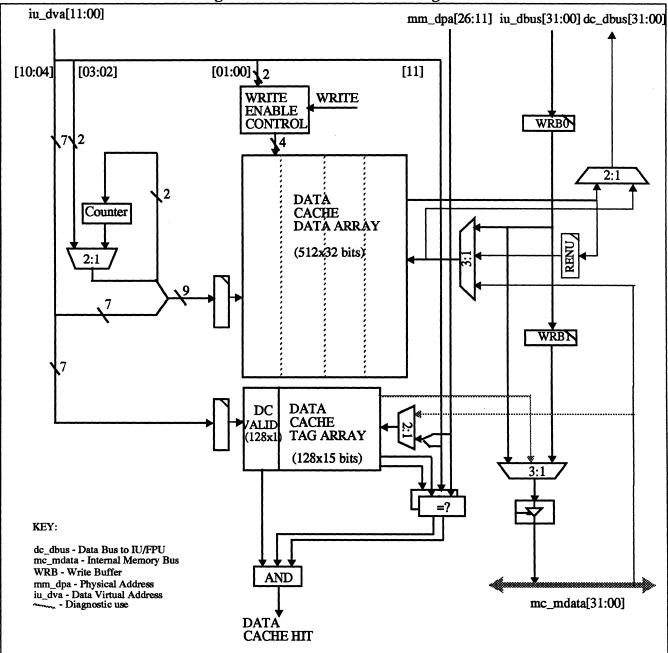

| Data Cao   | che                                                                                                                                                   | 67                               |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|            | Overview                                                                                                                                              | 67                               |

|            | Data Cache Data Array                                                                                                                                 | 69                               |

|            | Data Cache Tags                                                                                                                                       | 69                               |

|            | Write Buffers                                                                                                                                         | 70                               |

|            | Data Cache Fill                                                                                                                                       | 70                               |

|            | Internal Memory Bus Interface                                                                                                                         | 71                               |

|            | IU Data Bus Interface                                                                                                                                 | 71                               |

|            | RENU Register                                                                                                                                         | 71                               |

|            | Data Cache Flushing                                                                                                                                   |                                  |

|            | Cacheability of Memory Accesses                                                                                                                       | 71                               |

|            | Diagnostic Strategy                                                                                                                                   |                                  |

| <b>T</b>   |                                                                                                                                                       | 70                               |

| instructio | on Cache                                                                                                                                              |                                  |

|            | Overview                                                                                                                                              |                                  |

|            | Instruction Cache Data Array                                                                                                                          |                                  |

|            | Instruction Cache Tags                                                                                                                                |                                  |

|            | Instruction Cache Fill                                                                                                                                |                                  |

|            | Internal Memory Bus Interface                                                                                                                         |                                  |

|            | IU Instruction Bus Interface                                                                                                                          |                                  |

|            | Instruction Cache Flushing                                                                                                                            |                                  |

|            | Cacheability of Memory Accesses                                                                                                                       |                                  |

|            | Diagnostic Strategy                                                                                                                                   | 77                               |

| Memory     | Interface                                                                                                                                             | 7 <b>9</b>                       |

| 5          | Overview                                                                                                                                              |                                  |

|            | Memory Subsystem                                                                                                                                      |                                  |

|            | Memory Control Block (MCB)                                                                                                                            |                                  |

|            | Data aligner and Parity Check/generate logic (DPC)                                                                                                    |                                  |

|            | RAM Refresh Control (RFR)                                                                                                                             |                                  |

| 0D         |                                                                                                                                                       | 00                               |

| SBus Col   |                                                                                                                                                       | 99                               |

|            | Overview                                                                                                                                              |                                  |

|            | CPU Interface                                                                                                                                         |                                  |

|            | Address Steering                                                                                                                                      |                                  |

|            | SBus Arbiter 1                                                                                                                                        |                                  |

|            |                                                                                                                                                       | 1 ^                              |

|            | Main Control 1                                                                                                                                        |                                  |

|            | Data Transfer 1                                                                                                                                       | 13                               |

|            | Data Transfer                                                                                                                                         | 13<br>14                         |

|            | Data Transfer    1      Slave Control Cycle    1      Slave Target Control    1                                                                       | 13<br>14<br>16                   |

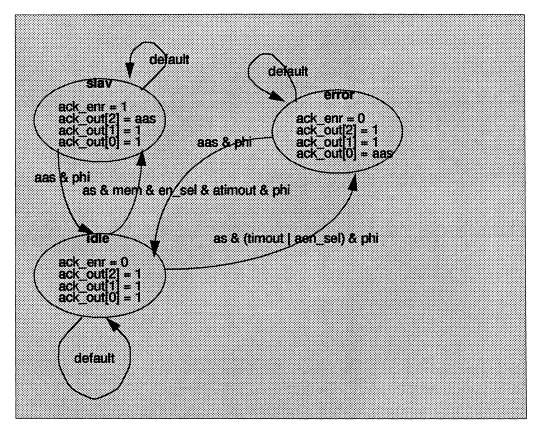

|            | Data Transfer       1         Slave Control Cycle       1         Slave Target Control       1         Data Path       1                              | 13<br>14<br>16<br>17             |

|            | Data Transfer       1         Slave Control Cycle       1         Slave Target Control       1         Data Path       1         Data Control       1 | 13<br>14<br>16<br>17<br>19       |

|            | Data Transfer       1         Slave Control Cycle       1         Slave Target Control       1         Data Path       1                              | 13<br>14<br>16<br>17<br>19<br>19 |

| Additional Work 120                      | ) |

|------------------------------------------|---|

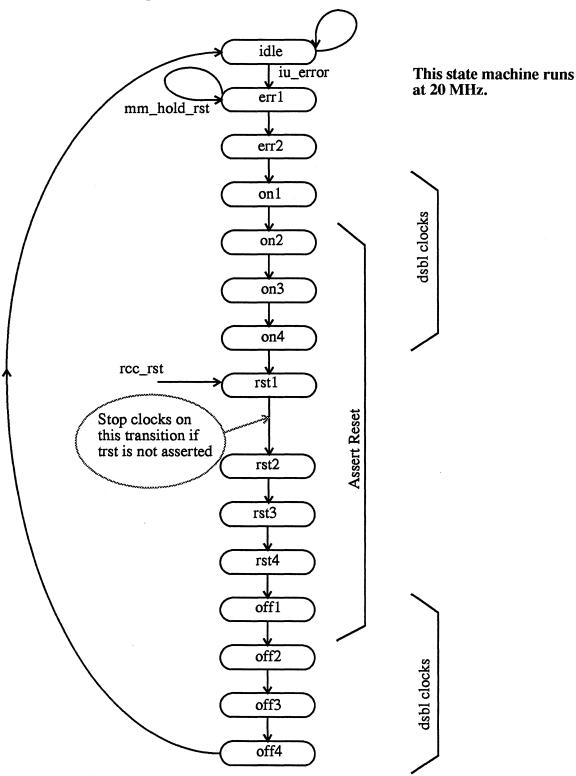

| Reset, Clock Control, JTAG 121           | L |

| Reset Controller                         | 1 |

| Reset Controller State Machine Operation | 4 |

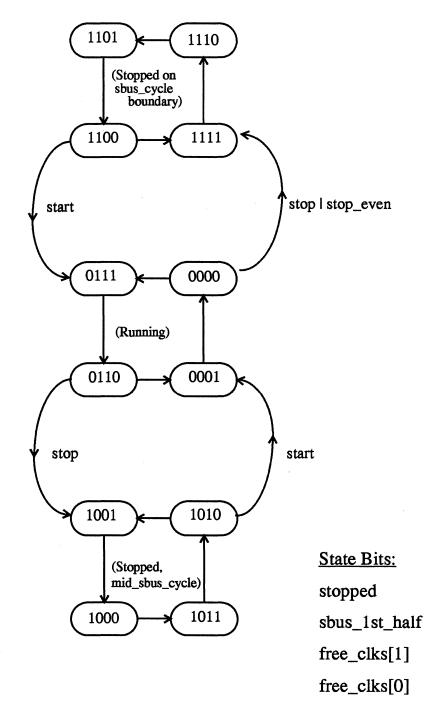

| Clock Controller 125                     |   |

| Clock Signals                            |   |

| Stopping Clocks                          | 7 |

| Starting Clocks                          |   |

| Single-Step 127                          |   |

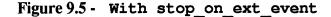

| Stop Clocks on Internal Event            |   |

| External Cycle Counter 128               |   |

| Counting Clocks                          |   |

| Issuing N Clocks                         |   |

| Count Clocks After Internal Event        |   |

| Stop Clocks After N Internal Events 139  | 9 |

| CCR Bits                                 |   |

| JTAG                                     |   |

| Board Level Architecture                 | 1 |

| TAP                                      | 1 |

| Data Registers                           | 2 |

| JTAG Instructions                        | 3 |

| JTAG Interface to MISC 144               | 4 |

| JTAG Operation 146                       |   |

|                                          |   |

| Error Handling 151                       | L |

| ASI Map                                  | 3 |

| Overview                                 |   |

|                                          | - |

| References                               | ) |

Revision 02 of 15 December 1992

vi

## List of Figures

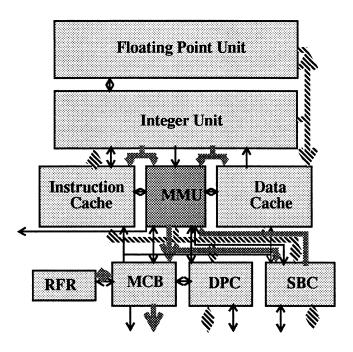

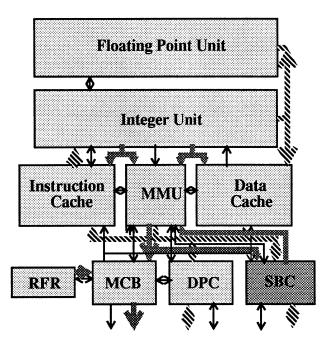

| microSPARC Block Diagram                       | 3          |

|------------------------------------------------|------------|

| microSPARC IU Block Diagram                    | 6          |

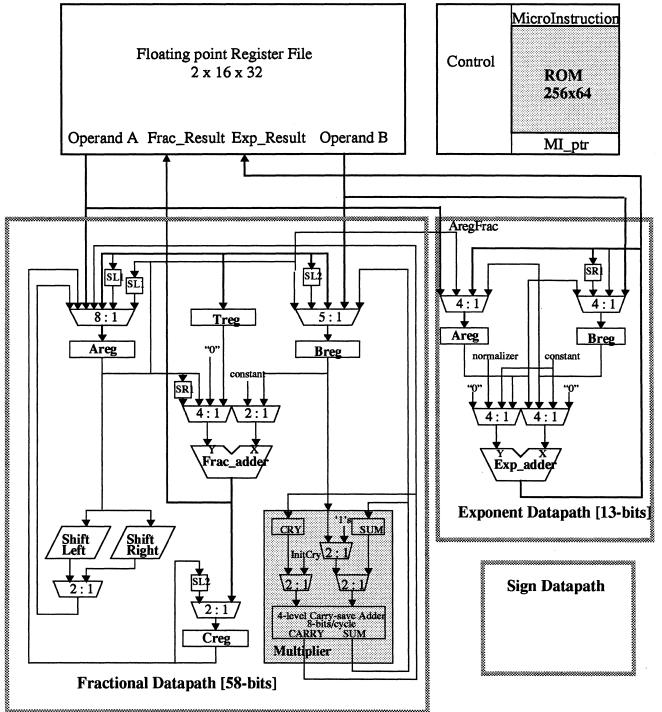

| Meiko FPU Block Diagram                        | . 20       |

| Untrapped FP Result in Same Format as Operands | . 21       |

| Untrapped FP Result in Different Format        | 22         |

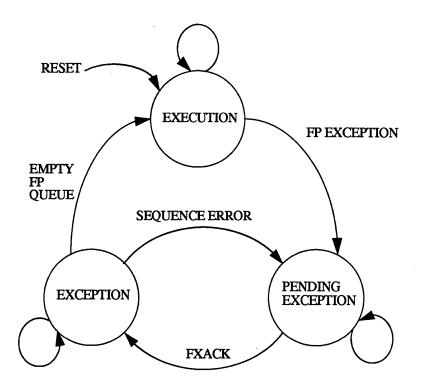

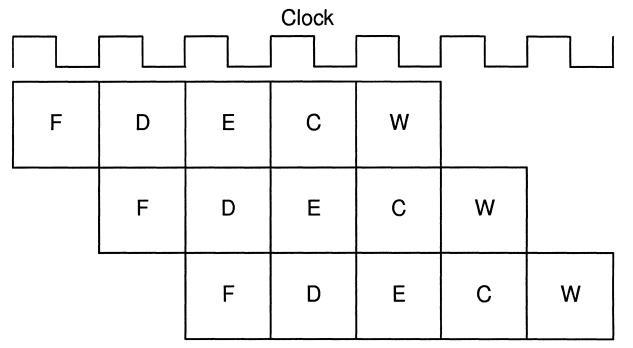

| FPU Operation Modes                            | 23         |

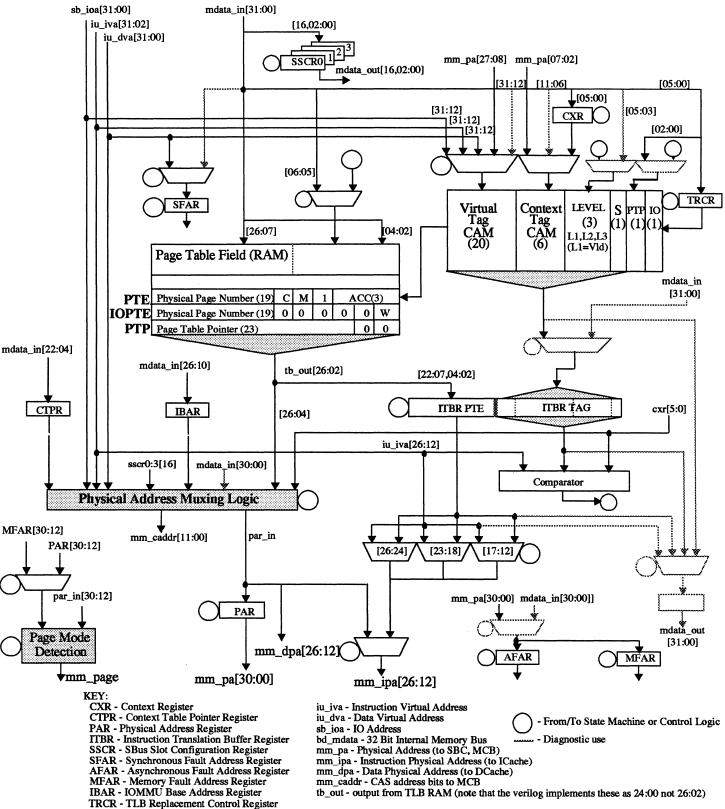

| MMU Address and Data Path Block Diagram        | . 28       |

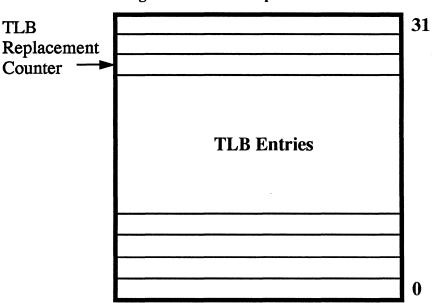

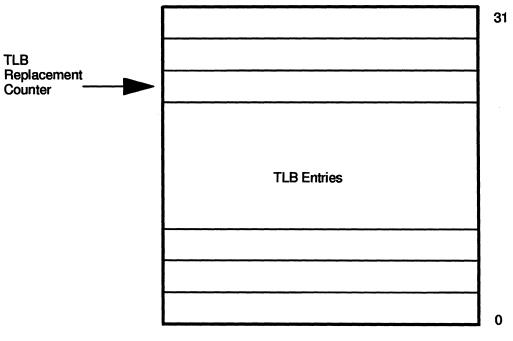

| TLB Replacement                                | 29         |

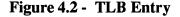

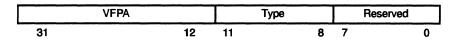

| TLB Entry                                      |            |

| Page Table Entry in Page Table                 | 31         |

| Page Table Entry in TLB                        |            |

| Page Table Pointer in Page Table               | 32         |

| Page Table Pointer in TLB                      | 33         |

| IO Page Table Entry in Page Table              | 34         |

| IO Page Table Entry in TLB                     | 34         |

| CPU TLB Flush or Probe Address Format          | 36         |

| Processor Control Register                     | 38         |

| Context Table Pointer Register                 | <b>4</b> 1 |

| Context Register                               | <b>4</b> 1 |

| Synchronous Fault Status Register              | 42         |

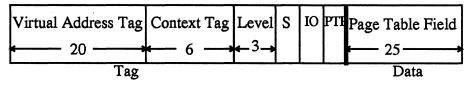

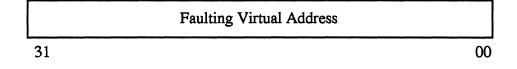

| Synchronous Fault Address Register             | 46         |

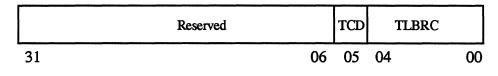

| TLB Replacement Control Register               | 46         |

| IO Control Register                            | 47         |

| IO MMU Base Address Register                   | 48         |

| IOPTE Address Based Flush Format               | 49         |

| Asynchronous Fault Status Register             | 50         |

| Asynchronous Fault Address Register            | 51         |

| SBUS Slot Configuration Register               | 51         |

| Memory Fault Status Register                   | 52         |

| Memory Fault Address Register                  | 53         |

| MID Register                                   | 54         |

| Physical Address Register                      | 55         |

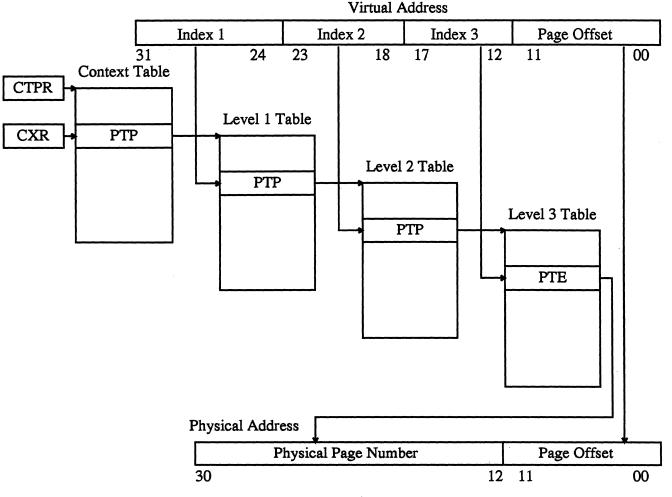

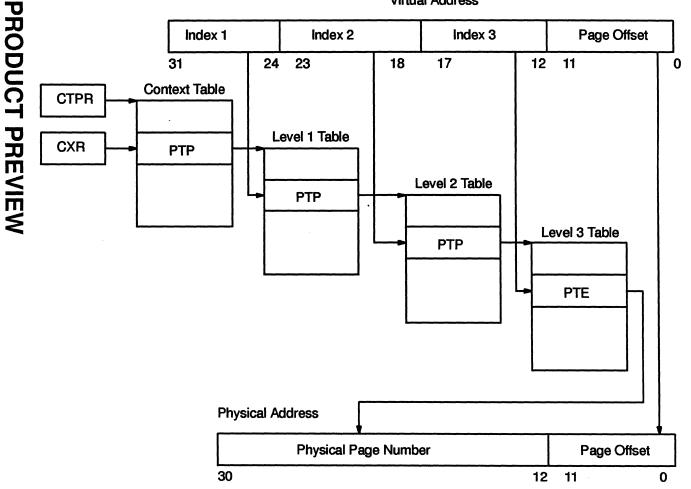

| CPU Address Translation Using Table Walk       | 56         |

| ITBR Page Table Entry                          |            |

| CPU Diagnostic TLB and ITLB Tag Access Format  | 60         |

| Data Cache Block Diagram                       | . 68       |

| Data Cache Tag Entry                           | 69         |

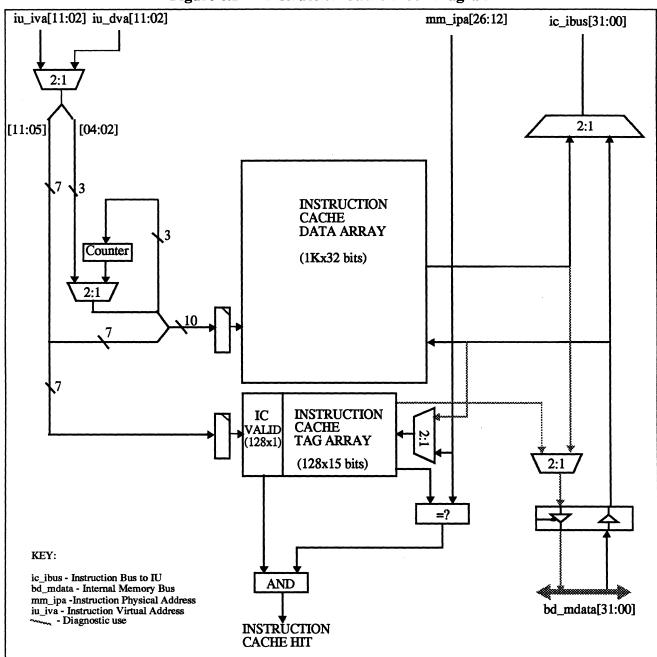

| Instruction Cache Block Diagram                | . 74       |

| Instruction Cache Tag Entry                    |            |

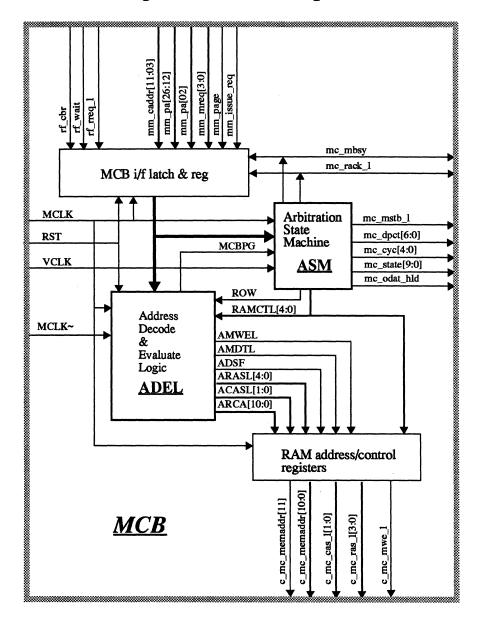

| MCB block diagram.                             | . 82       |

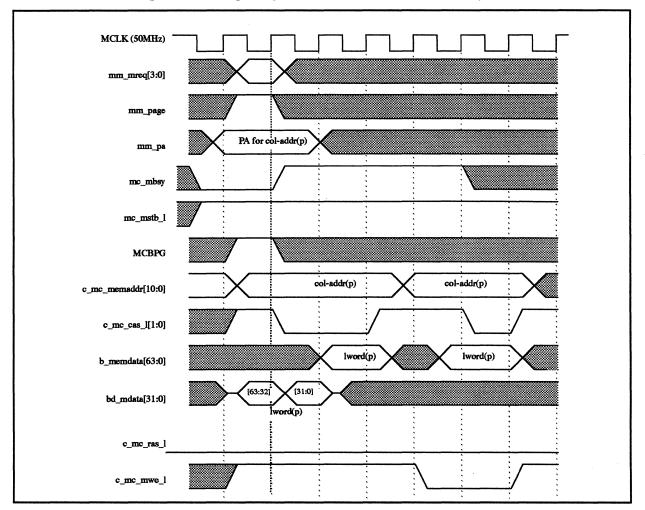

| MMU I-fetch beginning in page-mode             | 86         |

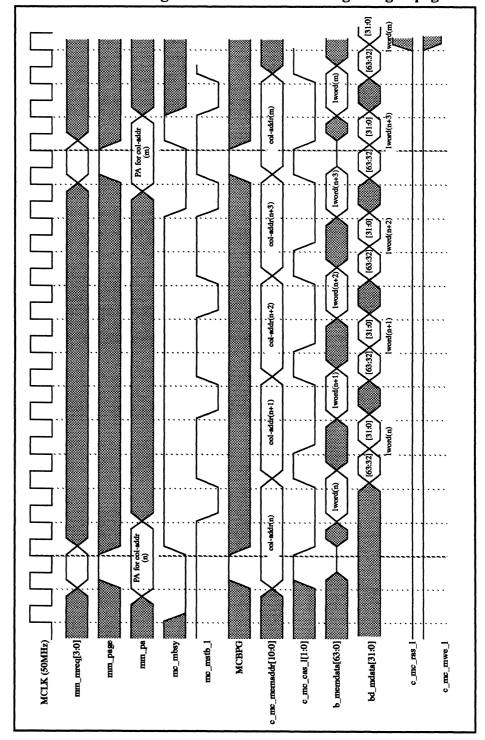

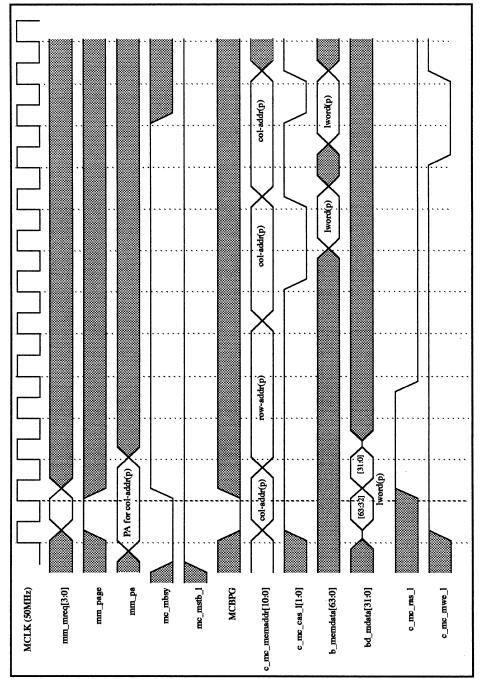

| MMU page-mode write after a read                             |  |

|--------------------------------------------------------------|--|

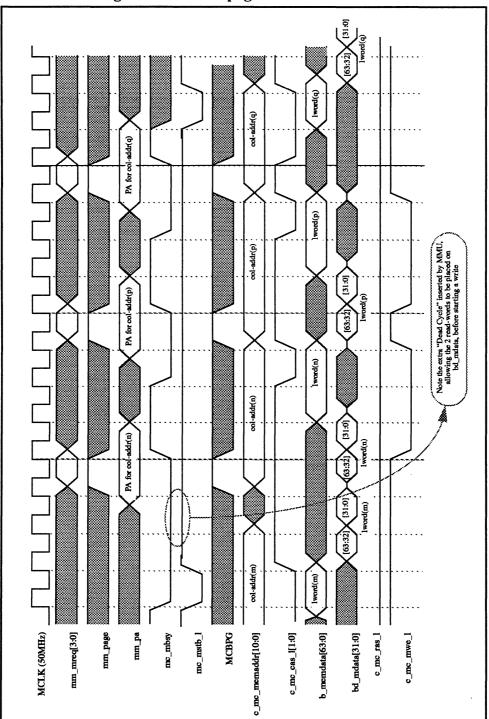

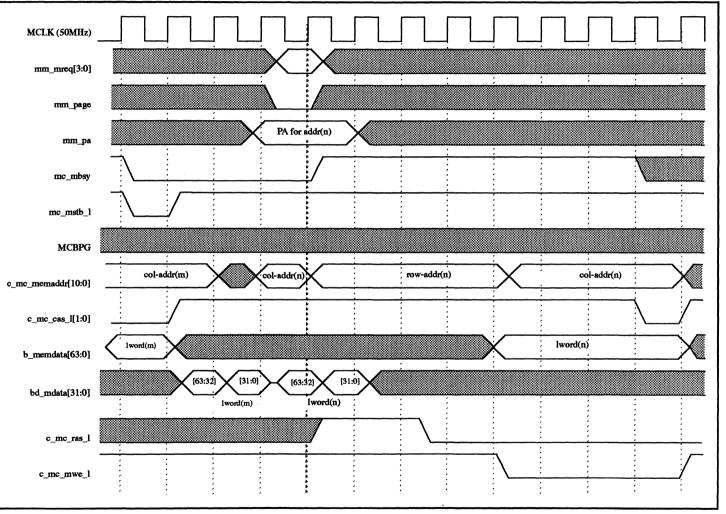

| Non-paged write cycle, shown following a read                |  |

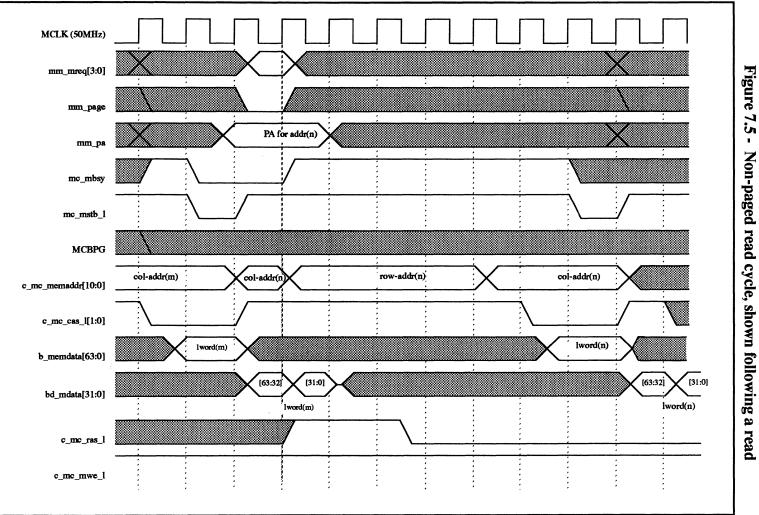

| Non-paged read cycle, shown following a read                 |  |

| Paged Byte/Halfword (8/16 bit) write cycle                   |  |

| Non-paged Byte/Halfword (8/16 bit) write cycle               |  |

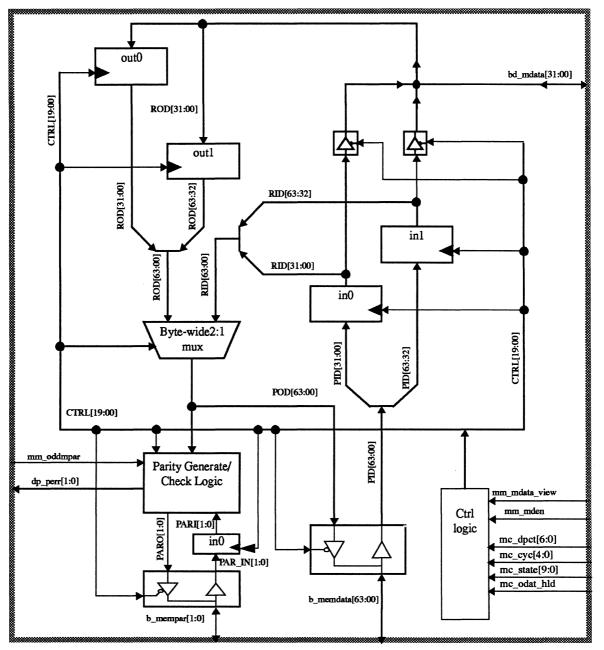

| Datapath and Parity Control (DPC) block diagram              |  |

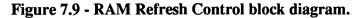

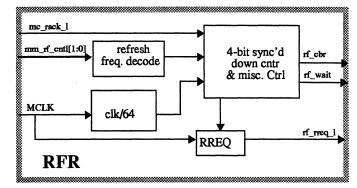

| RAM Refresh Control block diagram                            |  |

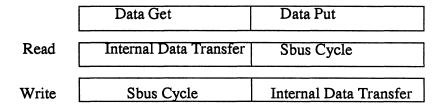

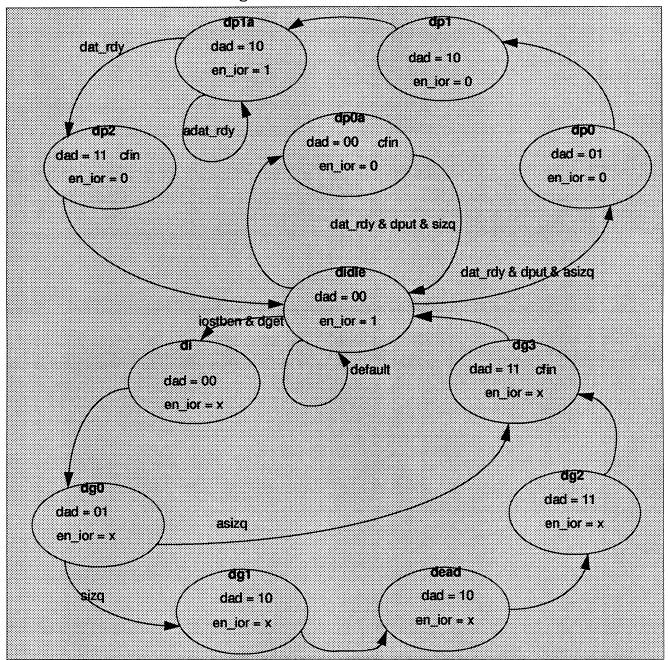

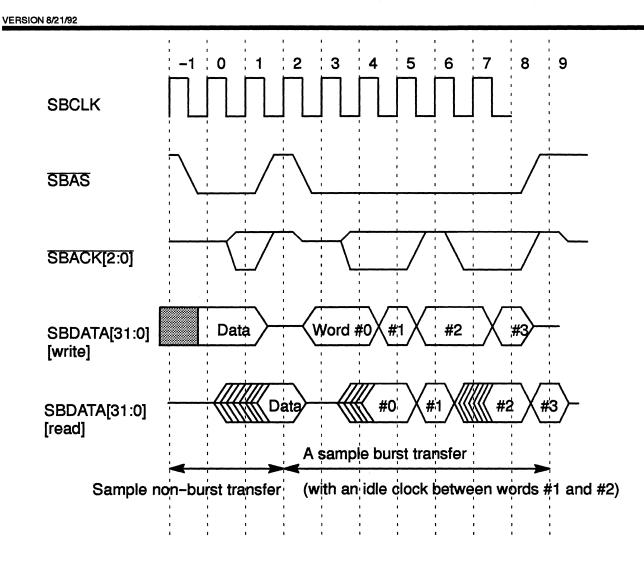

| Data Get and Data Put 101                                    |  |

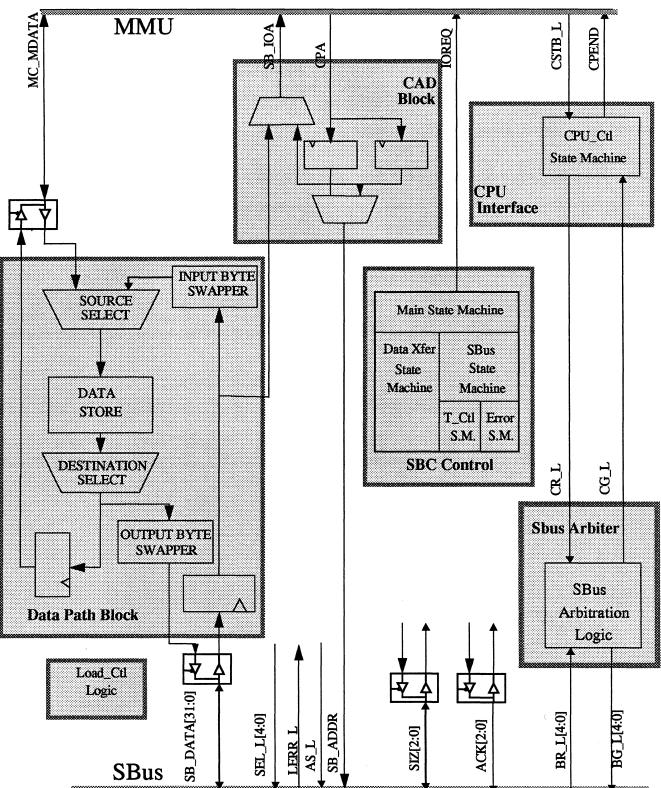

| SBus Controller Block Diagram 103                            |  |

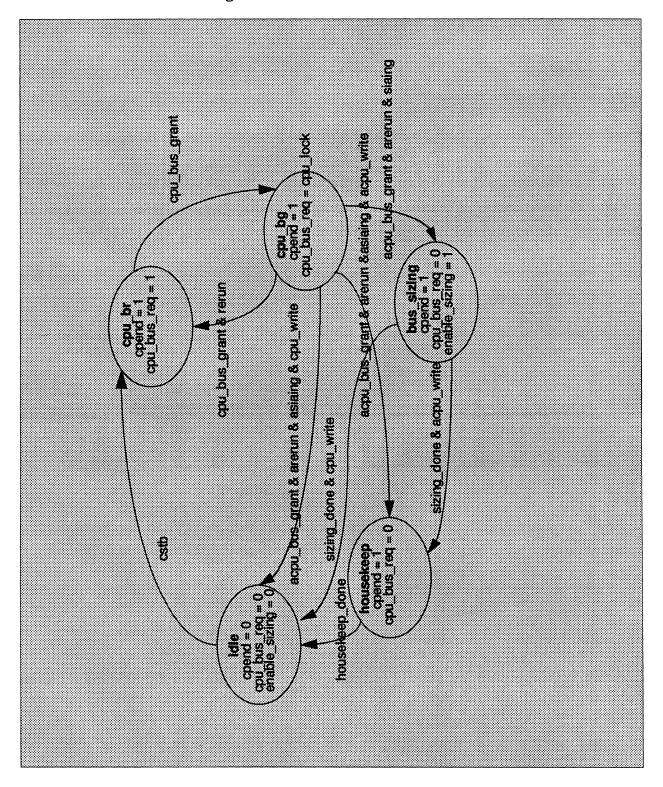

| CPU State Machine 106                                        |  |

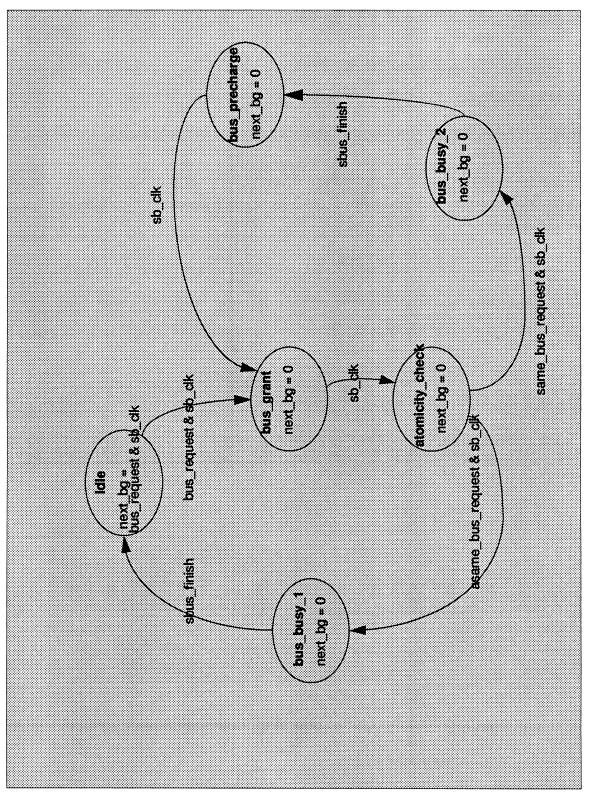

| Arbitor State Machine 109                                    |  |

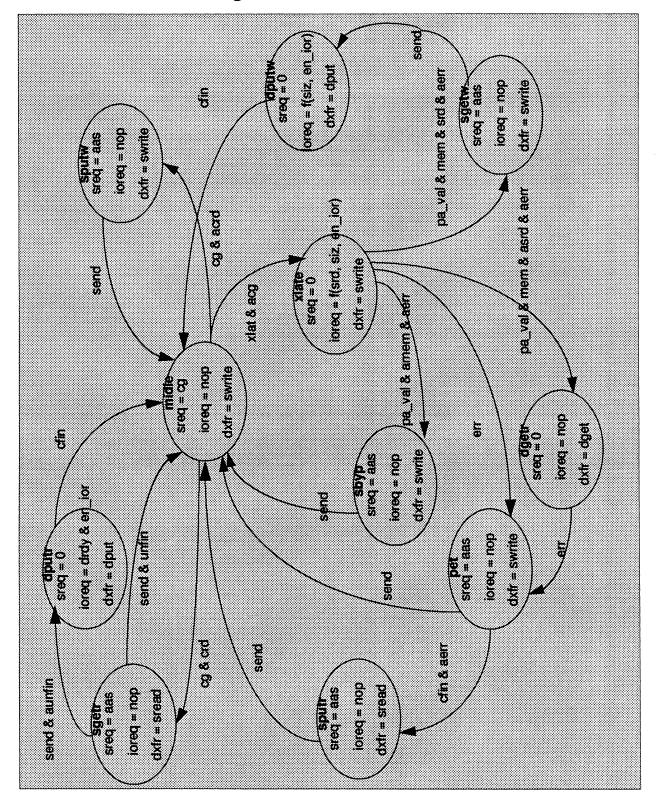

| Main State Machine 112                                       |  |

| D_ctl State Machine 113                                      |  |

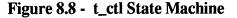

| S_ctl State Machine 115                                      |  |

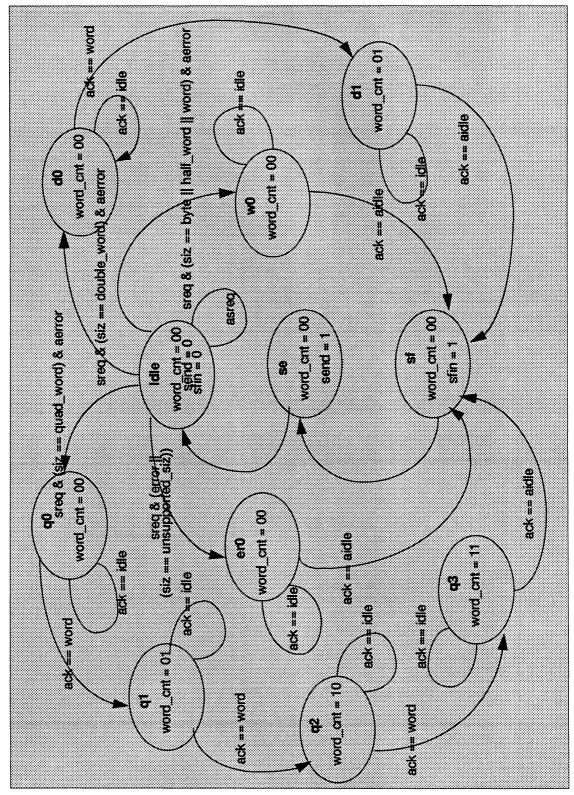

| t_ctl State Machine 116                                      |  |

| SBC Data Path 118                                            |  |

| microSPARC Reset State Machine 123                           |  |

| Clock Controller State Machine 126                           |  |

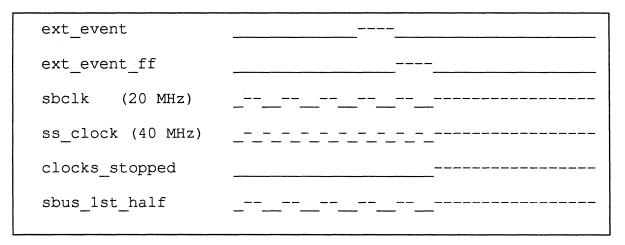

| Single Step with sbus_1st_half = 1 128                       |  |

| Single Step with sbus_1st_half = 0 128                       |  |

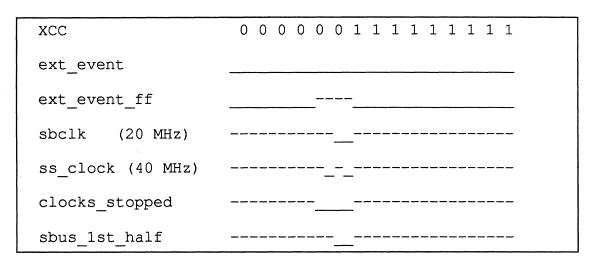

| With stop_on_ext_event                                       |  |

| With stop_even_on_ext_event                                  |  |

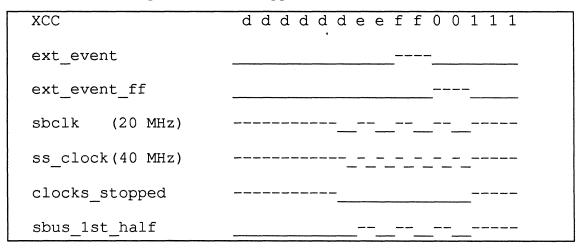

| N=2, stopped with sbus_1st_half=1                            |  |

| N=7, stopped with sbus_1st_half=0                            |  |

| N=7, stopped with sbus_1st_half=1133                         |  |

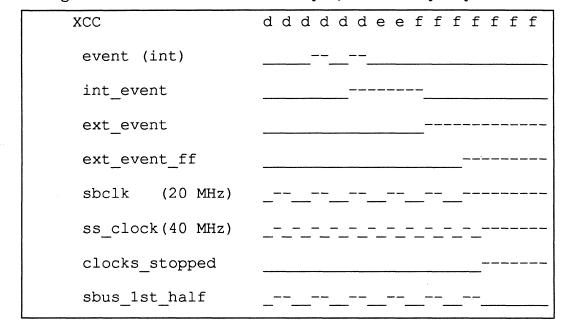

| Event in First half of bus cycle, N=8 135                    |  |

| Event in First half of bus cycle, N=8                        |  |

| Event in First half of bus cycle, N=9 137                    |  |

| Event in Second half of bus cycle, N=9                       |  |

| Event in first half of bus cycle, N=2. Latency=6 cycles      |  |

| Event in second half of bus cycle, N=2. Latency=5 cycles 140 |  |

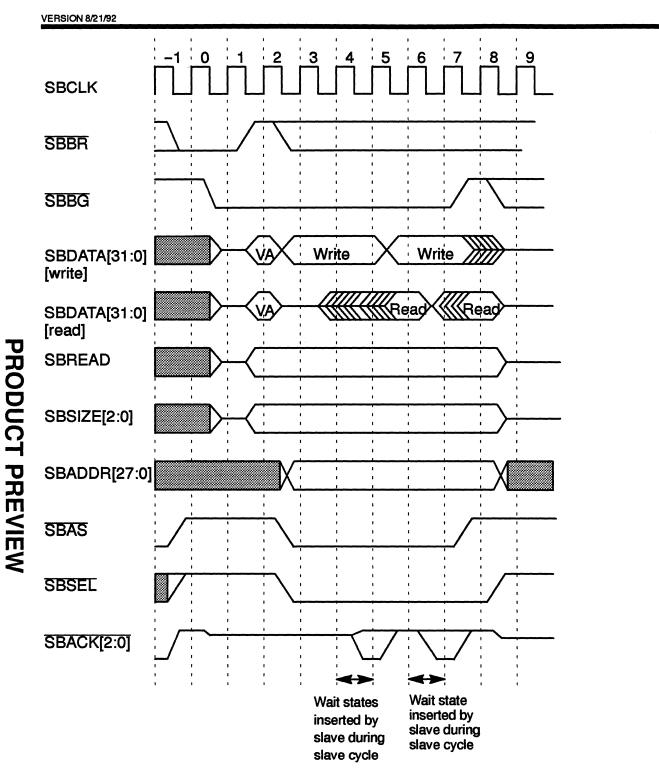

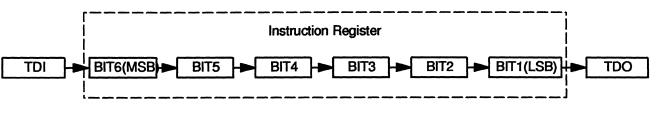

| JTAG ID Reg Contents 142                                     |  |

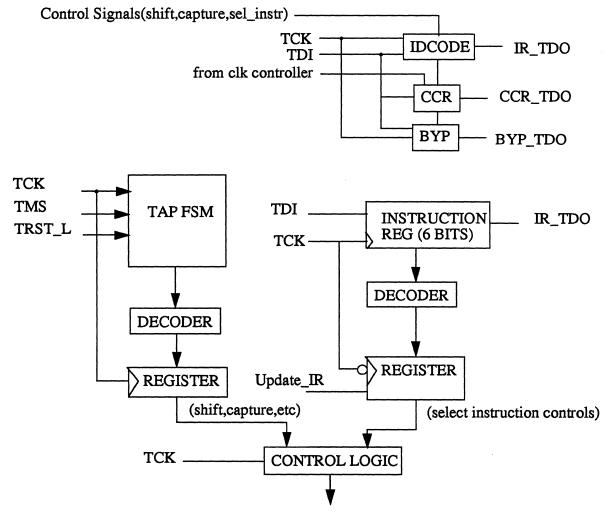

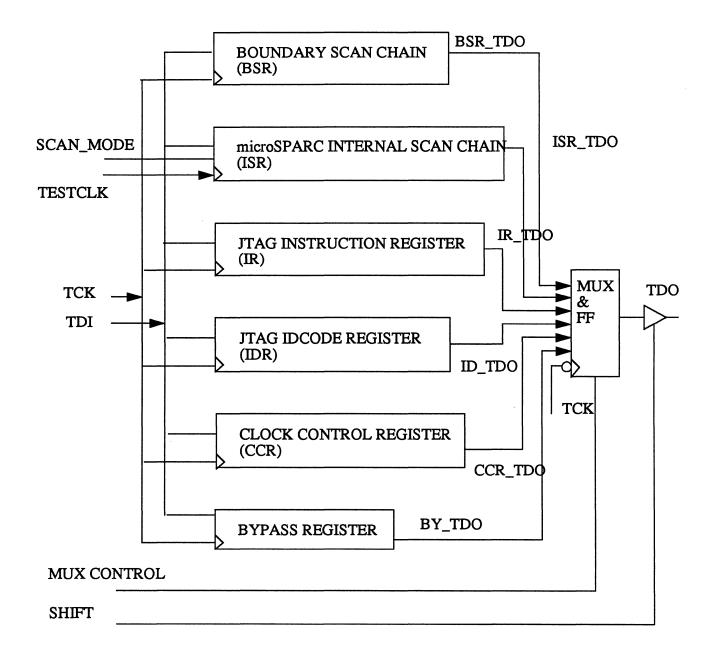

| JTAG LOGIC BLOCK DIAGRAM 148                                 |  |

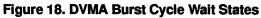

| microSPARC JTAG Data & Instruction Registers                 |  |

| TLB Flush or Probe Address Format                            |  |

| Instruction Cache Tag Entry156                               |  |

| Data Cache Tag Entry 157                                     |  |

## List of Tables

| FSR Summary24FPU Instruction Timings25Virtual Tag Match Criteria30Page Table Access Permissions31Page Table Entry Types32Sizes of Page Tables33Page Table Entry Types33Virtual Tag Match Criteria35TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59TLB Entry Address Mapping61 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Virtual Tag Match Criteria.30Page Table Access Permissions31Page Table Entry Types32Sizes of Page Tables33Page Table Entry Types33Virtual Tag Match Criteria35TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Fault Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                    |

| Page Table Access Permissions31Page Table Entry Types32Sizes of Page Tables33Page Table Entry Types33Virtual Tag Match Criteria35TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                |

| Page Table Entry Types32Sizes of Page Tables33Page Table Entry Types33Virtual Tag Match Criteria35TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                 |

| Sizes of Page Tables33Page Table Entry Types33Virtual Tag Match Criteria35TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                       |

| Page Table Entry Types33Virtual Tag Match Criteria35TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                             |

| Virtual Tag Match Criteria35TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                     |

| TLB Entry Flushing36CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                 |

| CPU TLB Entry Probing37Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                     |

| Address Map for MMU Registers38Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                                            |

| Memory Refresher Control Definition39Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                                                                           |

| Parity Control Definition40SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                                                                                                                |

| SFSR Level Field43SFSR Access Type Field43SFSR Fault Type Field43Setting of SFSR Fault Type Code44Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                                                                                                                                           |

| SFSR Access Type Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SFSR Fault Type Field                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Setting of SFSR Fault Type Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Overwrite Operations45Priority of Fault Types on Single Access45SBUS and IO MMU Control Space47IO MMU Page Table Address Generation48Memory Request Type53TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                                                                                                                                                                                                                                             |

| SBUS and IO MMU Control Space                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IO MMU Page Table Address Generation.48Memory Request Type.53TLB Reference Priority.59Translation Modes.59TLB Entry Address Mapping.61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Memory Request Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TLB Reference Priority59Translation Modes59TLB Entry Address Mapping61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Translation Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TLB Entry Address Mapping61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Virtual Address Match Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Virtual Address Field Enable Decode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Memory Request Type64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Data Cache Fill Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Address Map for Data Cache Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Instruction Cache Fill Ordering                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Memory operations performed by MCB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Physical Address decode for System Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Parity Control Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Refresh Rate Control bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Clock Control and Scan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| JTAG INSTRUCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Error Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ASI's Supported by microSPARC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TLB Entry Flushing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| CPU TLB Entry Probing                | 155 |

|--------------------------------------|-----|

| Address Map for MMU Registers        |     |

| Address Map for Data Cache Registers | 158 |

## Preface

This guide contains application information for the highly integrated SPARC processor, named the TMS390S10. Throughout this guide the term microSPARC is used to describe the TMS390S10 chip.

This User's Guide should be used in conjunction with the TMS390S10 data sheet. Where conflicts between these documents exist, particularly in reference to exact timings and frequency information, the TMS390S10 data sheet has precedence.

Revision 02 of 15 December 1992

.

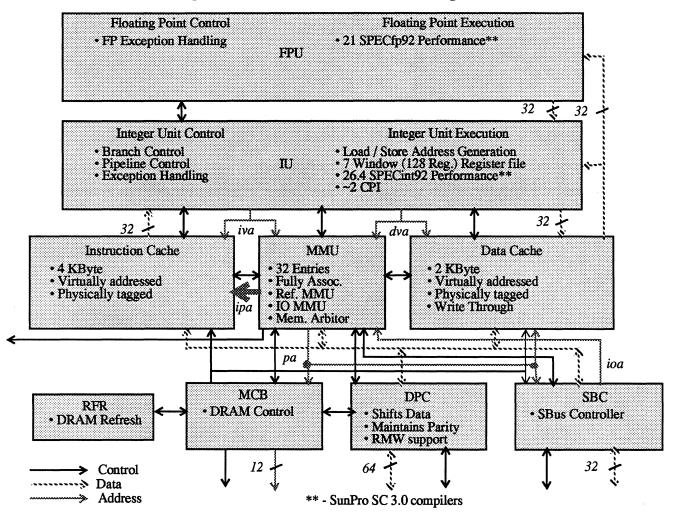

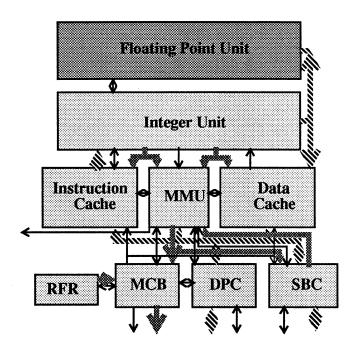

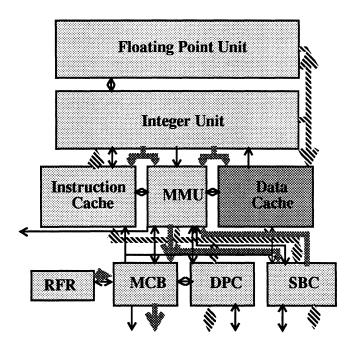

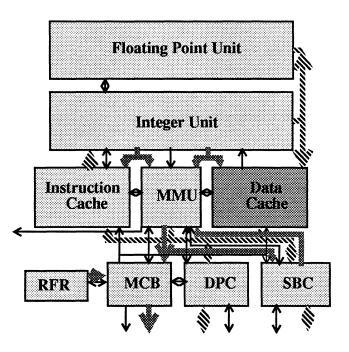

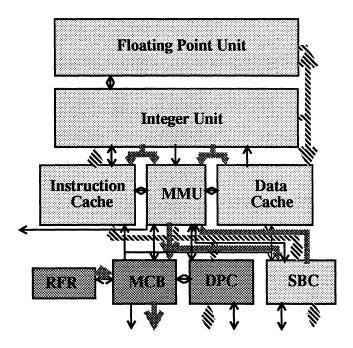

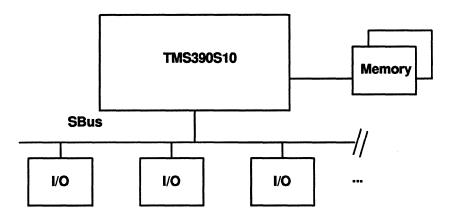

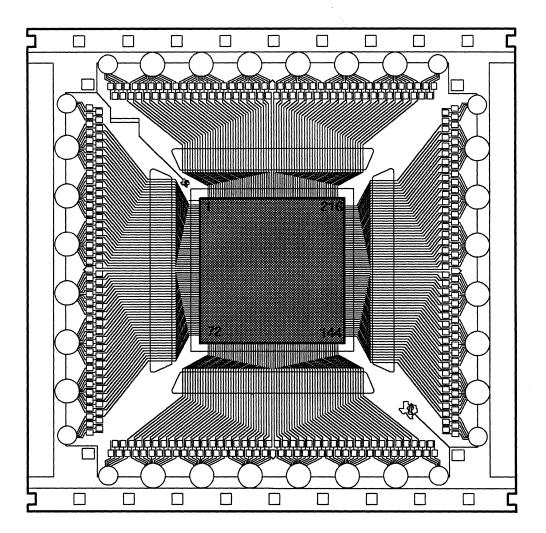

**1.0 Overview** The microSPARC CPU is a highly integrated, low-cost implementation of the SPARC RISC architecture. High performance is achieved by the high level of integration including on chip instruction and data caches and the close coupling of the CPU with main memory. A full custom implementation allows for a target frequency of 50 MHz providing sustained performance of 26.4 SPECint92 with SunPro SC 3.0 compilers. The design is highly testable with the use of the full JTAG scan support. The microSPARC chip will support up to 128MB of DRAM and 4 SBus slots.

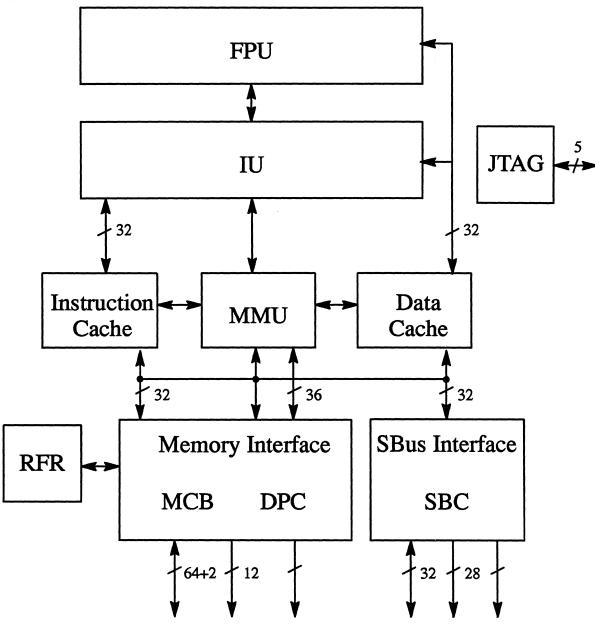

Integrated within microSPARC are a SPARC V8 Integer Unit core, a SPARC Reference Memory Management Unit, a Floating Point Unit, Instruction and Data Caches, DRAM controller, and an SBus Controller.

A simple block diagram follows.

Figure 1.0 - microSPARC Block Diagram

.

Revision 02 of 15 December 1992

4

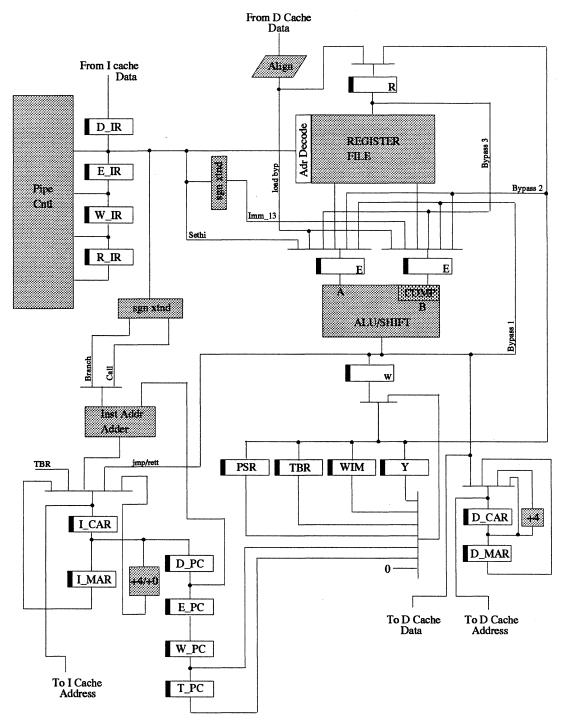

## 2.0 Integer Unit

The microSPARC integer unit is a SPARC integer unit as defined in the SPARC Architecture Manual (Version 8). The IU design goal is to maximize performance, given a constrained die size, using a predefined software architecture. The emphasis is on software compatibility, since the greatest cost impact would be on any software (i.e. kernel, compilers) that would need rewriting.

#### 2.0.1 Overview

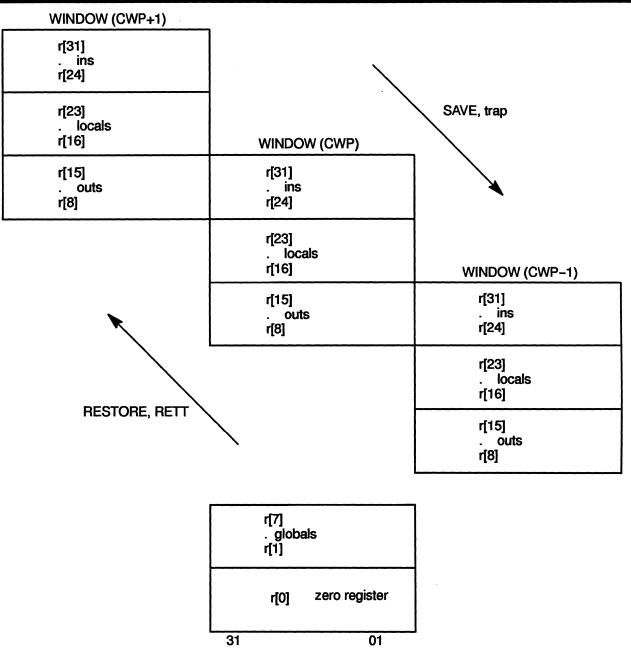

The microSPARC integer unit is a CMOS implementation of the SPARC 32-bit (Version 8) RISC architecture. Some important features of this design are:

- Single issue, 5 stage pipeline

- Harvard architecture

- Instruction and Data cache streaming support

- IMUL and IDIV implemented as integer operations

- 0 cycle branch penalty

- 120-register register file (7 register windows)

Figure 2.0 - microSPARC IU Block Diagram

6

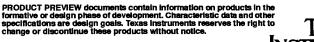

| 2.0.2 Instruction<br>Pipeline                                                                                                                                                     | 0 11                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |               |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|--|

|                                                                                                                                                                                   | F (Instruction Fetch): Inst<br>based on the address g<br>instruction is valid on<br>and are registered insi                                                                                                                                         | enerated in the pins of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ne previous c | ycle. The     |  |

|                                                                                                                                                                                   | to read the necessary of<br>register file or from in<br>2 independent read po<br>operand is in the pipel<br>register file, internal b<br>interlocks. In addition                                                                                    | D (Decode): The decode stage is used to decode the instruction and<br>to read the necessary operands. Operands may come from the<br>register file or from internal data bypasses. The register file has<br>2 independent read ports. For situations where the necessary<br>operand is in the pipeline and has not yet been written to the<br>register file, internal bypasses are supplied to prevent pipeline<br>interlocks. In addition, addresses are computed for CALL and<br>Branch in this cycle in the address adder. |               |               |  |

| E (Execute): The execute stage is used to perform ALU, logical,<br>shift operations. For memory operations (e.g.: LD) and for<br>JMPL/RETT the address is computed in this cycle. |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               | D) and for    |  |

|                                                                                                                                                                                   | W (Write): This stage is used to access the data cache. For cach<br>reads, the data will be valid by the end of this cycle, at whic<br>point it is aligned as appropriate. For cache writes, the data<br>presented to the data cache in this cycle. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               | cle, at which |  |

| R (Result): This stage writes the result of any ALU, logical, sl<br>cache read operation into the register file.                                                                  |                                                                                                                                                                                                                                                     | ogical, shift, or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |               |  |

| Table 2.0 - Cycles per Instruction                                                                                                                                                |                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | _             |               |  |

|                                                                                                                                                                                   | Instruction                                                                                                                                                                                                                                         | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Words         |               |  |

|                                                                                                                                                                                   | Call                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1             |               |  |

|                                                                                                                                                                                   | Single Loads                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1             |               |  |

|                                                                                                                                                                                   | Jump/Rett                                                                                                                                                                                                                                           | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1             |               |  |

|                                                                                                                                                                                   | Double Loads                                                                                                                                                                                                                                        | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1             |               |  |

| Instruction       | Cycles | Words |

|-------------------|--------|-------|

| Call              | 1      | 1     |

| Single Loads      | 1      | 1     |

| Jump/Rett         | 2      | 1     |

| Double Loads      | 2      | 1     |

| Single Stores     | 2      | 1     |

| Double Stores     | 3      | 1     |

| Taken Trap        | 3      | 1     |

| Atomic Load/Store | 2      | 1     |

| SWAP              | 2      | 1     |

| All Others        | 1      | 1     |

#### 2.0.3 Memory Operations 2.0.3.1 Loads

All load operations take 1 cycle in the microSPARC IU except for LDD which takes 2. For LD, LDB, and LDH the pipeline does the following:

- D Register operands are read from the register file or are bypassed from instructions still in the pipe. An immediate operand is sign extended.

- E Address operands are added to yield the memory address. This address is passed to the cache in this cycle.

- W Address is registered in the cache and access is started. Data is expected at the end of this cycle. Any necessary alignment and sign extension is done in the IU prior to being registered.

- R Data is registered in the IU and is written into the register file.

In the event of a cache miss, the miss indication is given to the IU in the R cycle. It is flagged early enough to prevent writing bad data to the register file. The pipe is held and the miss address is resent to the cache to service the miss. The cache indicates when the miss data is available - the IU can then register it into the appropriate R cycle register and write it into the register file.

An LDD takes 2 cycles to complete because of the 32 bit datapaths. The pipeline does the following:

- D Register operands are read from the register file or are bypassed from instructions still in the pipe. An immediate operand is sign extended.

- E Address operands are added to yield the even memory address. This address is passed to the data cache in this cycle.

- W (E2) Even memory address is registered in the cache and access is started. This data is sent to the IU. At the same time, the odd address is generated by the IU and sent to the cache.

- R (W2) Even word is registered in the IU and written to the register file. The odd word address is registered in the cache and its access is started. This data gets sent to the IU.

- R2 Odd word is registered in the IU and written to the register file.

In the event of a cache miss, the miss indication is in the R cycle of the LDD (the same as the W cycle of the LDD's help cycle). The miss is indicated early enough to prevent writing bad data into the even register. The pipe is held and the even address is resent to the cache. When the cache sends the correct data, the R register is written with the correct data and the odd address is resent to get the odd word.

8

| 2.0.3.2 Stores  | The microSPARC IU register file has only two independent read ports.<br>As a result, store operations take 2 cycles, except STD which takes 3.<br>For ST, STB, and STH the pipeline does the following:                                                                                                                      |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | D - Register operands are read from the register file or are bypassed from instructions still in the pipe. An immediate operand is sign extended.                                                                                                                                                                            |

|                 | E (D2) - The address operands are added to compute the memory<br>address. This address will be registered within the IU to provide<br>the data cache with the address in the correct cycle. At the same<br>time, the store data is read from the register file or bypassed from<br>instructions still in the pipe.           |

|                 | W (E2) - The store address is sent to the data cache.                                                                                                                                                                                                                                                                        |

|                 | R (W2) - The store data is sent to the data cache in this cycle along with the appropriate byte marks.                                                                                                                                                                                                                       |

|                 | R2 - Store is complete.                                                                                                                                                                                                                                                                                                      |

|                 | For STD the pipeline does the following:                                                                                                                                                                                                                                                                                     |

|                 | D - Register operands are read from the register file or are bypassed from instructions still in the pipe. An immediate operand is sign extended.                                                                                                                                                                            |

|                 | E (D2) - The address operands are added to compute the even<br>memory address. This address will be registered within the IU to<br>provide the data cache with the address in the correct cycle. At<br>the same time, the even store data is read from the register file or<br>bypassed from instructions still in the pipe. |

|                 | W (E2/D3) - Even address is sent to the data cache. Odd word is read from register file.                                                                                                                                                                                                                                     |

|                 | R (W2/E3) - Even store data is sent to the data cache. Odd address is sent to the data cache.                                                                                                                                                                                                                                |

|                 | R2 (W3) - Odd data is sent to the data cache.                                                                                                                                                                                                                                                                                |

|                 | R3 - STD complete.                                                                                                                                                                                                                                                                                                           |

| 2.0.3.3 Atomics | SWAP and LDSTUB each take two cycles to complete. The pipeline does the following on the SWAP instruction:                                                                                                                                                                                                                   |

|                 | D - Register operands are read from the register file or are bypassed from instructions still in the pipe. An immediate operand is sign extended.                                                                                                                                                                            |

|                 | E (D2) - The address operands are added to compute the swap<br>address. This address is sent to the data cache to start the cache<br>read portion of the operation. The address is also registered<br>inside of the IU to provide the data cache with the same address                                                       |

for the store in the next cycle. The register to be swapped is read out in this cycle.

- W (E2) The data cache returns the memory location accessed. The store address is sent to the data cache.

- R (W2) The IU registers the read data and writes it to the register file. Also the store data is sent to the data cache.

- R2 SWAP complete.

The pipeline does the following on the LDSTUB instruction:

- D Register operands are read from the register file or are bypassed from instructions still in the pipe. An immediate operand is sign extended.

- E (D2) The address operands are added to compute the ldst address. This address is sent to the data cache to start the cache read portion of the operation. The address is also registered inside of the IU to provide the data cache with the same address for the store in the next cycle.

- W (E2) The data cache returns the memory location accessed and it is shifted appropriately inside the IU. The store address is sent to the data cache.

- R (W2) The IU registers the read data and writes it to the register file. Also 0xffffffff is sent to the data cache along with the appropriate byte marks to complete the store.

- R2 LDSTUB complete.

Most ALU and shift operations take a single cycle to complete. The exceptions are Integer Multiply and Integer Divide. On Add, Subtract, Boolean, and Shift operations the pipeline does the following:

- D Read operands from register file or bypass from instructions still in the pipe.

- E Do appropriate operation in ALU or shifter. There is a selective inverter on the B input of the ALU to allow for subtracts and certain Boolean operation (e.g. ANDN).

- W Pipe result into R.

- R Write register file with result.

#### 2.0.5 Integer Multiply

2.0.4 ALU/Shift

**Operations**

Integer multiply takes 19 cycles to complete. The algorithm implemented in the microSPARC IU is a modified Booth's (2-bit) multiply. The multiply process can be broken up into 4 distinct steps:

Initialization Booth's iteration 1 cycle 16 cycles

| Correction (ala Booth) | 1 cycle |

|------------------------|---------|

| Writeback              | 1 cycle |

The first cycle is used to set up the registers used in the multiply. The rs1 and rs2 registers initialize to the operands of the multiply. The W stage result register and the rs2 register are used as accumulators. At the completion of the multiply, the W register contains the most significant 32 bits of the result and the rs2 register contains the least significant 32 bits of the result. The W register contents are then written to the Y register and the rs2 contents to the destination register in the register file.

Integer divide takes 39 cycles to complete. If an overflow is detected, the instruction completes in 6 cycles. The algorithm implemented in the microSPARC IU is non-restoring binary division (add and shift). The divide process can be broken into 5 distinct steps:

| Divide by zero detection         | 1 cycle   |

|----------------------------------|-----------|

| Initialization/Ovf detection     | 3 cycles  |

| Non-restoring division iteration | 33 cycles |

| Correction (for non-restoring)   | 1 cycle   |

| Writeback                        | 1 cycle   |

Because the microSPARC IU does not allow traps to be taken by help instructions, the first step is to determine if we have a divide by 0 condition.

The high order bits of the dividend are in the Y register. The low order bits are in the rs1 operand. The divisor is in the rs2 operand. In the initialization step, the Y register is read out and put into the rs1 register in the datapath. The rs1 operand is passed through to the W register. The rs2 operand is passed to the rs2 register (surprise!). The W and rs1 registers are used as accumulators. At the completion of the divide, the W register contains the final quotient.

There are two overflow options for signed divide with a negative result defined in the SPARC Version 8 manual. The microSPARC IU implements:

result  $< -2^{31}$  with remainder = 0.

If an overflow condition is detected, the divide terminates early with the appropriate result being written to the destination register.

If no overflow is detected, the non-restoring (add then shift) divide stage is started. A correction step is provided to correct the quotient (necessary for this algorithm). After the correction step, the quotient is written to the correct destination register.

#### 2.0.6 Integer Divide

| 2.0.7 CTI's      |                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.0.7.1 Branches | All branches take a single cycle to execute. There is no penalty for taken<br>vs. untaken branches, even in the event that the instruction previous to<br>the branch sets the condition codes.                                                                                                                                                                                                                             |

|                  | In the Decode stage, the IU evaluates the condition codes and branch<br>condition to determine taken or untaken. The IU outputs the correct<br>instruction address for either the target or fall through paths in time to<br>be registered by the instruction cache for the fetch occurring in the next<br>cycle.                                                                                                          |

| 2.0.7.2 JMPL     | JMPL is a two cycle instruction in the microSPARC IU. This is done<br>somewhat uniquely in that there are no help cycles for the JMPL.<br>Instead, there is an interlock that always occurs following the JMPL.<br>This is done to force the IU to fetch the JMPL's delay instruction. In this<br>way, the IU can evaluate whether an RETT is in the JMPL's delay slot<br>and evaluate user/supervisor accesses correctly. |

|                  | D - Read operands from register file or bypass from instructions still<br>in the pipe. Sign extend immediate operands. The delay slot<br>instruction is fetched in this cycle.                                                                                                                                                                                                                                             |

|                  | E - Compute target address and send this to the instruction cache.                                                                                                                                                                                                                                                                                                                                                         |