Part Number 800-1190-01 Revision: 50 of 1 July 1985

#### Hardware Reference Manual

for the

### **Sun Graphics Processor**

Sun Microsystems, Inc., 2550 Garcia Avenue, Mountain View, California 94043 (415) 960-1300

#### Credits and Trademarks

Multibus is a trademark of Intel Corporation.

Sun Microsystems and Sun Workstation are registered trademarks of Sun Microsystems, Incorporated. Sun-2, Sun-2/xxx, Deskside, SunStation, SunCore, SunWindows, and DVMA are trademarks of Sun Microsystems, Incorporated.

UNIX is a trademark of AT&T Bell Laboratories.

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

#### Copyright © 1985 by Sun Microsystems, Inc.

This publication is protected by Federal Copyright Law, with all rights reserved. No part of this publication may be reproduced, stored in a retrieval system, translated, transcribed, or transmitted, in any form, or by any means manual, electric, electronic, electro-magnetic, mechanical, chemical, optical, or otherwise, without prior explicit written permission from Sun Microsystems.

### Contents

| Chapter 1 Introduction                                      |              |

|-------------------------------------------------------------|--------------|

| Chapter 2 System Configuration                              | 7            |

| Chapter 3 Functional Description                            | 13           |

| Chapter 4 Detailed Description                              | 19           |

| Chapter 5 VME Interface                                     | 41           |

| Chapter 6 Internal Registers                                | 51           |

| Chapter 7 Microcode Format                                  |              |

| Appendix A Graphics Processor/Graphics Buffer Specification | ns <b>89</b> |

## Contents

| Preface                              | xiii |

|--------------------------------------|------|

| Chapter 1 Introduction               | 3    |

| 1.1. Overview                        | 3    |

| Chapter 2 System Configuration       | 7    |

| 2.1. Overview                        | 7    |

| Chapter 3 Functional Description     | 13   |

| 3.1. Overview                        | K    |

| 3.2. Viewing Processor               | 13   |

| 3.3. Painting Processor              | 14   |

| 3.4. Graphics Buffer Board           | 14   |

| 3.5. Summary                         | 15   |

| Chapter 4 Detailed Description       | 19   |

| 4.1. Overview                        | 19   |

| 4.2. Microstore                      | 21   |

| 4.3. Viewing Processor               | 22   |

| Program Sequencer and Program Memory | 24   |

| Branch Register                      | 24   |

| Instruction Register Buffer          | 24   |

| n Register                           | 25   |

| Interprocessor Flags                 | 25   |

| Status Flags Register                | 25   |

| FIFO                                        |    |

|---------------------------------------------|----|

| Shared Memory                               |    |

| VP PROM and VP PROM POINTER                 |    |

| 4.4. Floating Point Circuitry               |    |

| Overview of the Floating Point Circuitry    |    |

| Floating Point Registers                    |    |

| Weitek Floating Point Chips                 |    |

| 4.5. Painting Processor                     |    |

| Branch Register                             |    |

| Condition Code Select                       |    |

| Scratchpad Memory and Scratchpad Pointer    |    |

| Interrupt ID Register                       |    |

| VME Bus Interface Logic                     |    |

| Graphics Buffer Memory                      |    |

| AM29L517 Integer Multiplier                 |    |

| Mode Register                               |    |

| PP PROM                                     |    |

|                                             |    |

| Chapter 5 VME Interface                     | 41 |

| 5.1. Overview                               |    |

| 5.2. Microstore Interface                   |    |

| 5.3. Shared Memory                          |    |

| 5.4. VME Bus Addressing (GP as a VME Slave) |    |

| Microstore Interface Registers              |    |

| Shared Memory                               |    |

| 5.5. Microstore Interface Register Formats  |    |

| Board Identification                        |    |

| GP Control Register                         |    |

| GP Status Register                          |    |

| Microstore Address Register                 |    |

| Microstore Data Register                    |    |

| 5.6. VME Interrupts                         |    |

|                                             |    |

| Chapt | er 6 Internal Registers                  | 51 |

|-------|------------------------------------------|----|

|       | Viewing Processor                        | 51 |

|       | Shared Memory Pointer                    | 51 |

|       | Source A, Source B, Destination Pointers | 51 |

|       | VP PROM Pointer                          | 51 |

|       | Floating Point Status Register           | 51 |

|       | n Register                               | 52 |

|       | Interprocessor Flag #1 Register          | 52 |

|       | Interprocessor Flag #2 Register          | 53 |

|       | Status Flags/LED Register                | 53 |

|       | Branch Register                          | 54 |

|       | Shared Memory                            | 54 |

|       | Floating Point Registers                 | 54 |

|       | VP PROM Registers                        | 54 |

|       | FIFO Registers                           | 55 |

|       | 29116 Registers                          | 55 |

| 6.2.  | Painting Processor                       | 56 |

|       | Scratchpad Pointer                       | 56 |

|       | Graphics Buffer Address Pointers         | 56 |

|       | VME Control Register                     | 57 |

|       | VME Status Register                      | 57 |

|       | VME Address Registers                    | 58 |

| -     | Interrupt ID Register                    | 58 |

|       | PP PROM Pointer                          | 58 |

|       | Multiplier Mode Register                 | 58 |

|       | n Register                               | 59 |

|       | Interprocessor Flag #2 Register          | 60 |

|       | Interprocessor Flag #1 Register          | 60 |

|       | Status Flag/LED Register                 | 60 |

|       | Branch Register                          | 60 |

|       | Scratchpad Memory                        | 61 |

|       | GB Data Registers                        | 61 |

|       | VME Data Registers                       | 61 |

| PP PROM Registers                              |  |

|------------------------------------------------|--|

| Multiplier X, Y, and Result Registers          |  |

| FIFO Registers                                 |  |

| 29116 Registers                                |  |

| Chapter 7 Microcode Format                     |  |

| 7.1. Viewing Processor Microcode               |  |

| AM29116 Instruction                            |  |

| Miscellaneous Controls                         |  |

| Source and Destination                         |  |

| Hardware Protection                            |  |

| Branch Logic                                   |  |

| Count Hardware                                 |  |

| General Field                                  |  |

| Floating Point                                 |  |

| 7.2. Painting Processor Microcode              |  |

| AM29116 Instruction                            |  |

| Miscellaneous Controls                         |  |

| Source and Destination                         |  |

| Hardware Protection                            |  |

| Branch Logic                                   |  |

| Count Hardware                                 |  |

| General Field                                  |  |

| Graphics Buffer Board Memory (Graphics Buffer) |  |

## Tables

| Table 1 | Sun Documentation    | xiv |

|---------|----------------------|-----|

| Table 2 | Vendor Documentation | xv  |

## Figures

t

تو :

| Figure 2-1 | Sun-2/160 Color Workstation: System-Level View | 8  |

|------------|------------------------------------------------|----|

| Figure 2-2 | Block Diagram of the Graphics Processor        | Ŷ  |

|            |                                                |    |

| Figure 4-1 | The Microstore                                 | 20 |

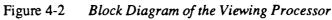

| Figure 4-2 | Block Diagram of the Viewing Processor         | 23 |

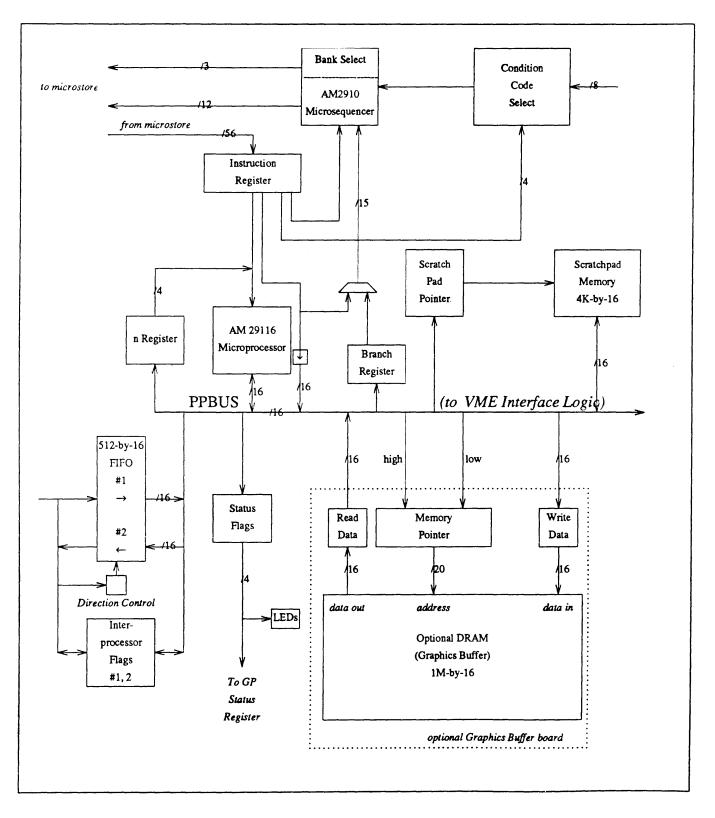

| Figure 4-3 | Painting Processor Block Diagram — Part 1      | 30 |

| Figure 4-4 | Painting Processor Block Diagram — Part 2      | 31 |

|            |                                                |    |

### Preface

|                     | Welcome to the Sun-2 Graphics Processor. This manual presents a description of the Graphics Processor hardware <i>from a programmer's point of view</i> : that is, sufficient for a programmer to be able to understand the workings of the board.                                                         |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary of Contents | This manual has seven chapters and an appendix:                                                                                                                                                                                                                                                            |

| Chapter 1           | Introduction — contains a basic overview of the the Graphics Processor, its position in the Sun-2 architecture, and associated Graphics Buffer board.                                                                                                                                                      |

| Chapter 2           | System Configuration — presents a simplified block diagram of the Graphics Processor and Graphics Buffer boards.                                                                                                                                                                                           |

| Chapter 3           | Functional Description — gives a functional description of the Viewing Processor, Painting Processor, and Graphics Buffer board.                                                                                                                                                                           |

| Chapter 4           | Detailed Description — gives a fairly detailed description of the circuitry intro-<br>duced in Chapter 3.                                                                                                                                                                                                  |

| Chapter 5           | VME Interface — describes the interface between the Graphics Processor and the rest of the Sun-2 Model 160.                                                                                                                                                                                                |

| Chapter 6           | Internal Registers — describes the format of the registers associated with the Viewing Processor and the Painting Processor.                                                                                                                                                                               |

| Chapter 7           | <i>Microcode Format</i> — describes the microcode instruction format for both the Viewing Processor and the Painting Processor. It also describes hardware implementations, and limitations of which the microcoder must be aware.                                                                         |

| Appendix A          | Specifications — gives VME and Performance specifications for the GP and GB boards.                                                                                                                                                                                                                        |

|                     | Finally, to help us maintain the currency and accuracy of this material we have<br>supplied a reader comment sheet at the end of this guide. Please use the com-<br>ment sheet to list errors and omissions. Your responses will help a great deal in<br>our efforts to keep our documentation up to date. |

| Glossary             | A few terms are used throughout this document which, without explanation, may seem confusing.                                                                                                                                                                                                                                                                                   |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                      | Positive Logic — positive logic means that the asserted level (see below) of<br>a signal is a logic 1 (see below also).                                                                                                                                                                                                                                                         |

|                      | <ul> <li>Asserted — when we say that a signal is "asserted," we mean that it is in<br/>its active, or true, state. In positive logic this means that a signal like<br/>READ, when asserted, is equal to its most positive state. When a signal like<br/>WRITE*, WRITE-, or WRITE\ (the three are synonymous) is asserted it is<br/>equal to its most negative state.</li> </ul> |

|                      | Logic 1 — in positive logic, a logic 1 stands for the more positive of the two<br>voltage levels. A logic 1 in negative logic stands for the more negative of<br>the two voltage levels.                                                                                                                                                                                        |

|                      | Logic 0 — in positive logic, a logic 0 stands for the more negative of the<br>two voltage levels. A logic 0 in negative logic stands for the more positive<br>of the two voltage levels.                                                                                                                                                                                        |

|                      | Set — means the same as logical 1.                                                                                                                                                                                                                                                                                                                                              |

|                      | □ Clear — means the same as a logical 0.                                                                                                                                                                                                                                                                                                                                        |

| Applicable Documents | We emphasize that this manual outlines rather than exhausts many of the topics<br>contained within. References to applicable documents supplied with your system<br>are given throughout; however, and we urge you to read these documents should<br>you need further information.                                                                                              |

| Table 1              | Sun Documentation                                                                                                                                                                                                                                                                                                                                                               |

| Sun Part Number | Description                           |

|-----------------|---------------------------------------|

| 800-1191        | Graphics Processor Engineering Manual |

#### Table 2Vendor Documentation

| Description                                              |

|----------------------------------------------------------|

| AMD Bipolar Microprocessor Logic and Interface Data Book |

| AMD Bipolar/MOS Memory Data Book                         |

| Fairchild Advanced Schottky TTL (FAST) Data Book         |

| Texas Instruments ALS/AS Logic Circuits Data Book        |

| Programmable Array Logic (PAL) Data Book                 |

| Weitek 1032/1033 floating-point processor data sheet     |

| 4501 FIFO data sheet                                     |

| VMEbus Specification                                     |

## Introduction

| Introduction  | 3 |

|---------------|---|

|               |   |

| 1.1. Overview | 3 |

1

#### Introduction

1.1. Overview

This manual describes the Graphics Processor (GP) board and the Graphics Buffer (GB) boards. The Graphics Processor is an attached processor to the host processor and can be used to perform many image display tasks. Since the Graphics Processor is faster than and runs in parallel with the host processor, there is a significant increase in system performance.

Floating point performance is a significant limiting factor to graphics performance. Since floating point performance is not suitable for interactive graphics, the intent of the GP is to provide a unit—separate from but controllable by the host processor—which has the necessary performance. It is a microprogrammable unit which, when invoked by the host processor, assists in the execution of a pre-defined task such as transforming, clipping, scaling, and rendering a two- or three-dimensional object.

#

## System Configuration

| System Configuration | 7 |

|----------------------|---|

|                      |   |

| 2.1. Overview        | 7 |

### System Configuration

#### 2.1. Overview

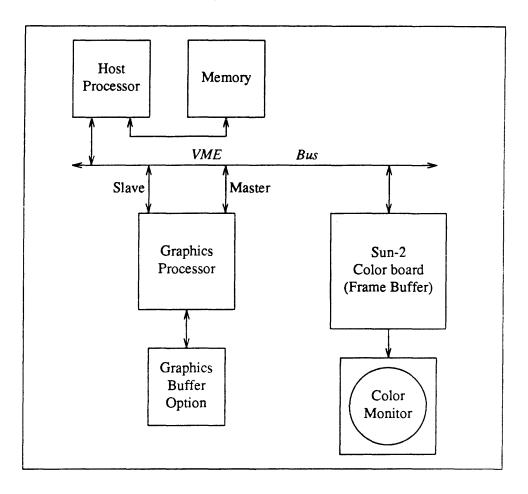

The following figure shows a simplified block diagram of a Sun color workstation with a Graphics Processor attached. The GP is either a one or two board set:

- the basic GP board, and

- an optional Graphics Buffer board.

Each board uses the triple high, quad depth (366.67mm by 400mm) Eurocard form factor.

Figure 2-1 Sun-2/160 Color Workstation: System-Level View

The VME bus is used as both the system bus and the graphics bus. The host processor passes commands and parameters to the GP which processes them and writes pixels into the Color board. Even though the GP is logically between the host processor and the Color board, the GP and Color board can be installed in any VME slots. The GP and GB (Graphics Buffer) boards, however, must be installed in adjacent VME slots with a private bus between them.

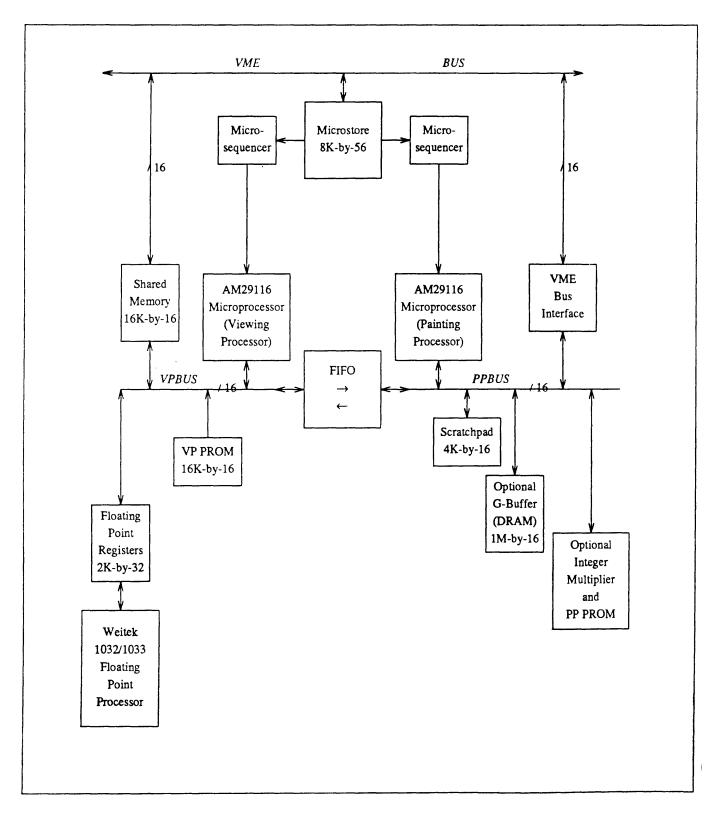

A more detailed block diagram of the GP board is shown in the next figure. As can be seen, the GP contains three interfaces to the VME bus. The shared memory and the microstore interface are bus slaves, used primarily to load commands/parameters and to load microcode, respectively. The third interface ("VME Bus Interface") provides a general-purpose bus master capability, used primarily to access the Color board.

Figure 2-2 Block Diagram of the Graphics Processor

The shared memory is a dual-ported, high-speed, static RAM (random access memory), accessible from the VME bus by the processors on the GP board. (These are described in more detail in the next chapter.) Using the VME bus as the system bus, the host processor can load commands and data into the shared memory and receive requested status and data from the same memory.

The VME bus can also be viewed as the graphics bus, since the GP uses this bus to access pixels in the Color board's frame buffer. (The GP can access any VME location in standard or I/O (input/output) address space.) Providing a general-purpose VME connection on the Color board rather than a dedicated GP-to-Color board connection allows you to have a color workstation without a GP. It also allows direct access to the Color board by the host processor or other devices even with the GP installed.

# 3

## Functional Description

| Functional Description     | 13 |

|----------------------------|----|

| 3.1. Overview              |    |

| 3.2. Viewing Processor     | 13 |

| 3.3. Painting Processor    | 14 |

| 3.4. Graphics Buffer Board | 14 |

| 3.5. Summary               | 15 |

#### **Functional Description**

#### 3.1. Overview

3.2. Viewing Processor

Referring again to the block diagram of the Graphics Processor (shown previously), the GP consists of three processors:

two Advanced Micro Devices (AMD) 29116 microprocessors, and

a Weitek 32-bit floating point processor chip set, the 1032/1033.

The AM29116 is a 10MHz, 16-bit Arithmetic and Logic Unit (ALU) which evolved from bit-slice technology. The Weitek chips consist of an ALU (add, subtract, data format conversions) and multiplier, each capable of 1.1 Mflops in flowthrough mode and 5 Mflops in pipeline mode. Further details on these processors are available in the vendors' documentation.

The programs for the GP are contained within the microstore. This memory is three-ported, readable by each AM29116 section and readable/writable via the VME microstore interface, and is configured as 8K of 56-bit words.

As shown in the block diagram, the GP consists of two sections: The Viewing Processor (VP) and the Painting Processor (PP). These two processors form a pipeline for the execution of graphic commands. A brief discussion of each section's components follows.

The first AM29116, with the attached floating point processor and registers, is called the Viewing Processor. Its function is to receive commands and parameters from the host processor and perform the floating point operations needed to transform the image from world coordinates into screen coordinates.

Shared memory was mentioned in the previous chapter. It is implemented with sixteen 16K-by-1 static RAM chips providing a 16K-by-16 memory. This memory is time-multiplexed allowing independent access from both the VME bus and the Viewing Processor (VPBUS).

Graphic operations are floating point intensive; hence the floating point processor and associated registers. The floating point processor can be configured in a pipeline mode which allows a floating point operation to be initiated every two cycles. This unit is used to transform, clip, and scale the graphic data from world coordinates to screen coordinates. Maximum floating point performance is 4.16 Mflops.

The VP PROM (programmable read only memory) is used for the storage of reciprocal estimates and other constants needed for numerical computations. For

example when calculating a reciprocal, the PROM is used as a look-up table containing the first estimate for the iterative reciprocal algorithm.

The FIFO (first in first out) buffer is used to transfer commands and data from the Viewing Processor to the Painting Processor. Under control of the Viewing Processor, the FIFO can be reversed allowing the Painting Processor to send data to the Viewing Processor. The FIFO size is 512 16-bit words. It is the FIFO which logically and physically separates the GP into the Viewing Processor and the Painting Processor.

3.3. Painting Processor The second AM29116 section is termed the Painting Processor. Its function is to render the graphic data (pixels) into the frame buffer on the Color board. The components discussed below are shown in the block diagram of the Graphics Processor board.

The scratchpad memory is a fast access, static RAM. Sequential accesses to this memory can be done in single cycles. The memory size is 4K-by-16. The scratchpad is a general-purpose memory useful for various algorithms.

The VME interface logic provides the capability to access VME devices from the Painting Processor, primarily the frame buffer on the Color board. However, the logic is general-purpose and any VME location can be accessed, including host memory and the GP's shared memory. In addition, this logic allows the GP to generate an interrupt to the host processor. This interrupt is under direct micro-code control allowing its use to be defined by the particular application.

#### 3.4. Graphics Buffer Board

The optional GB board contains a large memory implemented with dynamic RAM (DRAM) chips. The size of the memory is 1M 16-bit words (1M = 1,048,576). Dynamic RAMs provide large amounts of memory at slower access times. Random accesses to the DRAM take five cycles (two cycles to load the 21-bit address and three cycles to do the read or write) but sequential reads or sequential writes can be done in three cycles per read or write.

- A *fill* mode allows a data word to be written into four consecutive locations in the time required to do one write.

- A read/modify/write mode allows a write followed by a read of the next consecutive address to be done in five cycles.

This memory is designed to be general-purpose (font storage, anti-aliasing use, etc.) but is especially suitable for hidden surface elimination algorithms.

Also on the optional GB board are an integer multiplier and associated PROM for numerical constant storage. An AMD 29L517 chip is the multiplier chip used; a multiply of two 16-bit operands producing a 32-bit result takes six cycles (including data transfer cycles). This multiply capability greatly speeds up the performance of advanced shading algorithms.

# 3.5. Summary The pipeline architecture of the GP is well suited for graphics applications. Graphic data are manipulated serially and independently; therefore, partitioning the tasks for pipelining is straightforward. The intent is to divide the task so that all three stages of the pipeline—the host processor, the Viewing Processor, and the Painting Processor—are active as much as possible. The parallelism thus achieved will permit high performance graphics.

# 4

## Detailed Description

| Detailed Description                     | 19 |

|------------------------------------------|----|

| 4.1. Overview                            | 19 |

| 4.2. Microstore                          | 21 |

| 4.3. Viewing Processor                   | 22 |

| Program Sequencer and Program Memory     | 24 |

| Branch Register                          | 24 |

| Instruction Register Buffer              | 24 |

| n Register                               | 25 |

| Interprocessor Flags                     | 25 |

| Status Flags Register                    | 25 |

| FIFO                                     | 25 |

| Shared Memory                            | 26 |

| VP PROM and VP PROM POINTER              | 26 |

| 4.4. Floating Point Circuitry            | 27 |

| Overview of the Floating Point Circuitry | 27 |

| Floating Point Registers                 | 28 |

| Weitek Floating Point Chips              | 28 |

| 4.5. Painting Processor                  | 29 |

| Branch Register                          | 32 |

| Condition Code Select                    | 32 |

| Scratchpad Memory and Scratchpad Pointer | 32 |

| Interrupt ID Register                    | 33 |

| VME Bus Interface Logic                  | 33 |

| Graphics Buffer Memory      | 35 |

|-----------------------------|----|

| AM29L517 Integer Multiplier | 37 |

| Mode Register               | 37 |

| PP PROM                     | 37 |

#### **Detailed Description**

4.1. Overview

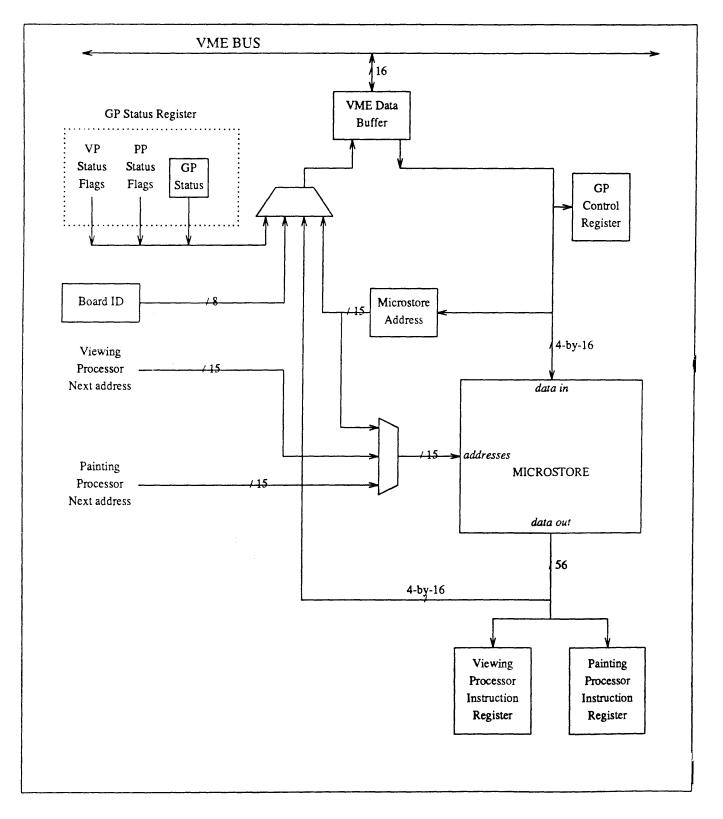

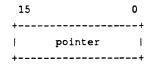

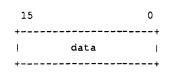

The Graphics Processor is actually two separate units, the Viewing Processor and the Painting Processor, with both processors sharing the microstore. The figure below details the common microstore. Subsequent figures contain detailed block diagrams of the two processors. The discussion below describes these block diagrams and the operational details of the processors.

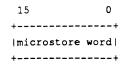

Figure 4-1 The Microstore

Both processors can be viewed as programmable state machines running with a 120 nanosecond cycle time. During each cycle several parallel operations are possible. On the Viewing Processor for example,

- an AM29116 instruction can be executed;

- a floating point operation performed;

- □ a branch executed;

- and a data word moved from a VPBUS source to a VPBUS destination.

Similarly, on the Painting Processor,

- an AM29116 instruction can be executed;

- □ a VME operation initiated;

- a branch executed; and

- a data word moved from a PPBUS source to a PPBUS destination.

The current operation of each processor is controlled by the current contents of each processor's instruction register, containing a microinstruction. The microinstruction format has been chosen to provide as much parallelism as possible within physical constraints (board area, power, etc.)

#### 4.2. Microstore

The microstore contains the microcode for both GP processors. The two units run 180 degrees out-of-phase and require half of the memory bandwidth; thus the microstore can be shared. A third port into memory is available for VME accesses into the microstore (initial program load and verification) but can be active only when the two processors are halted.

The microstore is built with fast, static RAMs. Twenty-eight physical RAM locations are provided and 8K of microstore (using 4K-by-4 chips) is available.

Contained in the block diagram of the microstore is:

- □ the microstore,

- each processor's next address source and instruction register,

- the microstore registers accessible from the VME.

The microstore registers reside in the first 32 Kbytes of VME address space allocated to the GP. (This allocation is determined by a hardware switch on the GP.) Shared memory resides in the next 32 Kbytes.

For each processor, the first half of each cycle is used to determine the address of the next microinstruction. In the second half-cycle, this next address is routed to the microstore, an access is made, and the instruction register is loaded at the beginning of the next cycle defining the new "current" instruction. The sequence then repeats. Since the two processors are running 180 degrees out-ofphase, the first half of a cycle on one processor is the second half for the other processor.

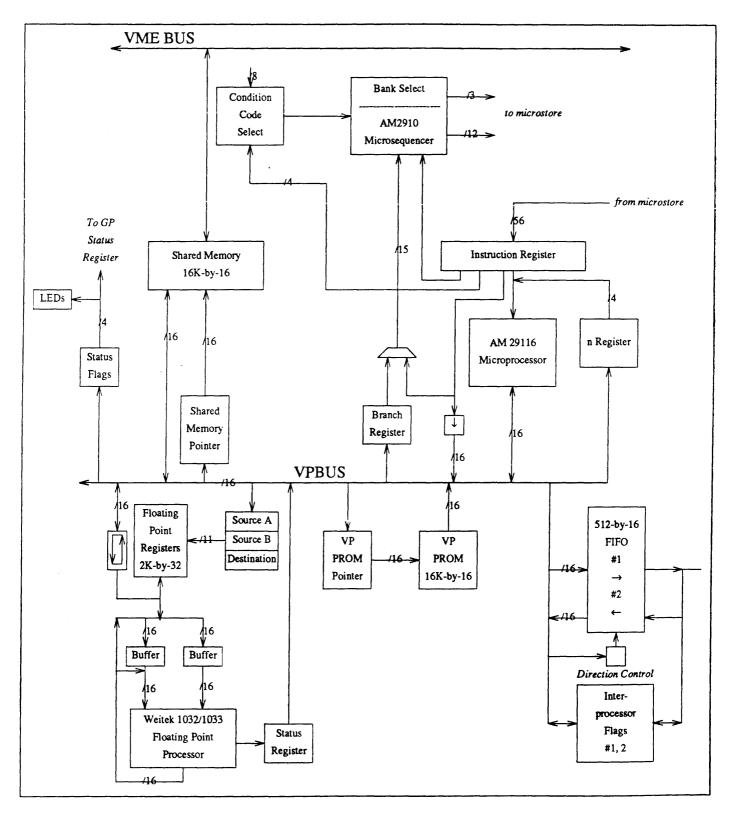

4.3. Viewing Processor The following figure is a block diagram of the Viewing Processor. The components of the block diagram of the GP Board are recognizable but more detail, especially around the AM29116 and the Weitek floating point units, is shown. Various references are made to the microinstruction in the discussions that follow. The format of this 56-bit word is defined in the chapter describing the microcode format.

| Program Sequencer and<br>Program Memory | To make the AM29116 into a useful computer, two major components are<br>required: a program sequencer and program memory. The microstore is the pro-<br>gram memory. The sequencer used is an AM2910 which contains a program<br>counter, a stack for subroutine linkage, and branch control logic. A branch is con-<br>ditional on the state of the condition code input to the AM2910. The condition<br>code select logic multiplexes 16 options (either polarity of eight status flags) into<br>this one input. A limitation of the AM2910 is its 4K address space. The bank<br>select logic is used to expand this space to 32K maximum by selecting one of<br>eight banks. The AM2910 and the bank select provide the address to the micro-<br>store. |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | A bank switch can only be done by executing the AM2910 JMAP instruction.<br>This is an unconditional jump for the AM2910 and is used to flag the bank select<br>logic that a (potential) bank switch is to be done. During the JMAP instruction,<br>the bank select state is updated. When doing a JMAP instruction, the D input to<br>the AM2910 can be either the branch register or the general field of the microin-<br>struction (see below).                                                                                                                                                                                                                                                                                                         |

|                                         | A JZ (jump zero) command to the AM2910 forces the microprogram counter to 0. A JZ instruction jumps to location 0 of bank 0. This command thus effects the bank select bits, potentially executing a bank switch.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NOTE                                    | The AM2910 contains an internal R register and stack. These registers are 12-<br>bit only so that branches to these addresses DO NOT perform bank switches.<br>Care must be taken to ensure that, for example, a call is not done in one bank<br>and the corresponding return done in another. Also, the sequencer does not<br>automatically flow from one bank to the next. That is, a continue from location<br>FFFF (hex) in bank 0 (the last location in this bank) will go to location 0000 in<br>bank 0, not location 0000 in bank 1.                                                                                                                                                                                                                |

| Branch Register                         | The <i>branch register</i> is a 15-bit register that contains a possible source of the next address selected by that AM2910. A branch to the location preloaded into the branch register is executed if two conditions are met. The branch register must be chosen as the D input of the AM2910 (controlled by the DS microinstruction bit), and the branch condition must be successful (determined by the AM2910 instruction and the state of the branch status flag chosen in the microinstruction). The branch register is loaded when it is chosen as the VPBUS destination (controlled by the source/destination field of the microinstruction).                                                                                                     |

| Instruction Register Buffer             | Shown in the block diagram of the Viewing Processor are <i>buffers enabling the</i><br>general field of the instruction register onto the VPBUS. These buffers are<br>turned on when the general field is chosen as the VPBUS source (controlled by<br>the microinstruction source/destination field). With this capability, the micro-<br>coder can route an assembly-time constant onto the VPBUS and route it to one of<br>several possible destinations, including for example, the AM29116, the shared-<br>memory pointer, or a floating point register pointer.                                                                                                                                                                                      |

| n Register            | Several AM29116 instructions include a 4-bit field (n) to determine, for example, the bit position to test or the number of bits to rotate. The usefulness of these instructions is diminished if the n value is hardcoded into the microinstruction. Therefore, a four-bit <i>n register</i> is provided. Under control of the microinstruction, the n register value can be substituted for the n field in the AM29116 instruction, thereby providing a way to calculate n at runtime, not at assembly time. The n register is loaded by chosing it as the VPBUS destination.                 |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interprocessor Flags  | An interprocessor flag mechanism is provided to pass status flags between the two processors. Two 8-bit registers are implemented, one in each direction; FIFO status can be read from them. <i>Interprocessor flag #1 register</i> can be written by the Viewing Processor and read by the Painting Processor. It is used by the Viewing Processor to control FIFO direction. <i>Interprocessor flag #2 register</i> can be written by the Painting Processor and read by the Viewing Processor. These registers are under total firmware control; they have no special hardware significance. |

|                       | An ninth bit is also read when the interprocessor flag is chosen as the bus source.<br>On the Viewing Processor this bit is read as a logic 0, and on the Painting Processor this bit is read as a logic 1. This provides a mechanism to distinguish the two processors at reset. After a reset, both processors begin executing at microstore location 0; both read their interprocessor flags; and then each processor branches to its respective initialization routine.                                                                                                                     |

|                       | There is a hardware constraint to the interprocessor flag register—it is not possible to read this register into the AM29116 and manipulate it in a single cycle. It must first be read into the AM29116 D-latch and then manipulated by subsequent instructions.                                                                                                                                                                                                                                                                                                                               |

| Status Flags Register | The status flags register is a four-bit VPBUS destination that provides a mechan-<br>ism to return general-purpose status bits to the host processor via the VME bus.<br>These bits can be written (chosen as a VPBUS destination) at any time by the<br>Viewing Processor and read at any time from the VME bus. Four LEDs (light<br>emitting diodes) are also driven by this register. This register also contains the<br>fpsel bit, which allows read-back of either set of floating point registers. For<br>further information, see the chapter which describes the internal registers.    |

| FIFO                  | The <i>FIFO</i> is the connection to the other processor. One "reversible" FIFO is implemented but for easier understanding the following nomenclature is used: FIFO #1 is for VP-to-PP transfers and FIFO #2 is for PP-to-VP transfers. The direction is controlled by two bits that are written whenever the interprocessor flags #1 register is written. The FIFO is 512 16-bit words deep.                                                                                                                                                                                                  |

|                       | If FIFO #1 is chosen as the destination, the data word on VPBUS is loaded into<br>the FIFO. A testable status flag (a condition code select option) is used to deter-<br>mine if the FIFO is full or not. Hardware protection is provided to ensure that a<br>data word is not written to a full FIFO, but the microcode must test the status to<br>determine the success or failure of a FIFO load and thus determine if the FIFO<br>load should be re-executed.                                                                                                                               |

If FIFO #2 is chosen as the source, the data word on the top of FIFO #2 is routed onto VPBUS. A testable status flag is used to determine if a valid data word was routed onto the bus. Hardware protection is provided to ensure that an empty FIFO is not read (and thereby prevent a timing glitch which could cause the loss of a data word), but the microcode must check the status flag to determine whether or not another read of the FIFO is necessary to receive valid data.

Because of the asynchronous nature of the FIFO, there is a "recovery time" after each FIFO access and it is therefore not possible for a FIFO to accept or supply data every processor cycle. On FIFO writes, there is a 1 cycle recovery time, so that writes can be done at most every other cycle. On FIFO reads, the recovery time is 2 cycles, so that reads can be done at most every third cycle. However, the FIFO status flags will be valid at all times.

If the FIFO direction is VP-to-PP, then VP readings of the FIFO will always succeed, but the data returned are meaningless. If the FIFO direction is PP-to-VP, then VP writes to the FIFO are also successful, but the data are discarded. Read/write success is determined by testing the FIFO status flags. This is done to prevent the microcode from hanging by accessing the FIFO in the wrong direction.

Shared Memory Shared memory has been mentioned several times. The dual-port capability is implemented by allocating two accesses to the memory every Viewing Processor cycle. The first half cycle is allocated for a read or write access by the Viewing Processor. The second half cycle is allocated for VME bus reads or writes. Obviously, a meaningful operation is not done every half cycle, but the allocation is fixed.

Before accessing shared memory, the Viewing Processor must load the sharedmemory pointer. This register points to the location at which subsequent Viewing Processor accesses will be made. Under microcode control, this pointer can be incremented, decremented, or cleared.

The shared-memory access is executed by chosing the shared memory as the VPBUS source or destination. By also counting the pointer when making the access, sequential reads or writes can be done at the rate of one per cycle.

Because of the shared-memory architecture, writes to the shared memory (and increments or decrements of the shared-memory pointer when done coincident with the write) are done in the cycle immediately following the cycle with the write instruction. This means that a read of shared memory cannot be done in the cycle immediately following a cycle doing a shared memory write. An increment or decrement of the shared-memory pointer executed in the next cycle is thus redundant unless the shared memory is coincidentally selected as the VPBUS destination.

VP PROM and VP PROMWhen selecting the VP PROM as the VPBUS source, the location pointed to by<br/>the VP PROM pointer is routed to the VPBUS. The functional VP PROM is<br/>implemented with two 16K-by-8 erasable PROMs providing for 16K of 16-bit<br/>words. After loading the VP PROM pointer with the address of the location to<br/>be read, a two cycle delay must be incurred before selecting the VP PROM as the<br/>VPBUS source to allow for the slow access time of the PROM.

4.4. Floating Point Circuitry

Overview of the Floating Point Circuitry This section covers the floating point registers, the pointers into these registers, and the Weitek floating point chips. All floating point operations are done through the floating point registers. The Weitek chips receive their input from these registers and all floating point results are loaded back into these registers.

There are three pointers into the *floating point registers*:

- □ source A, and

- □ source B, and

- destination.

Each of these pointers is 11 bits wide (2K addressing capability) and can be loaded as a destination from the VPBUS. Under microcode control these pointers can be incremented at the end of a cycle.

The floating point registers are implemented with 4K-by-4 static RAMs, providing 4K of 16-bit words. But since floating point numbers are 32-bits wide, these registers are treated as 2K 32-bit registers, explaining the 11-bit width of the pointers. The high (most significant) or low (least significant) word of the 32-bit floating point number is selected by the h/l bit in the current microinstruction. If h/l = 0 then the most significant word is selected; if h/l = 1 then the least significant word is selected.

The source A pointer is used to select

- 1. the register that is routed to VPBUS when a floating point register has been chosen as the source of data onto VPBUS, or

- 2. the A operand to the Weitek chips.

The source B pointer is used to select the B operand to the Weitek chip.

The destination pointer is used to select

- 1. the floating point register into which the Weitek result is loaded, or

- 2. the location into which the VPBUS data word is loaded when a floating point register is chosen as the VPBUS destination.

For diagnostic purposes, it is possible to route the data pointed to by the source B pointer onto the VPBUS. A flag under microcode control (as part of the status/LED register) determines whether the source A or source B pointer is used to determine the data word read.

NOTE A hardware implementation detail: the floating point registers are implemented as two banks in order to increase the bandwidth of these registers. The source A pointer points to bank A and the source B pointer points to bank B. The destination pointer points to both banks. Whenever a write is done, both banks are written; therefore, the banks are duplicates. Normally, when the floating point register is chosen as the VPBUS source, bank A is read. However for diagnostics, it is possible to read bank B directly by controlling the floating point flag described previously.

When the floating point registers are chosen as the VPBUS destination, the data word is first loaded into a holding buffer. It is actually written into the registers

|                             | in the next cycle. When the floating point register is the VPBUS destination and<br>the destination pointer count is enabled, the count, like the data load, is executed<br>in the next cycle. An increment the destination pointer executed in the next<br>cycle is thus redundant unless a floating point register is coincidentally selected<br>as the VPBUS destination.                                                                                                                                                        |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Floating Point Registers    | Similar to the shared memory, the floating point registers operate at twice the fre-<br>quency of the AM29116 cycle. The first half cycle is used to read the register file<br>and supply data for either the Weitek chips (A and B operands) or VPBUS. The<br>second half cycle is used to store VPBUS data or Weitek chip results into the<br>registers if so instructed by the microinstruction.                                                                                                                                 |

|                             | A hardware restriction is that on consecutive cycles, the floating point registers<br>cannot be used as the destination of a VPBUS operation and then as the destina-<br>tion of a floating point result. In addition, the source A pointer is used to select<br>both the A operand to the Weitek chips and the data word routed to the VPBUS<br>when selected as the source. It is unlikely that the source A pointer can be used<br>to select the VPBUS source data and the Weitek chip source A in a single<br>microinstruction. |

| Weitek Floating Point Chips | The Weitek Floating Point chips are controlled by fields within a microinstruc-<br>tion. The following three operations are possible:                                                                                                                                                                                                                                                                                                                                                                                               |

|                             | 1. (Source A pointer) op (Source B pointer),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             | 2. Weitek result op (Source B pointer),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                             | 3. Weitek result> (Destination pointer).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                             | 1 and 2 are mutually exclusive. 3 can be done in the same microinstruction as either 1 or 2.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                             | The operations of the Weitek chips take several cycles to complete. The micro-<br>coder must be aware of this and not attempt to use a Weitek result before it is<br>ready. In pipeline mode, it takes two cycles to load the 32-bit operands, 6 cycles<br>of execution delay, 2 cycles of unload instructions, and 2 cycles to output the<br>result. But because of the pipeline, a new operation can be started every two<br>cycles.                                                                                              |

|                             | To minimize hardware, floating point registers are treated as 32-bit numbers.<br>The microcoder must take care to control the h/l (hi/low word) bit and cause the<br>proper data word (most or least significant word) to be utilized at the proper time.<br>This is of concern in the following operations:                                                                                                                                                                                                                        |

|                             | Floating point register as VPBUS source,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                             | Floating point register as VPBUS destination,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             | Initiating a floating point operation to the Weitek chips,                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                             | Enabling an unload of the Weitek chip result,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                             | Unloading the Weitek chip result.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                             | The h/l bit directly controls the least significant bit of the address to the floating                                                                                                                                                                                                                                                                                                                                                                                                                                              |

The h/l bit directly controls the least significant bit of the address to the floating point registers and the U0 bit of the Weitek chips.

Sun Microsystems, Inc.

The Weitek chips provide status coincident with each result. This status information is made available on an individual operation and on an accrued basis as part of the floating point status register.

4.5. Painting Processor The following figures are the block diagrams for the Painting Processor. As before, the functional blocks of the block diagram of the Graphics Processor board are expanded now in greater detail.

Figure 4-3 Painting Processor Block Diagram — Part 1

Figure 4-4 Painting Processor Block Diagram — Part 2

As the figure suggests, much of this section is the same as the Viewing Processor. These components include

- an AM2910 microsequencer,

- □ bank select logic,

|                                             | <ul> <li>branch register,</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                             | □ general field,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                             | □ n register,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                             | interprocessor flag registers,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                             | status flag register,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                             | reversible FIFO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Branch Register                             | The <i>branch register</i> and the branch restrictions for this section are basically the same as for the Viewing Processor. The only difference is the method to perform on unconditional branch (or call or return). On the Viewing Processor a logic 1 is input to the condition select multiplexer and, if selected, causes a "pass" condition to the AM2910. On the Painting Processor the eight multiplexer inputs are otherwise occupied (see the chapter describing the microcode format) so that the AM2910 condition code enable signal is a microinstruction bit and is used to force a "pass" condition. |

| Condition Code Select                       | A difference also exists in the <i>condition code select</i> . When initiating a VME bus operation (described below), it is possible to do a 3-way branch. With the proper microinstruction, the following is possible:                                                                                                                                                                                                                                                                                                                                                                                              |

| . · · ·                                     | 1. If the VME busy flag is set, branch to the location specified in the general field.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                             | 2. If the VME busy flag is not set, then test another selectable condition (for example, negative) and either                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                             | a) branch to the location specified in the branch register for a pass condi-<br>tion, or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                             | b) branch to the next instruction for a fail condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Scratchpad Memory and<br>Scratchpad Pointer | The scratchpad memory is 4 Kwords by 16 bits per word of one-cycle access<br>memory. If chosen as the source, the data word pointed to by the scratchpad<br>pointer is loaded onto PPBUS. If chosen as the destination, the data word on the<br>bus is loaded into the location selected by the scratchpad pointer. The pointer<br>can be cleared or incremented under microcode control.                                                                                                                                                                                                                            |

|                                             | Because of the scratchpad-memory architecture, writes to the scratchpad memory<br>(and increments or decrements to the scratchpad-memory pointer when done<br>coincident with the write) are done in the cycle immediately following the cycle<br>with the write instruction. This means that a read of scratchpad memory cannot<br>be done in the cycle immediately following a cycle doing a scratchpad memory<br>write. An increment the scratchpad pointer executed in the next cycle is redun-<br>dant unless the scratchpad is coincidentally selected as the PPBUS destination.                               |

### Interrupt ID Register

The byte-wide *interrupt ID register* is used to trigger an interrupt on the VME bus. Loading a value into the register (selecting it as the PPBUS destination) causes the following:

- 1. the interrupt flag in the GP status register is set;

- 2. if the interrupt enable flag (in the GP control register) is set, a VME interrupt request is generated;

- 3. in response to the interrupt acknowledge, the value in the interrupt ID register is returned to the host processor as the interrupt vector.

If the interrupt enable is not set, the interrupt flag can be polled. If the interrupt flag is set when loading the interrupt ID register (signifying that the last interrupt has not been acknowledged by the host processor), the interrupt ID register contents are overwritten and the indication of the previous interrupt is lost. By reading the VME control register (see below), the microcoder can determine if there is a pending interrupt since the interrupt flag is replicated in this register as the interrupt pending bit.

VME Bus Interface Logic

A major component of the Painting Processor is the VME bus interface. Six registers interface this logic to PPBUS. The internal register format section of this document contains details of these registers.

The VME control register controls the data transfer width (byte or word) and the VME bus address modifier bits. The VME status register contains information on the results of the last VME bus operation, accrued results, and the interrupt status (pending or not pending).

Two registers are used to generate the 24-bit VME bus address: the high and low VME address registers. These registers are implemented as a 24-bit counter:

- the low address register is the low 16 bits of the counter, and

- the high address register is the high 8 bits.

This counter can be incremented or decremented under microcode control.

In addition, the counter is buffered before being routed to the bus so that these two registers can be updated while a VME data transfer is active. The VME address registers specify a byte in VME address space. If doing word transfers, the least significant address bit should be zero. (If it is not zero, the hardware will execute the VME access as if it were zero but will flag an error.) If using the increment or decrement capability when executing word transfers, the microcoder must count the VME address register twice.

The read- and write-data registers are used to store the data fetched on a VME bus read cycle and the data to be written on a VME write cycle.

The following steps are used to execute a VME bus write:

- 1. The VME control register is initialized.

- 2. The VME address registers are loaded.

- 3. The VME write-data register is loaded.

- 4. The write is started using the miscellaneous control section of the microinstruction.

- 5. Step 4 automatically causes the VME busy flag to be set.

- 6. When the VME write completes, the VME ready flag (the complement of the busy flag) is automatically set.

- 7. A new write or read can be initiated.

Steps 1-3 can be done in any order. Step 4 could be coincident with step 1 or 3 (but NOT 2) after the other registers are loaded. When the VME busy flag is set, the VME control register and the VME write-data register cannot (hardware protected) be altered. The address registers can be updated when the VME busy flag is set.

The following steps are used to execute a VME bus read:

- 1. The VME control register is initialized.

- 2. The VME address registers are loaded.

- 3. The read is started using the miscellaneous control section of the microinstruction.

- 4. Step 3 automatically causes the VME busy flag to be set.

- 5. The requested data word or byte is loaded into the VME read-data register.

- 6. Step 5 automatically causes the VME ready flag to be set.

- 7. The VME read-data register is read by the Painting Processor.

- 8. A new read or write can be initiated.

Steps 1 and 3 can be done in the same microinstruction after step 2. Reading the VME read-data register will return garbage while the VME busy flag is set. Testing the busy flag will determine when a valid data word is read. The VME address registers can be altered when the VME busy flag is set.

If doing byte accesses, only the low half (bits 7 to 0) of the VME read and writedata registers are used. The hardware routes the desired byte to/from the correct VME data lines.

NOTE The remaining sections of the Painting Processor are located on the optional GB board. That is, the GB board will contain all of the following features:

- Graphics Buffer Memory

- Integer Multiplier

- D Mode Register

- D PP PROM

If the optional board is not installed, no hardware restrictions exist on the GP board but the firmware should not attempt to use any of the GB board features.

Graphics Buffer Memory The *GB board memory* is implemented with 64 DRAM chips providing 1M 16bit words. As shown in the block diagram of the Painting Processor, there are two data registers and one address pointer interfacing the DRAM to the PPBUS. The Graphics Buffer ready flag is a testable branch condition and indicates whether the hardware is ready to accept an address change or to execute a DRAM access.

The DRAM has two operation modes: Normal and Read-Modify-Write (RMW). In normal mode, the DRAM is a linear array with hardware assist for sequential access. Fill mode is a submode of normal mode; a fill-mode write causes data to be written into four consecutive locations in the same time required to write a single location. The RMW mode is similar except that reads followed by a write can be done to a single location. RMW mode is useful for the inner loops of hidden surface elimination algorithms.

Normal mode works as follows: the address pointer is initialized by loading the high and low Graphics Buffer address pointers. If a start-read command, specified in the miscellaneous control field of the microinstruction, is coincident with the load of the low address pointer, then a DRAM read is initiated. When the read is complete three cycles later, the fetched data word is loaded into the Graphics Buffer read-data register and can be read by selecting this register as the PPBUS source.

The next sequential location can be read by executing a start-read command. This command may be done coincident with a read of the Graphics Buffer readdata register—or not, as desired. When the start-read command is received, the Graphics Buffer address pointer is incremented and a memory read initiated. When the read is complete three cycles later, the fetched data word is loaded into the Graphics Buffer read-data register and can be read by selecting this register as the PPBUS source. In this way sequential reads can be performed.

Sequential writes start the same way: the high and low Graphics Buffer address pointers are loaded. But no start-read is done. Instead, a write to the Graphics Buffer write-data register is done. The value just loaded into the write-data register is then written into memory at the address in the pointer. When the memory write completes, the pointer is incremented. It takes three cycles for the memory write to finish.

Reads and writes can be mixed. The rules are:

- a start-read increments the pointer (unless coincident with a write to the low address pointer),

- executes a read, and

- loads the Graphics Buffer read-data register.

A load of the Graphics Buffer write-data register

- executes a write, and then

- increments the address.

Fill mode can be used only in normal mode and only when doing writes. No hardware protection is provided to prevent using fill mode with reads or in RMW

mode (other than to protect the hardware from damage) and results will be indeterminate.

Fill mode is entered by writing the appropriate bits in the Graphics Buffer high address pointer (see the chapter describing microcode format). Then the low address pointer is loaded to define the location of the write. The low order two address bits are ignored so that 4 consecutive locations on a modulo 4 boundary are loaded. The actual memory write is triggered by choosing the Graphics Buffer write-data register as the PPBUS destination. The value written into the write-data register is the value written into the 4 memory locations. After the write completes, the address pointer is incremented by 4 so that the next group of 4 locations can be written with a single load of the Graphics Buffer write-data register.

In summary, fill-mode writes work similar to normal-mode writes except that 4 locations are written per load of the Graphics Buffer write-data register and the address pointer is incremented by 4 following each write.

*RMW mode* works as follows: as above, the address pointer is initialized by loading the high and low Graphics Buffer address pointers. A start-read command must be coincident with the load of the low address pointer (the microcoder must ensure this because there is no hardware protection), and a DRAM read/modify/write (RMW) cycle is initiated. When the read is completed four cycles later, the fetched data word is loaded into the Graphics Buffer read-data register and can be read by selecting this register as the PPBUS source. But the DRAM remains in the RMW state.

Reading the Graphics Buffer read-data register merely routes the register contents to the PPBUS destination. The DRAM remains in the RMW state.