# PROCESSOR ORGANIZATION AND MICROPROGRAMMING

.

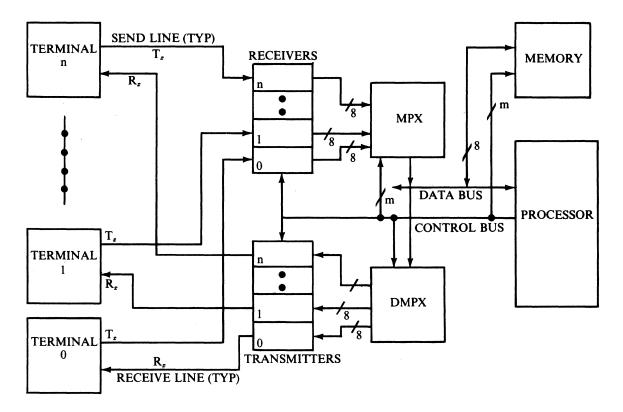

# PROCESSOR ORGANIZATION AND MICROPROGRAMMING

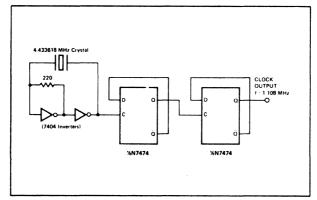

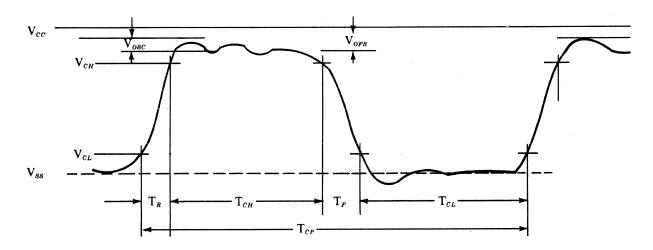

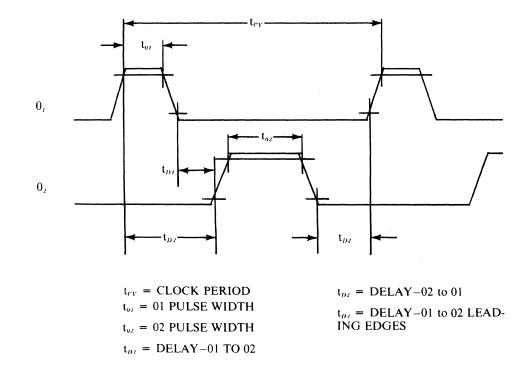

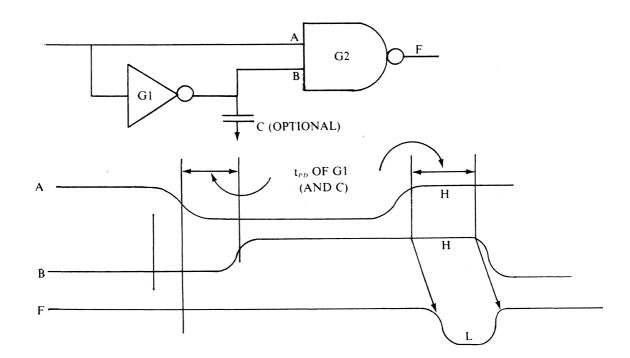

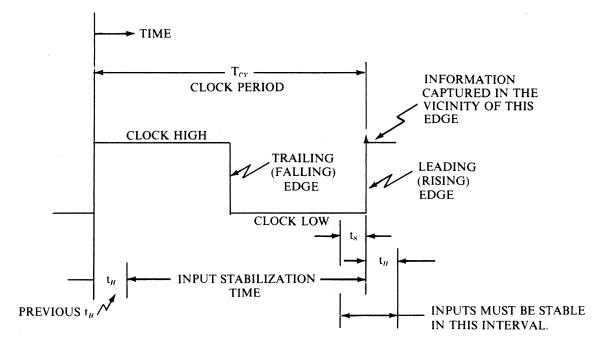

A PROJECT CASE STUDY

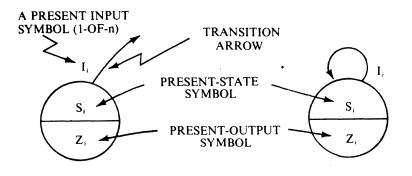

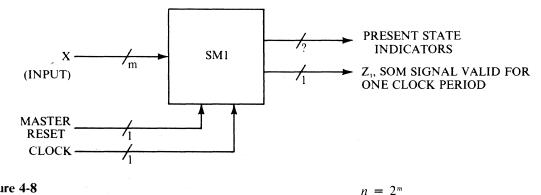

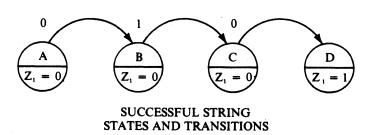

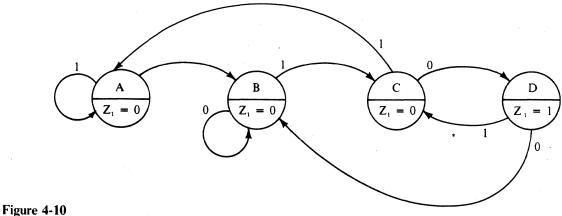

Daniel J. Nesin California State Polytechnic University, Pomona

SCIENCE RESEARCH ASSOCIATES, INC. Chicago, Henley-on-Thames, Sydney, Toronto A Subsidiary of IBM Acquisition Editor Project Editor Copy Editor Production Director Text Design, Cover Design, and Composition Al Lowe Geof Garvey Dan Kirklin Arthur Kuntz Baskerville Book

### Library of Congress Cataloging in Publication Data

Nesin, Daniel J., 1924– Processor organization and microprogramming.

1. Computer architecture.2. Microprocessors.3. Microprogramming.Microprogramming.I. Title.QA76.9.A73N461985001.64'2ISBN 0-574-21770-384-23560

Copyright © Science Research Associates, Inc., 1985 All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Science Research Associates, Inc.

Printed in the United States of America

10 9 8 7 6 5 4 3 2 1

|   | PREFACE                                                                                                                                                                                                                                                                                                                                               | vii                                                     |

|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 1 | OVERVIEW OF PROCESSOR ARCHITECTURE                                                                                                                                                                                                                                                                                                                    | 1                                                       |

|   | The Evolution of Computers<br>Architectural Types and the Cycle of Computation<br>Forms and Uniformity among Processors<br>Processor Fabrication Technologies and Personal Impacts<br>Bibliography<br>Problems                                                                                                                                        | 1<br>10<br>17<br>25<br>29<br>29                         |

| 2 | FEATURES AND DEVICES OF PROCESSORS                                                                                                                                                                                                                                                                                                                    | 33                                                      |

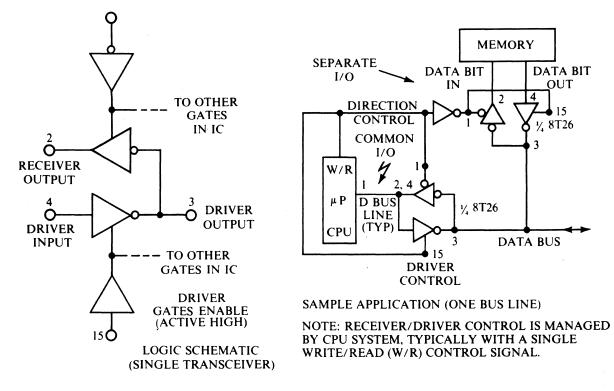

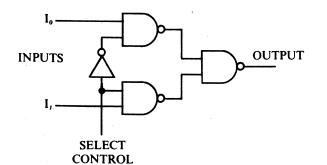

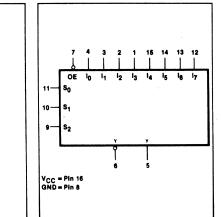

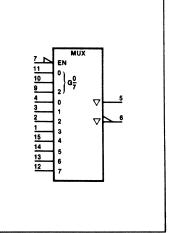

|   | Buses, Data Paths, Gates, and Buffers<br>Bus Hardware, Calculations, and Data Catalogs<br>Multiplexing (MPX) and Demultiplexing (DMPX)<br>Memory Cells<br>Bibliography<br>Problems                                                                                                                                                                    | 34<br>48<br>59<br>67<br>73<br>74                        |

| 3 | Assembling an Architecture                                                                                                                                                                                                                                                                                                                            | 77                                                      |

|   | Registers, Arrays, and Stacks<br>Organizing an Architecture<br>User/Executive Modes<br>The Arithmetic/Logic Unit: Operations and Flags<br>Effects of Architectural Variations on Operations: Putting It all Together<br>Clock Characteristics and System-Clock Periods<br>General Edge-Triggered Clocking Characteristics<br>Bibliography<br>Problems | 77<br>84<br>87<br>87<br>100<br>106<br>111<br>116<br>116 |

| 4 | SEQUENTIAL-MACHINE (SM) FUNDAMENTALS                                                                                                                                                                                                                                                                                                                  | 121                                                     |

|   | Microprogramming's Basis in State Machine Theory<br>Sequential-Machine Representation<br>Sequential-Machine Visualization<br>SM Design Procedures<br>Logical Properties of Flip-Flops<br>Bibliography<br>Problems                                                                                                                                     | 121<br>122<br>129<br>132<br>137<br>151<br>151           |

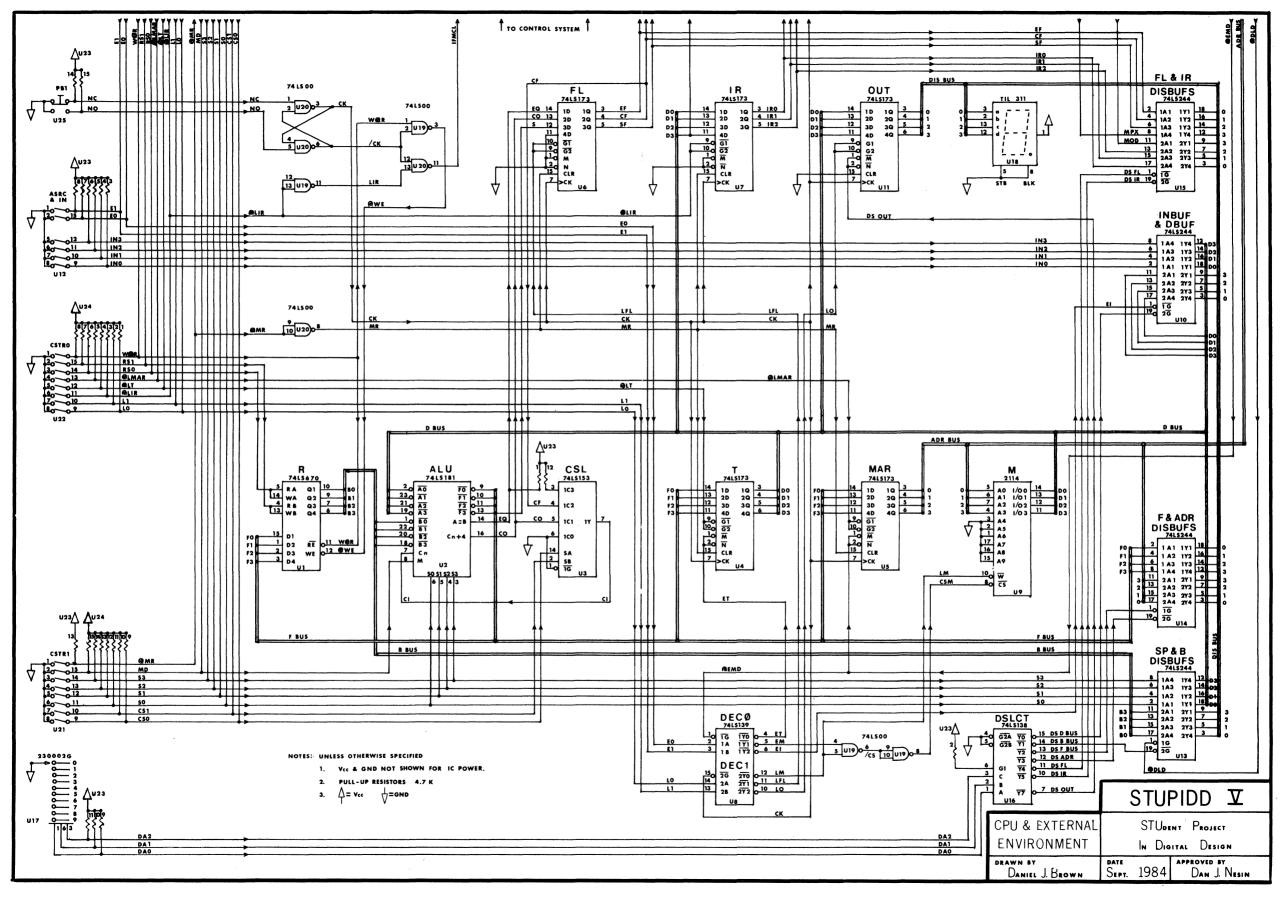

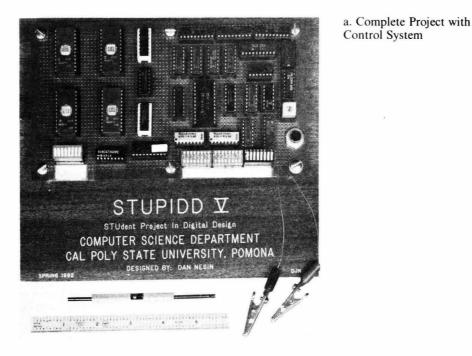

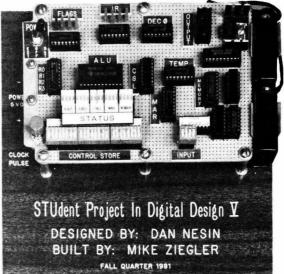

| 5 | STUPIDD V-A MICROPROCESSOR ANALYSIS AND CONSTRUCTION PROJECT | 155 |

|---|--------------------------------------------------------------|-----|

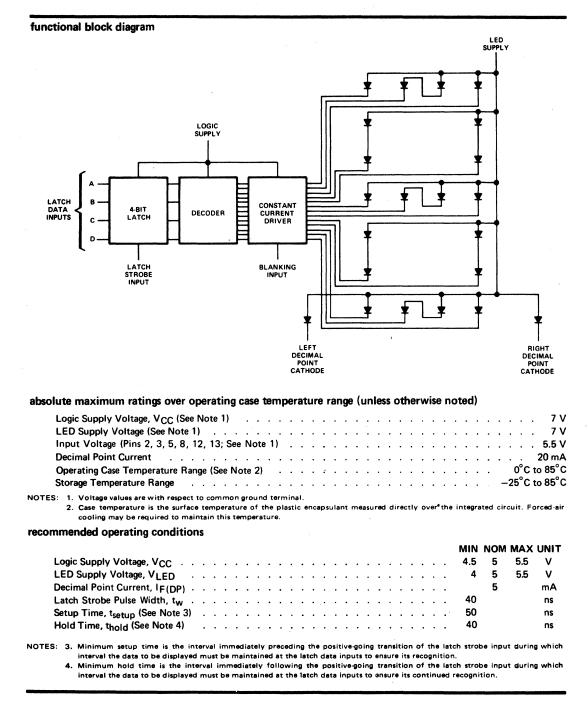

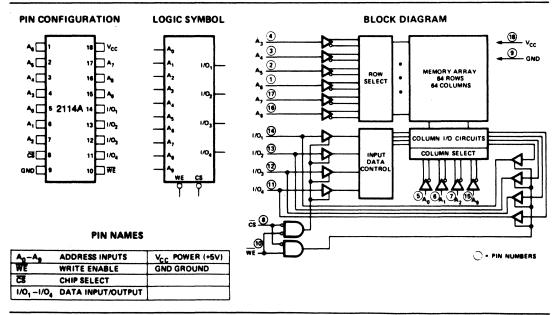

|   | Common IC's in a Systems Context                             | 155 |

|   | Commonality of Features of All Processors                    | 156 |

|   | Device Control and Nomenclature                              | 160 |

|   | The External World                                           | 168 |

|   | CPU Construction Project and Checkout                        | 182 |

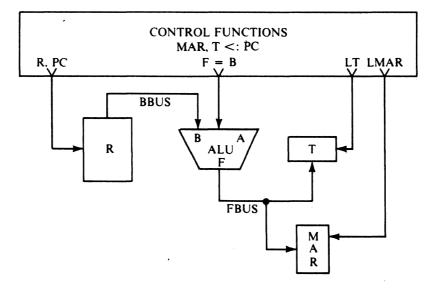

|   | Microprogramming Formats: The Control Word                   | 213 |

|   | Microcoding the EX Major State                               | 228 |

|   | Problems                                                     | 238 |

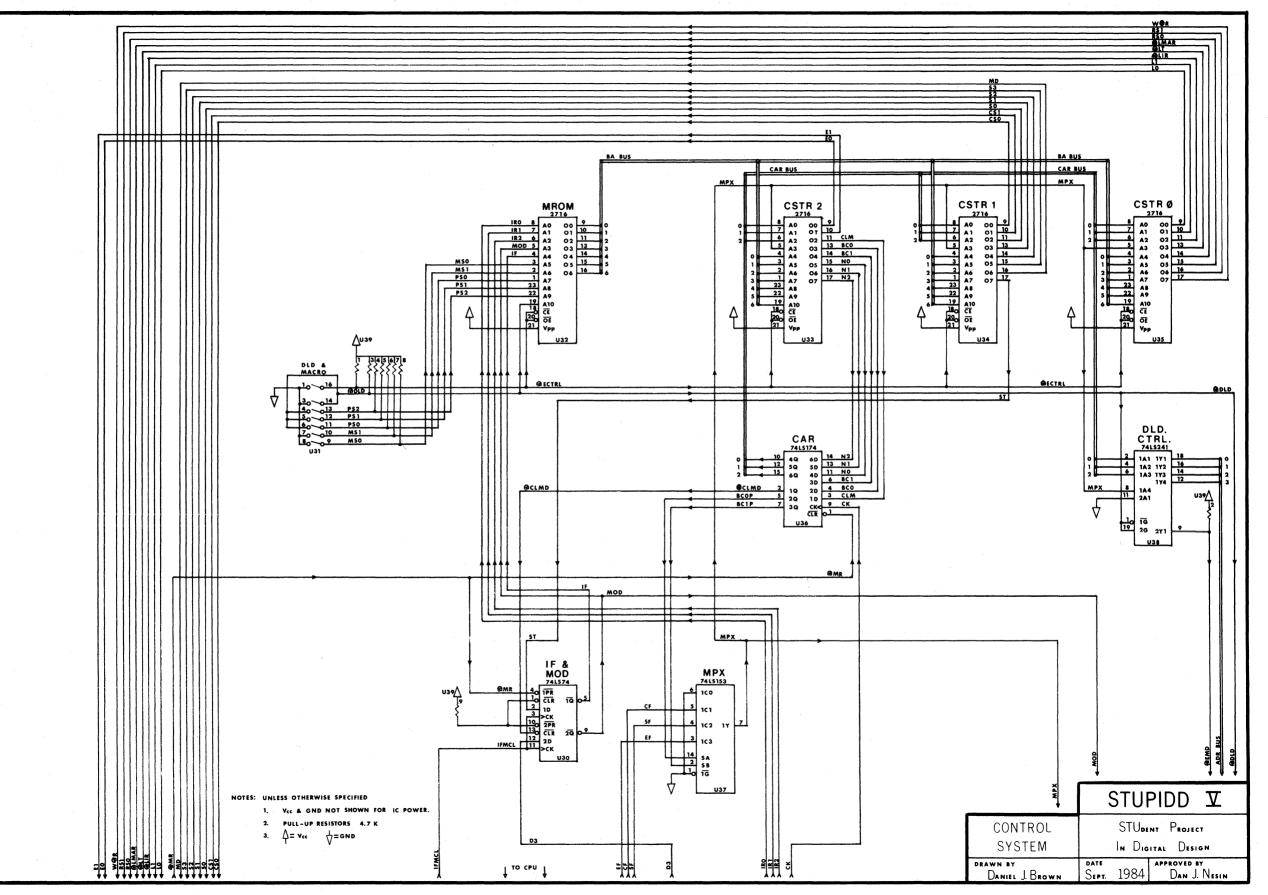

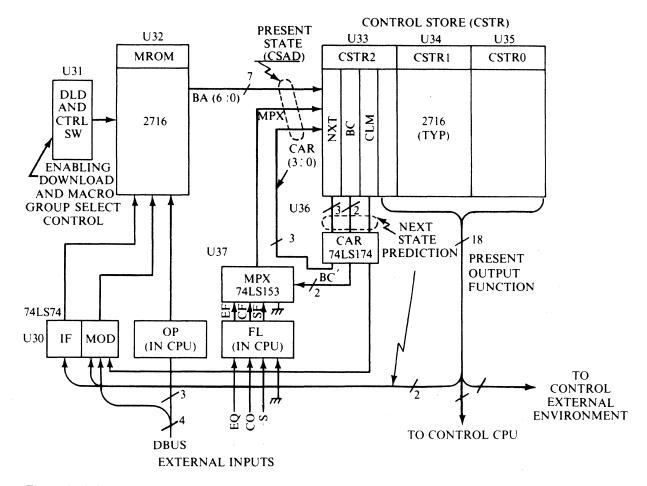

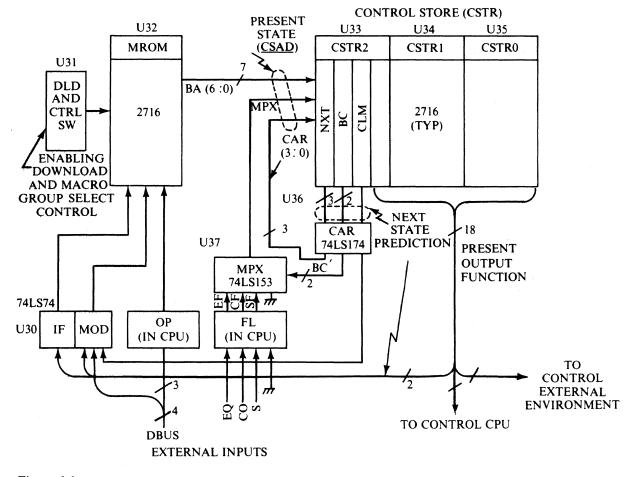

|   | Control System Overview                                      | 241 |

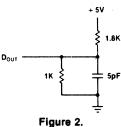

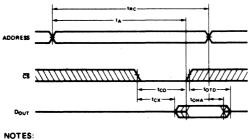

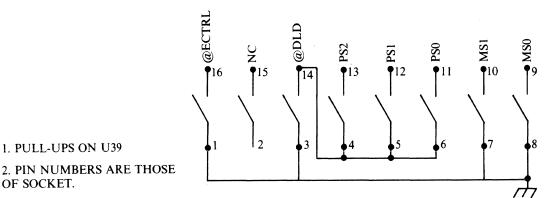

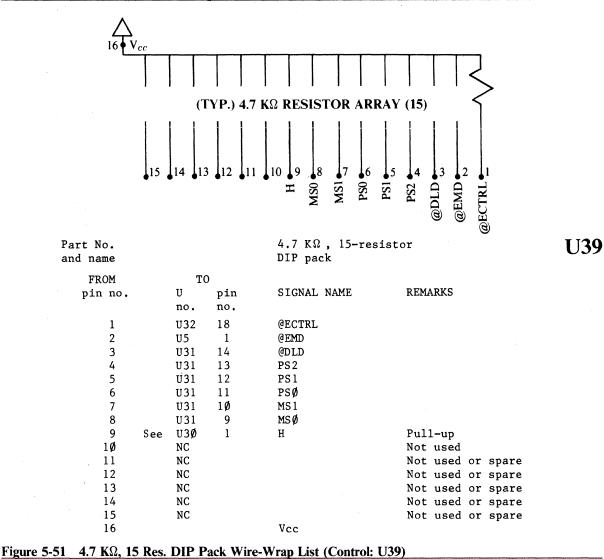

|   | Control-System Device Details and Memory Maps                | 249 |

|   | Control Store IC Details                                     | 259 |

|   | Microcoding and the Control System                           | 266 |

|   | Microcoding Examples                                         | 270 |

|   | PROM Programming the Control System                          | 283 |

|   | Bibliography                                                 | 304 |

|   | Problems                                                     | 304 |

|   | READY REFERENCE OF KEY TOPICS                                | 307 |

,

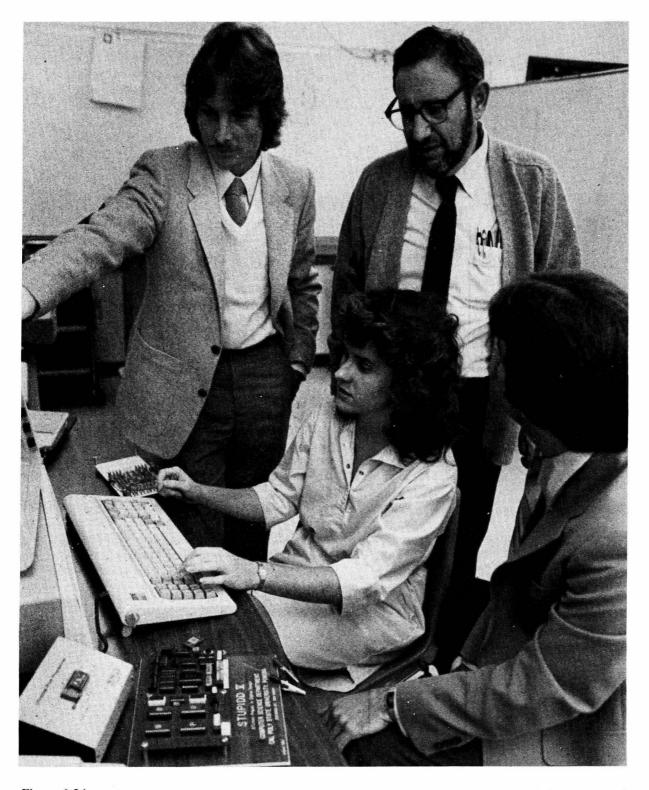

The material of this text arose out of a series of student projects in digital design initiated over a decade ago with electrical engineering students. The projects answered two observed needs of students to enhance their comprehension of digital processor systems: (1) to experience a complete processor—as opposed to partial amorphous architectural representations—in order to gain a comprehension of the nature of processing systems; (2) to work with real (rather than hypothetical) architectural constructs—thus demonstrating their mastery of an actual archetypical processor, which proved a particular satisfaction to them.

The associated Central Processor Unit construction project was designed to be built and operated at home, to encourage an appreciation of the development of the hardware and microprogramming.

In 1981 the author began instructing software-oriented computer science students who had very little, if any, prior exposure to hardware. It was felt that removing the mystery and hardware fright of these students should significantly improve their future careers, as the distinction between hardware and software knowledge becomes increasingly obsolete. These computer science students' comprehension of the material formalized into this text appeared to be no different from that of electrical engineers: 25 percent culture shock, 50 percent varying degrees of comprehension, and 25 percent enthusiasm accompanied by innovative suggestions and activities. A significant number of these software-emphasis students actually found that the material helped open up new career opportunities, such as software development for microprocessor-controlled instrumentation systems.

**Chapter 1** presents a historical perspective on computers and introduces the major fundamental systems architectures. It is shown that a computer system is composed of a number of processors, which possess unified underlying systems principles coordinated by the Central Processing Unit (CPU) and the systems software developed for it. The notion of the cycle of computation is introduced, with its two major states: Instruction Fetch and Instruction Execute. The role of the Program Counter in von Neumann architectures is explained, as is its effect on memory-usage maps. The increasing need for systems insight into the hardware/software relationship is stressed, with its current trends and impacts on people.

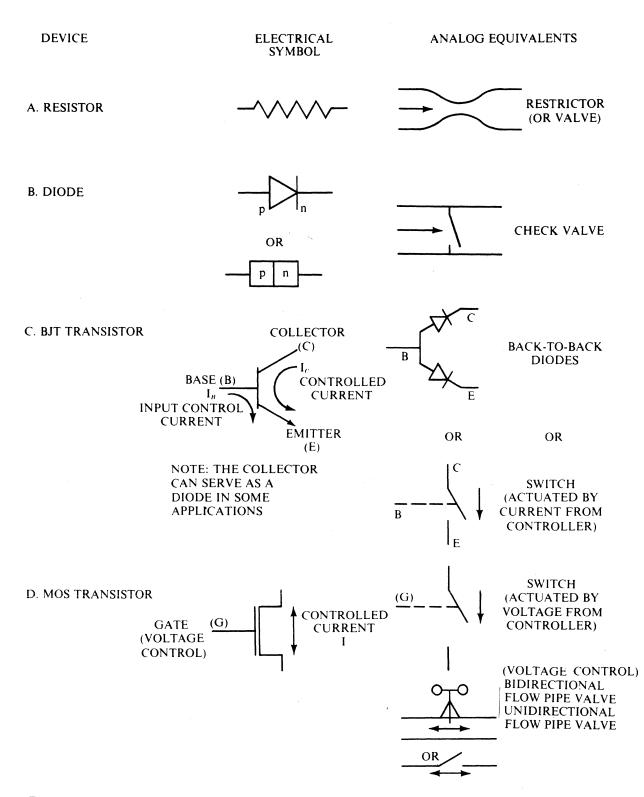

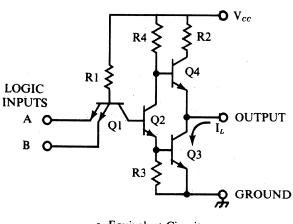

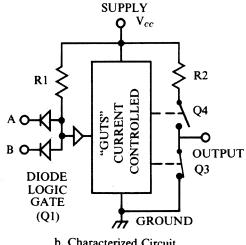

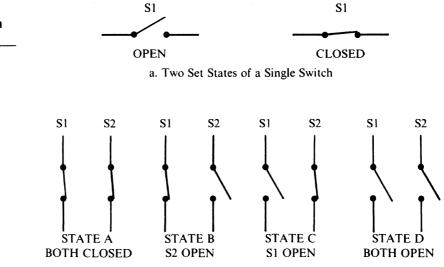

Chapters 2, 3, and 4 are included in this text in response to the many questions posed by the software-oriented student with little hardware exposure. It is presented as a broad survey or review of device and architecture fundamentals that an electrical engineering student may or may not already have been exposed to. The goal of these chapters is to create a working understanding and intuitive mental image of fundamental logic devices and how they are incorporated into architectural structures. The manner in which many of these devices of a digital system function can often be readily understood in terms of logically equivalent analogs. For example, the transistor's behavior, in the systems context, can be perceived as that of a simple switch. The functioning of logic and tri-state gates, buses, memory, Arithmetic/Logic Unit (ALU) devices, and system-clock coordination are presented.

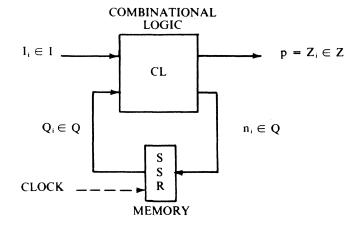

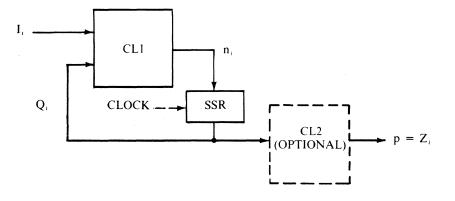

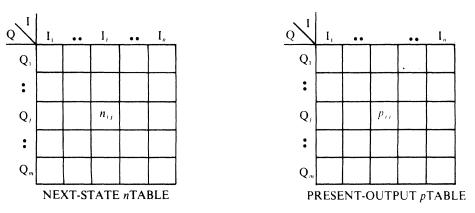

These structures are then incorporated into the larger architectural block-diagram structures of a processor system. The ALU is emphasized as the device that both transforms information and originates the system signals that control the conditional flow of software and state paths of the system. Chapter 4 reviews sequential machine theory and implementation, stressing the State Table form of representation and its relationship to microprogramming. The time spent on these chapters will depend on the students' prior exposure to hardware. It does not exceed four to five weeks with the author's students.

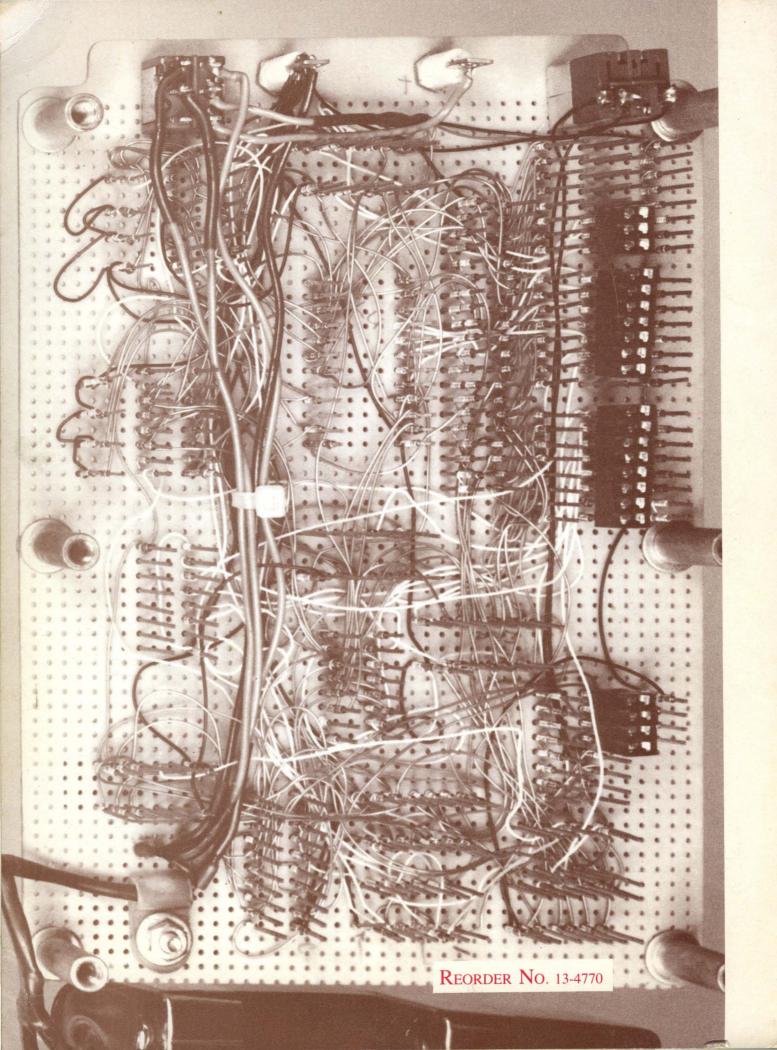

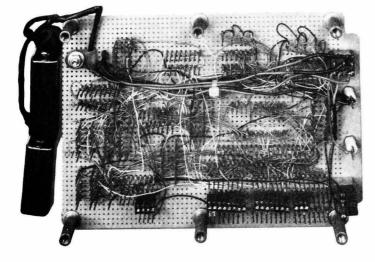

**Chapters 5 and 6** present the actual processor construction and microprogramming projects. The CPU is presented as the archetypical microprogrammable processor. Construction guidelines and a debugging overview are presented. It should be emphasized that the Central Processor Unit project has been constructed at home by computer science students and therefore requires no school laboratory facilities. A very simple wire-wrap tool and an inexpensive volt/ohmeter are all the student requires. The power-supply can be a 6-volt camping lantern battery and some silicon diodes. Several drilled holes and no more than five soldered connections are needed.

The wire-wrap form of construction is recommended as best for students who have little experience with hardware. Student feedback has made it clear that the hours spent handling each integrated circuit and consulting the data catalogs provide an extra dimension of "hands-on" experience. This exposure is especially helpful when the students are later required to work with the data catalogs of the programmable peripheral microcomputer devices, such as communications, disk, and Direct Memory Access (DMA) controllers. This good basic training has proved to be worth the time and expense of the project.

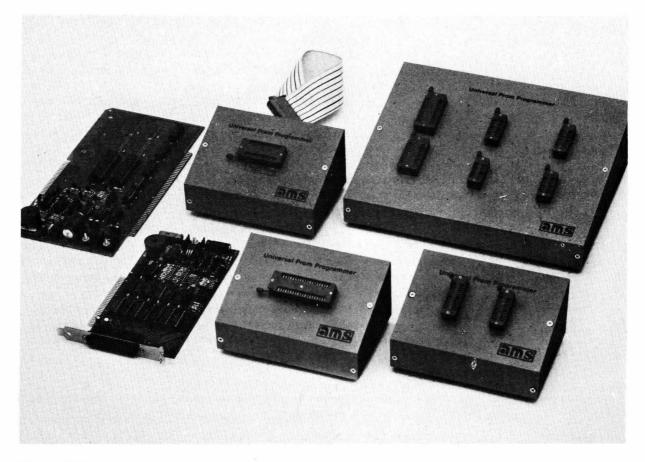

The author's computer science students have built the CPU portion of the project and demonstrated the switch-controlled operation of microcode, in a one-quarter course. The control system can be-and actually has been-constructed on an elective follow-up basis. It can, however, also be incorporated into a full-semester course. Very little extra construction is required for the control system. The advanced microprogramming activities of this phase of the projects require of the student great creativity, total systems understanding, and the drive to be innovative. These advanced activities require access to a PROM The last section of Chapter 6 covers the use of an IBM programmer. PC, with an aftermarket PROM programmer, for automating the development and demonstration of microprograms. (Aftermarket refers to components supplied by a secondary vendor.) Most flexible personal computer systems these days support the programming of PROM's (Programmable Read Only Memories). Advanced microcomputer hobbyists often already have such equipment.

#### A NOTE OF APPRECIATION

The drive to dominate the machine, as opposed to the reverse, grew out of actual hardware-innovation experiences with students, which the author would like to acknowledge here. In 1972 Xerox Corporation donated a 930 computer system on an "as-is" basis. This was a gift of considerable value. The author and dedicated students revived the system. They created a real-time operating system for it, with memory mapping and instructional traps, implemented interactive graphics, computer-aided drafting, etc. Their innovative hands-on hardware experiences had significant effects on industry. Companies were formed, jobs were created, and products most readers would be familiar with were marketed. It is impossible to name all these movers and shakers. They know who they are, and the author certainly remembers them. The author does, however, wish to acknowledge the many contributions from the students of the old Extracurricular Student Computer Lab-we all grew from our experiences with hardware and software basket cases. The author is appreciative because, after seventeen years in industry, another seventeen years in teaching could only offer the satisfaction of positively affecting the world we live in. These students provided that satisfaction-and then some.

# CHAPTER 1 OVERVIEW OF PROCESSOR ARCHITECTURE

## THE EVOLUTION OF COMPUTERS

The rapid pace of recent events, particularly in microprocessors, appears to make computing a completely new phenomenon to some. But computing is not new, nor has it always been electronic and digital in nature. For a better perspective, let us briefly review the historical background of computing.

There can be no doubt that the ability to predict seasonal variations was important to early man. Using data to predict is one form of computation. Cro-Magnon bone carvings, 300 centuries old, record the lunar cycles and seasonal changes noted by members of a hunting society, in relation to the flora and fauna of interest to them. While anthropologists may dispute some interpretations of these records, they definitely constitute an early form of data base-most likely used to predict seasons, migrations, and so on. Later agricultural societies were very dependent on the computation of the seasons and resulting harvest yields. Accurate astronomical observations, the development of some numbering systems, and their use in predicting seasons and accounting for harvests are, again, indications of data gathering for computational use. The likelihood that a few unscientific spirits were invoked to ensure the success of these processes only serves to indicate that ancient programmers may have shared something with a few modern ones. Thus we see our own natural propensities for computation applied to data collection, prediction, simulation, control, and the execution of events. These are the basis for the mechanization of applied computation. Efficient computation requires the application of advanced technologies.

### EARLY CALCULATORS

The early development of modern computation was extremely slow by today's standards. Much of the mathematics we use evolved before the existence of calculating machines, if we ignore our fingers and toes. The abacus was an early calculating instrument first used about the fourth century B.C. While useful for rapid addition of numbers, its chief advantage lay in its ability to "remember" partial results, thus enabling nimble fingers and unsure minds to perform tedious calculations. During the 1600s Schickhardt (1624), Pascal (1642), and Leibniz (1673) first developed the mechanical calculators that were widely applied in the 1800s, when the manufacturing technology was available. As technology evolved, these calculators were replaced by ones using solid-state devices. The industrial revolution is a reflection of our evolving ability to develop mechanisms for computational uses. The problem with these early calculators was that none of them had the ability to store a program. Each step had to be dictated by the human

operator-thus delineating the difference between these early calculators and the computers that followed them.

#### EARLY COMPUTER DEVELOPMENTS

Babbage's difference and analytical engines show that mechanical technology alone could not produce an effective computer. In the 1820s, Charles Babbage, an Englishman and a founder of the Royal Astronomical Society, became interested in developing a mechanical computer for the solution of mathematical equations. He was assisted in these efforts by Ada Augusta, Countess of Lovelace, after whom the programming language Ada is named. She is often referred to as the first programmer, but she was far more than that, for she understood the hardware, the software, and theoretical basis of the computer. They applied a good deal of thought and ingenuity to the task of designing a computer. The many original concepts developed foreshadowed the development of the modern computer. It is sad that, in the end, their valid concepts could not be incorporated into a useful machine because of the inability to hold to the required mechanical tolerances in its manufacture. These manufacturing obstacles were eventually surmounted by Scheutz, but the resulting machine's accuracy, speed, and cost would be unacceptable today. This is not to take away credit from these pioneers. New technologies and new concepts were necessary for further progress. Figure 1-1 displays some of these early calculators.

Some of the new concepts were provided by George Boole, who in 1854 developed an algebra of logic. This algebra was primarily of interest to mathematicians and philosophers until Claude Shannon published "A Symbolic Analysis of Relay and Switching Circuits" in 1938. Shannon dealt with relay logic, the technology of that day, as a result of his research in developing telephone switching circuits. Shannon made the first application of Boolean algebra to switching circuits, paving the way for it to become the important tool that it is today. Meanwhile, the need for an effective form of a stored-program digital computer was growing. We have to go back a bit in time to see how it evolved.

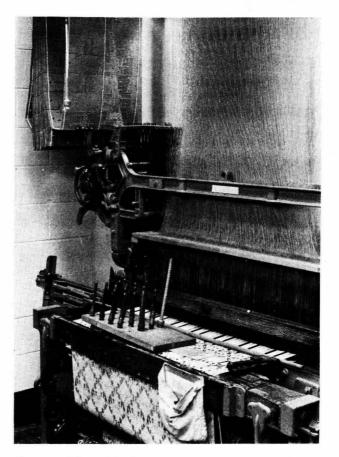

Babbage began work on his analytical engine in 1833. On a previous visit to France, he had seen the Jacquard looms in action, weaving fabrics. Jacquard developed this system of controlling looms by pasteboard cards with holes "punched" in them, in 1805. (See Figure 1-2.) Babbage was inspired by the Jacquard loom to formulate the design of his new engine, which was to use two sets of these punched cards. One set was the operation set of cards; the other, the variable set. Thus, the concept for the first computer was born. We now call the operation cards the program and the variable cards the data. Babbage was frustrated by the lack of an adequate implementation technology, but the machine he conceived became the basis for the Harvard-IBM Mark I computer, produced a century later. Jacquard's pierced pasteboards also provided the inspiration for Herman Hollerith's development of punched-card tabulation, used for the United States census of 1890. Hollerith, seeking a way to tabulate census data mechanically rather than manually, was advised to look at the Jacquard looms. In 1906 he founded the company that evolved into the International Business Machines Corporation. Tabulating systems had thus arrived, as well as their associated printer-listers, and they became common office

a. Abacus

c. Babbage's Difference Engine (Courtesy IBM Corporation)

equipment. This business office equipment was in turn used in the implementation of Babbage's concepts in the development of the Harvard-IBM Mark I computer (1939–44).

#### HARVARD MACHINES

The Harvard Mark I used relay logic; as an electromechanical rather than just mechanical device, it represents the beginning of the era of modern computers. The Mark I could multiply 23-digit numbers in about six seconds-not impressive by today's standards, but remarkable a relatively short time ago. One of its important tasks was the calculation and analysis of ballistics equations, a vital contribution to the nation's efforts in World War II. The success of the Harvard machines, the Mark I, II, III, and IV, spurred researchers to find even better technological answers to the problems of implementing computation.

The Harvard machines had two storage areas: one for the program and the other for data and results. The two storage areas were isolated from each other and were typically of different word size. These machines were termed automatic-sequence calculators and did not have the capability of modifying their own programs. They were dedicated special-purpose machines, whose principles are still used in many small microprocessors today. They are most advantageous in applications where the program is not expected to be modified during operation, such as in vending machines or toys. They also offer a hypothetical two-to-one speed advantage over the von Neumann-type machine, discussed next. This important advantage is based on the fact that the separate memories can be accessed simultaneously. Most 4-bit and some early 8-bit microprocessors are Harvard-type machines, huge numbers of which are still in use. Special-purpose high-speed dedicated processors, often called controllers, can use the Harvard (really, Babbage) approach to good advantage in their design. Today, the trend is to use the Harvard architecture in custom-designed integrated-circuit controllers (processors), where an inherent speed advantage can be an important consideration.

#### VON NEUMANN MACHINE

The shortcomings of the Harvard architecture were perceived in the mid-1940s by von Neumann, who recommended that a computer have only a single storage area for *both* programs and data. This gave rise to the prevalant form of digital computer extant today in business and scientific applications. Von Neumann's recommendations appear in a summary article (Burks, Goldstine, and von Neumann 1946) and are worthy of the reader's time. The essence of his idea is that, if a computer can operate on data, it can also operate on its own program, thus obtaining the ability to alter its course conditionally, *without operator intervention*, This was the beginning of the stored-program digital-computer concept, as distinct from the Harvard concept, discussed earlier.

Figure 1-2 The Jacquard Loom Photography by Jan Forman Philadelphia College of Textiles and Science

The very idea of letting a program operate on itself is repugnant to modern structured programmers, but it was a milestone in computer development and remains a powerful concept.

#### MICROPROGRAMMING CONCEPT

The late forties and the fifties produced many ideas on how to improve, design, and build computers. It was a decade of realization of what was practical in computation. Three-state logic devices (+, 0, -)were considered, for example, but these lost out because of the greater feasability of the two-state (on-off) transistor devices used today. Among the ferment of ideas produced in this era was Wilkes's (1951) concept of microprogramming. This important modification of the von Neumann concept was too powerful to lose out permanently in the feasibility contest. Rather, once a suitable modern implementation technology had evolved, Wilkes's concept became the rational basis for designing a computer's control system. Today, it is the internal organizational foundation around which we structure most processors, computers, and—what amounts to the same thing—microprocessors that the reader is likely to encounter. An applied understanding of microprogramming is a major goal of this text.

#### COMPUTER IMPLEMENTATION TECHNOLOGIES

Implementation technologies were rapidly improving. ENIAC, a Harvard-architecture program calculator, became operational in 1945. It was the first all-electronic computer, using vacuum-tube technology. EDSAC and EDVAC, von Neumann-type stored-program computers, became operational in 1949 and 1950. Subsequent development was extremely rapid; although interesting, the full details are beyond the scope of this book. By now, the major ways of organizing an architecture were well established. Let us then refocus on the development of implementation technologies. Digital computers were becoming better because we were finding better ways to implement them with emergent semiconductor technologies. The basic conceptual groundwork for the organization of the types of processor we are most likely to encounter had already been developed.

Tube-type computers are referred to as the "first generation." One could argue the point, if we consider the Harvard relay machines, but in fact they formed the first generation of stored-program digital computers, from 1950 to the early 1960s. In the early 1960s "secondgeneration" computers-based on transistor technology-came on the market. The "third generation"-based around small- and mediumscale integrated circuits (MSI)-began to appear in the late 1960s. The emphasis in that decade was primarily on how to build computers, for a lot was known about architecture, but there was little economical implementation technology available. Some very significant variations on von Neumann-type architecture were being developed, though. Noteworthy were Barton's concepts for stack architecture (1961), actual implementations of microprogrammed architectures, virtual memory, and interactive real-time computing. Each new "generation" of computers involved a reduction in size and power consumption by an order of magnitude. The need for air conditioning, for example, was once a major consideration. Figure 1-3 illustrates the relative sizes of these "generations" of computers. We shall not discuss here the evolution of programming and operating systems, except to note that they developed along with the increasingly available hardware.

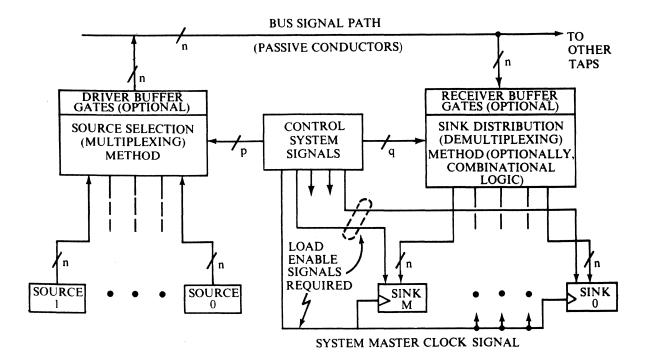

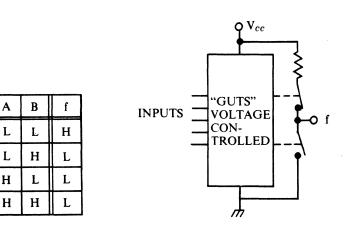

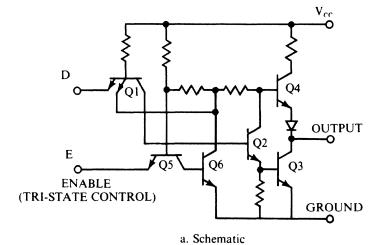

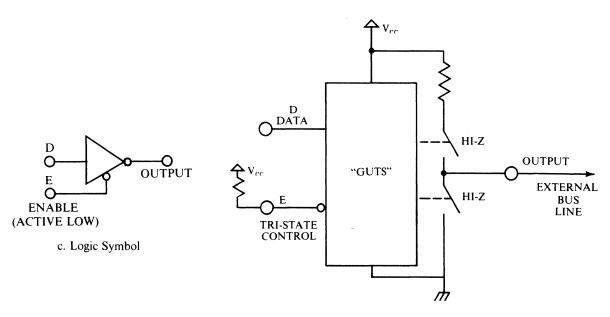

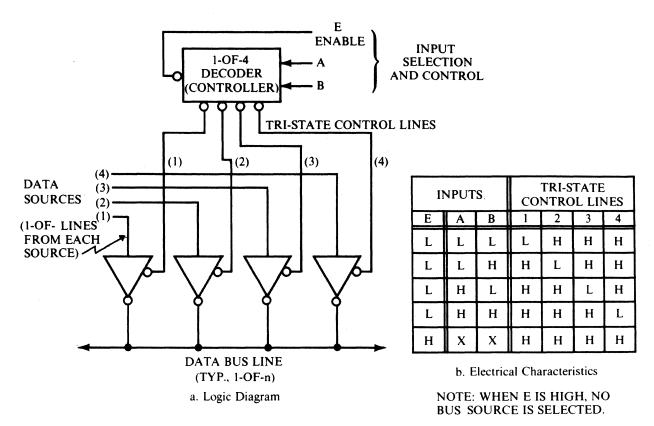

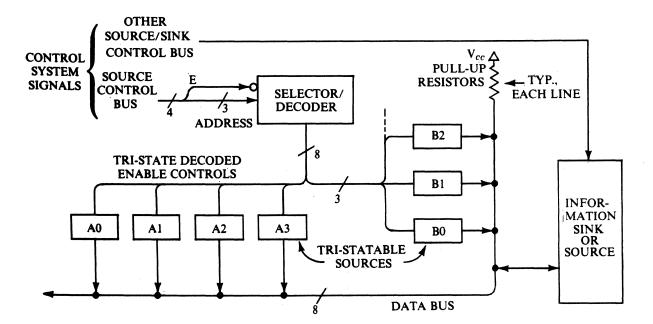

#### **BUS ORGANIZATION**

By 1970 part of the new hardware expertise developed concerned bus organization and *tri-state* logic. A *bus* is simply a data path for computer signals, consisting of one or more physical conductors of information. Bus organization includes the study of methods for timesharing the use of a single bus, thus reducing the total number of buses required in a given computer. *Tri-stating* is a means of interfacing separate entities to a time-shared bus. We shall study this important implementation technology subsequently. The combination of the ideas for bus organization and tri-state logic was widely applied in the 1970s. They became an important step in making microprocessors feasible. Bus organization is still a vital topic, involving federal standards, networking, multiprocessing, and many other aspects of computing.

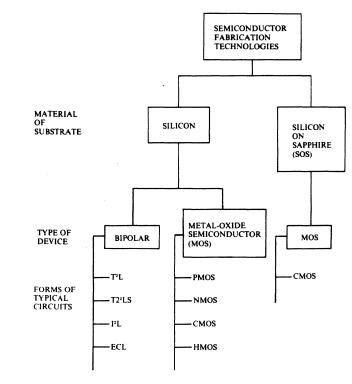

#### SEMICONDUCTOR TECHNOLOGY

Integrated Circuit (IC) manufacturing technologies continue to develop at an unabated pace. MSI combines the equivalent of several hundred transistor logic gates in a single design. Large Scale Integration (LSI) can put on the order of 10,000 transistor equivalents into a

**Overview of Processor Architecture**

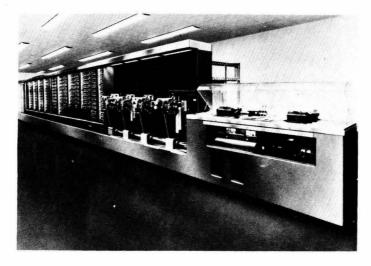

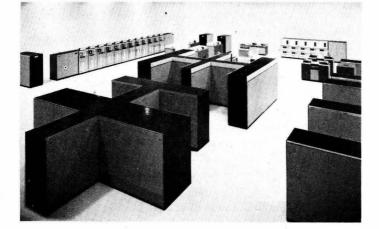

a. Relay Machine: The Harvard-IBM Mark I (Courtesy IBM Corporation)

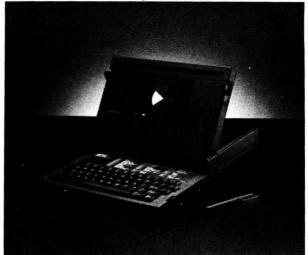

d. VLSI: GRiD Compass Computer (Courtesy GRiD Systems Corporation)

b. Tube-Type Machine: IBM 704 (Courtesy IBM Corporation)

c. Integrated-Circuit Machine: IBM System 360 Model 85 (Courtesy IBM Corporation)

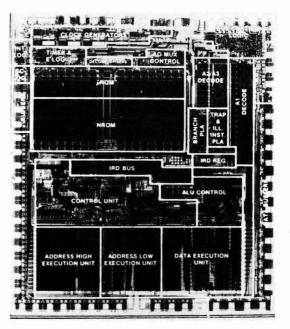

e. Modern IC Layout: Motorola MC38000 Microprocessor (Courtesy Motorola, Inc.)

Figure 1-3 Processor Development single monolithic structure. In the mid-1960s attempts to apply MSI and LSI technologies to commercial desk calculators were not fruitful, but these efforts led to the monolithic microprocessor in the early 1970s. As in the past, if we can calculate, why can we not compute? Thus, in 1971, Intel Corporation marketed the first microprocessor—the Intel 4004. It was a Harvard machine with a 4-bit data bus, and it contained the equivalent of 2,450 transistors on a "real estate" silicon chip 0.117  $\times$  0.159 inches in size. This led to the flood of microprocessors that continues to this day, as Very Large Scale Integrated (VLSI) circuits, approaching 500,000 transistor equivalents on a single mono-lithic IC, are produced.

#### PROCESSOR SYSTEMS

LSI and VLSI technology spawned another breed of processors besides the computer itself. These belong to the very important class of processor-support peripheral IC's. We have not only the computer in an IC today, but all the memory, communication channels, floatingpoint arithmetic processors, disk and display controllers, and so on, as well. Three important facts should be made apparent:

First, a computer is now a *system*, consisting of a collection of IC's ruled by the software and "firmware" created for it. The firmware is a program permanently recorded in a Read Only Memory (ROM).

Second, many of these IC's in the system are processors.

Third, by studying the organization and function of an archetypical microprogrammable processor, we can obtain an appreciation of all the others.

All these processors, combined into the system we call a computer, can be and in fact now are organized around a common set of microprogrammed design principles. An understanding of these principles is another of our main objectives in this text. Therefore, there is a common point of view through which we can gain an understanding of the design, function, and operation of all the processor-type IC's used in the modern computer. This insight is as essential to the programmer as it is to the hardware designer. It is not easy to write efficient code for the software that drives a synchronous communications IC, a disk controller, etc., without a secure grasp of the intrinsic nature of these devices.

Thus, with our technological advances in computing, we find that the distinction between hardware and software types is rapidly breaking down. This artificial distinction never existed for the creators, Charles Babbage and Ada Lovelace, who truly understood the nature of what they wrote programs for. They would have had no difficulty in recognizing that the modern computer is a *system* composed of a microprocessor and a collection of peripheral support IC's, all having many functional features in common. At this writing, one major producer is shipping 100,000 personal computers a month–each one having as much computing power as early mainframes and many minicomputers still in use. The microprocessor is not a "different" thing or a break with the past. It is a result of modern industry's ability to capitalize on past technological breakthroughs, now occurring at a bewildering pace. The development of the microprocessor has been so impressive that it leads to speculation about potential future applications. The microprocessor is becoming the mainframe computer of today. True 32-bit microprocessors are on the market now, with their full potential yet to be realized.

#### PERSONAL IMPACTS

And that is probably why you are reading this text. The utility of microprocessors (really, computers or just processors) is having a profound effect on our lives. Can any of us, whether software or hard-ware types, afford *not* to understand philosophically the tools by which we earn our livelihood? We all need insight into the intrinsic nature of these devices if we are to stay current in our respective fields and understand the world we live in. Perhaps our individual emphasis may not be on the computations of seasonal migrations, crops, ballistics, or astronomical calculations. These topics are still of interest to many. Our interests, on the other hand, might be on the business, scientific, educational, sociological, or even amusement aspects of applied computation. We are still interested in planning, controlling, simulating, and executing–except that highly sophisticated technology is now available to us for these purposes, on a mass basis, that would simply amaze the early pioneers–let alone Cro-Magnon man.

(Those of us with a strange philosophical bent may ponder what might have happened if Cro-Magnon man had turned his caves into video arcades, if he had had the microprocessor. This might have deprived us of some of our most moving works of art. The antitechnologist might presume that they would have planned anti-Neanderthal games with the computer.)

We have always been interested in computation, for better or worse. We can see the continuing evolution of the technologies used for applied computation all around us and, it seems, the evolution of our fascination with it. Table 1-1 summarizes this brief introduction into the history of computing. We hope that it also conveys a feeling for the rapidly accelerating pace of innovation that we are all caught up in. Some essential concepts, however, change only slowly. It is the innovative use of these concepts that avoids individual obsolescence. Our goal will be to gain an understanding of the fundamental concepts of microprogrammable processor organization. We will deal with the topic not hypothetically but rather in the very real terms of analyzing, implementing, and microprogramming an instructional 4-bit processor. In doing this, we can easily penetrate the mystique that still surrounds the computer CPU and other processors-to eliminate the "hardware fright" that accompanies a lack of understanding of these systems.

| Table 1-1<br><u>Historical Compu</u> | ting Perspective: Selected Key Benchmarks                                                                                                                                                                                       |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Year                                 | Event in the Evolution of Computers                                                                                                                                                                                             |

| 30,000 B.C.                          | Bone carvings show evidence of calculation of lunar                                                                                                                                                                             |

|                                      | and seasonal cycles by Cro-Magnon man.                                                                                                                                                                                          |

| 400 B.C.                             | Abacus first used.                                                                                                                                                                                                              |

| 1600-1700 a.d.                       | Schickhardt, Pascal, and Liebniz develop mechanical calculators.                                                                                                                                                                |

| 1805                                 | Jacquard loom uses "punched" pasteboards.                                                                                                                                                                                       |

| 1820                                 | Babbage conceives idea of difference engine.                                                                                                                                                                                    |

| 1833                                 | Babbage conceives idea of analytical engine. Device                                                                                                                                                                             |

|                                      | never built due to mechanical complexities. First true                                                                                                                                                                          |

|                                      | computer concept, using punched pasteboards for program storage.                                                                                                                                                                |

| 1854                                 | Boole developes an algebra of logic.                                                                                                                                                                                            |

| 1890                                 | Hollerith uses punched cards for 1890 census tabula-                                                                                                                                                                            |

|                                      | tion; later founds IBM Corporation.                                                                                                                                                                                             |

| 1938                                 | Shannon publishes "A Symbolic Analysis of Relay                                                                                                                                                                                 |

|                                      | Switching Circuits." Applied logic design flowers as a result.                                                                                                                                                                  |

| 1939–1944                            | Harvard-IBM Mark I-IV computers-relay logic imple-                                                                                                                                                                              |

|                                      | mentations of Babbage's concepts.                                                                                                                                                                                               |

| 1945                                 | ENIAC-Harvard-type tube computer.                                                                                                                                                                                               |

| 1946                                 | Von Neumann concept of stored-program computer                                                                                                                                                                                  |

|                                      | architecture published.                                                                                                                                                                                                         |

| 1949                                 | EDSAC-first von Neumann-type computer becomes                                                                                                                                                                                   |

|                                      | operational, using vacuum-tube technology.                                                                                                                                                                                      |

| 1952                                 | Wilkes proposes microprogramming as rational                                                                                                                                                                                    |

|                                      | approach to computer control-system design.                                                                                                                                                                                     |

| 1950s                                | Tube computers-first generation.                                                                                                                                                                                                |

| 1960s                                | Transistor computers-second generation.                                                                                                                                                                                         |

| Late 1960s                           | MSI technology employed: 1,000 transistor equivalents<br>on a monolithic IC.                                                                                                                                                    |

| 1960s-1970s                          | LSI technology employed. 10,000 transistor equivalents<br>on a monolithic IC.                                                                                                                                                   |

| 1968                                 | Calculator IC's produced.                                                                                                                                                                                                       |

| 1971                                 | First microprocessor produced (Intel 4004). Harvard-                                                                                                                                                                            |

|                                      | type 4-bit machine.                                                                                                                                                                                                             |

| 1970s                                | Personal computers. Processor-design methods applied to peripheral-support IC's.                                                                                                                                                |

| 1980s                                | VLSI in production. 500,000 transistor equivalents on<br>an IC. Microprocessors perform mainframe functions.<br>16-bit and 32-bit machines produced on a single IC.<br><i>Wall Street Journal</i> reports on personal computers |

|                                      | almost daily.                                                                                                                                                                                                                   |

# ARCHITECTURAL TYPES AND THE CYCLE OF COMPUTATION

In sketching the evolution of computers, we have referred to three major types: the Harvard architecture, the von Neumann approach, and its modification-the Wilkes's concept of a microprogrammed architecture. As noted, all three methods of organizing a processor's architecture are currently used. This categorization by major type

(Harvard vs. von Neumann) is apparent to a user who observes operational behavior. The recent VLSI processors are internally constructed on the basis of microprogramming principles, due to their complexity and this design method's simplicity. A review of the basic architectural features of these types, with comments on behaviorial characteristics, is in order. In the end, we shall study the microprogrammed type in depth.

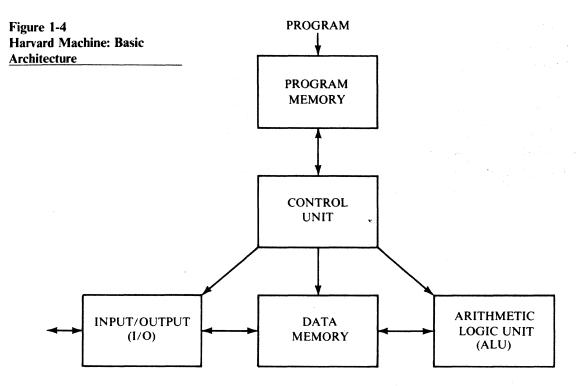

These architectural types may be reduced to their fundamental architectures. Figure 1-4 presents the essential block diagram for the Harvard architecture. Note that the control section communicates with all other blocks. It issues the command signals that dictate performance. The arrows of the diagram are important because, in this case, they indicate that the completely separate program memory communicates only with the control unit and not with any of the other structural blocks. There is another, also separate, memory for storage of data. These two typically possess different word sizes. They are not expected to communicate with each other, in normal operation. Of particular significance, in this Harvard approach, is the fact that the ALU does not interact with the program memory at all: no path exists for the ALU to operate on program information. The Input/Output block (I/O) transfers information between the data memory and the "outside" world." The ALU performs all transformations on data. That is, all arithmetic and logical manipulations take place in this block. It contains only combinational logic and no storage. It receives data from and returns it to the data memory. These are the basic blocks of the Harvard machine.

Already, the features of the Harvard machine that could affect our selection of a processor begin to emerge. First, its program is fixed in the program memory. The program is not dynamically alterable during operation, because only the ALU contains the power to alter information, and no path exists between it and the program store. We can expect this architecture to lend itself best to the less

11

complex, unchanging types of applications—as noted, toys, terminals, microwave ovens, etc. Somewhat less obvious is the fact that both memories may be active simultaneously. That is, the data memory may be used to fetch the current instruction's data at the same instant that the next instruction in the program store is also being fetched. While this inherent two-to-one speed advantage is not fully realized in practice, the fact remains that—for the same implementation technology and clock rate—Harvard machines can be faster than von Neumann machines.

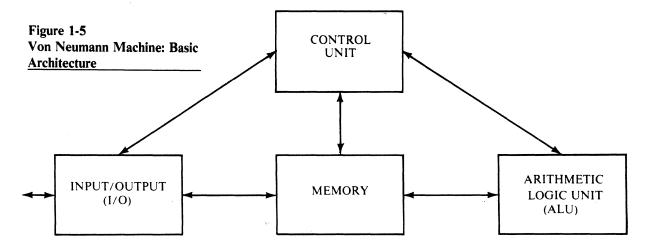

Figure 1-5 presents the von Neumann concept's fundamental block architecture, which contains the broad applicability features of the stored-program digital computer. In this case, we have only one memory system. Both data and instructions reside in this single memory. In their formats, both use the same-sized unit of addressing to communicate with memory. The first important ramification of this is that, if we look at a random location in memory, we cannot be sure whether the bit configuration is an instruction or merely data that happens to look like an instruction. This implies that we need a tool to separate instructions from data. This is provided by reserving one of the memory locations for use only as a Program Counter (PC), the function of which is to keep track of where the next program step resides in the rest of the memory. The second ramification is that, since the instructions reside in the same memory as the data, they can also be transformed by the ALU. Now the machine can dynamically alter its own program. The other essential blocks perform the same functions as in the Harvard architecture.

A disadvantage of the early von Neumann machines was that they were constructed on a *hard-wired* basis. That is, the instruction set was a fixed, wired entity. Obtaining a large and modifiable set of instructions requires resorting to microprogrammable-design methodology. Even though Wilkes's concepts on microprogramming, as a rational approach to the design of a computer's control system, were well known by 1952, they did not achieve widespread use until semiconductor Read Only Memory (ROM) technology became very economical. Actual implementation of computer concepts has often depended on the availability of suitable fabrication technologies. The microprogrammed architecture is the last one we shall consider at this point, but we shall work with it in the remainder of the text. This is not a separate architecture from the von Neumann approach, only a better way to implement it.

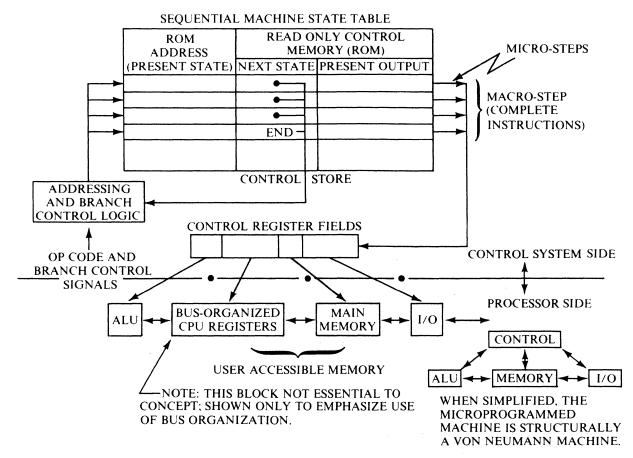

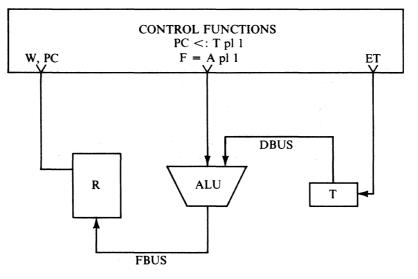

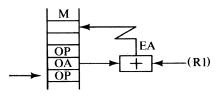

Figure 1-6 Microprogrammable Machine: Basic Architecture

Figure 1-6 portrays the organization of the Wilkes's microprogrammed architecture, stressing its State Table organizational features. Many simple things appear complex because they are sophisticated. This figure contains more detail than is comprehensible right away. Since it is the system we really aim to explore, let us introduce some of this detail in an overview. A ROM is the key feature of its control system. Again, we have a processor with two separate memory systems. The main memory contains both the data and the program's instructions that are to be executed during operation. The ROM memory is referred to as the Control Store. It, too, contains instructions, but of an entirely different class. These instructions are the sequence of marching orders that control the step-by-step operation of the system. Each discrete control order is properly termed a microstep. A collection of these microsteps, sequentially issued, forms a *macro* (or algorithm) that the machine performs. These macros contain the processor's sequence of orders for the execution of an instruction that has been fetched from main memory.

The collection of macros that reside in the control store makes up the stored algorithms for the step-by-step execution of each instruction of a program. This collection of macros makes up the *instruction set* of the system. It is of utmost importance to realize, at the very outset, that the contents of the control store ROM must have the form of a state table for a sequential machine. After all, a processor is a sequential machine that can be described (and controlled) by its state table. Each instruction step in your program is sequentially presented to the control store. The control store, figuratively, says "Aha! so that's what you want me to do. O.K., I will look up the steps for performing

your program's instruction in my State Table, and I will sequentially issue them to the hardware of the Central Processing Unit (CPU)." Therefore, your instructions in the program lead to the selection of the sequence of steps, found in the state table of the control store, that actually get executed. This addressing of control store's ROM and the subsequent receipt of a word (a command) are stressed in the figure.

If we analyze Figure 1-6 closely, we find that we can reduce it to the essential blocks of the von Neumann architecture, as shown. It only looks complex, now, because we have prematurely enlarged upon the details associated with the control system, to introduce its fundamental block structure and state-table organization.

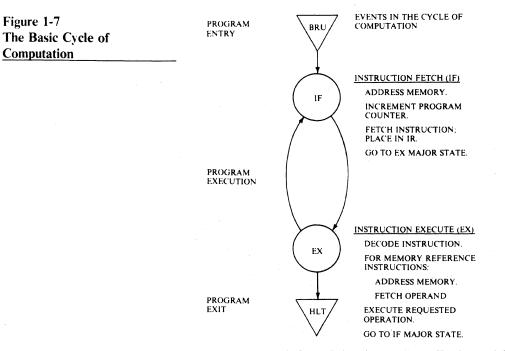

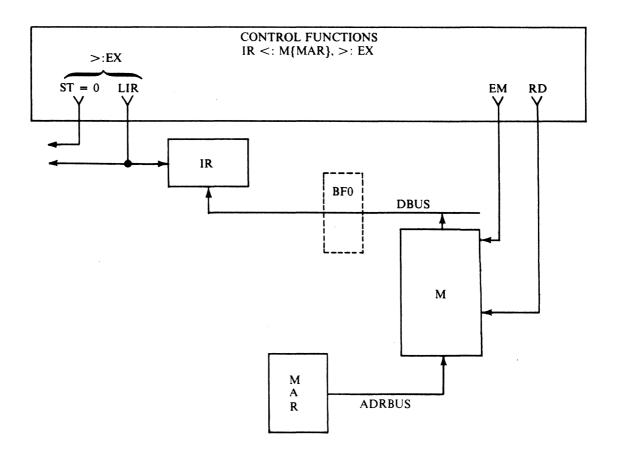

CYCLE OF COMPUTATION

Because architectural types are capable of affecting the computer's sequence and timing of the events in a cycle of computation, we must define this cycle. We shall do this for the architecture of interest in this text, the von Neumann architecture. A processor is a sequential machine. That is, it is a machine that can be in a finite, albeit large, number of states or conditions. Each "next state" of the system must be predictable from a knowledge of the "present state" and the "external inputs" applied to it in this state. For every input, the system must possess a defined state path. This information is contained in its control store. While we discuss these points in more detail later, the overall behavior of the computer can be reduced in complexity by considering its *two major states*—Instruction Fetch (IF) and EXecute (EX). All other states are minor states within these two. This is instructive because we can simply display the principal occurrences in a single cycle of computation in relation to these two major states.

The cycle of computation is portrayed in Figure 1-7. How is the cycle initiated? Let us assume a simple case, in which the operator has loaded the program to be run into the computer's main memory and has given the PC an initial value, which is the program's entry point.

The front-panel controls are assumed to have these capabilities, as in the old-time computers that required an operator. By way of initializing the PC, the operator could set the console switches to order the system to perform a BRanch Unconditional (BRU) to some starting address. At this point, the operator hits the Run switch and stands back. The cycle of computation's sequences commences with the operator's BRU command. The BRU execution consists of placing the branch address of this initial instruction, forced by the operator, into the PC. Thereafter the machine behaves as shown in the figure until a HALT instruction, say, is encountered.

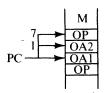

After the execution of the forced BRU, the machine automatically enters the IF major state. The system PC is now pointing to the memory location of the next instruction to be fetched. The essential events of the IF sequence are shown in Figure 1-7. The first event is to address memory by transferring the contents of the PC to the Memory Address Register (MAR). MAR is another portion of the system's memory reserved for a special purpose. This register only selects a location to be communicated with in main memory. It does not handle data. Since this address came from the PC, the contents of this memory location had better be a valid instruction. Let us assume, as in early computers, that each word in main memory contained the complete instruction format. The second event performed in the IF state is to readjust the PC so that it will point to the next instruction in main memory. This is done by incrementing its contents. Now, the PC is looking ahead again. As we use the PC, we also increment it. MAR still contains the original contents of the PC or the address of the instruction we wish to fetch. In another event, we read the contents of this location and transfer it into the Instruction Register (IR). The IR, like the PC, is yet another example of a dedicated specialized use of the system's generalized memory. In the final event, the system ends the IF phase by issuing the command to proceed on to the Execute (EX) phase of operation. We stress the point that a small portion of the system's total generalized memory is dedicated to these special usages.

These four events of the IF phase of operation occur on every von Neumann-type machine. Some of them may be performed in parallel, so it is not always true that a particular machine requires four separate clock pulses to complete the sequence. The control system records the fact that the EX state has been entered. In the EX state, it looks at the contents of IR and figuratively says "You want me to do that!" and so on. From decoding the contents of IR, it now can find the macro in its control-store state table for the sequential execution of "that." The OPeration portion (or field) of IR is, in reality, the encoded address of a macro's starting location in the control store. The last step of every macro contains an END order, to return the system to the IF phase. The system continuously cycles through this cycle of computation-IF to EX, and back again. Each time the machine returns to the IF state, the PC must already be conveniently pointing to the address of the next instruction. The microprogrammer that creates an instruction (macro) is responsible for properly advancing the PC; we shall practice this later.

In the EX major state, the processor may have to use memory again. This is important to recognize, since about 85 percent of all instructions are memory-reference instructions. That is, the instruction word itself contains a field that provides the address of an operand. In this case, the address field of the instruction is transferred to MAR Figure 1-8 Memory Map of a Program's Blocks

during the EX phase. The object, a piece of data, is brought in from memory to be operated on in the course of executing the instruction. Memory, then, is typically accessed *twice* within the full cycle of computation. The first time, during IF, was for the purpose of fetching the instruction (which usually contains an operand address). The second time memory is accessed, if the instruction mandates this during the EX state, the data to be operated on is fetched. Therefore, two memory accesses in a single cycle of operation are usual. This is natural, since *both* data and instructions reside in main memory.

The novice should carefully study the events in the cycle of computation, until they are fully understood. This cycle is the basic description of the operation of the von Neumann-type computer, the type of architecture used in most personal or business computers. It also illustrates when and why memory is accessed—usually twice during the cycle of computation. An understanding of these events is essential to the microprogrammer's proper control of the PC. It also leads to an appreciation of how a given system actually executes a particular instruction.

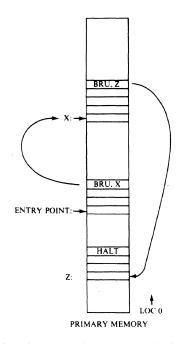

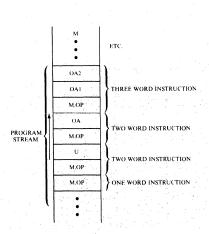

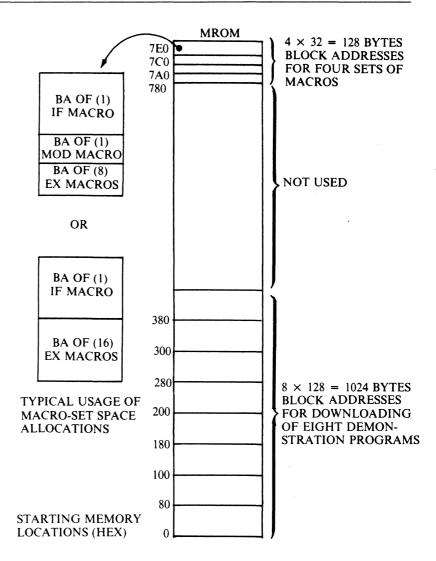

The von Neumann architecture's cycle of computation also tells us something about the way memory space is utilized by this type of machine. We can now see how a program is mapped into total mainmemory address space, shown in Figure 1-8. Since the PC carries the information of where the instructions are in memory—and since the PC is incremented only during the cycle of computation—one instruction *must* follow another in memory, except for branches. That is, instructions reside in contiguous locations in main memory. These contiguous locations of instructions may be formed into blocks of memory. For a given program, these blocks are linked by the address fields of the branch (or jump) type of instruction. Recall, the execution of a branch instruction simply amounts to a reloading of the PC. The rest of memory that is not occupied with blocks of instructions may now contain the data these instructions access or the results they store.

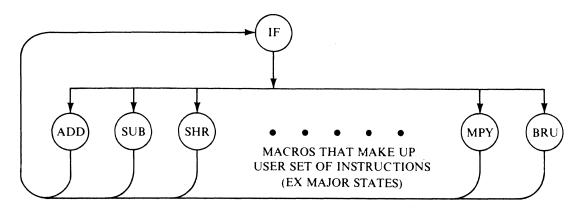

The cycle of computation simplifies the computer into a machine with two major states. This state diagram may be slightly expanded to

Figure 1-9 Expanded IF-EX Major State Diagram

better represent the actual case, as is shown in Figure 1-9. In this illustration, we have only one IF major state. After all, IF is IF, and we need only one copy of it in the control store's state table. However, the other macros in the user's instruction set are not used in every cycle of computation. Therefore, we require a separate state-table segment, in control store, for each macro of the EX major state. The actual cycle proceeds, in IF, to the fetch and subsequent decoding of the instruction word. This decoding process, during the EX major state, selects the particular macro specified in the instruction word. That is, the system executes only one user macro at a time and then returns to IF to fetch another. IF therefore is not categorized as a user macro. It is transparent to the user. Nevertheless, it is a macro-automatically invoked and performed by the system in the course of executing our programs. In a microprogrammable system, anything that the machine is capable of performing must be a macro residing in the state table of control store. We shall refer to the above cycle of computation as a basic frame of reference many, many times.

# FORMS AND UNIFORMITY AMONG PROCESSORS

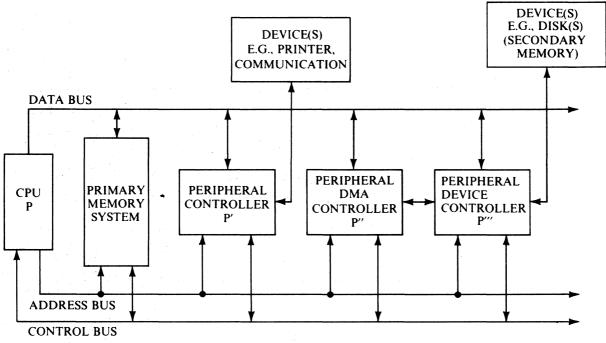

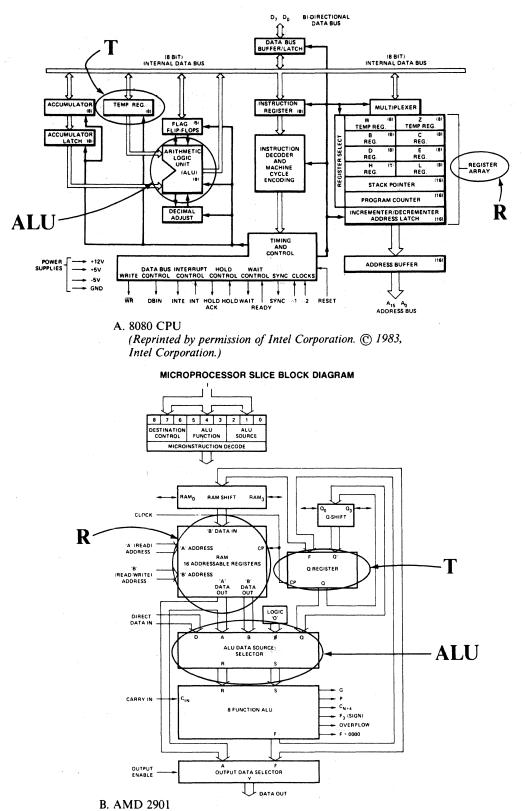

Having reviewed the major basic architectural types among computers which, as we have said, are one form of processor, we may now consider the question-what is a processor? We propose to answer this question in detail in this text by examining the internal organization, microprogramming, and functioning of an instructional archetypical Central Processor Unit. The essential structure of this CPU's architecture will be shown to be closely related to that of the Intel 8080 microprocessor, the DEC PDP-11 minicomputer, the AMD 2901 bit-slice IC, etc. Therefore, we are stressing the universality of the principles behind the organization of a processor. Here, we must be careful to distinguish between the organization of a computer's CPU and that of the total computer system. Briefly put, the organization of a computer system largely consists of the CPU and a number of other processors; a means of intercommunication, the so-called busing structure; and the system software that is executed by the CPU to coordinate the whole. Our emphasis is on the concept of the generalized processor and its essential characteristics.

To be more explicit, let us examine the block diagram of a computer system, Figure 1-10. This figure displays channelized computersystem organization, in the form most commonly seen in microcomputer systems. Variations of this structure are applied to large, so-

NOTE: P ... P''' ARE ALL PROCESSORS.

Figure 1-10 Channelized Computer Systems Organization called mainframe computer systems, as well as to small systems. It is a universally used form of organization and could be the starting point for a discussion on operating systems and their environment. What we wish to highlight now, however, is the large number of processors present within the system. The term CPU itself implies that a computer system consists of a central processor and a number of other ones. These other processors are the peripheral controllers whose coordination is orchestrated by the CPU. As shown, these processors peripheral to the CPU are of two types–Direct Memory Access (DMA) and those with indirect access to memory. By *access* we mean access to the system's primary memory–as opposed to access to mass-storage devices or to secondary memory, such as disks.

The indirect-access processors exchange data with primary memory via the CPU. The direct-access processors can assume direct control of primary memory for a transfer of information between it and another entity that does not involve the CPU.

Our point is, then, that a computer system consists of a number of processors, coordinated by the system's software. The peripheral processors are the Arithmetic Processor Units, the DMA controllers, communications controllers, disk (secondary-memory) controllers, graphics controllers, and others. These days, they are most often sophisticated programmable devices housed in a single IC. Any one of them can be as complex as the CPU. An 80-bit floating-point arithmetic processor peripheral is as complex as most CPU's. So far, we have said that these processors are all sequential machines. We will study the organization of the microprogrammable form of the CPU to learn what a processor really is-and we do mean what it really is. If we understand this one, we will have gained an intuitive feel for all the other forms of processors, for they all reduce essentially to sequential automata. In developing microprograms for an instructional CPU, we have to display an intimate knowledge of sequential machine behavior. If we gain an appreciation of the essential common features of processor organization, then we should be better prepared to understand, work with, and program the other processors of the total computer system. This information is also a background for the synthesis and implementation of processors.

Thus we consciously used the term processor-as opposed to computer, microprocessor, dedicated processor, arithmetic processor, DMA - channel, etc.-to stress the unity of their fundamental design and function. They are all sequential machines. Chapter 4 reviews sequentialmachine principles, because the fundamentals of sequential automata are the foundation for our understanding of processors. Microprogramming is a generalized approach to their design that, with today's emphasis, can have a strong software component. We wish eventually to explicitly illustrate how a microprogrammable type of architecture is implemented. Its basic nature is no different from all the other types of processors, regarded as sequential machines. An internal or even a user-accessible microprogrammed memory, used as the core of the sequential machine's control system, is an integral part of most present large-scale systems organizations. Via the techniques of microprogramming, we can view the rationalization of control-system design for processors as one of the technological advances that has made VLSI fabrication feasible.

Let us briefly look at the external physical details of a processor, as represented by some microprocessors. They are usually classified as members of one of the three previously mentioned architectural types. That is not to say that other important architectures do not exist. The array processor, for example, has a distinctly different systems organization, yet its individual functional blocks likely behave as a member of one of our major categories. Do microprocessors differ from what we mean by *computers*? Not really-the differences are only of degree, not kind. They still are computer-system processor units, implemented today through VLSI technology. The differences are variations in physical size, word size, instruction formats, program throughput, and the complexity of the instruction set. A microprocessor's instruction set now may be as sophisticated as any of the older mainframe computers. Even its bus and word size have entered the 32-bit region, formerly the domain of the mainframe. The speed and corresponding productivity of the microprocessor can be much better, due to the physically small, monolithic nature of its IC. The fact is that microprocessors are beginning to replace mainframes, in many applications. The mainframe will still be around in the future, but it will be a *main*frame.

Some physical statistics for a few IC processors are of interest. They indicate advances in fabrication techniques-rather than the essential nature-of processors. The first production microprocessor, the Intel 4004, came in a 16-pin Dual In-line Package (DIP), whose external measurements were  $0.30 \times 0.78$  inches. The silicon surface area (the amount of silicon "real estate") used for the fabrication of the actual IC measured  $0.117 \times 0.159$  inches. The number of active devices contained within this area, in several layers, is referred to as the number of *transistor equivalents*. The 4004 contained on the order of 2,500 transistor equivalents. Its word size was four bits: that is, the data bus handled and it internally operated on four bits of information at a time. It was followed by the 4040 microprocessor, packaged in a 24-pin DIP, externally measuring  $0.6 \times 1.25$  inches. The microprocessor surface area size measured only 0.118  $\times$  0.163 inches. The Motorola 6800 8-bit microprocessor was packaged in a 40-pin DIP measuring  $0.6 \times 2.0$  inches, as was the Intel 8080 and most other 8-bit microprocessors. The Intel 8086, a 16-bit machine, was also packaged in the same size 40-pin DIP. Many of the peripheral support processors are also packaged in the 40-pin DIP. For a time, 40 pins was the practical limit to package size. Current packages are larger, with approximately 60 interface pin connections. As manufacturing technologies have improved, more and more logic has been designed into the monolithic IC. The 8086 contains on the order of 80,000 transistor equivalents. The Intel 80286 16-bit processor contains approximately 130,000 transistor equivalents. The current frontier is about 500,000 transistor equivalents in a single monolithic IC.

Because of the growing sophistication of microprocessors and the limitations on package size, extensive time sharing of the interface pins was resorted to. Time sharing of an interface pin, also called *Time Division Multiplexing* (TDM), is frequently employed to reduce the number of required interface connections. Generally, manufacturing and reliability problems increase with the number of interface connections. TDM typically allows a particular interface pin to function, say, as an address-bus line in one clock period—yet serve as a data-bus line in another. TDM is common practice, often confusing to the beginner. It may help to imagine that an interface pin can be switch-connected to an internal address bus in one time frame, then to an internal data bus line in another. Thus, a single interface connection performs entirely different functions at different times.

All the preceding indicates two things. First, today's microprocessor is becoming the previous decade's smaller mainframe, because of the amount of logic a monolithic IC may now contain and because of improving design methodologies. Second, the typical processor of today is housed in a monolithic IC-from peripheral controllers to the CPU's of microprocessors and mainframes. What we hope will become apparent in the course of this text is the role of the techniques of microprogramming in the creative shaping of the functions these processors can perform; equally important is the fact that we can be in control of the specification of these functions.

We now also raise the rhetorical question: How does one learn about these production processors? The answer is that, after the introductory orientation of a text, we read manufacturers' data manuals. Much of the material of many good texts is obviously derived or even taken straight from the data catalogs of these IC's, unadulterated. We must stress the importance of learning how to go-independentlystraight to the source, thus gaining self sufficiency.

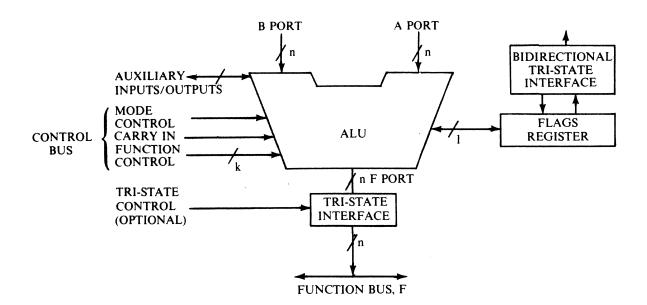

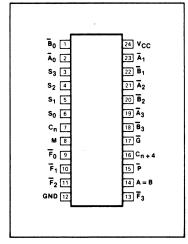

Mention should be made of a special group of processor IC's, the bit-sliced-based dedicated controllers, CPU's, and computer emulators. They have played an essential role in the technology of computation, with less publicity than the mainframes and microprocessors. These processors have been organized around the use of *bit-sliced* architectures. The bit-slice is a basic bus-organized central processor unit, containing only an Arithmetic/Logic Unit, a register array, and a general-purpose load and shift register, with associated bus paths and combinational logic. It does not have a control system built into it. The user supplies this, via microprogrammed design. In creating a computer or dedicated processor with these bit slices, we simply employ as many of the slices (in parallel) as we need to achieve the desired machine size. Typically, we now add to this a microprogrammable

control store, to form the processor's control system. The resulting machines have been used to create dedicated controllers, such as highspeed disk controllers. They have also been used to create fast emulators of existing older mainframes and to form specialized computers, such as those employed in avionics applications.

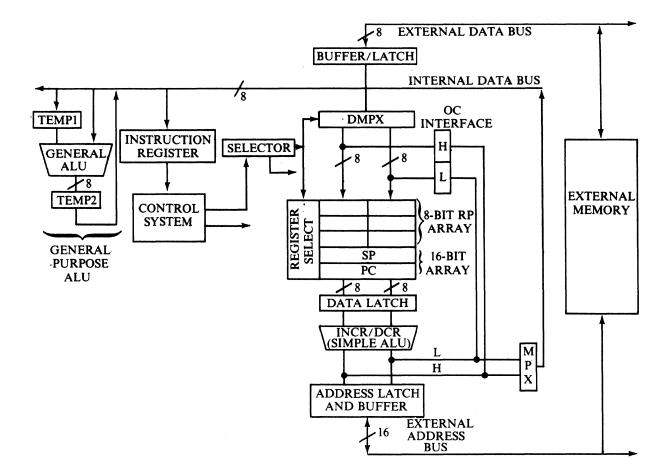

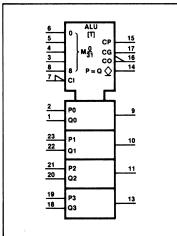

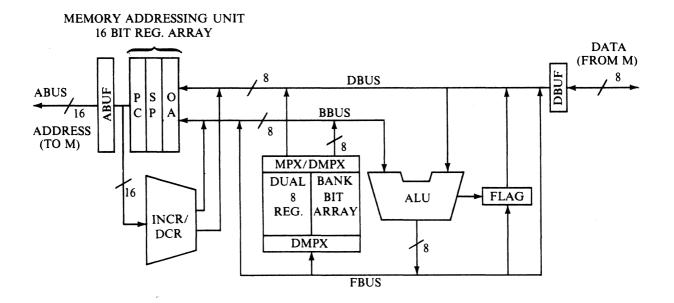

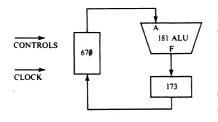

A popular bit slice has been the Advanced Micro Devices Am2901 and Am2903 4-bit slices, housed in the same 40-pin DIP as many of the other microprocessors and peripheral controllers. There is a family of other related IC's that support the creation of the total bitsliced processing system. This means that the designer forms a processing system, using several different types of IC's. In this do-it-yourself approach, the processor is not a single IC but consists of several coordinated IC's from the family. The control system that we shall study and implement here reflects the function and nature of these other IC's in the family. The 4-bit processor we shall study, construct, and microprogram is a simplified model of a bit-sliced IC. As we shall see, our own archetypical processor project will be a bus-organized CPU containing a Register Array, an ALU, and a few dedicated registersmuch like the bit slice. To this we will add a microprogrammable control store for sequential behavior control and an external memory system. These major structural features form the basis for the type of processing system we call the computer. It is a hands-on, nonhypothetical approach to the subject matter.

At the present writing, a new trend has emerged-due to the availability of advanced VLSI IC-development technologies. It is now possible for any of us to specify and design custom processor IC's. This, too, is a do-it-yourself approach to the design and implementation of custom IC's, which relies on the very same system structuralblock approach we shall consider here. Many applications-communications, disk and instrument controllers, for example-have sufficiently high production volumes to justify the development of custom processors in the form of the monolithic IC. We can apply the same organizational principles of microprogrammable systems to this task, too. This important phenomenon is one indication of the spread of processor design and implementation knowledgeability to the mass production, low-cost stage that each of us can participate or lead in. It is now realistic for us to anticipate our own involvement in any of the design, microprogramming, and software-development phases of processorcontrolled products-provided that we understand the systems organization of the archetypical processor.

From the discussion so far, we see that processors may be anything from a simple dedicated controller to a microprocessor to a computer mainframe. To understand this myriad of devices, we need a common center of reference. This we provide by examining the sequential machine organization and microprogramming of a 4-bit CPU. The applied microprogramming-systems principles that we shall study are exactly what a processor is organized around—this is the unifying factor, which encompasses both hardware and software. These processors may be used for many different purposes, but their fundamental sequential-machine organization is the same. Our view, then, is that processors consist of the systems application of a set of principles for the sequential-machine organization of computation and control. Differences are largely due to scale and end-function adaptations, rather than to their essential features.

Let us now proceed on to an important examination of the *apparent* difference of form between the instruction word formats among those processors we refer to as computers. A computer is a processor that contains a large, flexible, instruction set suitable for multipurpose adaptation, via user programming, to a variety of applications. These range from the 4-bit microprocessor to the 64-bit or larger mainframe. Common word sizes in microprocessors are 4, 8, 16, and now 32 bits. Minicomputers typically have 12- to 18-bit word sizes; mainframes are considered to have 24-bit and larger word sizes. An early number-crunching machine even had 128-bit words.

It is totally incorrect to say that microprocessors are slower than mainframes. The frequency of the driving clock for a microcomputer is often greater than that of a mainframe system. Execution times, say, for addition, are often comparable—even better. The real differences in performance, for a given clock rate, depend on the number of bits operated on at a single time in the process of executing a command. An 8-bit micro adds two 8-bit quantities in one clock period, while a mainframe may handle two 48-bit values in one period. By using repeated addition (with carries), the microprocessor can add two large 48-bit numbers just as well as a mainframe. Since this also requires a good deal of thrashing about between I/O, memory, register exchanges, etc., many extra operations are performed by the smallword machine to obtain the same resulting precision. If the small machine is not superfast, then its *throughput* suffers in comparison with the large machine.

Throughput is a key criterion of application performance. In measuring throughput, we refer to the techniques for evaluating how long it takes to process a set of problems relative to some proposed application. Two machines of the same word size may perform in significantly different ways in a given situation, often due to differences in their instruction sets. This important aspect of processor evaluation is called *benchmark* testing. A number of firms specialize in providing benchmark tests for competing processors for given applications. In practicing microprogramming, we shall *implement* an instruction set. This will create an acute awareness of the effects of architectural design and of the choice of instruction sets on the speed of operation, which affects a system's throughput.

The monolithic-IC computer often utilizes a clock frequency significantly higher than that of distributed mainframes. Associated with it is a smaller word size. It has to hustle to obtain the same throughput. Therefore, the distinctions between word sizes, instruction formats, instruction words, and the addressable unit of memory deserve to be discussed here. We will constantly be dealing with these concepts later.

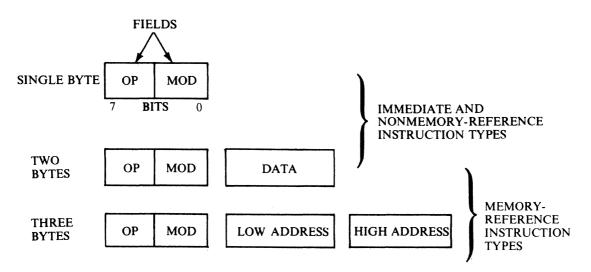

Figure 1-12 Eight-Bit Microprocessor Instruction Formats: Typical Fields Further, these concepts begin to make it clear that *apparent* differences are not fundamental ones.

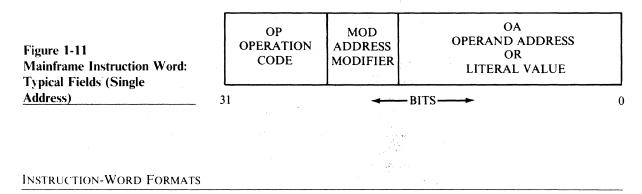

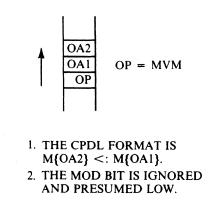

In the early computers, instruction formats were straightforward. The complete instruction word was stored in a single word in memory and could be held in a single register within the CPU. The format of this instruction word, however, is invariant for most machines of interest to us. That is, they all are divided into the same sets of fields. This is presented in Figure 1-11. The typical complete single-address instruction word consists of three subfields, as shown. These fundamental fields are the OP code, MODifier, and Operand Address (OA) fields. Two- or three-address machines simply make repeated use of one of these field types-the OA field. The OP field contains the binary code naming the operation to be executed. The OA field contains either the address of an operand or some value specified in the program. Whether this field contains an address or a value depends on the nature of the instruction specified in the OP field, that is, on whether the instruction is ADD or SHIFT. If the OA field is in fact an operand address, then the MOD field is used to specify how the final Effective Address (EA) is to be calculated. The MOD field specifies the addressing modes we can select for our programs.