### μPD70008/A 8-BIT CMOS MICROPROCESSORS

#### Description

The  $\mu$ PD70008 and  $\mu$ PD70008A are power saving, high performance, general purpose 8-bit microprocessor. It is a CMOS-process part with a standby mode that greatly reduces power consumption.

#### Features

- □ High performance µPD780 instruction set

- Instruction cycle:

1 μs at 4 MHz (μPD70008, μPD70008A-4)

0.66 μs at 6 MHz (μPD70008A-6)

- Direct addressing of up to 64 K bytes of memory

- □ Memory refresh function

- □ Interrupt functions:

- Maskable external interrupt (INT)

- Nonmaskable external interrupt (NMI)

- Low-power standby mode (HALT)

- □ CMOS standby mode (HALT)

- □ Single power supply

#### **Ordering Information**

| Part<br>Number | Package Typ <b>e</b>    | Max Frequency<br>of Operation |

|----------------|-------------------------|-------------------------------|

| µPD70008C      | 40-pin plastic DIP      | 4 MHz                         |

| µPD70008AC-4   | 40-pin plastic DIP      | 4 MHz                         |

| µPD70008AC-6   | 40-pin plastic DIP      | 6 MHz                         |

| µPD70008AG-4   | 44-pin plastic miniflat | 4 MHz                         |

| µPD70008AG-6   | 44-pin plastic miniflat | 6 MHz                         |

| µPD70008AL-6   | 44-pin PLCC             | 6 MHz                         |

#### Absolute Maximum Ratings

$T_A = 25 \degree C$

| Power supply voltage, V <sub>DD</sub>              | -0.3 V to +7 V                   |

|----------------------------------------------------|----------------------------------|

| Input voltage, V <sub>IN</sub>                     | -0.3 V to V <sub>DD</sub> +0.3 V |

| Output voltage, V <sub>0</sub>                     | -0.3 V to V <sub>DD</sub> +0.3 V |

| Operating temperature, T <sub>OPT</sub><br>PD70008 | - 10°C to +70°C                  |

| μPD70008A                                          | - 45°C to +85°C                  |

| Storage temperature, TSTG                          | - 65°C to +150°C                 |

**Comment:** Exposing the device to stresses above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational sections of the specification. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

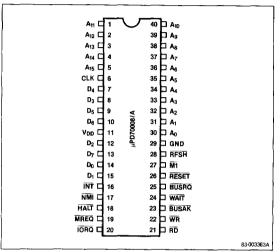

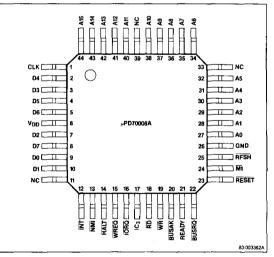

#### **Pin Configurations**

#### 40-Pin Plastic DIP

#### 44-Pin Plastic Miniflat

#### **Pin Identification**

#### 40-Pin Plastic DIP

| No.    | Symbol                           | Function                              |

|--------|----------------------------------|---------------------------------------|

| 1–5    | A <sub>11</sub> -A <sub>15</sub> | Address bus, high bits, outputs       |

| 6      | CLK                              | Clock input                           |

| 7-10   | D <sub>3</sub> -D <sub>6</sub>   | Data bus, bits 3-6, inputs /outputs   |

| 11     | V <sub>DD</sub>                  | Power supply                          |

| 12     | D <sub>2</sub>                   | Datra bus, bit 2, input/output        |

| 13     | D <sub>7</sub>                   | Data bus, bit 7, input /output        |

| 14, 15 | D <sub>0</sub> , D <sub>1</sub>  | Data bus, bits 0, 1, inputs / outputs |

| 16     | INT                              | Interrupt input                       |

| 17     | NMI                              | Nonmaskable interrupt input           |

| 18     | HALT                             | Halt / standby mode output            |

| 19     | MREQ                             | Memory request output                 |

| 20     | IORQ                             | 1 / 0 request output                  |

| 21     | RD                               | Read strobe output                    |

| 22     | WR                               | Write strobe output                   |

| 23     | BUSAK                            | Bus acknowledge output                |

| 24     | WAIT                             | Wait input                            |

| 25     | BUSRQ                            | Bus request input                     |

| 26     | RESET                            | Reset input                           |

| 27     | M1                               | Machine cycle 1 output                |

| 28     | RFSH                             | Refresh request output                |

| 29     | GND                              | Ground                                |

| 30-40  | A <sub>0</sub> -A <sub>10</sub>  | Address bus, low bits, outputs        |

#### **Pin Functions**

#### A<sub>15</sub>-A<sub>0</sub> (Address Bus)

These three-state output pins form a 16-bit address bus for addressing memory or peripheral devices. The address bus enters the high impedance state when bus acknowledge is active. In the standby mode, these pins output high- or low-level signals.

#### D7-D0 (Data Bus)

These three-state pins form an 8-bit bidirectional data bus. On this bus data is transferred between the  $\mu$ PD70008/A and memory or peripheral devices. This bus enters the high impedance state when bus acknowledge is active. In the standby mode, these pins are high-level.

#### INT (Interrupt)

This pin is an active-low interrupt input which can be masked by software.  $\overline{\text{NMI}}$  has a lower priority than  $\overline{\text{NMI}}$  and  $\overline{\text{BUSRQ}}$ .  $\overline{\text{INT}}$  releases the standby mode.

#### 44-Pin Plastic Miniflat

| No.          | Symbol                           | Function                              |

|--------------|----------------------------------|---------------------------------------|

| 40-44        | A <sub>11</sub> -A <sub>15</sub> | Address bus, high bits, outputs       |

| 1            | CLK                              | Clock input                           |

| 2-5          | D <sub>3</sub> -D <sub>6</sub>   | Data bus, bits 3-6, inputs /outputs   |

| 6            | V <sub>DD</sub>                  | Power supply                          |

| 7            | D <sub>2</sub>                   | Datra bus, bit 2, input / output      |

| 8            | D <sub>7</sub>                   | Data bus, bit 7, input / output       |

| 9-10         | D <sub>0</sub> , D <sub>1</sub>  | Data bus, bits 0, 1, inputs / outputs |

| 12           | INT                              | Interrupt input                       |

| 13           | NMI                              | Nonmaskable interrupt input           |

| 14           | HALT                             | Halt / standby mode output            |

| 15           | MREQ                             | Memory request output                 |

| 16           | IORQ                             | I / O request output                  |

| 18           | RD                               | Read strobe output                    |

| 19           | WR                               | Write strobe output                   |

| 20           | BUSAK                            | Bus acknowledge output                |

| 21           | WAIT                             | Wait input                            |

| 22           | BUSRO                            | Bus request input                     |

| 23           | RESET                            | Reset input                           |

| 24           | M1                               | Machine cycle 1 output                |

| 25           | RFSH                             | Refresh request output                |

| 26           | GND                              | Ground                                |

| 28-32, 34-38 | A <sub>0</sub> -A <sub>10</sub>  | Address bus, low bits, outputs        |

| 17           | IC                               | Internally connected                  |

| 11, 33, 39   | NC                               | Not connected                         |

#### **NMI** (Nonmaskable Interrupt)

This pin inputs an interrupt which is not maskable by software.  $\overline{\text{NMi}}$  is active-low in the  $\mu$ PD70008, and is falling edge triggered in the  $\mu$ PD70008A.  $\overline{\text{NMi}}$  has a higher priority than  $\overline{\text{INT}}$ , but a lower priority than  $\overline{\text{BUSRQ}}$  and  $\overline{\text{RESET}}$ .  $\overline{\text{NMi}}$  releases the standby mode.

#### **MREQ** (Memory Request)

This three-state pin is an active-low output. The  $\mu$ PD70008/A asserts MREQ to indicate that the information on the address bus is a memory address. This pin enters the high impedance state when bus acknowledge is active. MREQ is inactive (high) in the standby mode.

#### **Pin Functions (cont)**

#### IORQ (I/O Request)

This three-state pin is an active-low output. The  $\mu$ PD70008/A asserts IORQ to indicate that the information on the address bus is a peripheral device address. IORQ is also asserted during a maskable interrupt service to request the Interrupting device to output its interrupt vector to the data bus. This pin enters the high impedance state when bus acknowledge is active. IORQ is inactive (high) in the standby mode.

#### **RD** (Read Strobe)

This three-state active-low output provides a read strobe for the memory and peripheral devices. The pin enters the high impedance state when the bus acknowledge is active. RD is inactive (high) in the standby mode.

#### WR (Write Strobe)

This three-state active-low output provides a write strobe for the memory and peripheral devices. This pin enters the high impedance state when bus acknowledge is active. WR is inactive (high) in the standby mode.

#### **BUSRQ** (Bus Request)

This is an active-low input. Peripheral devices assert BUSRQ to request the  $\mu$ PD70008/A to release control of the address bus (A<sub>15</sub>-A<sub>0</sub>), data bus (D<sub>7</sub>-D<sub>0</sub>) and control bus (MREQ, IORQ, RD and WR) and assert bus acknowledge. BUSRQ has a higher priority than either INT or NMI, but is lower in priority than RESET. BUSRQ will temporarily suspend the standby mode. The  $\mu$ PD70008/A leaves standby mode when BUSRQ is asserted, but returns to the standby mode when BUSRQ is released.

#### **BUSAK** (Bus Acknowledge)

This active-low output indicates that the data bus  $(D_7-D_0)$ , address bus  $(A_{15}-A_0)$ , and control bus  $(\overline{MREQ}, \overline{IORQ}, \overline{RD} \text{ and } \overline{WR})$  have entered the high impedance state. This releases the buses from CPU control and makes them available to the peripheral devices for data exchange. This state cannot be released by  $\overline{NM}$  or  $\overline{INT}$ , but responds only to  $\overline{RESET}$  or the release of  $\overline{BUSRQ}$ .

#### HALT (Halt/Standby Mode)

This active-low output is asserted after the halt command has been executed and indicates that the  $\mu$ PD70008/A has entered the standby mode.

#### WAIT (Wait)

This pin is an active-low input. Memory and peripheral devices assert this signal to increase read or write access time. When WAIT is asserted, the  $\mu$ PD70008/A inserts wait states (TW) into the machine cycle until WAIT is released.

#### **RESET** (Reset)

This active-low input is used to reset the  $\mu$ PD70008/A. The standby mode is released on Reset. Reset has the highest priority.

INTI < NMI < BUSRQ < RESET

#### **RFSH** (Refresh Request)

This pin is an active-low output. The  $\mu$ PD70008/A asserts RFSH to trigger the external memory refresh operation. When RFSH is low, the lower seven bits of the address bus (A<sub>6</sub>-A<sub>0</sub>) are a refresh address. This pin is inactive (high) in the standby mode.

#### M1 (Machine Cycle 1)

This pin is an active-low output. When  $\overline{M1}$  is asserted, it indicates that the  $\mu$ PD70008/A is in the opcode fetch cycle,  $\overline{M1}$ .

#### CLK (Clock)

This pin is the system clock input.

#### V<sub>DD</sub> (Power Supply)

This pin is the +5 V power supply input.

#### GND (Ground)

This pin is the ground pin.

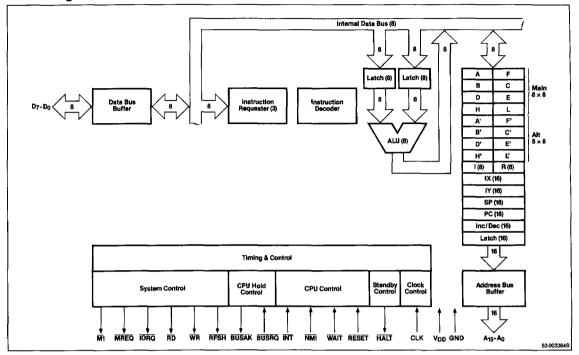

#### **Block Diagram**

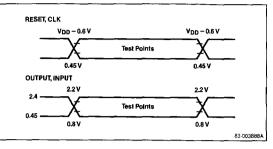

#### **DC Characteristics**

$\mu PD70008; T_A = -10^{\circ}C$  to  $+70^{\circ}C, \mu PD70008A; T_A = -40^{\circ}C$  to  $+85^{\circ}C, V_{DD} = +5 V \pm 10\%$

|                                |                  |                      | Limit | 8                    |      | Test                      |  |

|--------------------------------|------------------|----------------------|-------|----------------------|------|---------------------------|--|

| Parameter                      | Symbol           | Min Typ              |       | Max                  | Unit | Conditions                |  |

| Input voltage<br>high          | V <sub>IH1</sub> | 2.2                  |       | V <sub>DD</sub>      | V    | Except CLK,<br>RESET      |  |

|                                | V <sub>IH2</sub> | V <sub>DD</sub> -0.6 | ì     | V <sub>DD</sub> +0.3 | V    | CLK, RESET                |  |

| Input voltage<br>low           | V <sub>IL1</sub> | -0.3                 |       | 0.8                  | ۷    | Except CLK,<br>RESET      |  |

|                                | V <sub>IL2</sub> | -0.3                 |       | 0.45                 | ۷    | CLK, RESET                |  |

| Output voltage<br>high         | V <sub>OH</sub>  | 2.4                  |       |                      | ۷    | l <sub>OH</sub> = -400 μA |  |

| Output voltage<br>low          | V <sub>OL</sub>  |                      |       | 0.4                  | ۷    | $l_{0L} = 2.5 \text{mA}$  |  |

| Input leakage<br>current high  | <sup>1</sup> LIH |                      |       | 10                   | μA   | $V_I = V_{DD}$            |  |

| Input leakage<br>current low   | ILIL             |                      |       | - 10                 | μA   | $V_{IN} = 0 V$            |  |

| Output leakage<br>current high | <sup>1</sup> loh |                      |       | 10                   | μA   | $V_0 = V_{DD}$            |  |

| Output leakage<br>current low  | LOL              |                      |       | - 10                 | µА   | $V_0 = 0 V$               |  |

|                            |                  |     | Limits |     | Test |                               |

|----------------------------|------------------|-----|--------|-----|------|-------------------------------|

| Parameter                  | Symbol           | Min | Тур    | Max | Unit | Conditions                    |

| Supply current<br>(Note 1) |                  |     |        |     |      |                               |

| µPD70008                   | DD1              |     | 10     | 30  | mA   | $t_{CYK}\!=\!0.25\mu\text{s}$ |

|                            | DD2              |     | 500    |     | μA   | t <sub>CYK</sub> =0.25μs      |

| μPD70008A-4                | I <sub>DD1</sub> |     | 9      | 20  | mA   | t <sub>CYK</sub> =0.25 μs     |

|                            | DD2              |     | 80     | 240 | μA   | $t_{CYK} = 0.25 \mu s$        |

| µPD70008A-6                | DD1              |     | 14     | 30  | mA   | t <sub>CYK</sub> =0.165 µs    |

|                            | DD2              |     | 120    | 360 | μA   | t <sub>CYK</sub> =0.165 μs    |

Note:

(1) I<sub>DD1</sub> is normal operating current. I<sub>DD2</sub> is standby mode current.

#### Capacitance

$T_A = 25^{\circ}C$ ,  $I_C = 1 MHz$

|                          |                |     | Limits |     | Test |            |  |

|--------------------------|----------------|-----|--------|-----|------|------------|--|

| Parameter                | Symbol         | Min | Тур    | Max | Unit | Conditions |  |

| CLK input<br>capacitance | CK             |     |        | 35  | pF   | (Note 1)   |  |

| Input<br>capacitance     | CI             |     |        | 5   | рF   | (Note 1)   |  |

| Output<br>capacitance    | C <sub>0</sub> |     |        | 10  | pF   | (Note 1)   |  |

| I / O capacitance        | CIO            |     |        | 10  | рF   | (Note 1)   |  |

AC Test Points

#### Note:

(1) All unmeasured pins returned to 0 V.

#### **AC Characteristics**

$\mu$ PD70008: T<sub>A</sub> = -10°C to +70°C,  $\mu$ PD70008A: T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = 5 V ±10%

|           |                                                |                                   | Limits                                 |          |                     |          |      |                          |

|-----------|------------------------------------------------|-----------------------------------|----------------------------------------|----------|---------------------|----------|------|--------------------------|

|           |                                                |                                   | μ <b>PD70008/A-4</b>                   |          | μ <b>PD70008A-6</b> |          |      | Test                     |

| Signal    | Parameter                                      | Symbol                            | Min                                    | Max      | Min                 | Max      | Unit | Conditions               |

| CLK       | Clock period                                   | 1 <sub>CYK</sub>                  | 0.25                                   | (Note 1) | 0.165               | (Note 8) | μs   |                          |

|           | Clock pulse width high                         | t <sub>KKH</sub>                  | 0.11                                   | 200      | 0.065               | 200      | μs   |                          |

|           | Clock pulse width low                          | <sup>t</sup> kkl                  | 110                                    | 2000     | 65                  | 2000     | ns   |                          |

|           | Clock pulse rise and fall time                 | t <sub>KR</sub> , t <sub>KF</sub> |                                        | 30       |                     | 20       | ns   |                          |

| A15-A0    | Address output delay                           | t <sub>DKA</sub>                  |                                        | 110      |                     | 90       | ns   | C <sub>L</sub> = 100 pF  |

|           | Address delay to float                         | t <sub>FKA</sub>                  |                                        | 90       |                     | 80       | ns   | C <sub>L</sub> = 100 pF  |

|           | Address stable prior to MREQ, memory cycle     | tsam                              | (Note 2)                               |          | (Note 9)            |          | ns   | $C_L = 100  pF$          |

|           | Address stable prior to IORQ in<br>I / 0 cycle | t <sub>SAI</sub>                  | t <sub>CYK</sub> -70                   |          | (Note 10)           |          | ns   | $C_{L} = 100  pF$        |

|           | Address stable from RD, WR,<br>IORQ, MREQ      | thra                              | (Note 3)                               |          | (Note 11)           |          | ns   | $C_L = 100  pF$          |

|           | Address stable from RD, WR during float        | t <sub>FCA</sub>                  | (Note 4)                               |          | (Note 12)           |          | ns   | $C_L = 100  \text{pF}$   |

| 7-D0      | Data output delay                              | t <sub>DKD</sub>                  |                                        | 180      |                     | 130      | ns   | C <sub>L</sub> =100 pF   |

|           | Delay to float during write cycle              | t <sub>FKD</sub>                  |                                        | 90       |                     | 80       | ns   | C <sub>L</sub> = 100 pF  |

|           | Data setup time to CLK during M1 cycle         | t <sub>SDKR</sub>                 | 35                                     |          | 30                  |          | ns   | $C_{L} = 100  \text{pF}$ |

|           | Data setup time to CLK during M2 to M5 cycles  | <sup>t</sup> SDKF                 | 50                                     |          | 40                  |          | ns   | C <sub>L</sub> = 100 pF  |

|           | Data stable prior to WR (memory cycle)         | tsmdw                             | t <sub>CYK</sub> -170                  |          | (Note 13)           |          | ns   | C <sub>L</sub> =100 pF   |

|           | Data stable prior to WR (I / O cycle)          | tsidw                             | t <sub>KKL</sub> +t <sub>KR</sub> -170 |          | (Note 14)           |          | ns   | C <sub>L</sub> = 100 pF  |

|           | Data stable from WR                            | t <sub>FCD</sub>                  | (Note 5)                               |          | (Note 15)           |          | ns   | C <sub>L</sub> = 100 pF  |

| VR        | WR delay from CLK † to WR low                  | tDKRWL                            |                                        | 65       |                     | 60       | ns   |                          |

|           | WR delay from CLK ↓ to WR low                  | tDKFWL                            |                                        | 80       |                     | 70       | ns   |                          |

|           | WR delay from CLK ↓ to WR high                 | t <sub>DKFWH</sub>                |                                        | 80       |                     | 70       | ns   |                          |

|           | WR low pulse width                             | t <sub>WWL</sub>                  | t <sub>CYK</sub> - 30                  |          | (Note 18)           |          | ns   |                          |

| <u>/1</u> | M1 delay from CLK ↑ to M1 low                  | t <sub>DKM1L</sub>                |                                        | 100      |                     | 80       | ns   | C <sub>L</sub> = 100 pF  |

|           | MI delay from CLK 1 to MI high                 | t <sub>DKM1H</sub>                |                                        | 100      |                     | 80       | ns   | $C_{L} = 100  pF$        |

## 3

AC Characteristics (cont)  $\mu$ PD70008: T<sub>A</sub> = -10°C to +70°C,  $\mu$ PD70008A: T<sub>A</sub> = -40°C to +85°C, V<sub>CC</sub> = 5 V ± 10%

|                          |                                                 |                    |                                                                                         | L                    |           |     |                                          |                            |  |

|--------------------------|-------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|----------------------|-----------|-----|------------------------------------------|----------------------------|--|

|                          |                                                 |                    | μ <b>PD700</b>                                                                          | μΡD70008/Α-4 μΡD7000 |           |     |                                          | Test                       |  |

| Signal                   | Parameter                                       | Symbol             | Min                                                                                     | Max                  | Min       | Max | Unit                                     | Conditions                 |  |

| RFSH                     | RFSH delay from CLK ↑ to RFSH<br>low            | t <sub>DKRFL</sub> |                                                                                         | 130                  |           | 110 | ns                                       | C <sub>L</sub> = 100 pF    |  |

|                          | RFSH delay from CLK † to RFSH<br>high           | t <sub>dkrfh</sub> |                                                                                         | 120                  |           | 100 | ns                                       | $C_L = 100 \text{ pF}$     |  |

| WAIT                     | WAIT setup time to CLK +                        | tSWTK              | 70                                                                                      |                      | 60        |     | ns                                       |                            |  |

| HALT                     | HALT delay from CLK ↓                           | t <sub>DKHT</sub>  |                                                                                         | 300                  |           | 260 | ns                                       | $C_{L} = 100  pF$          |  |

| INT                      | INT setup time to CLK †                         | tsitk              | 80                                                                                      |                      | 70        |     | ns                                       |                            |  |

| NMI                      | NMI low pulse width                             | t <sub>NNL</sub>   | 80                                                                                      |                      | 70        |     | ns                                       | ···· ·                     |  |

| BUSRQ                    | BUSRQ setup time to CLK↓                        | tSBOK              | 50                                                                                      |                      | 50        |     | ns                                       |                            |  |

| BUSAK                    | BUSAK delay from CLK ↑ to<br>BUSAK low          | t <sub>DKRBA</sub> |                                                                                         | 100                  |           | 90  | ns                                       | $C_L = 100  pF$            |  |

|                          | BUSAK delay from CLK ↓ to<br>BUSAK high         | <sup>t</sup> dkfba |                                                                                         | 100                  |           | 90  | ns                                       | $C_L = 100  pF$            |  |

| RESET                    | RESET setup to CLK                              | t SRSK             | 60                                                                                      |                      | 60        |     | ns                                       |                            |  |

| Other                    | Delay to float (MREQ, TORQ, RD,<br>WR)          | t <sub>FKC</sub>   |                                                                                         | 80                   |           | 70  | ns                                       |                            |  |

|                          | M1 stable prior to IORQ (interrupt acknowledge) | t <sub>SM1I</sub>  | (Note 7)                                                                                |                      | (Note 19) |     | ns                                       |                            |  |

|                          | Hold time for setup time                        | tH                 | 0                                                                                       |                      | 0         |     | ns                                       |                            |  |

| MREQ                     | MREQ delay from CLK ↓ to MREQ<br>low            | <sup>t</sup> dkfml |                                                                                         | 85                   |           | 70  | ns                                       | $C_L = 100  pF$            |  |

|                          | MREQ delay from CLK ↑ to MREQ<br>high           | tdkrmh             |                                                                                         | 85                   |           | 70  | ns                                       | C <sub>L</sub> = 100 pF    |  |

|                          | MREQ delay from CLK ↓ MREQ<br>high              | tokfmh             |                                                                                         | 85                   |           | 70  | ns                                       | $C_L = 100 \text{ pF}$     |  |

|                          | Pulse width MREQ low                            | tMML               | t <sub>СҮК</sub> -30                                                                    |                      | (Note 16) |     | ns                                       | C <sub>L</sub> = 100 pF    |  |

|                          | Pulse width MREQ high                           | <sup>t</sup> ммн   | (Note 6)                                                                                |                      | (Note 17) |     | ns                                       | C <sub>L</sub> = 100 pF    |  |

| IORQ                     | IORQ delay from CLK 1 to IORQ<br>low            | t <sub>DKRIL</sub> |                                                                                         | 75                   |           | 65  | ns                                       | $C_L = 100  pF$            |  |

|                          | IORQ delay from CLK ↓ to IORQ<br>low            | <sup>t</sup> DKFIL |                                                                                         | 85                   |           | 70  | ns                                       | C <sub>L</sub> = 100 pF    |  |

|                          | IORQ delay from CLK † to IORQ<br>high           | <b>t</b> DKRIH     |                                                                                         | 85                   |           | 70  | ns                                       | $C_L = 100  pF$            |  |

|                          | IORQ delay from CLK ↓ to IORQ<br>high           | <sup>†</sup> DKFIH |                                                                                         | 85                   |           | 70  | ns                                       | C <sub>L</sub> =100 pF     |  |

| RD                       | RD delay from CLK ↑ to RD low                   | 1 <sub>DKRRL</sub> |                                                                                         | 85                   |           | 70  | ns                                       | C <sub>L</sub> = 100 pF    |  |

|                          | RD delay from CLK ↓ to RD low                   | <sup>t</sup> DKRFL |                                                                                         | 95                   |           | 80  | ns                                       | C <sub>L</sub> = 100 pF    |  |

|                          | RD delay from CLK † to RD high                  | t <sub>DKRRH</sub> |                                                                                         | 85                   |           | 70  | ns                                       | $C_L = 100 \text{ pF}$     |  |

|                          | RD delay from CLK ↓ to RD high                  | <sup>t</sup> dkfrh |                                                                                         | 85                   |           | 70  | ns                                       | $C_L = 100  pF$            |  |

| Note:                    |                                                 | (7)                | t <sub>SM1I</sub> = 2t <sub>CYK</sub> +t                                                | KKH +tKF             | - 65      |     | (14) $t_{SIDW} = t_{K}$                  | KL + t <sub>KR</sub> - 140 |  |

|                          |                                                 | (8)                | t <sub>CYK</sub> = t <sub>KKH</sub> +t <sub>KKL</sub> +t <sub>KR</sub> +t <sub>KF</sub> |                      |           |     | (15) $t_{FCD} = t_{KKL} + t_{KR} - 55$   |                            |  |

|                          | KH + tKF - 65                                   | (9)                | $t_{SAM} = t_{KKH} + t_{H}$                                                             | <sub>(F</sub> – 50   |           |     | (16) $t_{MML} = t_{CYK} - 30$            |                            |  |

|                          | KL + t <sub>HR</sub> - 50                       | (10)               | $t_{SAI} = t_{CYK} - 55$                                                                |                      |           |     | (17) $t_{MMH} = t_{KKH} + t_{KF} - 20$   |                            |  |

| (4) $t_{FCA} = t_K$      |                                                 | (11)               | $t_{HRA} = t_{KKL} + t_{K}$                                                             | R - 50               |           |     | (18) $t_{WWL} = t_{CYK} - 30$            |                            |  |

|                          | KL + 1 <sub>KR</sub> - 70                       | (12)               | $t_{FCA} = t_{KKL} + t_{K}$                                                             | R - 40               |           |     | (19) t <sub>SM1I</sub> = 2t <sub>6</sub> | CYK + tKKH + tKF - 5       |  |

| (6) t <sub>MMH</sub> ≕ t | ККH +t <sub>KF</sub> — 20                       | (13)               | tSMDW = tCYK -                                                                          | 140                  |           |     |                                          |                            |  |

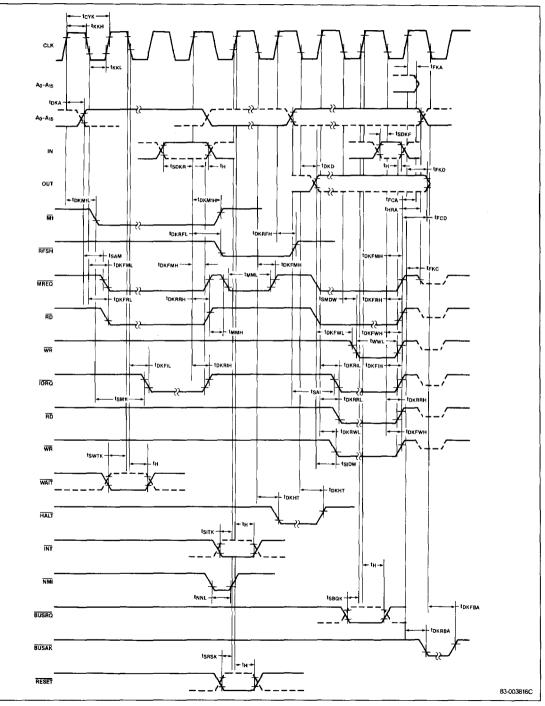

### **Timing Waveforms**

#### **Register Configuration**

#### **Program Counter (PC)**

The 16-bit program counter contains the address of the next instruction to be fetched and executed. It is set to 0000H at reset.

#### Stack Pointer (SP)

The 16-bit stack pointer stores the first address of the portion of main memory used as a LIFO stack. SP is decremented when a CALL or PUSH is executed, or when an interrupt occurs. It is incremented when a RET, POP, or interrupt return is executed.

#### Index Registers (IX, IY)

These two 16-bit registers are used to perform indexed addressing.

#### Accumulators (A, A')

The  $\mu$ PD70008/A has two 8-bit accumulators: the main accumulator (A) which is used to perform arithmetic and logic operations, and an alternate accumulator (A'). The contents of the main and alternate accumulators can be exchanged using the (EX) instruction. The alternate accumulator can be used for background operation, or to save the data in the main accumulator when an interrupt is processed.

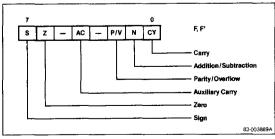

#### Flag Registers (F, F')

The  $\mu$ PD70008/A has two 8-bit flag registers: main (F) and alternate (F') of the format shown in figure 1. The main flag register (F) has the status flags resulting from normal operation. The contents of the main and alternate registers can be exchanged using the exchange (EX) instruction. The alternate (F') register can be used for background operation, or to save the state of the main flag register when an interrupt is processed.

#### **General Purpose Registers**

The  $\mu$ PD70008/A has twelve 8-bit general purpose registers: six main registers (B, C, D, E, H, and L) and six alternate registers (B', C', D', E', H', and L'). Each register can be used individually as an 8-bit register, or can be used in pairs as 16-bit registers (BC, B'C', DE, D'E', HL, and H'L').

The main registers are used when instructions are executed normally. The contents of the main and alternate registers are exchanged using the EX instruction. The alternate registers may be used for background operation or to save the contents of the main registers when an interrupt is processed.

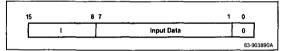

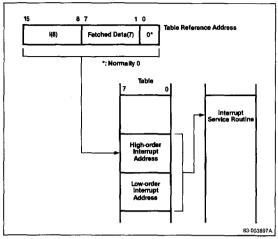

#### Interrupt Page Address Register (I)

This 8-bit register is used to generate addresses in maskable interrupt mode 2. See figure 2. These addresses are used with externally input data to reference an interrupt start address table.

This register is cleared to 00H at reset.

#### Figure 2. Interrupt Reference Address

#### **Memory Refresh Register (R)**

This 7-bit register retains the refresh address for the external dynamic memory. The contents of this register are automatically incremented in each opcode fetch (M1) cycle. The contents of this register are output on the lower 7 bits of the address bus  $(A_6-A_0)$ .

This register is cleared to 00H at reset.

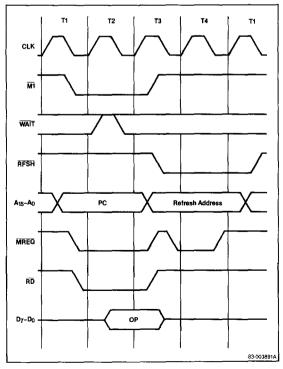

#### Timing

This section describes read and write timing for memory and I/O devices in connection with CPU operation timing. A single clock cycle (from one leading edge to the next) is defined as one timing state. The nth state is represented as Tn. A single instruction consists of two to six machine cycles. A single machine cycle requires three to six timing states. The nth machine cycle is represented as Mn.

Table 1 lists the number of states normally required by each cycle.

#### Table 1. Timing States per Cycle

| Cycle        | Number of States<br>per Machine Cycle |

|--------------|---------------------------------------|

| Opcode fetch | 4                                     |

| Memory read  | 3                                     |

| Memory write | 3                                     |

| I/O read     | 4                                     |

| I/O write    | 4                                     |

The four states for I/O read and write include a single wait state (TW). The  $\mu$ PD70008/A inserts one wait state in every I/O read or write. Slower external devices may assert the WAIT signal to request longer read and write access times. This time will be added to the original number of clock states. The WAIT signal is monitored on the trailing edge of clock state T2. If WAIT is asserted, a wait state (TW) is generated. The  $\mu$ PD70008/A continues to monitor WAIT on the clock's trailing edge, and supplies additional wait states a long as that signal is asserted. When WAIT is released the  $\mu$ PD70008/A proceeds to the T3 state.

Figure 3. Opcode Fetch Cycle

#### **Opcode Fetch Cycle**

The first machine cycle of each instruction, M1, is the opcode fetch cycle. See figure 3. The opcode is fetched from memory during the first half of this cycle, and the dynamic memory is refreshed during the latter half.

The memory outputs the opcode to the data bus when  $\overline{\text{MREQ}}$ ,  $\overline{\text{RD}}$ , or  $\overline{\text{M1}}$  is asserted. It is then read into the CPU at the leading edge of clock state T3.

The CPU outputs a refresh address onto  $A_6-A_0$  during T3. It is applied to the dynamic memory when RFSH or MREQ are asserted.

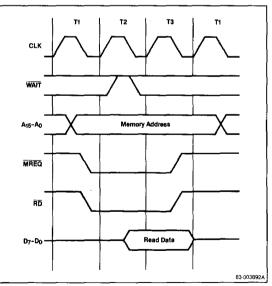

#### **Memory Read Cycle**

The memory contents are read out to the data bus when  $\overrightarrow{\text{MREQ}}$  or  $\overrightarrow{\text{RD}}$  is asserted. The  $\mu$ PD70008/A reads data from the data bus on the trailing edge of T3. See figure 4.

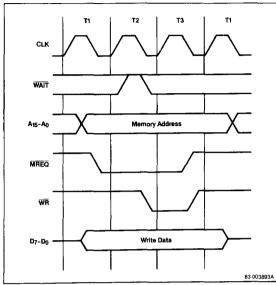

#### **Memory Write Cycle**

Write data is output to the data bus between the last half of state T1 of the current machine cycle and the first half of state T1 of the next cycle. It is written to memory when WR or MREQ is asserted. See figure 5.

#### Figure 4. Memory Read Cycle

#### Figure 5. Memory Write Cycle

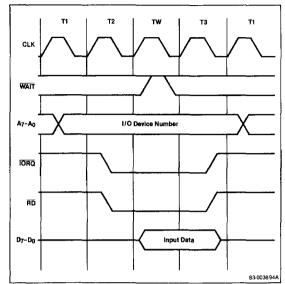

#### I/O Read Cycle

The contents of an I/O device are read out to the data bus when  $\overline{IORQ}$  or  $\overline{RD}$  is asserted. The  $\mu$ PD70008/A reads the data bus on the trailing edge of the T3 clock state. See figure 6. To compensate for I/O devices with longer access times, the  $\mu$ PD70008/A generates one wait state (TW) regardless of the condition of the WAIT signal. To extend the access time, the CPU must detect the WAIT signal asserted at the falling edge of TW.

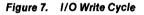

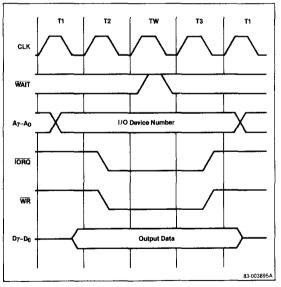

#### I/O Write Cycle

Write data is output to the data bus between the last half of state T1 of the current machine cycle and the first half of T1 of the next machine cycle. It is written to an I/O device when  $\overline{IORQ}$  or  $\overline{WR}$  is asserted. As in the I/O read cycle, one wait state is automatically inserted in the I/O write cycle. See figure 7. The WAIT signal is used to insert additional wait states in the I/O write cycle in exactly the same way as in the read cycle.

#### Figure 6. I/O Read Cycle

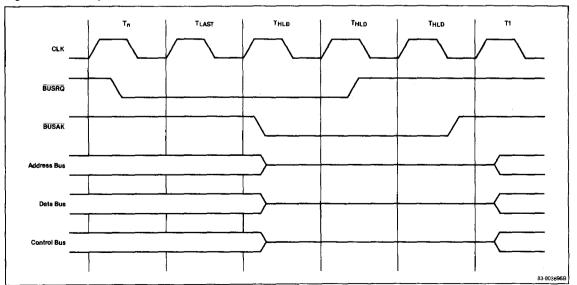

#### **Bus Request State**

The bus request causes the  $\mu$ PD70008/A address bus (A<sub>15</sub>-A<sub>0</sub>), data bus (D<sub>7</sub>-D<sub>0</sub>), and control bus (MREQ, IORQ, RD, and WR) pins to enter the high impedance state.This makes the buses available to external devices for DMA access.

The bus request state is controlled by the bus request (BUSRQ) signal. See figure 8. The  $\mu$ PD70008/A detects BUSRQ at the rising edge of the last state of each machine cycle. If it is active (low) the  $\mu$ PD70008/A does not move on the next machine cycle, but enters the bus request state. The  $\mu$ PD70008/A asserts BUSAK to indicate that the BUSRQ signal has been received, and the three buses have entered the high impedance state.

$\overline{\text{BUSRQ}}$  is checked at the rising edge of all clock states. When it becomes inactive the  $\mu$ PD70008/A leaves the bus request state, and proceeds to the next cycle.

BUSRQ temporarily suspends the standby mode. When BUSRQ is asserted, the  $\mu$ PD70008/A leaves the standby mode and enters the bus request state. When BUSRQ is released the  $\mu$ PD70008/A returns to the standby mode.

Interrupts are disabled during the bus request state.

#### Interrupts

The  $\mu$ PD70008/A has two types of interrupt: maskable (INT) and nonmaskable (NMI). The nonmaskable interrupt request cannot be masked by software. It will be acknowledged unless the  $\mu$ PD70008/A is in the bus

request state. The maskable interrupt can be masked by software. It is controlled by setting or resetting the interrupt enable flip-flop (IFF) using the EI or DI instructions. INT has a lower priority than the nonmaskable interrupt. The maskable interrupt will therefore not be acknowledged if there is a nonmaskable interrupt, or if the  $\mu$ PD70008/A is in the bus request state.

#### INTI < NMI < BUSRQ < RESET

#### Nonmaskable Interrupt Operation

The failing edge of  $\overline{\text{NMI}}$  always sets the nonmaskable interrupt flip-flop. The  $\mu$ PD70008/A checks the flip-flop at the rising edge of the last clock state of an instruction. If it is set, the  $\mu$ PD70008/A transfers control to the nonmaskable interrupt service routine. The interrupt process starts at the opcode fetch cycle, (M1, 5 states) but the opcode fetched at this point is ignored. The contents of the PC are stored on the stack in the next two machine cycles (M2, 3 states and M3, 3 states). At the same time, the address 0066H is loaded into the PC, and the state of the interrupt enable flip-flop is saved to an exclusive flip-flop. The entire interrupt routine requires 3 machine cycles (11 states). The contents of the PC and IFF are restored by the execution of the RETN instruction at the end of the interrupt procedure.

#### Figure 8. Bus Request State

#### Maskable Interrupt Operation

Maskable interrupts are processed in three modes. In each mode, the  $\overline{INT}$  signal is detected at the rising edge of the last clock state of each instruction. The M1 instruction specifies which mode is to be used.

**Mode 0.** In this mode, the data placed on the bus by the interrupting device is treated as an instruction. It is fetched in the opcode fetch cycle (M1, 7 states) and executed. The instruction used in this mode is usually a CALL (3 bytes) or RST (1 byte).

If a 1-byte RST instruction is executed, the contents of the PC are saved to the stack. A fixed address specified by the opcode is loaded into the PC during the next M2 (3 states) and M3 (3 states). The execution of this interrupt requires 3 machine cycles or 13 states.

If a 3-byte CALL instruction is executed, the second and third bytes are fetched during the M2 and M3 cycles (3 states each). During M4 and M5 (3 states each), the contents of the PC are saved to the stack and the second and third bytes of the CALL instruction are loaded into the PC. This interrupt requires 5 machine cyces and a total of 19 clock states.

**Mode 1.** In this mode, the data fetched during M1 (7 states) is ignored, and the  $\mu$ PD70008/A proceeds to the next cycle. During the M2 and M3 machine cycles (3 states each), the contents of the PC are saved to the stack and replaced by the interrupt address 0038H. This interrupt requires 3 machine cycles or 13 states.

**Mode 2.** In this mode, the data fetched from the interrupting device and the contents of the interrupt page register (I) are used to reference an interrupt start address table. Program execution jumps to the 16-bit address referenced by the table. See figure 9. The data is fetched during the opcode fetch cycle (M1, 7 states). During M2 and M3 (3 states each) the contents of the PC are saved to the stack. During the M4 and M5 cycles, (3 states each) the table is referenced and the contents of the table location are loaded into the PC. This interrupt requires 5 machine cycles or 19 states.

#### **Standby Mode**

The  $\mu$ PD70008/A is provided with a standby mode (HALT). In the standby mode, power consumption is approximately 2% of normal operating power consumption. The standby mode is set by executing the HALT instruction.

In the standby mode, the state of the  $\mu$ PD70008/A is retained. The contents of all registers and the state of all flags are retained as well. Clock signals are supplied only to indispensable circuits in the  $\mu$ PD70008/A to minimize power consumption.

External operations such as memory access and memory refresh are not performed in the standby mode.

Table 2 shows the state of each output pin in the standby mode.

#### Table 2. Standby Mode

| Pin                                            | Status                                              |

|------------------------------------------------|-----------------------------------------------------|

| Data bus<br>D7-D0                              | High level, pulled up through interna<br>resistance |

| Address bus<br>A <sub>15</sub> -A <sub>0</sub> | High or low level signals                           |

| Control bus<br>RD, WR, MREQ, IORQ, M1          | High level (inactive)                               |

| RFSH                                           | High level (inactive)                               |

| HALT                                           | Low level (active)                                  |

The standby mode is released when a reset or an interrupt occurs. The standby mode is temporarily suspended by a bus request, but not released.

#### **RESET** in Standby Mode

When the  $\overline{\text{RESET}}$  signal becomes active (low) the standby mode is released and a normal reset is performed.

#### **NMI** in Standby Mode

When the NMI signal is asserted (low) the standby mode is released and normal nonmaskable interrupt processing is performed. The interrupt is not performed in the bus request state.

#### INT in Standby Mode

When the INT signal is asserted (low) the standby mode is released. If the interrupt is enabled, normal interrupt processing is performed. If the interrupt is disabled, execution resumes at the instruction following the HALT instruction.

#### **BUSRQ** in Standby Mode

The BUSRQ signal is detected at the rising edge of each clock in the standby mode. If the BUSRQ signal is active (low) the  $\mu$ PD70008/A leaves the standby mode, and enters the bus request state. When BUSRQ is released, the standby mode is resumed. The standby mode is not released by the BUSRQ signal.

#### RESET

The RESET signal must be asserted (low) for over 3 clock cycles to be recognized. The following steps are the reset initialization process:

- The program counter (PC) is cleared to 0000H.

- The interrupt enable flip-flop (IFF) is reset to 0, disabling maskable interrupts. The interrupt mode is set to 0.

- The interrupt page address register (I) is cleared to 00H.

- The memory refresh register (R) is cleared to 00H.

- The address bus (A<sub>15</sub>-A<sub>0</sub>) and data bus (D<sub>7</sub>-D<sub>0</sub>) are set to high impedance.

- · All control outputs are set in their inactive state.

- The standby mode is released.

The following registers are undefined at reset:

Stack pointer (SP) Accumulators (A,A') Flag registers (F,F') General purpose registers (B, B', C, C', D, D', E, E', H, H', L, L') Index registers (IX,IY)

When RESET is released the program will begin execution from location 0000H.

#### Instruction Set

Each operand should be written in the operand column of an instruction according to the description in table 3. Capital letters are keywords and should be written as they appear.

#### Table 3. Operand Description

| Indentifier | Description                                                                  |

|-------------|------------------------------------------------------------------------------|

| addr        | 16-bit immediate data or label                                               |

| faddr       | 00H, 08H, 10H, 18H, 20H, 28H, 30H, 38H<br>immediate data or label            |

| word        | 16-bit immediate data or label                                               |

| byte        | 8-bit immediate data or label                                                |

| bit         | 3-bit immediate data or label (bit specification of 8-bit register / memory) |

| d           | 8-bit displacement (signed 2's complement)                                   |

| r           | A, B, C, D, E, H, L                                                          |

| r'          | A', B', C', D', E', H', L'                                                   |

| rp          | BC, DE, HL, AF                                                               |

| rp1         | BC, DE, HL, SP                                                               |

| rp2         | BC, DE, IX, SP                                                               |

| гр3         | BC, DE, IY, SP                                                               |

| e           | Displacement for relative jump (signed 2's complement)                       |

#### Selection of Register and Condition

| rp | 99 | rpi | ss, dd | rp2 | pp | rp3 | n  |

|----|----|-----|--------|-----|----|-----|----|

| BC | 00 | BC  | 00     | BC  | 00 | BC  | 00 |

| DE | 01 | DE  | 01     | DE  | 01 | DE  | 01 |

| HL | 10 | HL  | 10     | IX  | 10 | IY  | 10 |

| AF | 11 | SP  | 11     | SP  | 11 | SP  | 11 |

| r,#' | r, r' | bit | b   | faddr | t   |

|------|-------|-----|-----|-------|-----|

| B B' | 000   | 0   | 000 | DOH   | 000 |

| C C' | 001   | 1   | 001 | 08H   | 001 |

| D D' | 010   | 2   | 010 | 10H   | 010 |

| E E' | 011   | 3   | 011 | 18H   | 011 |

| H H′ | 100   | 4   | 100 | 20H   | 100 |

| LL'  | 101   | 5   | 101 | 28H   | 101 |

| A A' | 111   | 6   | 110 | 30H   | 110 |

|      |       | 7   | 111 | 38H   | 111 |

#### Flag Operation

(Blank): Flag not affected

0: Flag reset

1: Flag set

- X: Flag affected according to result of operation

- U: Flag unknown

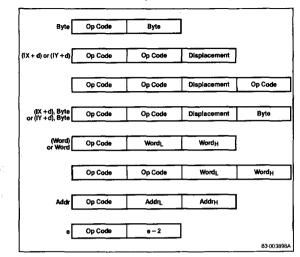

#### Structure of Instruction Byte for Addressing

#### **Instruction Set**

|              |                              |                                |    |   |   | _  |     |   | Op | orati | on Ca | de |   |   |   |   |   |   | No. of | No. of |   |            | F | lags |   |

|--------------|------------------------------|--------------------------------|----|---|---|----|-----|---|----|-------|-------|----|---|---|---|---|---|---|--------|--------|---|------------|---|------|---|

| nemonic      | Operands                     | Operation                      | 7  | 6 | 5 | 4  | 3   | 2 | 1  | 0     | 7     | 6  | 5 | 4 | 3 | 2 | 1 | 0 | Clocks | Bytes  |   | Z          | H | P/V  | N |

| Bit Transfei | r Instructions               |                                |    |   |   |    |     |   |    |       |       |    |   |   |   |   |   |   |        |        |   |            |   |      |   |

| )            | r, r′                        | r <del></del> r'               | 0  | 1 |   | ٢  |     |   | r' |       |       |    |   |   |   | _ |   |   | 4      | 1      |   |            |   |      |   |

|              | r, byte                      | r <del></del> byte             | 0  | 0 |   | r  |     | 1 | 1  | 0     |       |    |   |   |   |   |   |   | 7      | 2      |   |            |   |      |   |

|              | r, (HL)                      | r 🖛 (HL)                       | 0  | 1 |   | r  |     | 1 | 1  | 0     |       |    |   | _ |   |   |   |   | 7      | 1      |   |            |   |      |   |

|              | r, (IX + d)                  | r 🖛 (IX + disp)                | 1  | 1 | 0 | 1  | 1   | 1 | 0  | 1     | 0     | 1  |   | r |   | 1 | 1 | 0 | 19     | 3      |   |            | _ |      |   |

|              |                              |                                |    |   |   | di | sp  |   |    |       |       |    |   |   |   |   |   |   |        |        |   |            |   |      |   |

|              | $\mathbf{r},(IY=\mathbf{d})$ | r 🕶 (IY + disp)                | 1  | 1 | 1 | 1  | 1   | 1 | 0  | 1     | 0     | 1  |   | r |   | 1 | 1 | 0 | 19     | 3      |   |            |   |      |   |

|              |                              |                                |    |   |   | di | sp  |   |    |       |       |    |   |   |   |   |   |   |        |        |   |            |   | _    |   |

|              | (HL), r                      | (HL) ← r                       | 0  | 1 | 1 | 1  | 0   |   | r  |       |       |    |   |   |   |   |   |   | 7      | 1      |   |            |   |      |   |

|              | (IX + d), r                  | (IX + disp) <del>&lt;-</del> r | _1 | 1 | 0 | 1  | 1   | 1 | 0  | 1     | 0     | 1  | 1 | 1 | 0 |   | r |   | 19     | 3      |   |            |   |      |   |

|              |                              |                                |    |   |   | di | sp  |   |    |       |       |    |   |   |   |   |   |   |        |        | _ |            |   |      |   |

|              | (IY + d), r                  | (IY + disp) - r                | 1  | 1 | 1 | _1 | 1   | 1 | 0  | 1     | 0     | 1  | 1 | 1 | 0 |   | r |   | 19     | 3      |   |            | _ |      |   |

|              |                              |                                |    |   |   | di | isp |   |    |       |       |    |   |   |   |   |   |   |        |        |   |            |   | _    |   |

|              | (HL), byte                   | (HL) 🔶 byte                    | 0  | 0 | 1 | 1  | 0   | 1 | 1  | 0     | _     |    |   |   |   |   |   |   | 10     | 2      |   |            |   |      |   |

|              | (IX + d), byte               | (IX + disp) - byte             | 1  | 1 | 0 | 1  | 1   | 1 | 0  | 1     | 0     | 0  | 1 | 1 | 0 | 1 | 1 | 0 | 19     | 4      |   |            |   |      |   |

|              |                              |                                |    |   |   | di | lsp |   |    |       |       |    |   |   |   |   |   |   | _      |        |   |            |   |      |   |

|              | (IY + d), byte               | (IY + disp) - byte             | 1  | 1 | 1 | 1  | 1   | 1 | 0  | 1     | 0     | 0  | 1 | 1 | 0 | 1 | 1 | 0 | 19     | 4      |   |            |   |      |   |

|              |                              |                                |    |   |   | di | sp  |   |    |       |       |    |   |   |   |   |   |   |        |        |   |            |   |      |   |

|              | A, (BC)                      | A ← (BC)                       | 0  | 0 | 0 | 0  | 1   | 0 | 1  | 0     |       |    |   |   |   |   |   |   | 7      | 1      |   |            |   |      |   |

|              | A, (DE)                      | A 🖛 (DE)                       | 0  | 0 | 0 | 1  | 1   | 0 | 1  | 0     |       |    |   |   |   |   |   |   | 7      | 1      |   |            |   |      |   |

|              | A, (word)                    | A 🗕 (word)                     | 0  | 0 | 1 | 1  | 1   | 0 | 1  | 0     |       |    |   |   |   |   |   |   | 13     | 3      |   |            |   |      |   |

|              | (BC), A                      | (BC) - A                       | 0  | 0 | 0 | 0  | 0   | 0 | 1  | 0     |       |    |   |   |   |   |   |   | 7      | 1      |   |            |   |      |   |

|              | (DE), A                      | (DE) ← A                       | 0  | 0 | 0 | 1  | 0   | 0 | 1  | 0     |       |    |   |   |   |   |   | _ | 7      | 1      |   |            |   |      |   |

|              | (word), A                    | (word) - A                     | 0  | 0 | 1 | .1 | 0   | 0 | 1  | 0     |       |    |   |   |   |   |   |   | 13     | 3      |   |            |   |      |   |

|              | A, I                         | A ← i                          | 1  | 1 | 1 | 0  | 1   | 1 | 0  | 1     | 0     | 1  | 0 | 1 | 0 | 1 | 1 | 1 | 9      | 2      | x | . <b>x</b> | 0 | IFF  | 0 |

|              | A, R                         | A ← R                          | 1  | 1 | 1 | 0  | 1   | 1 | 0  | 1     | 0     | 1  | 0 | 1 | 1 | 1 | 1 | 1 | 9      | 2      | x | x          | 0 | IFF  | 0 |

|              | I, A                         | I <del></del> A                | 1  | 1 | 1 | 0  | 1   | 1 | 0  | 1     | 0     | 1  | 0 | 0 | 0 | 1 | 1 | 1 | 9      | 2      |   |            |   |      |   |

|              | R, A                         | R ← A                          | 1  | 1 | 1 | 0  | 1   | 1 | 0  | 1     | 0     | 1  | 0 | 0 | 1 | 1 | 1 | 1 | 9      | 2      |   |            |   |      |   |

|              | rp1, word                    | rp1 - word                     | 0  | 0 | d | d  | 0   | 0 | 0  | 1     |       |    |   |   |   |   | _ |   | 10     | 3      |   |            |   |      |   |

|              | IX, word                     | IX word                        | 1  | 1 | 0 | 1  | 1   | 1 | 0  | 1     | 0     | 0  | 1 | 0 | 0 | 0 | 0 | 1 | 14     | 4      |   |            |   |      |   |

|              | IY, word                     | IY - word                      | 1  | 1 | 1 | 1  | 1   | 1 | 0  | 1     | 0     | 0  | 1 | 0 | 0 | 0 | 0 | 1 | 14     | 4      |   |            |   |      | _ |

|              | HL, (word)                   | H (word + 1),<br>L (word)      | 0  | 0 | 1 | 0  | 1   | 0 | 1  | 0     |       |    |   |   |   |   |   |   | 16     | 3      |   |            |   |      |   |

ω

µ**PD70008/A**

NEC

3-17

3-18

|                |                    |                                                                                      |   |   |   |   |   |   | Op | erati | on Ca | ode |   |   |   |   |   |   | No. of | No. of |           |   | F | ags |   |   |

|----------------|--------------------|--------------------------------------------------------------------------------------|---|---|---|---|---|---|----|-------|-------|-----|---|---|---|---|---|---|--------|--------|-----------|---|---|-----|---|---|

| Mnemonic       | Operands           | Operation                                                                            | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0     | 7     | 6   | 5 | 4 | 3 | 2 | 1 | 0 | Clocks | Bytes  | 5         | Z | H | P/V | N | C |

| lixteen-Bit Tr | ansfer Instruction | S                                                                                    |   |   |   |   |   |   |    |       |       |     | _ |   |   |   |   |   |        |        |           |   |   |     |   |   |

| _D             | rp1, (word)        | rp1 <sub>H</sub> ← (word + 1),<br>rp1 <sub>L</sub> ← (word)                          | 1 | 1 | 1 | 0 | 1 | 1 | 0  | 1     | 0     | 1   | d | d | 1 | 0 | 1 | 1 | 20     | 4      |           |   |   |     | _ |   |

|                | IX, (word)         | $IX_H \leftarrow (word + 1),$<br>$IX_L \leftarrow (word)$                            | 1 | 1 | 0 | 1 | 1 | 1 | 0  | 1     | 0     | 0   | 1 | 0 | 1 | 0 | 1 | 0 | 20     | 4      |           |   |   |     |   |   |

|                | IY, (word)         | $IY_{H} \leftarrow (word + 1),$<br>$IY_{L} \leftarrow (word)$                        | 1 | 1 | 1 | 1 | 1 | 1 | 0  | 1     | 0     | 0   | 1 | 0 | 1 | 0 | 1 | 0 | 20     | 4      |           |   |   |     |   |   |

|                | (word), HL         | (word + 1) - H,<br>(word) - L                                                        | 0 | 0 | 1 | 0 | 0 | 0 | 1  | 0     |       |     |   |   |   |   |   |   | 16     | 3      | _         |   |   |     |   |   |

|                | (word), rp1        | $(word + 1) \leftarrow rp1_{H}$ .<br>$(word) \leftarrow rp1_{L}$                     | 1 | 1 | 1 | 0 | 1 | 1 | 0  | 1     | 0     | 1   | d | d | 0 | 0 | 1 | 1 | 20     | 4      | _         |   |   |     |   | _ |

|                | (word), IX         | $(word + 1) \leftarrow IX_H,$<br>$(word) \leftarrow IX_L$                            | 1 | 1 | 0 | 1 | 1 | 1 | 0  | 1     | 0     | 0   | 1 | 0 | 0 | 0 | 1 | 0 | 20     | 4      |           |   |   |     |   |   |

|                | (word), IY         | (word + 1) $\leftarrow$ IY <sub>H</sub> ,<br>(word) $\leftarrow$ IY <sub>L</sub>     | 1 | 1 | 1 | 1 | 1 | 1 | 0  | 1     | 0     | 0   | 1 | 0 | 0 | 0 | 1 | 0 | 20     | 4      |           |   |   |     |   |   |

|                | SP, HL             | SP 🗕 HL                                                                              | 1 | 1 | 1 | 1 | 1 | 0 | 0  | 1     |       |     |   |   |   |   |   |   | 6      | 1      |           |   |   |     |   | _ |

|                | SP, IX             | SP 🖛 IX                                                                              | 1 | 1 | 0 | 1 | 1 | 1 | 0  | 1     | 1     | 1   | 1 | 1 | 1 | 0 | 0 | 1 | 10     | 2      |           |   |   | -   |   |   |

|                | SP, IY             | SP - IY                                                                              | 1 | 1 | 1 | 1 | 1 | 1 | 0  | 1     | 1     | 1   | 1 | 1 | 1 | 0 | 0 | 1 | 10     | 2      |           |   |   |     |   |   |

| PUSH           | rp                 | $(SP - 1) \leftarrow rp_L,$<br>$(SP - 2) \leftarrow rp_H,$<br>$SP \leftarrow SP - 2$ | 1 | 1 | q | q | 0 | 1 | 0  | 1     |       |     |   |   | - |   |   |   | 11     | 1      |           |   |   |     |   |   |

|                | IX                 | $(SP - 1) \leftarrow IX_L,$<br>$(SP - 2) \leftarrow IX_H,$<br>$SP \leftarrow SP - 2$ | 1 | 1 | 0 | 1 | 1 | 1 | 0  | 1     | 1     | 1   | 1 | 0 | 0 | 1 | 0 | 1 | 15     | 2      | <b></b> . |   |   |     |   |   |

|                | 1Y                 | $(SP - 1) \leftarrow  Y_L,$<br>$(SP - 2) \leftarrow  Y_H,$<br>$SP \leftarrow SP - 2$ | 1 | 1 | 1 | 1 | 1 | 1 | 0  | 1     | 1     | 1   | 1 | 0 | 0 | 1 | 0 | 1 | 15     | 2      |           |   |   |     |   |   |

| POP            | rp                 | $rp_L \leftarrow (SP),$<br>$rp_H \leftarrow (SP + 1),$<br>$SP \leftarrow SP = 2$     | 1 | 1 | q | q | 0 | 0 | 0  | 1     |       |     |   |   |   |   |   |   | 10     | 1      |           |   |   |     |   | - |

|                | IX                 | $IX_{L} \leftarrow (SP),$<br>$IX_{H} \leftarrow (SP + 1),$<br>$SP \leftarrow SP + 2$ | 1 | 1 | 0 | 1 | 1 | 1 | 0  | 1     | 1     | 1   | 1 | 0 | 0 | 0 | 0 | 1 | 14     | 2      |           |   |   |     |   |   |

|                | IY                 | $IY_{L} \leftarrow (SP),$<br>$IY_{H} \leftarrow (SP + 1),$<br>$SP \leftarrow SP + 2$ | 1 | 1 | 1 | 1 | 1 | 1 | 0  | 1     | 1     | 1   | 1 | 0 | 0 | 0 | 0 | 1 | 14     | 2      |           |   | _ |     |   |   |

| -                    |                  | _                                                                                                                                |          |   |   |   |   |   |   | erati |   |   |   |   | _ |   |   |   | No. of   | No. of |   |   |   | ags |   |   |

|----------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------|----------|---|---|---|---|---|---|-------|---|---|---|---|---|---|---|---|----------|--------|---|---|---|-----|---|---|

| Mnemonic             | Operands         | Operation                                                                                                                        | 7        | 6 | 5 | 4 | 3 | 2 | 1 | 0     | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |          | Bytes  |   | Z | H | P/V | N | Ċ |

|                      | ion Instructions |                                                                                                                                  |          |   |   |   |   |   |   |       |   |   |   |   | - |   |   |   |          |        |   |   |   |     |   |   |

| EX                   | DE, HL           | DE ↔ HL                                                                                                                          | 1        | 1 | 1 | 0 | 1 | 0 | 1 | 1     |   |   |   |   |   |   |   |   | 4        | 1      |   |   |   |     |   |   |

|                      | AF, AF'          | $A \leftrightarrow A', F \leftrightarrow F'$                                                                                     | 0        | 0 | 0 | 0 | 1 | 0 | 0 | 0     |   |   |   |   | _ |   | _ |   | 4        | 1      |   |   |   |     |   |   |

| EXX                  |                  | BC ↔ BC' ,<br>DE ↔ DE' , HL ↔ HL'                                                                                                | 1        | 1 | 0 | 1 | 1 | 0 | 0 | 1     |   |   |   | _ |   |   | - |   | 4        | 1      |   |   |   |     |   |   |

| EX                   | (SP), HL         | $(SP) \leftrightarrow L,$<br>$(SP + 1) \leftrightarrow H,$<br>$SP \rightarrow SP + 2$                                            | 1        | 1 | 1 | 0 | 0 | 0 | 1 | 1     |   |   |   |   |   |   |   |   | 19       | 1      |   |   |   |     |   |   |

|                      | (SP), IX         | $(SP) \leftrightarrow IX_L,$<br>$(SP + 1) \leftrightarrow IX_H,$<br>$SP \rightarrow SP + 2$                                      | 1        | 1 | 0 | 1 | 1 | 1 | 0 | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 23       | 2      |   |   |   |     |   |   |

|                      | (SP), IY         | $(SP) \leftrightarrow IY_L,$<br>$(SP + 1) \leftrightarrow IY_H,$<br>$SP \leftarrow SP + 2$                                       | 1        | 1 | 1 | 1 | 1 | 1 | 0 | 1     | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 23       | 2      |   |   |   |     |   |   |

| <b>Block Transfe</b> | r Instructions   |                                                                                                                                  |          |   |   | - |   |   |   |       |   |   |   |   |   |   |   |   |          |        |   |   |   |     |   | - |

| LDI                  |                  | (DE) ← (HL),<br>DE ← DE + 1,<br>HL ← HL + 1,<br>BC ← BC - 1                                                                      | 1        | 1 | 1 | 0 | 1 | 1 | 0 | 1     | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 16       | 2      |   |   | 0 | x   | 0 |   |

| LDIR                 |                  | (DE) ← (HL),<br>DE ← DE + 1,<br>HL ← HL + 1,<br>BC ← BC - 1,<br>End if BC = 0                                                    | 1        | 1 | 1 | 0 | 1 | 1 | 0 | 1     | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 21/16(1) | 2      |   |   | 0 | 0   | 0 |   |

| LDD                  |                  | $(DE) \leftarrow (HL),$<br>$DE \leftarrow DE - 1,$<br>$HL \leftarrow HL - 1,$<br>$BC \leftarrow BC - 1$                          | 1        | 1 | 1 | 0 | 1 | 1 | 0 | 1     | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 16       | 2      |   |   | 0 | x   | 0 |   |

| LDDR                 |                  | (DE) ← (HL),<br>DE ← DE - 1,<br>HL ← HL - 1,<br>BC ← BC - 1,<br>End if BC = 0                                                    | 1        | 1 | 1 | 0 | 1 | 1 | 0 | 1     | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 21/16(1) | 2      |   |   | 0 | 0   | 0 |   |

| Block Search         | Instructions     |                                                                                                                                  | <u> </u> |   |   |   |   |   |   |       |   |   |   |   |   |   |   | _ |          |        |   |   |   |     |   | _ |

| CPI                  |                  | A – (HL),<br>HL ← HL + 1,<br>BC ← BC – 1                                                                                         |          |   |   |   |   |   | 0 |       |   |   |   |   |   |   |   |   | 16       | 2      | x | x | x | x   | 1 |   |

| CPIR                 |                  | $\begin{array}{l} A - (HL), \\ HL \leftarrow HL + 1, \\ BC \leftarrow BC - 1, \\ End if A = (HL) \text{ or } BC = 0 \end{array}$ | 1        | 1 | 1 | 0 | 1 | 1 | 0 | 1     | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 21/16(2) | 2      | x | x | x | x   | 1 |   |

NEC

µPD70008/A

3-20

|                |                           |                                                                                              |     |   |   |    |          |   | Op | erati | on Co | de |   |   |   |   |   |   | No. of   | No. of | -  |   | Fla | ngs |   |   |

|----------------|---------------------------|----------------------------------------------------------------------------------------------|-----|---|---|----|----------|---|----|-------|-------|----|---|---|---|---|---|---|----------|--------|----|---|-----|-----|---|---|

| Mnemonic       | Operands                  | Operation                                                                                    | 7   | 6 | 5 | 4  | 3        | 2 | 1  | 0     | 7     | 6  | 5 | 4 | 3 | 2 | 1 | 0 | Clocks   | Bytes  | \$ | Z | H   | P/V | N |   |

|                | Instructions (cont)       |                                                                                              |     |   |   |    |          |   |    |       |       |    |   |   |   |   |   | • |          |        |    |   |     |     |   |   |

| CPD            |                           | A — (HL),<br>HL <del>← </del> HL — 1,<br>BC <del>←</del> BC — 1                              | 1   | 1 | 1 | 0  | 1        | 1 | 0  | 1     | 1     | 0  | 1 | 0 | 1 | 0 | 0 | 1 | 16       | 2      | x  | x | х   | x   | 1 |   |

| CPDR           |                           | A - (HL),<br>HL $\leftarrow$ HL - 1,<br>BC $\leftarrow$ BC - 1,<br>End if A = (HL) or BC = 0 | . 1 | 1 | 1 | 0  | 1        | 1 | 0  | 1     | 1     | 0  | 1 | 1 | 1 | 0 | 0 | 1 | 21/16(2) | 2      | x  | x | x   | x   | 1 |   |

| Eight-Bit Arit | hmetic Operation In       | structions                                                                                   |     |   | _ |    |          |   |    |       |       |    |   |   |   |   |   |   |          |        |    |   |     |     |   |   |

| ADD            | A, r                      | A 🔶 A + r                                                                                    | 1   | 0 | 0 | 0  | 0        |   | r  |       |       |    |   | _ |   | _ |   |   | 4        | 1      | х  | х | х   | ۷   | 0 | × |

|                | A, byte                   | A - A + byte                                                                                 | 1   | 1 | 0 | 0  | 0        | 1 | 1  | 0     |       |    |   |   |   |   |   |   | 7        | 2      | x  | x | x   | ۷   | 0 | х |

|                | A, (HL)                   | A 🖛 A + (HL)                                                                                 | 1   | 0 | 0 | 0  | 0        | 1 | 1  | 0     |       |    |   |   |   |   |   |   | 7        | 1      | X  | x | x   | ٧   | 0 | Х |

|                | A, (IX + d)               | A ← A + (IX + disp)                                                                          | 1   | 1 | 0 | 1  | 1<br>isp | 1 | 0  | 1     | 1     | 0  | 0 | 0 | 0 | 1 | 1 | 0 | 19       | 3      | x  | x | x   | ۷   | 0 | x |

|                | A, (IY + d)               | A - A + (IY + disp)                                                                          | 1   | 1 | 1 |    | 1<br>1   | 1 | 0  | 1     | 1     | 0  | 0 | 0 | 0 | 1 | 1 | 0 | 19       | 3      | x  | x | x   | ٧   | 0 | > |

|                |                           |                                                                                              |     |   |   | di | sp       |   |    |       |       |    |   |   |   |   |   |   | -        |        |    |   |     |     |   |   |

| ADC            | A, r                      | A - A + r + CY                                                                               | 1   | 0 | 0 | 0  | 1        |   | r  |       |       |    |   |   |   |   |   |   | 4        | 1      | x  | x | x   | ٧   | 0 | > |

|                | A, byte                   | A - A + byte + CY                                                                            | 1   | 1 | 0 | 0  | 1        | 1 | 1  | 0     |       |    |   |   |   |   |   |   | 7        | 2      | x  | x | x   | ۷   | 0 | × |

|                | A, (HL)                   | A - A + (HL) + CY                                                                            | 1   | 0 | 0 | 0  | 1        | 1 | 1  | 0     |       |    |   | _ |   |   |   |   | 7        | 1      | х  | х | x   | ٧   | 0 | x |

|                | $\overline{A, (IX + d)}$  | A ← A + (IX + disp) + CY                                                                     | 1   | 1 | 0 | 1  | 1        | 1 | 0  | 1     | 1     | 0  | 0 | 0 | 1 | 1 | 1 | 0 | 19       | 3      | X  | X | x   | ٧   | 0 | х |

|                |                           |                                                                                              |     |   |   | d  | isp      |   |    |       |       |    |   | _ |   |   |   |   | -        |        |    |   |     |     |   |   |

|                | $\overline{A}$ , (IY + d) | A - A + (IY + disp) + CY                                                                     | 1   | 1 | 1 | 1  | 1        | 1 | 0  | 1     | 1     | 0  | 0 | 0 | 1 | 1 | 1 | 0 | 19       | 3      | x  | х | x   | ۷   | 0 | x |

|                |                           |                                                                                              |     |   |   | d  | isp      |   |    |       | _     |    |   |   |   |   |   |   | -        |        |    |   |     |     |   |   |

| SUB            | A, r                      | A A r                                                                                        | 1   | 0 | 0 | 1  | 0        |   | r  |       |       |    |   | · |   |   |   |   | 4        | 1      | х  | x | x   | ٧   | 1 | х |

|                | A, byte                   | A - A - byte                                                                                 | 1   | 1 | 0 | 1  | 0        | 1 | 1  | 0     |       |    |   |   |   |   |   |   | 7        | 2      | х  | х | x   | ٧   | 1 | × |

|                | A, (HL)                   | A - A - (HL)                                                                                 | 1   | 0 | 0 | 1  | 0        | 1 | 1  | 0     |       |    |   |   | - |   |   |   | 7        | 1      | х  | х | x   | ۷   | 1 | × |

|                | A, (IX + d)               | A - A - (1X + disp)                                                                          | 1   | 1 | 0 | 1  | 1        | 1 | 0  | 1     | 1     | 0  | 0 | 1 | 0 | 1 | 1 | 0 | 19       | 3      | x  | x | x   | ۷   | 1 | х |

|                |                           |                                                                                              |     |   |   | di | sp       |   |    |       |       |    |   |   |   |   |   |   | -        |        |    |   |     |     |   |   |

|                | A, (IY + d)               | A - A - (IY + disp)                                                                          | 1   | 1 | 1 | 1  | 1        | 1 | 0  | 1     | 1     | 0  | 0 | 1 | 0 | 1 | 1 | 0 | 19       | 3      | x  | x | x   | V   | 1 | Х |

|                |                           |                                                                                              |     |   |   | di | sp       |   |    |       |       |    |   |   |   |   |   |   | -        |        |    |   |     |     |   |   |

# µPD70008/A

|                |                           |                            |    |   |   |    |     |     | 0 | perati |   |   |   |   |   |   |   |   | No. of | No. of |   |   | Fi | ags |     |   |

|----------------|---------------------------|----------------------------|----|---|---|----|-----|-----|---|--------|---|---|---|---|---|---|---|---|--------|--------|---|---|----|-----|-----|---|

| Mnemonic       | Operands                  | Operation                  | 7  | 6 | 5 | 4  | 3   | 2   | 1 | 0      | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Clocks | Bytes  | S | Z | Η  | PIV | N   | C |

| Eight-Bit Arit | thmetic Operation I       | nstructions (cont)         |    |   |   |    |     |     |   |        |   |   |   |   |   |   |   |   |        |        |   |   |    |     |     |   |