Microcomputer Products, 2116 Walsh Avenue, Santa Clara, CA 95050, (408) 246-2707

# CB1A 8080 CPU BOARD

### FEATURES:

#### SYSTEM COMPATIBILITY

. S-100 bus computer systems.

#### PROCESSOR TYPE

. 8080A microprocessor ; 2MHz

#### **ON-BOARD RAM**

- . 1K bytes of scratchpad RAM (2114), DIP switch addressable to any 1K boundary.

- . One wait state added; EPROMs can be disabled.

#### ON-BOARD RAM

- . 256 bytes of scratchpad RAM (2112-4), DIP switch addressable to any  $\frac{1}{4}$ K boundary.

- . RAM can be disabled.

### **ON-BOARD INPUT**

- . 8 bit parallel input port (with separate status) for a keyboard or for up to 8 sensing lines for home or industrial control applications.

- . DIP switch addressable to any port address from 0 to 31 (decimal).

#### **VECTOR JUMP**

- . Power-on/reset vector jump to beginning address of on-board EPROM (any 2K boundary).

- . Jump circuit can be disabled.

# **OTHER FEATURES**

- . MWRITE signal can be generated by jumper option.

- . Fully buffered address and data lines.

- . Solder masked PC board with gold plated edge connector contacts.

- . Low profile sockets provided for all ICs.

- . Power requirements (less EPROMs) -- +8V @ 0.95A, +16V @ 0.5A, -16V @ 25mA typical.

# CONTENTS

1.0 Assembly Instructions

2.0 Function Check

3.0 Set-up

- 3.1 General

- 3.2 Minimum CPU

- Input Port 3.3

- 3.4 Vector Jump

- 3.5 Prom, 2K

- 3.6

- Ram, IK SSM 8080 Monitor 3.7

- 3.8 Input Sensor

- 3.9 Reduce Ram Size

- 4.0 Trouble Shooting Hints

5.0 Theory of Operation

6.0 Warranty

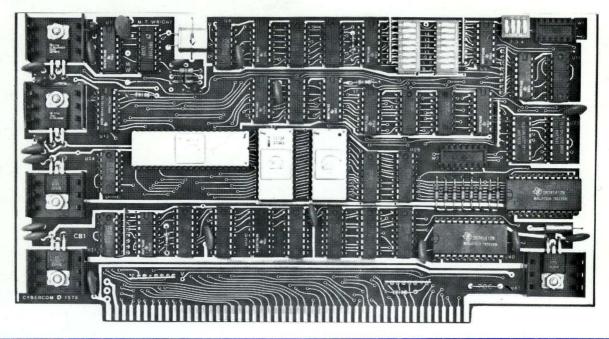

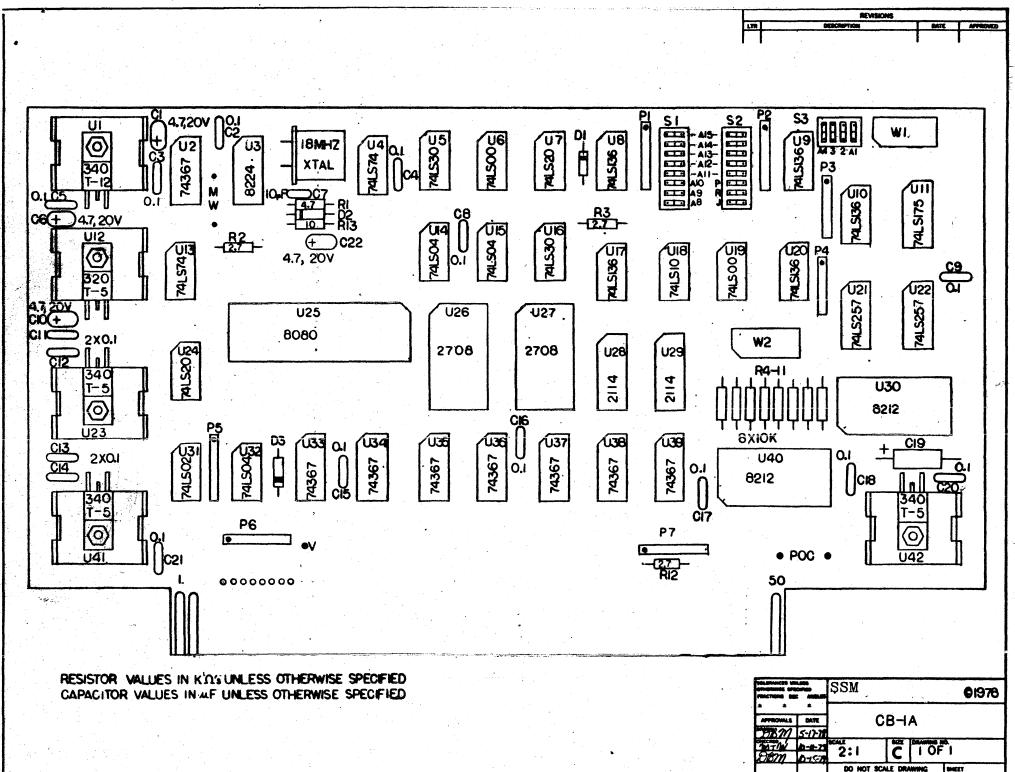

Assembly drawing

Parts Lists

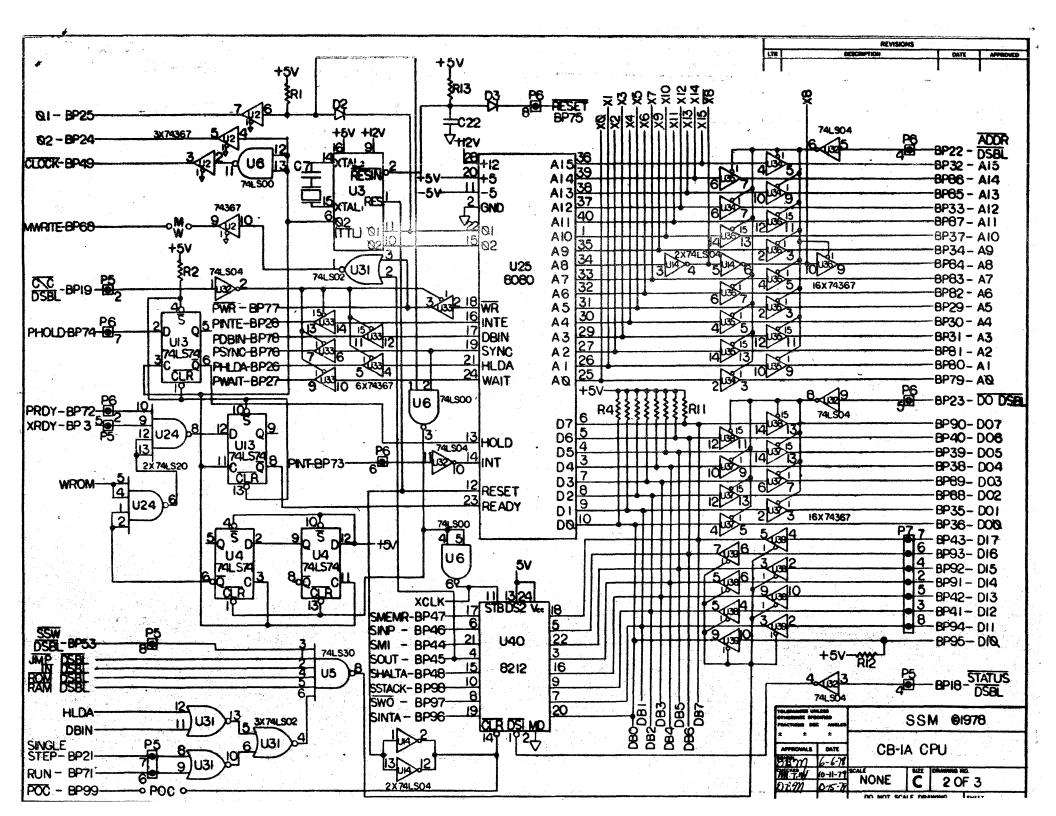

Schematic . . . .

|     | <u>CB1- CPU BOARD</u>                                                                                                                                                                                                                                                                                                    |                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.0 | ASSEMBLY INSTRUCTIONS (refer to Assembly Drawing)                                                                                                                                                                                                                                                                        |                                  |

|     | Chefk kit contents against parts list.                                                                                                                                                                                                                                                                                   |                                  |

|     | Check PC board for possible warpage and straighten if required.<br>To straighten the board, bend with the hands (not a vise) again<br>the warp. Sight down the edge of the board after bending to ch<br>if the warp was removed, if not then try bending again.                                                          | st                               |

|     | Insert the following sockets into the component side of the boa<br>with pin 1 indexed as indicated in the Assembly Drawing. DON'T                                                                                                                                                                                        |                                  |

|     | <pre>19- 14 pin sockets (U4-10,13-20,24,31,32,W1) 13 - 16 pin sockets (U2,3,11,21,22,33-39,W2) 2 - 18 pin sockets (U28,29) 4 - 24 pin sockets (U26,27,30,40) 1 - 40 pin socket (U25)</pre>                                                                                                                               |                                  |

|     | ( The component side is the side on which SSM (C) 1979 is printed                                                                                                                                                                                                                                                        | .)                               |

| П   | Place a flat piece of stiff cardboard of appropriate size on t<br>sockets to hold them in place.                                                                                                                                                                                                                         | op of the                        |

|     | Holding the cardboard in place against the sockets, turn the bo<br>and lay it on a flat surface. (Be sure that all of the socket<br>through the holes.)                                                                                                                                                                  |                                  |

|     | Note: Keep soldering iron tip clean to prevent rosin and sludg<br>being deposited on traces. Wipe tip frequently on a damp clot<br>wool.                                                                                                                                                                                 | 2                                |

|     | On each socket, solder two of the corner pins, choosing two tha<br>diagonally opposite of each other.                                                                                                                                                                                                                    | t are                            |

|     | Once the sockets are secured, lift the board and check to see i<br>are flat against the board. If not, seat the sockets by pressi<br>top while reheating each soldered pin.                                                                                                                                              |                                  |

|     | Complete soldering the remaining pins of each socket. Touch pi<br>with iron tip, allowing enough solder to flow to form a filet b<br>pin and pad. Keep the tip agianst the pin and pad just long en<br>produce the filet. Too much heat can cause separation of pad<br>from the board. A 600 degree iron is recommended. | etwe <b>en</b><br>ough <b>tq</b> |

|     | Insert and solder 7-2.7 K ohm resistor packs<br>(P1-P7). Be sure to observe polarity of pin 1 marked with<br>dot or notch,                                                                                                                                                                                               |                                  |

|     | Insert and solder the following resistors:                                                                                                                                                                                                                                                                               |                                  |

|     | <b>3-2.7K oh</b> m (Red, Violet, Red) (R2,3,12)<br><b>1-4.7K oh</b> m (Yellow, Violet, Red) (R1)<br><b>9-10K oh</b> m (Brown, Black, Grange) (R4-11,13)                                                                                                                                                                  |                                  |

|     |                                                                                                                                                                                                                                                                                                                          |                                  |

1

. .

•

Insert and solder 3 diodes (D1,2,3). Observe polarity of the banded end. 医无关的 医糖酸盐 计算法 计十分分子 Insert and solder: 医二溴酸盐酸酸盐盐酸盐酸 1-20 pf ceramic capacitor (C7) 16-0.1 uf ceramic capacitor (C2-5,8,9) (C11-18,20,21) Observing polarity (+ sign), insert and solder: terre a conservation de la constance de la cons 1- 10uf-33uf,10v (C19) 4-4.7uf dip tan. (C1,6,10,22) 化气化化的复数 白语的过去分词 Insert and solder 1-18 MHz crystal in place. Two holes have been provided on either side of the crystal to solder a strap over the crystal to hold it down. Insert and solder 2-8 position DIP switches with the numbers towards the left side of the board. Insert and solder 1-4 position DIP switch with the numbers towards the bottom of the board. Place regulators on the board so the mounting hole in the reglator is in line with the hole in the board. Mark leads for proper bending to match the board holes- allow for a bend radius Statute 1 18 1 Bend regulator leads to match holes in board. If available, apply thermal compound to the back side of each regulator case (the side that will contact the heat sink). Use just a little thermal compound. Too much is worse than none at all. Next position heatsink and insert regulator IC for each of the 5 regulators. (U1,12,23,41,42) Finally, position nut and lockwasher on top of regulator and secure from behind with screw in each case. Be sure regulators and heatsinks fit flat on board and then solder all regulator leads. Note: U1 & U12 are a different dash number than U23, U418 U42. 出,有**说**: "我,我 and a start start and a start and a start a st

,如意谋,将秦东山远的"月"。 清清:"我们来了你们是这个。"

an with a wat a point

LONGE COLOR

1-2

#### FUNCTIONAL CHECK 2.0

AND OTHER BOARDS COULD OCCUR.

If an ohmmeter is available, measure the resistance between the following pins:

化化化物学 化二乙烯酸 化丙乙烯

and the second

94 مربع 1004 م. مربع∎ م. ا

| Bus pin 50toBus pin 1: greater than 20Bus pin 50toBus pin 2: greater than 20Bus pin 52toBus pin 50greater than 30 | Negative Probe | Positive Probe | Resistance             |

|-------------------------------------------------------------------------------------------------------------------|----------------|----------------|------------------------|

|                                                                                                                   | Bus pin 50 to  | Bus pin 1      | greater than 20        |

| Bus pin 52 to Bus pin 50 greater than 30                                                                          | Bus pin 50 to  | Bus pin 2      | greater than 20        |

|                                                                                                                   | Bus pin 52 to  | Bus pin 50     | greater than <b>30</b> |

If your reading is below these values check for electrical shorts on your card.

Apply power (+8v to +10v) to board by plugging into the computer or by connection to a suitable power supply. Measure the outputs of the +5v regulators. 이번 사망 방문을 알았다.

The voltage should be between +4.8v and +5.2v...11# the regulator doesn't meet this test, then check the board for shorts or errors.

CAUTION: WHILE IT HAS NEVER HAPPENED TO US, SHORTED REGULATORS HAVE BEEN KNOWN TO EXPLODE WITH POSSIBLE INJURY TO EVES OR HANDS. BETTER SAFE THAN SORRY --- KEEP FACE AND HANDS CLEAR OF THE **REGULATOR SIDE OF THE BOARD DURING THIS TEST.**

Apply power +14v to +19v to Bus pin 2 and +14v to -19v to Bus pin 52 with Bus pin 50 ground. Verify that the outputs UI and U12 are about +12 volts and -5 volts respectfully...

Observing polarity, insert the rest of the chips into their sockets per the Assembly Drawing and user requirements per 3.0 (set-up),

Look the board over carefully. Check for bent 40 pins, poor solder joints or bridges and touch-up if necessarty. Using the Assembly Drawing, recheck part locations and polarity. A few minutes of careful inspection may save a few hours of trouble shooting.

### 3.0 SET-UP

Star Aste

11.0

3.1 General

The CB1 is equipped with four extra functions, not found on most \$7100 CPU cards:

(清)的高额()。

- 1) On-board 2708 Proms (8 X 2K).

- 2) On-board 2114 Ram (8 X 1K).

- 3) Vector Jump on Reset and Power-up.

- 4) Parallel input port with status port.

These different functions can be mixed in any combination to meet most user's needs. First a minimum CPU (see 3.2) must be assembled and then functions can be added per the instructions in sections 3.3 to 3.6.

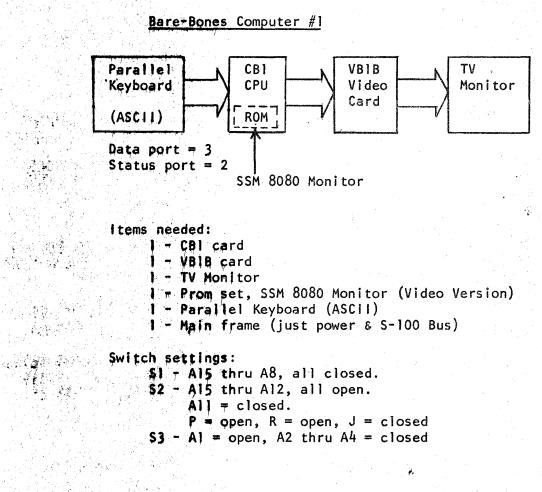

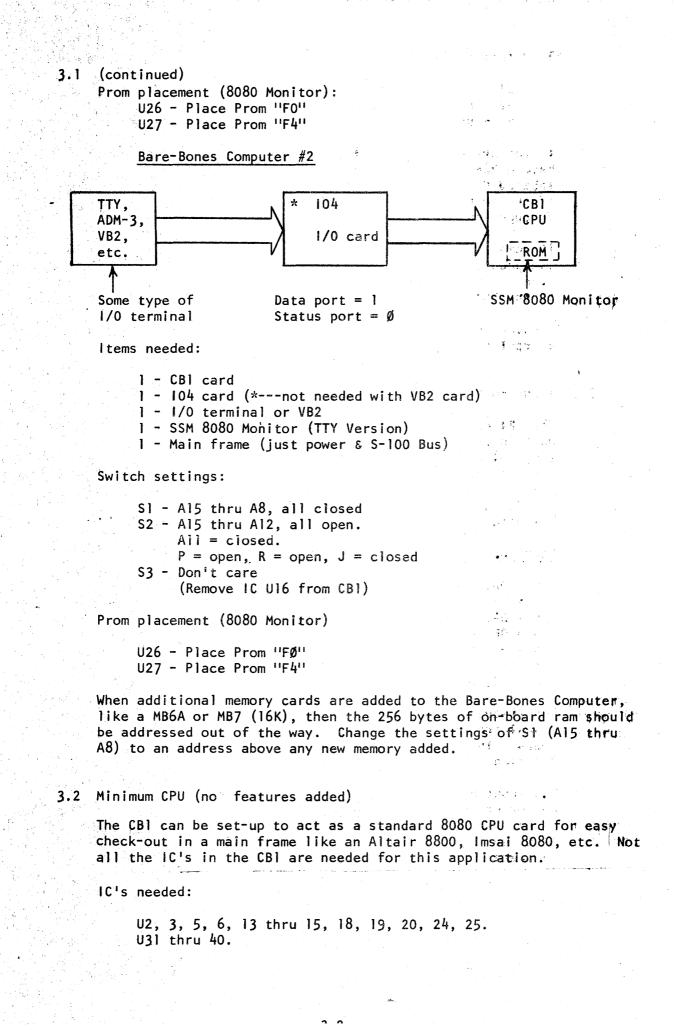

A basic computer system can be started around the CBI by the addition of only one more card --- the display! The output (or display) can be performed by using an 104 with a printer, VBIB with a TV monitor or the VB2 (to be announced in late-fall 1978). Here is an example of two Bare-Bones Computers:

To defeat the unused functions, set the following switches:

**\$1** - Don't care **\$2** - P = closed, R = closed, J = open **\$3** - Don't care

If you are using a system without a front control panel or doesn't have a MWRITE circuit, then add a jumper-wire between two pads labeled MW (upper left-hand corner). The CBl will provide MWRITE, if the jumper is added, by combining the signals PWR and SOUT together through logic.

If some of your S-100 cards use POC, then add a jumper-wire between two pads labeled POC (lower right-hand corner). The drive on the POC line is about 16 milliamperes maximum for a logic zero. A reset signal to the CBI will also generate a power-on-clear signal back to the bus.

A socket called "W2" has been provided on the CB1 for connecting it to a front control panel like a IMSA1 for check-out or normal operation.

#### 3.3 Input Port

The CBI has been designed with one on-board parallel input port. This port is really an input pair of ports with status at even addresses  $(A\emptyset = \emptyset)$  and data at odd addresses  $(A\emptyset = 1)$ . A 4-pole switch (S3) is used to set the wanted status address from  $\emptyset\emptyset$  to 1E.

Switch (S3)

| ۶S, | <b>=</b> | Status port | Ø  | <b>2</b> 5 | Switch | closed |  |

|-----|----------|-------------|----|------------|--------|--------|--|

| D   |          | Data port   | 1. | <b>1</b> 2 | Switch | open   |  |

Port Address (Hex)

| or c multicos (mext)                       |              |                  | ~** /~ | 11                |  |

|--------------------------------------------|--------------|------------------|--------|-------------------|--|

|                                            | 4            | 3                | 2      | 1                 |  |

| $S = \emptyset \emptyset, D = \emptyset 1$ | Ø            | ø                | Ø      | ø                 |  |

| $s = \emptyset 2, D = \emptyset 3$         | Ø            | ø                | Ø      | 1                 |  |

| $S = \emptyset 4, D = \emptyset 5$         | ø            | ø                | 11     | Ø                 |  |

| $S = \emptyset 6, D = \emptyset 7$         | ø            | ø                | 1      | 1                 |  |

| $S \neq \emptyset 8, D \neq \emptyset 9$   | Ø            | 1                | Ø      | ø                 |  |

| ~ 1# ~ 1m                                  | 400 Gan an o | , 100 000 000 00 |        | 9 400 CMB CMB CMB |  |

| S = 1E, D = 1F                             | 1            | 1                | 1      | a land            |  |

The status port is used to pass back to the 8080 CPU the Data-Available signal from the data port, if you have typed a character on the keyboard. The bit DØ (LSB) is used going low from the status port as a DAV flag.

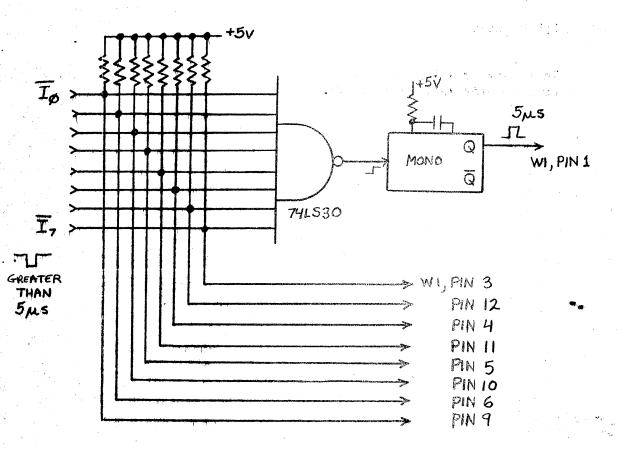

The input port socket is labeled "W1" and is in the upper right-hand corner of the board. Your parallel keyboard must provide a positive pulse of 5 microseconds wide or greater to W1, pin 1 to set the DAV flag when a key is depressed. Refer to schematics for pin numbers of the data input lines used in W1.

The parallel input port on the CB1 is designed to drive the vectorinterrupt lines of the S-100 bus, if you have a vector-interrupt board. The 8 vector-interrupt lines (Bus 4 thru 11) are provided with pads at the left side of the card's edge connector. The DAV flag from U30, pin 23 is brought out on a pad labeled "V" (near edge connector, lower left corner) to be connected directly to bus pin 4 thru pin 11 depending on system needs. Signal-V goes low if data is present at the input port and goes high when the input port is read. Only connect signal V if you have an interrupt driven system.

Additional IC's are needed to activate the input port.

IC's needed for Input: UIØ, 16, 30

To disable the input port in the future, just remove IC UI6 from the board.

3.4 Vector Jump

On power-up or reset, the CBI has a vector jump circuit which will get you to any 2K boundary address of your choice. This jump circuit is tied into the same DIP switch that selects the optional Prom's address, so it will jump to the beginning of the Prom no matter what address is set (refer to 3.5 for addressing). You do not need Phantom '(pin 67) control on any of your external Rom or Ram cards to allow the jump circuit to work.

To activate the Vector Jump, three IC's need to be added to the Minimum CPU board.

Ull, 21, 22

To enable the Vector Jump, close switch S2-J. To disable the jump circuit, open switch S2-J.

3.5 Prom (2 X 2708)

Two 2708 Proms can be added to the CBI with firmware devised by the user. Socket U26 should receive the first 1K of firmware and socket U27 will be the second 1K. The starting address for U26 is set by switch S2 at any 2K boundary.

with the switch closed, l = switch open and  $b \in \mathbb{R}^{n}$

3-4

# 3.5. (continued)

1

| Starting | Address |  |    | Swi | tch, | S2               |    |  |

|----------|---------|--|----|-----|------|------------------|----|--|

|          |         |  | 15 | 14  | 13   | 12               | 11 |  |

| ØØØØ     |         |  | ø  | ø   | Ø    | Ø                | Ø  |  |

| Ø8ØØ     |         |  | ø  | ø   | ø    | ø                | 1  |  |

| 1000     |         |  | ø  | ø   | ø    | 1                | ø  |  |

| 1800     |         |  | Ø  | Ø   | Ø    | 1.1              | 1  |  |

| 2000     |         |  | Ø  | Ø   | 1    | ø                | Ø  |  |

|          |         |  | -  |     | -    | · <del>-</del> . | •  |  |

| *FØØØ    |         |  | 1. | 1.4 | 1    | 1                | ø  |  |

| F8ØØ     |         |  | 1  | 1   | ]    | 1                | 1  |  |

\*---Switch setting for SSM 8080 Monitor ROMs.

To activate the on-board Proms, three IC's and two Proms need to be added to the CB1.

IC's needed for Prom: U4, 7, 9, 26 & 27

To enable the Proms, open switch S2-P. To disable the Proms, close switch S2-P.

U4 on the CBI forms a wait-state circuit that is used <u>only</u> when reading the Proms. One wait-state is added to the read cycle of the 8080, so that 500nsec or 1000nsec access time Proms can be used. If it is desired to defeat the wait-states for the Prom, then replace U4 with an IC Header with pin 6 tied to pin 7.

Since U26 & U27 are Proms tied to the internal bus of the CPU, no external (off card) device can read the Proms except the 8080 (U25), Some of the front control panels will not be able to examine the 2K area occupied by the Proms. (If you tried to examine the Proms on an Altair computer, all locations would show-up as FF.) The Proms can be read by software, since an on-board program like that SSM 8080 Monitor can be easily run on the CB1.

3.6 Ram (2 X 2114)

1

The CB1 has the option for on-board scratch Ram of IK bytes. This Ram can be set to any IK boundary from0000 to FF<sup>C</sup>0 by using switch \$1.

Do not try to DMA to the on-board Ram, since it is tied to the internal bi-directional bus of the 8080 and not the external \$-100. No DMA device can get access to the internal on-board Ram. U28 & U29 should be used for a Stack or Parameters used in a small operating system.

To activate the Ram, add four IC's to the card.

IC's needed for Ram: U8, 17, 28, 29

To enable the Ram, open switch S2-R.

The addressing of the Ram is similar to the Prom except you use switch S1.

Ø = switch closed, l = switch open

| Starting Address | -         | 15  | 14 | 13 | 12 | 11 | 10 |  |

|------------------|-----------|-----|----|----|----|----|----|--|

| *ØØØØ            |           | ø   | Ø  | ø  | ø  | ø  | ø  |  |

| Ø 4ØØ            |           | Ø   | ø  | Ø  | ø  | ø  | 1  |  |

| ø8øø             |           | ø   | ø  | ø  | ø  | 1  | 0  |  |

| ØCØØ             |           | Ø   | Ø  | ø  | 0  | 1  | 1  |  |

| 1000             | · · · · . | Ø   | ø  | Ø  | 1  | ø  | Ó  |  |

| ~ ~ ~ ~          |           | - ' |    | ·  | -  | -  |    |  |

| F8ØØ             |           | .1  | 1  | 1  | 1  | 1  | 0  |  |

| FCØØ             |           | •]  | I  | 1  | 1  | 1  | 1  |  |

Since the on-board Ram is internal to the CB1, some of the front control panels will not be able to examine this Ram. Software does have access to this Ram, it's just external hardware that doesn't.

# 3.7 SSM 8080 Monitor

If the SSM 8080 Monitor VI.O is used on the CB1 the following switch settings should be used:

SI - All switches closed, if no external memory is available.

S2 - Al5 thru Al2, open. All = closed. P = open. R = open, if

no external memory is at address zero. J = closed for Vectorjump.

S3 - A2 thru A4, all closed. Al = open for using VB1B. Al = closed for using VB2 or 1/0 terminal.

Be sure to connect-up the MWRITE jumper on the CB1, if you have no front control panel.

The SSM 8080 Monitor comes in two versions. One is called "TTY" and is intended to communicate with an I/O device like a ADM-3, teletype, VB-2, etc. on ports zero and one. The other version is called "Video" and will communicate with a parallel keyboard on ports two & three and the VBIB at address  $\beta 0 0 0$ . Be sure to specify the right Monitor program to meet your needs.

The SSM 8080 Monitor uses the top 64 bytes of contiguous memory starting at  $\emptyset \emptyset \emptyset \emptyset$  for its stack and parameters. If only the on-board Ram is used for memory at zero, then addresses  $\emptyset \Im \emptyset \emptyset$  to  $\emptyset \Im FF$  will be used as scratch memory. Don't write over  $\emptyset \Im \emptyset \emptyset$  to  $\emptyset \Im FF$ , unless you have more than IK -bytes of memory or the Monitor will go crazy.

If you are using only 1K bytes of memory with the SSM 8080 Monitor and you wish to write some very small programs, only write between  $\emptyset\emptyset1\emptyset$  to  $\emptyset3C\emptyset$ . The SSM Monitor has software breakpoints for debugging purposes which uses the restart 1 instruction (from  $\emptyset\emptyset\emptyset8$  to  $\emptyset\emptyset\emptysetF$ ). Before executing a small program, be sure to set the stack pointer into the useful memory range of  $\emptyset\emptyset1\emptyset$  to  $\emptyset3C\emptyset$ . To move the stack, do the following:

- 1) Type the letters (all capital) XS.

- The computer will respond with its user stack address of ØlØØ-.

- 3). Now type3CØ followed by a carriage-return. This will move the stack from 100 Hex up to 3C0 Hex. This stack pointer can be assigned to any place you have free memory. Remember that stack data grows downward in memory, so enter the top address of the stack, not the bottom.

- 4) If you re-enter the monitor routine at FØØØ or FØ21, the stack will be re-initialized at Ø1ØØ. Be sure to repeat steps (1) thru (3) everytime you execute a small program and are using only IK bytes of memory.

3.8 Input Sensor

If the parallel input port (section 3.3) is not used for a keyboard input, then here are a few other ways it can be used.

1) Byte Sensor (No hand-shaking signals)

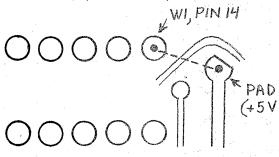

The input port (U30) can be set-up to sense continuous data on its input without any strobe pulses. W1, pin 1 has to be pulled up by a 2.7K resistor to +5 volts to enable the inputs of U30. There is +5 volts available from a pad just to the right of W1, pin 14 on the backside of the card. Add a jumper-wire from W1, pin 14 to pad.

### Backside of Card

(if you ever want to use the +5 volts from this pad for external power, don't draw more than 80 milliamperes from it.) Now connect the 2.7K resistor,  $\frac{1}{4}$  watt from W1, pin 14 to W1, pin 1 on the interfacing header-connector to W1.

The input port can now be used to sense switches (8 possible) or logic signals on its input in a continuous scanning program.

# 2) Byte Sensor (Hand-shaking)

The input port (U30) can be set-up as a interrupt sensor in a system that does polling. The strobe input (W1, pin 1) needs a positive pulse of about 5 microseconds. To provide a pulse, when only one input bit changes at a time, a two 10 circuit is needed.

This two IC circuit will set the status flag of the input port and place the interrupt code (10 thru 17) into U30. No more interrupts will be generated until the one low going interrupt line is back to a logic one. The interrupt lines can be normally-open momentary switches for special console features.

Be sure to connect pad "V" (lower left corner) into your interrupt system's bus line for vector interrupts, if you have that card.

# 3.9 Reduce Ram Size

If the user wishes to reduce the IK of on-board RAM to 512 or 256 bytes only, a couple of jumpers will have to be added.

| On-board Memory Size | Jumper 1                     | Jumper 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -1024 bytes          |                              | None the second s |

| 512 bytes            | U18, pin 4 to<br>U17, pin 11 | None                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 256 bytes            | Same                         | U17, pin 3 to<br>U17, pin 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

This memory size flexibility should give the user a wide choice of hardware configuration to better adapt the CB1 to any special system needs.

$\mathcal{D}_{1}[\mathcal{O}_{1}] = \{\mathcal{O}_{\mathcal{O}_{1}}\}$

나는 말 같다.

and story think to start if

1900 - 1913 1914 - 1913

1 2.

#### 4.0 TROUBLE SHOOTING HINTS

Check for proper settings of DIP switches. a. Verify that all ICs are in the correct sockets. Ь. Visually inspect all ICs to be sure that leads are in the sockets and c. not bent under. <del>,</del> 1999 Verify that the output voltage of each regulator is correct. **d**. Inspect back side of board for solder bridges. Run a small sharp knife e. blade between traces that appear suspicious. A magnifying glass is a must for this type of inspection. Actual and the f. If you have any problems with the Input Port: 1) Check U30 (8212) which is the data port. 2) Check U39 (74367). Part of this IC is used as a status port circuit. 3) Check U19 (74LS00) and U16 (74LS30) which form part of the addressing circuit for the port select. 4) Check Ul0 (74LS136) which is used for DIP switch selection of the port address. If you have any problems with the Vector Jump: α. 1) Check Ull (74LS175) which sequences the jump instruction to the 8080. 2) Check U21 & U22 (74LS257) which place the jump code and address onto the bi-directional bus of the 8080. h. If you have trouble reading the on-board Proms: 1) Check voltages to U26 & U27 (2708). · 这些我的问题,我们的问题,我们就是一个问题。 Pin 12 = ground Pin 18 = groundgeneral contractor and the second second Pin 19 = +12v. . Pin 21 = -5vPin 24 = +5v2) Gheck chip-select from U7 (74LS20) which drives the Proms. 3) Check U9 & U20 (74LS136) which controls Prom addressing. 4) Check U4 (74LS74), if the 8080 gets into a continuous wait-state when the Prom is read. a contra per line de ser i. If the On-board RAM has problems: 1) Check U18 (74LS10) and U19 (74LS00) which controls chip-select. Check U8 & U17 (74L\$136) for addressing problems.

Check U28 & U29 (2114) for bent pins. and the second 化合物化 化化化合物化化合物合物 , i di kana sana a sana sa the same that at the set of the set

# 5.0 THEORY OF OPERATION

Usage

1) U2 (74367) is used to buffer Phase 1 & 2, Clock and MWRITE signals onto the bus.

and the second

a part of a state

CAR CAR

- 2) U3 (8224) is used to generate Phase 1 & 2 to the 8080 and also Power-On-Clear.

- 3) U4 (74LS74) is used to time out two wait-states for on-board ROM read cycles.

- 4) U; (74L\$30) is used to decode the conditions necessary to disable the input trimstate buffers to the 8080.

- 5) US (74LSOO) is general logic.

- 6) U7 (74LS20) is used to decode the chip select signals for the two PROMs (U26  $\varepsilon$  U27).

- 7) U3  $\varepsilon$  U17 (74LS136) is used to decode the IK boundary address for the on-board RAM (U28  $\varepsilon$  U29).

ಬ್ ಕ್ಷೇಟ್ ಬಿ 🖕 🖓

- 8) UP & U20 (74LS136) is used to decode the 2K boundary address for the cn-board ROM (U26 & U27).

- 9) UIO (74LS136) is used to decode the lower address bits of the parallel input port.

- 10) UII (74LS175) is a sequencer of the 3 byte vector jump instruction.

- 11) U13 (74LS74) is used to time  $\pi$  in the presence of the PHOLD and PRDY s gnals to the 8080.

- 12) U 4 & U15 (74L\$04) is mainly used to invert & buffer the upper eight address lines from the 8080 IC into address decode logic (U8, U9, U10, U2, U16).

- 13) U 6 (74LS30) is used to decode the upper address bits of the parallel input port.

- 14) U 8 (74LS10) is used to decode chip-select and write-enable signals for the RAM (U28 & U29).

- 15) U.9 (74LS00) is mainly used to chip-select the status or input port on the CB1.

- 16) U21 & U22 (74LS258) are multiplexers used to drive the jump instruction onto the internal 8080 data bus.

- 17) U24 (74LS20) is used for inputting not-ready signals from PRDY, XRDY or the ROM into flip-flop U13.

- 18) U25 (8080). The Brains!

- 1) U30 (8212) is the parallel input port IC.

- 20) U31 (74LS02) is mainly used to decode conditions from a future front panel control circuit for which the input buffers to the 8080 should be disabled.

1. S. 1. 1.

- 21) U32 (74LSO4) is used to buffer special disable signals from the S-100 onto the CB1.

- 22) U33 (74367) is used to buffer PSYNC, PDBIN, PWR, PINTE, PHLDA, and PWAIT signals to the bus.

- 23) U34, U35, & U36 (74367) are used mainly to buffer the 8080 address lines onto the bus.

- 2) U37 & U38 (74367) are used to buffer the output data lines.

- 25) U38 & U39 (74367) are used to buffer the input data lines.

- 25) U40 (8212) is used to decode and drive CPU Status signals onto the S-100 bus.

### Overation

#### Address Buffering

The address lines AØ thru A15 of the 8080 IC are passed through Tri-State biffers (U34, U35, U36) for additional current drive to the bus. The address buffers can be turned off by applying a logic zero on bus line 22 which is called "Not\*Address Disable".

# Dita Buffering, Output

The data lines DOØ thru DO7 of the 8080 IC are passed through Tri-State buffers (U37, U38) for additional current drive to the bus. The output data lines can be turned off by applying a logic zero on bus line 23 which is called "Not Data Out Disable".

#### Data Buffering, Input

The data lines DIØ thru DI7 are Tri-Stateable to the 8080, so that external bus data or internal RAM, ROM or 1/0 data can be passed to the CPU. The input data buffers (U38, U39) are disabled on the following conditions:

- 1) The front panel wants access to the data lines, then SSW DSBL bus line is pulled low.

- 2) The jump circuit on the CB1 is activated, then U5, pin 1 is pulled low.

- 3) If the input port is being read on the CB1, then U5, pin 2 is pulled low.

\*--- Not is being used as a logic definition.

- 4) When reading on-board ROM, U5, pin 4 is pulled low for input bus data disable.

- 5) When reading on-board RAM, U5, pin 5 is pulled low.

- 6) If the computer is not running (bus line 71 low) and there is no "DBIN" signal (U31, pin 11 is low), then the buffers are off.

Processor Control Signal Buffering

The following control signals are buffered by U33: DBIN --- Strobe generated by the 8080 when it wants to read the bus. Called "Data Bit IN".

- WR --- Negative strobe generated by the 8080 when it wants to write to the bus. Called "Not WRite".

- INTE --- Interrupt enable flag.

- SYNC --- A strobe pulse generated at the beginning of each instruction fetch, write to memory or I/O operation.

- WAIT --- A flag to indicate that the CPU is in a waiting loop, if the Ready line (U25, pin 23) is pulled low.

- HLDA --- Hold Acknowledge flag indicates that the CPU has Tri-Stated (and stopped) and turned over its address and data lines to another device to use.

The control signals can be Tri-Stated by pulling bus line 19 to ground (called "Not C/C Disable").

#### Processor Status Buffering

The 8080 has eight status signals which are latched into a 8212 IC (U40) and distributive onto the bus.

- MEMR --- This flag is at a logic one when the CPU is reading memory.

- INP --- This flag is at a logic one when the CPU is reading 1/0.

- Ml --- This signal is high for the first byte of a one, two or three byte instruction.

OUT --- This flag is high when the CPU is writing to 1/0.

- HALTA -- This signal is high for the execution of a halt instruction.

- STACK -- This flag is a logic one when the CPU is using its 16-bit stack register to read or write to memory.

- WO --- This flag is a logic zero when the CPU is going to write to 1/0 or memory.

- INTA --- This flag is a logic one when the CPU has completed an instruction and is responding to an interrupt request.

The status signals can be disabled by pulling bus line 18 to ground (called "Not Status Disable").

#### Clock Signals

U3 is the master clock chip for the CB1 and divides a 18 mHz crystal frequency by nine to get a 2 mHz frequency. U3 generates a two phase clock:which is used by the CPU and the bus for timing. U3, pin 11 & pin 10 generates phase one and phase two clocks at +12V high for 8080 operation. U3, pin 6 generates a TTL signal (only +5v max.) for use with standard logic and this signal is buffered to provide bus signals called "Phase 2 and Not Clock". A phase one clock is created for the bus by driving a tri-state buffer through a diode (D2) pulled-up by a resistor (R1).

Special Memory Write Signal A memory write strobe signal has been created on the CBI to replace an old front control panel signal. The SOUT status signal has been combined (through U31) with WR to generate a signal that only goes high on memory write functions. The final signal is called MWRITE, and is jumper selected by the user.

#### Power-on Reset

Power-on reset is created by a long time constant network (R13 & C22) connected to the reset input of U3. When power is turned on, the relatively slow rate at which C22 charges up holds a logic zero on U3, pin | until a threshold on U3, pin 2 is passed. Standard reset is achieved by discharging C22 thru a diode controlled by bus line 75.

### Ready Signal

The CPU can be put into a wait-state by three control signals:

PRDY ---- Bus pin 72 (going low) XRDY ---- bus pin 3 (going low) WROM --- U24, pin 5 (going high)

The not-ready signal is sampled by U13, pin 12 in time to the phase two clock.

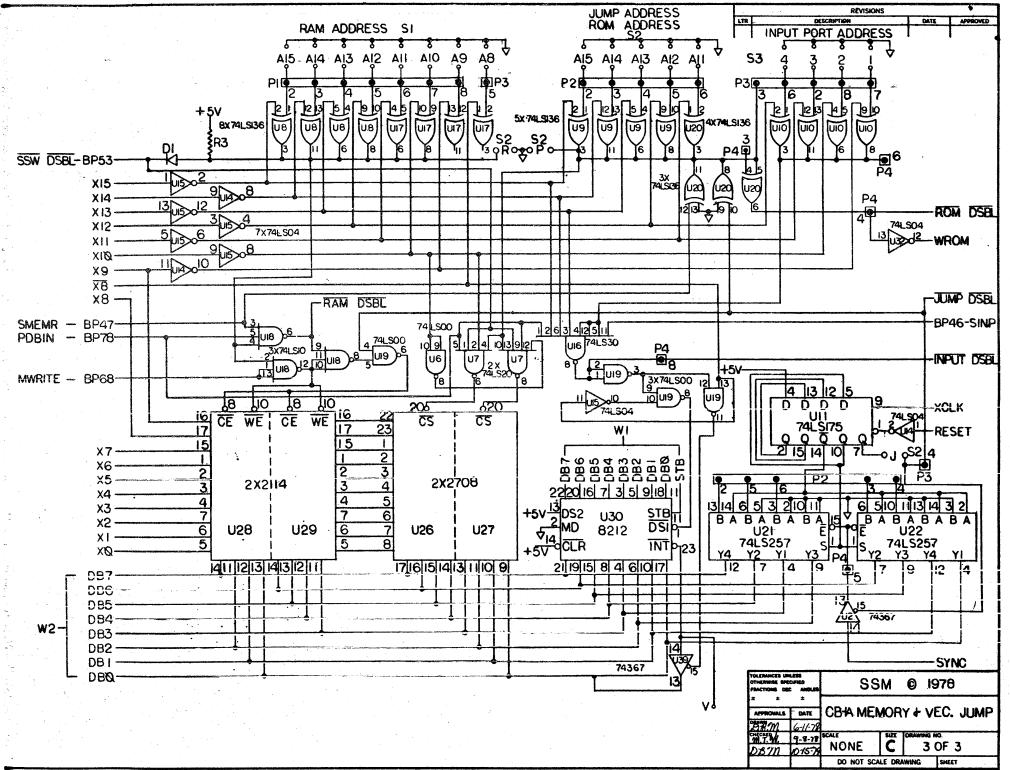

#### Ram Address (on-board)

The upper eight address lines A8 through A15 are inverted and then compared with the code on switch S1 by two exclusive-or chips U8 & U17. The outputs from U8 & U17 are strapped together and will only be a logic one when the switch code matches the inverted address. This logic one level is used as an enable signal at U18 for read, write and chip select of the Ram (U28 & U29). The logic one address enable signal can be made invalid by closing \$2-R or applying a low level to bus pin 53.

U18 conbines signals labeled SMEMR, PDBIN, and address enable to generate a low on UI8, pin 6 during memory read. U18 combines MWRITE and address enable to generate a low on U18, pin 12 during memory write. Both read and write (low going signals) are combined by two nand-gates to generate a chip select to U28 and U29.

5-4

### Rom Address (on-board)

Similar in operation as Ram addressing except U9 & U20 is used in decoding. S2-P and jump disable signal will make the Rom address invalid when they are low.

The address enable signal is applied to U7 along with PDBIN and AlØ to chip select the Roms on IK boundaries during memory read. SMEMR signal is combined with the address enable signal to U7 by the gate U20, pin 11. U26 is the first IK of EPROM and U27 is the second 1K.

### Input Address (on-board)

The input addressing circuit uses U16 (8-input nand) and U10 (quad exclusive-or) to select one of sixteen possible port address pairs. The upper three bits of the port address must be zero. The address bits, DBIN signal, and SINP status are combined in U16 to generate an input port enable signal (U16, pin 8 going low). U19 picks up the input enable signal and combines it with the least significant bit of the port address (inverted & non-inverted) to select the status port (U19, pin 11 low) or the data port (U19, pin 8 low).

#### Jump Code

The jump circuit uses three IC's, Ull sequences the instruction and U21 & U22 apply the code to the CPU to get a jump instruction, switch S2-J must be closed. If a reset is generate on the bus, this signal clears Ull to zero and the CPU starts a new M1 cycle. The first XCLK pulse (PSYNC and PHASE 1) clocks a one into Ull, pin 4. Ull is used like a 4-bit shift register and now has a logic one of pin 2 with zero's on pin 15, 10, 7. Ull, pin 14 ( $\overline{Q}$ ) is high and the A-inputs of U21 & U22 is selected to apply "C3" code to the bus. Another XCLK is generated by the CPU and now Ull, pin 15 is a one (pin 14 is a zero). The A-inputs of U21 & U22 are all zero's, so a "ØØ" code is applied to the bus. XCLK occurs again and Ull, pin 10 goes high to change the select line of U21 & U22 to the B-inputs. The B-inputs pass on the address selected by switch S2 to the CPU chip. With one more XCLK pulse, Ull, pin 7 goes high disabling U21 & U22.

The tri-state buffer U2, pin 13 which is driving the enable line of U21 & U22 is to prevent any data transfer during PSYNC so the status signals (SMEMR, SINP, etc.) can get out of the 8080 chip.

# 6.0 WARRANTY

SSM warrants its products to be free from defects in materials and/or workmanship for a period of 90 days for kits and bare boards, and one (1) year for factory assembled boards. In the event of malfunction or other indication of failure attributable directly to faulty workmanship and/or material, then, upon return of the product (postage paid) to Solid State Music at 2116A Walsh Ave., Santa Clara, California, 95050 "Attention Warranty Claims Department", Solid State Music will, at its option, repair or replace the defective part or parts to restore said product to proper operating condition. All such repairs and/or replacements shall be rendered by Solid State Music without charge for parts or labor when the product is returned within the specified period of the date of purchase. This warranty applies only to the original purchaser.

This warranty will not cover the failure of Solid State Music products which, at the discretion of Solid State Music, shall have resulted from accident, abuse, negligence, alteration, or misapplication of the product. While every effort has been made to provide clear and accurate technical information on the application of Solid State Music products, Solid State Music assumes no liability in any events which may arise from the use of said technical information.

This warranty is in lieu of all other warranties, expressed or implied, including warranties of mercantability and fitness for use. In no event will Solid State Music be liable for incidental and consequential damages arrising from or in any way connected with the use of its products.

A Black Chalance and

DO NOT SCALE DRAWING

# CB1 Parts List

# Chip Pack

| 2 - U6, 19        | 74L\$00                |

|-------------------|------------------------|

| 1 - U31           | 74L\$02                |

| 3 - U14, 15, 32   | 74L\$04                |

| 1 - U18           | 74L\$10                |

| 2 - U7, 24        | 74L\$20                |

| 2 - U5, 16        | 74L\$30                |

| 2 - U4, 13        | 74L\$74                |

| 5 - U8,9,10,17,20 | 74L\$136               |

| 1 - U11           | <b>74L\$175/7417</b> 5 |

| 2 - U21, 22       | 74L\$257               |

| 8 - U2,33-39      | 74367/8097             |

| 2 - U30, 40       | 74\$412/8212           |

| 1 - U3            | 74L\$424/8224          |

# Socket Pack

| 1<br>2<br>4 | <b>4</b> position DIP switch<br>8 position DIP switch<br>24 pin sockets<br>40 pin socket |

|-------------|------------------------------------------------------------------------------------------|

| 2           | 18 PIN sockets                                                                           |

# Diode Pack

| 3 - D1,2,3 |                                                                                                                       | lN270 | germanium |

|------------|-----------------------------------------------------------------------------------------------------------------------|-------|-----------|

| 1          | ан<br>1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - 1917 - | 18mhz | xtal      |

# Hardware Pack

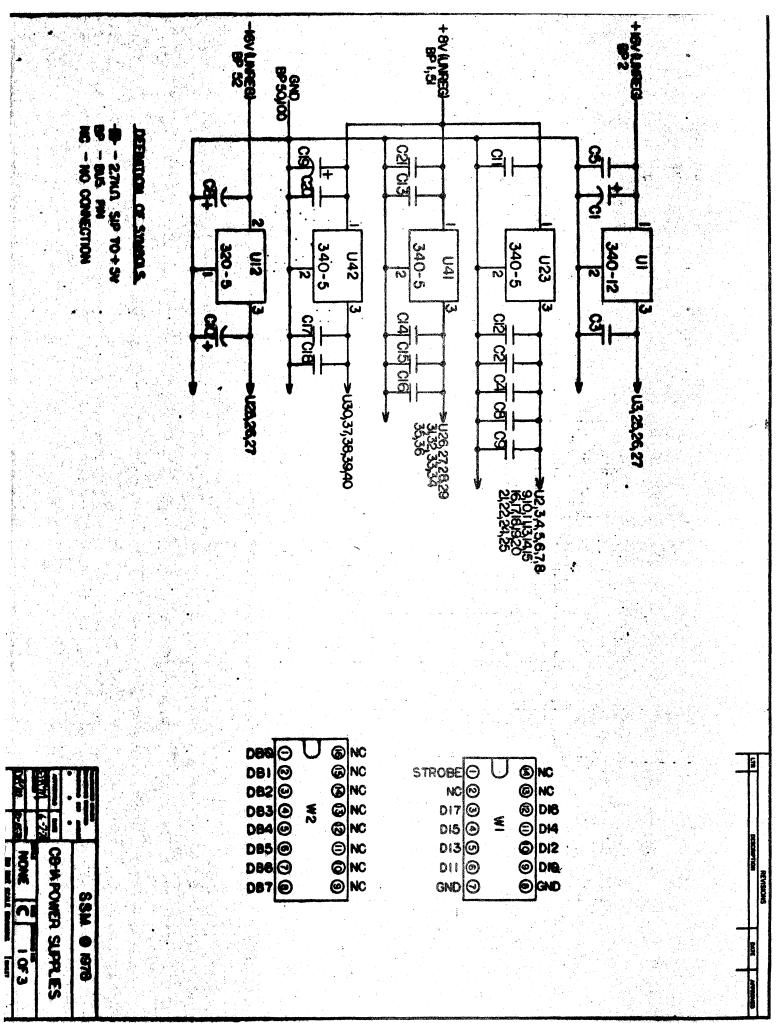

| 3 - U23,41,42 7805/<br>1 - U1 7812/ | '320T-5<br>'340T-5<br>'340T-12<br>#6 hardware<br>sinks |

|-------------------------------------|--------------------------------------------------------|

|-------------------------------------|--------------------------------------------------------|

### Memory Pack

| 2 | <br>U28,2 | 29 |    |  | 2114-4 |

|---|-----------|----|----|--|--------|

| 1 | <br>U25   |    | 14 |  | 8080   |

# Capacitor Pack

| <b>1 - C7</b>               | 20pf-22pf disc        |  |

|-----------------------------|-----------------------|--|

| 16 - C2 - 5, 8, 9, 11 - 18, |                       |  |

| 20,21                       | 0.luf disc            |  |

| 4 - C1, 6, 10, 22           | 4.7uf 20v dipped tant |  |

| <b>1 - C19</b>              | 10-33uf 10v tant      |  |

# Resistor Packs

3 - R2,3,12 7 - P1-7 1 - R1 9 - R4-11,13 2.7K 1/4w 5% 2.7K x 7 SIP/2.2K x 7 SIP 4.7K 1/4w 5% 10K 1/4w 5%

# Misc.

1

PC board

19

14 pin sockets

13

16 pin sockets

2 - U26,27

2708 (optional)

BERNES IN