# MDX SYSTEM OEM MANUAL

MDX SYSTEM

OEM MANUAL

|               |            |      | APPL       | ICABLE PRODU | JCT | NUMBERS   |       |

|---------------|------------|------|------------|--------------|-----|-----------|-------|

| Document No.: | 3000830    |      | Board      | PWB. Assy.   |     | Prog. As  | ssy.  |

| Revision:     | А          |      | FWD0106    | 0004220      |     | 100200    | 01    |

| Date:         | August 23, | 1982 | Formatter  | Rev. A and   | up  | Rev. A an | nd up |

|               |            |      | LSI-11 I/F | 0003770      |     | 100193    | 39    |

|               |            |      | <u>.</u>   | Rev. D and   | up  | Rev. B an | nd up |

.

Warning: This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instructions manual, may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference in which case the user at his own expense will be required to take whatever measures may be required to correct the interference.

See section II-M for additional information.

# CONTENTS

| I.   | INTRODUCTIONI -                                                                  | 7        |

|------|----------------------------------------------------------------------------------|----------|

|      | A. PRODUCT LINE OVERVIEWI -<br>B. FEATURESI -<br>C. FUNCTIONAL SPECIFICATIONSI - | 8        |

|      | D. PHYSICAL SPECIFICATIONS                                                       |          |

|      | E. DISK DRIVE DATA $I - 1$                                                       |          |

|      |                                                                                  | ·        |

| II.  | SYSTEM INSTALLATION AND OPERATIONII - 1                                          | .4       |

|      | A. UNPACKINGII - 1                                                               | .4       |

|      | B. SITE SELECTIONII - 1                                                          | •••      |

|      | C. SYSTEM GROUNDINGII - 1                                                        | .4       |

|      | D. POWER ON DELAYII - 1                                                          |          |

|      | E. SYSTEM CONFIGURATIONII - 1                                                    |          |

|      | Power Capacity and FeaturesII - 1                                                |          |

|      | System Fuses and Circuit Breakers                                                |          |

|      | Cooling CapacityII - 1                                                           |          |

|      | Board LocationII - 1                                                             |          |

|      | Bus LoadingII - 1                                                                |          |

|      | MDX Backplane ConfigurationII - 1                                                | -        |

|      | F. CABLE PROVISIONSII - 1                                                        |          |

|      | G. BUS TERMINATIONII - 1                                                         |          |

|      | H. MDX SYSTEM SWITCHESII - 2                                                     |          |

|      | AC PowerII $-2$                                                                  | -        |

|      | Input Voltage SelectionII - 2                                                    |          |

|      | External Switches and LED's                                                      |          |

|      | Internal Switches and LED'sII - 2                                                |          |

|      | I. SYSTEM STRAP OPTIONSII - 2                                                    |          |

|      | J. BOOTSTRAPPING (PROGRAM LOADING FROM DISK)                                     |          |

|      | Error Reporting                                                                  | •        |

|      |                                                                                  | 50<br>86 |

|      | M. MEETING FCC RULES AND REGULATIONS                                             | -        |

|      | M. MELTING FOC ROLES AND REGULATIONS                                             | ,0       |

| 111. | DISK SURFACE MANAGEMENT AND FORMATS                                              | ;7       |

|      | A. DISK SURFACE LAYOUT                                                           | 37       |

|      | B. DISK SURFACE ADDRESSING                                                       | 57       |

|      | C. SECTOR INTERLEAVING                                                           | 38       |

|      | D. CYLINDER OFFSETIII - 3                                                        | 38       |

|      | E. FLOPPY DISK TRACK FORMATS                                                     | 39       |

|      | F. FIXED DISK TRACK FORMAT                                                       |          |

|      | G. ERROR DETECTION AND CORRECTION                                                | +3       |

| IV.  | PROG                 | RAMMER'S GUIDEIV - 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | A.<br>E.<br>D.<br>F. | MODES OF OPERATION.IV - 44RX02 Compatible Mode.IV - 44Extended Mode.IV - 44Error Retry Policy.IV - 45Error Correction Policy.IV - 46HOST/CONTROLLER PROTOCOL.IV - 46RX02 Protocol.IV - 46CONTROLLER REGISTERS.IV - 46REGISTER DESCRIPTION FOR COMPATIBLE MODE.IV - 47Command and Status Register (CSR).IV - 47Multipurpose Data Register (DBK).IV - 51REGISTER DESCRIPTION IN THE EXTENDED MODE.IV - 56Command and Status Register (CSR).IV - 56Multipurpose Data Register (CSR).IV - 56Command and Status Register (DBR).IV - 58EVTENDED MODEIV - 58EVTENDED MODEIV - 58 |

|      | G.<br>H.             | EXTENDED MODE FUNCTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ۷.   |                      | TEM TESTING AND TROUBLE ISOLATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VI.  | WIN                  | CHESTER FLAW MANAGEMENTVI - 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|      | A.<br>B.<br>C.<br>D. | OVERVIEW.VI - 92FLAW MAP INITIALIZATION PROCEDURE.VI - 92FLAW MAP FORMAT.VI - 93PROCESSING THE RAW FLAW DATA.VI - 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VII. | SYS                  | TEM MAINTENANCEVII - 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      | А.<br>В.             | PREVENTIVE MAINTENANCEVII - 99<br>ENCLOSURE DISASSEMBLYVII - 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

r

5

.

# Figures

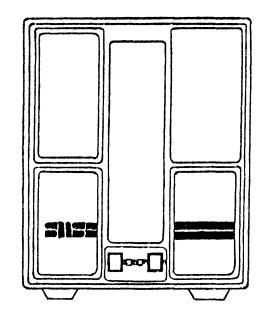

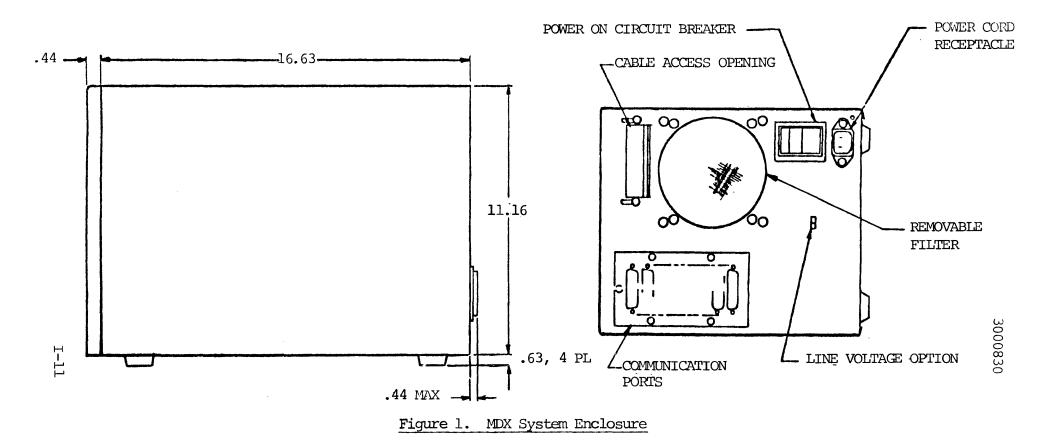

| Figure | 1.  | MDX System Enclosure                  | .11 |

|--------|-----|---------------------------------------|-----|

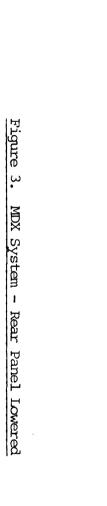

| Figure | 2.  | MDX System - Isometric View           | .12 |

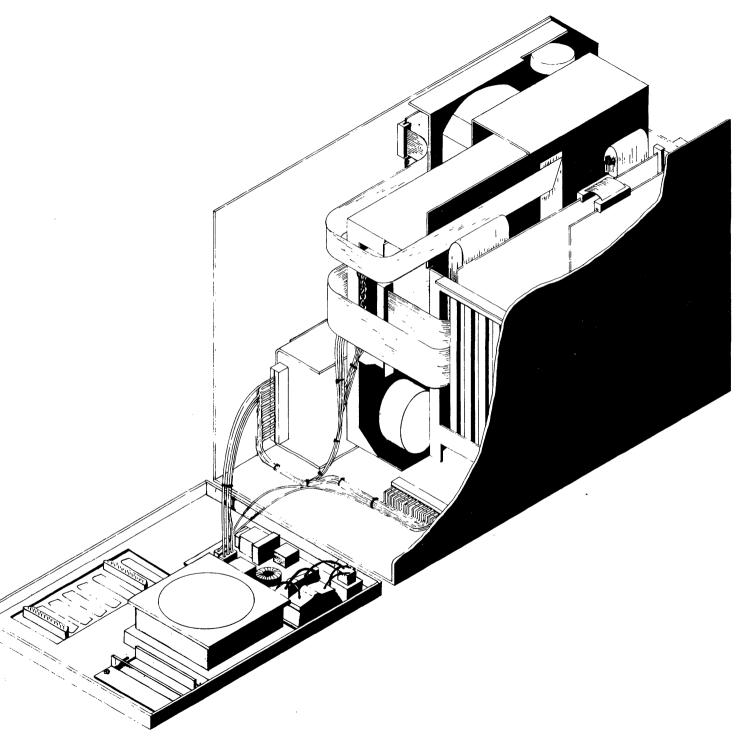

| Figure | 3.  | MDX System - Rear Panel Lowered       | .13 |

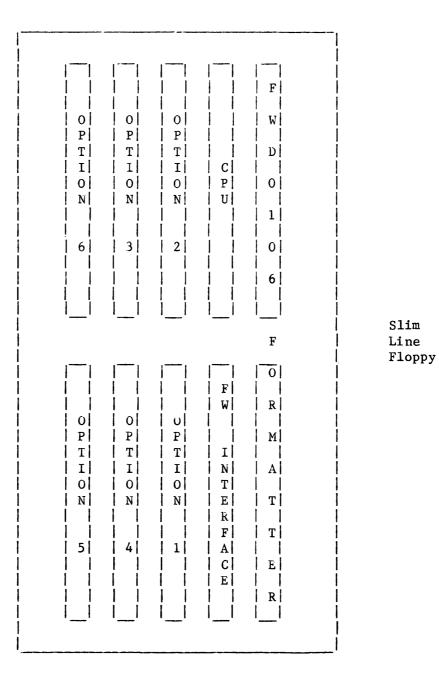

| Figure | 4.  | MDX Backplane Layout                  | .18 |

| Figure | 5.  | Cable Assembly, DLV11-J to Terminal   | .19 |

| Figure | 6.  | Cable Assembly, DLV11-J to Modem      | .20 |

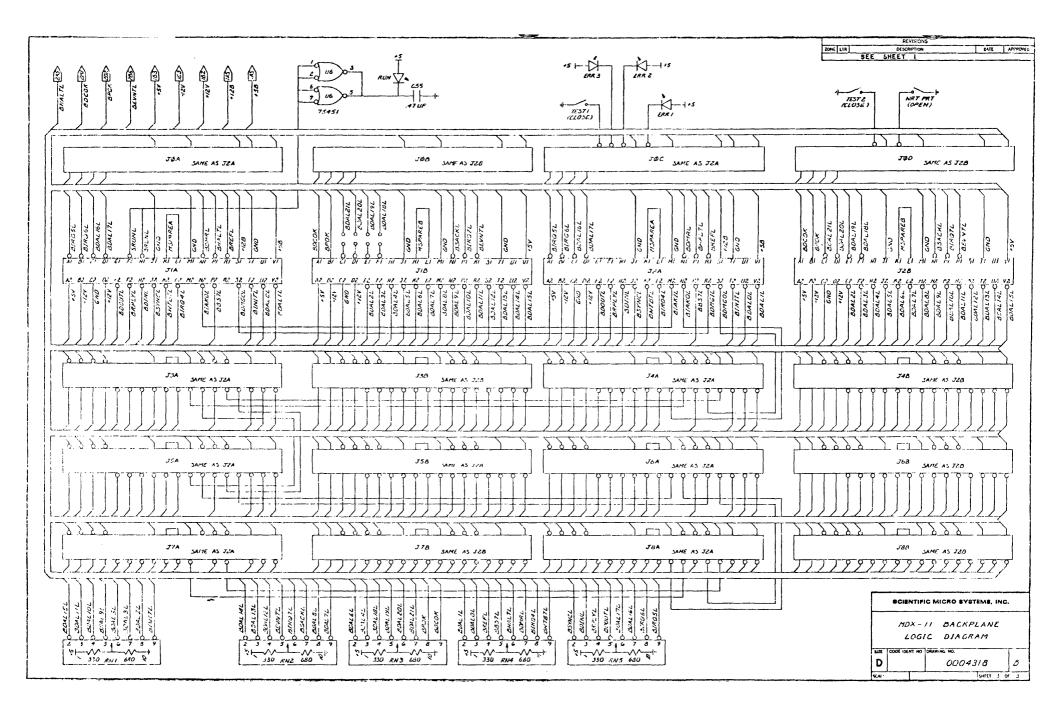

| Figure | 7.  | MDX System Backplane Logic Diagram    | .28 |

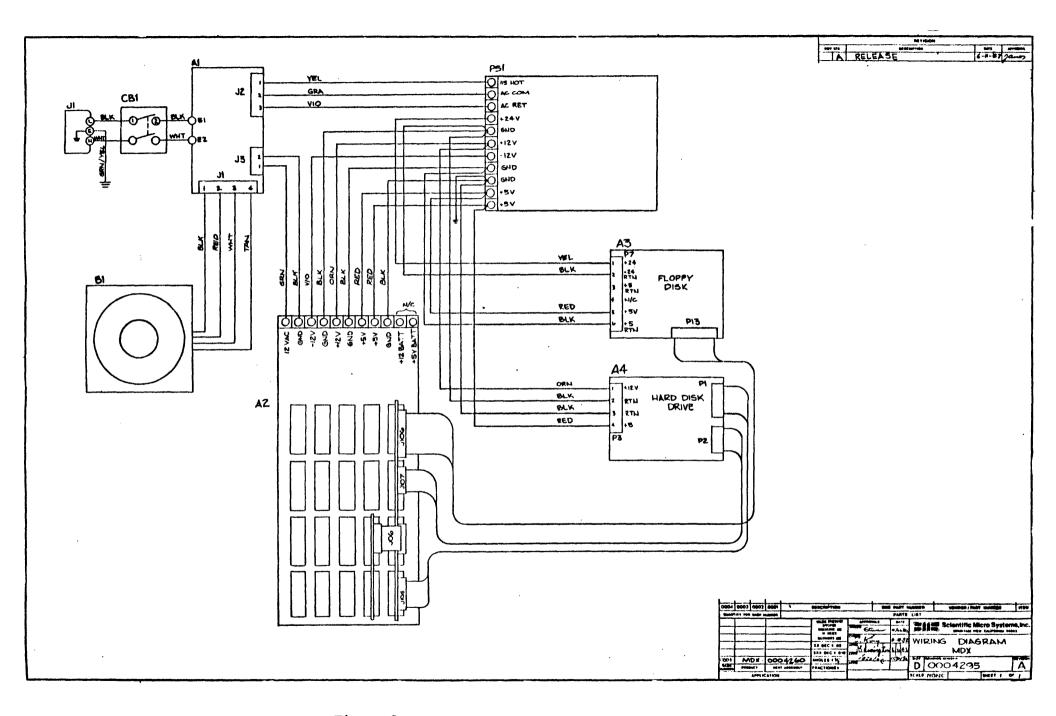

| Figure | 8.  | MDX System Wiring Diagram             | .31 |

| Figure | 9.  | Flaw Map Pointer Sector Format        | .94 |

| Figure | 10. | Processed Flaw Map Data Sector Format | .95 |

| Figure | 11. | Flaw Map Pointer Sector Example       | .96 |

| Figure | 12. | Processed Flaw Map Data Example       | .97 |

# Tables

| Table | 1.  | FW Formatter Straps                     | 23   |

|-------|-----|-----------------------------------------|------|

|       |     | LSI-11 FW Interface Straps              |      |

|       |     | Backplane Straps                        |      |

|       |     | Winchester Drive Options                |      |

|       |     | Floppy Drive Options                    |      |

| Table | 6.  | Bootstrap Halt/Hang Locations           | 35   |

|       |     | Winchester Format Selection             |      |

| Table | 8.  | Winchester Formatted Capacities         | 42   |

| Table | 9.  | LED Meaning During Self Test            | 89   |

| Table | 10. | LED Meaning During System Test          | 89   |

| Table | 11. | MDX System Major Replaceable Assemblies | .101 |

## I. INTRODUCTION

# A. PRODUCT LINE OVERVIEW

The MDX system provides power and an enclosure for a light weight, tabletop LSI-11 computer system. It includes an SMS floppy/Winchester disk controller, a choice of 5-1/4" Winchester drives plus a slim-line floppy. The disk controller is fully compatible with the SMS FW line of controllers which provide RXO2 emulation for the floppy plus full Winchester support.

The following MDX System models are available:

| Model Number | Winchester Capacity (formatted) |  |  |

|--------------|---------------------------------|--|--|

| MDX01171     | 5.3 MByte Winchester            |  |  |

| MDX01172     | 10.6 MByte Winchester           |  |  |

| MDX01173     | 15.9 MByte Winchester           |  |  |

Input line voltage is switch selectable to either 115VAC or 230VAC.

The MDX system is also available with the following system options:

| Option    | Configuration                                                              |

|-----------|----------------------------------------------------------------------------|

| CPU2/64   | LSI-11/2<br>MSV11-DD (64KB memory)<br>*DLV11-J (4 port serial line unit)   |

| CPU23/128 | LSI-11/23<br>MSV11-LF (128KB memory)<br>DLV11-J (4 port serial line unit)  |

| CPU23/256 | LSI-11/23<br>MSV11-LK (256KB memory)<br>*DLV11-J (4 port serial line unit) |

| MEM128    | MSV11-LF (additional 128KB memory)                                         |

| МЕМ256    | MSV11-LK (additional 256KB memory)                                         |

| SLU4      | *DLV11-J (additional serial line unit                                      |

\*includes cabling to D-type connectors on rear panel of the MDX chassis.

•

- **B.** FEATURES

- RX02 interface and command compatible with optional performance improvements

- Complete, high performance DMA controller for 5-1/4" Winchester and slim-line 8" floppy

- Four Quad height (8 dual height) backplane

- Dual height LSI-11 interface board for disk controller

- RX01, RX02, RX03, IBM 3740, IBM 2/2D floppy format compatibility plus additional formats

- Program selectable formats for floppy disks (128, 256, 512, 1024 bytes/sector), and for fixed disks (256, 512 bytes/sector)

- Patented data recovery circuit which requires no adjustments for maximum reliability

- Complete error retry

- Error correction

- Switch selectable input voltage (115VAC or 230VAC)

- Comprehensive self-diagnostics and test commands

- Flaw management for fixed disks

- Supports both physical and logical disk addresses

- Full 22-bit Q bus addressing

- Selectable device register and interrupt vector address

- Bootstrap from both floppy and fixed disk

- Complete RT-11 and RSX-11M Software Support for the extended function and performance mode

- Comprehensive standalone software utility package for disk formatting, backup, copying and system testing.

- Programmable sector interleave and track and head switch offsets on both the floppy and fixed disk drives for maximum performance

- Block reads/writes across cylinder boundaries up to 64K words

- Optimized DMA transfers for minimum bus loading

- Direct transfers to/from memory through 64 word First In, First Out buffer

3000830/A

C. FUNCTIONAL SPECIFICATIONS

| Floppy drives supported: | Slim line 8" drives: Shugart SA810/SA860,<br>Tandon TM848-1/TM848-2                                                                                                                                                                                                                                                                          |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Diskette formats:        | IBM Diskette 1, 2/2D. DEC RX01, RX02 double density<br>plus program selected bytes/sector of 128, 256, 512 or<br>1024 on both single and double density.                                                                                                                                                                                     |

| Fixed drives supported:  | Seagate ST400 series and compatible                                                                                                                                                                                                                                                                                                          |

|                          | Note: The CMI CM5000 series drives are fully com-<br>patible with the ST400 series.                                                                                                                                                                                                                                                          |

| Fixed drive format:      | MFM encoding with selectable formats of 256 or 512<br>bytes/sector                                                                                                                                                                                                                                                                           |

| Number of bus registers: | 2 (4 addresses)                                                                                                                                                                                                                                                                                                                              |

| Register addresses:      | Jumper selectable (1771708, 1771728 is configured at factory)                                                                                                                                                                                                                                                                                |

| Interrupt address:       | Jumper selectable (2648 is configured at factory)                                                                                                                                                                                                                                                                                            |

| Controller Bus Loading:  | All bus connections present 1 DC load and 2.5 AC loads to the bus.                                                                                                                                                                                                                                                                           |

| Bus Termination:         | Backplane mounted resistors terminate Q-bus in 180 ohm<br>characteristic impedance, which allows the bus to be<br>expanded.                                                                                                                                                                                                                  |

| DMA cycle time:          | On a read, if reply is asserted within 150 ns of the assertion of DIN, the DMA cycle will complete in 1.0us. On a write, if reply is asserted within 150ns of the assertion of DOUT, the DMA cycle will complete within 1.15us. On Winchester transfers, multiple word bursts (up to 4 max.) are performed, minimizing arbitration overhead. |

D. PHYSICAL SPECIFICATIONS

Environmental: Relative humidity: 20-80% (required by floppy drives) Operating temperature: 10 to 40 degrees C Wet bulb and dew point temperatures (i.e. humidity temperature combinations) which cause internal or external condensation are not allowed. Storage temperature: -20 to 50 degrees C NOTE: Environmental requirements for floppy disk media may vary. Diskettes should be allowed to reach ambient temperature before formatting, ÷ reading or writing. Electrical: Input: 90-130VAC or 180-260VAC switch selectable (See section II-E for Frequency: 47-63Hz detailed power requirements.) Maximum current: 5.0A at 115VAC 3.6A at 220VAC Mechanical: Size: 9.5" wide, 11.2" high, 17.0" deep (See Figure 1 for de-Weight: 35 pounds tailed mechanical information.)

# E. DISK DRIVE DATA

| Un           | formatted |           |       | Rot.    | Access  | [1]                  | ]              |

|--------------|-----------|-----------|-------|---------|---------|----------------------|----------------|

|              | Capacity  | No.       | No.   | Latency | Time    | Data XFI             | R Rate         |

| Drive        | (MB)      | Cylinders | Heads | (msec.) | (msec.) | Max.                 | Avg.           |

| 5.3MB Win    | 6.38      | 306       | 2     | 8.33    | 85      | 625                  | 492            |

| 10.6MB Win   | 12.76     | 306       | 4     | 8.33    | 85      | 625                  | 492            |

| 15.9MB Win   | 19.14     | 306       | 6     | 8.33    | 85      | 625                  | 492            |

| 1.2MB Floppy | 1.60      | 77        | 2     | 83.30   | 77      | 31.25[3]<br>62.50[4] | 20[2]<br>49[2] |

|              |           |           | Notes |         |         |                      | ,<br>,         |

[1] Data transfer in KBytes/second. AVG. = Average across track.

[2] Assumes no interleave. A 2:1 interleave (e.g. RX02) would cut average transfer rate by two.

[3] Single density.

[4] Double density.

0 0 1.11  $\bigcirc$ ê R h

#### II. SYSTEM INSTALLATION AND OPERATION

This section of the manual describes how to install, configure, and operate the MDX system. It also describes what options are available in the system and how to select these options.

#### A. UNPACKING

Examine all shipping containers for evidence of damage prior to unpacking the equipment. If any damage is found, notify an authorized representative of the shipping concern before unpacking the equipment.

No special unpacking instructions are provided since the shipping containers are of a standard type and easily disassembled. All sub-assemblies are adequately protected from normal shocks incurred during shipping.

Visually inspect each assembly in the shipment for damage. Check each item against the packing list to ascertain that all items have been received.

Insure that all boards in the backplane are firmly seated and that all cables are securely in place.

## B. SITE SELECTION

The site selected for the MDX System must provide ample space around the unit to allow adequate circulation of cool air and easy maintenance accessibility. Under no circumstances should any cables, walls, or mounting hardware be allowed to restrict air flow to the fan on the rear panel. Proper ac voltage must be provided for the unit as described in the specification section. The normal office environment is adequate for satisfactory operation of the unit.

## C. SYSTEM GROUNDING

As shown in the wiring diagram, Figure 8, signal ground is connected to the chassis. The chassis is then connected to the ground wire of the ac input. It is imperative for safety reasons that ground continuity be provided at the customer's installation. This may be accomplished with a three wire installation.

#### D. POWER ON DELAY

The MDX system has a 15 second delay at power on to allow the Winchester drive to reach operational speed.

#### E. SYSTEM CONFIGURATION

The MDX System chassis provides support for up to 8 dual wide or 4 quad wide LSI-11 Q-bus compatible pc boards. However, certain precautions must be taken by the customer as he configures his system. This section covers the configuration capabilities and limitations of MDX System.

### Power Capacity and Features

The power supply in the MDX is rated at 250 watts. To compute power available to the user, the power taken by the system components (Winchester, floppy, backplane and FWD0106 controller) must be subtracted from the 250 watts. Power available to the backplane for computer modules is as follows:

Total user power: 125 watts +5V up to 21 amps +12V up to 2.5 amps -12V up to .9 amps

Thus any combination of voltages can be used up to a total of 125 watts or to the current limit of the voltage (e.g. 21A at 5V). System component power, including the FWD0106 controller (formatter and interface), take 125 watts.

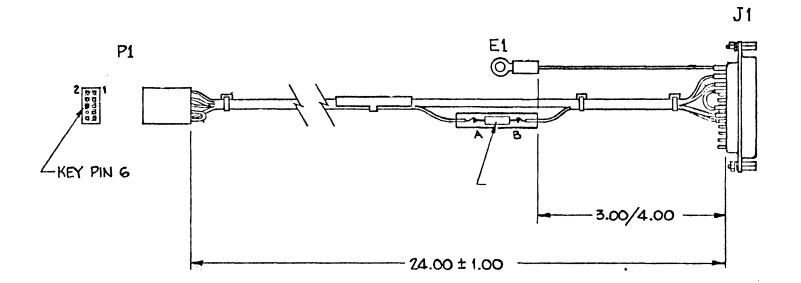

These voltages are available at all backplane slots on the DEC assigned pins. See backplane logic diagram (Figure 7). The customer must insure that his total system power requirements fall within these limits.

The MDX System backplane provides complete power up sequencing and power fail detection as shown in the backplane logic diagram. At power on, BDCOK is activated once the power supplies are within range. BPOK is activated 70 ms (min) after BDCOK. On power failure BPOK is deactivated a minimum of 4 ms before BDCOK is deactivated (i.e. 4 ms before DC power is out of range). This provides time for the system to gracefully shut down in case of power failure. Note also that battery connections are provided for +5V and +12V for those customers who desire battery backup. See Figure 4.

When the RESET switch, located on the front panel, is depressed the BPOK signal is activated on the Q-bus causing a system wide reset. This provides a convenient method of bootstrapping programs without powering down the system.

## System Fuses and Circuit Breakers

The power switch on the rear panel of the MDX system is also a circuit breaker which will trip in the unlikely event of a system AC power overload. In addition the power supply is protected by a 5A, 250V fuse mounted on the power supply itself.

### Cooling Capacity

Cooling is available for any reasonable user system from two quad slots to four quad slots. However, certain precautions must be followed to properly configure the system. The MDX System is shipped from the factory with card guides inserted in all slots and baffles inserted in the last two quad slots. If more than 2 quad slots are required, the baffles must be removed from both ends of the cage. Spare baffles are provided in the last 2 slots on the end of the cage away from the fan. In addition the MDX System must be placed where the fans are not blocked by walls or cables and the ambient temperature should be less than 40 degrees centigrade. If this procedure is followed, a minimum of 150 linear feet per minute of 40 degrees C air will be supplied to each board.

## Board Location

The MDX backplane consists of l quad slot (nearest the slim-line floppy) for the FWD0106 formatter plus four additional Q-Bus quad slots. The LSI-11 CPU must be inserted in the rear dual height slot next to the formatter as shown in Figure 4. The FW interface is installed in the front dual slot next to the formatter. Remaining options (memory, etc.) are installed in the sequence shown in Figure 4. This sequence must be followed to insure the priority chain is not broken. All boards must be installed with components facing the slim-line floppy.

# Bus Loading

The MDX backplane can accommodate modules of up to 35 AC loads (total) and 20 DC loads (total). One AC load equals 9.35pF of capacitance and one DC load equals 105 microamperes.

## Rules for Configuring the MDX Backplane

- Insure that the total available DC power is sufficient for all modules.

- Insure that no more than 20 DC bus loads and 35 AC bus loads are present.

- Insure that all modules are plugged into consecutive slots as shown in Figure 4. The slots follow an 'S' curve down the bus.

- Insure air baffles are inserted in slots which do not have boards installed.

- Insure that jumpers W1, W2, W3, W4 on the backplane are removed for operation with an LSI-11/2. The LSI-11/2 does not support 22-bit addressing and uses these lines for other purposes. An LSI-11/23 will operate correctly with the jumpers installed or removed, but the jumpers must be installed for full 22-bit addressing.

#### F. CABLE PROVISIONS

Cabling to external devices is provided by a variety of connector options on the MDX System rear panel. One group of 8 D-type communication connectors are provided with removable covers. The customer may uncover and use as many of these as required by sliding the plastic cover down. Do not uncover any unused connectors as this will disturb air flow for system cooling. In addition to the D connectors, a strain relieved slot is available for up to 50 conductor flat cable. Since one of the cable panels is removable, a small piece of sheet metal may be designed by the customer for any special cable requirements he may have.

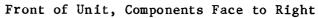

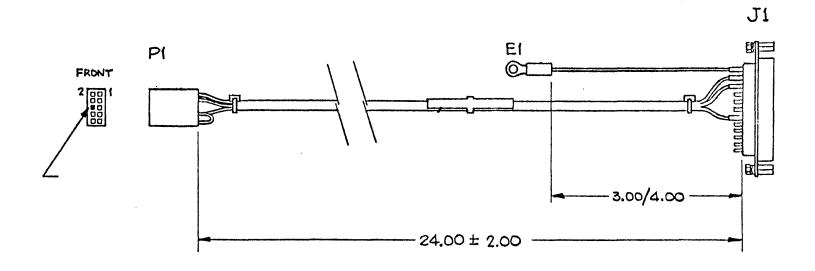

The MDX System is designed such that cables may be routed from the top of the boards to the rear panel without restricting air flow to the system. Please exercise care when routing cables. Do not allow excess cable length to block air flow. SMS provides two types of custom cables for use with the DEC DLV11-J communication board to facilitate customer configuration. The first cable is P/N 0003833 as shown in Figure 5. This cable allows direct connection to most terminals. The second cable is P/N 0003784 as shown in Figure 6. This cable allows connection to most modems. The customer may either order these cables from SMS, build them himself, or use them as models to design other special purpose cables.

## G. BUS TERMINATION

The MDX System backplane has termination resistors which combine with the resistors on the LSI-11 CPU to terminate the lines in its characteristic impedance. This means that the customer does not have to buy special termination boards. It also means that no board (other than the CPU) which has termination resistors should be inserted into the MDX backplane.

Extension of the Q-bus beyond the MDX System backplane is possible. Please refer to the DEC Microcomputer Processor Handbook for backplane expansion rules.

Note: Very early production models of MDX did not have backplane termination resistors. If you plan on extending the backplane, insure the backplane has termination resistors (RN2, RN3, RN4, RN5) installed or contact SMS for assistance.

Figure 4. MDX Backplane Layout

.

WIRE LIST

| SIGNAL         | FROM | ТО   | COLOR |

|----------------|------|------|-------|

| SIGNAL GROUND  | P1-2 | J1-7 | GREEN |

| XMIT DATA      | P1-3 | J1-3 | WHITE |

| RCV DATA -     | P1-7 | P1-9 | BLACK |

| RCV DATA +     | P1-8 | J1-2 | RED   |

| PROTECTIVE GND | J1-1 | E1   | BLACK |

Figure 5. Cable Assembly, DLV11-J to Terminal.

II **-** 19

| WI | RE | LIST |

|----|----|------|

|----|----|------|

| SIGNAL            | FROM  | TO    | NOTES       |

|-------------------|-------|-------|-------------|

| SIGNAL GROUND     | P1-2  | J1-7  | BLACK COND. |

| XMIT DATA         | P1-3  | J1-2  | RED COND.   |

| RCV DATA -        | P1-7  | P1-9  | JUMPER      |

| RCV DATA +        | P1-8  | J1-3  | WHITE COND. |

| +12VDC FUSED      | P1-10 | R1-A  | GREEN COND. |

| DTR               | R1-B  | J1-20 | GREEN COND. |

| RTS/DSR           | J1-4  | 6-1ل  | JUMPER      |

| PROTECTIVE GROUND | J1-1  | E1    | CHASSIS GND |

H. MDX SYSTEM SWITCHES

AC Power

The AC power switch is located on the left, bottom of the rear panel. This switch is also a circuit breaker which will protect the MDX system in the unlikely event of a short circuit.

Input Voltage Selection

The input voltage range is switch selectable to either 90-130VAC or 180-260VAC. This switch is located on the rear panel and is recessed to prevent accidentally changing it.

#### \*\* WARNING \*\*

Before applying power, insure this switch is in the correct position. If 220/240VAC power is applied when the switch is in the 115VAC range, the MDX system will be damaged.

External Switches and LED's

There are two switches and two LED indicators on the front of the MDX system. These are:

- Reset Switch This is a momentary switch which, when raised, causes a system wide reset by activating signal BPOK. This provides a method to bootstrap programs.

- WRT PROT Switch When raised, this switch write protects the entire Winchester drive.

- PWR LED When on, this LED indicates power is applied to the MDX.

- RUN LED When on, this LED indicates the CPU is running.

- Note: When the CPU is halted or executing the WAIT instruction, this LED will be off.

Internal Switches and LED's

There are four toggle switches and three LED's located behind the left lower panel on the MDX. To open this hinged panel, pull on the top of it.

The switches are:

Run/Halt The Run/Halt switch is used to halt the CPU. When the switch is in the RUN position signal BHALTL is not activated and the CPU can run. When the switch is in the HALT position signal BHALTL is activated and the CPU will be halted. 3000830/A

Line Time Clock When this switch is in the on position the signal BEVNTL is activated every 1/60 second (16.66ms). This can generate an interrupt through the vector at address 100g which is often used to keep the time of day.

TEST Switches These two switches select the type of diagnostic to be run as follows:

TST1TST2CCC0Self test is run once at power onOCSelf test is run continuouslyO0Drive test

\* indicates normal operational setting.

See section V for additinal details.

Test LED's There are three LED's which indicate the result of the self test and drive test. See section V, Tables 9 and 10 for details.

I. SYSTEM STRAP OPTIONS

Certain strap options are provided on both the controller interface board, the controller formatter board, and the backplane itself. These options are factory set to provide the most widely used system; however, the information is presented here to allow for special customer requirements and maintenance.

The interface board strap options are listed in Table 2. Notice that all jumpers must be wirewrapped, because of height restrictions, if they are required.

The formatter board options are listed in Table 1. Factory defaults are indicated with a double asterisk.

# TABLE 1. FW FORMATTER STRAPS

| STRAP  |    | ME AN ING VALUE S                                                                                                                                                                        |

|--------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W1     |    | OFF-BOARD LED CONTROL                                                                                                                                                                    |

|        | ** | INSTALLED - ON BOARD LED'S ARE ENABLED<br>REMOVED - ON BOARD LED'S ARE DISABLED; LED'S ARE OFF BOARD<br>(SECTION V-B).                                                                   |

| ₩2     |    | NUMBER OF WORDS TO TRANSFER PER DMA BURST                                                                                                                                                |

|        | ** | REMOVED - 4 WORD EURST<br>INSTALLED - 2 WORD BURST                                                                                                                                       |

|        |    | NOTE: NORMALLY A 4 WORD BURST IS USED FOR LSI-11 AND A 2 WORD BURST<br>IS USED FOR PDP-11. THIS STRAP MUST BE INSTALLED WHEN THE UNIT IS<br>USED IN A VAX COMPUTER.                      |

| W3     |    | W3 IS A HARDWARE DIAGNOSTIC STRAP AND MUST BE REMOVED.                                                                                                                                   |

| W4     |    | FLAW MAP (SEE SECTION VI)                                                                                                                                                                |

|        | ** | REMOVED - NO FLAW IS PRESENT ON WINCHESTER<br>INSTALLED - FLAW IS PRESENT ON WINCHESTER                                                                                                  |

| w5     |    | RESERVED                                                                                                                                                                                 |

| W6     |    | POWER UP AND INITIALIZE MODE                                                                                                                                                             |

|        | ** | REMOVED - COMPATIBLE MODE SET ON POWER UP AND BUS INIT.<br>INSTALLED - MODE IS NOT CHANGED ON POWER UP OR BUS INIT.                                                                      |

|        |    | NOTE: AFTER POWER ON OR BUS INIT, THE MODE CAN BE PROGRAMMATICALLY<br>CHANGED. ONLY THOSE SYSTEMS WHICH ARE FLOPPY ONLY AND DO NO<br>USE THE SMS BOOTSTRAP WILL NEED THIS STRAP REMOVED. |

| w7-w8  |    | WINCHESTER DRIVE 1 TYPE $\frac{7 \ 8}{C \ C}$ SAME DRIVE TYPE AS WIN. DRIVE                                                                                                              |

|        |    | C O RESERVED                                                                                                                                                                             |

|        |    | O C RESERVED                                                                                                                                                                             |

|        |    | O O RESERVED                                                                                                                                                                             |

| w9-w11 | L  | WINCHESTER DRIVE O TYPE 9 10 11                                                                                                                                                          |

|        |    | C C C RESERVED                                                                                                                                                                           |

|        |    | C C O RESERVED<br>C O C ST506, COMPATIBLE                                                                                                                                                |

|        |    | C O C ST506, COMPATIBLE<br>C O O RESERVED                                                                                                                                                |

|        |    | O C C ST406, CM5206, COMPATIBLE                                                                                                                                                          |

|        |    | O C O ST412, CM5412, COMPATIBLE                                                                                                                                                          |

|        |    | O O C ST419, CM5619, COMPATIBLE<br>O O O RESERVED                                                                                                                                        |

|        |    |                                                                                                                                                                                          |

| STRAP           | MEANING                                                                        |                                                                                                         | VALUES                                                                            |

|-----------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| W14             | W14 ENABLES THE WRITE OSCILLA                                                  | TOR AND MUS                                                                                             | T ALWAYS BE INSTALLED.                                                            |

| W15-W16         | PRECOMPENSATION                                                                | 15 16<br>C C<br>C C<br>C C<br>C<br>C C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C<br>C | NOT DEFINED<br>PRECOMPENSATION ENABLED<br>PRECOMPENSATION DISABLED<br>NOT DEFINED |

| W17             | WINCHESTER DRIVE O WRITE PROT                                                  | CECT (WWP)                                                                                              |                                                                                   |

| **              | INSTALLED - NOT WRITE PROTE<br>REMOVED - WRITE PROTECTED                       |                                                                                                         |                                                                                   |

|                 | NOTE: W17 MUST BE REMOVED FO                                                   | OR REMOTE CO                                                                                            | NTROL. SEE SECTION V-B.                                                           |

|                 | . 71                                                                           | ST1,TST2                                                                                                |                                                                                   |

|                 | *SELF TEST<br>*SEE SECTION V-D FOR SELF                                        | $\frac{18 \ 19}{C \ C}$                                                                                 | NO SELF TEST IS RUN                                                               |

| (1311,<br>TST2) |                                                                                |                                                                                                         | SELF TEST RUN ONCE AT POWER<br>ON OR INITIALIZATION                               |

|                 | NOTE: W18 AND W19 MUST BE<br>REMOVED FOR REMOTE CONTROL. *<br>SEE SECTION V-B. |                                                                                                         | SELF TEST RUN CONTINUOUSLY<br>DRIVE TEST                                          |

| W20-W22         | FLOPPY TYPE                                                                    | 20 21 22                                                                                                |                                                                                   |

|                 |                                                                                | CCC                                                                                                     | RESERVED                                                                          |

|                 |                                                                                | C C O                                                                                                   | RESERVED                                                                          |

|                 |                                                                                | C O C<br>C O O                                                                                          | SHUGART SA460<br>MPI 92                                                           |

|                 |                                                                                | 0 C C                                                                                                   |                                                                                   |

|                 |                                                                                | 0 C 0                                                                                                   |                                                                                   |

|                 |                                                                                | 0 0 C<br>0 0 0                                                                                          | TANDON TM100-4                                                                    |

|                 | _                                                                              | 0 0 0                                                                                                   | SHUGART SA860/SA810                                                               |

| W23             | POWER ON DELAY                                                                 |                                                                                                         |                                                                                   |

| **              | REMOVED - 15 SECONDS<br>INSTALLED - 2 MINUTES                                  |                                                                                                         |                                                                                   |

| W24-W29         | WHEN INSTALLED, THE THREE I                                                    | DIAGNOSTIC                                                                                              | LED SIGNALS AND THREE OPTIO                                                       |

# TABLE 1. FW FORMATTER STRAPS (CONTINUED)

W24-W29 WHEN INSTALLED, THE THREE DIAGNOSTIC LED SIGNALS AND THREE OPTION STRAP SIGNALS ARE GATED ONTO SIX Q-BUS SPARE LINES. SEE SECTION V-B. THESE STRAPS ARE INSTALLED WITH SHUNTS ON THE PWB. THE USER NEED NOT REMOVE THESE STRAPS UNLESS HE'S INSTALLING THE FORMATTER IN A Q-BUS BACKPLANE THAT BUSES AND USES SSPARE 2,3,6,8 OR MSPAREA, B. NO SMS OR DEC BACKPLANES BUS THESE SIGNALS.

w30-w31 ARE HARDWARE DIAGNOSTIC STRAPS AND MUST BE REMOVED.

NOTE: ALL FWD0106 STRAPS EXCEPT W17 ARE READ AT POWER ON/INIT TIME. CHANGES IN STRAPPING MUST BE FOLLOWED BY A CONTROLLER INIT. W17 IS READ EACH TIME A WRITE ACCESS TO WO IS PERFORMED.

TABLE 2. LSI-11 FW INTERFACE STRAPS

| STRAP NUMBER | MEANING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| W1           | *BOOT PROM'S DISABLE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| *            | <pre>** REMOVED - BOOT PROM'S ARE ENABLED<br/>INSTALLED - BOOT PROM'S ARE DISABLED, (CONTROLLER<br/>WILL NOT RESPOND TO BOOT PROM ADDRESS)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| W2, W3       | *PARITY CONTROL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ×            | W2 INSTALLED - PARITY ENABLED<br>** W3 INSTALLED - PARITY DISABLED                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| W4 - W9      | INTERRUPT PRIORITY<br>** BR4 R R R R I I<br>BR5 I R I R R R<br>BR6 I I R I R R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | NOTE: THE LSI-11 I/F BOARD CANNOT BE CONFIGURED AS A<br>BR7 DEVICE, HOWEVER IT DOES RECOGNIZE OTHER BR7<br>DEVICES AS SUCH, AND CORRECTLY ARBITRATES INTER-<br>RUPTS WHEN BR7 DEVICES ARE PRESENT.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| S1 (U42)     | INTERRUPT VECTOR SELECTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ×            | REMOVED – 270 <sub>8</sub><br>** INSTALLED – 264 <sub>8</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| S2-S4 (U42)  | BOOT PROM'S STARTING ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ×            | S2 S3 S4       S2 S3 S4         I I I I 160006       R I I 1640008         I I R 171000       R I R 175000         I R I 162000       R R I 166000         ** I R R 173000 (DEFAULT)       R R R 177000                                                                                                                                                                                                                                                                                                                                                                                                                |

| S5-S8 (U42)  | CONTROLLER COMMAND AND STATUS REGISTER ADDRESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | S5       S6       S7       S8         I       I       I       I       1770408       R       I       I       1772408         I       I       I       R       177060       R       I       I       1772408         I       I       R       177060       R       I       R       177260         I       I       R       I       177050       R       I       R       177250         I       I       R       I       177140       R       R       I       177340         I       R       I       177160       R       R       I       177360         I       R       I       177170 (DEFAULT)       R       R       177370 |

| U65          | FOR STRICT COMPATIBILITY WITH 18-BIT BACKPLANES THE COMPONENT (8T38) AT LOCATION U65 (SOCKETED) MAY BE REMOVED. THIS WILL PREVENT THE INTERFACE BOARD FROM ACCESSING THE FOUR EXTRA ADDRESS LINES (BDAL18-BDAL21).                                                                                                                                                                                                                                                                                                                                                                                                     |

\* Wirewrap must be used here or height restrictions will be violated. \*\* Factory Option

### TABLE 3. BACKPLANE STRAPS

STRAP NUMBER MEANING

w1,w2,w3,w4 EXTENDED ADDRESS LINES (BDAL18L, BDAL19L, BDAL20L, BDAL21L)

THESE STRAPS BUS THE EXTENDED ADDRESS LINES FROM THE CPU TO THE REST OF THE BACKPLANE. SINCE THE LSI-11/23 AND LATER CPU'S SOURCE THESE SIGNALS, THE W1 TO W4 STRAPS MUST BE INSTALLED WHEN THESE CPU'S ARE USED WITH MORE THAN 256KB OF MEMORY. HOWEVER THE LSI-11/2 MAKES SPECIAL USE OF THESE LINES AND DOES NOT USE THEM AS ADDRESS LINES. THUS, THE W1 TO W4 STRAPS MUST BE REMOVED WHEN AN LSI-11/2 IS INSTALLED IN THE SYSTEM. SMS SHIPS THE MDX SYSTEM WITH THESE STRAPS INSTALLED.

### TABLE 4. WINCHESTER DRIVE OPTIONS

Terminate last drive on cable and install jumpers as shown:

#### SEAGATE ST506

| DRIVE   | JUMPERS            |                           |                     |

|---------|--------------------|---------------------------|---------------------|

| DRIVE O | Remove shunts 16-1 | , 13-4, 12-5, 11-6, 10-7. | Install 15-2, 9-8.  |

| DRIVE 1 | Remove shunts 16-1 | , 13-4, 12-5, 11-6, 9-8.  | Install 15-2, 10-7. |

The Half Step option is selected.

#### SEAGATE ST400 SERIES

| DULIAN  | JUMPERS                               |                           |

|---------|---------------------------------------|---------------------------|

| DRIVE O | Remove shunts 16-1, 12-5, 11-6, 10-7. | Install 15-2, 13-4, 9-8.  |

| DRIVE 1 | Remove shunts 16-1, 12-5, 11-6, 9-8.  | Install 15-2, 13-4, 10-7. |

#### CMI CM5000 SERIES

DRIVE 0 JUMPERS DRIVE 0 Install shunt 1-2. DRIVE 1 Install shunt 3-4.

TIDADEDC

DDTVE

Note: Except for strapping differences, the CM5000 series drives are fully compatible with the ST400 series.

# TABLE 5. FLOPPY DRIVE OPTIONS AND SPECIFICATIONS

Terminate the last drive on the cable and option the drives as shown below:

## TANDON TM848-1/TM848-2

The default strapping as shipped by Tandon must be modified as follows:

DRIVEJUMPERSDRIVE 0Remove B, M1, M2, M3Install A,X,C,I,R,HL,Z,M4,DS1DRIVE 1Remove B, M1, M2, M3Install A,X,C,I,R,HL,Z,M4,DS2

The motor on and stepper power circuits are controlled by Head Load (HL).

## SHUGART SA860/SA810

| DRIVE   | JUMPERS   |                                    |         |                         |

|---------|-----------|------------------------------------|---------|-------------------------|

| DRIVE O | Remove D  | ,DC,I,MS,PD,S,SE,S1,S3,TS          | Install | MD,MO,R,SI,S2,TR,2S,DS1 |

| DRIVE 1 | Remove D, | , DC, I, MS, PD, S, SE, S1, S3, TS | Install | MD,MO,R,SI,S2,TR,2S,DS2 |

| REF. DE SIG. L<br>UI<br>UZ<br>U3<br>U4<br>U5<br>U6 | POIVER DISI<br>SESERIPTIAN<br>LM2901<br>LM2901<br>LM2901<br>LM2901<br>LM2901<br>LM224<br>75451 | 5<br>5<br>5<br>5<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7<br>7 | 10N<br>-12V<br>12<br>12<br>12<br>12 | ·5v<br>16<br>8 | 6ND<br>12<br>7,8,9 |                                                                                                                     |                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |       |                                                                                                          | AS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | PROTOTYPE I.<br>REF. DESIG.<br>RELEASE N.<br>NEW PWR FAN  | AND NEW R9,10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1011 0000<br>15 JANES / mari<br>12 JEEB 82 / mari<br>25 JUN 52 510<br>1 00 JUN 52 5100<br>1 00 JUN 52 510<br>1 0 |