FWD5000 Floppy/Fixed Disk Drive Controller OEM Manual

Scientific Micro Systems, Inc.

FWD5000 Floppy/Fixed Disk Drive Controller OEM Manual

-

1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 - 1997 -

## FWD5000 Floppy/Fixed Disk Drive Controller OEM Manual

| Document No:<br>Revision: |               | Applicable Product Numbers:                                        |

|---------------------------|---------------|--------------------------------------------------------------------|

|                           | March 1, 1983 | Assy.: 0004086 Rev. A and up<br>Prog. Assy.: 1001985 Rev. A and up |

$(X_{i}) \in \mathcal{A}_{i}$

. .

## CONTENTS

| I.   | CON      | TROLLER OVERVIEWI - 5            |

|------|----------|----------------------------------|

|      | Α.       | INTRODUCTION AND FEATURES        |

|      | в.       | FWD5000 COMMANDS AND STATUS      |

|      | с.       | FWD5000 DATA TRANSFER $I = 7$    |

|      | D.       | FWD5000 ECC/CRC. I - 7           |

|      | Б.<br>Е. |                                  |

|      | Ŀ.       | FWD5000 DIAGNOSTICSI - 8         |

| II.  | DIS      | K SURFACE MANAGEMENT AND FORMATS |

|      | Α.       | DISK SURFACE LAYOUT              |

|      | в.       | SECTOR INTERLEAVING              |

|      | с.       | CYLINDER OFFSET                  |

|      | D.       | HEAD OFFSETII - 10               |

|      | E.       | FLOPPY DISK FORMAT               |

|      | F.       | FIXED DISK FORMAT                |

|      | G.       | LOGICAL ADDRESSING               |

|      | G.       | LAGICAL ADDRESSING               |

| III. | COM      | MANDS AND STATUS                 |

|      | Α.       | FORMAT COMMAND                   |

|      | в.       | FORMAT TRACK COMMAND             |

|      | Ĉ.       | WRITE COMMAND                    |

|      | D.       | READ COMMAND                     |

|      | Ε.       | READID COMMAND                   |

|      | F.       | SEEK COMMAND                     |

|      | r.<br>G. |                                  |

|      |          | RECALIBRATE COMMAND              |

|      | н.       | TEST READY COMMAND               |

|      | I.       | SENSE COMMAND                    |

|      | J.       | STATUSIII - 32                   |

| IV.  | HOS      | T INTERFACE PROTOCOLIV - 33      |

|      | A.       | COMMAND TRANSFER                 |

|      | в.       | DATA TRANSFER                    |

|      | с.       | STATUS TRANSFER                  |

|      | D.       | INTERFACE INITIALIZATIONIV - 39  |

|      | Ε.       | PROTOCOL FEATURESIV - 39         |

| v.   | SPE      | CIFICATIONSV - 41                |

|      | Α.       | PERFORMANCE SPECIFICATIONS       |

|      | в.       | FWD5000 ENVIRONMENT RATING       |

|      |          | FWD5000 ENVIRONMENT RATING       |

|      | с.       |                                  |

|      | D.       | HOST INTERFACE SPECIFICATIONS    |

|      | Ε.       | DRIVE INTERFACE SPECIFICATIONS   |

| VI.  | SYS      | TEM INSTALLATIONVI - 49          |

# Figures

| Figure | 1. | FWD5000 Command Transfer Timing                            | .31 |

|--------|----|------------------------------------------------------------|-----|

|        |    | FWD5000 Buffered Data Transfer                             |     |

| Figure | 3. | FWD5000 Buffered Data Transfer with Fast Handshake Enabled | .33 |

|        |    | FWD5000 Direct Data Transfer                               |     |

| -      |    | Status Transfer                                            |     |

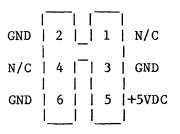

| -      |    | FWD5000 Printed Circuit Board Power Connector              |     |

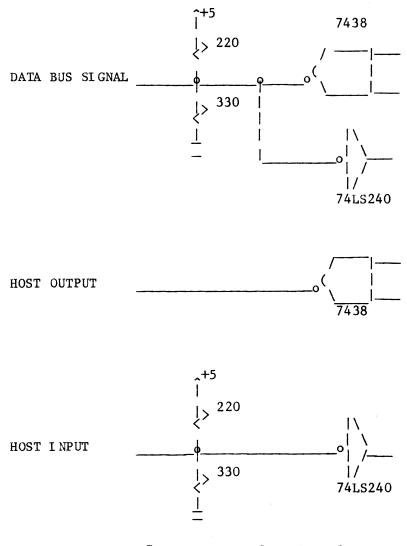

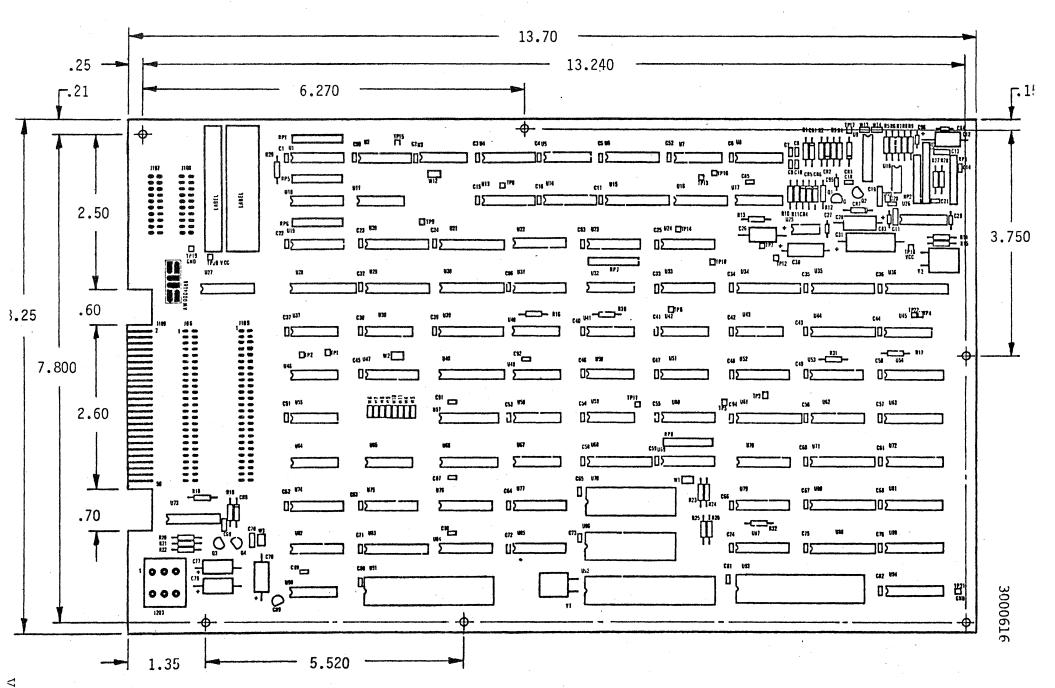

| Ų      |    | Host Interface Examples                                    |     |

|        |    | FWD5000 Printed Circuit Board                              |     |

## Tables

| Table | 1.  | Diagnostic Options                                        |

|-------|-----|-----------------------------------------------------------|

| Table | 2.  | Winchester Formats                                        |

| Table | 3.  | Winchester Capacities                                     |

| Table | 4.  | Maximum Logical Record Number14                           |

| Table | 5.  | FWD5000 READID Bytes                                      |

| Table | 6.  | FWD5000 SENSE Bytes                                       |

| Table | 7.  | FWD5000 Error Codes                                       |

| Table | 8.  | FWD5000 Performance Specifications                        |

| Table | 9.  | FWD5000 Environmental Specifications40                    |

| Table | 10. | Host Interface Connector                                  |

| Table | 11. | Disk Interface Connector (J109) Electrical Parameters     |

| Table | 12. | Disk Data Connector (J107 and J108) Electrical Parameters |

| Table | 13. | FWD5000 PCB Options                                       |

| Table | 14. | Disk Drive Options                                        |

| Table | 15. | Trouble Isolation Checklist                               |

## I. CONTROLLER OVERVIEW

## A. INTRODUCTION AND FEATURES

The FWD5000 controller is a complete preprogrammed controller for both Winchester and floppy disk drives. IBM compatible single and double density floppy formats are supported for 128, 256, 512, and 1K byte sectors and for single and dual sided diskettes. Optional single bit error correction is provided on the floppy by reduction of the standard IBM CRC residue. MFM encoding is used on the Winchester to support 256 and 512 byte sectors. A 24 bit ECC is used to provide correction of all 6-bit or less errors and detection of all 10-bit or less errors. The user may optionally use the ECC for error detection only. Physical sector interleave, head offset, and cylinder offset may be used to format both the Winchester and the floppy for maximum system performance. A full sector buffer (for up to 512 bytes) is provided on the FWD5000. Automatic buffer transfer, as well as direct transfer, is supported for multiple sector transfers across both head and cylinder boundaries. Error correction is performed on buffered transfers with no host interaction required.

The FWD5000 will support up to two 8" floppy disk drives and up to two 8" Winchester drives. The drive type which is to be used is programmed into straps on the pc board so that field changes may be accomplished without rewriting existing handlers. Other strap options include floppy write precompensation disable and various diagnostic and self test options. The FWD5000 is available completely packaged with drives and power in both rack mounting and table top versions as the FWT5000 series.

The host interface is a simple byte parallel port with optional parity. Commands to the controller and status from the controller are passed across this port a byte at a time following a handshake type protocol. This protocol has been designed to minimize the amount of hardware required to interface the FWD5000 to microprocessors and other byte oriented systems by utilizing the latest generation of support circuitry such as DMA controllers and intelligent I/O ports. See SMS application note number 3000672 for details and example circuits.

The host interface is hardware compatible with the Shugart SA1403D controller and supports a subset of the SA1403D command set. The following is an overview of the advantages provided by the FWD5000.

- o Comprehensive self test and drive test diagnostics included on board.

- o Cylinder and head offset at format as well as selectable sector interleave.

- o IBM deleted data address mark support on the floppy for true compatibility.

- o Direct transfers and sector buffered transfers.

- o 128, 256, 512 and 1K byte sectors on floppy in single and double density.

- o Programmable Winchester sector size of 256 or 512 bytes.

- o 6 bit ECC on the Winchester and single bit ECC on the floppy.

## 3000616/F

Additional FWD5000 features include:

- o Direct connection to Shugart 1000/1100, Quantum 2000 Winchester drives and Shugart 800/850/860 or Tandon TM848 floppy drives.

- o Single 8.25" x 13.7" PC controller supports Winchester and floppy disk drives.

o Controls up to 2 floppy drives and 2 Winchester drives.

o Supports single or dual head floppy drives.

o IBM compatible 3740 and 2/2D floppy disk formats.

o Patented data recovery phase lock loop design.

o Easy to use byte oriented TTL interface.

- o Logical or physical addressing of the disk surface.

- o Up to 256 contiguous sector data transfer with single command.

- o Programmable error retry operation.

- o Single +5 volt power supply.

#### B. FWD5000 COMMANDS AND STATUS

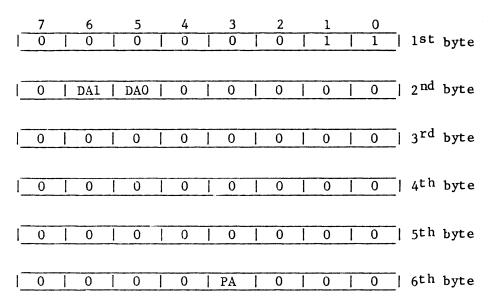

All disk operations performed by the FWD5000 are initiated by the transfer of a command from the host to the controller. Each command consists of six bytes. The content of these command bytes is detailed in section III for all commands. The method of transferring these bytes is detailed in section IV (Host Interface Protocol).

The command set minimizes host overhead by maximizing the function performed per command. A single FORMAT command will format the entire disk with specified head offset, cylinder offset and sector interleave factor. A single READ command will read up to 256 sectors, retry all access errors and perform data error correction before transferring the data to the host. Commands are provided for determining disk format, head location, and extensive operation status. The high level of function provided by the FWD5000 commands means that there will be less host software due to fewer commands per task, no host implemented retry etc., and higher system performance due to fewer interrupts and simple error diagnosis.

At the termination of each command, two bytes of status are provided to the host. The content of these bytes is detailed in section III. The method of transferring these bytes is detailed in section IV. These status bytes allow the host to determine whether the operation completed without error, and to determine complete drive status.

### C. FWD5000 DATA TRANSFER

Both direct and buffered data transfers are supported by the FWD5000. In a direct transfer operation, the host must be able to follow the data transfer rate of the disk. If this can be done, the direct transfer is the fastest transfer method. From 1 to 256 sectors may be transferred in one operation. No error correction is done on direct transfer since the controller cannot access the data. If an ECC error occurs on a direct transfer, the host may recover that sector by performing a buffered transfer.

In a buffered transfer operation there are no constraints on the host data rate. Once the host has completed its fill/empty buffer operation, the controller will perform the next disk access. Note that the fill/empty buffer operation is overlapped with any seek access to improve performance. A sector interleave may be specified at format time such that the next sequential sector is available once the buffer is ready without an entire disk revolution being required. From 1 to 256 sectors may be transferred in a single operation and error correction is automatically performed by the controller before the data is sent to the host on a read.

In both direct and buffered transfers, head switching and seeks are automatically handled by the controller. Head offset and cylinder offset may be chosen at format time such that the next sequential sector is available after the head select delay or the head step delay. The controller assumes that head 0 to N will be read in order before the next sequential cylinder is accessed to maximize performance.

The performance implications of direct transfer and formats with offsets should not be underestimated. For example, a complete backup of 1.2 Mbytes from a Winchester to a floppy diskette can be performed in less than 40 seconds (with a 16 Kbyte buffer). A controller without these features would require over a minute to backup to a 2 to 1 interleaved diskette.

#### D. FWD5000 ECC/CRC

The standard 16 bit IBM CRC is used for error detection on all sector ID fields and floppy disk data fields. The detection capability of this code is excellent when it is used for detection only. SMS recommends that the code be used for detection under normal operation. Occasionally however, a single bit error will develop in a valuable file, such as on a backup floppy diskette. Under these circumstances the FWD5000 may be used to recover the data by enabling ECC on the read.

Winchester disk data integrity is provided by a 24 bit Fire code. This code will detect all bursts of 10 bits or less and will correct all bursts of 6 bits or less. All error correction codes, including the SMS code, have some probability of miscorrection. This occurs when a group of independent errors result in the same error residue as would have occurred with a certain correctable error. To prevent this situation, the FWD5000 saves all error residues from the first read, reads the sector again, and compares the residue before making a correction. This process virtually guarantees user data integrity. The price for this reliability is that two disk revolutions, rather than one, elapse whenever an error is encountered. This results in negligible performance loss and is well worth the price. The error correction function may be disabled by the user if for some reason he desires detection only.

#### 3000616/F

### E. FWD5000 DIAGNOSTICS

W4

W5

Whenever power is applied, or a reset operation performed, W4 and W5 are checked to determine what diagnostic program is to be performed. See Table 1.

## TABLE 1. DIAGNOSTIC OPTIONS

|   | OUT | OUT | Run drive test continuously and halt on error.                      |

|---|-----|-----|---------------------------------------------------------------------|

|   | OUT | IN  | No test to be performed. Start functional program immediately.      |

|   | IN  | OUT | Format ready drives, run drive test continuously and halt on error. |

| * | IN  | IN  | Run self test once and start functional program if no error.        |

\*Factory configuration at shipment.

A single LED is supplied to report the result of the diagnostics as described in the following paragraphs.

Self Test

Self test is an exercise program designed to test the controller hardware as thoroughly as is possible. Pattern testing is done on the RAM, checksum is done on the ROM, and the disk interface hardware is checked. If the self test completes successfully, the on-board LED will be turned off.

## Drive Test

Drive test is an exercise program designed to test the entire drive controller sub-system. The first step of drive test is to run the self test. If the self test fails, the on-board LED will remain on. The next step of the drive test is a random seek and read operation on all ready drives in the system (no data is written). (The controller will wait for up to 30 sec. for W0 to go ready before starting the seek/read test or Winchester format.) If a failure occurs at this step, or if there are no ready drives, the on-board LED will blink on and off at a 100 ms rate and self test will continue to loop. If both parts of the test pass, the LED will be turned off and the test execution begun again. If self test fails at any point after the initial pass, the LED will be turned on. Note that if the format is performed before drive test, both the floppy and the Winchester will be formatted using the SA1403D compatible formats (FM0-FM2=000).

#### II. DISK SURFACE MANAGEMENT AND FORMATS

#### A. DISK SURFACE LAYOUT

The surface of a disk (both floppy and fixed) is divided into a series of concentric circles. Each one of these circles is called a track. As the disk rotates, a track passes under a read/write head which is used to transfer information from/to the disk. Many disk drives support multiple read/write heads, all of which are mounted on a single carriage. The carriage moves or positions the heads over the disk surface. On drives which support multiple heads, all tracks which can be accessed from one position of the carriage are called a cylinder. Thus a cylinder consists of 1 to N tracks where N is the number of read/write heads mounted on the carriage.

Each track is divided into several records called sectors. The sectors are numbered from 1 to X where X is the number of sectors per track. The number of sectors per cylinder is thus X times the number of heads. All sectors on one cylinder are of the same size.

#### B. SECTOR INTERLEAVING

When sector interleaving is used, consecutive sectors on a disk are never read or written. Interleaving typically does not affect disk storage capacity, but does affect system throughput and performance.

Interleaving normally is used to reduce the effective data transfer rate. For example, on a buffered transfer, an interleave may be used so that the next sector to be transferred is available immediately after the buffer has been filled or emptied. Interleaving can be accomplished logically by host software, or physically when the disk is formatted.

When interleaving is used, any physical offset (see next section) and interleave are not additive. The number of sectors skipped is the greater of the offset and interleave factor.

## C. CYLINDER OFFSET

Cylinder offsetting is a technique used to improve system performance on transfers crossing cylinder boundaries. To understand why cylinder offsetting is useful, it is necessary to look at the timing constraints of a disk drive. A disk drive can take from 10 to 20 msec to move a read/write head from one cylinder to the next (see specification section). If a transfer is taking place such that the last sector on track X has just been read and the next sector to be read is the first sector on track X+1, it is desirable to be able to read this sector as soon as the head has been positioned over track X+1. Typically this is not possible because step time is greater than the delay provided by the disk rotation. Thus the controller must wait an entire rotation before the desired sector can be read. This controller allows offsets on both the fixed and floppy disks to improve system performance. See Table 2 for SMS recommended cylinder offsets on the Winchester.

## 3000616/F

#### D. HEAD OFFSET

The head offset is similar in concept to the cylinder offset. A certain amount of time is required for the controller to deselect one head and select another due to controller overhead and drive requirements (see specification section). Head offset is provided such that the next sector to be transferred will be available after this delay has elapsed. See Table 2 for SMS recommended head offsets on the Winchester.

#### E. FLOPPY DISK FORMAT

This controller supports the IBM single/double density formats. These formats are 'soft-sectored' formats. This means that the position of each sector on a track is marked by the controller writing a special pattern, called an address mark (AM), on the diskette. The address mark, along with other identification data (track, head, sector and format), is written only when the diskette is formatted. In normal reads/writes only the data, data address mark and data CRC bytes are written.

It is important to distinguish between what 'formatting' a diskette means versus how the data is arranged on the diskette. Format implies what the encoding type is, what address marks are used and the number of bytes per sector. On the other hand, data can be arranged by the host on the diskette using various interleave and offset factors.

The IBM single density format implies frequency modulation (FM) encoding and single byte address marks. The IBM double density format implies Modified Frequency Modulation (MFM) and four byte address marks.

The IBM formats have one other important feature -- the format of the first track is constant regardless of the format of the remainder of the diskette. The format for cylinder 0, head 0 is IBM single density, 128 bytes/sector. If the diskette is double sided cylinder 0, head 1 can be one of two formats only. These are single density, 128 bytes/sector if the remainder of the diskette is single density or double density, 256 bytes/sector if the remainder of the diskette is double density.

The following table summarizes the aspects of the various formats:

| Density | Encoding | Bytes/<br>Sect.            | Sect./<br>Track    | Gap 4                 | Gap 5                    |

|---------|----------|----------------------------|--------------------|-----------------------|--------------------------|

| IBM SD  | FM       | 128<br>256<br>512          | 26<br>15<br>8      | 33<br>48<br>72        | 274<br>212<br>313<br>667 |

| IBM DD  | MFM      | 1024<br>256<br>512<br>1024 | 4<br>26<br>16<br>8 | 86<br>66<br>61<br>128 | 653<br>352<br>771        |

The arrangement of sectors, ID, etc. on each floppy track is shown below:

I NDEX 1 G XG IID CG DDATA CG IID CG DDATA CG LAST C G IG I |1 |A|2 |A|REC|R|3 |A|FIELD|R|4 |A|REC|R|3 |A|FIELD|R|4 |...|DATA|R| 5 11 | M |M|#1 |C| |M|REC#1|C| |M|#2 |C| |M|REC#2|C| | REC C where G1 to G5 is GAP1 to GAP5 XAM is Index Address Mark (1 byte in single density, 4 in double density) IAM is ID Address Mark (1 byte in single density, 4 in double density) ID REC is ID Record (4 bytes) DAM is Data address mark (1 byte in single density, 4 in double density) CRC is Cyclic Redundancy Check (2 bytes) Gaps 1,2 and 3 are fixed and have the following values: Gap 3 Gap 2 Gap l 32 IBM Single Density 17 46 IBM Double Density 92 62 34 Gaps 4 and 5 vary depending on the diskette format and drive tolerance. The nominal values for these gaps are shown on the previous page. Each ID record consists of 4 bytes in the following format: where format 00 (hex) = 128 bytes/sector CYLI NDE R 01 (hex) = 256 bytes/sector02 (hex) = 512 bytes/sectorHEAD 03 (hex) =1024 bytes/sector SECTOR FORMAT

Note that all floppy diskettes contain 77 cylinders addressed from 0 to 76. The single sided drive has one head addressed 0. The double sided drive has two heads per cylinder addressed 0 and 1. If a single sided diskette is used in a double sided drive, head 1 should not be accessed. On all floppy formats the sectors are addressed from 1 to N where N is the number of sectors per track (per side).

## F. FIXED DISK FORMAT

The SA1000 and Q2000 series are soft sectored Winchesters and the track format is similar to the floppy disk except that there is no index address mark (XAM) or gap 2 (G2). This means that gap 1 immediately precedes the ID address mark for sector 1. It should also be noted that the 2 byte data CRC which is used on the floppy disk is replaced with a 3 byte data ECC capable of detecting all bursts of up to 10 bits and correcting up to a 6 bit burst error. The arrangement of sectors, ID, etc., on each track is shown below:

| <br> _  INDEX                              |  |                                 | · · · · · · · · · · · · · · · · · · · |

|--------------------------------------------|--|---------------------------------|---------------------------------------|

| 1                                          |  |                                 | I                                     |

| I                                          |  |                                 | Ι                                     |

| G  I  ID  C <br> 1  A REC R <br>   M #1  C |  | LAST E <br>  DATA C <br>  REC C | G  G  <br>5  1  <br>                  |

where Gl to G5 is GAP1 to GAP5

IAM is ID Address Mark (3 bytes)

ID REC is ID Record (3 bytes)

DAM is Data address mark (1 byte)

CRC is Cyclic Redundancy Check (2 bytes)

ECC is Error Correction Code (3 bytes)

Gap 1 is fixed at 18 bytes (includes sync bytes which precede AM)

Gap 3 is fixed at 14 bytes (includes sync bytes which precede AM)

Gap 4 and Gap 5 depend on format (see Table 2).

Each ID record consists of 3 bytes in the following format:

| 7 54 3 0            |              |               |                        |

|---------------------|--------------|---------------|------------------------|

| FORMAT   CYL   HEAD | where format | 01 (hex) = 32 | 256 byte sectors/track |

| 765 0               |              | 05 (hex) = 31 | 256 byte sectors/track |

| CYL SECTOR          |              | 02 (hex) = 17 | 512 byte sectors/track |

| 7 0                 |              | 06 (hex) = 16 | 512 byte sectors/track |

| CYLI NDE R          |              |               |                        |

In the following table the capacities of the four different formats are shown. Due to the fact that there is no clock track on the Winchester, rotational velocity variation will result in changes in the gap size after the data has been overwritten. The users choice of format must then reflect the particular line frequency variation in his area of use. SMS feels that any of these formats may be used without sector interleave with U.S. domestic power.

|               | SPEED | TOL.* | GAP 4   | GAP 5 | CYL   | OFF    | HD  | COM | IAND BY | TE 6 |

|---------------|-------|-------|---------|-------|-------|--------|-----|-----|---------|------|

| FORMAT        | W     | W/0   | 1 -00-1 | -4E-1 | 1000  | 2000   | OFF | FM2 | FM1     | FM0  |

| 256 byte - 32 | 1.59% | 2.83% | 34      | 320   | 2 hex | 1C hex | 2   | 0   | 0       | 0    |

| sectors/track |       |       |         |       | 1     |        |     |     |         |      |

| 256 byte - 31 | 3.30% | 3.50% | 44      | 336   | 2 hex | 1C hex | 2   | 1   | 0       | 0    |

| sectors/track |       |       |         |       |       |        |     |     | 1       |      |

| 512 byte - 17 | 2.90% | 3.50% | 57      | 340   | 2 hex | F hex  | 2   | 0   | 1       | 0    |

| sectors/track |       |       |         |       |       |        |     |     |         | I    |

| 512 byte - 16 | 3.50% | 3.50% | 93      | 395   | 2 hex | F hex  | 2   | 1   | 1       | 0    |

| sectors/track |       |       |         |       |       |        |     |     |         |      |

TABLE 2. WINCHESTER FORMATS

\* W implies rotation to rotation with write to read recovery (i.e. used for consecutive sectors)

W/O implies rotation to rotation without write to read recovery (i.e. used for interleaved sectors).

Table 2 shows that if command byte 6 has FM2-FMO of 000, a format with 32 256 byte sectors per track is indicated. This format may be used reliably for consecutive sector transfer as long as the time from index to index does not vary by more than  $\pm 1.59\%$ .

The user should select interleave based upon his system performance requirements and limitations.

The Shugart SA1000 series of drives all contain 256 cylinders addressed from 0 to 255. The SA1002 has two heads per cylinder addressed 0 and 1. The SA1004 has four heads per cylinder addressed 0 to 3. The SA1100 series of drives all contain 660 cylinders addressed from 0 to 659. The SA1104 has three heads per cylinder addressed 0 to 2. The SA1106 has five heads addressed 0 to 4. In all cases, the sectors are addressed from 1 to N where N is the maximum number of sectors per track (per head). The total formatted capacities are shown in Table 3.

The Quantum 2000 series of drives contain 512 cylinders addressed from 0 to 511 except Q2080 which contains 1172 cylinders, addressed from 0 to 1171. The Q2010 has two heads per cylinder addressed 0 and 1. The Q2020 has four heads per cylinder address 0 to 3. The Q2080 has seven heads addressed 0 to 6. The Q2040 has eight heads per cylinder addressed 0 to 7. Formatted capacities are shown in Table 3.

| FORMAT        | SA1002 | SA1004 | SA1104 | SA1106 | Q2010  | Q2020  | Q2080  | Q2040  |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

| 256 byte - 32 | 4.194M | 8.388M | 16.22M | 27.03M | 8.388M | 16.77M | 67.21M | 33.55M |

| sectors/track |        |        | 1      | 1      | 1      |        |        |        |

| 256 byte - 31 | 4.063M | 8.126M | 15.71M | 26.18M | 8.126M | 16.25M | 65.11M | 32.50M |

| sectors/track |        |        |        |        |        |        |        |        |

| 512 byte - 17 |        | 8.912M | 17.23M | 28.72M | 8.912M | 17.82M | 71.41M | 35.65M |

| sectors/track |        |        |        |        |        |        |        |        |

| 512 byte - 16 | 4.194M | 8.388M | 16.22M | 27.03M | 8.388M | 16.77M | 67.21M | 33.55M |

| sectors/track |        |        |        |        |        |        |        |        |

TABLE 3. WINCHESTER CAPACITIES.

## G. LOGICAL ADDRESSING

The FWD5000 allows sectors to be addressed logically as well as physically. Logical records are addressed sequentially with logical record 0 beginning at cylinder 0, head 0, and sector 1. All heads are accessed sequentially up to the maximum number, then the next sequential cylinder is accessed beginning with head zero. The number of logical records available is one less than the number of sectors on the disk (since logical records start at 0). Table 4 lists the maximum logical record number (MLRN) as a function of device type and format. Note: The maximum logical record numbers for the SA860 and the TM848 are the same as listed for the SA850.

Logical addressing is used by the FWD5000 controller whenever the PA bit is set to zero in the sixth command byte. Twenty-one bits are used to form the logical address with byte 2 bit 4 as most significant bit and byte 4 bit 0 as least significant bit. When logical addressing is enabled, the command format is identical to the SA1403D. See command descriptions for details.

## TABLE 4. MAXIMUM LOGICAL RECORD NUMBER

| DE VI CE<br>SA800<br>SA300<br>SA800<br>SA800 | FORMAT<br>SD 128<br>SD 256<br>SD 512<br>SD 1024 | MLRN<br>2001*<br>1165<br>633<br>329 | DE VI CE<br>SA800<br>SA800<br>SA800 | FORMAT<br>DD 256<br>DD 512<br>DD 1024 | MLRN<br>2001<br>1241<br>633 |

|----------------------------------------------|-------------------------------------------------|-------------------------------------|-------------------------------------|---------------------------------------|-----------------------------|

| SA850<br>SA850<br>SA850<br>SA850<br>SA850    | SD 128<br>SD 256<br>SD 512<br>SD 1024           | 4003<br>2331<br>1267<br>659         | SA850<br>SA850<br>SA850             | DD 256<br>DD 512<br>DD 1024           | 4003*<br>2483<br>1267       |

| SA1002                                       | 32 x 256                                        | 16383 <b>*</b>                      | SA1002                              | 17 x 512                              | 8703                        |

| SA1002                                       | 31 x 256                                        | 15871                               | SA1002                              | 16 x 512                              | 8191                        |

| SA1004                                       | 32 x 256                                        | 32767 <b>*</b>                      | SA1004                              | 17 x 512                              | 17407                       |

| SA1004                                       | 31 x 256                                        | 31743                               | SA1004                              | 16 x 512                              | 16383                       |

| Q2010                                        | 32 x 256                                        | 32767                               | Q2010                               | 17 x 512                              | 17407                       |

| Q2010                                        | 31 x 256                                        | 31743                               | Q2010                               | 16 x 512                              | 16383                       |

| Q2020                                        | 32 x 256                                        | 65535                               | Q2020                               | 17 x 512                              | 34815                       |

| Q2020                                        | 31 x 256                                        | 63487                               | Q2020                               | 16 x 512                              | 32767                       |

| Q2080                                        | 32 x 256                                        | 262527                              | Q2080                               | 17 x 512                              | 139467                      |

| Q2080                                        | 31 x 256                                        | 254323                              | Q2080                               | 16 x 512                              | 131263                      |

| Q2040                                        | 32 x 256                                        | 131071                              | Q2040                               | 17 x 512                              | 69631                       |

| Q2040                                        | 31 x 256                                        | 126 <b>9</b> 75                     | Q2040                               | 16 x 512                              | 65535                       |

| SA1104                                       | 32 x 256                                        | 63359                               | SA1104                              | 17 x 512                              | 33659                       |

| SA1104                                       | 31 x 256                                        | 61379                               | SA1104                              | 16 x 512                              | 31679                       |

| SA1106                                       | 32 x 256                                        | 105599                              | SA1106                              | 17 x 512                              | 56099                       |

| SA1106                                       | 31 x 256                                        | 102299                              | SA1106                              | 16 x 512                              | 52799                       |

| <b>*</b> SA1403D                             | compatible                                      | format                              |                                     |                                       |                             |

|                                              |                                                 |                                     |                                     |                                       |                             |

#### III. COMMANDS AND STATUS

Each FWD5000 command consists of six bytes which are sent to the controller according to the protocol described in section IV. Two bytes of status are returned at the completion of each command according to the protocol defined in section IV. The following section describes the content of the command and status bytes and details command operation.

In all cases the floppy and Winchester drive types are determined from W6, W8, W9, W10, and W11 (see Table 13) which must be properly set when power is applied to the board. For all commands, drive addresses 0 and 1 are reserved for Winchester drives, and drive addresses 2 and 3 are reserved for floppy drives.

For all the following command descriptions, bit 0 is shown on the right and is assumed to be the least significant bit. The least significant bit of any field is the rightmost bit or the bit with the smallest bit position number. These bit position numbers are carried through as the data bus numbers on the interface connector. In other words, command bit 0 corresponds to data bus bit 0 on J06 pin 2 and should be wired to the least significant bit of the host port.

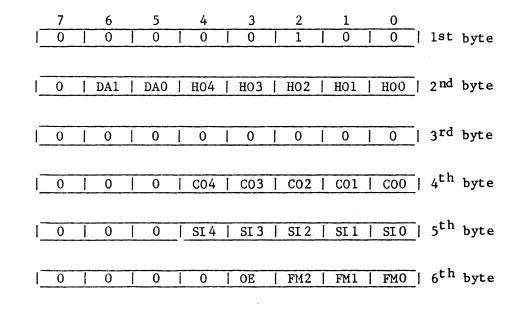

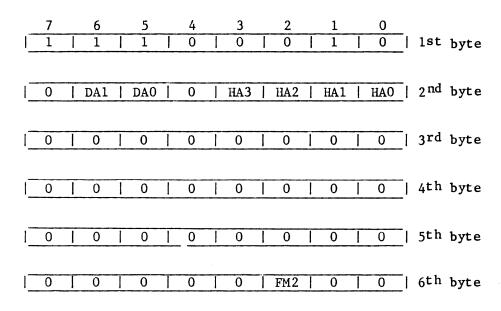

A. FORMAT COMMAND

DAO - DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy)

OE: Offset enable bit. If OE=0 the H0 and C0 fields are ignored (SA1403D compatible).

COO - CO4: Cylinder offset field specifies the number of sectors following the last sector on the last head of the previous cylinder, and preceeding sector 1 on the current cylinder. An offset of zero or one results in no intermediate sectors, an offset of two results in a single intermediate sector, etc. See Table 2 for recommended offsets.

#### 3000616/F

- HOO HO4: Head offset field determines the number of sectors following the last sector on the last head of the previous track, and preceeding sector 1 on the current track. An offset of zero or one results in no intermediate sectors, an offset of two results in a single intermediate sector, etc. The head offset is not used at cylinder boundaries. See Table 2 for recommended offsets.

- SIO SI4: Sector interleave field determines the number of intermediate sectors between sectors with sequential addresses (i.e. sequential data). An interleave of zero or one is defined to be no interleave. An interleave of two has a single sector between sectors which are read consecutively. At a cylinder boundary, the greater of cylinder offset and the interleave will be chosen as the actual offset. At a track boundary the greater of head offset and interleave will be used as the actual offset.

- FMO FM2: Format field determines density, sector size and number of sectors per track as shown (see II-E and F for details):

For Winchester (DA=0 or 1):

| FM2 | FM1 | FM0 |          | FM2 | FM1 | FM0 |          |

|-----|-----|-----|----------|-----|-----|-----|----------|

| 1   | 1   | 1   | illegal  | 0   | 1   | 1   | illegal  |

| 1   | 1   | 0   | 16 x 512 | 0   | 1   | 0   | 17 x 512 |

| 1   | 0   | 1   | illegal  | 0   | 0   | 1   | illegal  |

| 1   | 0   | 0   | 31 x 256 | 0   | 0   | 0   | 32 x 256 |

For floppy (DA=2 or 3):

| FM2 | FM1 | FM0 |    |      | FM2 | FM1 | FM0 |    |      |                      |

|-----|-----|-----|----|------|-----|-----|-----|----|------|----------------------|

| 1   | 1   | 1   | SD | 1024 | 0   | 1   | 1   | DD | 1024 |                      |

| 1   | 1   | 0   | SD | 512  | 0   | 1   | 0   | DD | 512  |                      |

| 1   | 0   | 1   | SD | 256  | 0   | 0   | 1   | DD | 256  |                      |

| 1   | 0   | 0   | SD | 128  | 0   | 0   | 0   | DD | 256  | if 2 sided diskette, |

|     |     |     |    |      |     |     |     |    |      | else SD 128.         |

The FORMAT command causes the controller to initialize an entire disk (or diskette) with address marks, sector ID fields, record gaps, and E5 (hex) bytes in every sector as specified by the selected drive and format.

If a single density diskette is being formatted, track 0 sides 0 and 1 (cylinder 0) will be formatted using 128 byte sectors irrespective of the specified sector size. If a double density diskette is being formatted, track 0 side 0 will be formatted using 128 byte single density sectors and track 0 side 1 will be formatted using 256 byte double density sectors irrespective of the specified sector size. All other sectors will be formatted according to the sector size and density specified in command byte 6. This procedure is required for IBM compatibility.

Status is returned upon completion of the FORMAT command or upon error termination. See section IV for state and timing details on status transfer.

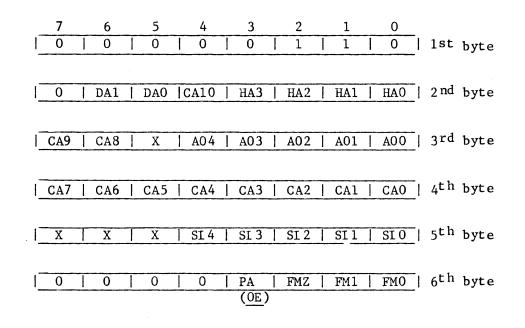

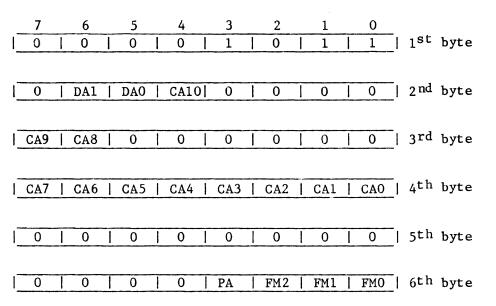

DAO - DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy)

CAO - CA10: Cylinder address field (if PA = 1)

HAO - HA3: Head address field (if PA = 1)

- A00 A04: Absolute offsetfield (if PA = 1). Determines the offset from index to the first sector on the selected track. A0=1, first sector will start at index.

- PA (OE): The physical addressing (offset enable) bit, If PA=1, allows physical addressing with the absolute offset (AOO-AO4) enabled. If PA=0, logical addressing with no offsetting is used (SA1403D compatible). The 21 bit logical address is determined with byte 2 bit 4 the MS bit and byte 4 bit 0 the LS bit. The FWD5000 converts the logical address to physical and uses only the head and cylinder address, the sector is unused in format track.

- SIO SI4: Sector interleave field determines the number of intermediate sectors between sectors with sequential addresses (i.e. sequential data). An interleave of zero or one is defined to be no interleave. An interleave of two has a single sector between sectors which are read consecutively.

- FMO FM2: Format field determines density, sector size and number of sectors per track as shown (see II-E and F for details):

For Winchester (DA=0 or 1):

FM2 FM1 FM0

| 1          | 1   | 1            | <b>il</b> 10 | egal  | 0           | 1   | 1   | <b>i</b> 1 | legal |     |    |        |      |       |

|------------|-----|--------------|--------------|-------|-------------|-----|-----|------------|-------|-----|----|--------|------|-------|

| 1          | 1   | 0            | 16 :         | x 512 | 0           | 1   | 0   | 17         | x 512 | 2   |    |        |      |       |

| 1          | 0   | 1            | <b>i</b> 110 | egal  | 0           | 0   | 1   | <b>i</b> 1 | legal |     |    |        |      |       |

| 1          | 0   | 0            |              | x 256 | 0           | 0   | 0   |            | x 256 | 5   |    |        |      |       |

| For<br>FM2 | _   | ру (1<br>FM( |              | or 3) | FM2         | FM1 | FM0 |            |       |     |    |        |      |       |

| <u>rmz</u> | rm1 |              |              |       | <u>rriz</u> |     | FHU |            |       |     |    |        |      |       |

| 1          | 1   | 1            | SD           | 1024  | 0           | 1   | 1   | DD         | 1024  |     |    |        |      |       |

| 1          | 1   | 0            | SD           | 512   | 0           | 1   | 0   | DD         | 512   |     |    |        |      |       |

| 1          | 0   | 1            | SD           | 256   | 0           | 0   | 1   | DD         | 256   |     |    |        |      |       |

| 1          | 0   | 0            | SD           | 128   | 0           | 0   | 0   | DD         | 256   | if  | 2  | sided  | disk | ette, |

|            |     |              |              |       |             |     |     |            |       | els | se | SD 128 | 3.   |       |

FM2 FM1 FM0

The format track command causes the controller to initialize a single track on a Winchester disk (or floppy diskette) with address marks, sector ID fields, Record gaps, and E5 (NEX) bytes in every sector.

If a single density diskette is being formatted, track 0 sides 0 and 1 (cylinder 0) will be formatted using 128 byte sectors irrespective of the specified sector size. If a double density diskette is being formatted, track 0 side 0 will be formatted using 128 byte single density sectors and track 0 side 1 will be formatted using 256 byte double density sectors irrespective of the specified sector size. All other sectors will be formatted according to the sector size and density specified in command byte 6. This procedure is required for IBM compatibility.

Status is returned upon completion of the FORMAT TRACK command or upon error termination. See section IV for state and timing details on status transfer.

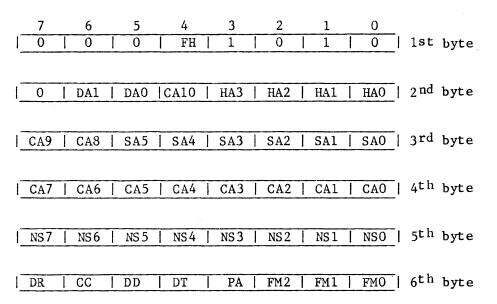

#### C. WRITE COMMAND

DAO - DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy)

- FH: Fast handshake bit. When FH=1, the fast handshake is used on buffered transfers to allow the user more time to perform the memory access (thereby reducing interleave). See section IV-B DATA TRANSFER for timing details.

- DT: Direct transfer bit. When DT=1 the transfer is direct from host to disk. When DT=0 the transfer is through the buffer.

- DD: Deleted data bit. When DD=1 each sector is written with IBM compatible deleted data address marks. DD is not used on the Winchester.

- CC: Correction control for buffered transfers; does not affect write operation.

- DR: Disable retry bit. When DR=1 no retries are performed.

- FMO FM2: Format field. For Winchester (DA=0 or 1):

| FM2            | FM1 | FM0 |          | FM2 | FM1 | FM0 |          |

|----------------|-----|-----|----------|-----|-----|-----|----------|

| $\overline{1}$ | 1   | 1   | illegal  | 0   | 1   | 1   | illegal  |

| 1              | 1   | 0   | 16 x 512 | 0   | 1   | 0   | 17 x 512 |

| 1              | 0   | 1   | illegal  | 0   | 0   | 1   | illegal  |

| 1              | 0   | 0   | 31 x 256 | 0   | 0   | 0   | 32 x 256 |

For floppy (DA=2 or 3):

| FM 2           | FM1 | FM0 |    |      | FM2 | FM1 | FM0 |    |      |                      |

|----------------|-----|-----|----|------|-----|-----|-----|----|------|----------------------|

| $\overline{1}$ | 1   | 1   | SD | 1024 | 0   | 1   | 1   | DD | 1024 |                      |

| 1              | 1   | 0   | SD | 512  | 0   | 1   | 0   | DD | 512  |                      |

| 1              | 0   | 1   | SD | 256  | 0   | 0   | 1   | DD | 256  |                      |

| 1              | 0   | 0   | SD | 128  | 0   | 0   | 0   | DD | 256  | if 2 sided diskette, |

|                |     |     |    |      |     |     |     |    |      | else SD 128.         |

- PA: Physical address bit. If PA=1 then physical addressing is used (as shown in command bytes and described below). If PA=0, a 21-bit logical sector address is determined with byte 2 bit 4 the MS bit and byte 4 bit 0 the LS bit.

- CAO -CA10: Cylinder address of starting sector (if PA=1).

- HAO HA3: Head address of starting sector (if PA=1).

- SAO SA5: Sector address field of starting sector (if PA=1).

- NSO NS7: Number of sectors to be written on this operation. When this field is zero, 256 sectors will be transferred.

The WRITE command initiates a write of one or more sectors on the disk. The controller will seek the heads to the specified cylinder and verify position automatically.

If the transfer is direct, the controller will wait for the target sector and then handshake the data from the host at disk rate until all sectors have been transferred. Note that interruptions in the data stream timing will occur during gaps and access operations. See section IV for handshake and timing details. The data address mark and ECC/CRC bytes are automatically written by the controller. Note that if a data overrun error occurs during a direct transfer (see section IV), the handshake will stop and the controller will complete the sector with random data and correct CRC/ECC.

If the transfer is buffered, the controller will handshake the data from the host at host rate until the first sector is in the buffer. Any required seek will be done while the buffer is being filled. The buffer will then be written to the target sector and the buffer fill operation begun again until all sectors have been transferred. See section IV for handshake and timing details. The data address mark and ECC/CRC bytes are automatically written by the controller.

If for any reason a sector cannot be located, the WRITE command will be terminated and status returned with the error bit set. The SENSE command is used to determine the cause of failure. If retries are enabled, any error which could be caused by incorrect head positioning (i.e. positioning error, no AM's error, sector ID error) is retried up to two times with a head recalibrate on each retry before status is returned. The retry bit in the second status byte will be set if retries were performed even if the operation was successful. See section IV for details on command termination and see status description at end of this section for status details. Status is returned at the end of the command operation if no errors occur during transfer.

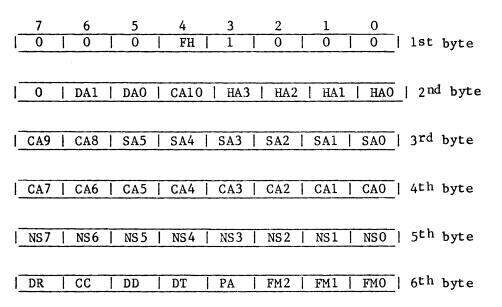

#### D. READ COMMAND

DAO - DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy)

- FH: Fast handshake bit. When FH=1, the fast handshake is used on buffered transfers to allow the user more time to perform the memory access (thereby reducing interleave). See section IV-B for timing details.

- DT: Direct transfer bit. When DT=1 the transfer is direct from host to disk. When DT=0 the transfer is through the buffer.

- DD: Deleted data bit. Unused for read operations.

- CC: Correction control bit. Error correction disable for buffered Winchester transfers. Error correction enable for buffered floppy transfers. For example if CC=0, error correction is performed on Winchester reads but not on floppy reads.

- DR: Disable retry bit. When DR=1 no retries are performed.

- FMO FM2: Format field. For Winchester (DA=0 or 1):

| FM2 | FM1 | FM0 |          | FM2 | FM1 | FM0 |          |

|-----|-----|-----|----------|-----|-----|-----|----------|

| 1   | 1   | 1   | illegal  | 0   | 1   | 1   | illegal  |

| 1   | 1   | 0   | 16 x 512 | 0   | 1   | 0   | 17 x 512 |

| 1   | 0   | 1   | illegal  | 0   | 0   | 1   | illegal  |

| 1   | 0   | 0   | 31 x 256 | 0   | 0   | 0   | 32 x 256 |

For floppy (DA=2 or 3):

| FM 2 | FM1 | FM0 |    |      | FM2 | FM1 | FM0 |    |      |                      |

|------|-----|-----|----|------|-----|-----|-----|----|------|----------------------|

| 1    | 1   | 1   | SD | 1024 | 0   | 1   | 1   | DD | 1024 |                      |

| 1    | 1   | 0   | SD | 51 2 | 0   | 1   | 0   | DD | 512  |                      |

| 1    | 0   | 1   | SD | 256  | 0   | 0   | 1   | DD | 256  |                      |

| 1    | 0   | 0   | SD | 128  | 0   | 0   | 0   | DD | 256  | if 2 sided diskette, |

|      |     |     |    |      |     |     |     |    |      | else SD 128.         |

- PA: Physical address bit. If PA=0, a 21-bit logical sector address is determined with byte 2 bit 4 the MS bit and byte 4 bit 0 the LS bit. If PA=1, the address is physical as described below.

- CAO -CA10: Cylinder address of starting sector (if PA=1).

- HAO HA3: Head address of starting sector (if PA=1).

- SAO SA5: Sector address field of starting sector (if PA=1).

- NSO NS7: Number of sectors to be read on this operation. When this field is zero, 256 sectors will be transferred.

The READ command initiates a read of one or more sectors on the disk. Controller will seek the heads to the specified cylinder and verify position automatically.

If the transfer is direct, the controller will wait for the target sector and then handshake the data to the host at disk rate until all sectors have been transferred. Note that interruptions in the data stream will occur during gaps and access operations. See section IV for handshake and timing details.

If the transfer is buffered, the controller will wait for the target sector and transfer the sector into the buffer. The host must then empty the buffer at host rate. See section IV for handshake and timing details. Any required seek will be performed while the buffer is being emptied. Once the host has emptied the buffer the controller will read the next sector into the buffer. This process continues until all sectors have been transferred. If a correctable ECC error occurs, and error correction has been enabled, the controller will correct the data in the buffer before transfer to the host.

If retries are enabled, any error which could be caused by incorrect head positioning (i.e. positioning error, no AM's error, sector ID error) is retried up to two times with a head recalibrate on each retry before status is returned. A no data AM error or a data ECC/CRC error is fatal on direct transfer and will not be automatically retried even if retries are enabled. A non-correctable ECC error, data CRC error, or no data AM error will be retried up to eight times (with no recalibrate) on buffered transfers.

If the read command operation completes successfully, status will be returned at completion with no errors. The second status byte will contain information on successful retries and error correction. If a fatal error occurs, status will be returned with the error bit set. The SENSE command is used to determine error type. If a deleted data address mark is encountered at any time during a floppy read, the command will be terminated and status returned with the error bit set. The deleted data sector is transferred to the host before termination. The deleted data error code is set in the sense bytes (see SENSE command section III-H).

## E. READID COMMAND

DAO - DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy)

HAO - HA3: Head address for read operation

FM2: Single density bit; if set to 0 the read will first be attempted in double density; if set to 1 the read will first be attempted in single density; used for floppy only

The READID command initiates a sector ID search on the current cylinder. The specified head is selected but no seek is performed. If the floppy is addressed, both densities will be attempted before the operation is terminated. The first attempt will be with the density specified in the command.

Six bytes will be transferred to the host according to the normal data transfer protocol. These bytes are described in Table 5. The first four of these bytes are determined from the sector ID field which is read by the READID command. These bytes are valid only if the operation completed without an error as determined by the status bytes. The last two bytes are controller configuration bytes and are valid even though an error occurred on the read access. This allows the host to determine configuration information, such as drive type, even though the drive is not ready.

Normal status is returned at the completion of the READID command. See the status section for details.

|    | 7   |   | 6   |   | 5   |   | 4    |   | 3   |   | 2   |   | . 1 |          | 0   |    |                  |      |

|----|-----|---|-----|---|-----|---|------|---|-----|---|-----|---|-----|----------|-----|----|------------------|------|

| 1  | CA7 | Τ | CA6 | Τ | CA5 | Ι | CA4  | Ι | CA3 | Ι | CA2 | 1 | CA1 | 1        | CA0 | -  | 1st              | byte |

|    |     |   |     |   |     |   |      |   |     |   |     |   |     |          |     |    |                  |      |

| 1  | CA9 | 1 | CA8 | 1 | *   |   | CA10 | ) | HA3 | 1 | HA2 |   | HA1 |          | HA0 |    | 2 nd             | byte |

| -  |     |   |     |   |     |   |      |   |     |   |     |   |     |          |     | -  |                  |      |

| 1_ | *   |   | *   |   | SA5 |   | SA4  |   | SA3 |   | SA2 |   | SA1 |          | SA0 |    | 3rd              | byte |

|    |     |   |     |   |     |   |      |   |     |   | ·   |   |     |          |     | -  | . 1              |      |

| 1_ | *   |   | *   |   | *   |   | *    |   | *   |   | FM2 |   | FM1 | 1        | FMO |    | 4t n             | byte |

|    |     |   |     |   |     |   |      |   |     |   |     |   |     |          |     |    | - <b>*</b> h     |      |

| 1_ | W4  |   | W5  |   | W6  |   | W7   |   | *   |   | *   |   | *   | <u> </u> | *   | _  | 5t n             | byte |

|    |     |   |     |   |     |   |      |   |     |   |     |   |     |          |     |    | . <b>.</b>       |      |

| 1_ | W8  | 1 | W9  | İ | W10 | 1 | W11  | 1 | *   | 1 | *   | 1 | *   | 1        | *   | _1 | 6 <sup>c n</sup> | byte |

TABLE 5. FWD5000 READID BYTES

CAO -CA10: Cylinder address of the sector ID field which was read by the Read ID operation.

HAO - HA3: Head address of the sector ID field.

SAO - SA5: Sector address of the sector ID field.

FMO - FM2: Format of the disk or diskette. For Winchester (DA=0 or 1):

| FM2 | FM1 | FM0 |          | FM2 | FM1 | FM0 |          |

|-----|-----|-----|----------|-----|-----|-----|----------|

| 1   | 1   | 1   | illegal  | 0   | 1   | 1   | illegal  |

| 1   | 1   | 0   | 16 x 512 | 0   | 1   | 0   | 17 x 512 |

| 1   | 0   | 1   | illegal  | 0   | 0   | 1   | illegal  |

| 1   | 0   | 0   | 31 x 256 | 0   | 0   | 0   | 32 x 256 |

For floppy (DA=2 or 3):

| FM2 | FM1 | FM0 |    |      |   | FM2 | FM1 | FM0 |     |       |

|-----|-----|-----|----|------|---|-----|-----|-----|-----|-------|

| 1   | 1   | 1   | SD | 1024 | - | 0   | 1   | 1   | DD  | 1024  |

| 1   | 1   | 0   | SD | 512  |   | 0   | 1   | 0   | DD  | 512   |

| 1   | 0   | 1   | SD | 256  |   | 0   | 0   | 1   | DD  | 256   |

| 1   | 0   | 0   | SD | 128  |   | 0   | 0   | 0   | i1] | legal |

W4 - W11: Configuration straps read from the FWD5000 controller board. See Table 13 for detailed description of strap meaning.

~

F. SEEK COMMAND

DAO - DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy)

PA: Physical address bit. If PA=0, a 21-bit logical sector address is determined with byte 2 bit 4 the MS bit and byte 4 bit 0 the LS bit. If PA=1, the physical cylinder address (CAO-CA9) is the target.

FMO - FM2: Format field determines the format. For Winchester (DA=0 or 1):

| FM2             | FM1             | FM0             |             |                 | FM2          | FM1             | FM0             |             |             |          |  |  |

|-----------------|-----------------|-----------------|-------------|-----------------|--------------|-----------------|-----------------|-------------|-------------|----------|--|--|

| 1               | 1               | 1               | <b>il</b> ] | legal           | 0            | 1               | 1               | <b>i</b> 12 | legal       |          |  |  |

| 1               | 1               | 0               | 16          | x 512           | 0            | 1               | 0               | 17          | x 512       | 2        |  |  |

| 1               | 0               | 1               | <b>i1</b>   | legal           | 0            | 0               | 1               | <b>i</b> 11 | legal       |          |  |  |

| 1               | 0               | 0               | 31          | x 256           | 0            | 0               | 0               | 32          | x 256       | <b>,</b> |  |  |

| For             | floj            | рру             | (DA=        | =2 or 3         | 3):          |                 |                 |             |             |          |  |  |

|                 | flog<br>FM1     |                 | (DA=        | =2 or 3         |              | FM1             | FMO             |             |             |          |  |  |

|                 | _               |                 |             | =2 or 3<br>1024 |              | $\frac{FM1}{1}$ | $\frac{FMO}{1}$ | DD          | 1024        |          |  |  |

|                 | _               | FMO             |             |                 | FM2          | FM1<br>1<br>1   |                 | DD<br>DD    | 1024<br>512 |          |  |  |

| <u>FM2</u><br>1 | $\frac{FM1}{1}$ | $\frac{FMO}{1}$ | SD<br>SD    | 1024            | <u>FM2</u> 0 | 1               | 1               |             |             |          |  |  |

CAO -CA10: Cylinder address field determines the target cylinder (if PA=1).

The SEEK command performs a seek operation on the addressed drive. The destination cylinder is specified in the command bytes. (If PA=0, the heads will be positioned to the cylinder which contains the specified logical sector.) No verification of target cylinder is performed until a subsequent read or write operation.

If the seek operation is successful, status will be returned with no errors. If an error occurs, the error bit will be set in the status bytes.

## 3000616/F

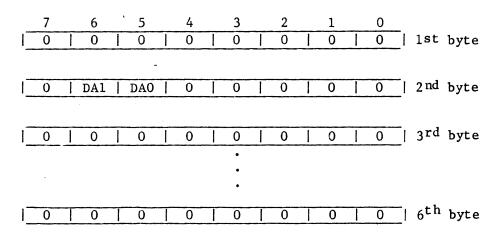

## G. RECALIBRATE COMMAND

The RECAL command positions the heads of the addressed drive at cylinder zero. The normal two bytes of status are returned at command completion.

Note that this command is supported for compatibility with the SA1403D. It is never necessary to perform a RECAL on the FWD5000 since the controller will automatically perform a RECAL before a new operation if a new disk has been installed, a seek error has occurred, or power has been applied.

H. TEST READY COMMAND

The TEST READY command selects the drive which is addressed by the DAO-1 bits and tests for ready. The returned status bytes will indicate an error if the drive is not ready.

The TEST READY command is supported for compatibility. It should never be required since the FWD5000 returns both new disk and drive ready bits in the completion status byte.

III - 26

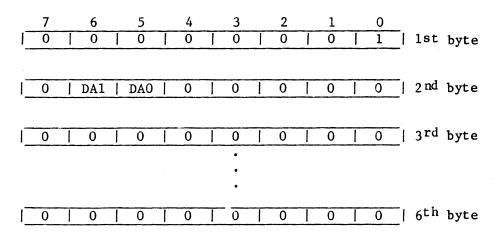

I. SENSE COMMAND

- DAO DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy). This field determines the drive for which status will be returned, however, the sense bytes which are returned DO NOT necessarily apply to this drive address.

- PA: Physical address bit. If PA=0, a 21-bit logical sector address is returned in the sense bytes with byte 2 bit 4 as MS bit and byte 4 bit 0 as LS bit. If PA=1, the returned address will be a physical address as described in Table 6.

The SENSE command initiates the transfer of four bytes to the host according to the normal data transfer protocol. These bytes contain the status of the last operation (except for error code byte not necessarily for the drive addressed in the 2nd byte). The structure of these bytes is shown in Table 6. The SENSE command is used to determine the cause of an error and the problem sector when an error is detected in the returned status. The address which is returned in the bytes (see Table 6) is valid only after an error condition on a read or write command.

Note that normal status is returned at the completion of the SENSE command as it is for all commands. These two status bytes will always contain information on the addressed drive rather than on the last operation. See the status section.

#### TABLE 6. FWD5000 SENSE BYTES

| ۱ <u> </u> | 0   |   |    | )  | 1 | EC5 | 1 | EC4  | 1 | EC3 | 1 | EC2 |   | EC1 | 1 | EC0 | 1 | lst  | sense | byte |

|------------|-----|---|----|----|---|-----|---|------|---|-----|---|-----|---|-----|---|-----|---|------|-------|------|

| ۔<br>ا     | 0   | 1 | DA | 1  | I | DAO | 1 | CA10 | ) | HA3 | 1 | HA2 | 1 | HA1 | 1 | нао | 1 | 2 nd | sense | byte |

| 1          | CA9 | ) | C. | 48 | 1 | SA5 | 1 | SA4  | 1 | SA3 | 1 | SA2 | 1 | SA1 | 1 | SA0 | 1 | 3rd  | sense | byte |

| 1_         | CA7 | 1 | C  | 46 | 1 | CA5 | 1 | CA4  | I | CA3 | 1 | CA2 |   | CA1 | Ι | CA0 | 1 | 4th  | sense | byte |

ECO - EC5: Error code as described in Table 7.

DAO - DA1: Drive address field (0 and 1 Winchester; 2 and 3 floppy)

HAO - HA3: Head address of last operation (if PA=1 in command).\*

SAO - SA5: Sector address of last operation (if PA=1 in command).\*

CAO -CAlO: Cylinder address of last operation (if PA=1 in command).\*

\*If PA=0 in command, a 21-bit logical sector address is returned with byte 2 bit 4 as MS bit and byte 4 bit 0 as LS bit (SA1403D compatible).

Note: The address returned in the sense bytes is valid only after an error condition on a read or a write command. The error code is the last error on the addressed drive. The error code and the address refer to the same error situation only when the drive addressed in the command bytes is the drive which had the most recent read/write error.

III - 28

TABLE 7. FWD5000 ERROR CODES

#### ERROR CODE

- 00 (00 hex) No error occurred.

- 01 (01) No index error -- no index signal detected from drive.

- 02 (02) No seek complete error -- seek did not complete on Winchester.

- 03 (03) Write fault error -- Winchester write fault detected.

- 04 (04) Not ready error -- unit accessed was not ready.

- 06 (06) Track zero error -- no track zero detected on a recalibrate operation.

- 17 (11) Data ECC/CRC error -- a CRC error or a non-correctable ECC error was encountered on data field. (May be correctable ECC error if transfer was direct.)

- 18 (12) No AM's error -- no sector ID address marks of the specified format were found on track.

- 19 (13) No data AM error -- no data AM found on target sector.

- 20 (14) Sector ID error -- target sector was not found due to address mismatch or sector ID CRC error.

- 21 (15) Positioning error -- cylinder address in sector ID did not compare with target cylinder.

- 22 (16) Data overrun error -- host acknowledge occurred late during direct transfer -- transfer stops at error and error reported end of sector.

- 23 (17) Write protected error -- command attempted a write or format operation on a write protected diskette.

- 27 (1B) Deleted data error -- last sector transferred had a deleted data address mark. (The sector transfer is always completed before this error is reported.)

- 28 (1C) Sector length error -- a valid sector ID was found but incorrect sector length was specified in the command bytes.

- 29 (1D) Head select error -- a valid sector ID was found but head address field did not match command bytes.

- 30 (1E) Density error -- a valid sector ID was found on the floppy but incorrect density was specified in the command bytes.

- 31 (1F) Data parity error -- one or more bytes were received with incorrect parity on a write data operation.

3000616/F

## TABLE 7. FWD5000 ERROR CODES (continued)

## ERROR CODE

- 32 (20) Command error -- illegal command format received. May be illegal op code or ECC enabled on direct transfer.

- 33 (21) Logical address error -- illegal logical sector address received on a command using logical addressing.

- 34 (22) Sector address error -- illegal sector address received on a command using physical addressing.

- 35 (23) Head address error -- illegal head address received on a command using physical addressing.

- 36 (24) Cylinder address error -- illegal cylinder address error received on a command using physical addressing.

- 37 (25) Buffer error -- received command requested a buffer operation on a 1K byte sector.

- 39 (27) Disk overrun error -- transfer attempted beyond end of disk.

- 40 (28) Command parity error -- one or more command bytes were received with incorrect parity.

- 49 (31) Drive type error -- W8-W11 are strapped illegally such that the controller cannot determine drive type.

- 50 (32) Illegal state error -- high speed processor in illegal state. Hardware failure.

- 51 (33) Timeout error 1 -- high speed processor did not advance to state 111. Hardware failure.

- 52 (34) Timeout error 2 -- high speed processor did not advance to state OXX. Hardware failure.

- 53 (35) Timeout error 3 -- high speed processor did not advance to state XXO. Hardware failure.

J. STATUS

| - |   | •   |   | 5   |   | •  |   | -  |   | _  | _    |   | -  |    |      |              |      |

|---|---|-----|---|-----|---|----|---|----|---|----|------|---|----|----|------|--------------|------|

| 0 | Γ | DA1 | Τ | DA0 | Ι | 0  | Ι | 0  | Ι | 0  | ER   | Ι | PE |    | 1st  | byte         |      |

|   |   |     |   |     |   |    |   |    |   |    | <br> |   |    | -, | and  |              | •    |

| * |   | то  |   | WP  |   | TS |   | DR |   | RT | EC   | 1 | ND |    | 2 na | (completion) | bvte |

PE: Parity error occurred on a previous transfer. Data parity errors will terminate data transfer to/from the host and will be reported at the completion of the current sector on direct transfers. Transfer will continue to end of sector on buffered transfers.

ER: Fatal error occurred on last operation (or deleted data AM found).

DAO - DA1: Drive address for which the status is valid.

ND: This command was the first after insertion of a new diskette into the floppy. A recalibration was performed automatically on receipt of the previous command. Note: The ND bit is undefined if Tandon TM848 floppy drives are used.

EC: Error correction was performed on transfer -- not a fatal error.

RT: Retries were performed on transfer -- not a fatal error.

- DR: Drive is ready if DR is set.

- TS: Two sided diskette is installed if TS is set.

- WP: Write protected diskette is installed if WP is set.

- TO: Drive is positioned at track zero if TO is set.

- \*: Undefined state

Two bytes of status are returned by the controller at the completion of each command. If the command were terminated by an error condition an error bit in the first byte would be set. If the command completed successfully, the error bits would be zero. The second byte contains drive status information for the drive addressed by the terminating command.

If the error bit is set in the first byte, operation information may be obtained by issuing the SENSE command as previously described. Note however that the SENSE command must be issued before an operation is begun on another drive. The information returned by the SENSE command is valid only for the last operation even though the two status bytes are always valid for the addressed drive. For example, if an error occurred on drive 1, then a write was performed on drive 2, and then a SENSE command was issued to drive 1, the three bytes of address returned by the SENSE command would apply to the write operation on drive 2 (error code status byte applies to addressed drive) and the two status bytes returned at the completion of the SENSE command would apply to drive 1.

The controller notifies the host that status is available by asserting CON and OUT as described in the protocol section. The status bytes are transferred as described in the protocol section.

## IV. HOST INTERFACE PROTOCOL

The following section describes the protocol used to transfer commands, data and status between the host and the controller. All commands, data and status are transferred on an 8-bit bidirectional data bus. The controller will generate and check odd parity on this bus if parity is enabled (i.e. W2 is installed).

The host sources three control signals to the controller. The first line is RST. Assertion of this line will force the controller to terminate any current operation and to become ready to accept a command. The second line is SEL. Assertion of this line indicates that the host is prepared to transfer a command to the controller. The third line is ACK. Assertion of this line indicates that the host has accepted the data from the data bus or that the host has placed data on the data bus for transfer to the controller.

The controller sources five state signals to the host. The first line is BSY. Assertion by the controller indicates that an operation is in progress and the controller is not ready to accept a new command. The second line is CON. Assertion by the controller indicates that a command byte or status byte is being transferred on the bus. The third line is OUT. Assertion by the controller indicates that the current transfer is from controller to host. The fourth line is REQ. Assertion by the controller indicates that the controller has accepted the data from the data bus or that the controller has placed data on the data bus for transfer to the host. The last state signal is MSG. Assertion by the controller indicates that the final status byte is to be transferred on the data bus.

### A. COMMAND TRANSFER

All disk controller activity is initiated by the host system via commands. Each of the commands requires a transfer of six bytes from the host to the controller. The content of these bytes and the controller response was discussed in the preceding section.

The host system may request a disk operation by initiating a command transfer. The protocol is shown in Figure 1. The host may initiate command sequences whenever the controller has not asserted the BSY signal. (Note that whenever the controller is not busy, OUT will be deasserted.) The sequence is begun by asserting DO and then asserting the SEL signal. The controller will then assert BSY and the host must then deassert SEL. The FWD5000 will indicate that it is ready to transfer the first byte by asserting the CON and the REQ signals. The host should then place the first command byte on the data port and assert ACK. The command byte should remain stable until the controller deasserts REQ. When the FWD5000 is ready to receive the next byte, it asserts REQ again. The host should place the next command byte on the data port and assert ACK. This procedure should be repeated until six bytes have been transferred. The CON line will remain asserted and OUT will remain deasserted until all command bytes have been passed.

Note that in all cases the command byte must be stable by 400ns after the host asserts ACK and remain stable until REQ is deasserted by the controller. This means that the host may assert ACK prior to placing the byte on the port as long as the byte becomes stable within 400ns. This feature greatly simplifies the hardware required to interface to the controller. After the last command byte has been transferred, the controller will prepare for either a status or a data transfer. In the case of a WRITE command, OUT will remain deasserted. OUT will be asserted for all other commands. In all cases, OUT will be stable before CON is deasserted to insure that no hazards exist in the host logic. Even if an error was detected during the command transfer or if no data transfer is required, CON will be deasserted for lus (min) and then reasserted to indicate that status is available.

Figure 1. Command Transfer Timing

## 3000616/F

## B. DATA TRANSFER

A data byte transfer request (read or write) is indicated when the controller asserts REQ. The host system, in turn, acknowledges the data byte transfer request by reading/writing the data byte and asserting ACK. When writing to the controller, the byte and parity must be stable 400ns after asserting ACK. When reading, the byte and parity will be stable 350ns before the controller asserts REQ. This is true for buffered and unbuffered transfers.

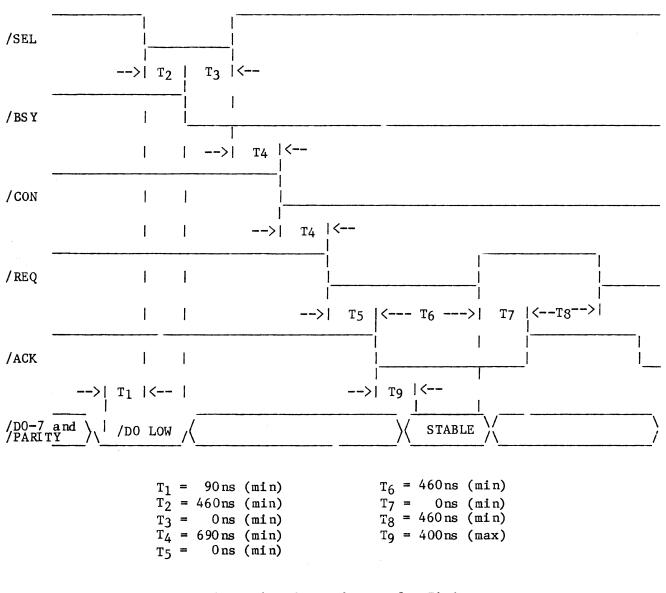

### Buffered Data Transfers

Figure 2 shows the timing for both buffered reading and buffered writing by the host system. In this mode, the controller asserts the REQ signal after placing a data byte on the DATA port (buffered read) or when it is waiting for a new byte from the host (buffered write). When the host acknowledges the data transfer by accepting/sourcing the data and asserting ACK, the controller continues. There are no timing constraints placed on the user's response.

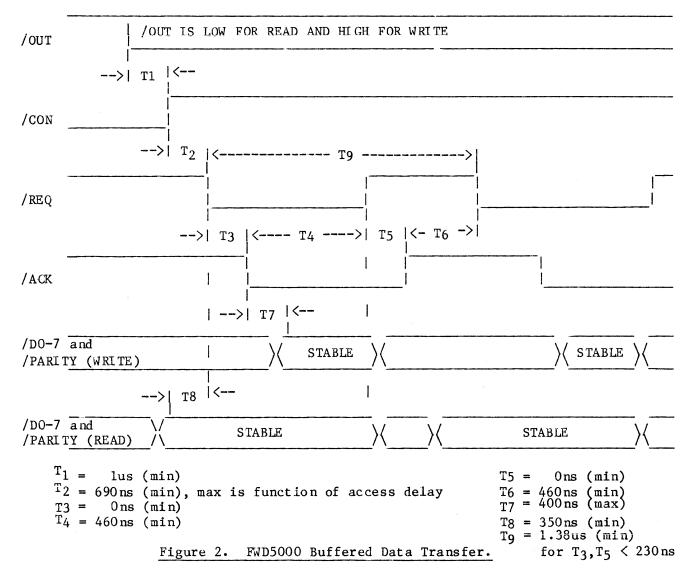

Figure 3 shows the timing for buffered reading and buffered writing when the fast handshake is enabled (FH bit set in command byte). Note that the host memory access is performed during T3 between the assertion of REQ by the controller and the assertion of ACK by the host. With the SA1403D compatible handshake shown in Figure 2, the amount of time allowed for the user memory access is:

$$T_{access (max)} = (N \times 230 ns) - 1.38 us + 230 ns$$

where N x 230 is the desired cycle time to read or write one byte. For a single sector interleave on the Winchester, a cycle time of 1.84us (N=8) is required (must empty the buffer in a sector time). Therefore the memory access must be performed in about 690ns maximum. With the SMS fast handshake shown in Figure 3, the amount of time allowed for the user memory access is:

which means that a single sector interleave on the Winchester may be achieved with a host memory access time of 1.15us.

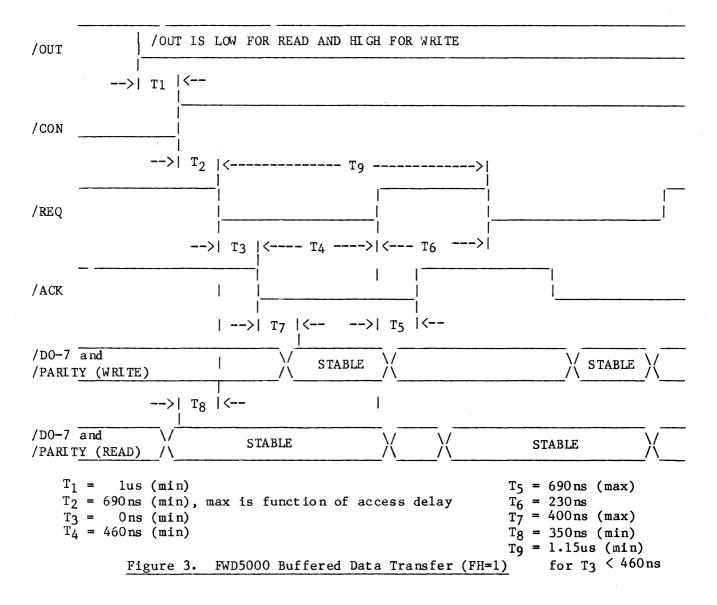

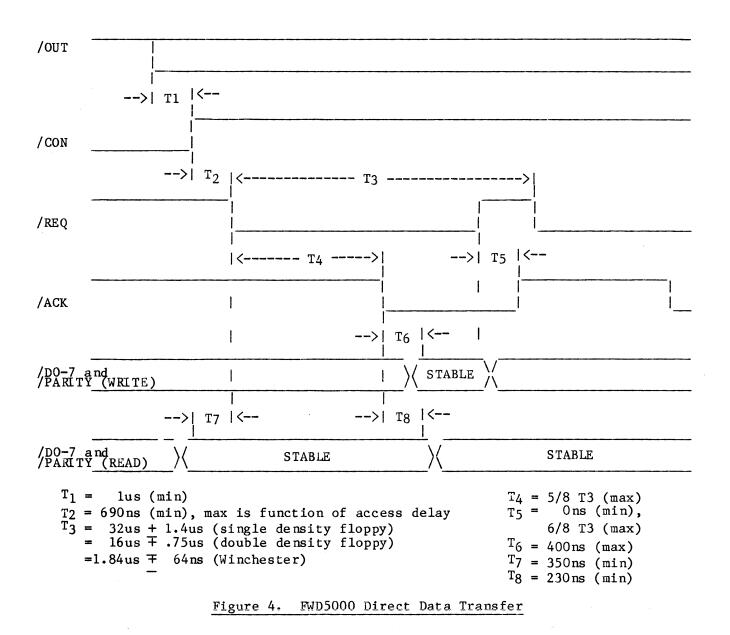

### Direct Data Transfers

Figure 4 illustrates direct read/write data transfer. During a floppy read/write operation, REQ is asserted every  $32 \pm 1.4$ usec in single density and every  $16 \pm .75$  usec in double density to indicate data is available on the DATA port (read) or data is requested from the host (write). The host acknowledges the data transfer request by asserting ACK. If the host fails to acknowledge a data transfer within 20 usec (nominal) for single density or within 10 usec (nominal) for double density, the read/write operation is aborted and a data overrun error generated. REQ is asserted every 1.84usec  $\pm$  64ns during a read/write Winchester operation and the host must acknowledge the transfer within 1.15us (nominal).

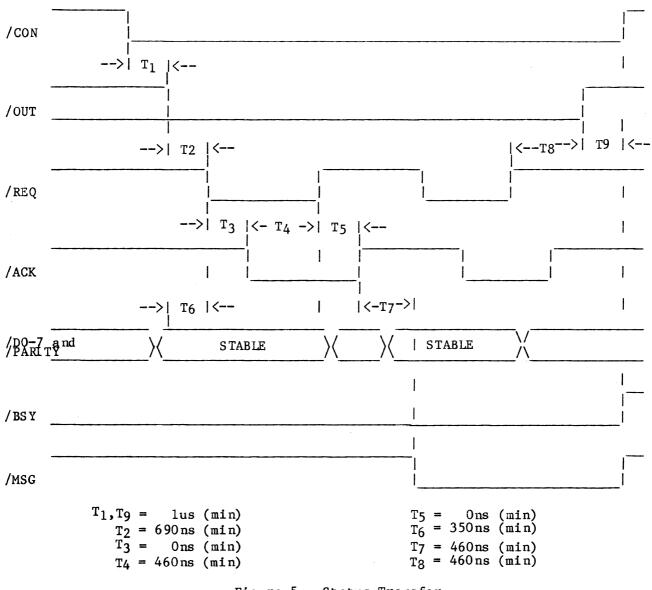

### C. STATUS TRANSFER

Status is presented as two bytes which are made available at completion of all commands. Status is available when the controller asserts CON and OUT. The first byte indicates if an error occurred on the last command. The second byte contains drive status information. The first status byte is placed on the data port by the FWD5000 and REQ is asserted. When the host has read the byte from the data port, it asserts ACK. The FWD5000 then asserts REQ again to indicate the second byte is ready. It then waits for the host to assert ACK after it has read the byte. The controller then deasserts REQ, deasserts CON, deasserts OUT, deasserts BSY, and becomes ready to accept a new command. In all cases the status byte and parity will be stable 350ns before REQ is asserted.

Figure 5. Status Transfer

## 3000616/F

## D. INTERFACE INITIALIZATION

The controller may be reset from any state when power is applied or the FWD5000 RST is asserted. The RST is asserted by pulling the /RST line to a low level for 1 usec (min) and then returning the line to a high level. The controller performs a self test sequence (if W4 and W5 are installed) and becomes ready to accept a new command. During the self test the /BSY line will be deasserted. However, if /SEL is asserted by the host during self test, the controller will assert /BSY, /CON, and /REQ only after self test completes. The self test requires less than 500ms to complete.

### E. PROTOCOL FEATURES